Philips 74ABT651N, 74ABT651DB, 74ABT651D Datasheet

Philips Semiconductors Product specification

74ABT651Octal transceiver/register, inverting (3-State)

FEA TURES

•Independent registers for A and B buses

•The 74ABT651 is the inverting version of the 74ABT652

•Multiplexed real-time and stored data

•3-State outputs

•Live insertion/extraction permitted.

•Power-up 3-State

•Power-up reset

•Output capability: +64mA/–32mA

•Latch-up protection exceeds 500mA per Jedec Std 17

•ESD protection exceeds 2000 V per MIL STD 883 Method 3015

and 200 V per Machine Model

QUICK REFERENCE DATA

SYMBOL PARAMETER

t

PLH

t

PHL

C

C

I

CCZ

IN

I/O

Propagation delay

CPBA to An or CPAB to Bn

Input capacitance VI = 0V or V

I/O capacitance Outputs disabled; VO = 0V or V

Total supply current Outputs disabled; VCC =5.5V 110 µA

DESCRIPTION

The 74ABT651 high-performance BiCMOS device combines low

static and dynamic power dissipation with high speed and high

output drive.

The 74ABT651 transceiver/register consists of bus transceiver

circuits with 3-State outputs, D-type flip-flops, and control circuitry

arranged for multiplexed transmission of data directly from the input

bus or the internal registers. Data on the A or B bus will be clocked

into the registers as the appropriate clock pin goes High. Output

Enable (OEAB, OEBA

bus management.

The following examples demonstrate the four fundamental

bus-management functions that can be performed with the

74ABT651.

The select pins determine whether data is stored or transferred

through the device in real time.

The output enable pins determine the direction of the data flow.

CONDITIONS

= 25°C; GND = 0V

T

amb

CL = 50pF; VCC = 5V

CC

) and Select (SAB, SBA) pins are provided for

TYPICAL UNIT

3.8

4.4

4 pF

CC

7 pF

ns

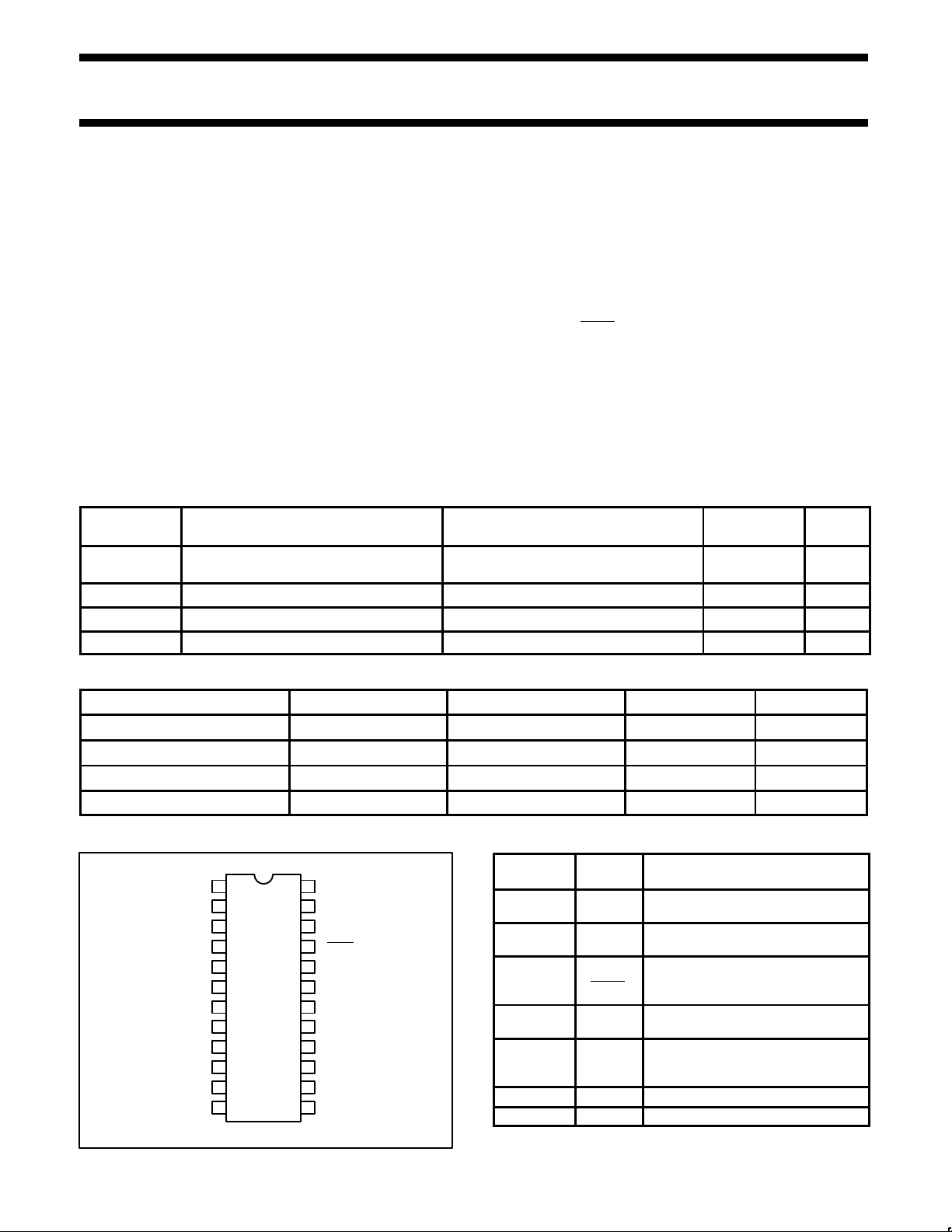

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

24-Pin Plastic DIP –40°C to +85°C 74ABT651 N 74ABT651 N SOT222-1

24-Pin plastic SO –40°C to +85°C 74ABT651 D 74ABT651 D SOT137-1

24-Pin Plastic SSOP Type II –40°C to +85°C 74ABT651 DB 74ABT651 DB SOT340-1

24-Pin Plastic TSSOP Type I –40°C to +85°C 74ABT651 PW 74ABT651PW DH SOT355-1

PIN CONFIGURA TION

1

CPAB

2

SAB

3

OEAB

4

A0

5

A1

6

A2

7

A3

8

A4

9

A5

10

A6

11

A7

12

GND

V

24

CC

CPBA

23

SBA

22

OEBA

21

B0

20

B1

19

B2

18

B3

17

B4

16

B5

15

B6

14

B713

SA00094

PIN DESCRIPTION

PIN

NUMBER

1, 23

2, 22

3, 21

4, 5, 6, 7, 8,

9, 10, 11

20, 19, 18,

17, 16, 15,

14, 13

12 GND Ground (0V)

24 V

SYMBOL FUNCTION

CPAB /

CPBA

SAB /

SBA

OEAB /

OEBA

A0 – A7 Data inputs/outputs (A side)

B0 – B7 Data inputs/outputs (B side)

CC

A to B clock input / B to A clock input

A to B select input / B to A select input

A to B Output Enable input /

B to A Output Enable input

(active–Low)

Positive supply voltage

1995 Sep 06 853-1783 15703

1

Philips Semiconductors Product specification

74ABT651Octal transceiver/register, inverting (3-State)

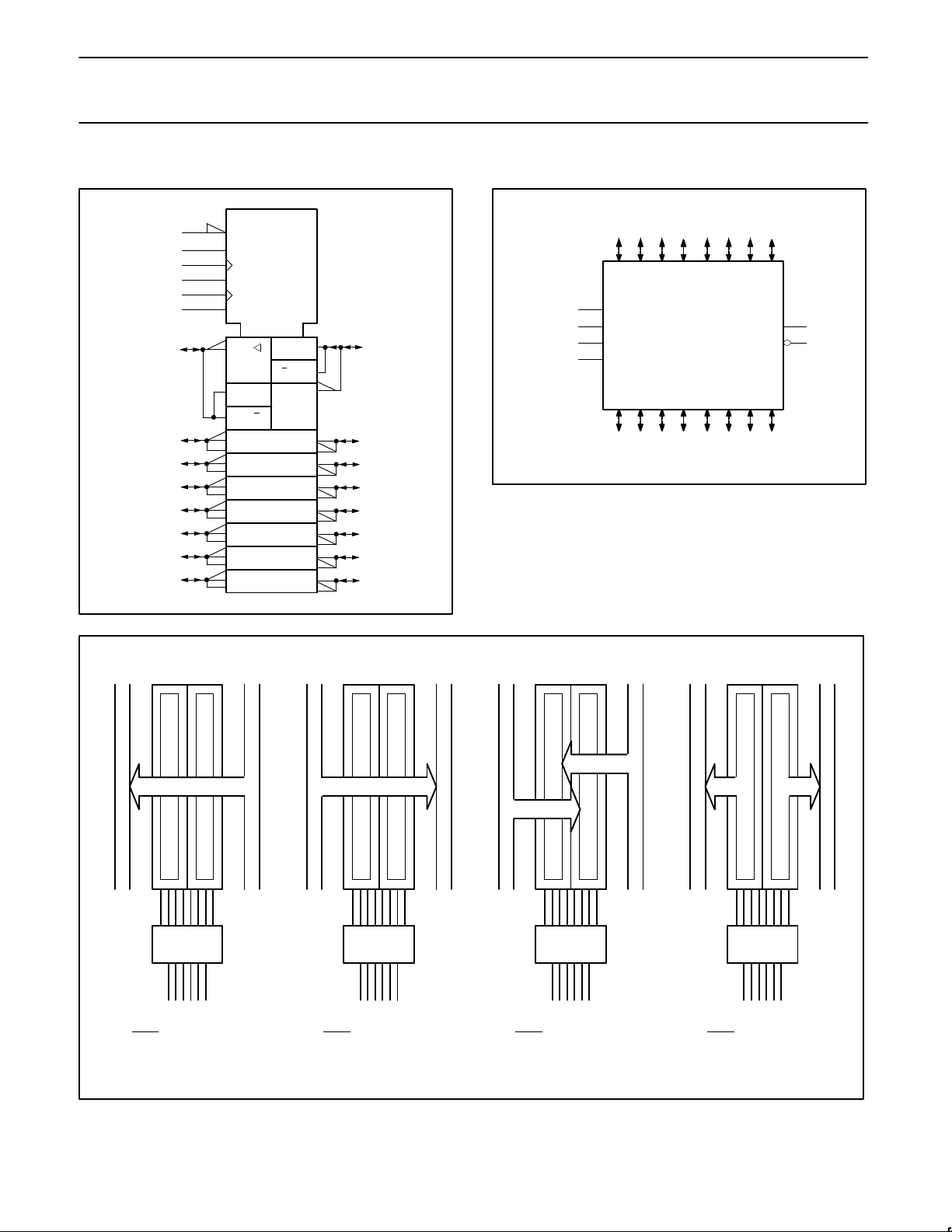

LOGIC SYMBOL (IEEE/IEC)

21

3

23

22

1

2

4

5

6

7

8

9

10

11

EN1 [BA]

EN2 [AB]

C4

G5

C6

G7

1

1

6D 7

17

54D

5

1

1

2

LOGIC SYMBOL

4567 891011

A0 A1 A2 A3 A4 A5 A6 A7

23 CPBA

22 SBA

20

19

18

17

16

15

14

13

SA00125

SAB2

CPAB1

B0 B1 B2 B3 B4 B5 B6 B7

20 19 18 17 16 15 14 13

3OEAB

21OEBA

SA00095

REAL TIME BUS TRANSFER

BUS B TO BUS A

REAL TIME BUS TRANSFER

BUS A TO BUS B

STORAGE FROM

A, B, OR A AND B

TRANSFER STORED DATA

TO A OR B

ABABABAB

}

OEABOEBA

CPABCPBA SAB SBA

LLXXXL

OEABOEBA

HHXXLX

}

CPABCPBA SAB SBA

}

OEABOEBA

CPABCPBA SAB SBA

XH↑XXX

LXX↑XX

LH↑↑XX

}

OEABOEBA

CPABCPBA SAB SBA

H L H | L H | L H H

SA00097

1995 Sep 06

2

Philips Semiconductors Product specification

OPERATING MODE

74ABT651Octal transceiver/register, inverting (3-State)

FUNCTION TABLE

INPUTS DATA I/O

OEAB OEBA CPAB CPBA SAB SBA An Bn

L

L

X

H

L

L

L

L

H

H

H L H or L H or L H H Output Output

H = High voltage level

L = Low voltage level

X = Don’t care

↑ = Low-to-High clock transition

* The data output function may be enabled or disabled by various signals at the OEBA

enabled, i.e., data at the bus pins will be stored on every Low-to-High transition of the clock.

** If both Select controls (SAB and SBA) are Low, then clocks can occur simultaneously. If either Select control is High, the clocks must be

staggered in order to load both registers.

H

H

H

H

X

L

L

L

H

H

H or L

↑

↑

↑

H or L

↑

X

X

X

H or L

H or L

↑

H or L

↑

↑

↑

X

H or L

X

X

X

X

X

**

X

X

X

X

L

H

X

X

X

X

Input Input

Input

X**Unspecified

output*

L

H

X

X

Output Input

Input Output

Unspecified

output*

Input

Isolation

Store A and B data

Store A, Hold B

Store A in both registers

Hold A, Store B

Store B in both registers

Real time B data to A bus

Stored B

data to A bus

Real time A data to B bus

data to B bus

Store A

Stored A data to B bus

Stored B

data to A bus

and OEAB inputs. Data input functions are always

LOGIC DIAGRAM

OEBA

OEAB

CPBA

SBA

CPAB

SAB

A0

A1

A2

A3

A4

A5

A6

A7

21

3

23

22

1

2

1of 8 Channels

4

1D

C1

Q

5

6

7

8

9

10

11

DETAIL A X 7

1D

C1

Q

20

B0

19

B1

18

B2

17

B3

16

B4

15

B5

14

B6

13

B7

1995 Sep 06

SA00098

3

Loading...

Loading...