Philips 74ABT161543 Technical data

查询74ABT161543供应商

INTEGRATED CIRCUITS

74ABT161543

74ABTH161543

16-bit latched transceiver with

dual enable and master reset (3-State)

Product specification

Supersedes data of 1995 Sep 18

IC23 Data Handbook

1998 Feb 27

Philips Semiconductors Product specification

Quiescent su ly current

16-bit latched transceiver with dual enable

and master reset (3-State)

FEA TURES

•Two 8-bit octal transceivers with D-type latch

•Live insertion/extraction permitted

•Power-up 3-State

•Power-up reset

•Multiple V

•Back-to-back registers for storage

•Separate controls for data flow in each direction

•74ABTH161543 incorporates Bus hold data inputs which eliminate

the need for external pull-up resistors to hold unused inputs

•Output capability: +64mA/–32mA

•Latch-up protection exceeds 500mA per Jedec Std 17

and GND pins minimize switching noise

CC

DESCRIPTION

The 74ABT161543 high-performance BiCMOS device combines low

static and dynamic power dissipation with high speed and high

output drive.

The 74ABT161543 16-bit registered transceiver contains two sets

of D-type latches for temporary storage of data flowing in either

direction. Separate Latch Enable (nLEAB

Enable (nOEAB

permit independent control of data transfer in either direction. Master

reset (MR

The outputs are guaranteed to sink 64mA.

Two options are available, 74ABT161543 which does not have the

Bus hold feature and 74ABTH161543 which inorporates the Bus

hold feature.

, nOEBA) inputs are provided for each register to

) clears all registers simultaneously and sets them Low.

74ABT161543

74ABTH161543

•ESD protection exceeds 2000V per MIL STD 883 Method 3015

and 200V per Machine Model

•Same function as ABT16543 except for additional Master Reset

control pins

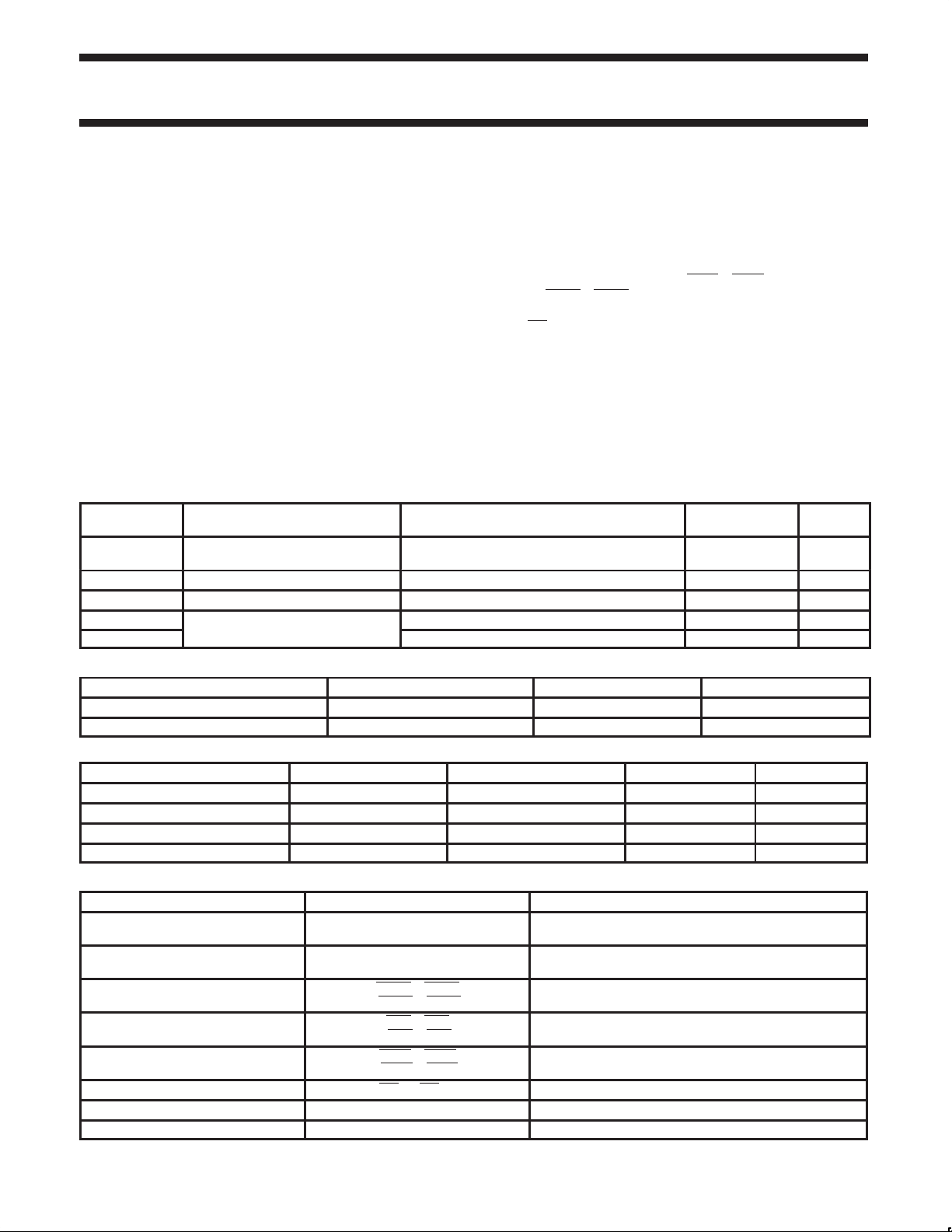

QUICK REFERENCE DATA

SYMBOL PARAMETER

t

PLH

t

PHL

C

C

I

CCZ

I

CCL

IN

I/O

Propagation delay

nAx to nBx

Input capacitance VI = 0V or V

I/O capacitance VO = 0V or V

pp

CL = 50pF; VCC = 5V

Outputs disabled; VCC = 5.5V 500 µA

Outputs low; V

ORDERING INFORMATION

PACKAGES TEMPERATURE RANGE ORDER CODE DRAWING NUMBER

56-pin plastic SSOP Type III –40°C to +85°C BT161543DL SOT371-1

56-pin plastic TSSOP Type II –40°C to +85°C BT161543DGG SOT364-1

CONDITIONS

T

= 25°C; GND = 0V

amb

CC

3-State 7 pF

CC;

= 5.5V 9 mA

CC

TYPICAL UNIT

, nLEBA) and Output

2.5

2.2

3 pF

ns

ORDERING INFORMATION

56-Pin Plastic SSOP Type III –40°C to +85°C 74ABT161543 DL BT161543 DL SOT371-1

56-Pin Plastic TSSOP Type II –40°C to +85°C 74ABT161543 DGG BT161543 DGG SOT364-1

56-Pin Plastic SSOP Type III –40°C to +85°C 74ABTH161543 DL BH161543 DL SOT371-1

56-Pin Plastic TSSOP Type II –40°C to +85°C 74ABTH161543 DGG BH161543 DGG SOT364-1

PIN DESCRIPTION

5, 6, 8, 9, 10, 12, 13, 14

15, 16, 17, 19, 20, 21, 23, 24

52, 51, 49, 48, 47, 45, 44, 43

42, 41, 40,38, 37, 36, 34, 33

1998 Feb 27 853-1798 19026

PACKAGES TEMPERATURE RANGE OUTSIDE NORTH AMERICA NORTH AMERICA DWG NUMBER

PIN NUMBER SYMBOL NAME AND FUNCTION

1A0 – 1A7,

2A0 – 2A7

1B0 – 1B7,

2B0 – 2B7

1, 56

28, 29

3, 54

26, 31

2, 55

27, 30

4, 25 MRab, MRba Master reset

11, 18, 32, 39, 46, 53 GND Ground (0V)

7, 22, 35, 50 V

1OEAB, 1OEBA,

2OEAB, 2OEBA

1EAB, 1EBA,

2EAB, 2EBA

1LEAB, 1LEBA,

2LEAB, 2LEBA

CC

2

Data inputs/outputs

Data inputs/outputs

A to B / B to A Output Enable inputs (active-Low)

A to B / B to A Enable inputs (active-Low)

A to B / B to A Latch Enable inputs (active-Low)

Positive supply voltage

Philips Semiconductors Product specification

16-bit latched transceiver with dual enable

and master reset (3-State)

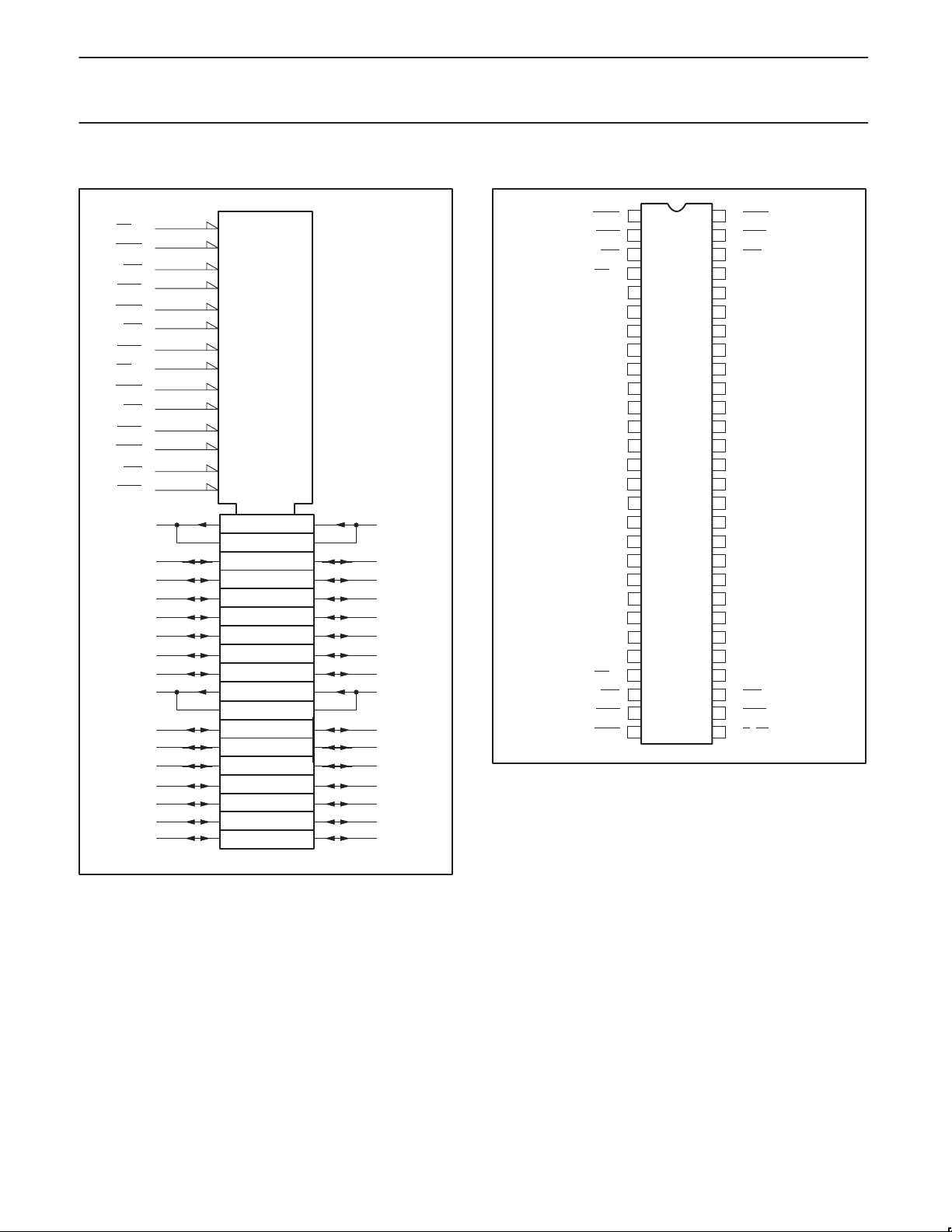

LOGIC SYMBOL (IEEE/IEC)

4

MR

1OEAB

1EAB

1LEAB

2OEAB

2EAB

2LEAB

MRba

1OEBA

1EBA

1LEBA

2OEBA

2EBA

2LEBA

1A0

1A1

1A2

1A3

1A4

1A5

1A6

1A7

2A0

2A1

2A2

2A3

2A4

2A5

2A6

2A7

ab

1

3

2

28

26

27

25

56

54

55

29

31

30

5

6

8

9

10

12

13

14

15

16

17

19

20

21

23

24

R6/R12

2EN4

G2

2C6

8EN10

G8

8C12

R5/R11

1EN3

G1

1C5

7EN9

G7

7C11

∇3

6D 4 ∇

∇911D

12D

5D

10 ∇

52

1B0

51

1B1

49

1B2

48

1B3

47

1B4

45

1B5

44

1B6

43

1B7

42

2B0

41

2B1

40

2B2

38

2B3

37

2B4

36

2B5

34

2B6

33

2B7

PIN CONFIGURA TION

1

1OEAB

2

1LEAB

1EAB

3

4

MRab

5

1A0

6

1A1

7

V

CC

8

1A2

9

1A3

10

1A4

11

GND

12

1A5

13

1A6

14

1A7

15

2A0

16

2A1

17

2A2

18

GND

19

2A3

20

2A4

21

2A5

22

V

CC

23

2A6

24

2A7

MRba

25

26

2EAB

27

2LEAB

28

2OEAB

74ABT161543

74ABTH161543

56

1OEBA

55

1LEBA

1EBA

54

53

GND

52

1B0

51

1B1

50

V

CC

49

1B2

48

1B3

47

1B4

46

GND

45

1B5

44

1B6

43

1B7

42

2B0

41

2B1

40

2B2

39

GND

38

2B3

37

2B4

2B5

36

35

V

CC

34

2B6

33

2B7

32

GND

31

2EBA

30

2LEBA

29

2OEBA

SH00061

1998 Feb 27

SH00060

3

Philips Semiconductors Product specification

STATUS

16-bit latched transceiver with dual enable

and master reset (3-State)

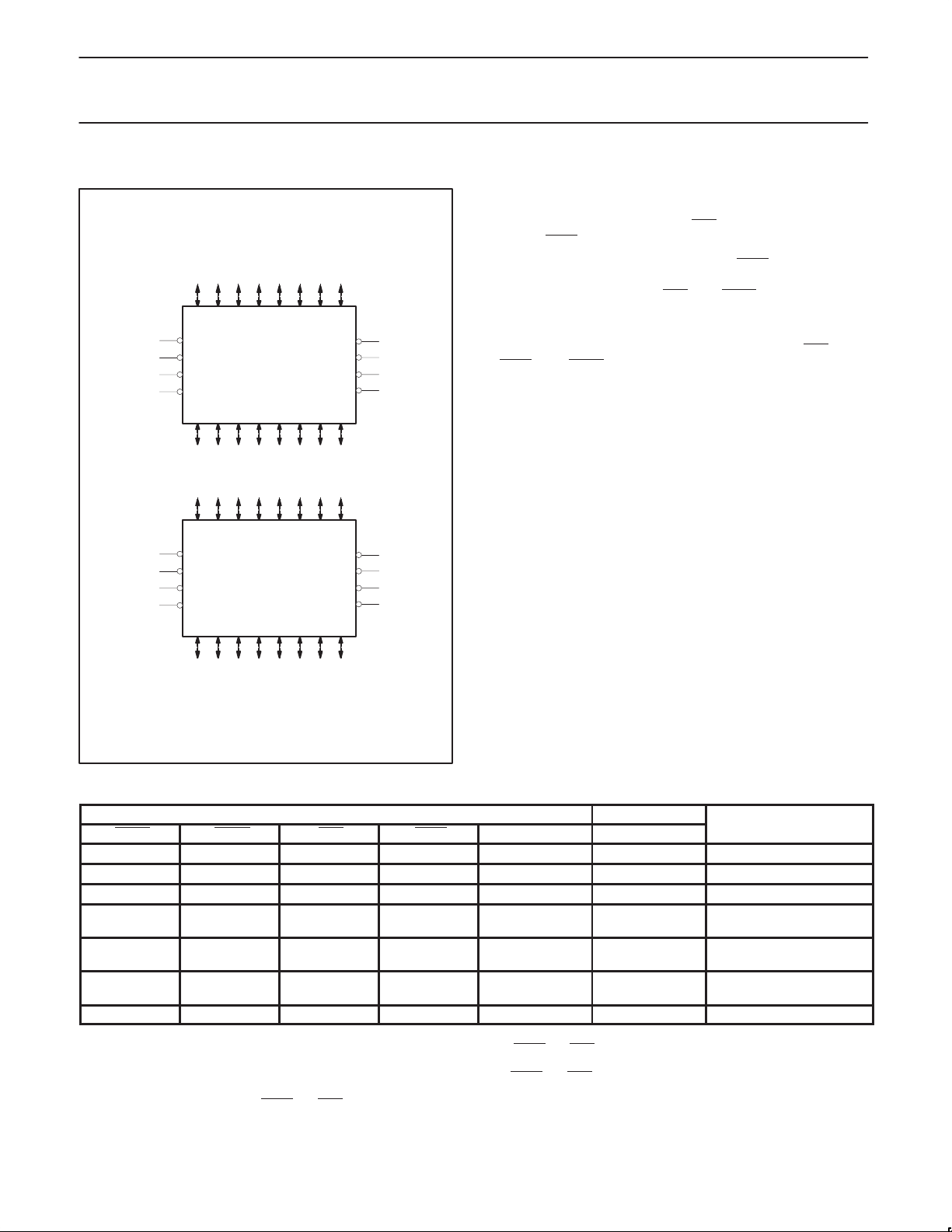

LOGIC SYMBOL

5 6 10 12 13 1489

1A0 1A1 1A2 1A3 1A4 1A5 1A6 1A7

3

1EAB

54

1EBA

2 1LEAB

55 1LEBA

1B0 1B1 1B2 1B3 1B4 1B5 1B6 1B7

52 51 47 45 44 4349 48

15 16 20 21 23 2417 19

2A0 2A1 2A2 2A3 2A4 2A5 2A6 2A7

26

2EAB

31

2EBA

27 2LEAB

30 2LEBA

2B0 2B1 2B2 2B3 2B4 2B5 2B6 2B7

4MRab

11OEAB

561OEBA

25MRba

4MRab

282OEAB

292OEBA

25MRba

74ABT161543

74ABTH161543

FUNCTIONAL DESCRIPTION

The 74ABT161543 contains two sets of eight D-type latches, with

separate control pins for each set. Using data flow from A to B as an

example, when the A-to-B Enable (nEAB

Enable (nLEAB

) input are Low the A-to-B path is transparent.

A subsequent Low-to-High transition of the nLEAB signal puts the A

data into the latches where it is stored and the B outputs no longer

change with the A inputs. With EAB

3-State B output buffers are active and display the data present at

the outputs of the A latches.

Control of data flow from B to A is similar, but using the nEBA

nLEBA

, and nOEBA inputs.

) input and the A-to-B Latch

and nOEAB both Low, the

,

42 41 37 36 34 3340 38

SH00064

FUNCTION TABLE

INPUTS OUTPUTS

nOEXX nMRXX nEXX nLEXX nAx or nBx nBx or nAx

L L L X X L Clear

H X X X X Z Disabled

X X H X X Z Disabled

L

L

L

L

L

L

L H L H X NC Hold

H = High voltage level

h = High voltage level one set-up time prior to the Low-to-High transition of nLEXX

L = Low voltage level

l = Low voltage level one set-up time prior to the Low-to-High transition of nLEXX

X = Don’t care

↑ = Low-to-High transition of nLEXX

NC= No change

Z = High impedance or “off” state

H

H

H

H

H

H

↑

↑

L

L

L

L

L

L

↑

↑

L

L

h

l

h

l

H

L

Z

Z

H

L

H

L

or nEXX (XX = AB or BA)

or nEXX (XX = AB or BA)

or nEXX (XX = AB or BA)

Disabled + Latch

Latch + Display

Transparent

1998 Feb 27

4

Loading...

Loading...