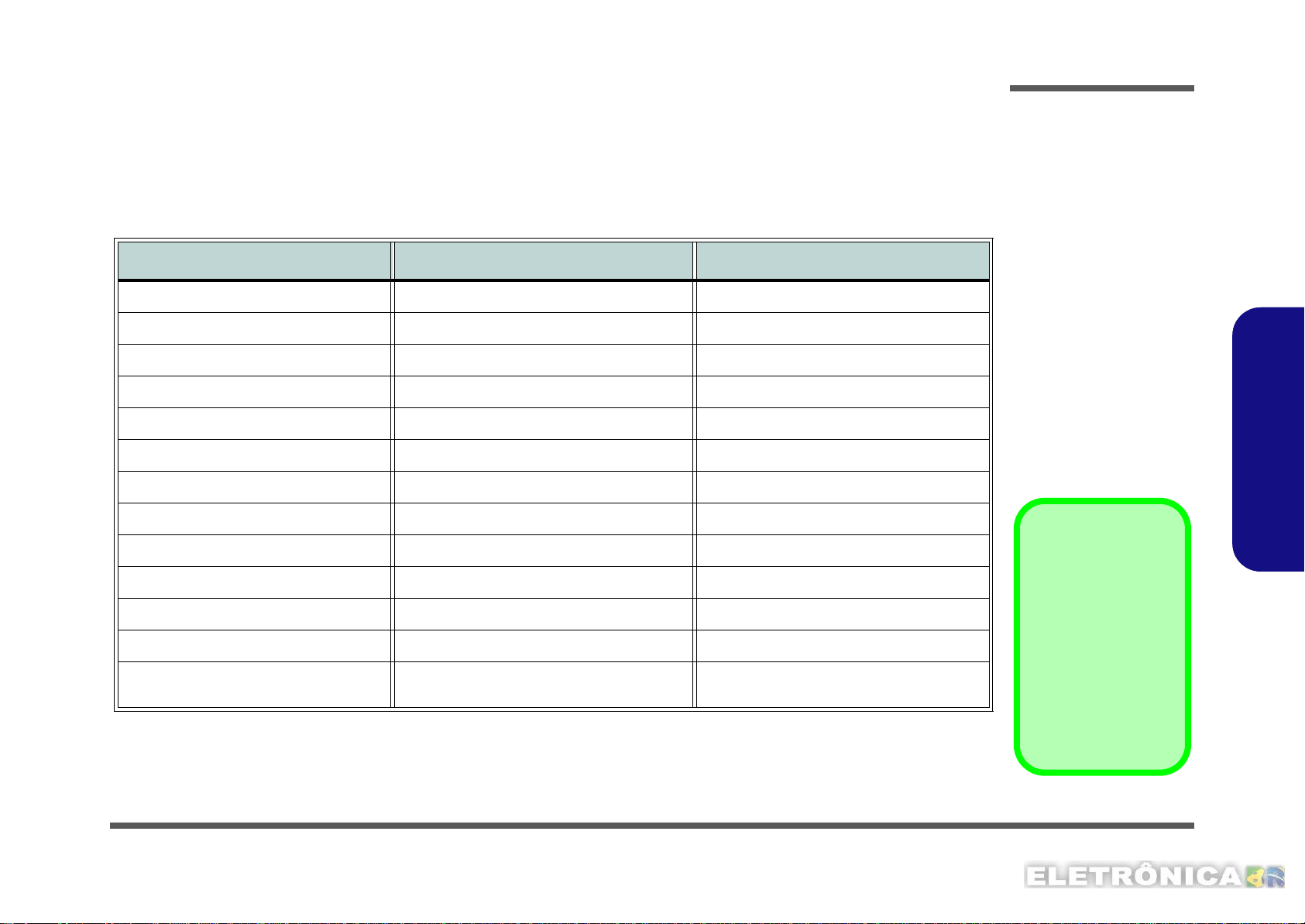

Appendix B:Schematic Diagrams

Table B - 1

Schematic

Diagrams

Version Note

The schematic diagrams in this chapter

are based upon version 6-7P-C5505-002.

If your mainboard (or

other boards) are a later version, please

check with the Service

Center for updated diagrams (if required).

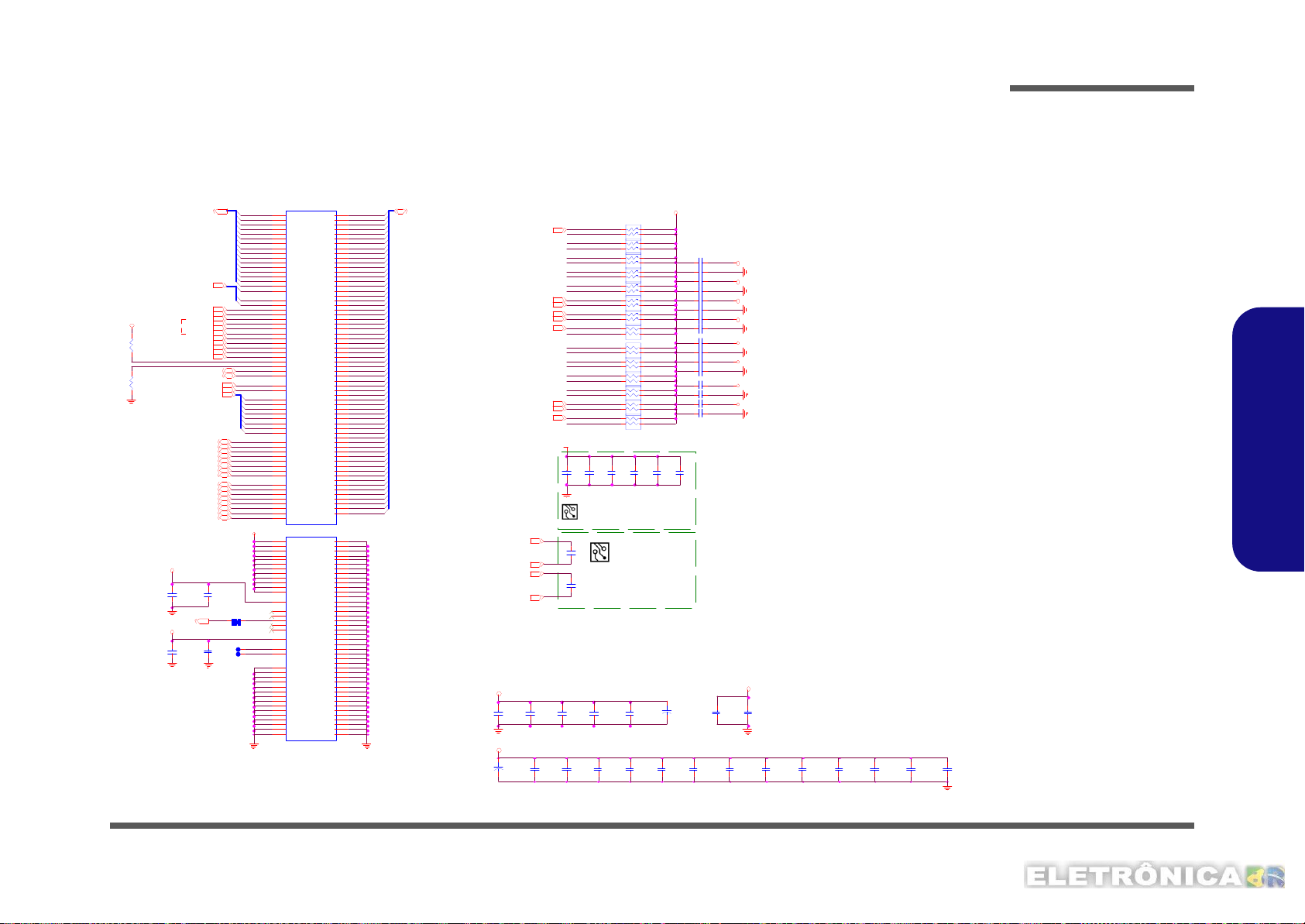

This appendix has circuit diagrams of the C5505/C5505Q/C5505C/C5505Q-C notebook’s PCB’s. The following table

indicates where to find the appropriate schematic diagram.

Diagram - Page Diagram - Page Diagram - Page

System Block Diagram - Page B - 2 SB700-1 - Page B - 15 VCORE_Core - Page B - 28

Clock Generator - Page B - 3 SB700-2 - Page B - 16 0.9V, 1.8V, 1.8VS, 1.5VS - Page B - 29

CPU-1 - Page B - 4 SB700-3 - Page B - 17 1.1VS, 1.2V, 1.2VS - Page B - 30

CPU-2 - Page B - 5 SB700-4 - Page B - 18 VDD3, VDD5 - Page B - 31

CPU-3 - Page B - 6 New Card, Mini PCIE - Page B - 19 Charger, DC In - Page B - 32

CPU-4 - Page B - 7 CCD, 3G, SATA ODD - Page B - 20 Click Board - Page B - 33

DDRII SO-DIMM_0 - Page B - 8 USB, Fan, TP, Multi-Con - Page B - 21 Audio Board/USB - Page B - 34

DDRII SO-DIMM_1 - Page B - 9 Card Reader/LAN JMC261 - Page B - 22 Power Switch Board - Page B - 35

Schematic Diagrams

B.Schematic Diagrams

RS780M-1 - Page B - 10 SATA HDD, LED, MDC, BT - Page B - 23 External ODD Board - Page B - 36

RS780M-2 - Page B - 11 Audio Codec ALC272 - Page B - 24

RS780M-3 - Page B - 12 KBC ITE IT8502E - Page B - 25

LVDS, Inverter - Page B - 13 System PWR, 2.5V - Page B - 26

HDMI, CRT - Page B - 14

PWRGD, RST - Page B - 27

B-1

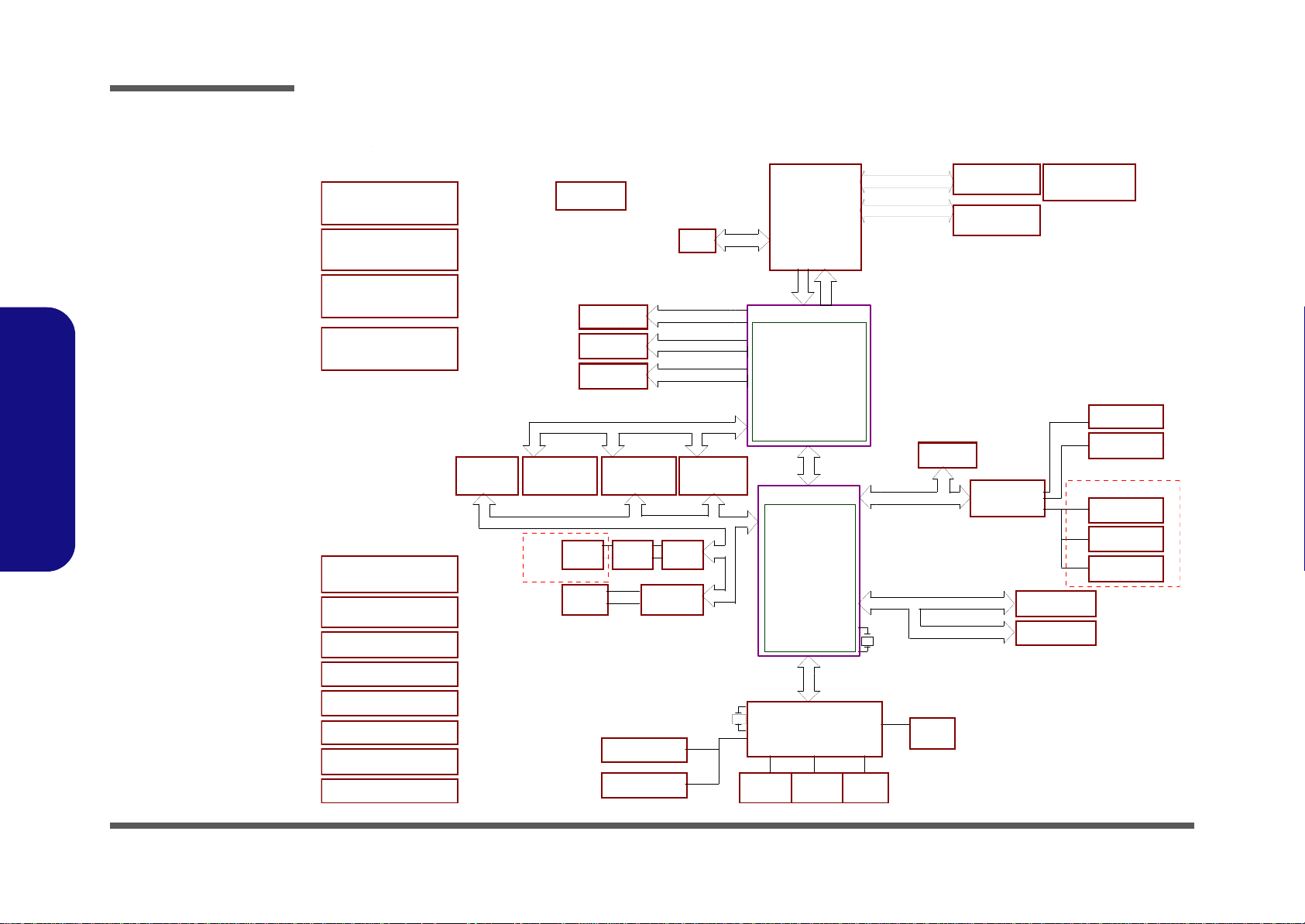

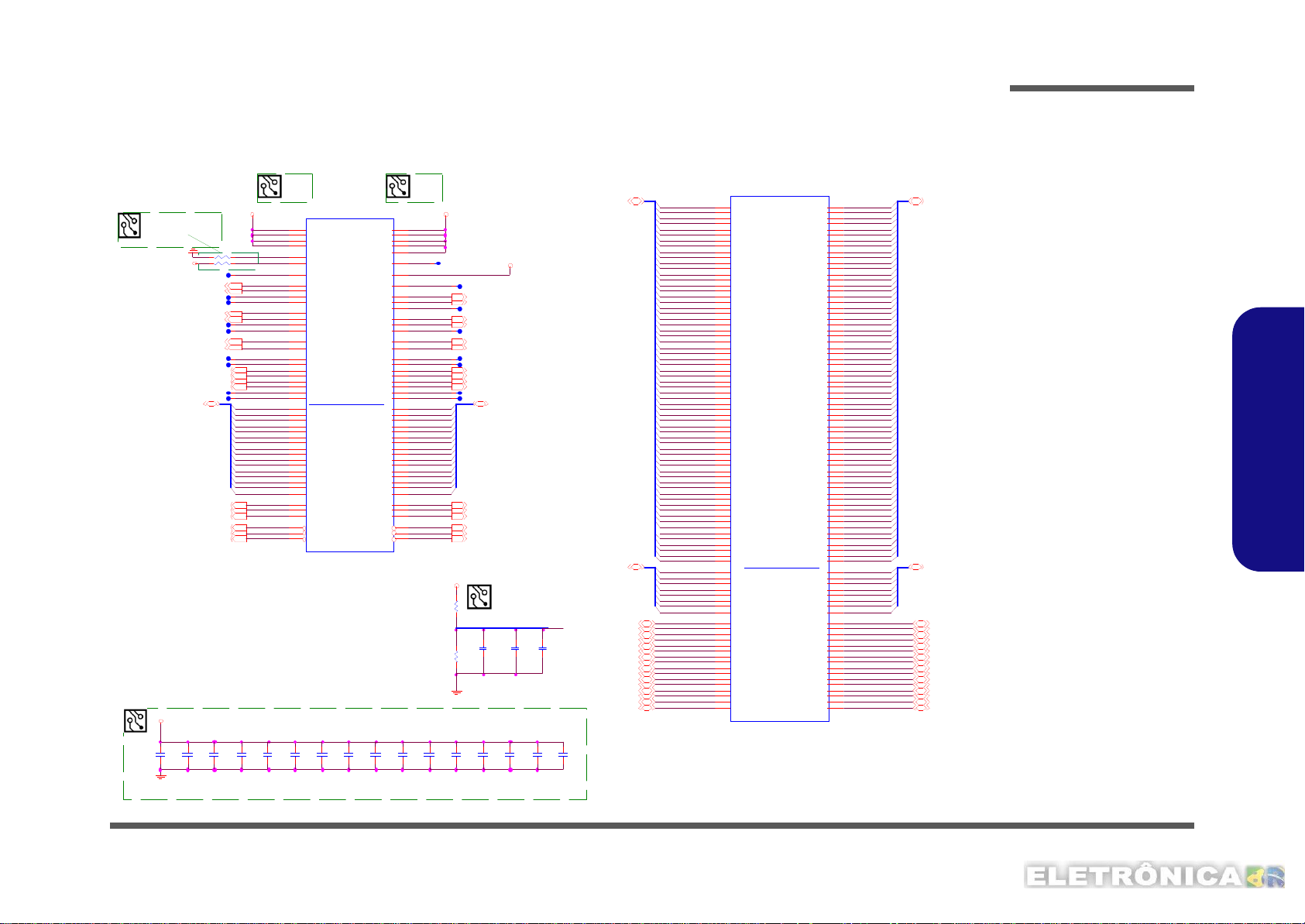

Schematic Diagrams

Sheet 1 of 35

System Block

Diagram

AUDIO BOARD

6- 71 -E51 QN- D01

EXTERNAL O DD B OA RD

VC ORE_VD D_NB

B ATTERY CH AG ER

Port 1

SPI ROM

POWER SWITCH BO ARD

AM D S 1 G2 CP U

A TA 66/100/133

128pins LQFP

PCIE0

VC ORE_VD D_CO RE

CPU_ VD D0, CPU_ VDDD 1

USB #0

CRT CON

CCD

DEBUG PORT

KBC IT8502E

480 Mbps

Bluetooth

Port 2

IN

14*14*1.6mm

1 X8 PCIE I/F

USB8

AC 97 2 .3

33 MHz

UN BU FFE RED D D R2

SODIM M 0

OU T

USB# 2

PS2

TO UCH P A D

PW RG D, RST

Channel A

SB700

PCIE3

CLEVO C5500Q

Card Reader \Lan

X4

SP I I/F

0.9V ,1.8V ,

1.8V S,1.5VS

PCIE2

USB# 1

32.768 KHz

1 X4 PCIE I/F WIT H SB

CLI CK BO A RD

638-P in uFCPGA 638

LVD S/ CRT

4 X1 PCIE I/F

SATA I I (4PORTS)

E XTE RN AL CL OC K GEN ERA TO R

64 PIN

ICS9LPRS480

HyperTransport LINK0 CPU I/F

GPP PCIE IN TERFACE

AZAL I A H D AUDI O

Channel B

SYSTEM PWR,2.5V

1.8V S,3.3VS,5VS,3.3V ,1.2VS

INT

KE YB OA RD

Port 0

U SB9 or USB6

P owe r s w i t ch + H ot k ey X 3

100 MHz

AUD IO BOAR D

NEW CARD ONLY C4500

RS7 80M(C)

US B2.0 (10 )

NE W CA RD

CPU

Temperature sen sor

DDR II

1.1V S,1.2V,1.2VS,1. 2V_HT

IN T RTC

CPU FAN

JM C261

PCIE

VD D3 , VD D5

MINIPCIE-WLMINIPCIE-3G

I NTE GRAT ED G RAP HIC S

USB4

USB X 1

6-7P-C5505-002

PCB 5? 1 ? ? :

6-71-C5500-D02

6-71-E51Q2-D01A

6-71-C4508-D02A

6-71-E51QS-D01A

6-71-E51QN-D01

6- 71 -E 51 Q2 -D0 1

USB 2.0

USB7

LPC I/F

AC PI 1. 1

6-71-C4508-D02A

LPC

HDMI CON

UN BU FFE RED D D R2

SODIM M 1

USB5

6- 71 -E51 QS- D01

CH AR GE R,D C I N

32.768 KHz

LV DS CON

HDT

HyperTransport (HT)

Headphon e Jack

ALC 2 72 CO DE C/

TPA6017 AMP

HD AUDIO I/F

Int Spea ker

MIC In Jack

MDC

24 MHz

549PIN FCB GA

SATA I/F

HD D

SATA#1

SATA O DD

SATA#4

AUDIO BOARD

R

L

INT MIC

465PIN FC BG A

Int Spea ker

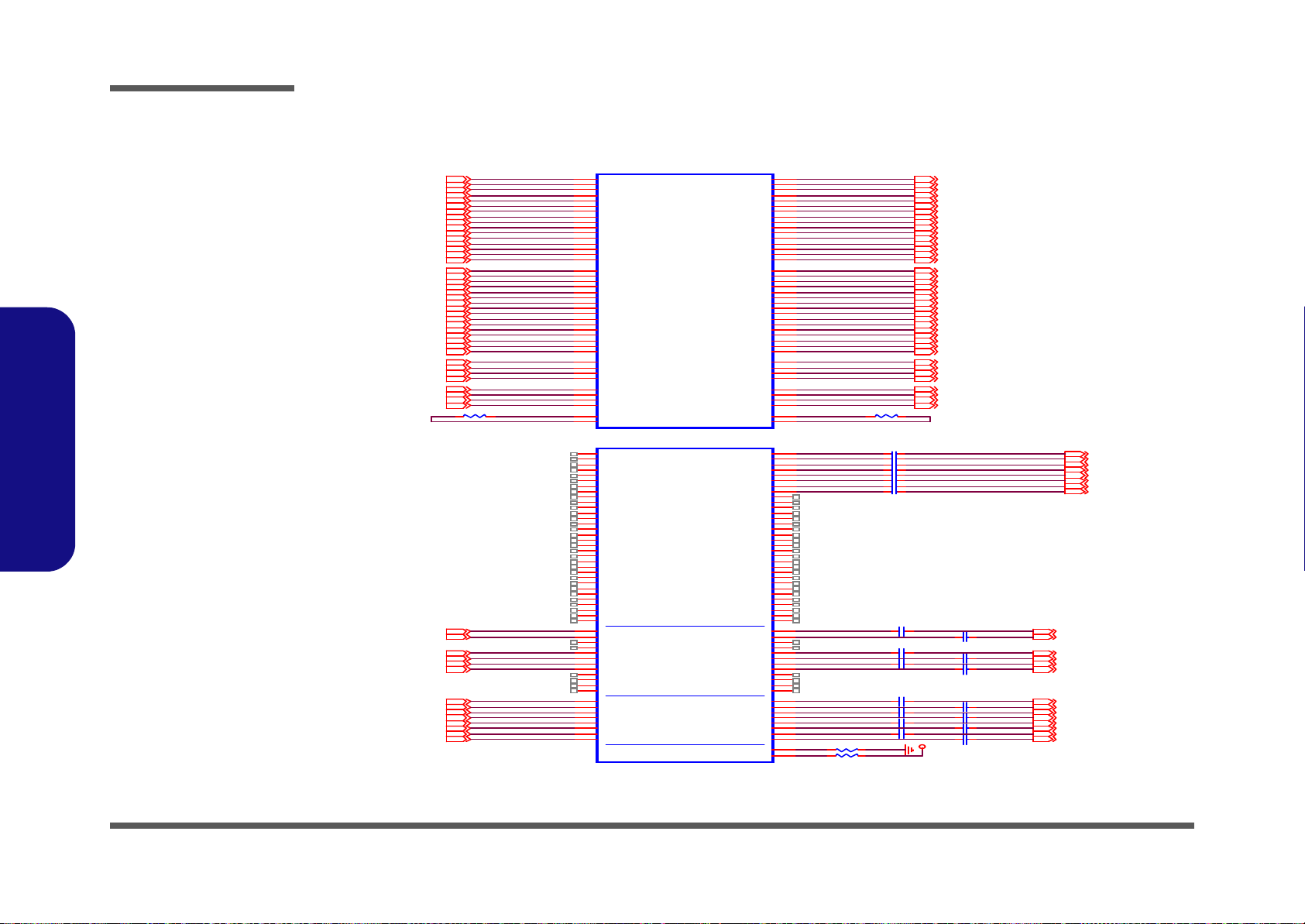

System Block Diagram

B.Schematic Diagrams

B - 2 System Block Diagram

Clock Generator

0514-J

add for SB710

SEL_27M Hz

PC IE_ EX PCA RD _C L K REQ #

Z0206

Place next to VDD48

20 08 /0 3/ 1 8

WLAN_CLKREQ#

Z0204

PCIE_EXPC ARD _CL KR EQ#

WLAN _CLKREQ#

Z0202

100 MH z non-spreading differential S ATA clock

100 MH z spreading dif ferential SR C clock

SEL_27M Hz

100 MH z spreading dif ferential SR C clock

SEL_SATA

0*

SEL_HTT66

27 MHz singled clock

1

100 M Hz dif ferential HTT clock

0 *

1 *

* default

66 MH z 3.3V single ended HTT clock

0

1

P lace very

cl o se t o U1

P lace within 0.5" of

CLKGEN

SE L_27MH z

SE L_H T66

C270

.1U_16V_04

R142

*8.2K_04

R135

*8 . 2 K _ 04

RN31 *0_4P2R_04_4mil_short1

2 3

4

C293

.1U_16V _04

L25 HCB1608KF-121T25-06

RN34 *0_4P2R_04_4mil_short

1

2 3

4

R134

*8.2K_04

R151

90.9_1%_06

C258

. 1U _16V_04

U4

ICS9LP RS480

VDDA_27

4

GNDA_27

7

VD DR EF

56

GNDREF

60

VD DSATA

40

G ND SATA

43

VD D4 8

63

GND48

1

VD DC PU

48

GNDCPU

46

VD DH TT

55

GNDHTT

52

VD DATIG

26

VD DSR C_IO 1

11

VD DSR C

16

VD DSB_ SR C

35

GNDATIG1

24

GNDSRC 1

10

GNDSRC 2

18

G ND SB_SRC

33

X1

61

X2

62

C LKR EQ 2#

44

SM BCLK

2

SM BDAT

3

PD #

51

REF 0/S E L _H T T66

59

R EF 1/SEL_ SATA

58

RE F 2/ SEL _2 7

57

CPUKG0T_LPRS

50

CPUKG0C_LPRS

49

ATI G0T_L PR S

30

ATIG0C _LPR S

29

ATI G1T_L PR S

28

ATIG1C _LPR S

27

SB_SR C0T_LPR S

37

SB_SRC0C _LPRS

36

SB_SR C1T_LPR S

32

SB_SRC1C _LPRS

31

SR C0T_LPR S

22

SRC0C_LPRS

21

SR C1T_LPR S

20

SRC1C_LPRS

19

SR C2T_LPR S

15

SRC2C_LPRS

14

SR C3T_LPR S

13

SRC3C_LPRS

12

SR C4T_LPR S

9

SRC4C_LPRS

8

SRC 7T_LPR S/27MHz_SS

6

SRC 7C_LPRS/ 27M Hz_N S

5

SR C6 C /SATAC _LPR S

41

SRC6 T/SATAT_LPR S

42

HTT 0 T/ 66M _LPR S

54

HTT0C/66M_LPRS

53

48MH z_0

64

C LKR EQ 0#

23

C LKR EQ 1#

45

VD DATIG _I O

25

VD DC PU_IO

47

VD DSB_ SR C_ IO

34

VD DSR C_IO 2

17

C LKR EQ 3#

39

C LKR EQ 4#

38

Therma l_GN D1

GND 1

Therma l_GN D2

GND 2

Therma l_GN D3

GND 3

Therma l_GN D4

GND 4

Ther mal_GN D5

GND5

Ther mal_GN D6

GND6

Ther mal_GN D7

GND7

Ther mal_GN D8

GND8

Ther mal_GN D9

GND9

RN36 *0_4P2R_04_4mil_short

1

2 3

4

C291

.1U_16V_04

C527

10U _6.3V_08

R 176 33_1%_04

C240

.1U_16V_04

R158 158_1%_06

RN37 *0_4P2R_04_4mil_short

1

2 3

4

R159

*8.2K _04

R133 8.2K_04

C 281

27P_50V_04

C259

.1U_1 6V_04

L54 HCB1608KF-121T25-06

R150

8.2K_04

L32 H CB1608K F-121T25-06

C 321

10U _6.3V_08

R152

*8. 2K_04

C237

.1U_16V_04

C292

.1U_16V_04

L31 HCB1608KF-121T25-06

C260

.1U _16V_04

RN32 *0_4P2R_04_4mil_short

1

2 3

4

SB_ 14.318M_OSC 1 4

C239

.1U _16V_04

RN30 *0_4P2R_04_4mil_short1

2 3

4

RN35 *0_4P2R_04_4mil_short

1

2 3

4

R179

*0_0402_5m il_short

C290

.1U_1 6V_04

R143

8 . 2K _0 4

C249

*1U _16V_06

C238

.1U_16V_04

R175

*1M_04

C320

27P_50V_04

C 241

.1U_16V_04

C289

.1U_1 6V_04

X2

14.318MHz

12

R160

*8.2K _04

RN33 *0_4P2R_04_4mil_short

1

2 3

4

C 306

1U _16V_06

CLK _ VDD

CLK _ VD D

1. 2 V S

CLK _ VD D

CLK _ VD D

3.3VS

CLK _ VDD

CLK_VDD

CLK _ VD DIO

C L K_VDD IO

CPU _ CLKP 5

CLK_VDD

Z0203

NB GFX_CLK N 10

NB GFX_CLK P 10

CPU _ CLKN 5

Z0201

SB LINK_CLK P 10

SB SR C_CLKP 14

SB SR C_CLKN 14

SB LINK_CLK N 1 0

PCIE _P E2_C LKP_ R

PCIE _ EXPCARD_CLKN 1 8

PCIE _ EXPCARD_CLKP 18

PCIE _P E1_C LKN_R

PCIE _P E3_C LKN_R

PCIE _P E3_C LKP_ R

PCIE _P E2_C LKN_R

PCIE _P E1_C LKP_ R

PCIE_WLAN_CLKP 18

PCIE_CR_CLK P 21

PCIE_CR_CLK N 21

PC IE_ EXPCA RD _C L KP_R

PC IE_ EX PCA RD _C L K N_ R

NBHT_CLKN 10

NBHT_CLKP 10

PCIE_WLAN_CLKN 18

SE L_SATA

SCLK07,8,15

SDA TA07,8,15

CLK _48M_USB 15

Z0208

WLAN _CLKRE Q#18

PC IE_ EXPCAR D_C LK REQ #15 , 1 8

NB_OSC 10

Z 0205

SEL_HT66

NBG PP_ CL KP _R

NBG PP_ CL KN _R

Z0207

NBG FX_ CL K P_ R

NBG FX_ CL K N _R

CPU _ CL KP_ R

CPU _ CL KN _R

GFX_CLKN _R

GFX_CLKP _R

R446

*0_0402_5m il_short

R S780 1.1 V

SEL_SATA

Layout note:

PLACE CRYSTAL WITHIN 500

MILS OF ICS9LPR S480

SBSR C_ CLKP _R

SBSR C_ CLKN _R

NBS LINK_ CLKP_ R

NBS LIN K_ CL K N _ R

NBH TRE F_ C LK N_ R

NBH TRE F_ C LK P_ RZ0209

Z0210

Z0211

Cl ock c hi p ha s in ter na l se ri al te rm in atio ns

fo r d iffe ren cia l pa i rs , exte rn al r es ist ors are

reserve d f or de bu g p ur po se .

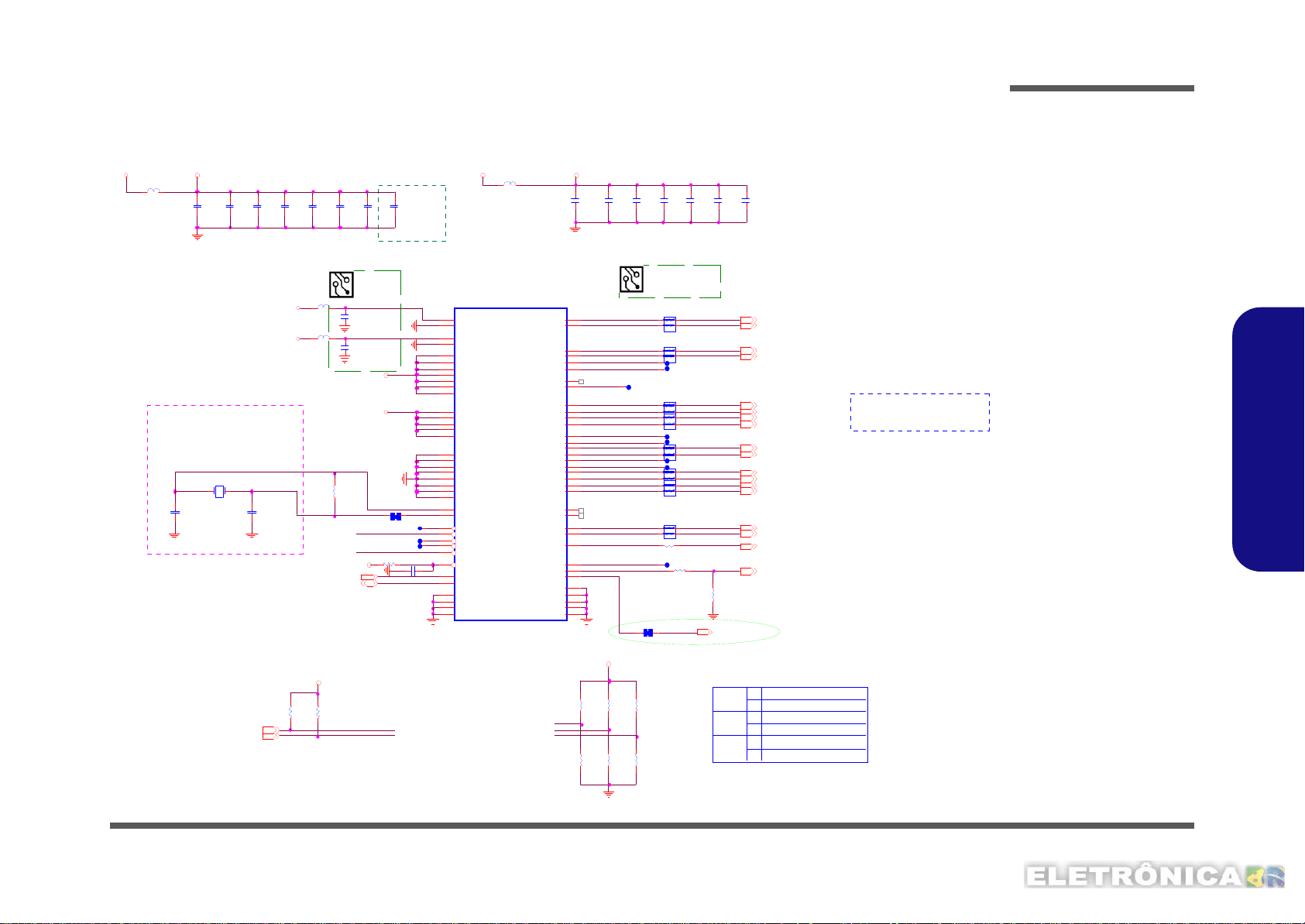

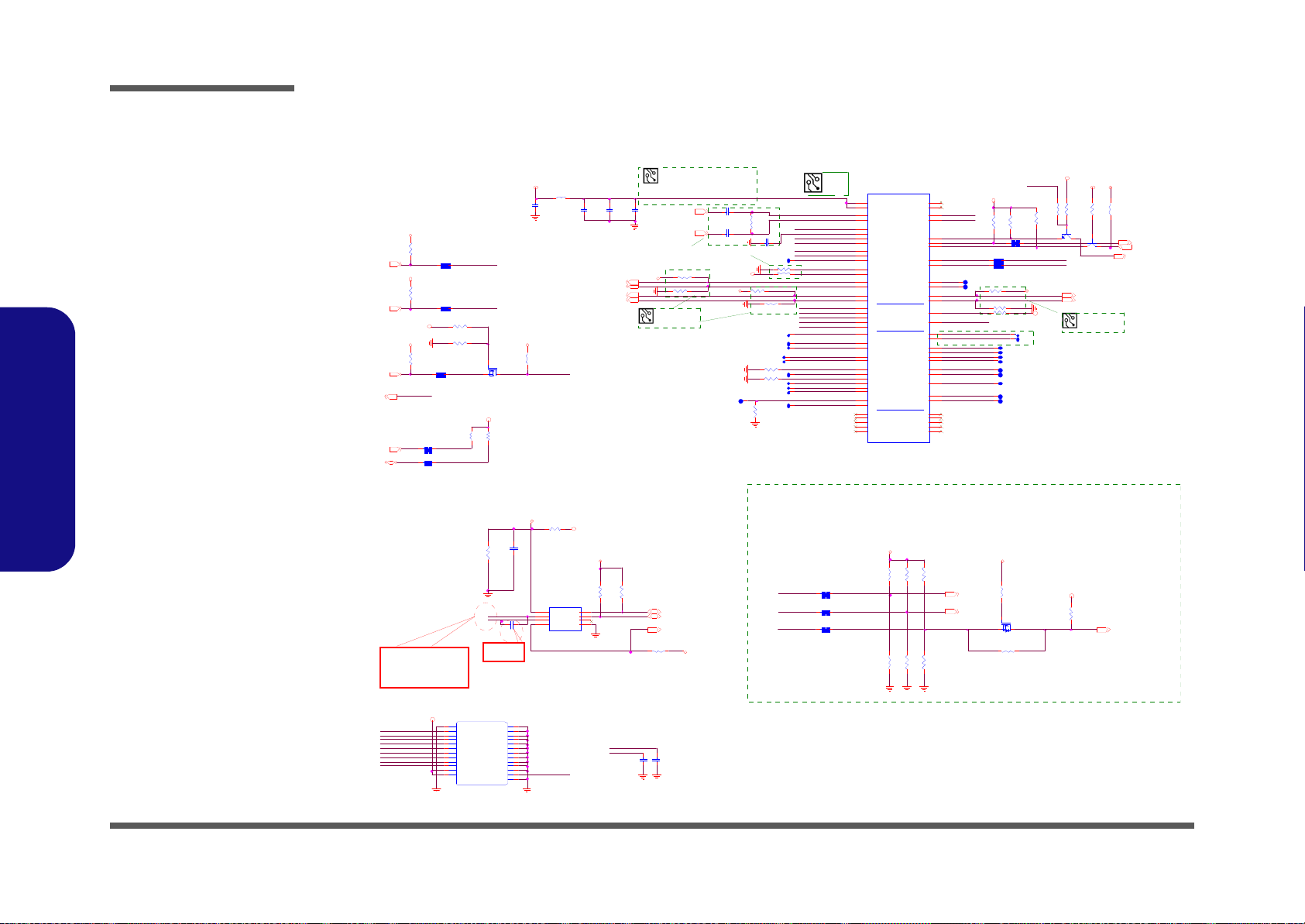

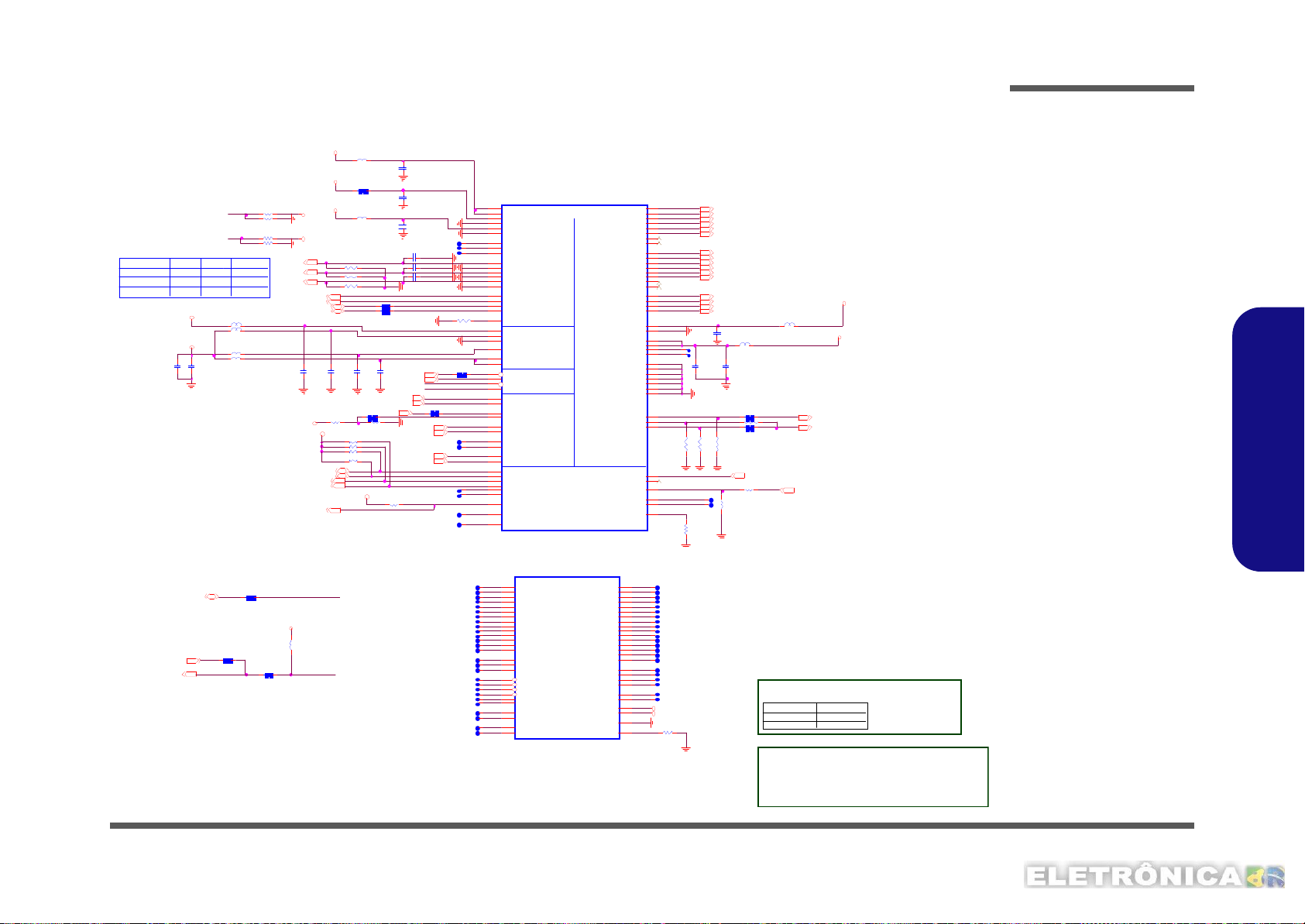

Sheet 2 of 35

Clock Generator

Schematic Diagrams

B.Schematic Diagrams

Clock Generator B - 3

Schematic Diagrams

Sheet 3 of 35

CPU-1

* If VLDT is connected only on one side,

o ne 4.7uF cap sh ou ld b e ad de d t o

the isla nd sid e

1.5A

60M I L

1.5A

60MIL

Place cl ose to soc ket

C440

4.7U_ 6.3V_06

C447

4. 7U_6.3V_06

C452

.22 U_10V_04

C451

.22U _10V_ 04

HT LINK

U15A

SOCKET_638_PIN

VL DT_ A3

D4

VL DT_ A2

D3

VL DT_ A1

D2

VL DT_ A0

D1

VLDT_B3

AE5

VLDT_B2

AE4

VLDT_B1

AE3

VLDT_B0

AE2

L0_CADI N_H15

N5

L0_CADI N_L15

P5

L0_CADI N_H14

M3

L0_CADI N_L14

M4

L0_CADI N_H13

L5

L0_CADI N_L13

M5

L0_CADI N_H12

K3

L0_CADI N_L12

K4

L0_CADI N_H11

H3

L0_CADI N_L11

H4

L0_CADI N_H10

G5

L0_CADI N_L10

H5

L0_CADI N_H9

F3

L0_CADI N_L9

F4

L0_CADI N_H8

E5

L0_CADI N_L8

F5

L0_CADI N_H7

N3

L0_CADI N_L7

N2

L0_CADI N_H6

L1

L0_CADI N_L6

M1

L0_CADI N_H5

L3

L0_CADI N_L5

L2

L0_CADI N_H4

J1

L0_CADI N_L4

K1

L0_CADI N_H3

G1

L0_CADI N_L3

H1

L0_CADI N_H2

G3

L0_CADI N_L2

G2

L0_CADI N_H1

E1

L0_CADI N_L1

F1

L0_CADI N_H0

E3

L0_CADI N_L0

E2

L0_CADOUT_H15

T4

L0_CAD OUT_L1 5

T3

L0_CADOUT_H14

V5

L0_CAD OUT_L1 4

U5

L0_CADOUT_H13

V4

L0_CAD OUT_L1 3

V3

L0_CADOUT_H12

Y5

L0_CAD OUT_L1 2

W5

L0_CADOUT_H11

AB5

L0_CAD OUT_L1 1

AA5

L0_CADOUT_H10

AB4

L0_CAD OUT_L1 0

AB3

L0_CAD OUT_H9

AD 5

L0_CAD OUT_L 9

AC 5

L0_CAD OUT_H8

AD 4

L0_CAD OUT_L 8

AD 3

L0_CAD OUT_H7

T1

L0_CAD OUT_L 7

R1

L0_CAD OUT_H6

U2

L0_CAD OUT_L 6

U3

L0_CAD OUT_H5

V1

L0_CAD OUT_L 5

U1

L0_CAD OUT_H4

W2

L0_CAD OUT_L 4

W3

L0_CAD OUT_H3

AA2

L0_CAD OUT_L 3

AA3

L0_CAD OUT_H2

AB1

L0_CAD OUT_L 2

AA1

L0_CAD OUT_H1

AC 2

L0_CAD OUT_L 1

AC 3

L0_CAD OUT_H0

AD 1

L0_CAD OUT_L 0

AC 1

L0_CLKI N_H1

J5

L0_CLKI N_ L1

K5

L0_CLKI N_H0

J3

L0_CLKI N_ L0

J2

L0_CTLIN_H1

P3

L0_CTLIN_L1

P4

L0_CTLIN_H0

N1

L0_CTLIN_L0

P1

L0_CL KOUT_H 1

Y4

L0_CLKOUT_L1

Y3

L0_CL KOUT_H 0

Y1

L0_CLKOUT_L0

W1

L0_ CTL OU T_H 1

T5

L0_CTLOUT_L1

R5

L0_ CTL OU T_H 0

R2

L0_CTLOUT_L0

R3

C441

180P_NPO_50V_04

C442

180P_NPO_50V_04

C443

4.7 U_6.3V_06

1.2 VS

1.2VS

HT_NB_ CPU_CA D_L09

HT_C PU_NB_CAD _H0 9

1.2VS

HT_NB_ CPU_CA D_H29

HT_NB_ CPU_CA D_L19

HT_NB_ CPU_CA D_H19

HT_NB_ CPU_CA D_H49

HT_NB_ CPU_CA D_L39

HT_NB_ CPU_CA D_H39

HT_NB_ CPU_CA D_L29

HT_NB_ CPU_CA D_L59

HT_NB_ CPU_CA D_H59

HT_NB_ CPU_CA D_L49

HT_NB_ CPU_CA D_H79

HT_NB_ CPU_CA D_L69

HT_NB_ CPU_CA D_H69

HT_NB_ CPU_CA D_L89

HT_NB_ CPU_CA D_H89

HT_NB_ CPU_CA D_L79

HT_NB_ CPU_CA D_H109

HT_NB_ CPU_CA D_L99

HT_NB_ CPU_CA D_H99

HT_NB_ CPU_CA D_H129

HT_NB_ CPU_CA D_L119

HT_NB_ CPU_CA D_H119

HT_NB_ CPU_CA D_L109

HT_NB_ CPU_CA D_L139

HT_NB_ CPU_CA D_H139

HT_NB_ CPU_CA D_L129

HT_NB_ CPU_CA D_H159

HT_NB_ CPU_CA D_L149

HT_NB_ CPU_CA D_H149

HT_NB_ CPU_CLK_ L09

HT_NB_ CPU_CLK_ H09

HT_NB_ CPU_CA D_L159

HT_NB_ CPU_CTL _H09

HT_NB_ CPU_CLK_ L19

HT_NB_ CPU_CLK_ H19

HT_C PU_NB_CAD _L0 9

HT_NB_ CPU_CTL _L19

HT_NB_ CPU_CTL _H19

HT_NB_ CPU_CTL _L09

HT_C PU_NB_CAD _H2 9

HT_C PU_NB_CAD _L1 9

HT_C PU_NB_CAD _H1 9

HT_C PU_NB_CAD _L3 9

HT_C PU_NB_CAD _H3 9

HT_C PU_NB_CAD _L2 9

HT_C PU_NB_CAD _H5 9

HT_C PU_NB_CAD _L4 9

HT_C PU_NB_CAD _H4 9

HT_C PU_NB_CAD _L6 9

HT_C PU_NB_CAD _H6 9

HT_C PU_NB_CAD _L5 9

HT_C PU_NB_CAD _L8 9

HT_C PU_NB_CAD _H8 9

HT_C PU_NB_CAD _L7 9

HT_C PU_NB_CAD _H7 9

HT_C PU_NB_CAD _H10 9

HT_C PU_NB_CAD _L9 9

HT_C PU_NB_CAD _H9 9

HT_C PU_NB_CAD _L11 9

HT_C PU_NB_CAD _H11 9

HT_C PU_NB_CAD _L10 9

HT_C PU_NB_CAD _H13 9

HT_C PU_NB_CAD _L12 9

HT_C PU_NB_CAD _H12 9

HT_C PU_NB_CAD _L14 9

HT_C PU_NB_CAD _H14 9

HT_C PU_NB_CAD _L13 9

HT_CPU_NB_CLK_L0 9

HT_CPU_NB_CLK_H0 9

HT_C PU_NB_CAD _L15 9

HT_C PU_NB_CAD _H15 9

HT_C PU_NB_CTL_H 0 9

HT_CPU_NB_CLK_L1 9

HT_CPU_NB_CLK_H1 9

HT_CPU_NB_CT L_L1 9

HT_C PU_NB_CTL_H 1 9

HT_CPU_NB_CT L_L0 9

HT_NB_ CPU_CA D_H09

CPU-1

B.Schematic Diagrams

B - 4 CPU-1

CPU-2

Sheet 4 of 35

CPU-2

C499

4.7U_6.3V _06

C492

*.22U _10V_04

CPU _M_VREF _SUS

C483

1000P_X7R_50V_04

C491

*4 .7U _ 6.3 V _ 0 6

R301 39.2_1%_04

C86

180P_NPO_50V_04

C493

4.7U _6.3V_06

C115

.1U _X7R _10V_04

C485

.22U_10V_04

MEM : C M D/ C T R L / CL K

U15B

SOCKET_638_PIN

VTT 1

D10

VTT 2

C10

VTT 3

B10

VTT 4

AD 1 0

VTT5

W10

VTT6

AC10

VTT7

AB10

VTT8

AA10

VTT9

A10

MA1_OD T1

V19

MA1_OD T0

U21

MA0_OD T1

V22

MA0_OD T0

T19

MB1_OD T0

Y26

MB0_OD T1

W23

MB0_OD T0

W26

R SVD_ M2

B18

MB1_C S_L0

U22

MB0_C S_L1

W25

MB0_C S_L0

V26

MA0_CS_L1

U19

MA1_CS_L1

V20

MA1_CS_L0

U20

MA0_CS_L0

T20

MA_ADD15

K19

MA_ADD14

K24

MA_ADD13

V24

MA_ADD12

K20

MA_ADD11

L22

MA_ADD10

R21

MA_ A D D 9

K22

MA_ A D D 8

L19

MA_ A D D 7

L21

MA_ A D D 6

M24

MA_ A D D 5

L20

MA_ A D D 4

M22

MA_ A D D 3

M19

MA_ A D D 2

N22

MA_ A D D 1

M20 MA_ A D D 0

N21

MA_BAN K2

J21

MA_BAN K1

R23

MA_BAN K0

R20

MA_ R A S _L

R19

MA_ C A S _L

T22

MA_ W E _ L

T24

MEM Z P

AF10

MEM Z N

AE10

VTT_SE NSE

Y10

MEMV REF

W17

MA_CLK_H4

P19

MA_CLK_L4

P20

MA_CLK_H7

Y16

MA_CLK_L7

AA16

MA_CLK_H1

E16

MA_CLK_L1

F16

MA_CLK_H5

N19

MA_CLK_L5

N20

MB_CLK_H4

R26

MB_CLK_L4

R25

MB_CLK_H7

AF18

MB_CLK_L7

AF17

MB_CLK_H1

A17

MB_CLK_L1

A18

MB_CLK_H5

P22

MB_CLK_L5

R22

MA_ C K E 0

J22

MA_ C K E 1

J20

M B_CKE0

J25

M B_CKE1

H26

MB_ADD 15

J24

MB_ADD 14

J23

MB_ADD 13

W24

MB_ADD 12

L25

MB_ADD 11

L26

MB_ADD 10

T26

M B _A DD9

K26

M B _A DD8

M26

M B _A DD7

L24

M B _A DD6

N25

M B _A DD5

L23

M B _A DD4

N26

M B _A DD3

N23

M B _A DD2

P26

M B _A DD1

N24M B_A DD0

P24

M B_BANK2

J26

M B_BANK1

U26

M B_BANK0

R24

MB_R AS_L

U25

MB_C AS_L

U24

MB_W E_L

U23

RSVD _M 1

H16

C105

1000P_X7R_50V_04

C85

*1000P_X7R _50V_04

C490

*180P_N PO_50V_04

C495

1000P _X7R_50V_04

C500

4.7U_6.3V_06

C488

180P_N PO_50V_04

R96

1K_04_1%

C477

*.22U_10V_04

C478

*1000P_X7R _50V_04

C489

.22U_10V_04

PLA C E T HEM C LOSE TO

CP U W I TH I N 1 "

R293 39.2_1%_04

C484

180P_NPO_50V_04

MEM : D A T A

U15C

SO CKET_ 638_PIN

MB_ D A TA 63

AD11

MB_ D A TA 62

AF11

MB_ D A TA 61

AF14

MB_ D A TA 60

AE14

MB_ D A TA 59

Y11

MB_ D A TA 58

AB11

MB_ D A TA 57

AC12

MB_ D A TA 56

AF13

MB_ D A TA 55

AF15

MB_ D A TA 54

AF16

MB_ D A TA 53

AC18

MB_ D A TA 52

AF19

MB_ D A TA 51

AD14

MB_ D A TA 50

AC14

MB_ D A TA 49

AE18

MB_ D A TA 48

AD18

MB_ D A TA 47

AD20

MB_ D A TA 46

AC20

MB_ D A TA 45

AF23

MB_ D A TA 44

AF24

MB_ D A TA 43

AF20

MB_ D A TA 42

AE20

MB_ D A TA 41

AD22

MB_ D A TA 40

AC22

MB_ D A TA 39

AE25

MB_ D A TA 38

AD26

MB_ D A TA 37

AA25 MB _ D A TA 36

AA26

MB_ D A TA 35

AE24 MB _ D A TA 34

AD24

MB_ D A TA 33

AA23 MB _ D A TA 32

AA24

MB_ D A TA 31

G2 4 MB _ D ATA 30

G2 3

MB_ D A TA 29

D26 MB _ D ATA 28

C26

MB_ D A TA 27

G2 6 MB _ D ATA 26

G2 5

MB_ D A TA 25

E24

MB_ D A TA 24

E23

MB_ D A TA 23

C24

MB_ D A TA 22

B24

MB_ D A TA 21

C20

MB_ D A TA 20

B20

MB_ D A TA 19

C25

MB_ D A TA 18

D24

MB_ D A TA 17

A21

MB_ D A TA 16

D20

MB_ D A TA 15

D18

MB_ D A TA 14

C18

MB_ D A TA 13

D14

MB_ D A TA 12

C14

MB_ D A TA 11

A20

MB_ D A TA 10

A19

MB_ D A TA 9

A16

MB_ D A TA 8

A15

MB_ D A TA 7

A13

MB_ D A TA 6

D12

MB_ D A TA 5

E11

MB_ D A TA 4

G1 1

MB_ D A TA 3

B14

MB_ D A TA 2

A14

MB_ D A TA 1

A11

MB_ D A TA 0

C11

MA_DATA63

AA12

MA_DATA62

AB12

MA_DATA61

AA14

MA_DATA60

AB14

MA_DATA59

W11

MA_DATA58

Y12

MA_DATA57

AD13

MA_DATA56

AB13

MA_DATA55

AD15

MA_DATA54

AB15

MA_DATA53

AB17

MA_DATA52

Y17

MA_DATA51

Y14

MA_DATA50

W14

MA_DATA49

W16

MA_DATA48

AD17

MA_DATA47

Y18

MA_DATA46

AD19

MA_DATA45

AD21

MA_DATA44

AB21

MA_DATA43

AB18

MA_DATA42

AA18

MA_DATA41

AA20

MA_DATA40

Y20

MA_DATA39

AA22

MA_DATA38

Y22

MA_DATA37

W21MA_DATA36

W22

MA_DATA35

AA21MA_DATA34

AB22

MA_DATA33

AB24MA_DATA32

Y24

MA_DATA31

H22MA_DATA30

H20

MA_DATA29

E22MA_DATA28

E21

MA_DATA27

J1 9MA_DATA26

H24

MA_DATA25

F22

MA_DATA24

F20

MA_DATA23

C23

MA_DATA22

B22

MA_DATA21

F18

MA_DATA20

E18

MA_DATA19

E20

MA_DATA18

D22

MA_DATA17

C19

MA_DATA16

G18

MA_DATA15

G17

MA_DATA14

C17

MA_DATA13

F14

MA_DATA12

E14

MA_DATA11

H17

MA_DATA10

E17

MA _D ATA9

E15

MA _D ATA8

H15

MA _D ATA7

E13

MA _D ATA6

C13

MA _D ATA5

H12

MA _D ATA4

H11

MA _D ATA3

G14

MA _D ATA2

H14

MA _D ATA1

F12

MA _D ATA0

G12

MB_ D M7

AD12

MB_ D M6

AC16

MB_ D M5

AE22

MB_ D M4

AB26

MB_ D M3

E25

MB_ D M2

A22

MB_ D M1

B16

MB_ D M0

A12

MB_DQS_H7

AF12

MB_DQS_L7

AE12

MB_DQS_H6

AE16

MB_DQS_L6

AD16

MB_DQS_H5

AF21

MB_DQS_L5

AF22

MB_DQS_H4

AC25

MB_DQS_L4

AC26

MB_DQS_H3

F26

MB_DQS_L3

E26

MB_DQS_H2

A24

MB_DQS_L2

A23

MB_DQS_H1

D16

MB_DQS_L1

C16

MB_DQS_H0

C12

MB_DQS_L0

B12

MA_DM7

Y13

MA_DM6

AB16

MA_DM5

Y19

MA_DM4

AC24

MA_DM3

F24

MA_DM2

E19

MA_DM1

C15

MA_DM0

E12

MA_D QS_H 7

W12

MA_DQS_L7

W13

MA_D QS_H 6

Y15

MA_DQS_L6

W15

MA_D QS_H 5

AB19

MA_DQS_L5

AB20

MA_D QS_H 4

AD23

MA_DQS_L4

AC23

MA_D QS_H 3

G22

MA_DQS_L3

G21

MA_D QS_H 2

C22

MA_DQS_L2

C21

MA_D QS_H 1

G16

MA_DQS_L1

G15

MA_D QS_H 0

G13

MA_DQS_L0

H13

R97

1K_04_1%

0.9V

0.9V

1. 8 V

0.9V

CPU _M _VREF_ SU S

MEM_MA_ADD[0..15]7

1. 8 V

ME M_ MA _ B A N K17

ME M_ MA _ B A N K07

M EM_M B_D ATA[0 ..63 ]8

ME M_ MA _ W E#7

ME M_ MA _ C AS #7

ME M_ MA _ R AS #7

ME M_ MA _ B A N K27

MEM_MA0_CS#07

MEM_MA0_ODT17

MEM_MA0_ODT07

MEM_MA_CKE17

MEM_MA_CKE07

MEM_MA0_CS#17

ME M_ MA _ C LK7 _ P7

ME M_ MA _ C LK1 _ N7

ME M_ MA _ C LK1 _ P7

MEM _ MB 0 _ OD T1 8

MEM _ MB 0 _ OD T0 8

ME M_ MA _ C LK7 _ N7

MEM _ MB _ C K E 1 8

MEM _ MB _ C K E 0 8

MEM _ MB 0 _ CS # 1 8

MEM _ MB 0 _ CS # 0 8

MEM_MB_CLK7_P 8

MEM_MB_CLK1_N 8

MEM_MB_CLK1_P 8

MEM_ MB_BAN K0 8

MEM _ MB _ A DD [0 . .1 5] 8

MEM_MB_CLK7_N 8

MEM _ MB _ R A S # 8

MEM_ MB_BAN K2 8

MEM_ MB_BAN K1 8

MEM_MB_DM[0..7]8

MEM _ MB _ W E# 8

MEM _ MB _ C A S # 8

MEM_MB_DQ S1_N8

MEM_MB_DQ S1_P8

MEM_MB_DQ S0_N8

MEM_MB_DQ S0_P8

MEM_MB_DQ S3_P8

MEM_MB_DQ S2_N8

MEM_MB_DQ S2_P8

MEM_MB_DQ S4_N8

MEM_MB_DQ S4_P8

MEM_MB_DQ S3_N8

MEM_MB_DQ S6_P8

MEM_MB_DQ S5_N8

MEM_MB_DQ S5_P8

MEM_MB_DQ S7_N8

MEM_MB_DQ S7_P8

MEM_MB_DQ S6_N8

MEM_MA_DQ S0_N 7

MEM_MA_DQ S0_P 7

M EM_ MA _ D M[0 . .7 ] 7

M EM_ MA _ D AT A [ 0.. 63 ] 7

MEM_MA_DQ S2_P 7

MEM_MA_DQ S1_N 7

MEM_MA_DQ S1_P 7

MEM_MA_DQ S3_N 7

MEM_MA_DQ S3_P 7

MEM_MA_DQ S2_N 7

MEM_MA_DQ S5_P 7

MEM_MA_DQ S4_N 7

MEM_MA_DQ S4_P 7

MEM_MA_DQ S6_N 7

MEM_MA_DQ S6_P 7

MEM_MA_DQ S5_N 7

MEM_MA_DQ S7_N 7

MEM_MA_DQ S7_P 7

Place close to socket

To SO - D I M M 0

socket

To SO-DIMM 1

socket

Wid th 20 mil ,l e ngth <6 in ch

C138

10U _10V_08

VTT

75 0m A

VTT

75 0m A

Z0401

Z0402

Z0403

Z0404

Z0405

Z0406

Z0410

Z0409

Z0408

Z0411

Z0412

M_ZN

M_ZP

M EM_MB_D ATA6

M EM_MB_D ATA1

M EM_MB_D ATA11

M EM_MB_D ATA16

M EM_MB_D ATA20

M EM_MB_D ATA14

M EM_MB_D ATA12

M EM_MB_D ATA13

M EM_MB_D ATA7

M EM_MB_D ATA4

M EM_MB_D ATA15

M EM_MB_D ATA21

M EM_MB_D ATA19

M EM_MB_D ATA0

M EM_MB_D ATA10

M EM_MB_D ATA9

M EM_MB_D ATA2

M EM_MB_D ATA18

M EM_MB_D ATA5

M EM_MB_D ATA3

M EM_MB_D ATA17

M EM_MB_D ATA8

ME M_ MA _ D ATA5 4

ME M_ MA _ D ATA0

ME M_ MA _ D ATA1

ME M_ MA _ D ATA2

ME M_ MA _ D ATA5 5

ME M_ MA _ D ATA3

ME M_ MA _ D ATA5 6

ME M_ MA _ D ATA5

ME M_ MA _ D ATA7

ME M_ MA _ D ATA4

ME M_ MA _ D ATA8

MEM_MA_DATA12

MEM_MA_DATA10

ME M_ MA _ D ATA6

ME M_ MA _ D ATA5 7

ME M_ MA _ D ATA9

ME M_ MA _ D ATA1 5

MEM_MA_DATA11

ME M_ MA _ D ATA1 3

ME M_ MA _ D ATA1 6

ME M_ MA _ D ATA1 9

ME M_ MA _ D ATA5 8

ME M_ MA _ D ATA1 7

ME M_ MA _ D ATA1 4

ME M_ MA _ D ATA1 8

ME M_ MA _ D ATA5 9

ME M_ MA _ D ATA2 0

ME M_ MA _ D ATA2 2

ME M_ MA _ D ATA2 1

ME M_ MA _ D ATA2 6

ME M_ MA _ D ATA2 3

ME M_ MA _ D ATA2 5

ME M_ MA _ D ATA2 4

ME M_ MA _ D ATA2 9

ME M_ MA _ D ATA2 8

ME M_ MA _ D ATA3 1

ME M_ MA _ D ATA3 2

ME M_ MA _ D ATA2 7

ME M_ MA _ D ATA3 0

ME M_ MA _ D ATA3 6

ME M_ MA _ D ATA4 0

ME M_ MA _ D ATA3 4

ME M_ MA _ D ATA3 3

ME M_ MA _ D ATA3 5

ME M_ MA _ D ATA6 0

ME M_ MA _ D ATA3 9

ME M_ MA _ D ATA4 1

ME M_ MA _ D ATA3 8

ME M_ MA _ D ATA3 7

ME M_ MA _ D ATA4 5

ME M_ MA _ D ATA4 3

ME M_ MA _ D ATA4 6

ME M_ MA _ D ATA4 4

ME M_ MA _ D ATA6 1

ME M_ MA _ D ATA4 2

ME M_ MA _ D ATA5 3

ME M_ MA _ D ATA4 7

ME M_ MA _ D ATA5 1

ME M_ MA _ D ATA4 8

ME M_ MA _ D ATA5 0

ME M_ MA _ D ATA4 9

MEM_MB_ADD 14

MEM_MB_ADD 3

MEM_MB_ADD 12

ME M_ MA _ D ATA6 2

ME M_ MA _ D ATA5 2

MEM_MB_ADD 6

MEM_MB_ADD 1

MEM_MB_ADD 7

MEM_MB_ADD 10

MEM_MB_ADD 13

MEM_MB_ADD 11

MEM_MB_ADD 8

MEM_MB_ADD 4

MEM_MB_ADD 2

MEM_MB_ADD 5

MEM_MB_ADD 9

MEM_MB_ADD 0

MEM_MB_ADD 15

ME M_ MA _ D ATA6 3

Z0407

MEM _ MA _ A D D 1 4

MEM _ MA _ A D D 1 3

MEM _ MA _ A D D 3

MEM _ MA _ A D D 1 2

MEM _ MA _ A D D 1 0

MEM _ MA _ A D D 1 1

MEM _ MA _ A D D 2

MEM _ MA _ A D D 1

MEM _ MA _ A D D 8

MEM _ MA _ A D D 9

MEM _ MA _ A D D 5

MEM _ MA _ A D D 6

MEM _ MA _ A D D 7

MEM _ MA _ A D D 4

MEM _ MA _ A D D 0

MEM _ MA _ A D D 1 5

MEM_MA_DM5

MEM _ MA _ R E S ET #

MEM_MA_DM6

MEM_MA_DM2

MEM_MA_DM4

MEM_MA_DM1

MEM_MA_DM0

MEM_MA_DM3

MEM_MA_DM7

M EM_ MB 1_ O D T 0

MEM _ MA 1 _ O D T0

MEM _ MA 1 _ O D T1

M EM_ MB _ D M5

M EM_ MB _ D M6

M EM_ MB _ D M4

M EM_ MB _ D M3

M EM_ MB _ D M7

M EM_ MB _ D M2

M EM_ MB _ D M1

M EM_ MB _ D M0

M EM_MB _R ESET#

M EM_MB_D ATA40

M EM_MB_D ATA26

M EM_MB_D ATA37

M EM_MB_D ATA23

M EM_MB_D ATA31

M EM_MB_D ATA41

M EM_MB_D ATA28

M EM_MB_D ATA38

M EM_MB_D ATA43

M EM_MB_D ATA42

M EM_MB_D ATA32

M EM_MB_D ATA39

M EM_MB_D ATA34

M EM_MB_D ATA24

M EM_MB_D ATA22

M EM_MB_D ATA29

M EM_MB_D ATA35

M EM_MB_D ATA33

M EM_MB_D ATA30

M EM_MB_D ATA62

M EM_MB_D ATA25

M EM_MB_D ATA27

M EM_MB_D ATA36

M EM_MB_D ATA52

M EM_MB_D ATA55

M EM_MB_D ATA56

M EM_MB_D ATA54

M EM_MB_D ATA53

M EM_MB_D ATA50

M EM_MB_D ATA51

M EM_MB_D ATA46

M EM_MB_D ATA48

M EM_MB_D ATA44

M EM_MB_D ATA49

M EM_MB_D ATA45

M EM_MB_D ATA60

M EM_MB_D ATA59

M EM_MB_D ATA63

M EM_MB_D ATA47

M EM_MB_D ATA57

M EM_MB_D ATA61

M EM_MB_D ATA58

Processor Memory Inter face

Schematic Diagrams

CPU-2 B - 5

B.Schematic Diagrams

Schematic Diagrams

Sheet 5 of 35

CPU-3

EX IT BAL L F IELD) A ND 500 mils L ONG .

50 m ils WIDE (USE 2x25 m il TRACES TO

CPU_SVD_R

K e ep t r ac e f r om r es isor to CPU with in 0.6"

keep trace from caps to CPU within 1.2"

CPU_MEMHOT#_1.8V

LAYOUT: ROUTE VDDA TRAC E APPRO X .

CPU_VDDA_RUN

CPU_HTREF0

R 2 85 * 0_0 40 2_ 10m il _s hor t

C47

.1U_X7R_10V_ 04

C83

10U_10V_06

P R 3 6 2. 2_ 1%_ 06

R43

*0_ 040 2_ 5m i l _sh or t

R320

300_04

R85

300_04

R 319

*0_0402_5m il_s hort

R45

*220_04

R 191

300 _ 0 4

Q39

2N 39 04

B

E C

U13

ADM 1 03 2A R M

SCLK

8

SD A T A

7

AL ER T #

6

GND5THERM#

4

D-

3

D+

2

VDD

1

R316

*0_ 04 02_ 5m il _s hor t

Q38

*2N3904

B

EC

R308

10 0K _0 4

R 274

*0 _04

R300

4.7K_04

R317

390_04

P R 109 2. 2 _1 %_0 6

R36

1K _0 4

R89

*2 .2K_04

Q11

MTN 7 00 2Z H S3

G

DS

R63 44.2_1%_04

R94

*220_ 04

C475

1 U _1 6V _0 6

R56 44.2_1%_04

R44

*0 _0 40 2_5 m i l_ s h or t

R324

1K _ 04

R314

30 0_ 04

R64

300 _0 4

P R 37 2 . 2_ 1%_ 06

R88 *0_04

P R 10 8 2. 2_ 1%_ 06

U15D

S O C K ET _6 38 _P I N

VD D A 1

F8

VD D A 2

F9

RESET_L

B7

PW R O K

A7

LDTSTOP_L

F1 0

SI C

AF4

SI D

AF5

HT_REF1

P6

HT_REF0

R6

VD D 0 _ F B _H

F6

VD D 0 _ F B _L

E6

VDDIO_ F B_H

W9

VDDIO_FB_L

Y9

THERMTRIP_L

AF6

PROCHOT_L

AC7

RSVD2

A5

LD T REQ_L

C6

SVC

A6

SVD

A4

RSVD6

C5

RSVD4

B5

RSVD1

A3

CLKIN_H

A9

CLKIN_L

A8

DBRDY

G1 0

TM S

AA9

TC K

AC9

TR S T_ L

AD9

TD I

AF9

DBREQ_L

E10

TDO

AE9

TE S T25 _H

E9

TE S T25 _L

E8

TE S T19

G9

TE S T18

H10

RSVD8

AA7

TE S T9

C2

TE ST 17

D7

TE ST 16

E7

TE ST 15

F7

TE ST 14

C7

TE S T12

AC8

TE S T7

C3

TE S T6

AA6

TH E R M D C

W7

TH E R M D A

W8

VD D 1 _ F B _H

Y6

VD D 1 _ F B _L

AB6

TEST29_H

C9

TEST29_L

C8

TE S T24

AE7

TE S T23

AD7

TE S T22

AE8

TE S T21

AB8

TE S T20

AF7

TEST28_H

J7

TEST28_L

H8

TE S T27

AF8

AL E RT_L

AE6

TE ST 10

K8

TE S T8

C4

RSVD3

B3

RSVD5

C1

VDDNB_ F B_H

H6

VDDNB_FB_L

G6

RSVD7

D5

KEY2

W18

MEMHOT _L

AA8

RSVD10

H18

RSVD9

H19

KEY1

M11

Q12

MTN7002ZHS3

G

DS

R325

*10K _04

P R 11 6 2 . 2_1 %_ 06

R35

1K_04

PWRGD

R76

*0 _0 40 2_5 m i l_ s h or t

C48

.1 U _X 7R _ 10V _ 04

R48

*220_04

R318

300_04

R321

39 0_0 4

PR113 2.2_1%_06

R292 10K_04

C75

39 0 0 P_ X7 R _5 0 V_ 0 4

CPU_THERMTRIP#_1.8V

R278

300 _0 4

R80

* 0_0 40 2_ 5m i l_ s h or t

C459 .1U_X7R_ 10V_04

R91 34 .8K_04

R 75 3 00 _04

C463

4. 7U _ 6. 3V _0 6

R84

300 _ 0 4

R95

10K_04

C474

10 00P _ X7R _ 50 V_ 04

R90 20K_04

R83

4. 7K _ 04

R312

0_ 04

R 189

300 _ 0 4

R322

*10K_04

R299

4. 7K _ 04

C464

.2 2U _ 16 V_ 06

LD T _R S T#

C84

390 0P _X 7R _ 50 V_ 04

R47

*0_ 040 2_ 5m i l _sh or t

L4 8 F C M 16 08K T-3 00 T07

R323

10K_04

R62

169_1%_04

R 315

*0_0402_5m il_s hort

R46

*0_ 040 2_ 5m i l _sh or t

R 2 79 * 0_0 40 2_ 10m il _s hor t

C76

39 0 0 P_ X7 R _5 0 V_ 0 4

1. 8V

1.8V

LDT_RST#

1.8VS

2. 5V _C P U

1.8V

1. 8 V

VDD3

TH M _ VD D

1.8VS

1.8VS

pl a ce th e m to C P U w ith in 1 .5"

THM_VDD

3. 3 V

LDT_RST#_HDT

3. 3 V

3. 3 VS

3. 3V S

CPU_VDD1

CPU_VDD0

CPU_VDDNB

3.3VS

1. 2 VS

1. 8V

1. 8 V

1. 8 V

CPU_ SVC 27

CPU_MEMHOT# 7,8

CPU_THERMTRIP# 15

CPU_ CLKP2

CPU_ CLKN2

CPU_ SVD 27

SCLK315

SD A T A315

CPU_LDT_STOP#10 ,14

CPU_LDT_RST #14

SMC_CPU_ THERM 2 4

CPU_LDT_ REQ#10

CPU_PWRGD14

THERM_ALERT# 15,24

SMD_CPU_ THERM 2 4

CPU_V DD1_RUN_ FB _H27

CPU_V DD0_RUN_ FB _L27

CPU_V DD1_RUN_ FB _L27

CPU_VDDNB_RUN_FB_H 2 7

CPU_VDDNB_RUN_FB_L 27

CPU_V DD0_RUN_ FB _H27

CPU_PWRGD_SVID_REG 27

CPU_PROCHOT# 14

CPU_SVC_R

Z0502

Z0 5 0 3

Z0 50 5

CPU_PWRGD_SVID_ RE G

CPU_ALERT

Nea r to

ADM 1032

10 MILE

Layo ut Note :

Route H_THERMDA and

H_TH ERM DC o n s ame laye r.

10 m il trac e o n 10 mil

spac ing .

10 MILE

PWRGD

20 m il

Thermal IC

CPU_TDI

CPU_TMS

CPU_DBREQ#

CPU_TDO

CPU_DBRDY

CPU_TCK

LDT_RST#_HDT

CPU_TRST#

KE Y

J1

*AS P-68200-0 7

1

19

21

23

2

4

6

8

10

12

3

14

16

18

20

22

24

26

5

7

9

11

13

15

17

CP U_ DB RE Q #

PWRGD

2008/03/24

Z05 01

CPU_LDT_ REQ#

CPU_ CLKIN_SC_P

CPU_ CLKIN_SC_N

LDT_RST#

CPU_TDO

CPU_DBREQ#

C P U _ TE ST 25 _L _B Y PA S SCL K _L

H_THERMDA

CLOSE TO SOC KET

CLOSE TO SOCKET

H_THERMDC

CPU_PROCHOT# _R

CPU_TEST28_ L_PL LCHRZ_N

CPU_TEST17_ BP3

CPU_TES T 8_DI G_ T

CPU_TEST28_ H_PLL CHRZ_P

CPU_TEST16_ BP2

CPU_TEST10_ ANALOGOUT

CPU_TEST29_L_FBCLKOUT_N

CPU_TEST15_ BP1

CPU_TEST7_ANALOG_T

CPU_TEST14_ BP0

C P U _T ES T 29_ H _F B C LK O U T_ P

VDDA

250mA

CPU_SID

CPU_HTREF1

CPU_SIC

CPU_TEST25_H_BYPASSCLK_H

LDT_STOP#

CPU_SVC_R

H_THERMDA

H_THERMDC

PWRGD

CPU_SVC

CPU_SVD_R

CPU_TEST12_SCANSHIFTENB

CPU_TEST9_ANALOGIN

CPU_TDI

CPU_TEST20_SCANCL K 2

CPU_TEST27_SINGLECHAIN

CPU_TRST#

CPU_TEST23_TSTUPD

CPU_SVD

CPU_TEST21_SCANEN

CPU_DBRDY

CPU_TMS

CPU_TCK

CPU_TEST6_DIECRACKMON

CPU_TEST22_SCANSHIFTEN

CPU_TEST24_SCANCL K 1

C P U _T E ST 18 _P LLT E ST 1

C P U _T E ST 19 _P LLT E ST 0

PW RGD1

CPU_ LDT_REQ#

CPU_THERMDC

CPU_THERMDA

CPU_SID

CPU_SIC

VID Override Circuit

LDT_STOP#

AMD CHECK

tolerance 10% 1113

PWRGD

HDT Connector

1.8V

Kno w n low tem per ature PG issue,

Replace w ith anot her par t

PWRGD

CPU-3

B.Schematic Diagrams

B - 6 CPU-3

CPU-4

Sheet 6 of 35

CPU-4

C594

* 1 0U _6 . 3 V _ 0 6

VDDIO

2A

C5 95

*10U _6.3V_06

C596

*1 0 U_ 6 .3 V _06

C129

4.7U_6.3V _06

C1 1 4

.01U_16V_04

C121

.01U _16V_04

C125

4.7U _6.3V_06

C1 1 7

.22U_10V _04

C9 1

.22U _10V_04

C116

.22U_10V _04

U15F

SOC KET_638 _P IN

V SS1

AA4

V SS2

AA11

V SS3

AA13

V SS4

AA15

V SS5

AA17

V SS6

AA19

V SS7

AB2

V SS8

AB7

V SS9

AB9

V SS10

AB23

V SS11

AB25

V SS12

AC 11

V SS13

AC 13

V SS14

AC 15

V SS15

AC 17

V SS16

AC 19

V SS17

AC 21

V SS18

AD6

V SS19

AD8

V SS20

AD 25

V SS21

AE11

V SS22

AE13

V SS23

AE15

V SS24

AE17

V SS25

AE19

V SS26

AE21

V SS27

AE23

V SS28

B4

V SS29

B6

V SS30

B8

V SS31

B9

V SS32

B11

V SS33

B13

V SS34

B15

V SS35

B17

V SS36

B19

V SS37

B21

V SS38

B23

V SS39

B25

V SS40

D6

V SS41

D8

V SS42

D9

V SS43

D11

V SS44

D13

V SS45

D15

V SS46

D17

V SS47

D19

V SS48

D21

V SS49

D23

V SS50

D25

V SS51

E4

V SS52

F2

V SS53

F11

V SS54

F13

V SS55

F15

V SS56

F17

V SS57

F19

V SS58

F21

V SS59

F23

V SS60

F25

V SS61

H7

V SS62

H9

V SS63

H21

V SS64

H23

V SS65

J4

VSS 66

J6

VSS 67

J8

VSS 68

J10

VSS 69

J12

VSS 70

J14

VSS 71

J16

VSS 72

J18

VSS 73

K2

VSS 74

K7

VSS 75

K9

VSS 76

K11

VSS 77

K13

VSS 78

K15

VSS 79

K17

VSS 80

L6

VSS 81

L8

VSS 82

L10

VSS 83

L12

VSS 84

L14

VSS 85

L16

VSS 86

L18

VSS 87

M7

VSS 88

M9

VSS 89

AC 6

VSS 90

M17

VSS 91

N4

VSS 92

N8

VSS 93

N10

VSS 94

N16

VSS 95

N18

VSS 96

P2

VSS 97

P7

VSS 98

P9

VSS 99

P11

V SS1 00

P17

V SS1 01

R8

V SS1 02

R10

V SS1 03

R16

V SS1 04

R18

V SS1 05

T7

V SS1 06

T9

V SS1 07

T11

V SS1 08

T13

V SS1 09

T15

V SS1 10

T17

V SS1 11

U4

V SS1 12

U6

V SS1 13

U8

V SS1 14

U10

V SS1 15

U12

V SS1 16

U14

V SS1 17

U16

V SS1 18

U18

V SS1 19

V2

V SS1 20

V7

V SS1 21

V9

V SS1 22

V11

V SS1 23

V13

V SS1 24

V15

V SS1 25

V17

V SS1 26

W6

V SS1 27

Y21

V SS1 28

Y23

V SS1 29

N6

C6 5

180P_N PO_50V_04

C78

. 0 1 U _ 1 6V _0 4

C120

*4.7U _6.3V_06

C9 4

.22U _10V_04

C1 2 4

*.22U_10V _04

C112

180P_X7R_50V_04

C1 1 8

.22U_10V _04

C128

4. 7 U _6 . 3 V _ 06

C111

*.22U _10V_04

C110

180P_N PO_50V_04

C113

180P_X7R_50V_04

U15E

SOCKET_638_PIN

VDD 1_25

AC4

VDD 1_26

AD2

VD D0_1

G4

VD D0_2

H2

VD D0_3

J9

VD D0_4

J11

VD D0_5

J13

VD D0_7

K6

VD D0_8

K10

VD D0_9

K12

VD D0_10

K14

VD D0_11

L4

VD D0_12

L7

VD D0_13

L9

VD D0_14

L11

VD D0_15

L13

VD D0_17

M2

VD D0_18

M6

VD D0_19

M8

VD D0_20

M1 0

VD D0_21

N7

VD D0_22

N9

VD D0_23

N1 1

VDD1_1

P8

VDD1_2

P10

VDD1_3

R4

VDD1_4

R7

VDD1_5

R9

VDD1_6

R1 1

VDD1_7

T2

VDD1_8

T6

VDD1_9

T8

VDD 1_10

T10

VDD 1_11

T12

VDD 1_12

T14

VDD 1_13

U7

VDD 1_14

U9

VDD 1_15

U1 1

VDD 1_16

U1 3

VDD 1_18

V6

VDD 1_19

V8

VDD 1_20

V10

VDD 1_21

V12

VDD 1_22

V14

VDD 1_23

W4

VDD 1_24

Y2

VD D0_6

J15

VD DNB _1

K16

VD D0_16

L15

VD DNB _2

M1 6

VD DNB _3

P16

VD DNB _4

T16

VDD 1_17

U1 5

VD DNB _5

V16

VD DIO1

H2 5

VD DIO2

J17

VD DIO3

K18

VD DIO4

K21

VD DIO5

K23

VD DIO6

K25

VD DIO7

L17

VD DIO8

M1 8

VD DIO9

M2 1

VD DIO10

M2 3

VD DIO11

M2 5

VD DIO12

N1 7

VDD IO13

P18

VDD IO14

P21

VDD IO15

P23

VDD IO16

P25

VDD IO17

R1 7

VDD IO18

T18

VDD IO19

T21

VDD IO20

T23

VDD IO21

T25

VDD IO22

U1 7VDD IO23

V18

VDD IO24

V21

VDD IO25

V23

VDD IO26

V25

VDD IO27

Y25

C3 4

10U _6.3V_06

C98

. 0 1 U _ 1 6V _0 4

C104

.22U_10V_04

C5 97

*10U _6.3V_06

C7 7

180P_NP O_50V_04

CPU _V D D0

CP U_ VDD 1

1.8V

CPU_VDDNB

CPU _ VDD 1

CP U_ VDD NB 1. 8 V

1.8V

1.8V

CP U_ VDD 0

C79

10U_6.3V _06

C93

10U_6.3V_06

BOTTOM SIDE DECOUPLING

C103

10U_6.3V_06

C9 2

10U_6.3V_06

PLACE C LO SE TO PROCES SOR AS PO SSIBLE

DECOUPLING BETWEEN PROCESSOR AND DIMMs

C100

10U_6. 3V_06

C97

10U _6. 3V_06

C99

10U _6.3V_06

C35

10U_6.3V _06

C1 02

10U_6.3V_06

VDDI O

2A

CPU _VDDN B

3A

C133

10U_6.3V _06

VD D1 CORE

1.37 5-1.500 V

18 A

VDD0 CORE

0.37 5-1.5 00V

18A

C132

10U_6.3V_06

Schematic Diagrams

B.Schematic Diagrams

CPU-4 B - 7

Schematic Diagrams

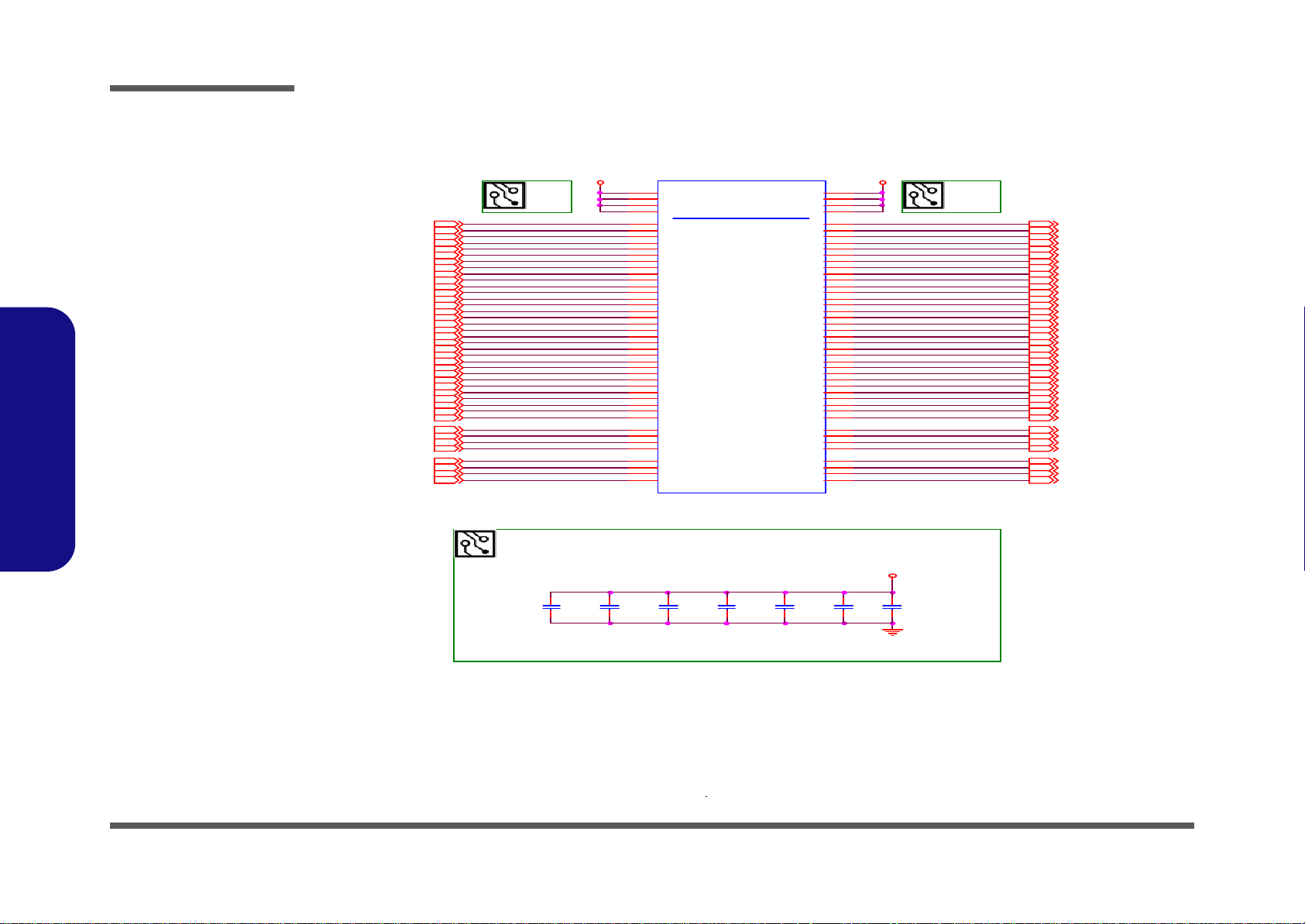

Sheet 7 of 35

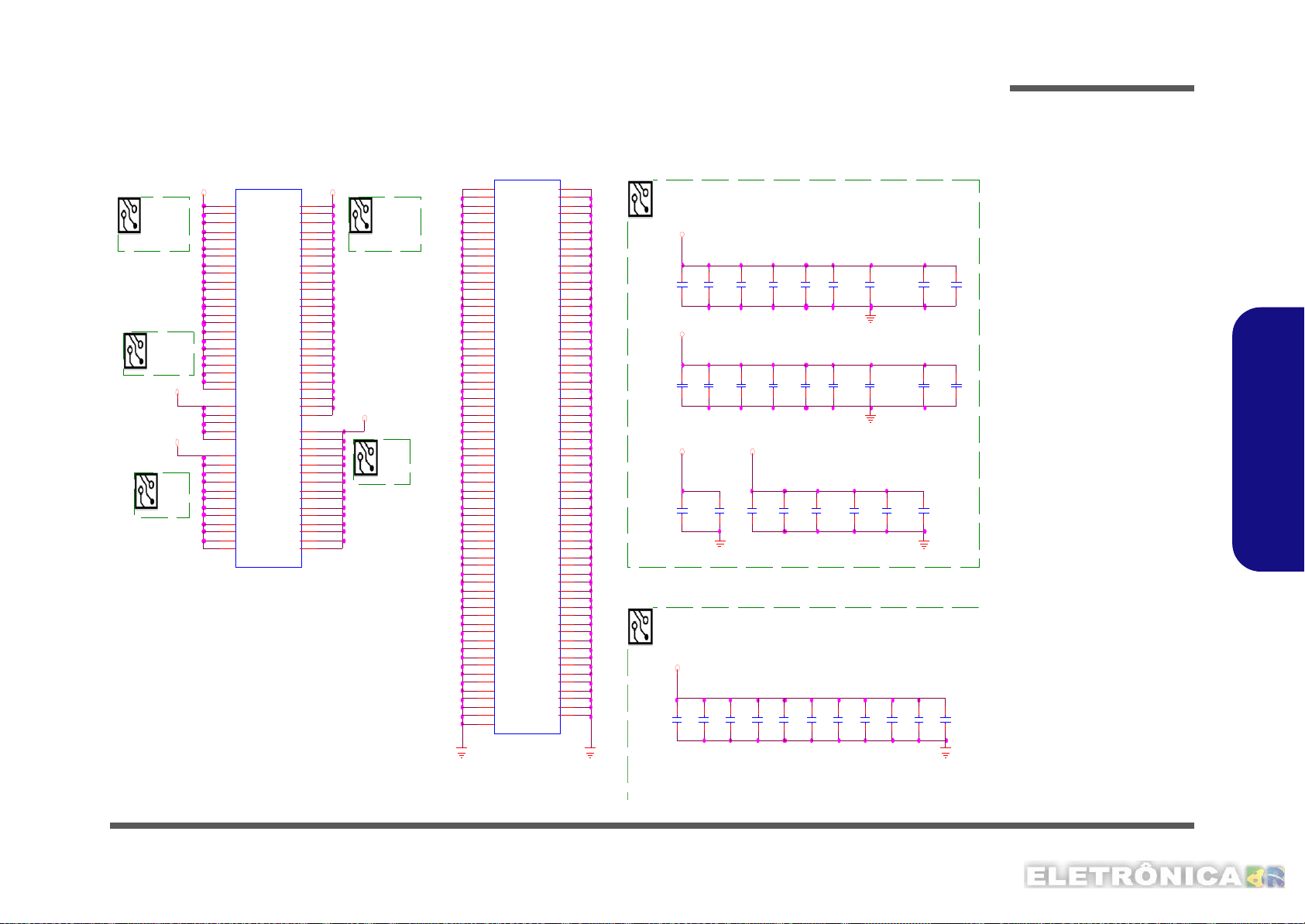

DDRII SO-DIMM_0

20mils

20mils

MEM_ MA_BA N K2

SO- DI MM 0

MEM_ MA_AD D9

CLO SE TO SO-D IMM _0

MEM_ MA_AD D12

Width 20 mil ,len gth <6 inch

MVR EF _DI M

Z0704

Z0702

MEM_ MA_AD D8

Z0703

MEM_ MA_B A N K2

MEM_ MA_B A N K0

MEM_ MA_AD D1

MEM_ MA_AD D5

MEM_ MA_AD D3

MEM_ MA_AD D10

MEM_ MA_BA N K0

MEM_MA_DA T A20

MEM_MA_DA T A55

MEM_MA_DA T A30

MEM _MA_DQ S 0_ N

MEM_MA_DA T A63

MEM_MA_DA T A52

MEM_MA_DA T A3

MEM_MA_DA T A40

MEM_MA_DA T A31

MEM _MA_CL K7_N

MEM_ MA_ DM3

MEM_MA_DA T A1

MEM_MA_DA T A38

MEM_MA_DA T A57

MEM _MA_DQ S 0_ P

MEM_MA_DA T A25

MEM_MA_DA T A47

MEM_MA_DA T A6

MEM_MA_DA T A5

MEM _MA_DQ S 6_ N

MEM_MA_DA T A61

MEM_MA_DA T A8

MEM _MA_DQ S 5_ P

MEM _MA_DQ S 1_ N

MEM_ MA_ DM1

MEM_MA_DA T A48

MEM_MA_DA T A56

MEM_MA_DA T A49

MEM_MA_DA T A62

MEM_ MA0_C S#1

MEM_MA_DA T A41

MEM_MA_DA T A13

MEM_MA_DA T A19

MEM _MA_DQ S 4_ N

MEM_ MA_ DM5

MEM_MA_DA T A14

MEM_MA_DA T A58

MEM _MA_CL K7_P

SA 1 _ D I M0 _ 1

MEM_ MA_ DM7

MEM _MA_CL K1_N

MEM _MA_CL K1_P

MEM_ MA_ DM4

MEM _MA_DQ S 7_ N

MEM_ MA0_O D T1

MEM_MA_DA T A32

MEM_MA_DA T A26

MEM_MA_DA T A23

MEM_MA_DA T A11

MEM _MA_DQ S 2_ P

SD A T A0

MEM_ MA_ DM0

MEM_MA_DA T A18

MEM_MA_DA T A15

MEM_MA_DA T A7

MEM_MA_DA T A51

MEM_MA_DA T A0

MEM_MA_DA T A60MEM _MA_DQ S 3_ N

MEM _MA_CK E 0

MEM_ MA_W E#

MEM_ MA_ DM6

MEM_MA_DA T A29

MEM_MA_DA T A45

MEM_ MA_RA S #

MEM _MA_DQ S 7_ P

MEM_MA_DA T A4

MEM_MA_DA T A9

MEM_MA_DA T A42

SC L K 0

MEM _MA_DQ S 6_ P

MEM_MA_DA T A33

MEM_MA_DA T A37

MEM_MA_DA T A39

MEM_MA_DA T A21

MEM_MA_DA T A2

SA 0 _ D I M0 _ 1

MEM_ MA0_O D T0

MEM _MA_DQ S 2_ N

MEM_MA_DA T A34

MEM_MA_DA T A24

MEM_MA_DA T A46

MEM_MA_DA T A12

MEM_ MA_CA S #

MEM _MA_DQ S 4_ P

MEM_MA_DA T A22

MEM_MA_DA T A16

MEM_MA_DA T A44

MEM_MA_DA T A10

MEM _MA_CK E 1

MEM_ MA_ DM2

MEM _MA_DQ S 5_ N

MEM_MA_DA T A17

MEM_MA_DA T A35

MEM_MA_DA T A54

MEM_MA_DA T A43

MEM_MA_DA T A28

MEM_MA_DA T A36

MEM_MA_DA T A50

MEM_MA_DA T A27

MEM_MA_DA T A59

MEM _MA_DQ S 1_ P

MEM _MA_DQ S 3_ P

MEM_ MA0_C S#0

MEM_MA_DA T A53

MEM_ MA_AD D15

MEM_ MA_A D D5

MEM_ MA_A D D11

MEM_ MA_A D D1

MEM_ MA_A D D9

MEM_ MA_A D D13

MEM_ MA_A D D7

MEM_ MA_A D D2

MEM_ MA_A D D0

MEM_ MA_A D D3

MEM_ MA_A D D8

MEM_ MA_A D D4

MEM_ MA_A D D10

MEM_ MA_A D D6

MEM_ MA_A D D12

MEM_ MA_AD D14

MEM_ MA_AD D7

R109

1K _1 %_ 04

C191

*10 U _1 0V _0 8

RN14

4P2RX47_04

1 4

2 3

C179

1 0U _ 10 V_ 08

R113

*1 0K _0 4

C177

. 1U _ X7 R _10 V _04

C123

*. 1U _ X7 R _1 0V _0 4

C150

1U_6.3 V _04

MEM_ MA_A D D15

C147

.22U_X7 R_06

RN6

4P2RX47_04

14

23

C174

. 1U _ X7 R _10 V _04

C 1 85 *. 1U _ X7 R _1 0V _0 4

C 1 68 . 1U _ X7 R _10 V _04

C158

.1U_X7R_10V_04

C 1 63 *. 1U _ X7 R _1 0V _0 4

C 1 87 *. 1U _ X7 R _1 0V _0 4

MEM_ MA_AD D11

RN2

4P2RX47_04

14

23

R 110 * 0 _04

C122

. 1U _ X7 R _10 V _04

C109

.1 U _X 7R _ 10 V_ 04

C 1 84 . 1U _ X7 R _10 V _04

C106

1. 5P _ X7R _ 50 V _04

RN4

4P2RX47_04

14

23

J_D IMM_1 B

1-7 34 074 - 1

VDD1

112

VDD2

111

VDD3

117

VDD4

96

VDD5

95

VDD6

118

VDD7

81

VDD8

82

VDD9

87

VDD10

103

VDD11

88

VDD12

104

VDDSPD

199

NC1

83

NC2

120

NC3

50

NC4

69

NCTEST

163

VREF

1

GND0

201

GND1

202

VSS1

47

VSS2

133

VSS3

183

VSS4

77

VSS5

12

VSS6

48

VSS7

184

VSS8

78

VSS9

71

VSS10

72

VSS11

121

VSS12

122

VSS13

196

VSS14

193

VSS15

8

VSS1 6

18

VSS1 7

24

VSS1 8

41

VSS1 9

53

VSS2 0

42

VSS2 1

54

VSS2 2

59

VSS2 3

65

VSS2 4

60

VSS2 5

66

VSS2 6

12 7

VSS2 7

13 9

VSS2 8

12 8

VSS2 9

14 5

VSS3 0

16 5

VSS3 1

17 1

VSS3 2

17 2

VSS3 3

17 7

VSS3 4

18 7

VSS3 5

17 8

VSS3 6

19 0

VSS3 7

9

VSS3 8

21

VSS3 9

33

VSS4 0

15 5

VSS4 1

34

VSS4 2

13 2

VSS4 3

14 4

VSS4 4

15 6

VSS4 5

16 8

VSS4 6

2

VSS4 7

3

VSS4 8

15

VSS4 9

27

VSS5 0

39

VSS5 1

14 9

VSS5 2

16 1

VSS5 3

28

VSS5 4

40

VSS5 5

13 8

VSS5 6

15 0

VSS5 7

16 2

C152

. 1U_X 7R_ 10 V_ 04

C 1 72 . 1U _ X7 R _10 V _04

R112

1K_1%_04

R123

10K _ 04

MEM_ MA_A D D14

RN15

4P2RX47_04

1 4

2 3

C149

*.22U _X7R _06

C 1 76 *. 1U _ X7 R _1 0V _0 4

RN7

4P2RX47_04

14

23

C 146

10U_ 10 V_ 08

RN12

4P2RX47_04

1 4

2 3

C101

1.5P_X7R_50V_04

C 1 78 . 1U _ X7 R _10 V _04

R125

*0_ 04 02_ 5m il _s ho rt

C134

*. 1 U F_ 16 V _04

C154

.1U_X7R_10V_04

C162

1U_6.3V_04

MEM_ MA_AD D6

C190

.1U_X7R_10V_04

R126

10 K _04

C 1 83 *. 1U _ X7 R _1 0V _0 4

C 1 69 . 1U _ X7 R _10 V _04

C170

*4 . 7U _ 6. 3V _0 6

R111 0_04

C161

.1U_X7R_10V_04

C160

1000P_X7R_50V_04

C151

.01U_16 V _04

C126

*.1U_X7R_10V_04

C 1 73 *. 1U _ X7 R _1 0V _0 4

RN10

4P2RX47_04

1 4

2 3

C182

*1 U_6.3V_04

C165

10U_10V_08

C 1 75 . 1U _ X7 R _10 V _04

+

-

U3B

*L M 35 8

5

6

7

84

RN8

4P2RX47_04

14

23

R108 *0_04

RN13

4P2RX47_04

1 4

2 3

J_D IMM_1 A

1-7 34 074 - 1

A0

102

A1

101

A2

100

A3

99

A4

98

A5

97

A6

94

A7

92

A8

93

A9

91

A10/AP

105

A11

90

A12

89

A13

116

A14

86

A15

84

A 1 6_B A 2

85

DQ0

5

DQ1

7

DQ2

17

DQ3

19

DQ4

4

DQ5

6

DQ6

14

DQ7

16

DQ8

23

DQ9

25

DQ10

35

DQ11

37

DQ12

20

DQ13

22

DQ14

36

DQ15

38

DQ16

43

DQ17

45

DQ18

55

DQ19

57

DQ20

44

DQ21

46

DQ22

56

DQ23

58

DQ24

61

DQ25

63

DQ26

73

DQ27

75

DQ28

62

DQ29

64

DQ30

74

DQ31

76

DQ32

12 3

DQ33

12 5

DQ34

13 5

DQ35

13 7

DQ36

12 4

DQ37

12 6

DQ38

13 4

DQ39

13 6

DQ40

14 1

DQ41

14 3

DQ42

15 1

DQ43

15 3

DQ44

14 0

DQ45

14 2

DQ46

15 2

DQ47

15 4

DQ48

15 7

DQ49

15 9

DQ50

17 3

DQ51

17 5

DQ52

15 8

DQ53

16 0

DQ54

17 4

DQ55

17 6

DQ56

17 9

DQ57

18 1

DQ58

18 9

DQ59

19 1

DQ60

18 0

DQ61

18 2

DQ62

19 2

DQ63

19 4

BA0

107

BA1

106

RAS#

108

WE#

109

CAS#

113

S0#

110

S1#

115

CKE0

79

CKE1

80

CK0

30

CK0 #

32

CK1

164

CK1 #

166

SDA

195

SCL

197

SA1

200

SA0

198

DM0

10

DM1

26

DM2

52

DM3

67

DM4

130

DM5

147

DM6

170

DM7

185

DQS0

13

DQS1

31

DQS2

51

DQS3

70

DQS4

131

DQS5

148

DQS6

169

DQS7

188

DQS0#

11

DQS1#

29

DQS2#

49

DQS3#

68

DQS4#

129

DQS5#

146

DQS6#

167

DQS7#

186

ODT 0

114

ODT 1

119

MEM_ MA_AD D4

C156

*. 1U _ X7 R _1 0V _0 4

C153

4. 7 U _6 .3V_06

C 1 88 . 1U _ X7 R _10 V _04

C130

.1U_X7R_10V_04

C140

1000PF_50V_04

R104

*1 0_ 04 _1%

RN3

4P2RX47_04

14

23

C148

1 0U _ 10 V_ 08

C171

. 1U _ X7 R _10 V _04

RN11

4P2RX47_04

1 4

2 3

C155

.1U_X7R _10V_04

C 1 81 *. 1U _ X7 R _1 0V _0 4

C 127

.01U_16V_ 04

C 159

2. 2U _ 6. 3V _ 06

+

C167

100U_6.3V_B2

RN9

4P2RX47_04

1 4

2 3

RN5

4P2RX47_04

14

23

C 1 86 . 01 U _1 6V _0 4

C189

2. 2U _6. 3 V_ 06

C157

*. 1U _ X7 R _1 0V _0 4

C 1 64 *. 1U _ X7 R _1 0V _0 4

0. 9V

1. 8V

1.8V

3.3VS

1.8V

1.8V

1.8V

1.8V

0. 9 V

1.8V

1.8V

1.8V

1.8V

1. 8 V

1.8V

1.8V

1.8V

MEM_ MA_AD D2

3.3V

MVREF_DIM

MEM_ MA_DQ S 7_ P4

MEM_MA0_ OD T04

MEM_MA0_ OD T14

MVREF _ DIM

MEM_MA0 _CS#04

MEM_ MA_DQ S 1_ P4

MEM_ MA_DQ S 3_ P4

MEM_ MA_DQ S 6_ P4

MEM_ MA_DQ S 4_ P4

MEM_ MA_DQ S 5_ P4

MEM_ MA_DQ S 2_ P4

MEM_ MA_DQ S 0_ P4

MEM_MA_C KE04

MEM_MA_ CLK7_ N4

MEM_MA_C KE14

MEM_MA0 _CS#14

MEM_ MA_DQ S 0_ N4

MEM_ MA_DQ S 4_ N4

MEM_ MA_DQ S 7_ N4

MEM_ MA_DM[ 0..7 ]4

MEM_ MA_DQ S 3_ N4

MEM_ MA_DQ S 5_ N4

MEM_ MA_DQ S 6_ N4

MEM_MA_ ADD[0 ..15]4

MEM_ MA_DQ S 2_ N4

MEM_ MA_DQ S 1_ N4

MEM_MA_ CLK1_ P4

MEM_MA_ CLK1_ N4

MEM_MA_ CLK7_ P4

MEM_MA_ CLK1_ N4

CPU_MEMHOT#5,8

MEM_MA_BA N K[0..2]4

MEM_ MA_W E#4

MEM_MA_ CLK7_ P4

MEM_MA_ CLK7_ N4

MEM_MA_ CLK1_ P4

SC L K 02,8,15

MEM_ MA_CA S#4

MEM_ MA_RA S#4

MEM_MA_ CKE04

MEM_MA0 _CS#14

SD A T A02,8,15

MEM_MA0 _ODT14

MEM_MA_ WE#4

MEM_MA_ CKE14

MEM_MA0 _CS#04

MEM_MA0 _ODT04

M EM_ MA_D A TA[ 0..63 ] 4

MEM_MA_ CAS#4

MEM_MA_ RAS#4

MEM_ MA_AD D0

MEM_ MA_BA N K1

MEM_ MA_AD D13

PLACE CLO SE TO PR OCESSOR

WITHIN 1 .5 INC H

PLACE CLOSE TO SO CKET( PER EM I/EM C )

Z07 01

MEM_ MA_B A N K1

tole ran ce 10% 11 13

tole ran ce 10% 11 13

MVRE F_DIM

DIMM0_GND1

DIMM0_GND0

B.Schematic Diagrams

B - 8 DDRII SO-DIMM_0

DDRII SO-DIMM_0

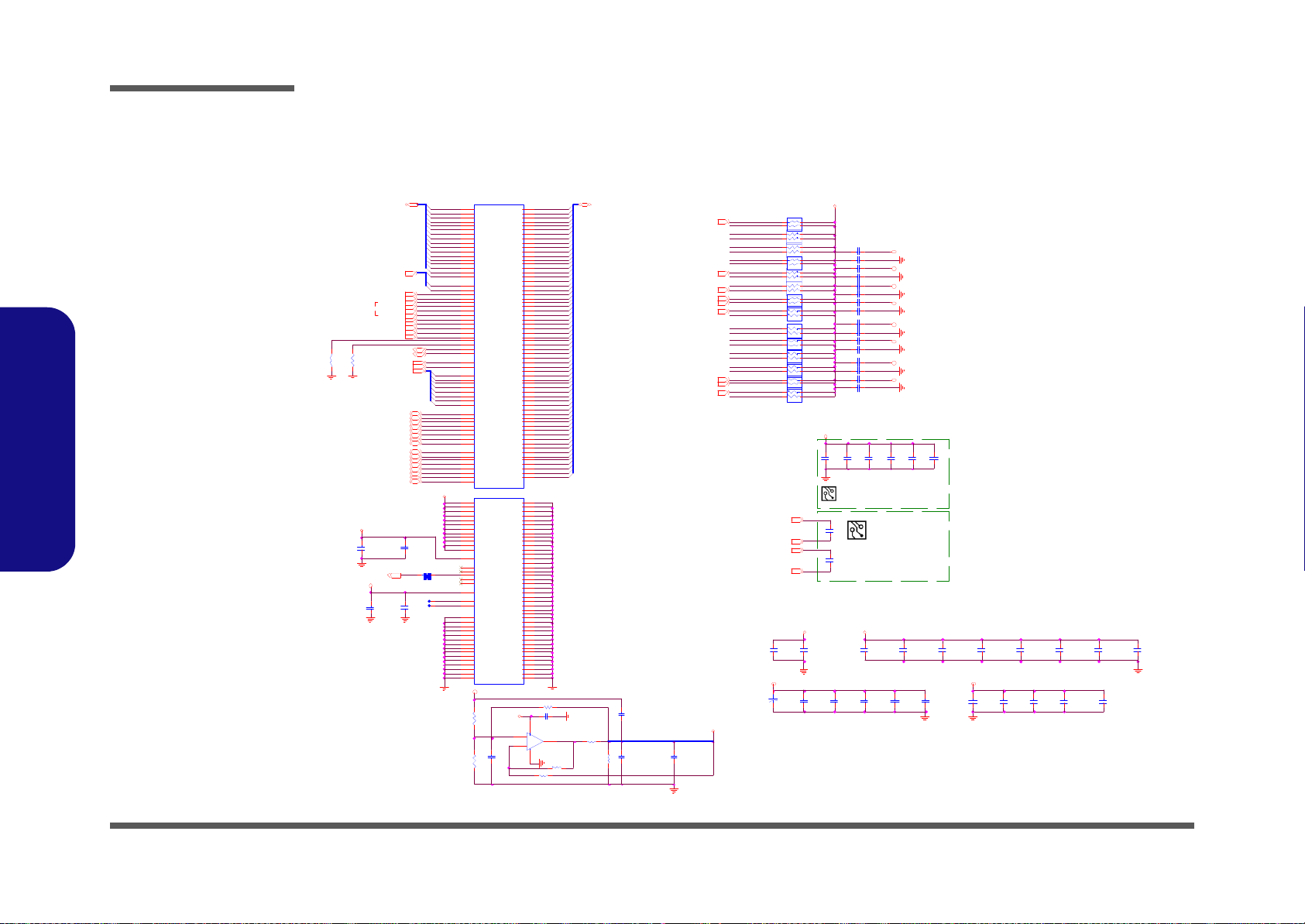

DDRII SO-DIMM_1

Sheet 8 of 35

DDRII SO-DIMM_1

20 m i ls

20 m i ls

M EM_MB _BAN K 2

M EM_MB _ADD 1 2

M EM_MB _ADD 9

MEM_ MB _ADD 2

MEM_ MB _ADD 1 4

MEM_ MB _RAS #

MEM_ MB _BAN K 2

MEM_ MB _CL K 1_ P

MEM_ MB _ADD 3

MEM_ MB _CKE 0

MEM_ MB _CL K 7_ N

M EM_MB _ADD 8

MEM_ MB _CAS #

MEM_ MB _ADD 9

MEM_ MB _BAN K 0

MEM_ MB _CL K 1_ N

MEM_ MB _ADD 6

MEM_ MB _ADD 1 3

MEM_ MB _CKE 1

MEM_ MB _ADD 7

MEM_ MB _W E #

MEM_ MB _ADD 0

MEM_ MB _ADD 4

MEM_ MB 0_C S #0

MEM_ MB 0_C S #1

MEM_ MB _ADD 1 2

MEM_ MB _BAN K 1

MEM_ MB _ADD 8

MEM_ MB _ADD 5

MEM_ MB _ADD 1 5

MEM_ MB _ADD 1 0

MEM_ MB _ADD 1 1

MEM_ MB _ADD 1

MEM_ MB _CL K 7_ P

M EM_MB _ADD 5

PLAC E C LOSE TO P ROCESSOR

W IT HIN 1 .5 INCH

PLAC E CLOSE TO SOCK ET( P ER EM I/EM C)

M EM_MB _ADD 3

M EM_MB _ADD 1

M EM_MB _ADD 1 0

M EM_MB _BAN K 0

M EM_MB _ADD 1 4

M EM_MB _ADD 1 5

M EM_MB _ADD 7

M EM_MB _ADD 1 1

M EM_MB _ADD 6

M EM_MB _ADD 1 3

SDATA0

Z0801

SCLK0

SA0_DIM1_ 1

MEM_M B_D A TA1 3

MEM_M B_D A TA2 8

MEM_M B_D A TA5 6

MEM_M B_D A TA4 6

MEM_M B_D A TA2 4

MEM_M B_D A TA1 1

MEM_M B_D A TA3 1

MEM_M B_D A TA6 1

MEM_M B_D A TA2 2

MEM_M B_D A TA1 9

MEM_M B_D A TA4 0

MEM_M B_D A TA5 8

MEM_M B_D A TA5 0

MEM_M B_D A TA2

MEM_M B_D A TA5 4

MEM_M B_D A TA6 3

MEM_M B_D A TA1

MEM_M B_D A TA5 7

MEM_M B_D A TA6 0

MEM_M B_D A TA4 1

MEM_M B_D A TA3 7

MEM_M B_D A TA4 4

MEM_M B_D A TA3 0

MEM_M B_D A TA9

MEM_M B_D A TA3 4

MEM_M B_D A TA1 7

MEM_M B_D A TA2 5

MEM_M B_D A TA5

MEM_M B_D A TA3 8

MEM_M B_D A TA7

MEM_M B_D A TA3

MEM_M B_D A TA2 7

MEM_M B_D A TA3 6

MEM_M B_D A TA5 9

MEM_M B_D A TA4 3

MEM_M B_D A TA4 7

MEM_M B_D A TA8

MEM_M B_D A TA3 5

MEM_M B_D A TA3 3

MEM_M B_D A TA6 2

MEM_M B_D A TA4

MEM_M B_D A TA1 5

MEM_M B_D A TA2 6

MEM_M B_D A TA4 2

MEM_M B_D A TA4 8

MEM_M B_D A TA2 9

MEM_M B_D A TA4 5

MEM_M B_D A TA5 5

MEM_M B_D A TA1 6

MEM_M B_D A TA5 3

MEM_M B_D A TA1 0

MEM_M B_D A TA5 2

MEM_M B_D A TA1 8

MEM_M B_D A TA1 2

MEM_M B_D A TA0

MEM_M B_D A TA6

SA1_DIM1_ 1

MEM_M B_D A TA2 0

MEM_M B_D A TA3 9

MEM_M B_D A TA4 9

MEM_M B_D A TA2 1

MEM_M B_D A TA5 1

MEM_M B_D A TA2 3

MEM_M B_D A TA3 2

MEM_M B_D A TA1 4

DIMM1_G ND0

DIMM1_G ND1

MVREF_DIM

RN20

4P 2R X4 7_ 04

14

23

RN16

4P 2R X4 7_ 04

14

23

C231

. 22 U _X 7R _ 06

C244

1U_6.3V_04

C228 .1U_X7R_10V_04

C221 *.1U_X7R_10V_04

C519

.1U_X7R_ 10V_04

R132

0_ 04

RN28

4P 2R X4 7_ 04

1 4

2 3

C218 .1U_X7R_10V_04

+

C515

*220U_ 4V_ D

C225 *.1U_X7R_10V_04

R131

*0_0402_5mil_short

RN25

4P 2R X4 7_ 04

1 4

2 3

RN17

4P 2R X4 7_ 04

14

23

C215

.1U_X7R_10V_04

C205 *.1U_X7R_10V_04

C234

*4.7U_6.3V_06

C224 .1U_X7R_10V_04

C199

4. 7 U _6 . 3V _0 6

C210

*.1 U _X 7R _1 0V _0 4

C211 .1U_X7R_10V_04

RN22

4P 2R X4 7_ 04

14

23

C243

1U _6 .3V_04

C212 *.1U_X7R_10V_04

RN24

4P 2R X4 7_ 04

1 4

2 3

C206

*.1U_X7R_10V_04

C229

10 U _ 10 V_ 08

C217

.1U_X7R_10V_04

C242

*10U_10V_08

C227 *.1U_X7R_10V_04

C197

.1U_X7R_10V_04

C207 .1U_X7R_10V_04

C517

.1U_X7R_10V_04

RN18

4P 2R X4 7_ 04

14

23

RN23

4P 2R X4 7_ 04

1 4

2 3

C108

1. 5 P _X 7R _ 50 V_ 04

RN27

4P 2R X4 7_ 04

1 4

2 3

J_D I MM_2A

2- 17 34 07 2- 2

A0

10 2

A1

10 1

A2

10 0

A3

99

A4

98

A5

97

A6

94

A7

92

A8

93

A9

91

A10/AP

10 5

A11

90

A12

89

A13

11 6

A14

86

A15

84

A16_BA2

85

DQ0

5

DQ1

7

DQ2

17

DQ3

19

DQ4

4

DQ5

6

DQ6

14

DQ7

16

DQ8

23

DQ9

25

DQ10

35

DQ11

37

DQ12

20

DQ13

22

DQ14

36

DQ15

38

DQ16

43

DQ17

45

DQ18

55

DQ19

57

DQ20

44

DQ21

46

DQ22

56

DQ23

58

DQ24

61

DQ25

63

DQ26

73

DQ27

75

DQ28

62

DQ29

64

DQ30

74

DQ31

76

DQ32

12 3

DQ33

12 5

DQ34

13 5

DQ35

13 7

DQ36

12 4

DQ37

12 6

DQ38

13 4

DQ39

13 6

DQ40

14 1

DQ41

14 3

DQ42

15 1

DQ43

15 3

DQ44

14 0

DQ45

14 2

DQ46

15 2

DQ47

15 4

DQ48

15 7

DQ49

15 9

DQ50

17 3

DQ51

17 5

DQ52

15 8

DQ53

16 0

DQ54

17 4

DQ55

17 6

DQ56

17 9

DQ57

18 1

DQ58

18 9

DQ59

19 1

DQ60

18 0

DQ61

18 2

DQ62

19 2

DQ63

19 4

BA0

10 7

BA1

10 6

RAS#

10 8

WE#

10 9

CAS#

11 3

S0#

11 0

S1#

11 5

CKE0

79

CKE1

80

CK0

30

CK0#

32

CK1

16 4

CK1#

16 6

SDA

19 5

SCL

19 7

SA1

20 0 SA0

19 8

DM0

10

DM1

26

DM2

52

DM3

67

DM4

13 0

DM5

14 7

DM6

17 0

DM7

18 5

DQS0

13

DQS1

31

DQS2

51

DQS3

70

DQS4

13 1

DQS5

14 8

DQS6

16 9

DQS7

18 8

DQS0 #

11

DQS1 #

29

DQS2 #

49

DQS3 #

68

DQS4 #

12 9

DQS5 #

14 6

DQS6 #

16 7

DQS7 #

18 6

ODT 0

11 4

ODT 1

11 9

C107

1. 5 P _X 7R _ 50 V_ 04

C245

10 U _1 0V _ 08

C518

.1U_X7R _10V_0 4

C230

. 22 U _X 7R _ 06

C198

2. 2 U _6 . 3V _0 6

C521

. 1U _ X7 R _ 10V _ 04

J_D I MM_2B

2- 17 34 07 2- 2

VDD1

11 2

VDD2

11 1

VDD3

11 7

VDD4

96

VDD5

95

VDD6

11 8

VDD7

81

VDD8

82

VDD9

87

VDD10

10 3

VDD11

88

VDD12

10 4

VDDSPD

19 9

NC1

83

NC2

12 0

NC3

50

NC4

69

NCTE ST

16 3

VREF

1

GND0

20 1

GND1

20 2

VSS1

47

VSS2

13 3

VSS3

18 3

VSS4

77

VSS5

12

VSS6

48

VSS7

18 4

VSS8

78

VSS9

71

VSS1 0

72

VSS1 1

12 1

VSS1 2

12 2

VSS1 3

19 6

VSS1 4

19 3

VSS1 5

8

VS S 1 6

18

VS S 1 7

24

VS S 1 8

41

VS S 1 9

53

VS S 2 0

42

VS S 2 1

54

VS S 2 2

59

VS S 2 3

65

VS S 2 4

60

VS S 2 5

66

VS S 2 6

12 7

VS S 2 7

13 9

VS S 2 8

12 8

VS S 2 9

14 5

VS S 3 0

16 5

VS S 3 1

17 1

VS S 3 2

17 2

VS S 3 3

17 7

VS S 3 4

18 7

VS S 3 5

17 8

VS S 3 6

19 0

VS S 3 7

9

VS S 3 8

21

VS S 3 9

33

VS S 4 0

15 5

VS S 4 1

34

VS S 4 2

13 2

VS S 4 3

14 4

VS S 4 4

15 6

VS S 4 5

16 8

VS S 4 6

2

VS S 4 7

3

VS S 4 8

15

VS S 4 9

27

VS S 5 0

39

VS S 5 1

14 9

VS S 5 2

16 1

VS S 5 3

28

VS S 5 4

40

VS S 5 5

13 8

VS S 5 6

15 0

VS S 5 7

16 2

C200

2. 2 U _6 . 3V _0 6

C223 *.1U_X7R_10V_04

RN21

4P 2R X4 7_ 04

14

23

C226 .1U_X7R_10V_04

C201

.1U_X7R_10V_04

C214 .1U_X7R_10V_04

C203

1U _ 6. 3 V _0 4

C213

.1U_X7R_10V_04

RN26

4P 2R X4 7_ 04

1 4

2 3

C193

10U _1 0V _0 8

C520

. 1U _X 7R _ 10 V_ 04

R130

4. 7 K _0 4

C209 *.1U_X7R_10V_04

C192

10U _10V_08

RN19

4P 2R X4 7_ 04

14

23

C219

.1U_X7R_10V_04

C208

.1U_X7R_10V_04

C516

.01U_16V_04

C222 .01U_16V_04

RN29

4P 2R X4 7_ 04

1 4

2 3

+

C220

100U_6.3V_B2

C204

.1U_X7R_10V_04

C216 *.1U_X7R_10V_04

3.3VS

0. 9 V

1.8V

0.9V

3. 3 V S

1.8V

1.8V

1.8V

1.8V

1.8V

1.8V

1.8V

MEM_ MB 0_OD T1

MEM_ MB _DM6

1. 8 V

1.8V

1.8V

1.8V

MEM_ MB _DM5

MEM_ MB _DM4

M EM_ MB _CL K1_ P4

M EM_ MB _CK E 04

MVR E F_D I M

M EM_ MB 0_ C S#04

M EM_ MB _CL K7_ N4

M EM_ MB _CL K1_ N4

M EM_ MB 0_ C S#14

MEM_ MB _DM3

MEM_MB_ADD[0..15]4

M EM_ MB _CK E 14

M EM_ MB _CL K7_ P4

MEM_ MB _DM0

MEM_M B_D M[ 0.. 7 ]4

MEM _M B_ W E#4

MEM_ MB_B AN K[0 .. 2]4

MEM_ MB 0_OD T0

ME M_MB _ DQ S3_ P4

M EM_ MB 0_ OD T04

M EM_ MB 0_ OD T14

MEM_ MB _DM7

MEM_ MB _DM2

ME M_MB _ DQ S7_ N4

ME M_MB _ DQ S3_ N4

ME M_MB _ DQ S6_ P4

MEM_ MB _DM1

ME M_MB _ DQ S0_ N4

ME M_MB _ DQ S1_ P4

ME M_MB _ DQ S2_ P4

ME M_MB _ DQ S4_ P4

ME M_MB _ DQ S7_ P4

ME M_MB _ DQ S5_ N4

ME M_MB _ DQ S4_ N4

ME M_MB _ DQ S1_ N4

ME M_MB _ DQ S2_ N4

ME M_MB _ DQ S6_ N4

C PU_ME MHOT #5, 7

ME M_MB _ DQ S5_ P4

ME M_MB _ DQ S0_ P4

MEM_MB_ C LK7_ N4

MEM_MB_ C LK1_ P4

MEM_MB_ C LK7_ P4

SCLK02, 7 ,15

ME M_MB _ CA S#4

ME M_MB _ RA S#4

MEM_MB_ C LK1_ N4

MEM _MB_WE #4

ME M_MB _ DA TA[ 63: 0] 4

SDATA02, 7 ,15

MEM _MB0_O D T 04

MEM _MB_C KE04

MEM _M B 0_ C S #14

MEM _MB0_O D T 14

MEM _MB_C KE14

MEM _M B 0_ C S #04

MEM _MB_C AS#4

MEM _MB_R AS#4

MEM_ MB _DQS4 _P

MEM_ MB _DQS3 _N

MEM_ MB _DQS6 _N

MEM_ MB _DQS0 _P

MEM_ MB _DQS1 _N

MEM_ MB _DQS7 _N

MEM_ MB _DQS5 _P

MEM_ MB _DQS2 _N

MEM_ MB _DQS4 _N

MEM_ MB _DQS3 _P

MEM_ MB _DQS0 _N

MEM_ MB _DQS5 _N

MEM_ MB _DQS2 _P

MEM_ MB _DQS7 _P

MEM_ MB _DQS6 _P

MEM_ MB _DQS1 _P

SO-DIMM 1

M EM_MB _ADD 2

M EM_MB _ADD 4

to le ran ce 10 % 111 3

to le ran ce 10 % 111 3

M EM_MB _BAN K 1

M EM_MB _ADD 0

Schematic Diagrams

B.Schematic Diagrams

DDRII SO-DIMM_1 B - 9

Sheet 9 of 35

RS780M-1

HD MI_ CL KP

HD MI_ CL KN

C466 0.1u_10V_X7R_04

HD MI_ DA TA1 P

HD MI_ DA TA1 N

C467 0.1u_10V_X7R_04

C461 0.1u_10V_X7R_04

C460 0.1u_10V_X7R_04

C453 0.1u_10V_X7R_04

C454 0.1u_10V_X7R_04

C449 0.1u_10V_X7R_04

C448 0.1u_10V_X7R_04

HT_RXCALN

HT_RXCALP

GFX _ TX0P

GFX _ TX0N

GFX _ TX1P

GFX _ TX1N

GFX _ TX2P

GFX _ TX2N

GFX _ TX3P

GFX _ TX3N

HDMI _DAT A0P 13

HDMI _DAT A1P 13

HDMI _DAT A0N 1 3

HDMI _DAT A1N 1 3

HDMI _DAT A2P 13

HDMI _DAT A2N 1 3

HDMI_CLKP 13

HDMI_CLKN 13

H T_ T XC AL N

HT_TXCALP

C431 .1U_X7R _16V_04

C439 .1U_X7R _16V_04

R303 301_1%_04

PART 2 OF 6

PC IE I/F GFX

PCIE I/F GPP

PCIE I/F SB

U10B

RS780(RX780)

SB_TX3P

AD5

SB_TX3N

AE5

GPP_TX2P

AA2

GPP_ TX2N

AA1

GPP_TX3P

Y1

GPP_ TX3N

Y2

SB_RX3P

W5

SB_RX3N

Y5

GPP_RX2P

AD1

GPP_RX2N

AD2

GPP_RX3P

V5

GPP_RX3N

W6

SB_TX0P

AD7

SB_TX0N

AE7

SB_TX1P

AE6

SB_TX1N

AD6

SB_RX0P

AA8

SB_RX0N

Y8

SB_RX1P

AA7

SB_RX1N

Y7

PCE_C ALRP(PC E_B CALR P)

AC8

PCE_C ALRN (PCE_BC ALRN )

AB8

SB_TX2N

AC6

SB_RX2P

AA5

SB_RX2N

AA6

SB_TX2P

AB6

GPP_RX0P

AE3

GPP_RX0N

AD4

GPP_RX1P

AE2

GPP_RX1N

AD3

GPP_TX0P

AC1

GPP_ TX0N

AC2

GPP_TX1P

AB4

GPP_ TX1N

AB3

GFX_R X0P

D4

GFX_R X0N

C4

GFX_R X1P

A3

GFX_R X1N

B3

GFX_R X2P

C2

GFX_R X2N

C1

GFX_R X3P

E5

GFX_R X3N

F5

GFX_R X4P

G5

GFX_R X4N

G6

GFX_R X5P

H5

GFX_R X5N

H6

GFX_R X6P

J6

GFX_R X6N

J5

GFX_R X7P

J7

GFX_R X7N

J8

GFX_R X8P

L5

GFX_R X8N

L6

GFX_R X9P

M8

GFX_R X9N

L8

GFX_R X10P

P7

GFX_R X10N

M7

GFX_R X11P

P5

GFX_R X11N

M5

GFX_R X12P

R8

GFX_R X12N

P8

GFX_R X13P

R6

GFX_R X13N

R5

GFX_R X14P

P4

GFX_R X14N

P3

GFX_R X15P

T4

GFX_R X15N

T3

GFX_TX0P

A5

GFX_TX0N

B5

GFX_TX1P

A4

GFX_TX1N

B4

GFX_TX2P

C3

GFX_TX2N

B2

GFX_TX3P

D1

GFX_TX3N

D2

GFX_TX4P

E2

GFX_TX4N

E1

GFX_TX5P

F4

GFX_TX5N

F3

GFX_TX6P

F1

GFX_TX6N

F2

GFX_TX7P

H4

GFX_TX7N

H3

GFX_TX8P

H1

GFX_TX8N

H2

GFX_TX9P

J2

GFX_TX9N

J1

GF X_ TX1 0P

K4

GFX_TX10N

K3

GF X_ TX1 1P

K1

GFX_TX11N

K2

GF X_ TX1 2P

M4

GFX_TX12N

M3

GF X_ TX1 3P

M1

GFX_TX13N

M2

GF X_ TX1 4P

N2

GFX_TX14N

N1

GF X_ TX1 5P

P1

GFX_TX15N

P2

GPP_TX4P

Y4

GPP_ TX4N

Y3

GPP_TX5P

V1

GPP_ TX5N

V2

GPP_RX4P

U5

GPP_RX4N

U6

GPP_RX5P

U8

GPP_RX5N

U7

R269 1.27K_1%_04

C 1 1 . 1U _X 7 R_ 1 6V_ 04

C4 25 . 1U_X7R_1 6V_04

C9 .1 U_ X7R _16V _0 4

PART 1 OF 6

HYPER TRANSPORT CPU I/F

U10A

RS780(RX780)

HT_RXCAD15P

U19

HT_RXCAD15N

U18

HT_RXCAD14P

U20

HT_RXCAD14N

U21

HT_RXCAD13P

V21

HT_RXCAD13N

V20

HT_RXCAD12P

W21

HT_RXCAD12N

W20

HT_RXCAD11P

Y22

HT_RXCAD11N

Y23

HT_RXCAD10P

AA 24

HT_RXCAD10N

AA 25

HT_RXC AD9P

AB 25

HT_RXC AD9N

AB 24

HT_RXC AD8P

AC24

HT_RXC AD8N

AC25

HT_RXC AD7P

N24

HT_RXC AD7N

N25

HT_RXC AD6P

P25

HT_RXC AD6N

P24

HT_RXC AD5P

P22

HT_RXC AD5N

P23

HT_RXC AD4P

T25

HT_RXC AD4N

T24

HT_RXC AD3P

U24

HT_RXC AD3N

U25

HT_RXC AD2P

V25

HT_RXC AD2N

V24

HT_RXC AD1P

V22

HT_RXC AD1N

V23

HT_RXC AD0P

Y25

HT_RXC AD0N

Y24

HT_RXCLK1P

AB 23

HT_RXCLK1N

AA 22

HT_RXCLK0P

T22

HT_RXCLK0N

T23

HT_RXCTL0P

M22

HT_RXCTL0N

M23

HT_RXCTL1P

R21

HT_RXCTL1N

R20

HT_RXC ALP

C23

HT_RXC ALN

A24

HT_TXCAD15P

P18

HT_TXCAD15N

M1 8

HT_TXCAD14P

M2 1

HT_TXCAD14N

P21

HT_TXCAD13P

M1 9

HT_TXCAD13N

L1 8

HT_TXCAD12P

L1 9

HT_TXCAD12N

J19

HT_TXCAD11P

J18

HT_TXCAD11N

K17

HT_TXCAD10P

J20

HT_TXCAD10N

J21

HT_TXCAD9P

G2 0

HT_TXCAD9N

H21

HT_TXCAD8P

F21

HT_TXCAD8N

G2 1

HT_TXCAD7P

K23

HT_TXCAD7N

K22

HT_TXCAD6P

K24

HT_TXCAD6N

K25

HT_TXCAD5P

J25

HT_TXCAD5N

J24

HT_TXCAD4P

H23

HT_TXCAD4N

H22

HT_TXCAD3P

F23

HT_TXCAD3N

F22

HT_TXCAD2P

F24

HT_TXCAD2N

F25

HT_TXCAD1P

E24

HT_TXCAD1N

E25

HT_TXCAD0P

D24

HT_TXCAD0N

D25

H T_ TXC LK 1P

L2 1

HT_TXCLK1N

L2 0

H T_ TXC LK 0P

H24

HT_TXCLK0N

H25

HT_ TXCTL 0P

M2 4

HT_TXC TL0N

M2 5

HT_ TXCTL 1P

P19

HT_TXC TL1N

R18

HT_ TXCA LP

B24

HT_TXCALN

B25

C4 44 . 1U_X7R_1 6V_04

R23 2K_1%_04

C1 0 . 1 U_ X7R _1 6V _0 4

C434 .1U_X7R _16V_04

C 1 2 . 1U _X 7 R_ 1 6V_ 04

C438 .1U_X7R _16V_04

R302 301_1%_04

C4 35 . 1U_X7R_1 6V_04

C 1 6 . 1U _X 7 R_ 1 6V_ 04

C8 .1 U_ X7R _16V _0 4

C4 36 . 1U_X7R_1 6V_04

HT _CPU _NB_CAD _H03

VDD_ PCIE

HT _CPU _NB_CAD _L13

HT _CPU _NB_CAD _H13

HT _CPU _NB_CAD _L03

HT _CPU _NB_CAD _H23

HT _CPU _NB_CAD _H33

HT _CPU _NB_CAD _L23

HT _CPU _NB_CAD _H73

HT _CPU _NB_CAD _L53

HT _CPU _NB_CAD _H43

HT _CPU _NB_CAD _L63

HT _CPU _NB_CAD _H63

HT _CPU _NB_CAD _L43

HT _CPU _NB_CAD _H53

HT _CPU _NB_CAD _H83

HT _CPU _NB_CAD _L73

HT _CPU _NB_CAD _L33

HT _CPU _NB_CAD _L93

HT _CPU _NB_CAD _H93

HT _CPU _NB_CAD _L83

HT _CPU _NB_CAD _H1 13

HT _CPU _NB_CAD _L103

HT _CPU _NB_CAD _H1 03

HT _CPU _NB_CAD _H1 43

HT _CPU _NB_CAD _H1 23

HT _CPU _NB_CAD _L113

HT _CPU _NB_CAD _L123

HT _CPU _NB_CAD _L153

HT _CPU _NB_CAD _H1 33

HT _CPU _NB_CAD _L143

HT _CPU _NB_CL K_H03

HT _CPU _NB_CAD _L133

HT _CPU _NB_CAD _H1 53

HT _CPU _NB_CL K_H13

HT _CPU _NB_CL K_L13

HT _CPU _NB_CL K_L03

HT _CPU _NB_CTL _H03