Page 1

5

4

3

2

1

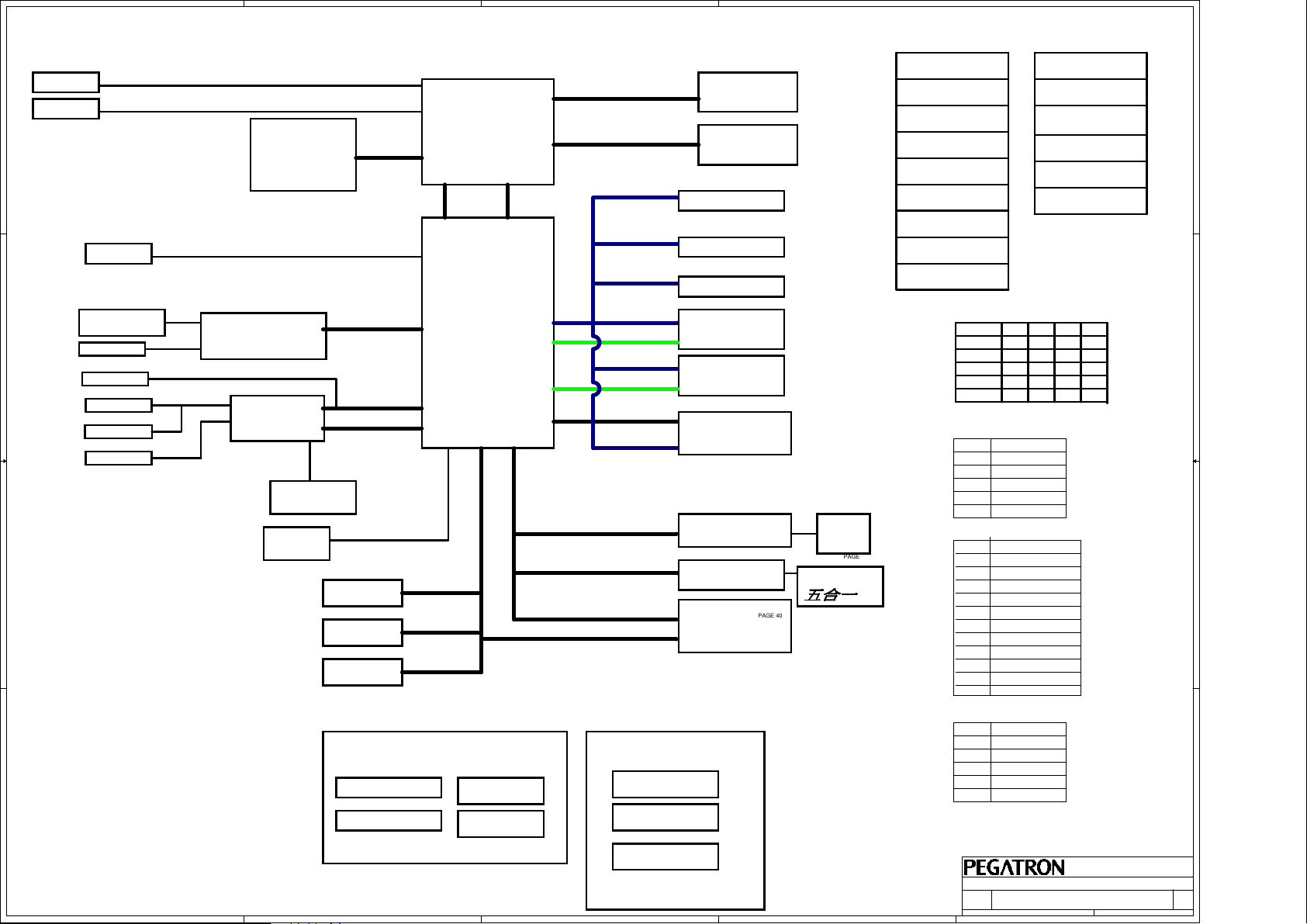

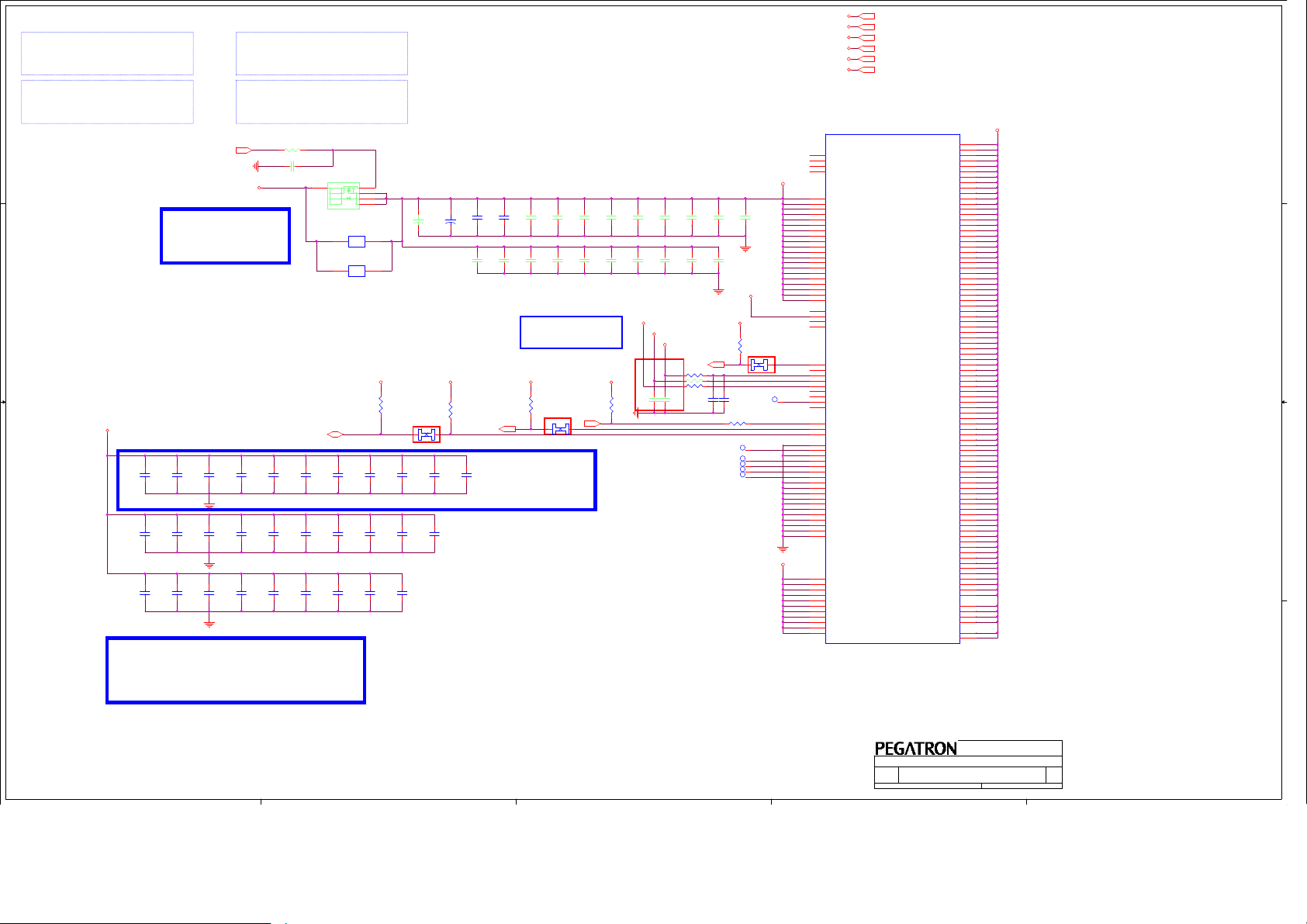

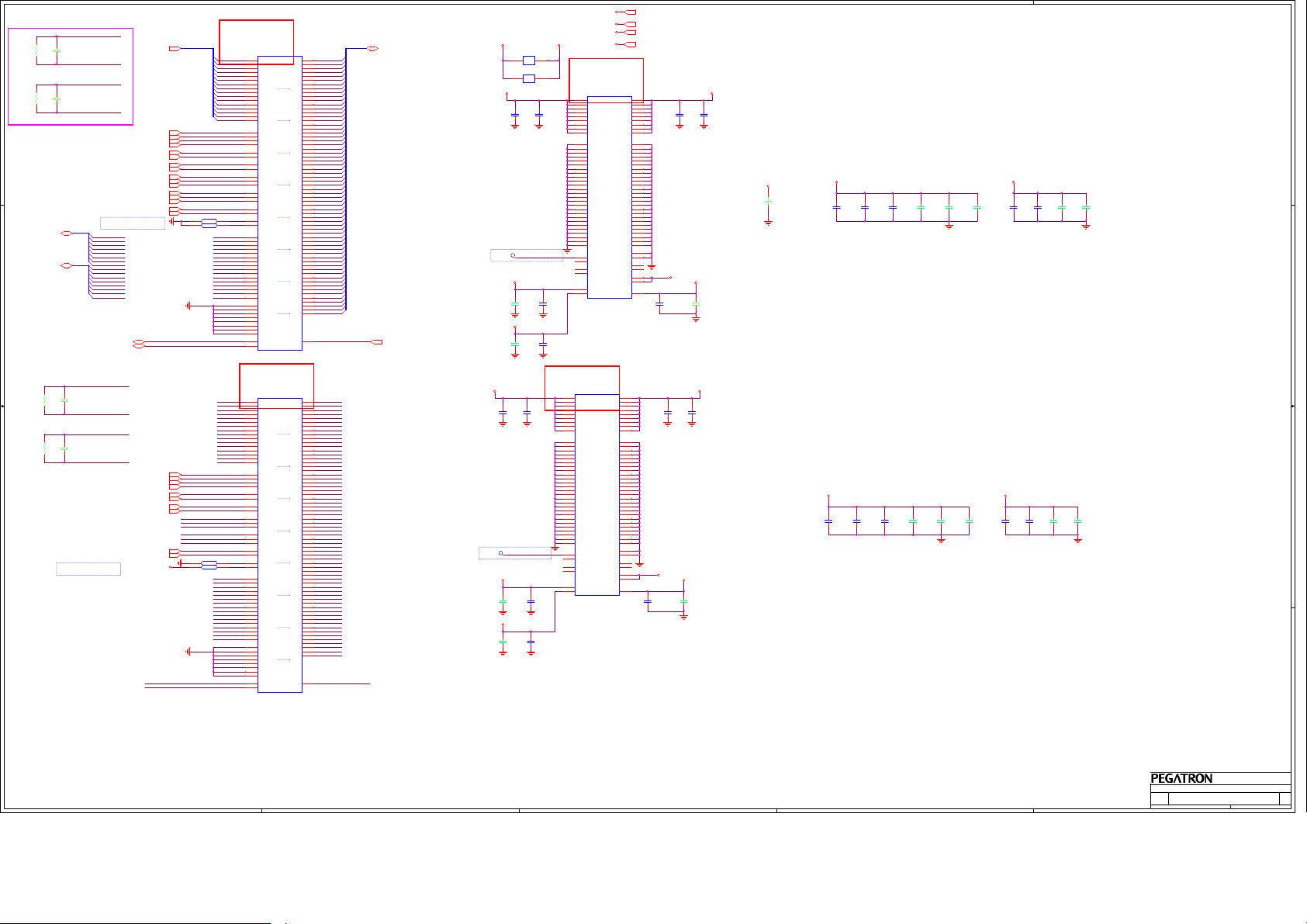

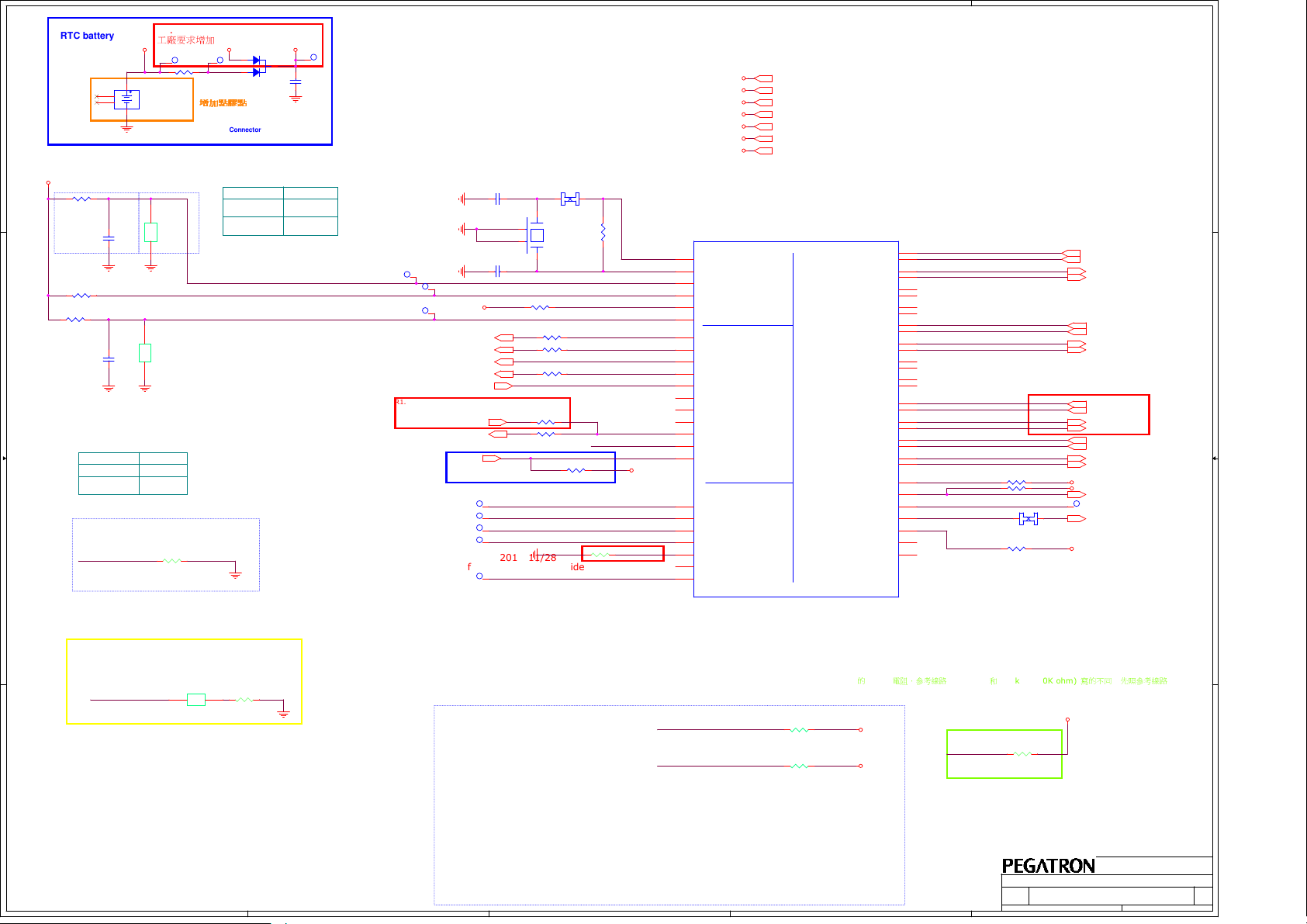

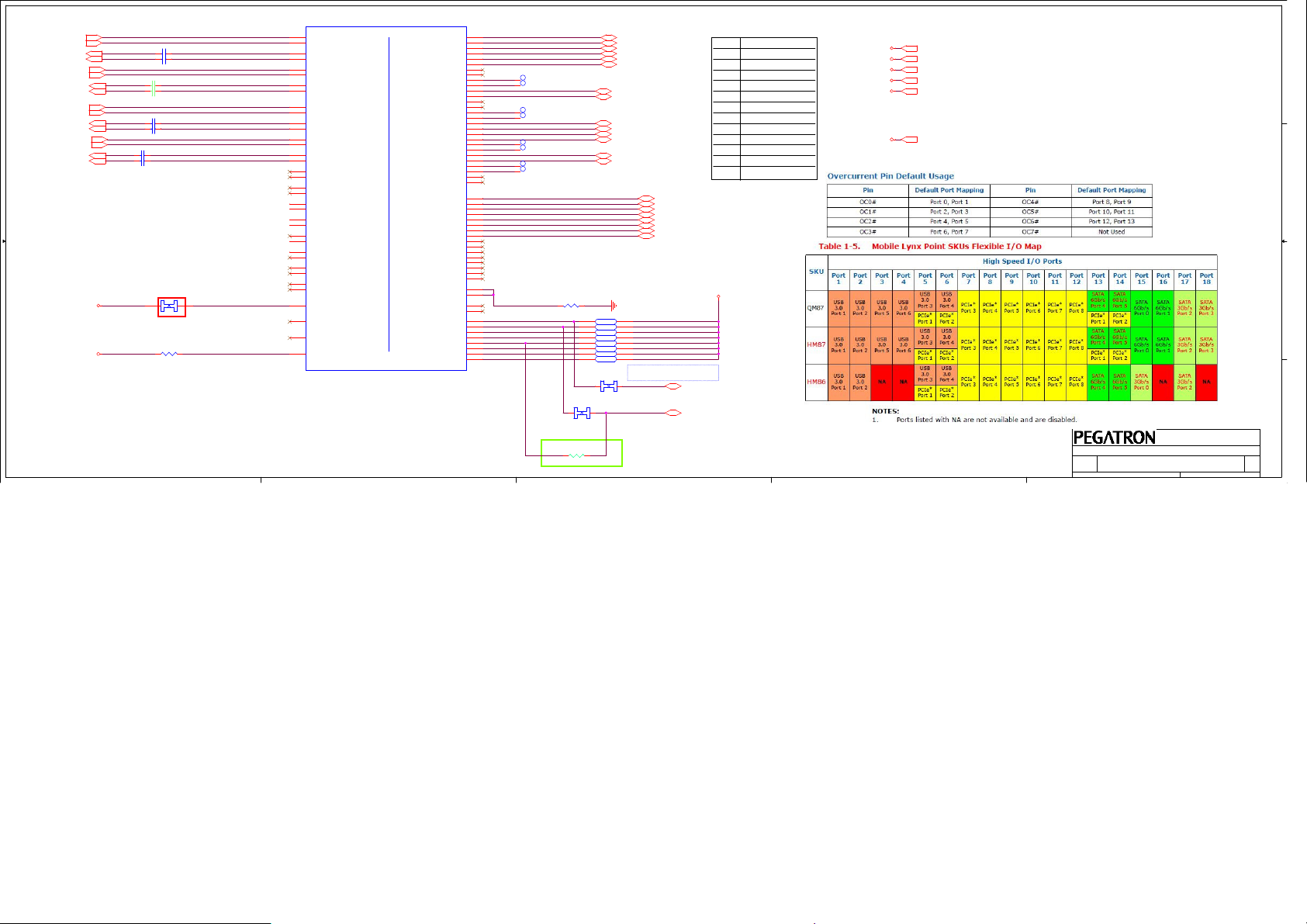

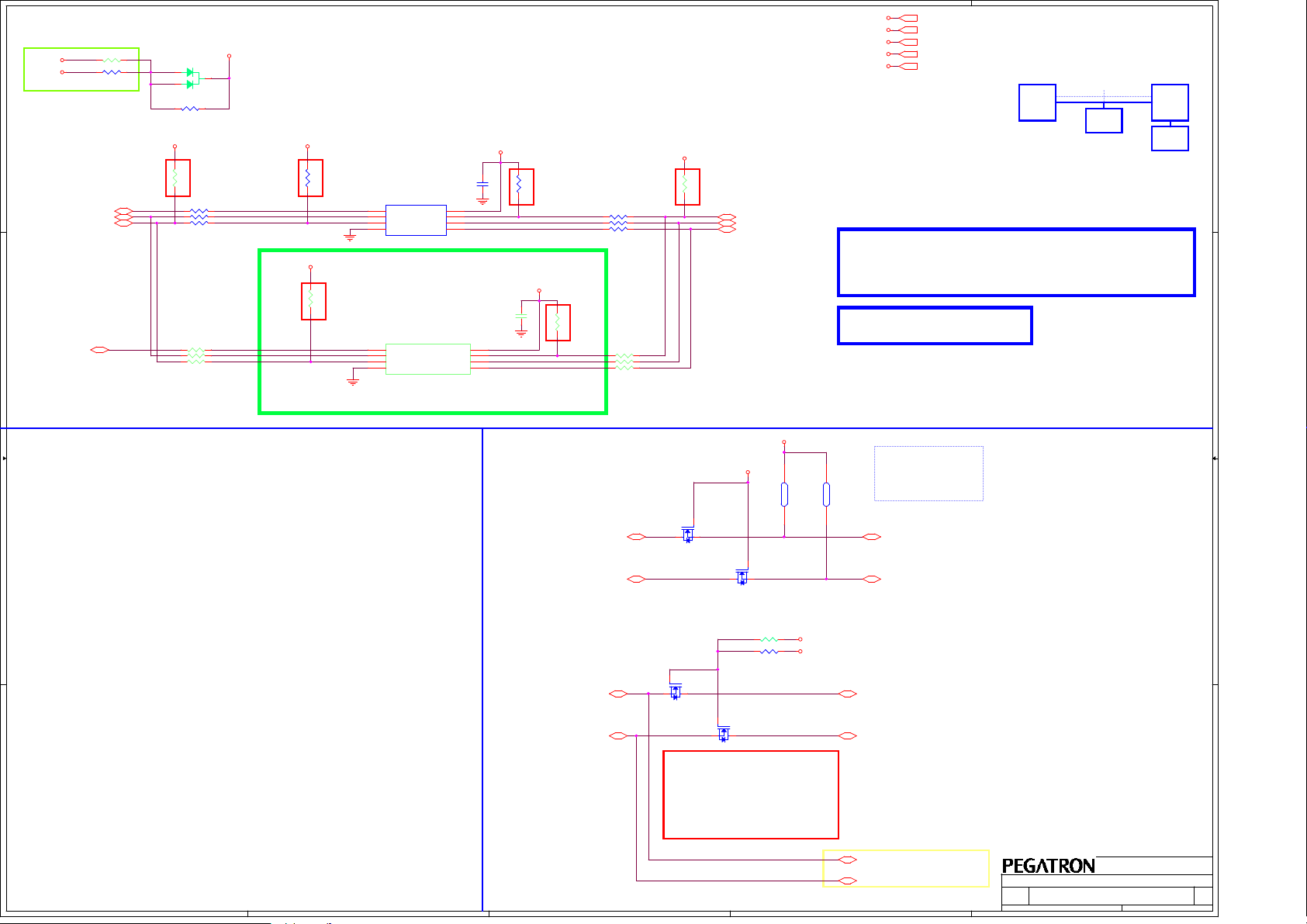

VA70HW BLOCK DIAGRAM

HDMI

PAGE 38

eDP Panel

D D

C C

B B

PAGE 37

CRT

Head Phone

(Combo Jack)

MIC

TPM

K/B

Click T/P

FAN

PAGE 39

PAGE 58

PAGE 43

PAGE 48

PAGE 48

PAGE 49

DDIC

eDP x 2

NVIDIA N14E

Azalia Codec

RTK/ALC3225

EC

IT8528E

SPI ROM

4MB (BIOS/EC)

SPI ROM

2MB (ME)

dGPU

PAGE 41 42

PAGE 30

PAGE 28

PAGE 70~79

PAGE 30

SATA HDD

SATA HDD

SATA ODD

PCIE X 16

VGA

Azalia

LPC

HSPI

SPI

PAGE 60

PAGE 60

PAGE 60

CPU

Haswell

FDI x 2

PCH

Lynx Point

SATA

PAGE 3-10

DMI x 4

PAGE 13-19

PCIE *1

PCIE *1

PCIE *1

SATA 3.0

DDR3L 1333/1600 MHz

channel A

DDR3L 1333/1600 MHz

channel B

USB2.0

USB2.0

USB2.0

USB2.0

USB3.0

USB2.0

USB3.0

PCIE *1

USB2.0

DDR-III

SO-DIMM*2

DDR-III

SO-DIMM*2

Camera

USB PORT9

USB PORT2

USB20 PORT1

USB30 PORT2

USB20 PORT0

USB30 PORT1

MiniCard

WLAN/WMAX

BT combo

Giga LAN

BCM57780

Card Reader

RTS5209

mSATA/SSD

PAGE 16

PAGE 17

PAGE 58

PAGE 61

PAGE 55

PAGE 33

PAGE 40

PAGE 40

PAGE 53

RJ45

PAGE 34

SD Socket

五五五五五五五五五五五五

PAGE 40

POWER

CPU VCORE

SYSTEM, +3V, +5V

+VCCP & +VCCP_VT

DDR & VTT

2.5V & 1.5VS &1.1VS

SMART CHARGER

POWER DETECT

LOAD SWITCH

POWER PROTECT

Power Rails

Sleep State

S0 ON

S3 OFFON ONON

PCIe Port

PCIE_P1

PCIE_P2

PCIE_P3

PCIE_P4

PCIE_P5

PCIE_P6

USB20 PORT

USB P00

USB P01

USB P02

USB P03

USB P04

USB P05

USB P08

USB P09

USB P10

USB P11

USB P12

USB P13

PAGE 80

PAGE 81

PAGE 82

PAGE 83

PAGE 84

PAGE 88

PAGE 90

PAGE 91

PAGE 92

RTC VA VSUS

ON ON

CARDREADER

mSATA

Mini CARD (WLAN)

LAN

External MB

External MB

External DB

WiFi

Camera

External DB

BT

PCIE/mSATA

VGA POWER

GPU VCORE

+1.05VS_VGA

+3VS_VGA

+12VS_VGA

LOAD SWITCH

POWER PROTECT

ON

PAGE 80

PAGE 91

PAGE 92

VS

OFFS4 ON ONON

OFFON ONONS5/ AC

OFFS5/ DC ON OFFON

SATA PORT

SATA P0 HDD 1

SATA P1

ODD

IO BOARD PWR BOARD

USB PORT3

A A

USB PORT9

5

4

HP_OUT

MIC IN

POWER Button

POWER LED

LID SW

3

2

SATA P2

SATA P3

SATA P4

mSATA

SATA P5

HDD 2

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Title :

Title :

Title :

Wing_Cheng

Wing_Cheng

Wing_Cheng

Engineer:

Engineer:

BU1-RD Div.1-HW RD Dept.1

BU1-RD Div.1-HW RD Dept.1

BU1-RD Div.1-HW RD Dept.1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

VA70_HW

VA70_HW

VA70_HW

1

Rev

Rev

Rev

1.0

1.0

1 96Monday, February 04, 2013

1 96Monday, February 04, 2013

1 96Monday, February 04, 2013

1.0

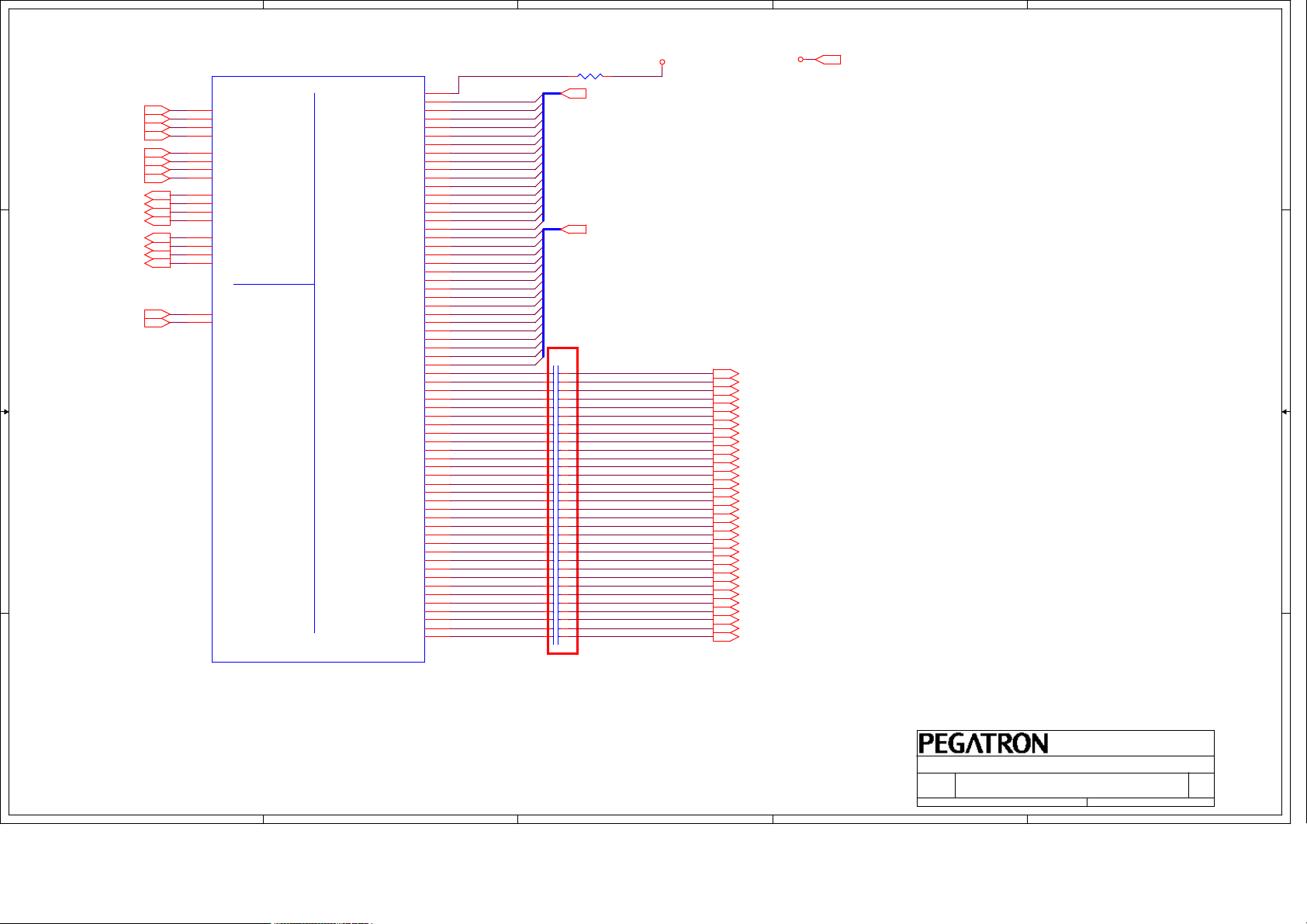

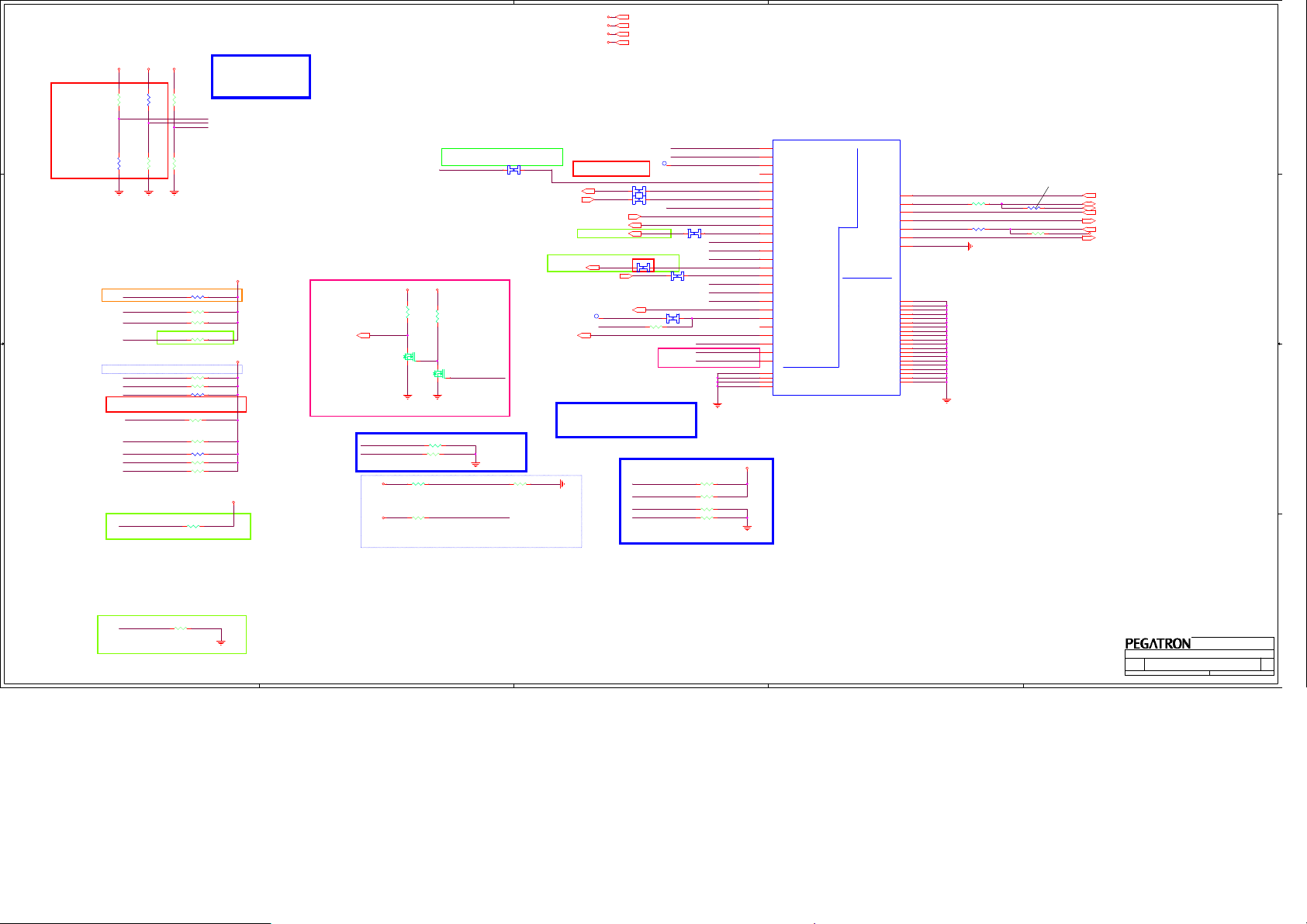

Page 2

5

4

3

2

1

+VCCIOA_OUT

U0301A

D D

C C

B B

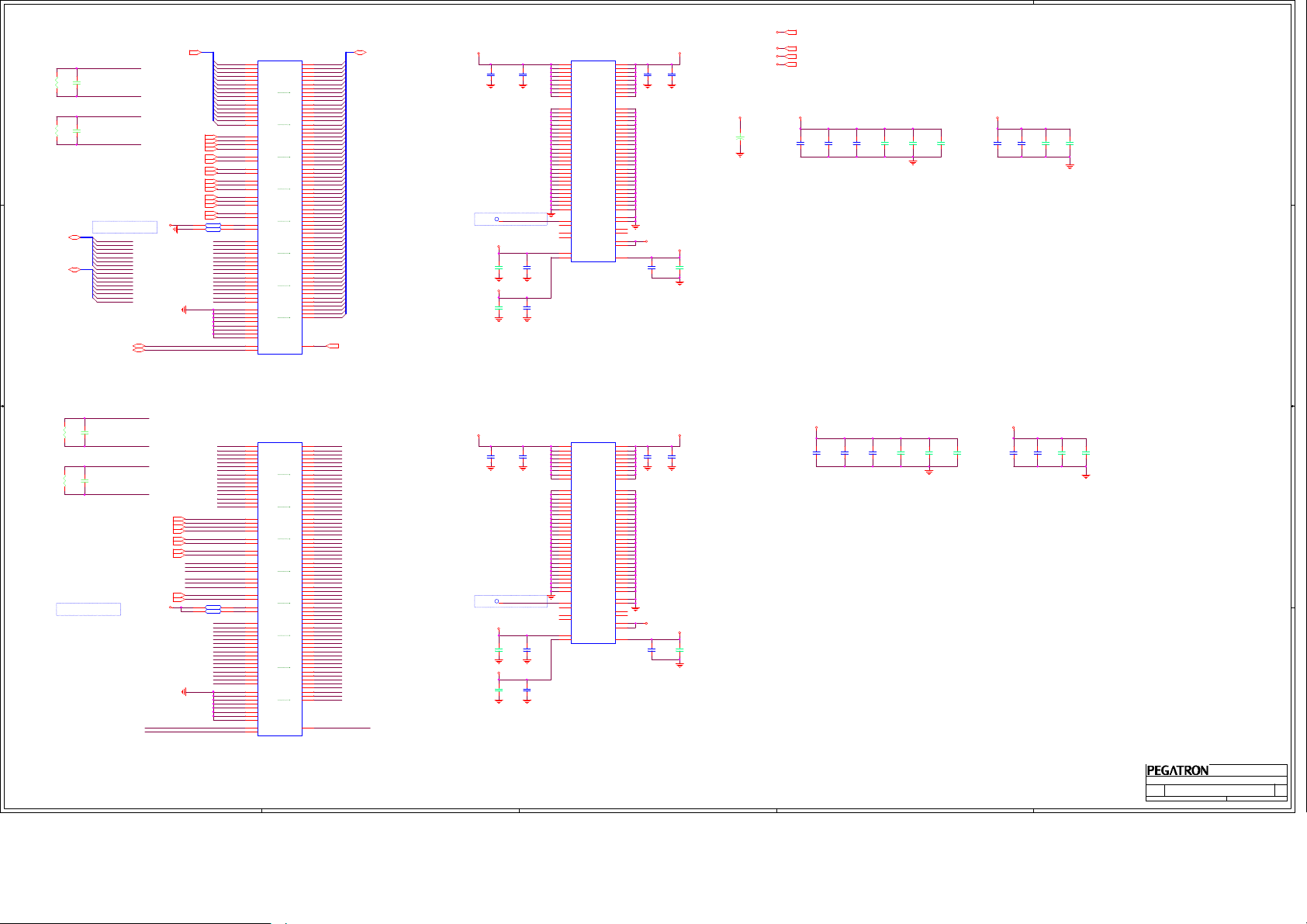

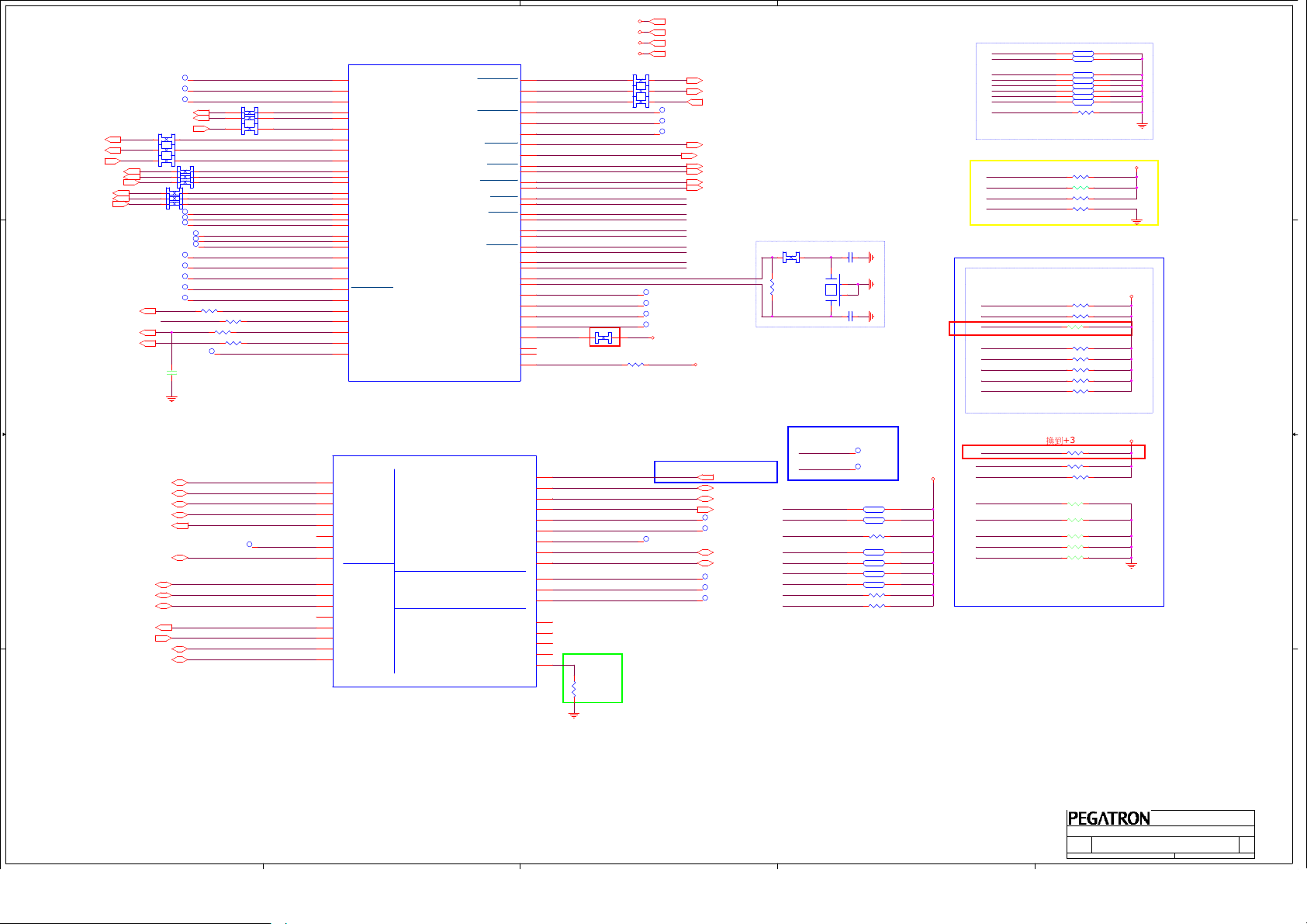

DMI_TXN022

DMI_TXN122

DMI_TXN222

DMI_TXN322

DMI_TXP022

DMI_TXP122

DMI_TXP222

DMI_TXP322

DMI_RXN022

DMI_RXN122

DMI_RXN222

DMI_RXN322

DMI_RXP022

DMI_RXP122

DMI_RXP222

DMI_RXP322

FDI_CSYNC22

FDI_INT22

D21

C21

B21

A21

D20

C20

B20

A20

D18

C17

B17

A17

D17

C18

B18

A18

H29

J29

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

FDI_CSYNC

DISP_INT

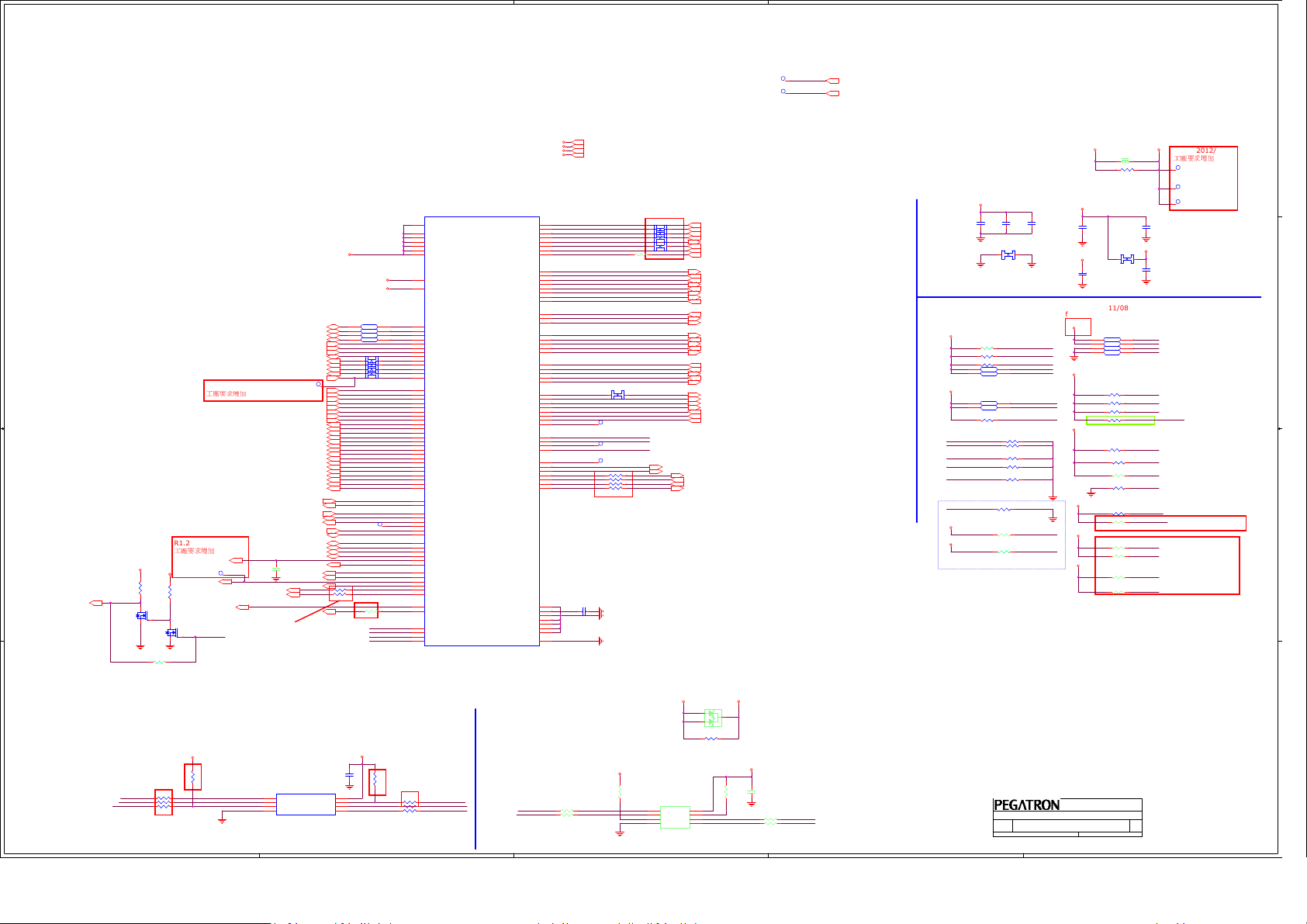

Haswell rPGA EDS

DMI FDI

PEG_RCOMP

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

PEG

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG_RXN_7

PEG_RXN_8

PEG_RXN_9

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG_RXP_9

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

E23

M29

K28

M31

L30

M33

L32

M35

L34

E29

D28

E31

D30

E35

D34

E33

E32

L29

L28

L31

K30

L33

K32

L35

K34

F29

E28

F31

E30

F35

E34

F33

D32

H35

H34

J33

H32

J31

G30

C33

B32

B31

A30

B29

A28

B27

A26

B25

A24

J35

G34

H33

G32

H31

H30

B33

A32

C31

B30

C29

B28

C27

B26

C25

B24

PEG_COMP

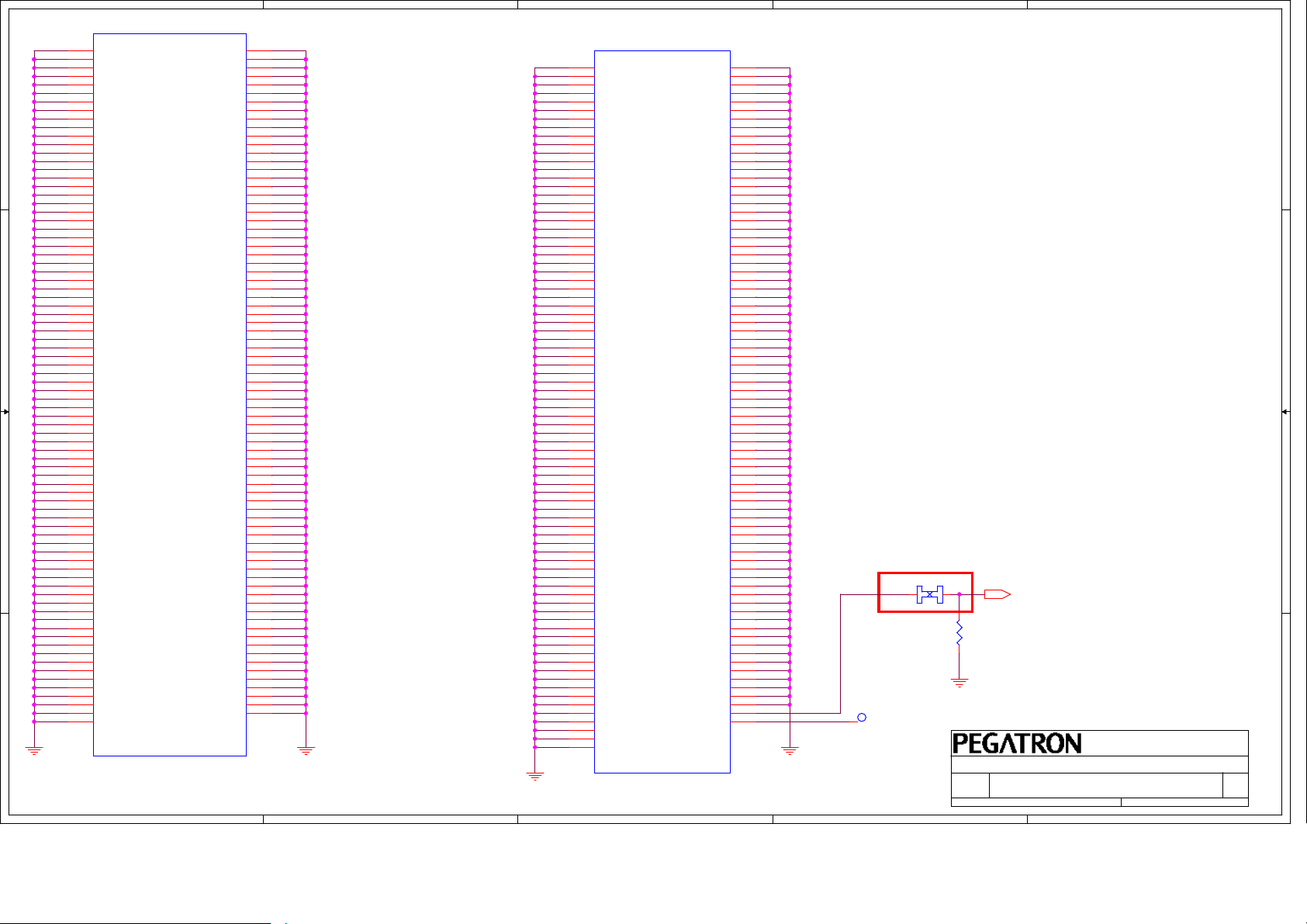

PEG_RXN15

PEG_RXN14

PEG_RXN13

PEG_RXN12

PEG_RXN11

PEG_RXN10

PEG_RXN9

PEG_RXN8

PEG_RXN7

PEG_RXN6

PEG_RXN5

PEG_RXN4

PEG_RXN3

PEG_RXN2

PEG_RXN1

PEG_RXN0

PEG_RXP15

PEG_RXP14

PEG_RXP13

PEG_RXP12

PEG_RXP11

PEG_RXP10

PEG_RXP9

PEG_RXP8

PEG_RXP7

PEG_RXP6

PEG_RXP5

PEG_RXP4

PEG_RXP3

PEG_RXP2

PEG_RXP1

PEG_RXP0

PEG_TXN0_C

PEG_TXN1_C

PEG_TXN2_C

PEG_TXN3_C

PEG_TXN4_C

PEG_TXN5_C

PEG_TXN6_C

PEG_TXN7_C

PEG_TXN8_C

PEG_TXN9_C

PEG_TXN10_C

PEG_TXN11_C

PEG_TXN12_C

PEG_TXN13_C

PEG_TXN14_C

PEG_TXN15_C

PEG_TXP0_C

PEG_TXP1_C

PEG_TXP2_C

PEG_TXP3_C

PEG_TXP4_C

PEG_TXP5_C

PEG_TXP6_C

PEG_TXP7_C

PEG_TXP8_C

PEG_TXP9_C

PEG_TXP10_C

PEG_TXP11_C

PEG_TXP12_C

PEG_TXP13_C

PEG_TXP14_C

PEG_TXP15_C

CX0301 0.22UF/10V /EGL

CX0302 0.22UF/10V /EGL

CX0303 0.22UF/10V /EGL

CX0304 0.22UF/10V /EGL

CX0305 0.22UF/10V /EGL

CX0306 0.22UF/10V /EGL

CX0307 0.22UF/10V /EGL

CX0308 0.22UF/10V /EGL

CX0309 0.22UF/10V /DGPU

CX0310 0.22UF/10V /DGPU

CX0311 0.22UF/10V /DGPU

CX0312 0.22UF/10V /DGPU

CX0313 0.22UF/10V /DGPU

CX0314 0.22UF/10V /DGPU

CX0315 0.22UF/10V /DGPU

CX0316 0.22UF/10V /DGPU

CX0317 0.22UF/10V /EGL

CX0318 0.22UF/10V /EGL

CX0319 0.22UF/10V /EGL

CX0320 0.22UF/10V /EGL

CX0321 0.22UF/10V /EGL

CX0322 0.22UF/10V /EGL

CX0323 0.22UF/10V /EGL

CX0324 0.22UF/10V /EGL

CX0325 0.22UF/10V /DGPU

CX0326 0.22UF/10V /DGPU

CX0327 0.22UF/10V /DGPU

CX0328 0.22UF/10V /DGPU

CX0329 0.22UF/10V /DGPU

CX0330 0.22UF/10V /DGPU

CX0331 0.22UF/10V /DGPU

CX0332 0.22UF/10V /DGPU

1 2

R0301 24.9Ohm1%

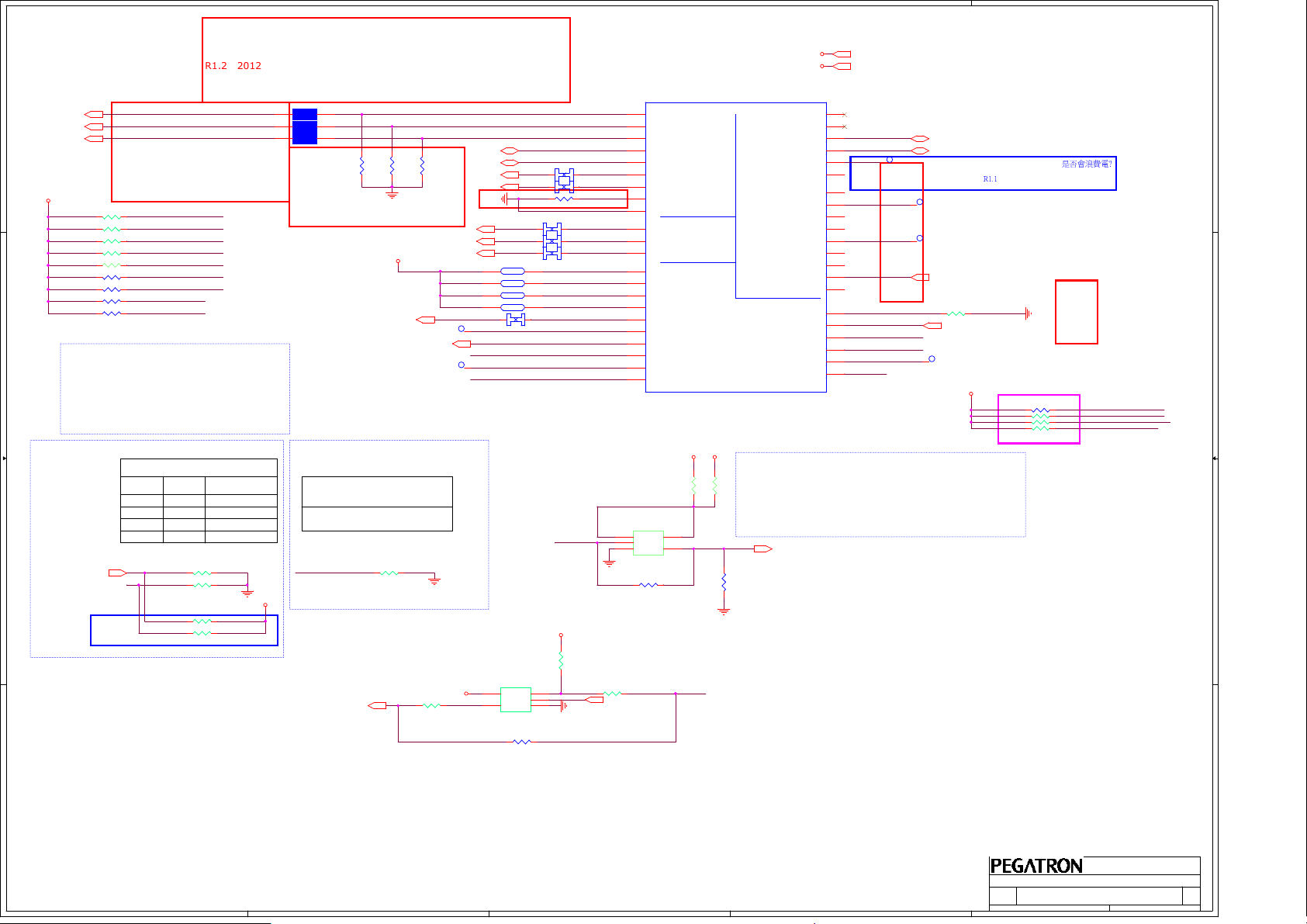

R1.2 2012/12/19

CX0301~CX0308, CX0317~CX0324 options are changed to /EGL

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

PEG_RXN[15:0] 70

PEG_RXP[15:0] 70

+VCCIOA_OUT

+VCCIOA_OUT 4,6

PEG Compensation

Enable PCIE Lane Reversal

Need to PD CFG[2]

PEG_TXN15 70

PEG_TXN14 70

PEG_TXN13 70

PEG_TXN12 70

PEG_TXN11 70

PEG_TXN10 70

PEG_TXN9 70

PEG_TXN8 70

PEG_TXN7 70

PEG_TXN6 70

PEG_TXN5 70

PEG_TXN4 70

PEG_TXN3 70

PEG_TXN2 70

PEG_TXN1 70

PEG_TXN0 70

PEG_TXP15 70

PEG_TXP14 70

PEG_TXP13 70

PEG_TXP12 70

PEG_TXP11 70

PEG_TXP10 70

PEG_TXP9 70

PEG_TXP8 70

PEG_TXP7 70

PEG_TXP6 70

PEG_TXP5 70

PEG_TXP4 70

PEG_TXP3 70

PEG_TXP2 70

PEG_TXP1 70

PEG_TXP0 70

SOCKET_947P

12V012BSM001

A A

5

4

If Support PCIE Gen3, change AC Cap to 0.22uF

3

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

2

VA70_HW

VA70_HW

VA70_HW

Engineer:

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

Wing_Cheng

Wing_Cheng

Wing_Cheng

3 96Friday, January 18, 2013

3 96Friday, January 18, 2013

3 96Friday, January 18, 2013

1

Rev

Rev

Rev

1.0

1.0

1.0

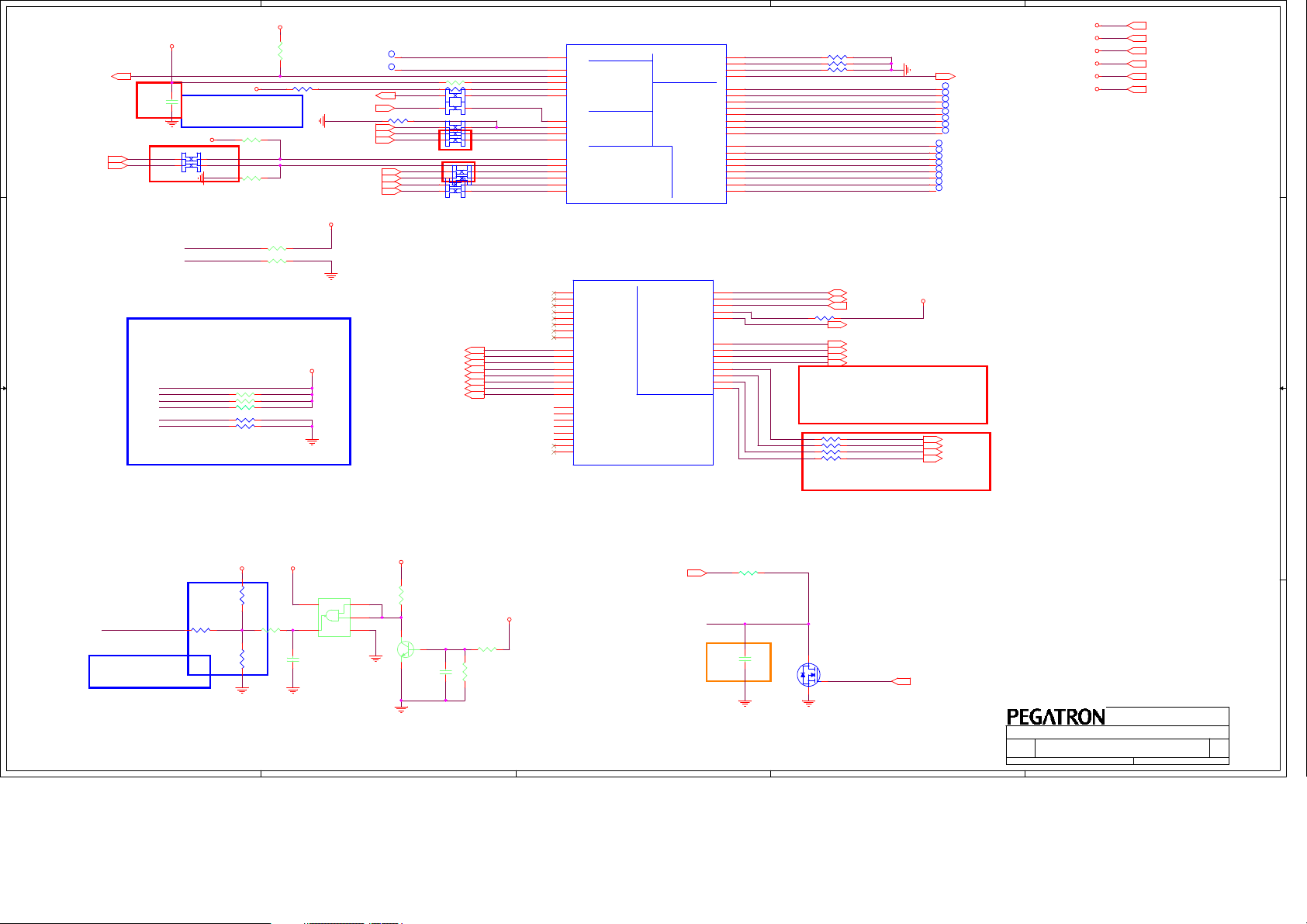

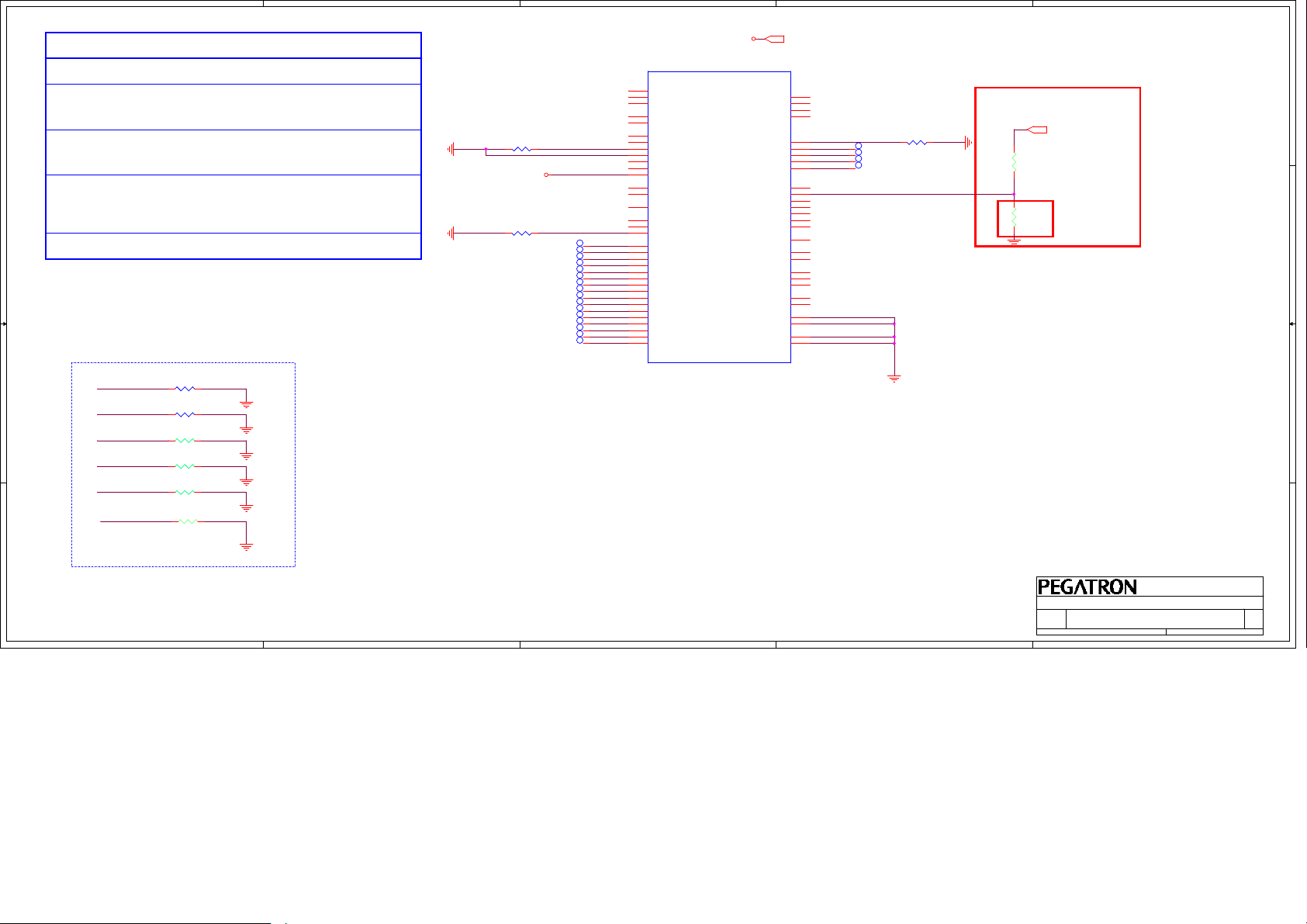

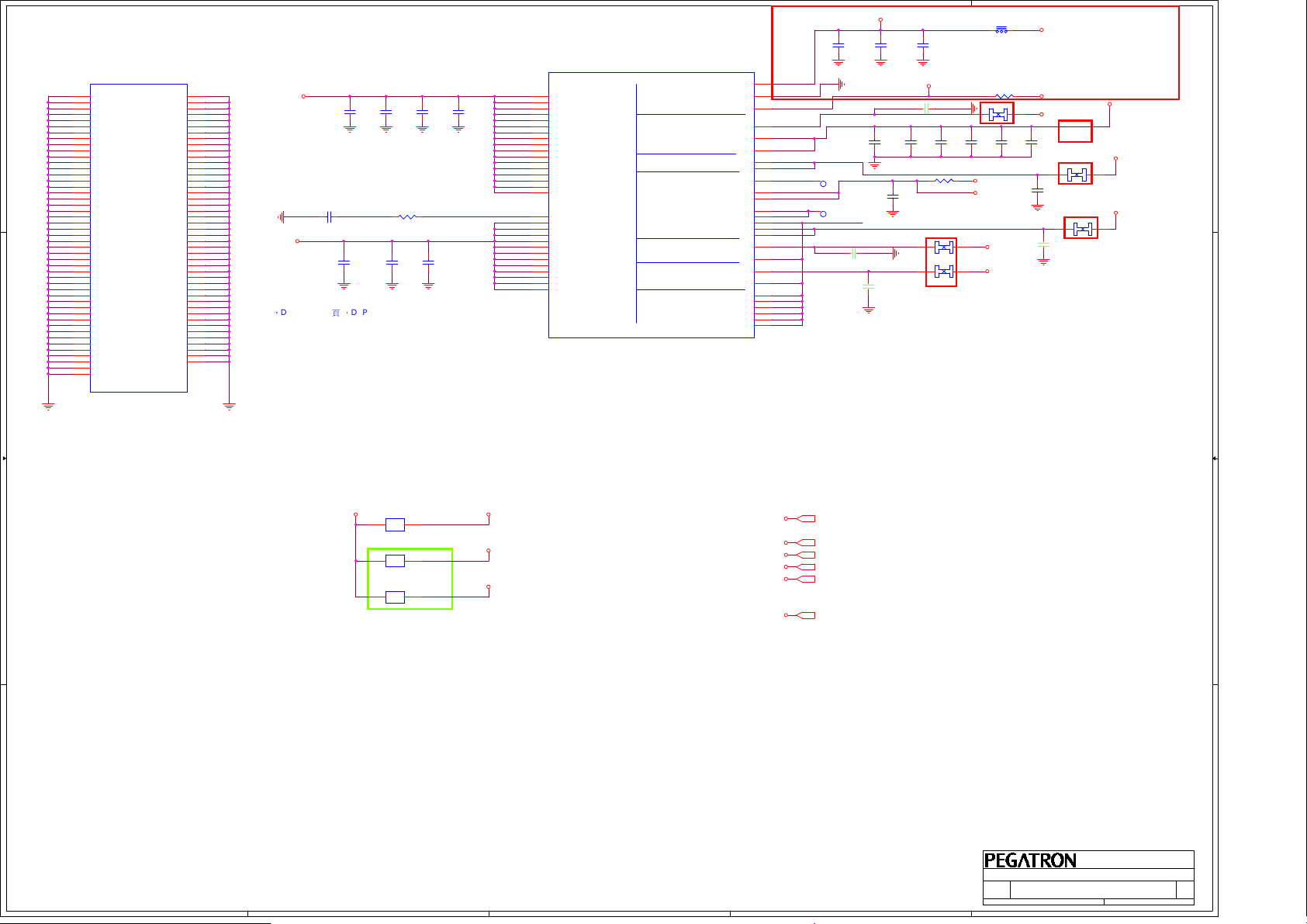

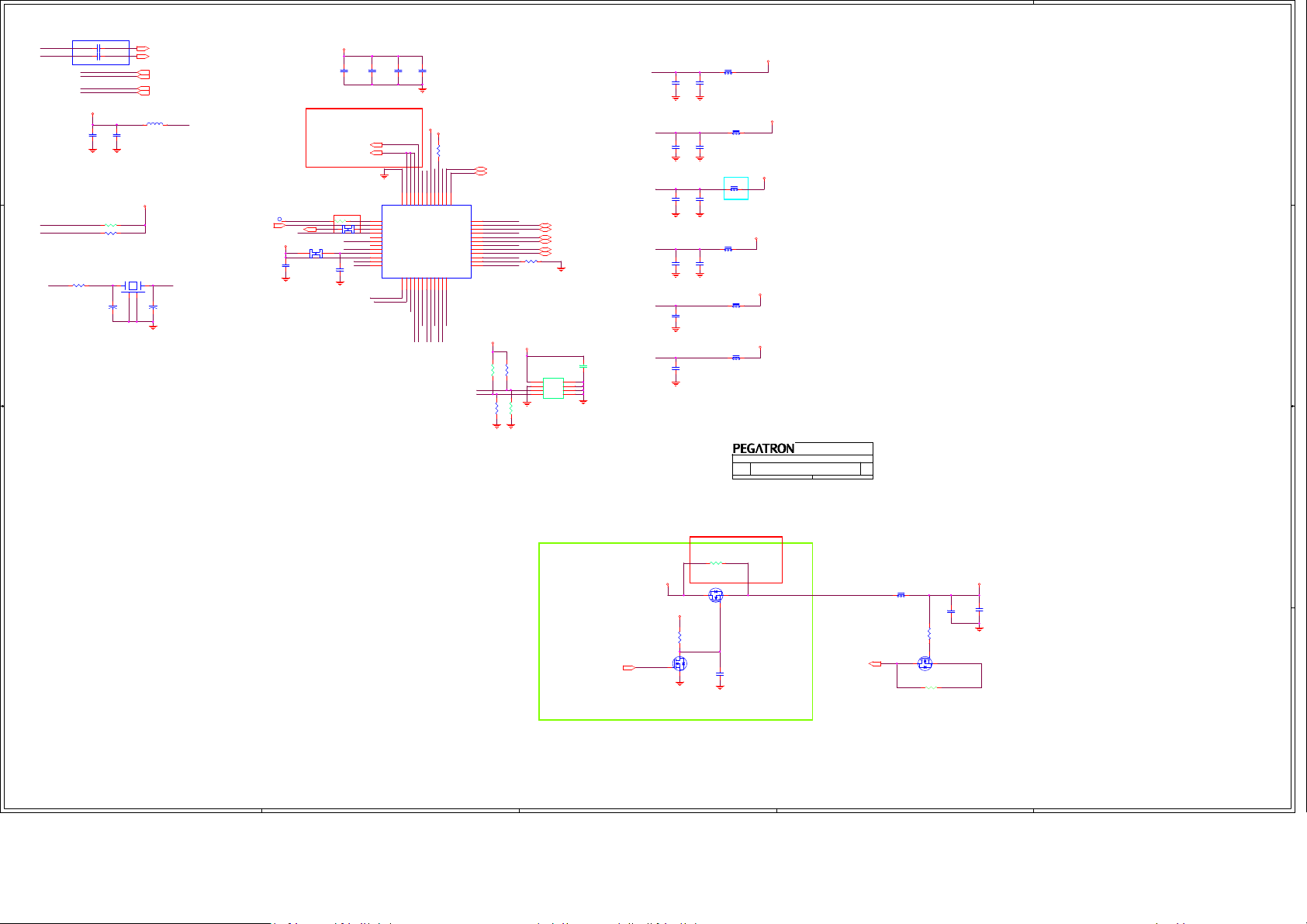

Page 3

5

+VCCIO_OUT

+1.05VS

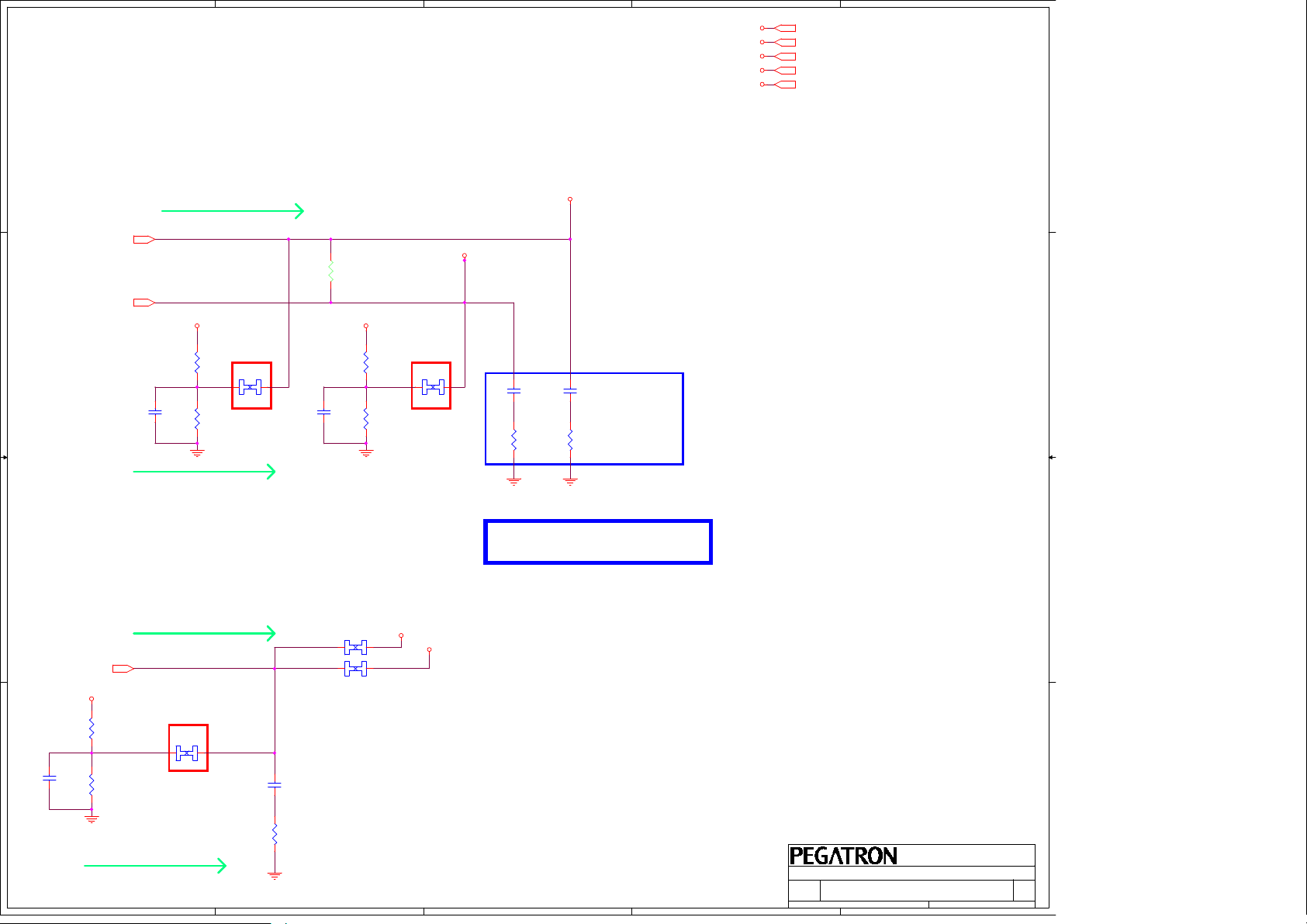

H_PECI25

D D

R1.2 2012/11/26

reserved for 2014 processor

CLK_DP_N21

CLK_DP_P21

C C

C0404

0.1UF/10V

+VCCIO_OUT

SP0406 R0603

SP0407 R0603

R1.2 2012/11/08

cost dwon 0ohm

+VCCIO_OUT

12

Stuff R0408

@

Intel MOW WW14: stuff

H_CPUPWRGD PD 10Kohm

1 2

1 2

1KOhm

CLK_DP_SSC _P_R

CLK_DP_SSC _N_R

12

R0440

100KOhm

@

H_PECI

R1.1

12

@

R04171KOh m

CLK_DP_N_R

CLK_DP_P_R

R0418

12

@

@

1 2

R0419 10KOhm

1 2

R0420 10KOhm

@

12

R040462Ohm

H_THRMTR IP#25,47

H_CPUPW RGD25

PM_DRAM_PW RGD22

PCH_PLTRS T_CPU#25

CLK_DP_SSC _N21

CLK_DP_SSC _P21

+VCCIO_OUT

H_PM_SYNC22

R1.0 PU/PD for JTAG signals

+1.05VS

VCCST

XDP_TMS

XDP_TDI_R

XDP_PREQ#

XDP_TCK

XDP_TRST#

B B

1 2

R0401 51Ohm@

1 2

R0402 51Ohm@

1 2

R0406 51Ohm

@

1 2

R0407 51Ohm

1 2

R0405 51Ohm

4

1

T0419

1

T0420

H_PROCHOT#

CLK_EXP_N21

CLK_EXP_P21

SSC CLOCK TERMINATION

Stuff R0445 & R0446 only when SSC clock not used

1 2

R0430 0Ohm@

R0403 56Ohm

12

R040810KOhm

SP0408 R0 402

SP0409 R0 402

SP0405 R0402

SP0404 R0402

HDMI_TXN2_PCH39

HDMI_TXP2_PCH39

HDMI_TXN1_PCH39

HDMI_TXP1_PCH39

HDMI_TXN0_PCH39

HDMI_TXP0_PCH39

HDMI_CLKN_PC H39

HDMI_CLKP_PCH39

DDI Port B: N/A

DDI Port C: HDMI

DDI Port D: DP to VGA

DDI signals Mapping, check 497750

12

12

SP0401R0402

12

SP0402R0402

12

SP0403R0402

1 2

1 2

1 2

SP0410 R0 603

1 2

SP0411 R0 603

1 2

1 2

TP_SKTOCC# _R

TP_CATERR# _R

H_PROCHOT# _D

H_THRMTR IP#_R

H_PM_SYNC_R

H_CPUPW RGD_R

VDDPWRGOOD_ R

R1.2 2012/11/08

cost dwon 0ohm

CLK_DP_SSC _N_R

CLK_DP_SSC _P_R

CLK_EXP_N_R

CLK_EXP_P_R

U0301B

AP32

SKTOCC#

AN32

CATERR#

AR27

PECI

AK31

FC1

AM30

PROCHOT#

AM35

THERMTRIP#

AT28

PM_SYNC

AL34

PWRGOOD

AC10

SM_DRAMPWROK

AT26

PLTRSTIN#

G28

DPLL_REF_CLKN

H28

DPLL_REF_CLKP

F27

SSC_DPLL_REF_CLKN

E27

SSC_DPLL_REF_CLKP

D26

BCLKN

E26

BCLKP

SOCKET_947P

12V012BSM001

T28

U28

T30

U30

U29

V29

U31

V31

T34

U34

U35

V35

U32

T32

U33

V33

P29

R29

N28

P28

P31

R31

N30

P30

SOCKET_947P

12V012BSM001

U0301H

DDIB_TXBN_0

DDIB_TXBP_0

DDIB_TXBN_1

DDIB_TXBP_1

DDIB_TXBN_2

DDIB_TXBP_2

DDIB_TXBN_3

DDIB_TXBP_3

DDIC_TXCN_0

DDIC_TXCP_0

DDIC_TXCN_1

DDIC_TXCP_1

DDIC_TXCN_2

DDIC_TXCP_2

DDIC_TXCN_3

DDIC_TXCP_3

DDID_TXDN_0

DDID_TXDP_0

DDID_TXDN_1

DDID_TXDP_1

DDID_TXDN_2

DDID_TXDP_2

DDID_TXDN_3

DDID_TXDP_3

Haswell rPGA EDS

MISC

PWR

CLOCKTHERMAL

Haswell rPGA EDS

DDI

3

eDP

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

DDR3

SM_DRAMRST#

JTAG

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

EDP_AUXN

EDP_AUXP

EDP_HPD

EDP_RCOMP

EDP_DISP_UTIL

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

PRDY#

PREQ#

TMS

TRST#

TDO

DBR#

2

+VCCIO_OUT

+1.35V_VCCDDQ

AP3

SM_RCOMP_0

AR3

SM_RCOMP_1

AP2

SM_RCOMP_2

AN3

AR29

AT29

AM34

TCK

AN33

AM33

AM31

XDP_TDI_R

TDI

AL33

XDP_TDO_R

AP33

H_DBR#_R

AR30

AN31

AN29

AP31

AP30

AN28

AP29

AP28

M27

N27

P27

E24

R27

P35

R35

N34

P34

P33

R33

N32

P32

R0411 100Ohm1%

R0412 75Ohm1%

R0413 100Ohm1%

XDP_PRDY#

XDP_PREQ#

XDP_TCK

XDP_TMS

XDP_TRST#

DP_COMP

R0410 2 4.9Ohm1%

R1.2 2012/10/29

option changed from /non_FDI

R1.2 2012/12/06

remove R0436~R0439 for GDDR5

R0432 0Ohm

R0433 0Ohm

R0434 0Ohm

R0435 0Ohm

12

12

12

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_BPM4

XDP_BPM5

XDP_BPM6

XDP_BPM7

EDP_AUXN 37

EDP_AUXP 37

EDP_HPD# 37

1 2

EDP_DISP_UTIL 37

EDP_TXN0 37

EDP_TXP0 37

EDP_TXN1 37

EDP_TXP1 37

12

12

12

12

R1.2 2012/10/29

option changed from /FDI

+VCCIOA_OUT

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

CPUDRAMRST# 5

T0403

T0404

T0405

T0406

T0407

T0408

T0409

T0410

T0411

T0412

T0413

T0414

T0415

T0416

T0417

T0418

FDI_TXN0 22

FDI_TXP0 22

FDI_TXN1 22

FDI_TXP1 22

+3VSUS

+3V

+1.05VS

+VCCIOA_OUT

1

+VCCIO_OUT 6,37,47,63

+1.35V_VCCDDQ 6

+3VSUS 22,23,27,28 ,30,33,43,61,81,92

+3V 37,43,63,65,91

+1.05VS 25,26,27,47 ,63,80,82

+VCCIOA_OUT 3,6

R1.2 2012/11/27

design gude and check list use 5%

Intel CRB 1%

PM_DRAM_PW RGD

Intel MOW WW14:

A A

change R0449, R0450 va lue

5

+1.35V_VCCDDQ

12

R04230Ohm

R1.1

Power good for +1.35V_VCCDDQ (delay > 15ns)

Processor may be damaged if VIH exceeds the maximum voltage for extended periods.

SM_DRAMPWROK VIH MAX = 1.0V ; VIH MIN=0.45*VDDQ

12

12

R0421

1.8KOhm

1%

0.87 Volt

R0424

9.09KOHM

R0422

3.3KOHM

1%

+3VSUS

@

U0401

A

5

VCC

Y

Vcc=1.65~5.5

@

C0403

0.22UF/10V

B

GND

12

12

@

+3VSUS

12

R0425

1

2

34

10KOhm

@

Q0402

3

PMBS3904

C

B

1

E

2

C0402

@

0.22UF/10V

@

4

+1.35V_VCCDDQ

R0426

1 2

12

17.4KOhm

12

@

R0427

47KOhm

1%

@

VR_HOT#80

Intel Comments

3

1 2

R0431 0Ohm@

H_PROCHOT#

C0401

47PF/50V

@

3

Q0401

2N7002

D

1

THRO_CPU

G

S

2

THRO_CPU 30

2

Title :

Title :

Title :

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

Engineer:

Engineer:

VA70_HW

VA70_HW

VA70_HW

Engineer:

PEGATRON COMPUT ER INC

PEGATRON COMPUT ER INC

PEGATRON COMPUT ER INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Wing_Cheng

Wing_Cheng

Wing_Cheng

4 96Friday, January 18, 2013

4 96Friday, January 18, 2013

4 96Friday, January 18, 2013

1

Rev

Rev

Rev

1.0

1.0

1.0

1 2

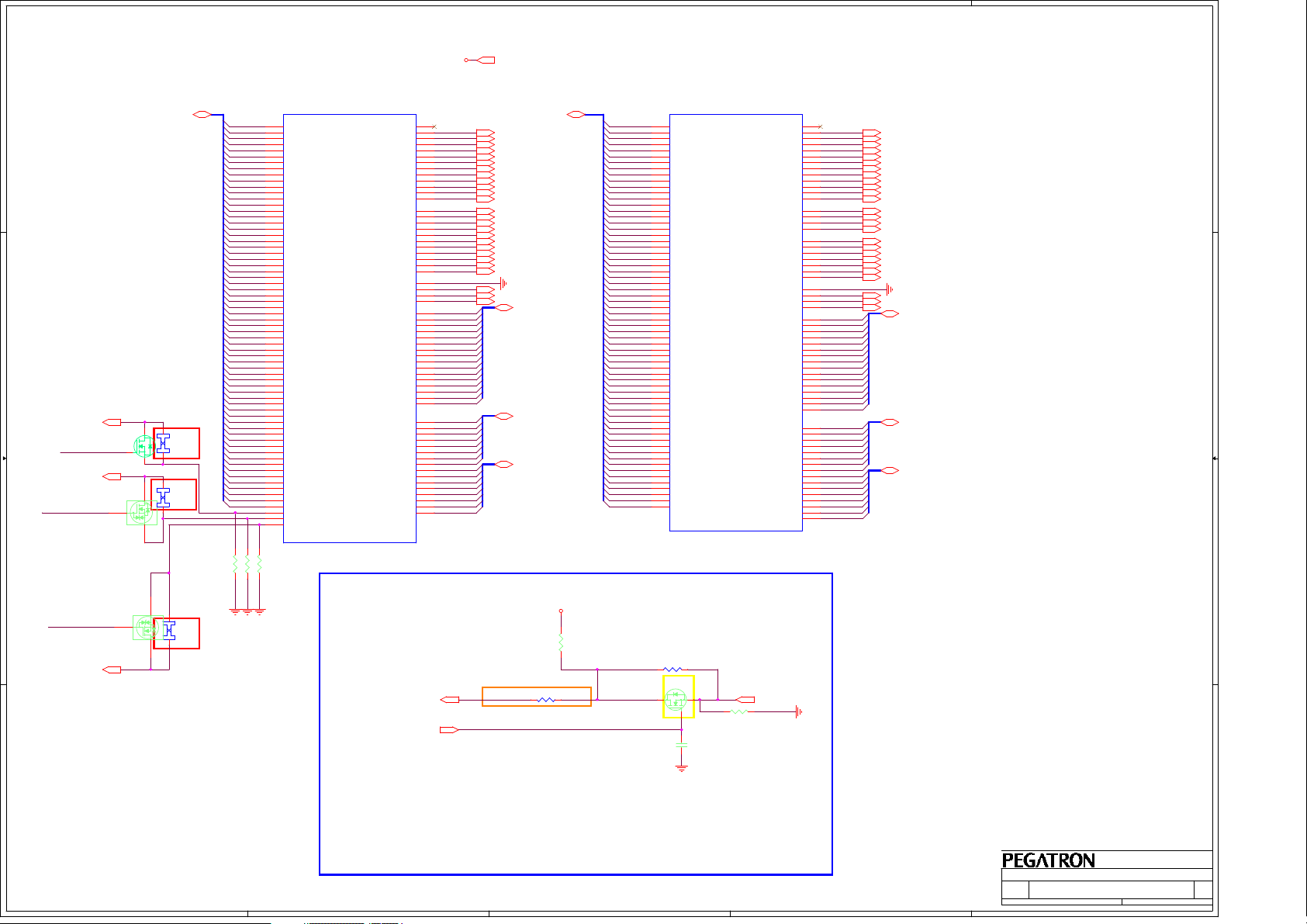

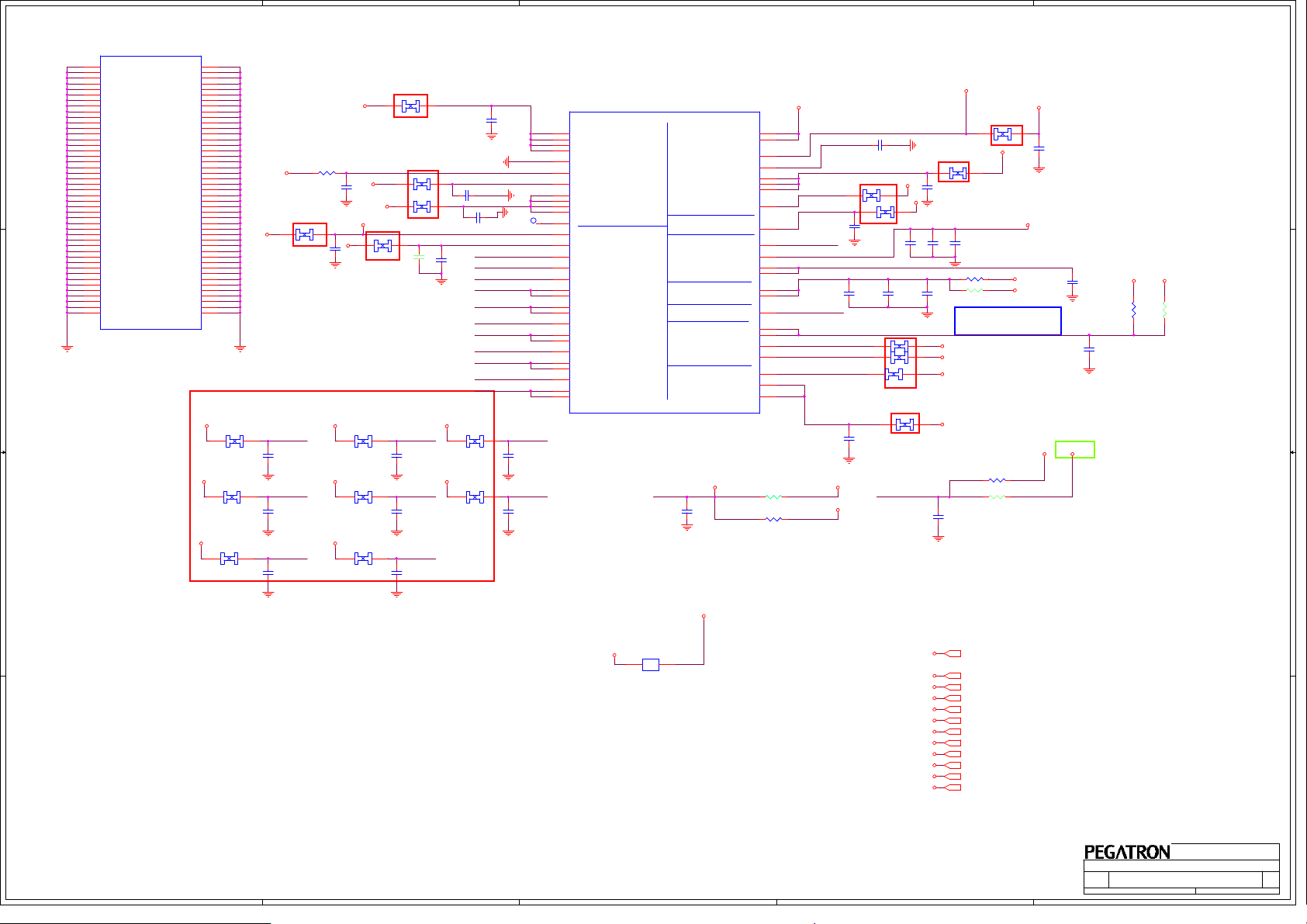

Page 4

5

4

3

2

1

+1.35V

D D

C C

DIMM_VREF_CA18

DRAMRST_CNTRL_PCH

DIMM0_VREF_DQ16,18

R1.2 2012/11/28

cost dwon 0ohm

DRAMRST_CNTRL_PCH DDR_CA_VREF

B B

DRAMRST_CNTRL_PCH

DIMM1_VREF_DQ17,18

CPU driven VREF path is stuffed by default

CRB 0.7

M_A_DQ[63:0]16

R1.2 2012/11/08

2N7002

cost dwon 0ohm

Q0506

12

3

D

SP0501

R0603

1

G

S

2

@

12

SP0502

34

Q0502B

R0603

D

@

5

S

G

UM6K1NG1DTN

UM6K1NG1DTN

G

12

S

2

@

Q0502A

D

6 1

SP0503

R0603

R1.2 2012/11/28

cost dwon 0ohm

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

DDR_WR_VREF01

DDR_WR_VREF02

R05151KOhm

12

1%

1%

@

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AM9

AN9

AM8

AN8

AR9

AT9

AR8

AT8

AJ9

AK9

AJ6

AK6

AJ10

AK10

AJ7

AK7

AF4

AF5

AF1

AF2

AG4

AG5

AG1

AG2

J1

J2

J5

H5

H2

H1

J4

H4

F2

F1

D2

D3

D1

F3

C3

B3

B5

E6

A5

D6

D5

E5

B6

A6

E12

D12

B11

A11

E11

D11

B12

A12

AM3

F16

F13

R05101KOhm

R05091KOhm

12

12

1%

@

@

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

Haswell rPGA EDS

U0301C

AC7

RSVD_AC7

U4

SA_CK_N_0

V4

SA_CK_P_0

AD9

SA_CKE_0

U3

SA_CK_N_1

V3

SA_CK_P_1

AC9

SA_CKE_1

U2

SA_CK_N_2

V2

SA_CK_P_2

AD8

SA_CKE_2

U1

SA_CK_N_3

V1

SA_CK_P_3

AC8

SA_CKE_3

M7

SA_CS_N_0

L9

SA_CS_N_1

M9

SA_CS_N_2

M10

SA_CS_N_3

M8

SA_ODT_0

L7

SA_ODT_1

L8

SA_ODT_2

L10

SA_ODT_3

V5

SA_BS_0

U5

SA_BS_1

AD1

SA_BS_2

V10

VSS1

U6

SA_RAS#

U7

SA_WE#

U8

SA_CAS#

V8

AC6

V9

U9

AC5

AC4

AD6

AC3

AD5

AC2

V6

AC1

AD4

V7

AD3

AD2

AP15

AP8

AJ8

AF3

J3

E2

C5

C11

AP14

AP9

AK8

AG3

H3

E3

C6

C12

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_DQS_N_0

SA_DQS_N_1

SA_DQS_N_2

SA_DQS_N_3

SA_DQS_N_4

SA_DQS_N_5

SA_DQS_N_6

SA_DQS_N_7

SA_DQS_P_0

SA_DQS_P_1

SA_DQS_P_2

SA_DQS_P_3

SA_DQS_P_4

SA_DQS_P_5

SA_DQS_P_6

SA_DQS_P_7

SOCKET_947P

12V012BSM001

R1.0 S3 circuit:- DRAM_RST# to memory should be high during S3

R1.0 0209

Change R0508 to 1K ohm

R0508 close to DIMM

DDR3_DRAMRST#16,17 CPUDRAMRST# 4

DRAMRST_CNTRL_PCH21

+1.35V 6,16,18,63,83

M_B_DQ[63:0]17

M_A_DIM0_CLK_DDR#0 16

M_A_DIM0_CLK_DDR0 16

M_A_DIM0_CKE0 16

M_A_DIM0_CLK_DDR#1 16

M_A_DIM0_CLK_DDR1 16

M_A_DIM0_CKE1 16

M_A_DIM0_CLK_DDR#2 16

M_A_DIM0_CLK_DDR2 16

M_A_DIM0_CKE2 16

M_A_DIM0_CLK_DDR#3 16

M_A_DIM0_CLK_DDR3 16

M_A_DIM0_CKE3 16

M_A_DIM0_CS#0 16

M_A_DIM0_CS#1 16

M_A_DIM0_CS#2 16

M_A_DIM0_CS#3 16

M_A_DIM0_ODT0 16

M_A_DIM0_ODT1 16

M_A_DIM0_ODT2 16

M_A_DIM0_ODT3 16

M_A_BS0 16

M_A_BS1 16

M_A_BS2 16

M_A_RAS# 16

M_A_WE# 16

M_A_CAS# 16

M_A_A[15:0] 16

M_A_DQS#[7:0] 16

M_A_DQS[7:0] 16

+1.35V

1 2

R0508 1KOhm

R0520,R0521 must be grounded.

CRB 0.7

12

S

2

G

1

12

Haswell rPGA EDS

1 2

R0506 4.99KOhm

@

AR18

M_B_DQ0

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

R0507

1KOhm

@

1 2

0614-change Q0501 from UM6K1N to 2N7002

CPUDRAMRST#_R

SB_DQ_0

AT18

SB_DQ_1

AM17

SB_DQ_2

AM18

SB_DQ_3

AR17

SB_DQ_4

AT17

SB_DQ_5

AN17

SB_DQ_6

AN18

SB_DQ_7

AT12

SB_DQ_8

AR12

SB_DQ_9

AN12

SB_DQ_10

AM11

SB_DQ_11

AT11

SB_DQ_12

AR11

SB_DQ_13

AM12

SB_DQ_14

AN11

SB_DQ_15

AR5

SB_DQ_16

AR6

SB_DQ_17

AM5

SB_DQ_18

AM6

SB_DQ_19

AT5

SB_DQ_20

AT6

SB_DQ_21

AN5

SB_DQ_22

AN6

SB_DQ_23

AJ4

SB_DQ_24

AK4

SB_DQ_25

AJ1

SB_DQ_26

AJ2

SB_DQ_27

AM1

SB_DQ_28

AN1

SB_DQ_29

AK2

SB_DQ_30

AK1

SB_DQ_31

L2

SB_DQ_32

M2

SB_DQ_33

L4

SB_DQ_34

M4

SB_DQ_35

L1

SB_DQ_36

M1

SB_DQ_37

L5

SB_DQ_38

M5

SB_DQ_39

G7

SB_DQ_40

J8

SB_DQ_41

G8

SB_DQ_42

G9

SB_DQ_43

J7

SB_DQ_44

J9

SB_DQ_45

G10

SB_DQ_46

J10

SB_DQ_47

A8

SB_DQ_48

B8

SB_DQ_49

A9

SB_DQ_50

B9

SB_DQ_51

D8

SB_DQ_52

E8

SB_DQ_53

D9

SB_DQ_54

E9

SB_DQ_55

E15

SB_DQ_56

D15

SB_DQ_57

A15

SB_DQ_58

B15

SB_DQ_59

E14

SB_DQ_60

D14

SB_DQ_61

A14

SB_DQ_62

B14

SB_DQ_63

R0501 0Ohm

Q0501

@

2N7002

D

3

C0501

@

0.047UF/16V

U0301D

AG8

RSVD1

Y4

SB_CKN0

AA4

SB_CK0

AF10

SB_CKE_0

Y3

SB_CKN1

AA3

SB_CK1

AG10

SB_CKE_1

Y2

SB_CKN2

AA2

SB_CK2

AG9

SB_CKE_2

Y1

SB_CKN3

AA1

SB_CK3

AF9

SB_CKE_3

P4

SB_CS_N_0

R2

SB_CS_N_1

P3

SB_CS_N_2

P1

SB_CS_N_3

R4

SB_ODT_0

R3

SB_ODT_1

R1

SB_ODT_2

P2

SB_ODT_3

R7

SB_BS_0

P8

SB_BS_1

AA9

SB_BS_2

R10

VSS2

R6

SB_RAS#

P6

SB_WE#

P7

SB_CAS#

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

AP18

AP11

AP5

AJ3

L3

H9

C8

C14

AP17

AP12

AP6

AK3

M3

H8

C9

C15

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_A15

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_DQS_N_0

SB_DQS_N_1

SB_DQS_N_2

SB_DQS_N_3

SB_DQS_N_4

SB_DQS_N_5

SB_DQS_N_6

SB_DQS_N_7

SB_DQS_P_0

SB_DQS_P_1

SB_DQS_P_2

SB_DQS_P_3

SB_DQS_P_4

SB_DQS_P_5

SB_DQS_P_6

SB_DQS_P_7

SOCKET_947P

12V012BSM001

1%

M_B_DIM0_CLK_DDR#0 17

M_B_DIM0_CLK_DDR0 17

M_B_DIM0_CKE0 17

M_B_DIM0_CLK_DDR#1 17

M_B_DIM0_CLK_DDR1 17

M_B_DIM0_CKE1 17

M_B_DIM0_CLK_DDR#2 17

M_B_DIM0_CLK_DDR2 17

M_B_DIM0_CKE2 17

M_B_DIM0_CLK_DDR#3 17

M_B_DIM0_CLK_DDR3 17

M_B_DIM0_CKE3 17

M_B_DIM0_CS#0 17

M_B_DIM0_CS#1 17

M_B_DIM0_CS#2 17

M_B_DIM0_CS#3 17

M_B_DIM0_ODT0 17

M_B_DIM0_ODT1 17

M_B_DIM0_ODT2 17

M_B_DIM0_ODT3 17

M_B_BS0 17

M_B_BS1 17

M_B_BS2 17

M_B_RAS# 17

M_B_WE# 17

M_B_CAS# 17

M_B_A[15:0] 17

M_B_DQS#[7:0] 17

M_B_DQS[7:0] 17

Reserve S3 power reduction schematic

If don't support S3 power reduction

A A

5

1. Unmount R0450, R0452, U0404, R0453, Q0403, C0404, R0455, R0454, C0405

2. Change R0449 to 200ohm from 1kohm, change R0409 to 130ohm from 0ohm - Design Guide 1.0 page 106

3. Unmount Q0501, C0501, R0506, R0504, R0507

4. Mount R0501, change r0508 to 0ohm from 1kohm

5 Unmount Q0701, R0703, R0705, Q0702

6. Mount R0702 and short JP0701

7. Unmount R2232, R2231, Q2203

4

3

Title :

Title :

Title :

CPU(2)_DDR3

CPU(2)_DDR3

CPU(2)_DDR3

Wing_Cheng

Wing_Cheng

Engineer:

Engineer:

VA70_HW

VA70_HW

VA70_HW

Engineer:

1

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Wing_Cheng

5 96Friday, January 18, 2013

5 96Friday, January 18, 2013

5 96Friday, January 18, 2013

Rev

Rev

Rev

1.0

1.0

1.0

Page 5

5

Decoupling guide from Intel (SPEC)

VDDQ 22uF * 11 pcs (stuff)

10uF * 10 pcs (stuff)

330uF * 2 pcs (stuff)

Decoupling guide from Intel ( SPEC)

+VCORE 10uF * 11pcs (stuff)

22uF * 19pcs (stuff)

D D

470uF * 4pcs (stuff)

PS_S3CNTRL_1.5V22

Default: no sup port

S3 power reduct ion

C C

+VCORE

12

12

C0654

C0647

22UF/6.3V

22UF/6.3V

vx_c0805_h57_small

12

C0630

22UF/6.3V

vx_c0805_h57_small

12

C0638

22UF/6.3V

vx_c0805_h57_small

vx_c0805_h57_small

12

C0641

22UF/6.3V

vx_c0805_h57_small

12

C0628

22UF/6.3V

vx_c0805_h57_small

B B

vx_c0805_h57_small

vx_c0805_h57_small

vx_c0805_h57_small

Decoupling guide from Intel (EE)

VDDQ 22uF * 2pcs (stuff)

10uF * 2pcs (stuff)

330uF * 1pcs (stuff)

Decoupling guide from Intel ( EE)

+VCORE 10uF * 11 pcs (stuff)

22uF * 19 pcs (stuff)

470uF * 5 pcs (stuff)

1 2

@

R0608 0Ohm

@

+1.35V

VR_SVID_DATA80

12

12

C0652

22UF/6.3V

vx_c0805_h57_small

12

C0640

22UF/6.3V

vx_c0805_h57_small

12

C0632

22UF/6.3V

vx_c0805_h57_small

C0650

22UF/6.3V

vx_c0805_h57_small

12

C0636

22UF/6.3V

vx_c0805_h57_small

12

C0629

22UF/6.3V

vx_c0805_h57_small

12

C0648

22UF/6.3V

vx_c0805_h57_small

12

C0634

22UF/6.3V

vx_c0805_h57_small

12

C0631

22UF/6.3V

vx_c0805_h57_small

12

C0623470PF/50V

12

C0653

22UF/6.3V

12

C0639

22UF/6.3V

12

C0635

22UF/6.3V

PS_S3CNTRL_1.5V_R

PS_S3CNTRL_1.5V_R

@

SIR472DP-T1-GE3

5 4

5

6

7

8

Q0601

4.2A

3MM_OPEN_5MIL

1MM_OPEN_M1M2

12

vx_c0805_h57_small

12

vx_c0805_h57_small

12

vx_c0805_h57_small

4

G

D

3

S

2

1

JP0601

2

112

JP0602

2

112

Placement note:

1. R0602 close to CPU

2. R0603 close to CPU

3. R0605 close to VR

4. R0608 close to CPU

5. R0607 close to VR

6. R0611 close to CPU

+VCCIO_OUT +VCCIO_OUT

R0610

130Ohm

1%

R1.2 2012/11/08

1 2

cost dwon 0ohm

SP0602 R0 402

12

C0649

C0651

22UF/6.3V

22UF/6.3V

vx_c0805_h57_small

vx_c0805_h57_small

12

C0637

C0607

22UF/6.3V

22UF/6.3V

vx_c0805_h57_small

vx_c0805_h57_small

12

C0609

C0633

22UF/6.3V

22UF/6.3V

vx_c0805_h57_small

vx_c0805_h57_small

12

+

1 2

12

C0645

22UF/6.3V

vx_c0805_h57_small

12

C0627

22UF/6.3V

vx_c0805_h57_small

12

C0610

22UF/6.3V

CE0602

560UF/2.5V

@

12

C0644

22UF/6.3V

12

C0608

22UF/6.3V

3

12

12

+

C0604

CE0601

22UF/6.3V

560UF/2.5V

vx_c0805_h57_small

vx_c0805_h57_small

12

@

C0603

10UF/10V

vx_c0805_h57_small

vx_c0805_h57_small

R0609

130Ohm

1%

1 2

VR_SVID_CLK80

Power team sugg estion

12

C0616

22UF/6.3V

vx_c0805_h57_small

12

12

C0605

22UF/6.3V

vx_c0805_h57_small

12

@

C0622

10UF/10V

vx_c0805_h57_small

If XDP not implemented, then Route Processor PWR_DEBUG as a test point.

This Test point must be clearly labeled(shark bay schematic check list 497750)

12

@

C0614

22UF/6.3V

vx_c0805_h57_small

vx_c0805_h57_small

12

12

@

C0642

10UF/10V

vx_c0805_h57_small

Unstuff R0622

Intel MOW WW09: renamed

VCCIO2PCH to RSVD

+VCCIO_OUT

R0613

54.9Ohm

R1.2 2012/11/08

1%

cost dwon 0ohm

1 2

VR_SVID_ALERT#80

1 2

SP0603 R0 402

12

12

@

@

C0625

C0626

22UF/6.3V

22UF/6.3V

vx_c0805_h57_small

12

@

@

C0643

C0646

10UF/10V

10UF/10V

vx_c0805_h57_small

vx_c0805_h57_small

R1.2 2012/11/16

follow Intel CRB

Place as close to CPU as possible

R1.2 2012/11/26

follow design guide

+VCCIO_OUT

12

@

@

C0606

C0618

22UF/6.3V

22UF/6.3V

vx_c0805_h57_small

vx_c0805_h57_small

12

12

@

@

C0615

C0613

10UF/10V

10UF/10V

vx_c0805_h57_small

vx_c0805_h57_small

+VCCIO_OUT(1---1.05V) output from CPU

+VCCIOA_OUT

+VCCIO2PCH

R0611

75Ohm

+VCCIO_OUT

R0603 0Ohm

R0604 0Ohm@

R0605 0Ohm

12

C0657

22UF/6.3V

@

1%

R1.1

12

12

12

@

C0619

22UF/6.3V

vx_c0805_h57_small

vx_c0805_h57_small

12

12

@

C0601

10UF/10V

vx_c0805_h57_small

VCCSENSE80

1 2

1 2

1 2

C0655

12

4.7UF/6.3V

C0611

0.01UF/50V

@

12

@

@

C0620

C0621

22UF/6.3V

22UF/6.3V

vx_c0805_h57_small

12

@

@

C0602

C0617

10UF/10V

10UF/10V

vx_c0805_h57_small

R0601

100Ohm

1%

SP0601 R0 402

+VCCIO_OUT_R

+VCCIO2PCH_R

+VCCIOA_OUT_R

12

12

R0612 43Ohm

T0606

T0602

T0603

T0605

T0604

12

@

C0624

22UF/6.3V

+VCORE

+VCORE

R1.2 2012/11/08

cost dwon 0ohm

1 2

1 2

C0612

0.01UF/50V

1

1

1

1

1

+1.35V_VCCDDQ

VCC_SENSE_R

T0601

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

PWR_DEBUG

+VCORE

+1.35V_VCCDDQ

+1.35V

+VCORE

+VCCIO_OUT

+VCCIO2PCH

+VCCIOA_OUT

U0301E

K27

RSVD23

L27

RSVD22

T27

RSVD21

V27

RSVD20

AB11

VDDQ13

AB2

VDDQ12

AB5

VDDQ11

AB8

VDDQ10

AE11

VDDQ9

AE2

VDDQ8

AE5

VDDQ7

AE8

VDDQ6

AH11

VDDQ14

K11

VDDQ15

N11

VDDQ5

N8

VDDQ16

T11

VDDQ4

T2

VDDQ17

T5

VDDQ3

T8

VDDQ18

W11

VDDQ2

W2

VDDQ19

W5

VDDQ1

W8

VDDQ20

N26

RSVD19

K26

VCC103

AL27

RSVD18

AK27

RSVD24

AL35

VCC_SENSE

E17

RSVD27

AN35

VCCIO_OUT

A23

RSVD25

F22

VCOMP_OUT

W32

RSVD30

AL16

RSVD29

J27

1

RSVD26

AL13

RSVD28

AM28

VIDALERT#

AM29

VIDSCLK

AL28

VIDSOUT

AP35

VSS3

H27

PWR_DEBUG

AP34

VSS4

AT35

RSVD_TP4

AR35

RSVD_TP3

AR32

RSVD_TP2

AL26

RSVD_TP1

AT34

VSS5

AL22

VSS6

AT33

VSS7

AM21

VSS8

AM25

VSS9

AM22

VSS10

AM20

VSS11

AM24

VSS12

AL19

VSS13

AM23

VSS14

AT32

VSS15

Y25

VCC11

Y26

VCC10

Y27

VCC9

Y28

VCC8

Y29

VCC7

Y30

VCC6

Y31

VCC5

Y32

VCC4

Y33

VCC3

Y34

VCC2

Y35

VCC1

SOCKET_947P

12V012BSM001

2

+1.35V_VCCDDQ 4

+1.35V 5,16,18,63,83

+VCORE 9,63,80

+VCCIO_OUT 4,37,47,63

+VCCIO2PCH 27

+VCCIOA_OUT 3,4

Haswell rPGA EDS

VCC100

VCC99

VCC98

VCC97

VCC96

VCC95

VCC94

VCC93

VCC92

VCC91

VCC90

VCC89

VCC88

VCC87

VCC86

VCC85

VCC84

VCC83

VCC82

VCC81

VCC80

VCC79

VCC78

VCC77

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

VCC56

VCC55

VCC54

VCC53

VCC52

VCC51

VCC50

VCC49

VCC48

VCC102

VCC101

VCC47

VCC46

VCC45

VCC44

VCC43

VCC42

VCC41

VCC40

VCC39

VCC38

VCC37

VCC36

VCC35

VCC34

VCC33

VCC32

VCC31

VCC30

VCC29

VCC28

VCC27

VCC26

VCC25

VCC24

VCC23

VCC22

VCC21

VCC20

VCC19

VCC18

VCC17

VCC16

VCC15

VCC14

VCC13

VCC12

AA26

AA28

AA34

AA30

AA32

AB26

AB29

AB25

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AG30

AG32

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

+VCORE

1

Cap of 470UF or more place at power schematic

A A

Title :

Title :

Title :

CPU(4)_PWR

CPU(4)_PWR

CPU(4)_PWR

Wing_Cheng

Wing_Cheng

Wing_Cheng

Engineer:

Engineer:

VA70_HW

VA70_HW

VA70_HW

Engineer:

Rev

Rev

Rev

1.0

1.0

1.0

6 96Friday, January 18, 2013

6 96Friday, January 18, 2013

6 96Friday, January 18, 2013

1

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Nam e

Size Project Nam e

Size Project Nam e

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

5

4

3

2

Page 6

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

CPU(4)_PWR

CPU(4)_PWR

CPU(4)_PWR

Wing_Cheng

Wing_Cheng

Engineer:

Engineer:

VA70_HW

VA70_HW

VA70_HW

Engineer:

1

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Wing_Cheng

7 96Friday, January 18, 2013

7 96Friday, January 18, 2013

7 96Friday, January 18, 2013

Rev

Rev

Rev

1.0

1.0

1.0

Page 7

5

Haswell rPGA EDS

U0301F

A10

VSS16

A13

VSS127

A16

VSS238

A19

VSS268

A22

VSS279

A25

VSS290

A27

VSS301

A29

D D

C C

B B

A A

A31

A33

AA11

AA25

AA27

AA31

AA29

AB1

AB10

AA33

AA35

AB3

AC25

AC27

AB4

AB6

AB7

AB9

AC11

AD11

AC29

AC31

AC33

AC35

AD7

AE1

AE10

AE25

AE29

AE3

AE27

AE35

AE4

AE6

AE7

AE9

AF11

AF6

AF8

AG11

AG25

AE31

AG31

AE33

AG6

AH1

AH10

AH2

AG27

AG29

AH3

AG33

AG35

AH4

AH5

AH6

AH7

AH8

AH9

AJ11

AJ5

AK11

AK25

AK26

AK28

AK29

AK30

AK32

E19

A3

A4

A7

VSS312

VSS323

VSS17

VSS28

VSS39

VSS50

VSS61

VSS72

VSS83

VSS94

VSS105

VSS116

VSS128

VSS139

VSS150

VSS161

VSS172

VSS183

VSS194

VSS205

VSS216

VSS227

VSS239

VSS250

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS313

SOCKET_947P

12V012BSM001

5

VSS314

VSS315

VSS316

VSS317

VSS318

VSS319

VSS320

VSS321

VSS322

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

AK34

AK5

AL1

AL10

AL11

AL12

AL14

AL15

AL17

AL18

AL2

AL20

AL21

AL23

E22

AL3

AL4

AL5

AL6

AL7

AL8

AL9

AM10

AM13

AM16

AM19

E25

AM32

AM4

AM7

AN10

AN13

AN16

AN19

AN2

AN21

AN24

AN27

AN30

AN34

AN4

AN7

AP1

AP10

AP13

AP16

AP19

AP4

AP7

W25

AR10

AR13

AR16

AR19

AR2

AR22

AR25

AR28

AR31

AR34

AR4

AR7

AT10

AT13

AT16

AT19

AT21

AT24

AT27

AT3

AT30

AT4

AT7

B10

B13

B16

B19

B2

B22

4

B34

B4

B7

C1

C10

C13

C16

C19

C2

C22

C24

C26

C28

C30

C32

C34

C4

C7

D10

D13

D16

D19

D22

D25

D27

D29

D31

D33

D35

D4

D7

E1

E10

E13

E16

E4

E7

F10

F11

F12

F14

F15

F17

F18

F20

F21

F23

F24

F26

F28

F30

F32

F34

F4

F6

F7

F8

F9

G1

G11

G2

G27

G29

G3

G31

G33

G35

G4

G5

H10

H26

H6

H7

J11

J26

J28

J30

J32

J34

J6

K1

SOCKET_947P

12V012BSM001

4

U0301G

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS173

3

Haswell rPGA EDS

3

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS_SENSE

RSVD31

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W10

W3

W35

W4

W6

W7

W9

Y11

H11

AL24

F19

T26

AK35

AK33

2

Placement note:

1. SP0801 close to CPU

SP0801 R0 402

VSS_SENSE_R

T0801

1

2

R1.2 2012/11/08

cost dwon 0ohm

1 2

1 2

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Projec t Name

Size Projec t Name

Size Projec t Name

B

B

B

Date: Sheet of

Date: Sheet of

Date: Sheet of

R0802

100Ohm

1%

VSSSENSE 80

VA70_HW

VA70_HW

VA70_HW

Engineer:

Engineer:

Engineer:

Title :

Title :

Title :

1

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

Wing_Cheng

Wing_Cheng

Wing_Cheng

8 96Friday, January 18, 2013

8 96Friday, January 18, 2013

8 96Friday, January 18, 2013

1

Rev

Rev

Rev

1.0

1.0

1.0

Page 8

5

4

3

2

1

CFG strapping information:

CFG[1:0]: Reserved configuration lane.

D D

C C

B B

CFG[2]: PCIE Static Numbering Lane Reversal- CFG[2] is for the 16x

- 1: (Default) Normal Operation, Lane # definition matches sockect pin map definition

- 0: Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

CFG[4]: eDP enable

-1 = Disabled

-0 = Enabled

CFG[6:5]: PCI Express Port Bifurcation Straps

-00 = 1 x8, 2 x4 PCI Express*

-01 = reserved

-10 = 2 x8 PCI Express*

-11 = 1 x16 PCI Express*

CFG[19:7]: Reserved configuration lane.

CFG2

R0903 1KOhm

CFG4

R0905 1KOhm

CFG5

R0904 1KOhm@

CFG6

R0906 1KOhm@

CFG7

R0907 1KOhm@

CFG9

R0909 1KOhm

The CFG signals have a default value of '1'

1 2

1%

1 2

1%

1 2

1%

1 2

1%

1 2

1%

1 2

1%

@

R0901 49.9Ohm1%

R0902 49.9Ohm1%

+VCORE

U0301I

AT1

RSVD_TP17

AT2

RSVD_TP16

AD10

RSVD2

A34

RSVD_TP15

A35

RSVD_TP14

W29

RSVD_TP18

W28

RSVD_TP19

12

H_CPU_RSVDG26

12

H_CPU_RSVDW34

T0905

T0906

T0907

T0908

T0910

T0911

T0912

T0914

T0913

T0915

T0917

T0916

T0918

T0919

T0920

T0921

G26

TESTLO1

W33

RSVD3

AL30

RSVD4

AL29

RSVD5

F25

VCC104

C35

RSVD_TP13

B35

RSVD_TP12

AL25

RSVD_TP20

W30

RSVD_TP21

W31

RSVD_TP22

W34

AT20

AR20

AP20

AP22

AT22

AN22

AT25

AN23

AR24

AT23

AN20

AP24

AP26

AN25

AN26

AP25

TESTLO2

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

SOCKET_947P

12V012BSM001

1

CFG0

1

CFG1

1

CFG2

1

CFG3

1

CFG4

1

CFG5

1

CFG6

1

CFG7

1

CFG8

1

CFG9

1

CFG10

1

CFG11

1

CFG12

1

CFG13

1

CFG14

1

CFG15

+VCORE

Haswell rPGA EDS

RSVD_TP11

RSVD_TP10

RSVD_TP9

RSVD_TP8

CFG_RCOMP

CFG_16

CFG_18

CFG_17

CFG_19

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD_TP7

RSVD_TP6

RSVD_TP5

RSVD16

RSVD17

VSS258

VSS259

+VCORE 6,63,80

C23

B23

D24

D23

AT31

AR21

AR23

AP21

AP23

AR33

G6

FC2

AM27

AM26

F5

AM2

K6

E18

U10

P10

B1

NC

A2

AR1

E21

E20

AP27

AR26

AL31

AL32

R1.2 2012/11/26

reserved for 2014 processor

PM_PWROK 22,30,92

12

R0910

4.7KOhm

@

1%

R1.2 2012/11/28

channged from 2.2k/5%

12

R0911

2.2KOhm

1%

@

T0922

T0923

T0925

T0924

1 2

R090849.9Ohm 1%

CFG_RCOMP

1

CFG16

1

CFG17

1

CFG18

1

CFG19

FC_G6

FC signals are signals that are available for compatibility with other processors. A test point

may be placed on the board for these lands. Refer to the appropriate platform design guide

for implementation details.(haswell EDS 487246)

A A

Title :

Title :

Title :

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

Wing_Cheng

Wing_Cheng

1

Wing_Cheng

9 96Friday, January 18, 2013

9 96Friday, January 18, 2013

9 96Friday, January 18, 2013

Rev

Rev

Rev

1.0

1.0

1.0

Engineer:

Engineer:

VA70_HW

VA70_HW

VA70_HW

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Page 9

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

NB(3)_****

NB(3)_****

NB(3)_****

Wing_Cheng

Wing_Cheng

Engineer:

Engineer:

VA70_HW

VA70_HW

VA70_HW

Engineer:

1

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Wing_Cheng

10 96Friday , January 18, 2013

10 96Friday , January 18, 2013

10 96Friday , January 18, 2013

Rev

Rev

Rev

1.0

1.0

1.0

Page 10

5

R1.2 2012/11/20

1 2

3 4

M_A_WE #

M_A_RAS #

M_A_CAS #

M_A_BS2

M_A_BS1

M_A_BS0

1 2

3 4

10KOhm

10KOhm

10KOhm

10KOhm

/DGPU

/DGPU

Part ref. changed

98

M_A_A0

97

M_A_A1

96

M_A_A2

95

M_A_A3

92

M_A_A4

91

M_A_A5

90

M_A_A6

86

M_A_A7

89

M_A_A8

85

M_A_A9

107

M_A_A10

84

M_A_A11

83

M_A_A12

119

M_A_A13

80

M_A_A14

78

M_A_A15

102

104

101

103

121

114

120

116

113

110

115

79

108

109

74

73

201

RN1601A

197

RN1601B

188

M_A_DQS 7

186

M_A_DQS #7

171

M_A_DQS 6M_A_DQS 2

169

M_A_DQS #6

154

M_A_DQS 5

152

M_A_DQS #5

137

M_A_DQS 4

135

M_A_DQS #4

64

M_A_DQS 3

62

M_A_DQS #3

47

M_A_DQS 2

45

M_A_DQS #2

29

M_A_DQS 1

27

M_A_DQS #1

12

M_A_DQS 0

10

M_A_DQS #0

187

170

153

136

63

46

28

11

202

200

R1.2 2012/11/20

Part ref. changed

98

M_A_A0

97

M_A_A1

96

M_A_A2

95

M_A_A3

92

M_A_A4

91

M_A_A5

90

M_A_A6

86

M_A_A7

89

M_A_A8

85

M_A_A9

107

M_A_A10

84

M_A_A11

83

M_A_A12

119

M_A_A13

80

M_A_A14

78

M_A_A15

102

104

101

103

121

114

120

116

113

110

115

79

108

109

74

73

201

RN1602A

197

RN1602B

188

M_A_DQS 7

186

M_A_DQS #7

171

M_A_DQS 6

169

M_A_DQS #6

154

M_A_DQS 5

152

M_A_DQS #5

137

M_A_DQS 4

135

M_A_DQS #4

64

M_A_DQS 3

62

M_A_DQS #3

47

M_A_DQS 2

45

M_A_DQS #2

29

M_A_DQS 1

27

M_A_DQS #1

12

M_A_DQS 0

10

M_A_DQS #0

187

170

153

136

63

46

28

11

202

200

H:4mm

CON1601 A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

CK1

CK1#

CK0

CK0#

S1#

S0#

ODT1

ODT0

WE#

RAS#

CAS#

BA2

BA1

BA0

CKE1

CKE0

SA1

SA0

DQS7

DQS#7

DQS6

DQS#6

DQS5

DQS#5

DQS4

DQS#4

DQS3

DQS#3

DQS2

DQS#2

DQS1

DQS#1

DQS0

DQS#0

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

SCL

SDA

DDR3_D IMM_204P

12V02G IRM001

H:8mm

CON1602 A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

CK1

CK1#

CK0

CK0#

S1#

S0#

ODT1

ODT0

WE#

RAS#

CAS#

BA2

BA1

BA0

CKE1

CKE0

SA1

SA0

DQS7

DQS#7

DQS6

DQS#6

DQS5

DQS#5

DDR3_D IMM_204P

DQS4

12V02G BRM001

DQS#4

DQS3

DQS#3

DQS2

DQS#2

DQS1

DQS#1

DQS0

DQS#0

DM7

DM6

DM5

DM4

DM3

DM2

DM1

DM0

SCL

SDA

/DGPU

5

M_A_DQ0

DQ0

7

M_A_DQ4

DQ1

15

M_A_DQ3

DQ2

17

M_A_DQ2

DQ3

4

M_A_DQ7

0

DQ4

6

M_A_DQ6

DQ5

16

M_A_DQ1

DQ6

18

M_A_DQ5

DQ7

21

M_A_DQ1 1

DQ8

23

M_A_DQ9

DQ9

33

M_A_DQ1 5

DQ10

35

M_A_DQ1 4

DQ11

22

M_A_DQ1 0

DQ12

24

M_A_DQ8

1

DQ13

34

M_A_DQ1 2

DQ14

36

M_A_DQ1 3

DQ15

39

M_A_DQ2 0

DQ16

41

M_A_DQ1 7

DQ17

51

M_A_DQ1 8

DQ18

53

M_A_DQ2 3

DQ19

40

M_A_DQ1 6

2

DQ20

42

M_A_DQ2 1

DQ21

50

M_A_DQ1 9

DQ22

52

M_A_DQ2 2

DQ23

57

M_A_DQ2 4

DQ24

59

M_A_DQ2 8

DQ25

67

M_A_DQ2 7

DQ26

69

M_A_DQ3 1

DQ27

56

M_A_DQ2 5

3

DQ28

58

M_A_DQ2 9

DQ29

68

M_A_DQ3 0

DQ30

70

M_A_DQ2 6

DQ31

129

M_A_DQ3 7

DQ32

131

M_A_DQ3 2

DQ33

141

M_A_DQ3 5

DQ34

143

M_A_DQ3 4

DQ35

130

M_A_DQ3 8

DQ36

132

M_A_DQ3 3

DQ37

140

M_A_DQ3 6

4

DQ38

142

M_A_DQ3 9

DQ39

147

M_A_DQ4 4

DQ40

149

M_A_DQ4 2

DQ41

157

M_A_DQ4 7

DQ42

159

M_A_DQ4 5

DQ43

146

M_A_DQ4 0

DQ44

148

M_A_DQ4 1

DQ45

158

M_A_DQ4 3

5

DQ46

160

M_A_DQ4 6

DQ47

163

M_A_DQ5 2

DQ48

165

M_A_DQ5 3

DQ49

175

M_A_DQ5 5

DQ50

177

M_A_DQ5 4

DQ51

164

M_A_DQ5 1

DQ52

166

M_A_DQ4 9

DQ53

174

M_A_DQ4 8

6

DQ54

176

M_A_DQ5 0

DQ55

181

M_A_DQ5 8

DQ56

183

M_A_DQ6 1

DQ57

191

M_A_DQ6 3

DQ58

193

M_A_DQ5 7

DQ59

180

M_A_DQ6 0

DQ60

182

M_A_DQ5 6

DQ61

192

M_A_DQ6 2

7

DQ62

194

M_A_DQ5 9

DQ63

30

RESET#

5

M_A_DQ0

DQ0

7

M_A_DQ4

DQ1

15

M_A_DQ3

DQ2

17

M_A_DQ2

DQ3

4

M_A_DQ7

DQ4

6

M_A_DQ6

DQ5

16

M_A_DQ1

DQ6

18

M_A_DQ5

0

DQ7

21

M_A_DQ1 1

DQ8

23

M_A_DQ9

DQ9

33

M_A_DQ1 5

DQ10

35

M_A_DQ1 4

DQ11

22

M_A_DQ1 0

DQ12

24

M_A_DQ8

DQ13

34

M_A_DQ1 2

DQ14

36

M_A_DQ1 3

1

DQ15

39

M_A_DQ2 0

DQ16

41

M_A_DQ1 7

DQ17

51

M_A_DQ1 8

DQ18

53

M_A_DQ2 3

DQ19

40

M_A_DQ1 6

DQ20

42

M_A_DQ2 1

DQ21

50

M_A_DQ1 9

DQ22

52

M_A_DQ2 2

2

DQ23

57

M_A_DQ2 4

DQ24

59

M_A_DQ2 8

DQ25

67

M_A_DQ2 7

DQ26

69

M_A_DQ3 1

DQ27

56

M_A_DQ2 5

DQ28

58

M_A_DQ2 9

DQ29

68

M_A_DQ3 0

DQ30

70

M_A_DQ2 6

3

DQ31

129

M_A_DQ3 7

DQ32

131

M_A_DQ3 2

DQ33

141

M_A_DQ3 5

DQ34

143

M_A_DQ3 4

DQ35

130

M_A_DQ3 8

DQ36

132

M_A_DQ3 3

DQ37

140

M_A_DQ3 6

DQ38

142

M_A_DQ3 9

4

DQ39

147

M_A_DQ4 4

DQ40

149

M_A_DQ4 2

DQ41

157

M_A_DQ4 7

DQ42

159

M_A_DQ4 5

DQ43

146

M_A_DQ4 0

DQ44

148

M_A_DQ4 1

DQ45

158

M_A_DQ4 3

DQ46

160

M_A_DQ4 6

5

DQ47

163

M_A_DQ5 2

DQ48

165

M_A_DQ5 3

DQ49

175

M_A_DQ5 5

DQ50

177

M_A_DQ5 4

DQ51

164

M_A_DQ5 1

DQ52

166

M_A_DQ4 9

DQ53

174

M_A_DQ4 8

DQ54

176

M_A_DQ5 0

6

DQ55

181

M_A_DQ5 8

DQ56

183

M_A_DQ6 1

DQ57

191

M_A_DQ6 3

DQ58

193

M_A_DQ5 7

DQ59

180

M_A_DQ6 0

DQ60

182

M_A_DQ5 6

DQ61

192

M_A_DQ6 2

DQ62

194

M_A_DQ5 9

7

DQ63

30

DDR3_D RAMRST#SMB_CLK _S

RESET#

R1601

150Ohm

150Ohm

D D

C C

B B

A A

C1621

10PF/50 V

@

M_A_DIM0 _CLK_D DR#0

@

M_A_DIM0 _CLK_D DR1

12

12

R1602

C1622

10PF/50 V

@

M_A_DIM0 _CLK_D DR#1

@

150Ohm

150Ohm

M_A_DQS [7:0]5

M_A_DQS #[7:0]5

12

R1604

@

12

R1603

@

M_A_DIM0 _CLK_D DR2

12

C1624

10PF/50 V

M_A_DIM0 _CLK_D DR#2

@

M_A_DIM0 _CLK_D DR3

12

C1623

10PF/50 V

M_A_DIM0 _CLK_D DR#3

@

SMBus Slave Address: A2H

M_A_DQS 0

M_A_DQS 1

M_A_DQS 3

M_A_DQS 4

M_A_DQS 5

M_A_DQS 6

M_A_DQS 7

M_A_DQS #0

M_A_DQS #1

M_A_DQS #2

M_A_DQS #3

M_A_DQS #4

M_A_DQS #5

M_A_DQS #6

M_A_DQS #7

M_A_DIM0 _CLK_D DR15

M_A_DIM0 _CLK_D DR#15

M_A_DIM0 _CLK_D DR05

M_A_DIM0 _CLK_D DR#05

M_A_DIM0 _CS#15

M_A_DIM0 _CS#05

M_A_DIM0 _ODT15

M_A_DIM0 _ODT05

M_A_DIM0 _CKE15

M_A_DIM0 _CKE05

SMBus Slave Address: A0H

DM should connect to GND directly

Design Guide 0.9 p86 (436735)

SMB_CLK _S1 7,28,48,5 3,55

SMB_DAT _S17 ,28,48,53 ,55

M_A_DIM0 _CLK_D DR35

M_A_DIM0 _CLK_D DR#35

M_A_DIM0 _CLK_D DR25

M_A_DIM0 _CLK_D DR#25

M_A_DIM0 _CS#35

M_A_DIM0 _CS#25

M_A_DIM0 _ODT35

M_A_DIM0 _ODT25

M_A_DIM0 _CKE35

M_A_DIM0 _CKE25

DM should connect to GND directly

Design Guide 0.9 p86 (436735)

M_A_A[15 :0]5

M_A_WE #5

M_A_RAS #5

M_A_CAS #5

M_A_BS25

M_A_BS15

M_A_BS05

SMB_DAT _S

+3VS

M_A_DIM0 _CLK_D DR0

12

12

ok

ok

ok

ok

ok

ok

ok

ok

4

M_A_DQ[6 3:0] 5

DDR3_D RAMRST# 5,17

JP1601

112

3MM_OPEN_5 MIL

JP1602

2

112

2MM_OPEN_5 MIL

+1.35V_D DR3

12

C1601

0.1UF/10V

Layout Note: Place th ese caps near SO DIM M 0

1

PM_EXTT S#0_DI M_A

T1601

Reserve

+V_VREF _CA_D IMM0

12

C1609

2.2UF/6.3V

@

+V_VREF _DQ_D IMM0

12

C1607

2.2UF/6.3V

@

+1.35V_D DR3

12

12

C1616

C1612

0.1UF/10V

0.1UF/10V

/DGPU

T1602

Reserve

+V_VREF _CA_D IMM0

+V_VREF _DQ_D IMM0

1

PM_EXTT S#0_DI M_A

12

C1619

2.2UF/6.3V

@

12

C1611

2.2UF/6.3V

@

/DGPU

12

C1618

0.1UF/10V

/DGPU

12

C1613

0.1UF/10V

/DGPU

Layout Note: Place th ese caps near SO DIM M 0

+1.35V_D DR3+1.35V

2

12

C1602

0.1UF/10V

12

C1608

0.1UF/10V

12

C1610

0.1UF/10V

R1.2 2012/11/20

Part ref. changed

75

99

105

111

117

123

13

19

25

31

37

43

48

54

60

65

71

127

133

138

144

150

155

161

167

172

178

184

189

195

198

125

77

122

126

+1.35V

+0.675VS

+3VS

+1.35V_D DR3

R1.2 2012/11/20

Part ref. changed

CON1601 B

75

VDD1

VDD381VDD4

VDD587VDD6

VDD793VDD8

99

VDD9

105

VDD11

111

VDD13

117

VDD15

123

VDD17

2

VSS1

8

VSS3

13

VSS5

19

VSS7

25

VSS9

31

VSS11

37

VSS13

43

VSS15

48

VSS17

54

VSS19

60

VSS21

65

VSS23

71

VSS25

127

VSS27

133

VSS29

138

VSS31

144

VSS33

150

VSS35

155

VSS37

161

VSS39

167

VSS41

172

VSS43

178

VSS45

184

VSS47

189

VSS49

195

VSS51

198

EVENT#

125

TEST

77

NC1

122

NC2

126

VREFCA

1

VREFDQ

CON1602 B

DDR3_D IMM_204P

12V02G IRM001

VDD1

VDD2

VDD381VDD4

VDD587VDD6

VDD793VDD8

VDD10

VDD9

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

2

VSS2

VSS1

8

VSS4

VSS3

VSS6

VSS5

VSS8

VSS7

VSS9

VSS10

VSS12

VSS11

VSS14

VSS13

VSS16

VSS15

VSS18

VSS17

VSS20

VSS19

VSS22

VSS21

VSS24

VSS23

VSS26

VSS25

VSS28

VSS27

VSS30

VSS29

VSS32

VSS31

VSS34

VSS33

VSS36

VSS35

VSS38

VSS37

VSS40

VSS39

VSS42

VSS41

VSS44

VSS43

VSS46

VSS45

VSS48

VSS47

VSS50

VSS49

VSS52

VSS51

GND1

EVENT#

GND2

TEST

NP_NC1

NC1

NP_NC2

NC2

VTT1

VTT2

VREFCA

1

VDDSPD

VREFDQ

DDR3_D IMM_204P

12V02G BRM001

/DGPU

3

+1.35V 5,6,18 ,63,83

+0.675VS 17 ,63,83

+3VS 17,20,21 ,22,23,25 ,26,27,2 8,30,33,3 7,38,39,4 0,41,43 ,47,48,49 ,53,55,6 0,63,65,6 6,91,92

+1.35V_D DR3 1 7

C1606

0.1UF/10V

12

/DGPU

+0.675VS

C1617

0.1UF/10V

12

+3VS

C1603

0.1UF/10V

/DGPU

12

C1615

2.2UF/6.3V

@

+3VS

12

+1.35V_D DR3

12

C1614

0.1UF/10V

12

C1605

2.2UF/6.3V

@

+1.35V_D DR3

C1604

0.1UF/10V

Reference schematic have 2.2 uf cap.

VDD10

VDD12

VDD14

VDD16

VDD18

VSS10

VSS12

VSS14

VSS16

VSS18

VSS20

VSS22

VSS24

VSS26

VSS28

VSS30

VSS32

VSS34

VSS36

VSS38

VSS40

VSS42

VSS44

VSS46

VSS48

VSS50

VSS52

NP_NC1

NP_NC2

VDDSPD

76

VDD2

82

88

94

100

106

112

118

124

3

VSS2

9

VSS4

14

VSS6

20

VSS8

26

32

38

44

49

55

61

66

72

128

134

139

145

151

156

162

168

173

179

185

190

196

207

GND1

208

GND2

205

206

203

VTT1

204

VTT2

199

12

76

82

88

94

100

106

112

118

124

3

9

14

20

26

32

38

44

49

55

61

66

72

128

134

139

145

151

156

162

168

173

179

185

190

196

207

208

205

206

203

+0.675VS

204

199

12

C1620

0.1UF/10V

/DGPU

+1.35V_D DR3

12

+

1BV090 000003

@

CE1603

220UF/6.3 V

2

+1.35V_D DR3

Layout Note: Place th ese caps near SO DIM M 0

12

12

C1626

10UF/10V

C1625

10UF/10V

12

C1628

10UF/10V

Layout Note: Place th ese caps near SO DIM M 0

12

12

C1636

10UF/10V

/DGPU

12

C1635

C1638

10UF/10V

10UF/10V

/DGPU

/DGPU

1

+0.675VS

12

C1633

10UF/10V

@

12

C1643

10UF/10V

@

C1627

C1631

10UF/10V

10UF/10V

@

@

12

12

C1637

C1641

10UF/10V

10UF/10V

@

@

12

12

12

12

C1632

1UF/6.3V

+0.675VS+1.35V_D DR3

12

12

C1639

C1642

1UF/6.3V

1UF/6.3V

/DGPU

/DGPU

C1629

1UF/6.3V

12

12

C1634

C1630

1UF/6.3V

1UF/6.3V

@

@

12

12

C1640

C1644

1UF/6.3V

1UF/6.3V

@

@

Title :

Title :

Title :

DDR3(1)_SO-DIMM0

DDR3(1)_SO-DIMM0

DDR3(1)_SO-DIMM0

Engineer:

Wing_Cheng

Engineer:

Wing_Cheng

Engineer:

BG1-CSC -HW R&D D ept.5

BG1-CSC -HW R&D D ept.5

BG1-CSC -HW R&D D ept.5

Size P roject Name

Size P roject Name

Size P roject Name

D

D

D

VA70_HW

VA70_HW

VA70_HW

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

1

Wing_Cheng

16 96Friday, January 18, 20 13

16 96Friday, January 18, 20 13

16 96Friday, January 18, 20 13

Rev

Rev

Rev

1.0

1.0

1.0

Page 11

5

H:4MM

CON1701 A

98

M_B_A0

97

M_B_WE #5

M_B_RAS #5

M_B_CAS #5

M_B_BS25

M_B_BS15

M_B_BS05

M_B_WE #

M_B_RAS #

M_B_CAS #

M_B_BS2