Page 1

5

smd.db-x7.ru

4

3

2

1

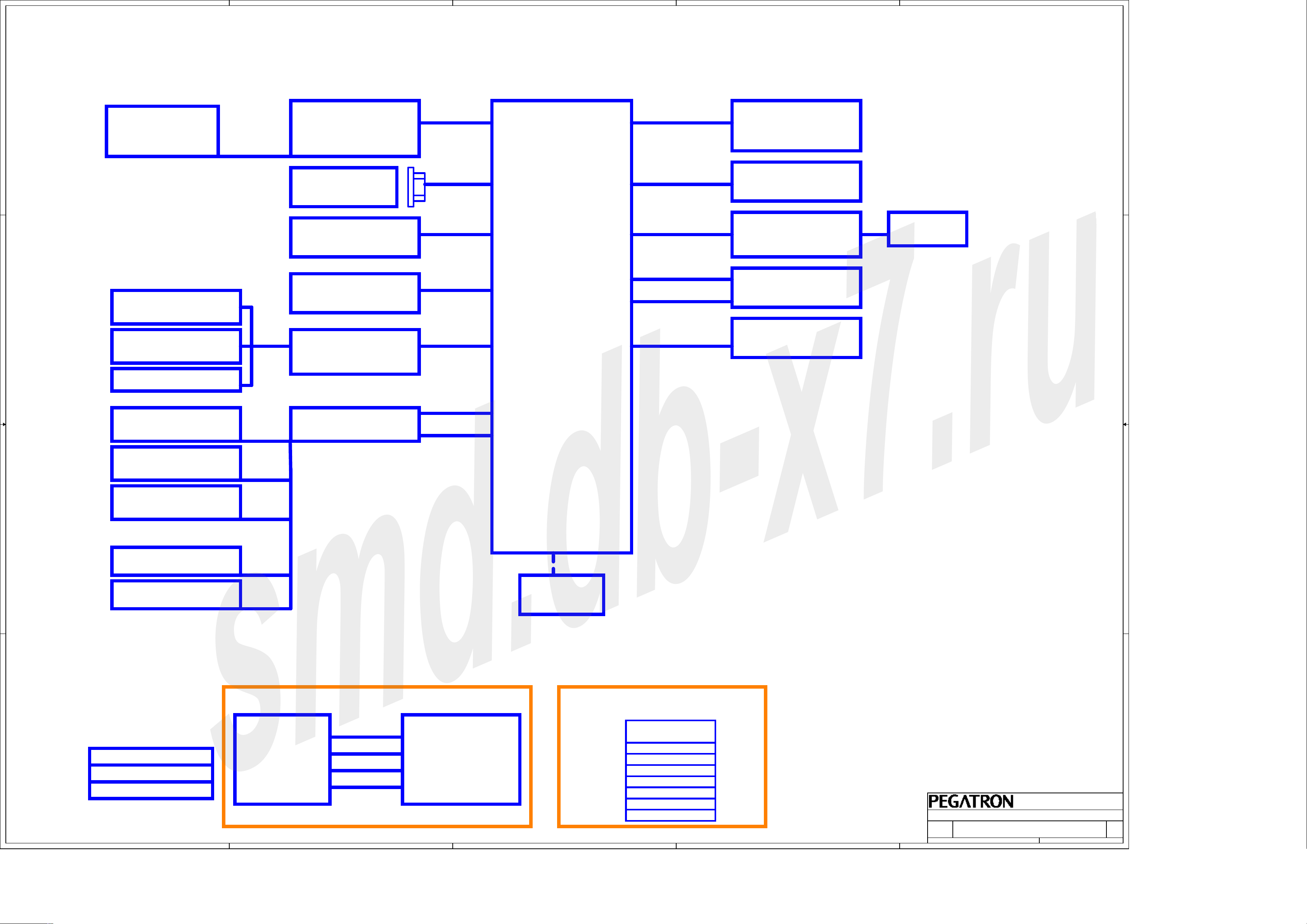

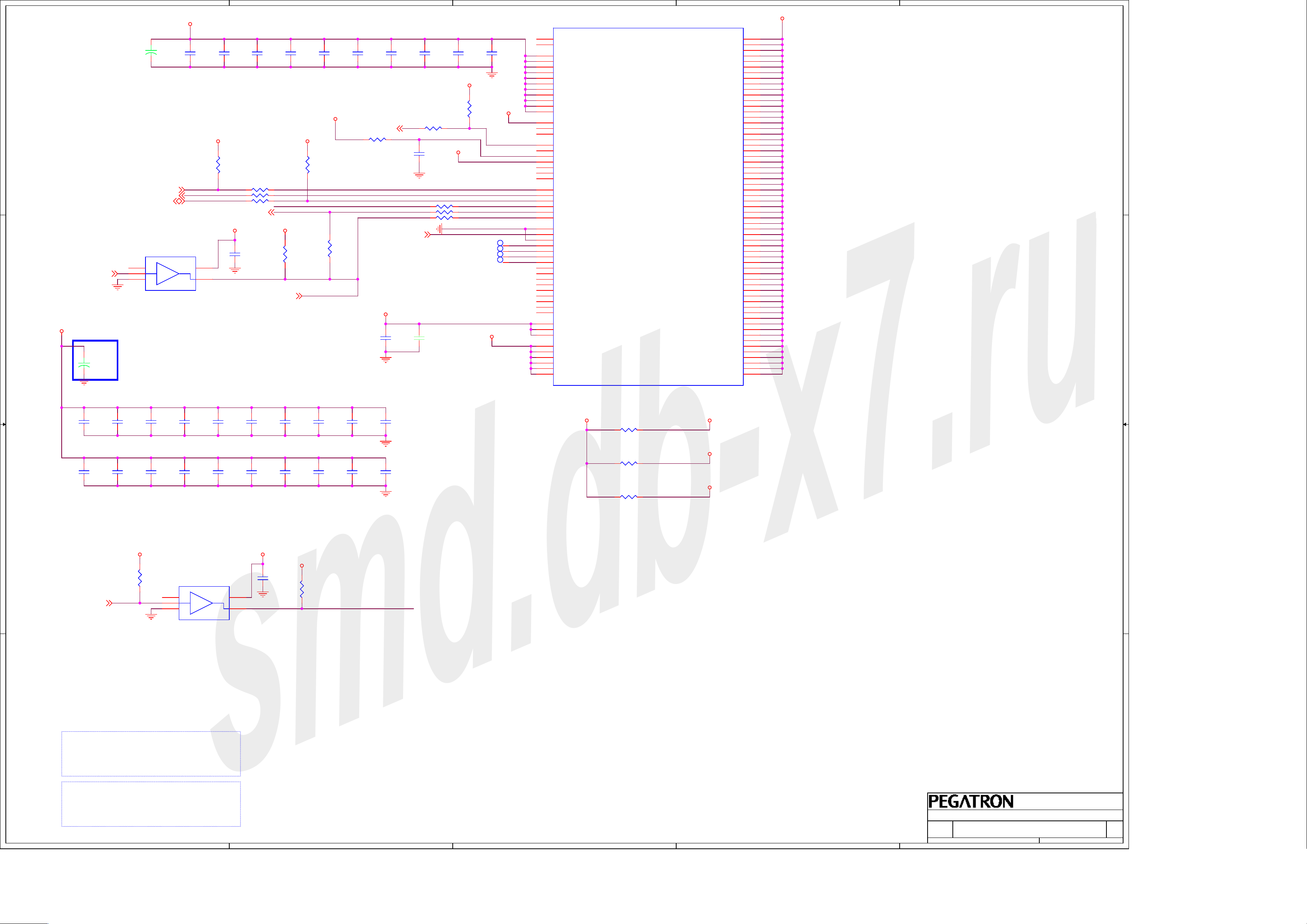

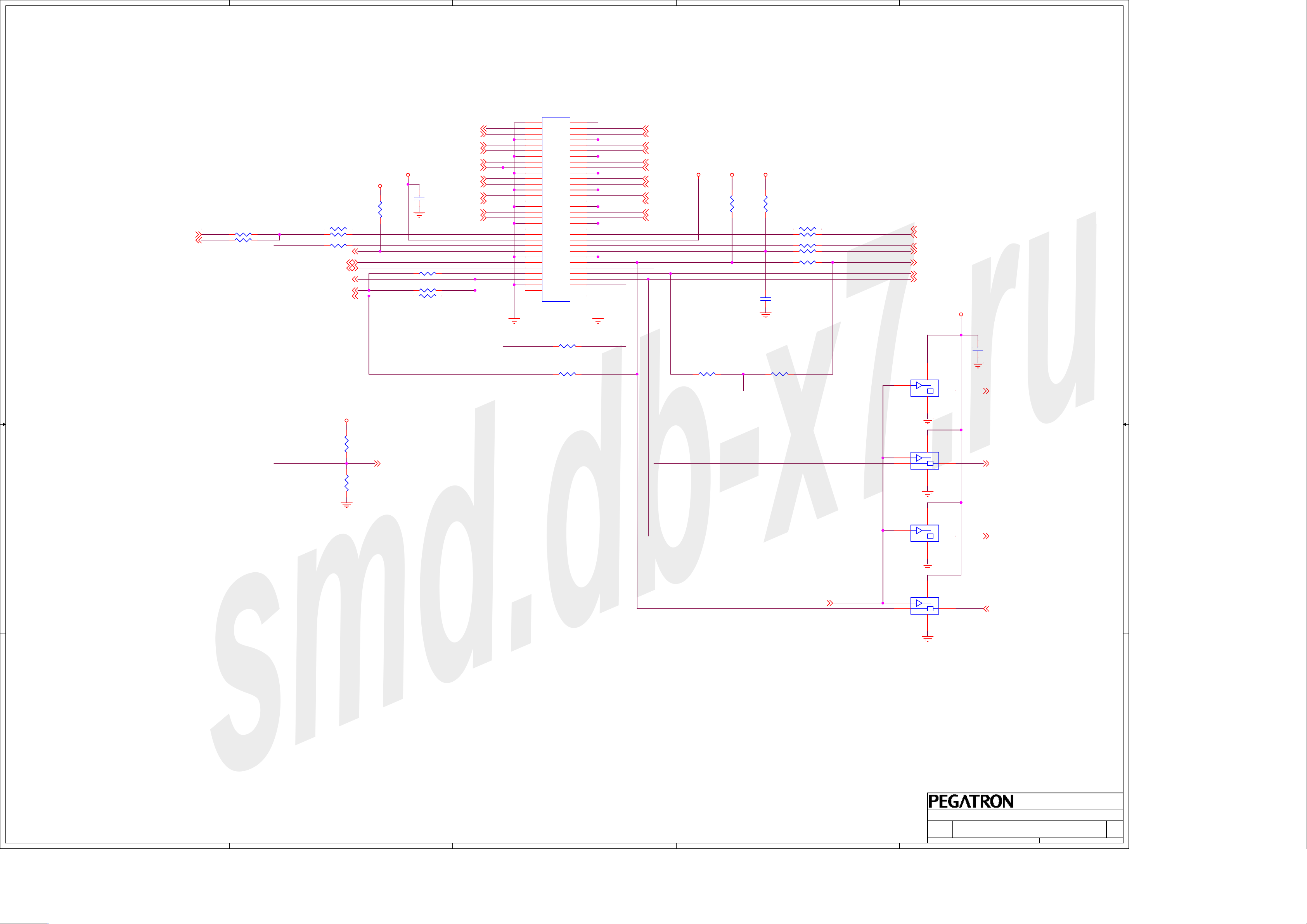

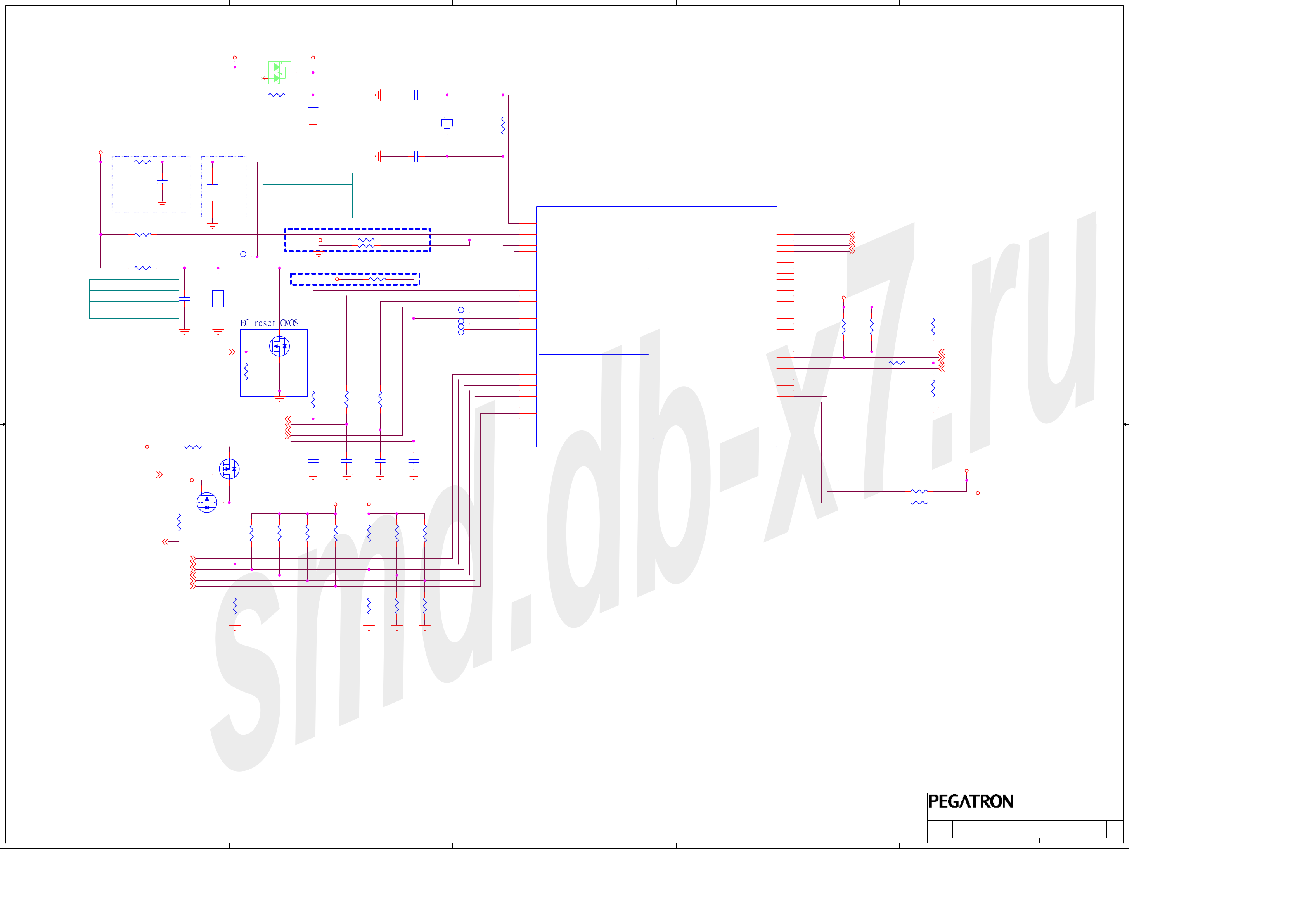

Longchamp_Block Diagram

D D

LED Driver

6 Channel

Ti TPS61185RGE

+VSYS +3VS

Panel

eDPx4 (11.6'') FHD

11.6'' FHD

eDP

DDR3L

Intel

Touch screen

Synaptics 7508

+5VS

I2C

SATA

Haswell Y

HDMI

u-HDMI CONN

+5VS

HD

Speaker

C C

R/L 1Wx2

DMIC x1

+1.8VS

I2C

+3VS

Audio Codec

Realtek ALC283

+5VS +3VS +1.5VS

DDI

TDP 7.5W

USB2.0Camera

HD

SDP 6W

SDP 4.5W

USB2.0

PCIE

USB2.0

USB 3.0

LPDDR3

1333 / 1600 MHz

2Ch 4GB

+1.2V +1.8V +0.6VS

SSD

M2 2280

+3VS

SD3.0 CardReader

Realtek RTS5170

+3VS

WiFi + BT

M2 2230 Card

+3VS

USB 3.0

USB CONNx1

+5VO

uSD CONN

+3VS

Universal Jack

I2C

G+Gryo Sensor

Invensence

PMU6500

E-Compass

AKM AK9911

ALS

Capella CM32181

B B

Charger IC

Ti BQ24725ARGRR

Gauge IC

Ti BQ27520

I2C

I2C

I2C

I2C

I2C

EC+Sensor Hub

ITE IT8380

LPC

SPI ROM

16 MB

+3VSUS

Audio_DBDocking Cable

DET 0/1

A A

USB 2.0

AC Adapter 45W

Battery 3S1P 35W

O.S Win8.1

5

WTB CONN

KBD_EN

Power

4

POGO CONN

9 Pins9 Pins

3

Battery LED

Dual Color

Battery Jack

Hall Sensor

Universal Jack

Power Bottom

Volume Up

Volume Down

Home Key

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Longchamp

Longchamp

Longchamp

Engineer:

1

Block Diagram

Block Diagram

Block Diagram

Kang_Kang

Kang_Kang

Kang_Kang

198Tuesday, April 15, 2014

198Tuesday, April 15, 2014

198Tuesday, April 15, 2014

Rev

Rev

Rev

1.0

1.0

1.0

Page 2

5

smd.db-x7.ru

4

3

2

1

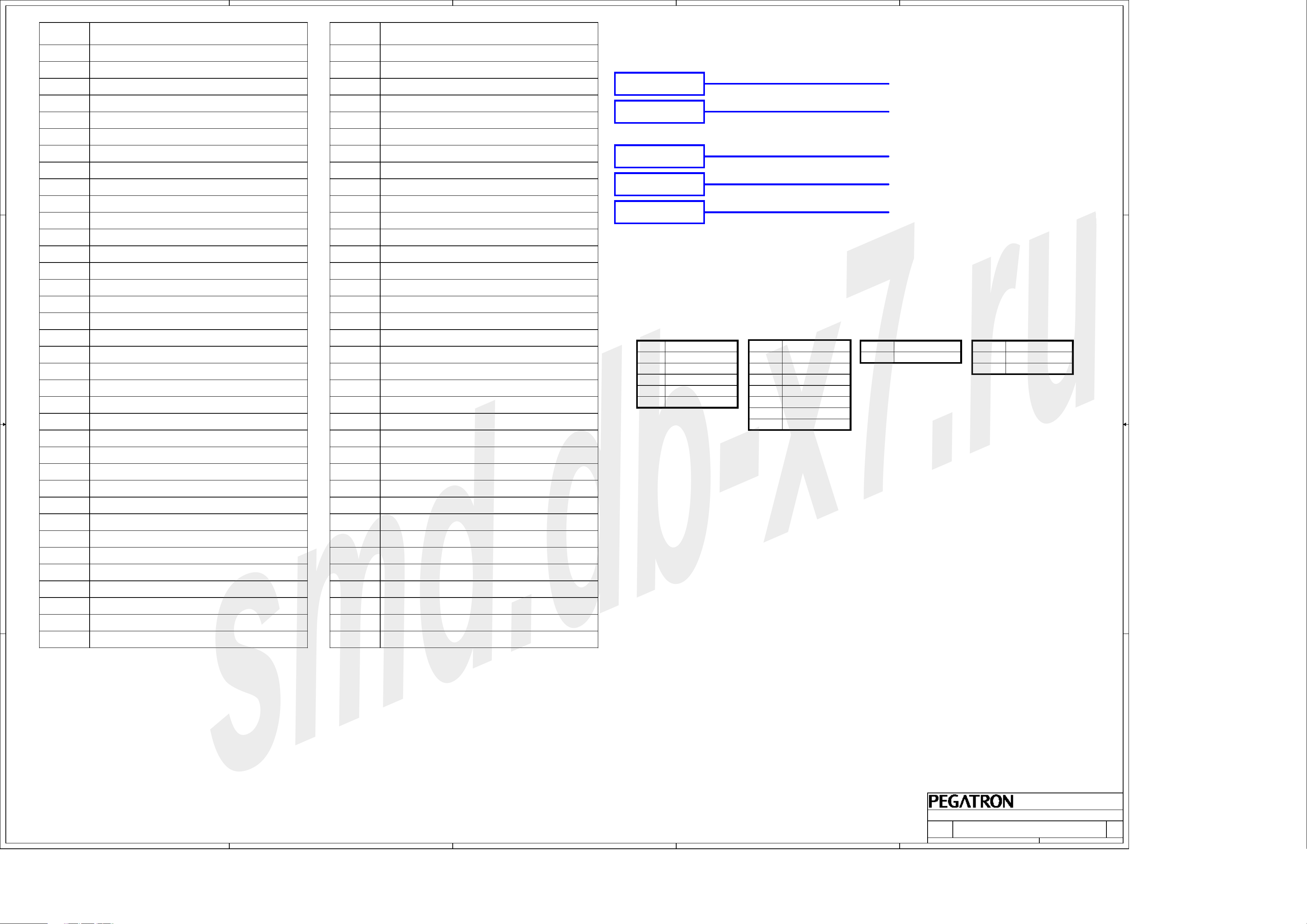

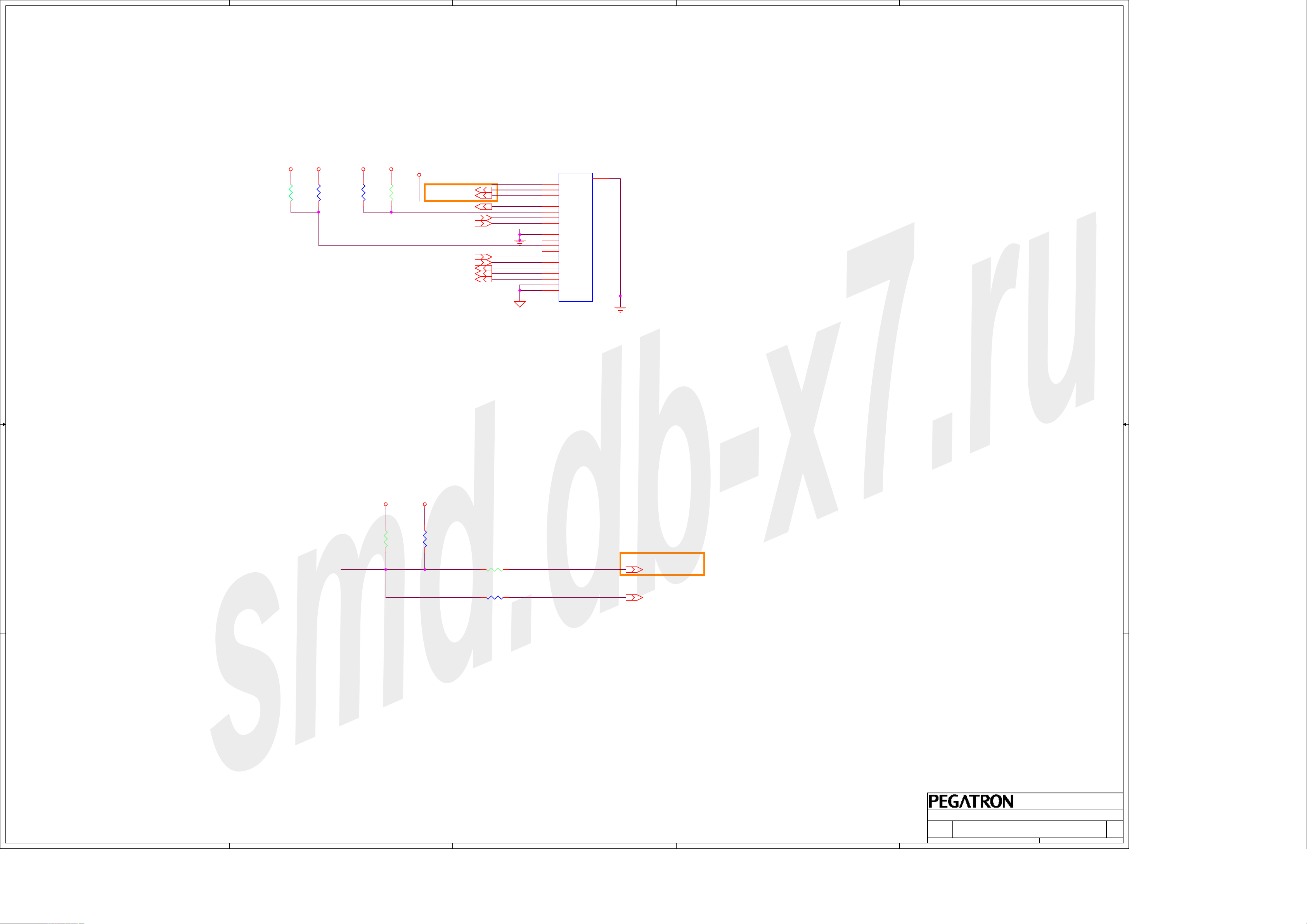

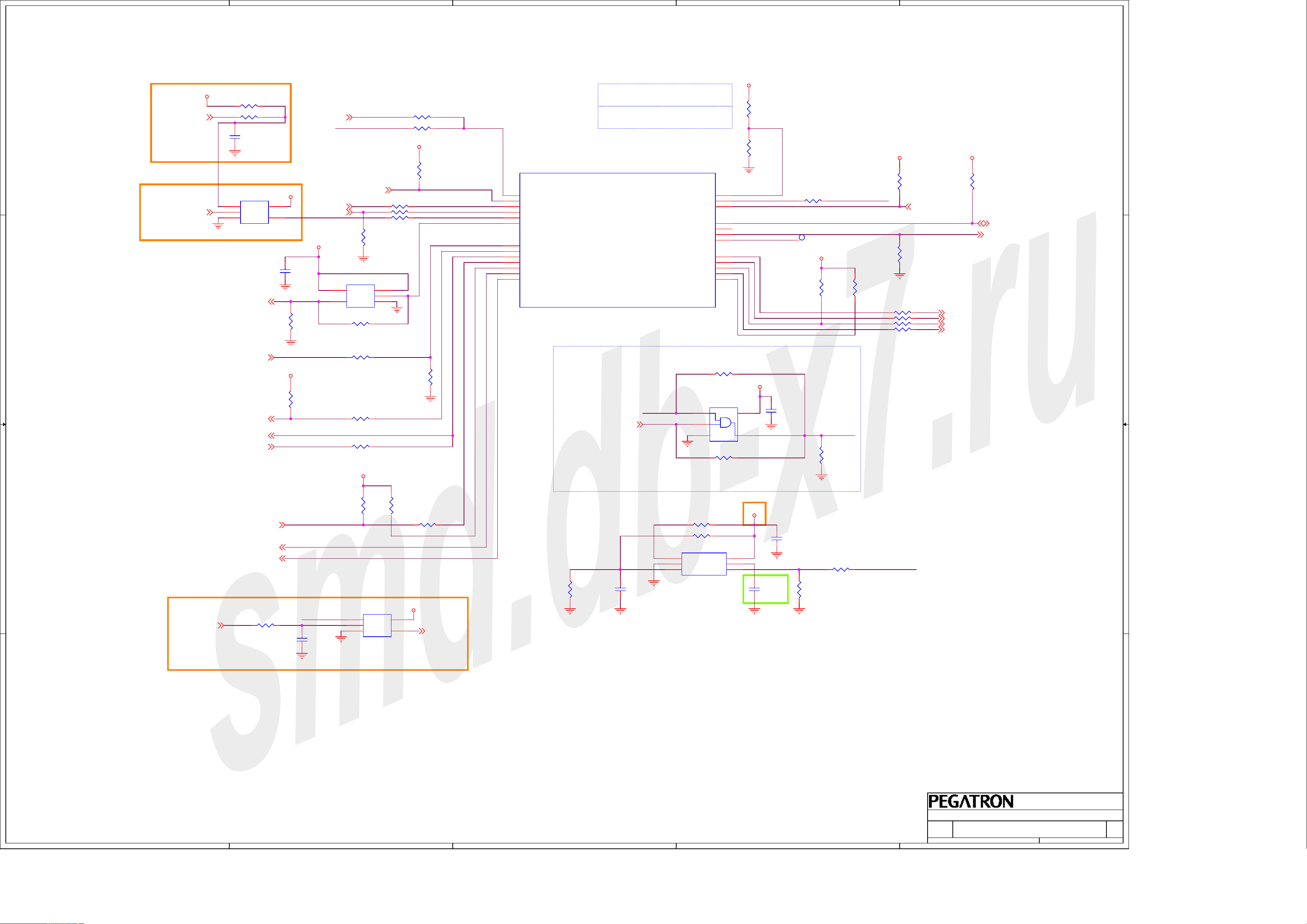

PAGE TITLE

01

02

03

04

D D

05

06

07

08

09

10

14

15

16

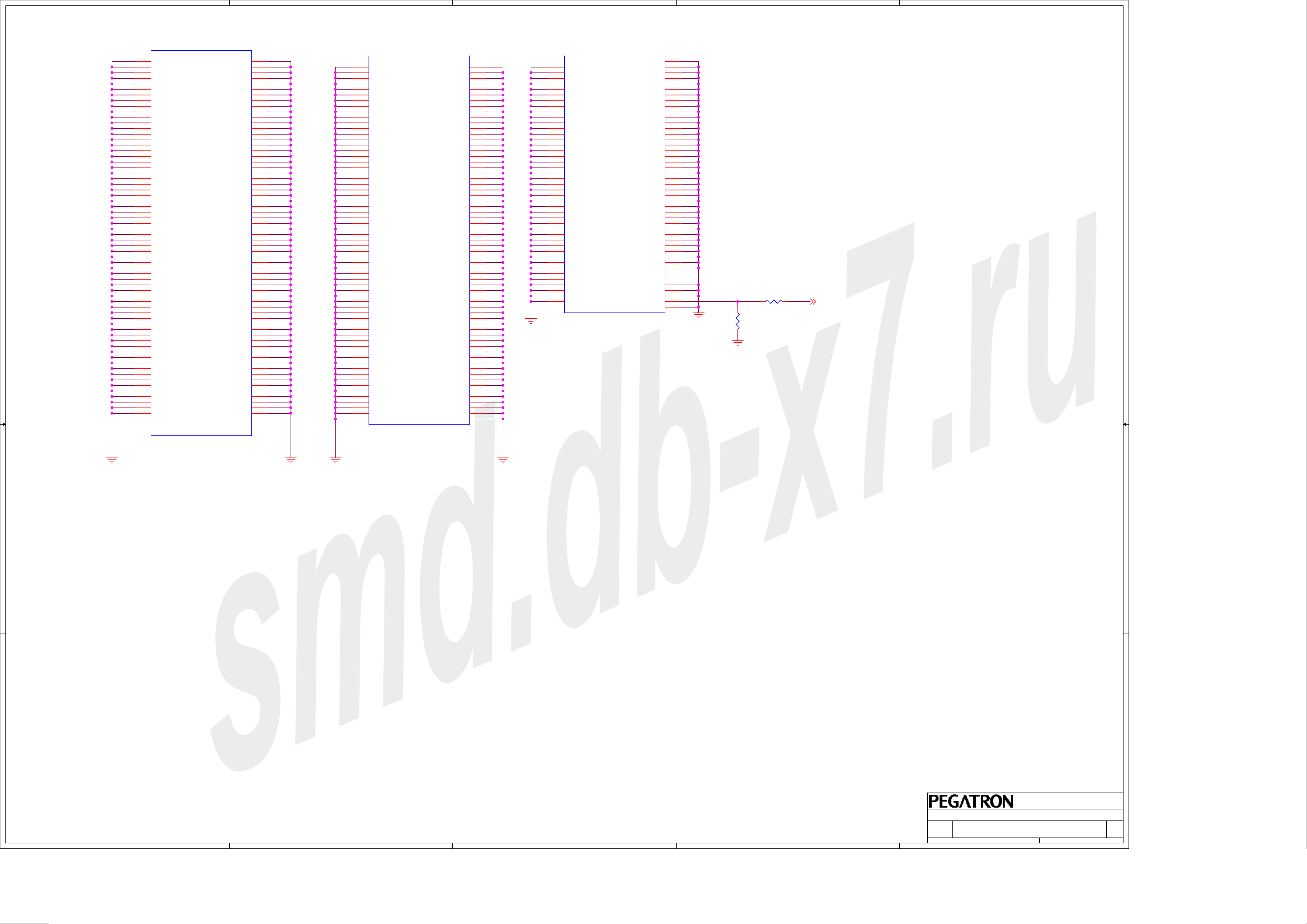

BLOCK DIAGRAM

REF PAGE

CPU(1)_DMI,DP,PEG,FDI***

CPU(2)_MISC,JTAG,DDI.EDP

CPU(3)_DDR3-rs

CPU(4)_HSW POWER

CPU(5)_****

CPU(6)_GND

CPU(7)_RESERVED

CPU_PCH_XDP

DDR3L-rs(1)_MEMORY DOWN

DDR3L-rs(2)_MEMORY DOWN

DDR3L-rs(3)_MEMORY DOWN

52

53

54

55

56

57

58

59

60

62

63

65

66

Micro USB charging detect

NGFF_WLAN

NGFF_WWAN

NGFF_SSD

Volume Switch

Discharge

SENSOR HUB / SENSOR x3

PROXIMITY SENSOR

DC_DC/BAT CONN

TPM

USB3.0 connector

ME_CONN,Skew Hole

VIBRATOR CONTROLLER

TITLEPAGE

I2C/SMBUS Block Diagram

I2C Port 0 DSP / eDP / Sensor Hub

I2C Port 1 VIBRATOR / Touch Panel / DOCK

SMBUS SPD / WWAN / CPU XDP / PCH XDP

SMBUS Port 0 NFC

SMBUS Port 1 EC

17

18

19

C C

20

21

22

23

24

25

26

27

28

30

31

DDR3L-rs(4)_MEMORY DOWN

DDR3L-rs(5)_CA/DQ Voltage

VID Controller_****

PCH(1)_SATA,IHDA,RTC

PCH(2)_CLK,SMB,LPC

PCH(3)_FDI,DMI,SYS PWR

PCH(4)_DP,PCI,CRT

PCH(5)_PCIE,NVRAM,USB

PCH(6)_CPU,GPIO,MISC

PCH(7)_POWER,GND

PCH(8)_***

PCH(9)_SPI,SMB

EC_MEC1641

EC_MSP430

67

68

69

80

81

82

83

84

87

88

89

90

91

92

NFC

DB CONN

HDMI Repeater

POWER_VCORE

POWER_SYSTEM

POWER_ +1.05VSUS

POWER_ DDR & VTT

POWER_1.5V & 1.8VS

POWER_+12VUSB

POWER_ CHARGER

POWER_LED_DRIVER

POWER_DETECT

POWER_LOAD SWITCH

POWER_PROTECT

PCIE 1

PCIE 2

PCIE 3

PCIE 4

PCIE 5

PCIE 6

NGFF (WLAN)

Card Reader

USB2.0 0

USB2.0 1

USB2.0 2

USB2.0 3

USB2.0 4

USB2.0 5

USB2.0 6

USB2.0 7

I/O Port Mapping

DOCK

USB3.0 (Debug Use)

CAMERA_2M

POGO

CAMERA_8M

WWAN

WLAN

USB HUB

USB3.0 0

USB3.0 1

DOCK

USB3.0 SATA 1

SATA 0

SATA 2

SSD

32

36

B B

37

38

39

44

45

46

50

RST_Reset Circuit

AUD(1)_DSP ALC5505

AUD(2)_ALC3223

AUD(3)_PWR / JACK

AUD(4)_Docking Headphone

BUG_Debug

eDP Connector

CAMERA / LED Flash Driver

THERMAL / FAN

93

95

96

97

98

POWER_SIGNAL

POWER_HISTORY

Power On Sequence

I2C/SMBus/Thermal sense MAP

POWER TREE_DDR3L-RS

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Junction

Junction

Junction

Engineer:

1

REF PAGE

REF PAGE

REF PAGE

Chinhung_Wang

Chinhung_Wang

Chinhung_Wang

298Tuesday, April 15, 2014

298Tuesday, April 15, 2014

298Tuesday, April 15, 2014

Rev

Rev

Rev

2.2

2.2

2.2

Page 3

5

smd.db-x7.ru

D D

4

3

2

1

C C

B B

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

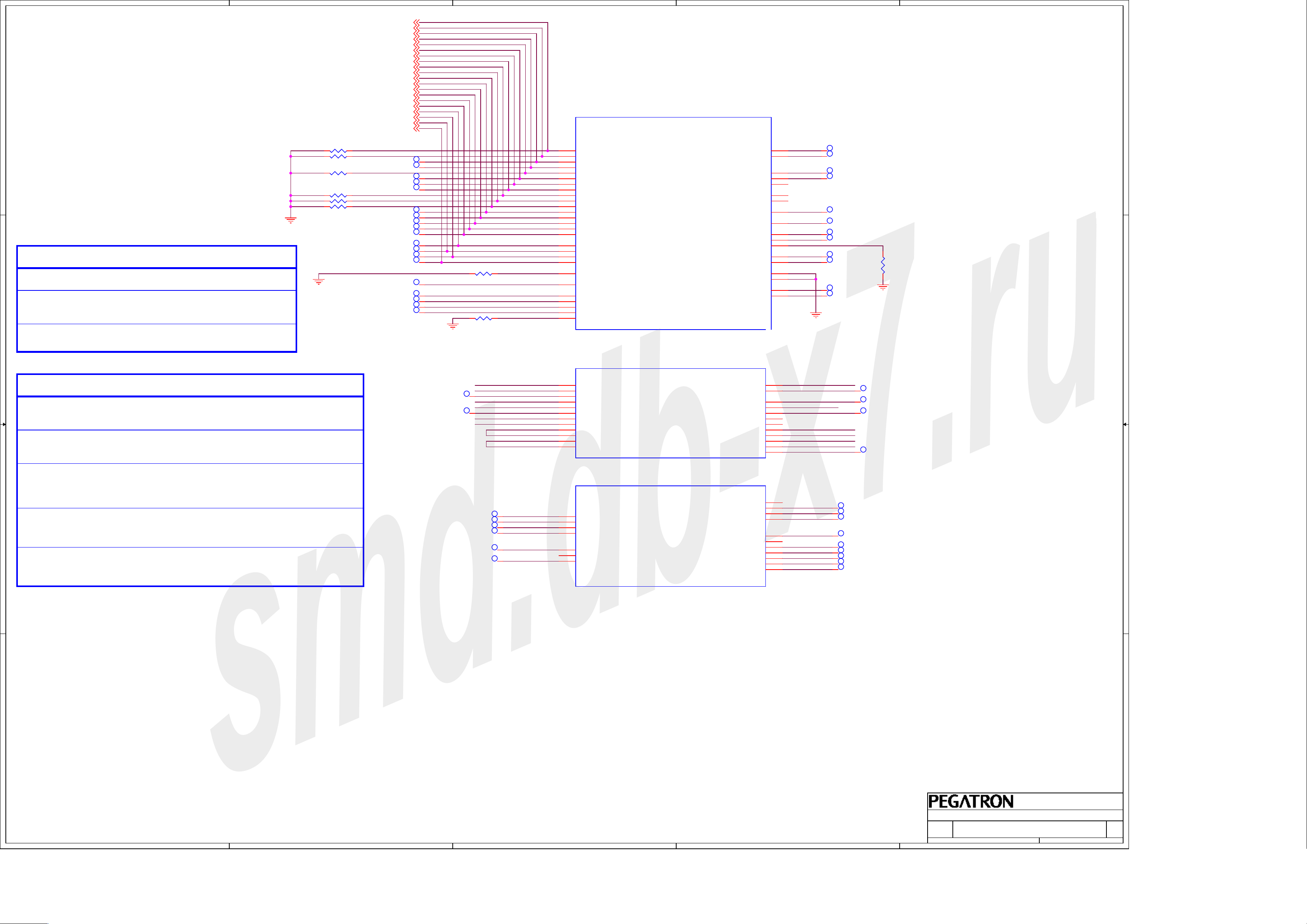

CPU(1)_DMI,DP,PEG,FDI

CPU(1)_DMI,DP,PEG,FDI

CPU(1)_DMI,DP,PEG,FDI

Chinhung_Wang

Chinhung_Wang

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Junction

Junction

Junction

Engineer:

1

Chinhung_Wang

Rev

Rev

Rev

2.2

2.2

2.2

398Tuesday, April 15, 2014

398Tuesday, April 15, 2014

398Tuesday, April 15, 2014

Page 4

5

smd.db-x7.ru

4

3

2

1

04

D D

DDI1_TX0_DN41

DDI1_TX0_DP41

DDI1_TX1_DN41

DDI1_TX1_DP41

DDI1_TX2_DN41

DDI1_TX2_DP41

DDI1_TX3_DN41

DDI1_TX3_DP41

C C

CPU(1)_MISC,JTAG,DDI,EDP

HASWELL_MCP_E

DDI EDP

EDP_TXN0

EDP_TXP0

EDP_TXN1

EDP_TXP1

EDP_TXN2

EDP_TXP2

EDP_TXN3

EDP_TXP3

EDP_AUXN

EDP_AUXP

EDP_RCOMP

EDP_DISP_UTIL

C45

B46

A47

B47

C47

C46

A49

B49

A45

B45

D20

A43

C54

C55

B58

C58

B55

A55

A57

B57

C51

C50

C53

B54

C49

B50

A53

B53

U0301A

DDI1_TXN0

DDI1_TXP0

DDI1_TXN1

DDI1_TXP1

DDI1_TXN2

DDI1_TXP2

DDI1_TXN3

DDI1_TXP3

DDI2_TXN0

DDI2_TXP0

DDI2_TXN1

DDI2_TXP1

DDI2_TXN2

DDI2_TXP2

DDI2_TXN3

DDI2_TXP3

haswell_mcp

EDP_TXN0 45

EDP_TXP0 45

EDP_TXN1 45

EDP_TXP1 45

EDP_TXN2 45

EDP_TXP2 45

EDP_TXN3 45

EDP_TXP3 45

EDP_AUXN 45

EDP_AUXP 45

DP_COMP

EDP_DISP_UTIL_S

eDP x 4DDI Port 1: u_HDMI

GND

+VCCIOA_OUT

12

R0407

24.9Ohm

1%

U0402

1

NC

2

A

3 4

GND

74AUP1G07GW

@

VCC

Y

+1.05VS

12

C0402

0.1UF/6.3V

5

GND

@

12

R0417

2MOHM

@

GND

EDP_DISP_UTIL 45

+1.05VS_VCCST

12

R0410

62Ohm

B B

1 2

VR_HOT#80

THRO_CPU30

A A

R0411 0Ohm

1

1

G

3

2

GND

32

H_PROCHOT#

D

S

Q0401

2N7002

12

12

R0412

200Ohm

1%

GND GND GND

C0403

47PF/50V

1AT200000015

12

R0413

121OHM

1%

+V_VDDQ_VTT

12

R0414

100Ohm

1%

GND

5

+VCCIO_OUT

12

R0420

49.9Ohm

1%

@

T0402

T0401

1

H_PECI30

1 2

R0423 1MOhm

4

U0301B

1

PROC_DETECT#

TP_CATERR#_R

12

12

H_PROCHOT#_D

R040956Ohm

H_CPUPWRGD_R

R040810KOhm

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

1%

D61

K61

N62

K63

C61

AU60

AV60

AU61

AV15

AV61

DDR_PG_CTRL_S

12

R0422

10KOhm

@

GND

PROC_DETECT#

CATERR#

PECI

PROCHOT#

PROCPWRGD

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

SM_DRAMRST#

SM_PG_CNTL1

haswell_mcp

GND

1

2

3 4

HASWELL_MCP_E

MISC

THERMAL

PWR

DDR3

U0401

NC

A

GND

74AUP1G07GW

VCC

R1.0 PU/PD for JTAG signals

J62

PRDY#

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

K62

E60

E61

E59

F63

F62

J60

H60

H61

H62

K59

H63

K60

J61

XDP_TCK

XDP_TRST#

XDP_TDO

XDP_BPM0

XDP_BPM1

XDP_BPM2

XDP_BPM3

XDP_BPM4

XDP_BPM5

XDP_BPM6

XDP_BPM7

12

R0416

220KOhm

1%

@

12

R0415

2MOHM

@

GND

+3VS+3VSUS

1

1

1

1

1

1

12

R0419

220KOhm

1%

T0403

T0404

T0405

T0406

T0407

T0408

PREQ#

PROC_TCK

JTAG

5

Y

3

PROC_TMS

PROC_TRST#

PROC_TDI

PROC_TDO

+DDR_V

12

C0401

0.1UF/6.3V

GND

XDP_PRDY# 10

XDP_PREQ# 10

XDP_TCK 10

XDP_TMS 10

XDP_TRST# 10,20

XDP_TDI 10

XDP_TDO 10

XDP_BPM0 10

XDP_BPM1 10

DDR_PG_CTRL 83

2

R1d

R9

R2

+1.05VS_VCCST

XDP_TDO

XDP_TRST#

XDP_TCK

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

1 2

R0403 51Ohm

1 2

R0406 51Ohm

R0405 51Ohm

@

1 2

P1HBC

P1HBC

P1HBC

GND

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

CPU(1)_MISC,JTAG,DDI,EDP

CPU(1)_MISC,JTAG,DDI,EDP

CPU(1)_MISC,JTAG,DDI,EDP

Kang_Kang

Kang_Kang

Kang_Kang

498Tuesday, April 15, 2014

498Tuesday, April 15, 2014

498Tuesday, April 15, 2014

Rev

Rev

Rev

1.0

1.0

1.0

Page 5

5

smd.db-x7.ru

4

3

2

1

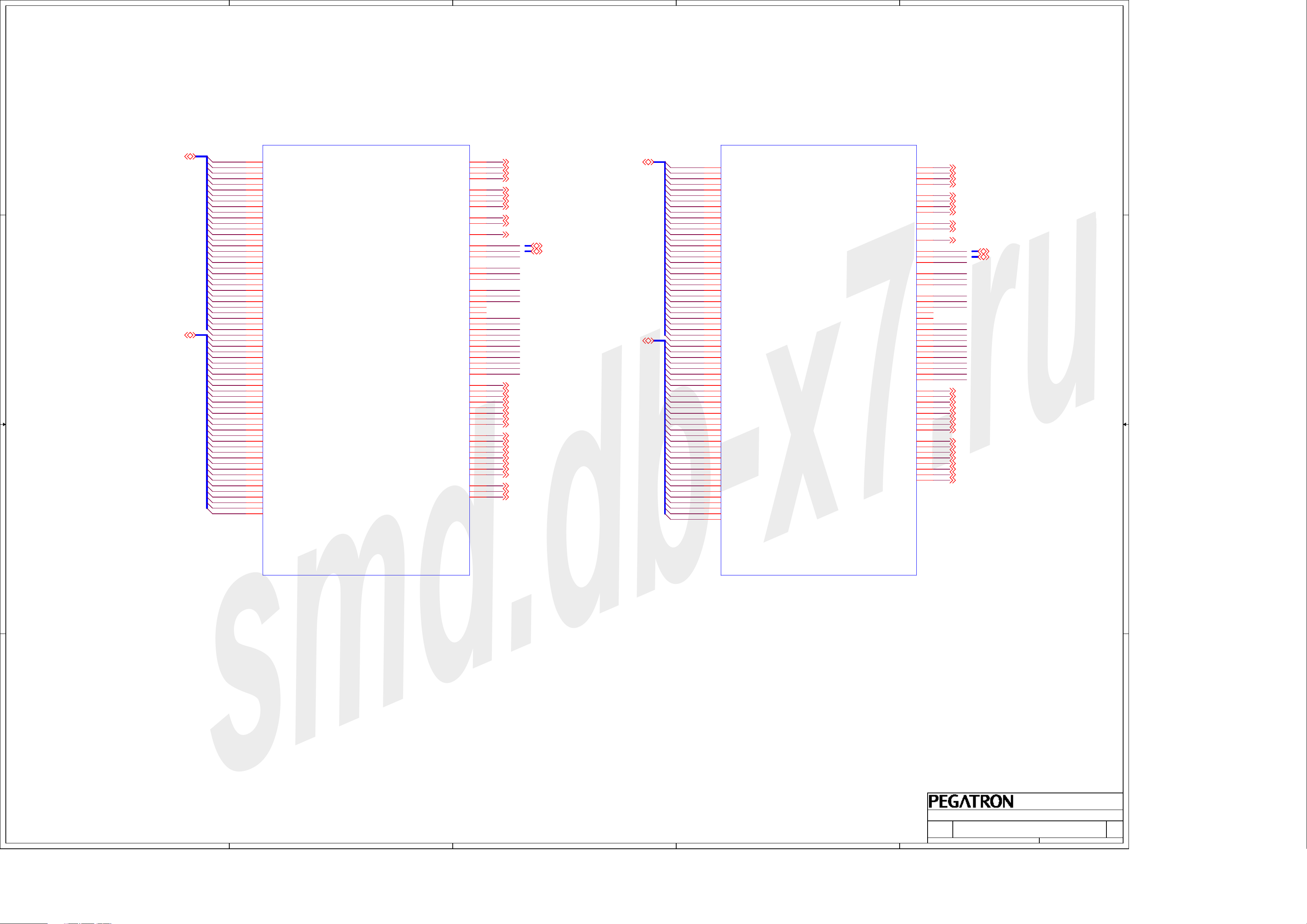

CPU(2)_LPDDR35

D D

U0301C

M_A_D[31:0]16

C C

M_A_D[63:32]16

B B

M_A_D0

M_A_D1

M_A_D2

M_A_D3

M_A_D4

M_A_D5

M_A_D6

M_A_D7

M_A_D8

M_A_D9

M_A_D10

M_A_D11

M_A_D12

M_A_D13

M_A_D14

M_A_D15

M_A_D16

M_A_D17

M_A_D18

M_A_D19

M_A_D20

M_A_D21

M_A_D22

M_A_D23

M_A_D24

M_A_D25

M_A_D26

M_A_D27

M_A_D28

M_A_D29

M_A_D30

M_A_D31

M_A_D32

M_A_D33

M_A_D34

M_A_D35

M_A_D36

M_A_D37

M_A_D38

M_A_D39

M_A_D40

M_A_D41

M_A_D42

M_A_D43

M_A_D44

M_A_D45

M_A_D46

M_A_D47

M_A_D48

M_A_D49

M_A_D50

M_A_D51

M_A_D52

M_A_D53

M_A_D54

M_A_D55

M_A_D56

M_A_D57

M_A_D58

M_A_D59

M_A_D60

M_A_D61

M_A_D62

M_A_D63

AH63

AH62

AK63

AK62

AH61

AH60

AK61

AK60

AM63

AM62

AP63

AP62

AM61

AM60

AP61

AP60

AP58

AR58

AM57

AK57

AL58

AK58

AR57

AN57

AP55

AR55

AM54

AK54

AL55

AK55

AR54

AN54

AY58

AW58

AY56

AW56

AV58

AU58

AV56

AU56

AY54

AW54

AY52

AW52

AV54

AU54

AV52

AU52

AK40

AK42

AM43

AM45

AK45

AK43

AM40

AM42

AM46

AK46

AM49

AK49

AM48

AK48

AM51

AK51

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

HASWELL_MCP_E

DDR CHANNEL A

SA_CLK#0

SA_CLK0

SA_CLK#1

SA_CLK1

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_CS#0

SA_CS#1

SA_ODT0

SA_RAS#

SA_WE#

SA_CAS#

SA_BA0

SA_BA1

SA_BA2

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_DQSN0

SA_DQSN1

SA_DQSN2

SA_DQSN3

SA_DQSN4

SA_DQSN5

SA_DQSN6

SA_DQSN7

SA_DQSP0

SA_DQSP1

SA_DQSP2

SA_DQSP3

SA_DQSP4

SA_DQSP5

SA_DQSP6

SA_DQSP7

SM_VREF_CA

SM_VREF_DQ0

SM_VREF_DQ1

AU37

AV37

AW36

AY36

AU43

AW43

AY42

AY43

AP33

AR32

AP32

AY34

AW34

AU34

AU35

AV35

AY41

AU36

AY37

AR38

AP36

AU39

AR36

AV40

AW39

AY39

AU40

AP35

AW41

AU41

AR35

AV42

AU42

AJ61

AN62

AM58

AM55

AV57

AV53

AL43

AL48

AJ62

AN61

AN58

AN55

AW57

AW53

AL42

AL49

AP49

AR51

AP51

M_A_DIM0_CLK#0 16

M_A_DIM0_CLK0 16

M_A_DIM0_CLK#1 16

M_A_DIM0_CLK1 16

M_A_DIM0_CKE0 16

M_A_DIM0_CKE1 16

M_A_DIM0_CKE2 16

M_A_DIM0_CKE3 16

M_A_DIM0_CS#0 16

M_A_DIM0_CS#1 16

M_A_DIM0_ODT0 16

M_A_CAB3

M_A_CAB2

M_A_CAB1

M_A_CAB4

M_A_CAB6

M_A_CAA5

M_A_CAB9

M_A_CAB8

M_A_CAB5

M_A_CAA0

M_A_CAA2

M_A_CAA4

M_A_CAA3

M_A_CAA1

M_A_CAB7

M_A_CAA7

M_A_CAA6

M_A_CAB0

M_A_CAA9

M_A_CAA8

M_A_DQS#0 16

M_A_DQS#1 16

M_A_DQS#2 16

M_A_DQS#3 16

M_A_DQS#4 16

M_A_DQS#5 16

M_A_DQS#6 16

M_A_DQS#7 16

M_A_DQS0 16

M_A_DQS1 16

M_A_DQS2 16

M_A_DQS3 16

M_A_DQS4 16

M_A_DQS5 16

M_A_DQS6 16

M_A_DQS7 16

DIMM_VREF_CA 18

DIMM0_VREF_DQ 18

DIMM1_VREF_DQ 18

U0301D

M_B_D[31:0]17

M_A_CAA[9:0] 16

M_A_CAB[9:0] 16 M_B_CAA[9:0] 17

M_B_D[63:32]17

M_B_D0

M_B_D1

M_B_D2

M_B_D3

M_B_D4

M_B_D5

M_B_D6

M_B_D7

M_B_D8

M_B_D9

M_B_D10

M_B_D11

M_B_D12

M_B_D13

M_B_D14

M_B_D15

M_B_D16

M_B_D17

M_B_D18

M_B_D19

M_B_D20

M_B_D21

M_B_D22

M_B_D23

M_B_D24

M_B_D25

M_B_D26

M_B_D27

M_B_D28

M_B_D29

M_B_D30

M_B_D31

M_B_D32

M_B_D33

M_B_D34

M_B_D35

M_B_D36

M_B_D37

M_B_D38

M_B_D39

M_B_D40

M_B_D41

M_B_D42

M_B_D43

M_B_D44

M_B_D45

M_B_D46

M_B_D47

M_B_D48

M_B_D49

M_B_D50

M_B_D51

M_B_D52

M_B_D53

M_B_D54

M_B_D55

M_B_D56

M_B_D57

M_B_D58

M_B_D59

M_B_D60

M_B_D61

M_B_D62

M_B_D63

AY31

AW31

AY29

AW29

AV31

AU31

AV29

AU29

AY27

AW27

AY25

AW25

AV27

AU27

AV25

AU25

AM29

AK29

AL28

AK28

AR29

AN29

AR28

AP28

AN26

AR26

AR25

AP25

AK26

AM26

AK25

AL25

AY23

AW23

AY21

AW21

AV23

AU23

AV21

AU21

AY19

AW19

AY17

AW17

AV19

AU19

AV17

AU17

AR21

AR22

AL21

AM22

AN22

AP21

AK21

AK22

AN20

AR20

AK18

AL18

AK20

AM20

AR18

AP18

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

HASWELL_MCP_E

DDR CHANNEL B

SB_CK#0

SB_CK0

SB_CK#1

SB_CK1

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_CS#0

SB_CS#1

SB_ODT0

SB_RAS#

SB_WE#

SB_CAS#

SB_BA0

SB_BA1

SB_BA2

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_DQSN0

SB_DQSN1

SB_DQSN2

SB_DQSN3

SB_DQSN4

SB_DQSN5

SB_DQSN6

SB_DQSN7

SB_DQSP0

SB_DQSP1

SB_DQSP2

SB_DQSP3

SB_DQSP4

SB_DQSP5

SB_DQSP6

SB_DQSP7

AM38

AN38

AK38

AL38

AY49

AU50

AW49

AV50

AM32

AK32

AL32

AM35

AK35

AM33

AL35

AM36

AU49

AP40

AR40

AP42

AR42

AR45

AP45

AW46

AY46

AY47

AU46

AK36

AV47

AU47

AK33

AR46

AP46

AW30

AV26

AN28

AN25

AW22

AV18

AN21

AN18

AV30

AW26

AM28

AM25

AV22

AW18

AM21

AM18

M_B_DIM0_CLK#0 17

M_B_DIM0_CLK0 17

M_B_DIM0_CLK#1 17

M_B_DIM0_CLK1 17

M_B_DIM0_CKE0 17

M_B_DIM0_CKE1 17

M_B_DIM0_CKE2 17

M_B_DIM0_CKE3 17

M_B_DIM0_CS#0 17

M_B_DIM0_CS#1 17

M_B_DIM0_ODT0 17

M_B_CAB3

M_B_CAB2

M_B_CAB1

M_B_CAB4

M_B_CAB6

M_B_CAA5

M_B_CAB9

M_B_CAB8

M_B_CAB5

M_B_CAA0

M_B_CAA2

M_B_CAA4

M_B_CAA3

M_B_CAA1

M_B_CAB7

M_B_CAA7

M_B_CAA6

M_B_CAB0

M_B_CAA9

M_B_CAA8

M_B_DQS#0 17

M_B_DQS#1 17

M_B_DQS#2 17

M_B_DQS#3 17

M_B_DQS#4 17

M_B_DQS#5 17

M_B_DQS#6 17

M_B_DQS#7 17

M_B_DQS0 17

M_B_DQS1 17

M_B_DQS2 17

M_B_DQS3 17

M_B_DQS4 17

M_B_DQS5 17

M_B_DQS6 17

M_B_DQS7 17

M_B_CAB[9:0] 17

haswell_mcp

A A

haswell_mcp

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

Engineer:

Engineer:

BG1\CORE

BG1\CORE

BG1\CORE

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

P1HBC

P1HBC

P1HBC

Engineer:

1

CPU(2)_LPDDR3

CPU(2)_LPDDR3

CPU(2)_LPDDR3

Kang_Kang

Kang_Kang

Kang_Kang

594Tuesday, April 15, 2014

594Tuesday, April 15, 2014

594Tuesday, April 15, 2014

Rev

Rev

Rev

1.0

1.0

1.0

Page 6

5

smd.db-x7.ru

+DDR_V

12

+

CE0603

330UF/2.5V

@

D D

VR_SVID_ALERT#80

VR_SVID_CLK80

VR_SVID_DATA80

Placement note:

1. R0601 close to CPU

2. R0602 close to CPU

3. R0605 close to CPU

4. R0606 close to CPU

U0601

1

NC

2

VRM_PWRGD30,80,92

GND

C C

+VCORE

A

3 4

GND

74AUP1G07GW

12

VCC

Y

C0606

10UF/6.3V

5

12

C0607

10UF/6.3V

+1.05VS_VCCST

12

R0602

75Ohm

1%

R0601 43Ohm

R0610 0Ohm

R0612 0Ohm

+3VS

GND

1 2

1 2

1 2

CPU_VR_EN80

12

C0645

0.1UF/6.3V

X5R

vx_c0201

12

C0603

10UF/6.3V

+1.05VS_VCCST

ULT_DELAY_VRGD30

12

C0604

10UF/6.3V

+1.05VS_VCCST

12

R0605

130Ohm

1%

+1.05VS_PWRGD_S

12

NI

R0603

10KOhm

Put on Top side

12

+

CE0601

330UF/2.5V

@

4

12

C0605

10UF/6.3V

+VCCIO_OUT

1 2

12

C0608

10UF/6.3V

1 2

R0608 0Ohm

ULT_DELAY_VRGD

R0618

10KOhm

12

C0609

2.2UF/10V

VCCSENSE80

C0642

4.7UF/6.3V

CPU_PWR_DEBUG10

+1.05VS_VCCST

12

C0643

22UF/6.3V

GND

12

C0610

2.2UF/10V

1 2

R0607 0Ohm

12

NI

GND

1 2

R0615 0Ohm

1 2

R0616 0Ohm

1 2

R0617 0Ohm

GND

12

@

C0644

1UF/6.3V

1AT200000068

12

+VCORE

+VCCIOA_OUT

12

C0601

2.2UF/10V

GND

12

R0606

100Ohm

1%

VCC_SENSE_R

+VCCIO_OUT_R

H_CPU_SVIDALRT#

H_CPU_SVIDCLK

H_CPU_SVIDDAT

+1.05VS_PWRGD_S_R

CPU_VR_EN_R

ULT_DELAY_VRGD_R

T0603

T0604

T0605

T0606

+VCORE

C0602

2.2UF/10V

+VCORE

1

1

1

1

RSVD_69

RSVD_70

RSVD_71

RSVD_72

L59

J58

AH26

AJ31

AJ33

AJ37

AN33

AP43

AR48

AY35

AY40

AY44

AY50

F59

N58

AC58

E63

AB23

A59

E20

AD23

AA23

AE59

L62

N63

L63

B59

F60

C59

D63

H59

P62

P60

P61

N59

N61

T59

AD60

AD59

AA59

AE60

AC59

AG58

U59

V59

AC22

AE22

AE23

AB57

AD57

AG57

C24

C28

C32

3

U0301L

RSVD4

RSVD5

VDDQ3

VDDQ2

VDDQ6

VDDQ5

VDDQ4

VDDQ8

VDDQ7

VDDQ10

VDDQ9

VDDQ1

VDDQ11

VCCIN

RSVD7

RSVD6

VCC_SENSE

RSVD8

VCCIO_OUT

VCCIOA_OUT

RSVD9

RSVD11

RSVD10

VIDALERT#

VIDSCLK

VIDSOUT

VCCST_PWRGD

VR_EN

VR_READY

VSS1

PWR_DEBUG

VSS2

RSVD_TP1

RSVD_TP2

RSVD_TP3

RSVD_TP4

RSVD54

RSVD38

RSVD37

RSVD34

RSVD39

RSVD36

RSVD40

RSVD55

RSVD56

VCCST3

VCCST2

VCCST1

VCC67

VCC66

VCC4

VCC1

VCC3

VCC2

HASWELL_MCP_E

HSW ULT POWER

VCC62

VCC63

VCC64

VCC60

VCC61

VCC57

VCC58

VCC59

VCC55

VCC56

VCC52

VCC53

VCC54

VCC50

VCC51

VCC47

VCC48

VCC49

VCC45

VCC46

VCC42

VCC43

VCC44

VCC41

VCC40

VCC37

VCC38

VCC39

VCC36

VCC35

VCC34

VCC32

VCC33

VCC31

VCC30

VCC29

VCC27

VCC28

VCC26

VCC25

VCC24

VCC22

VCC23

VCC21

VCC19

VCC20

VCC16

VCC17

VCC18

VCC14

VCC15

VCC12

VCC13

VCC65

VCC11

VCC10

VCC7

VCC8

VCC9

VCC6

VCC5

C36

C40

C44

C48

C52

C56

E23

E25

E27

E29

E31

E33

E35

E37

E39

E41

E43

E45

E47

E49

E51

E53

E55

E57

F24

F28

F32

F36

F40

F44

F48

F52

F56

G23

G25

G27

G29

G31

G33

G35

G37

G39

G41

G43

G45

G47

G49

G51

G53

G55

G57

H23

J23

K23

K57

L22

M23

M57

P57

U57

W57

2

+VCORE

1

GND

12

C0612

22UF/6.3V

12

C0622

22UF/6.3V

B B

+1.05VS_PWRGD10,82,92

12

C0613

22UF/6.3V

12

C0623

22UF/6.3V

12

10KOhm

R0621

12

C0614

22UF/6.3V

12

C0624

22UF/6.3V

12

C0615

22UF/6.3V

12

NI

C0625

22UF/6.3V

U0602

1

NC

2

A

3 4

GND

12

C0616

22UF/6.3V

12

C0626

22UF/6.3V

VCC

Y

12

12

12

R0620

10KOhm

C0619

22UF/6.3V

C0629

22UF/6.3V

12

C0617

22UF/6.3V

12

C0627

22UF/6.3V

+3VS+3VS

5

GND

NI

12

C0646

0.1UF/6.3V

X5R

vx_c0201

12

C0618

22UF/6.3V

12

C0628

22UF/6.3V

+1.05VS_VCCST

12

C0620

22UF/6.3V

12

C0630

22UF/6.3V

+1.05VS_PWRGD_S

12

GND

12

GND

NI

C0621

22UF/6.3V

C0631

22UF/6.3V

haswell_mcp

+1.05VS +1.05VS_VCCST

1 2

R0611 0Ohm

vx_r0805_h24_small

1 2

R0613 0Ohm

R0619 0Ohm

NI

vx_r0805_h24_small

1 2

vx_r0805_h24_small

1.29A

0.67A

+VCCIO_OUT

+VCCIO_OUT_XDP

GND

A A

Decoupling guide from Intel (EE)

74AUP1G07GW

VDDQ(+1.2V) 2.2uF * 4pcs (stuff)

10uF * 6pcs (stuff)

330uF * 2pcs (non stuff)

Decoupling guide from Intel ( EE)

+VCORE 22uF * 4pcs (non stuff)

22uF * 16pcs (stuff)

330uF * 1pcs (non stuff)

5

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Junction

Junction

Junction

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

CPU(4)_PWR

CPU(4)_PWR

CPU(4)_PWR

Chinhung_Wang

Chinhung_Wang

Chinhung_Wang

698Tuesday, April 15, 2014

698Tuesday, April 15, 2014

698Tuesday, April 15, 2014

Rev

Rev

Rev

2.2

2.2

2.2

Page 7

5

smd.db-x7.ru

D D

4

3

2

1

C C

B B

A A

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Junction

Junction

Junction

Engineer:

1

CPU(5)_****

CPU(5)_****

CPU(5)_****

Chinhung_Wang

Chinhung_Wang

Chinhung_Wang

798Tuesday, April 15, 2014

798Tuesday, April 15, 2014

798Tuesday, April 15, 2014

Rev

Rev

Rev

2.2

2.2

2.2

Page 8

5

smd.db-x7.ru

HASWELL_MCP_E

U0301N

A11

VSS128

A14

VSS127

A18

VSS126

A24

VSS125

A28

VSS129

A32

VSS124

A36

VSS123

A40

VSS122

A44

VSS121

D D

C C

A48

A52

A56

AA1

AA58

AB10

AB20

AB22

AB7

AC61

AD21

AD3

AD63

AE10

AE5

AE58

AF11

AF12

AF14

AF15

AF17

AF18

AG1

AG11

AG21

AG23

AG60

AG61

AG62

AG63

AH17

AH19

AH20

AH22

AH24

AH28

AH30

AH32

AH34

AH36

AH38

AH40

AH42

AH44

AH49

AH51

AH53

AH55

AH57

AJ13

AJ14

AJ23

AJ25

AJ27

AJ29

VSS120

VSS119

VSS118

VSS117

VSS116

VSS115

VSS114

VSS113

VSS112

VSS111

VSS110

VSS109

VSS108

VSS107

VSS106

VSS105

VSS104

VSS103

VSS102

VSS19

VSS101

VSS20

VSS100

VSS99

VSS98

VSS97

VSS96

VSS95

VSS94

VSS93

VSS92

VSS91

VSS90

VSS89

VSS88

VSS87

VSS86

VSS85

VSS12

VSS13

VSS136

VSS84

VSS83

VSS139

VSS138

VSS137

VSS82

VSS81

VSS80

VSS79

VSS78

VSS77

VSS76

VSS75

VSS74

haswell_mcp

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS16

VSS14

VSS15

VSS73

VSS72

VSS17

VSS71

VSS70

VSS18

VSS69

VSS68

VSS67

VSS66

VSS65

VSS64

VSS63

VSS62

VSS61

VSS60

VSS59

VSS58

VSS57

VSS56

VSS55

VSS54

VSS53

VSS52

VSS51

VSS50

VSS49

VSS48

VSS47

VSS46

VSS45

VSS44

VSS43

VSS42

VSS41

VSS40

VSS39

VSS38

VSS37

VSS36

VSS35

VSS34

VSS33

VSS32

VSS31

VSS30

VSS29

VSS28

VSS27

VSS26

VSS25

VSS24

VSS23

VSS22

VSS21

AJ35

AJ39

AJ41

AJ43

AJ45

AJ47

AJ50

AJ52

AJ54

AJ56

AJ58

AJ60

AJ63

AK23

AK3

AK52

AL10

AL13

AL17

AL20

AL22

AL23

AL26

AL29

AL31

AL33

AL36

AL39

AL40

AL45

AL46

AL51

AL52

AL54

AL57

AL60

AL61

AM1

AM17

AM23

AM31

AM52

AN17

AN23

AN31

AN32

AN35

AN36

AN39

AN40

AN42

AN43

AN45

AN46

AN48

AN49

AN51

AN52

AN60

AN63

AN7

AP10

AP17

AP20

4

HASWELL_MCP_E

U0301O

AP22

AP23

AP26

AP29

AP3

AP31

AP38

AP39

AP48

AP52

AP54

AP57

AR11

AR15

AR17

AR23

AR31

AR33

AR39

AR43

AR49

AR5

AR52

AT13

AT35

AT37

AT40

AT42

AT43

AT46

AT49

AT61

AT62

AT63

AU1

AU16

AU18

AU20

AU22

AU24

AU26

AU28

AU30

AU33

AU51

AU53

AU55

AU57

AU59

AV14

AV16

AV20

AV24

AV28

AV33

AV34

AV36

AV39

AV41

AV43

AV46

AV49

AV51

AV55

VSS148

VSS252

VSS251

VSS250

VSS254

VSS249

VSS253

VSS248

VSS247

VSS246

VSS245

VSS244

VSS262

VSS243

VSS242

VSS241

VSS240

VSS239

VSS238

VSS237

VSS236

VSS235

VSS234

VSS233

VSS232

VSS231

VSS230

VSS229

VSS228

VSS227

VSS226

VSS225

VSS224

VSS223

VSS222

VSS221

VSS220

VSS219

VSS218

VSS217

VSS216

VSS140

VSS215

VSS261

VSS214

VSS213

VSS260

VSS212

VSS211

VSS210

VSS267

VSS263

VSS266

VSS264

VSS265

VSS149

VSS209

VSS208

VSS207

VSS206

VSS205

VSS204

VSS203

VSS255

haswell_mcp

VSS147

VSS146

VSS145

VSS202

VSS201

VSS200

VSS199

VSS198

VSS144

VSS197

VSS196

VSS195

VSS194

VSS193

VSS192

VSS143

VSS191

VSS190

VSS189

VSS188

VSS187

VSS186

VSS185

VSS184

VSS183

VSS182

VSS181

VSS180

VSS179

VSS178

VSS177

VSS176

VSS175

VSS174

VSS173

VSS172

VSS171

VSS170

VSS169

VSS168

VSS167

VSS166

VSS165

VSS142

VSS141

VSS164

VSS163

VSS162

VSS161

VSS160

VSS159

VSS158

VSS157

VSS156

VSS155

VSS154

VSS153

VSS256

VSS257

VSS259

VSS258

VSS152

VSS151

VSS150

AV59

AV8

AW16

AW24

AW33

AW35

AW37

AW4

AW40

AW42

AW44

AW47

AW50

AW51

AW59

AW60

AY11

AY16

AY18

AY22

AY24

AY26

AY30

AY33

AY4

AY51

AY53

AY57

AY59

AY6

B20

B24

B26

B28

B32

B36

B4

B40

B44

B48

B52

B56

B60

C11

C14

C18

C20

C25

C27

C38

C39

C57

D12

D14

D18

D2

D21

D23

D25

D26

D27

D29

D30

D31

GND

D33

D34

D35

D37

D38

D39

D41

D42

D43

D45

D46

D47

D49

D5

D50

D51

D53

D54

D55

D57

D59

D62

D8

E11

E17

F20

F26

F30

F34

F38

F42

F46

F50

F54

F58

F61

G18

G22

G3

G5

G6

G8

H13

3

U0301P

VSS277

VSS307

VSS308

VSS309

VSS310

VSS311

VSS280

VSS281

VSS306

VSS305

VSS304

VSS303

VSS268

VSS302

VSS301

VSS300

VSS299

VSS298

VSS297

VSS296

VSS352

VSS295

VSS294

VSS293

VSS315

VSS292

VSS291

VSS314

VSS316

VSS320

VSS317

VSS290

VSS319

VSS289

VSS288

VSS287

VSS286

VSS313

VSS285

VSS284

VSS312

VSS283

VSS282

haswell_mcp

HASWELL_MCP_E

VSS321

VSS279

VSS276

VSS322

VSS323

VSS324

VSS325

VSS326

VSS327

VSS328

VSS329

VSS330

VSS331

VSS332

VSS333

VSS278

VSS334

VSS335

VSS336

VSS337

VSS338

VSS339

VSS341

VSS340

VSS342

VSS343

VSS344

VSS346

VSS345

VSS347

VSS348

VSS269

VSS270

VSS271

VSS272

VSS349

VSS350

VSS351

VSS275

VSS274

VSS273

VSS_SENSE

VSS318

H17

H57

J10

J22

J59

J63

K1

K12

L13

L15

L17

L18

L20

L58

L61

L7

M22

N10

N3

P59

P63

R10

R22

R8

T1

T58

U20

U22

U61

U9

V10

V3

V7

W20

W22

Y10

Y59

Y63

V58

AH46

V23

E62

AH16

VSS_SENSE_R

GND

Placement note:

1. R0801 close to CPU

1 2

R0801 0Ohm

12

R0802

100Ohm

1%

GND

2

VSSSENSE 80

1

GND GND GND GND

B B

A A

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Junction

Junction

Junction

Engineer:

1

CPU(6)_GND

CPU(6)_GND

CPU(6)_GND

Chinhung_Wang

Chinhung_Wang

Chinhung_Wang

898Tuesday, April 15, 2014

898Tuesday, April 15, 2014

898Tuesday, April 15, 2014

Rev

Rev

Rev

2.2

2.2

2.2

Page 9

5

smd.db-x7.ru

D D

4

CFG010

CFG110

CFG210

CFG310

CFG410

CFG510

CFG610

CFG710

CFG810

CFG910

CFG1010

CFG1110

CFG1210

CFG1310

CFG1410

CFG1510

CFG1610

CFG1710

CFG1810

CFG1910

3

U0301S

HASWELL_MCP_E

2

1

12

R09021KOhm

NI

12

R09041KOhm

NI

12

R09031KOhm

12

R09051KOhm

NI

12

R09061KOhm

NI

12

R09121KOhm

NI

GND

CFG strapping information:

The CFG signals have a default value of '1'

CFG[20:0] - INT. PU

CFG[3:0]: Reserved configuration lane.

A test point may be placed on the board for these lanes.

GND

CFG[4]: eDP enable

-1 = Disabled

-0 = Enabled

C C

CFG[19:5]: Reserved configuration lanes.

CFG0

CFG1

T0903

T0904

CFG4

T0905

T0906

T0907

CFG8

CFG9

CFG10

T0911

T0912

T0913

T0914

T0915

T0916

T0918

T0917

T0919

T0920

T0921

T0922

T0923

T0924

1

1

1

1

1

1

1

1

1

1

1

1

1

1

R0910 49.9Ohm1%

1

1

1

1

1

R0908 8.2KOhm

GND

12

12

CFG_RCOMP

RSVD33

TP9

TP10

TP11

TP12

TD_IREF

AC60

AC62

AC63

AA63

AA60

Y62

Y61

Y60

V62

V61

V60

U60

T63

T62

T61

T60

AA62

U63

AA61

U62

V63

J20

H18

B12

A5

E1

D1

haswell_mcp

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG18

CFG17

CFG19

CFG_RCOMP

RSVD33

TP9

TP10

TP11

TP12

TD_IREF

RESERVED

RSVD_TP5

RSVD_TP11

RSVD_TP10

RSVD_TP9

EDP_SPARE

RSVD_TP6

RSVD_TP7

RSVD_TP8

RSVD32

RSVD30

PROC_OPI_COMP

RSVD31

RSVD28

RSVD29

VSS353

VSS354

RSVD52

RSVD53

AV63

RSVD_TP5

AU63

RSVD_TP11

C63

RSVD_TP10

C62

RSVD_TP9

B43

A51

B51

L60

RSVD_TP8

N60

RSVD32

W23

RSVD30

Y22

RSVD31

AY15

PROC_OPI_COMP

AV62

RSVD28

D58

RSVD29

P22

N21

P20

RSVD52

R20

RSVD53

GND

1

T0925

1

T0926

1

T0927

1

T0928

1

T0932

1

T0933

1

T0934

1

T0935

1

T0938

1

T0939

1

T0936

1

T0937

12

GND

R0911

49.9Ohm

1%

A test point may be placed on the board for these lands.

Follow Harris Beach

U0301Q

HASWELL_MCP_E

CFG strapping information:

The CFG signals have a default value of '1'

CFG[0]: EAR-STALL/NOT STALL RESET SEQUENCE AFTER PCU PLL IS LOCKED

-1 = (DEFAULT) NORMAL OPERATION; NO STALL

-0 = STALL

CFG[1]: PCH/ PCH LESS MODE SELECTION

-1 = (DEFAULT) NORMAL OPERATION

-0 = PCH-LESS MODE

T0940

T0941

DC_TEST_AY2_AW2

DC_TEST_AY3_AW3

1

TP_DC_TEST_AY60

DC_TEST_AY61_AW61

DC_TEST_AY62_AW62

1

TP_DC_TEST_B2

DC_TEST_A3_B3

DC_TEST_A61_B61

DC_TEST_B62_B63

DC_TEST_C1_C2

AY2

DAISY_CHAIN_NCTF_AY2

AY3

DAISY_CHAIN_NCTF_AY3

AY60

DAISY_CHAIN_NCTF_AY60

AY61

DAISY_CHAIN_NCTF_AY61

AY62

DAISY_CHAIN_NCTF_AY62

B2

DAISY_CHAIN_NCTF_B2

B3

DAISY_CHAIN_NCTF_B3

B61

DAISY_CHAIN_NCTF_B61

B62

DAISY_CHAIN_NCTF_B62

B63

DAISY_CHAIN_NCTF_B63

C1

DAISY_CHAIN_NCTF_C1

C2

DAISY_CHAIN_NCTF_C2

haswell_mcp

DAISY_CHAIN_NCTF_A3

DAISY_CHAIN_NCTF_A4

DAISY_CHAIN_NCTF_A60

DAISY_CHAIN_NCTF_A61

DAISY_CHAIN_NCTF_A62

DAISY_CHAIN_NCTF_AV1

DAISY_CHAIN_NCTF_AW1

DAISY_CHAIN_NCTF_AW2

DAISY_CHAIN_NCTF_AW3

DAISY_CHAIN_NCTF_AW61

DAISY_CHAIN_NCTF_AW62

DAISY_CHAIN_NCTF_AW63

A3

DC_TEST_A3_B3

A4

TP_DC_TEST_A4

A60

TP_DC_TEST_A60

A61

DC_TEST_A61_B61

A62

TP_DC_TEST_A62

AV1

AW1

AW2

DC_TEST_AY2_AW2

AW3

DC_TEST_AY3_AW3

AW61

DC_TEST_AY61_AW61

AW62

DC_TEST_AY62_AW62

AW63

TP_DC_TEST_AW63

1

T0942

1

T0943

1

T0945

1

T0944

CFG[8]: ALLOW THE USE OF NOA ON LOCKED UNITS

-1 = DISABLED(DEFAULT);

U0301R

HASWELL_MCP_E

IN THIS CASE, NOA WILL BEDISABLED IN LOCKED UNITS AND ENABLED IN UN-LOCKED UNITS

-0 = ENABLED;

NOA WILL BE AVAILABLE REGARDLESS OF THE LOCKING OF THE UNIT

1

CFG[9]: NO SVID PROTOCOL CAPABLE VR CONNECTED

-1 = VRS SUPPORTING SVID PROTOCOL ARE PRESENT

B B

-0 = NO VR SUPPORTING SVID IS PRESENT.

THE CHIP WILL NOT GENERATE (OR RESPOND TO) SVID ACTIVITY

CFG[10]: SAFE MODE BOOT

T0959

T0960

T0961

T0962

T0963

T0965

RSVD12

1

RSVD13

1

RSVD14

1

RSVD15

1

RSVD16

1

RSVD18

AT2

AU44

AV44

D15

F22

H22

J21

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD18

-1 = POWER FEATURES ACTIVATED DURING RESET

-0 = POWER FEATURES (ESPECIALLY CLOCK GATINE ARE NOT ACTIVATED

haswell_mcp

RSVD20

RSVD21

RSVD19

RSVD26

RSVD25

RSVD24

RSVD27

RSVD23

RSVD22

RSVD44

RSVD45

N23

R23

T23

U10

AL1

AM11

AP7

AU10

AU15

AW14

AY14

RSVD21

RSVD19

RSVD26

RSVD25

RSVD27

RSVD23

RSVD22

RSVD44

RSVD45

1

T0949

1

T0950

1

T0951

1

T0952

1

T0954

1

T0955

1

T0956

1

T0957

1

T0958

A A

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Junction

Junction

Junction

Engineer:

1

CPU(7)_RESERVED

CPU(7)_RESERVED

CPU(7)_RESERVED

Chinhung_Wang

Chinhung_Wang

Chinhung_Wang

Rev

Rev

Rev

2.2

2.2

2.2

998Tuesday, April 15, 2014

998Tuesday, April 15, 2014

998Tuesday, April 15, 2014

Page 10

5

smd.db-x7.ru

4

3

2

1

10

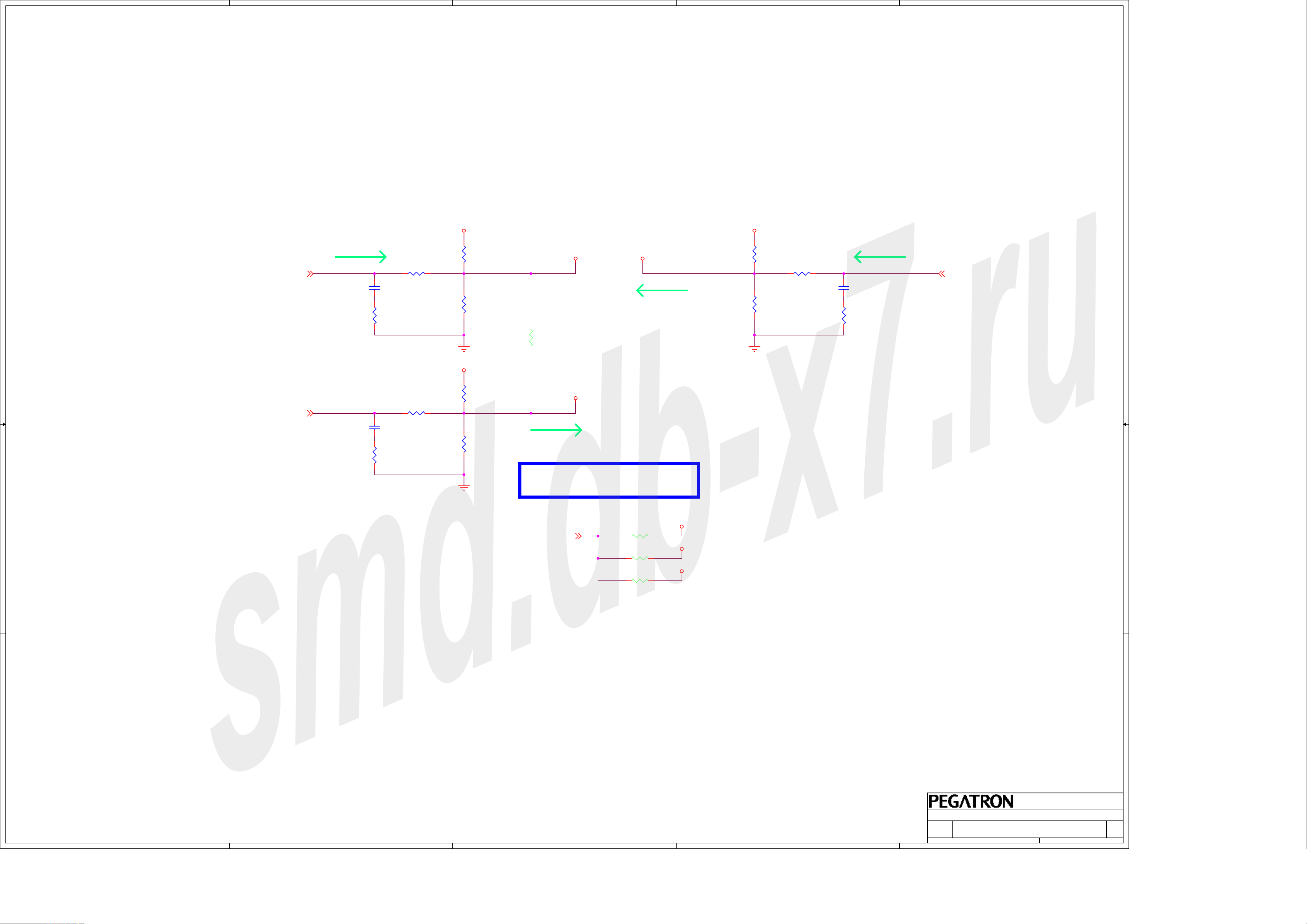

CPU XDP connector

Intel recommend (R1.0 on 9/10)

XDP pin 40, 42/HOOK4, 5 should be left Open, unstuff R1006, R1007.

D D

XDP_PREQ#4

XDP_PRDY#4

CFG09

CFG19

CFG29

+VCCIO_OUT_XDP

+3VSUS

12

12

NI

R1005

1KOhm

+1.05VS_PWRGD_S +1.05VS_PWRGD_XDP CLK_XDP_P_R

PM_PWRBTN#_R22

PWR_SW#

C C

R1008 0Ohm

R1004 0Ohm

NI

/XDP

12

12

R1001 1KOhm

R1002 0Ohm

R1003 0Ohm

SYS_PWROK22

SMB_DAT_S28

SMB_CLK_S28

XDP_TCK4

PCH_JTAG_TCK20

PCH_JTAGX20

12

/XDP

12

/XDP

12

/XDP

+1.05VS_VCCST

J1d

J1s

J2d

NI

C1005

1UF/6.3V

GND

PWR_DEBUG_R XDP_RST#_R

/XDP

NI

/XDP

CFG39

XDP_BPM04

XDP_BPM14

CFG49

CFG59

CFG69

CFG79

12

R10740Ohm

12

R10730Ohm

12

R10170Ohm

XDP_TCK1

/XDP

J1001

1

1

3

5

7

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

NP_NC1

NP_NC2

/XDP

1 2

2

4

6

8

NI

3

5

7

9

11

13

15

17

19

21

23

25

27

29

31

33

35

37

39

41

43

45

47

49

51

53

55

57

59

61

AXK6F60335

R1071 0Ohm

J2s

2

4

6

8

10

12

14

16

18

20

22

24

26

28

30

32

34

36

38

40

42

44

46

48

50

52

54

56

58

60

62

12

R10781KOhm

CLK_XDP_N_RPM_PWRBTN#_XDP

XDP_DBRESET#_R

XDP_TDO_BUF

CFG3_R

GNDGND

CFG17 9

CFG16 9

CFG8 9

CFG9 9

CFG10 9

CFG11 9

CFG19 9

CFG18 9

CFG12 9

CFG13 9

CFG14 9

CFG15 9

+VCCIO_OUT_XDP +1.05VSUS +3VS

12

12

GND

1 2

R1072 0Ohm

XDP_TDI_BUF

/XDP

12

R7

NI

R1079

51Ohm

12

R10750Ohm

NI

R1076

1KOhm

12

/XDP

/XDP

/XDP

1 2

/XDP

1 2

R1013 0Ohm

/XDP

C1001

0.01UF/10V

X5R

vx_c0201

R10060Ohm

12

R10070Ohm

12

R10101KOhm

R10160Ohm

J3sJ4d

NI

J3d

CLK_XDP_P 21

CLK_XDP_N 21

PLT_RST#_BUF 53

PM_SYSRST#_R 22

PCH_JTAG_TDO 20

PCH_JTAG_TDI 20

PCH_JTAG_TMS 20

/XDP

147

U1001C

VCC

10

9

GND

SN74CBTLV3126PWR

06T150000012

8

SW

+3VS

S3

12

C1004

0.1UF/6.3V

X5R

vx_c0201

GND

XDP_TDI 4

12

150Ohm

R1024

1%

XDP_TRST#_BUF

12

NI

R1023

10KOhm

GND

B B

+1.05VS_PWRGD6,82,92

+1.05VS_PWRGD

GND

/XDP

147

U1001A

VCC

1

2

GND

SN74CBTLV3126PWR

06T150000012

/XDP

U1001B

4

5

GND

SN74CBTLV3126PWR

06T150000012

/XDP

U1001D

13

12

GND

SN74CBTLV3126PWR

06T150000012

GND

VCC

GND

VCC

3

SW

147

6

SW

147

11

SW

S1

S2

S4

XDP_TRST# 4,20CPU_PWR_DEBUG 6

XDP_TMS 4

XDP_TDO 4

74CBTLV3126

GND

A A

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORPORATION

PEGATRON CORPORATION

PEGATRON CORPORATION

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

P1HBC

P1HBC

P1HBC

Engineer:

1

CPU_PCH_XDP

CPU_PCH_XDP

CPU_PCH_XDP

Kang_Kang

Kang_Kang

Kang_Kang

10 98Tuesday, April 15, 2014

10 98Tuesday, April 15, 2014

10 98Tuesday, April 15, 2014

Rev

Rev

Rev

1.0

1.0

1.0

Page 11

5

smd.db-x7.ru

4

3

2

1

12

D D

Audio_BDCONN

Audio DB

+3VS+3VA

12

C C

R1254

0Ohm

@

12

R1255

0Ohm

+5VS +5VSUS

12

R1256

0Ohm

12

R1257

0Ohm

+3VS

to PCH

VOLUMEDOWN#

BAT_ORG_LED#30

CHG_LED_BLUE#30

AU_HP_CON_L36

AU_HP_CON_R36

VOLUMEUP#

PWR_SW#_M30

AU_HP_JD#36

SLEEVE_R36

RING2_R36

@

HOMEKEY#

VOLUMEDOWN#

VOLUMEUP#

AGND_AUD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

CON1201

GND1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

GND2

FPC_CON_20P

21

22

MB Pin Definition

1.HOMEKEY#

2.VOLUMEDOWN#

3.VOLUMEUP#

4.+3VS

5.PWR_SW#_M

6.+5VS

7.BAT_ORG_LED#

8.CHG_LED_BLUE#

9.GND

10.GND

11.NC

12.+3VS

13.NC

14.AU_HP_CON_L

15.AU_HP_CON_R

16.AU_HP_JD#

17.SLEEVE_R

18.RING2_R

19.GND_AUDIO

20.GND_AUDIO

Win8 Home Key

+3VA

B B

HOMEKEY#

12

R1251

10KOhm

@

+3VS

12

R1250

10KOhm

@

R1253 0Ohm

R1252 0Ohm

12

12

HOME_KEY#_SOC

to PCH

HOMEKEY 30

A A

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CONFIDENTIAL

PEGATRON CONFIDENTIAL

PEGATRON CONFIDENTIAL

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

P1HBC

P1HBC

P1HBC

1

Audio_BDCONN

Audio_BDCONN

Audio_BDCONN

Kang_Kang

Kang_Kang

Kang_Kang

12 99Tuesday, April 15, 2014

12 99Tuesday, April 15, 2014

12 99Tuesday, April 15, 2014

Rev

Rev

Rev

1.0

1.0

1.0

Page 12

5

smd.db-x7.ru

4

3

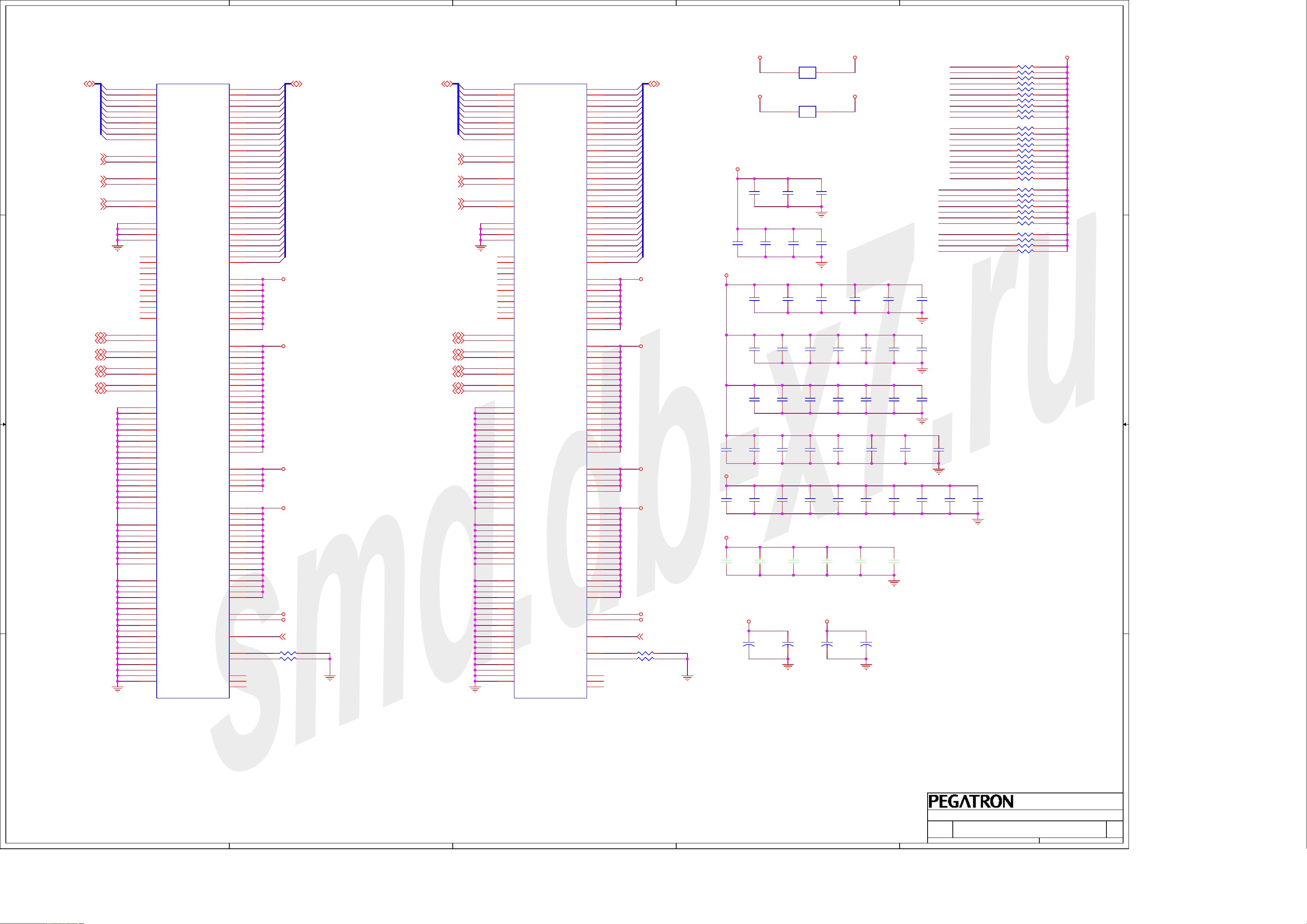

16 LPDDR3(1)_MEMORY DOWN

2

1

+1.2V_DDR3+DDR_V

JP1601

2

112

U1601

M_A_CAA0

M_A_CAA1

M_A_CAA2

M_A_CAA3

D D

M_A_DIM0_CLK05

M_A_DIM0_CLK#05

M_A_DIM0_CKE05

M_A_DIM0_CKE15 M_A_DIM0_CKE35

M_A_DIM0_CS#05,16

M_A_DIM0_CS#15,16

C C

M_A_DQS15

M_A_DQS#15 M_A_DQS#55

M_A_DQS75

M_A_DQS#75

M_A_DQS05

M_A_DQS#05

M_A_DQS65

M_A_DQS#65

B B

M_A_CAA4

M_A_CAA5

M_A_CAA6

M_A_CAA7

M_A_CAA8

M_A_CAA9

GND GND

R2

CA0

P2

CA1

N2

CA2

N3

CA3

M3

CA4

F3

CA5

E3

CA6

E2

CA7

D2

CA8

C2

CA9

J3

CK_t

J2

CK_c

K3

CKE0

K4

CKE1

L3

CS0_n

L4

CS1_n

L8

DM0

G8

DM1

P8

DM2

D8

DM3

A1

DNU_1

A2

DNU_5

A12

DNU_7

A13

DNU_9

B1

DNU_2

B13

DNU_10

T1

DNU_3

T13

DNU_11

U1

DNU_4

U2

DNU_6

U12

DNU_8

U13

DNU_12

L10

DQS0_t

L11

DQS0_c

G10

DQS1_t

G11

DQS1_c

P10

DQS2_t

P11

DQS2_c

D10

DQS3_t

D11

DQS3_c

B2

VSS_1

B5

VSS_10

C5

VSS_11

E4

VSS_6

E5

VSS_12

F5

VSS_13

H2

VSS_2

J12

VSS_19

K2

VSS_3

L6

VSS_18

M5

VSS_14

N4

VSS_7

N5

VSS_15

R4

VSS_8

R5

VSS_16

T2

VSS_4

T3

VSS_5

T4

VSS_9

T5

VSS_17

C3

VSSCA_1

D3

VSSCA_2

F4

VSSCA_5

G3

VSSCA_3

G4

VSSCA_6

J4

VSSCA_7

M4

VSSCA_8

P3

VSSCA_4

B6

VSSQ_1

B12

VSSQ_14

C6

VSSQ_2

D12

VSSQ_15

E6

VSSQ_3

F6

VSSQ_4

F12

VSSQ_16

G6

VSSQ_5

G9

VSSQ_10

H10

VSSQ_12

K10

VSSQ_13

L9

VSSQ_11

M6

VSSQ_6

M12

VSSQ_17

N6

VSSQ_7

P12

VSSQ_18

R6

VSSQ_8

T6

VSSQ_9

T12

VSSQ_19

H9CCNNNBLTMLAR-NTM

03T150000040

VDD1_1

VDD1_3

VDD1_5

VDD1_7

VDD1_9

VDD1_2

VDD1_4

VDD1_6

VDD1_8

VDD1_10

VDD2_15

VDD2_17

VDD2_1

VDD2_3

VDD2_10

VDD2_4

VDD2_5

VDD2_11

VDD2_19

VDD2_6

VDD2_12

VDD2_7

VDD2_13

VDD2_20

VDD2_8

VDD2_2

VDD2_9

VDD2_14

VDD2_16

VDD2_18

VDDCA_1

VDDCA_2

VDDCA_5

VDDCA_3

VDDCA_4

VDDQ_8

VDDQ_12

VDDQ_1

VDDQ_13

VDDQ_14

VDDQ_2

VDDQ_5

VDDQ_9

VDDQ_6

VDDQ_7

VDDQ_3

VDDQ_10

VDDQ_15

VDDQ_4

VDDQ_16

VDDQ_17

VDDQ_11

Vref(CA)

Vref(DQ)

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

ODT

ZQ0

ZQ1

NC_2

NC_3

NC_1

P9

M_A_D14

N9

M_A_D10

N10

M_A_D12

N11

M8

M9

M10

M11

F11

F10

F9

F8

E11

E10

E9

D9

T8

T9

T10

T11

R8

R9

R10

R11

C11

C10

C9

C8

B11

B10

B9

B8

A3

A4

A5

A6

A10

U3

U4

U5

U6

U10

A8

A9

D4

D5

D6

G5

H5

H6

H12

J5

J6

K5

K6

K12

L5

P4

P5

P6

U8

U9

F2

G2

H3

L2

M2

A11

C12

E8

E12

G12

H8

H9

H11

J9

J10

K8

K11

L12

N8

N12

R12

U11

H4

J11

J8

B3

B4

C4

K9

R3

M_A_D8

M_A_D15

M_A_D11

M_A_D9

M_A_D13

M_A_D56

M_A_D0

M_A_D5

M_A_D2

M_A_D3

M_A_D4

M_A_D1

M_A_D6

M_A_D7

M_A_D55 M_A_D18

1 2

R1601 240Ohm

1 2

R1602 240Ohm

M_A_D[31:0] 5 M_A_D[63:32] 5M_A_CAA[9:0]5 M_A_CAB[9:0]5

M_A_DIM0_CLK15

M_A_DIM0_CLK#15

M_A_DIM0_CKE25

M_A_DIM0_CS#05,16

M_A_DIM0_CS#15,16

+1.8V_DDR3 +1.8V_DDR3

M_A_DQS55

+1.2V_DDR3

+1.2V_DDR3

+1.2V_DDR3 +1.2V_DDR3

+V_VREF_CA_DIMM

+V_VREF_DQ_DIMM0

M_A_DIM0_ODT0 5,16 M_A_DIM0_ODT0 5,16

GND

M_A_DQS35

M_A_DQS#35

M_A_DQS45

M_A_DQS#45

M_A_DQS25

M_A_DQS#25

M_A_CAB0

M_A_CAB1

M_A_CAB2

M_A_CAB3

M_A_CAB4

M_A_CAB5

M_A_CAB6

M_A_CAB7

M_A_CAB8

M_A_CAB9

GNDGND

U1602

R2

CA0

P2

CA1

N2

CA2

N3

CA3

M3

CA4

F3

CA5

E3

CA6

E2

CA7

D2

CA8

C2

CA9

J3

CK_t

J2

CK_c

K3

CKE0

K4

CKE1

L3

CS0_n

L4

CS1_n

L8

DM0

G8

DM1

P8

DM2

D8

DM3

A1

DNU_1

A2

DNU_5

A12

DNU_7

A13

DNU_9

B1

DNU_2

B13

DNU_10

T1

DNU_3

T13

DNU_11

U1

DNU_4

U2

DNU_6

U12

DNU_8

U13

DNU_12

L10

DQS0_t

L11

DQS0_c

G10

DQS1_t

G11

DQS1_c

P10

DQS2_t

P11

DQS2_c

D10

DQS3_t

D11

DQS3_c

B2

VSS_1

B5

VSS_10

C5

VSS_11

E4

VSS_6

E5

VSS_12

F5

VSS_13

H2

VSS_2

J12

VSS_19

K2

VSS_3

L6

VSS_18

M5

VSS_14

N4

VSS_7

N5

VSS_15

R4

VSS_8

R5

VSS_16

T2

VSS_4

T3

VSS_5

T4

VSS_9

T5

VSS_17

C3

VSSCA_1

D3

VSSCA_2

F4

VSSCA_5

G3

VSSCA_3

G4

VSSCA_6

J4

VSSCA_7

M4

VSSCA_8

P3

VSSCA_4

B6

VSSQ_1

B12

VSSQ_14

C6

VSSQ_2

D12

VSSQ_15

E6

VSSQ_3

F6

VSSQ_4

F12

VSSQ_16

G6

VSSQ_5

G9

VSSQ_10

H10

VSSQ_12

K10

VSSQ_13

L9

VSSQ_11

M6

VSSQ_6

M12

VSSQ_17

N6

VSSQ_7

P12

VSSQ_18

R6

VSSQ_8

T6

VSSQ_9

T12

VSSQ_19

H9CCNNNBLTMLAR-NTM

03T150000040

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VDD1_1

VDD1_3

VDD1_5

VDD1_7

VDD1_9

VDD1_2

VDD1_4

VDD1_6

VDD1_8

VDD1_10

VDD2_15

VDD2_17

VDD2_1

VDD2_3

VDD2_10

VDD2_4

VDD2_5

VDD2_11

VDD2_19

VDD2_6

VDD2_12

VDD2_7

VDD2_13

VDD2_20

VDD2_8

VDD2_2

VDD2_9

VDD2_14

VDD2_16

VDD2_18

VDDCA_1

VDDCA_2

VDDCA_5

VDDCA_3

VDDCA_4

VDDQ_8

VDDQ_12

VDDQ_1

VDDQ_13

VDDQ_14

VDDQ_2

VDDQ_5

VDDQ_9

VDDQ_6

VDDQ_7

VDDQ_3

VDDQ_10

VDDQ_15

VDDQ_4

VDDQ_16

VDDQ_17

VDDQ_11

Vref(CA)

Vref(DQ)

ODT

ZQ0

ZQ1

NC_2

NC_3

NC_1

P9

M_A_D46

N9

M_A_D42

N10

M_A_D45

N11

M_A_D40

M8

M_A_D47

M9

M_A_D43

M10

M_A_D41

M11

M_A_D44

F11

M_A_D25M_A_D58

F10

M_A_D24M_A_D59

F9

M_A_D26M_A_D63

F8

M_A_D27

E11

M_A_D28M_A_D62

E10

M_A_D29M_A_D57

E9

M_A_D30M_A_D60

D9

M_A_D31M_A_D61

T8

M_A_D36

T9

M_A_D33

T10

M_A_D34

T11

M_A_D35

R8

M_A_D37

R9

M_A_D32

R10

M_A_D38

R11

M_A_D39

C11

M_A_D23M_A_D51

C10

M_A_D22M_A_D50

C9

C8

M_A_D21M_A_D49

B11

M_A_D16M_A_D52

B10

M_A_D17M_A_D53

B9

M_A_D20M_A_D54

B8

M_A_D19M_A_D48

A3

A4

A5

A6

A10

U3

U4

U5

U6

U10

A8

A9

D4

D5

D6

G5

H5

H6

H12

J5

J6

K5

K6

K12

L5

P4

P5

P6

U8

U9

F2

G2

H3

L2

M2

A11

C12

E8

E12

G12

H8

H9

H11

J9

J10

K8

K11

L12

N8

N12

R12

U11

H4

J11

J8

B3

B4

C4

K9

R3

1 2

R1603 240Ohm

1 2

R1604 240Ohm

+1.2V_DDR3

+1.2V_DDR3

+V_VREF_CA_DIMM

+V_VREF_DQ_DIMM0

GND

+1.8V_DDR3

12

C1605

10UF/6.3V

C1608

1UF/6.3V

12

12

12

12

12

C1601

0.047UF/16V

12

C1609

1UF/6.3V

C1612

10UF/6.3V

C1618

1UF/6.3V

C1625

1UF/6.3V

C1633

1UF/6.3V

C1641

1UF/6.3V

12

C1653

22UF/6.3V

@

12

+1.2V_DDR3

12

C1632

1UF/6.3V

+V_VDDQ_VTT

12

C1640

1UF/6.3V

+V_VDDQ_VTT

12

C1652

22UF/6.3V

@

+V_VREF_CA_DIMM +V_VREF_DQ_DIMM0

3MM_OPEN_5MIL

+1.8V_DDR3+1.8V

JP1602

2

112

1MM_OPEN_M1M2

C1610

1UF/6.3V

12

C1620

1UF/6.3V

12

C1627

1UF/6.3V

12

C1635

1UF/6.3V

12

C1643

1UF/6.3V

C1654

22UF/6.3V

@

12

GND

12

GND

12

12

C1607

10UF/6.3V

C1611

1UF/6.3V

C1614

10UF/6.3V

12

C1621

1UF/6.3V

12

C1628

1UF/6.3V

12

0.1UF/16V

12

C1646

1UF/6.3V

C1655

22UF/6.3V

@

C1603

0.047UF/16V

12

C1636

12

12

C1606

10UF/6.3V

12

12

C1613

10UF/6.3V

12

C1619

1UF/6.3V

12

C1626

1UF/6.3V

12

C1634

1UF/6.3V

12

C1642

1UF/6.3V

12

C1602

0.047UF/16V

GND GND

C1615

10UF/6.3V

12

C1622

1UF/6.3V

12

C1629

1UF/6.3V

12

0.1UF/16V

12

C1647

1UF/6.3V

C1656

22UF/6.3V

@

C1604

0.047UF/16V

12

C1637

C1616

10UF/6.3V

12

C1623

1UF/6.3V

12

C1630

1UF/6.3V

12

C1648

1UF/6.3V

12

C1657

22UF/6.3V

GND

12

C1638

0.1UF/16V

@

12

GND

12

GND

12

GND

12

C1617

10UF/6.3V

C1624

1UF/6.3V

C1631

1UF/6.3V

C1649

1UF/6.3V

M_A_CAA0

M_A_CAA1

M_A_CAA2

M_A_CAA3

M_A_CAA4

M_A_CAA5

M_A_CAA6

M_A_CAA7

M_A_CAA8

M_A_CAA9

M_A_CAB0

M_A_CAB1

M_A_CAB2

M_A_CAB3

M_A_CAB4

M_A_CAB5

M_A_CAB6

M_A_CAB7

M_A_CAB8

M_A_CAB9

M_A_DIM0_ODT0

M_A_DIM0_CS#0

M_A_DIM0_CS#1

M_A_DIM0_CKE0

M_A_DIM0_CKE1

M_A_DIM0_CKE2

M_A_DIM0_CKE3

M_A_DIM0_CLK0

M_A_DIM0_CLK#0

M_A_DIM0_CLK1

M_A_DIM0_CLK#1

12

C1639

0.1UF/16V

GND

12

C1650

22UF/6.3V

12

GND

C1651

22UF/6.3V

1 2

R1605 54.9Ohm

1 2

R1606 54.9Ohm

1 2

R1607 54.9Ohm

1 2

R1608 54.9Ohm

1 2

R1609 54.9Ohm

1 2

R1610 54.9Ohm

1 2

R1611 54.9Ohm

1 2

R1612 54.9Ohm

1 2

R1613 54.9Ohm

1 2

R1614 54.9Ohm

1 2

R1615 54.9Ohm

1 2

R1616 54.9Ohm

1 2

R1617 54.9Ohm

1 2

R1618 54.9Ohm

1 2

R1619 54.9Ohm

1 2

R1620 54.9Ohm

1 2

R1621 54.9Ohm

1 2

R1622 54.9Ohm

1 2

R1623 54.9Ohm

1 2

R1624 54.9Ohm

1 2

R1629 80.6Ohm

1 2

R1628 80.6Ohm

1 2

R1627 80.6Ohm

1 2

R1625 80.6Ohm

1 2

R1626 80.6Ohm

1 2

R1635 80.6Ohm

1 2

R1634 80.6Ohm

1 2

R1630 37.4Ohm

1 2

R1631 37.4Ohm

1 2

R1632 37.4Ohm

1 2

R1633 37.4Ohm

+V_VDDQ_VTT

A A

LPDDR3(1)_MEMORY DOWN

LPDDR3(1)_MEMORY DOWN

Title :

Title :

Title :

Engineer:

Engineer:

BG1\CORE

BG1\CORE

BG1\CORE

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

P1HBC

P1HBC

P1HBC

Engineer:

1

LPDDR3(1)_MEMORY DOWN

Kang_Kang

Kang_Kang

Kang_Kang

Rev

Rev

Rev

1.0

1.0

1.0

16 94Tuesday, April 15, 2014

16 94Tuesday, April 15, 2014

16 94Tuesday, April 15, 2014

Page 13

5

smd.db-x7.ru

4

3

2

1

C1751

22UF/6.3V

+V_VDDQ_VTT

LPDDR3(2)_MEMORY DOWN17

M_B_CAA[9:0]5

D D

M_B_DIM0_CLK05

M_B_DIM0_CLK#05

M_B_DIM0_CKE05

M_B_DIM0_CKE15

M_B_DIM0_CS#05,17

M_B_DIM0_CS#15,17

C C

M_B_DQS35

M_B_DQS#35

M_B_DQS05

M_B_DQS#05

M_B_DQS25

M_B_DQS#25

M_B_DQS15

M_B_DQS#15

B B

M_B_CAA0

M_B_CAA1

M_B_CAA2

M_B_CAA3

M_B_CAA4

M_B_CAA5

M_B_CAA6

M_B_CAA7

M_B_CAA8

M_B_CAA9

GND GND

U1701

R2

CA0

P2

CA1

N2

CA2

N3

CA3

M3

CA4

F3

CA5

E3

CA6

E2

CA7

D2

CA8

C2

CA9

J3

CK_t

J2

CK_c

K3

CKE0

K4

CKE1

L3

CS0_n

L4

CS1_n

L8

DM0

G8

DM1

P8

DM2

D8

DM3

A1

DNU_1

A2

DNU_5

A12

DNU_7

A13

DNU_9

B1

DNU_2

B13

DNU_10

T1

DNU_3

T13

DNU_11

U1

DNU_4

U2

DNU_6

U12

DNU_8

U13

DNU_12

L10

DQS0_t

L11

DQS0_c

G10

DQS1_t

G11

DQS1_c

P10

DQS2_t

P11

DQS2_c

D10

DQS3_t

D11

DQS3_c

B2

VSS_1

B5

VSS_10

C5

VSS_11

E4

VSS_6

E5

VSS_12

F5

VSS_13

H2

VSS_2

J12

VSS_19

K2

VSS_3

L6

VSS_18

M5

VSS_14

N4

VSS_7

N5

VSS_15

R4

VSS_8

R5

VSS_16

T2

VSS_4

T3

VSS_5

T4

VSS_9

T5

VSS_17

C3

VSSCA_1

D3

VSSCA_2

F4

VSSCA_5

G3

VSSCA_3

G4

VSSCA_6

J4

VSSCA_7

M4

VSSCA_8

P3

VSSCA_4

B6

VSSQ_1

B12

VSSQ_14

C6

VSSQ_2

D12

VSSQ_15

E6

VSSQ_3

F6

VSSQ_4

F12

VSSQ_16

G6

VSSQ_5

G9

VSSQ_10

H10

VSSQ_12

K10

VSSQ_13

L9

VSSQ_11

M6

VSSQ_6

M12

VSSQ_17

N6

VSSQ_7

P12

VSSQ_18

R6

VSSQ_8

T6

VSSQ_9

T12

VSSQ_19

H9CCNNNBLTMLAR-NTM

03T150000040

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

VDD1_1

VDD1_3

VDD1_5

VDD1_7

VDD1_9

VDD1_2

VDD1_4

VDD1_6

VDD1_8

VDD1_10

VDD2_15

VDD2_17

VDD2_1

VDD2_3

VDD2_10

VDD2_4

VDD2_5

VDD2_11

VDD2_19

VDD2_6

VDD2_12

VDD2_7

VDD2_13

VDD2_20

VDD2_8

VDD2_2

VDD2_9

VDD2_14

VDD2_16

VDD2_18

VDDCA_1

VDDCA_2

VDDCA_5

VDDCA_3

VDDCA_4

VDDQ_8

VDDQ_12

VDDQ_1

VDDQ_13

VDDQ_14

VDDQ_2

VDDQ_5

VDDQ_9

VDDQ_6

VDDQ_7

VDDQ_3

VDDQ_10

VDDQ_15

VDDQ_4

VDDQ_16

VDDQ_17

VDDQ_11

Vref(CA)

Vref(DQ)

ODT

ZQ0

ZQ1

NC_2

NC_3

NC_1

P9

M_B_D30

N9

M_B_D29

N10

M_B_D28

N11

M_B_D24

M8

M_B_D26

M9

M_B_D25

M10

M_B_D27

M11

M_B_D31

F11

F10

F9

F8

E11

E10

E9

D9

T8

T9

T10

T11

R8

R9

R10

R11

C11

C10

C9

C8

B11

B10

B9

B8

A3

A4

A5

A6

A10

U3

U4

U5

U6

U10

A8

A9

D4

D5

D6

G5

H5

H6

H12

J5

J6

K5

K6

K12

L5

P4

P5

P6

U8

U9

F2

G2

H3

L2

M2

A11

C12

E8

E12

G12

H8

H9

H11

J9

J10

K8

K11

L12

N8

N12

R12

U11

H4

J11

J8

B3

B4

C4

K9

R3

M_B_D3

M_B_D2

M_B_D4

M_B_D1

M_B_D6

M_B_D7

M_B_D5

M_B_D0

M_B_D19

M_B_D16

M_B_D21

M_B_D22

M_B_D18

M_B_D17

M_B_D23

M_B_D20

M_B_D13

M_B_D9

M_B_D11

M_B_D14

M_B_D8

M_B_D12

M_B_D10

M_B_D15

1 2

R1701 240Ohm

1 2

R1702 240Ohm

M_B_D[31:0] 5 M_B_D[63:32] 5

+1.8V_DDR3 +1.8V_DDR3

+1.2V_DDR3

+1.2V_DDR3

+1.2V_DDR3 +1.2V_DDR3

+V_VREF_CA_DIMM

+V_VREF_DQ_DIMM1

M_B_CAB[9:0]5

M_B_DIM0_CLK15

M_B_DIM0_CLK#15

M_B_DIM0_CKE25

M_B_DIM0_CKE35

M_B_DIM0_CS#05,17

M_B_DIM0_CS#15,17

M_B_DQS65

M_B_DQS#65

M_B_DQS55

M_B_DQS#55

M_B_DQS75

M_B_DQS#75

M_B_DQS45

M_B_DQS#45

M_B_CAB0

M_B_CAB1

M_B_CAB2

M_B_CAB3

M_B_CAB4

M_B_CAB5

M_B_CAB6

M_B_CAB7

M_B_CAB8

M_B_CAB9

GNDGND

U1702

R2

CA0

P2

CA1

N2

CA2

N3

CA3

M3

CA4

F3

CA5

E3

CA6

E2

CA7

D2

CA8

C2

CA9

J3

CK_t

J2

CK_c

K3

CKE0

K4

CKE1

L3

CS0_n

L4

CS1_n

L8

DM0

G8

DM1

P8

DM2

D8

DM3

A1

DNU_1

A2

DNU_5

A12

DNU_7

A13

DNU_9

B1

DNU_2

B13

DNU_10

T1

DNU_3

T13

DNU_11

U1

DNU_4

U2

DNU_6

U12

DNU_8

U13

DNU_12

L10

DQS0_t

L11

DQS0_c

G10

DQS1_t

G11

DQS1_c

P10

DQS2_t

P11

DQS2_c

D10

DQS3_t

D11

DQS3_c

B2

VSS_1

B5

VSS_10

C5

VSS_11

E4

VSS_6

E5

VSS_12

F5

VSS_13

H2

VSS_2

J12

VSS_19

K2