Page 1

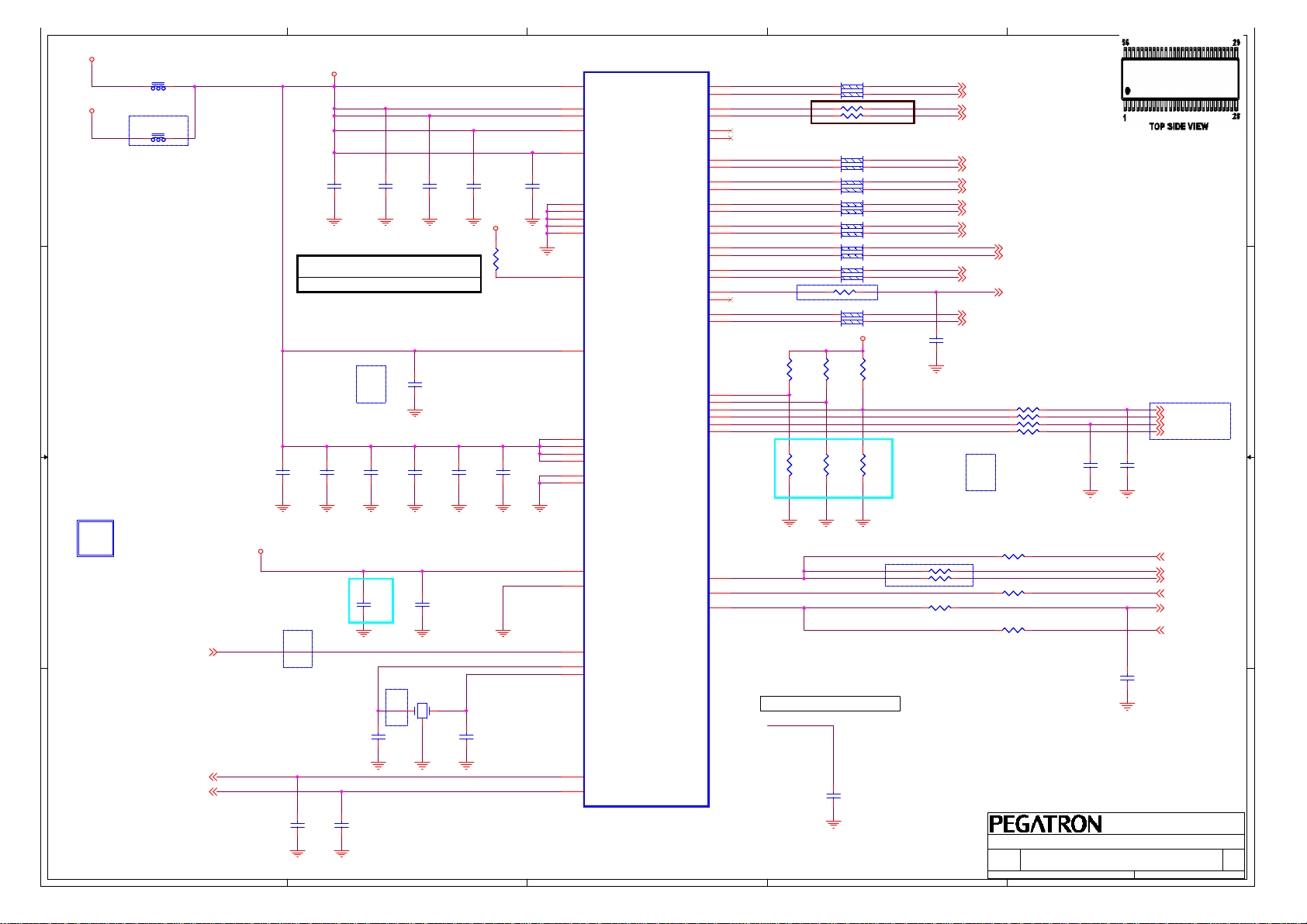

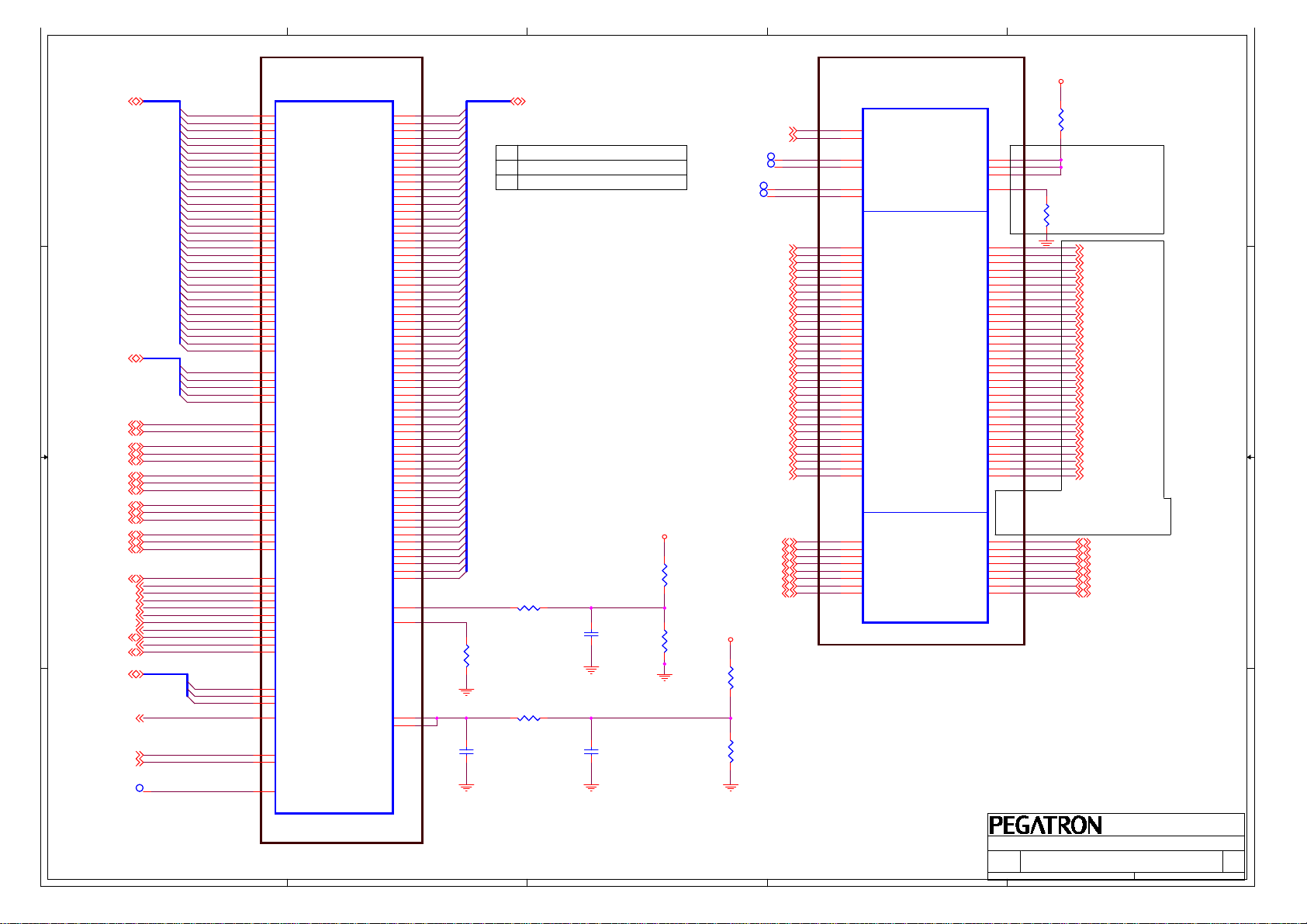

5

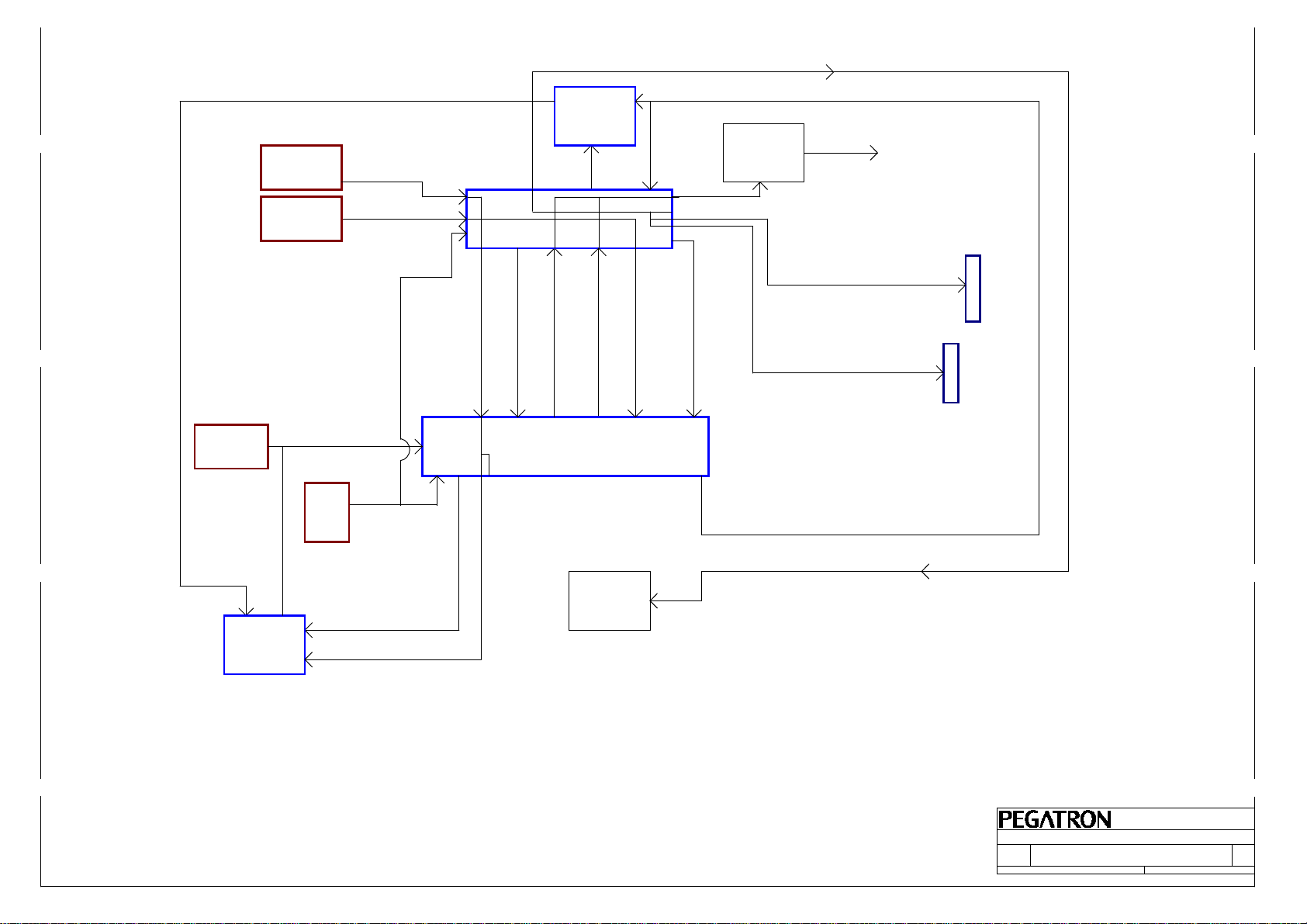

IPX41-D3

D D

Intel Pentium processor

Conroe-L/Conroe/Wolfdate

VGA

C C

B B

A A

PCI Express

X16 SLOT

HDMI

PCI Express

X1 SLOT

Audio

ALC662

USB2.0

8 ports

LAN

Realtek

RTL8111DL

PCI-E X4

PCI-E X16

PCI-E X1

Azalia Link

480Mb/s

e

e

PCI-E X1

P

P

www.schematic-x.blogspot.com

4

Revision:1.02

LGA775

HOST BUS

INTEL

GMCH

EagleLake

DMI Link

INTEL

ICH7

t

t

a

a

g

g

SPI

r

r

SPI

Channel A

Channel B

SATA

o

o

n

n

LPC

3

53.+5V_DUAL53

545554.+3P3V_PCIE&+3P3V_LAN

56

DDR3 DIMM A1

DDR3 DIMM B1

f

f

n

n

o

o

SATA1

SATA2

C

C

SUPER I/O

Fintek F71808EU

PS2 KB/MS

FAN Control

H/W Monitor

i

i

d

d

2

e

e

01

01.Block Diagram

02

02.ECN CONTROL TABLE

03.Power Sequence

03

04.Power Flow

04

05

05.Clock Distribution

06.CLOCK06

07

07.PROCESSOR LGA775 1 - 3

08

08.PROCESSOR LGA775 2 - 3

09

09.PROCESSOR LGA775 3 - 3

10

10.INTEL EAGLELAKE 1 - 7

11

11.INTEL EAGLELAKE 2 - 7

12

12.INTEL EAGLELAKE 3 - 7

13

13.INTEL EAGLELAKE 4 - 7

14

14.INTEL EAGLELAKE 5 - 7

15

15.INTEL EAGLELAKE 6 - 7

16.INTEL EAGLELAKE 7 - 7

16

17.DDR3 CHANNEL A

17

i

i

18

18.DDR3 CHANNEL B

t

t

19

19.DDR3 TERMINATION A&B

20

n

n

20.INTEL ICH7 1 - 4

21

21.INTEL ICH7 2 - 4

22

22.INTEL ICH7 3 - 4

23

23.INTEL ICH7 4 - 4

24

24.PCI EXPRESS X1 SLOT

25

25.PCI EXPRESS X16 SLOT

26

26.INTEGRATED VGA PORT

27.DVI/HDMI CONTROL

27

28.DVI&HDMI / PCIE MUX

28

29.DVI&HDMI LEVEL SHIFTER

29

303230.DVI&HDMI CONNECTOR

31

31.USB CON.

32.USB HEADER CONNECTOR

33

33.SATA CONNECTOR FOR CPC

34

34.Realtek RTL8111DL

35.RJ-45+USB CONNECTOR

35

36.REALTEK ALC662 AZALIA CODEC

36

37.REAR AUDIO CONNECTOR

37

38

38.EMI CAP

39.SUPER I/O - F71808EU

39

40.PS2 KB &MS CONNECTOR FOR CPC

40

41.FAN CIRCUIT

41

42.FRONT PANEL CIRCUIT FOR CPC

42

43.SPI SERIAL FLASH LPC DEGUG

43

44.RTC / CMOS / SPKR/SCREW HOLE

44

45.ATX POWER_24P CONNECTOR

45

46

46.VCORE CONTROLLER

47

47.VCORE DRIVER1

48

48.VCORE DRIVER2

49

49.+1P1V_CORE

50

50.+1P1V_FSB_VTT

51

51.VTT_DDR&3P3VSB SWITCHING&1P5

52

52.+1P5V_DUAL

l

l

a

a

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPX41-D3

IPX41-D3

IPX41-D3

1

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

Block Diagram

Block Diagram

Block Diagram

Ttepic Zhu

Ttepic Zhu

Ttepic Zhu

1 54Thursday, December 10, 2009

1 54Thursday, December 10, 2009

1 54Thursday, December 10, 2009

1.02

Rev

Rev

Rev

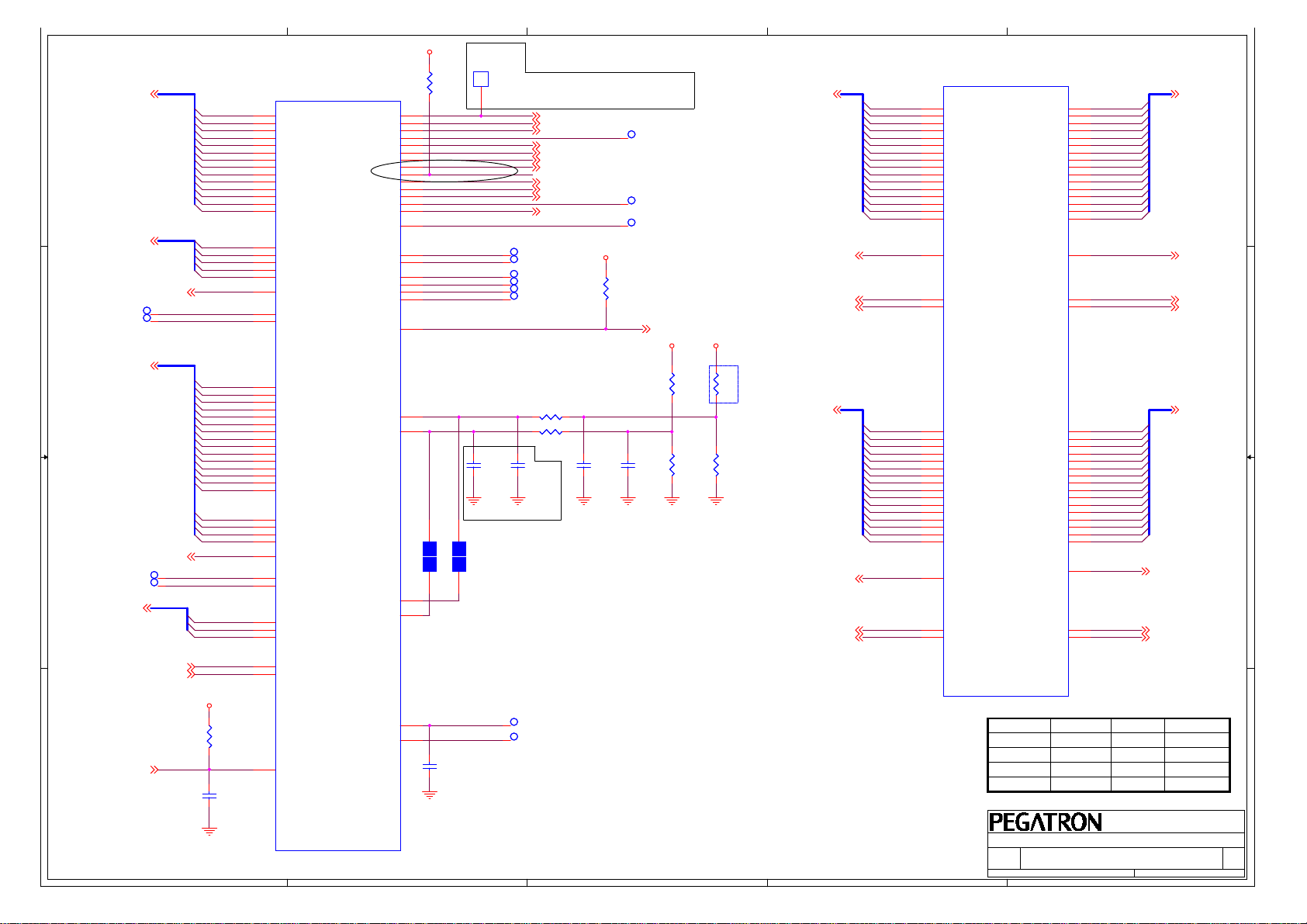

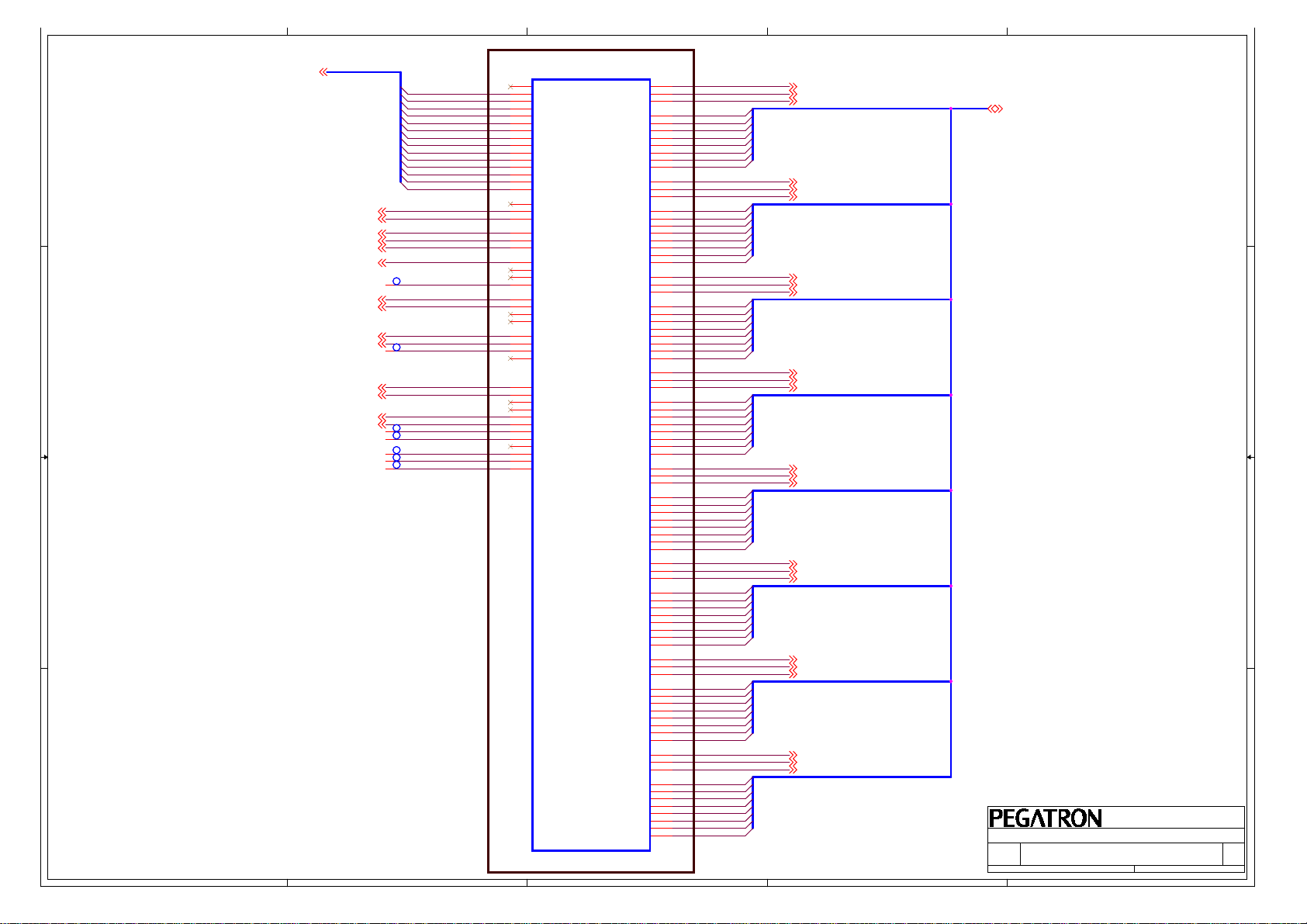

Page 2

5

ECN Control Table

ECN Control Table

ECN Control TableECN Control Table

4

3

2

1

D D

C C

B B

ECN No.

ECN No.

ECN No.ECN No.

DATE

DATE Schematics Revision

DATEDATE

Subject

Subject

SubjectSubject

n

n

C

C

Schematics Revision BOM Part Number

Schematics RevisionSchematics Revision

d

d

i

i

f

f

n

n

o

o

e

e

BOM Part Number PCB

BOM Part NumberBOM Part Number

l

l

a

a

i

i

t

t

n

n

PCBA

PCBA

PCBAPCBA

Revision

Revision

RevisionRevision

PCB

PCBPCB

Revision

Revision

RevisionRevision

o

o

r

r

t

t

a

a

g

g

e

e

P

P

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

ECN

ECN

ECN

Ttepic Zhu

Ttepic Zhu

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IPX41-D3

IPX41-D3

IPX41-D3

Engineer:

Ttepic Zhu

2 54Thursday, December 10, 2009

2 54Thursday, December 10, 2009

1

2 54Thursday, December 10, 2009

1.02

1.02

1.02

Rev

Rev

Rev

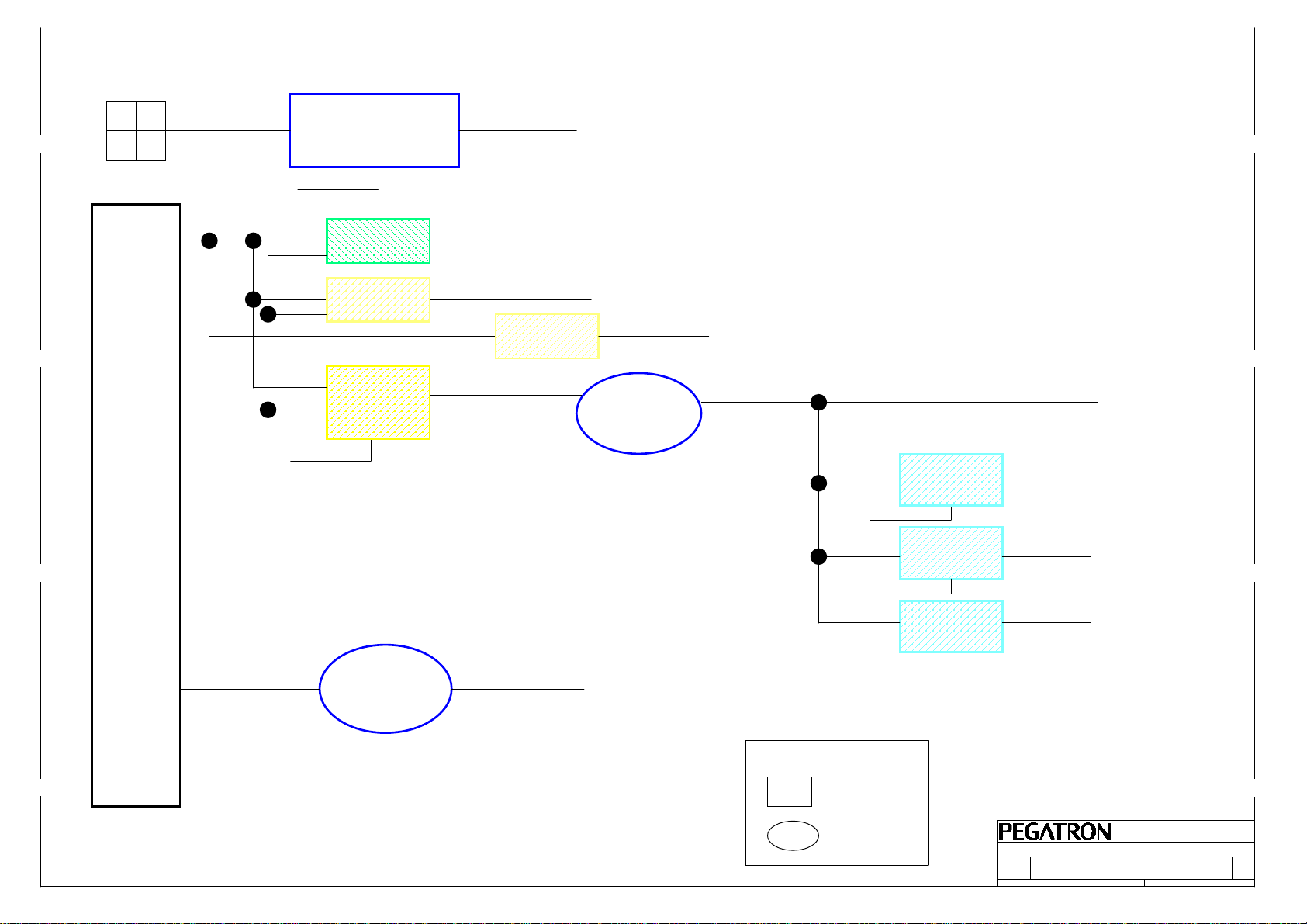

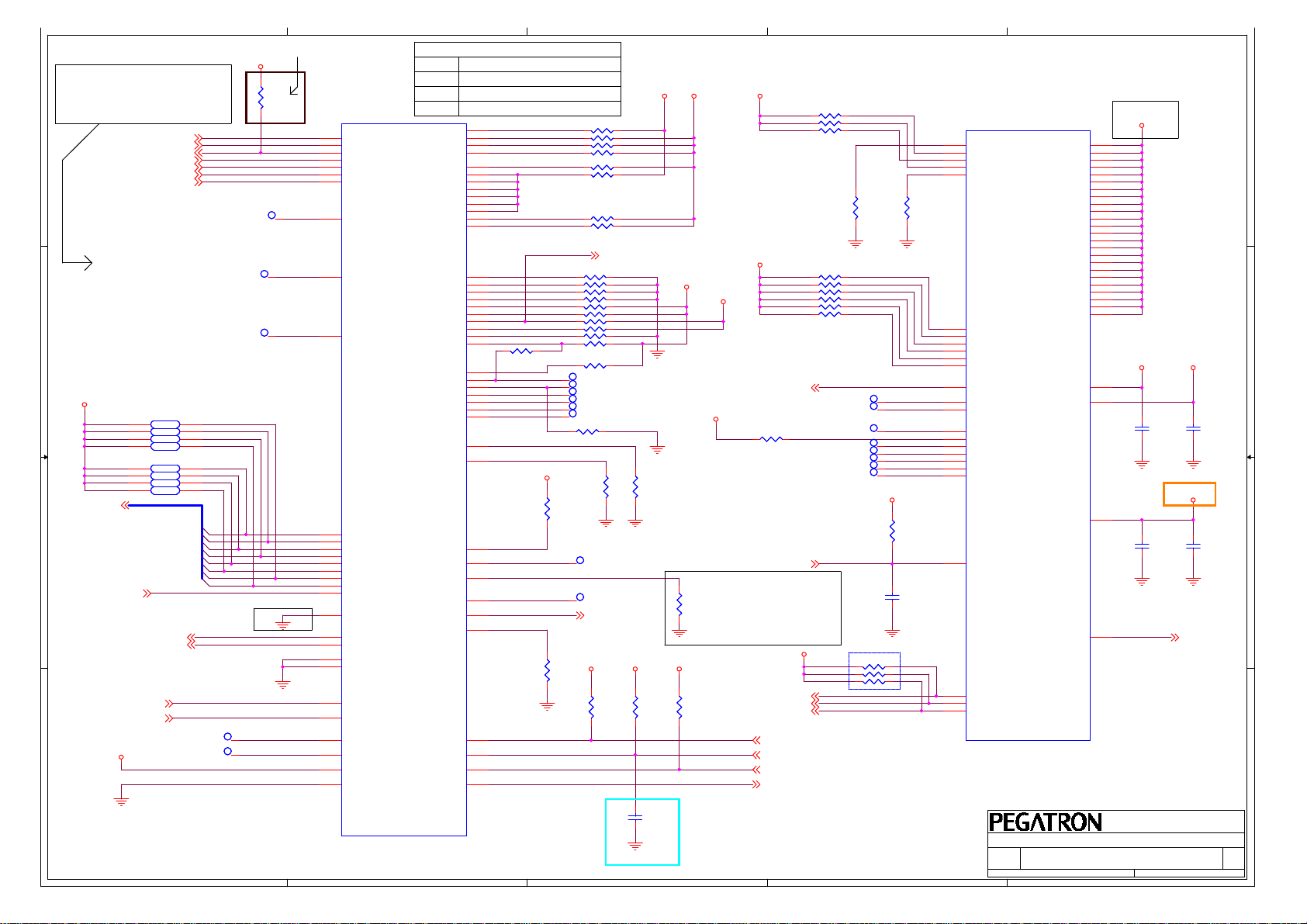

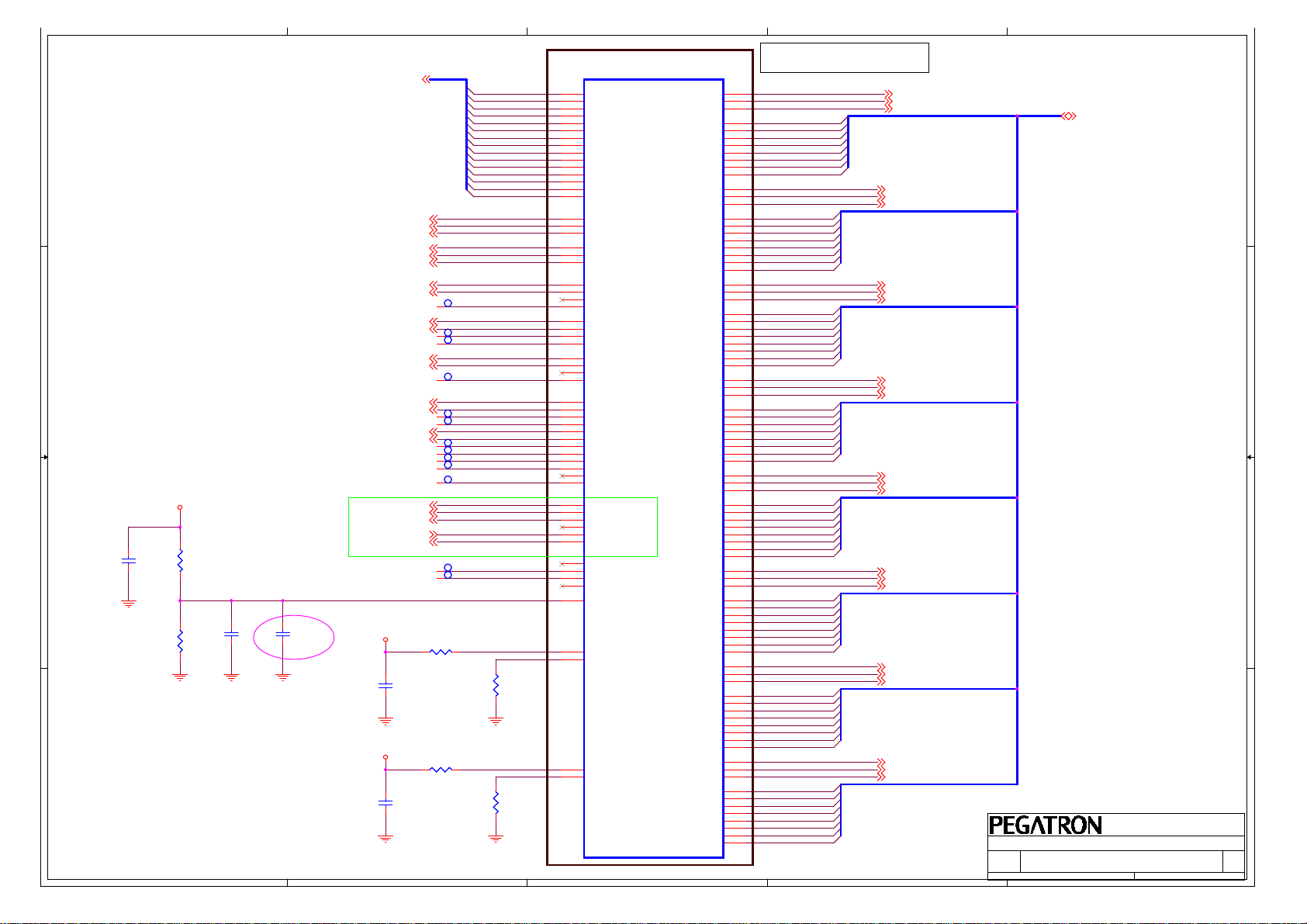

Page 3

5

A

4

3

PCIRST#

2

1

3.3V

o

o

3.3V

8

PLTRST#

PSON#

7

PWROK

Power

Supply

6

8

n

n

8

f

f

PWROK_PS

PCIRST#_PCIEX16

PCIRST#_PCIEX1

d

d

i

i

/X

e

e

PCI Express X16

9

t

t

n

n

PCI Express X1

9

PCIRST#

3.3V

i

i

3.3V

a

a

l

l

8

GMCH

D D

C C

User press

Reset

button

10

B B

CPURST#

User press

Ctrl+Alt+Del

User press

Power

button

RSTCON#

Default

CPU

User

Clear

CMOS

PWRBTN#

Default

RTCRST#

CPUPWRGD

HINIT#

RTCRST#

1

Vcore

a

a

8

3

Super IO

3.3V

3.3V

RST_KB

RSMRST#

2

3.3V

3.3V

3.3V

3.3V

3.3V

o

o

r

r

t

t

Vcore

5

SLP_S3#

3.3V

ICH7

n

n

RTL8111DL

PWROK

7

5

SLP_S4#

3.3V

PLTRST#

Buffer Out

4

IO_PWRBTN#

3.3V

PLTRST#

C

C

3.3V

PCIRST#

g

g

e

e

P

P

1.02

1.02

1.02

A

Rev

Rev

Rev

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

Power Sequence

Power Sequence

Power Sequence

Ttepic Zhu

Ttepic Zhu

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPX41-D3

IPX41-D3

IPX41-D3

Engineer:

Ttepic Zhu

3 54Thursday, December 10, 2009

3 54Thursday, December 10, 2009

3 54Thursday, December 10, 2009

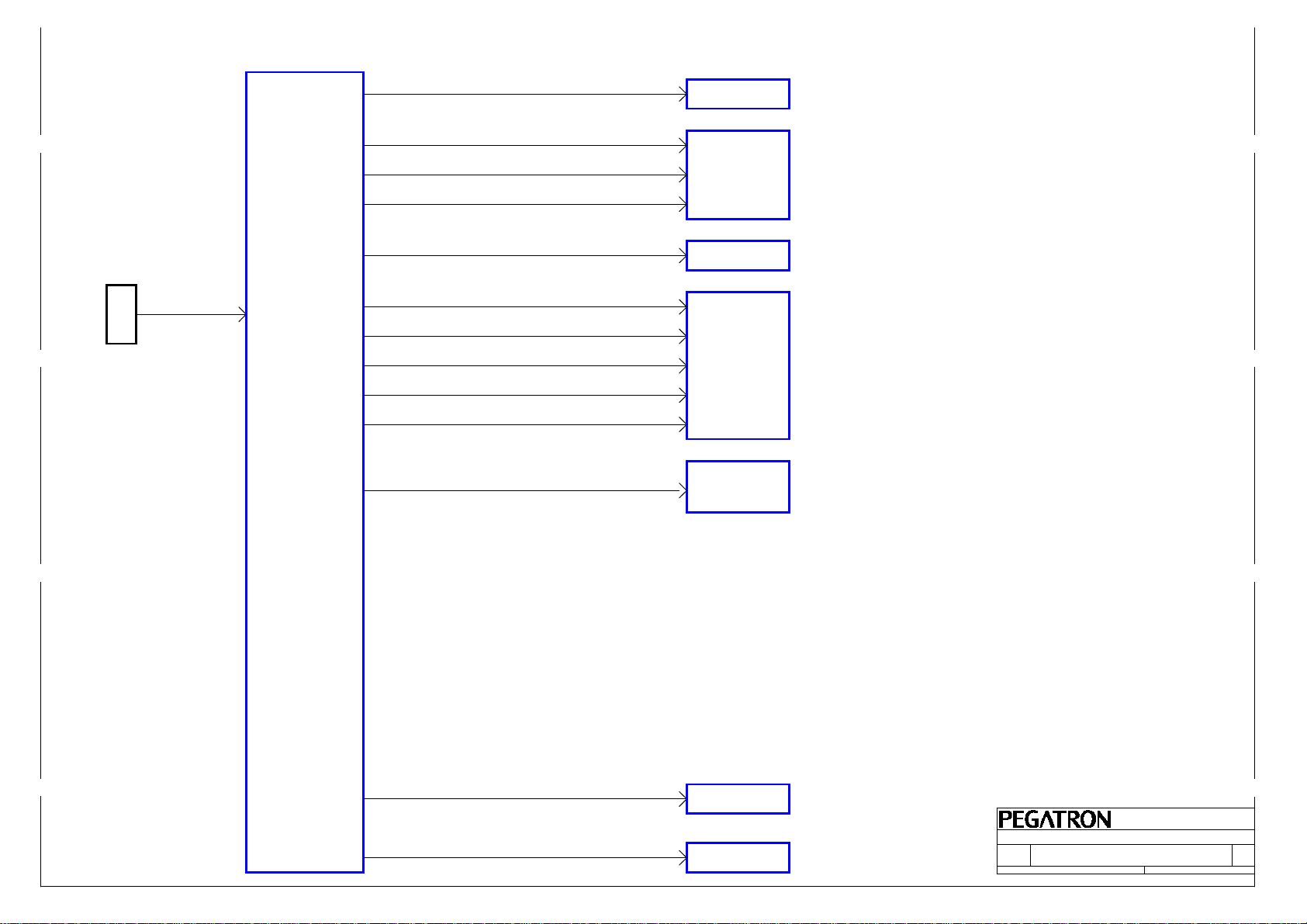

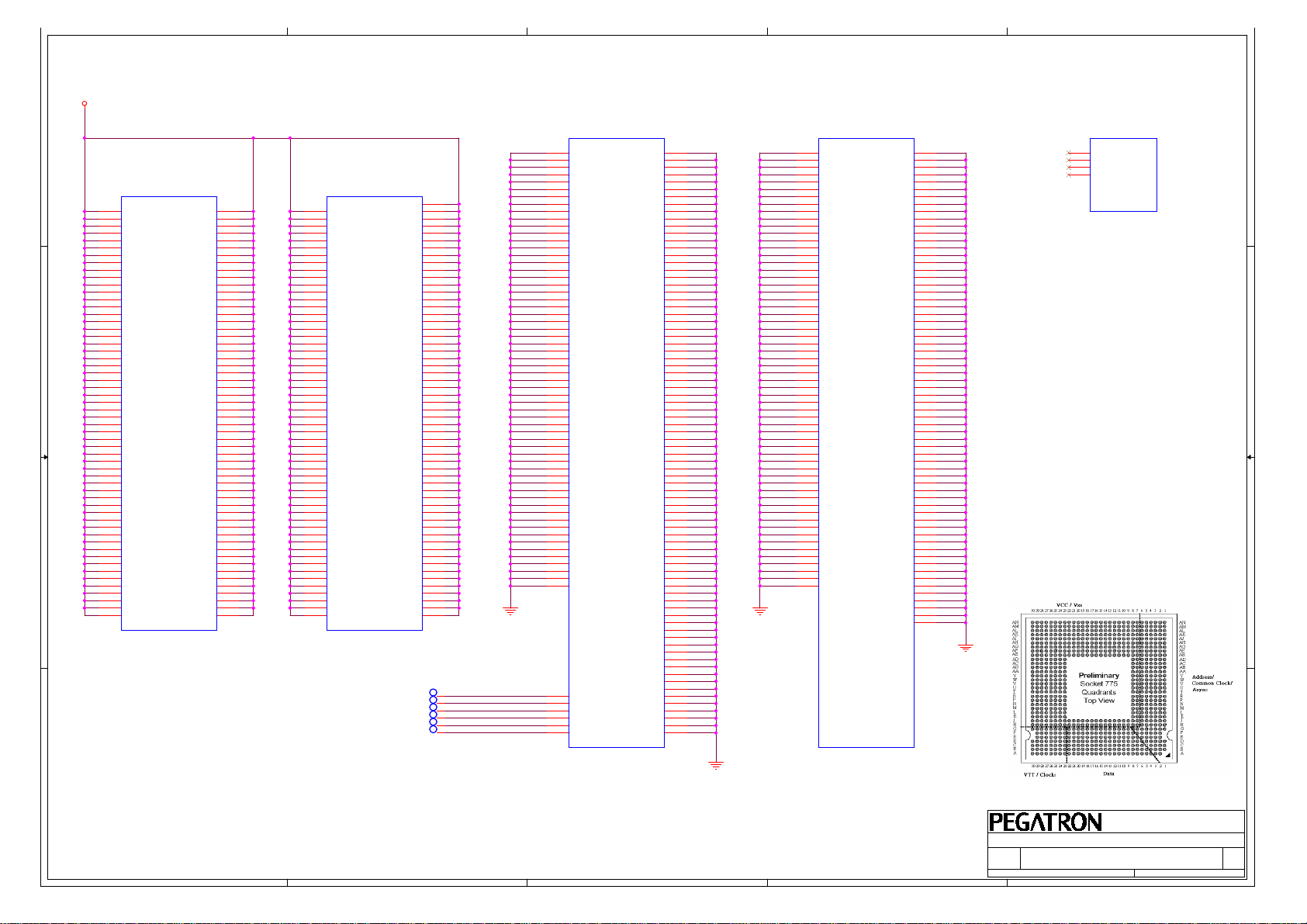

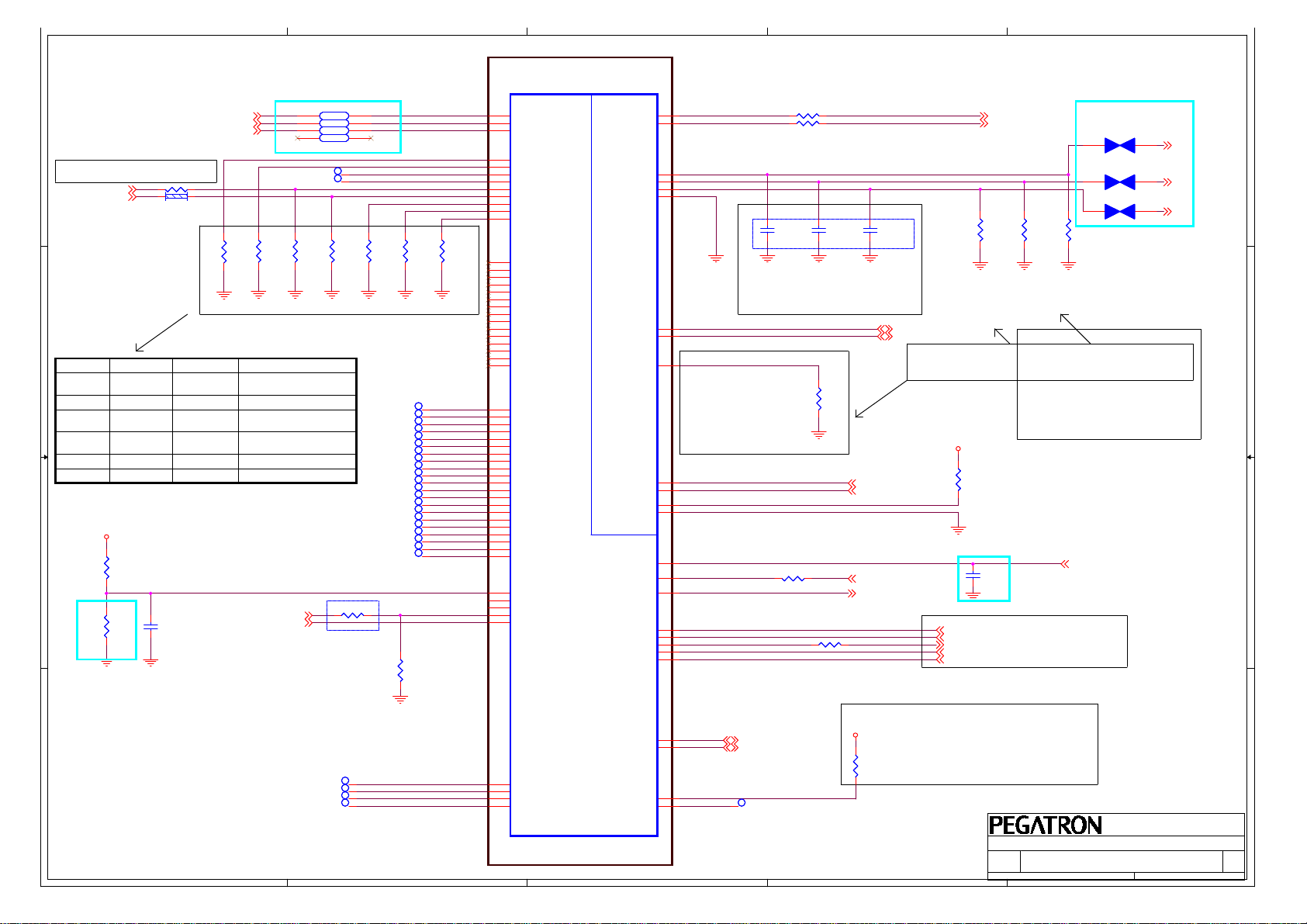

Page 4

5

A

ATX12V

NCP5392MNR2G

3Phases

D D

ATXPWR

S0

VCORE_EN

I max.=75A.

TDC: 60A.

TDP:65W.(6)

4

VCORE

I max.=75A.

TDC: 60A.

TDP:65W.(6)

3

2

1

+5VSB

C C

+5V

+3VSBSW (S3)

+12V

B B

+3.3V

APM9932CKC

S0/S3/S5

APM9932CKC

S0/S3/S5

AOD452*2

S3/S5:+5VS B

S0/S3

APW7120+AOD452*2

e

e

g

g

+5V_DUAL_USB_R

+5V_DUAL_USB_F

LIN REG,1085

S0/S3/S5

+5V_DUAL

r

r

t

t

a

a

+1P1V_CORE

o

o

Io: 9A

Io: 3A

Io: 3A

+3P3VSB

Switch

APW7120KE_TRL

S0/S1/S3

n

n

Io: 1.5A

o

o

C

C

+1P5V_DUAL

Io

f

f

S0/S1: 12A

n

n

i

i

d

d

VTT_SELEC T

+12V

a

a

i

i

t

t

n

n

e

e

Io: 6.0A

+1P5V_DUAL

LM358 +

FDU8780_F071

S0

AOD472

S0

RT9045GSP +0P75V_VTT_DDR

S0

Io: 1.5A

+1P1V_FSB_VTT

Io: 1.5A

+1P5_ICH

Io

S0:1A

l

l

P

P

NOTE:

Linear REG

Switch REG

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

Power Flow

Power Flow

Power Flow

Ttepic Zhu

Ttepic Zhu

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPX41-D3

IPX41-D3

IPX41-D3

Engineer:

Ttepic Zhu

4 54Thursday, December 10, 2009

4 54Thursday, December 10, 2009

4 54Thursday, December 10, 2009

1.02

1.02

1.02

A

Rev

Rev

Rev

Page 5

5

A

4

3

2

1

200/266/333 MHz

ICS

SLG8XP548T

D D

14.318 MHz

XTAL

C C

200/266/333 MHz

100 MHz

96 MHz

100 MHz

100 MHz

33 MHz

14.318 MHz

CK_FSB_CPU/#

CK_FSB_NB/#

CK_96M_DREF/#

CK_100M_PCIEX16/#100 MHz

CK_100M_ICH/#

CK_100M_SATA/#

CK_48M_USB48 MHz

CK_33M_ICH

CK_14M_ICH

CK_33M_SIO33 MHz

C

C

CPU

MCH

EagleLake

PCIEX16

ICH7

o

o

Super I/O

n

n

f

f

i

i

d

d

e

e

n

n

t

t

i

i

a

a

l

l

n

o

o

n

CK_PCIE_SLOT1/#100 MHz

CK_100M_LAN/#

PCIEX1_1

LAN

<Variant Name>

<Variant Name>

<Variant Name>

Clock Distribution

Clock Distribution

Clock Distribution

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPX41-D3

IPX41-D3

IPX41-D3

Engineer:

Ttepic Zhu

Ttepic Zhu

Ttepic Zhu

B B

r

r

t

t

a

a

g

g

e

e

P

P

100 MHz

A

Rev

Rev

Rev

1.02

1.02

5 54Thursday, December 10, 2009

5 54Thursday, December 10, 2009

5 54Thursday, December 10, 2009

1.02

Page 6

5

+3P3V

CKL1 600O hm/100Mhz/0.5A

mx_l0603CKL1 600O hm/100Mhz/0.5A

mx_l0603

NI

NI

+3P3VSB

CKL2 600O hm/100Mhz/0.5A

I

D D

C C

B B

A A

I

PCB40

PCB40

PCB

PCB

PCB_BOA RD

PCB_BOA RD

I

I

21

mx_l0603CKL2 600O hm/100Mhz/0.5A

mx_l0603

21

2009.08.04 shawn

Clock gen power change to +3P3VSB for WOL function.

+CLKVCC3

VRMPW RGD_ICH[22]

SMB_CLK _S[17,18,22,2 4,25]

SMB_DAT A_S[17,18,22,2 4,25]

5

+CLKVCC3

12

I

I

CKCB2

CKCB2

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

NOTE:

CKR2 CKR10

2009.08.04 shawn

CKCB19 removed.

12

12

NI

NI

I

I

CKCB11

CKCB11

CKCB12

CKCB12

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

X5R 10%

X5R 10%

X5R 10%

X5R 10%

mx_c0805

mx_c0805

mx_c0805

mx_c0805

GND GND

GND

GND

2009.08.04 shawn

LR24 0ohm VP removed.

e

e

P

P

12

12

GND

NI

NI

CKC10

CKC10

33PF/50V

33PF/50V

NPO 5%

NPO 5%

GND

NI

NI

CKC11

CKC11

33PF/50V

33PF/50V

NPO 5%

NPO 5%

4

12

12

GND

PIN17 PIN18

25MHz

12

I

I

CKCB13

CKCB13

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

NI

NI

CKCB17

CKCB17

4.7UF/6.3 V

4.7UF/6.3 V

X5R 10%

X5R 10%

mx_c0805

mx_c0805

2009.08.04 shawn

LR19 0ohm VP removed.

g

g

12

I

I

CKC8

CKC8

33PF/50V

33PF/50V

NPO 5%

NPO 5%

GND GND GND

I

I

CKCB3

CKCB3

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

GND

1 2

1 2

4

I

I

CKCB4

CKCB4

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

25MHzNI I

12

I

I

CKCB9

CKCB9

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

I

I

CKCB14

CKCB14

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

I

I

CKCB18

CKCB18

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

a

a

I

I

Y1

Y1

14.318Mh z

14.318Mh z

GND

GND

3

3

12

I

I

CKCB5

CKCB5

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

+CLKVCC3

GND

12

I

I

CKCB15

CKCB15

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GNDGND

VDD48_BW

r

r

t

t

CLK_PW RGD

OSC_CK14 M_XTALIN

OSC_CK14 M_XTALOUT

12

I

I

CKC9

CKC9

33PF/50V

33PF/50V

NPO 5%

NPO 5%

VDDPCI

VDD_PL L3

VDD_SRC

VDDCPU

VDDREF

12

I

I

CKR2

CKR2

10K

10K

VOUT_VDDI O

VDD_IO_9 6

+VDD_IO

12

I

I

CKCB16

CKCB16

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

o

o

GND

12

GNDGND

I

I

CKCB6

CKCB6

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

GND

IIII

IIII

CKU2

CKU2

CKU2

CKU2

CKU2CKU2

CKU2CKU2

2

VDD_PCI

16

VDD_PLL3

31

VDD_SRC

47

VDD_CPU

53

VDD_REF

8

VSS_PCI

23

VSS_SRC1

34

VSS_SRC2

44

VSS_CPU

50

VSS_REF

40

SEL_24.576MHz

12

VDD_I/O_3.3

20

VDD_PLL3_I/O

26

VDD_SRC_I/O1

37

VDD_SRC_I/O2

41

VDD_CPU_I/O

19

VSS_PLL3

15

VSS_I/O

n

n

9

VDD_48

11

VSS_48

48

CKPWRGD/PD#

52

XTAL_IN

51

XTAL_OUT

56

SCL

55

SDA

CLOCK Gen. IN06

CLOCK Gen. IN06

C

C

3

CPU_0

CPU_0#

CPU_1_AMT

CPU_1_AMT#

SRC_8/CPU_ITP

SRC_8#/CPU_ITP#

SRC_7

SRC_7#

SRC_6

SRC_6#

PCI_STOP#/SRC_5

CPU_STOP#SRC_5#

SRC_4

SRC_4#

SRC_3

SRC_3#

SRC_2

SRC_2#

25MHz_0_F

25MHz_1/24.576MHz

SRC_0/DOT_96

SRC_0#/DOT_96#

ITP_EN/PCI_5

PCI_4/SRC_5_EN

PCI_3

PCI_2

PCI_1

PCI_0

o

o

FS_A/48MHz_0

FS_B/TEST_MODE

REF/FS_C/TEST_SEL

3

RCPUHC LK

46

RCPUHC LK#

45

RMCHHCL K

43

RMCHHC LK#

42

39

38

RCK_100M_ ICH

36

RCK_100M _ICH#

35

RCK_10 0M_PE16

33

RCK_100 M_PE16#

32

RCK_100 M_PE1

30

RCK_10 0M_PE1#

29

RCK_100M _MCH

27

RCK_100 M_MCH#

28

RCK_100 M_LAN

24

RCK_10 0M_LAN#

25

RCK_100 M_SATA

21

RCK_100 M_SATA#

22

R_LAN_2 5M

17

18

RCK_96M_ DREF

13

RCK_96M _DREF#

14

PCIF5/ITP_EN(Pin7):

1: CPU_ITP

PCI4/SRC5_EN(Pin6):

1: SRC5 Output

PCI_5

7

CK_33M_P CI4

6

RCK_33M_ SIO

5

RCK_33M _DBG

4

RCK_33M_ ICH

f

n

n

RCK_48M _USB

FSLB

RCK_14M_ ICH

f

Del CK_48_SIO to FS

CK_48M_U SB

3

1

PCI3/CFG0(Pin5):

Strap for SATA PLL

1: PLL2, SS OFF

PCI2/TME(Pin4):

1: SR enable

10

49

54

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

I

I

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

CKR1 33

CKR1 33

1 2

I

I

0

0

0

0

NOBOM

NOBOM

NOBOM

NOBOM

12

NI

NI

CKR68

CKR68

4.7K

4.7K

i

i

12

NI

NI

CKR64

CKR64

4.7K

4.7K

GND GND GND

+CLKVCC3

12

I

I

CKR67

CKR67

4.7K

4.7K

d

d

12

NI

NI

CKR61

CKR61

4.7K

4.7K

12

NI

NI

CKC12

CKC12

10PF/50V

10PF/50V

NPO 5%

NPO 5%

GND

2

CKR23

CKR23

12

CKR22

CKR22

12

CKR210ICKR210

12

CKR240ICKR240

12

CKR5

CKR5

12

CKR6

CKR6

12

CKR7

CKR7

12

CKR8

CKR8

12

CKR10

CKR10

12

CKR11

CKR11

12

CKR9

CKR9

12

CKR14

CKR14

12

CKR12

CKR12

12

CKR13

CKR13

12

CKR20

CKR20

12

CKR19

CKR19

12

t

CKR25

CKR25

12

CKR26

CKR26

12

12

e

e

I

I

CKR66

CKR66

4.7K

4.7K

12

NI

NI

CKR60

CKR60

4.7K

4.7K

2009.08.04 shawn

Add CKR41 for SIO CK_48M_SIO clock.

CKR40, CKR41 change to 22ohm.

I

I

I

I

CKR39 33

CKR39 33

I

I

NOTE:

Single End damping resistor

Single Load => 33 OHM

Double Load => 22 OHM

2

t

n

n

12

NI

NI

CKC5

CKC5

10PF/50V

10PF/50V

NPO 5%

NPO 5%

GND

CKR41 22 OHM 5%

CKR41 22 OHM 5%

1 2

CKR40 22 OHM 5%

CKR40 22 OHM 5%

1 2

1 2

1

CPUHCLK [7]

CPUHCLK # [7]

MCHHCL K [10]

MCHHCL K# [10]

CK_100M_ ICH [20]

CK_100M_ ICH# [20]

CK_100M _PE16 [25]

CK_100M _PE16# [25]

CK_100M _PE1 [24]

CK_100M _PE1# [24]

CK_100M _MCH [10]

CK_100M_ MCH# [10]

CK_100M _SATA [21]

CK_100M _SATA# [21]

i

i

CK_96M_ DREF [ 13]

CK_96M_ DREF# [13]

l

l

CK_100M _LAN [34]

CK_100M _LAN# [34]

a

a

CK_25M _LAN [34]

1 2

I

1 2

I

1 2

I

1 2

NI

2009.08.13 shawn

CKC6 removed.

AR72 1KIAR72 1K

I

1 2

AR27 1KIAR27 1K

I

1 2

AR28 1KIAR28 1K

I

1 2

PEGATRON DT-MB RESTRICTED SECRET

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

2009.08.04 shawn

CKR1 form NI change to I for LAN 25M clock.

NOTE:

PCIF_5 is dedicated for ICH

PCI4 is for the shortest route

PCI3 is for the longest route

SR5833ISR5833

SR5933ISR5933

SR5733ISR5733

SR6033NISR6033

12

NI

NI

CKC3

CKC3

10PF/50V

10PF/50V

NPO 5%

NPO 5%

GND GND

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPX41-D3

IPX41-D3

IPX41-D3

GND

12

NI

NI

CKC4

CKC4

10PF/50V

10PF/50V

NPO 5%

NPO 5%

12

NI

NI

CKC13

CKC13

10PF/50V

10PF/50V

NPO 5%

NPO 5%

1

CK_33M_SI O [39]

CK_33M_T PM [43 ]

CK_33M_IC H [20]

CK_33M_D EBUG [43]

CLOCK CK505

CLOCK CK505

CLOCK CK505

Ttepic Zhu

Ttepic Zhu

Ttepic Zhu

FSBSEL0 [ 8,13]

CK_48M_SI O [39]

CK_48M_U SB [20]

FSBSEL1 [ 8,13]

CK_14M_IC H [22]

FSBSEL2 [ 8,13]

6 54Thursday, December 10, 2009

6 54Thursday, December 10, 2009

6 54Thursday, December 10, 2009

Rev

Rev

Rev

1.02

1.02

1.02

Page 7

5

I

I

XU1A

XU1A

SOCKET77 5/ATX

HA#[3..35][10]

HA#3

HA#4

HA#5

HA#6

D D

HREQ#[0..4][10]

HADSTB0#[10]

HT2

HT2

HT7

HT7

NOBOM

NOBOM

NOBOM

NOBOM

C C

B B

A A

NOBOM

NOBOM

NOBOM

NOBOM

HRS#[0..2][10]

CPURES ET#[10]

HA#[3..35][10]

TPC26b

TPC26b

TPC26b

TPC26b

HADSTB1#[10]

TPC26b

TPC26b

TPC26b

TPC26b

CPUHCLK[6]

CPUHCLK #[6]

HT12

HT12

HT13

HT13

1

1

1

1

5

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15 CPU_TP _AD3

HA#16

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

CPU_TP_ N4

CPU_TP_ P5

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35

CPU_TP _AC4

CPU_TP _AE4

HRS#2

HRS#1

HRS#0

+VTT_O UT_R

12

I

I

HR13

HR13

62

62

12

NI

NI

HC1

HC1

22PF/50V

22PF/50V

NPO 5%

NPO 5%

GND

SOCKET77 5/ATX

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

N4

RSVD1

P5

RSVD2

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

AD5

ADSTB1#

AC4

RSVD3

AE4

RSVD4

A3

RS2#

F5

RS1#

B3

RS0#

F28

BCLK0

G28

BCLK1

G23

RESET#

P

P

REV=1.3

REV=1.3

e

e

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

MCERR#

AP0#

AP1#

DP0#

DP1#

DP2#

DP3#

BR0#

GTLREF1

GTLREF0

GTLREF2

GTLREF3

g

g

FC10

FC15

4

+1P1V_FS B_VTT

12

I

I

HR1

HR1

62

62

D2

C2

D4

CPU_TP_ H4

H4

G8

B2

C1

E4

HIERR#

AB2

P3

C3

E3

AD3

G7

CPU_TP _AB3

AB3

CPU_TP_ U2

U2

CPU_TP_ U3

U3

CPU_TP_J 16

J16

CPU_TP _H15

H15

CPU_TP _H16

H16

CPU_TP_J 17

J17

F3

H2

CPU_GTL REF0

H1

1 2

F2

G10

a

a

CPU_MC H_GTLREF

E24

CPU_GTL REF_SEL

H29

12

NI

NI

HCB5

HCB5

220PF/5 0V

220PF/5 0V

X7R 10%

X7R 10%

GND

4

RMA1

RMA1

NOBOM

NOBOM

SMD4X25_ NP

SMD4X25_ NP

RMA1 is soldermask on trace for RMA

1

purpose. Place on suitable location where

1

can be easily reached by Probe

HADS# [10]

HBNR# [10]

HIT# [10]

HBPRI# [10]

HDBSY# [10]

HDRDY# [10]

HITM# [10]

HINIT# [21]

HLOCK# [10]

HTRDY# [10]

HDEFER# [10]

HT9

HT9

HT10

HT10

1

NOBOM

NOBOM

1

NOBOM

NOBOM

TPC26b

TPC26b

HT11

HT11

TPC26b

TPC26b

HT5

HT5

1

NOBOM

NOBOM

HT6

HT6

1

NOBOM

NOBOM

TPC26b

TPC26b

HT1

HT1

1

NOBOM

NOBOM

TPC26b

TPC26b

1

NOBOM

NOBOM

TPC26b

TPC26b

TPC26b

TPC26b

I

I

HR5

HR5

10

12

NI

NI

HCB2

HCB2

220PF/5 0V

220PF/5 0V

X7R 10%

X7R 10%

o

o

HT39

HT39

1

HT14

HT14

TPC26b

TPC26b

1

TPC26b

TPC26b

10

I

I

HR6

HR6

10

10

n

n

NOBOM

NOBOM

NOBOM

NOBOM

12

12

CPU_GTL REF1

12

NI

NI

HCB1

HCB1

220PF/5 0V

220PF/5 0V

X7R 10%

X7R 10%

GND GND GNDGND

NOTE:

Place near CPU

NJP11

NJP11

NJP10

NJP10

SHORTPIN _RECT

SHORTPIN _RECT

SHORTPIN _RECT

SHORTPIN _RECT

NOBOM

NOBOM

NOBOM

NOBOM

1 2

r

r

t

t

+VTT_O UT_L

12

I

I

HR2

HR2

62

62

CPU_GTL REF1_R

CPU_GTL REF0_R

12

I

I

HCB3

HCB3

1UF/10V

1UF/10V

mx_c0603

mx_c0603

3

HT8

HT8

1

NOBOM

NOBOM

TPC26b

TPC26b

HT3

HT3

1

NOBOM

NOBOM

TPC26b

TPC26b

HT4

HT4

1

NOBOM

NOBOM

TPC26b

TPC26b

HBREQ0# [10]

+VTT_O UT_L

12

12

12

I

I

HCB4

HCB4

1UF/10V

1UF/10V

mx_c0603

mx_c0603

C

C

3

+VTT_O UT_L

12

I

I

HR4

HR4

57.6

57.6

1%

1%

12

I

I

HR8

HR8

100

100

1%

1%

o

o

GNDGND

HD#[0..63][10]

I

I

2009.08.04 shawn

HR3

HR3

HR3 from 49.9ohm change to 57.6ohm

57.6

57.6

1%

1%

n

n

I

I

HR7

HR7

100

100

1%

1%

i

i

HD#[0..63][10] HD#[0..63] [10]

f

f

HDBI0#[10]

HDSTBN0 #[10]

HDSTBP0#[10]

d

d

HDBI1#[10]

HDSTBN1 #[10]

HDSTBP1#[10]

2

I

I

XU1B

XU1B

SOCKET77 5/ATX

SOCKET77 5/ATX

HD#0

B4

A10

A11

B10

C11

B12

C12

D11

E10

D10

F11

F12

D13

E13

G13

F14

G14

F15

G15

G11

G12

E12

C5

A4

C6

A5

B6

B7

A7

D8

A8

C8

B9

G9

F8

F9

E9

D7

D00#

D01#

D02#

D03#

D04#

D05#

D06#

D07#

D08#

D09#

D10#

D11#

D12#

D13#

D14#

D15#

DBI0#

a

a

i

i

t

t

DSTBN0#

DSTBP0#

D16#

D17#

D18#

D19#

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DBI1#

DSTBN1#

DSTBP1#

REV=1.3

REV=1.3

NOTE:

ICH_GPIOA

PEGATRON DT-MB RESTRICTED SECRET

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7 HD#39

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

n

n

e

e

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

2

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

l

l

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

Default is 0.63*VTT

ICH_GPIOB

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

0

10

01

11

1

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

GTLREF

0.615*VTT0

0.63*VTT

0.65*VTT

0.67*VTT

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPX41-D3

IPX41-D3

IPX41-D3

1

HD#[0..63] [10]

HDBI2# [10]

HDSTBN2 # [10]

HDSTBP2# [10]

HDBI3# [10]

HDSTBN3 # [10]

HDSTBP3# [10]

COMMENTS

HQ1 off, HQ2 on

HQ3 off, HQ4 on

HQ1 off, HQ2 on

HQ3 on, HQ4 off

HQ1 on, HQ2 off

HQ3 off, HQ4 on

HQ1 on, HQ2 off

HQ3 on, HQ4 off

INTEL LGA-775 1 - 3

INTEL LGA-775 1 - 3

INTEL LGA-775 1 - 3

Ttepic Zhu

Ttepic Zhu

Ttepic Zhu

7 54Thursday, December 10, 2009

7 54Thursday, December 10, 2009

7 54Thursday, December 10, 2009

Rev

Rev

Rev

1.02

1.02

1.02

Page 8

5

PLACE NEAR SB

+1P1V_FS B_VTT

PLACE COMPONENTS AS CLOSE AS

POSSIBLE TO CPU SOCKET. THE

TRACE WIDTH TO CAPS MUST BE

NO SMALLER THAN 12 MIL.

D D

C C

+VTT_O UT_R

RCVID[0..7][46]

B B

VID_SELEC T[46]

VCC_MB _SENSE[46]

VSS_MB_S ENSE[46]

+VCORE

A A

SMI#[21]

A20M#[21]

HFERR#[21]

INTR[21]

NMI[21]

IGNNE#[21]

STPCLK#[21]

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOTE:

The VCCIO PLL Filter Circuit is no longer

needed since Conroe CPU

HRN2C

680

680

680

680

680

680

680

680

680

680

680

680

680

680

680

680

NOBOM

NOBOM

NOBOM

NOBOM

HRN2C

HRN1A

HRN1A

HRN1D

HRN1D

HRN2D

HRN2D

HRN2A

HRN2A

HRN2B

HRN2B

HRN1B

HRN1B

HRN1C

HRN1C

HT32

HT32

TPC26b

TPC26b

5

GND

5 6

I

I

1 2

I

I

7 8

I

I

7 8

I

I

1 2

I

I

3 4

I

I

3 4

I

I

5 6

I

I

TRD_CPU _P[39]

TRD_CPU _N[39]

HT31

HT31

TPC26b

TPC26b

1

1

12

I

I

HR17

HR17

62

62

HT42

HT42

TPC26b

TPC26b

HT43

HT43

1

TPC26b

TPC26b

HT44

HT44

1

TPC26b

TPC26b

VCC_SEN _AN3

VSS_SEN _AN4

HT42

1

HT43

HT44

RCVID0

RCVID1

RCVID2

RCVID3

RCVID4

RCVID5

RCVID6

RCVID7

GND

GND

P

P

I

I

XU1C

XU1C

SOCKET77 5/ATX

SOCKET77 5/ATX

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

C23

VCCIOPLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

VID6

AM7

VID7

AN7

VID_SECECT

AE8

SKTOCC#

AL1

THERMDA

AK1

THERMDC

AJ7

VSS_AJ7

AH7

VSS_AH7

AN5

VCC_MB_REGULATION

AN6

e

e

VSS_MB_REGULATION

AN3

VCC_SENSE

AN4

VSS_SENSE

AL8

VCC_D_SENSE

AL7

VSS_D_SENSE

4

( CPU_SLP )

BOOTSELECT

g

g

REV=1.3

REV=1.3

4

If NOT support C3/ C4, these 4 signals

Note:

can be NC with a PU resistor

Install HR24 for pin: L2

PM_SLP#

DPSLP#

Install HR22 for pin: P1

CPU_PSI

Install HR36 for pin: Y3

DPRSTP#

Install HR37 for pin: T2

TESTHI0

F26

TESTHI00

TESTHI01

TESTHI10

TESTHI11

TESTHI13

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

TESTHI08

TESTHI09

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

COMP8

TESTHI12

RSVD33

RSVD34

RSVD35

RSVD36

RSVD12

RSVD21

RSVD9

MSID0

MSID1

LL_ID1

LL_ID0

PECI

IMPSEL

a

a

FORCEPR#

PWRGOOD

PROCHOT#

THERMTRIP#

TESTHI1

W3

TESTHI10

H5

TESTHI11

P1

TESTHI13

L2

TESTHI2_7

F25

G25

G27

G26

G24

F24

TESTHI8

G3

TESTHI9

G4

HCOMP0

A13

HCOMP1

T1

HCOMP2

G2

HCOMP3

R1

HCOMP4

J2

HCOMP5

T2

Y3

HCOMP7

AE3

HCOMP8

B13

TESTHI12

W2

HR48

HR48

NI

NI

CPU_RSV D33

G1

CPU_TP_R C2

CPU_TP_R C2

U1

CPU_TP_R C3

A24

CPU_TP_R C4

E29

CPU_TP _AH2

AH2

CPU_TP_ G6

G6

CPU_TP _F29

F29

MSID0

W1

MSID1

V1

CPU_LL_ID 1

AA2

CPU_LL_ID 0

V2

CPU_BOO T

Y1

VRDSEL

AL3

o

NC

t

t

o

G5

r

r

IMPSEL_F 6

F6

AK6

N1

AL2

M2

THERMALTRIP# NEED A PULL UP RESISTOR NEAR SB

HR41 51

HR41 51

I

I

HR19 51

HR19 51

I

I

HR20 51

HR20 51

I

I

HR22 51

HR22 51

I

I

HR24 51

HR24 51

I

I

HR23 51

HR23 51

I

I

HR25 51

HR25 51

I

I

HR44 51

HR44 51

I

I

HR49 49.9 1%

HR49 49.9 1%

I

I

HR46 49.9 1%

HR46 49.9 1%

I

I

HR28 49.9 1%

HR28 49.9 1%

I

I

HR33 49.9 1%

HR33 49.9 1%

I

I

HR32 49.9 1%

HR32 49.9 1%

NI

NI

HR37 49.9 1%

HR37 49.9 1%

I

I

HR36 49.9 1%

HR36 49.9 1%

I

I

HR47 49.9 1%

HR47 49.9 1%

NI

NI

HR39 24.9 1%

HR39 24.9 1%

I

I

HR21 51

HR21 51

I

I

0

0

12

HR54 51

HR54 51

I

I

1

1

TPC26b

TPC26b

1

TPC26b

TPC26b

1

TPC26b

TPC26b

1

TPC26b

TPC26b

1

TPC26b

TPC26b

TPC26b

TPC26b

+VTT_O UT_L

12

NI

NI

HR53

HR53

62

62

n

n

12

I

I

HR56

HR56

51

51

GND

3

+1P1V_FS B_VTT

12

12

12

12

12

12

1 2

1 2

CPU_PSI [46]

1 2

1 2

1 2

1 2

12

12

12

12

1 2

12

12

HT21

HT21

HT15

HT15

NOBOM

NOBOM

HT22

HT22

NOBOM

NOBOM

HT16

HT16

NOBOM

NOBOM

HT24

HT24

NOBOM

NOBOM

HT25

HT25

NOBOM

NOBOM

NOBOM

NOBOM

HR641K

HR641K

1 2

12

NI

NI

HR50

HR50

51

51

GND

HT29

HT29

1

NOBOM

NOBOM

TPC26b

TPC26b

HT30

HT30

1

NOBOM

NOBOM

TPC26b

TPC26b

PECI [39]

+VTT_O UT_R +VTT_OUT _L +V TT_OUT_R

12

I

I

HR61

HR61

130

130

1%

1%

+VTT_O UT_L

GND

NI

NI

GND

12

NI

NI

HR51

HR51

o

o

51

51

C

C

GND

12

GND

12

12

NI

NI

HR62

HR62

100

100

12

NI

NI

HCB16

HCB16

0.1UF/16V

0.1UF/16V

GND

3

+VTT_O UT_L

I

I

HR55

HR55

51

51

I

I

HR63

HR63

130

130

1%

1%

+VTT_O UT_R

I

I

I

I

I

I

+VTT_O UT_R

I

I

I

I

I

SYS_RESE T#[22,39,42]

f

f

1 2

VRM_PW RGD[22,46]

FSBSEL0[6, 13]

FSBSEL1[6, 13]

FSBSEL2[6, 13]

HFORCE PH# [48]

CPUPW RGD [22]

PROCHO T# [48]

H_THMTR IP# [21]

I

I

I

I

I

I

I

+1P1V_FS B_VTT

+VTT_O UT_R

+VTT_O UT_L

HR60 5 1

HR60 5 1

I

I

n

n

BOOTSELECT:

Install PD resistor to

prevent PSC SMF CDM PSL

CPU from booting

HR18 49.9 1%

HR18 49.9 1%

1 2

HR43 49.9 1%

HR43 49.9 1%

1 2

HR42 49.9 1%

HR42 49.9 1%

1 2

12

I

I

HR26

HR26

49.9

49.9

1%

1%

GND

HR30 51

HR30 51

1 2

HR29 51

HR29 51

1 2

HR31 51

HR31 51

1 2

HR34 51

HR34 51

1 2

HR35 51

HR35 51

1 2

HR38 51

HR38 51

1 2

e

e

d

NOBOM

NOBOM

i

i

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

d

HT23

HT23

HT17

HT17

TPC26b

TPC26b

TPC26b

TPC26b

HT18

HT18

HT19

HT19

TPC26b

TPC26b

HT26

HT26

HT20

HT20

TPC26b

TPC26b

HT27

HT27

TPC26b

TPC26b

HT28

HT28

TPC26b

TPC26b

TPC26b

TPC26b

TPC26b

TPC26b

HR57 470 1%

HR57 470 1%

1 2

I

I

HR59 470 1%

HR59 470 1%

1 2

I

I

HR58 470 1%

HR58 470 1%

1 2

I

I

2009.08.14 shawn

HR57, HR58, HR59 from 470 5% change to 470 1%.

2

I

I

XU1D

XU1D

SOCKET77 5/ATX

SOCKET77 5/ATX

TCK

AE1

TCK

TDI

AD1

TDI

TDO

AF1

TDO

TMS

AC1

TMS

TRST#

AG1

t

t

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

N5

C9

E7

AE6

D16

A20

E23

AM6

G29

H30

G30

TRST#

i

i

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLK<0>

ITPCLK<1>

RSVD17

RSVD18

RSVD19

RSVD20

RSVD22

RSVD23

RSVD31

VTTPWRGD

BSEL0

BSEL1

BSEL2

a

a

REV=1.3

REV=1.3

12

I

I

HR27

HR27

49.9

49.9

1%

1%

GND

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

n

n

CPU_ITPH CLK

1

CPU_ITPHC LK#

1

CPU_TP_ N5

1

H_BPM1 _2

CPU_TP_ E7

1

CPU_TP _AE6

1

CPU_TP _D16

1

CPU_TP _A20

1

CPU_TP _E23

1

+VTT_O UT_R +1P5V_ICH

12

I

I

HR52

HR52

680

680

12

NI

NI

HC2

HC2

100PF/5 0V

100PF/5 0V

NPO 5%

NPO 5%

GND

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

l

l

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT_OUT1

VTT_OUT2

VCC_PLL

2009.10.22 shawn

+CPU_VCCPLL floating, change power net name to +1P5V_ICH.

VTT_SEL

1

NOTE:

FSB_VTT Net Name changed

+1P1V_FS B_VTT

A29

B25

B29

B30

C29

A26

B27

C28

A25

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

+VTT_O UT_R

AA1

J1

D23

F27

+VTT_O UT_L

12

NI

NI

HCB13

HCB13

0.1UF/16V

0.1UF/16V

GND GND

12

I

I

HCB14

HCB14

0.01UF/25 V

0.01UF/25 V

X7R 10%

X7R 10%

GNDGND

VTT_SE LECT [50]

12

12

PEGATRON DT-MB RESTRICTED SECRET

INTEL LGA-775 2 - 3

INTEL LGA-775 2 - 3

INTEL LGA-775 2 - 3

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

IPX41-D3

IPX41-D3

IPX41-D3

1

Ttepic Zhu

Ttepic Zhu

Ttepic Zhu

8 54Thursday, December 10, 2009

8 54Thursday, December 10, 2009

8 54Thursday, December 10, 2009

NI

NI

HCB12

HCB12

0.1UF/16V

0.1UF/16V

NI

NI

HCB15

HCB15

10UF/6.3V

10UF/6.3V

X5R 10%

X5R 10%

mx_c0805

mx_c0805

Rev

Rev

Rev

1.02

1.02

1.02

Page 9

5

4

3

2

1

+VCORE

D D

I

I

I

XU1E

XU1E

SOCKET77 5/ATX

SOCKET77 5/ATX

AA8

VCC1

AB8

VCC2

AC23

VCC3

AC24

VCC4

AC25

VCC5

AC26

VCC6

AC27

VCC7

AC28

VCC8

AC29

VCC9

AC30

VCC10

AC8

VCC11

AD23

VCC12

AD24

VCC13

AD25

VCC14

AD26

VCC15

AD27

VCC16

AD28

VCC17

AD29

VCC18

AD30

VCC19

AD8

C C

B B

A A

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AE9

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

AF8

AF9

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

AG8

AG9

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

REV=1.3

REV=1.3

VCC112

VCC111

VCC110

VCC109

VCC108

VCC107

VCC106

VCC105

VCC104

VCC103

VCC102

VCC101

VCC100

VCC99

VCC98

VCC97

VCC96

VCC95

VCC94

VCC93

VCC92

VCC91

VCC90

VCC89

VCC88

VCC87

VCC86

VCC85

VCC84

VCC83

VCC82

VCC81

VCC80

VCC79

VCC78

VCC77

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

AM14

AM12

AM11

AL9

AL30

AL29

AL26

AL25

AL22

AL21

AL19

AL18

AL15

AL14

AL12

AL11

AK9

AK8

AK26

AK25

AK22

AK21

AK19

AK18

AK15

AK14

AK12

AK11

AJ9

AJ8

AJ26

AJ25

AJ22

AJ21

AJ19

AJ18

AJ15

AJ14

AJ12

AJ11

AH9

AH8

AH30

AH29

AH28

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

I

XU1F

XU1F

SOCKET77 5/ATX

SOCKET77 5/ATX

AM15

VCC113

AM18

VCC114

AM19

VCC115

AM21

VCC116

AM22

VCC117

AM25

VCC118

AM26

VCC119

AM29

VCC120

AM30

VCC121

AM8

VCC122

AM9

VCC123

AN11

VCC124

AN12

VCC125

AN14

VCC126

AN15

VCC127

AN18

VCC128

AN19

VCC129

AN21

VCC130

AN22

VCC131

AN25

VCC132

AN26

VCC133

AN29

VCC134

AN30

VCC135

AN8

VCC136

AN9

VCC137

J10

VCC138

J11

VCC139

J12

VCC140

J13

VCC141

J14

VCC142

J15

VCC143

J18

VCC144

J19

VCC145

J20

VCC146

J21

VCC147

J22

VCC148

J23

VCC149

J24

VCC150

J25

VCC151

J26

VCC152

J27

VCC153

J28

VCC154

J29

VCC155

J30

VCC156

J8

VCC157

J9

VCC158

K30

VCC159

K29

VCC160

K28

VCC161

K27

VCC162

K26

VCC163

K25

VCC164

K24

VCC165

K23

VCC166

K8

VCC167

Y8

VCC168

P

P

REV=1.3

REV=1.3

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

e

e

NOBOM

NOBOM

NOBOM

NOBOM

VCC225

VCC224

VCC223

VCC222

VCC221

VCC220

VCC219

VCC218

VCC217

VCC216

VCC215

VCC214

VCC213

VCC212

VCC211

VCC210

VCC209

VCC208

VCC207

VCC206

VCC205

VCC204

VCC203

VCC202

VCC201

VCC200

VCC199

VCC198

VCC197

VCC196

VCC195

VCC194

VCC193

VCC192

VCC191

VCC190

VCC189

VCC188

VCC187

VCC186

VCC185

VCC184

VCC183

VCC182

VCC181

VCC180

VCC179

VCC178

VCC177

VCC176

VCC175

VCC174

VCC173

VCC172

VCC171

VCC170

VCC169

g

g

L8

M23

M24

M25

M26

M27

M28

M29

M30

M8

N23

N24

N25

N26

N27

N28

N29

N30

N8

P8

R8

T23

T24

T25

T26

T27

T28

T29

T30

T8

U23

U24

U25

U26

U27

U28

U29

U30

U8

V8

W23

W24

W25

W26

W27

W28

W29

W30

W8

Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

a

a

HT33

HT33

HT34

HT34

1

HT35

HT35

1

TPC26b

TPC26b

HT36

HT36

1

TPC26b

TPC26b

HT37

HT37

1

TPC26b

TPC26b

HT38

HT38

1

TPC26b

TPC26b

1

TPC26b

TPC26b

TPC26b

TPC26b

r

r

t

t

CPU_TP_ D1

CPU_TP _D14

CPU_TP_ E5

CPU_TP_ E6

CPU_TP _F23

CPU_TP_ J3

o

o

GND

I

I

XU1G

XU1G

SOCKET77 5/ATX

SOCKET77 5/ATX

AF28

VSS1

AF27

VSS2

AF26

VSS3

AF25

VSS4

AF24

VSS5

AF23

VSS6

AF20

VSS7

AF17

VSS8

AF16

VSS9

AF13

VSS10

AF10

VSS11

AE7

VSS12

AE5

VSS13

AE30

VSS14

AE29

VSS15

AE28

VSS16

AE27

VSS17

AE26

VSS18

AE25

VSS19

AE24

VSS20

AE20

VSS21

AE2

VSS22

AE17

VSS23

AE16

VSS24

AE13

VSS25

AE10

VSS26

AD7

VSS27

AD4

VSS28

AC7

VSS29

AC3

VSS30

AC6

VSS31

AB7

VSS32

AB30

VSS33

AB29

VSS34

AB28

VSS35

AB27

VSS36

AB26

VSS37

AB25

VSS38

AB24

VSS39

AB23

VSS40

AB1

VSS41

AA7

VSS42

AA6

VSS43

AA30

VSS44

AA3

VSS45

AA29

VSS46

AA28

VSS47

AA27

VSS48

AA26

VSS49

AA25

VSS50

A12

VSS51

A15

VSS52

A18

VSS53

A2

VSS54

A21

VSS55

A6

VSS56

A9

VSS57

n

n

AA23

VSS58

AA24

VSS59

AF29

VSS60

D1

RSVD27

D14

RSVD28

E5

RSVD29

E6

RSVD30

F23

RSVD37

J3

RSVD32

C

C

REV=1.3

REV=1.3

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

AF3

AF30

AF6

AF7

AG10

AG13

AG16

AG17

AG20

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

o

o

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AM1

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AM4

AN1

AN10

AN13

AN16

AN17

AN2

AN20

AN23

AN24

AN27

AN28

B1

n

n

GND

f

f

GND

B11

B14

B17

B20

B24

B5

B8

C10

C13

C16

C19

C22

C24

C4

C7

D12

D15

D18

D21

D24

D3

D5

D6

D9

E11

E14

E17

E2

E20

E25

E26

E27

E28

E8

F10

i

i

F13

F16

F19

F22

F4

F7

H10

H11

H12

H13

H14

H17

H18

H19

H20

H21

H22

H23

H24

H25

H26

H27

H28

H3

H6

I

I

XU1H

XU1H

SOCKET77 5/ATX

SOCKET77 5/ATX

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

d

d

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

REV=1.3

REV=1.3

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

e

e

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

Y7

Y5

Y2

W7

W4

V7

V6

V30

V3

V29

V28

V27

V26

V25

V24

V23

U7

T7

T6

T3

R7

R5

R30

R29

R28

n

n

R27

R26

R25

R24

R23

R2

P7

P4

P30

P29

P28

P27

P26

P25

P24

P23

N7

N6

N3

M7

M1

L7

L6

L30

L3

L29

L28

L27

L26

L25

L24

L23

K7

K5

K2

J7

J4

H9

H8

H7

t

t

i

i

GND

a

a

l

l

I

I

XU1I

XU1I

SOCKET77 5/ATX

SOCKET77 5/ATX

1

RM_POST_NC1

2

RM_POST_NC2

3

RM_POST_NC3

4

RM_POST_NC4

REV=1.3

REV=1.3

PEGATRON DT-MB RESTRICTED SECRET

INTEL LGA-775 3 - 3

INTEL LGA-775 3 - 3

INTEL LGA-775 3 - 3

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPX41-D3

IPX41-D3

IPX41-D3

1

Ttepic Zhu

Ttepic Zhu

Ttepic Zhu

9 54Thursday, December 10, 2009

9 54Thursday, December 10, 2009

9 54Thursday, December 10, 2009

Rev

Rev

Rev

1.02

1.02

1.02

Page 10

5

I

I

NU1A

AA35

AA37

AA36

H39

N39

N35

N37

N40

M45

R35

R36

R34

R37

R39

U38

U34

U40

Y36

U35

U37

Y37

Y34

Y38

G38

K35

C43

G39

C39

B39

B40

K31

K25

C32

D32

D30

G44

K44

H45

H40

H37

H42

G43

G42

D27

P30

P29

N25

L36

L37

J38

F40

L38

L43

J41

T36

T37

T34

J39

J40

T39

J31

F33

J25

F26

J42

L40

J43

L42

J44

L44

NU1A

FSB_AB_3

FSB_AB_4

FSB_AB_5

FSB_AB_6

FSB_AB_7

FSB_AB_8

FSB_AB_9

FSB_AB_10

FSB_AB_11

FSB_AB_12

FSB_AB_13

FSB_AB_14

FSB_AB_15

FSB_AB_16

FSB_AB_17

FSB_AB_18

FSB_AB_19

FSB_AB_20

FSB_AB_21

FSB_AB_22

FSB_AB_23

FSB_AB_24

FSB_AB_25

FSB_AB_26

FSB_AB_27

FSB_AB_28

FSB_AB_29

FSB_AB_30

FSB_AB_31

FSB_AB_32

FSB_AB_33

FSB_AB_34

FSB_AB_35

FSB_REQB_0

FSB_REQB_1

FSB_REQB_2

FSB_REQB_3

FSB_REQB_4

FSB_ADSTBB_0

FSB_ADSTBB_1

FSB_DSTBPB_0

FSB_DSTBNB_0

FSB_DINVB_0

FSB_DSTBPB_1

FSB_DSTBNB_1

FSB_DINVB_1

FSB_DSTBPB_2

FSB_DSTBNB_2

FSB_DINVB_2

FSB_DSTBPB_3

FSB_DSTBNB_3

FSB_DINVB_3

FSB_ADSB

FSB_TRDYB

FSB_DRDYB

FSB_DEFERB

FSB_HITMB

FSB_HITB

FSB_LOCKB

FSB_BREQ0B

FSB_BNRB

FSB_BPRIB

FSB_DBSYB

FSB_RSB_0

FSB_RSB_1

FSB_RSB_2

FSB_CPURSTB

P

P

HPL_CLKINN

HPL_CLKINP

RSVD21

EAGLELA KE

EAGLELA KE

FSB

FSB

REV=1.4

REV=1.4

FSB_DB_0

FSB_DB_1

FSB_DB_2

FSB_DB_3

FSB_DB_4

FSB_DB_5

FSB_DB_6

FSB_DB_7

FSB_DB_8

FSB_DB_9

FSB_DB_10

FSB_DB_11

FSB_DB_12

FSB_DB_13

FSB_DB_14

FSB_DB_15

FSB_DB_16

FSB_DB_17

FSB_DB_18

FSB_DB_19

FSB_DB_20

FSB_DB_21

FSB_DB_22

FSB_DB_23

FSB_DB_24

FSB_DB_25

FSB_DB_26

FSB_DB_27

FSB_DB_28

FSB_DB_29

FSB_DB_30

FSB_DB_31

FSB_DB_32

FSB_DB_33

FSB_DB_34

FSB_DB_35

FSB_DB_36

FSB_DB_37

FSB_DB_38

FSB_DB_39

FSB_DB_40

FSB_DB_41

FSB_DB_42

FSB_DB_43

FSB_DB_44

FSB_DB_45

FSB_DB_46

FSB_DB_47

FSB_DB_48

FSB_DB_49

FSB_DB_50

FSB_DB_51

FSB_DB_52

FSB_DB_53

FSB_DB_54

FSB_DB_55

FSB_DB_56

FSB_DB_57

FSB_DB_58

FSB_DB_59

FSB_DB_60

FSB_DB_61

FSB_DB_62

FSB_DB_63

FSB_SWING

FSB_RCOMP

e

e

FSB_DVREF

FSB_ACCVREF

HA#[3..35][ 7] HD#[0..63] [7]

D D

C C

HREQ#[0..4][7]

HADSTB0#[7]

HADSTB1#[7]

HDSTBP0#[7]

HDSTBN0 #[7]

HDBI0#[7]

HDSTBP1#[7]

HDSTBN1 #[7]

HDBI1#[7]

HDSTBP2#[7]

HDSTBN2 #[7]

HDBI2#[7]

HDSTBP3#[7]

HDSTBN3 #[7]

HDBI3#[7]

B B

A A

HRS#[0..2][7]

CPURES ET#[7]

MCHHCL K#[6]

MCHHCL K[6]

NOBOM

NOBOM

HADS#[7]

HTRDY#[7]

HDRDY#[7]

HDEFER#[7]

HITM#[7]

HIT#[7]

HLOCK#[7]

HBREQ0#[7]

HBNR#[7]

HBPRI#[7]

HDBSY#[7]

NT3

NT3

1

TPC26b

TPC26b

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

TP_MCH_ N25

5

4

F44

C44

D44

C41

E43

B43

D40

B42

B38

F38

A38

B37

D38

C37

D37

B36

E37

J35

H35

F37

G37

J33

L33

G33

L31

M31

M30

J30

G31

K30

M29

G30

J29

F29

H29

L25

K26

L29

J26

M26

H26

F25

F24

G25

H24

L24

J24

N24

C28

B31

F35

C35

B35

D35

D31

A34

B32

F31

D28

A29

C30

B30

E27

B28

B24

A23

g

g

C22

B23

4

3

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HXSW ING

HXRCOM P

a

a

MCH_GT LREF0

r

r

t

t

12

I

I

NR5

NR5

16.5

16.5

1%

1%

GND

12

NI

NI

NCB2

NCB2

220PF/5 0V

220PF/5 0V

X7R 10%

X7R 10%

GND GND GND

MCH_GTL REF0 W/S =10/7

MCH_GTL REF0 W/S =10/7

MCH_GTL REF0 W/S =10/7MCH_GTL REF0 W/S =10/7

1

SDVO_CTRL_DATA

1

SDVO CARD PRESENT, PEG DISABLE

0

SDVO DISABLE(DEFAULT)

0

n

n

12

GND

12

HXSW ING_R

I

I

NCB1

NCB1

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

R_MCH_G TLREF0

I

I

NCB3

NCB3

1UF/16V

1UF/16V

X7R 10%

X7R 10%

mx_c0603

mx_c0603

HXSWING W/S=10/ 10

HXSWING W/S=10/ 10

HXSWING W/S=10/ 10HXSWING W/S=10/ 10

HXRCOMP W/S=10/ 7

HXRCOMP W/S=10/ 7

HXRCOMP W/S=10/ 7HXRCOMP W/S=10/ 7

I

I

NR4

NR4

51

51

o

o

12

I

I

NR8

NR8

51

51

12

C

C

+1P1V_FS B_VTT

3

NT43 T PC26b

NT43 T PC26b

NT42 TPC 26b

NT42 TPC 26b

NOBOM

NOBOM

NOBOM

NOBOM

o

o

12

I

I

NR3

NR3

301

301

1%

1%

12

I

I

NR6

NR6

100

100

1%

1%

GND

CK_100M _MCH[6]

CK_100M_ MCH#[ 6]

NOBOM

NOBOM

NOBOM

NOBOM

n

n

+1P1V_FS B_VTT

12

I

I

NR7

NR7

57.6

57.6

1%

1%

12

I

I

NR9

NR9

100

100

1%

1%

TPC26b

TPC26b

TPC26b

TPC26b

EXP_RXP0[25]

EXP_RXN0[25]

EXP_RXP1[25]

EXP_RXN1[25]

EXP_RXP2[25]

EXP_RXN2[25]

EXP_RXP3[25]

EXP_RXN3[25]

EXP_RXP4[25]

EXP_RXN4[25]

EXP_RXP5[25]

EXP_RXN5[25]

EXP_RXP6[25]

EXP_RXN6[25]

EXP_RXP7[28]

EXP_RXN7[28]

EXP_RXP8[25]

EXP_RXN8[25]

EXP_RXP9[25]

EXP_RXN9[25]

EXP_RXP 10[25]

EXP_RXN 10[25]

EXP_RXP 11[25]

EXP_RXN 11[25]

EXP_RXP 12[25]

EXP_RXN 12[25]

EXP_RXP 13[25]

EXP_RXN 13[25]

EXP_RXP 14[25]

EXP_RXN 14[25]

EXP_RXP 15[25]

EXP_RXN 15[25]

DMI_RXP0[20]

DMI_RXN0[20]

DMI_RXP1[20]

DMI_RXN1[20]

DMI_RXP2[20]

DMI_RXN2[20]

DMI_RXP3[20]

DMI_RXN3[20]

NT1

NT1

NT2

NT2

1

1

f

f

TP_SDVO_ DATA

1

TP_SDVO _CLK

1

TP_MCH_ AD13

i

i

D9

E9

J13

G13

AB13

AD13

F6

G7

H6

G4

J6

J7

L6

L7

N9

N10

N7

N6

R7

R6

R9

R10

U10

U9

U6

d

d

U7

AA9

AA10

R4

P4

AA7

AA6

AB10

AB9

AB3

AA2

AD10

AD11

AD7

AD8

AE9

AE10

AE6

AE7

AF9

AF8

2

I

I

NU1B

NU1B

EXP_CLKP

EXP_CLKN

SDVO_CTRLDATA

SDVO_CTRLCLK

RSVD2

RSVD4

PEG_RXP_0

PEG_RXN_0

PEG_RXP_1

PEG_RXN_1

PEG_RXP_2

PEG_RXN_2

PEG_RXP_3

PEG_RXN_3

PEG_RXP_4

PEG_RXN_4

PEG_RXP_5

n

n

PEG_RXN_5

PEG_RXP_6

PEG_RXN_6

PEG_RXP_7

e

e

PEG_RXN_7

PEG_RXP_8

PEG_RXN_8

PEG_RXP_9

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

PEG_RXP_11

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

DMI_RXP_0

DMI_RXN_0

DMI_RXP_1

DMI_RXN_1

DMI_RXP_2

DMI_RXN_2

DMI_RXP_3

DMI_RXN_3

EAGLELA KE

EAGLELA KE

2

SDVO

SDVO

PCIE

PCIE

DMI

DMI

REV=1.4

REV=1.4

EXP_RCOMPO

EXP_COMPI

EXP_ICOMPO

EXP_RBIAS

PEG_TXP_0

PEG_TXN_0

PEG_TXP_1

PEG_TXN_1

PEG_TXP_2

i

i

PEG_TXN_2

PEG_TXP_3

t

t

PEG_TXN_3

PEG_TXP_4

PEG_TXN_4

PEG_TXP_5

PEG_TXN_5

PEG_TXP_6

PEG_TXN_6

PEG_TXP_7

PEG_TXN_7

PEG_TXP_8

PEG_TXN_8

PEG_TXP_9

PEG_TXN_9

PEG_TXP_10

PEG_TXN_10

PEG_TXP_11

PEG_TXN_11

PEG_TXP_12

PEG_TXN_12

PEG_TXP_13

PEG_TXN_13

PEG_TXP_14

PEG_TXN_14

PEG_TXP_15

PEG_TXN_15

DMI_TXP_0

DMI_TXN_0

DMI_TXP_1

DMI_TXN_1

DMI_TXP_2

DMI_TXN_2

DMI_TXP_3

DMI_TXN_3

1

+1P1V_C ORE

12

I

I

NR1

NR1

49.9

49.9

1%

1%

l

l

12

NOTE:

Breakout W/S:10/6

W/S:10/10

I

I

NR2

NR2

750

750

1%

1%

EXP_TX P0 [ 25]

EXP_TX N0 [25]

EXP_TX P1 [ 25]

EXP_TX N1 [25]

EXP_TX P2 [ 25]

EXP_TX N2 [25]

EXP_TX P3 [ 25]

EXP_TX N3 [25]

EXP_TX P4 [ 28]

EXP_TX N4 [28]

EXP_TX P5 [ 28]

EXP_TX N5 [28]

EXP_TX P6 [ 28]

EXP_TX N6 [28]

EXP_TX P7 [ 28]

EXP_TX N7 [28]

EXP_TX P8 [ 25]

EXP_TX N8 [25]

EXP_TX P9 [ 25]

EXP_TX N9 [25]

EXP_TXP 10 [25]

EXP_TXN 10 [25]

EXP_TXP 11 [25]

EXP_TXN 11 [25]

EXP_TXP 12 [25]

EXP_TXN 12 [25]

EXP_TXP 13 [25]

EXP_TXN 13 [25]

EXP_TXP 14 [25]

EXP_TXN 14 [25]

EXP_TXP 15 [25]

EXP_TXN 15 [25]

DMI_TXP0 [20]

DMI_TXN0 [20]

DMI_TXP1 [20]

DMI_TXN1 [20]

DMI_TXP2 [20]

DMI_TXN2 [20]

DMI_TXP3 [20]

DMI_TXN3 [20]

EXP_RCO MP

Y7

Y8

Y6

EXP_RBIA STP_MCH_ AB13

AG1

GND

C11

B11

A10

a

a

B9

C9

D8

B8

C7

B7

B6

B3

B4

D2

C2

H2

G2

J2

K2

K1

L2

P2

M2

T2

R1

U2

V2

W4

V3

AA4

Y4

AC1

AB2

NOTE:

Check Eaglelake PDG for detai if wanna

support Integrated HDMI/DVI/DP

AC2

AD2

AD4

AE4

AE2

AF2

AF4

AG4

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

EAGLELAKE 1- 7

EAGLELAKE 1- 7

EAGLELAKE 1- 7

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Pr oject Name

Size Pr oject Name

Size Pr oject Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPX41-D3

IPX41-D3

IPX41-D3

1

Ttepic Zhu

Ttepic Zhu

Ttepic Zhu

10 54Thursday, December 10, 2009

10 54Thursday, December 10, 2009

10 54Thursday, December 10, 2009

Rev

Rev

Rev

1.02

1.02

1.02

Page 11

5

M_CHA_MAA [1..14][17]

D D

M_CHA_C AS#[17]

M_CHA_R AS#[17]

M_CHA_B A0[17]

M_CHA_B A1[17]

M_CHA_B A2[17]

M_CHA_C S#0[1 7]

NOBOM

NOBOM

M_CHA_C KE0[17]

M_CHA_C KE1[17]

M_CHA_O DT0[17]

M_CHA_O DT1[17]

NOBOM

C C

B B

P

P

A A

5

NOBOM

M_CHA_C LK0[1 7]

M_CHA_C LK0#[17]

M_CHA_C LK2[1 7]

M_CHA_C LK2#[17]

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

e

e

4

HT49

HT49

1

HT48

HT48

1

HT45

HT45

1

HT47

HT47

1

HT46

HT46

1

HT40

HT40

1

HT41

HT41

1

g

g

4

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

N27146 510

N27146 424

N27146 426

N27146 514

N27146 515

N27146 428

N27146 516

a

a

t

t

r

r

I

I

NU1C

NU1C

BC41

DDR_A_MA_0

BC35

DDR_A_MA_1

BB32

DDR_A_MA_2

BC32

DDR_A_MA_3

BD32

DDR_A_MA_4

BB31

DDR_A_MA_5

AY31

DDR_A_MA_6

BA31

DDR_A_MA_7

BD31

DDR_A_MA_8

BD30

DDR_A_MA_9

AW43

DDR_A_MA_10

BC30

DDR_A_MA_11

BB30

DDR_A_MA_12

AM42

DDR_A_MA_13

BD28

DDR_A_MA_14

AW42

DDR_A_WEB

AU42

DDR_A_CASB

AV42

DDR_A_RASB

AV45

DDR_A_BS_0

AY44

DDR_A_BS_1

BC28

DDR_A_BS_2

AU43

DDR_A_CSB_0

AR40

DDR_A_CSB_1

AU44

DDR_A_CSB_2

AM43

DDR_A_CSB_3

BB27

DDR_A_CKE_0

BD27

DDR_A_CKE_1

BA27

DDR_A_CKE_2

AY26

DDR_A_CKE_3

AR42

DDR_A_ODT_0

AM44

DDR_A_ODT_1

AR44

DDR_A_ODT_2

AL40

DDR_A_ODT_3

AY37

DDR_A_CK_0

BA37

DDR_A_CKB_0

AW29

DDR_A_CK_1

AY29

DDR_A_CKB_1

AU37

DDR_A_CK_2

AV37

DDR_A_CKB_2

AU33

DDR_A_CK_3

AT33

DDR_A_CKB_3

AT30

DDR_A_CK_4

AR30

DDR_A_CKB_4

AW38

DDR_A_CK_5

AY38

DDR_A_CKB_5

o

o

EAGLELA KE

EAGLELA KE

DDR_A

DDR_A

n

n

REV=1.4

REV=1.4

DDR_A_DQS_0

DDR_A_DQSB_0

DDR_A_DM_0

DDR_A_DQ_0

DDR_A_DQ_1

DDR_A_DQ_2

DDR_A_DQ_3

DDR_A_DQ_4

DDR_A_DQ_5