Page 1

Vinafix.com

5

4

3

2

1

IPPLP-RH

PAGE

01

02

03

D D

04

05

06

07

08~13

14

15~16

17

18

19~24

25

26

27

28

29

C C

30

31

32

33

34

35

36

37

38

39

40

41

42

43

B B

44

45

46

47

48

49

50

51~52

53

54

55

56

57

58

A A

59

60

61

62

63

64~66

67

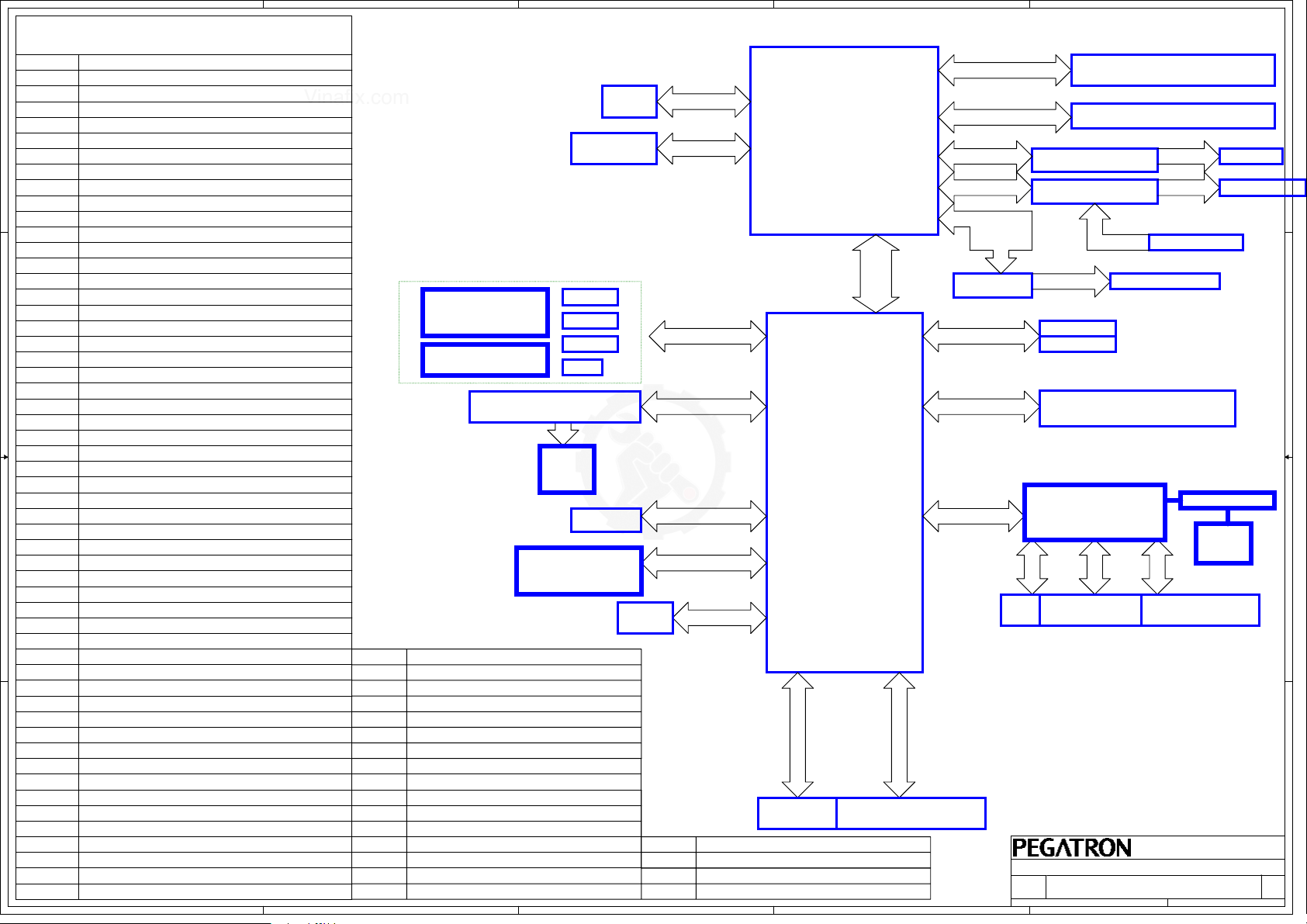

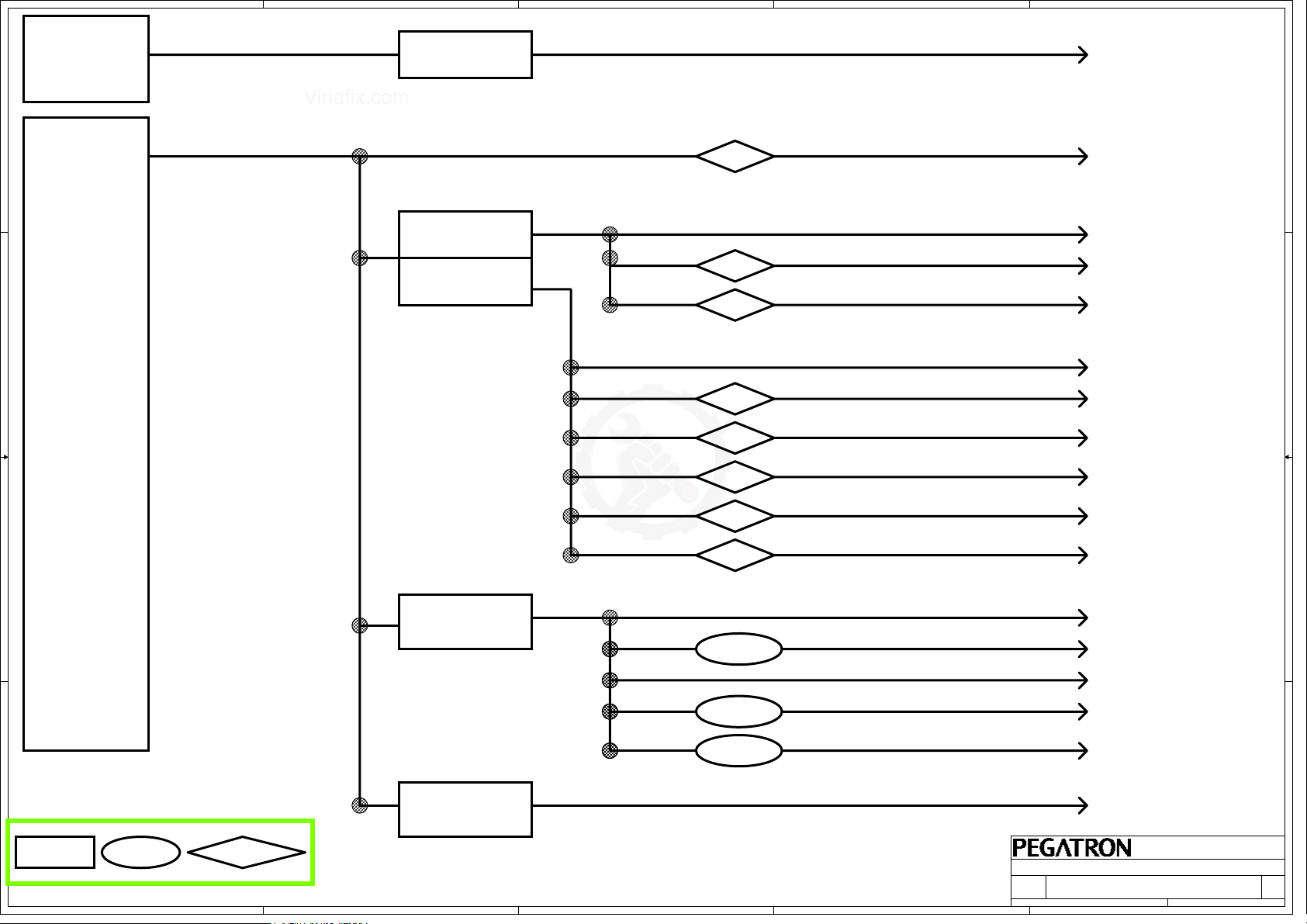

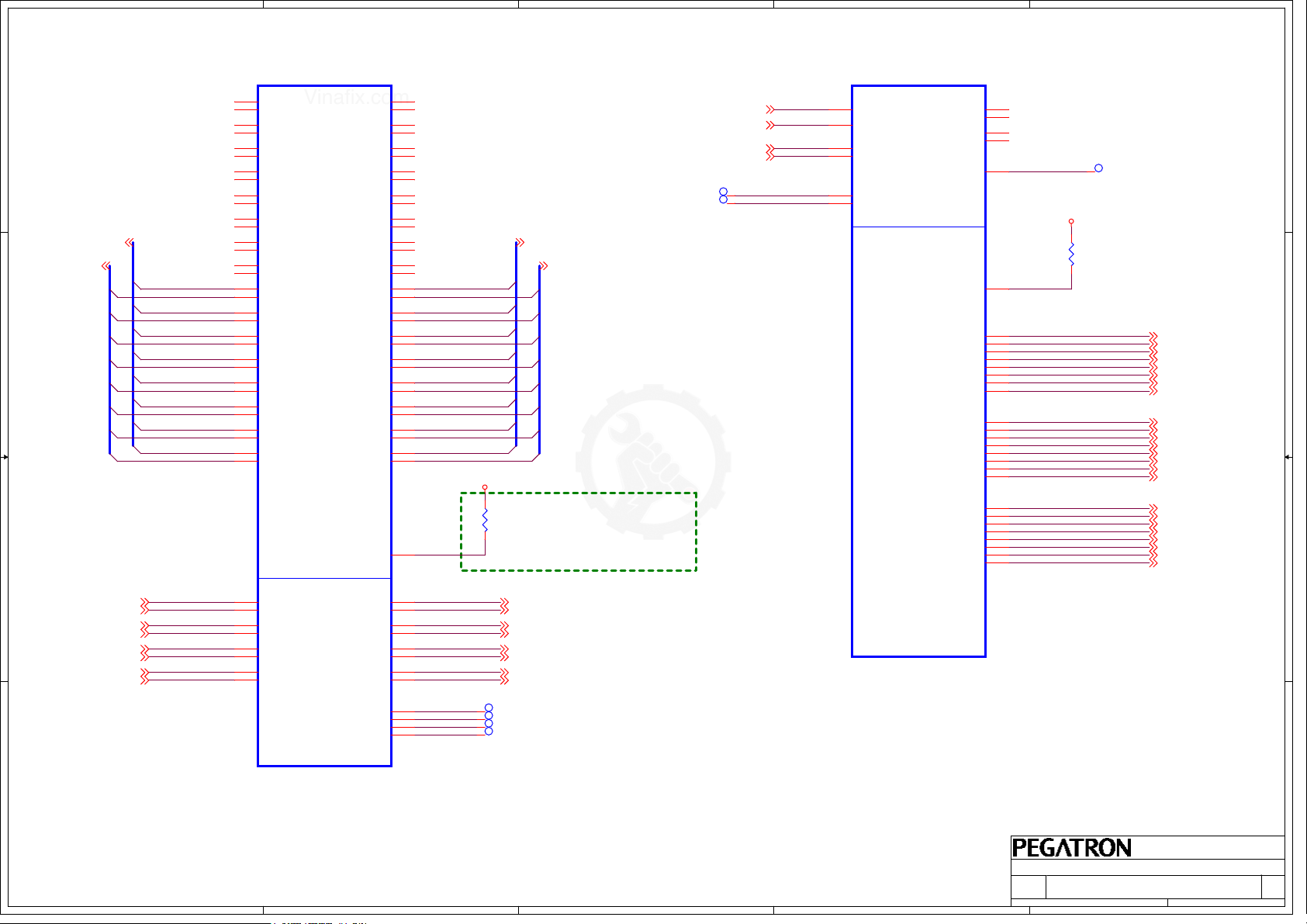

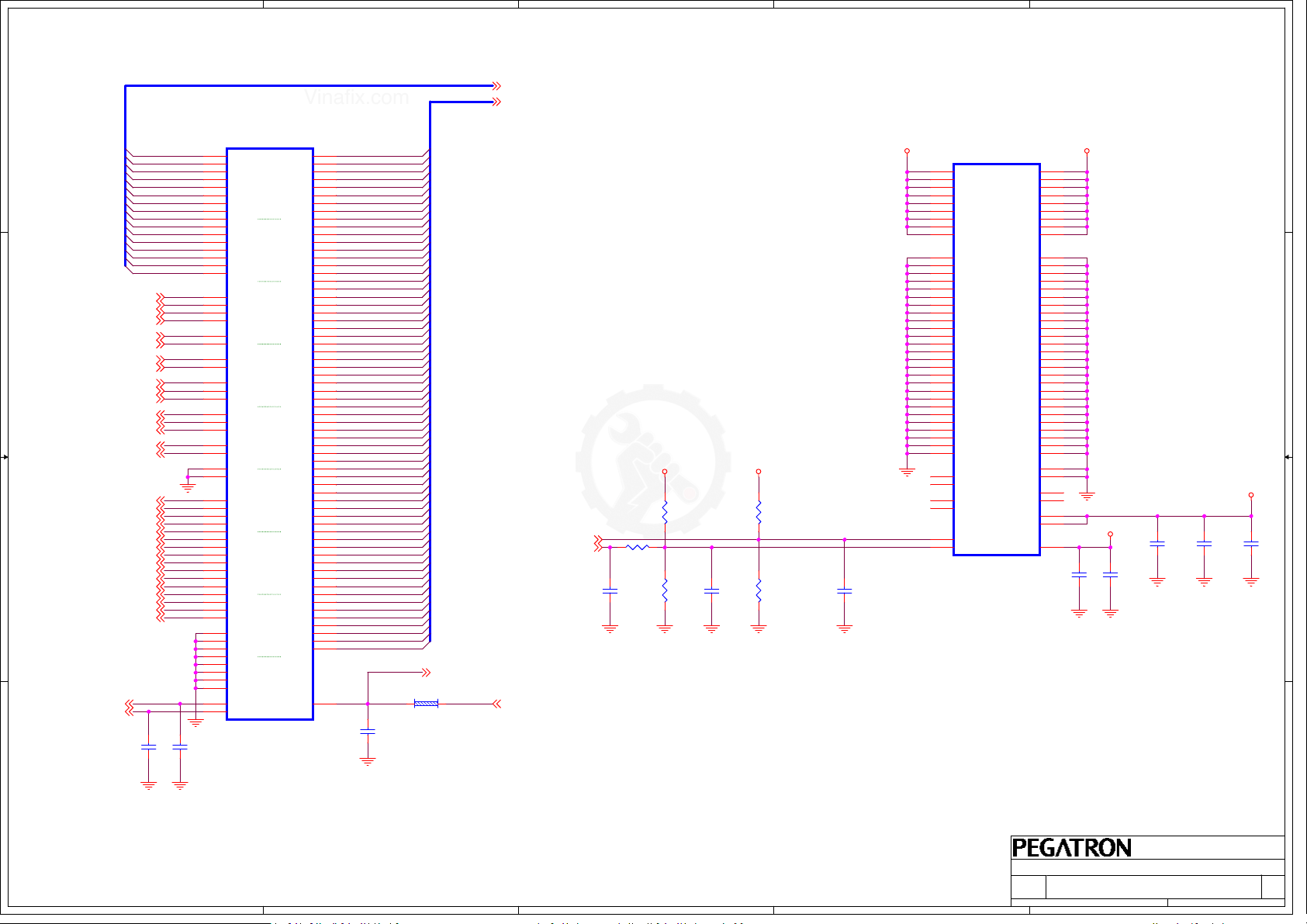

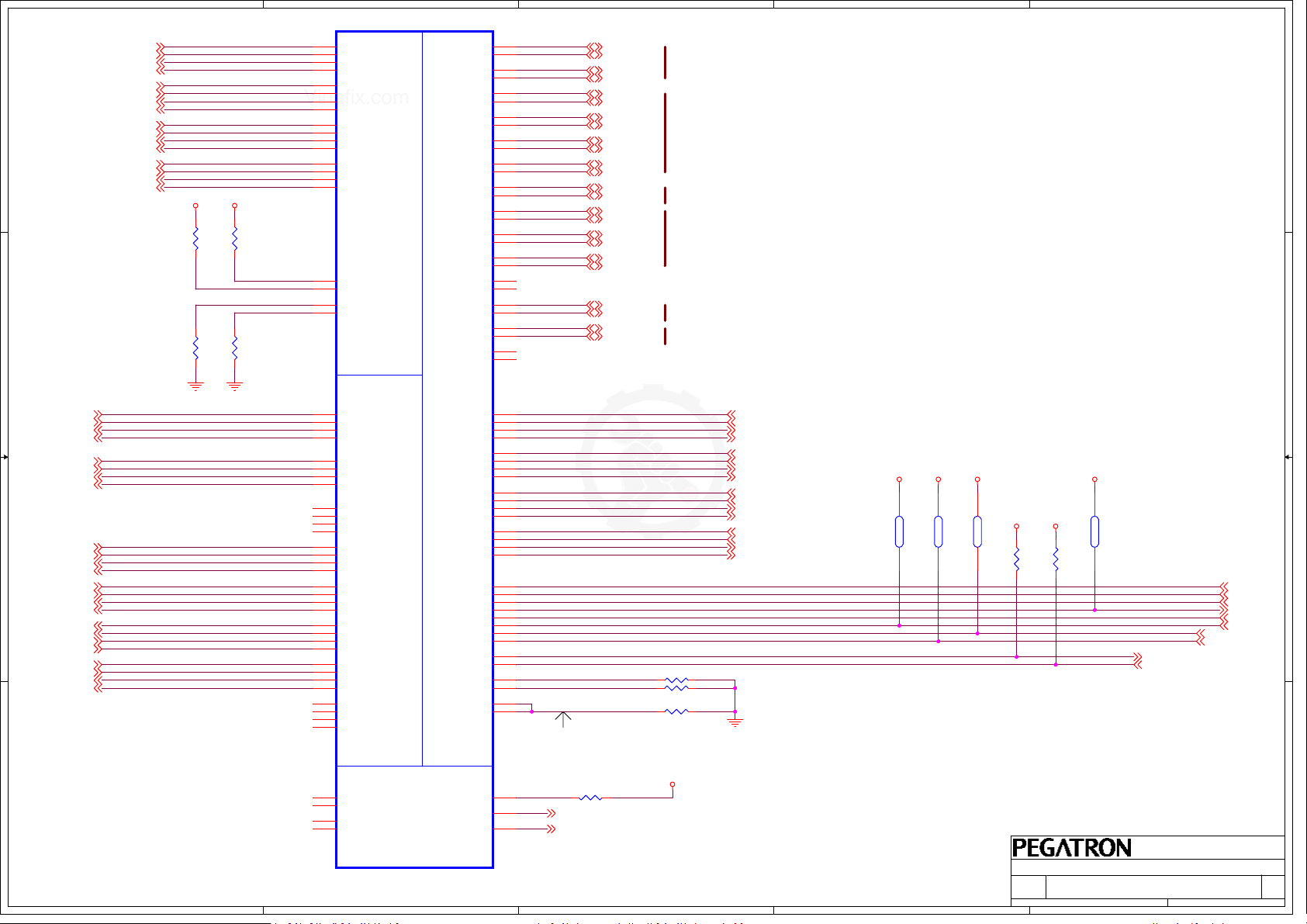

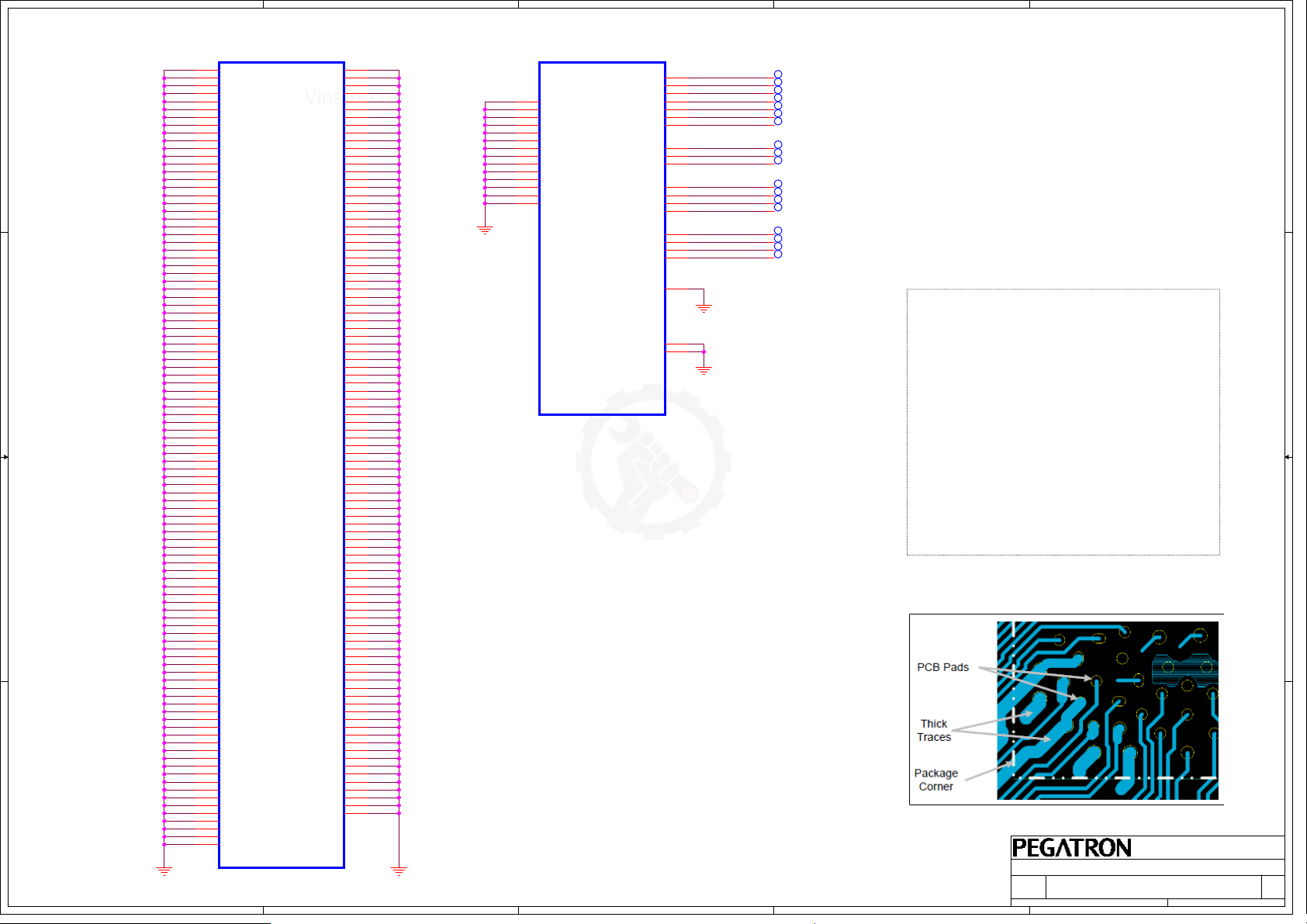

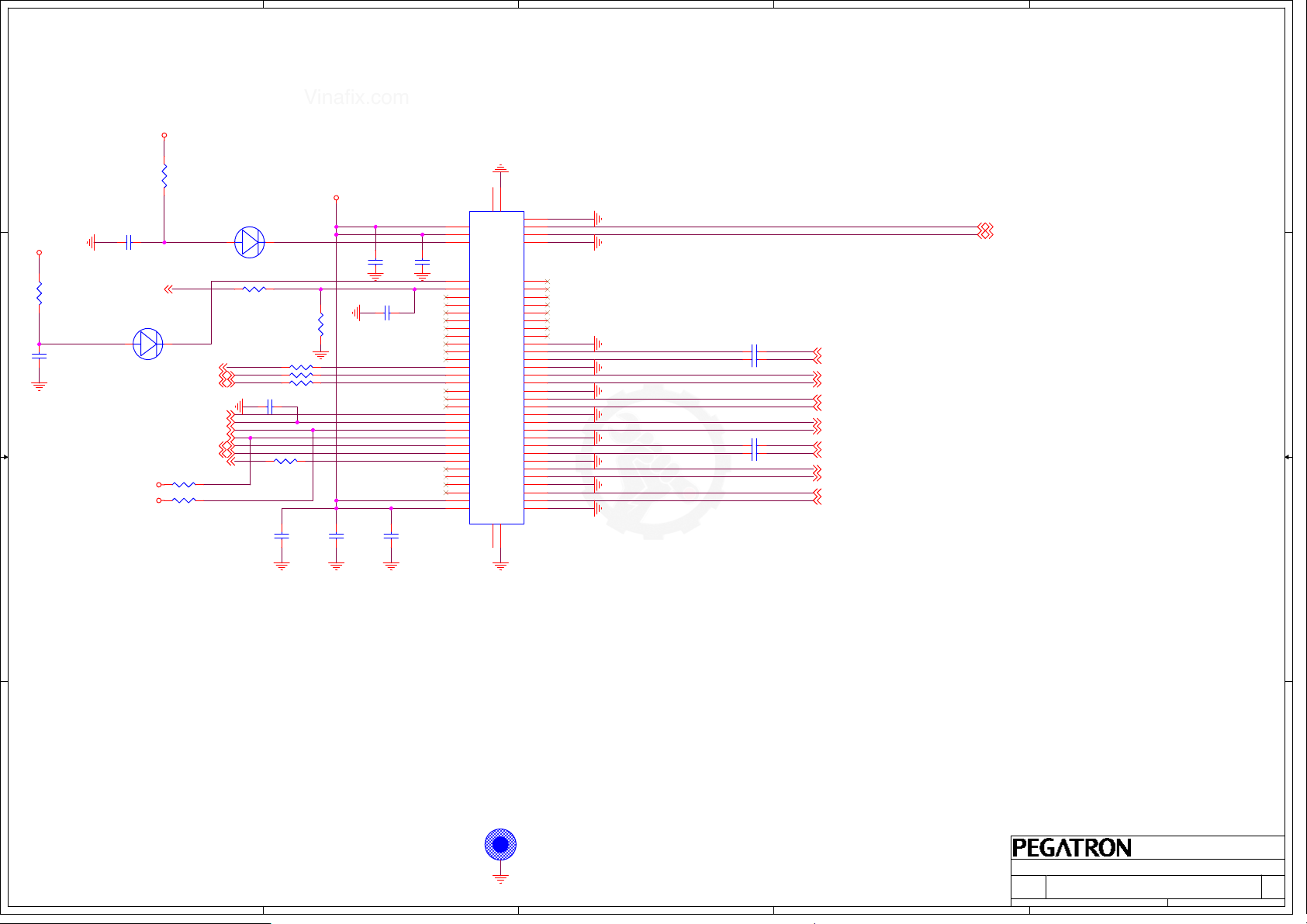

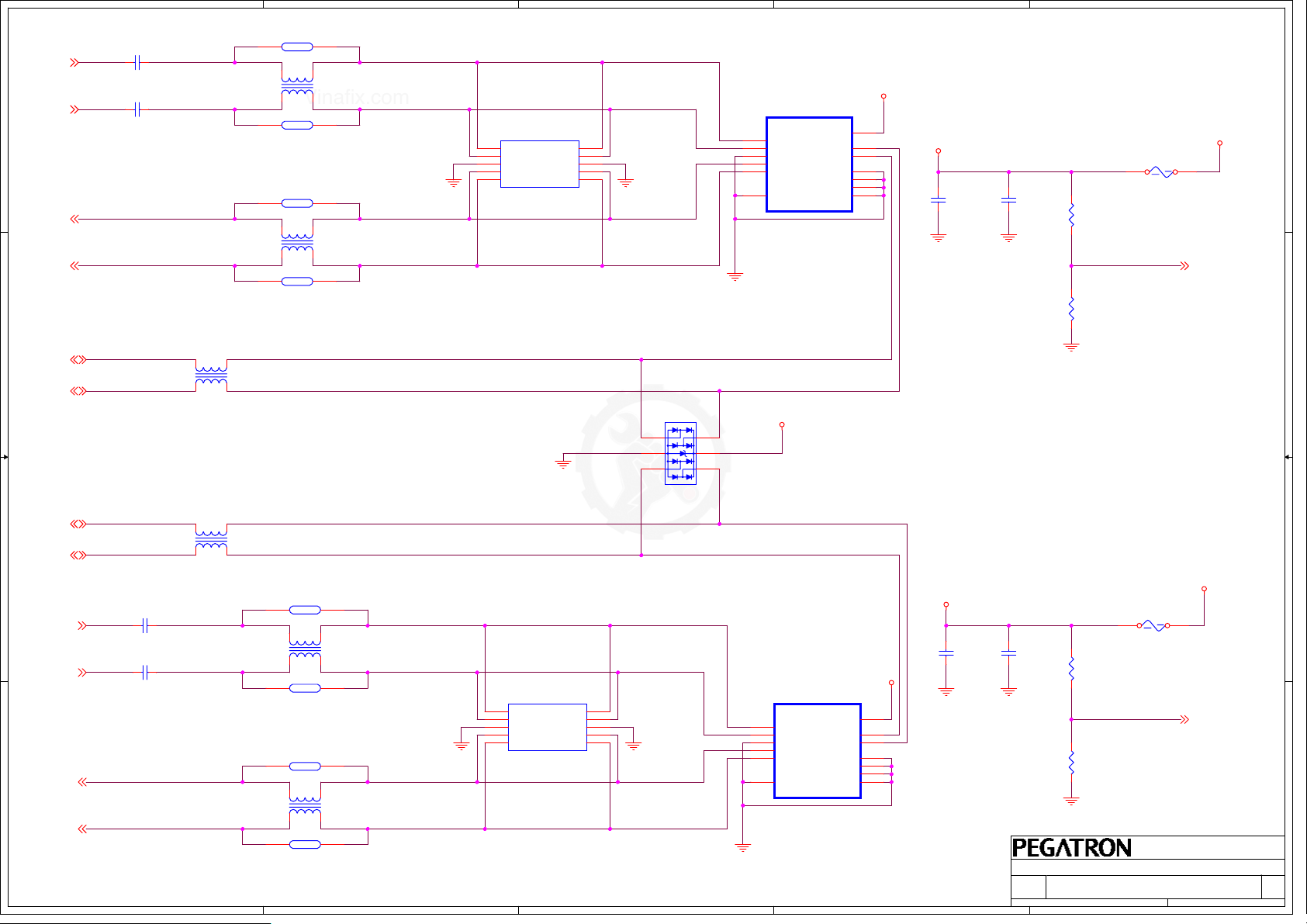

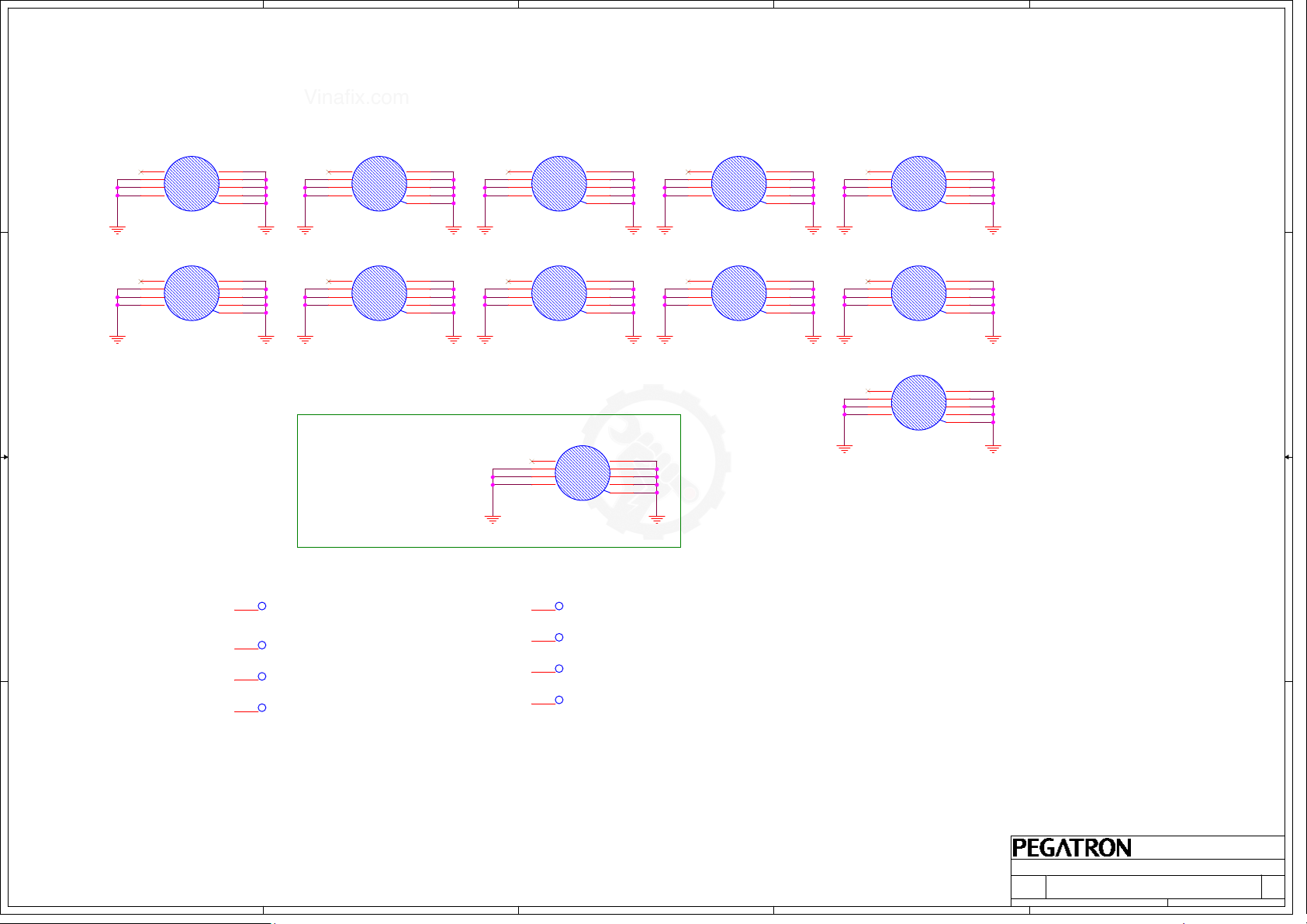

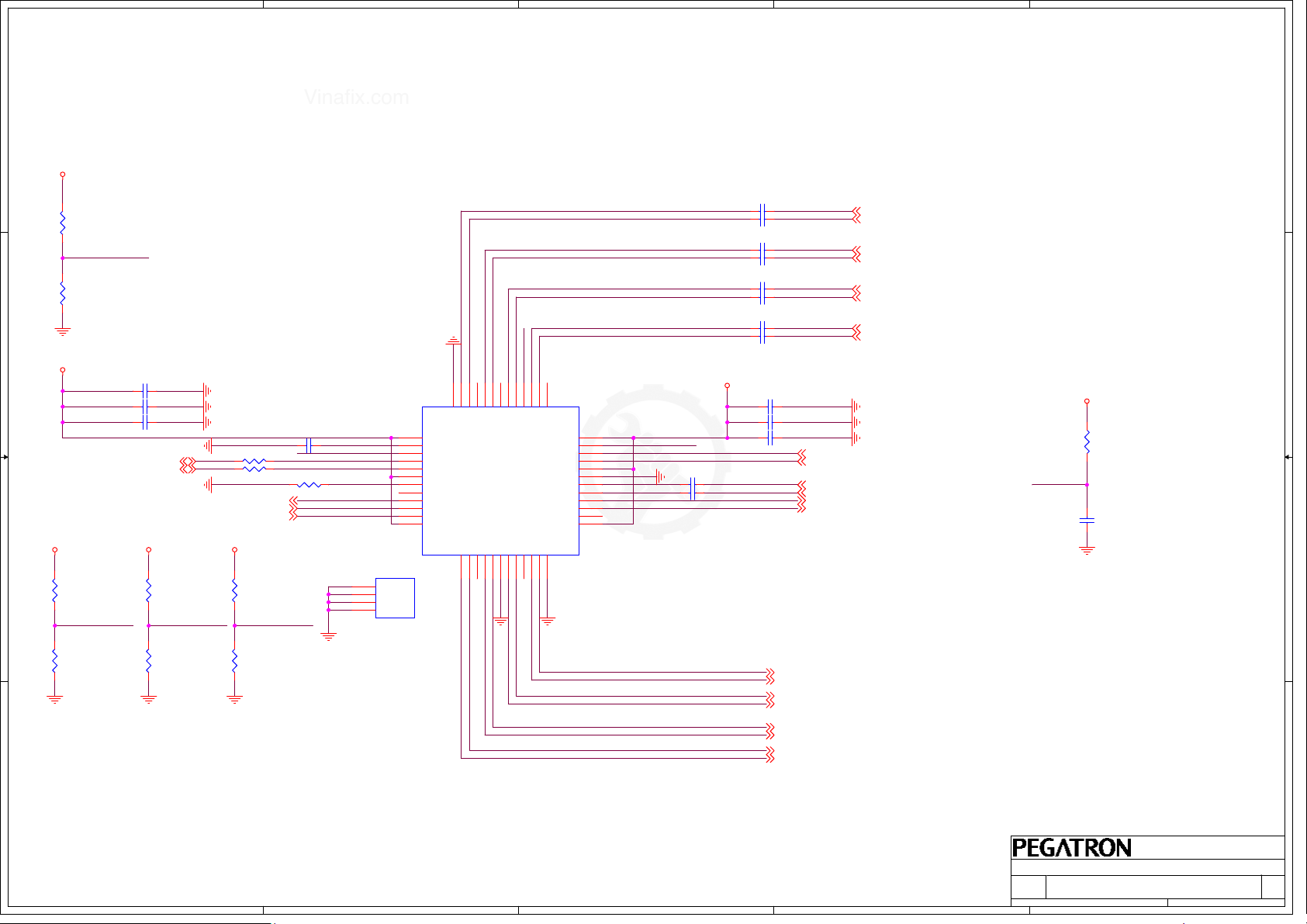

BLOCK DIAGRAM

CLOCKS DISTRIBUTION

SIGNAL & RESET MAP

CHANGE HISTORY

POWER FLOW

POWER DISTRIBUTION

POWER SEQUENCE

Haswell LGA-1150

VGA DEBUG

DDR3 CHANNEL A&B

DDR3 TERMINATION A&B

N/A

INTEL_PCH(1~6)

N/A

SM BUS & SPI ROM

ME DISABLE

MINI-PCIE SLOT-1(WLAN)

MINI-PCIE SLOT-3(mSATA)

CARD READER

INTEL CLARKVILLE

LAN JACK

SIDE USB3.0 PORT

REAR USB3.0 PORT

REAR USB3.0 PORT

REAR USB2.0 PORT

TOUCH & WEBCAM

N/A

SATA CONN

AUDIO CODEC ALC3661

AMP

REAR LINE OUT& GHS CONNECTOR

N/A

SIO SMSC5555

N/A

SCREW HOLE

FAN CIRCUIT

COM PORT

DEBUG LED

APS/LPC DEBUG

SCALAR_TSUMU88BDC2

LVDS & CONVERTER CONN

SCALAR LCD ENABLE

FRONT PANEL

HDMI IN

HDMI LEVEL SHIFT

HDMI OUT

G-SENSOR

DP REDRIVER

DP CONN

TPM

DC IN

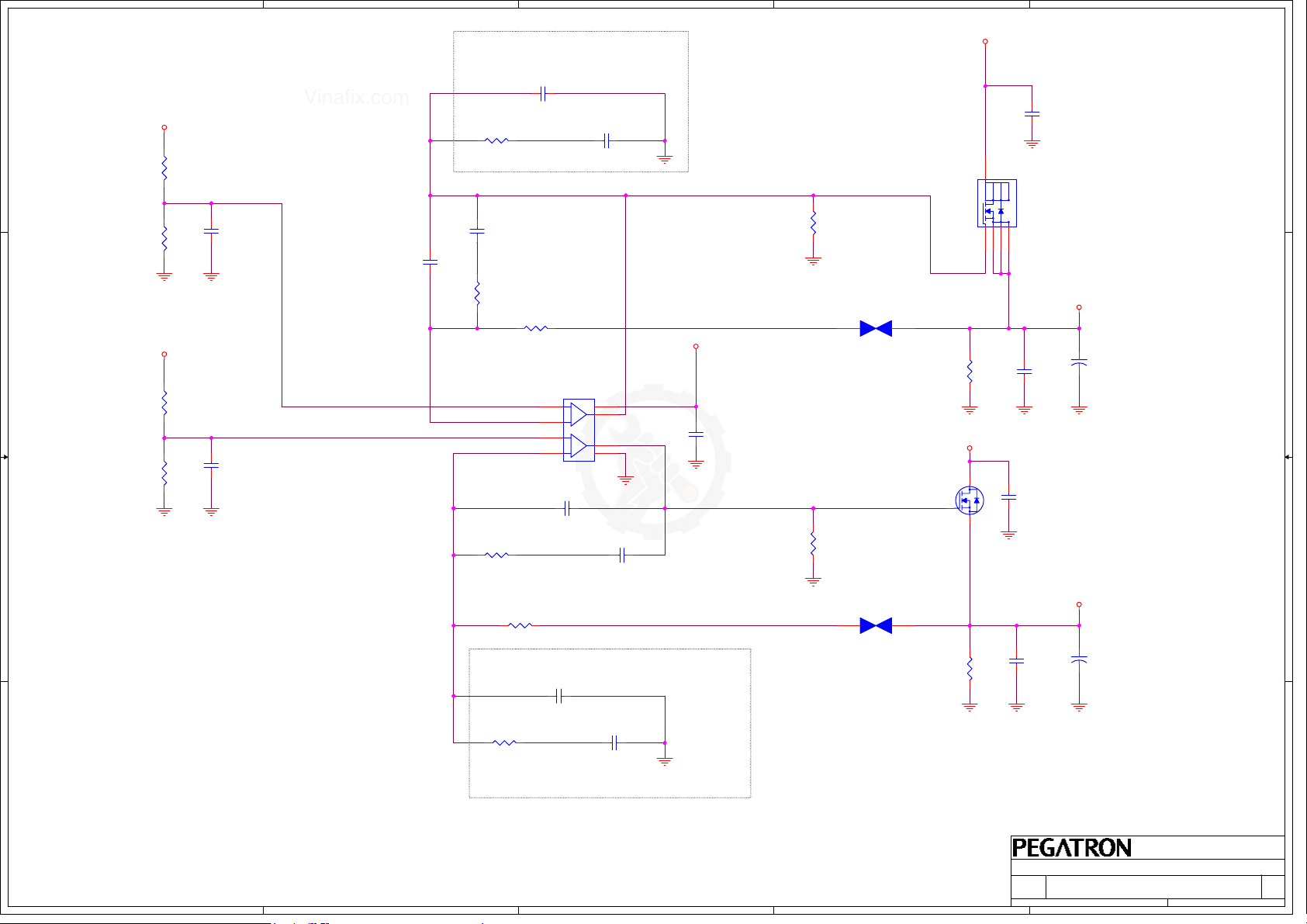

VCORE CONTROLLER

3P3_LAN,12V,1P5V_PCH,3P3V_BG

TITLE

5

Revision: B00

GPU MARS

USB3.0 x 4

USB2.0 x 2

USB3.0 x 2

<Rear>

<Side>

Intel WGI217LM

10/100/1000

WLAN/MSATA

(NGFF)

68

69

70

71

72

73 N/A

74 +3P3V_WLAN & +3P3V_mSATA

75

76

77

78

79~85

86~89 VRAM

90 +1P8V

92

5V, 3P3V, 1P5V, 5V_Dual

+1P05V_PCH & +1P22V

+5VSB, +3P3VA

+5VSB, +12VSB

+1P5V_DUAL , +VTT_DDR

N/A

CPU XDP DEBUG CONNECTOR

PCH XDP DEBUG CONNECTOR

N/A

GPU

3P3V_GPU&+0P95V91

+1P35V_GPU & +1P05V_ME 95 TP

4

WiFi

MSATA

Webcam

Touch

RJ 45

Card Reader

OZ777FJ2LN

XDP

PCIE X8

USB

PCIE BUS

100MHz

PCIE BUS

PCIE BUS/SATA

XDP

SMSC5555

93~94 VDDC CONTROLLER

95 SIDE KEY

96 CONVERTER BOARD

3

Intel Processor

Haswell

LGA-1150 Pin Socket

TDP = 65W

DMI

INTEL

Lynx Point

PCH

708 Pin

23mm X 22mm

LPC BUS

33MHz

ST33ZP24AR28PVSP

LPC BUS

33MHz

TPM

2

Channel A

Channel B

DDIB(Port B)

TMDS(Port C)

TMDS(Port D)

PS8201 HDMI OUT

SATA BUS

SPI

HD Audio

DIGI

MIC

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Dual Channel DDR3 MEMORY x 2 Slots

DDR3 SO-DIMM 1333/1600

DDR3 SO-DIMM 1333/1600

PS8330B

TSUMU88BDC2

LVDS

HDMI IN

HDMI 3.0G

SATA 3.0

SATA 3.0

SPI FLASH

ALAZIA AUDIO

ALC3661

UNIVERSAL JACK

64Mb+32Mb

REAR LINE OUT

(RE-TASKING)

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

1

DP

23" LCD

TPA3131MP

SPK.

5W per

Channel

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

197Friday, January 17, 2014

197Friday, January 17, 2014

197Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

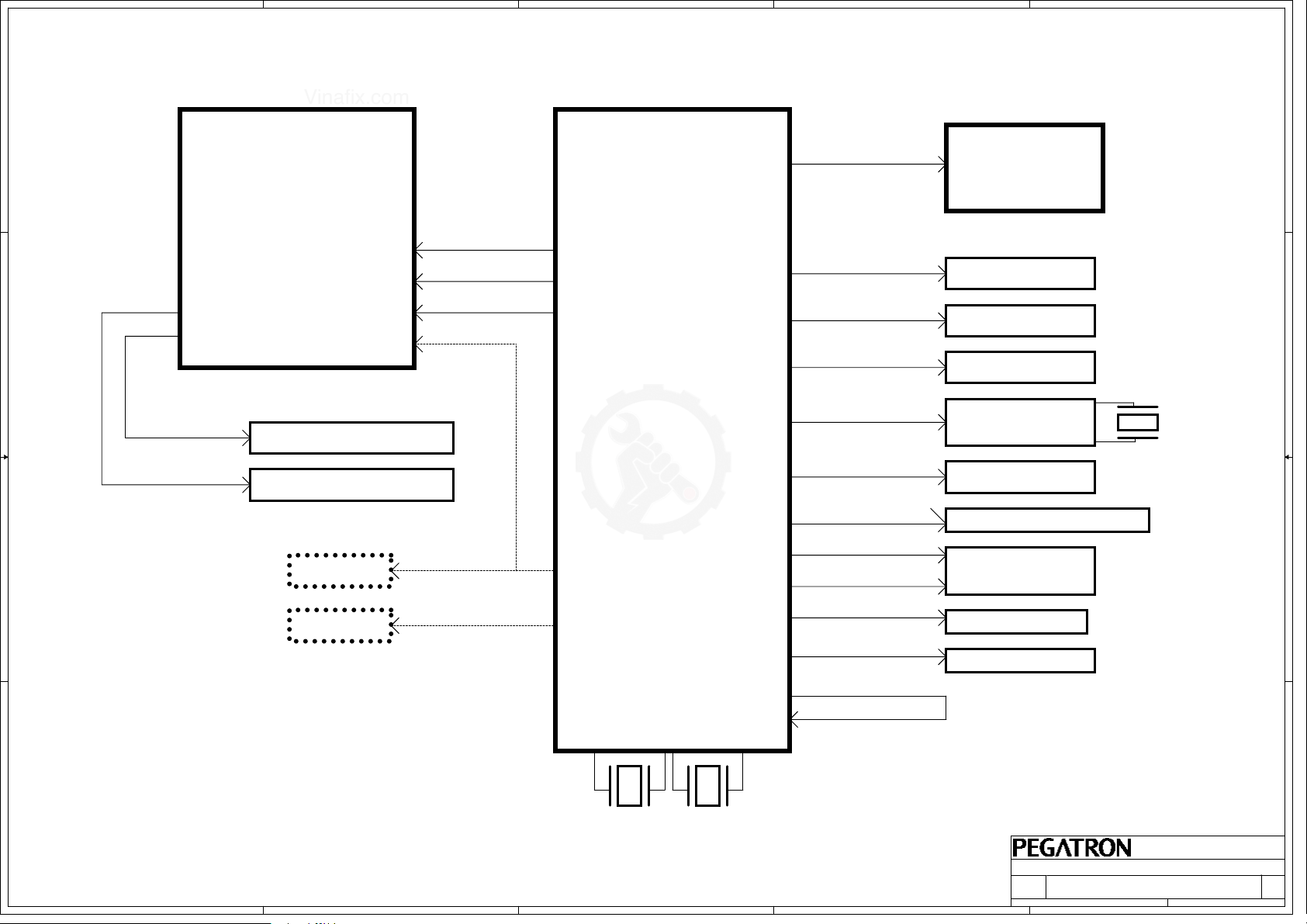

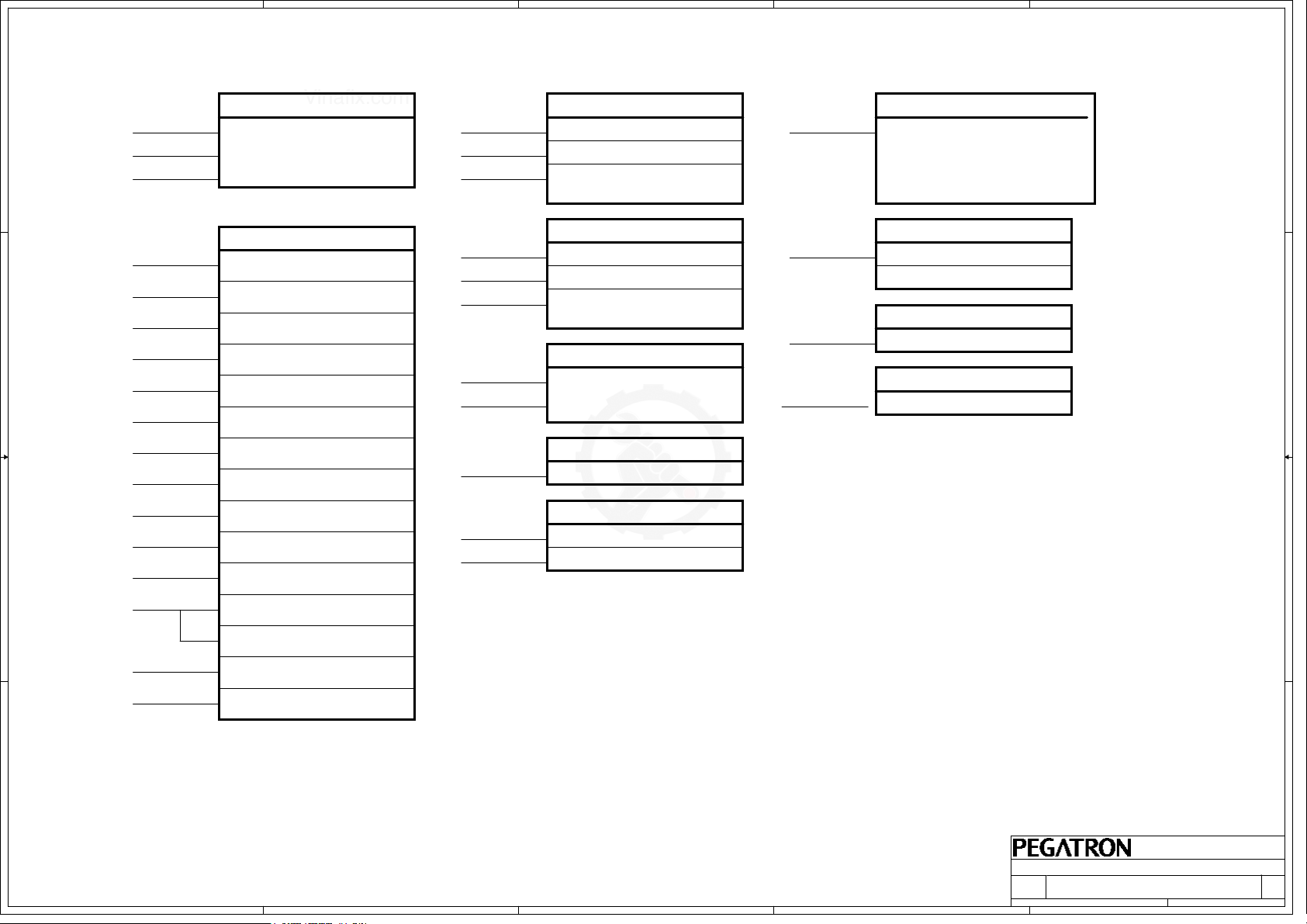

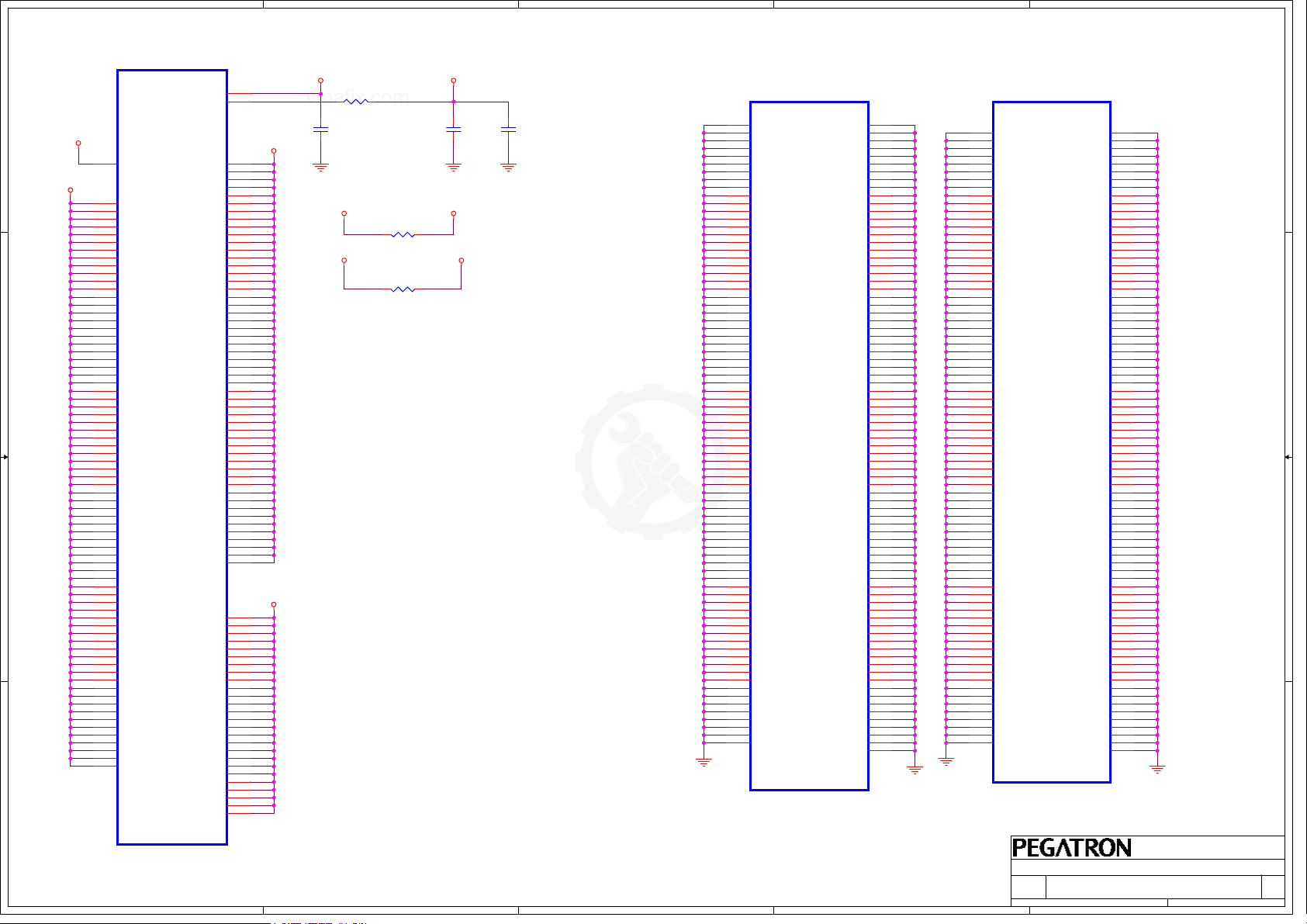

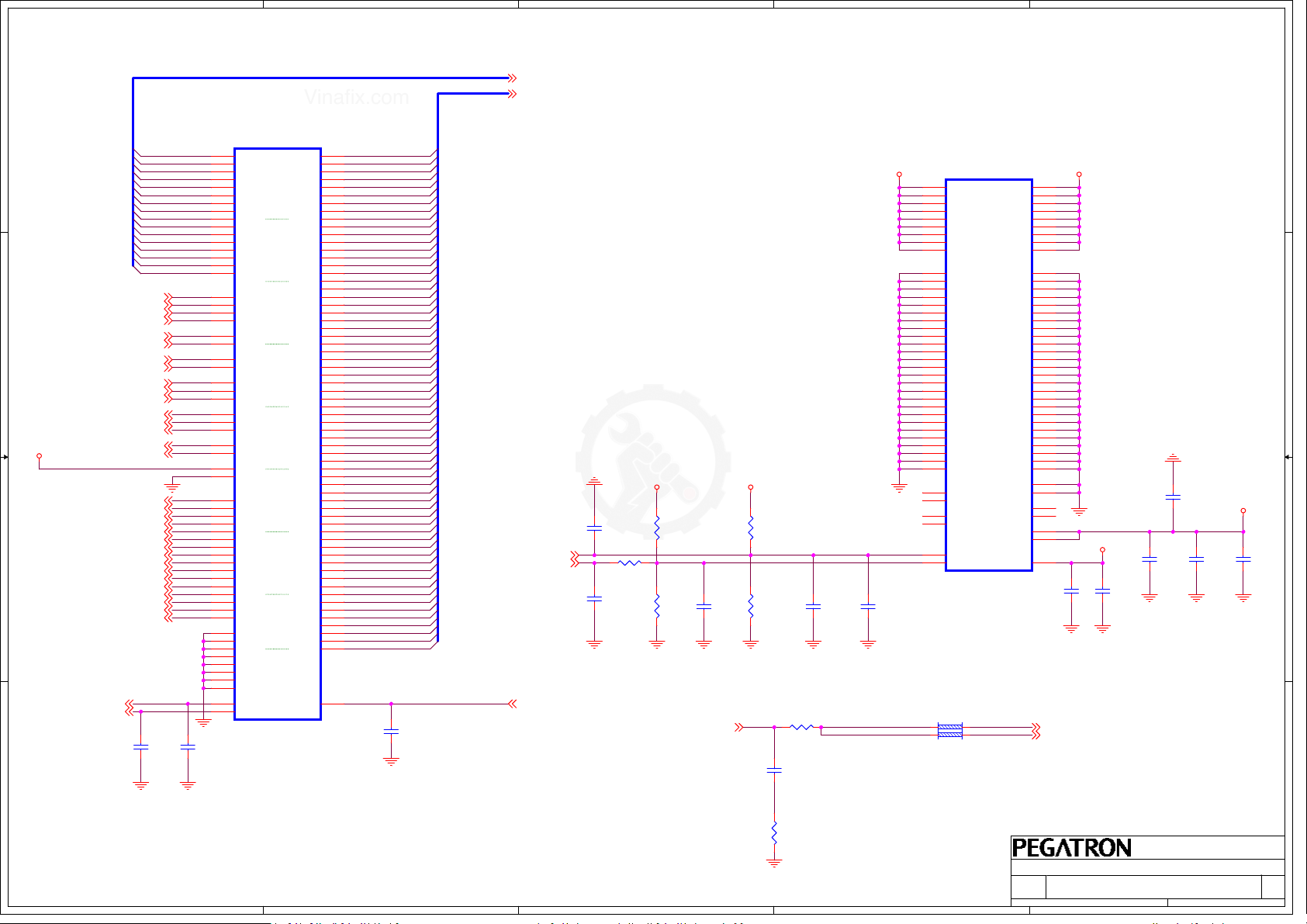

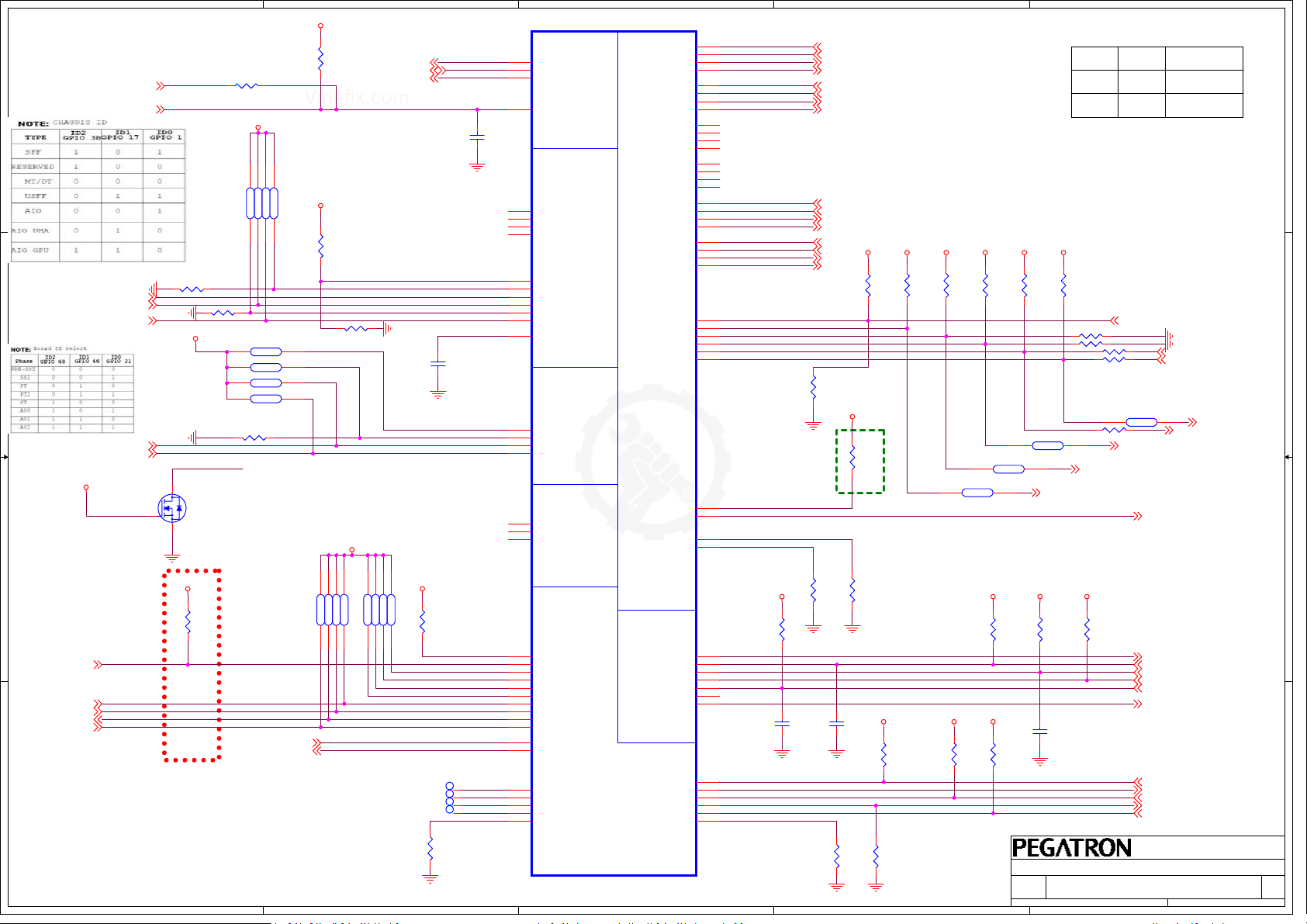

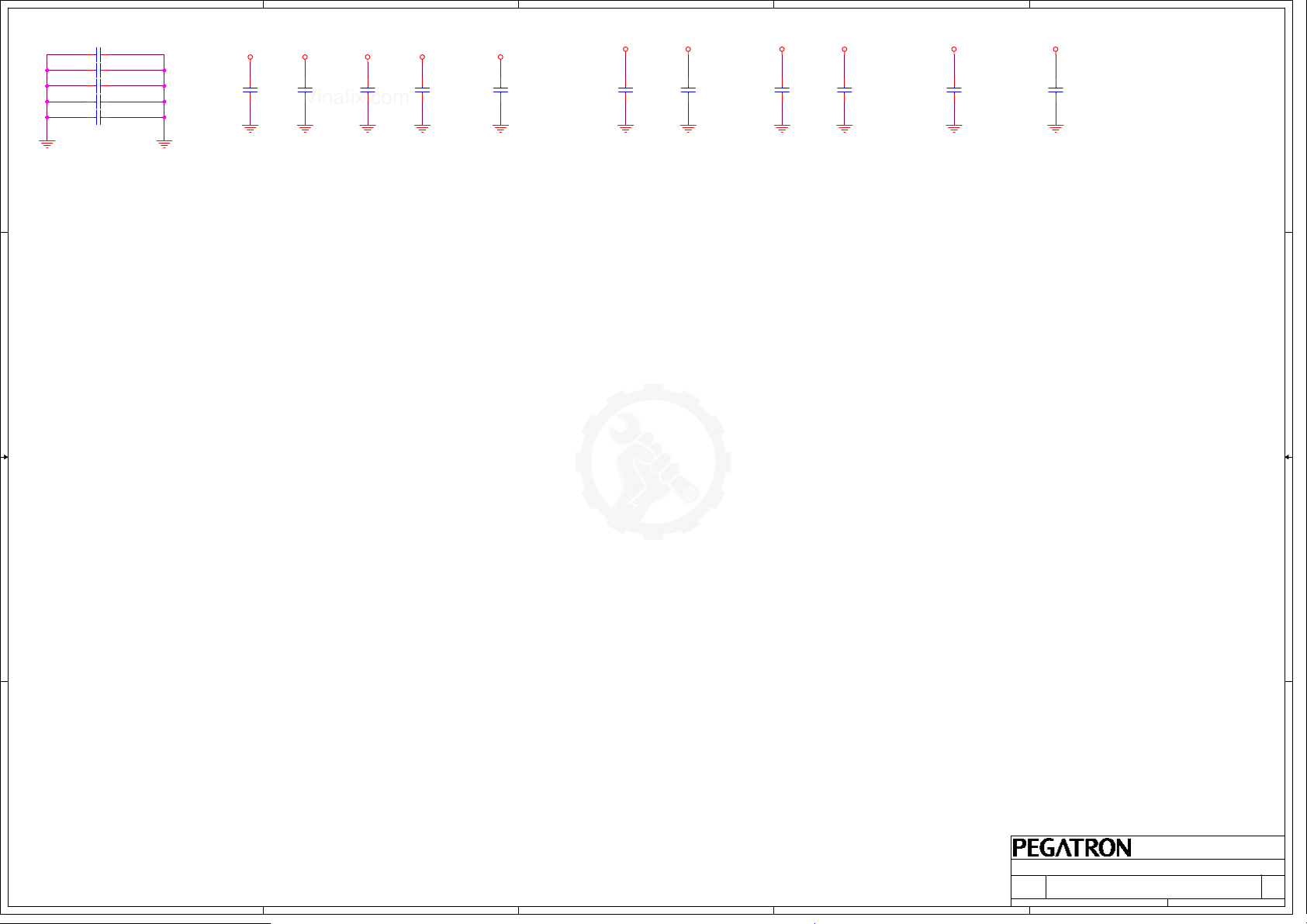

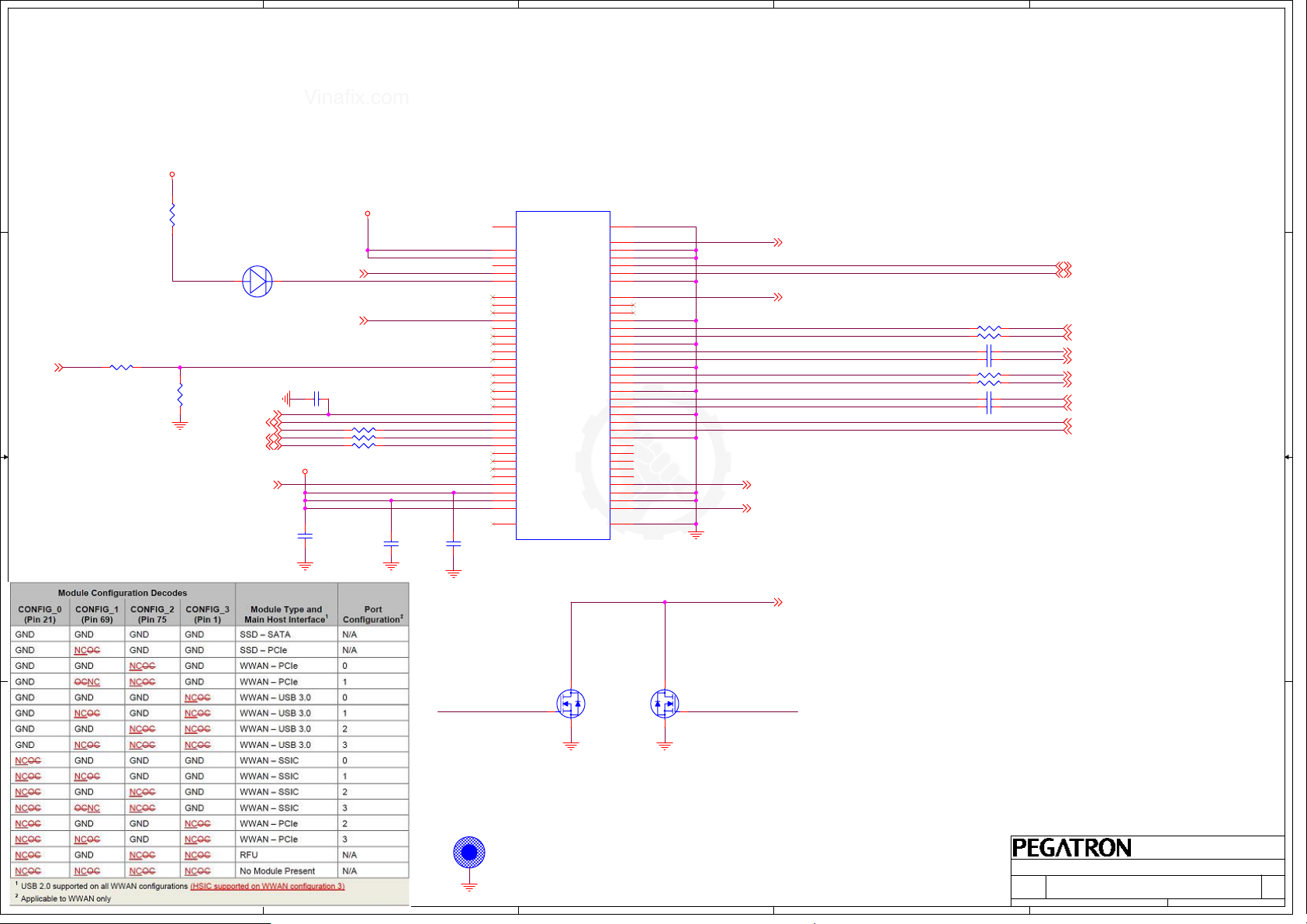

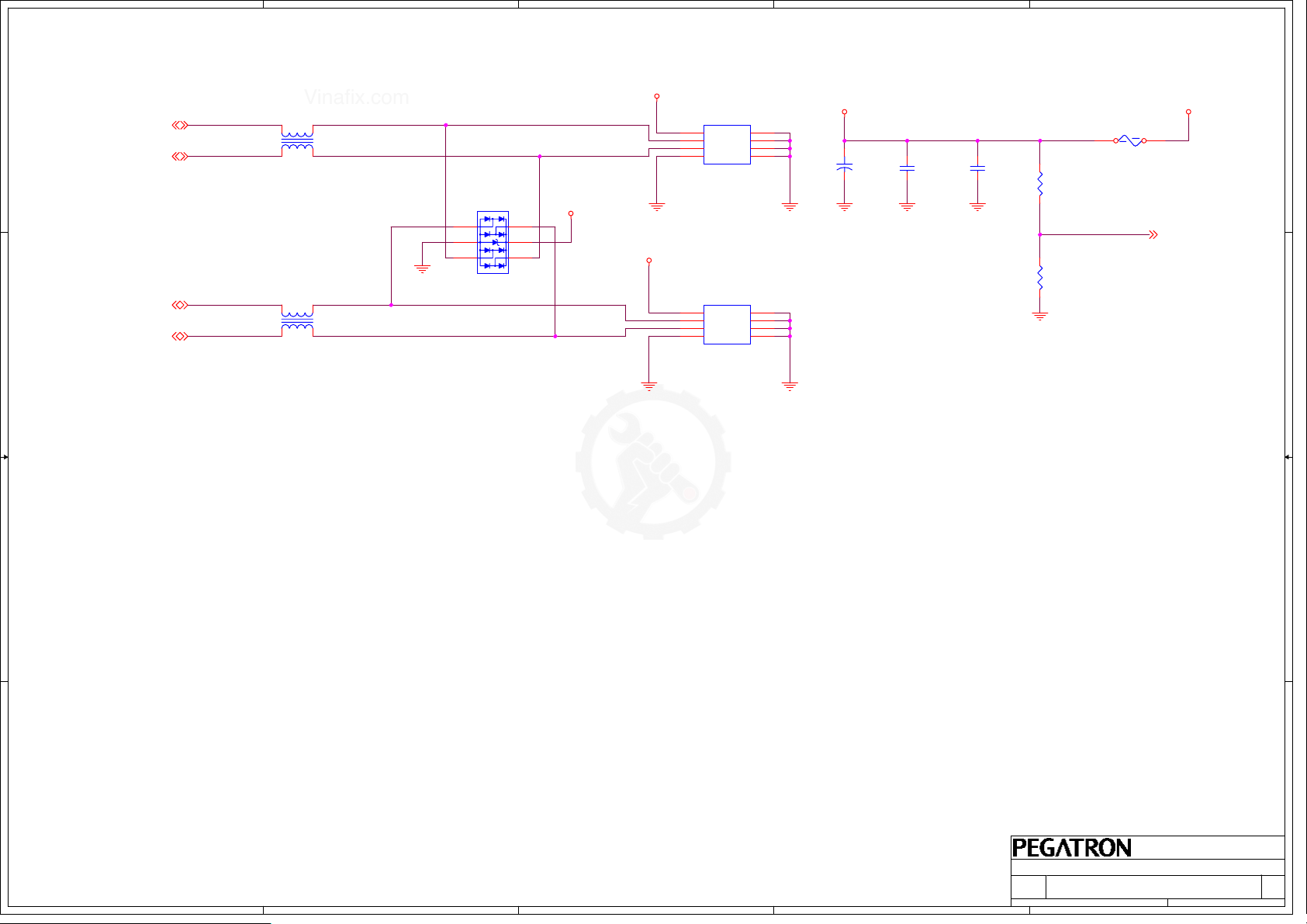

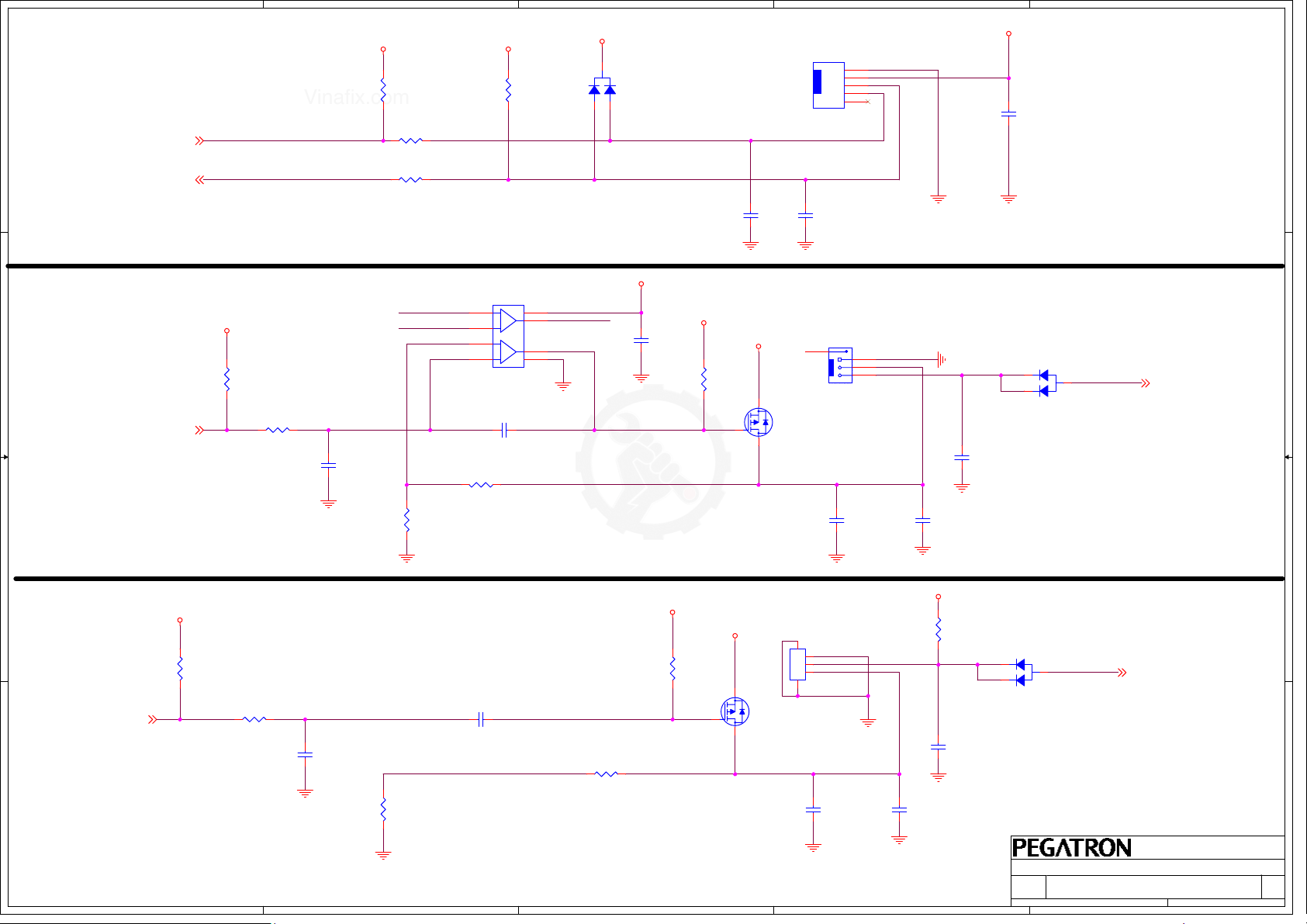

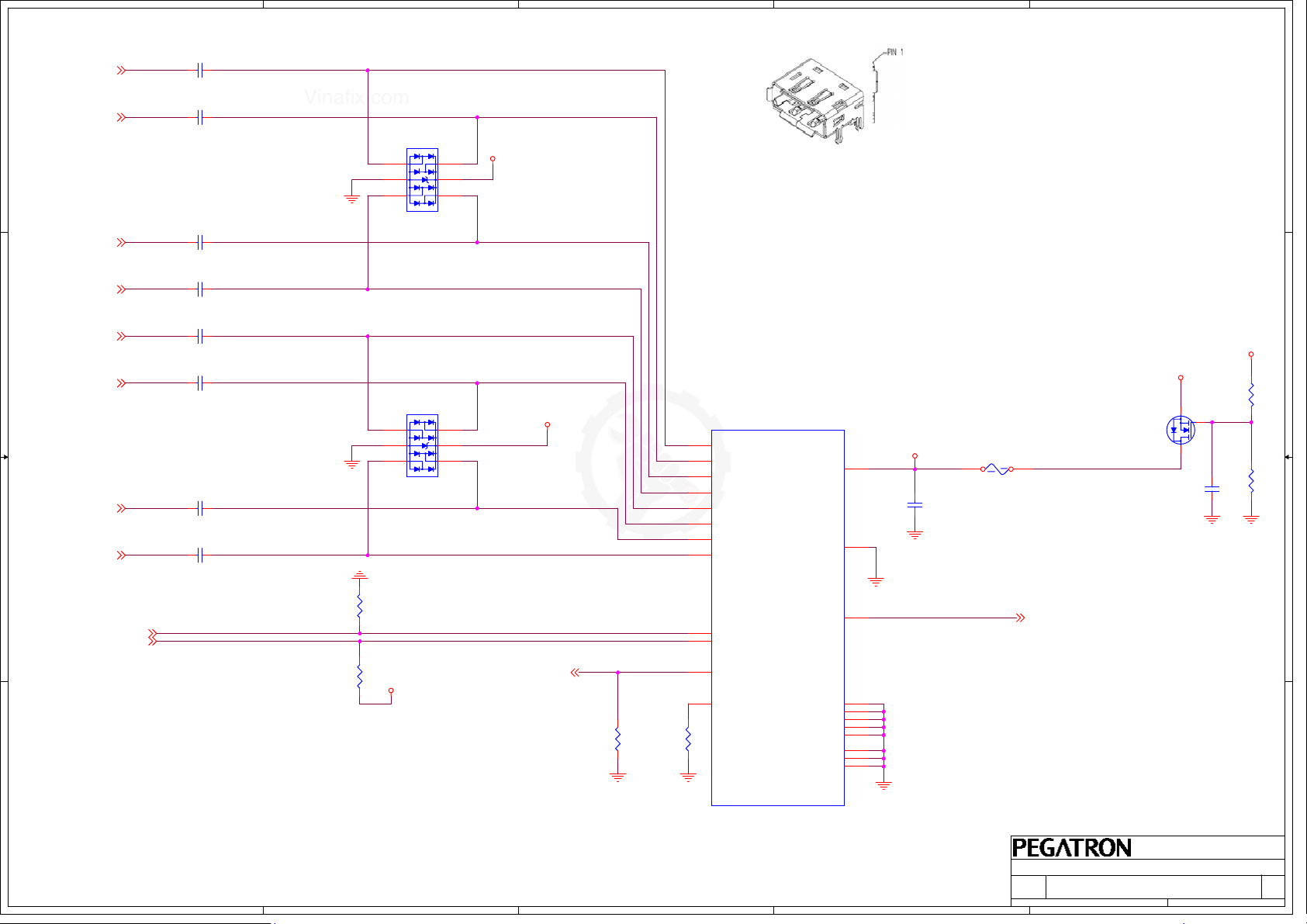

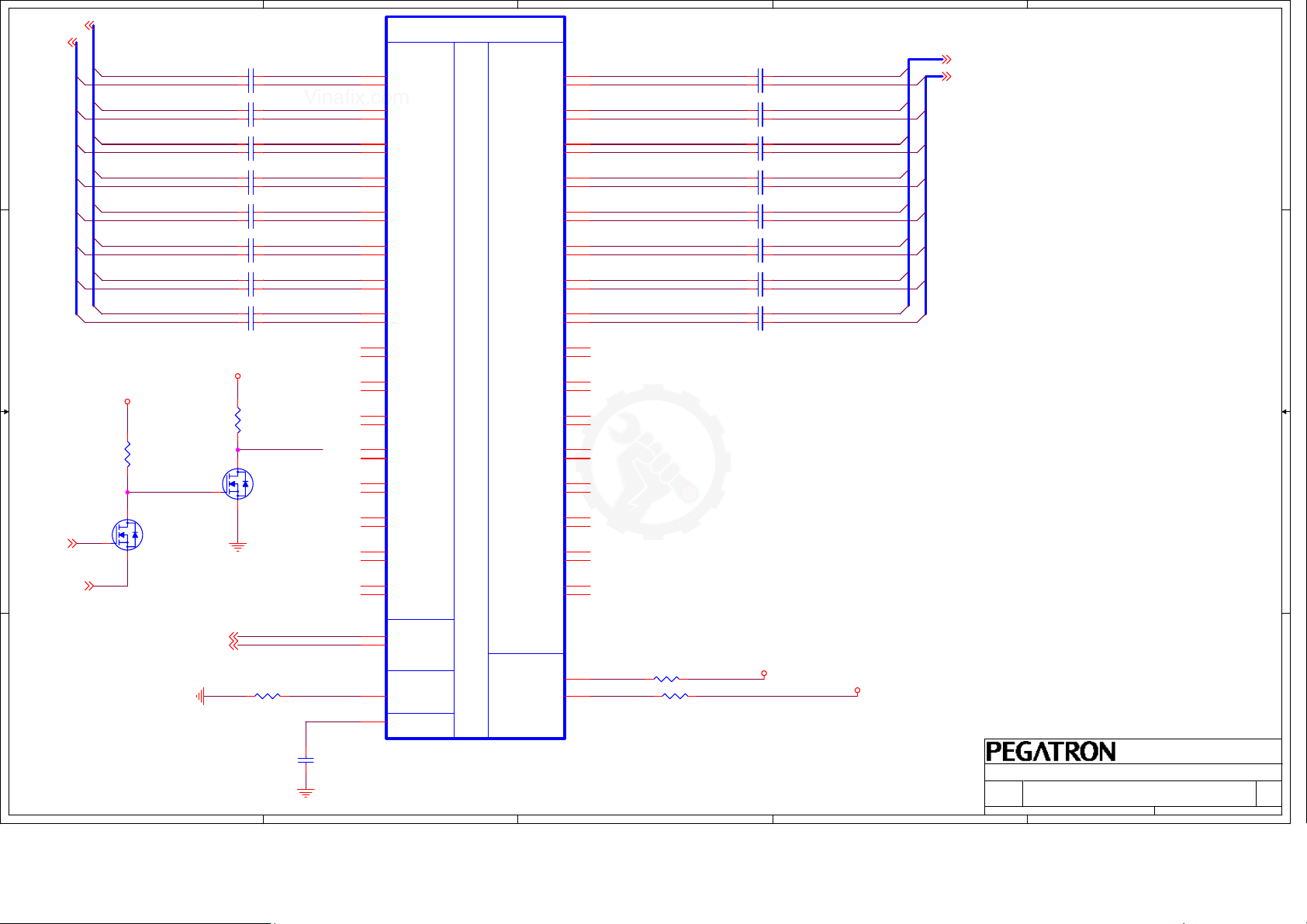

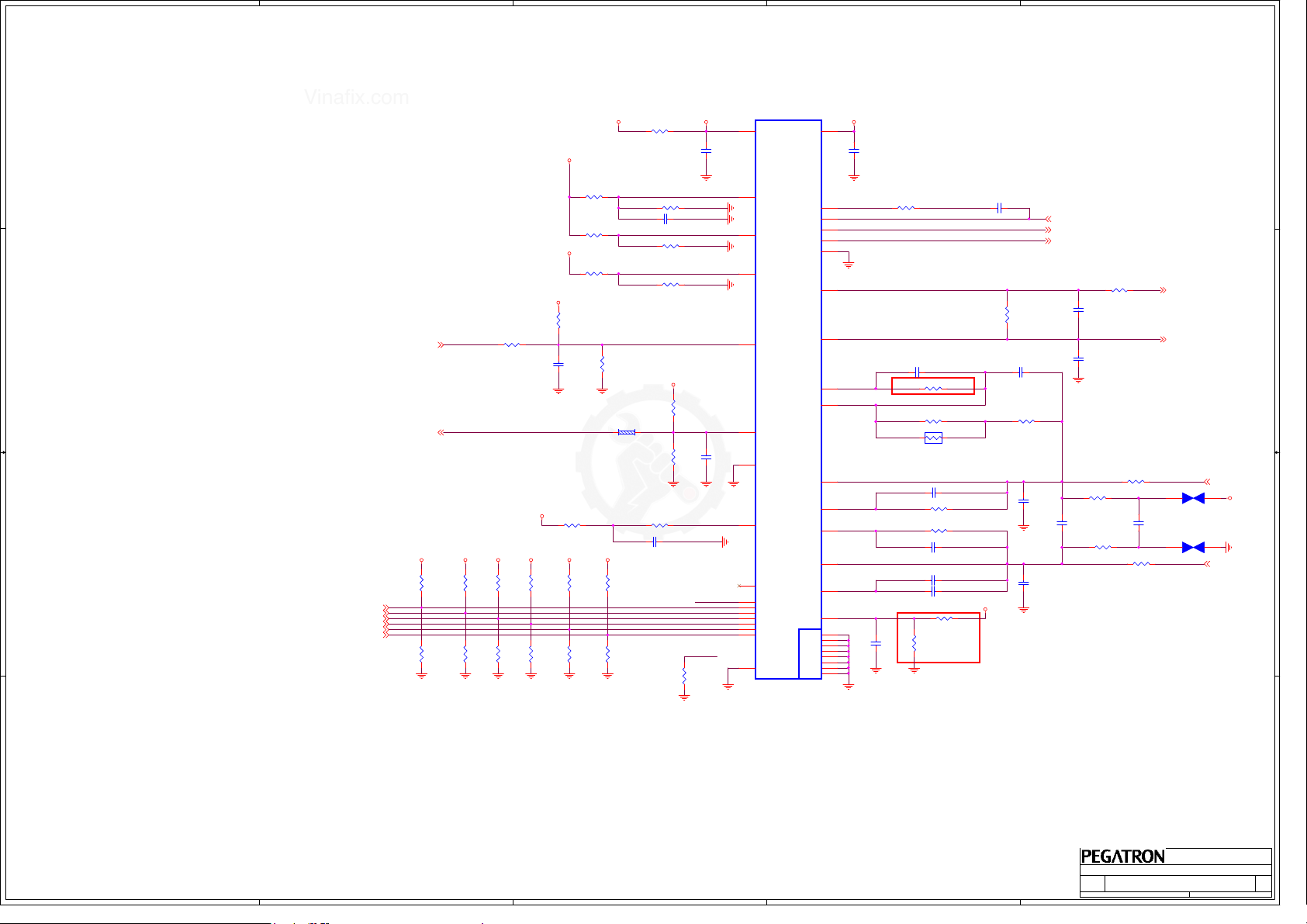

Page 2

Vinafix.com

5

4

3

2

1

D D

Intel Processor

Haswell

LGA-1150 Pin Socket

Intel

Platform Controller Hub

Lynx Point

CK_100M_PE16/#

NVidia

GPU (N14E-GE)

CLKOUT_PEG_A_P/N

BCLK/#_0

SSC_DPLL_REF_CLK/#

SB_CK[0~1]/#

C C

SA_CK[0~1]/#

M_CHA_CLK[0~1]/#

M_CHB_CLK[0~1]/#

B B

DPLL_REF_CLK/#

BCLK_ITP_P/N

XMM1

XMM2

CPU XDP

PCH XDP

CK_100M_DMI/#

CK_135M_DP/#

CK_135M_DPNS/#

CK_100M_CPU_XDP

CLKOUT_DMI_P/N

CLKOUT_DP_P/N

CLKOUT_DPNS_P/N

CLKOUT_PCIE0_P/N

CLKOUT_PCIE1_P/N

CLKOUT_PCIE5_P/N

CLKOUT_PCIE2_P/N

CLKOUT_ITPXDP_P/N

CLKOUT_PCIE7_P/N

CLKOUTTFLEX2

HDA_BCLK

CLKOUTTFLEX3

CLKOUT_33MHZ2

SPI_CLK

CLKOUT_33MHZ3

CK_100M_PE1/#

CK_100M_PE2/#

CK_100M_PE2/#

RL_CK_100M_LAN/#

CK_48M_CR

AZ_BITCLK (24MHz)

CK_48M_SIO

CK_33M_SIO

SPI_CLK

CK_33M_DEBUG

PCIEx1 Slot(Half)

PCIEx1 Slot(Full)

PCIEx1 Slot(Full)

REALTEK

RTL8111GA

CARD READER

AUDIO CODEC ALC663

SIO IT8772E

SPI ROM

LPC Debug Header

25 MHz

CLKOUT_33MHZ4

CKKIN_PCILOOPBACK

CK_33M_PCIFB

XTAL25_IN RTCX

A A

32.768KHz25MHz

5

4

3

2

<CORE DESIGN>

<CORE DESIGN>

<CORE DESIGN>

PEGATRON DT-MB RESTRICTED SECRET

CLCOK DISTRIBUTION

CLCOK DISTRIBUTION

CLCOK DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPPLP-TH

IPPLP-TH

IPPLP-TH

Engineer:

1

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

297Friday, January 17, 2014

297Friday, January 17, 2014

297Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

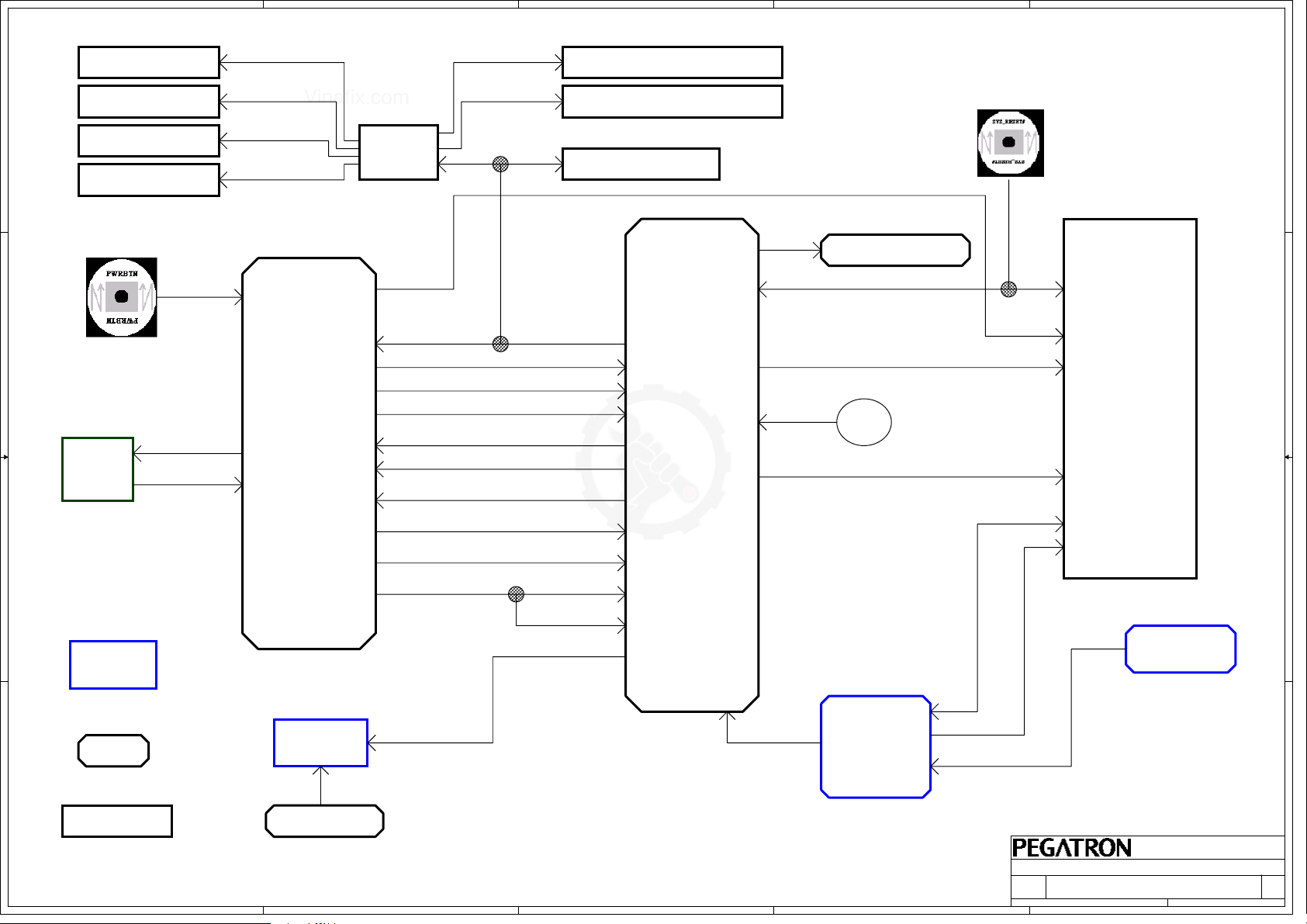

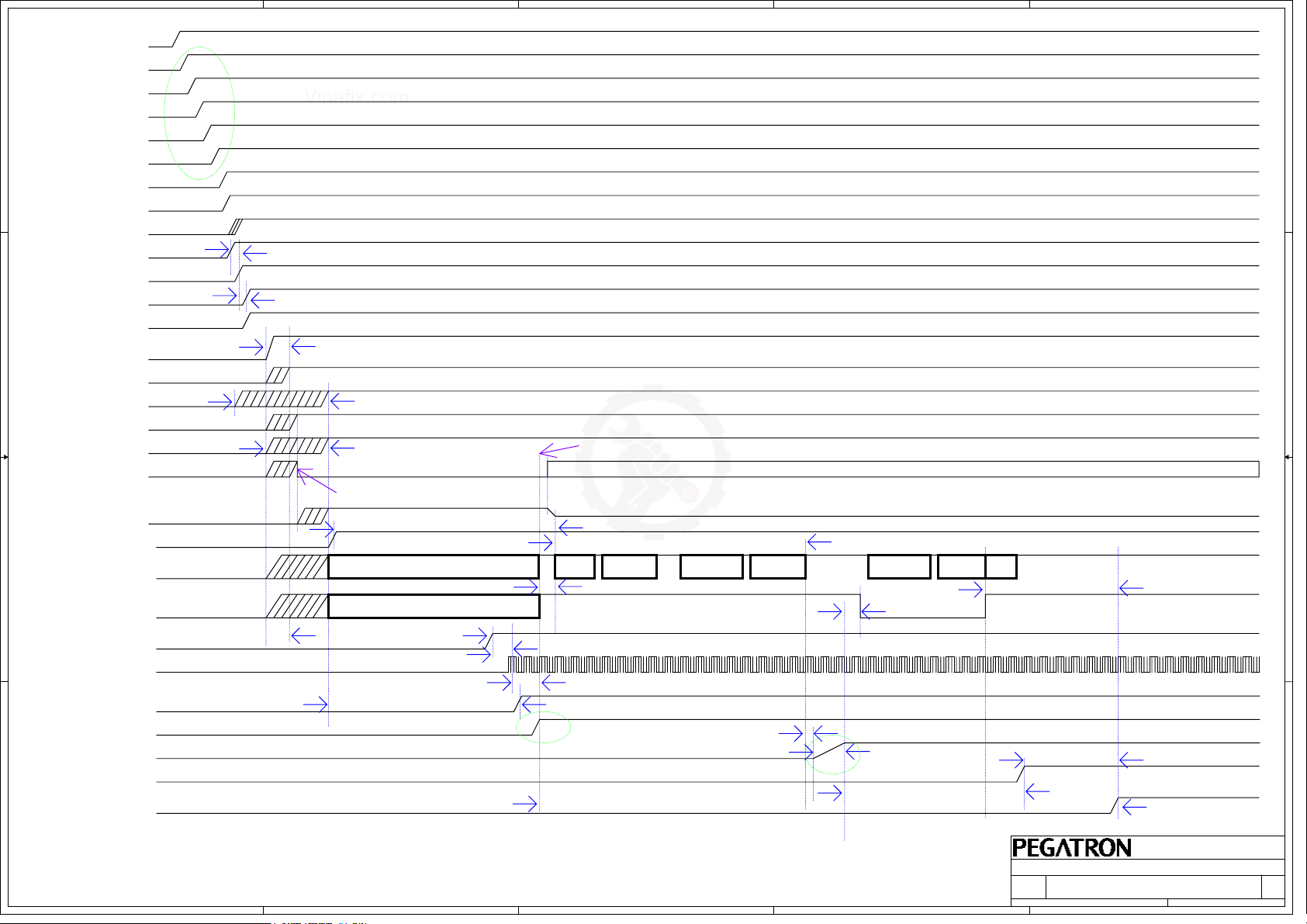

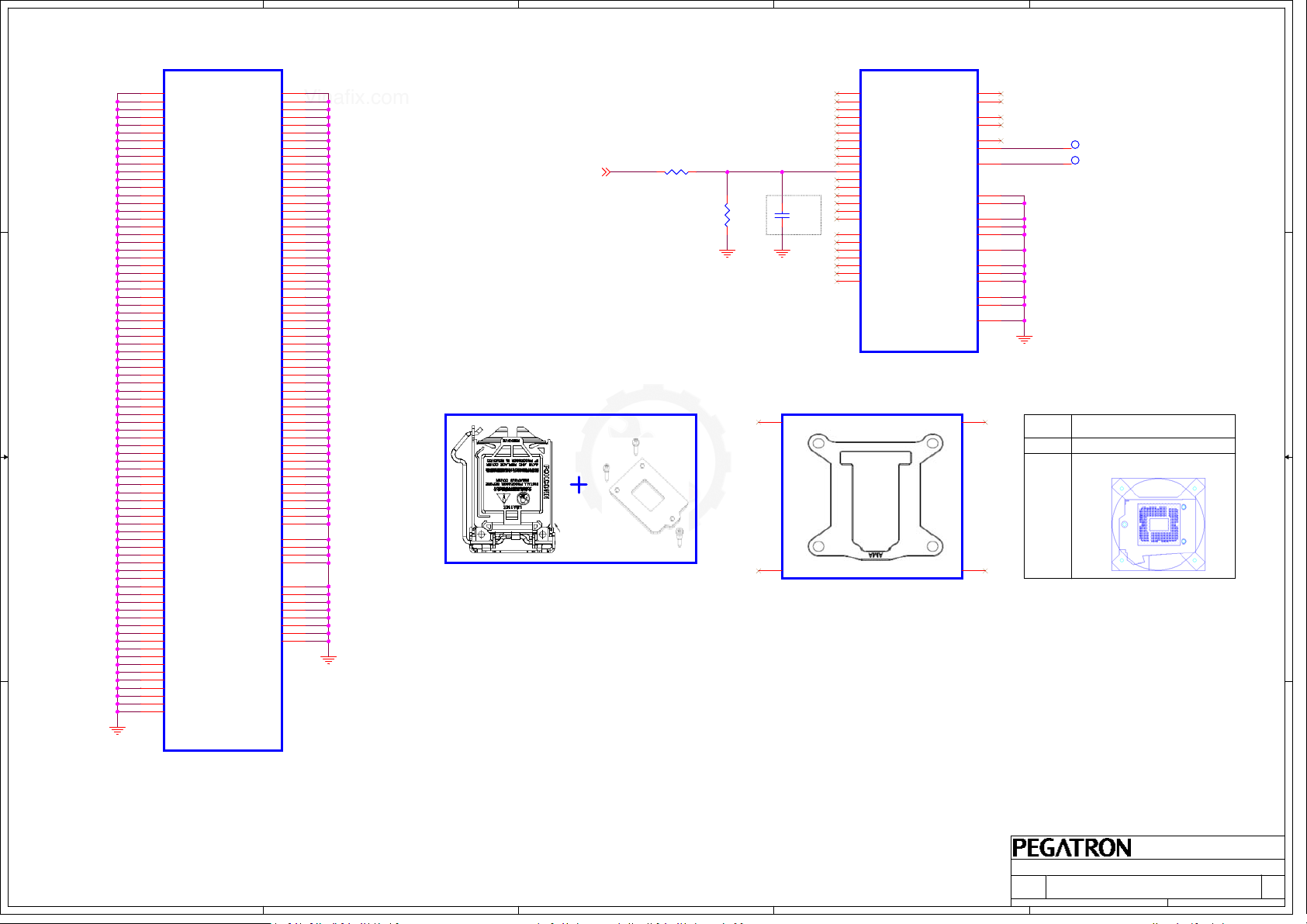

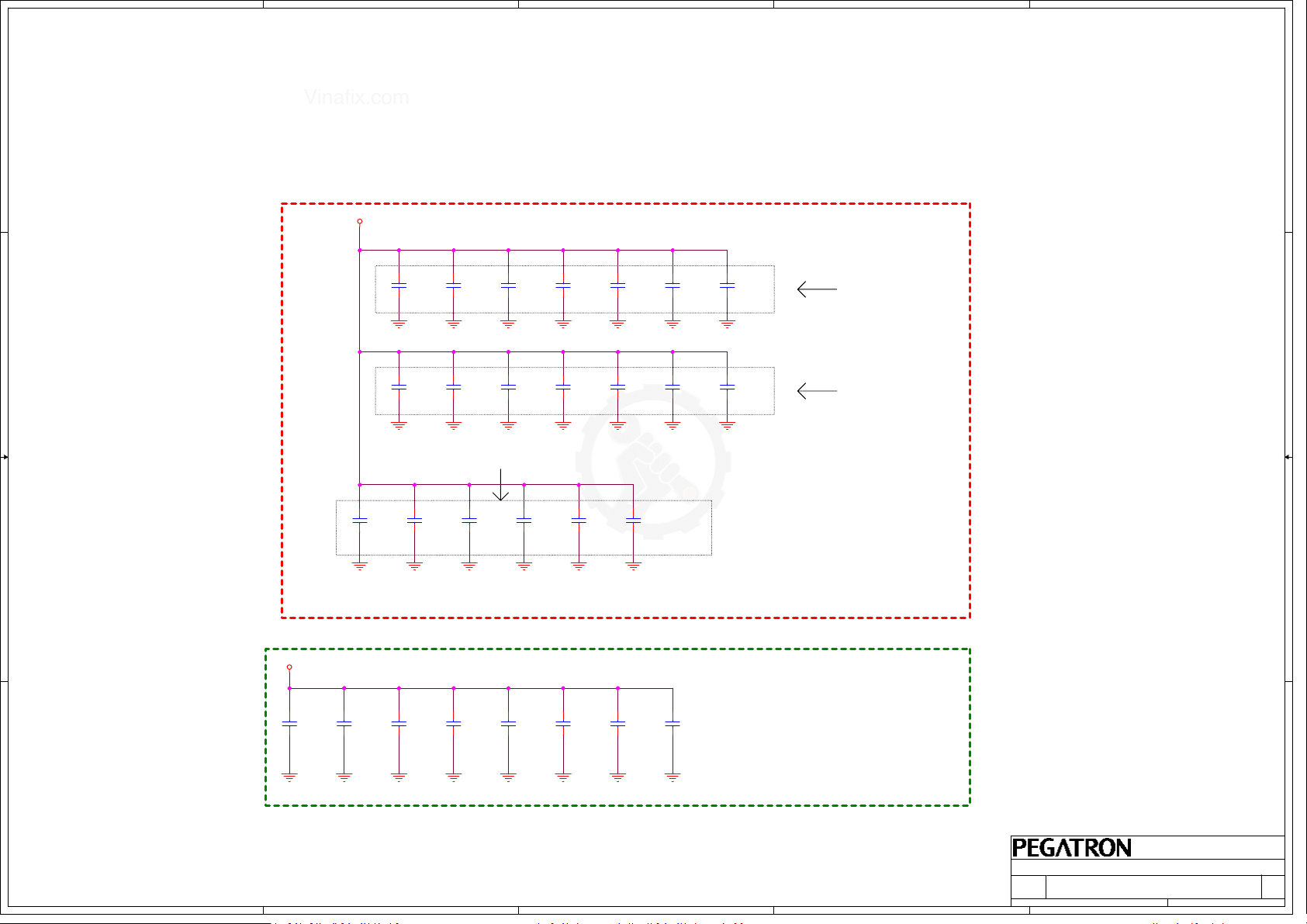

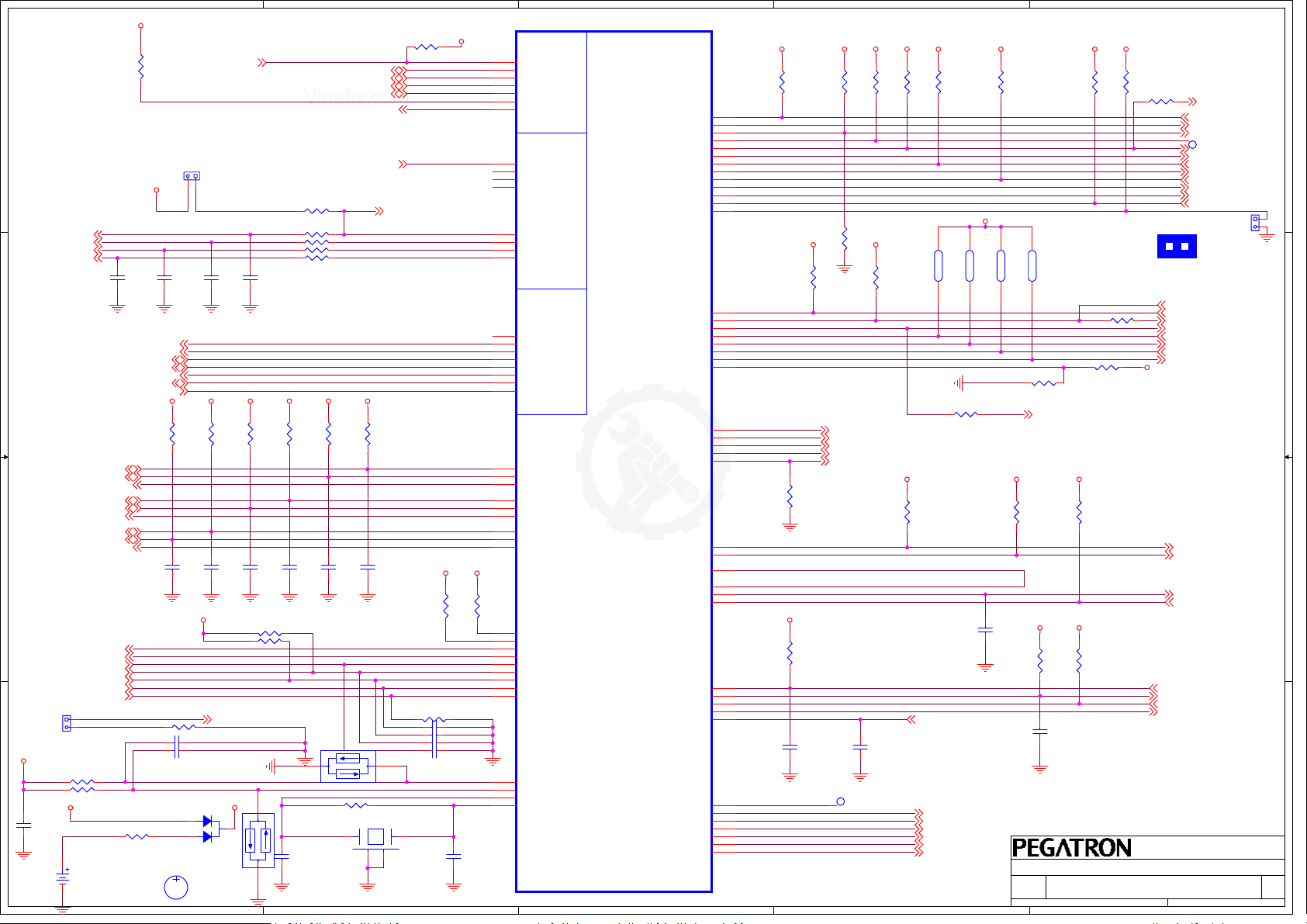

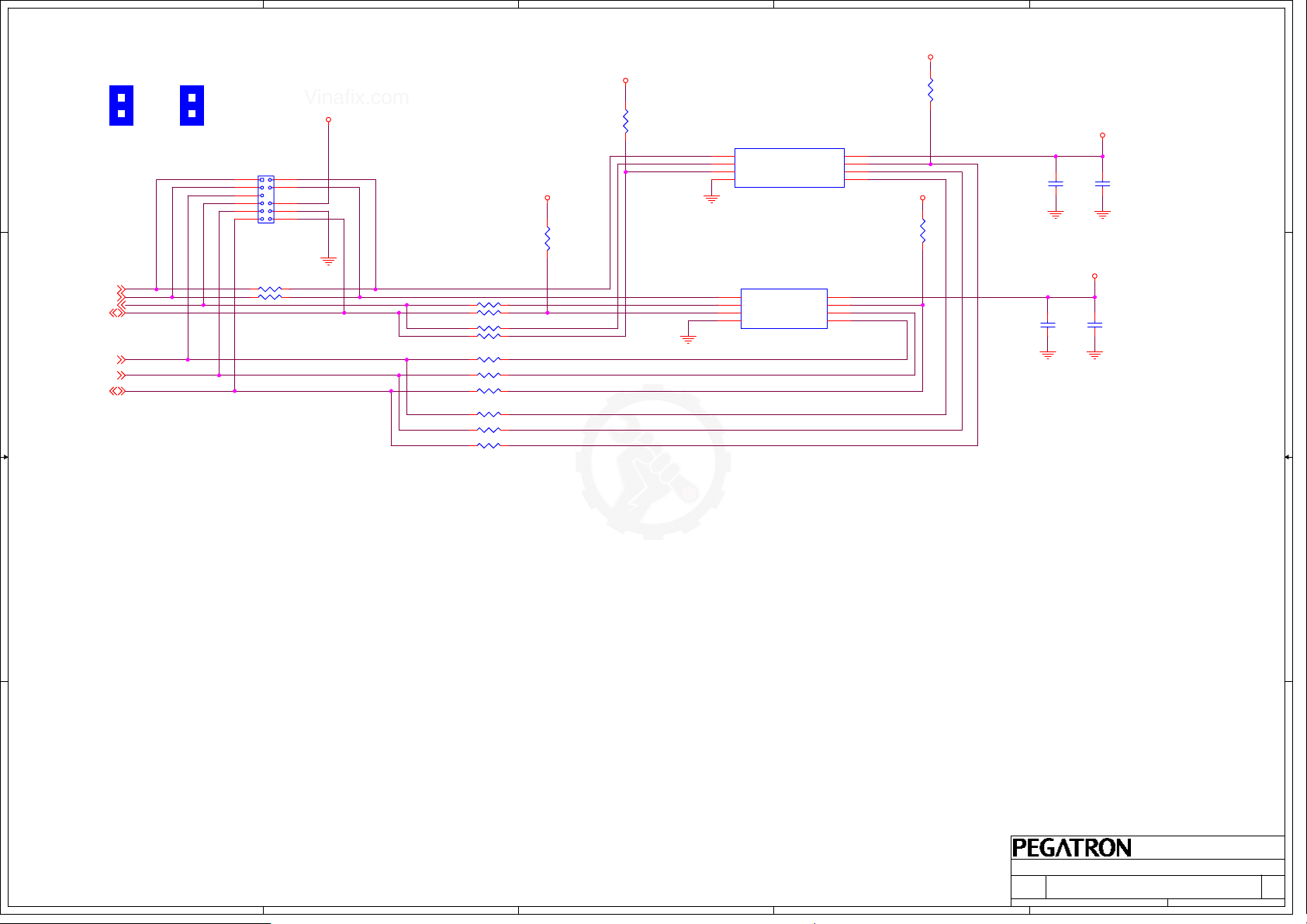

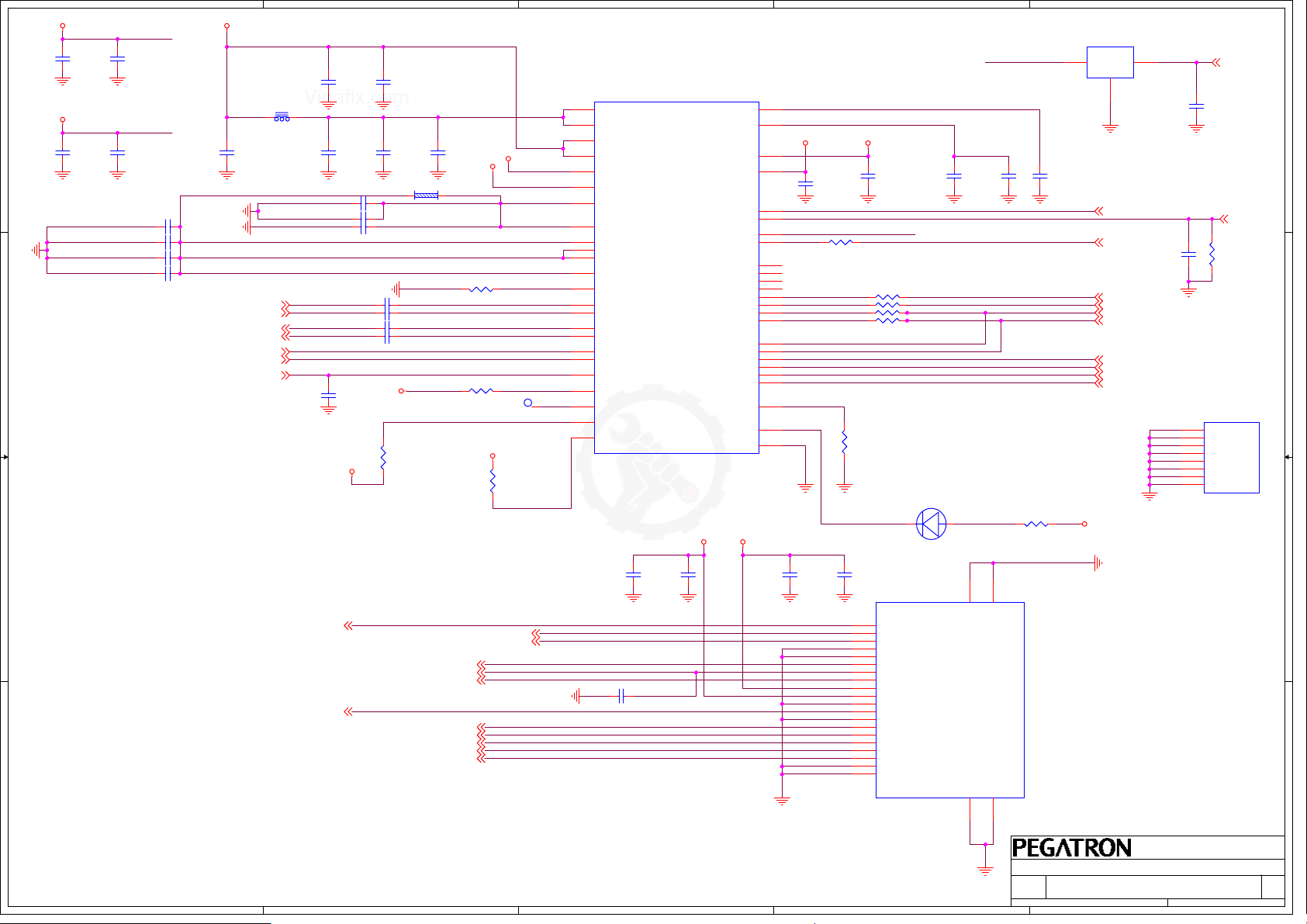

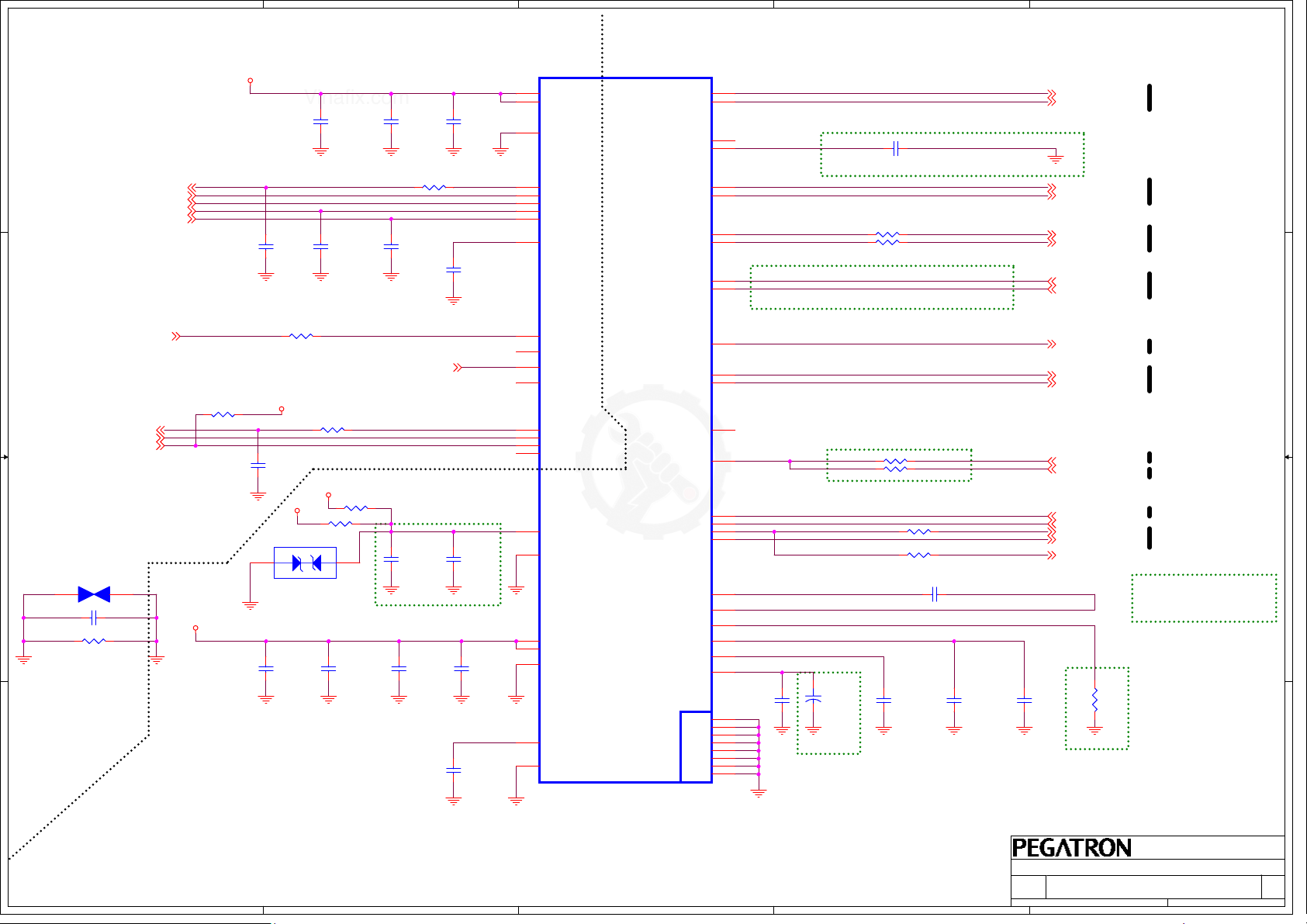

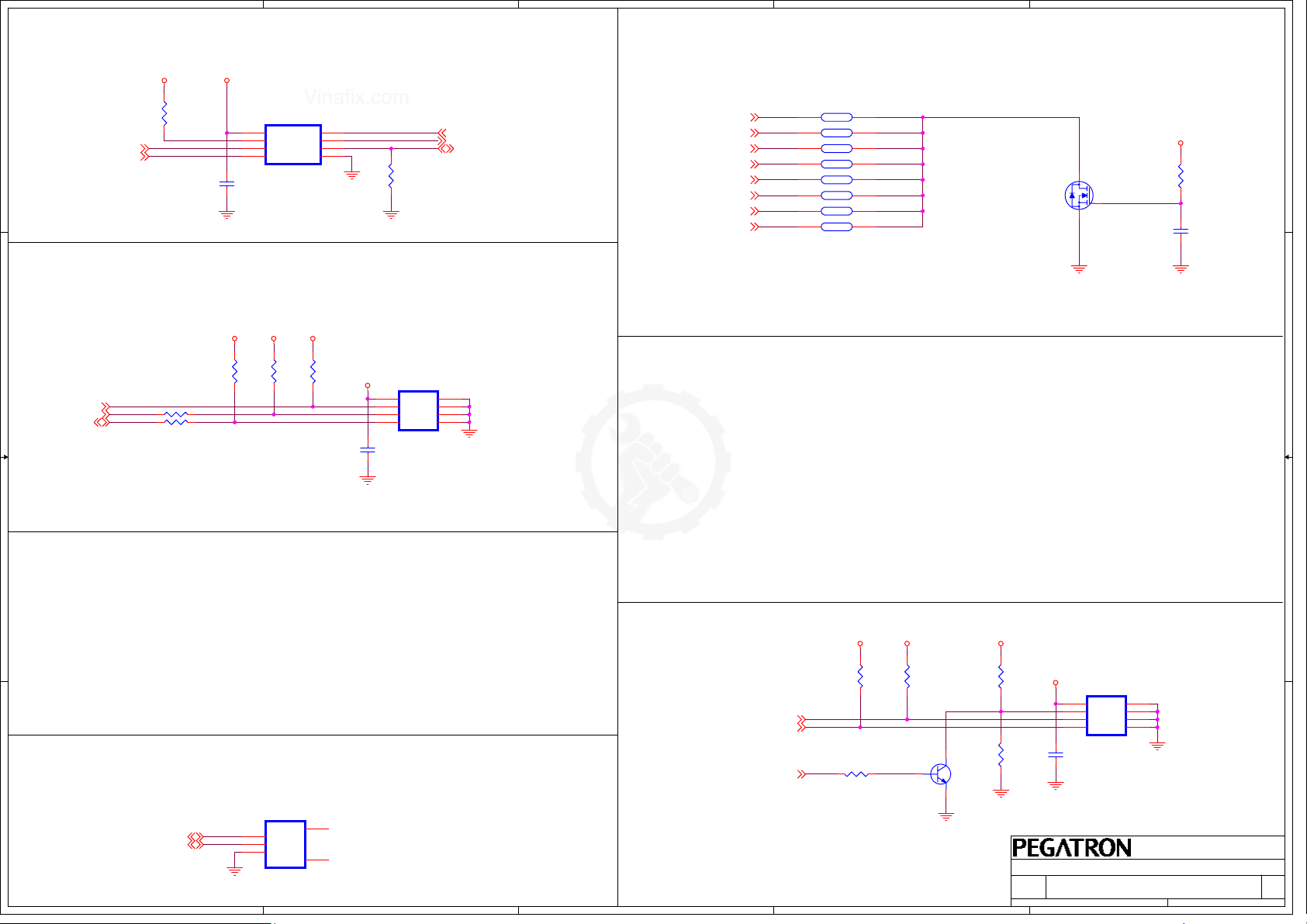

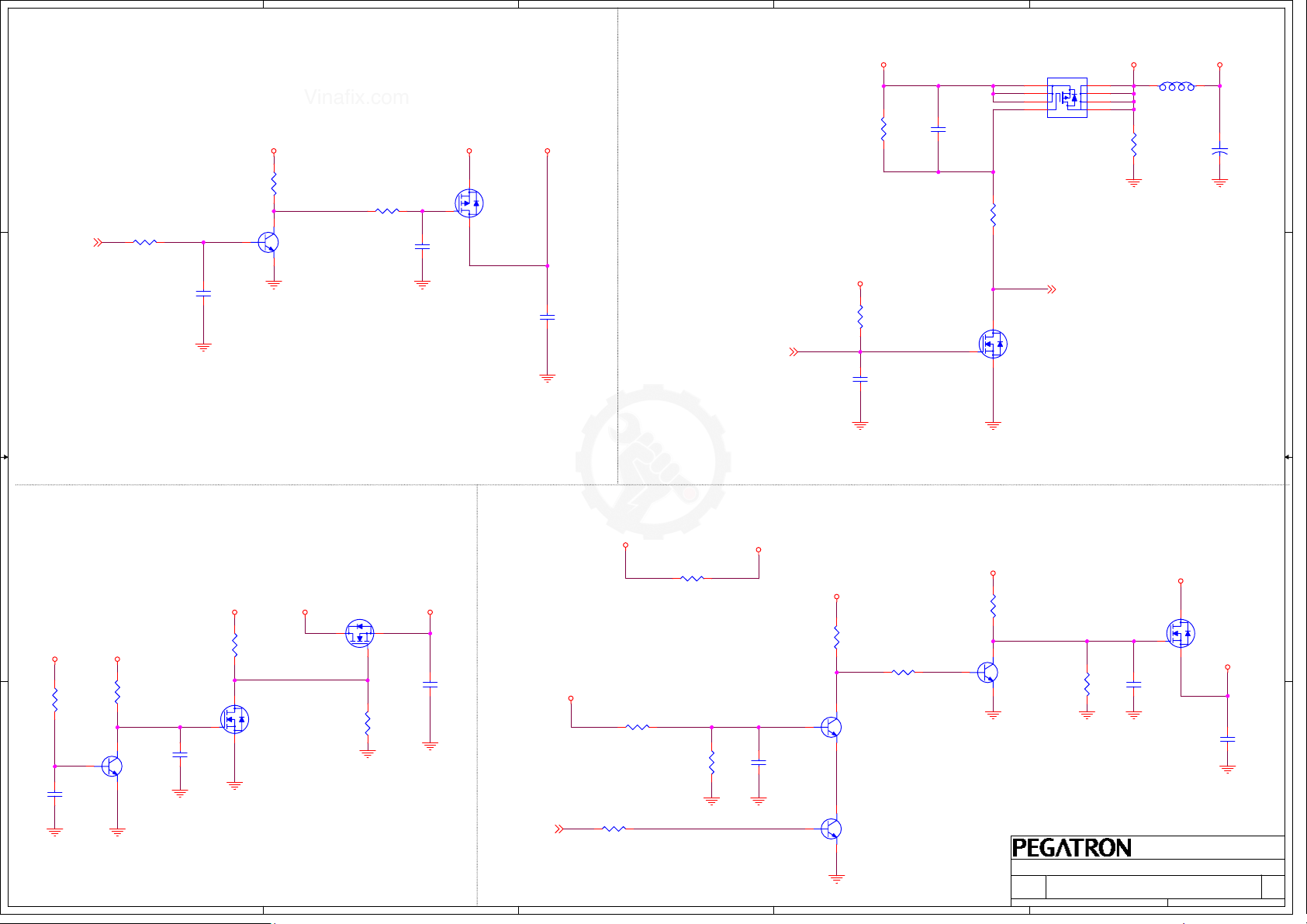

Page 3

Vinafix.com

5

4

3

2

1

LAN 8111E

PERSTB

PCI_Express x 16

<23>PCIE_RST#

<23>PCIE_RST#

PWRGD

D D

PCI_Express x 1

PERST#

PCI_Express x 1

<23>PCIE_RST#

<23>PCIE_RST#

PCIE_RST#

PLTRST#

PERST#

<23>PCIE_RST#

<23>PCIE_RST#

EtronTech EJ168 USB3.0

P_RST_

Card Reader RTS5209-GR

PERST#

LPC DEBUG HEADER

<23>PLTRST_CPU#

Intel AMT 7.0 and DSW supported

RESET_SWITCH

PCH PROCESSOR

POWER_SWITCH

<4>PWRBTN#

ITE Tech SIO IT8772E

PANSWH#

PCIRST1#

HDA_RST#

AZ_RST#

RESET#

PCIRST#

C C

2X12 ATX PSU

<12>PSON#

PSON#

PWROK

B B

<14>ATX_PWRGD

PSON#

ATXPG_IN

LRESET#

KRST# RCIN#

RSMRST#

PWRON# PWRBTN#

SUSB#(S3#) SLP_S3#

SUSC#(S4#)

SUSWARN#

SUSACK#

DPWROK

RST_KB#

<7>RSMRST#

<4>SB_PWRBTN#

<11>SLP_S3#

<10>SLP_S4#

<8>SUS_WARN#

<9>SUS_ACK#

<3>PCH_DPWROK

<15>PWROK

<22>PLTRST#

PLTRST#

RSMRST#

SLP_S4#

SUSWARN#

SUSACK#

DPWROK

PWROK

DRAMPWROK

RTCRST#

PROCPWRGD

<1>RTCRST#

CPU SVID buffers are Hi-Z once +1P05V_CPUIO is

stable and UNCOREPWRGOOD = 0

PWRGD3

APWROK

<5>SLP_SUS#

SLP_SUS#

AUDIO

ALC663-VA4

SYS_RESET#

<16>DRAM_PWROK

BATTERY

<17>CPUPWRGD

<15~20>SVIDs

DBR#SYS_RESET#

RESET#

SM_DRAMPWROK

UNCOREPWRGOOD

VIDSOUT/VIDSCLK

VCORE

<13>

RT8204LGQW

ONBOARD POWER

STANDBY POWER

<6>

+5VSB

APWROK

SYS_PWROK

<21>VRM_PWRGD

+3P3VSB

A A

CHIP

<2>+5VA

RT8239CGQW

SOCKET or SLOT

5

4

3

Vcore Controller

VDIO/VCLK

VR_RDY

RT8859AGQW

VCORE

EN

2

<20>VCORE

<13>+1P05V_CPUIO

<CORE DESIGN>

<CORE DESIGN>

<CORE DESIGN>

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPPLP-TH

IPPLP-TH

IPPLP-TH

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

SIGNAL&RESET MAP

SIGNAL&RESET MAP

SIGNAL&RESET MAP

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

397Friday, January 17, 2014

397Friday, January 17, 2014

397Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

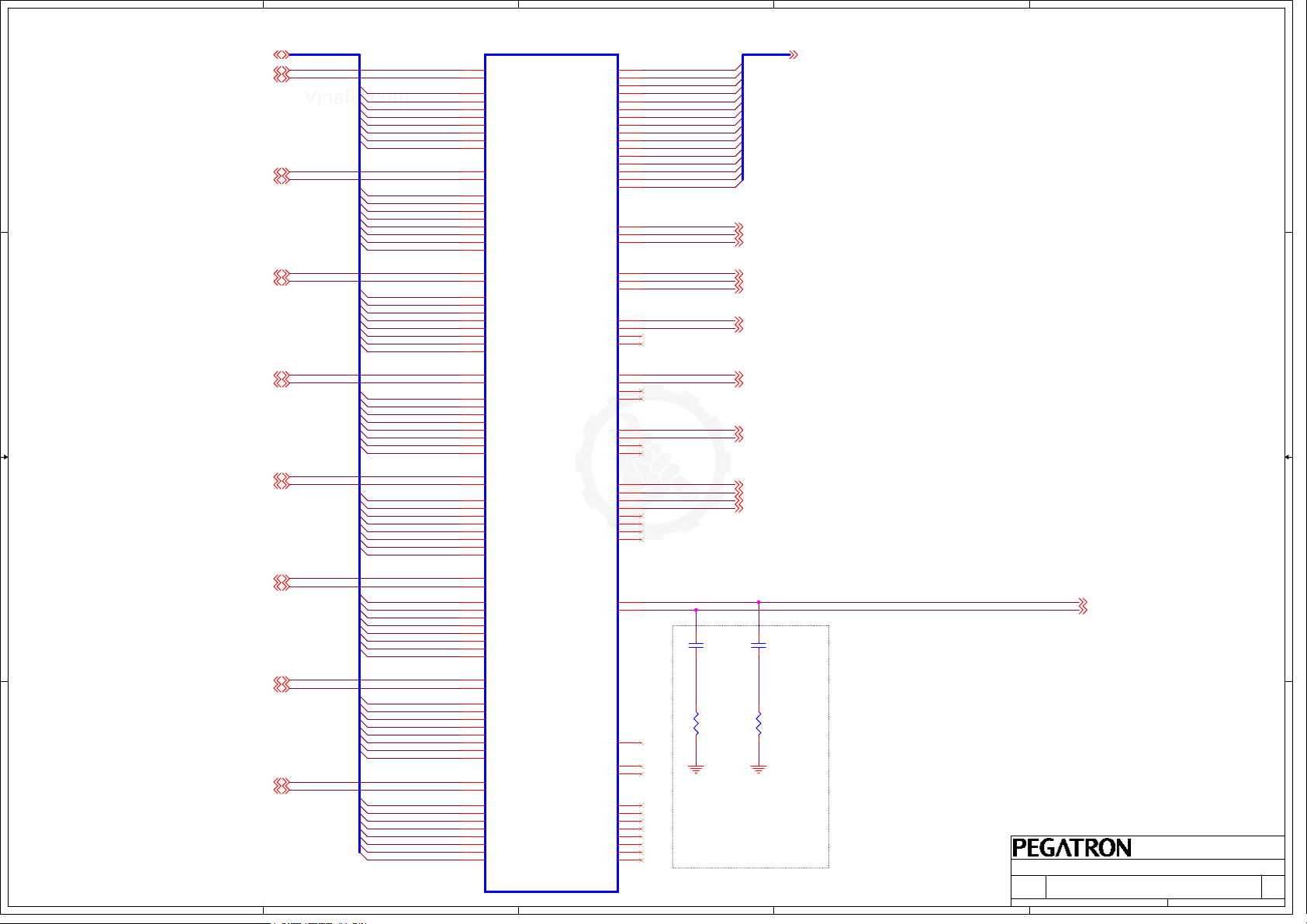

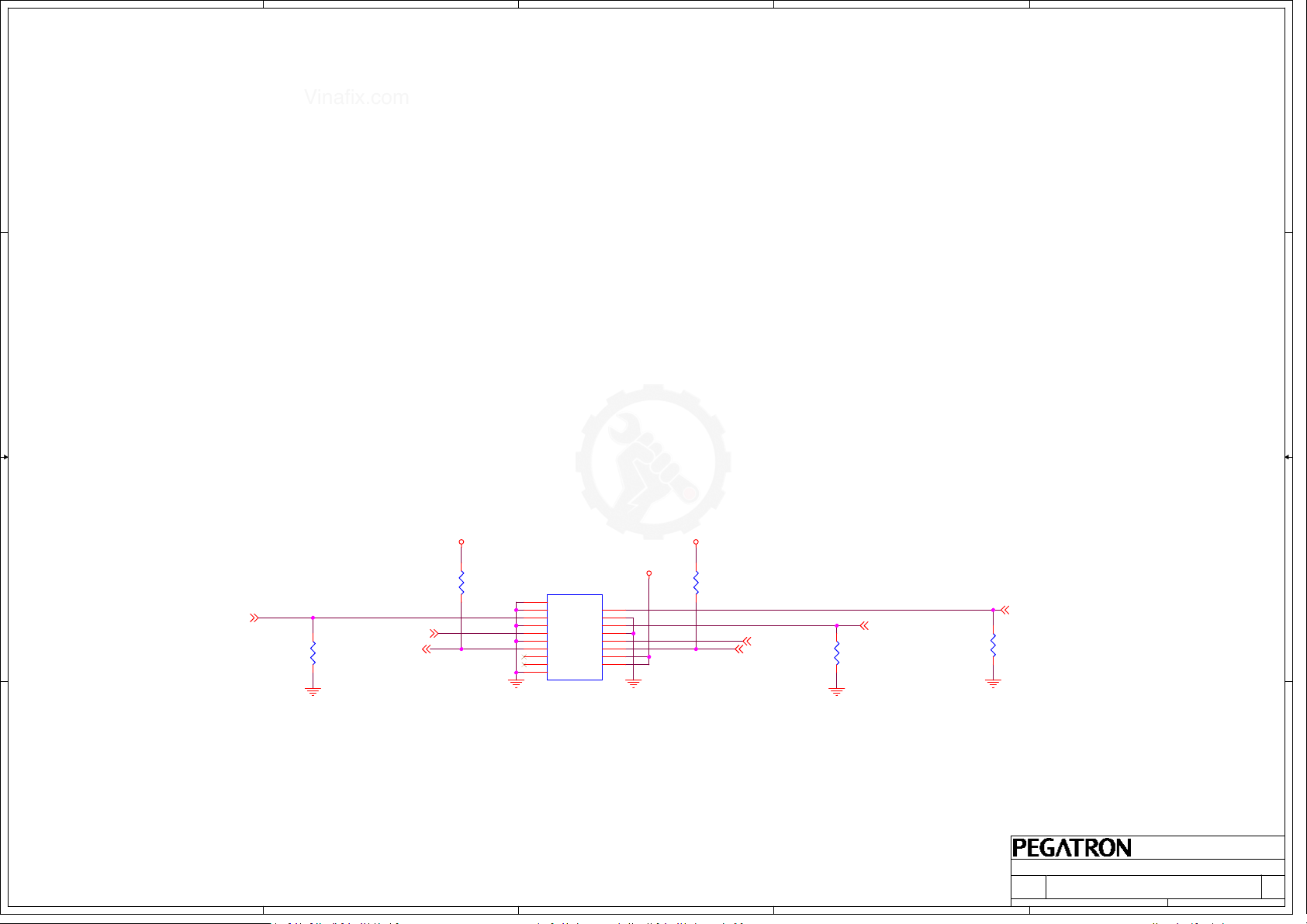

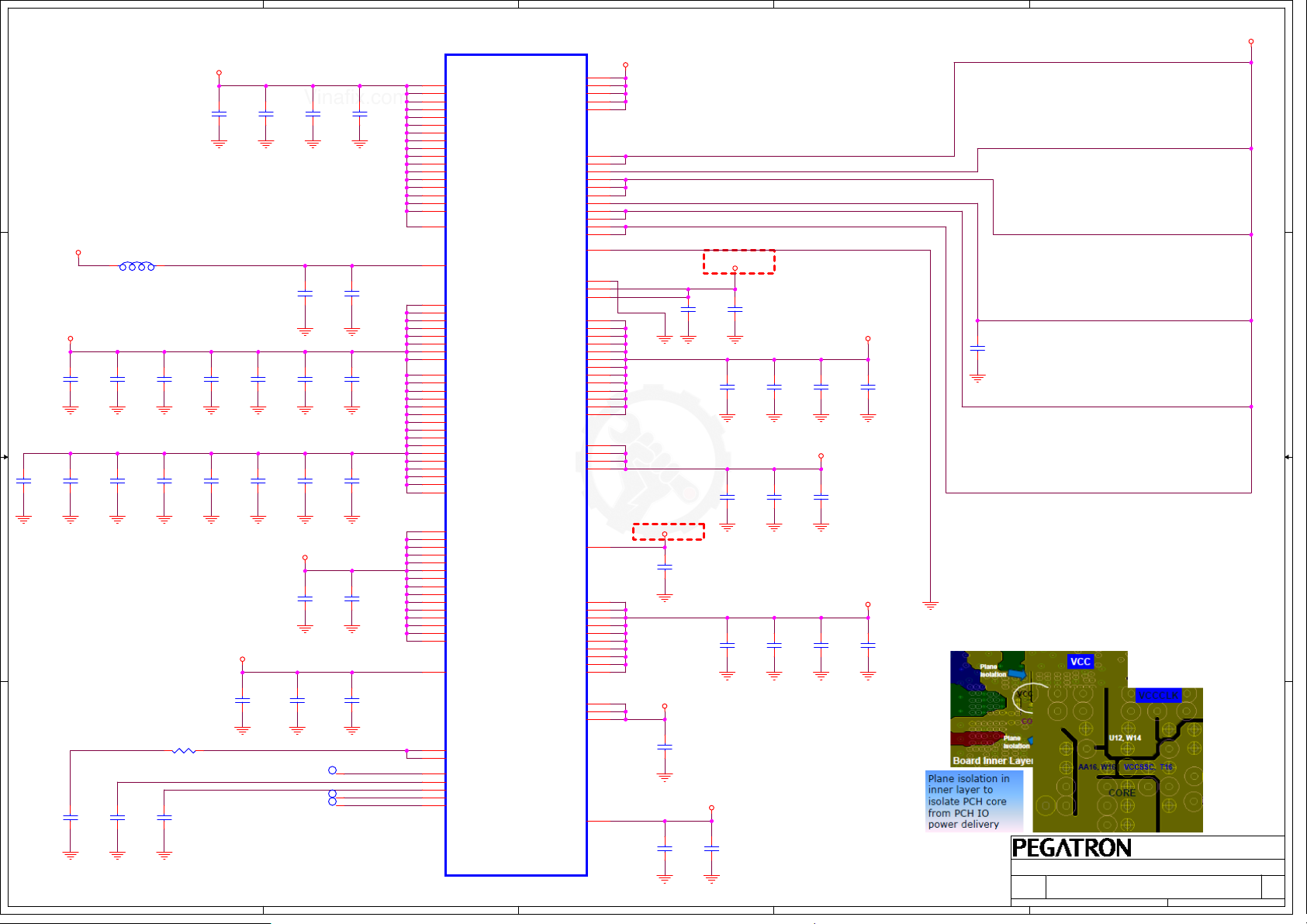

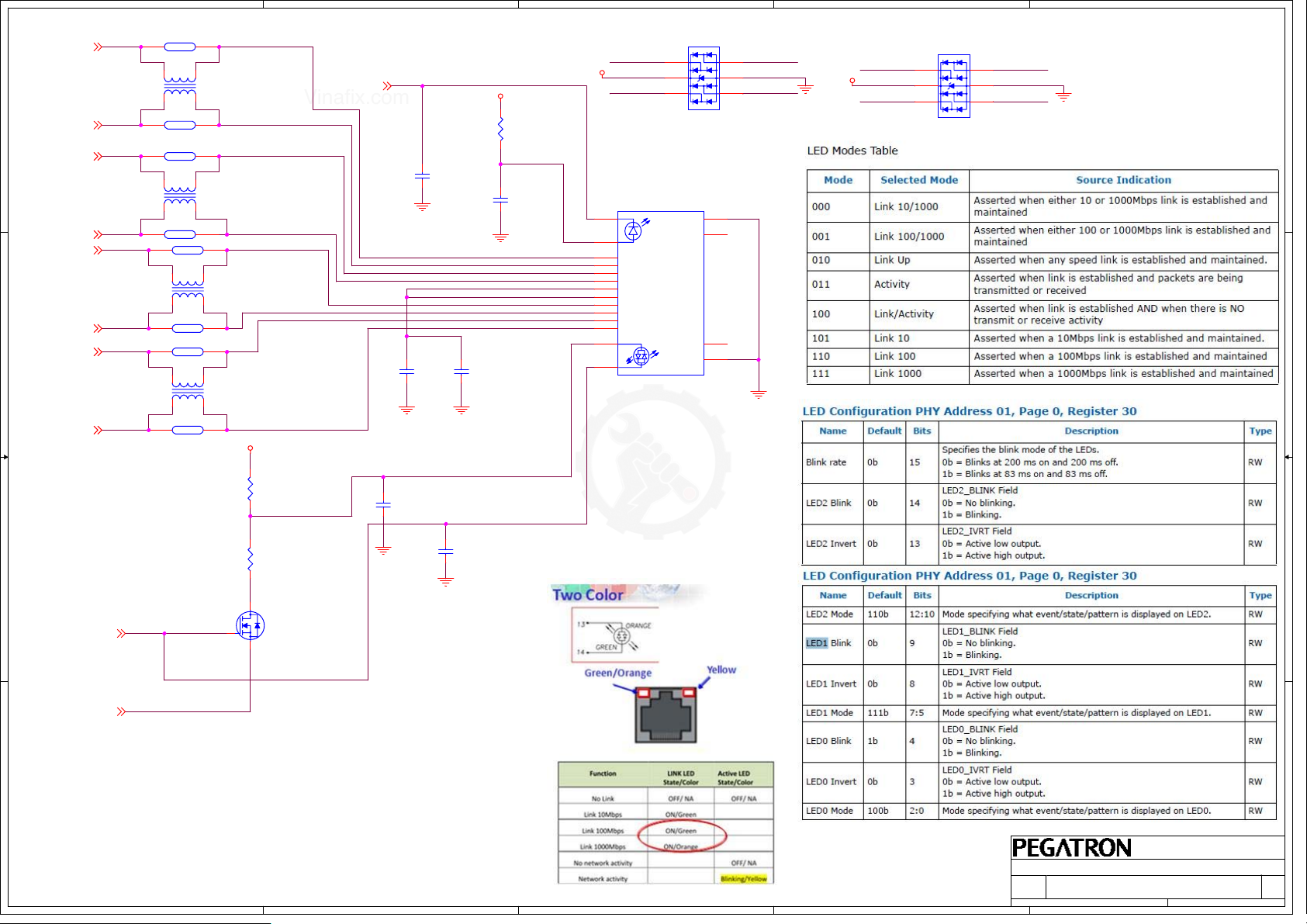

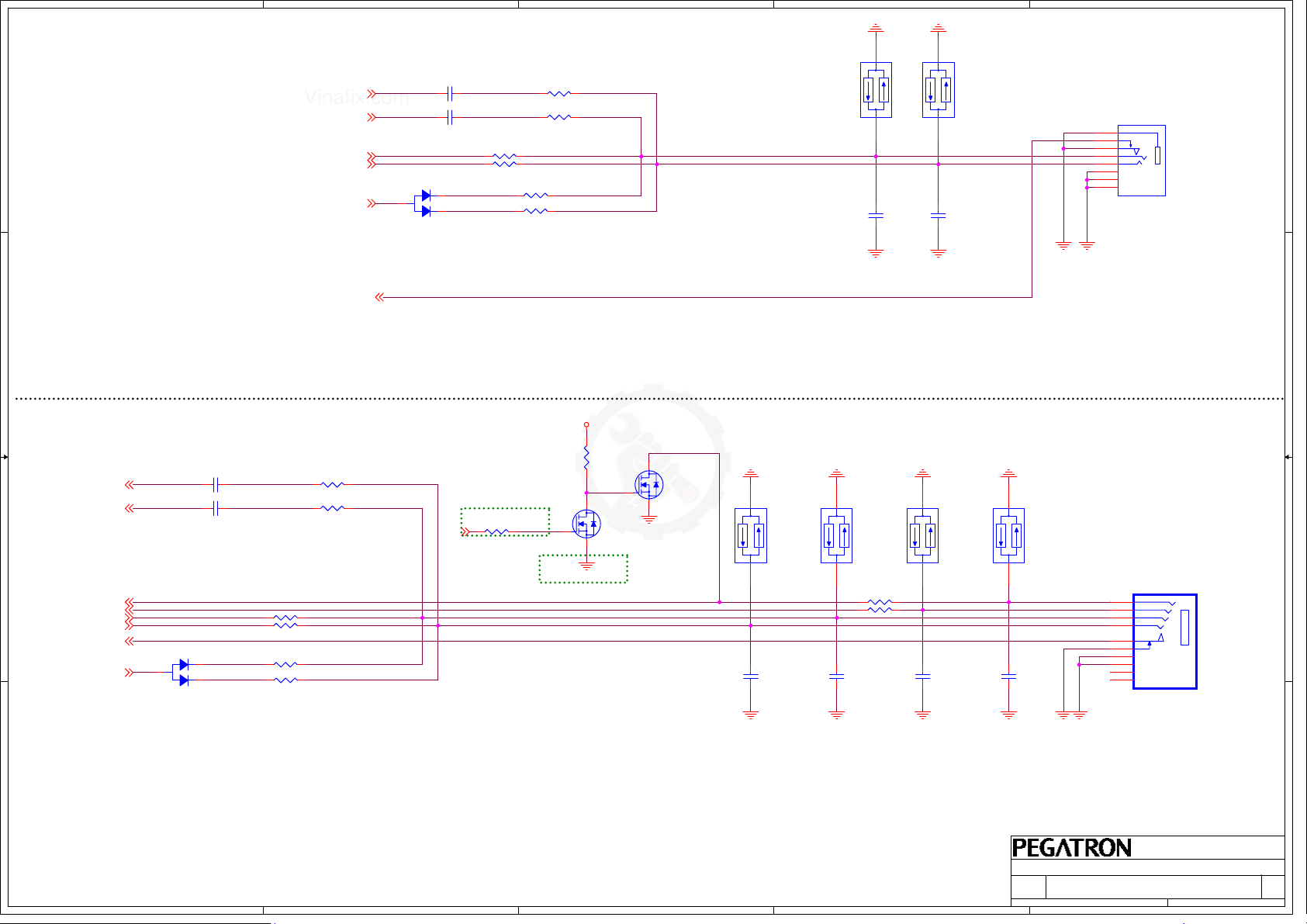

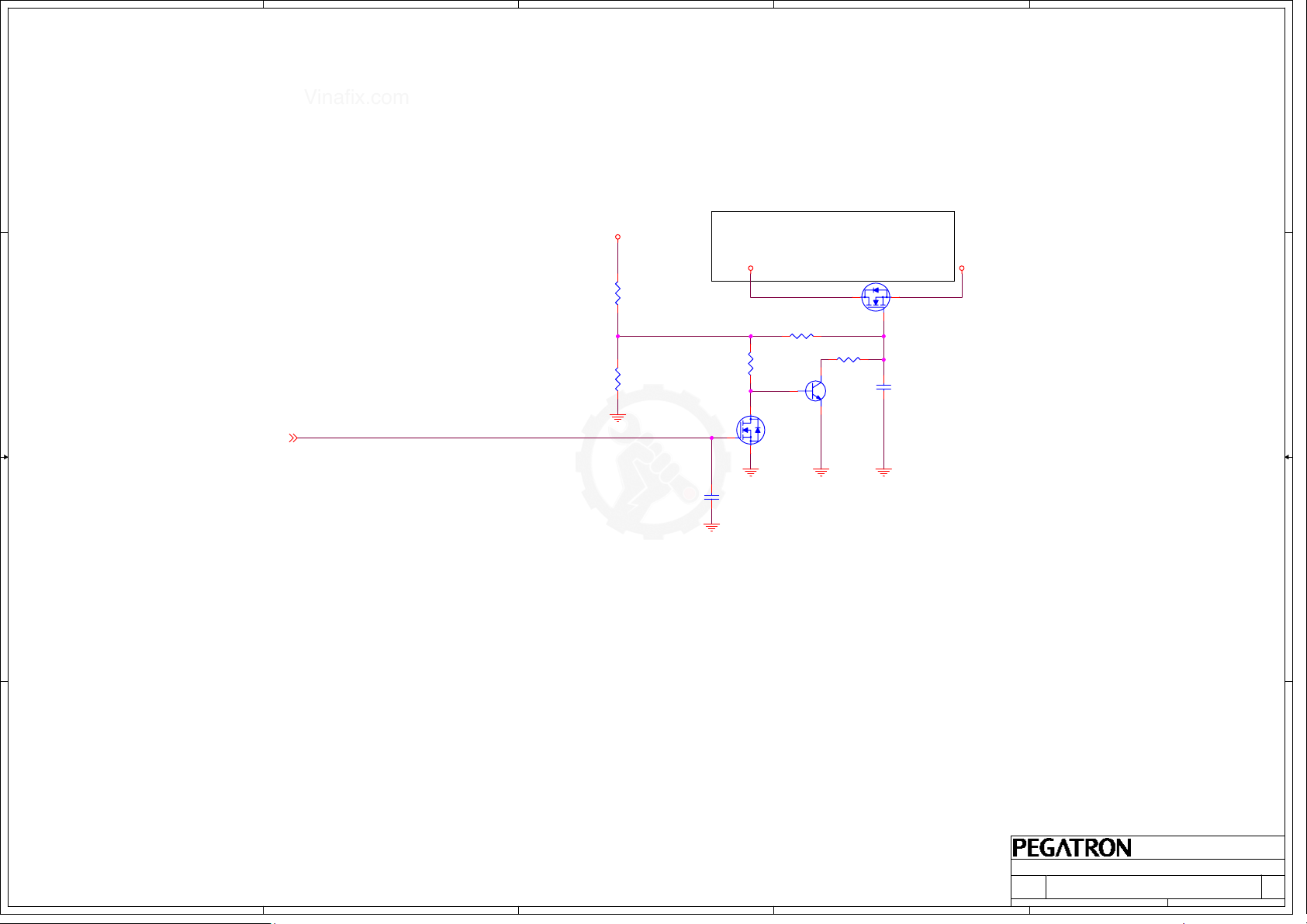

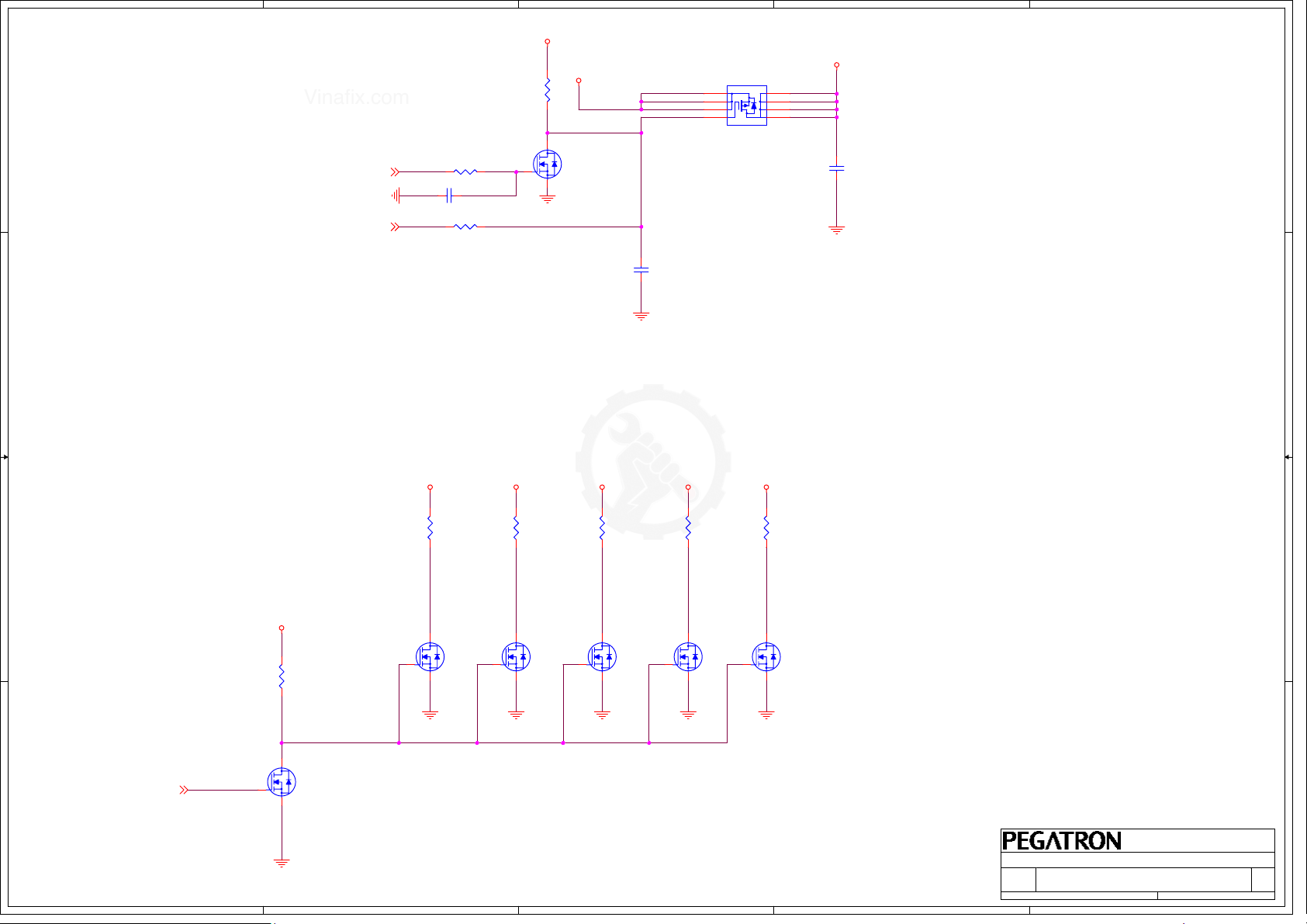

Page 4

Vinafix.com

5

Schematics Change History

4

3

2

1

Version

Date

Comments

2012/11/19 PCIEX16 RVS(20121119_2100)

D D

C C

B B

A A

CAD Note:

Default component footprint is SMD 0402, Y5V, 5% type. Difference footprint show on schematics.

Property: BOM

I = Installed Part.

NI = Not Installed Part.

5

PROTO = PROTO Phase Only.

VP = Virtual Part.

4

3

2

<CORE DESIGN>

<CORE DESIGN>

<CORE DESIGN>

PEGATRON DT-MB RESTRICTED SECRET

CHANGE HISTORY

CHANGE HISTORY

CHANGE HISTORY

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPPLP-TH

IPPLP-TH

IPPLP-TH

Engineer:

1

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

497Friday, January 17, 2014

497Friday, January 17, 2014

497Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 5

Vinafix.com

5

4

3

2

1

+12V_CPU

D D

+12VSA

C C

TPS51631+CSD97374

Vcore:3Phase

TPS51225

H/N-MOS 9mOhmx1

L/N-MOS 6mOhmx1

TPS51225

H/N-MOS 9mOhmx1

L/N-MOS 6mOhmx1

SPDT/Switch

18.62A

SPDT/Switch

14.6A

SPDT/Switch

SPDT/Switch

SPDT/Switch

SPDT/Switch

+VDD Imax=90A/TDC=120A (S0,S1)

+12V Imax=9A/TDC=6.3A (S0,S1)

+5VSB Imax=0.1A (S0~S5)

+5V_DUAL Imax=12.1A/TDC=8.5A

(S0,S1,S3)

+5V Imax=6.42A/TDC=4.5A (S0,S1)

+3P3VA Imax=0.44A/TDC=0.3A

(S0-S5)

+3P3V Imax=8.57A/TDC=6A

(S0,S1)

+3P3V_ME Imax=0.045A (S0,S1)

+3P3V_LAN Imax=0.188A (S0~S5)

SPDT/Switch

SPDT/Switch

B B

TPS51216

H/N-MOS 9mOhmx1

L/N-MOS 6mOhmx2

TPS51216

RT9025

RT9025

+3P3VSB Imax=5.4A/TDC=3.8A

(S0~S5)

+3P3V_BG Imax=0.028A (S0~S5)

+1P5V_DUAL Imax=11.74A/TDC=8.2A

(S0,S1,S3)

+VTT Imax=1.57A/TDC=1.1A (S0,S1)

+1P5V_PCH Imax=0.357A/TDC=0.258A

(S0,S1)

+1P50V_PCH Imax=1A/TDC=0.65A

(S0,S1)

+1P22V Imax=0.4A/TDC=0.28A

(S0,S1)

0.62A

A A

RT8153

H/N-MOS 9mOhmx2

L/N-MOS 6mOhmx2

5.3A

+NVVD Imax=37.5A/TDC=25A (S0,S1)

PEGATRON DT-MB RESTRICTED SECRET

POWER FLOW

POWER FLOW

POWER FLOW

Title :

Title :

Switching

SPDT/SwitchLinear

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IPPLP-TH

IPPLP-TH

IPPLP-TH

Title :

Engineer:

Engineer:

Engineer:

1

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

597Friday, January 17, 2014

597Friday, January 17, 2014

597Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 6

Vinafix.com

5

4

3

2

1

D D

+VCORE

VDDQ

VCCST

+1P05V_PCH

+1P05V_PCH

-> 95A(TDC) - 65W

-> 4.2A(Imax) - W

-> 300mA(Imax) - W

PCH Lynx Point

-> 1.312A (VCC)- W

-> 0.306A(VCCCLK) - W

+12V

+3P3V

+3P3VSB

+12V

+3P3V

+3P3VSB

+1P05V_PCH

-> 3.629A(VCCIO) - W

CPU Sandy Bridge

C C

+1V_CPU2PCH

+1P05V_ME

-> 0.004A(V_PROC_IO) - W

-> 0.67A(VCCASW) - W

+3P3VSB

+1P05V_LAN

+1P5V_PCH

PCI Express x 1

-> 5A - 60W

-> 3A - 9.9W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

PCI Express x 16

-> 5.5A - 66W

-> 3.0A - 9.9W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

REALTEK 8111FA

-> 70mA - 231mW

-> 300mA - 315mW

+5V_DUAL_B/F

+5V

+12V

+3P3V_ME

Rear(USB3*4) -> 4A - 20W

Front(USB3*1 USB2*1) -> 2.5A - 12.5W

Internal(USB2) -> 3A - 15W

-> mA - mW

-> mA - mW

-> 1.2A - 14.4W

-> 40mA - 132mW

USB 12 PORTS

HDMI

FANS

SPI

-> 0.183A(VCCVRM) - W

+1P5V_PCH

+3P3V_BG

+3P3V

+3P3V

B B

+3P3V_ME

+3P3VSB

-> 0.0133A(VCC3_3) - W

-> 0.133A(VCC3_3) - W

-> 0.055A(VCCCLK3_3) - W

-> 0.022A(VCCSPI) - W

-> 0.261A(VCCSUS3_3) - W

-> 0.07A(VCCDAC1_5) - W

+3P3V

+5VSB

+3P3V

SIO IT8772E

-> 200mA - mW

ALC663 Codec

-> 45mA - 225mW

-> 25mA - 82.5mW

-> 0.01(VCCSUSHDA)A - W

+3P3VA

+BATT

A A

5

-> 0.015A(VCCDSW3_3) - W

RTC(G3) -> 6uA - 0.0198mW

<CORE DESIGN>

<CORE DESIGN>

<CORE DESIGN>

PEGATRON DT-MB RESTRICTED SECRET

POWER DISTRIBUTION

POWER DISTRIBUTION

POWER DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

IPPLP-TH

IPPLP-TH

IPPLP-TH

Engineer:

1

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

697Friday, January 17, 2014

697Friday, January 17, 2014

697Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 7

Vinafix.com

5

4

3

2

1

S5 to S0 Power Sequence

DPWROK

SLP_SUS#

+5VSB / +3P3VSB

D D

RSMRST#

SUSWARN#

SUSACK#

SLP_LAN#

SLP_A#

+1P05V_ME

SLP_S5#

SLP_S4#

SLP_S3#

APWROK

C C

+12V / +5V

+3P3V

+1P5V_DUAL

+1P05V_CPUIO

+1P8V_SFR

VCCSA_VID

+0P925V_SA

VCORE EN

B B

VIDSCLK / VIDSOUT

VIDALERT#

ATX_PWRGD

BCLK / PCIE CLOCKS

DRAM_PWROK

CPUPWRGD

+VCORE

VRM_PWRGD

A A

PLTRST#

5

DSW exit

30uS

30uS

>1mS

PSU: <=20mS

=500mS

=50mS

UNCOREPWRGOOD must be stable (low) at this time

CPU SVID buffers are Hi-Z once VCCIO is

stable and Uncorepowergood = 0

CPU SVID buffers are Hi-Z once VCCIO is

stable and Uncorepowergood = 0

PSU: 100ms~500ms

4

UNCOREPWRGOOD assertion

VCCSA_VID[0] FINAL

Recommended that +0P925V_SA ramp after +1P05V_CPUIO has ramped to ensure VCCSA_VID[0] is stable

<5mS

Typ 60uS

MISC ACK0/1...

Set VID

slow packet status packet

ACK0/1...

Get Reg

ACK0/1...

<600uS

<1uS

1mS

Min 10 PCIe BCLKs

<5uS

<2mS

3

2

+0P925V_SA FINAL

Pay

load

>400uS

5mS

<5mS

1~100mS

<CORE DESIGN>

<CORE DESIGN>

<CORE DESIGN>

PEGATRON DT-MB RESTRICTED SECRET

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPPLP-TH

IPPLP-TH

IPPLP-TH

Engineer:

1

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

797Friday, January 17, 2014

797Friday, January 17, 2014

797Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 8

Vinafix.com

5

M_CHA_DQ[0..63][15]

M_CHA_DQS0[15]

M_CHA_DQS0#[15]

D D

M_CHA_DQS1[15]

M_CHA_DQS1#[15]

M_CHA_DQS2[15]

M_CHA_DQS2#[15]

C C

M_CHA_DQS3[15]

M_CHA_DQS3#[15]

M_CHA_DQS4[15]

M_CHA_DQS4#[15]

B B

A A

5

M_CHA_DQS5[15]

M_CHA_DQS5#[15]

M_CHA_DQS6[15]

M_CHA_DQS6#[15]

M_CHA_DQS7[15]

M_CHA_DQS7#[15]

4

M_CHA_DQ0

M_CHA_DQ1

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ4

M_CHA_DQ5

M_CHA_DQ6

M_CHA_DQ7

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ12

M_CHA_DQ13

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ18

M_CHA_DQ19

M_CHA_DQ20

M_CHA_DQ21

M_CHA_DQ22

M_CHA_DQ23

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ42

M_CHA_DQ43

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ47

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ50

M_CHA_DQ51

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ58

M_CHA_DQ59

M_CHA_DQ60

M_CHA_DQ61

M_CHA_DQ62

M_CHA_DQ63

4

AE39

AE38

AD38

AD39

AF38

AF39

AD37

AD40

AF37

AF40

AJ39

AJ38

AH40

AH39

AK38

AK39

AH37

AH38

AK37

AK40

AN39

AN38

AM40

AM39

AP38

AP39

AM37

AM38

AP37

AP40

AV36

AU36

AV37

AW37

AU35

AV35

AT37

AU37

AT35

AW35

AV5

AW5

AY6

AU6

AV4

AU4

AW6

AV6

AW4

AY4

AP3

AP2

AR1

AR4

AN3

AN4

AR2

AR3

AN2

AN1

AK3

AK2

AL1

AL4

AJ3

AJ4

AL2

AL3

AJ2

AJ1

AF3

AF2

AG1

AG4

AE3

AE4

AG2

AG3

AE2

AE1

I

XU1A

LGA_1150P

SA_DQS0

SA_DQSN0

SA_DQ0

SA_DQ1

SA_DQ2

SA_DQ3

SA_DQ4

SA_DQ5

SA_DQ6

SA_DQ7

SA_DQS1

SA_DQSN1

SA_DQ8

SA_DQ9

SA_DQ10

SA_DQ11

SA_DQ12

SA_DQ13

SA_DQ14

SA_DQ15

SA_DQS2

SA_DQSN2

SA_DQ16

SA_DQ17

SA_DQ18

SA_DQ19

SA_DQ20

SA_DQ21

SA_DQ22

SA_DQ23

SA_DQS3

SA_DQSN3

SA_DQ24

SA_DQ25

SA_DQ26

SA_DQ27

SA_DQ28

SA_DQ29

SA_DQ30

SA_DQ31

SA_DQS4

SA_DQSN4

SA_DQ32

SA_DQ33

SA_DQ34

SA_DQ35

SA_DQ36

SA_DQ37

SA_DQ38

SA_DQ39

SA_DQS5

SA_DQSN5

SA_DQ40

SA_DQ41

SA_DQ42

SA_DQ43

SA_DQ44

SA_DQ45

SA_DQ46

SA_DQ47

SA_DQS6

SA_DQSN6

SA_DQ48

SA_DQ49

SA_DQ50

SA_DQ51

SA_DQ52

SA_DQ53

SA_DQ54

SA_DQ55

SA_DQS7

SA_DQSN7

SA_DQ56

SA_DQ57

SA_DQ58

SA_DQ59

SA_DQ60

SA_DQ61

SA_DQ62

SA_DQ63

DDR3_A

SA_MA0

SA_MA1

SA_MA2

SA_MA3

SA_MA4

SA_MA5

SA_MA6

SA_MA7

SA_MA8

SA_MA9

SA_MA10

SA_MA11

SA_MA12

SA_MA13

SA_MA14

SA_MA15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS0

SA_BS1

SA_BS2

SA_CS#0

SA_CS#1

SA_CS#2

SA_CS#3

SA_CKE0

SA_CKE1

SA_CKE2

SA_CKE3

SA_ODT0

SA_ODT1

SA_ODT2

SA_ODT3

SA_CK0

SA_CKN0

SA_CK1

SA_CKN1

SA_CK2

SA_CKN2

SA_CK3

SA_CKN3

SM_DRAMRST#

RSVD16

RSVD13

RSVD19

SA_DQS8

SA_DQSN8

SA_ECC_CB0

SA_ECC_CB1

SA_ECC_CB2

SA_ECC_CB3

SA_ECC_CB4

SA_ECC_CB5

SA_ECC_CB6

SA_ECC_CB7

AU13

AV16

AU16

AW17

AU17

AW18

AV17

AT18

AU18

AT19

AW11

AV19

AU19

AY10

AT20

AU21

AU11

AU9

AU12

AV12

AY11

AT21

AU14

AV9

AU10

AW8

AV22

AT23

AU22

AU23

AW10

AY8

AW9

AU8

AY15

AY16

AW15

AV15

AV14

AW14

AW13

AY13

AK22

AW12

AV20

AW27

AV32

AU32

AW33

AV33

AU31

AV31

AT33

AU33

AT31

AW31

3

3

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

M_CHA_MAA14

M_CHA_MAA15

M_CHA_WE# [15]

M_CHA_CAS# [15]

M_CHA_RAS# [15]

M_CHA_BA0 [15]

M_CHA_BA1 [15]

M_CHA_BA2 [15]

M_CHA_CS#0 [15]

M_CHA_CS#1 [15]

M_CHA_CKE0 [15]

M_CHA_CKE1 [15]

M_CHA_ODT0 [15]

M_CHA_ODT1 [15]

M_CHA_CLK0 [15]

M_CHA_CLK0# [15]

M_CHA_CLK1 [15]

M_CHA_CLK1# [15]

2

M_CHA_MAA[0..15] [15]

2

DDR3_DRAMRST# [15]

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

1

DDR3_A 1-6

DDR3_A 1-6

DDR3_A 1-6

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

897Friday, January 17, 2014

897Friday, January 17, 2014

897Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 9

Vinafix.com

5

M_CHB_DQ[0..63][16]

M_CHB_DQS0[16]

M_CHB_DQS0#[16]

D D

M_CHB_DQS1[16]

M_CHB_DQS1#[16]

M_CHB_DQS2[16]

M_CHB_DQS2#[16]

C C

M_CHB_DQS3[16]

M_CHB_DQS3#[16]

M_CHB_DQS4[16]

M_CHB_DQS4#[16]

B B

A A

5

M_CHB_DQS5[16]

M_CHB_DQS5#[16]

M_CHB_DQS6[16]

M_CHB_DQS6#[16]

M_CHB_DQS7[16]

M_CHB_DQS7#[16]

4

M_CHB_DQ0

M_CHB_DQ1

M_CHB_DQ2

M_CHB_DQ3

M_CHB_DQ4

M_CHB_DQ5

M_CHB_DQ6

M_CHB_DQ7

M_CHB_DQ8

M_CHB_DQ9

M_CHB_DQ10

M_CHB_DQ11

M_CHB_DQ12

M_CHB_DQ13

M_CHB_DQ14

M_CHB_DQ15

M_CHB_DQ16

M_CHB_DQ17

M_CHB_DQ18

M_CHB_DQ19

M_CHB_DQ20

M_CHB_DQ21

M_CHB_DQ22

M_CHB_DQ23

M_CHB_DQ24

M_CHB_DQ25

M_CHB_DQ26

M_CHB_DQ27

M_CHB_DQ28

M_CHB_DQ29

M_CHB_DQ30

M_CHB_DQ31

M_CHB_DQ32

M_CHB_DQ33

M_CHB_DQ34

M_CHB_DQ35

M_CHB_DQ36

M_CHB_DQ37

M_CHB_DQ38

M_CHB_DQ39

M_CHB_DQ40

M_CHB_DQ41

M_CHB_DQ42

M_CHB_DQ43

M_CHB_DQ44

M_CHB_DQ45

M_CHB_DQ46

M_CHB_DQ47

M_CHB_DQ48

M_CHB_DQ49

M_CHB_DQ50

M_CHB_DQ51

M_CHB_DQ52

M_CHB_DQ53

M_CHB_DQ54

M_CHB_DQ55

M_CHB_DQ56

M_CHB_DQ57

M_CHB_DQ58

M_CHB_DQ59

M_CHB_DQ60

M_CHB_DQ61

M_CHB_DQ62

M_CHB_DQ63

4

AF35

AF34

AE34

AE35

AG35

AH35

AD34

AD35

AG34

AH34

AL33

AK33

AL34

AL35

AK31

AL31

AK34

AK35

AK32

AL32

AP33

AN33

AN34

AP34

AN31

AP31

AN35

AP35

AN32

AP32

AN28

AN29

AM29

AM28

AR29

AR28

AL29

AL28

AP29

AP28

AN12

AN13

AR12

AP12

AL13

AL12

AR13

AP13

AM13

AM12

AP8

AR8

AR9

AP9

AR6

AP6

AR10

AP10

AR7

AP7

AL8

AM8

AM9

AL9

AL6

AL7

AM10

AL10

AM6

AM7

AG7

AG6

AH6

AH7

AE6

AE7

AJ6

AJ7

AF6

AF7

I

XU1B

LGA_1150P

SB_DQSP0

SB_DQSN0

SB_DQ0

SB_DQ1

SB_DQ2

SB_DQ3

SB_DQ4

SB_DQ5

SB_DQ6

SB_DQ7

SB_DQSP1

SB_DQSN1

SB_DQ8

SB_DQ9

SB_DQ10

SB_DQ11

SB_DQ12

SB_DQ13

SB_DQ14

SB_DQ15

SB_DQSP2

SB_DQSN2

SB_DQ16

SB_DQ17

SB_DQ18

SB_DQ19

SB_DQ20

SB_DQ21

SB_DQ22

SB_DQ23

SB_DQSP3

SB_DQSN3

SB_DQ24

SB_DQ25

SB_DQ26

SB_DQ27

SB_DQ28

SB_DQ29

SB_DQ30

SB_DQ31

SB_DQSP4

SB_DQSN4

SB_DQ32

SB_DQ33

SB_DQ34

SB_DQ35

SB_DQ36

SB_DQ37

SB_DQ38

SB_DQ39

SB_DQSP5

SB_DQSN5

SB_DQ40

SB_DQ41

SB_DQ42

SB_DQ43

SB_DQ44

SB_DQ45

SB_DQ46

SB_DQ47

SB_DQSP6

SB_DQSN6

SB_DQ48

SB_DQ49

SB_DQ50

SB_DQ51

SB_DQ52

SB_DQ53

SB_DQ54

SB_DQ55

SB_DQSP7

SB_DQSN7

SB_DQ56

SB_DQ57

SB_DQ58

SB_DQ59

SB_DQ60

SB_DQ61

SB_DQ62

SB_DQ63

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

SB_ECC_CB0

SB_ECC_CB1

SB_ECC_CB2

SB_ECC_CB3

SB_ECC_CB4

SB_ECC_CB5

SB_ECC_CB6

SB_ECC_CB7

DDR3_B

SB_MA0

SB_MA1

SB_MA2

SB_MA3

SB_MA4

SB_MA5

SB_MA6

SB_MA7

SB_MA8

SB_MA9

SB_MA10

SB_MA11

SB_MA12

SB_MA13

SB_MA14

SB_MA15

SB_WE#

SB_CAS#

SB_RAS#

SB_BS0

SB_BS1

SB_BS2

SB_CS#0

SB_CS#1

SB_CS#2

SB_CS#3

SB_CKE0

SB_CKE1

SB_CKE2

SB_CKE3

SB_ODT0

SB_ODT1

SB_ODT2

SB_ODT3

SB_CK0

SB_CKN0

SB_CK1

SB_CKN1

SB_CK2

SB_CKN2

SB_CK3

SB_CKN3

RSVD7

SB_DQSP8

SB_DQSN8

AL19

AK23

AM22

AM23

AP23

AL23

AY24

AV25

AU26

AW25

AP18

AY25

AV26

AR15

AV27

AY28

AK16

AP16

AM18

AK17

AL18

AW28

AP17

AN15

AN17

AL15

AW29

AY29

AU28

AU29

AM17

AL16

AM16

AK15

AM20

AM21

AP22

AP21

AN20

AN21

AP19

AP20

AB39

AB40

AL20

AN25

AN26

AM26

AM25

AP25

AP26

AL26

AL25

AR26

AR25

3

M_CHB_MAA0

M_CHB_MAA1

M_CHB_MAA2

M_CHB_MAA3

M_CHB_MAA4

M_CHB_MAA5

M_CHB_MAA6

M_CHB_MAA7

M_CHB_MAA8

M_CHB_MAA9

M_CHB_MAA10

M_CHB_MAA11

M_CHB_MAA12

M_CHB_MAA13

M_CHB_MAA14

M_CHB_MAA15

12

HC1

0.022UF/16V

SB_VDQ_RC

X7R/+/-10%

I

12

HR1

24.9 OHM

1%

I

GND GND

NOTE:

Low pass filter to

cancel the noise during

switch

between CPU driven and

on board driven.

3

M_CHB_WE# [16]

M_CHB_CAS# [16]

M_CHB_RAS# [16]

M_CHB_BA0 [16]

M_CHB_BA1 [16]

M_CHB_BA2 [16]

M_CHB_CS#0 [16]

M_CHB_CS#1 [16]

M_CHB_CKE0 [16]

M_CHB_CKE1 [16]

M_CHB_ODT0 [16]

M_CHB_ODT1 [16]

M_CHB_CLK0 [16]

M_CHB_CLK0# [16]

M_CHB_CLK1 [16]

M_CHB_CLK1# [16]

12

HC2

0.022UF/16V

SA_VDQ_RC

X7R/+/-10%

I

12

HR2

24.9 OHM

1%

I

M_CHB_MAA[0..15] [16]

2

DIMM_DQ_VREF_A [15]

DIMM_DQ_VREF_B [16]

1

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

1

DDR3_B 2-6

DDR3_B 2-6

DDR3_B 2-6

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

997Friday, January 17, 2014

997Friday, January 17, 2014

997Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 10

Vinafix.com

5

4

3

2

1

I

XU1C

LGA_1150P

E15

PEG_RXP0

F15

PEG_RXN0

D D

PEG_RXP[0..7][79]

PEG_RXN[0..7][79]

C C

B B

DMI_RXP0[19]

DMI_RXN0[19]

DMI_RXP1[19]

DMI_RXN1[19]

DMI_RXP2[19]

DMI_RXN2[19]

DMI_RXP3[19]

DMI_RXN3[19]

D14

PEG_RXP1

E14

PEG_RXN1

E13

PEG_RXP2

F13

PEG_RXN2

D12

PEG_RXP3

E12

PEG_RXN3

E11

PEG_RXP4

F11

PEG_RXN4

F10

PEG_RXP5

G10

PEG_RXN5

E9

PEG_RXP6

F9

PEG_RXN6

F8

PEG_RXP7

G8

PEG_RXN7

D3

PEG_RXP8

PEG_RXN7 PEG_TXN7

PEG_RXP6

PEG_RXN6

PEG_RXP5

PEG_RXN5

PEG_RXP4

PEG_RXN4

PEG_RXP3

PEG_RXN3

PEG_RXP2

PEG_RXN2

PEG_RXP1

PEG_RXN1

PEG_RXP0

PEG_RXN0

D4

E4

E5

F5

F6

G4

G5

H5

H6

J4

J5

K5

K6

L4

L5

U3

T3

U1

V1

W2

V2

Y3

W3

PEG_RXN8

PEG_RXP9

PEG_RXN9

PEG_RXP10

PEG_RXN10

PEG_RXP11

PEG_RXN11

PEG_RXP12

PEG_RXN12

PEG_RXP13

PEG_RXN13

PEG_RXP14

PEG_RXN14

PEG_RXP15

PEG_RXN15

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

PEG

DMI

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

PEG_RCOMP

PEG_TXP0

PEG_TXN0

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

A12

B12

B11

C11

C10

D10

B9

C9

C8

D8

B7

C7

A6

B6

B5

C5

E1

PEG_TXP7

E2

F2

PEG_TXP6

F3

PEG_TXN6

G1

PEG_TXP5

G2

PEG_TXN5

H2

PEG_TXP4

H3

PEG_TXN4

J1

PEG_TXP3

J2

PEG_TXN3

K2

PEG_TXP2

K3

PEG_TXN2

M2

PEG_TXP1

M3

PEG_TXN1

L1

PEG_TXP0

L2

PEG_TXN0

P3

H_PEG_RCOMP

AA4

AA5

AB3

AB4

AC5

AC4

AC1

AC2

+VCOMP_OUT

12

1%

I

PEG_TXP[0..7] [79]

PEG_TXN[0..7] [79]

HR4

24.9 OHM

NOTE:

W/S=12/15 mil, length<400mil

DMI_TXP0 [19]

DMI_TXN0 [19]

DMI_TXP1 [19]

DMI_TXN1 [19]

DMI_TXP2 [19]

DMI_TXN2 [19]

DMI_TXP3 [19]

DMI_TXN3 [19]

NOBOM

NOBOM

HT2

HT3

FDI_CSYNC[19]

CK_135M_DP#[21]

CK_135M_DP[21]

FDI_INT[19]

1

TP_CPU_RSVD_K11

1

TP_CPU_RSVD_J12

I

XU1D

LGA_1150P

D16

FDI_CSYNC

D18

DISP_INT

U5

SSC_DPLL_REF_CLKN

U6

SSC_DPLL_REF_CLKP

K11

RSVD_TP11

J12

RSVD_TP8

FDI

EDP_DISP_UTIL

DP

FDI_TX0N0

FDI_TX0P0

FDI_TX0N1

FDI_TX0P1

DP_RCOMP

DDIB_TXP0

DDIB_TXN0

DDIB_TXP1

DDIB_TXN1

DDIB_TXP2

DDIB_TXN2

DDIB_TXP3

DDIB_TXN3

DDIC_TXP0

DDIC_TXN0

DDIC_TXP1

DDIC_TXN1

DDIC_TXP2

DDIC_TXN2

DDIC_TXP3

DDIC_TXN3

DDID_TXP0

DDID_TXN0

DDID_TXP1

DDID_TXN1

DDID_TXP2

DDID_TXN2

DDID_TXP3

DDID_TXN3

B14

A14

C13

B13

E16

TP_EDP_DISP_UTIL

R4

CPU_DP_COMPPEG_RXP7

E17

F17

F18

G18

G19

H19

F20

G20

D19

E19

C20

D20

D21

E21

C22

D22

B15

C15

A16

B16

B17

C17

A18

B18

1

+VCOMP_OUT

12

HR3

24.9 OHM

1%

I

DP out

Scalar

HDMI OUT

HT1

NOBOM

DP_TXP0_RD_IN [60]

DP_TXN0_RD_IN [60]

DP_TXP1_RD_IN [60]

DP_TXN1_RD_IN [60]

DP_TXP2_RD_IN [60]

DP_TXN2_RD_IN [60]

DP_TXP3_RD_IN [60]

DP_TXN3_RD_IN [60]

HDMIC_TMDSC_DATA2 [51]

HDMIC_TMDSC_DATA2# [51]

HDMIC_TMDSC_DATA1 [51]

HDMIC_TMDSC_DATA1# [51]

HDMIC_TMDSC_DATA0 [51]

HDMIC_TMDSC_DATA0# [51]

HDMIC_TMDSC_CLK [51]

HDMIC_TMDSC_CLK# [51]

HDMI_TXP2 [57]

HDMI_TXN2 [57]

HDMI_TXP1 [57]

HDMI_TXN1 [57]

HDMI_TXP0 [57]

HDMI_TXN0 [57]

HDMI_CLKP [57]

HDMI_CLKN [57]

D1

RSVD_TP7

RSVD_TP5

RSVD_TP4

RSVD_TP1

A A

TP_H_RSVD_D1

C2

TP_H_RSVD_C2

B3

TP_H_RSVD_B3

A4

TP_H_RSVD_A4

1

HT4

HT5

HT6

HT7

NOBOM

NOBOM

NOBOM

NOBOM

1

1

1

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

1

PCIE/DMI/DP 3-6

PCIE/DMI/DP 3-6

PCIE/DMI/DP 3-6

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

10 97Friday, January 17, 2014

10 97Friday, January 17, 2014

10 97Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 11

Vinafix.com

5

+1V_CPUIOOUT

12

HR12

90.9Ohm

1%

D D

NOTE:

C C

The 20 CFG[19:0] signals should be length matched as a

group to within 25ps of flight time.

Stub on these nets should be limited to

less than 50ps in length.

VIDSCLK[64]

VIDSOUT[64]

VIDALERT#[64]

1 2

XDP_PLTRST_CPU#[76]

PLTRST_CPU#[20]

CPUPWRGD[22]

DRAM_PWROK[22]

1 2

XDP_CPUPWRGD#[76]

R1 0 Ohm PROTO

PECI_SIO[44]

CATERR#[49]

PROCHOT#[44,64]

H_THMTRIP#[20,80]

PM_SYNC[20]

SKTOCC#[22]

PROTO

HR10 1K 1%

mx_r0402_small

12

I

12

HR18

10KOhm

1%

GND GND

GND GND

NOTE:

CFG[17:0] are internal PU

CFG[1:0]: Reserved configuration

lane.

CFG[2]: PCIE* Static x16 Lane

Numbering Reversal.

x1 = Normal operation

x0 = Lane numbers reversed.

CFG[3]: PCIE* Static x4 Lane

Numbering Reversal.

x1 = Normal operation

B B

x0 = Lane numbers reversed

CFG[4]: Reserved configuration

lane.

CFG[6:5]: PCIE* Bifurcation:

x00 = 1 x8, 2 x4 PCIE*

x01 = reserved

x10 = 2 x8 PCIE*

x11 = 1 x16 PCIE*

CFG[19:7]: Reserved configuration

lanes.

A A

HSW_STRAP[22,77]

5

PRIVACY_MSR_EN_N[76]

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

NI

GND

CPU_CFG[0..15][76]

mx_r0402_small

HR29 1KOhm

HR30 1KOhm

HR31 1K 1%Imx_r0402_small

HR32 1KOhm

HR33 1KOhm

HR34 1KOhm

HR35 1KOhm

HR36 1KOhm

HR38 1KOhm

HR37 1KOhm

HR39 1KOhm

HR40 1KOhm

HR41 1KOhm

HR42 1KOhm

HR44 1KOhm

HR45 1KOhm

HR46 1KOhm

HR47 1KOhm

HR48 1KOhm

HSW_PCUSTB_DN1[76]

HSW_PCUSTB_DP1[76]

HSW_PCUSTB_DP0[76]

HSW_PCUSTB_DN0[76]

+3P3V

12

NI

HR57

1K

1%

NI

I

12

I

HC3

47PF/50V

NPO 5%

X7R/+/-10%

NI

12

NI

SC138

10PF/50V

NPO/+/-5%

GND

PROTO

SR633 1K 1%

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

NI

HR59

10K

1 2

12

HR5

110 Ohm

HC4

0.1UF/16V

H_CFG13

4

12

1%

I

+1P5V_DUAL

12

12

12

I

12

B

1

4

HR6

75 OHM

I

HR14

1.8KOHM

1%

I

HR19

3.3KOHM

1%

HR23

51 OHM

+3P3VSB

12

GND

1 2

HR13

44.2 OHM

1%

I

+1V_CPUIOOUT

12

PROTO

HR24

1K

1%

mx_r0402_small

NOBOM

NOBOM

NI

HR55

10K

H_CFG13#

3

C

NI

HQ2

E

PMBS3904

2

3

I

XU1E

LGA_1150P

AB35

AK21

W6

W5

C38

C37

B37

M39

V4

V5

BCLKN

BCLKP

DPLL_REF_CLKN

DPLL_REF_CLKP

VIDSCLK

VIDSOUT

VIDALERT#

RESET#

PWRGOOD

SM_DRAMPWROK

VCC_SENSE

VSS_SENSE

VCOMP_OUT

PWR_DEBUG

CK_100M_DMI#[21]

CK_100M_DMI[21]

CK_135M_DPNS#[21]

CK_135M_DPNS[21]

CPU_VIDALERT#

12

HR8

100 Ohm

NI

GND

NI

12

HC5

180PF/50V

NPO 5%

GND

VCC126

SM_VREF

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

E40

F40

P4

M8

AB38

N40

F39

F38

TDI

D39

E39

E37

L39

L37

G40

H_DBR#

VCC_SENSE [64]

VSS_SENSE [64]

+VCOMP_OUT

PROTO

+VCORE

1 2

HR20 0

MISC

G39

BPM#0

J39

N37

PECI

M36

CATERR#

K38

PROCHOT#

F37

THERMTRIP#

P36

PM_SYNC

D38

SKTOCC#

AA37

AA36

W38

AA34

W34

W36

Y38

V39

U39

U40

V38

T40

Y35

V37

Y34

U38

V35

Y37

Y36

V36

K8

J10

RSVD_TP19

RSVD_TP20

CFG0

CFG1

CFG2

CFG3

CFG4

CFG5

CFG6

CFG7

CFG8

CFG9

CFG10

CFG11

CFG12

CFG13

CFG14

CFG15

CFG16

CFG17

CFG19

CFG18

3

1

TP_H_RSVD_K8

HT14

1

TP_H_RSVD_J10

HT16

CPU_CFG0

CPU_CFG1

CPU_CFG2

CPU_CFG3

CPU_CFG4

CPU_CFG5

CPU_CFG6

CPU_CFG7

CPU_CFG8

CPU_CFG9

CPU_CFG10

CPU_CFG11

CPU_CFG12

CPU_CFG13

CPU_CFG14

CPU_CFG15

12

NI

HR51

1K

HQ6_C

3

C

B

1

NI

E

HQ1

2

PMBS3904

GND

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

RSVD42

RSVD36

FC_K9

RSVD23

RSVD30

RSVD22

RSVD12

RSVD_TP21

RSVD_TP22

VSS478

VSS479

RSVD_TP13

RSVD_TP10

RSVD3

RSVD_TP3

RSVD_TP2

RSVD5

RSVD43

RSVD2

RSVD46

RSVD34

RSVD32

RSVD35

RSVD33

RSVD45

RSVD39

RSVD38

RSVD37

TESTLO_P6

TESTLO_N5

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

CFG_RCOMP

VSS420

RSVD

VSS418

VSS354

VSS414

VSS363

G38

TP_H_BPM#2

H37

TP_H_BPM#3

H38

TP_H_BPM#4

J38

TP_H_BPM#5

K39

TP_H_BPM#6

K37

TP_H_BPM#7

T35

TP_H_RSVD_T35

M38

TP_H_RSVD_M38

K9

H15

TP_H_RSVD_H15

J9

TP_H_RSVD_J9

H14

TP_H_RSVD_H14

AV2

TP_H_RSVD_AV2

J16

TP_H_RSVD_J16

H16

TP_H_RSVD_H16

V7

TP_H_RSVD_V7

AB6

TP_H_RSVD_AB6

K13

TP_H_RSVD_K13

J8

TP_H_RSVD_J8

AB36

TP_H_RSVD_AB36

AW2

TP_H_RSVD_AW2

AV1

TP_H_RSVD_AV1

AC8

TP_H_RSVD_AC8

U8

TP_H_RSVD_U8

AB33

TP_H_RSVD_AB33

Y8

TP_H_RSVD_Y8

M10

TP_H_RSVD_M10

L10

TP_H_RSVD_L10

M11

TP_H_RSVD_M11

L12

TP_H_RSVD_L12

W8

TP_H_RSVD_W8

R33

TP_H_RSVD_R33

P33

TP_H_RSVD_P33

N35

1P05V_PECI_VCOM

P6

CPU_TESTLOW1

N5

CPU_TESTLOW2

R1

CPU_SM_RCOMP_0

P1

CPU_SM_RCOMP_1

R2

CPU_SM_RCOMP_2

H40

H_CFG_RCOMP

N39

T8

N33

J11

M9

J7

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

TP_VSS_T8

NOTE: NC on pin T8

+1P05V_PCH

12

12

GND

HT8

HT9

HT10

HT11

HT12

HT13

HT15

HT17

HT18

HT19

HT20

HT21

HT22

HT23

HT24

HT25

HT26

HT27

HT28

HT29

HT30

HT31

HT32

HT33

HT34

HT35

HT36

HT37

HT38

HT39

HT40

HT41

HR50 49.9 OHM1%I

HR52 49.9 OHM1%I

HR53 100 Ohm 1%I

HR54 75 OHM 1%I

HR56 100 Ohm 1%I

HT42

2

HR7

150 Ohm

1%

I

HR15

10KOhm

NI

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

1 2

1 2

1 2

1 2

1 2

NOBOM

2

1 2

HR9 0

NI

+1V_CPUIOOUT

H_PRDY# [76]

H_PREQ# [76]

SYS_RESET# [22,50,76,77]

HSW_XDP_MBP0 [76]

HSW_XDP_MBP1 [76]

+1V_VCCST

HR49

0 OhmNI

12

1%

I

GNDGND

+1P05V_PCH

12

GND

HR58

49.9 OHM

Date: Sheet of

Date: Sheet of

Date: Sheet of

1

H_SM_VREF [16]

XDP_PWR_DEBUG [76]

12

12

HR16

51 OHM

NI

HR21

51 OHM

PROTO

GNDGND

12

12

HR17

51 OHM

NI

HR22

51 OHM

PROTO

TDO [76]

TDI [76]

TCK [76]

TMS [76]

TRST# [76]

NOTE:

Place near CPU

HC6

1 2

0.1UF/16V

NI

GND

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Title :

Engineer:

Engineer:

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

1

MISC 4-6

MISC 4-6

MISC 4-6

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

11 97Friday, January 17, 2014

11 97Friday, January 17, 2014

11 97Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 12

Vinafix.com

5

I

XU1F

LGA_1150P

RSVD1

VCC21

VCC23

VCC97

VCC96

VCC86

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC83

VCC85

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC116

VCC94

VCC95

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC113

VCC114

VCC118

VCC117

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

VDDQ20

VDDQ21

VDDQ22

VDDQ23

VDDQ24

VDDQ25

VDDQ26

L40

AB8

C31

C33

L16

L15

J35

H33

H35

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J32

J34

K19

K21

K23

K25

K27

K29

K31

M13

K33

K35

L19

L20

L21

L22

L23

L24

L25

L26

L27

L28

L29

L30

L32

L33

M17

M15

M19

M21

M23

M25

M27

M29

M33

AJ12

AJ13

AJ15

AJ17

AJ20

AJ21

AJ24

AJ25

AJ28

AJ29

AJ9

AT17

AT22

AU15

AU20

AU24

AV10

AV11

AV13

AV18

AV23

AV8

AW16

AY12

AY14

AY9

VCCIO_OUT

D D

VCC 70A

C C

B B

A A

+VCORE

+VCORE

G33

B25

B27

B29

B31

B33

G31

B35

C24

C25

C26

C27

C28

C29

C30

C32

C34

C35

D25

D27

D29

D31

E33

D33

E31

D35

E24

E25

E26

E27

E28

E29

E30

E32

E34

E35

G22

G23

G24

G25

G26

G27

G28

G29

G30

G32

G34

G35

H23

H25

H27

H29

H31

L31

L18

L17

J33

A24

A25

A26

A27

A28

A29

A30

J31

F23

F25

F27

F29

F31

F33

F35

L34

P8

VCC127

VCC112

VCC99

VCC98

VCC84

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC62

VCC8

VCC9

VCC10

VCC11

VCC82

VCC12

VCC60

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC22

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC41

VCC30

VCC39

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC40

VCC42

VCC44

VCC45

VCC46

VCC47

VCC48

VCC43

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC61

VCC63

VCC64

VCC65

VCC66

VCC67

VCC68

VCC69

VCC115

+1V_CPUIOOUT

VCCIO_OUT 300mA

R_+1V_CPU2PCH

12

+VCORE

+1P5V_DUAL

X5R/+/-10%

mx_c0603

GND

+1P05V_PCH

VDDQ 4.2A

HR60

1 2

0 Ohm NI

NI

HCB1

4.7UF/6.3V

VP

VP

4

+1V_VCCST

VCCIO2PCH 100mA

+1V_CPU2PCH+1V_VCCST

12

R2 0

mx_r0603

mx_r0603

12

R3 0

+1V_CPU2PCH

GND

12

NI

SCB1

0.1UF/16V

GND

12

NI

SCB2

0.1UF/16V

3

I

XU1G

LGA_1150P

A13

GND

A15

A17

A23

A11

AA3

AA33

AA35

AA38

AA6

AA7

AA8

AB34

AB37

AB5

AB7

AC3

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

AC6

AC7

AD1

AD2

AD3

AD33

AD36

AD4

AD5

AD6

AD7

AD8

AE33

AE36

AE37

AE40

AE5

AE8

AF1

AF33

AF36

AF4

AF5

AF8

AG33

AG36

AG37

AG38

AG39

AG40

AG5

AG8

AH1

AH2

AH3

AH33

AH36

AH4

AH5

AH8

AJ11

AJ14

AJ16

AJ18

AJ19

AJ22

AJ23

AJ26

AJ27

AJ30

AJ31

AJ32

AJ33

VSS2

VSS3

VSS4

VSS5

VSS1

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

A5

VSS6

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

A7

VSS7

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

AJ34

AJ35

AJ36

AJ37

AJ40

AJ5

AJ8

AK1

AK10

AK11

AK12

AK13

AK14

AK18

AK19

AK24

AK25

AK26

AK27

AK28

AK29

AK30

AK36

AK4

AK5

AK6

AK7

AK8

AK9

AL11

AL14

AL17

AL21

AL22

AL24

AL27

AL30

AL36

AL37

AL38

AL39

AL40

AL5

AM1

AM11

AM14

AM15

AM19

AM2

AM24

AM27

AM3

AM30

AM31

AM32

AM33

AM34

AM35

AM36

AM4

AM5

AN10

AN11

AN14

AN16

AN18

AN19

AN22

AN23

AN24

AN27

AN30

AN36

AN37

AN40

AN5

AN6

AN7

AN8

AN9

AP1

2

I

XU1H

LGA_1150P

AP11

GND

GND

AP14

AP15

AP24

AP27

AP30

AP36

AP4

AP5

AR11

AR14

AR16

AR17

AR18

AR19

AR20

AR21

AR22

AR23

AR24

AR27

AR30

AR31

AR32

AR33

AR34

AR35

AR36

AR37

AR38

AR39

AR40

AR5

AT1

AT10

AT11

AT12

AT13

AT14

AT15

AT16

AT2

AT24

AT25

AT26

AT27

AT28

AT29

AT3

AT30

AT32

AT34

AT36

AT38

AT39

AT4

AT5

AT6

AT7

AT8

AT9

AU2

AU25

AU3

AU30

AU34

AU38

AU5

AU7

AV21

AV28

AV3

AV30

AV34

AV38

AV7

AW26

AW3

AW30

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS254

VSS255

VSS256

VSS257

VSS259

VSS260

VSS261

VSS262

VSS272

VSS273

VSS263

VSS264

VSS265

VSS266

VSS267

VSS268

VSS269

VSS271

VSS252

VSS253

VSS270

VSS291

VSS274

VSS275

VSS276

VSS277

VSS278

VSS279

VSS280

VSS281

VSS282

VSS283

VSS285

VSS286

VSS287

VSS288

VSS289

VSS290

VSS301

VSS302

VSS292

VSS293

VSS297

VSS294

VSS295

VSS296

VSS298

VSS299

VSS258

VSS300

VSS303

VSS314

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS312

VSS313

VSS315

VSS316

VSS317

VSS284

VSS318

VSS332

VSS319

AW32

AW34

AW36

AW7

AY17

AY23

AY26

AY27

AY30

AY5

AY7

B24

B26

B28

B30

B34

B36

B4

B8

C4

C6

C12

C14

C16

C18

C19

C21

C23

C36

B10

B23

C3

D9

D11

D13

D15

D17

D2

D23

D24

D26

D28

D30

D34

D36

D37

D5

D6

D7

E7

E8

E10

E18

E3

E20

E22

E23

E36

E38

B32

E6

F1

F32

F12

F14

F16

F19

F21

F22

F24

F26

F28

F30

F34

F36

F4

D32

F7

G9

G11

1

GND

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

1

VCC 5 - 6

VCC 5 - 6

VCC 5 - 6

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

12 97Friday, January 17, 2014

12 97Friday, January 17, 2014

12 97Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 13

Vinafix.com

5

4

3

2

1

I

XU1I

LGA_1150P

G12

VSS320

G13

VSS321

G14

VSS322

G16

VSS324

D D

C C

B B

H11

G17

G21

H13

H22

H32

G36

G37

G15

H10

H17

H18

H20

H21

H24

H26

H28

H30

H34

H36

H39

K10

K14

K18

K20

K22

K24

K26

K28

K30

K34

K36

K40

K17

M12

M14

M18

M16

M20

M22

M24

M26

M28

M30

M32

M34

M37

VSS335

VSS325

VSS326

G3

VSS327

VSS336

VSS341

VSS346

VSS328

VSS329

G6

VSS330

G7

VSS331

VSS323

H1

VSS333

VSS334

VSS337

VSS338

VSS339

VSS340

VSS342

VSS343

VSS344

VSS345

VSS347

VSS348

VSS349

H4

VSS350

H7

VSS351

H8

VSS352

H9

VSS353

J19

VSS357

J20

VSS358

J3

VSS359

J18

VSS356

VSS365

VSS366

J36

VSS360

J37

VSS361

J6

VSS362

K1

VSS364

VSS370

VSS371

VSS372

VSS373

VSS374

VSS375

VSS376

VSS378

VSS379

K4

VSS380

VSS381

K7

VSS382

L7

VSS391

L8

VSS392

L9

VSS393

L11

VSS383

L3

VSS386

L13

VSS384

L14

VSS385

L35

VSS387

L38

VSS389

L6

VSS390

M1

VSS394

VSS369

VSS395

VSS396

VSS398

VSS397

VSS399

VSS400

VSS401

VSS402

VSS403

VSS404

VSS405

VSS406

VSS408

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

VSS_NCTF8

VSS409

VSS410

VSS411

VSS412

VSS413

VSS367

VSS368

VSS415

VSS416

VSS417

VSS423

VSS419

VSS421

VSS422

VSS377

VSS425

VSS426

VSS428

VSS431

VSS432

VSS424

VSS433

VSS388

VSS434

VSS438

VSS439

VSS440

VSS441

VSS443

VSS444

VSS445

VSS407

VSS449

VSS450

VSS451

VSS452

VSS453

VSS442

VSS455

VSS456

VSS457

VSS460

VSS461

VSS462

VSS427

VSS463

VSS464

VSS466

VSS467

VSS468

VSS469

VSS470

VSS471

VSS472

VSS473

VSS474

VSS475

VSS476

VSS477

VSS480

M4

M40

M5

M6

M7

K15

K16

N1

N2

N3

N7

N34

N4

N6

K32

P2

P34

P38

P5

P7

N8

R3

L36

R35

R40

R5

R6

R7

T1

T2

T33

M35

T39

T4

T5

T6

T7

R8

U2

U33

U34

U37

U4

U7

P35

V3

V33

V40

V6

V8

W1

W33

W35

W37

W4

W7

Y33

Y4

Y5

Y6

AU40

AV39

AW38

AY3

B38

B39

C40

D40

GND

I

ILM1

PT44A69-6411

12

VCCST_PWROKVCCST_PWROKVCCST_PWROK

1%

PWROK[20,22,44]

R46.04KOHM

I

EMI

1%

12

R5

2.67KOHM

I

1 2

GND GND

NI

C1

470PF/50V

X7R 10%

NOTE:

The resistirs need near the CPU pin (Within 1.5")

NI

BP1

1

NP_NC1

3

NP_NC3

INTEL_1156_BP

AY18

AW24

AW23

AV29

AV24

AU39

AU27

AU1

AT40

AK20

T34

R34

H12

Y7

J40

J17

J15

1

2

3

4

5

6

7

I

XU1J

LGA_1150P

RSVD20

RSVD18

RSVD17

RSVD15

RSVD14

RSVD11

RSVD10

RSVD9

RSVD8

RSVD6

FC_Y7

RSVD41

RSVD40

RSVD29

RSVD28

RSVD26

RSVD21

NP_NC1

NP_NC2

NP_NC3

NP_NC4

NP_NC5

NP_NC6

NP_NC7

RSVD_TP12

RSVD_TP9

RSVD_TP16

RSVD_TP15

RSVD_TP17

RSVD_TP6

RSVD_TP14

VSS458

VSS430

VSS436

VSS447

VSS465

VSS437

VSS448

VSS459

VSS429

VSS446

VSS435

VSS355

NP_NC2

NP_NC4

K12

J13

P37

N38

R36

C39

N36

U35

P40

R38

T37

V34

R39

T38

U36

P39

T36

R37

J14

2

1

1

GND

NOTE: (CPU)

Part

HT45

NOBOM

HT46

NOBOM

Standard

PE115027_4041_01F_INTEL

mx_socket_1150p

(with 4 screws)

Symbol

4

GND

A A

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

1

VSS 6 - 6

VSS 6 - 6

VSS 6 - 6

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

13 97Friday, January 17, 2014

13 97Friday, January 17, 2014

13 97Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Page 14

Vinafix.com

5

D D

C C

4

3

2

1

+3P3V +3P3V

B B

GPU_DEBUG_VGA_BLU[80]

12

NI

VR32

150

1%

GND

A A

GPU_HSYNC[80]

GPU_DDCVGACLK[80]

12

VR27

2.2KOHM

NI

17

SIDE1

2

2

4

4

6

6

8

8

10

10

12

12

14

14

16

16

18

SIDE2

WtoB_CON_2X8P

GND GND

J214

1

3

5

7

9

11

13

15

NI

+5V

1

3

5

7

9

11

13

15

12

VR39

2.2KOHM

NI

GPU_VSYNC [80]

GPU_DDCVGADATA [80]

GPU_DEBUG_VGA_GRN [80]

12

NI

VR37

150

1%

GND

GPU_DEBUG_VGA_RED [80]

12

NI

VR38

150

1%

GND

PEGATRON DT-MB RESTRICTED SECRET

VGA DEBUG

VGA DEBUG

1

VGA DEBUG

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

14 97Friday, January 17, 2014

14 97Friday, January 17, 2014

14 97Friday, January 17, 2014

Rev

Rev

Rev

A00

A00

A00

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

Page 15

Vinafix.com

5

4

3

2

1

XMM1 9.2H(STD)

D D

I

DIMM1A

GND

GND

12

NI

SC2

150PF/50V

NPO 5%

mx_c0402_small

GNDGND

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM_204P

0

1

2

3

4

5

6

7

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

M_CHA_MAA14

M_CHA_MAA15

M_CHA_CLK1[8]

M_CHA_CLK1#[8]

M_CHA_CLK0[8]

M_CHA_CLK0#[8]

M_CHA_CS#1[8]

C C

B B

9,60,76,77]

9,60,76,77]

A A

SMB_CLK_RESUME

SMB_DATA_RESUME

M_CHA_CS#0[8]

M_CHA_ODT1[8]

M_CHA_ODT0[8]

M_CHA_WE#[8]

M_CHA_RAS#[8]

M_CHA_CAS#[8]

M_CHA_BA2[8]

M_CHA_BA1[8]

M_CHA_BA0[8]

M_CHA_CKE1[8]

M_CHA_CKE0[8]

M_CHA_DQS7[8]

M_CHA_DQS7#[8]

M_CHA_DQS6[8]

M_CHA_DQS6#[8]

M_CHA_DQS5[8]

M_CHA_DQS5#[8]

M_CHA_DQS4[8]

M_CHA_DQS4#[8]

M_CHA_DQS3[8]

M_CHA_DQS3#[8]

M_CHA_DQS2[8]

M_CHA_DQS2#[8]

M_CHA_DQS1[8]

M_CHA_DQS1#[8]

M_CHA_DQS0[8]

M_CHA_DQS0#[8]

NI

SC1

150PF/50V

NPO 5%

mx_c0402_small

12

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

RESET#

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

30

M_CHA_DQ5

M_CHA_DQ4

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ1

M_CHA_DQ0

M_CHA_DQ7

M_CHA_DQ6

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ13

M_CHA_DQ12

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ19

M_CHA_DQ18

M_CHA_DQ21

M_CHA_DQ20

M_CHA_DQ23

M_CHA_DQ22

M_CHA_DQ25

M_CHA_DQ24

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ35

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ39

M_CHA_DQ34

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ43

M_CHA_DQ47

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ42

M_CHA_DQ49

M_CHA_DQ48

M_CHA_DQ55

M_CHA_DQ54

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ51

M_CHA_DQ50

M_CHA_DQ61

M_CHA_DQ60

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ63

M_CHA_DQ62

M_CHA_DQ59

M_CHA_DQ58

12

D3CB6

0.1UF/6.3V

MLCC/+/-10%

GND

I

0~7

8~15

16~23

24~31

32~39

40~47

48~55

56~63

DDR3_DRAMRST#_R [16]

HR61

1 2

0Ohm

5%

NOBOM

M_CHA_MAA[0..15] [8]

M_CHA_DQ[0..63] [8]

DIMM_CA_VREF_A[16]

DIMM_DQ_VREF_A[9]

DDR3_DRAMRST# [8]

1 2

12

GND

+1P5V_DUAL

R6

NI

C3

10UF/6.3V

GND

12

2OHMI

12

I

D3R1

1KOhm

1%

I

D3R3

1KOhm

1%

12

I

D3CB3

0.1UF/6.3V

MLCC/+/-10%

+1P5V_DUAL

12

12

GNDGND

I

D3R2

1K

1%

mx_r0402_small

I

D3R4

1K

1%

mx_r0402_small

DIMM_DQ_VREF_A_R

12

I

D3CB5

0.1UF/6.3V

MLCC/+/-10%

GND

GND

I

DIMM1B

75

VDD1

81

VDD3

87

VDD5

93

VDD7

99

VDD9

105

VDD11

111

VDD13

117

VDD15

123

VDD17

2

VSS1

8

VSS3

13

VSS5

19

VSS7

25

VSS9

31

VSS11

37

VSS13

43

VSS15

48

VSS17

54

VSS19

60

VSS21

65

VSS23

71

VSS25

127

VSS27

133

VSS29

138

VSS31

144

VSS33

150

VSS35

155

VSS37

161

VSS39

167

VSS41

172

VSS43

178

VSS45

184

VSS47

189

VSS49

195

VSS51

198

EVENT#

125

TEST

77

NC1

122

NC2

126

VREFCA

1

VREFDQ

DDR3_DIMM_204P

VDD2

VDD4

VDD6

VDD8

VDD10

VDD12

VDD14

VDD16

VDD18

VSS2

VSS4

VSS6

VSS8

VSS10

VSS12

VSS14

VSS16

VSS18

VSS20

VSS22

VSS24

VSS26

VSS28

VSS30

VSS32

VSS34

VSS36

VSS38

VSS40

VSS42

VSS44

VSS46

VSS48

VSS50

VSS52

GND1

GND2

NP_NC1

NP_NC2

VTT1

VTT2

VDDSPD

76

82

88

94

100

106

112

118

124

3

9

14

20

26

32

38

44

49

55

61

66

72

128

134

139

145

151

156

162

168

173

179

185

190

196

207

208

205

206

203

204

199

C300

10PF/50V

NPO/+/-5%

+1P5V_DUAL+1P5V_DUAL

+VTT_DDR

GND

+3P3V

I

12

C301

10PF/50V

GND

NPO/+/-5%

12

12

D3CB4

0.1UF/6.3V

MLCC/+/-10%

GND

I

GND

I

D3CB1

0.1UF/6.3V

MLCC/+/-10%

12

I

D3CB2

4.7UF/6.3V

MLCC/+/-10%

12

I

GNDGND

PEGATRON DT-MB RESTRICTED SECRET

DDR3 CHANNEL A

DDR3 CHANNEL A

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPPLP-TH

IPPLP-TH

IPPLP-TH

DDR3 CHANNEL A

Shrek_Tseng

Shrek_Tseng

Shrek_Tseng

1

Rev

Rev

Rev

A00

A00

15 97Friday, January 17, 2014

15 97Friday, January 17, 2014

15 97Friday, January 17, 2014

A00

Page 16

Vinafix.com

5

XMM2 5.2H(STD)

D D

I

DIMM2A

M_CHB_MAA0

M_CHB_MAA1

M_CHB_MAA2

M_CHB_MAA3

M_CHB_MAA4

M_CHB_MAA5

M_CHB_MAA6