Page 1

5

4

3

2

1

POS-PIQ57BQ

PAGE

01

02

03

D D

04

05

06

07

08

09

10~15

16

17

18

19

20~28

29

30

31

C C

32

33

34

35

36

37

38

39

40

41

42

43

44

45

B B

46

47

48

49

50

51

52

53

54

55

56

57

58

59

A A

60

61

62

63

64

65

66

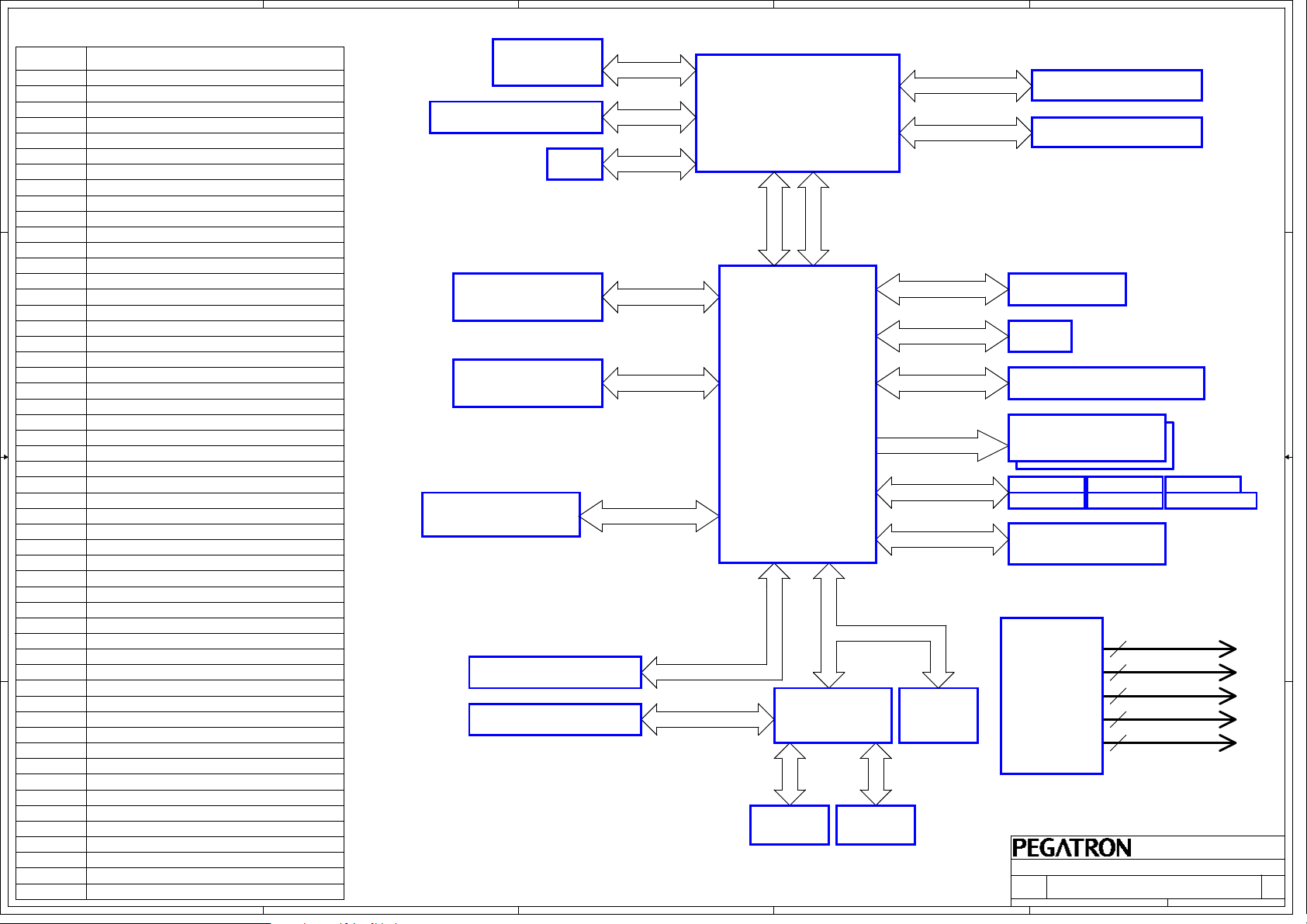

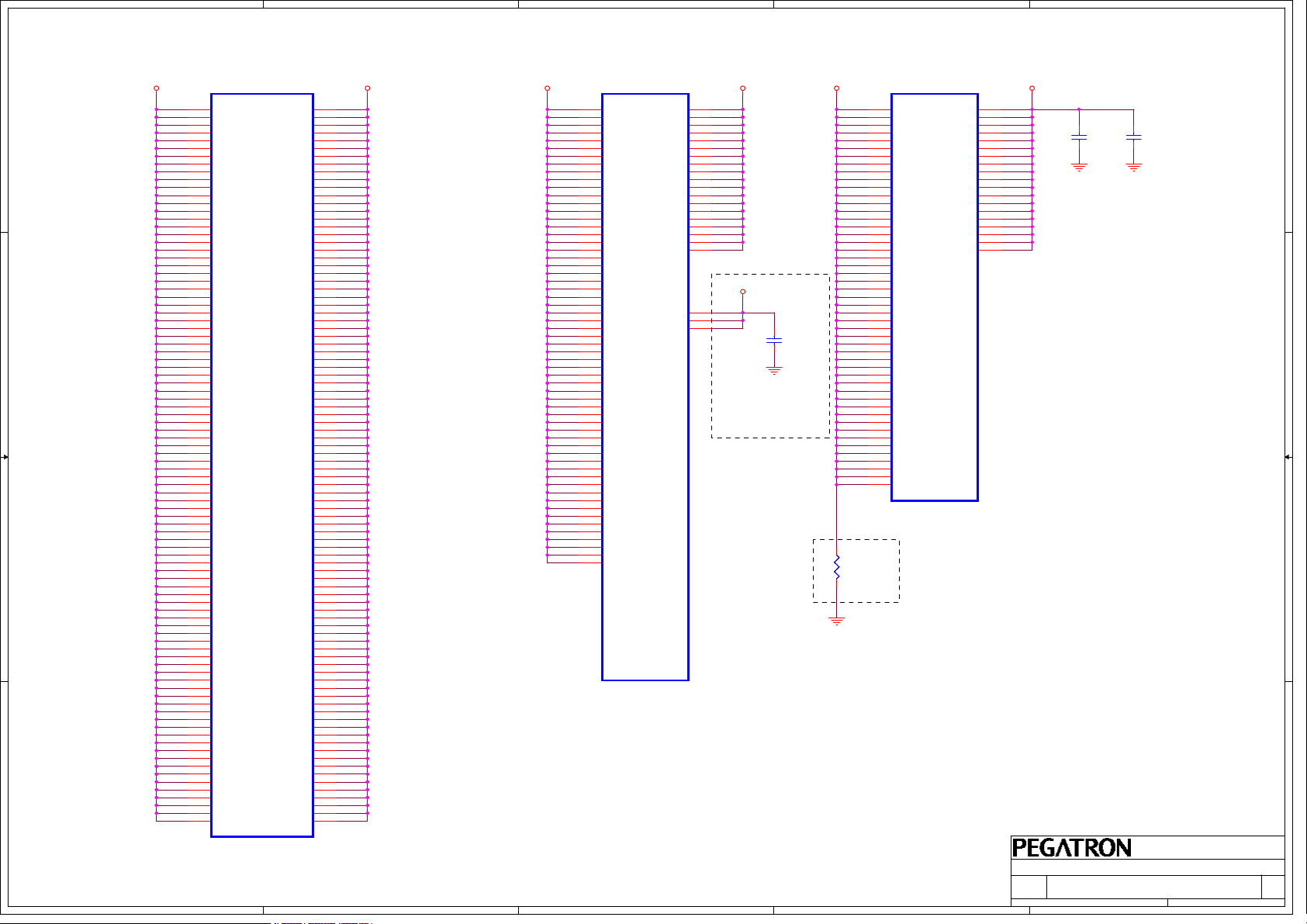

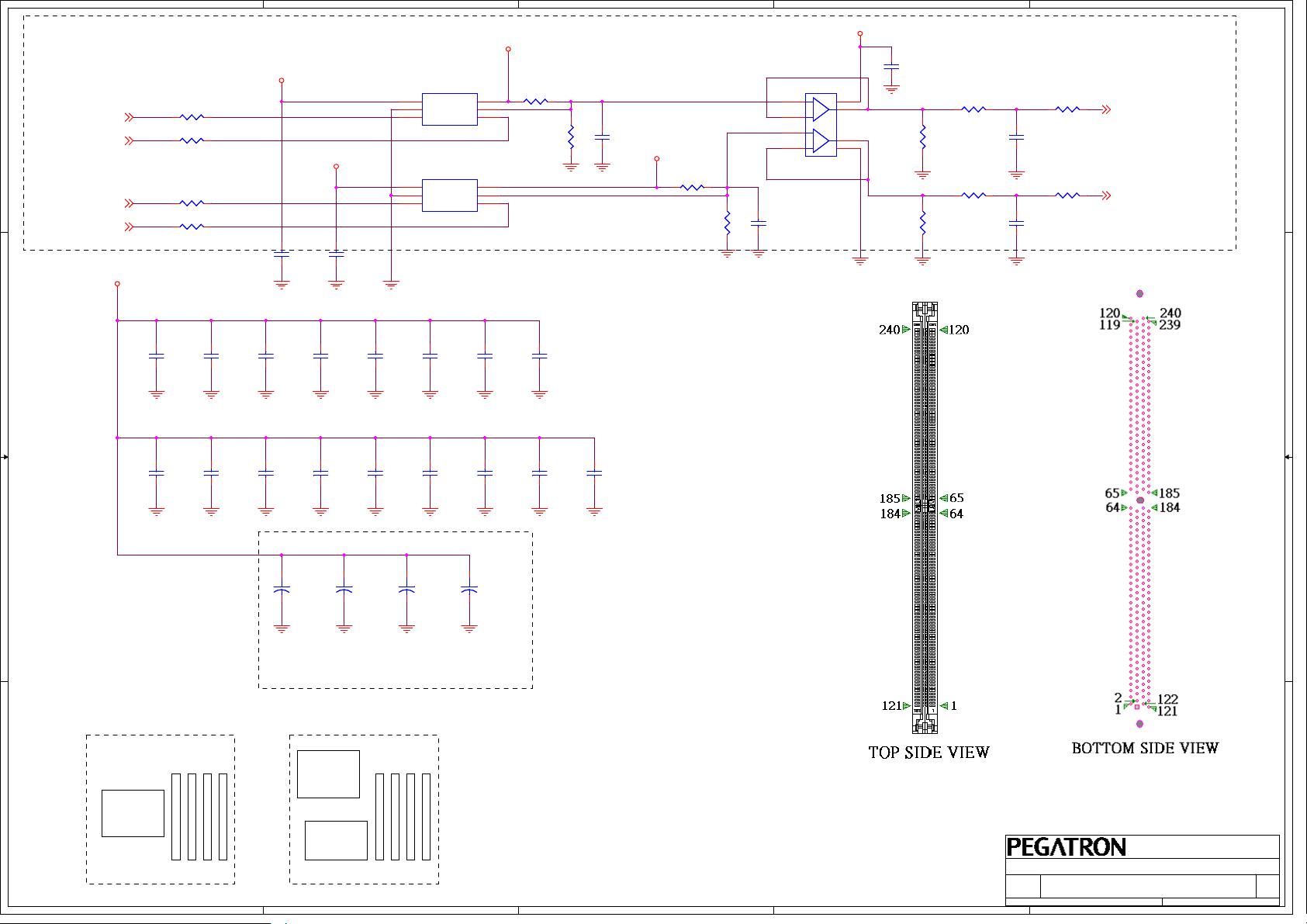

BLOCK DIAGRAM

CHANGE HISTORY

CLOCKS DISTRIBUTION

SIGNAL & RESET MAP

POWER FLOW

POWER DISTRIBUTION

POWER SEQUENCE

CLOCK SLG8SP424

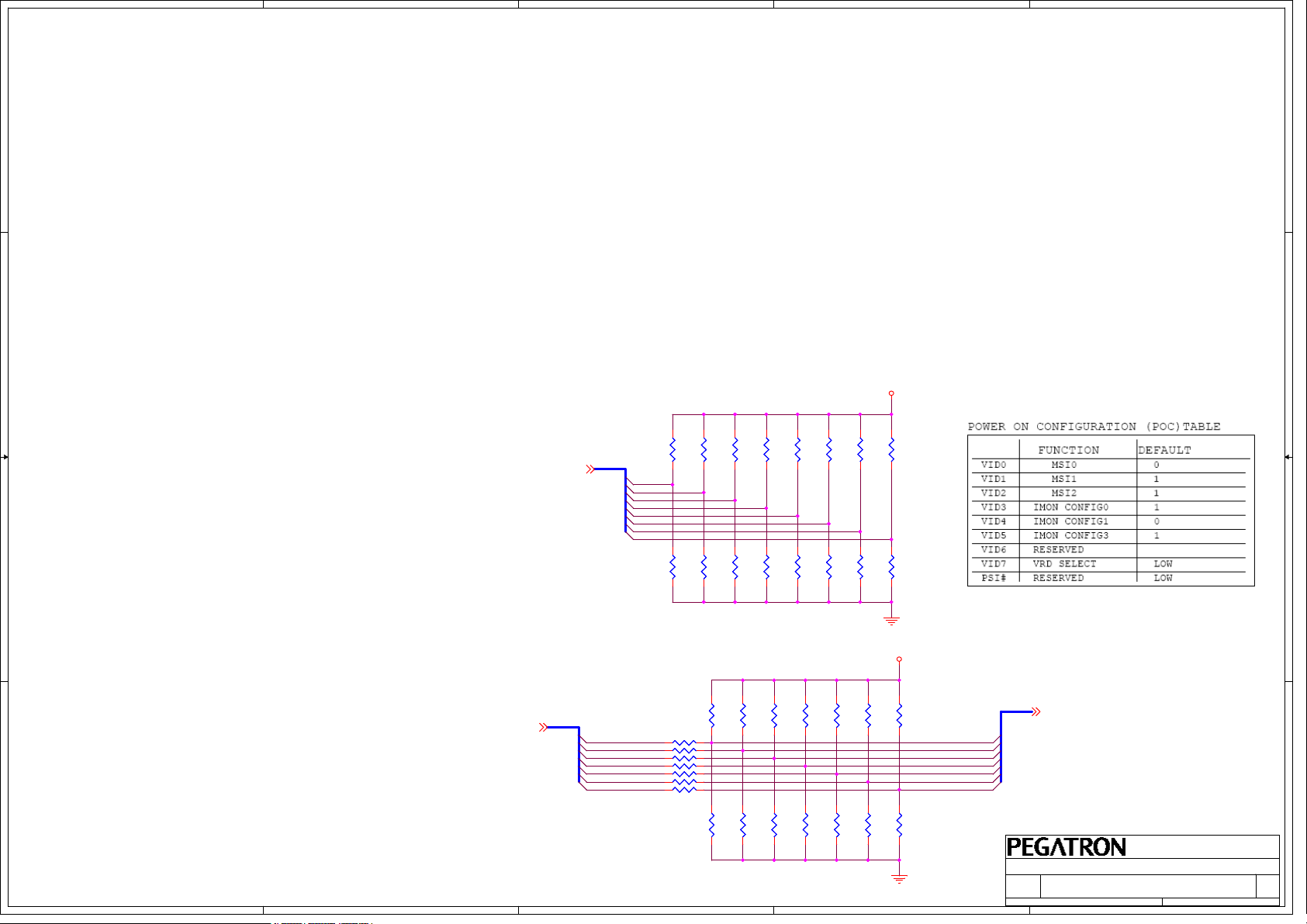

VID RESISTER

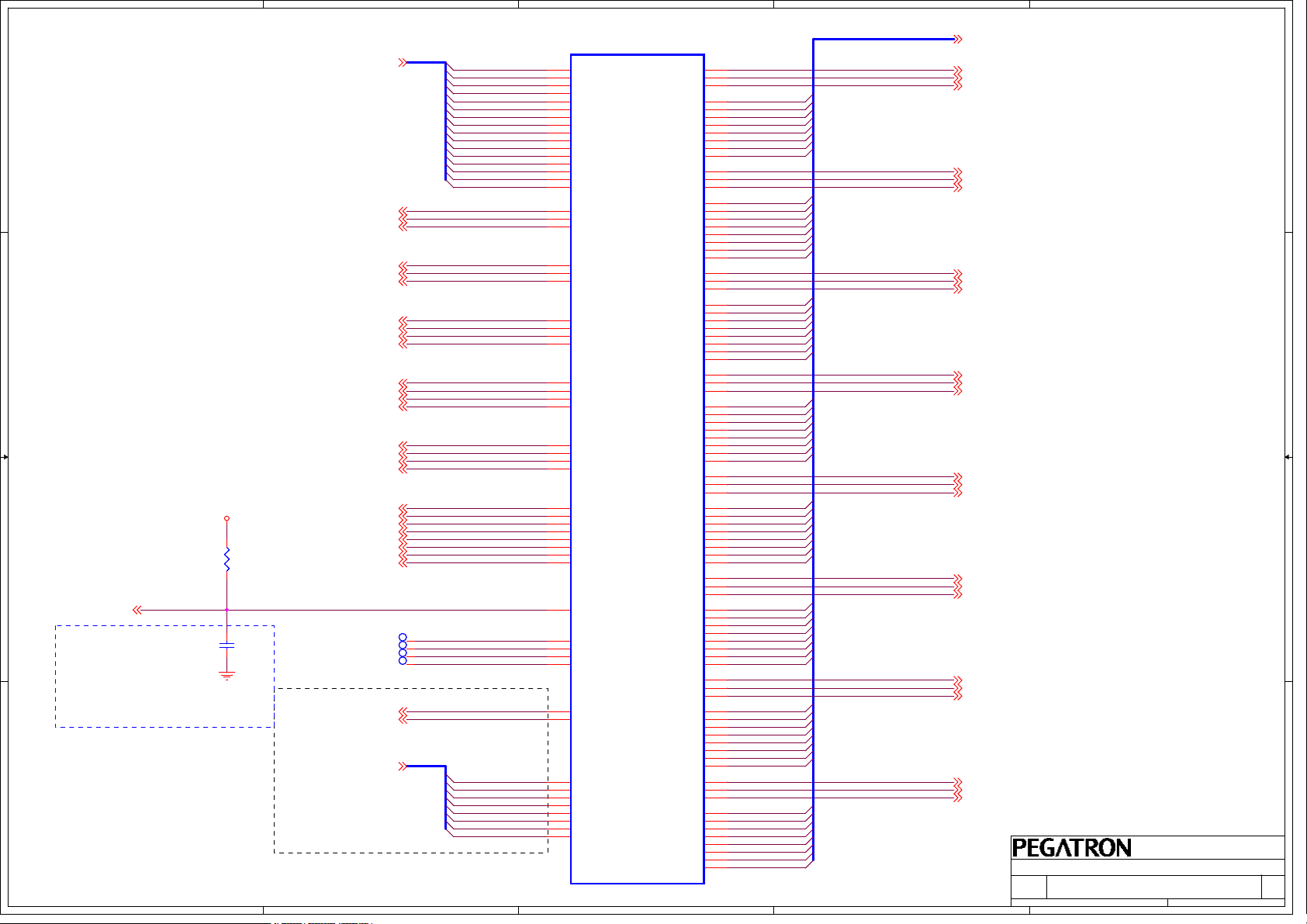

CPU_SOCKET1160_MEMORY 1 - 6

DDR3 CHANNEL A

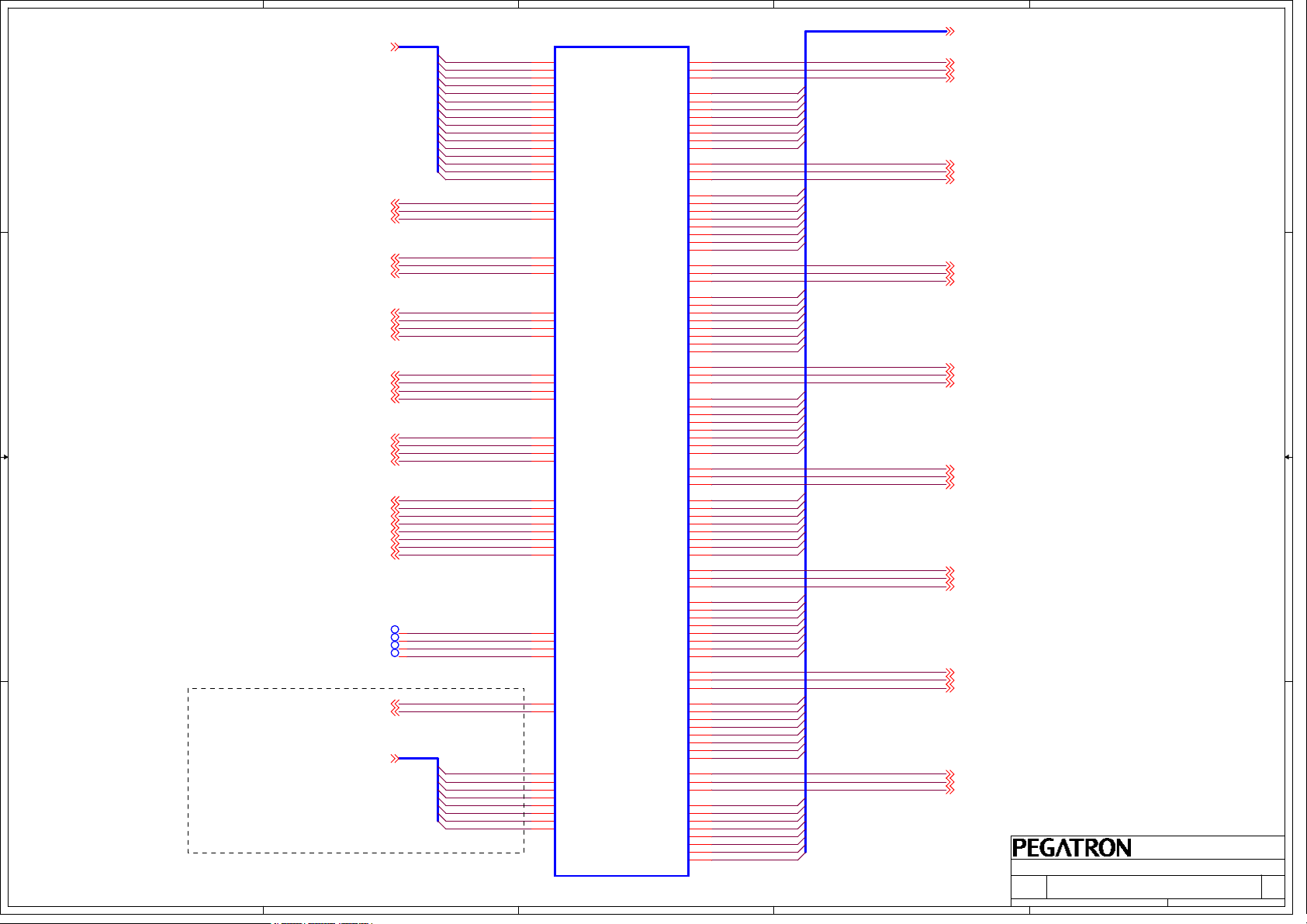

DDR3 CHANNEL B

DDR3 TERMINATION A&B

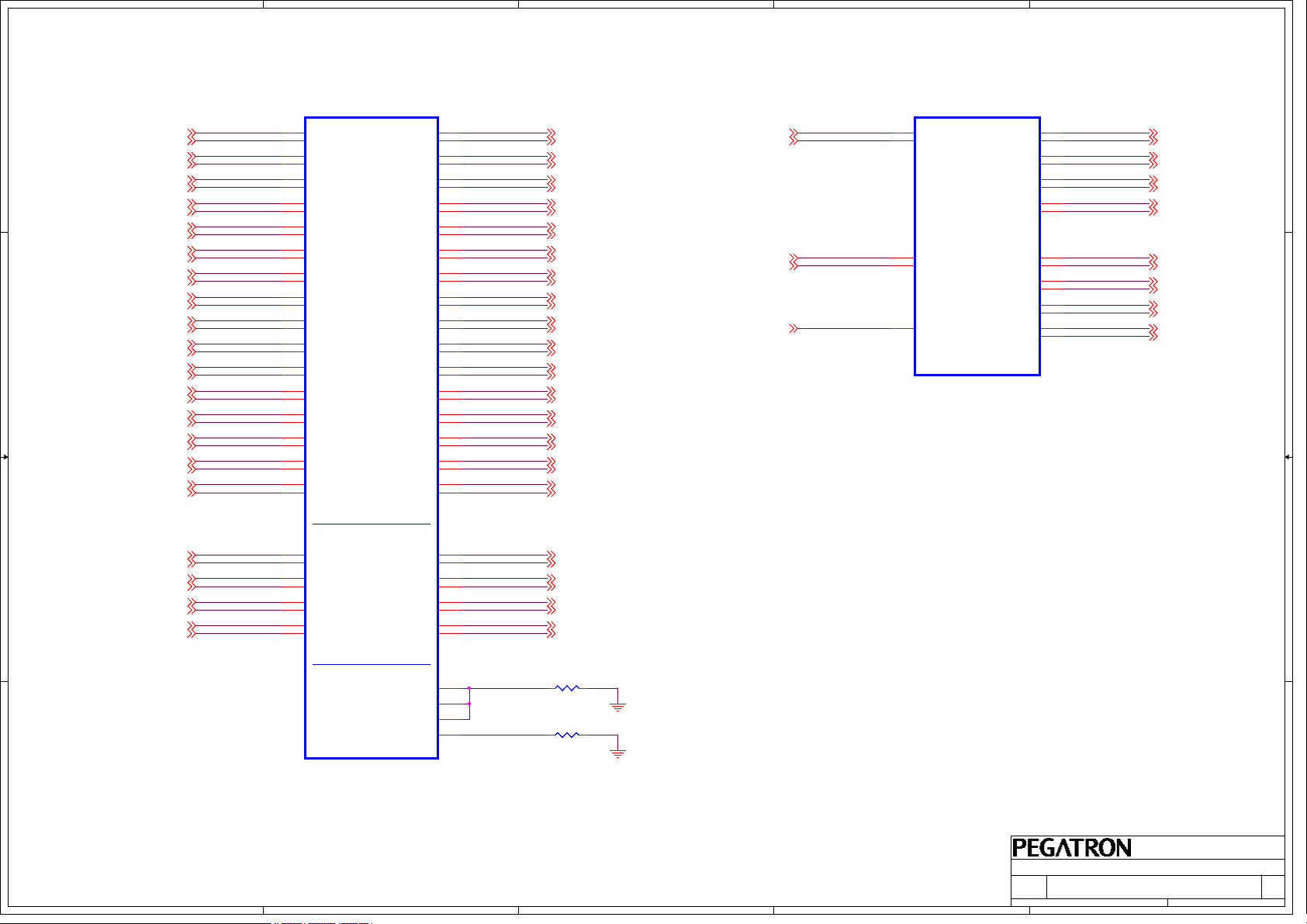

PCI EXPRESS X 16 SLOT

INTEL PCH 1 - 9

INTEGRATED VGA PORT

DVI LEVEL SHIFTER

DVI CONTROL

DVI-I CONNECTOR

Intel 82578DC LAN

RJ45+USB CONNECTER

Dual USB CONNECTER

PCI EXPRESS X1 SLOT -1

PCI SLOT INTERFACE - PCI-1

PCI SLOT INTERFACE - PCI-2

RTL 888S/662 AZALIA CODEC

FRONT AUDIO CONNECTOR

Azalia Rear Audio Connector

USB HEADER CONNECTOR - 1

USB HEADER CONNECTOR - 2

SATA & TPM CONNECTOR

SPI SERIAL FLASH & SMBUS

SUPER I/O - ITE 8721-1

SUPER I/O - ITE 8721-2

FAN CIRCUIT FOR 4 - PIN

FRONT PANEL CIRCUIT FOR CPC

RTC / CMOS / SCREW/KM

RSMRST CIRCUIT / EMI

CPU ITP / LPC DEBUG CONN

RTL8111DL LAN

LED / COM / SPKR / INTRUDER

LPT

ATX POWER CONNECTOR

VCORE CONTROLLER

VCORE DRIVER1

VCORE DRIVER2

VAGX CONTROLLER

VAGX DRIVER

+1P1V_VTT

+1P5V_DUAL

+1P05V_PCH / +1P05V_ME

+5V_DUAL / +3P3V_ME

+SM_VTT / +1P8V_SFR

TITLE

5

Revision: R1.01 (2010/04/20)

VRD 11.1

on Board

100MHz

PCI-E X16 SLOT

ITP

High-Speed USB

12 ports

Audio Reartek

ALC888S/662

Intel 82578DC

10/100/1000

PCI-E X1 SLOT2

Print port

4

PCI_E BUS

PCIE x1

100MHz

480Mb/s

24MHz

3

Intel Processor

Clarkdale/ Lynnfield

LGA-1156 Pin Socket

FDI LINK

DMI

INTEL

Ibex Peak

PCH

951 Pin

27mm X 27mm

LPC BUS

PCIE BUS

100MHz

SIO

ITE 8721

KB/MS

PCI BUS

33MHz

33MHz

COM x 2

128-bit Dual-Channel Memory x 4 Slots

Channel A

Channel B

RGB

SATA BUS

SPI

TPM

SLB9635TT

2

DDR3 800/1066/1333

DDR3 800/1066/1333

VGA CONN

DVI

Display Port

2* PCI SLOT

SATA2SATA0

SATA3SATA1

SPI FLASH

8MB

CLOCK

SILEGO

424

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPMIP-DP

IPMIP-DP

IPMIP-DP

SATA4

SATA5(e-SATA)

133 MHz

100 MHz

100 MHz

96 MHz

14.318 MHz

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Vic_Chen

Vic_Chen

Vic_Chen

1 68Friday, April 23, 2010

1 68Friday, April 23, 2010

1 68Friday, April 23, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Page 2

5

Schematics Change History

Schematics Change History

Schematics Change HistorySchematics Change History

Version

Version

VersionVersion

1.01

D D

1.01

1.01

1.01

1.01

1.01

1.01

1.01

1.01

1.01

1.01

C C

1.01

1.01

1.01

1.01

Date

Date

DateDate

2010/03/23 1.Change PCE20,PCE21BOM to 11X090567160. SR92 BOM to 10X212100510.

2.SIO pin 76 pull high to +5VSB_ATX form ITE vender request.(Fix EuP mode issue)2010/03/23

2010/03/23 3.Remove +3P3V_ME schematic to meet core team request.

2010/03/23

2010/03/23

4.Change VC10,VC11,VC12,VC13 BOM default NI.10X212300040

5.Change VR8 , VR9 to 10X212300040

2010/03/24

2010/03/24

7.Change P1R4 to 10X212100140 , Del P1R1 , ADD O2R28.

8.D3CB7,D3CB15 from 0.1uF to 2.2uF,to fix EA VREF_CA issue2010/03/24

2010/03/25 9 . O3Q1' O3R2'O3R10 to NI.Change O3R6'O3Q2'O3R11 to I.

2010/03/29

10.Change [VL2,4,6 change to 0 ohm]_[VL3,5,7 to 0.068UH/300mA]_[VC1,4,7 default NI]to fix EA VGA signal issue.

2010/03/29

2010/03/29

12.SR83,SR88 from 33 ohm to 22 ohm,to Fix VGA EA issue.

13.Add HR60,to fix EA RESET signal issue.2010/03/30

14.Change +1P5V_DUAL_OV to SIO GP10.2010/04/01

2010/04/02 13.Add M1C15 , M1C18 for DP.

4

3

Comments

Comments

CommentsComments

2

1

B B

CAD Note:

Default component footprint is SMD 0402, Y5V, 5% type. Difference footprint show on schematics.

A A

Property: BOM

I = Installed Part.

NI = Not Installed Part.

PROTO = PROTO Phase Only.

VP = Virtual Part.

5

4

3

2

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

CHANGE HISTORY

CHANGE HISTORY

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPMIP-DP

IPMIP-DP

IPMIP-DP

CHANGE HISTORY

Vic_Chen

Vic_Chen

Vic_Chen

2 68Wednesd ay, April 07, 2010

2 68Wednesd ay, April 07, 2010

2 68Wednesd ay, April 07, 2010

1

Rev

Rev

Rev

1.01

1.01

1.01

Page 3

5

4

3

2

1

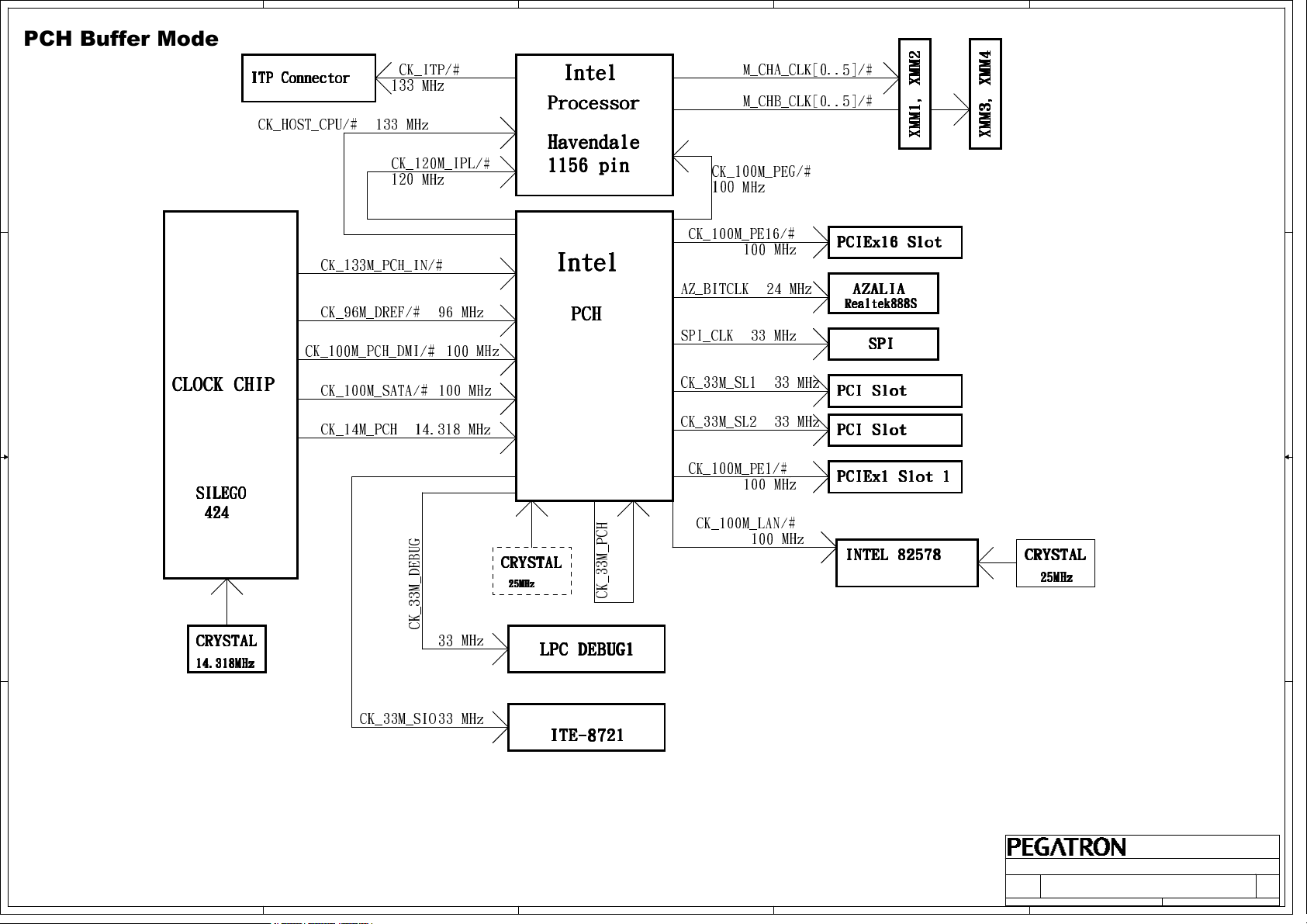

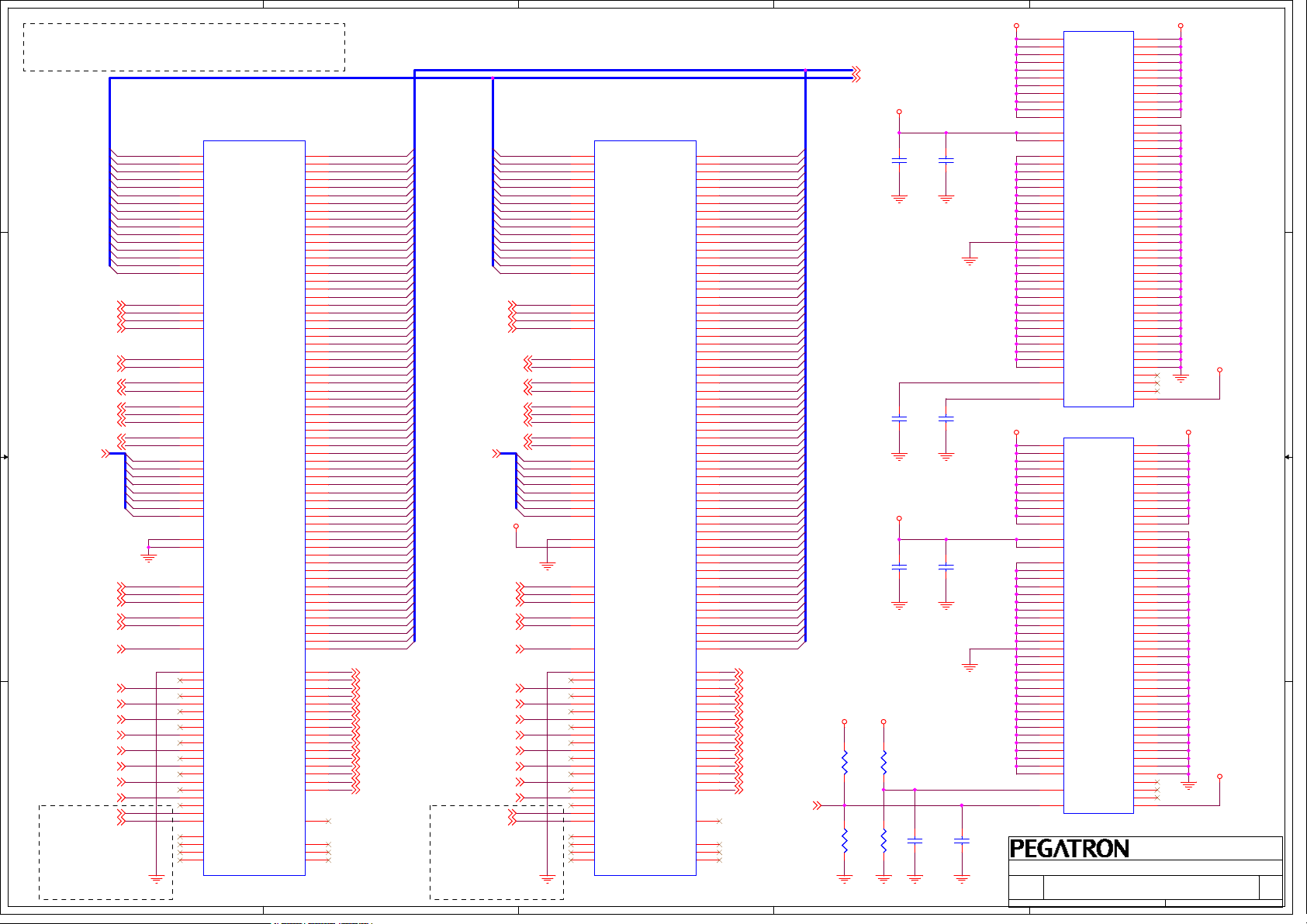

PCH Buffer Mode

ITP Connector

ITP Connector

ITP ConnectorITP Connector

D D

CK_HOST_CPU/#

CK_ITP/#

133 MHz

133 MHz

CK_120M_IPL/#

120 MHz

Intel

Intel

IntelIntel

Processor

Processor

ProcessorProcessor

Havendale

Havendale

HavendaleHavendale

1156 pin

1156 pin

1156 pin1156 pin

CK_100M_PE16/#

CK_133M_PCH_IN/#

CK_96M_DREF/# 96 MHz

C C

CLOCK CHIP

CLOCK CHIP

CLOCK CHIPCLOCK CHIP

CK_100M_SATA/#

CK_14M_PCH

100 MHzCK_100M_PCH_DMI/#

100 MHz

14.318 MHz

Intel

Intel

IntelIntel

PCH

PCH

PCHPCH

SPI_CLK

CK_33M_SL1 33 MHz

CK_33M_SL2 33 MHz

CK_100M_PE1/#

SILEGO

SILEGO

SILEGOSILEGO

424

424

424 424

G

U

B

B B

CRYSTAL

CRYSTAL

CRYSTALCRYSTAL

14.318MHz

14.318MHz

14.318MHz14.318MHz

E

D

_

M

3

3

_

K

C

33 MHz

CRYSTAL

CRYSTAL

CRYSTALCRYSTAL

25MHz

25MHz

25MHz25MHz

LPC DEBUG1

LPC DEBUG1

LPC DEBUG1LPC DEBUG1

H

C

P

_

M

3

3

_

K

C

CK_100M_LAN/#

M_CHA_CLK[0..5]/#

M_CHB_CLK[0..5]/#

CK_100M_PEG/#

100 MHz

100 MHz

24 MHzAZ_BITCLK

33 MHz

100 MHz

100 MHz

PCIEx16 Slot

PCIEx16 Slot

PCIEx16 SlotPCIEx16 Slot

AZALIA

AZALIA

AZALIAAZALIA

Realtek888S

Realtek888S

Realtek888SRealtek888S

SPI

SPI

SPISPI

PCI Slot

PCI Slot

PCI SlotPCI Slot

PCI Slot

PCI Slot

PCI SlotPCI Slot

PCIEx1 Slot 1

PCIEx1 Slot 1

PCIEx1 Slot 1PCIEx1 Slot 1

INTEL 82578

INTEL 82578

INTEL 82578INTEL 82578

2

2

2

2

M

M

M

M

M

M

M

M

X

X

X

X

,

,

,

,

1

1

1

1

M

M

M

M

M

M

M

M

X

X

X

X

4

4

4

4

M

M

M

M

M

M

M

M

X

X

X

X

,

,

,

,

3

3

3

3

M

M

M

M

M

M

M

M

X

X

X

X

CRYSTAL

CRYSTAL

CRYSTALCRYSTAL

25MHz

25MHz

25MHz25MHz

CK_33M_SIO33 MHz

ITE-8721

ITE-8721

ITE-8721 ITE-8721

A A

PEGATRON DT-MB RESTRICTED SECRET

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPMIP-DP

IPMIP-DP

IPMIP-DP

1

Vic_Chen

Vic_Chen

Vic_Chen

3 68Tuesday, March 23, 2 010

3 68Tuesday, March 23, 2 010

3 68Tuesday, March 23, 2 010

Rev

Rev

Rev

1.01

1.01

1.01

Page 4

5

4

3

2

1

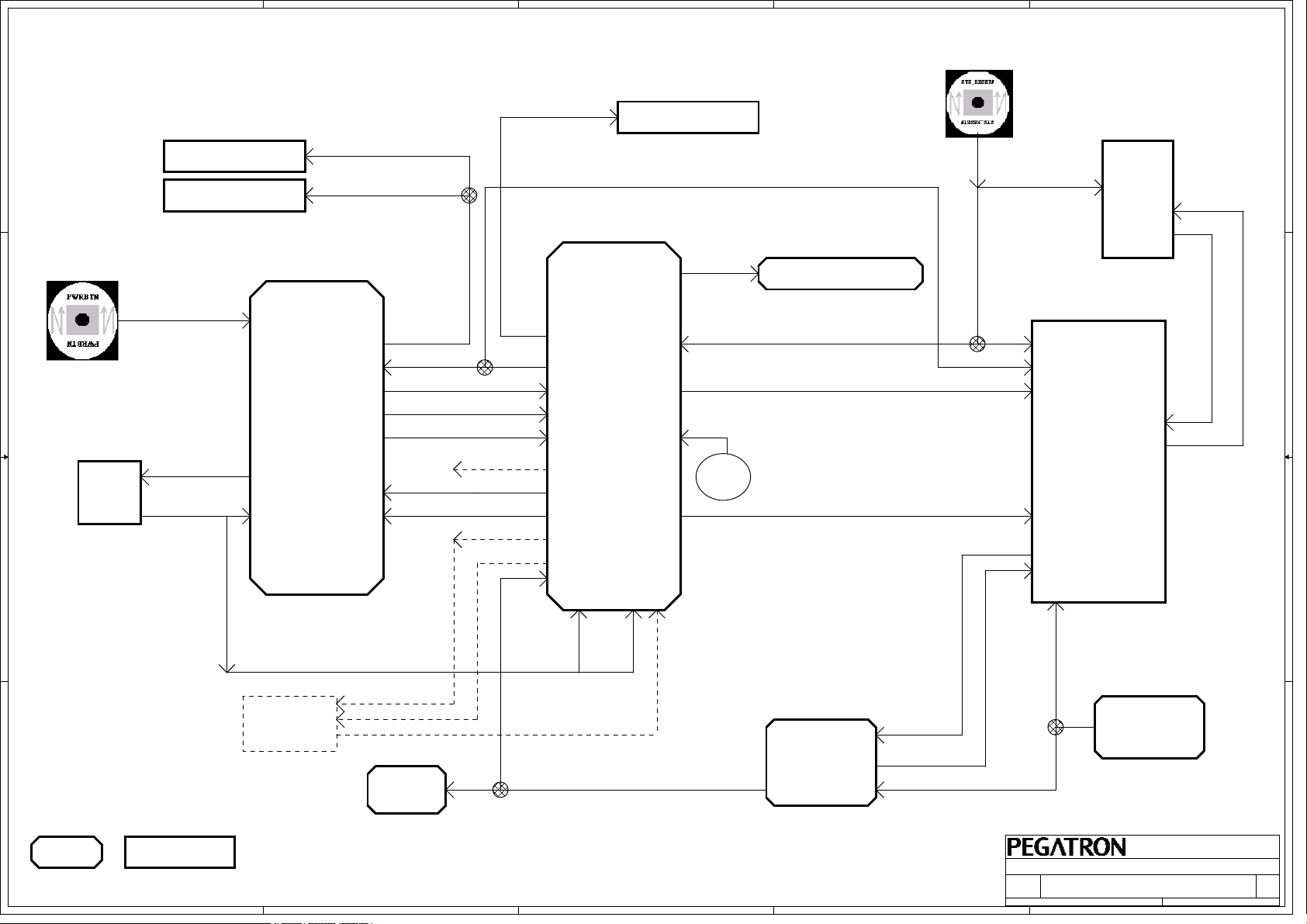

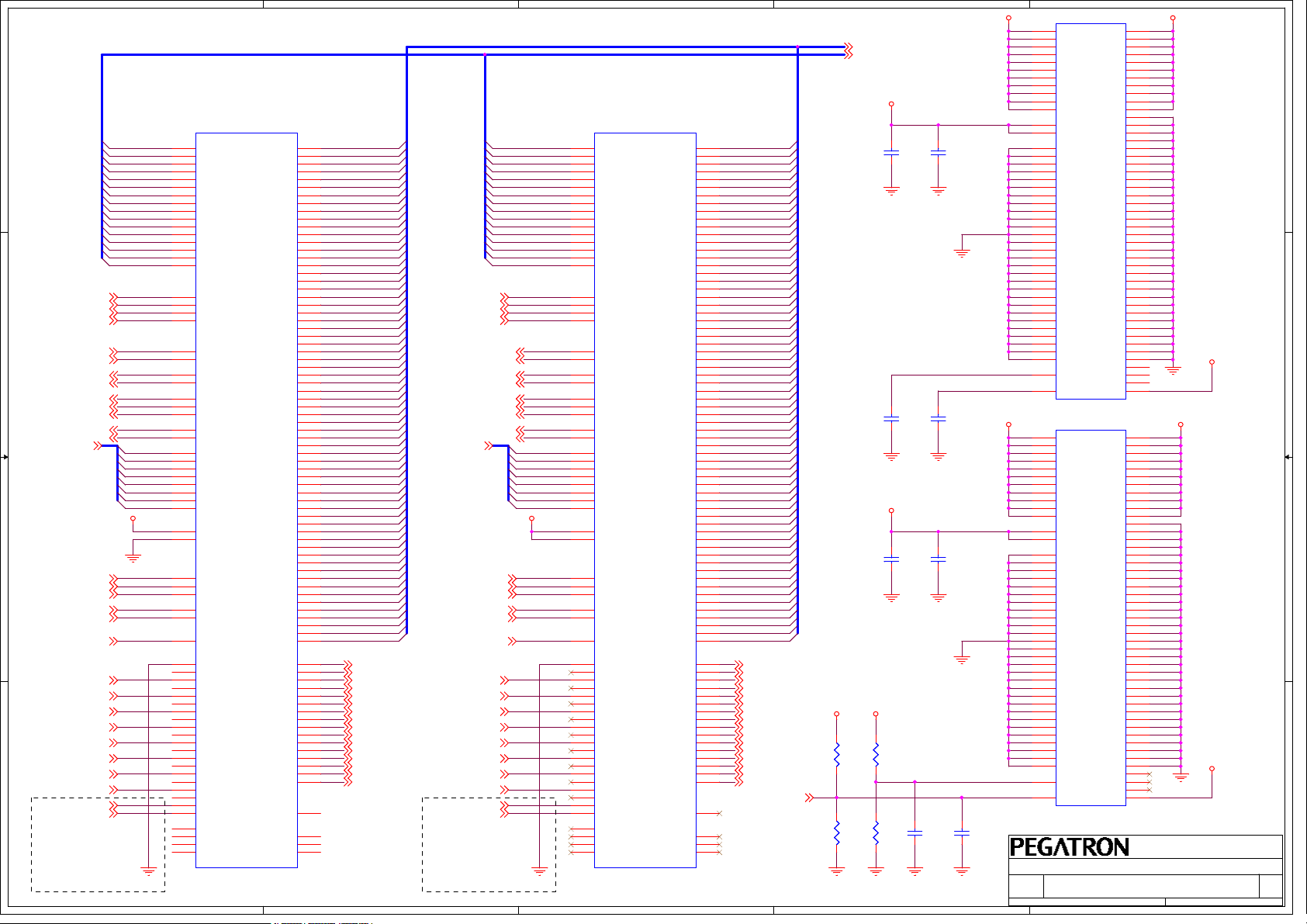

RESET_SWITCH

D D

PCI_Express x 16

<18>PCIES_RST#

PWRGD

<17>PCH_PCIRST#

PCI_Express x 1

<18>PCIES_RST#

PWRGD

POWER_SWITCH

<3>PWRBTN#

C C

POWER SUPPLY

<8>PSON#

PSON#

PWROK

B B

<9>ATX_PWRGD

SIO ITE-8721

PSIN#

PSON#

ATXPGD

RSTOUT0#

LRESET#

KBRST# RCIN#

RSMRST#

PSOUT# PWRBTN#

<17>PLTRST#

RST_KB#

<2>RSMRST#

<4>SB_PWRBTN#

<5>SLP_S5#

SLP_S5#

SLP_S3# SLP_S3#

<6>SLP_S4#

<7>SLP_S3#

<5.1>SLP_M#

<5.1>SLP_LAN#

PCIRST#

PLTRST#

RSMRST#

SLP_S5#

SLP_S4#

SLP_M#

SLP_LAN#

SYS_PWROK

PWROK

RST#

PCI SLOT

<17>PLTRST#

SYS_RESET#

PCH

HDA_RST#

AZ_RST#

RESET#

SYS_RESET#

DRAMPWROK

RTCRST#

<1>RTCRST#

BATTERY

CPUPWRGD VCCPWRGOOD

MEPWROK

AUDIO

ALC888S

SYS_RESET#

<15>DRAM_PWROK

<16>CPUPWRGD

<11>VRM_VID[0..7]

PROCESSOR

DBR#

RSTIN#

SM_DRAMPWROK

RESET_OBS#

VID[0..7]

VCORE

VTTPWRGD

DBR#

ITP

RESET#

TRST#

TRST#

H_RSTOUT#

TRST#

<14>PWROK

ME_POWER

If support AMT, SLP_M#

will come with SLP_S5

If not support AMT, SLP_M#

will come with SLP_S3

A A

+1P05V_ME

+3P3V_ME

CK 505

CKPWRGD/PD#

<5.2>MEPWROK

<13>VRM_PWRGD

Vcore Controller

VID[0..7]

VCORE

VR_RDY

EN_VTT

<12>VCORE

<10>VTTPWRGD

+1P1V_VTT

VTTPWRGD

ISL6341

NCP5395

PEGATRON DT-MB RESTRICTED SECRET

SIGNAL & RESET MAP

SIGNAL & RESET MAP

SIGNAL & RESET MAP

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

SOCKET or SLOTCHIP

5

4

3

2

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPMIP-DP

IPMIP-DP

IPMIP-DP

1

Vic_Chen

Vic_Chen

Vic_Chen

4 68Tuesday, March 23, 2 010

4 68Tuesday, March 23, 2 010

4 68Tuesday, March 23, 2 010

Rev

Rev

Rev

1.01

1.01

1.01

Page 5

5

+12V_VCORE

22.1875A

4

16.042A

Controller : NCP5395

H/S:FDU8780_F071*2

L/S:IPDH6N03LAG*2

3 Phase

3

2

+1.4V_CPU/110A

1

3.4375A

D D

2.708A

+5V

C C

+5VSB

11.8305A

2A

SPDT

+5V_DUAL

13.8305A

Controller : ISL6341CRZ_TR

H/S:AOD452*2

L/S:AOD472*2

Controller : ISL6314

H/S:IPD09N03LAG*1

L/S:IPD09N03LAG*2

7.8305A

Controller:RT8105/AWN7120

H/S:AOD452*2

L/S:AOD452*2

USB/6A

+1P5V_DUAL

19.548A

RT9173C

0.549A

RT8015APQW

+1P05V_ME 2.222A

LM358+MOS

3.44A

Controller : MP2307

2.838A

+3VSB

3.18A

+1.1V_VTT/30A

+1.3V_AXG/20A

+1.5V_Dual/13.2A

+0P75V_VTT_DDR/0.83A

+1P05V_PCH/5.598A

UP7704U8

B B

SPDT

+3P3V_ME

0.26A

+3.3V

+12V

A A

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

SWITCHING

LINEAR

SWITCH ON/OFF

Title :

Engineer:

Engineer:

PEGATRO N CORPOATION

PEGATRO N CORPOATION

PEGATRO N CORPOATION

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPMIP-DP

IPMIP-DP

IPMIP-DP

Engineer:

POWER FLOW

POWER FLOW

POWER FLOW

Michael Lee

Michael Lee

Michael Lee

5 68Tuesday, March 23, 2 010

5 68Tuesday, March 23, 2 010

5 68Tuesday, March 23, 2 010

Rev

Rev

Rev

1.01

1.01

1.01

Page 6

5

Lynnfield/Clarkdale

VCORE

+1.1V_VTT

+1.5V

+1.8V

D D

V_CPU_IO

+5V

+5V

+3.3V

-> 90A - 95(TBD)W

-> 30A(TBD) - 33W

Vddq -> 6A - 9W

Vccpll -> 1.35A - 2.43W

Intel Ibex Peak

Intel Ibex Peak

Intel Ibex PeakIntel Ibex Peak

-> <1mA - 1.1mW

V5REF -> <1mA - 5mW

V5REF_Sus -> <1mA - 5mW

Vcc3_3 -> 0.357A - 1.178W

VccDAC -> 0.069A - 0.228W

+1.1V

VccDMI -> 0.065A - 0.07W

VccADPLLA -> 0.075A - 0.079W

VccADPLLB-> 0.075A - 0.079W

+1.05V

C C

VccCORE -> 1.629A - 1.71W

VccIO -> 3.251A - 3.414W

VccLAN -> 0.372A - 0.39W

VccME -> 2.222A - 2.333W

+1.8V

VccqNAND -> 0.156A - 0.281W

VccVRM -> 0.196A - 0.353W

VccTX_LVDS -> 0.059A - 0.106W

+3P3V

VccALVDS -> <1mA - 3.3mW

VccRTC -> 2mA - 6.6mW

+3P3VSB

VccSus3_3 -> 0.168A - 0.554W

VccSusHDA -> 0.006A - 0.02W

VccME3_3-> 0.086A - 0.284W

B B

CLOCK- CK505

+3P3V

+VDD_IO (0.8V)

+1.5V_DAUL

-> 250mA - 0.825W

-> 80mA - 64mW

DDR3 DIMM (4) & Termination

DDR3 DIMM (4) & Termination

DDR3 DIMM (4) & TerminationDDR3 DIMM (4) & Termination

VDD (S0, S1) -> 7.2 A - 10.8W

VDD (S3) -> 712mA - 1.07W

SM_VTT(0.75V)

SM VTT (S0, S1) -> 0.83A - 0.623W

4

+12V

+3P3V

+3P3V_PCI

+12V

+3P3V

+3P3V_PCI

+12V

-12V

+5V

+3P3V

+3P3V_PCI

+3P3V_CL

+1P8VSB_LAN

VCC_LAN(1.05V)

+5V

+3.3VSB

+3.3V

+5VSB

+3P3V

+5V_DUAL

PCI Express x 1

PCI Express x 1

PCI Express x 1PCI Express x 1

-> 0.5A - 6W

-> 3.0A - 9.9W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

PCI Express x 16

PCI Express x 16

PCI Express x 16PCI Express x 16

-> 5.5A - 66W

-> 3.0A - 9.9W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

PCI SLOTS

PCI SLOTS

PCI SLOTSPCI SLOTS

-> 0.5A - 6W

-> 0.1A - 1.2W

-> 5.0A - 25W

-> 7.6A - 25.08W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

INTEL 82578

INTEL 82578

INTEL 82578INTEL 82578

-> 15.5mA(TBD) - 51.15mW

-> 300mA - 540mW

-> 300mA -315mW

SIO ITE-8721

SIO ITE-8721

SIO ITE-8721SIO ITE-8721

-> 1mA - 5mW

-> 2.4uA - 7.92uW

-> 2mA - 6.6mW

ALC888S Azalia Codec

ALC888S Azalia Codec

ALC888S Azalia CodecALC888S Azalia Codec

-> 0.6A - 3W

-> 0.4A - 1.32W

USB 12 PORTS

USB 12 PORTS

USB 12 PORTSUSB 12 PORTS

(S0, S1) -> 8.4A - 42W

(S3) -> 0.336A - 1.68W

3

+3P3V

+3P3V

+2P5V_DVI

+5V

+12V

+12V

+5V_DUAL

+3V

+12V

+5V

+12V

+5V

1394A

1394A

1394A1394A

-> mA - W

HDMI

HDMI

HDMIHDMI

-> mA - mW

-> mA - mW

SATA 6 PORTS

SATA 6 PORTS

SATA 6 PORTSSATA 6 PORTS

-> 0.975A - 4.875W

-> 0.9A - 10.8W

FAN

FAN

FANFAN

-> 0.6A - 7.2W

PS2 KB/MS

PS2 KB/MS

PS2 KB/MSPS2 KB/MS

(S0, S1) -> 0.345A - 1.73W

(S3) -> 2mA - 10mW

SPI

SPI

SPISPI

-> 30mA - 99mW

HDD

HDD

HDDHDD

-> 0.75A - 9.0W

-> 0.75A - 3.75W

CD ROM

CD ROM

CD ROMCD ROM

-> 0.75A - 9.0W

-> 0.75A - 3.75W

2

1

A A

PEGATRON DT-MB RESTRICTED SECRET

POWER DISTRIBUTION

POWER DISTRIBUTION

POWER DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPMIP-DP

IPMIP-DP

IPMIP-DP

1

Vic_Chen

Vic_Chen

Vic_Chen

6 68Tuesday, March 23, 2 010

6 68Tuesday, March 23, 2 010

6 68Tuesday, March 23, 2 010

Rev

Rev

Rev

1.01

1.01

1.01

Page 7

5

4

3

2

1

G5 S5 S4 S3 S0

t1

D D

t2

+5VSB

t3

+3VSB

t4

t5

t10

t14

RSMRST#

C C

t11

SLP_S4#

SLP_S3#

t7

SLP_SM#

t6

PS_ON#

Latch Latch

+12V, +5V

B B

+3V

VTTPWRGD

t8

t12

VRM_PWRGD

PWROK

DRAM_PWROK

t9

A A

The data is not final

5

t1>18ms

t2>0ms

t4>0ms

t5>10ms

t6>0ms

t7>0ms

t9>99ms

t10<110ms

t11>1RTCCLK

t12>5ms

t13:35~74RTCCLK

t14<110ms

4

3

t13

2

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

POWER SEQUENCE

POWER SEQUENCE

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPMIP-DP

IPMIP-DP

IPMIP-DP

POWER SEQUENCE

Michael Lee

Michael Lee

Michael Lee

7 68Tuesday, March 23, 2 010

7 68Tuesday, March 23, 2 010

7 68Tuesday, March 23, 2 010

1

Rev

Rev

Rev

1.01

1.01

1.01

Page 8

5

4

3

2

1

ICS9LRS4180AKLFT: 0610-0038000

SLG8SP424VTR: 0610-007D000

D D

21

+CLKVCC 3

12

GND GND

VRM_PW RGD22 ,59

SMB_CLK _M16,17,49,5 7

SMB_DAT A_M16,17,49,5 7

I

I

CKCB4

CKCB4

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

12

12

NI

NI

CKCB11

CKCB11

10UF/6.3V

10UF/6.3V

X5R 10%

X5R 10%

mx_c0805

mx_c0805

GNDGND

12

I

I

CKCB5

CKCB5

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND GND

VP

VP

CKR43

CKR43

1 2

1 2

12

I

I

CKC8

CKC8

33PF/50V

33PF/50V

NPO 5%

NPO 5%

GND GND GND

I

I

CKCB12

CKCB12

10UF/6.3V

10UF/6.3V

X5R 10%

X5R 10%

mx_c0805

mx_c0805

I

I

CKCB3

CKCB3

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

0

0

VP

VP

CKR48

CKR48

0

0

12

I

I

CKCB6

CKCB6

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND GND

12

I

I

CKCB8

CKCB8

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

Y1_R

12

NI

NI

CKC10

CKC10

33PF/50V

33PF/50V

NPO 5%

NPO 5%

12

12

GND

12

GND

I

I

Y1

Y1

14.318Mh z

14.318Mh z

1 2

1 2

GND

GND

3

3

I

I

CKCB7

CKCB7

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

I

I

CKCB9

CKCB9

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

CKCB10

CKCB10

NI

NI

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

GNDGND

12

I

I

CKCB2

CKCB2

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

CK505_P WRGD

OSC_CK1 4M_XTALIN

OSC_CK1 4M_XTALOUT

12

I

I

CKC9

CKC9

33PF/50V

33PF/50V

NPO 5%

NPO 5%

NI

NI

CKC11

CKC11

33PF/50V

33PF/50V

NPO 5%

NPO 5%

GND

1

VDD1

30

VDD2

19

VDD_CPU

12

VDD_SRC

9

VDD_SATA

3

VDD_96

16

VDD_A

25

VDD_REF

22

VSS_CPU

13

VSS_SRC

5

VSS_96

31

VSS1

32

VSS2

17

VSS_A

28

VSS_REF

33

GND

34

GND1

35

GND2

36

GND3

37

GND4

2

CKPWRGD/PD#

27

XIN

26

XOUT

23

SCL

24

SDA

CKU1

CKU1

USB_48M/FS_A

CPU

CPU#

SRC

SRC#

SATA

SATA#

DOT_96

DOT_96#

FS_B

REF/FS_C

RCPUHCL K

21

RCPUHCL K#

20

RCK_100 M_PCIE

15

RCK_100 M_PCIE#

14

RCK_100 M_SATA

10

RCK_100 M_SATA#

11

RCK_96M _DREF

6

RCK_96M _DREF#

7

+CLKVCC 3

12

NI/SLG8SP424

NI/SLG8SP424

CKR39

CKR39

4.7K

4.7K

CK_RESE T#

18

NC

CK_48MH z

4

CK_FSLB

8

RCK_REF _14P318

29

PU in F_PANEL

+CLKVCC 3

1 2

12

GND

CKR3

CKR4

CKR12

CKR13

CKR20

CKR21

CKR24

CKR25

+CLKVCC 3 +CLKVCC 3

12

CKR36

CKR36

10KOhm

10KOhm

5%

5%

I

I

CKR47

CKR47

10KOhm

10KOhm

5%

5%

NI

NI

CKR38

CKR38

10KOhm

10KOhm

5%

5%

NI

NI

12

CKR49

CKR49

10KOhm

10KOhm

5%

5%

I

I

GND GND

0CKR3

0

12

NOBOM

NOBOM

0CKR4

0

12

NOBOM

NOBOM

0CKR12

0

12

NOBOM

NOBOM

0CKR13

0

12

NOBOM

NOBOM

0CKR20

0

12

NOBOM

NOBOM

0CKR21

0

12

NOBOM

NOBOM

0CKR24

0

12

NOBOM

NOBOM

0CKR25

0

12

NOBOM

NOBOM

RESET(Pin 18) on ICS9LRS4180A

NOTE:

Real time system reset signal for frequency gear

ratio change or watchdog timer timeout.

NC(Pin 18) on SLG8SP424

NOTE:

CKR5

CKR5

NI

12

12

CKR37

CKR37

10KOhm

10KOhm

5%

5%

NI

NI

CKR50

CKR50

10KOhm

10KOhm

5%

5%

I

I

NI

1 2

0

0

CKR27 33

CKR27 33

I

I

CKR29 33

CKR29 33

I

I

1 2

1 2

12

NI

NI

CKC2

CKC2

10PF/50V

10PF/50V

NPO 5%

NPO 5%

GND GND

CK_133M _PCH_IN 24

CK_133M _PCH_IN# 24

CK_100M _PCH_DMI 20

CK_100M _PCH_DMI# 20

CK_100M _PCH_SATA 21

CK_100M _PCH_SATA# 21

CK_96M_ PCH_DREF 23

CK_96M_ PCH_DREF# 23

SYS_RESET # 13,22 ,52,57

CK_48M_ SIO 47

CK_14M_ PCH 24

12

NI

NI

CKC5

CKC5

10PF/50V

10PF/50V

NPO 5%

NPO 5%

+3P3VSB

+3P3V

C C

B B

NI

NI

CKR55

CKR55

0

0

mx_r0603

mx_r0603

1 2

I

I

CKR56

CKR56

0

0

mx_r0603

mx_r0603

1 2

+CLKPW

I

I

CKL1

CKL1

600Ohm/1 00Mhz/0.5A

600Ohm/1 00Mhz/0.5A

mx_l0603

mx_l0603

SLG8SP4 24VTR

SLG8SP4 24VTR

I

I

A A

5

4

3

NOTE:

FSLC FSLB FSLA CPU FREQ

0 0 1 133MHz

1 10 100MHz

PEGATRON DT-MB RESTRICTED SECRET

ICS 4180/SLG 424

ICS 4180/SLG 424

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

IPMIP-DP

IPMIP-DP

IPMIP-DP

ICS 4180/SLG 424

Vic_Chen

Vic_Chen

Vic_Chen

1

Rev

Rev

Rev

1.01

1.01

8 68Wednesd ay, April 07, 2010

8 68Wednesd ay, April 07, 2010

8 68Wednesd ay, April 07, 2010

1.01

Page 9

5

D D

C C

4

3

2

+1P1V_V TT

1

12

NI

NI

HR9

HR9

1K

VRM_VID[0..7]13,5 9

B B

GFX_VID[0..6]13

A A

5

4

GFX_VID6

GFX_VID5

GFX_VID4

GFX_VID3

GFX_VID2

GFX_VID1

GFX_VID0

VP

VP

VP

VP

VP

VP

VP

VP

VP

VP

VP

VP

VP

VP

VRM_VID0

VRM_VID1

VRM_VID2

VRM_VID3

VRM_VID4

VRM_VID5

VRM_VID6

VRM_VID7

HR53 0

HR53 0

1 2

HR54 0

HR54 0

1 2

HR55 0

HR55 0

1 2

HR56 0

HR56 0

1 2

HR57 0

HR57 0

1 2

HR58 0

HR58 0

1 2

HR59 0

HR59 0

1 2

3

1K

12

I

I

HR10

HR10

1K

1K

12

12

I

I

I

I

HR18

HR18

HR11

HR11

1K

1K

1K

1K

12

12

NI

NI

NI

NI

HR41

HR41

HR17

HR17

1K

1K

1K

1K

12

12

I

I

NI

NI

HR62

HR62

HR52

HR52

1K

1K

1K

1K

12

12

NI

NI

NI

NI

HR61

HR61

HR63

HR63

1K

1K

1K

1K

12

12

I

I

HR42

HR42

1K

1K

12

NI

NI

HR43

HR43

1K

1K

12

NI

NI

HR64

HR64

1K

1K

12

NI

NI

HR65

HR65

1K

1K

12

NI

NI

I

I

HR44

HR44

HR46

HR46

1K

1K

1K

1K

12

12

I

I

NI

NI

HR45

HR45

HR47

HR47

1K

1K

1K

1K

12

12

NI

NI

NI

NI

HR66

HR66

HR68

HR68

1K

1K

1K

1K

12

12

NI

NI

NI

NI

HR69

HR69

HR67

HR67

1K

1K

1K

1K

12

12

NI

NI

NI

NI

HR50

HR50

HR48

HR48

1K

1K

1K

1K

12

12

I

I

I

I

HR49

HR49

HR51

HR51

1K

1K

1K

1K

GND

+1P1V_V TT

12

12

NI

NI

NI

NI

HR72

HR72

HR70

HR70

1K

1K

1K

1K

VAXG_VID7

VAXG_VID6

VAXG_VID5

VAXG_VID4

VAXG_VID3

VAXG_VID2

VAXG_VID1

12

12

NI

NI

NI

NI

HR71

HR71

HR73

HR73

1K

1K

1K

1K

GND

2

VAXG_VID[1 ..7] 62

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

VID RES

VID RES

1

VID RES

Vic_Chen

Vic_Chen

Vic_Chen

9 68Wednesd ay, April 07, 2010

9 68Wednesd ay, April 07, 2010

9 68Wednesd ay, April 07, 2010

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPMIP-DP

IPMIP-DP

IPMIP-DP

Rev

Rev

Rev

1.01

1.01

1.01

Page 10

5

M_CHA_M AA[0..15]16

D D

C C

+1P5V_D UAL

12

I

I

HR60

HR60

0

GND

0

12

NI

NI

HC1

HC1

220PF/50 V

220PF/50 V

X7R 10%

X7R 10%

B B

DDR3_DR AMRST#16,17

IP R1.02 added to reduce

The glitch.

M_CHA_C LK01 6

M_CHA_C LK0#16

M_CHA_C LK11 6

M_CHA_C LK1#16

M_CHA_C LK21 6

M_CHA_C LK2#16

M_CHA_C LK31 6

M_CHA_C LK3#16

M_CHA_D QS816

M_CHA_D QS8#16

NOTE:

For ECC DIMM

MA_ECC_ CB[0..7]16

A A

5

4

I

I

HU1A

HU1A

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

M_CHA_M AA15

M_CHA_W E#16

M_CHA_C AS#16

M_CHA_R AS#16

M_CHA_B A016

M_CHA_B A116

M_CHA_B A216

M_CHA_C S#01 6

M_CHA_C S#11 6

M_CHA_C S#21 6

M_CHA_C S#31 6

M_CHA_C KE016

M_CHA_C KE116

M_CHA_C KE216

M_CHA_C KE316

M_CHA_O DT016

M_CHA_O DT116

M_CHA_O DT216

M_CHA_O DT316

HT1TPC26bNOBOM HT1TPC26bNOBOM

1

HT2TPC26bNOBOM HT2TPC26bNOBOM

1

HT3TPC26bNOBOM HT3TPC26bNOBOM

1

HT4TPC26bNOBOM HT4TPC26bNOBOM

1

4

M_CHA_B A0

M_CHA_B A1

M_CHA_B A2

M_CHA_C S#0

M_CHA_C S#1

M_CHA_C S#2

M_CHA_C S#3

M_CHA_C KE0

M_CHA_C KE1

M_CHA_C KE2

M_CHA_C KE3

M_CHA_O DT0

M_CHA_O DT1

M_CHA_O DT2

M_CHA_O DT3

TP_CPU_ AK22

TP_CPU_ AM22

TP_CPU_ AL23

TP_CPU_ AK23

M_CHA_D QS8

M_CHA_D QS8#

MA_ECC_ CB0

MA_ECC_ CB1

MA_ECC_ CB2

MA_ECC_ CB3

MA_ECC_ CB4

MA_ECC_ CB5

MA_ECC_ CB6

MA_ECC_ CB7

AW18

AY15

AV15

AU15

AW14

AY13

AV14

AW13

AU14

AW12

AT19

AU13

AW11

AU24

AT11

AR10

AT22

AU22

AT20

AV20

AU19

AU12

AV21

AW24

AU21

AU23

AU10

AW10

AV10

AY10

AV23

AV24

AW23

AY24

AR22

AR21

AP18

AN18

AN21

AP21

AP19

AN19

AV8

AK22

AM22

AL23

AK23

AL10

AM10

AP10

AN10

AR11

AP11

AK9

AL9

AK11

AM11

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

SA_WE#

SA_CAS#

SA_RAS#

SA_BS[0]

SA_BS[1]

SA_BS[2]

SA_CS[0]#

SA_CS[1]#

SA_CS[2]#

SA_CS[3]#

SA_CKE[0]

SA_CKE[1]

SA_CKE[2]

SA_CKE[3]

SA_ODT[0]

SA_ODT[1]

SA_ODT[2]

SA_ODT[3]

SA_CK[0]

SA_CK[0]#

SA_CK[1]

SA_CK[1]#

SA_CK[2]

SA_CK[2]#

SA_CK[3]

SA_CK[3]#

SM_DRAMRST#

SA_CS[4]#

SA_CS[5]#

SA_CS[6]#

SA_CS[7]#

SA_DQS[8]

SA_DQS[8]#

SA_ECC_CB[0]

SA_ECC_CB[1]

SA_ECC_CB[2]

SA_ECC_CB[3]

SA_ECC_CB[4]

SA_ECC_CB[5]

SA_ECC_CB[6]

SA_ECC_CB[7]

DDR_A

DDR_A

SOCKET_ 1156P

SOCKET_ 1156P

3

SA_DQS#[0]

SA_DQS#[1]

SA_DQS[2]#

SA_DQS#[3]

SA_DQS[4]#

SA_DQS[5]#

SA_DQS[6]#

SA_DQS[7]#

3

SA_DQS[0]

SA_DM[0]

SA_DQ[0]

SA_DQ[1]

SA_DQ[2]

SA_DQ[3]

SA_DQ[4]

SA_DQ[5]

SA_DQ[6]

SA_DQ[7]

SA_DQS[1]

SA_DM[1]

SA_DQ[8]

SA_DQ[9]

SA_DQ[10]

SA_DQ[11]

SA_DQ[12]

SA_DQ[13]

SA_DQ[14]

SA_DQ[15]

SA_DQS[2]

SA_DM[2]

SA_DQ[16]

SA_DQ[17]

SA_DQ[18]

SA_DQ[19]

SA_DQ[20]

SA_DQ[21]

SA_DQ[22]

SA_DQ[23]

SA_DQS[3]

SA_DM[3]

SA_DQ[24]

SA_DQ[25]

SA_DQ[26]

SA_DQ[27]

SA_DQ[28]

SA_DQ[29]

SA_DQ[30]

SA_DQ[31]

SA_DQS[4]

SA_DM[4]

SA_DQ[32]

SA_DQ[33]

SA_DQ[34]

SA_DQ[35]

SA_DQ[36]

SA_DQ[37]

SA_DQ[38]

SA_DQ[39]

SA_DQS[5]

SA_DM[5]

SA_DQ[40]

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

SA_DQ[44]

SA_DQ[45]

SA_DQ[46]

SA_DQ[47]

SA_DQS[6]

SA_DM[6]

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

SA_DQ[52]

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQS[7]

SA_DM[7]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

Rev 1.2

Rev 1.2

AK3

AJ3

AJ2

AH1

AJ4

AL2

AL1

AG2

AH2

AK1

AK2

AP2

AP3

AN1

AN3

AN2

AR3

AR2

AM3

AM2

AP1

AR4

AU4

AU3

AU1

AT4

AU2

AW3

AW4

AT3

AT1

AV2

AV4

AY6

AW6

AV6

AW5

AY5

AU8

AY8

AU5

AV5

AV7

AW7

AR28

AT29

AN29

AN27

AT28

AP28

AP30

AN26

AR27

AR29

AN30

AV32

AW32

AW31

AU30

AU31

AV33

AU34

AV30

AW30

AU33

AW33

AW36

AV35

AU35

AW35

AY35

AV37

AU37

AY34

AW34

AV36

AW37

AR39

AR38

AT38

AT39

AT40

AN38

AN39

AU38

AU39

AP39

AP40

M_CHA_D QS0

M_CHA_D QS0#

M_CHA_D M0

M_CHA_D Q0

M_CHA_D Q1

M_CHA_D Q2

M_CHA_D Q3

M_CHA_D Q4

M_CHA_D Q5

M_CHA_D Q6

M_CHA_D Q7

M_CHA_D QS1

M_CHA_D QS1#

M_CHA_D M1

M_CHA_D Q8

M_CHA_D Q9

M_CHA_D Q10

M_CHA_D Q11

M_CHA_D Q12

M_CHA_D Q13

M_CHA_D Q14

M_CHA_D Q15

M_CHA_D QS2

M_CHA_D QS2#

M_CHA_D M2

M_CHA_D Q16

M_CHA_D Q17

M_CHA_D Q18

M_CHA_D Q19

M_CHA_D Q20

M_CHA_D Q21

M_CHA_D Q22

M_CHA_D Q23

M_CHA_D QS3

M_CHA_D QS3#

M_CHA_D M3

M_CHA_D Q24

M_CHA_D Q25

M_CHA_D Q26

M_CHA_D Q27

M_CHA_D Q28

M_CHA_D Q29

M_CHA_D Q30

M_CHA_D Q31

M_CHA_D QS4

M_CHA_D QS4#

M_CHA_D M4

M_CHA_D Q32

M_CHA_D Q33

M_CHA_D Q34

M_CHA_D Q35

M_CHA_D Q36

M_CHA_D Q37

M_CHA_D Q38

M_CHA_D Q39

M_CHA_D QS5

M_CHA_D QS5#

M_CHA_D M5

M_CHA_D Q40

M_CHA_D Q41

M_CHA_D Q42

M_CHA_D Q43

M_CHA_D Q44

M_CHA_D Q45

M_CHA_D Q46

M_CHA_D Q47

M_CHA_D QS6

M_CHA_D QS6#

M_CHA_D M6

M_CHA_D Q48

M_CHA_D Q49

M_CHA_D Q50

M_CHA_D Q51

M_CHA_D Q52

M_CHA_D Q53

M_CHA_D Q54

M_CHA_D Q55

M_CHA_D QS7

M_CHA_D QS7#

M_CHA_D M7

M_CHA_D Q56

M_CHA_D Q57

M_CHA_D Q58

M_CHA_D Q59

M_CHA_D Q60

M_CHA_D Q61

M_CHA_D Q62

M_CHA_D Q63

2

M_CHA_D Q[0..63] 16

M_CHA_D QS0 16

M_CHA_D QS0# 16

M_CHA_D M0 16

M_CHA_D QS1 16

M_CHA_D QS1# 16

M_CHA_D M1 16

M_CHA_D QS2 16

M_CHA_D QS2# 16

M_CHA_D M2 16

M_CHA_D QS3 16

M_CHA_D QS3# 16

M_CHA_D M3 16

M_CHA_D QS4 16

M_CHA_D QS4# 16

M_CHA_D M4 16

M_CHA_D QS5 16

M_CHA_D QS5# 16

M_CHA_D M5 16

M_CHA_D QS6 16

M_CHA_D QS6# 16

M_CHA_D M6 16

M_CHA_D QS7 16

M_CHA_D QS7# 16

M_CHA_D M7 16

1

PEGATRON DT-MB RESTRICTED SECRET

CPU 1160 + MEMORY - 1

CPU 1160 + MEMORY - 1

CPU 1160 + MEMORY - 1

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

IPMIP-DP

IPMIP-DP

IPMIP-DP

Engineer:

Vic_Chen

Vic_Chen

Vic_Chen

10 68Wednesd ay, April 07, 2010

10 68Wednesd ay, April 07, 2010

1

10 68Wednesd ay, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Page 11

5

M_CHB_M AA[0..15]17

D D

M_CHB_W E#17

M_CHB_C AS#17

M_CHB_R AS#17

M_CHB_B A017

M_CHB_B A117

M_CHB_B A217

M_CHB_C S#01 7

M_CHB_C S#11 7

M_CHB_C S#21 7

C C

B B

NOTE:

M_CHB_C S#31 7

M_CHB_C KE017

M_CHB_C KE117

M_CHB_C KE217

M_CHB_C KE317

M_CHB_O DT017

M_CHB_O DT117

M_CHB_O DT217

M_CHB_O DT317

M_CHB_C LK01 7

M_CHB_C LK0#17

M_CHB_C LK11 7

M_CHB_C LK1#17

M_CHB_C LK21 7

M_CHB_C LK2#17

M_CHB_C LK31 7

M_CHB_C LK3#17

M_CHB_D QS817

M_CHB_D QS8#17

For ECC DIMM

MB_ECC_ CB[0..7]17

A A

5

4

I

I

HU1B

HU1B

M_CHB_M AA0

M_CHB_M AA1

M_CHB_M AA2

M_CHB_M AA3

M_CHB_M AA4

M_CHB_M AA5

M_CHB_M AA6

M_CHB_M AA7

M_CHB_M AA8

M_CHB_M AA9

M_CHB_M AA10

M_CHB_M AA11

M_CHB_M AA12

M_CHB_M AA13

M_CHB_M AA14

M_CHB_M AA15

M_CHB_B A0

M_CHB_B A1

M_CHB_B A2

M_CHB_C S#0

M_CHB_C S#1

M_CHB_C S#2

M_CHB_C S#3

M_CHB_C KE0

M_CHB_C KE1

M_CHB_C KE2

M_CHB_C KE3

M_CHB_O DT0

M_CHB_O DT1

M_CHB_O DT2

M_CHB_O DT3

HT5TPC26bNOBOM HT5TPC26bNOBOM

1

HT6TPC26bNOBOM HT6TPC26bNOBOM

1

HT7TPC26bNOBOM HT7TPC26bNOBOM

1

HT8TPC26bNOBOM HT8TPC26bNOBOM

1

4

TP_CPU_ AM23

TP_CPU_ AM24

TP_CPU_ AL24

TP_CPU_ AK24

M_CHB_D QS8

M_CHB_D QS8#

MB_ECC_ CB0

MB_ECC_ CB1

MB_ECC_ CB2

MB_ECC_ CB3

MB_ECC_ CB4

MB_ECC_ CB5

MB_ECC_ CB6

MB_ECC_ CB7

AU20

AU18

AV18

AU17

AY18

AV17

AW17

AU16

AT17

AY16

AY25

AW16

AW15

AW28

AY12

AV11

AU26

AW27

AW26

AU25

AW25

AV12

AY27

AW29

AV26

AV29

AW8

AY9

AU9

AV9

AU27

AU29

AV27

AU28

AR17

AR16

AT15

AR15

AN17

AN16

AR19

AR18

AM23

AM24

AL24

AK24

AR14

AR13

AR12

AT13

AN15

AP14

AM12

AN12

AN14

AP13

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

SB_WE#

SB_CAS#

SB_RAS#

SB_BS[0]

SB_BS[1]

SB_BS[2]

SB_CS[0]#

SB_CS[1]#

SB_CS[2]#

SB_CS[3]#

SB_CKE[0]

SB_CKE[1]

SB_CKE[2]

SB_CKE[3]

SB_ODT[0]

SB_ODT[1]

SB_ODT[2]

SB_ODT[3]

SB_CK[0]

SB_CK[0]#

SB_CK[1]

SB_CK[1]#

SB_CK[2]

SB_CK[2]#

SB_CK[3]

SB_CK[3]#

SB_CS[4]#

SB_CS[5]#

SB_CS[6]#

SB_CS[7]#

SB_DQS[8]

SB_DQS[8]#

SB_ECC_CB[0]

SB_ECC_CB[1]

SB_ECC_CB[2]

SB_ECC_CB[3]

SB_ECC_CB[4]

SB_ECC_CB[5]

SB_ECC_CB[6]

SB_ECC_CB[7]

DDR_B

DDR_B

SOCKET_ 1156P

SOCKET_ 1156P

3

SB_DQS[0]

SB_DQS[0]#

SB_DM[0]

SB_DQ[0]

SB_DQ[1]

SB_DQ[2]

SB_DQ[3]

SB_DQ[4]

SB_DQ[5]

SB_DQ[6]

SB_DQ[7]

SB_DQS[1]

SB_DQS[1]#

SB_DM[1]

SB_DQ[8]

SB_DQ[9]

SB_DQ[10]

SB_DQ[11]

SB_DQ[12]

SB_DQ[13]

SB_DQ[14]

SB_DQ[15]

SB_DQS[2]

SB_DQS#[2]

SB_DM[2]

SB_DQ[16]

SB_DQ[17]

SB_DQ[18]

SB_DQ[19]

SB_DQ[20]

SB_DQ[21]

SB_DQ[22]

SB_DQ[23]

SB_DQS[3]

SB_DQS#[3]

SB_DM[3]

SB_DQ[24]

SB_DQ[25]

SB_DQ[26]

SB_DQ[27]

SB_DQ[28]

SB_DQ[29]

SB_DQ[30]

SB_DQ[31]

SB_DQS[4]

SB_DQS[4]#

SB_DM[4]

SB_DQ[32]

SB_DQ[33]

SB_DQ[34]

SB_DQ[35]

SB_DQ[36]

SB_DQ[37]

SB_DQ[38]

SB_DQ[39]

SB_DQS[5]

SB_DQS[5]#

SB_DM[5]

SB_DQ[40]

SB_DQ[41]

SB_DQ[42]

SB_DQ[43]

SB_DQ[44]

SB_DQ[45]

SB_DQ[46]

SB_DQ[47]

SB_DQS[6]

SB_DQS#[6]

SB_DM[6]

SB_DQ[48]

SB_DQ[49]

SB_DQ[50]

SB_DQ[51]

SB_DQ[52]

SB_DQ[53]

SB_DQ[54]

SB_DQ[55]

SB_DQS[7]

SB_DQS[7]#

SB_DM[7]

SB_DQ[56]

SB_DQ[57]

SB_DQ[58]

SB_DQ[59]

SB_DQ[60]

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

Rev 1.2

Rev 1.2

3

AF4

AE5

AE4

AD7

AD6

AH8

AJ8

AC7

AC6

AF5

AE6

AH6

AJ5

AH4

AG5

AH7

AK6

AL4

AG6

AG4

AJ7

AK7

AN6

AM6

AM7

AL6

AN5

AP6

AR5

AL5

AM4

AN7

AP5

AR8

AP8

AT7

AT6

AR7

AR9

AM8

AN8

AR6

AL8

AT9

AT25

AR24

AN24

AN23

AP23

AR25

AR26

AT23

AP22

AP25

AT26

AP32

AR32

AN32

AT32

AP31

AR33

AM32

AT31

AR31

AR34

AT33

AR36

AR37

AM33

AR35

AT36

AN33

AP36

AP34

AT35

AN34

AP37

AL37

AM36

AK35

AL35

AM35

AJ36

AJ37

AN35

AM34

AJ35

AL36

M_CHB_D QS0

M_CHB_D QS0#

M_CHB_D M0

M_CHB_D Q0

M_CHB_D Q1

M_CHB_D Q2

M_CHB_D Q3

M_CHB_D Q4

M_CHB_D Q5

M_CHB_D Q6

M_CHB_D Q7

M_CHB_D QS1

M_CHB_D QS1#

M_CHB_D M1

M_CHB_D Q8

M_CHB_D Q9

M_CHB_D Q10

M_CHB_D Q11

M_CHB_D Q12

M_CHB_D Q13

M_CHB_D Q14

M_CHB_D Q15

M_CHB_D QS2

M_CHB_D QS2#

M_CHB_D M2

M_CHB_D Q16

M_CHB_D Q17

M_CHB_D Q18

M_CHB_D Q19

M_CHB_D Q20

M_CHB_D Q21

M_CHB_D Q22

M_CHB_D Q23

M_CHB_D QS3

M_CHB_D QS3#

M_CHB_D M3

M_CHB_D Q24

M_CHB_D Q25

M_CHB_D Q26

M_CHB_D Q27

M_CHB_D Q28

M_CHB_D Q29

M_CHB_D Q30

M_CHB_D Q31

M_CHB_D QS4

M_CHB_D QS4#

M_CHB_D M4

M_CHB_D Q32

M_CHB_D Q33

M_CHB_D Q34

M_CHB_D Q35

M_CHB_D Q36

M_CHB_D Q37

M_CHB_D Q38

M_CHB_D Q39

M_CHB_D QS5

M_CHB_D QS5#

M_CHB_D M5

M_CHB_D Q40

M_CHB_D Q41

M_CHB_D Q42

M_CHB_D Q43

M_CHB_D Q44

M_CHB_D Q45

M_CHB_D Q46

M_CHB_D Q47

M_CHB_D QS6

M_CHB_D QS6#

M_CHB_D M6

M_CHB_D Q48

M_CHB_D Q49

M_CHB_D Q50

M_CHB_D Q51

M_CHB_D Q52

M_CHB_D Q53

M_CHB_D Q54

M_CHB_D Q55

M_CHB_D QS7

M_CHB_D QS7#

M_CHB_D M7

M_CHB_D Q56

M_CHB_D Q57

M_CHB_D Q58

M_CHB_D Q59

M_CHB_D Q60

M_CHB_D Q61

M_CHB_D Q62

M_CHB_D Q63

2

M_CHB_D Q[0..63] 17

M_CHB_D QS0 17

M_CHB_D QS0# 17

M_CHB_D M0 17

M_CHB_D QS1 17

M_CHB_D QS1# 17

M_CHB_D M1 17

M_CHB_D QS2 17

M_CHB_D QS2# 17

M_CHB_D M2 17

M_CHB_D QS3 17

M_CHB_D QS3# 17

M_CHB_D M3 17

M_CHB_D QS4 17

M_CHB_D QS4# 17

M_CHB_D M4 17

M_CHB_D QS5 17

M_CHB_D QS5# 17

M_CHB_D M5 17

M_CHB_D QS6 17

M_CHB_D QS6# 17

M_CHB_D M6 17

M_CHB_D QS7 17

M_CHB_D QS7# 17

M_CHB_D M7 17

1

PEGATRON DT-MB RESTRICTED SECRET

CPU 1160 + MEMORY - 2

CPU 1160 + MEMORY - 2

CPU 1160 + MEMORY - 2

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

IPMIP-DP

IPMIP-DP

IPMIP-DP

Engineer:

Vic_Chen

Vic_Chen

Vic_Chen

11 68Wednesd ay, April 07, 2010

11 68Wednesd ay, April 07, 2010

1

11 68Wednesd ay, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Page 12

5

I

I

HU1C

D D

C C

EXP_RXP 038

EXP_RXN 038

EXP_RXP 138

EXP_RXN 138

EXP_RXP 238

EXP_RXN 238

EXP_RXP 338

EXP_RXN 338

EXP_RXP 438

EXP_RXN 438

EXP_RXP 538

EXP_RXN 538

EXP_RXP 638

EXP_RXN 638

EXP_RXP 738

EXP_RXN 738

EXP_RXP 838

EXP_RXN 838

EXP_RXP 938

EXP_RXN 938

EXP_RXP 1038

EXP_RXN 1038

EXP_RXP 1138

EXP_RXN 1138

EXP_RXP 1238

EXP_RXN 1238

EXP_RXP 1338

EXP_RXN 1338

EXP_RXP 1438

EXP_RXN 1438

EXP_RXP 1538

EXP_RXN 1538

EXP_RXP 0

EXP_RXN 0

EXP_RXP 1

EXP_RXN 1

EXP_RXP 2

EXP_RXN 2

EXP_RXP 3

EXP_RXN 3

EXP_RXP 4

EXP_RXN 4

EXP_RXP 5

EXP_RXN 5

EXP_RXP 6

EXP_RXN 6

EXP_RXP 7

EXP_RXN 7

EXP_RXP 8

EXP_RXN 8

EXP_RXP 9

EXP_RXN 9

EXP_RXP 10

EXP_RXN 10

EXP_RXP 11

EXP_RXN 11

EXP_RXP 12

EXP_RXN 12

EXP_RXP 13

EXP_RXN 13

EXP_RXP 14

EXP_RXN 14

EXP_RXP 15

EXP_RXN 15

C9

D9

B8

C8

A7

A6

B6

C6

A5

B5

B4

C4

C3

D3

D2

E2

E1

F1

G3

G2

G1

H1

J3

J2

J1

K1

L2

L3

P3

P4

T3

T4

HU1C

PEG_RX[0]

PEG_RX[0]#

PEG_RX[1]

PEG_RX[1]#

PEG_RX[2]

PEG_RX[2]#

PEG_RX[3]

PEG_RX[3]#

PEG_RX[4]

PEG_RX[4]#

PEG_RX[5]

PEG_RX[5]#

PEG_RX[6]

PEG_RX[6]#

PEG_RX[7]

PEG_RX[7]#

PEG_RX[8]

PEG_RX[8]#

PEG_RX[9]

PEG_RX[9]#

PEG_RX[10]

PEG_RX[10]#

PEG_RX[11]

PEG_RX[11]#

PEG_RX[12]

PEG_RX[12]#

PEG_RX[13]

PEG_RX[13]#

PEG_RX[14]

PEG_RX[14]#

PEG_RX[15]

PEG_RX[15]#

4

PEG_TX[0]

PEG_TX[0]#

PEG_TX[1]

PEG_TX[1]#

PEG_TX[2]

PEG_TX[2]#

PEG_TX[3]

PEG_TX[3]#

PEG_TX[4]

PEG_TX[4]#

PEG_TX[5]

PEG_TX[5]#

PEG_TX[6]

PEG_TX[6]#

PEG_TX[7]

PEG_TX[7]#

PEG_TX[8]

PEG_TX[8]#

PEG_TX[9]

PEG_TX[9]#

PEG_TX[10]

PEG_TX[10]#

PEG_TX[11]

PEG_TX[11]#

PEG_TX[12]

PEG_TX[12]#

PEG_TX[13]

PEG_TX[13]#

PEG_TX[14]

PEG_TX[14]#

PEG_TX[15]

PEG_TX[15]#

3

EXP_TXP 0

C7

EXP_TXN 0

D7

EXP_TXP 1

E7

EXP_TXN 1

E6

EXP_TXP 2

E5

EXP_TXN 2

F5

EXP_TXP 3

F3

EXP_TXN 3

F4

EXP_TXP 4

G6

EXP_TXN 4

G5

EXP_TXP 5

H4

EXP_TXN 5

H3

EXP_TXP 6

F7

EXP_TXN 6

G7

EXP_TXP 7

J6

EXP_TXN 7

J5

EXP_TXP 8

K3

EXP_TXN 8

K4

EXP_TXP 9

H8

EXP_TXN 9

J8

EXP_TXP 10

L6

EXP_TXN 10

L5

EXP_TXP 11

M4

EXP_TXN 11

M3

EXP_TXP 12

K7

EXP_TXN 12

L7

EXP_TXP 13

N6

EXP_TXN 13

N5

EXP_TXP 14

M8

EXP_TXN 14

N8

EXP_TXP 15

R5

EXP_TXN 15

R6

EXP_TXP 0 38

EXP_TXN 0 3 8

EXP_TXP 1 38

EXP_TXN 1 3 8

EXP_TXP 2 38

EXP_TXN 2 3 8

EXP_TXP 3 38

EXP_TXN 3 3 8

EXP_TXP 4 38

EXP_TXN 4 3 8

EXP_TXP 5 38

EXP_TXN 5 3 8

EXP_TXP 6 38

EXP_TXN 6 3 8

EXP_TXP 7 38

EXP_TXN 7 3 8

EXP_TXP 8 38

EXP_TXN 8 3 8

EXP_TXP 9 38

EXP_TXN 9 3 8

EXP_TXP 10 38

EXP_TXN 10 38

EXP_TXP 11 38

EXP_TXN 11 38

EXP_TXP 12 38

EXP_TXN 12 38

EXP_TXP 13 38

EXP_TXN 13 38

EXP_TXP 14 38

EXP_TXN 14 38

EXP_TXP 15 38

EXP_TXN 15 38

DL_FSYNC_ 024

DL_LSYNC_ 024

DL_FSYNC_ 124

DL_LSYNC_ 124

DL_INT24

2

I

I

HU1D

HU1D

AC4

AD4

AC3

AD3

AC2

SOCKET_ 1156P

SOCKET_ 1156P

FDI_FSYNC[0]

FDI_LSYNC[0]

FDI_FSYNC[1]

FDI_LSYNC[1]

FDI_INT

FDI_TX[0]

FDI_TX[0]#

FDI_TX[1]

FDI_TX[1]#

FDI_TX[2]

FDI_TX[2]#

FDI_TX[3]

FDI_TX[3]#

DISPLAY LINK

DISPLAY LINK

FDI_TX[4]

FDI_TX[4]#

FDI_TX[5]

FDI_TX[5]#

FDI_TX[6]

FDI_TX[6]#

FDI_TX[7]

FDI_TX[7]#

Rev 1.2

Rev 1.2

1

U6

U5

V4

V3

U8

U7

W8

W7

W5

W4

R8

R7

Y4

Y3

Y6

Y5

FDI_TXP0 24

FDI_TXN0 24

FDI_TXP1 24

FDI_TXN1 24

FDI_TXP2 24

FDI_TXN2 24

FDI_TXP3 24

FDI_TXN3 24

FDI_TXP4 24

FDI_TXN4 24

FDI_TXP5 24

FDI_TXN5 24

FDI_TXP6 24

FDI_TXN6 24

FDI_TXP7 24

FDI_TXN7 24

DMI_RXP020

B B

A A

DMI_RXN020

DMI_RXP120

DMI_RXN120

DMI_RXP220

DMI_RXN220

DMI_RXP320

DMI_RXN320

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

R1

DMI_RX[0]

T1

DMI_RX[0]#

U3

DMI_RX[1]

U2

DMI_RX[1]#

U1

DMI_RX[2]

V1

DMI_RX[2]#

W3

DMI_RX[3]

W2

DMI_RX[3]#

SOCKET_ 1156P

SOCKET_ 1156P

DMI_TX[0]

DMI_TX[0]#

DMI_TX[1]

DMI_TX[1]#

DMI_TX[2]

DMI_TX[2]#

DMI PEG

DMI PEG

DMI_TX[3]

DMI_TX[3]#

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

Rev 1.2

Rev 1.2

L1

M1

N3

N2

N1

P1

R2

R3

D11

C10

B10

A11

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

CPU_GRC OMP

CPU_GRB IAS

DMI_TXP0 20

DMI_TXN0 20

DMI_TXP1 20

DMI_TXN1 20

DMI_TXP2 20

DMI_TXN2 20

DMI_TXP3 20

DMI_TXN3 20

I

I

HR1

HR1

49.9 1%

49.9 1%

1 2

I

I

HR2

HR2

750

750

1%

1%

1 2

GND

GND

PEGATRON DT-MB RESTRICTED SECRET

CPU 1160 + MEMORY - 3

CPU 1160 + MEMORY - 3

CPU 1160 + MEMORY - 3

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IPMIP-DP

IPMIP-DP

IPMIP-DP

Engineer:

Vic_Chen

Vic_Chen

Vic_Chen

12 68Wednesd ay, April 07, 2010

12 68Wednesd ay, April 07, 2010

1

12 68Wednesd ay, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Page 13

5

CK_133M _PCH_OUT24

CK_133M _PCH_OUT#24

CK_100M _PEG_DMI24

CK_100M _PEG_DMI#24

D D

HR108

HR108

0

Divide to 1P1V

+1P5V_D UAL

12

HR78

HR78

1.1K

1.1K

1%

1%

CPUPW RGD22,5 7

PLTRST#22 ,36,47,50,57

VTTPW RGD59 ,64

DRAM_PW ROK22

HR75

HR75

VP

VP

C C

B B

A A

PECI_SIO48

PECI21

H_THMTR IP#21

PM_SYNC21

PEG CONFIG TABLE

CFG[0~5] All have internal P-U

CFG1

CFG0

1

1

0 1

H

NORM Reversal

CFG3

CFG4 Disabled

CFG7

Engineering experiment

CFG15

Engineering experiment

1 2

NI

NI

1 2

+3P3VSB

12

VTTPG_G ATE2

3

3

C

C

B

1

B

1

E

E

2

2

GND

VTTPG_G ATE1

CFG2

1

1

L

Enabled

HR74

HR74

I

I

HR76

HR76

10K

10K

I

I

HQ4

HQ4

PMBS390 4

PMBS390 4

1 2

1

1

PMBS390 4

PMBS390 4

I

I

HR77

HR77

4.7K

4.7K

GND

PCIE CONFIG

1 x 16

2 x 8

12

0

0

GND

0

0

3

3

HQ3

HQ3

C

C

I

I

B

B

E

E

2

2

3

GND

HR21 1.5K

HR21 1.5K

NI

NI

HR22 1.5K

HR22 1.5K

NI

NI

HR23 1.5K

HR23 1.5K

NI

NI

HR24 1.5K

HR24 1.5K

NI

NI

HR25 1.5K

HR25 1.5K

NI

NI

HR26 1.5K

HR26 1.5K

NI

NI

Description

PEG Lane Reversal

DP Presence

I

I

HR79

HR79

3K

3K

1%

1%

I

I

HD2

NI HD 2

NI

BAT54AW

BAT54AW

+1P1V_V TT

12

NI

NI

HR6

HR6

49.9

49.9

1%

1%

12

12

NI

NI

HR30

HR30

51

51

+1P1V_V TT

2

1

NOTE:

CFG[0:5] have i nternal pull-up

12

12

12

12

12

12

HR86 1.5K

HR86 1.5K

NI

NI

HR84 1.5K

HR84 1.5K

NI

NI

HR85 1.5K

HR85 1.5K

NI

NI

GND

0

NOBOM

NOBOM

1 2

GND GND

HR7

HR4

HR5 1.3K 1%

HR5 1.3K 1%

1 2

I

I

+1P1V_V TT+1P1V_V TT+1P1V_V TT +1P1V_V TT

+1P1V_V TT

12

I

I

I

I

HR29

HR29

HR28

HR28

51

51

51

51

HR13 20 1 %

HR13 20 1 %

I

I

HR12 20 1 %

HR12 20 1 %

I

I

HR14 100 1%

HR14 100 1%

I

I

HR16 24.9 1%

HR16 24.9 1%

I

I

HR15 130 1%

HR15 130 1%

I

I

HR20 49.9 1%

HR20 49.9 1%

I

I

HR19 49.9 1%

HR19 49.9 1%

I

I

GND

SLP_S3# 22,48,64,66

12

12

12

1 2

0H R7

0

12

0H R4

0

12

12

I

I

HR33

HR33

51

51

12

12

12

12

12

12

12

4

HR109

HR109

0

0

NOBOM

NOBOM

PU in SIO

NOBOM

NOBOM

NOBOM

NOBOM

12

NI

NI

HR31

HR31

51

51

SKTOCC#22

HT21TPC26bNOBOM HT21TPC26bNOBOM

HT84TPC26bNOBOM HT84TPC26bNOBOM

HT85TPC26bNOBOM HT85TPC26bNOBOM

HT86TPC26bNOBOM HT86TPC26bNOBOM

HT88TPC26bNOBOM HT88TPC26bNOBOM

HT24TPC26bNOBOM HT24TPC26bNOBOM

HT25TPC26bNOBOM HT25TPC26bNOBOM

HT26TPC26bNOBOM HT26TPC26bNOBOM

HT28TPC26bNOBOM HT28TPC26bNOBOM

HT29TPC26bNOBOM HT29TPC26bNOBOM

HT95TPC26b

HT95TPC26b

NOBOM

NOBOM

+1P1V_V TT

12

NI

NI

HR32

HR32

51

51

PROC_PW RGD_AH36

PROC_PW RGD_AH35

12

I

I

HR8

HR8

665

665

1%

1%

GND

PCH_PEC I

HIERR#

PROCHOT #

MCP_COM P2

MCP_COM P3

MCP_SM_ RCOMP0

MCP_SM_ RCOMP1

MCP_SM_ RCOMP2

MCP_NOR TH_COMP

MCP_SOU TH_COMP

TP_GFX_ DPRSLPVR

1

1

1

1

1

1

1

1

1

1

CPU_BCL K1#

CPU_BCL K1

TDO_TDI_M

1

H_CPURS T

12

I

I

HC20

HC20

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

H_CFG0

H_CFG1

H_CFG2

H_CFG3

H_CFG4

H_CFG5

CFG6

CFG7

TP_CFG8

TP_CFG9

TP_CFG1 0

TP_CFG1 1

TP_CFG1 2

TP_CFG1 3

TP_CFG1 4

CFG15

TP_CFG1 6

TP_CFG1 7

AA7

AA6

AA3

AA4

AA8

AF37

AF38

AH36

AH35

AF34

AG37

AH37

AG35

AG39

AH34

AF35

AH39

AB5

AB4

B11

C11

AG1

AD1

AE1

AF2

AF36

AK38

E10

H10

G12

H12

K10

K12

Y8

J10

E8

G8

F10

H9

E9

F9

K8

J12

L8

K9

H7

L11

I

I

HU1E

HU1E

BCLK[0]

BCLK[0]#

PEG_CLK

PEG_CLK#

BCLK[1]#

BCLK[1]

TDI_M

TDO_M

VCCPWRGOOD_1

VCCPWRGOOD_0

RSTIN#

VTTPWRGOOD

SM_DRAMPWROK

PECI

CATERR#

PROCHOT#

THERMTRIP#

PM_SYNC

PM_EXT_TS[0]#

PM_EXT_TS[1]#

COMP2

COMP3

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

COMP1

COMP0

SKTOCC#

GFX_DPRSLPVR

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

MISC

MISC

3

VID[0]/MSID[0]

VID[1]/MSID[1]

VID[2]/MSID[2]

VID[3]/CSC[0]

VID[4]/CSC[1]

VID[5]/CSC[2]

VID[6]

VID[7]

PSI#

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

FC_AE38

VTT_SELECT

FC_AG40

VCC_SENSE

VSS_SENSE

VTT_SENSE

VSS_SENSE_VTT

VAXG_SENSE

VSSAXG_SENSE

ISENSE

TCK

TDO

TMS

TRST#

BCLK_ITP#

BCLK_ITP

PRDY#

PREQ#

DBR#

TAPPWRGOOD

RESET_OBS#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

BPM[4]#

BPM[5]#

BPM[6]#

BPM[7]#

2

VRM_VID0

U40

VRM_VID1

U39

VRM_VID2

U38

VRM_VID3

U37

VRM_VID4

U36

VRM_VID5

U35

VRM_VID6

U34

VRM_VID7

U33

AG38

GFX_VID0

G10

GFX_VID1

B12

GFX_VID2

E12

GFX_VID3

E11

GFX_VID4

C12

GFX_VID5

G11

GFX_VID6

J11

F12

GFX_IMON

F6

TP_CPU_ AE38

AE38

AF39

TP_CPU_ AG40

AG40

T35

T34

AE35

AE36

A13

B13

T40

AN37

AM37

TDI

AM38

AN40

AM39

AK40

AK39

AJ38

AK37

AL40

AK34

AL39

AL33

AL32

AK33

AK32

AM31

AL30

AK30

AK31

NOTE:

Lynnfield --> NI HR105/HR107

I

I

I

I

IPMIP-GS Add HR105 and HR107

+1P1V_V TT

BPM#0

BPM#1

BPM#2

BPM#3

BPM#4

BPM#5

BPM#6

BPM#7

1

1

HR105 0

HR105 0

1 2

HR107 0

HR107 0

1 2

+1P1V_V TT+1P1V _VTT

12

12

NI

NI

I

I

HR38

HR38

HR39

HR39

51

51

51

51

+1P1V_V TT+1P1V_V TT

12

12

NI

NI

HR35

HR35

51

51

1

1

1

1

1

1

1

1

VRM_VID[0..7] 9,5 9

GFX_VID[0..6] 9

HT9 TP C26b NOBOMHT9 TP C26b NOBOM

HT12 TPC26b NOBOMH T12 TPC 26b NOBOM

NI HR36,38,40

( CRB1.1 page.102 )

12

NI

NI

HR40

HR40

NOTE:

51

51

PLACE TCK, TDI, TMS RESISTOR C LOSE TO CPU SOC KET

NI

NI

HR34

HR34

51

51

HT11 TPC26b NOBOMH T11 TPC 26b NOBOM

HT16 TPC26b NOBOMH T16 TPC 26b NOBOM

HT20 TPC26b NOBOMH T20 TPC 26b NOBOM

HT89 TPC26b NOBOMH T89 TPC 26b NOBOM

HT90 TPC26b NOBOMH T90 TPC 26b NOBOM

HT91 TPC26b NOBOMH T91 TPC 26b NOBOM

HT92 TPC26b NOBOMH T92 TPC 26b NOBOM

HT93 TPC26b NOBOMH T93 TPC 26b NOBOM

12

NI

NI

HR36

HR36

51

51

GND GND

VRM_PSI# 59

GFX_VR_ EN 62

VTT_SEL ECT 64

VCC_SEN SE_A 59

VSS_SEN SE_A 59

VCCVTT_ SENSE_A 64

VSSVTT_ SENSE_A 64

VCCAXG_ SENSE_A 62

VSSAXG_ SENSE_A 62

MCP_ISENS E_A 59

12

I

I

HR37

HR37

51

51

CK_ITP# 57

CK_ITP 57

H_PRDY# 57

H_PREQ# 57

SYS_RESET # 8,22,52,57

H_TAPPW RGOOD 57

H_RSTOU T# 5 7

HR3

TCK 57

TDI 5 7

TDO 57

TMS 57

TRST# 57

Pin AJ38: PRDY#

CRB V1.1 , page.6 (Reserved pull-up for PRDY#)

PDG V1.0 , page.70(System Pull-up required)

Pin AL39: RESET_OBS#

CRB V1.1 , page.6 (Reserved pull-up for RESET_OBS#)

PDG V1.0 , page.393(System Pull-up required)

12

0H R3

0

NOBOM

NOBOM

1

GND

Rev 1.2

Rev 1.2

SOCKET_ 1156P

SOCKET_ 1156P

5

4

3

2

PEGATRON DT-MB RESTRICTED SECRET

CPU 1160 + MEMORY - 4

CPU 1160 + MEMORY - 4

CPU 1160 + MEMORY - 4

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPMIP-DP

IPMIP-DP

IPMIP-DP

Engineer:

Vic_Chen

Vic_Chen

Vic_Chen

13 68Wednesd ay, April 07, 2010

13 68Wednesd ay, April 07, 2010

1

13 68Wednesd ay, April 07, 2010

Rev

Rev

Rev

1.01

1.01

1.01

Page 14

5

I

I

HU1F

HU1F

CPU POWER

CPU POWER

A38

VCC_NCTF1

C40

VCC_NCTF2

D D

C C

B B

A A

5

A23

VCC1

A24

VCC2

A26

VCC3

A27

VCC4

A33

VCC5

A35

VCC6

A36

VCC7

B23

VCC8

B25

VCC9

B26

VCC10

B28

VCC11

B29

VCC12

B31

VCC13

B32

VCC14

B34

VCC15

B35

VCC16

B37

VCC17

B38

VCC18

C23

VCC19

C24

VCC20

C25

VCC21

C27

VCC22

C28

VCC23

C30

VCC24

C31

VCC25

C33

VCC26

C34

VCC27

C36

VCC28

C37

VCC29

C39

VCC30

D23

VCC31

D24

VCC32

D26

VCC33

D27

VCC34

D29

VCC35

D30

VCC36

D32

VCC37

D33

VCC38

D35

VCC39

D36

VCC40

D38

VCC41

D39

VCC42

E22

VCC43

E23

VCC44

E25

VCC45

E26

VCC46

E28

VCC47

E29

VCC48

E31

VCC49

E32

VCC50

E34

VCC51

E35

VCC52

E37

VCC53

E38

VCC54

E40

VCC55

F21

VCC56

F22

VCC57

F24

VCC58

F25

VCC59

F27

VCC60

F28

VCC61

F30

VCC62

F31

VCC63

F33

VCC64

F34

VCC65

F36

VCC66

F37

VCC67

F39

VCC68

F40

VCC69

G20

VCC70

G21

VCC71

G23

VCC72

G24

VCC73

G26

VCC74

G27

VCC75

G29

VCC76

G30

VCC77

G32

VCC78

G33

VCC79

G35

VCC80

G36

VCC81

G38

VCC82

G39

VCC83

H19

VCC84

H20

VCC85

H22

VCC86

H23

VCC87

H25

VCC88

R39

VCC181

R40

VCC182

SOCKET_ 1156P

SOCKET_ 1156P

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC104

VCC105

VCC106

VCC107

VCC108

VCC109

VCC110

VCC111

VCC112

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

VCC156

VCC157

VCC158

VCC159

VCC160

VCC161

VCC162

VCC163

VCC164

VCC165

VCC166

VCC167

VCC168

VCC169

VCC170

VCC171

VCC172

VCC173

VCC174

VCC175

VCC176

VCC177

VCC178

VCC179

VCC180

Rev 1.2

Rev 1.2

H26

H28

H29

H31

H32

H34

H35

H37

H38

H40

J18

J19

J21

J22

J24

J25

J27

J28

J30

J31

J33

J34

J36

J37

J39

J40

K17

K18

K20

K21

K23

K24

K26

K27

K29

K30

K32

K33

K35

K36

K38

K39

L17

L19

L20

L22

L23

L25

L26

L28

L29

L31

L32

L34

L35

L37

L38

L40

M17

M19

M21

M22

M24

M25

M27

M28

M30

M33

M34

M36

M37

M39

M40

N33

N35

N36

N38

N39

P33

P34

P35

P36

P37

P38

P39

P40

R33

R34

R35

R36

R37

R38

4

+1P1V_V TT+VCORE+VCORE +V_AXG+1P1V_V TT +1P5V_D UAL

AA33

AA34

AA35

AA36

AA37

AA38

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

AD33

AD34

AD35

AD36

AD37

AD38

AD39

AD40

AE33

AE34

AE39

AE40

AF33

AG33

AJ31

AJ32

V33

V34

V35

V36

V37

V38

V39

V40

Y33

Y34

Y35

Y36

Y37

Y38

AJ21

AJ25

AJ27

AJ29

AK20

AK21

AL20

AL21

AC8

AE8

AJ17

AJ19

AK19

AC5

AJ23

I

I

HU1G

HU1G

CPU POWER

CPU POWER

VTT1

VTT2

VTT3

VTT4

VTT5

VTT6

VTT7

VTT8

VTT9

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT25

VTT26

VTT27

VTT28

VTT29

VTT30

VTT31

VTT32

VTT33

VTT34

VTT35

VTT36

VTT37

VTT38

VTT39

VTT40

VTT41

VTT42

VTT43

VTT44

VTT45

VTT46

VTT47

VTT48

VTT49

VTT50

VTT51

VTT52

VTT53

VTT54

VTT55

VTT56

VTT57

VTT58

VTT59

SOCKET_ 1156P

SOCKET_ 1156P

3

VCCPLL1

VCCPLL2

VCCPLL3

Rev 1.2

Rev 1.2

VTT60

VTT61

VTT62

VTT63

VTT64

VTT78

VTT65

VTT66

VTT67

VTT68

VTT69

VTT70

VTT71

VTT72

VTT73

VTT74

VTT75

VTT76

VTT77

T6

T7

T8

V7

V8

AB7

V6

W1

W6

L10

M10

M11

M9

N7

P6

P7

P8

T2

V2

+1P8V_S FR

AF7

AF8

AG8

Check PDG 0.7

& CPU EDS REV.0 .7

Ch6.12 POWER SI GNALS

12

GND

I

I

HCB2

HCB2

1UF/16V

1UF/16V

X7R 10%

X7R 10%

mx_c0603

mx_c0603

GND

12

NI

NI

HR117

HR117

0

0

mx_r0603

mx_r0603

I

I

HU1H

HU1H

A14

A15

A17

A18

B14

B15

B17

B18

C14

C15

C17

C18

C20

C21

D14

D15

D17

D18

D20

D21

E14

E15

E17

E18

E20

F14

F15

F17

F18

F19

G14

G15

G17

G18

H14

H15

H17

J14

J15

J16

K14

K15

K16

L14

L15

L16

M14

M15

M16

SOCKET_ 1156P

SOCKET_ 1156P

2

MCH POWER

MCH POWER

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VAXG37

VAXG38

VAXG39

VAXG40

VAXG41

VAXG42

VAXG43

VAXG44

VAXG45

VAXG46

VAXG47

VAXG48

VAXG49

NOTE:

HR117 FOR

Lynnfield Only

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VDDQ19

Rev 1.2

Rev 1.2

AJ11

AJ13

AJ15

AT18

AT21

AT10

AU11

AV13

AV16

AV19

AV22

AV25

AV28

AW9

AY11

AY14

AY17

AY23

AY26

12

GND

I

I

HCB1

HCB1

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805

mx_c0805

12

GND

1

I

I

HCB3

HCB3

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805

mx_c0805

PEGATRON DT-MB RESTRICTED SECRET

CPU 1160 + MEMORY - 5

CPU 1160 + MEMORY - 5

CPU 1160 + MEMORY - 5

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

IPMIP-DP

IPMIP-DP

IPMIP-DP

Engineer:

Vic_Chen

Vic_Chen

Vic_Chen

14 68Tuesday, March 23, 2 010

14 68Tuesday, March 23, 2 010

1

14 68Tuesday, March 23, 2 010

Rev

Rev

Rev

1.01

1.01

1.01

Page 15

5

I

I

HU1I

HU1I

A16

VSS1

A25

VSS2

A28

VSS3

A34

VSS4

D D

C C

B B

A A

A37

VSS5

AA5

VSS6

AB3

VSS7

AB33

VSS8

AB34

VSS9

AB35

VSS10

AB36

VSS11

AB37

VSS12

AB38

VSS13

AB39

VSS14

AB40

VSS15

AB6

VSS16

AB8

VSS17

AC1

VSS18

AD5

VSS19

AD8

VSS20

AE3

VSS21

AE37

VSS22

AE7

VSS23