Page 1

5

IPM61-BE

Revision: 1.00

vinafix

PAGE

01

02

D D

04

05

06

07

08

09~14

15

16~18

19~27 INTEL_PCH(1~9)

28

29

30

31

32

C C

33

34

35

36

37

38

39

40

41~4203RJ45+USB 3.0 CONTROLLER

43~46

47

48~49

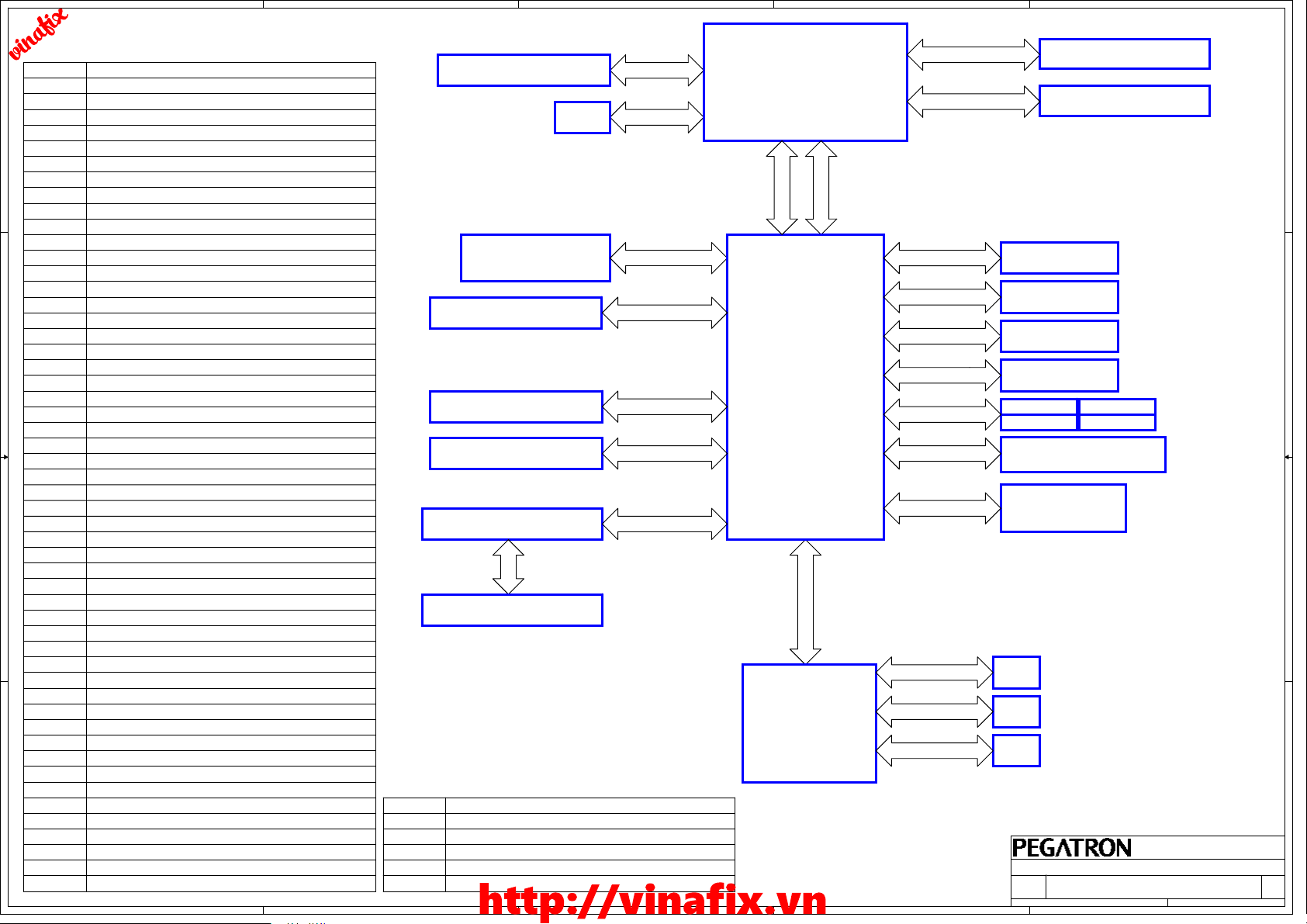

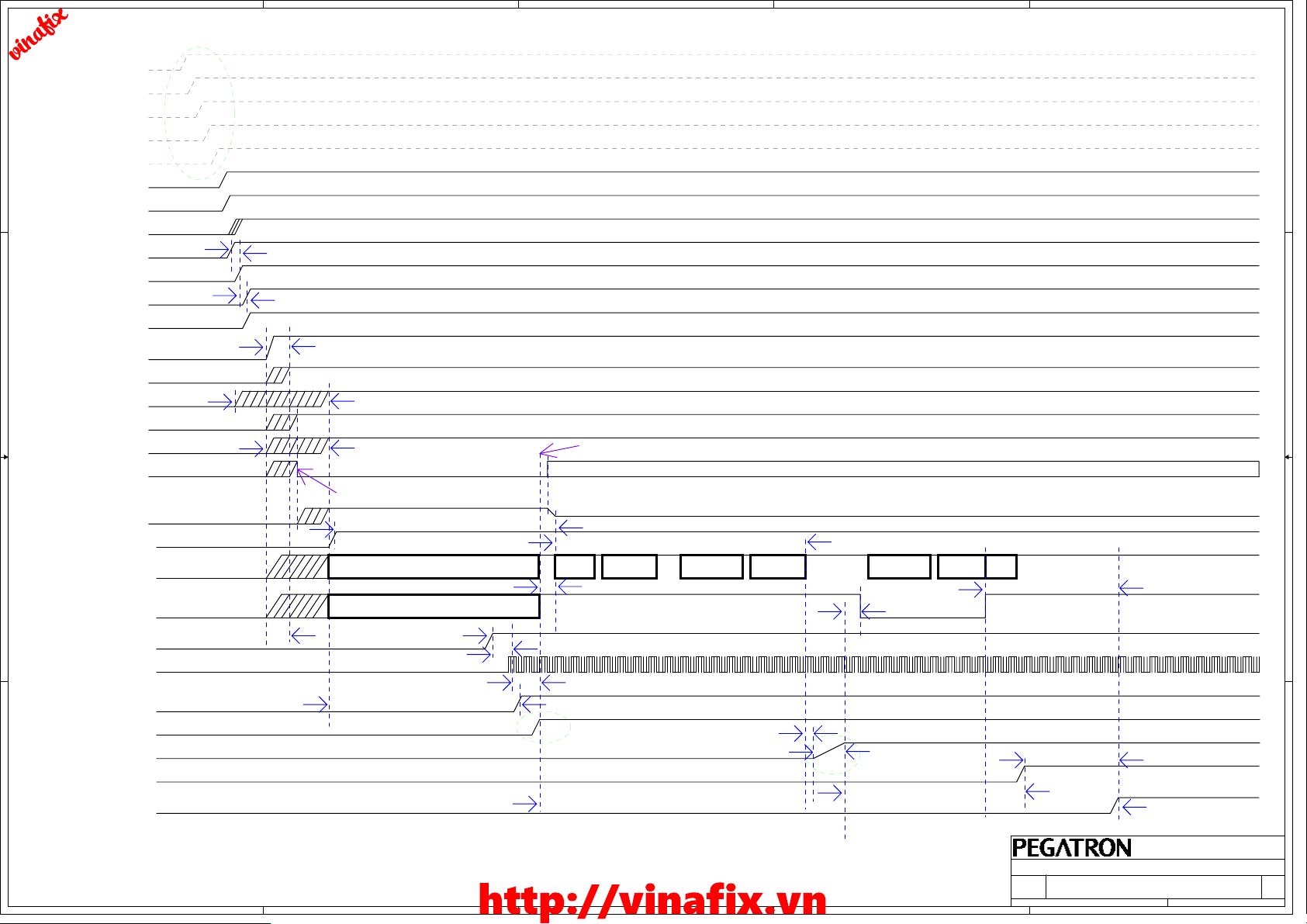

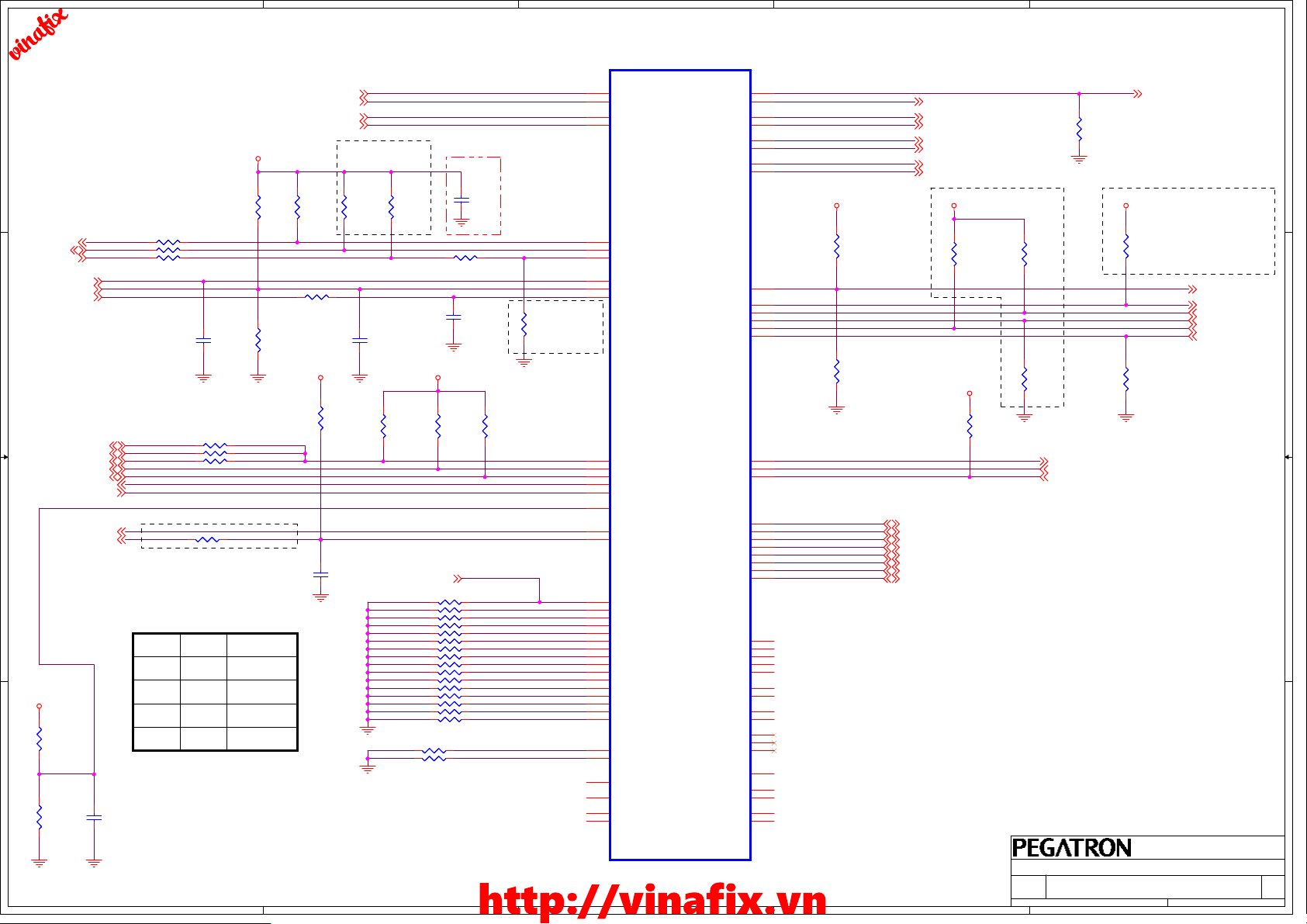

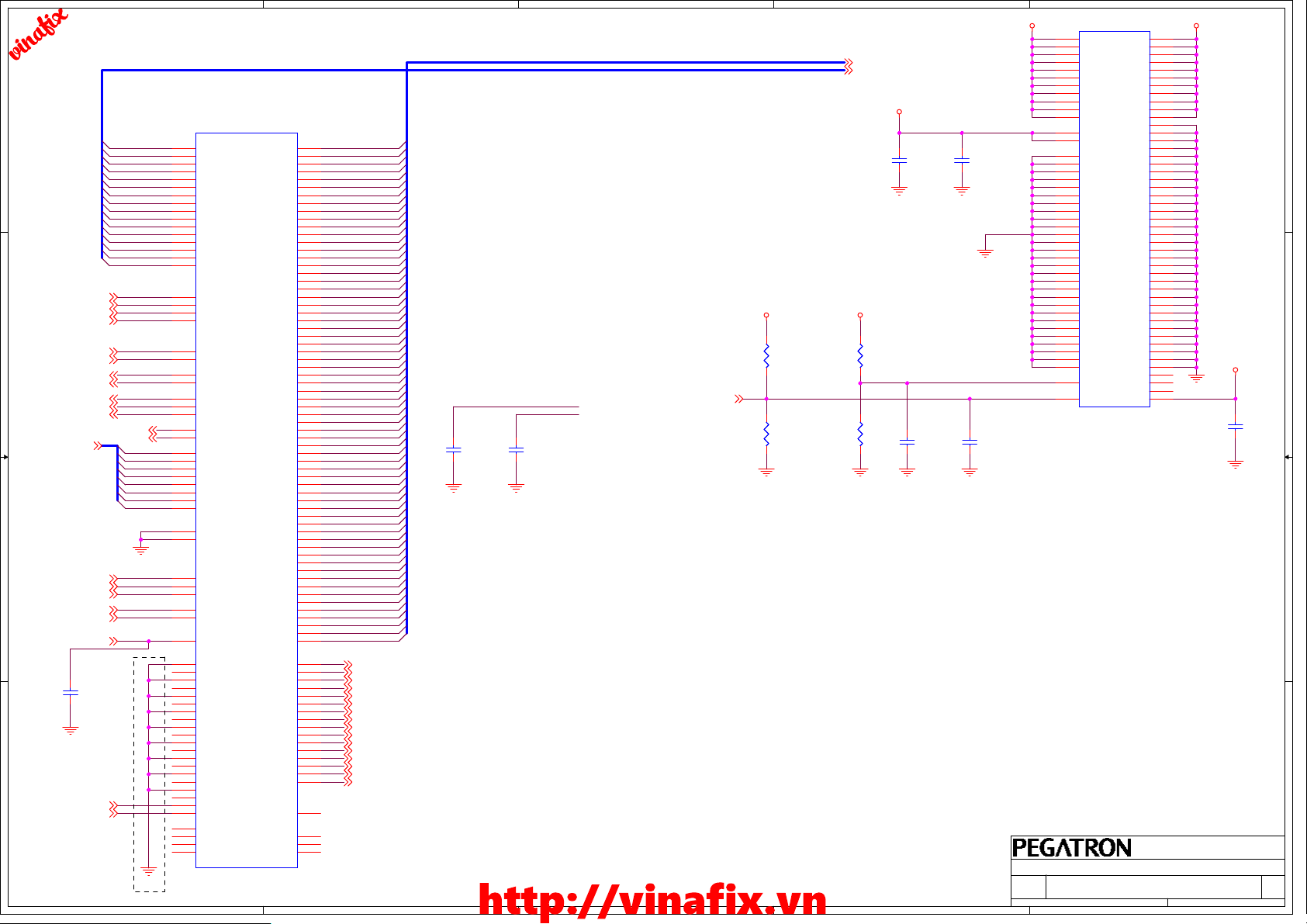

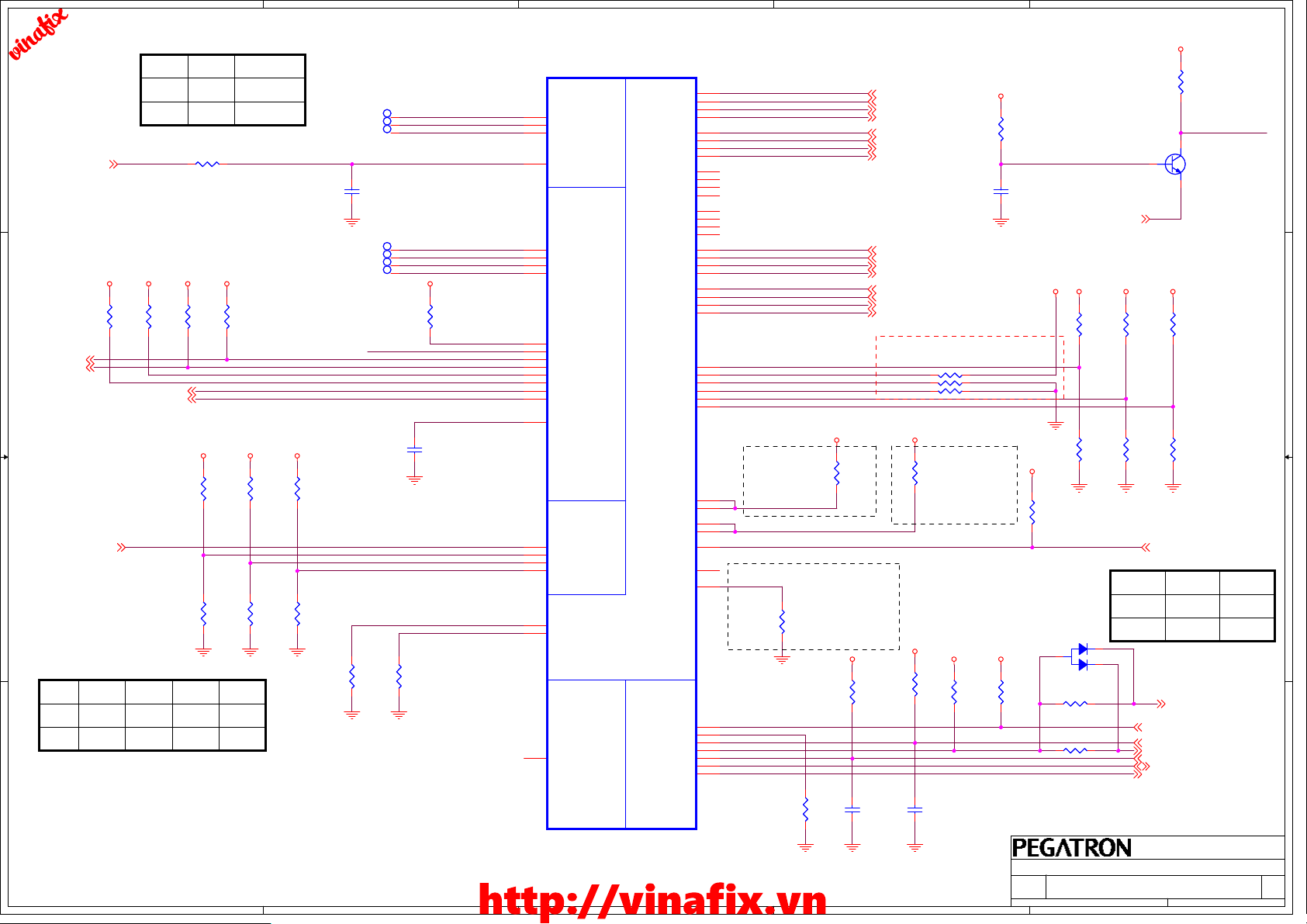

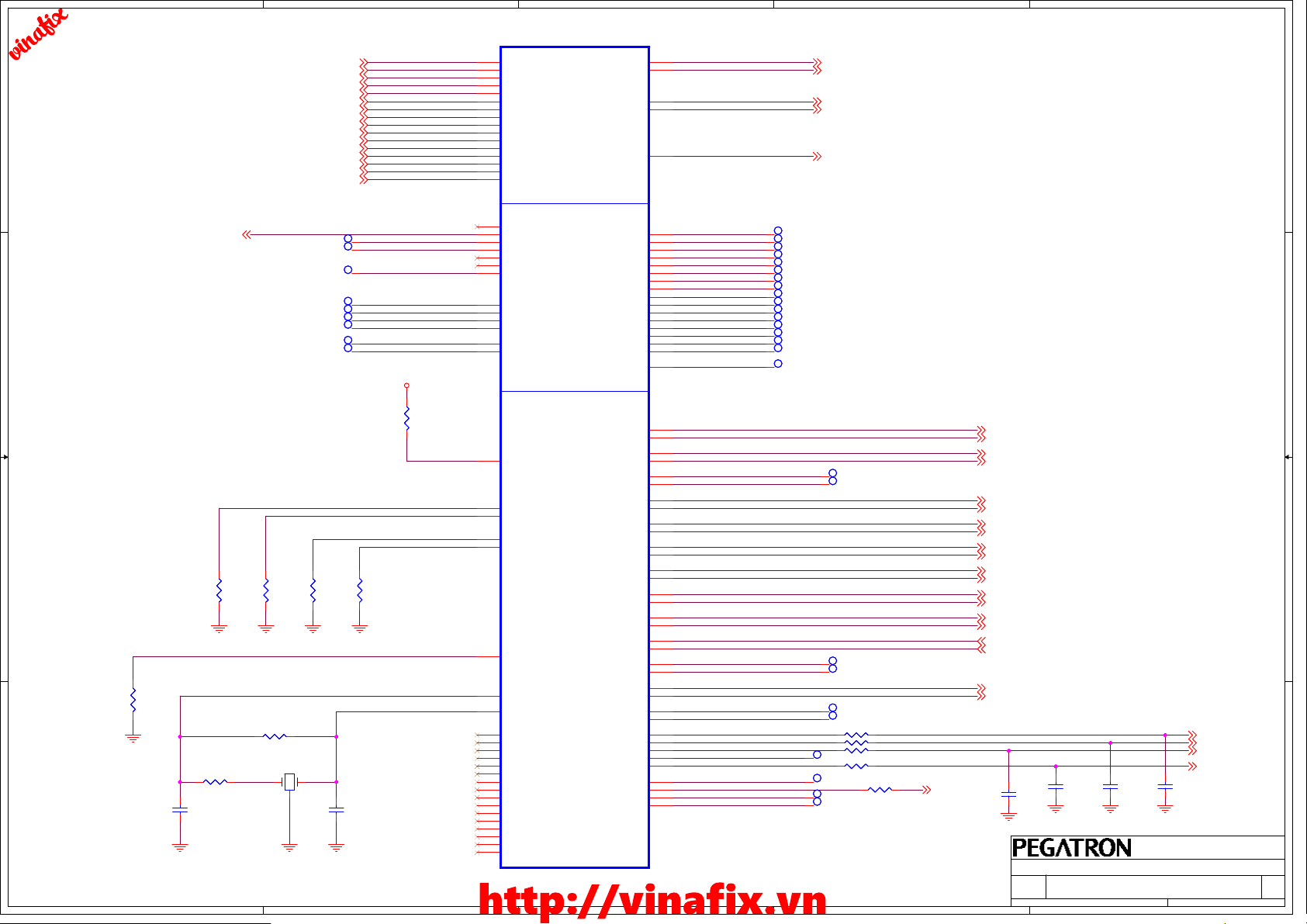

BLOCK DIAGRAM

CHANGE HISTORY - 1

CHANGE HISTORY - 2

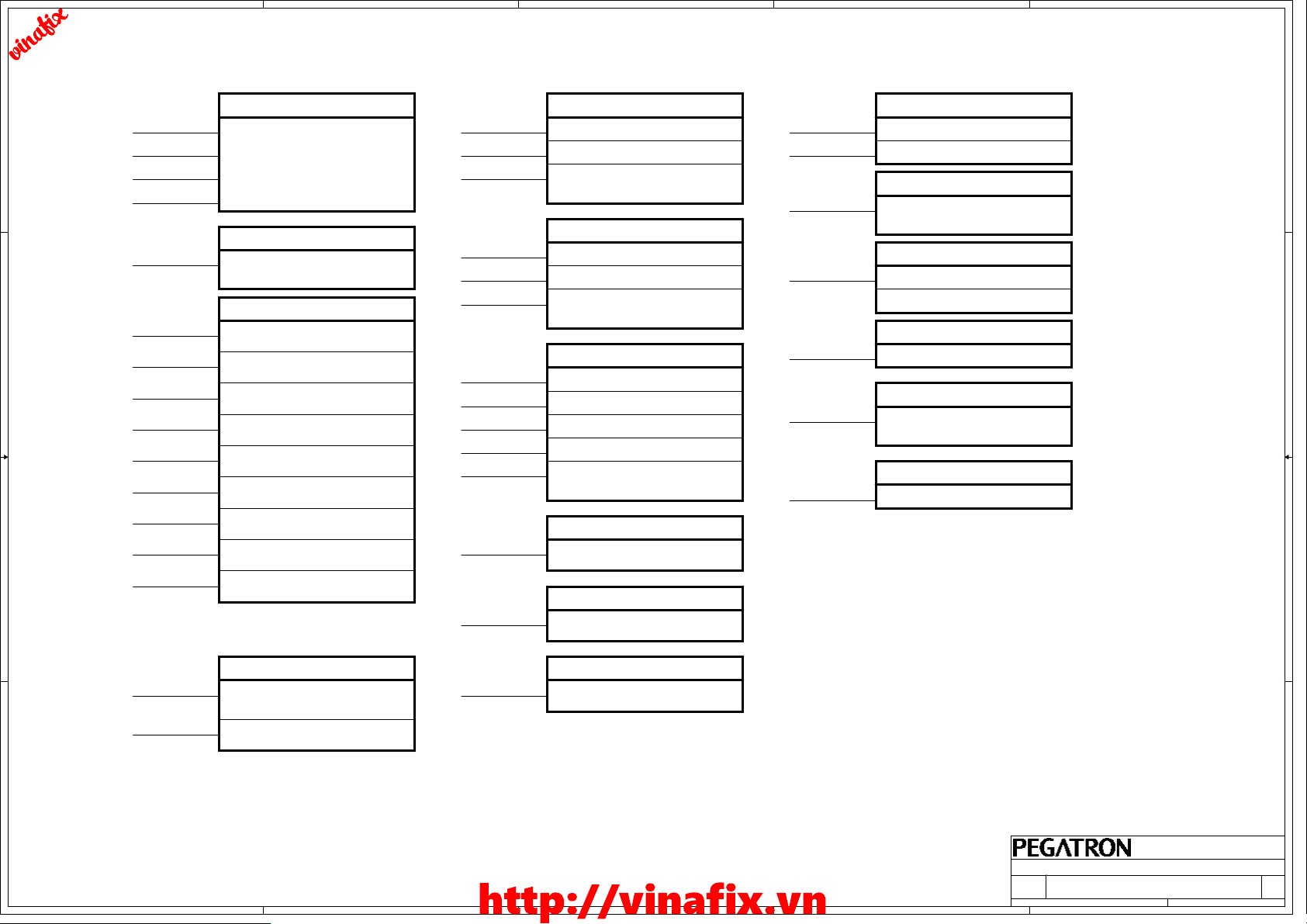

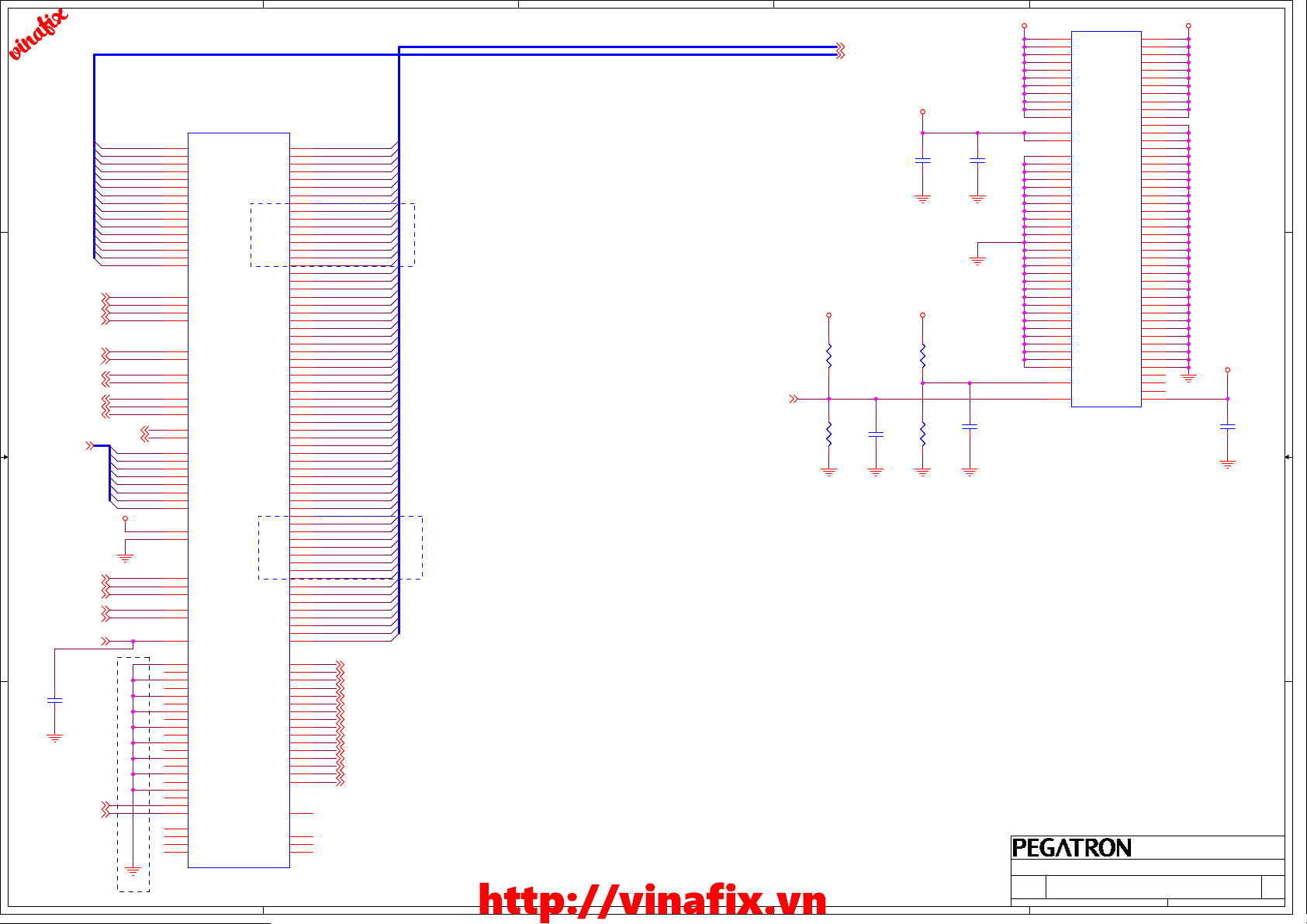

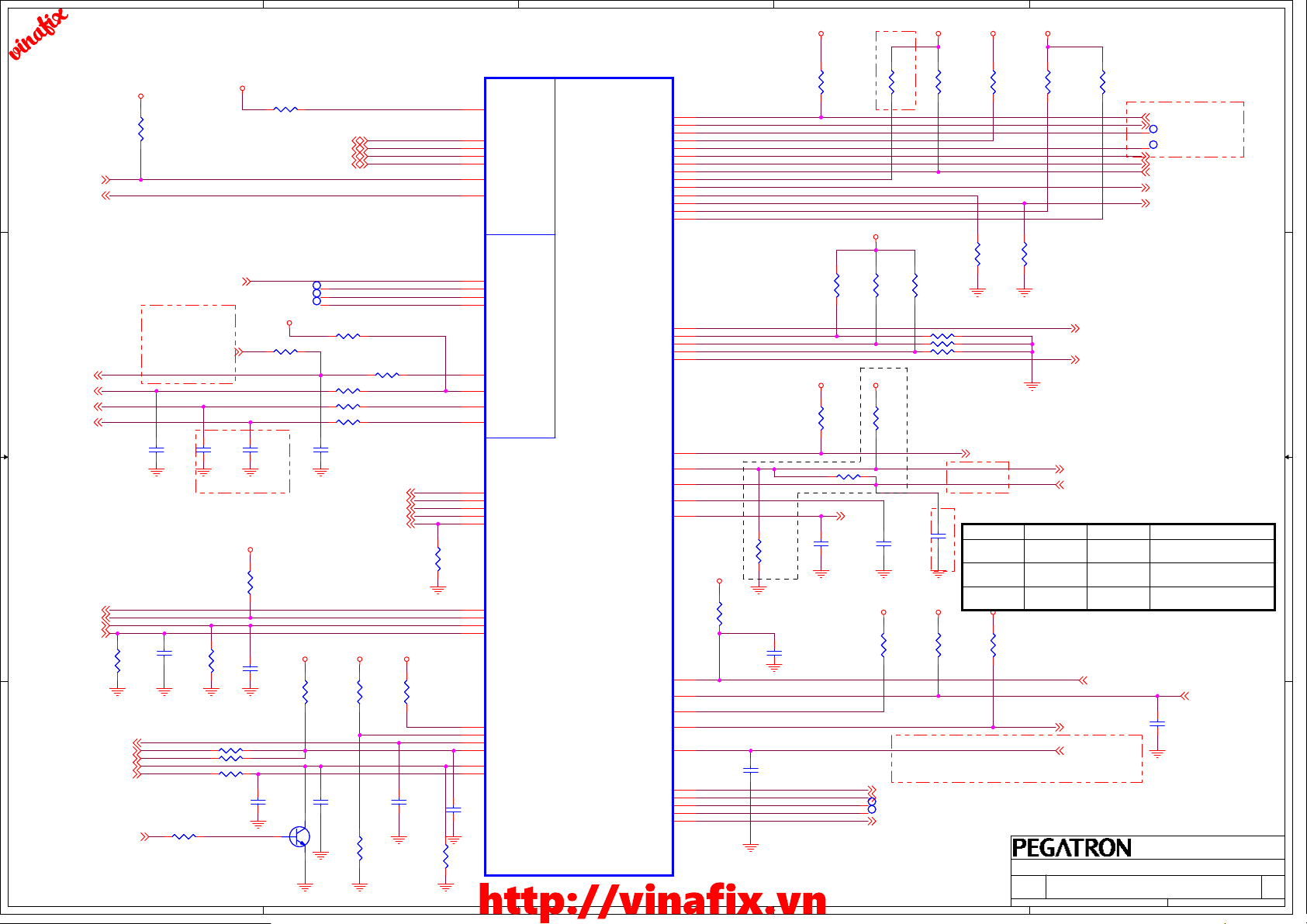

CLOCKS DISTRIBUTION

SIGNAL & RESET MAP

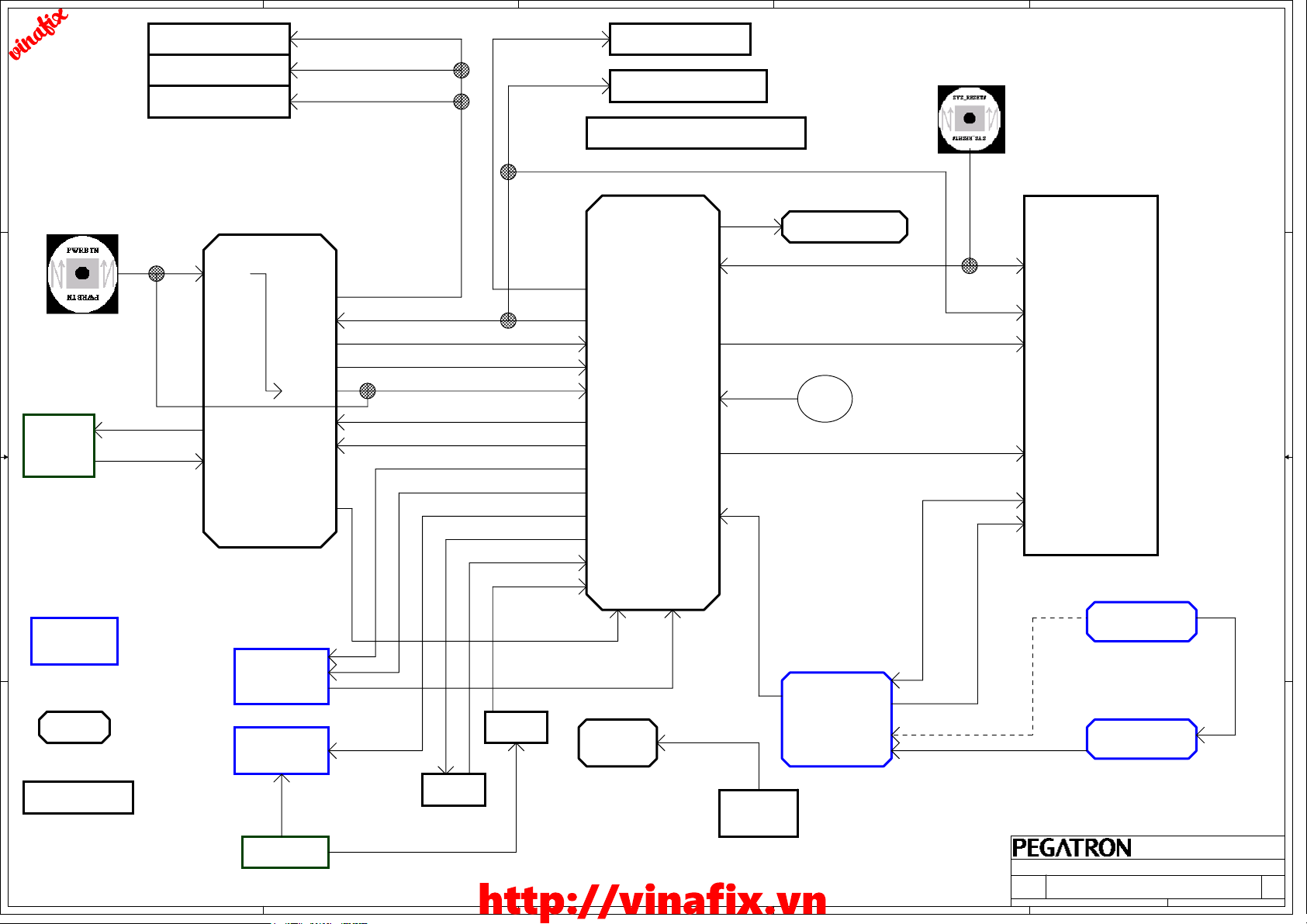

POWER FLOW

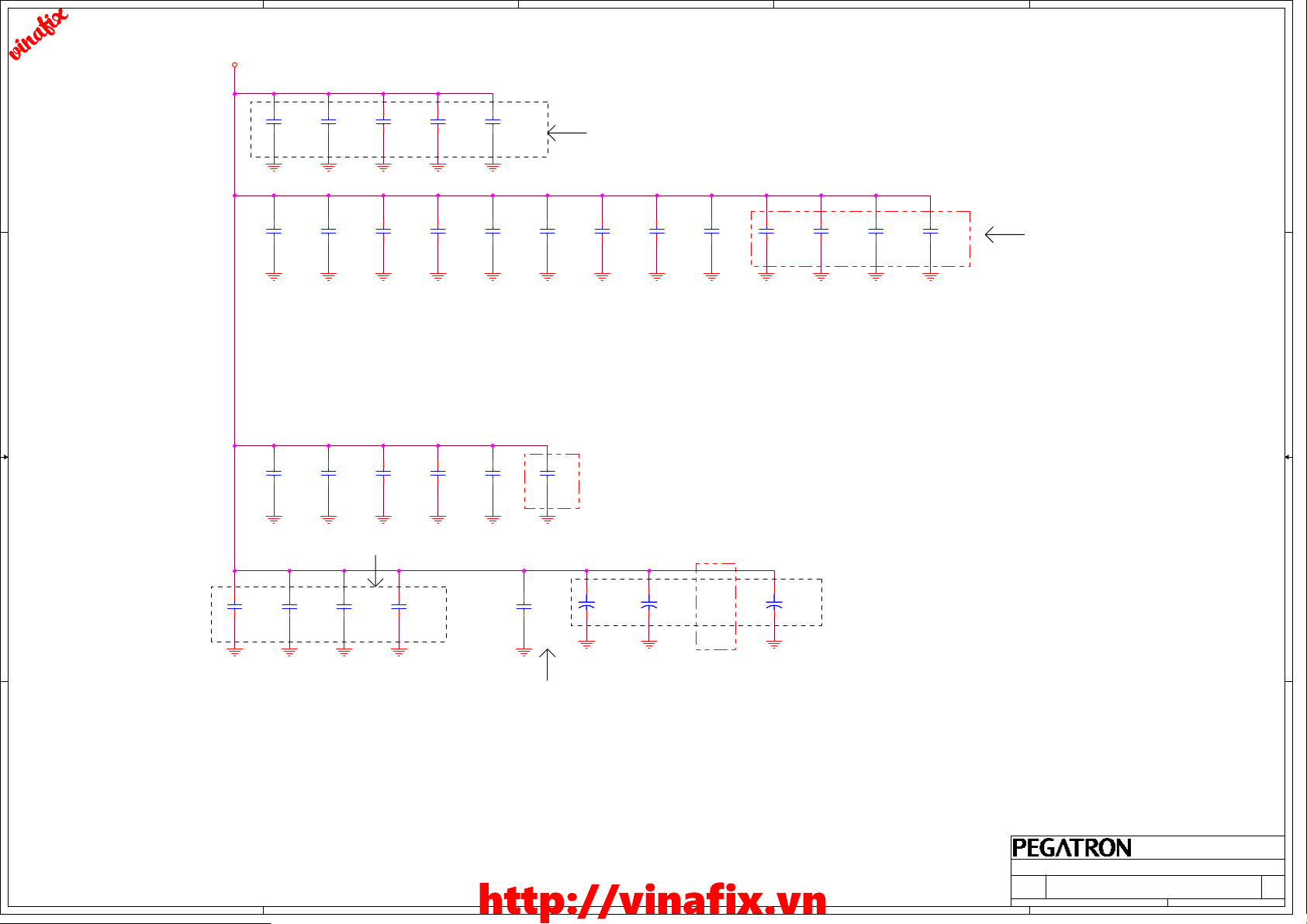

POWER DISTRIBUTION

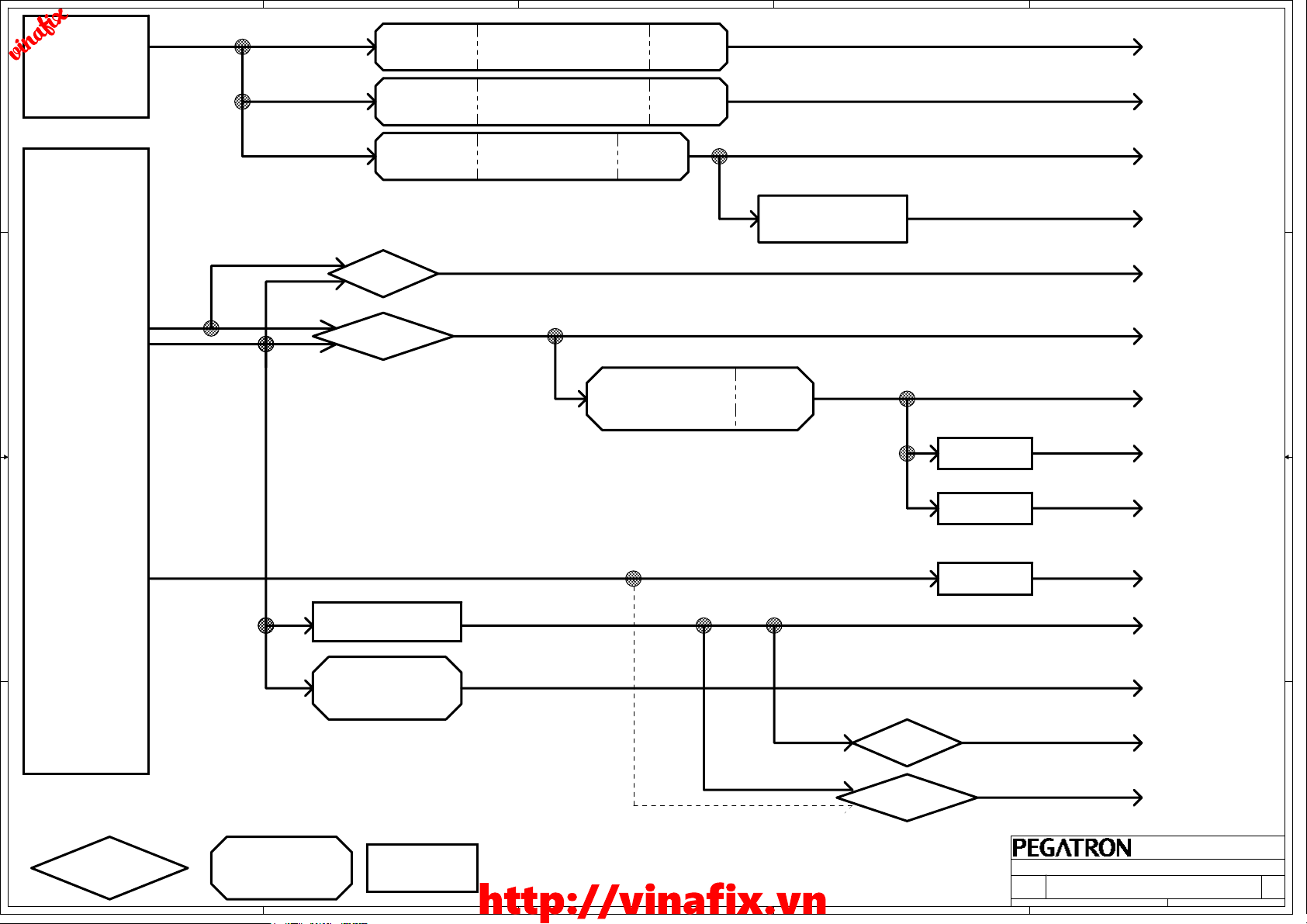

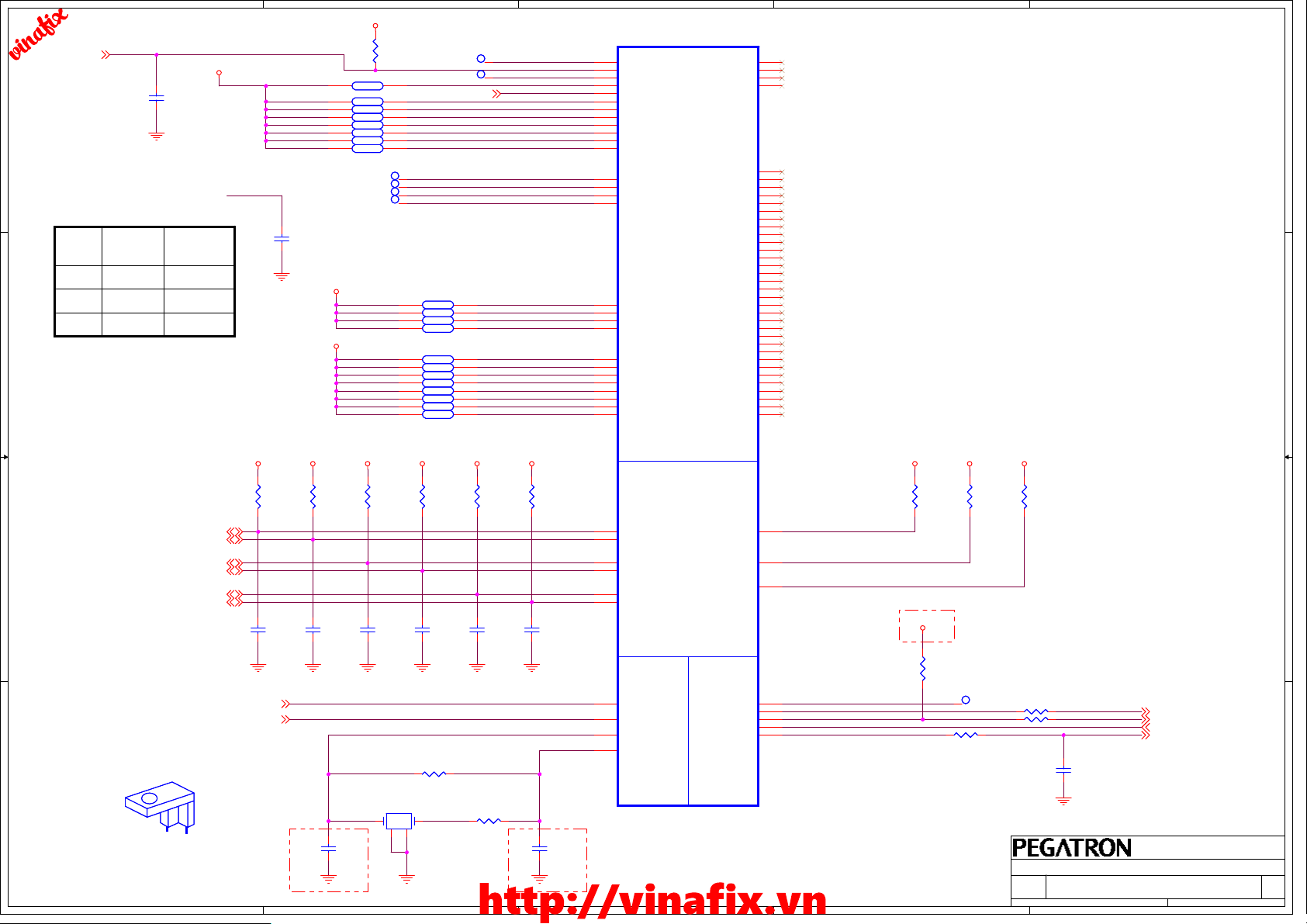

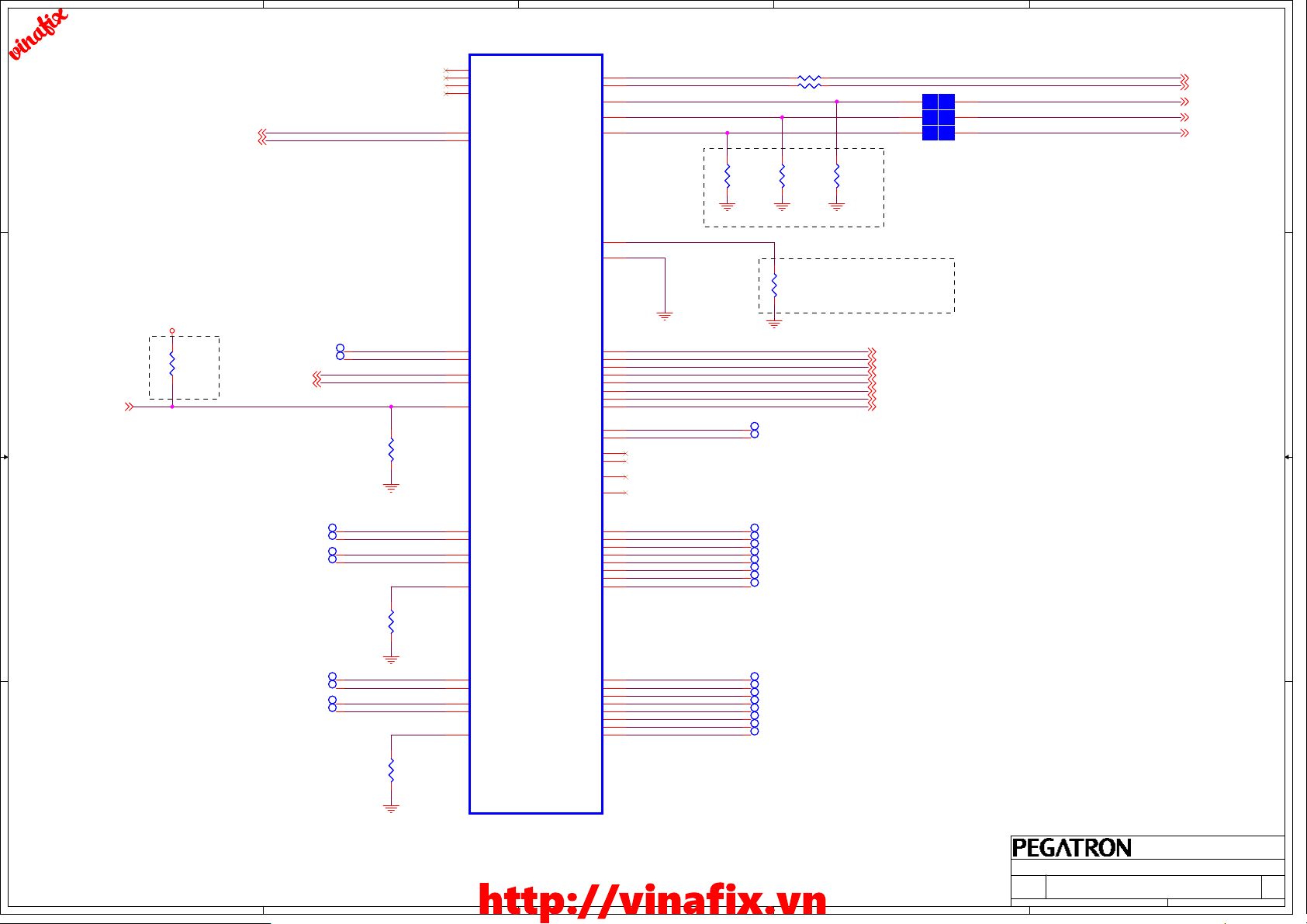

POWER SEQUENCE

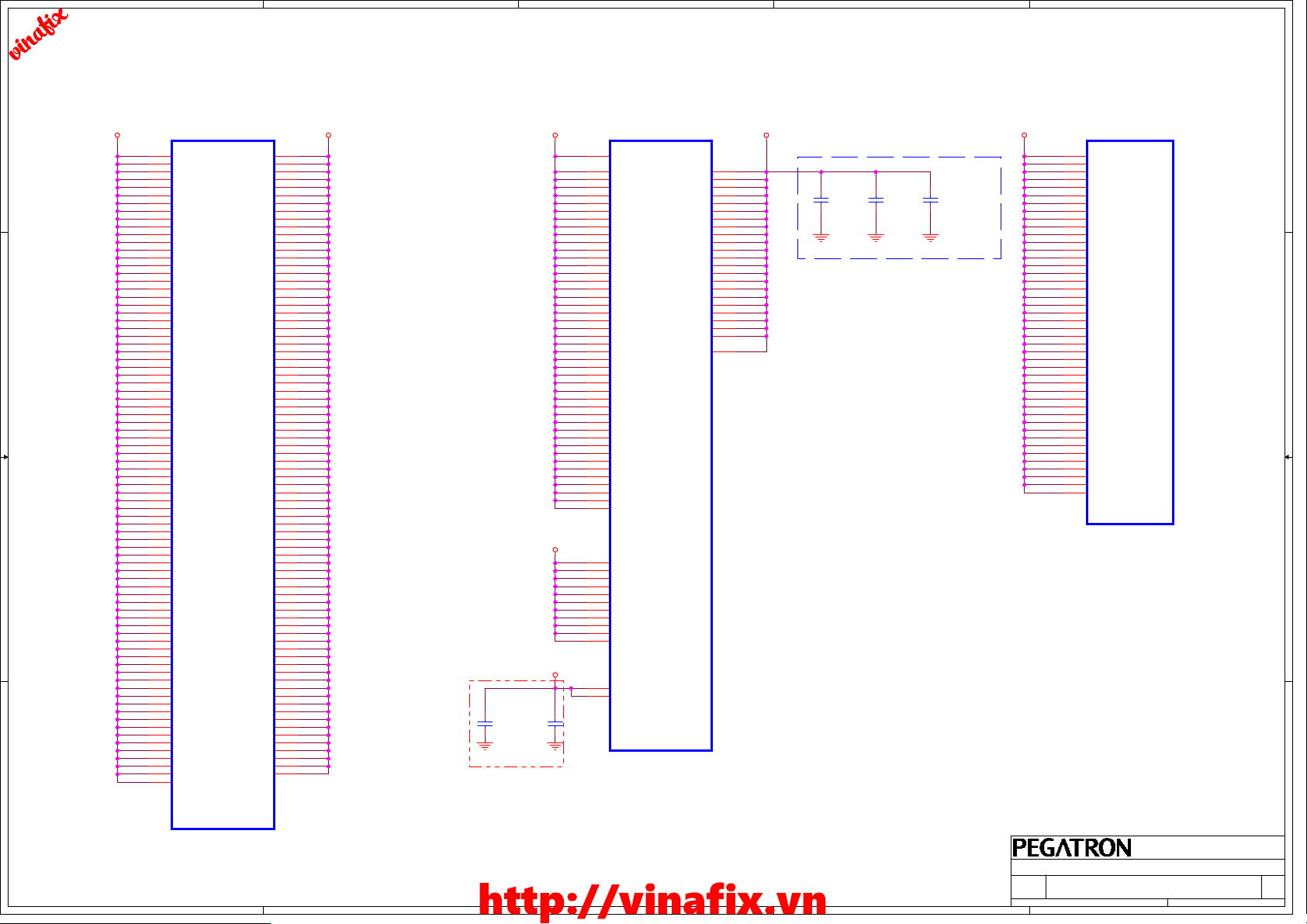

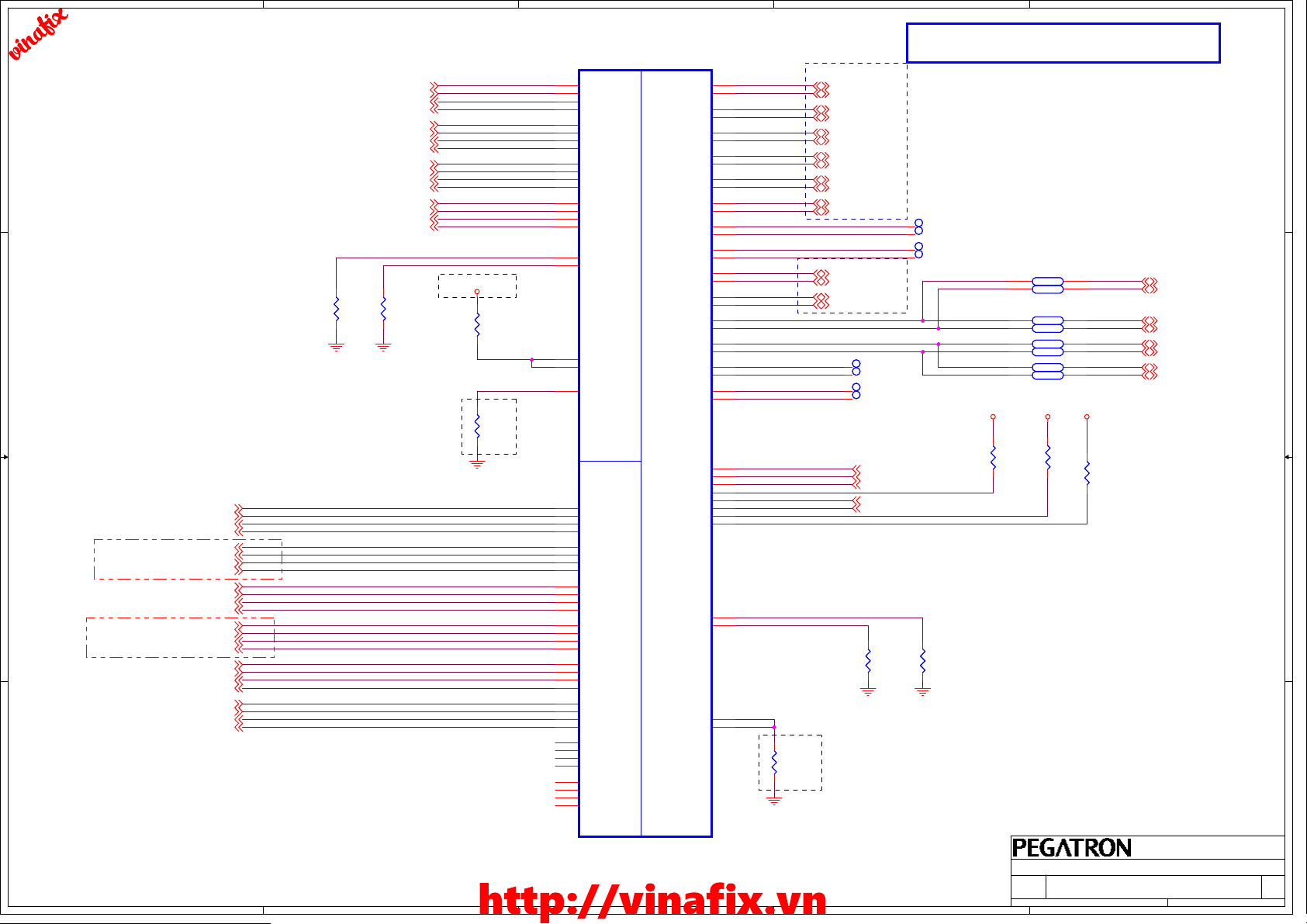

INTEL CPU_SOCKET1155(1~6)

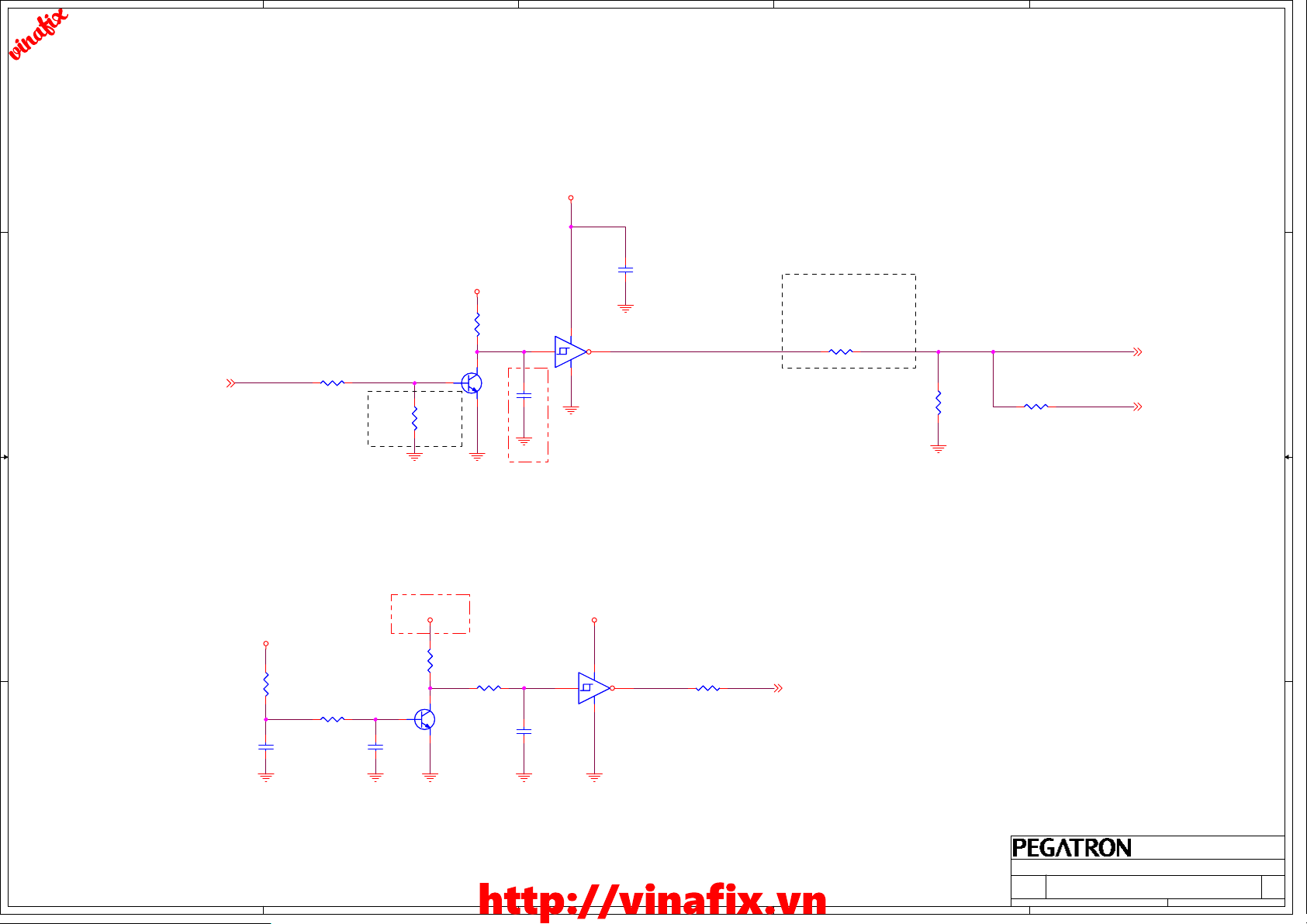

PLTRST_CPU# & RSMRST#

DDR3 & TERMINATION

PCH_DPWROK & SUS_ACK#

*********

VGA CONNECTOR

DVI-D CONNECTOR

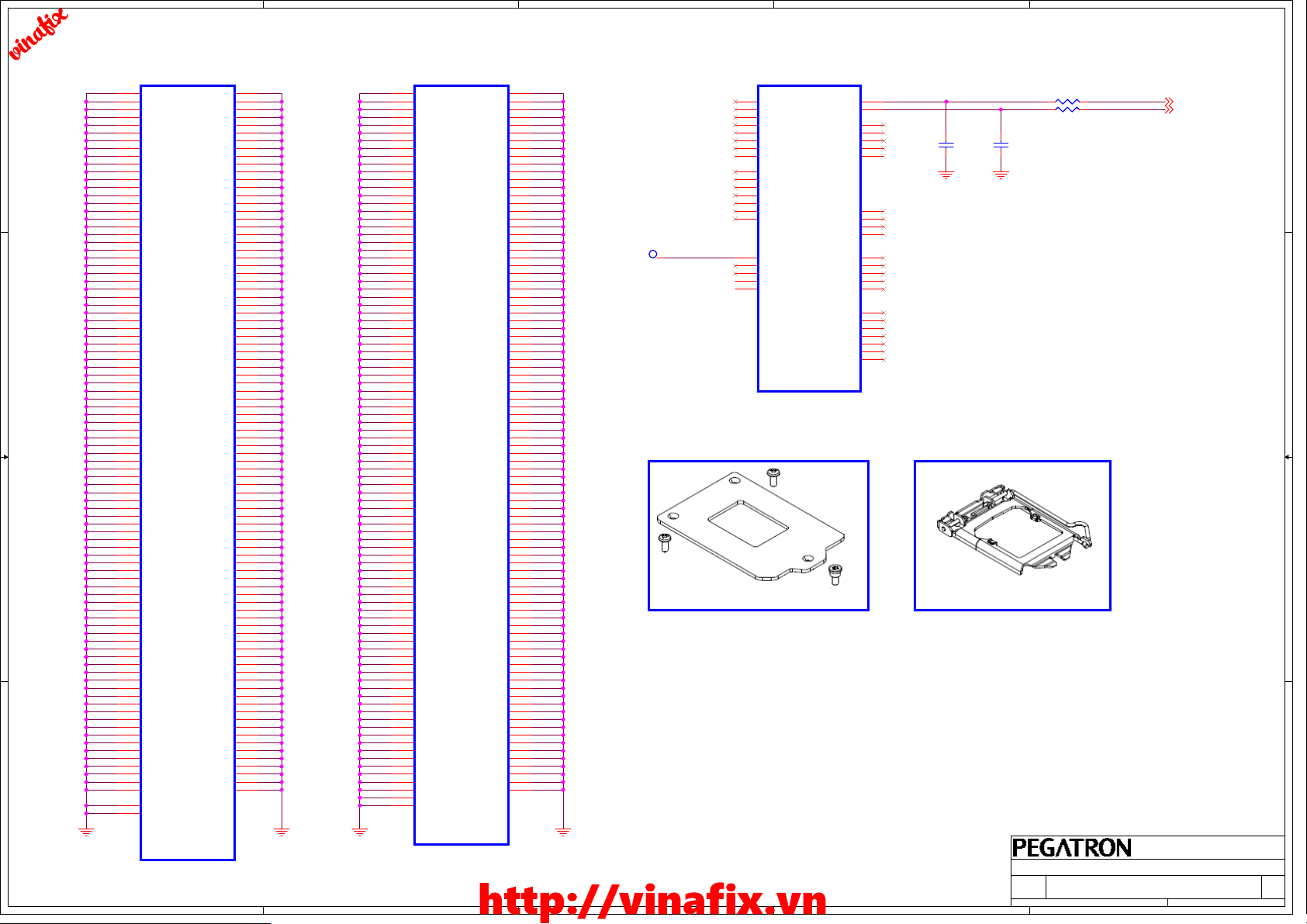

PCI EXPRESS X16 SLOT

PCI SLOT

PCI EXPRESS X1 SLOT x2

INTEL 82579 LAN CONTROLLER

RJ45+USB2.0 CONNECTOR

PRINT PORT

SERIAL PORT

USB 3.0 CONTROLLER

USB 3.0 POWER

REALTEK ALC892 AUDIO CIRCUIT

PCI-E to PCI Bridge

USB HEADER

TITLE

4

PCI-E X16 SLOT

High-Speed USB

10 PORTS

Intel 82579

10/100/1000

PCI-E X1 SLOT

PCI-E X1 SLOT

PCI-E to PCI Bridge

XDP

3

100MHz

PCI-E BUS

480Mb/s

PCIE BUS

100MHz

PCIE BUS

PCIE BUS

PCIE BUS

Intel Processor

Sandy Bridge

LGA-1155 H2 Socket

FDI LINK

DMI

INTEL

Cougar Point

PCH

942 Pin

27mm X 27mm

2

TMDS

RGB

PCI-e x1

PCI-e x1

SATA BUS

SPI

Azalia

Channel A

Channel B

Dual-Channel Memory x 2 Slots

DDR3 1066/1333

DDR3 1066/1333

8GB MAX

DVI-D

VGA

SATA 3.0

USB 3.0

SATA 2.0SATA 2.0

SATA 2.0SATA 2.0

SPI FLASH

AUDIO CODEC

ALC892

32Mb

1

50 SATA CONN

51

B B

52~53

54

55

56~57

58

59

60

61

62

63

64

65

66

67

68

A A

69

70

71~72

73~75

76

77 PS2 + USB CONN

SATA 3.0 CONTROLLER

SUPER I/O -WINBOND W83677

SMBUS CONTROL

TPM

FAN circuit

FRONT PANEL CIRCUIT

SPI ROM

ATX POWER_24P CONNECTOR

+3VA & +3VSB & +5VSB

+1P5V_DUAL

+VTT_DDR & +1P5V_DUAL_EN

+1P8V FOR SATA3.0 CONTROLLER

VSA_OV_Function

+0P925V_SA & +1P05V_PCH

5V DUAL POWER

+1P8V_SFR

+1V_USB3 & VRM_EN

+3P3V_LAN & +3P3V_ME

+1P05V_CPUIO

VCORE CONTROLLER + DRIVER

+V_AXG DRIVER

5

LPC BUS

33MHz

PCI SLOT

LPT

SIO

WINBOND W83677

78

79

80

81

82

83

4

EMI CAP

RTC/LED/SPKR/SCREW

BIOS and LPC header

Heceta Fan Control

CPU XDP DEBUG CONNECTOR

PCH XDP DEBUG CONNECTOR

http://vinafix.vn

3

2

FAN

COM

PEGATRON DT-MB RESTRICTED SECRET

BLOCK DIAGRAM

BLOCK DIAGRAM

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

BLOCK DIAGRAM

1

Livy_Zhu

Livy_Zhu

Livy_Zhu

183Friday, September 24, 2010

183Friday, September 24, 2010

183Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

Page 2

5

Schematics Change History

vinafix

Version

D D

C C

Date

4

3

2

1

Comments

B B

A A

CAD Note:

Default component footprint is SMD 0402, Y5V, 5% type. Difference footprint show on schematics.

Property: BOM

I = Installed Part.

NI = Not Installed Part.

5

PROTO = PROTO Phase Only.

VP = Virtual Part.

4

http://vinafix.vn

3

2

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

CHANGE HISTORY-1

CHANGE HISTORY-1

CHANGE HISTORY-1

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Engineer:

Livy_Zhu

Livy_Zhu

Livy_Zhu

283Friday, September 24, 2010

283Friday, September 24, 2010

283Friday, September 24, 2010

of

1

of

Rev

Rev

Rev

1.00

1.00

1.00

Page 3

5

4

3

2

1

Schematics Change History

vinafix

Version

D D

C C

Date

Comments

B B

A A

CAD Note:

Default component footprint is SMD 0402, Y5V, 5% type. Difference footprint show on schematics.

Property: BOM

I = Installed Part.

NI = Not Installed Part.

5

PROTO = PROTO Phase Only.

VP = Virtual Part.

4

http://vinafix.vn

3

2

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

CHANGE HISTORY-2

CHANGE HISTORY-2

CHANGE HISTORY-2

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Engineer:

Livy_Zhu

Livy_Zhu

Livy_Zhu

383Friday, September 24, 2010

383Friday, September 24, 2010

383Friday, September 24, 2010

of

1

of

Rev

Rev

Rev

1.00

1.00

1.00

Page 4

5

4

3

2

1

vinafix

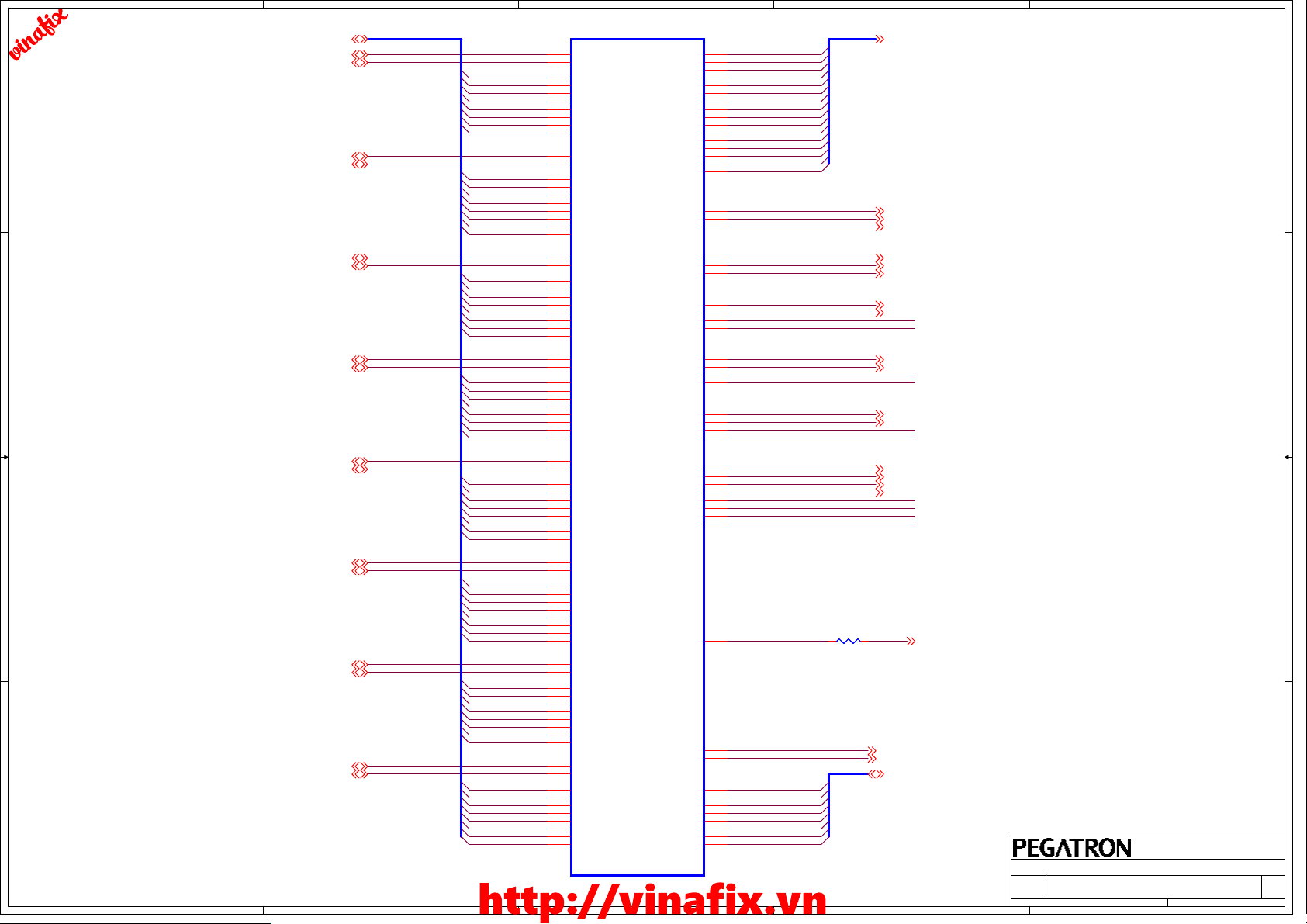

M_CHA_CLK[0..3]/#

D D

XMM3 / XMM4

C C

CK_100M_DMI2/#_CK505

CK_133M_BCLK_CK505/#

CK505

CK_100M_DMI_CK505/#

M_CHB_CLK[0..3]/#

XMM1 / XMM2

Intel Processor

Sandy Bridge

LGA-1155 Pin Socket

RSVD_001/002

BCLK/#_0

Intel

Platform Controller Hub

Cougar Point

942 Pin

CLKIN_GND1_P/N

CLKIN_GND0_P/N

CLKIN_DMI_P/N

CPU XDP

CK_100M_DMI/#

CK_100M_CPUXDP/#

100 MHz

CK_100M_PCHXDP/#

100 MHz

CK_100M_PE16/#

100 MHz

CK_100M_PE1/#

100 MHz

CK_100M_LAN/#

100 MHz

CK_100M_CPU_XDP/#_CK505

PCH XDP

PCIEx1 Slot

Intel 82579

PCIEx16 Slot

25 MHz

PCH Buffer Through Mode for Pre-Silicon

CK_100M_SATA_CK505/#

SLG8SP424VTR

ICS9LRS4180A/B

B B

CK_96M_DOT_CK505/#

CK_14M_REF_CK505

NOTE:

Reserved PD resistors for FCIM

CLKIN_SATA_P/N

CLKIN_DOT_96_P/N

REFCLK14IN

32 Pin

CK_33M_TPM

33 MHz

CK_48M_SIO

48 MHz

CK_33M_SIO

33 MHz

CK_33M_SL1

33 MHz

CK_33M_PCIFB

TPM Header

W83677

PCI Slot

CK_48M_SIO_CK505

48 MHz

CKKIN_PCILOOPBACK

HDA_BCLK

AZ_BITCLK

24 MHz

14.318MHz

A A

XTAL25_IN RTCX

SPI_CLK

SPI_CLK

33 MHz

32.768KHz25MHz

5

4

http://vinafix.vn

3

AUDIO CODEC

ALC892

SPI ROM

2

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

CLCOK DISTRIBUTION

CLCOK DISTRIBUTION

CLCOK DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Engineer:

Livy_Zhu

Livy_Zhu

Livy_Zhu

483Friday, September 24, 2010

483Friday, September 24, 2010

483Friday, September 24, 2010

of

1

of

Rev

Rev

Rev

1.00

1.00

1.00

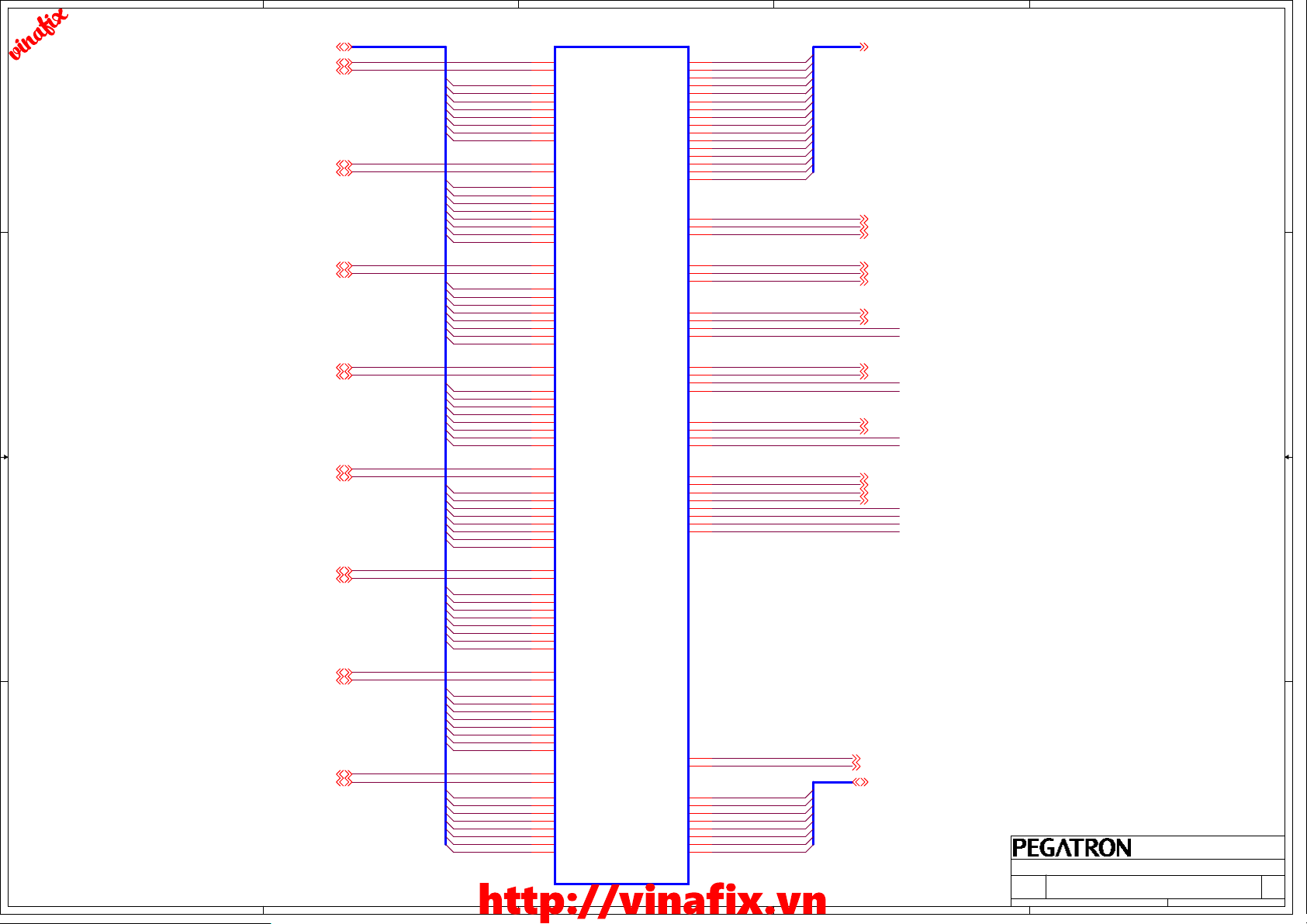

Page 5

vinafix

5

PCI_Express x 16

PCI_Express x 4

PCI_Express x 1

<28>PCIE_RST#

PWRGD

<28>PCIE_RST#

PWRGD

<28>PCIE_RST#

4

<29>PCH_PCIRST#

<27>PLTRST#

3

RST#

PCI SLOT #1

PE_RSTN

LAN 82579

2

1

Intel AMT 7.0 and non-DSW supported

RESET_SWITCH

PWRGD

D D

USB3.0

PERSTB

<27.1>PLTRST_CPU#

PCH PROCESSOR

POWER_SWITCH

<4>PWRBTN#

C C

2X12 ATX PSU

<15>PSON#

PSON#

PWROK

B B

<21>ATX_PWRGD

W83677

PWSIN#

PS_ON#

ATXPG_IN

PCIRST3#

PCIRST2#

PCIRST1#

LRESET#

KBRST# RCIN#

RSMRST#

PWSOUT# PWRBTN#

S3# SLP_S3#

S4#

<27>PLTRST#

RST_KB#

<9>RSMRST#

<4>SB_PWRBTN#

<13>SLP_S3#

<12>SLP_S4#

<11>SLP_A#

<10>SLP_LAN#

PWROK

<7>SLP_SUS#

<5>SUS_WARN#

<6>SUS_ACK#

<3>PCH_DPWROK

PCIRST#

PLTRST#

RSMRST#

SLP_S4#

SLP_A#

SLP_LAN#

SLP_SUS#

SUS_WARN#

SUS_ACK#

DPWROK

PWROK

ME & LAN POWER

<22>PWROK

HDA_RST#

DRAMPWROK

RTCRST#

PROCPWRGD

SYS_PWROK

APWROK

+1P05V_ME

ONBOARD POWER

+3P3V_LAN

<14>APWROK

+3P3V_ME

STANDBY POWER

<8>

+5VSB

CHIP

A A

+3P3VSB

MB Logic

<2>+5VA

MB Logic

CK505

CKPWRGD/PD#

<22>CK505_PWRGD

AZ_RST#

<1>RTCRST#

RESET#

CPU SVID buffers are Hi-Z once +1P05V_CPUIO is

stable and UNCOREPWRGOOD = 0

<26>VRM_PWRGD

Vcore Controller

VR_RDY

MB Logic

SOCKET or SLOT

2X12 ATX PSU

5

<2>+5VA

4

http://vinafix.vn

3

AUDIO

ALC8889

SYS_RESET#

<23>DRAM_PWROK

BATTERY

<24>CPUPWRGD

VDIO/VCLK

VCORE

EN

RT8859AGQW

<20~24>SVIDs

<25>VCORE

<16>+1P05V_CPUIO

<19>+1P05V_CPUIO

2

DBR#SYS_RESET#

RESET#

SM_DRAMPWROK

UNCOREPWRGOOD

VIDSOUT/VIDSCLK

VCORE

<16>

+1P05V_CPUIO

<17>1P05V_CPUIO_PWRGD

PWRGD

NCP5380MNTXG

<18>

+0P925V_SA

EN

LM358

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

SIGNAL&RESET MAP

SIGNAL&RESET MAP

SIGNAL&RESET MAP

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Engineer:

Livy_Zhu

Livy_Zhu

Livy_Zhu

583Friday, September 24, 2010

583Friday, September 24, 2010

583Friday, September 24, 2010

of

1

of

Rev

Rev

Rev

1.00

1.00

1.00

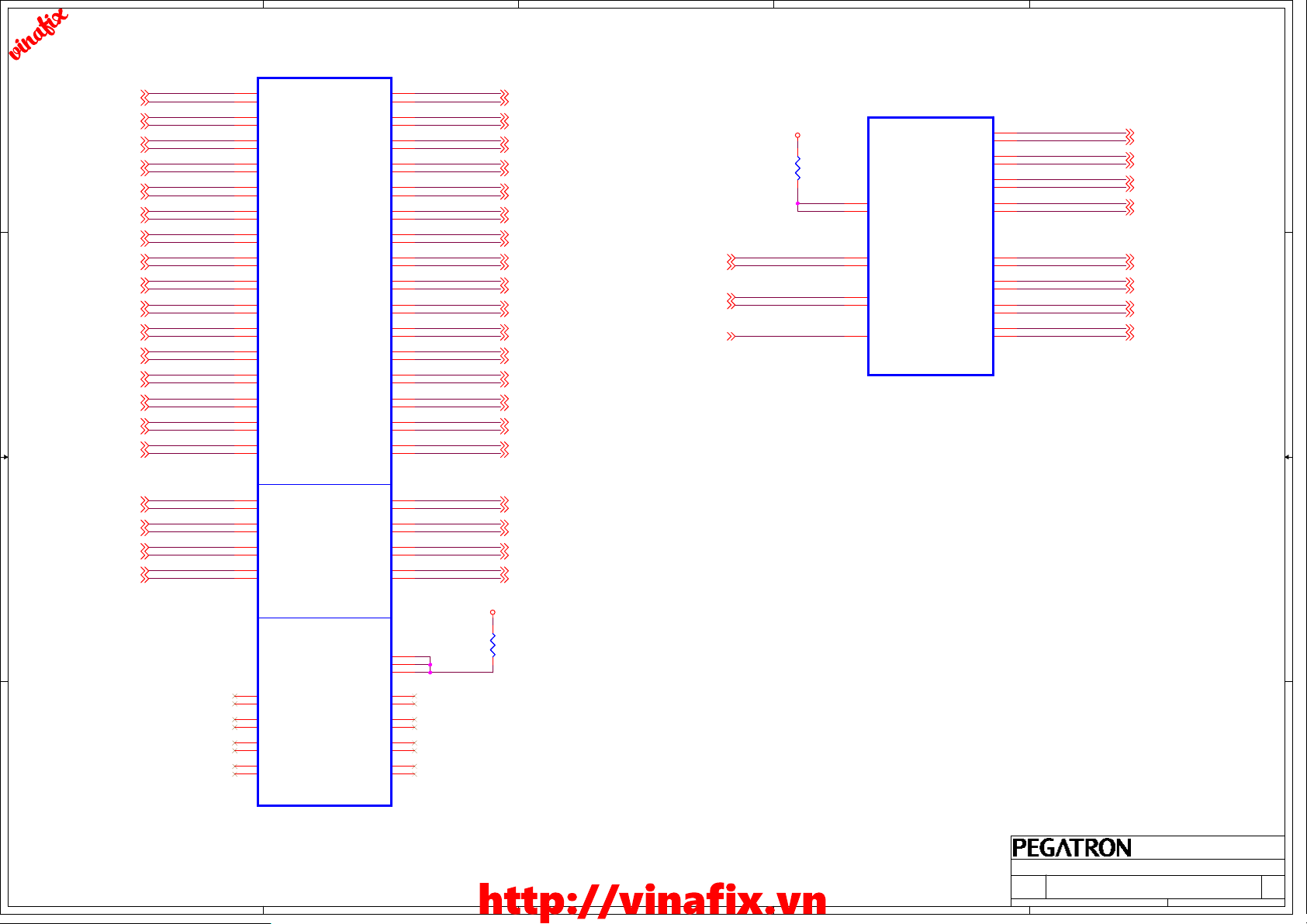

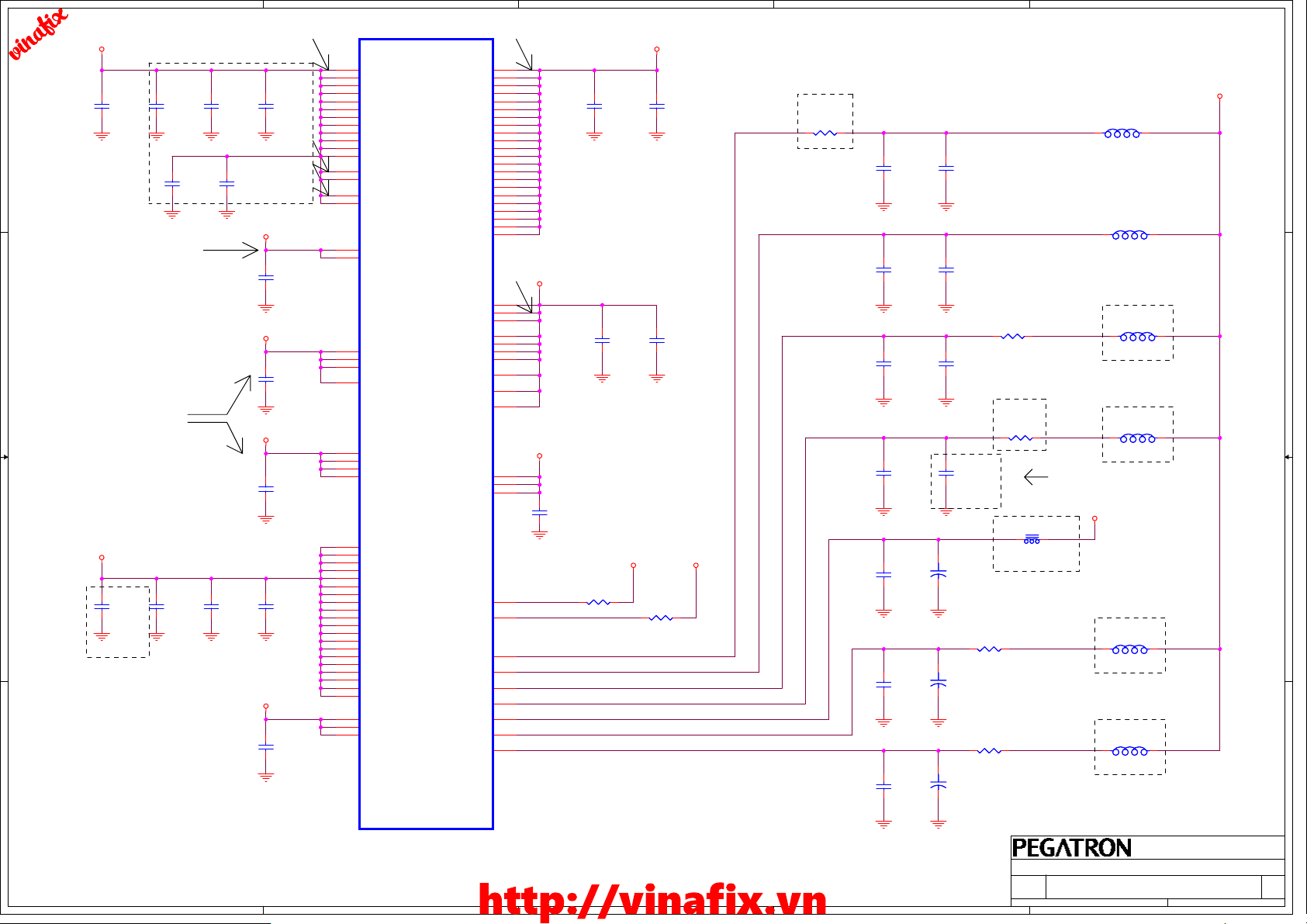

Page 6

5

4

3

2

1

vinafix

+12V_CPU

+

L/S * 6

H/S * 1

+

H/S * 3

D D

L/S * 2

H/S * 2

+

L/S * 2

HIGH SIDE: NTMFS4839NHT1G

LOW SIDE: IPS06N03LAG

HIGH SIDE: NTMFS4839NHT1G

LOW SIDE: IPS06N03LAG

HIGH SIDE: FDU8780_F071

LOW SIDE: IPS06N03LAG

Imax = 17A

eff = TBD%

Imax = ?A

eff = TBD%

TDP = 95W

Imax = 35A

eff = TBD%

LM358 Linear Regulator

0.925V / 0.85V

APM9932CKC

+5V

C C

+5VA

AOD472 (S0,S1)

FDN340P_NL (S3)

RT8204AGQW

HIGH SIDE: AOD452

LOW SIDE: IPDH6N03LAG

Iocp = TBD A

Imax = TBD A

eff = TBD %

RT9045GSP

+VCORE

Idc(TDC) = 85A

+V_AXG

Idc(TDC) = 25A

+1P05V_CPUIO

Imax = 17A

+0P925V_SA

Imax = 8.8A

+5V_DUAL_USB_B/F

Idc = 7A

(S0, S1, S3)

+5V_DUAL

Idc = TBD A

(S0, S1, S3)

+1P5V_DUAL

Imax = 28.5A

(S0, S1, S3)

VTT_DDR

Idc = 1A

(S0, S1)

+1P05V_PCH

LM358

B B

+3P3V

LM358

LIN REG, 1085

RT8015APQW

Imax = 6.2A

+1P8V_SFR

Imax = 1.6A

+3P3VSB

Idc = TBD A

+1P05V_ME

Imax = 1.8A

+12V

+3P3V_ME

FDN340P_NL

A A

Switch ON/OFF

5

LinearSwitching

4

Note: Ixx/Ioo

means

Itdc/Imax

http://vinafix.vn

3

AOD452

FDN340P_NL

2

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

Date: Sheet of

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Idc = 0.016A

+3P3V_LAN

Idc = 0.218A

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

POWER FLOW

POWER FLOW

POWER FLOW

Livy_Zhu

Livy_Zhu

Livy_Zhu

683Friday, September 24, 2010

683Friday, September 24, 2010

683Friday, September 24, 2010

of

of

Rev

Rev

Rev

1.00

1.00

1.00

Page 7

vinafix

5

4

3

2

1

D D

+VCORE

+1P05V_CPUIO

+0P925V_SA

+V_AXG

-> 95A(TDC) - 95W

-> 17A(Imax) - W

-> 8.8A(Imax) - W

-> 25A(TDC) - W

+12V

+3P3V

+3P3VSB

CPU Sandy Bridge

PCI Express x 1

-> 5A - 60W

-> 3.0A - 9.9W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

+3P3V

+1P05V_USB

+5V_DUAL_B/F

FL1009 USB3.0

-> mA - W

-> mA - W

USB 14 PORTS

(S0, S1) -> 7A - 35W

+3P3V

CLOCK GEN

-> 125mA - W

+12V

+3P3V

+3P3VSB

PCH

+1P05V_PCH

C C

+1P05V_CPUIO

+1P8V_SFR

+3P3V

+3P3VSB

-> 5.831A - W

-> 0.043A - W

-> 0.16A - W

-> 0.267A - W

-> 0.107A - W

+12V

-12V

+5V

+3P3V

+3P3VSB

+1P05V_ME

-> 1.01A - W

PCI Express x 16

-> 5.5A - 66W

-> 3.0A - 9.9W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

PCI SLOTS

-> 0.5A - 6W

-> 0.1A - 1.2W

-> 5.0A - 25W

-> 7.6A - 25.08W

WAKE -> 0.375A - 1.24W

No WAKE-> 20mA - 66mW

+5V

+12V

+5V_DUAL

+3P3V_ME

DVI

-> mA - mW

-> mA - mW

FANS

-> 1.2A - 14.4W

PS2 KB/MS

(S0, S1) -> 0.345A - 1.73W

(S3) -> 2mA - 10mW

SPI

-> 30mA - 99mW

+3P3V_ME

-> 0.02A - W

+3P3VA

B B

+BATT

-> 0.002A - W

RTC(G3) -> 6uA - 0.0198mW

+3P3V_LAN

+3P3V

-> mA - 720mW

-> 35mA - mW

INTEL 82579

83677

DDR2 DIMM (4) & Termination

+1P5V_DAUL

+3P3V

VDD (S0, S1,S3) ->7.5 A - 11.25W

+VTT_DDR(0.75V)

A A

5

SM VTT (S0, S1) -> 1A - 0.75W

4

http://vinafix.vn

-> mA - mW

ALC892

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

POWER DISTRIBUTION

POWER DISTRIBUTION

POWER DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

3

2

Date: Sheet of

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Engineer:

Livy_Zhu

Livy_Zhu

Livy_Zhu

783Friday, September 24, 2010

783Friday, September 24, 2010

1

783Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

of

of

Page 8

5

4

3

2

1

S5 to S0 Power Sequence

vinafix

SLP_SUS#

DSW exit

+5VSB / +3P3VSB

D D

RSMRST#

SUSWARN#

SUSACK#

SLP_LAN#

SLP_A#

+1P05V_ME

SLP_S5#

30uS

SLP_S4#

SLP_S3#

30uS

APWROK

C C

PSU: <=20mS

+12V / +5V

+3P3V

+1P5V_DUAL

=500mS

+1P05V_CPUIO

+1P8V_SFR

=50mS

VCCSA_VID

UNCOREPWRGOOD must be stable (low) at this time

+0P925V_SA

VCORE EN

B B

VIDSCLK / VIDSOUT

VIDALERT#

CPU SVID buffers are Hi-Z once VCCIO is

stable and Uncorepowergood = 0

CPU SVID buffers are Hi-Z once VCCIO is

stable and Uncorepowergood = 0

UNCOREPWRGOOD assertion

VCCSA_VID[0] FINAL

Recommended that +0P925V_SA ramp after +1P05V_CPUIO has ramped to ensure VCCSA_VID[0] is stable

<5mS

Typ 60uS

MISC ACK0/1...

Set VID

slow packet status packet

ACK0/1...

Get Reg

ACK0/1...

<600uS

<1uS

Pay

load

+0P925V_SA FINAL

>400uS

PSU: 100ms~500ms

ATX_PWRGD

BCLK / PCIE CLOCKS

DRAM_PWROK

>1mS

CPUPWRGD

+VCORE

VRM_PWRGD

A A

PLTRST#

5

4

http://vinafix.vn

1mS

Min 10 PCIe BCLKs

<5uS

<2mS

5mS

<5mS

1~100mS

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet

3

2

Date: Sheet of

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Engineer:

Livy_Zhu

Livy_Zhu

Livy_Zhu

883Friday, September 24, 2010

883Friday, September 24, 2010

1

883Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

of

of

Page 9

5

M_CHA_DQ[0..63]16

vinafix

D D

C C

B B

A A

5

M_CHA_DQS016

M_CHA_DQS0#16

M_CHA_DQS116

M_CHA_DQS1#16

M_CHA_DQS216

M_CHA_DQS2#16

M_CHA_DQS316

M_CHA_DQS3#16

M_CHA_DQS416

M_CHA_DQS4#16

M_CHA_DQS516

M_CHA_DQS5#16

M_CHA_DQS616

M_CHA_DQS6#16

M_CHA_DQS716

M_CHA_DQS7#16

4

I

I

HU1A

HU1A

M_CHA_DQS0

M_CHA_DQS0#

M_CHA_DQ0

M_CHA_DQ1

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ4

M_CHA_DQ5

M_CHA_DQ6

M_CHA_DQ7

M_CHA_DQS1

M_CHA_DQS1#

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ12

M_CHA_DQ13

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQS2

M_CHA_DQS2#

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ18

M_CHA_DQ19

M_CHA_DQ20

M_CHA_DQ21

M_CHA_DQ22

M_CHA_DQ23

M_CHA_DQS3

M_CHA_DQS3#

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQS4

M_CHA_DQS4#

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQS5

M_CHA_DQS5#

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ42

M_CHA_DQ43

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ47

M_CHA_DQS6

M_CHA_DQS6#

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ50

M_CHA_DQ51

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQS7

M_CHA_DQS7#

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ58

M_CHA_DQ59

M_CHA_DQ60

M_CHA_DQ61

M_CHA_DQ62

M_CHA_DQ63

4

http://vinafix.vn

AK3

AK2

AP3

AP2

AN1

AN4

AR3

AR4

AN2

AN3

AR2

AR1

AW4

AV4

AV2

AW3

AV5

AW5

AU2

AU3

AU5

AY5

AV8

AW8

AY7

AU7

AV9

AU9

AV7

AW7

AW9

AY9

AV37

AV36

AU35

AW37

AU39

AU36

AW35

AY36

AU38

AU37

AP38

AP39

AR40

AR37

AN38

AN37

AR39

AR38

AN39

AN40

AK38

AK39

AL40

AL37

AJ38

AJ37

AL39

AL38

AJ39

AJ40

AF38

AF39

AG40

AG37

AE38

AE37

AG39

AG38

AE39

AE40

AJ3

AJ4

AL3

AL4

AJ2

AJ1

AL2

AL1

SA_DQS_0

SA_DQS#_0

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQS_1

SA_DQS#_1

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQS_2

SA_DQS#_2

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQS_3

SA_DQS#_3

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQS_4

SA_DQS#_4

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQS_5

SA_DQS#_5

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQS_6

SA_DQS#_6

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQS_7

SA_DQS#_7

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SOCKET_1155P

SOCKET_1155P

3

SM_DRAMRST#

SA_ECC_CB_0

SA_ECC_CB_1

SA_ECC_CB_2

SA_ECC_CB_3

SA_ECC_CB_4

SA_ECC_CB_5

SA_ECC_CB_6

SA_ECC_CB_7

DDR3_A

DDR3_A

3

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS#_0

SA_CS#_1

SA_CS#_2

SA_CS#_3

SA_CKE_0

SA_CKE_1

SA_CKE_2

SA_CKE_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_CK_0

SA_CK#_0

SA_CK_1

SA_CK#_1

SA_CK_2

SA_CK#_2

SA_CK_3

SA_CK#_3

SA_DQS_8

SA_DQS#_8

AV27

AY24

AW24

AW23

AV23

AT24

AT23

AU22

AV22

AT22

AV28

AU21

AT21

AW32

AU20

AT20

AW29

AV30

AU28

AY29

AW28

AV20

AU29

AV32

AW30

AU33

AV19

AT19

AU18

AV18

AV31

AU32

AU30

AW33

AY25

AW25

AU24

AU25

AW27

AY27

AV26

AW26

AW18

AV13

AV12

AU12

AU14

AW13

AY13

AU13

AU11

AY12

AW12

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

M_CHA_MAA14

M_CHA_MAA15

TP_HU1_AW30

TP_HU1_AU33

TP_HU1_AU18

TP_HU1_AV18

TP_HU1_AU30

TP_HU1_AW33

R_DDR3_DRAMRST#

MA_ECC_CB0

MA_ECC_CB1

MA_ECC_CB2

MA_ECC_CB3

MA_ECC_CB4

MA_ECC_CB5

MA_ECC_CB6

MA_ECC_CB7

TP_HU1_AW27

TP_HU1_AY27

TP_HU1_AV26

TP_HU1_AW26

I

I

SR283

SR283

1 2

0

0

2

M_CHA_MAA[0..15] 16

M_CHA_WE# 16

M_CHA_CAS# 16

M_CHA_RAS# 16

M_CHA_BA0 16

M_CHA_BA1 16

M_CHA_BA2 16

M_CHA_CS#0 16

M_CHA_CS#1 16

M_CHA_CKE0 16

M_CHA_CKE1 16

M_CHA_ODT0 16

M_CHA_ODT1 16

M_CHA_CLK0 16

M_CHA_CLK0# 16

M_CHA_CLK1 16

M_CHA_CLK1# 16

DDR3_DRAMRST# 16,17

M_CHA_DQS8 16

M_CHA_DQS8# 16

MA_ECC_CB[0..7] 16

NOTE:

For ECC DIMM

2

1

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

1

DDR3_A 1-6

DDR3_A 1-6

DDR3_A 1-6

Livy_Zhu

Livy_Zhu

Livy_Zhu

983Friday, September 24, 2010

983Friday, September 24, 2010

983Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

Page 10

5

vinafix

D D

C C

B B

A A

5

M_CHB_DQ[0..63]17

M_CHB_DQS017

M_CHB_DQS0#17

M_CHB_DQS117

M_CHB_DQS1#17

M_CHB_DQS217

M_CHB_DQS2#17

M_CHB_DQS317

M_CHB_DQS3#17

M_CHB_DQS417

M_CHB_DQS4#17

M_CHB_DQS517

M_CHB_DQS5#17

M_CHB_DQS617

M_CHB_DQS6#17

M_CHB_DQS717

M_CHB_DQS7#17

4

I

I

HU1B

HU1B

M_CHB_DQS0

M_CHB_DQS0#

M_CHB_DQ0

M_CHB_DQ1

M_CHB_DQ2

M_CHB_DQ3

M_CHB_DQ4

M_CHB_DQ5

M_CHB_DQ6

M_CHB_DQ7

M_CHB_DQS1

M_CHB_DQS1#

M_CHB_DQ8

M_CHB_DQ9

M_CHB_DQ10

M_CHB_DQ11

M_CHB_DQ12

M_CHB_DQ13

M_CHB_DQ14

M_CHB_DQ15

M_CHB_DQS2

M_CHB_DQS2#

M_CHB_DQ16

M_CHB_DQ17

M_CHB_DQ18

M_CHB_DQ19

M_CHB_DQ20

M_CHB_DQ21

M_CHB_DQ22

M_CHB_DQ23

M_CHB_DQS3

M_CHB_DQS3#

M_CHB_DQ24

M_CHB_DQ25

M_CHB_DQ26

M_CHB_DQ27

M_CHB_DQ28

M_CHB_DQ29

M_CHB_DQ30

M_CHB_DQ31

M_CHB_DQS4

M_CHB_DQS4#

M_CHB_DQ32

M_CHB_DQ33

M_CHB_DQ34

M_CHB_DQ35

M_CHB_DQ36

M_CHB_DQ37

M_CHB_DQ38

M_CHB_DQ39

M_CHB_DQS5

M_CHB_DQS5#

M_CHB_DQ40

M_CHB_DQ41

M_CHB_DQ42

M_CHB_DQ43

M_CHB_DQ44

M_CHB_DQ45

M_CHB_DQ46

M_CHB_DQ47

M_CHB_DQS6

M_CHB_DQS6#

M_CHB_DQ48

M_CHB_DQ49

M_CHB_DQ50

M_CHB_DQ51

M_CHB_DQ52

M_CHB_DQ53

M_CHB_DQ54

M_CHB_DQ55

M_CHB_DQS7

M_CHB_DQS7#

M_CHB_DQ56

M_CHB_DQ57

M_CHB_DQ58

M_CHB_DQ59

M_CHB_DQ60

M_CHB_DQ61

M_CHB_DQ62

M_CHB_DQ63

4

http://vinafix.vn

AH7

AH6

AG7

AG8

AG5

AG6

AM8

AM7

AM10

AL10

AM6

AM9

AR8

AP8

AP7

AR7

AP10

AR10

AP6

AR6

AP9

AR9

AN13

AN12

AM12

AM13

AR13

AP13

AL12

AL13

AR12

AP12

AN29

AN28

AR28

AR29

AL28

AL29

AP28

AP29

AM28

AM29

AP33

AR33

AP32

AP31

AP35

AP34

AR32

AR31

AR35

AR34

AL33

AM33

AM32

AM31

AL35

AL32

AM34

AL31

AM35

AL34

AG35

AG34

AH35

AH34

AE34

AE35

AJ35

AJ34

AF33

AF35

AJ9

AJ8

AJ6

AJ7

AL8

AL7

AL6

AL9

SB_DQS_0

SB_DQS#_0

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQS_1

SB_DQS#_1

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQS_2

SB_DQS#_2

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQS_3

SB_DQS#_3

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQS_4

SB_DQS#_4

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQS_5

SB_DQS#_5

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQS_6

SB_DQS#_6

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQS_7

SB_DQS#_7

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

DDR3_B

DDR3_B

SOCKET_1155P

SOCKET_1155P

3

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SA_CK[2]

SA_CK[1]

SA_ODT[2]

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS#_0

SB_CS#_1

SB_CS#_2

SB_CS#_3

SB_CKE_0

SB_CKE_1

SB_CKE_2

SB_CKE_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK_0

SB_CK#_0

SB_CK_1

SB_CK#_1

SB_CK_2

SB_CK#_2

SB_CK_3

SB_CK#_3

SB_DQS_8

SB_DQS#_8

SB_ECC_CB_0

SB_ECC_CB_1

SB_ECC_CB_2

SB_ECC_CB_3

SB_ECC_CB_4

SB_ECC_CB_5

SB_ECC_CB_6

SB_ECC_CB_7

3

AK24

AM20

AM19

AK18

AP19

AP18

AM18

AL18

AN18

AY17

AN23

AU17

AT18

AR26

AY16

AV16

AR25

AK25

AP24

AP23

AM24

AW17

AN25

AN26

AL25

AT26

AU16

AY15

AW15

AV15

AL26

AP26

AM26

AK26

AL21

AL22

AL20

AK20

AL23

AM22

AP21

AN21

AN16

AN15

AL16

AM16

AP16

AR16

AL15

AM15

AR15

AP15

M_CHB_MAA0

M_CHB_MAA1

M_CHB_MAA2

M_CHB_MAA3

M_CHB_MAA4

M_CHB_MAA5

M_CHB_MAA6

M_CHB_MAA7

M_CHB_MAA8

M_CHB_MAA9

M_CHB_MAA10

M_CHB_MAA11

M_CHB_MAA12

M_CHB_MAA13

M_CHB_MAA14

M_CHB_MAA15

MB_ECC_CB0

MB_ECC_CB1

MB_ECC_CB2

MB_ECC_CB3

MB_ECC_CB4

MB_ECC_CB5

MB_ECC_CB6

MB_ECC_CB7

TP_HU1_AL25

TP_HU1_AT26

TP_HU1_AW15

TP_HU1_AV15

TP_HU1_AM26

TP_HU1_AK26

TP_HU1_AL23

TP_HU1_AM22

TP_HU1_AP21

TP_HU1_AN21

2

M_CHB_MAA[0..15] 17

M_CHB_WE# 17

M_CHB_CAS# 17

M_CHB_RAS# 17

M_CHB_BA0 17

M_CHB_BA1 17

M_CHB_BA2 17

M_CHB_CS#0 17

M_CHB_CS#1 17

M_CHB_CKE0 17

M_CHB_CKE1 17

M_CHB_ODT0 17

M_CHB_ODT1 17

M_CHB_CLK0 17

M_CHB_CLK0# 17

M_CHB_CLK1 17

M_CHB_CLK1# 17

M_CHB_DQS8 17

M_CHB_DQS8# 17

MB_ECC_CB[0..7] 17

NOTE:

For ECC DIMM

2

1

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

1

DDR3_B 2-6

DDR3_B 2-6

DDR3_B 2-6

Livy_Zhu

Livy_Zhu

Livy_Zhu

10 83Friday, September 24, 2010

10 83Friday, September 24, 2010

10 83Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

Page 11

5

4

3

2

1

vinafix

EXP_RXP032

EXP_RXN032

D D

C C

B B

EXP_RXP132

EXP_RXN132

EXP_RXP232

EXP_RXN232

EXP_RXP332

EXP_RXN332

EXP_RXP432

EXP_RXN432

EXP_RXP532

EXP_RXN532

EXP_RXP632

EXP_RXN632

EXP_RXP732

EXP_RXN732

EXP_RXP832

EXP_RXN832

EXP_RXP932

EXP_RXN932

EXP_RXP1032

EXP_RXN1032

EXP_RXP1132

EXP_RXN1132

EXP_RXP1232

EXP_RXN1232

EXP_RXP1332

EXP_RXN1332

EXP_RXP1432

EXP_RXN1432

EXP_RXP1532

EXP_RXN1532

DMI_RXP020

DMI_RXN020

DMI_RXP120

DMI_RXN120

DMI_RXP220

DMI_RXN220

DMI_RXP320

DMI_RXN320

B11

B12

D12

D11

C10

E10

AA4

AA5

C9

E9

B8

B7

C6

C5

A5

A6

E2

E1

F4

F3

G2

G1

H3

H4

J1

J2

K3

K4

L1

L2

M3

M4

N1

N2

W5

W4

V3

V4

Y3

Y4

I

I

HU1C

HU1C

PEG_RX_0

PEG_RX#_0

PEG_RX_1

PEG_RX#_1

PEG_RX_2

PEG_RX#_2

PEG_RX_3

PEG_RX#_3

PEG_RX_4

PEG_RX#_4

PEG_RX_5

PEG_RX#_5

PEG_RX_6

PEG_RX#_6

PEG_RX_7

PEG_RX#_7

PEG_RX_8

PEG_RX#_8

PEG_RX_9

PEG_RX#_9

PEG_RX_10

PEG_RX#_10

PEG_RX_11

PEG_RX#_11

PEG_RX_12

PEG_RX#_12

PEG_RX_13

PEG_RX#_13

PEG_RX_14

PEG_RX#_14

PEG_RX_15

PEG_RX#_15

DMI_RX_0

DMI_RX#_0

DMI_RX_1

DMI_RX#_1

DMI_RX_2

DMI_RX#_2

DMI_RX_3

DMI_RX#_3

PEG

PEG

PEG_TX_0

PEG_TX#_0

PEG_TX_1

PEG_TX#_1

PEG_TX_2

PEG_TX#_2

PEG_TX_3

PEG_TX#_3

PEG_TX_4

PEG_TX#_4

PEG_TX_5

PEG_TX#_5

PEG_TX_6

PEG_TX#_6

PEG_TX_7

PEG_TX#_7

PEG_TX_8

PEG_TX#_8

PEG_TX_9

PEG_TX#_9

PEG_TX_10

PEG_TX#_10

PEG_TX_11

PEG_TX#_11

PEG_TX_12

PEG_TX#_12

PEG_TX_13

PEG_TX#_13

PEG_TX_14

PEG_TX#_14

PEG_TX_15

PEG_TX#_15

DMI_TX_0

DMI_TX#_0

DMI_TX_1

DMI_TX#_1

DMI_TX_2

DMI_TX#_2

DMI_TX_3

DMI_TX#_3

C13

C14

E14

E13

G14

G13

F12

F11

J14

J13

D8

D7

D3

C3

E6

E5

F8

F7

G10

G9

G5

G6

K7

K8

J5

J6

M8

M7

L6

L5

N5

N6

V7

V6

W7

W8

Y6

Y7

AA7

AA8

EXP_TXP0 32

EXP_TXN0 32

EXP_TXP1 32

EXP_TXN1 32

EXP_TXP2 32

EXP_TXN2 32

EXP_TXP3 32

EXP_TXN3 32

EXP_TXP4 32

EXP_TXN4 32

EXP_TXP5 32

EXP_TXN5 32

EXP_TXP6 32

EXP_TXN6 32

EXP_TXP7 32

EXP_TXN7 32

EXP_TXP8 32

EXP_TXN8 32

EXP_TXP9 32

EXP_TXN9 32

EXP_TXP10 32

EXP_TXN10 32

EXP_TXP11 32

EXP_TXN11 32

EXP_TXP12 32

EXP_TXN12 32

EXP_TXP13 32

EXP_TXN13 32

EXP_TXP14 32

EXP_TXN14 32

EXP_TXP15 32

EXP_TXN15 32

DMI_TXP0 20

DMI_TXN0 20

DMI_TXP1 20

DMI_TXN1 20

DMI_TXP2 20

DMI_TXN2 20

DMI_TXP3 20

DMI_TXN3 20

I

I

HU1D

HU1D

+1P05V_CPUIO

12

I

I

HR2

HR2

24.9

24.9

1%

1%

mx_r0402

mx_r0402

FDI_COMP

AE2

FDI_COMPIO

AE1

FDI_ICOMPO

FDI

FDI

FDI_FSYNC_024

FDI_LSYNC_024

FDI_FSYNC_124

FDI_LSYNC_124

FDI_INT24

AC5

AC4

AE5

AE4

AG3

SOCKET_1155P

SOCKET_1155P

FDI_FSYNC_0

FDI_LSYNC_0

FDI_FSYNC_1

FDI_LSYNC_1

FDI_INT

FDI_TX_0

FDI_TX#_0

FDI_TX_1

FDI_TX#_1

FDI_TX_2

FDI_TX#_2

FDI_TX_3

FDI_TX#_3

FDI_TX_4

FDI_TX#_4

FDI_TX_5

FDI_TX#_5

FDI_TX_6

FDI_TX#_6

FDI_TX_7

FDI_TX#_7

AC8

AC7

AC2

AC3

AD2

AD1

AD4

AD3

AD7

AD6

AE7

AE8

AF3

AF2

AG2

AG1

FDI_TXP0 24

FDI_TXN0 24

FDI_TXP1 24

FDI_TXN1 24

FDI_TXP2 24

FDI_TXN2 24

FDI_TXP3 24

FDI_TXN3 24

FDI_TXP4 24

FDI_TXN4 24

FDI_TXP5 24

FDI_TXN5 24

FDI_TXP6 24

FDI_TXN6 24

FDI_TXP7 24

FDI_TXN7 24

PEG_COMP

+1P05V_CPUIO

12

I

I

HR3

HR3

24.9

24.9

1%

1%

mx_r0402

mx_r0402

DMI

DMI

PE_TX_0

PE_TX#_0

PE_TX_1

PE_TX#_1

PE_TX_2

PE_TX#_2

PE_TX_3

PE_TX#_3

B5

C4

B4

P8

P7

T7

T8

R6

R5

U5

U6

PEG_ICOMPO

PEG_RCOMPO

PEG_COMPI

P3

PE_RX_0

P4

PE_RX#_0

R2

PE_RX_1

R1

PE_RX#_1

T4

PE_RX_2

T3

PE_RX#_2

U2

PE_RX_3

U1

PE_RX#_3

A A

SOCKET_1155P

SOCKET_1155P

GEN

GEN

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet of

5

4

http://vinafix.vn

3

2

Date: Sheet of

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

1

PCIE/DMI/FDI 3-6

PCIE/DMI/FDI 3-6

PCIE/DMI/FDI 3-6

Livy_Zhu

Livy_Zhu

Livy_Zhu

11 83Friday, September 24, 2010

11 83Friday, September 24, 2010

11 83Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

of

Page 12

vinafix

5

4

I

I

HU1E

HU1E

3

2

1

NOTE:

H_CFG0

H_CFG1

H_CFG2

H_CFG3

H_CFG4

H_CFG5

H_CFG6

H_CFG7

H_CFG8

H_CFG9

H_CFG10

H_CFG11

H_CFG12

H_CFG13

H_CFG14

H_CFG15

W2

BCLK_0

W1

BCLK#_0

C40

RSVD_001

D40

RSVD_002

C37

VIDSCLK

B37

VIDSOUT

A37

VIDALERT#

F36

RESET#

J40

UNCOREPWRGOOD

AJ19

SM_DRAMPWROK

J35

PECI

E37

CATERR#

H34

PROCHOT#

G35

THERMTRIP#

E38

PM_SYNC

AJ22

SM_VREF

AJ33

SKTOCC#

K32

PROC_SEL

H36

CFG_0

J36

CFG_1

J37

CFG_2

K36

CFG_3

L36

CFG_4

N35

CFG_5

L37

CFG_6

M36

CFG_7

J38

CFG_8

L35

CFG_9

M38

CFG_10

N36

CFG_11

N38

CFG_12

N39

CFG_13

N37

CFG_14

N40

CFG_15

G37

CFG_16

G36

CFG_17

AT14

RSVD_016

AY3

RSVD_023

H7

RSVD_028

H8

RSVD_029

SOCKET_1155P

SOCKET_1155P

3

MISC

MISC

VCCSA_VID

VCCSA_SENSE

VCC_SENSE

VSS_SENSE

VCCIO_SENSE

VSSIO_SENSE

VCCAXG_SENSE

VSSAXG_SENSE

VCCP_SELECT

CK_100M_DMI24

CK_100M_DMI#24

D D

HR55 0Imx_r0402HR55 0Imx_r0402

VIDSCLK73

VIDSOUT73

VIDALERT#73

PLTRST_CPU#15

CPUPWRGD22,69,82

DRAM_PWROK22

C C

PECI_HECETA81

PECI_SIO52

PECI_PCH21

CATERR#21,79

PROCHOT#73

H_THMTRIP#21

PM_SYNC21

SKTOCC#52

NVR_CLE24

B B

+1P5V_DUAL

12

I

I

D3R39

D3R39

100

100

1%

1%

mx_r0402

mx_r0402

A A

12

I

I

D3R40

D3R40

100

100

1%

1%

mx_r0402

mx_r0402

12

GNDGND

1 2

HR56 0Imx_r0402HR56 0Imx_r0402

1 2

HR57 0Imx_r0402HR57 0Imx_r0402

1 2

NI

NI

12

HC7

HC7

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

mx_c0402

mx_c0402

HR51 0NImx_r0402HR51 0NImx_r0402

1 2

HR20 0Imx_r0402HR20 0Imx_r0402

1 2

HR21 0NImx_r0402HR21 0NImx_r0402

1 2

HR23 4.7KImx_r0402HR23 4.7KImx_r0402

12

Place HR23 close to NVRAM connector

and minimize this stub to <100 mils

with PCH and NVRAM

connector

CFG[0~15] is IPU

NOTE:

I

I

D3CB17

D3CB17

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

mx_c0402

mx_c0402

CFG6 CFG5

11

10

01

00

5

Description

X16(Default)

2X8

Reserved

X8, X4/X4

CK_100M_CPU_XDP82

CK_100M_CPU_XDP#82

+1P05V_CPUIO

12

GND

12

I

I

12

NI

NI

NI

NI

HR5

HR5

HR4

HR4

90.9

90.9

51

51

1%

1%

mx_r0402

mx_r0402

mx_r0402

mx_r0402

VIDALERT#_R H_VIDALERT#

R1458 120 Ohm 1%

R1458 120 Ohm 1%

1 2

I

I

HR58

HR58

1K

1K

mx_r0402

mx_r0402

12

12

GND

NOTE:

Place near CPU

12

I

I

HR6

HR6

110

110

1%

1%

mx_r0402

mx_r0402

NI

NI

12

HC6

HC6

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

mx_c0402

mx_c0402

GNDGND

I

I

HR14

HR14

2.2K

2.2K

mx_r0402

mx_r0402

NI

NI

HCB2

HCB2

0.1UF/16V

0.1UF/16V

Y5V +80-20%

Y5V +80-20%

mx_c0402

mx_c0402

GND

GND

8/17

NI

NI

+1P05V_CPUIO+1P8V_NANDIO

12

HC11

HC11

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

mx_c0402

mx_c0402

GND

1 2

R_DRAM_PWROK

NI

NI

12

HC5

HC5

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

mx_c0402

mx_c0402

GND

12

NI

NI

HR17

HR17

1K

1K

mx_r0402

mx_r0402

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

12

http://vinafix.vn

12

I

I

HR7

HR7

75

75

1%

1%

mx_r0402

mx_r0402

HR11 44.2 1%Imx_r0402HR11 44.2 1%Imx_r0402

12

NI

NI

HR16

HR16

1K

1K

mx_r0402

mx_r0402

CPU_CFG082

HR24 1KNImx_r0402HR24 1KNImx_r0402

HR25 1KNImx_r0402HR25 1KNImx_r0402

HR27 1KNImx_r0402HR27 1KNImx_r0402

HR26 1KNImx_r0402HR26 1KNImx_r0402

HR28 1KNImx_r0402HR28 1KNImx_r0402

HR29 1KNImx_r0402HR29 1KNImx_r0402

HR30 1KNImx_r0402HR30 1KNImx_r0402

HR32 1KNImx_r0402HR32 1KNImx_r0402

HR31 1KNImx_r0402HR31 1KNImx_r0402

HR33 1KNImx_r0402HR33 1KNImx_r0402

HR34 1KNImx_r0402HR34 1KNImx_r0402

HR35 1KNImx_r0402HR35 1KNImx_r0402

HR37 1KNImx_r0402HR37 1KNImx_r0402

HR36 1KNImx_r0402HR36 1KNImx_r0402

HR39 1KNImx_r0402HR39 1KNImx_r0402

HR38 1KNImx_r0402HR38 1KNImx_r0402

HR41 1KNImx_r0402HR41 1KNImx_r0402

HR40 1KNImx_r0402HR40 1KNImx_r0402

4

H_VIDSCLK

H_VIDSOUT

12

NI

NI

HR59

HR59

100

100

mx_r0402

mx_r0402

For VR Debug

GND

I

I

HR18

HR18

51

51

mx_r0402

mx_r0402

H_PECI_R

CATERR_R#

H_DDR_VREF

PROC_SEL

H_CFG16_SNB_PCUSTB0

H_CFG17_SNB_PCUSTB1

TDO

TCK

TMS

TRST#

PRDY#

PREQ#

DBR#

BPM#_0

BPM#_1

BPM#_2

BPM#_3

BPM#_4

BPM#_5

BPM#_6

BPM#_7

RSVD_024

RSVD_030

RSVD_037

RSVD_036

RSVD_033

RSVD_040

RSVD_039

RSVD_018

RSVD_020

RSVD_038

RSVD_032

RSVD_034

RSVD_035

RSVD_050

RSVD_053

RSVD_051

RSVD_052

P34

T2

A36

B36

AB4

AB3

L32

M32

+5V

12

I

I

HR52

HR52

10K

10K

mx_r0402

mx_r0402

P33

L39

L40

TDI

M40

L38

J39

12

I

I

HR53

HR53

4.7K

4.7K

mx_r0402

mx_r0402

GND

K38

K40

E39

H40

H38

G38

G40

G39

F38

E40

F40

B39

J33

L34

L33

K34

N33

M34

AV1

AW2

L9

J9

K9

L31

J31

K31

AD34

AD35

VCCSA_SENSE 66

VCC_SENSE 73

VSS_SENSE 73

VCCIO_SENSE 71

VSSIO_SENSE 71

VCCAXG_SENSE 73

VSSAXG_SENSE 73

12

I

I

HR8

HR8

51

51

mx_r0402

mx_r0402

+3P3VSB

12

NI

NI

HR15

HR15

220

220

mx_r0402

mx_r0402

NOTE:

Place near CPU

12

I

I

HR9

HR9

51

51

mx_r0402

mx_r0402

12

I

I

HR12

HR12

51

51

mx_r0402

mx_r0402

GND

+1P05V_CPUIO +1P05V_CPUIO

BPM0# 82

BPM1# 82

BPM2# 82

BPM3# 82

BPM4# 82

BPM5# 82

BPM6# 82

BPM7# 82

12

GND

H_PRDY# 82

H_PREQ# 82

SYS_RESET_DBR# 22,82,83

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet of

2

Date: Sheet of

NI

NI

HR60

HR60

1K

1K

mx_r0402

mx_r0402

VCCSA_VID 66

NOTE:

Place near XDP connector

12

I

I

HR10

HR10

51

51

mx_r0402

mx_r0402

12

I

I

HR13

HR13

51

51

mx_r0402

mx_r0402

GND

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

1

VCCIO_SEL 71

TDO 82

TDI 82

TCK 82

TMS 82

TRST# 82

MISC 4-6

MISC 4-6

MISC 4-6

Livy_Zhu

Livy_Zhu

Livy_Zhu

12 83Friday, September 24, 2010

12 83Friday, September 24, 2010

12 83Friday, September 24, 2010

of

Rev

Rev

Rev

1.00

1.00

1.00

Page 13

5

4

3

2

1

vinafix

I

AG33

AJ16

AJ17

AJ26

AJ28

AJ32

AK15

AK17

AK19

AK21

AK23

AK27

AK29

AK30

AK11

AK12

M13

A11

AA3

AB8

AF8

D10

H10

H11

H12

K10

K11

M10

M11

M12

A7

B9

D6

E3

E4

G3

G4

J3

J4

J7

J8

L3

L4

L7

N3

N4

N7

R3

R4

R7

U3

U4

U7

V8

W3

J10

L11

L12

I

HU1H

HU1H

VCCIO_34

VCCIO_01

VCCIO_02

VCCIO_03

VCCIO_04

VCCIO_05

VCCIO_06

VCCIO_07

VCCIO_08

VCCIO_09

VCCIO_10

VCCIO_11

VCCIO_12

VCCIO_13

VCCIO_14

VCCIO_15

VCCIO_16

VCCIO_17

VCCIO_18

VCCIO_19

VCCIO_20

VCCIO_21

VCCIO_22

VCCIO_23

VCCIO_24

VCCIO_25

VCCIO_26

VCCIO_27

VCCIO_28

VCCIO_29

VCCIO_30

VCCIO_31

VCCIO_32

VCCIO_33

VCCIO_35

VCCIO_36

VCCIO_37

VCCIO_38

VCCIO_39

VCCIO_40

VCCIO_41

VCCIO_42

VCCIO_43

VCCIO_44

VCCIO_45

VCCSA_01

VCCSA_02

VCCSA_03

VCCSA_04

VCCSA_05

VCCSA_06

VCCSA_07

VCCSA_08

VCCSA_09

VCCSA_10

VCCSA_11

VCCPLL_01

VCCPLL_02

SOCKET_1155P

SOCKET_1155P

VDDQ_01

VDDQ_02

VDDQ_04

VDDQ_05

VDDQ_06

VDDQ_07

VDDQ_08

VDDQ_09

VDDQ_10

VDDQ_11

VDDQ_12

VDDQ_13

VDDQ_14

VDDQ_15

VDDQ_16

VDDQ_17

VDDQ_18

VDDQ_19

VDDQ_20

VDDQ_21

VDDQ_22

VDDQ_23

VDDQ_03

AJ13

AJ14

AJ23

AJ24

AR20

AR21

AR22

AR23

AR24

AU19

AU23

AU27

AU31

AV21

AV24

AV25

AV29

AV33

AW31

AY23

AY26

AY28

AJ20

+1P5V_DUAL+1P05V_CPUIO

I

I

12

HCB1

HCB1

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805_small

mx_c0805_small

GND GND GND

I

I

12

HCB6

HCB6

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805_small

mx_c0805_small

Inside processor socket cavity

8/17: change to 22UF 11X234226160

I

I

12

HCB3

HCB3

22UF/6.3V

22UF/6.3V

X5R 20%

X5R 20%

mx_c0805_small

mx_c0805_small

+V_AXG

AB33

AB34

AB35

AB36

AB37

AB38

AB39

AB40

AC33

AC34

AC35

AC36

AC37

AC38

AC39

AC40

W33

W34

W35

W36

W37

W38

T33

T34

T35

T36

T37

T38

T39

T40

U33

U34

U35

U36

U37

U38

U39

U40

Y33

Y34

Y35

Y36

Y37

Y38

I

I

HU1G

HU1G

VCCAXG_01

VCCAXG_02

VCCAXG_03

VCCAXG_04

VCCAXG_05

VCCAXG_06

VCCAXG_07

VCCAXG_08

VCCAXG_09

VCCAXG_10

VCCAXG_11

VCCAXG_12

VCCAXG_13

VCCAXG_14

VCCAXG_15

VCCAXG_16

VCCAXG_17

VCCAXG_18

VCCAXG_19

VCCAXG_20

VCCAXG_21

VCCAXG_22

VCCAXG_23

VCCAXG_24

VCCAXG_25

VCCAXG_26

VCCAXG_27

VCCAXG_28

VCCAXG_29

VCCAXG_30

VCCAXG_31

VCCAXG_32

VCCAXG_33

VCCAXG_34

VCCAXG_35

VCCAXG_36

VCCAXG_37

VCCAXG_38

VCCAXG_39

VCCAXG_40

VCCAXG_41

VCCAXG_42

VCCAXG_43

VCCAXG_44

SOCKET_1155P

SOCKET_1155P

I

A12

A13

A14

A15

A16

A18

A24

A25

A27

A28

B15

B16

B18

B24

B25

B27

B28

B30

B31

B33

B34

C15

C16

C18

C19

C21

C22

C24

C25

C27

C28

C30

C31

C33

C34

C36

D13

D14

D15

D16

D18

D19

D21

D22

D24

D25

D27

D28

D30

D31

D33

D34

D35

D36

E15

E16

E18

E19

E21

E22

E24

E25

E27

E28

E30

E31

E33

E34

E35

F15

F16

F18

F19

F21

F22

F24

F25

F27

F28

F30

F31

I

HU1F

HU1F

VCC_001

VCC_002

VCC_003

VCC_004

VCC_005

VCC_006

VCC_007

VCC_008

VCC_009

VCC_010

VCC_011

VCC_012

VCC_013

VCC_014

VCC_015

VCC_016

VCC_017

VCC_018

VCC_019

VCC_020

VCC_021

VCC_022

VCC_023

VCC_024

VCC_025

VCC_026

VCC_027

VCC_028

VCC_029

VCC_030

VCC_031

VCC_032

VCC_033

VCC_034

VCC_035

VCC_036

VCC_037

VCC_038

VCC_039

VCC_040

VCC_041

VCC_042

VCC_043

VCC_044

VCC_045

VCC_046

VCC_047

VCC_048

VCC_049

VCC_050

VCC_051

VCC_052

VCC_053

VCC_054

VCC_055

VCC_056

VCC_057

VCC_058

VCC_059

VCC_060

VCC_061

VCC_062

VCC_063

VCC_064

VCC_065

VCC_066

VCC_067

VCC_068

VCC_069

VCC_070

VCC_071

VCC_072

VCC_073

VCC_074

VCC_075

VCC_076

VCC_077

VCC_078

VCC_079

VCC_080

VCC_081

VCC_082

VCC_083

VCC_084

VCC_085

VCC_086

VCC_087

VCC_088

VCC_089

VCC_090

VCC_091

VCC_092

VCC_093

VCC_094

VCC_095

VCC_096

VCC_097

VCC_098

VCC_099

VCC_100

VCC_101

VCC_102

VCC_103

VCC_104

VCC_105

VCC_106

VCC_107

VCC_108

VCC_109

VCC_110

VCC_111

VCC_112

VCC_113

VCC_114

VCC_115

VCC_116

VCC_117

VCC_118

VCC_119

VCC_120

VCC_121

VCC_122

VCC_123

VCC_124

VCC_125

VCC_126

VCC_127

VCC_128

VCC_129

VCC_130

VCC_131

VCC_132

VCC_133

VCC_134

VCC_135

VCC_136

VCC_137

VCC_138

VCC_139

VCC_140

VCC_141

VCC_142

VCC_143

VCC_144

VCC_145

VCC_146

VCC_147

VCC_148

VCC_149

VCC_150

VCC_151

VCC_152

VCC_153

VCC_154

VCC_155

VCC_156

VCC_157

VCC_158

VCC_159

VCC_160

VCC_161

F32

F33

F34

G15

G16

G18

G19

G21

G22

G24

G25

G27

G28

G30

G31

G32

G33

H13

H14

H15

H16

H18

H19

H21

H22

H24

H25

H27

H28

H30

H31

H32

J12

J15

J16

J18

J19

J21

J22

J24

J25

J27

J28

J30

K15

K16

K18

K19

K21

K22

K24

K25

K27

K28

K30

L13

L14

L15

L16

L18

L19

L21

L22

L24

L25

L27

L28

L30

M14

M15

M16

M18

M19

M21

M22

M24

M25

M27

M28

M30

+VCORE+VCORE

+0P925V_SA

+1P8V_SFR

09/07

I

I

12

HCB5

HCB5

0.1UF/16V

0.1UF/16V

Y5V +80-20%

Y5V +80-20%

mx_c0402

mx_c0402

I

I

12

HCB4

HCB4

0.1UF/16V

0.1UF/16V

Y5V +80-20%

Y5V +80-20%

mx_c0402

mx_c0402

GNDGND

D D

C C

B B

A A

5

SOCKET_1155P

SOCKET_1155P

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

4

http://vinafix.vn

3

2

Date: Sheet

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

1

VCC 5 - 6

VCC 5 - 6

VCC 5 - 6

Livy_Zhu

Livy_Zhu

Livy_Zhu

13 83Friday, September 24, 2010

13 83Friday, September 24, 2010

13 83Friday, September 24, 2010

of

Rev

Rev

Rev

1.00

1.00

1.00

Page 14

5

4

3

2

1

vinafix

D D

C C

B B

A A

GND GND GND GND

A17

A23

A26

A29

A35

AA33

AA34

AA35

AA36

AA37

AA38

AA6

AB5

AC1

AC6

AD33

AD36

AD38

AD39

AD40

AD5

AD8

AE3

AE33

AE36

AF1

AF34

AF36

AF37

AF40

AF5

AF6

AF7

AG36

AH2

AH3

AH33

AH36

AH37

AH38

AH39

AH40

AH5

AH8

AJ12

AJ15

AJ18

AJ21

AJ25

AJ27

AJ36

AJ5

AK1

AK10

AK13

AK14

AK16

AK22

AK28

AK31

AK32

AK33

AK34

AK35

AK36

AK37

AK4

AK40

AK5

AK6

AK7

AK8

AK9

AL11

AL14

AL17

AL19

AL24

AL27

AL30

AL36

AL5

AM1

AM11

AM14

AM17

AM2

AM21

AM23

AM25

AV39

A4

I

I

HU1I

HU1I

VSS_001

VSS_002

VSS_003

VSS_004

VSS_005

VSS_006

VSS_007

VSS_008

VSS_009

VSS_010

VSS_011

VSS_012

VSS_013

VSS_014

VSS_015

VSS_016

VSS_017

VSS_018

VSS_019

VSS_020

VSS_021

VSS_022

VSS_023

VSS_024

VSS_025

VSS_026

VSS_027

VSS_028

VSS_029

VSS_030

VSS_031

VSS_032

VSS_033

VSS_034

VSS_035

VSS_036

VSS_037

VSS_038

VSS_039

VSS_040

VSS_041

VSS_042

VSS_043

VSS_044

VSS_045

VSS_046

VSS_047

VSS_048

VSS_049

VSS_050

VSS_051

VSS_052

VSS_053

VSS_054

VSS_055

VSS_056

VSS_057

VSS_058

VSS_059

VSS_060

VSS_061

VSS_062

VSS_063

VSS_064

VSS_065

VSS_066

VSS_067

VSS_068

VSS_069

VSS_070

VSS_071

VSS_072

VSS_073

VSS_074

VSS_075

VSS_076

VSS_077

VSS_078

VSS_079

VSS_080

VSS_081

VSS_082

VSS_083

VSS_084

VSS_085

VSS_086

VSS_087

VSS_088

VSS_089

VSS_090

VSS_NCTF_01

VSS_NCTF_02

SOCKET_1155P

SOCKET_1155P

5

GND

GND

VSS_091

VSS_092

VSS_093

VSS_094

VSS_095

VSS_096

VSS_097

VSS_098

VSS_099

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

VSS_125

VSS_126

VSS_127

VSS_128

VSS_129

VSS_130

VSS_131

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

VSS_139

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

VSS_149

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

VSS_155

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

VSS_167

VSS_168

VSS_169

VSS_170

VSS_171

VSS_172

VSS_173

VSS_174

VSS_175

VSS_176

VSS_177

VSS_178

VSS_179

VSS_180

AM27

AM3

AM30

AM36

AM37

AM38

AM39

AM4

AM40

AM5

AN10

AN11

AN14

AN17

AN19

AN22

AN24

AN27

AN30

AN31

AN32

AN33

AN34

AN35

AN36

AN5

AN6

AN7

AN8

AN9

AP1

AP11

AP14

AP17

AP22

AP25

AP27

AP30

AP36

AP37

AP4

AP40

AP5

AR11

AR14

AR17

AR18

AR19

AR27

AR30

AR36

AR5

AT1

AT10

AT12

AT13

AT15

AT16

AT17

AT2

AT25

AT27

AT28

AT29

AT3

AT30

AT31

AT32

AT33

AT34

AT35

AT36

AT37

AT38

AT39

AT4

AT40

AT5

AT6

AT7

AT8

AT9

AU1

AU15

AU26

AU34

AU4

AU6

AU8

AV10

AV11

AV14

AV17

AV35

AV38

AW10

AW11

AW14

AW16

AW36

AW6

AY11

AY14

AY18

AY35

AY37

4

AV3

AV6

AY4

AY6

AY8

B10

B13

B14

B17

B23

B26

B29

B32

B35

B38

C11

C12

C17

C20

C23

C26

C29

C32

C35

D17

D20

D23

D26

D29

D32

D37

D39

E11

E12

E17

E20

E23

E26

E29

E32

E36

F10

F13

F14

F17

F20

F23

F26

F29

F35

F37

F39

G11

G12

G17

G20

G23

G26

G29

G34

B6

C7

C8

D2

D4

D5

D9

E7

E8

F1

F2

F5

F6

F9

G7

B3

I

I

HU1J

HU1J

VSS_181

VSS_182

VSS_183

VSS_184

VSS_185

VSS_186

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSS_243

VSS_244

VSS_245

VSS_246

VSS_247

VSS_248

VSS_249

VSS_250

VSS_251

VSS_252

VSS_253

VSS_254

VSS_255

VSS_256

VSS_257

VSS_258

VSS_259

VSS_260

VSS_261

VSS_262

VSS_263

VSS_264

VSS_265

VSS_266

VSS_267

VSS_268

VSS_269

VSS_270

VSS_NCTF_03

VSS_NCTF_04

GND

GND

SOCKET_1155P

SOCKET_1155P

G8

VSS_271

H1

VSS_272

H17

VSS_273

H2

VSS_274

H20

VSS_275

H23

VSS_276

H26

VSS_277

H29

VSS_278

H33

VSS_279

H35

VSS_280

H37

VSS_281

H39

VSS_282

H5

VSS_283

H6

VSS_284

H9

VSS_285

J11

VSS_286

J17

VSS_287

J20

VSS_288

J23

VSS_289

J26

VSS_290

J29

VSS_291

VSS_292

VSS_293

VSS_294

VSS_295

VSS_296

VSS_297

VSS_298

VSS_299

VSS_300

VSS_301

VSS_302

VSS_303

VSS_304

VSS_305

VSS_306

VSS_307

VSS_308

VSS_309

VSS_310

VSS_311

VSS_312

VSS_313

VSS_314

VSS_315

VSS_316

VSS_317

VSS_318

VSS_319

VSS_320

VSS_321

VSS_322

VSS_323

VSS_324

VSS_325

VSS_326

VSS_327

VSS_328

VSS_329

VSS_330

VSS_331

VSS_332

VSS_333

VSS_334

VSS_335

VSS_336

VSS_337

VSS_338

VSS_339

VSS_340

VSS_341

VSS_342

VSS_343

VSS_344

VSS_345

VSS_346

VSS_347

VSS_348

VSS_349

VSS_350

VSS_351

VSS_352

VSS_353

VSS_354

VSS_355

VSS_356

VSS_357

VSS_358

VSS_359

VSS_360

J32

K1

K12

K13

K14

K17

K2

K20

K23

K26

K29

K33

K35

K37

K39

K5

K6

L10

L17

L20

L23

L26

L29

L8

M1

M17

M2

M20

M23

M26

M29

M33

M35

M37

M39

M5

M6

M9

N8

P1

P2

P36

P38

P40

P5

P6

R33

R35

R37

R39

R8

T1

T5

T6

U8

V1

V2

V33

V34

V35

V36

V37

V38

V39

V40

V5

W6

Y5

Y8

NOBOM

NOBOM

HT38

HT38

http://vinafix.vn

TP_H_NCTF_A38

1

I

I

BACKPLATE1

BACKPLATE1

INTEL LGA 1156P BACK PLATE,3 SCREW

INTEL LGA 1156P BACK PLATE,3 SCREW

PT44P11-6401

PT44P11-6401

3

AB7

AD37

AG4

AJ29

AJ30

AJ31

AV34

AW34

P35

P37

P39

R34

R36

R38

R40

A38

AU40

AW38

C2

D1

I

I

HU1K

HU1K

RSVD_04

RSVD_05

RSVD_08

RSVD_10

RSVD_11

RSVD_12

RSVD_19

RSVD_21

RSVD_43

RSVD_44

RSVD_45

RSVD_46

RSVD_47

RSVD_48

RSVD_49

NCTF_01

NCTF_02

NCTF_03

NCTF_04

NCTF_05

SOCKET_1155P

SOCKET_1155P

FC_AH1

FC_AH4

RSVD_15

RSVD_14

RSVD_13

RSVD_17

RSVD_22

RSVD_07

RSVD_03

RSVD_06

RSVD_09

RSVD_27

RSVD_26

RSVD_25

RSVD_31

RSVD_41

NP_NC1

NP_NC2

NP_NC3

NP_NC4

NP_NC5

NP_NC6

NP_NC7

AH1

AH4

AT11

AP20

AN20

AU10

AY10

AF4

AB6

AE6

AJ11

D38

C39

C38

J34

N34

1

2

3

4

5

6

7

SA_DIMM_VR

SB_DIMM_VR

I

I

ILM1

ILM1

SOCKET1156_ILM

SOCKET1156_ILM

2

HR42 0Imx_r0402HR42 0Imx_r0402

1 2

HR43 0Imx_r0402HR43 0Imx_r0402

1 2

I

I

I

12

HC2

HC2

0.1UF/16V

0.1UF/16V

Y5V +80-20%

Y5V +80-20%

mx_c0402

mx_c0402

GND GND

INTEL LGA1156 SOCKET ILM

INTEL LGA1156 SOCKET ILM

I

12

HC3

HC3

0.1UF/16V

0.1UF/16V

Y5V +80-20%

Y5V +80-20%

mx_c0402

mx_c0402

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet

Date: Sheet of

Date: Sheet of

DIMM_DQ_VREF_A 16

DIMM_DQ_VREF_B 17

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

1

VSS 6 - 6

VSS 6 - 6

VSS 6 - 6

Livy_Zhu

Livy_Zhu

Livy_Zhu

14 83Friday, September 24, 2010

14 83Friday, September 24, 2010

14 83Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

of

Page 15

5

4

3

2

1

vinafix

D D

+3P3VA

I

I

12

HC9

HC9

0.1UF/16V

0.1UF/16V

X7R 10%

+3P3VA

12

I

I

HR44

HR44

1K

1K

mx_r0402

C C

PLTRST#22,35,53,55,80,82,83

I

I

HR47

HR47

10K

10K

mx_r0402

mx_r0402

1 2

TBD

HQ1_B

12

NI

NI

HR50

HR50

5.1K

5.1K

mx_r0402

mx_r0402

mx_r0402

PLTRST

3

3

C

C

I

I

B

1

B

1

HQ1

HQ1

12

PMBS3904

PMBS3904

E

E

2

2

GND

GNDGND

8/24

5 6

NI

NI

SC84

SC84

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

147

VCC

VCC

GND

GND

I

I

SU2C

SU2C

74LVC14AD

74LVC14AD

X7R 10%

mx_c0402

mx_c0402

GND

PLTRST_CPU#_SHT

178 ohm in CRB and PDG

I

I

HR46

HR46

180

180

1%

1%

MX_R0402

MX_R0402

1 2

GND

12

I

I

HR49

HR49

75

75

1%

1%

mx_r0402

mx_r0402

I

I

HR48

HR48

1K

1K

mx_r0402

mx_r0402

1 2

PLTRST_CPU# 12

CPURST_XDP# 82,83

PLTRST_CPU#

B B

+3P3VA

+3P3VSB

12

I

I

SR276

SR276

47K

47K

I

I

SR278

SQ11_B_R SQ11_B

12

SC80

SC80

2.2UF/6.3V

2.2UF/6.3V

X5R 10%

X5R 10%

I

I

mx_c0603

mx_c0603

A A

5

GND

SR278

1 2

0

0

12

1

1

NI

NI

SC81

SC81

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

4

12

I

I

SR279

SR279

10K

10K

I

I

SR282

SR282

SQ12_BSQ12_B_R RSMRST#_R

1 2

0

I

I

SQ11

SQ11

PMBS3904

PMBS3904

0

12

3

3

C

C

B

B

E

E

2

2

GND GNDGNDGND

http://vinafix.vn

NI

NI

SC82

SC82

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

+3P3VA

I

I

SU2D

SU2D

147

74LVC14AD

74LVC14AD

VCC

VCC

9 8

GND

GND

I

I

SR12

SR12

4.7K

4.7K

12

RSMRST# 22,52,83

PEGATRON DT-MB RESTRICTED SECRET

PLTRST_CPU#

PLTRST_CPU#

1

PLTRST_CPU#

Livy_Zhu

Livy_Zhu

Livy_Zhu

15 83Friday, September 24, 2010

15 83Friday, September 24, 2010

15 83Friday, September 24, 2010

Rev

Rev

Rev

1.00

1.00

1.00

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Engineer:

IPMSB-BE/CR

IPMSB-BE/CR

IPMSB-BE/CR

Page 16

5

vinafix

XMM1 COLOR: BLUE

D D

M_CHA_MAA0

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

M_CHA_MAA14

M_CHA_MAA15

M_CHA_CLK19

M_CHA_CLK1#9

M_CHA_CLK09

M_CHA_CLK0#9

C C

B B

A A

M_CHA_CS#19

M_CHA_CS#09

M_CHA_CKE19

M_CHA_CKE09

M_CHA_BA29

M_CHA_BA19

M_CHA_BA09

SMB_DATA_MAIN17,54,81,82,83

MA_ECC_CB[0..7]9

SMB_CLK_MAIN17,54,81,82,83

MA_ECC_CB7

MA_ECC_CB6

MA_ECC_CB5

MA_ECC_CB4

MA_ECC_CB3

MA_ECC_CB2

MA_ECC_CB1

MA_ECC_CB0

GND

M_CHA_WE#9

M_CHA_RAS#9

M_CHA_CAS#9

M_CHA_ODT19

M_CHA_ODT09

DDR3_DRAMRST#9,17

12

NI

NI

HC1

HC1

150PF/50V

150PF/50V

NPO 5%

NPO 5%

mx_c0402

mx_c0402

GND

M_CHA_DQS89

M_CHA_DQS8#9

GND

5

IDIMMA0A

IDIMMA0A

188

A0

181

A1

61

A2

180

A3

59

A4

58

A5

178

A6

56

A7

177

A8

175

A9

70

A10/AP

55

A11

174

A12

196

A13

172

A14

171

A15

63

CK1P/NU

64

CK1N/NU

184

CK0P

185

CK0N

76

CS1#

193

CS0#

169

CKE1

50

CKE0

52

BA2

190

BA1

71

BA0

238

SDA

118

SCL

165

CB7

164

CB6

159

CB5

158

CB4

46

CB3

45

CB2

40

CB1

39

CB0

237

SA1

117

SA0

73

WE#

192

RAS#

74

CAS#

77

ODT1

195

ODT0

168

RESET#

161

DM8/DQS17P

162

NC/DQS17N

230

DM7/DQS16P

231

NC/DQS16N

221

DM6/DQS15P

222

NC/DQS15N

212

DM5/DQS14P

213

NC/DQS14N

203

DM4/DQS13P

204

NC/DQS13N

152

DM3/DQS12P

153

NC/DQS12N

143

DM2/DQS11P

144

NC/DQS11N

134

DM1/DQS10P

135

NC/DQS10N

125

DM0/DQS9P

126

NC/DQS9N

43

NC/DQS8P

42

NC/DQS8N

198