Page 1

5

A

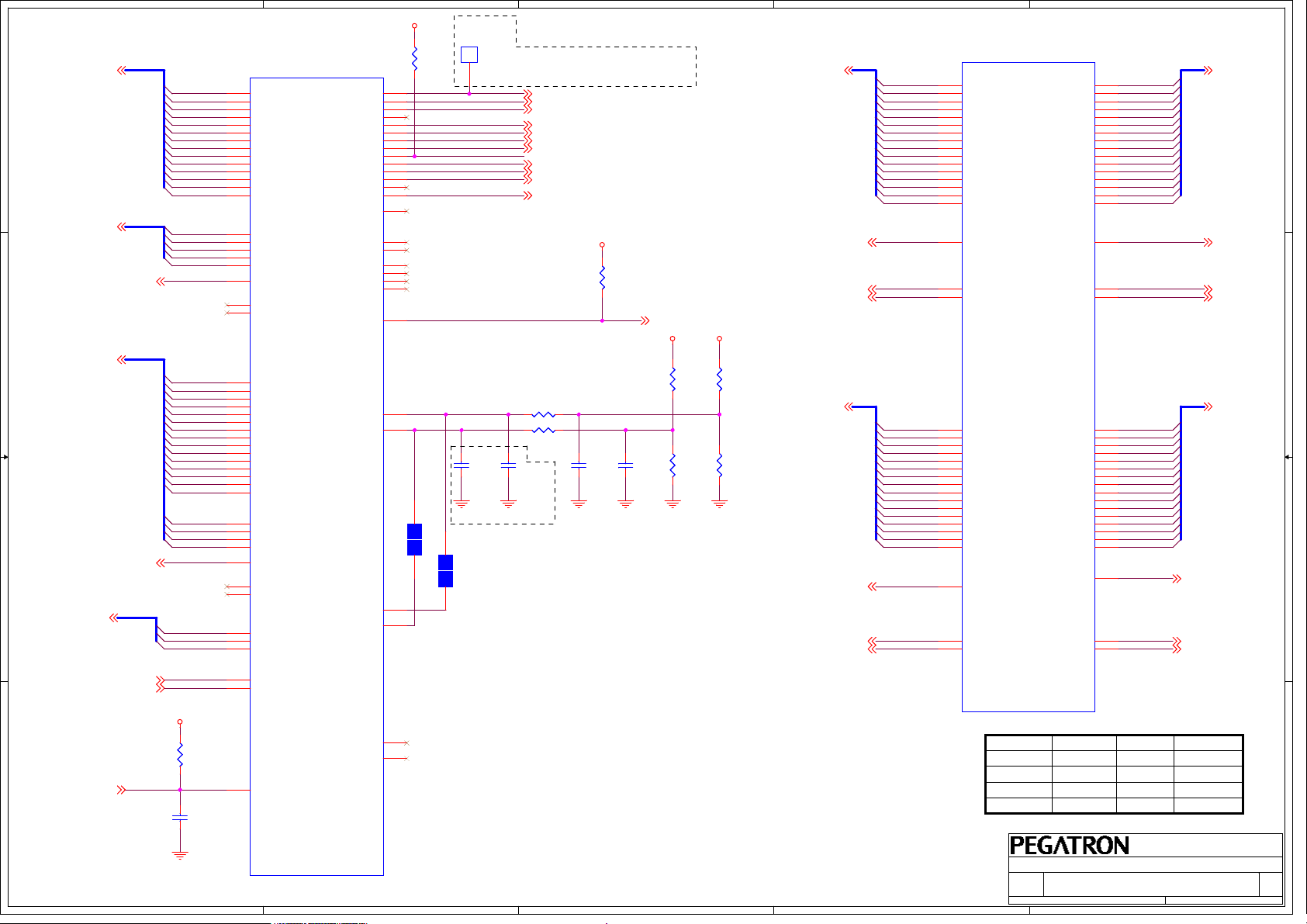

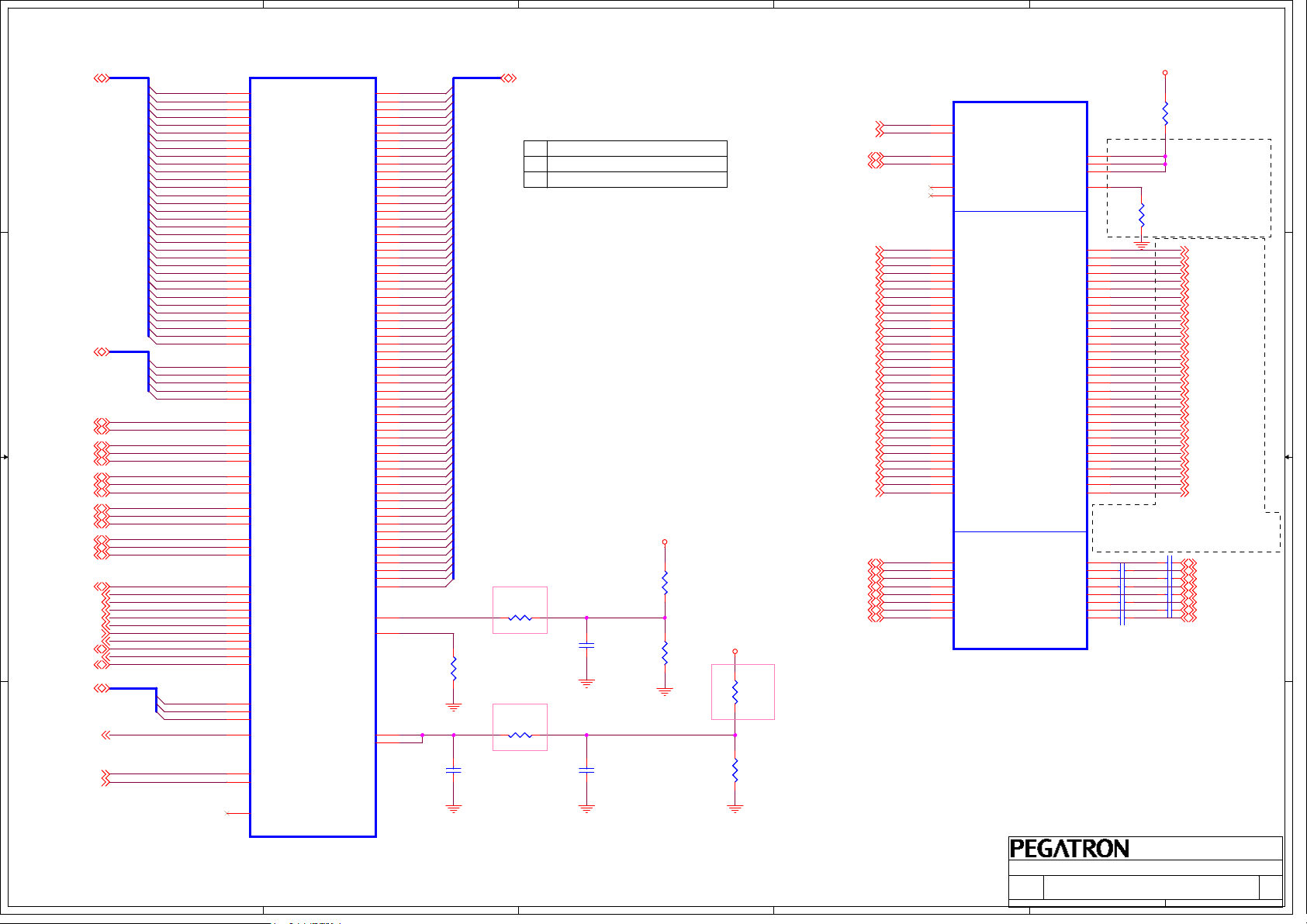

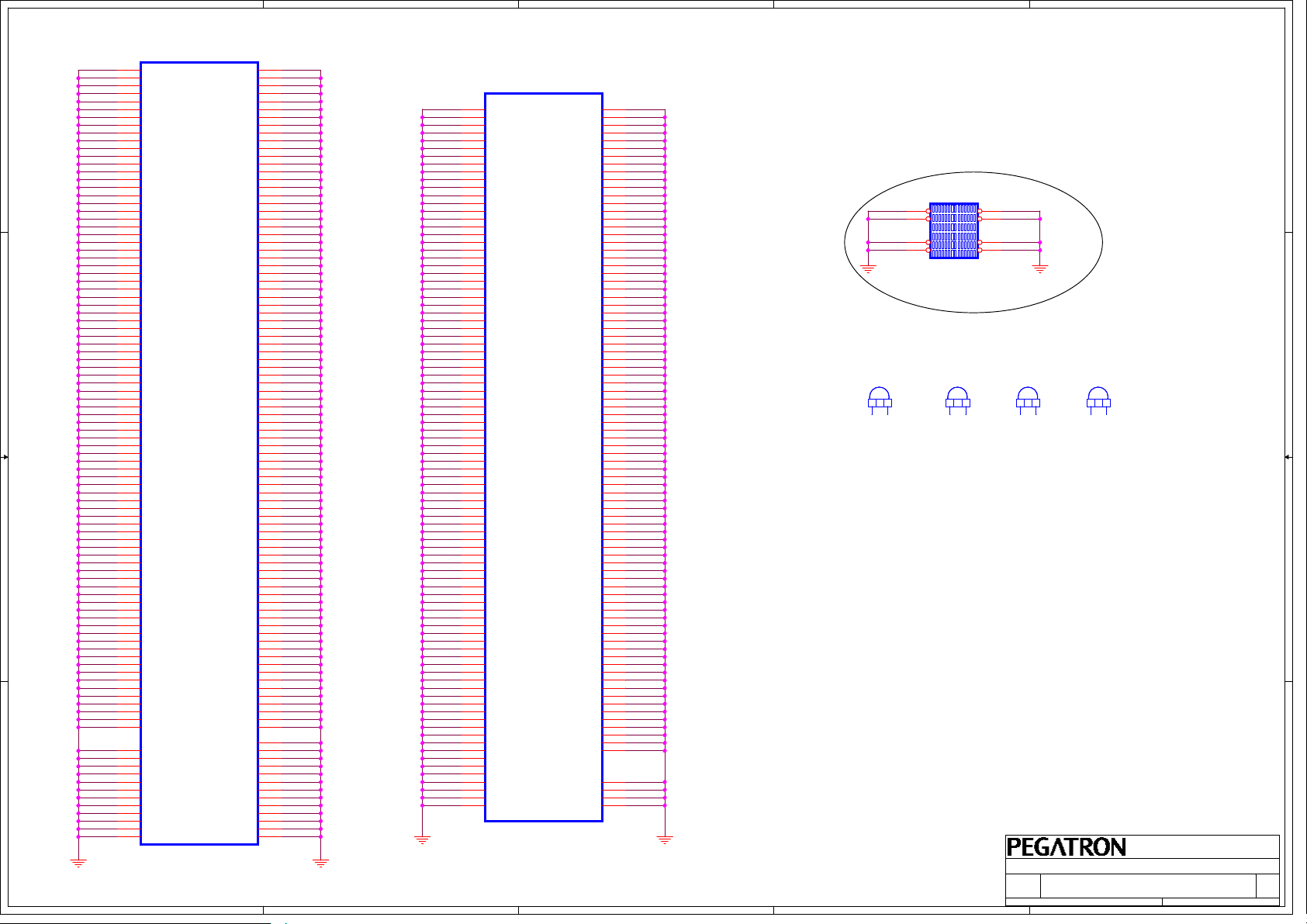

IPM41-D3

D D

Intel Pentium processor

Conroe-L/Conroe/Wolfdate

On board

VGA

C C

PCI Express

X16 SLOT

PCI-E X16

4

Revision:1.00

LGA775

HOST BUS

INTEL

GMCH

EagleLake

DMI Link

Channel A

Channel B

3

53

+1P1V_CORE

54

SPI 4Mb

55

RTC / CMOS / SPKR/SCREW HOLE

DDR3 DIMM A1

DDR3 DIMM B1

2

01

02

03

04

05

06

07

08

09

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

Block Diagram

Power Sequence

Power Flow

Clock Distribution

Clock

PROCESSOR LGA775 1 - 3

PROCESSOR LGA775 2 - 3

PROCESSOR LGA775 3 - 3

ITP_31P DEBUG CONNECTOR

INTEL EAGLELAKE 1 - 7

INTEL EAGLELAKE 2 - 7

INTEL EAGLELAKE 3 - 7

INTEL EAGLELAKE 4 - 7

INTEL EAGLELAKE 5 - 7

INTEL EAGLELAKE 6 - 7

INTEL EAGLELAKE 7 - 7

DDR2 CHANNEL A

DDR2 CHANNEL B

DDR2 TERMINATION A&B

ICH7-1

ICH7-2

ICH7-3

ICH7-4

PCI EXPRESS X16 SLOT

PCI EXPRESS X1 SLOT

INTEGRATED VGA PORT

SATA CONNECTORS

PCI SLOT INTERFACE - PCI1

PCI SLOT INTERFACE - PCI2

1

3032DOUBLE STACK PORT CONNECTOR

PCI Express

X1 SLOT

PCI-E X1

SATA

INTEL

B B

ALC662/ALC888S

Audio

Azalia Link

24MHz

ICH7

SATA1

SATA2

SATA3

SATA4

33

34

35

36

37

38

39

40

31

USB2.0

8 ports

480Mb/s

LPC

SUPER I/O

Winbond83627DHG-A

41

42

43

44

45

PCI Slot1

PCI Slot2

PCI Bus

SPI

Parallel Port

SPI

LAN

RealTek

PCI-E X

RTL8111D(L)

TPM

Serial Port

PS2 KB/MS

FAN Control

H/W Monitor

46

47

48

49

50

51

52

USB HEADER CONNECTOR

REALTEK RTL8111C CONTROLLER

RJ-45+USB CONNECTOR

ALC662/883

AUDIO Connector

FRONT AUDIO CONNECTOR

TPM HEADER INTERFACE

SUPER I/O W83627DHG - 1 OF 2

SUPER I/O W83627DHG - 2 OF 2

PARALLEL PORT - CPC

SERIAL PORT CONNECTOR- SI

PS2 KB &MS CONNECTOR FOR CPC

FAN CIRCUIT FOR 4 - PIN

FRONT PANEL CIRCUIT FOR CPC

ATX POWER_24P CONNECTOR

VCORE CONTROLLER - RT8857

VCORE DRIVER - RT9619_1

VCORE DRIVER - RT9619_2

+0P9V_VTT_DDR_LDO

+1P1V_FSB_VTT&+5V_DUAL

PSI CIRCUIT

+1P8V_DUAL

<Variant Name>

<Variant Name>

<Variant Name>

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPM41-D3

IPM41-D3

IPM41-D3

Engineer:

Block Diagram

Block Diagram

Block Diagram

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

1 55Thursday, July 09, 2009

1 55Thursday, July 09, 2009

1 55Thursday, July 09, 2009

1.00G

1.00G

1.00G

Rev

Rev

Rev

A

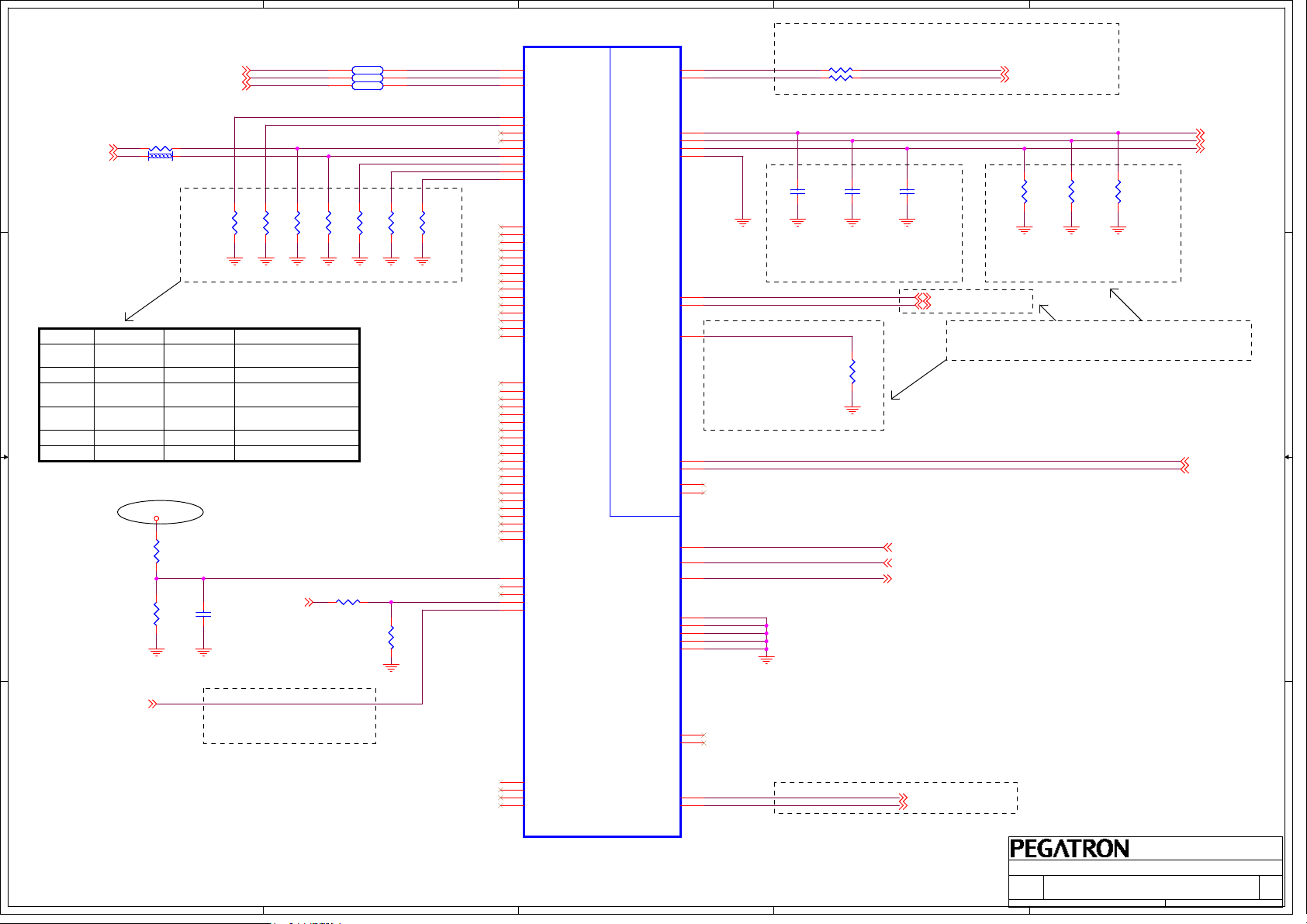

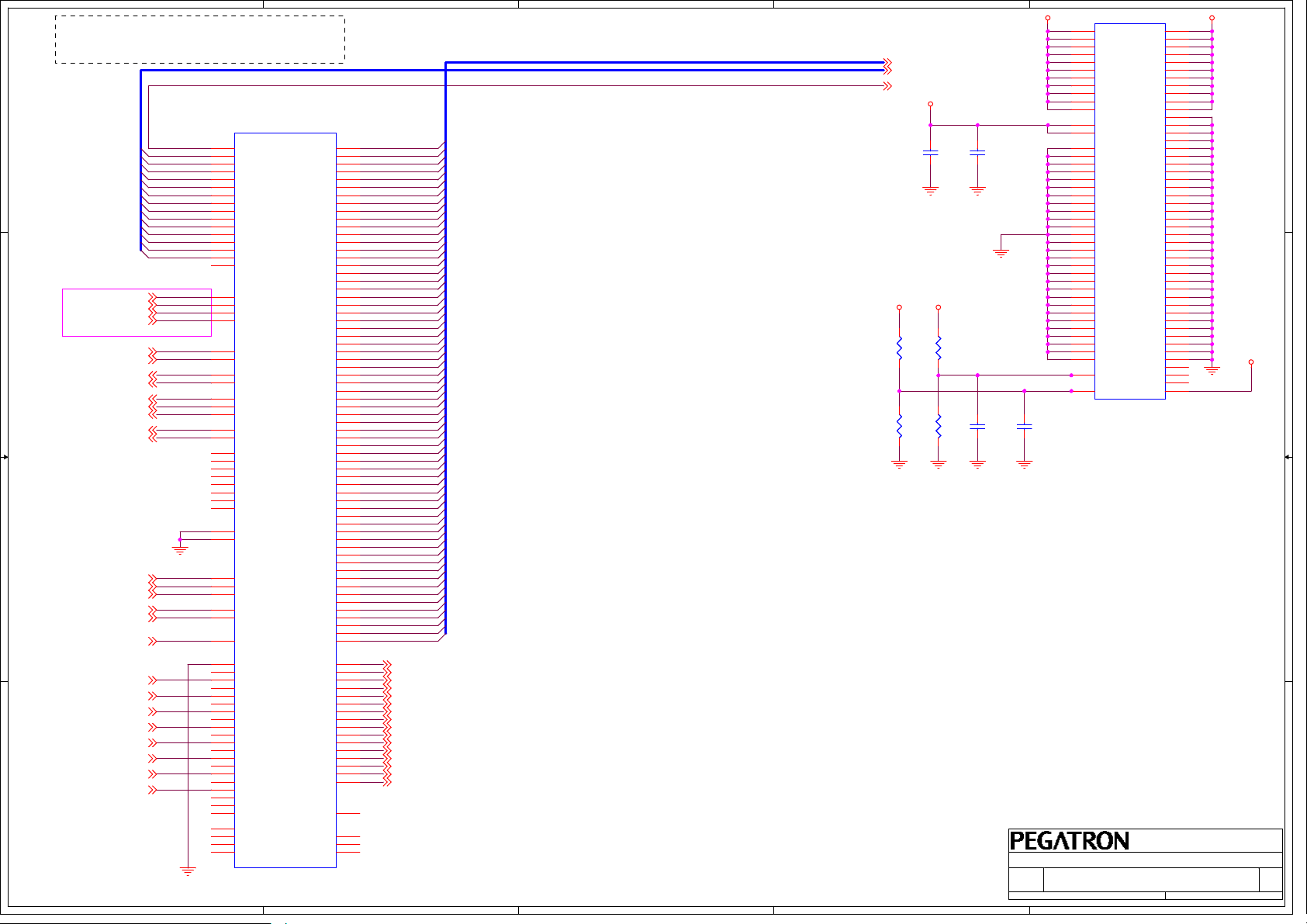

Page 2

5

A

4

3

2

1

8

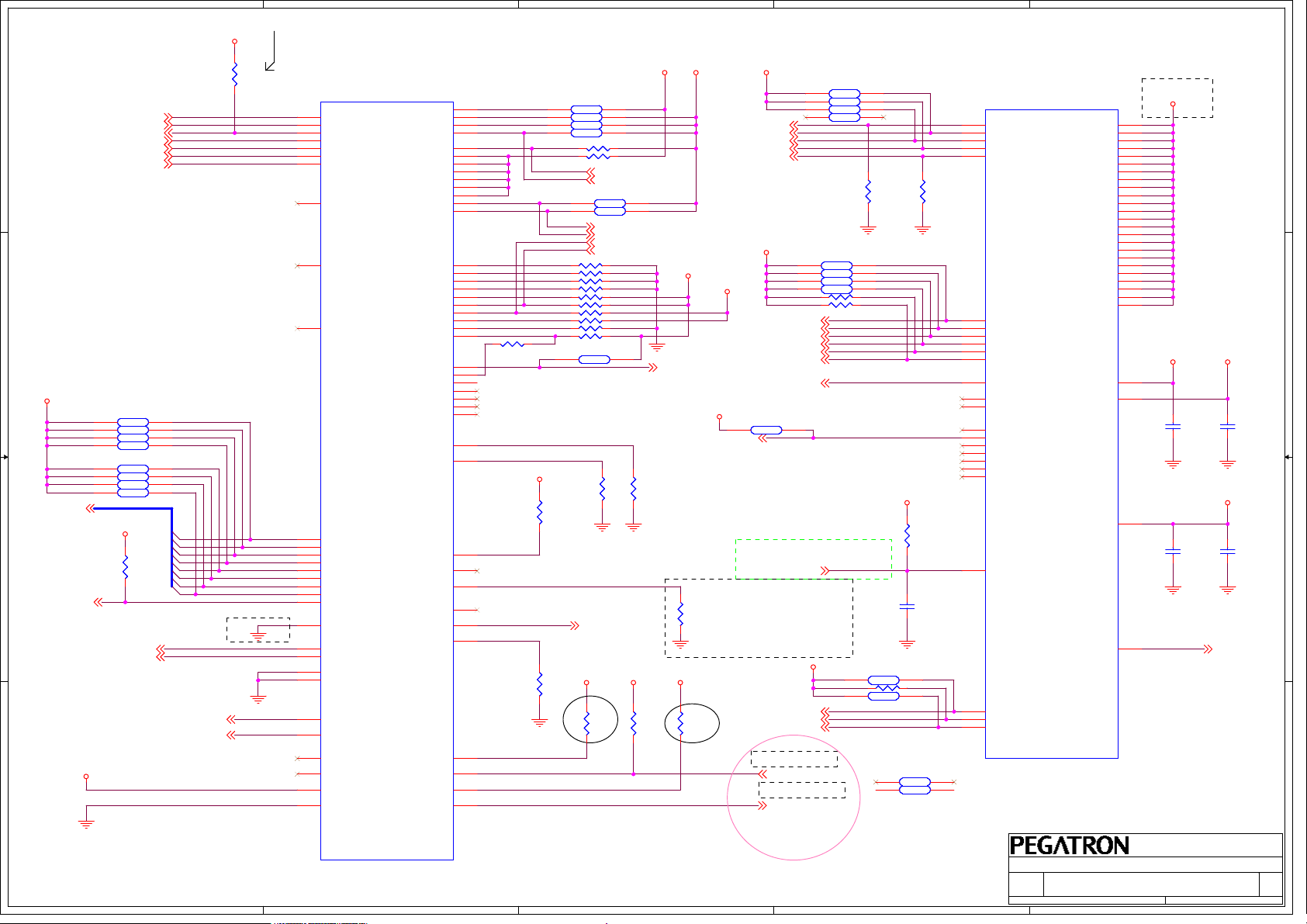

PLTRST#

GMCH

7

PWROK

PSON#

Power

Supply

6

PLTRST#_PCIEX16

PLTRST#_PCIEX1

5V

PWROK_PS

RST#_IDE

/X

5V Level

9

IDE

PCI Express X16

9

3.3V

PCI Express X1

9

3.3V

D D

User press

Ctrl+Alt+Del

User press

Power

button

PWRBTN#

Default

3

C C

Super IO

3.3V

RST_KB

8

3.3V

RSMRST#

2

PWROK

7

Buffer Out

4

5

5

SLP_S3#

SLP_S4#

IO_PWRBTN#

PCI slots

3.3V

3.3V

3.3V

3.3V

PLTRST#

8

8

3.3V

PCIRST#

User press

Reset

button

RSTCON#

Default

User

Clear

CMOS

RTCRST#

3.3V

3.3V

3.3V

1

3.3V

3.3V

3.3V

ICH7

B B

10

CPURST#

CPU

CPUPWRGD

HINIT#

Vcore

Vcore

FWHHINIT#

RTL8111C

3.3V

FWH

3.3V

3.3V

3.3V

3.3V

8

8

8

<Variant Name>

<Variant Name>

<Variant Name>

8

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPM41-D3

IPM41-D3

IPM41-D3

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

Power Sequence

Power Sequence

Power Sequence

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

1.00G

1.00G

2 55Thursday, July 09, 2009

2 55Thursday, July 09, 2009

2 55Thursday, July 09, 2009

1.00G

Rev

Rev

Rev

A

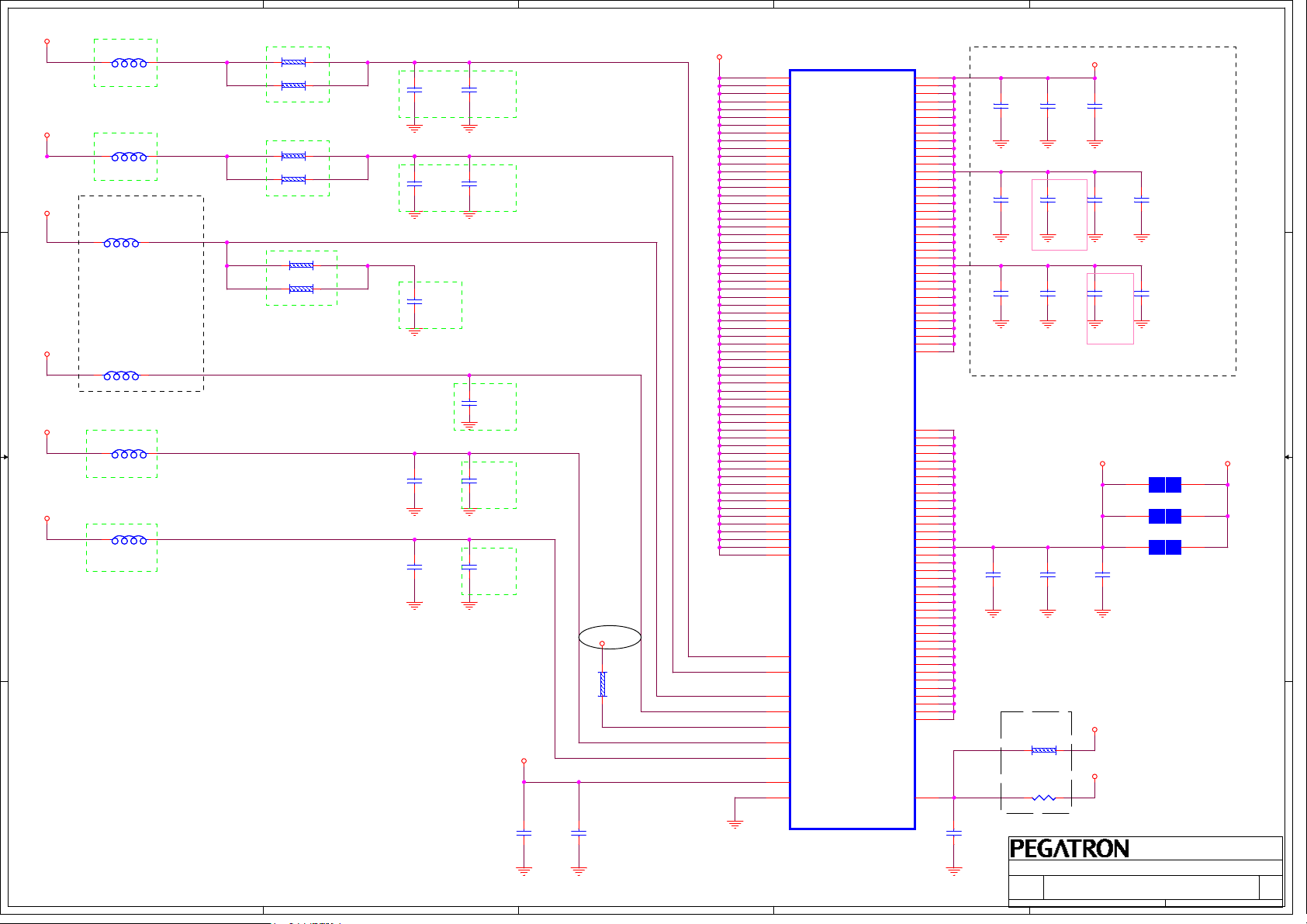

Page 3

5

A

4

3

2

1

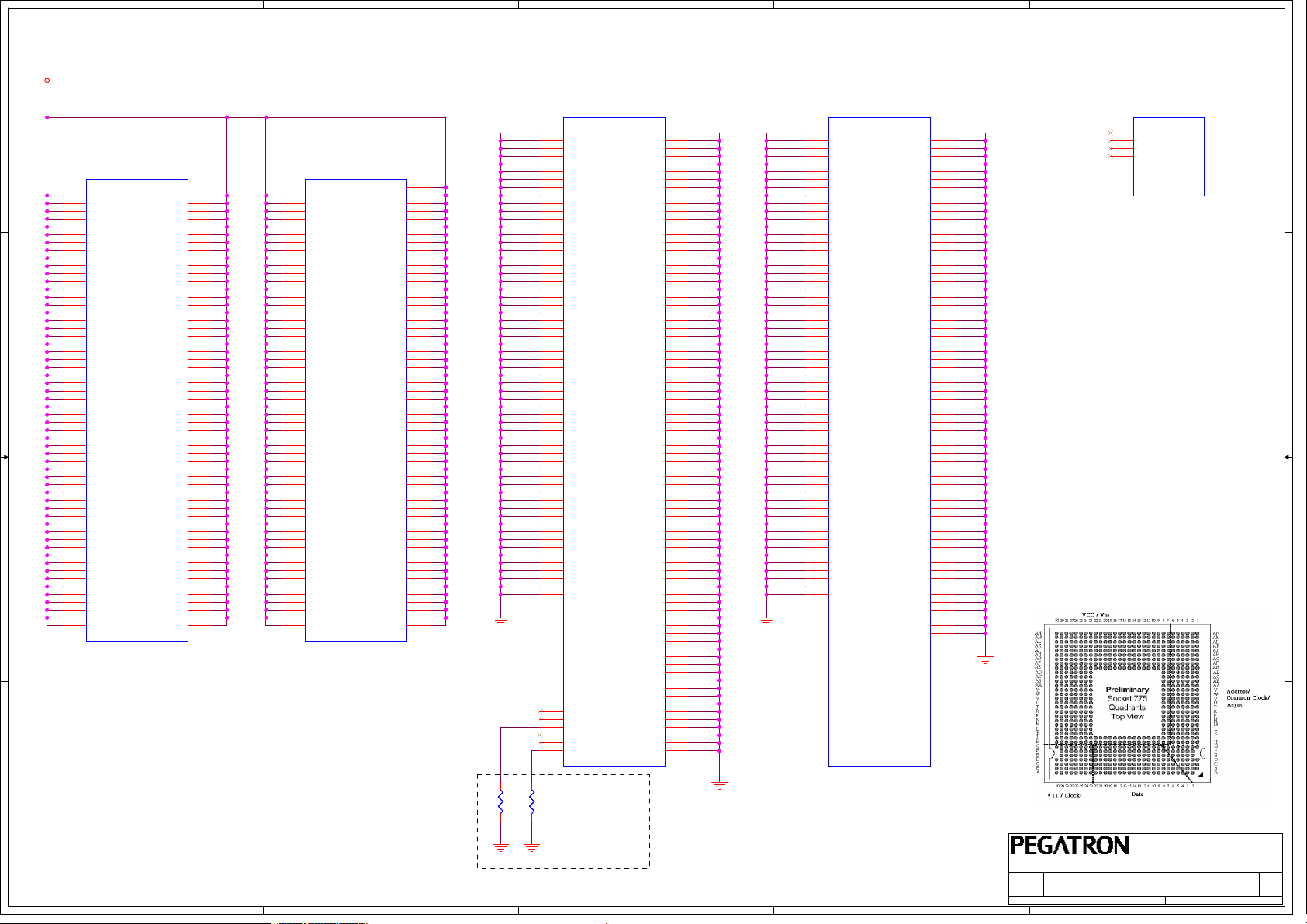

ATX12V

ISL6312

3.5Phases

I max.=125A.

TDC: 100A.

D D

S0

VCORE_EN

TDP:65W.(05A)

VCORE

ATXPWR

+5VSB

L1085DG

S0/S3/S5

L1117LG

S0/S3/S5

+3VSB

LAN_2.5V

Io: 2A

Io: 260mA

L1117LG

S0/S3/S5

LAN_1.5V

+3VDUAL

Io: 380mA

Io

S0: 500mA

S3: 12mA

AME1117ACGTZ

C C

+5V

APM9932CKC

+

AP2306GN

S3/S5:+5VSB

S0:+5V

+5V_DUAL

S0/S3/S5

Switch

APW7120KE_TRL

S0/S1/S3

+1.8V_DUAL

Io

S0/S1: 14A

LM324DR+

AP60T03H*2

S0

Io: >10.4A

+1.5V

S3: 425mA

LM324DR

+P3055LDG

S0

+3.3V

LM324DR+7002

S0

+2.5V_DAC

Io: 70mA

LM324DR

+P3055LDG

B B

LM324DR+7002

S0

VR_ProtHot

S0

Io: 6A

+VTT_CPU

Io: 1.31A

+1.05V

CM8562PGISTR VTT_DDR

S0/S3

Io

S0: 1.2A

S3: 420mA

NOTE:

Linear REG

1.00G

1.00G

1.00G

Rev

Rev

Rev

A

<Variant Name>

<Variant Name>

Switch REG

<Variant Name>

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPM41-D3

IPM41-D3

IPM41-D3

Engineer:

Power Flow

Power Flow

Power Flow

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

3 55Thursday, July 09, 2009

3 55Thursday, July 09, 2009

3 55Thursday, July 09, 2009

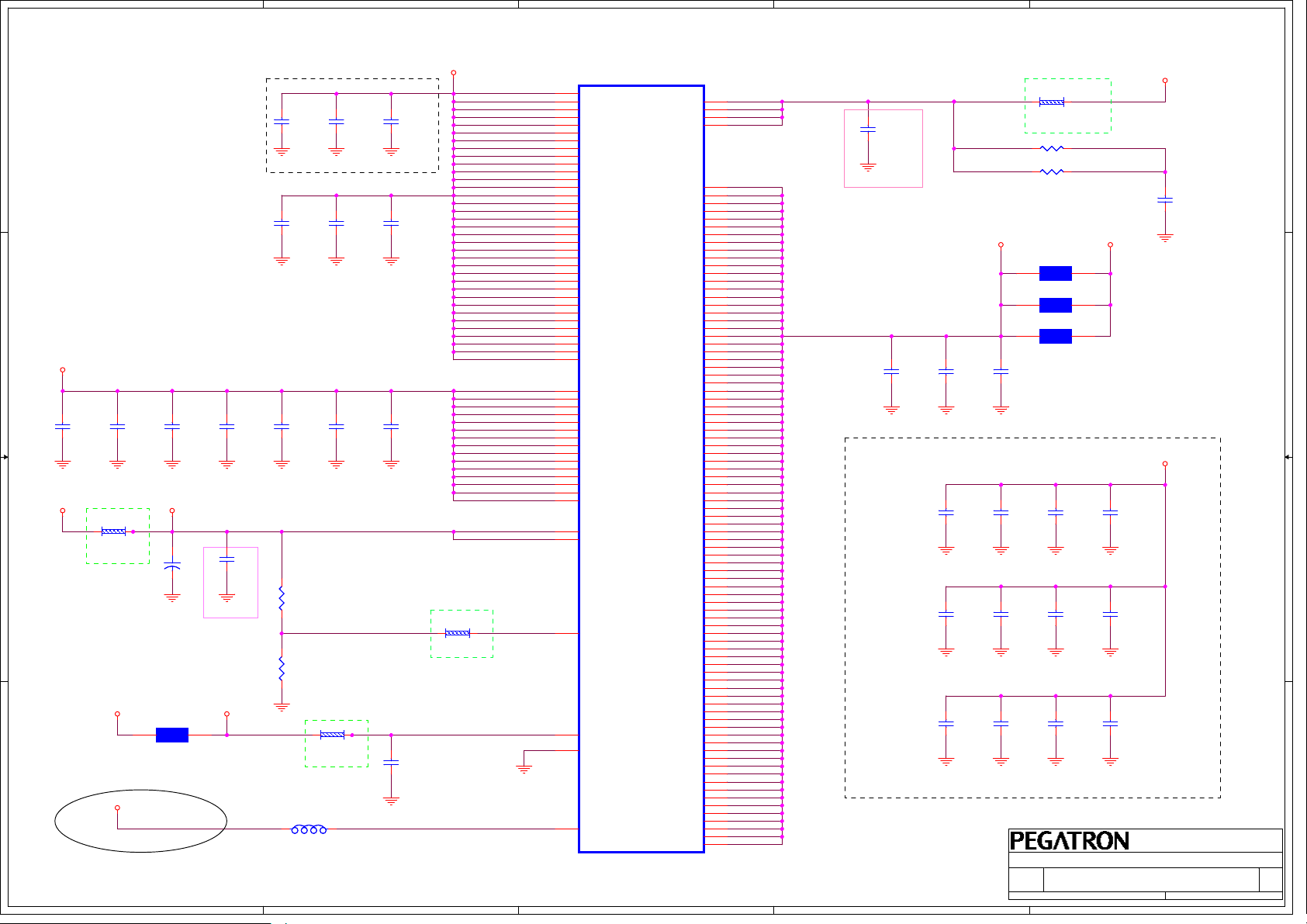

Page 4

5

A

4

3

2

1

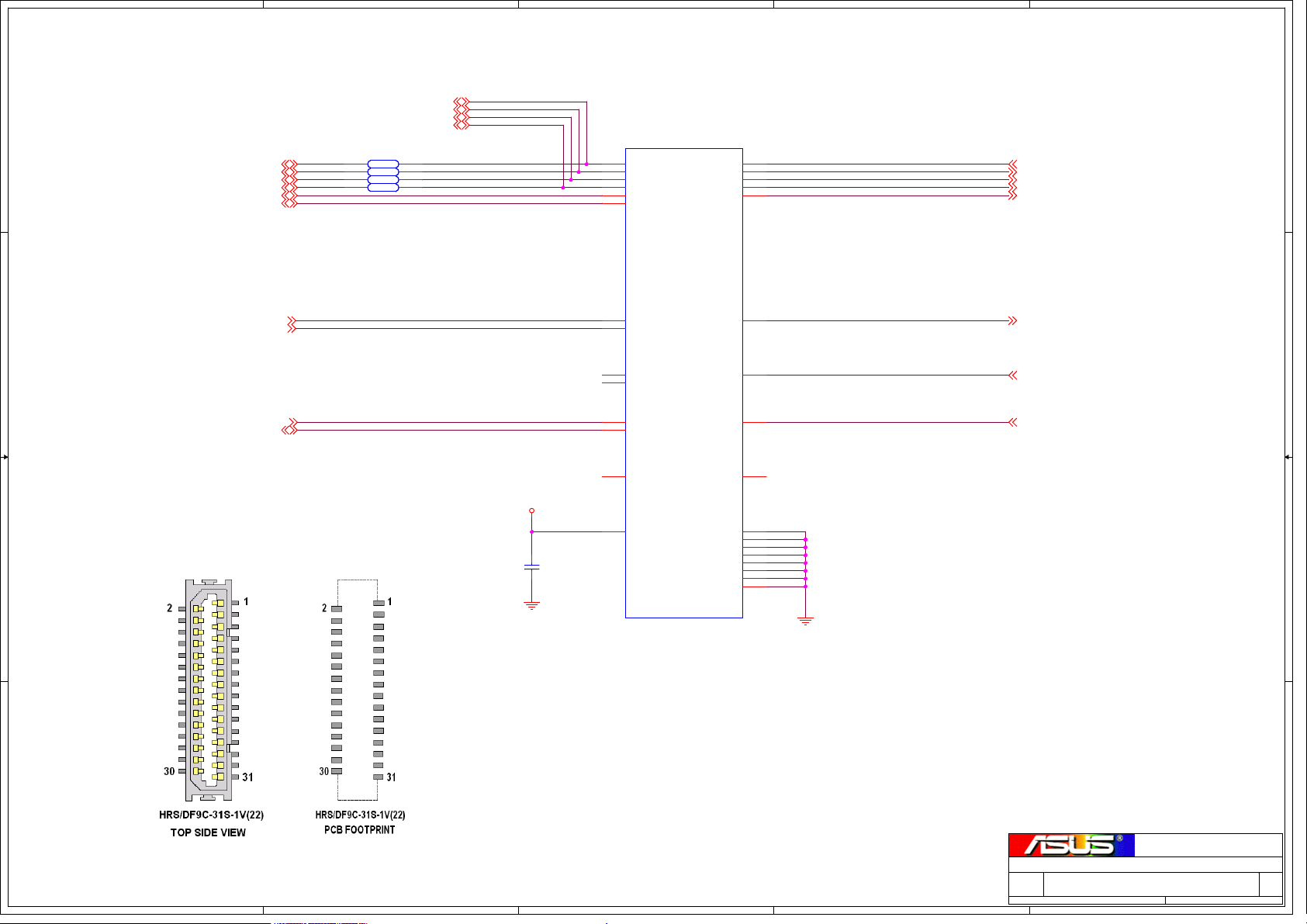

133/200/266 MHz

CK_FSB_CPU/#

CPU

ICS

D D

9LPRS552AGLF_T

133/200/266 MHz

100 MHz

96 MHz

CK_FSB_NB/#

CK_100M_MCH/#

CK_96M_DREF/#

MCH

Lakeport

CK_100M_PCIEX16/#100 MHz

PCIEX16

14.318 MHz

XTAL

100 MHz

100 MHz

C C

33 MHz

14.318 MHz

48 MHz CK_48M_SIO

CK_100M_ICH/#

CK_100M_SATA/#

CK_48M_USB48 MHz

CK_33M_ICH

CK_14M_ICH

CK_33M_SIO33 MHz

ICH7

Super I/O

33 MHz

B B

33 MHz

CK_PCI_TPM

TCM

CK_33M_SL133 MHz

PCI SLOT 1

33 MHz

CK_33M_SL2

PCI SLOT 2

CK_PCIE_SLOT1/#100 MHz

PCIEX1_1

100 MHz

CK_100M_LAN/#

LAN

<Variant Name>

<Variant Name>

<Variant Name>

Clock Distribution

Clock Distribution

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IPM41-D3

IPM41-D3

IPM41-D3

Engineer:

Clock Distribution

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

4 55Thursday, July 09, 2009

4 55Thursday, July 09, 2009

4 55Thursday, July 09, 2009

1.00G

1.00G

1.00G

Rev

Rev

Rev

A

Page 5

5

I

+3P3VSB

+3P3V

D D

I

CKL1

CKL1

600Ohm/100Mhz/0.5A

600Ohm/100Mhz/0.5A

mx_l0603

mx_l0603

21

NI

NI

CKL2

CKL2

600Ohm/100Mhz/0.5A

600Ohm/100Mhz/0.5A

mx_l0603

mx_l0603

21

+CLKVCC3

12

I

I

CKCB2

CKCB2

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

NOTE:

CKR2 CKR10

4

I

I

CKCB3

CKCB3

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

12

GND

PIN17 PIN18

25MHzI NI

24.576MHz

I

I

CKCB4

CKCB4

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

12

I

I

CKCB5

CKCB5

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

VDDPCI

VDD_PLL3

VDD_SRC

VDDCPU

VDDREF

+CLKVCC3

12

I

I

CKR2

CKR2

10K

10K

12

I

I

CKCB6

CKCB6

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GNDGND

GND

VOUT_VDDIO

I

I

CRITICAL

CRITICAL

CKU2

CKU2

2

VDD_PCI

16

VDD_PLL3

31

VDD_SRC

47

VDD_CPU

53

VDD_REF

8

VSS_PCI

23

VSS_SRC1

34

VSS_SRC2

44

VSS_CPU

50

VSS_REF

40

SEL_24.576MHz

3

CPU_0

CPU_0#

CPU_1_AMT

CPU_1_AMT#

SRC_8/CPU_ITP

SRC_8#/CPU_ITP#

SRC_7

SRC_7#

SRC_6

SRC_6#

PCI_STOP#/SRC_5

CPU_STOP#SRC_5#

SRC_4

SRC_4#

SRC_3

SRC_3#

SRC_2

SRC_2#

25MHz_0_F

25MHz_1/24.576MHz

SRC_0/DOT_96

SRC_0#/DOT_96#

2

46

45

43

42

39

38

36

35

33

32

30

29

27

28

24

25

21

22

17

18

13

14

1 2

CKR1

CKR1

I

I

33

33

8/19 modify

CPUHCLK [6]

CPUHCLK# [6]

CK_FSB_NB [10]

CK_FSB_NB# [10]

CK_ITP [9]

CK_ITP# [9]

CK_100M_ICH [20]

CK_100M_ICH# [20]

CK_100M_PCIEX16 [24]

CK_100M_PCIEX16# [24]

CK_100M_PCIEX1 [25]

CK_100M_PCIEX1# [25]

CK_100M_MCH [10]

CK_100M_MCH# [10]

CK_100M_LAN [32]

CK_100M_LAN# [32]

CK_100M_SATA [20]

CK_100M_SATA# [20]

CK_25M_LAN [32]

CK_96M_DREF [13]

CK_96M_DREF# [13]

1

NOTE:

SRC[3 4 6 and 7] are

designated for PCIe GEN2,

must be used for GMCH and

PCIe Gen2 slot

NOTE:

PIN [29 30] tie to ICH

through 1K ohm if iAMT support

(PCI_STOP#, CPU_STOP#),

Strap SRC5 disable

C C

12

I

I

CKCB9

CKCB9

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

I

I

CKCB12

CKCB12

10UF/6.3V

10UF/6.3V

X5R 10%

X5R 10%

mx_c0805

mx_c0805

12

12

I

I

CKCB13

CKCB13

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

12

I

I

CKC8

CKC8

33PF/50V

33PF/50V

NPO 5%

NPO 5%

GND GND GND

12

NI

NI

CKC10

CKC10

33PF/50V

33PF/50V

NPO 5%

NPO 5%

GND

4

12

PCB40

PCB40

PCB

PCB

PCB_BOARD

PCB_BOARD

I

I

B B

VRMPWRGD_ICH[21,51]

A A

SMB_CLK_R[9,17,18,21,24,25,28,29]

SMB_DATA_R[9,17,18,21,24,25,28,29]

5

GND

+CLKVCC3

VRMPWRGD_ICH

12

NI

NI

CKCB11

CKCB11

10UF/6.3V

10UF/6.3V

X5R 10%

X5R 10%

mx_c0805

mx_c0805

GND GND

I

I

CKCB14

CKCB14

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

I

I

CKCB18

CKCB18

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

I

I

Y1

Y1

14.318Mhz

14.318Mhz

1 2

1 2

GND

GND

3

3

GND

12

GNDGND

12

NI

NI

CKC11

CKC11

33PF/50V

33PF/50V

NPO 5%

NPO 5%

I

I

CKCB15

CKCB15

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

12

VDD_IO_96

+VDD_IO

12

I

I

CKCB16

CKCB16

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

VDD48_BW

GND

OSC_CK14M_XTALIN

OSC_CK14M_XTALOUT

I

I

CKC9

CKC9

33PF/50V

33PF/50V

NPO 5%

NPO 5%

GND

12

VDD_I/O_3.3

20

VDD_PLL3_I/O

26

VDD_SRC_I/O1

37

VDD_SRC_I/O2

41

VDD_CPU_I/O

19

VSS_PLL3

15

VSS_I/O

9

VDD_48

11

VSS_48

48

CKPWRGD/PD#

52

XTAL_IN

51

XTAL_OUT

56

SCL

55

SDA

SLG8XP548T

SLG8XP548T

ITP_EN/PCI_5

PCI_4/SRC_5_EN

FS_A/48MHz_0

FS_B/TEST_MODE

REF/FS_C/TEST_SEL

3

PCIF5/ITP_EN(Pin7):

1: CPU_ITP

PCI4/SRC5_EN(Pin6):

1: SRC5 Output

7

6

5

PCI_3

4

PCI_2

3

PCI_1

1

PCI_0

PCI3/CFG0(Pin5):

Strap for SATA PLL

1: PLL2, SS OFF

PCI2/TME(Pin4):

1: SR enable

10

49

54

RCK_33M_ICH

CK_33M_PCI4

RCK_33M_TPM

RCK_33M_SL2

RCK_33M_SL1

RCK_33M_SIO

RCK_48M_USB

FSLB

RCK_14M_ICH

1 2

+CLKVCC3

I

I

CKRN1A

CKRN1A

4.7KOHM

4.7KOHM

5%

5%

CKRN1B

CKRN1B

4.7KOHM

4.7KOHM

3 4

CKRN2A

CKRN2B

CKRN2C

CKRN2D

I

I

I

I

CKRN1C

CKRN1C

CKRN1D

CKRN1D

4.7KOHM

4.7KOHM

4.7KOHM

5%

5%

5 6

4.7KOHM

5%

5%

5%

5%

7 8

CKR42 22

CKR42 22

I

I

CKR40 22

CKR40 22

I

I

CKR39 33

CKR39 33

I

I

NOTE:

Single End damping resistor

Single Load => 33 OHM

Double Load => 22 OHM

2

1 2

33 Ohm

33 Ohm

3 4

33 Ohm

33 Ohm

5 6

33 Ohm

33 Ohm

7 8

33 Ohm

33 Ohm

I

I

1 2

1 2

1 2

NOTE:

PCIF_5 is dedicated for ICH

5%I CKRN2A

5%I

5%I CKRN2B

5%I

5%I CKRN2C

5%I

5%I CKRN2D

5%I

1 2

CKR34

CKR34

I

I

CKRN3A

I CKRN3A

I

CKRN3C

I CKRN3C

I

CKRN3B

I CKRN3B

I

33

33

12

12

NI

NI

CKC3

CKC3

10PF/50V

10PF/50V

NPO 5%

NPO 5%

GND GND GND GND GND

1 2

1KOHM

1KOHM

5 6

1KOHM

1KOHM

3 4

1KOHM

1KOHM

PCI4 is for the shortest route

PCI0 is for the longest route

8/27 modify

12

12

NI

NI

NI

NI

CKC5

CKC5

CKC4

CKC4

10PF/50V

10PF/50V

10PF/50V

10PF/50V

NPO 5%

NPO 5%

NPO 5%

NPO 5%

5%

5%

5%

5%

5%

5%

I

I

CKC6

CKC6

10PF/50V

10PF/50V

NPO 5%

NPO 5%

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPM41-D3

IPM41-D3

IPM41-D3

1

CK_33M_ICH [20]

CK_33M_TPM [37]

CK_33M_SL2 [29]

CK_33M_SL1 [28]

CK_33M_SIO [39]

12

NI

NI

CKC7

CKC7

10PF/50V

10PF/50V

NPO 5%

NPO 5%

M_HBSEL0 [7,13]

CK_48M_SIO [39]

CK_48M_USB [20]

M_HBSEL1 [7,13]

CK_14M_ICH [21]

M_HBSEL2 [7,13]

CLOCK CK505

CLOCK CK505

CLOCK CK505

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

5 55Thursday, July 09, 2009

5 55Thursday, July 09, 2009

5 55Thursday, July 09, 2009

Rev

Rev

Rev

1.00G

1.00G

1.00G

Page 6

5

I

I

XU1A

XU1A

SOCKET775/ATX

HA#[3..35][10]

HA#3

HA#4

HA#5

HA#6

HRS#2

HRS#1

HRS#0

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35

D D

HREQ#[0..4][10]

HADSTB0#[10]

C C

B B

HA#[3..35][10]

HADSTB1#[10]

HRS#[0..2][10]

SOCKET775/ATX

L5

A03#

P6

A04#

M5

A05#

L4

A06#

M4

A07#

R4

A08#

T5

A09#

U6

A10#

T4

A11#

U5

A12#

U4

A13#

V5

A14#

V4

A15#

W5

A16#

K4

REQ0#

J5

REQ1#

M6

REQ2#

K6

REQ3#

J6

REQ4#

R6

ADSTB0#

N4

RSVD1

P5

RSVD2

AB6

A17#

W6

A18#

Y6

A19#

Y4

A20#

AA4

A21#

AD6

A22#

AA5

A23#

AB5

A24#

AC5

A25#

AB4

A26#

AF5

A27#

AF4

A28#

AG6

A29#

AG4

A30#

AG5

A31#

AH4

A32#

AH5

A33#

AJ5

A34#

AJ6

A35#

AD5

ADSTB1#

AC4

RSVD3

AE4

RSVD4

A3

RS2#

F5

RS1#

B3

RS0#

ADS#

BNR#

HIT#

RSP#

BPRI#

DBSY#

DRDY#

HITM#

IERR#

INIT#

LOCK#

TRDY#

BINIT#

DEFER#

MCERR#

AP0#

AP1#

DP0#

DP1#

DP2#

DP3#

BR0#

GTLREF1

GTLREF0

GTLREF2

GTLREF3

4

+1P1V_FSB_VTT

12

I

I

HR1

HR1

62

62

D2

C2

D4

H4

G8

B2

C1

E4

HIERR#

AB2

P3

C3

E3

AD3

G7

AB3

U2

U3

J16

H15

H16

J17

F3

H2

CPU_GTLREF0

H1

NJP4

NJP4

SHORTPIN_RECT

SHORTPIN_RECT

NOBOM

NOBOM

1 2

F2

G10

RMA1

RMA1

NOBOM

NOBOM

SMD4X25_NP

SMD4X25_NP

RMA1 is soldermask on trace for RMA

1

purpose. Place on suitable location where

1

can be easily reached by Probe

HADS# [10]

HBNR# [10]

HIT# [10]

HBPRI# [10]

HDBSY# [10]

HDRDY# [10]

HITM# [10]

HINIT# [20]

HLOCK# [10]

HTRDY# [10]

HDEFER# [10]

+VTT_OUT_L

12

I

I

HR2

HR2

62

62

I

I

HR5

HR5

10

12

NI

NI

HCB2

HCB2

220PF/50V

220PF/50V

X7R 10%

X7R 10%

10

I

I

HR6

HR6

10

10

12

12

12

CPU_GTLREF0_R

I

I

HCB3

HCB3

1UF/10V

1UF/10V

mx_c0603

mx_c0603

CPU_GTLREF1 CPU_GTLREF1_R

12

NI

NI

HCB1

HCB1

220PF/50V

220PF/50V

X7R 10%

X7R 10%

GND GND GNDGND

NOTE:

Place near CPU

NJP5

NJP5

SHORTPIN_RECT

SHORTPIN_RECT

NOBOM

NOBOM

1 2

12

I

I

HCB4

HCB4

1UF/10V

1UF/10V

mx_c0603

mx_c0603

3

HBREQ0# [10]

+VTT_OUT_L

12

12

I

I

HR4

HR4

57.6

57.6

1%

1%

I

I

HR8

HR8

100

100

1%

1%

+VTT_OUT_L

12

I

I

HR3

HR3

57.6

57.6

1%

1%

12

I

I

HR7

HR7

100

100

1%

1%

GNDGND

2

I

I

XU1B

XU1B

SOCKET775/ATX

SOCKET775/ATX

HD#[0..63][10]

HDBI0#[10]

HDSTBN0#[10]

HDSTBP0#[10]

HD#[0..63][10] HD#[0..63] [10]

HDBI1#[10]

HDSTBN1#[10]

HDSTBP1#[10]

HD#0

B4

A10

A11

B10

C11

B12

C12

D11

E10

D10

F11

F12

D13

E13

G13

F14

G14

F15

G15

G11

G12

E12

D00#

C5

D01#

A4

D02#

C6

D03#

A5

D04#

B6

D05#

B7

D06#

A7

D07#

D08#

D09#

D10#

D11#

D8

D12#

D13#

D14#

D15#

A8

DBI0#

C8

DSTBN0#

B9

DSTBP0#

G9

D16#

F8

D17#

F9

D18#

E9

D19#

D7

D20#

D21#

D22#

D23#

D24#

D25#

D26#

D27#

D28#

D29#

D30#

D31#

DBI1#

DSTBN1#

DSTBP1#

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7 HD#39

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

D32#

D33#

D34#

D35#

D36#

D37#

D38#

D39#

D40#

D41#

D42#

D43#

D44#

D45#

D46#

D47#

DBI2#

DSTBN2#

DSTBP2#

D48#

D49#

D50#

D51#

D52#

D53#

D54#

D55#

D56#

D57#

D58#

D59#

D60#

D61#

D62#

D63#

DBI3#

DSTBN3#

DSTBP3#

G16

E15

E16

G18

G17

F17

F18

E18

E19

F20

E21

F21

G21

E22

D22

G22

D19

G20

G19

D20

D17

A14

C15

C14

B15

C18

B16

A17

B18

C21

B21

B19

A19

A22

B22

C20

A16

C17

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

1

HD#[0..63] [10]

HDBI2# [10]

HDSTBN2# [10]

HDSTBP2# [10]

HDBI3# [10]

HDSTBN3# [10]

HDSTBP3# [10]

I

I

HR13

HR13

62

62

NI

NI

HC1

HC1

22PF/50V

22PF/50V

NPO 5%

NPO 5%

G28

G23

F28

BCLK0

BCLK1

RESET#

FC10

FC15

E24

H29

REV=1.3

REV=1.3

NOTE:

ICH_GPIOA

Default is 0.63*VTT

ICH_GPIOB

0

10

01

11

GTLREF

0.615*VTT0

0.65*VTT

0.63*VTT

0.67*VTT

COMMENTS

HQ1 off, HQ2 on

HQ3 off, HQ4 on

HQ1 off, HQ2 on

HQ3 on, HQ4 off

HQ1 on, HQ2 off

HQ3 off, HQ4 on

HQ1 on, HQ2 off

HQ3 on, HQ4 off

ASUS OEM-DT MB RESTRICTED SECRET

REV=1.3

REV=1.3

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

4

3

2

Date: Sheet of

Engineer:

IPM41-D3

IPM41-D3

IPM41-D3

INTEL LGA-775 1 - 3

INTEL LGA-775 1 - 3

INTEL LGA-775 1 - 3

Title :

Title :

Title :

1

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

6 55Thursday, July 09, 2009

6 55Thursday, July 09, 2009

6 55Thursday, July 09, 2009

Rev

Rev

Rev

1.00G

1.00G

1.00G

CPUHCLK[5]

CPUHCLK#[5]

+VTT_OUT_R

12

A A

CPURESET#[9,10,51]

12

GND

5

Page 7

5

4

3

2

1

PLACE NEAR SB

+1P1V_FSB_VTT

12

I

I

HR17

HR17

62

62

D D

C C

+VTT_OUT_R

RCVID[0..7][46]

B B

VID_SELECT[46]

+VCORE

A A

SMI#[20]

A20M#[20]

HFERR#[20]

INTR[20]

NMI[20]

IGNNE#[20]

STPCLK#[20]

NOTE:

The VCCIO PLL Filter Circuit is no longer

needed since Conroe CPU

HRN1D

HRN1D

680

680

HRN1C

HRN1C

680

680

HRN1B

HRN1B

680

680

HRN1A

HRN1A

680

680

HRN2D

HRN2D

680

680

HRN2C

HRN2C

680

680

HRN2B

HRN2B

680

680

HRN2A

HRN2A

680

680

I

I

HR65

HR65

680

680

VCC_SENSE[46]

VSS_SENSE[46]

5

GND

I

I

7 8

I

I

5 6

I

I

3 4

I

I

1 2

I

I

7 8

I

I

5 6

I

I

3 4

I

I

1 2

+VTT_OUT_R

TRD_CPU_P[38]

TRD_CPU_N[38]

12

RCVID0

RCVID1

RCVID2

RCVID3

RCVID4

RCVID5

RCVID6

RCVID7

VID_SELECT

GND

GND

I

I

XU1C

XU1C

SOCKET775/ATX

SOCKET775/ATX

P2

SMI#

K3

A20M#

R3

FERR#/PBE#

K1

LINT0

L1

LINT1

N2

IGNNE#

M3

STPCLK#

A23

VCCA

B23

VSSA

C23

VCCIOPLL

AM2

VID0

AL5

VID1

AM3

VID2

AL6

VID3

AK4

VID4

AL4

VID5

AM5

VID6

AM7

VID7

AN7

VID_SECECT

AE8

SKTOCC#

AL1

THERMDA

AK1

THERMDC

AJ7

VSS_AJ7

AH7

VSS_AH7

AN5

VCC_MB_REGULATION

AN6

VSS_MB_REGULATION

AN3

VCC_SENSE

AN4

VSS_SENSE

AL8

VCC_D_SENSE

AL7

VSS_D_SENSE

REV=1.3

REV=1.3

TESTHI00

TESTHI01

TESTHI10

TESTHI11

TESTHI13

TESTHI02

TESTHI03

TESTHI04

TESTHI05

TESTHI06

TESTHI07

TESTHI08

TESTHI09

TESTHI12

BOOTSELECT

FORCEPR#

PWRGOOD

PROCHOT#

THERMTRIP#

4

COMP0

COMP1

COMP2

COMP3

COMP4

COMP5

COMP6

COMP7

COMP8

RSVD33

RSVD34

RSVD35

RSVD36

RSVD12

RSVD21

RSVD9

MSID0

MSID1

LL_ID1

LL_ID0

PECI

IMPSEL

TESTHI0

F26

TESTHI1

W3

TESTHI10

H5

TESTHI11

P1

TESTHI13

L2

TESTHI2_7

F25

G25

G27

G26

G24

F24

TESTHI8

G3

TESTHI9

G4

HCOMP0

A13

HCOMP1

T1

HCOMP2

G2

HCOMP3

R1

HCOMP4

J2

DPRSTP#

T2

CPU_PSI

Y3

HCOMP7

AE3

HCOMP8

B13

TESTHI12

W2

HR48

HR48

NI

NI

G1

U1

A24

E29

AH2

G6

F29

MSID0

W1

MSID1

V1

CPU_LL_ID1

AA2

V2

CPU_BOOT

Y1

AL3

NC

PECI_CPU

G5

IMPSEL_F6

F6

HFORCEPH#

AK6

CPUPWRGD

N1

PROCHOT#

AL2

H_THMTRIP#

M2

THERMALTRIP# NEED A PULL UP RESISTOR NEAR SB

0.05 IHRN3A

0.05 I

1 2

0.05 IHRN3B

0.05 I

3 4

0.05 IHRN3C

0.05 I

5 6

0.05 IHRN3D

0.05 I

7 8

HR24 51

HR24 51

I

I

HR23 51

HR23 51

I

I

HR49 49.9 1%

HR49 49.9 1%

I

I

HR46 49.9 1%

HR46 49.9 1%

I

I

HR28 49.9 1%

HR28 49.9 1%

I

I

HR33 49.9 1%

HR33 49.9 1%

I

I

HR32 49.9 1%

HR32 49.9 1%

NI

NI

HR37 49.9 1%

HR37 49.9 1%

I

I

HR36 49.9 1%

HR36 49.9 1%

I

I

HR47 49.9 1%

HR47 49.9 1%

NI

NI

HR39 24.9 1%

HR39 24.9 1%

I

I

HR21 51

HR21 51

I

I

0

0

12

0.05 IHRN6C

0.05 I

+VTT_OUT_L

12

NI

NI

HR53

HR53

62

62

12

I

I

HR56

HR56

51

51

GND

51OHM

51OHM

51OHM

51OHM

51OHM

51OHM

51OHM

51OHM

0.05 IHRN6A

0.05 I

0.05 IHRN6B

0.05 I

1 2

1 2

1 2

1 2

1 2

5 6

+VTT_OUT_R +VTT_OUT_L +VTT_OUT_R

+1P1V_FSB_VTT

HRN3A

HRN3B

HRN3C

HRN3D

12

12

PM_SLP# [13,20 ]

DPSLP# [21]

1 2

51OHM

51OHM

3 4

51OHM

51OHM

H_BPM2_2 [9]

H_BPM3_2 [9]

CPU_PSI [51]

DPRSTP# [13]

12

12

12

12

12

HRN6C

51OHM

51OHM

12

NI

NI

HR50

HR50

51

51

GND

GND

PECI_CPU [38]

12

I

I

HR61

HR61

130

130

1%

1%

HRN6A

HRN6B

12

12

NI

NI

HR51

HR51

51

51

NI

NI

HR62

HR62

100

100

+VTT_OUT_L

GND

H_BPM0_2 [9]

12

GND

12

3

+VTT_OUT_L

+VTT_OUT_L

+VTT_OUT_R

TRST#[9]

+VTT_OUT_R

+VTT_OUT_R

0.05 IHRN6D

0.05 I

7 8

51OHM

51OHM

H_BPM1_2[9]

TCK[9]

TDI[9]

TDO[9]

TMS[9]

I

I

I

I

BPM0#[9 ]

BPM1#[9 ]

BPM2#[9 ]

BPM3#[9 ]

BPM4#[9 ]

BPM5#[9 ]

SYS_RESET#[9,21,38,44]

HRN6D

Check PWM controller

VRMPWRGD[46,51]

BOOTSELECT:

I

I

Install PD resistor to

HR55

HR55

51

51

prevent PSC SMF CDM PSL

CPU from booting

+1P1V_FSB_VTT

I

I

HR63

HR63

130

130

1%

1%

M_HBSEL0[5,13]

M_HBSEL1[5,13]

M_HBSEL2[5,13]

CPUPWRGD [9,21]

H_THMTRIP# [20]

9/8 modify

0.05 IHRN4A

0.05 I

1 2

0.05 IHRN4B

0.05 I

3 4

0.05 IHRN4C

0.05 I

5 6

0.05 IHRN4D

0.05 I

7 8

0.05 IHRN5A

0.05 I

1 2

0.05 IHRN5B

0.05 I

3 4

0.05 IHRN5C

0.05 I

5 6

0.05 IHRN5D

0.05 I

7 8

HR35 51

HR35 51

1 2

HR38 51

HR38 51

1 2

HRN4A

51OHM

51OHM

HRN4B

51OHM

51OHM

HRN4C

51OHM

51OHM

HRN4D

51OHM

51OHM

12

I

I

HR26

HR26

49.9

49.9

1%

1%

GND

HRN5A

51OHM

51OHM

HRN5B

51OHM

51OHM

HRN5C

51OHM

51OHM

HRN5D

51OHM

51OHM

5%I HRN7A

5%I

HR500 470 OHM 5% IHR500 470 OHM 5% I

1 2

470 OHM

470 OHM

5%I

5%I

1 2

5 6

470 OHM

470 OHM

06/20 modify

5%I HRN7D

5%I

5%I HRN7B

5%I

I

I

XU1D

XU1D

SOCKET775/ATX

SOCKET775/ATX

AE1

TCK

AD1

TDI

AF1

TDO

AC1

TMS

AG1

HRN7D

HRN7B

AJ2

AJ1

AD2

AG2

AF2

AG3

AC2

AK3

AJ3

AE6

D16

A20

E23

AM6

G29

H30

G30

N5

C9

E7

TRST#

BPM0#

BPM1#

BPM2#

BPM3#

BPM4#

BPM5#

DBR#

ITPCLK<0>

ITPCLK<1>

RSVD17

RSVD18

RSVD19

RSVD20

RSVD22

RSVD23

RSVD31

VTTPWRGD

BSEL0

BSEL1

BSEL2

REV=1.3

REV=1.3

VTT10

VTT11

VTT12

VTT13

VTT14

VTT15

VTT16

VTT17

VTT18

VTT19

VTT20

VTT21

VTT22

VTT23

VTT24

VTT_OUT1

VTT_OUT2

VCC_PLL

VTT_SEL

12

I

I

HR27

HR27

49.9

49.9

1%

1%

GND

+VTT_OUT_R +CPU_VCCPLL

12

I

I

HR52

HR52

680

680

12

NI

NI

HC2

HC2

100PF/50V

100PF/50V

NPO 5%

NPO 5%

GND

HRN7A

HRN7C

HRN7C

7 8

470 OHM

470 OHM

3 4

470 OHM

470 OHM

ASUS OEM-DT MB RESTRICTED SECRET

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

NOTE:

FSB_VTT Net Name changed

+1P1V_FSB_VTT

A29

VTT1

B25

VTT2

B29

VTT3

B30

VTT4

C29

VTT5

A26

VTT6

B27

VTT7

C28

VTT8

A25

VTT9

A28

A27

C30

A30

C25

C26

C27

B26

D27

D28

D25

D26

B28

D29

D30

+VTT_OUT_R

AA1

J1

12

GND GND

D23

12

F27

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPM41-D3

IPM41-D3

IPM41-D3

1

+VTT_OUT_L

12

NI

NI

NI

HCB13

HCB13

0.1UF/16V

0.1UF/16V

I

I

HCB14

HCB14

0.01UF/25V

0.01UF/25V

X7R 10%

X7R 10%

INTEL LGA-775 2 - 3

INTEL LGA-775 2 - 3

INTEL LGA-775 2 - 3

NI

HCB12

HCB12

0.1UF/16V

0.1UF/16V

12

NI

NI

HCB15

HCB15

10UF/6.3V

10UF/6.3V

X5R 10%

X5R 10%

mx_c0805

mx_c0805

GNDGND

VTT_SELECT [50]

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

7 55Thursday, July 09, 2009

7 55Thursday, July 09, 2009

7 55Thursday, July 09, 2009

Rev

Rev

Rev

1.00G

1.00G

1.00G

Page 8

5

4

3

2

1

+VCORE

D D

I

AM15

AM18

AM19

AM21

AM22

AM25

AM26

AM29

AM30

AM8

AM9

AN11

AN12

AN14

AN15

AN18

AN19

AN21

AN22

AN25

AN26

AN29

AN30

AN8

AN9

K30

K29

K28

K27

K26

K25

K24

K23

J10

J11

J12

J13

J14

J15

J18

J19

J20

J21

J22

J23

J24

J25

J26

J27

J28

J29

J30

J8

J9

K8

Y8

I

XU1F

XU1F

SOCKET775/ATX

SOCKET775/ATX

VCC113

VCC114

VCC115

VCC116

VCC117

VCC118

VCC119

VCC120

VCC121

VCC122

VCC123

VCC124

VCC125

VCC126

VCC127

VCC128

VCC129

VCC130

VCC131

VCC132

VCC133

VCC134

VCC135

VCC136

VCC137

VCC138

VCC139

VCC140

VCC141

VCC142

VCC143

VCC144

VCC145

VCC146

VCC147

VCC148

VCC149

VCC150

VCC151

VCC152

VCC153

VCC154

VCC155

VCC156

VCC157

VCC158

VCC159

VCC160

VCC161

VCC162

VCC163

VCC164

VCC165

VCC166

VCC167

VCC168

REV=1.3

REV=1.3

VCC225

VCC224

VCC223

VCC222

VCC221

VCC220

VCC219

VCC218

VCC217

VCC216

VCC215

VCC214

VCC213

VCC212

VCC211

VCC210

VCC209

VCC208

VCC207

VCC206

VCC205

VCC204

VCC203

VCC202

VCC201

VCC200

VCC199

VCC198

VCC197

VCC196

VCC195

VCC194

VCC193

VCC192

VCC191

VCC190

VCC189

VCC188

VCC187

VCC186

VCC185

VCC184

VCC183

VCC182

VCC181

VCC180

VCC179

VCC178

VCC177

VCC176

VCC175

VCC174

VCC173

VCC172

VCC171

VCC170

VCC169

L8

M23

M24

M25

M26

M27

M28

M29

M30

M8

N23

N24

N25

N26

N27

N28

N29

N30

N8

P8

R8

T23

T24

T25

T26

T27

T28

T29

T30

T8

U23

U24

U25

U26

U27

U28

U29

U30

U8

V8

W23

W24

W25

W26

W27

W28

W29

W30

W8

Y23

Y24

Y25

Y26

Y27

Y28

Y29

Y30

4

GND

12

NI

NI

HR66

HR66

1K

1K

GND GND

I

I

XU1E

XU1E

SOCKET775/ATX

SOCKET775/ATX

AA8

VCC1

AB8

VCC2

AC23

VCC3

AC24

VCC4

AC25

VCC5

AC26

VCC6

AC27

VCC7

AC28

VCC8

AC29

VCC9

AC30

VCC10

AC8

VCC11

AD23

VCC12

AD24

VCC13

AD25

VCC14

AD26

VCC15

AD27

VCC16

AD28

VCC17

AD29

VCC18

AD30

VCC19

AD8

C C

B B

A A

AE11

AE12

AE14

AE15

AE18

AE19

AE21

AE22

AE23

AE9

AF11

AF12

AF14

AF15

AF18

AF19

AF21

AF22

AF8

AF9

AG11

AG12

AG14

AG15

AG18

AG19

AG21

AG22

AG25

AG26

AG27

AG28

AG29

AG30

AG8

AG9

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

REV=1.3

REV=1.3

5

VCC112

VCC111

VCC110

VCC109

VCC108

VCC107

VCC106

VCC105

VCC104

VCC103

VCC102

VCC101

VCC100

VCC99

VCC98

VCC97

VCC96

VCC95

VCC94

VCC93

VCC92

VCC91

VCC90

VCC89

VCC88

VCC87

VCC86

VCC85

VCC84

VCC83

VCC82

VCC81

VCC80

VCC79

VCC78

VCC77

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

AM14

AM12

AM11

AL9

AL30

AL29

AL26

AL25

AL22

AL21

AL19

AL18

AL15

AL14

AL12

AL11

AK9

AK8

AK26

AK25

AK22

AK21

AK19

AK18

AK15

AK14

AK12

AK11

AJ9

AJ8

AJ26

AJ25

AJ22

AJ21

AJ19

AJ18

AJ15

AJ14

AJ12

AJ11

AH9

AH8

AH30

AH29

AH28

AH27

AH26

AH25

AH22

AH21

AH19

AH18

AH15

AH14

AH12

AH11

I

I

XU1G

XU1G

SOCKET775/ATX

SOCKET775/ATX

AF28

VSS1

AF27

VSS2

AF26

VSS3

AF25

VSS4

AF24

VSS5

AF23

VSS6

AF20

VSS7

AF17

VSS8

AF16

VSS9

AF13

VSS10

AF10

VSS11

AE7

VSS12

AE5

VSS13

AE30

VSS14

AE29

VSS15

AE28

VSS16

AE27

VSS17

AE26

VSS18

AE25

VSS19

AE24

VSS20

AE20

VSS21

AE2

VSS22

AE17

VSS23

AE16

VSS24

AE13

VSS25

AE10

VSS26

AD7

VSS27

AD4

VSS28

AC7

VSS29

AC3

VSS30

AC6

VSS31

AB7

VSS32

AB30

VSS33

AB29

VSS34

AB28

VSS35

AB27

VSS36

AB26

VSS37

AB25

VSS38

AB24

VSS39

AB23

VSS40

AB1

VSS41

AA7

VSS42

AA6

VSS43

AA30

VSS44

AA3

VSS45

AA29

VSS46

AA28

VSS47

AA27

VSS48

AA26

VSS49

AA25

VSS50

A12

VSS51

A15

VSS52

A18

VSS53

A2

VSS54

A21

VSS55

A6

VSS56

A9

VSS57

AA23

VSS58

AA24

VSS59

AF29

VSS60

D1

RSVD27

D14

RSVD28

E5

RSVD29

E6

RSVD30

F23

RSVD37

J3

RSVD32

12

NI

NI

HR67

HR67

1K

1K

NOTE:

Intel ENG Feature

REV=1.3

REV=1.3

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

3

AF3

AF30

AF6

AF7

AG10

AG13

AG16

AG17

AG20

AG23

AG24

AG7

AH1

AH10

AH13

AH16

AH17

AH20

AH23

AH24

AH3

AH6

AJ10

AJ13

AJ16

AJ17

AJ20

AJ23

AJ24

AJ27

AJ28

AJ29

AJ30

AJ4

AK10

AK13

AK16

AK17

AK2

AK20

AK23

AK24

AK27

AK28

AK29

AK30

AK5

AK7

AL10

AL13

AL16

AL17

AL20

AL23

AL24

AL27

AL28

AM1

AM10

AM13

AM16

AM17

AM20

AM23

AM24

AM27

AM28

AM4

AN1

AN10

AN13

AN16

AN17

AN2

AN20

AN23

AN24

AN27

AN28

B1

GND

GND

I

I

XU1H

XU1H

SOCKET775/ATX

SOCKET775/ATX

B11

VSS141

B14

VSS142

B17

VSS143

B20

VSS144

B24

VSS145

B5

VSS146

B8

VSS147

C10

VSS148

C13

VSS149

C16

VSS150

C19

VSS151

C22

VSS152

C24

VSS153

C4

VSS154

C7

VSS155

D12

VSS156

D15

VSS157

D18

VSS158

D21

VSS159

D24

VSS160

D3

VSS161

D5

VSS162

D6

VSS163

D9

VSS164

E11

VSS165

E14

VSS166

E17

VSS167

E2

VSS168

E20

VSS169

E25

VSS170

E26

VSS171

E27

VSS172

E28

VSS173

E8

VSS174

F10

VSS175

F13

VSS176

F16

VSS177

F19

VSS178

F22

VSS179

F4

VSS180

F7

VSS181

H10

VSS182

H11

VSS183

H12

VSS184

H13

VSS185

H14

VSS186

H17

VSS187

H18

VSS188

H19

VSS189

H20

VSS190

H21

VSS191

H22

VSS192

H23

VSS193

H24

VSS194

H25

VSS195

H26

VSS196

H27

VSS197

H28

VSS198

H3

VSS199

H6

VSS200

REV=1.3

REV=1.3

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS238

VSS239

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS250

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

VSS258

VSS259

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

2

Y7

Y5

Y2

W7

W4

V7

V6

V30

V3

V29

V28

V27

V26

V25

V24

V23

U7

T7

T6

T3

R7

R5

R30

R29

R28

R27

R26

R25

R24

R23

R2

P7

P4

P30

P29

P28

P27

P26

P25

P24

P23

N7

N6

N3

M7

M1

L7

L6

L30

L3

L29

L28

L27

L26

L25

L24

L23

K7

K5

K2

J7

J4

H9

H8

H7

I

I

XU1I

XU1I

SOCKET775/ATX

SOCKET775/ATX

1

RM_POST_NC1

2

RM_POST_NC2

3

RM_POST_NC3

4

RM_POST_NC4

REV=1.3

REV=1.3

GND

ASUS OEM-DT MB RESTRICTED SECRET

INTEL LGA-775 3 - 3

INTEL LGA-775 3 - 3

INTEL LGA-775 3 - 3

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

Engineer:

IPM41-D3

IPM41-D3

IPM41-D3

1

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

8 55Thursday, July 09, 2009

8 55Thursday, July 09, 2009

8 55Thursday, July 09, 2009

Rev

Rev

Rev

1.00G

1.00G

1.00G

Page 9

5

4

3

2

1

INTEL LGA-775 PROCESSOR ITP DEBUG PORT

BPM0#[7]

BPM1#[7]

0 Ohm

0 Ohm

0 Ohm

0 Ohm

0 Ohm

0 Ohm

0 Ohm

0 Ohm

BPM2#[7]

BPM3#[7]

GRN1A

GRN1B

GRN1C

GRN1D

ITP_SMBDATA

XDP

XDP

9

BPM0#

7

BPM1#

6

BPM2#

4

BPM3#

3

BPM4#

1

BPM5#

13

BCLK0

15

BCKL1

16

GCLKp

18

GCLKn

22

SCL

24

SDA

PWRGOOD

TDO

TMS

TCK

TRST#

RESET#

DBR#

23

29

TDI

31

30

25

CPUPWRGD

10

CPURST_ITP#

19

MR_R#ITP_SMBCLK

21

TDO [7]

TDI [7]

TMS [7]

TCK [7]

TRST# [7]

CPUPWRGD [7,21]

CPURESET# [6,10,51]

SYS_RESET# [7,21,38,44]

D D

5%NI GRN1A

5%NI

H_BPM0_2[7]

H_BPM1_2[7]

H_BPM2_2[7]

H_BPM3_2[7]

BPM4#[7]

BPM5#[7]

CK_ITP[5]

CK_ITP#[5]

C C

SMB_CLK_R[5,17,18,21,24,25,28,29]

SMB_DATA_R[5,17,18,21,24,25,28,29]

1 2

5%NI GRN1B

5%NI

3 4

5%NI GRN1C

5%NI

5 6

5%NI GRN1D

5%NI

7 8

GND1

GND5

GND2

GND6

GND7

GND3

GND4

GND8

12

2

5

8

11

17

20

26

27

GND

28

NC

+VTT_OUT_R

14

VTT

12

NI/PROTO/ITP

NI/PROTO/ITP

GCB1

GND

GCB1

0.1UF/16V

0.1UF/16V

BtoB_CON_31P

BtoB_CON_31P

NI/PROTO

NI/PROTO

B B

RESERVED

PEGATRON P/N: 12X64A531W00

A A

ASUS OEM-DT MB RESTRICTED SECRET

ITP_31P CONN.

ITP_31P CONN.

ITP_31P CONN.

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IPM41-D3

IPM41-D3

IPM41-D3

1

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

9 55Thursday, April 29, 2010

9 55Thursday, April 29, 2010

9 55Thursday, April 29, 2010

Rev

Rev

Rev

1.00G

1.00G

1.00G

Page 10

5

I

I

NU1A

H39

N39

N35

N37

N40

M45

R35

R36

R34

R37

R39

U38

U34

U40

Y36

U35

AA35

U37

Y37

Y34

Y38

AA37

AA36

G38

K35

C43

G39

C39

B39

B40

K31

K25

C32

D32

D30

G44

K44

H45

H40

H37

H42

G43

G42

D27

P30

P29

N25

L36

L37

J38

F40

L38

L43

J41

T36

T37

T34

J39

J40

T39

J31

F33

J25

F26

J42

L40

J43

L42

J44

L44

NU1A

HA3#

HA4#

HA5#

HA6#

HA7#

HA8#

HA9#

HA10#

HA11#

HA12#

HA13#

HA14#

HA15#

HA16#

HA17#

HA18#

HA19#

HA20#

HA21#

HA22#

HA23#

HA24#

HA25#

HA26#

HA27#

HA28#

HA29#

HA30#

HA31#

HA32#

HA33#

HA34#

HA35#

HREQ0#

HREQ1#

HREQ2#

HREQ3#

HREQ4#

HADSTB0#

HADSTB1#

HDSTBP0#

HDSTBN0#

HDINV#0

HDSTBP1#

HDSTBN1#

HDINV#1

HDSTBP2#

HDSTBN2#

HDINV#2

HDSTBP3#

HDSTBN3#

HDINV#3

HADS#

HTRDY#

HDRDY#

HDEFER#

HITM#

HIT#

HLOCK#

HBREQ0#

HBNR#

HBPRI#

HDBSY#

HRS0#

HRS1#

HRS2#

HCPURST#

HCLKN

HCLKP

RESERVED

EAGLELAKE

EAGLELAKE

FSB

FSB

REV=1.4

REV=1.4

HSWING

HRCOMP

HDVREF

HACCVREF

HA#[3..35][6] HD#[0..63] [6]

D D

C C

HREQ#[0..4][6]

HADSTB0#[6]

HADSTB1#[6]

HDSTBP0#[6]

HDSTBN0#[6]

HDBI0#[6]

HDSTBP1#[6]

HDSTBN1#[6]

HDBI1#[6]

HDSTBP2#[6]

HDSTBN2#[6]

HDBI2#[6]

HDSTBP3#[6]

HDSTBN3#[6]

HDBI3#[6]

B B

A A

HADS#[6]

HTRDY#[6]

HDRDY#[6]

HDEFER#[6]

HITM#[6]

HIT#[6]

HLOCK#[6]

HBREQ0#[6]

HBNR#[6]

HBPRI#[6]

HDBSY#[6]

HRS#[0..2][6]

CPURESET#[6,9,51]

CK_FSB_NB#[5]

CK_FSB_NB[5]

HA#3

HA#4

HA#5

HA#6

HA#7

HA#8

HA#9

HA#10

HA#11

HA#12

HA#13

HA#14

HA#15

HA#16

HA#17

HA#18

HA#19

HA#20

HA#21

HA#22

HA#23

HA#24

HA#25

HA#26

HA#27

HA#28

HA#29

HA#30

HA#31

HA#32

HA#33

HA#34

HA#35

HREQ#0

HREQ#1

HREQ#2

HREQ#3

HREQ#4

HRS#0

HRS#1

HRS#2

5

HD0

HD1

HD2

HD3

HD4

HD5

HD6

HD7

HD8

HD9

HD10

HD11

HD12

HD13

HD14

HD15

HD16

HD17

HD18

HD19

HD20

HD21

HD22

HD23

HD24

HD25

HD26

HD27

HD28

HD29

HD30

HD31

HD32

HD33

HD34

HD35

HD36

HD37

HD38

HD39

HD40

HD41

HD42

HD43

HD44

HD45

HD46

HD47

HD48

HD49

HD50

HD51

HD52

HD53

HD54

HD55

HD56

HD57

HD58

HD59

HD60

HD61

HD62

HD63

F44

C44

D44

C41

E43

B43

D40

B42

B38

F38

A38

B37

D38

C37

D37

B36

E37

J35

H35

F37

G37

J33

L33

G33

L31

M31

M30

J30

G31

K30

M29

G30

J29

F29

H29

L25

K26

L29

J26

M26

H26

F25

F24

G25

H24

L24

J24

N24

C28

B31

F35

C35

B35

D35

D31

A34

B32

F31

D28

A29

C30

B30

E27

B28

B24

A23

C22

B23

4

4

3

HD#0

HD#1

HD#2

HD#3

HD#4

HD#5

HD#6

HD#7

HD#8

HD#9

HD#10

HD#11

HD#12

HD#13

HD#14

HD#15

HD#16

HD#17

HD#18

HD#19

HD#20

HD#21

HD#22

HD#23

HD#24

HD#25

HD#26

HD#27

HD#28

HD#29

HD#30

HD#31

HD#32

HD#33

HD#34

HD#35

HD#36

HD#37

HD#38

HD#39

HD#40

HD#41

HD#42

HD#43

HD#44

HD#45

HD#46

HD#47

HD#48

HD#49

HD#50

HD#51

HD#52

HD#53

HD#54

HD#55

HD#56

HD#57

HD#58

HD#59

HD#60

HD#61

HD#62

HD#63

HXSWING

HXRCOMP

12

GND

MCH_GTLREF0

12

GND GND GND

MCH_GTLREF0 W/S=10/7

MCH_GTLREF0 W/S=10/7

MCH_GTLREF0 W/S=10/7MCH_GTLREF0 W/S=10/7

HXSWING W/S=10/10

HXSWING W/S=10/10

HXSWING W/S=10/10HXSWING W/S=10/10

HXRCOMP W/S=10/7

HXRCOMP W/S=10/7

HXRCOMP W/S=10/7HXRCOMP W/S=10/7

10/07 modify

I

I

NR5

NR5

16.5

16.5

1%

1%

10/07 modify

NI

NI

NCB2

NCB2

220PF/50V

220PF/50V

X7R 10%

X7R 10%

SDVO_CTRL_DATA

1

SDVO CARD PRESENT, PEG DISABLE

SDVO DISABLE(DEFAULT)

0

02G010024100

C.S EAGLELAKE 82G41 A-3 G41

+1P1V_FSB_VTT

12

I

I

NR4

NR4

49.9 1%

49.9 1%

I

I

NR8

NR8

49.9 1%

49.9 1%

12

12

HXSWING_R

12

I

I

NCB1

NCB1

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

GND

R_MCH_GTLREF0

12

I

I

NCB3

NCB3

1UF/16V

1UF/16V

X7R 10%

X7R 10%

mx_c0603

mx_c0603

12

GND

3

I

I

NR3

NR3

301

301

1%

1%

I

I

NR6

NR6

100

100

1%

1%

+1P1V_FSB_VTT

12

I

I

NR7

NR7

49.9

49.9

1%

1%

12

I

I

NR9

NR9

100

100

1%

1%

CK_100M_MCH[5]

CK_100M_MCH#[5]

SDVO_CTRL_DATA[24]

SDVO_CTRL_CLK[24]

9/9 modify

2

I

I

NU1B

NU1B

SDVO

D9

EXP_CLKINP

E9

EXP_CLKINN

J13

SDVO_CTRLDATA

G13

SDVO_CTRLCLK

AB13

RESERVED3

AD13

RESERVED4

N10

R10

U10

AA9

AA10

AA7

AA6

AB10

AB9

AB3

AA2

AD10

AD11

AD7

AD8

AE9

AE10

AE6

AE7

AF9

AF8

F6

G7

H6

G4

J6

J7

L6

L7

N9

N7

N6

R7

R6

R9

U9

U6

U7

R4

P4

PEG_RXP_0

PEG_RXN_0

PEG_RXP_1

PEG_RXN_1

PEG_RXP_2

PEG_RXN_2

PEG_RXP_3

PEG_RXN_3

PEG_RXP_4

PEG_RXN_4

PEG_RXP_5

PEG_RXN_5

PEG_RXP_6

PEG_RXN_6

PEG_RXP_7

PEG_RXN_7

PEG_RXP_8

PEG_RXN_8

PEG_RXP_9

PEG_RXN_9

PEG_RXP_10

PEG_RXN_10

PEG_RXP_11

PEG_RXN_11

PEG_RXP_12

PEG_RXN_12

PEG_RXP_13

PEG_RXN_13

PEG_RXP_14

PEG_RXN_14

PEG_RXP_15

PEG_RXN_15

DMI_RXP0

DMI_RXN0

DMI_RXP1

DMI_RXN1

DMI_RXP2

DMI_RXN2

DMI_RXP3

DMI_RXN3

EAGLELAKE

EAGLELAKE

EXP_RXP0[24]

EXP_RXN0[24]

EXP_RXP1[24]

EXP_RXN1[24]

EXP_RXP2[24]

EXP_RXN2[24]

EXP_RXP3[24]

EXP_RXN3[24]

EXP_RXP4[24]

EXP_RXN4[24]

EXP_RXP5[24]

EXP_RXN5[24]

EXP_RXP6[24]

EXP_RXN6[24]

EXP_RXP7[24]

EXP_RXN7[24]

EXP_RXP8[24]

EXP_RXN8[24]

EXP_RXP9[24]

EXP_RXN9[24]

EXP_RXP10[24]

EXP_RXN10[24]

EXP_RXP11[24]

EXP_RXN11[24]

EXP_RXP12[24]

EXP_RXN12[24]

EXP_RXP13[24]

EXP_RXN13[24]

EXP_RXP14[24]

EXP_RXN14[24]

EXP_RXP15[24]

EXP_RXN15[24]

DMI_RXP0[20]

DMI_RXN0[20]

DMI_RXP1[20]

DMI_RXN1[20]

DMI_RXP2[20]

DMI_RXN2[20]

DMI_RXP3[20]

DMI_RXN3[20]

SDVO

PCIE

PCIE

DMI

DMI

REV=1.4

REV=1.4

EXP_RCOMPO

EXP_COMPI

EXP_ICOMPO

EXP_RBIAS

PEG_TXP0

PEG_TXN0

PEG_TXP1

PEG_TXN1

PEG_TXP2

PEG_TXN2

PEG_TXP3

PEG_TXN3

PEG_TXP4

PEG_TXN4

PEG_TXP5

PEG_TXN5

PEG_TXP6

PEG_TXN6

PEG_TXP7

PEG_TXN7

PEG_TXP8

PEG_TXN8

PEG_TXP9

PEG_TXN9

PEG_TXP10

PEG_TXN10

PEG_TXP11

PEG_TXN11

PEG_TXP12

PEG_TXN12

PEG_TXP13

PEG_TXN13

PEG_TXP14

PEG_TXN14

PEG_TXP15

PEG_TXN15

DMI_TXP0

DMI_TXN0

DMI_TXP1

DMI_TXN1

DMI_TXP2

DMI_TXN2

DMI_TXP3

DMI_TXN3

Y7

Y8

Y6

AG1

C11

B11

A10

B9

C9

D8

B8

C7

B7

B6

B3

B4

D2

C2

H2

G2

J2

K2

K1

L2

P2

M2

T2

R1

U2

V2

W4

V3

AA4

Y4

AC1

AB2

NOTE:

Check Eaglelake PDG for detai if wanna

support Integrated HDMI/DVI/DP

AC2

1 2

AD2

AD4

1 2

AE4

AE2

AF2

1 2

AF4

AG4

1 2

+1P1V_CORE

EXP_RCOMP

EXP_RBIAS

12

GND

NCB66

NCB66

NCB68

NCB68

NCB78

NCB78

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

NCB80

NCB80

0.1UF/16V

0.1UF/16V

I

I

X7R 10%

X7R 10%

0.1UF/16V

0.1UF/16V

I

I

X7R 10%

X7R 10%

0.1UF/16V

0.1UF/16V

I

I

X7R 10%

X7R 10%

I

I

1

12

I

I

NR1

NR1

49.9

49.9

1%

1%

NOTE:

Breakout W/S:10/6

W/S:10/10

I

I

NR2

NR2

750

750

1%

1%

EXP_TXP0 [24]

EXP_TXN0 [24]

EXP_TXP1 [24]

EXP_TXN1 [24]

EXP_TXP2 [24]

EXP_TXN2 [24]

EXP_TXP3 [24]

EXP_TXN3 [24]

EXP_TXP4 [24]

EXP_TXN4 [24]

EXP_TXP5 [24]

EXP_TXN5 [24]

EXP_TXP6 [24]

EXP_TXN6 [24]

EXP_TXP7 [24]

EXP_TXN7 [24]

EXP_TXP8 [24]

EXP_TXN8 [24]

EXP_TXP9 [24]

EXP_TXN9 [24]

EXP_TXP10 [24]

EXP_TXN10 [24]

EXP_TXP11 [24]

EXP_TXN11 [24]

EXP_TXP12 [24]

EXP_TXN12 [24]

EXP_TXP13 [24]

EXP_TXN13 [24]

EXP_TXP14 [24]

EXP_TXN14 [24]

EXP_TXP15 [24]

EXP_TXN15 [24]

NCB26

NCB26

1 2

1 2

1 2

1 2

NCB67

NCB67

NCB77

NCB77

0.1UF/16V

0.1UF/16V

X7R 10%

X7R 10%

NCB79

NCB79

0.1UF/16V

0.1UF/16V

I

I

X7R 10%

X7R 10%

0.1UF/16V

0.1UF/16V

I

I

X7R 10%

X7R 10%

0.1UF/16V

0.1UF/16V

I

I

X7R 10%

X7R 10%

I

I

DMI_TXP0 [2 0]

DMI_TXN0 [20]

DMI_TXP1 [2 0]

DMI_TXN1 [20]

DMI_TXP2 [2 0]

DMI_TXN2 [20]

DMI_TXP3 [2 0]

DMI_TXN3 [20]

ASUS OEM-DT MB RESTRICTED SECRET

EAGLELAKE 1- 7

EAGLELAKE 1- 7

EAGLELAKE 1- 7

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

Engineer:

IPM41-D3

IPM41-D3

IPM41-D3

1

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

10 55Thursday, July 09, 2009

10 55Thursday, July 09, 2009

10 55Thursday, July 09, 2009

Rev

Rev

Rev

1.00G

1.00G

1.00G

Page 11

5

M_CHA_MAA[1..14][17]

D D

M_CHA_CAS#[17]

M_CHA_RAS#[17]

M_CHA_BA0[17]

M_CHA_BA1[17]

M_CHA_BA2[17]

M_CHA_CS#0[17]

NOBOM

NOBOM

1

M_CHA_CKE0[17]

M_CHA_CKE1[17]

M_CHA_ODT0[17]

C C

B B

A A

5

M_CHA_ODT1[17]

M_CHA_CLK0[17]

M_CHA_CLK0#[17]

M_CHA_CLK2[17]

M_CHA_CLK2#[17]

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

1

1

1

1

1

1

HT8

HT8

HT11

HT11

HT15

HT15

HT16

HT16

HT18

HT18

HT19

HT19

HT20

HT20

4

M_CHA_MAA1

M_CHA_MAA2

M_CHA_MAA3

M_CHA_MAA4

M_CHA_MAA5

M_CHA_MAA6

M_CHA_MAA7

M_CHA_MAA8

M_CHA_MAA9

M_CHA_MAA10

M_CHA_MAA11

M_CHA_MAA12

M_CHA_MAA13

M_CHA_MAA14

N27146510

N27146424

N27146426

N27146514

N27146515

N27146428

N27146516

4

BC41

BC35

BB32

BC32

BD32

BB31

AY31

BA31

BD31

BD30

AW43

BC30

BB30

AM42

BD28

AW42

AU42

AV42

AV45

AY44

BC28

AU43

AR40

AU44

AM43

BB27

BD27

BA27

AY26

AR42

AM44

AR44

AL40

AY37

BA37

AW29

AY29

AU37

AV37

AU33

AT33

AT30

AR30

AW38

AY38

I

I

NU1C

NU1C

SMA_A0

SMA_A1

SMA_A2

SMA_A3

SMA_A4

SMA_A5

SMA_A6

SMA_A7

SMA_A8

SMA_A9

SMA_A10

SMA_A11

SMA_A12

SMA_A13

SMA_A14

SWE_A#

SCAS_A#

SRAS_A#

SBS_A0

SBS_A1

SBS_A2

SCS_A0#

SCS_A1#

SCS_A2#

SCS_A3#

SCKE_A0

SCKE_A1

SCKE_A2

SCKE_A3

SODT_A0

SODT_A1

SODT_A2

SODT_A3

SCLK_A0

SCLK_A0#

SCLK_A1

SCLK_A1#

SCLK_A2

SCLK_A2#

SCLK_A3

SCLK_A3#

SCLK_A4

SCLK_A4#

SCLK_A5

SCLK_A5#

DDR_A

DDR_A

EAGLELAKE

EAGLELAKE

REV=1.4

REV=1.4

SDQS_A0

SDQS_A0#

SDM_A0

SDQ_A0

SDQ_A1

SDQ_A2

SDQ_A3

SDQ_A4

SDQ_A5

SDQ_A6

SDQ_A7

SDQS_A1

SDQS_A1#

SDM_A1

SDQ_A8

SDQ_A9

SDQ_A10

SDQ_A11

SDQ_A12

SDQ_A13

SDQ_A14

SDQ_A15

SDQS_A2

SDQS_A2#

SDM_A2

SDQ_A16

SDQ_A17

SDQ_A18

SDQ_A19

SDQ_A20

SDQ_A21

SDQ_A22

SDQ_A23

SDQS_A3

SDQS_A3#

SDM_A3

SDQ_A24

SDQ_A25

SDQ_A26

SDQ_A27

SDQ_A28

SDQ_A29

SDQ_A30

SDQ_A31

SDQS_A4

SDQS_A4#

SDM_A4

SDQ_A32

SDQ_A33

SDQ_A34

SDQ_A35

SDQ_A36

SDQ_A37

SDQ_A38

SDQ_A39

SDQS_A5

SDQS_A5#

SDM_A5

SDQ_A40

SDQ_A41

SDQ_A42

SDQ_A43

SDQ_A44

SDQ_A45

SDQ_A46

SDQ_A47

SDQS_A6

SDQS_A6#

SDM_A6

SDQ_A48

SDQ_A49

SDQ_A50

SDQ_A51

SDQ_A52

SDQ_A53

SDQ_A54

SDQ_A55

SDQS_A7

SDQS_A7#

SDM_A7

SDQ_A56

SDQ_A57

SDQ_A58

SDQ_A59

SDQ_A60

SDQ_A61

SDQ_A62

SDQ_A63

BC5

BD4

BC3

BC2

BD3

BD7

BB7

BB2

BA3

BE6

BD6

BB9

BC9

BD9

BB8

AY8

BD11

BB11

BC7

BE8

BD10

AY11

BD15

BB15

BD14

BB14

BC14

BC16

BB16

BC11

BE12

BA15

BD16

AR22

AT22

AV22

AW21

AY22

AV24

AY24

AU21

AT21

AR24

AU24

AH43

AH42

AK42

AL41

AK43

AG42

AG44

AL42

AK44

AH44

AG41

AD43

AE42

AE45

AF43

AF42

AC44

AC42

AF40

AF44

AD44

AC41

Y43

Y42

AA45

AB43

AA42

W42

W41

AB42

AB44

Y44

Y40

T44

T43

T42

V42

U45

R40

P44

V44

V43

R41

R44

3

M_CHA_DQ0

M_CHA_DQ1

M_CHA_DQ2

M_CHA_DQ3

M_CHA_DQ4

M_CHA_DQ5

M_CHA_DQ6

M_CHA_DQ7

M_CHA_DQ8

M_CHA_DQ9

M_CHA_DQ10

M_CHA_DQ11

M_CHA_DQ12

M_CHA_DQ13

M_CHA_DQ14

M_CHA_DQ15

M_CHA_DQ16

M_CHA_DQ17

M_CHA_DQ18

M_CHA_DQ19

M_CHA_DQ20

M_CHA_DQ21

M_CHA_DQ22

M_CHA_DQ23

M_CHA_DQ24

M_CHA_DQ25

M_CHA_DQ26

M_CHA_DQ27

M_CHA_DQ28

M_CHA_DQ29

M_CHA_DQ30

M_CHA_DQ31

M_CHA_DQ32

M_CHA_DQ33

M_CHA_DQ34

M_CHA_DQ35

M_CHA_DQ36

M_CHA_DQ37

M_CHA_DQ38

M_CHA_DQ39

M_CHA_DQ40

M_CHA_DQ41

M_CHA_DQ42

M_CHA_DQ43

M_CHA_DQ44

M_CHA_DQ45

M_CHA_DQ46

M_CHA_DQ47

M_CHA_DQ48

M_CHA_DQ49

M_CHA_DQ50

M_CHA_DQ51

M_CHA_DQ52

M_CHA_DQ53

M_CHA_DQ54

M_CHA_DQ55

M_CHA_DQ56

M_CHA_DQ57

M_CHA_DQ58

M_CHA_DQ59

M_CHA_DQ60

M_CHA_DQ61

M_CHA_DQ62

M_CHA_DQ63

3

M_CHA_DQS0 [17]

M_CHA_DQS0# [17]

M_CHA_DM0 [17]

M_CHA_DQS1 [17]

M_CHA_DQS1# [17]

M_CHA_DM1 [17]

M_CHA_DQS2 [17]

M_CHA_DQS2# [17]

M_CHA_DM2 [17]

M_CHA_DQS3 [17]

M_CHA_DQS3# [17]

M_CHA_DM3 [17]

M_CHA_DQS4 [17]

M_CHA_DQS4# [17]

M_CHA_DM4 [17]

M_CHA_DQS5 [17]

M_CHA_DQS5# [17]

M_CHA_DM5 [17]

M_CHA_DQS6 [17]

M_CHA_DQS6# [17]

M_CHA_DM6 [17]

M_CHA_DQS7 [17]

M_CHA_DQS7# [17]

M_CHA_DM7 [17]

2

M_CHA_DQ[0..63] [17]

PEGATRON CORP.

PEGATRON CORP.

PEGATRON CORP.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

1

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

IPM41-D3

IPM41-D3

IPM41-D3

1

EAGELLAKE 2 - 7

EAGELLAKE 2 - 7

EAGELLAKE 2 - 7

Wayne Hsieh

Wayne Hsieh

Wayne Hsieh

11 55Thursday, July 09, 2009

11 55Thursday, July 09, 2009

11 55Thursday, July 09, 2009

Rev

Rev

Rev

1.00

1.00

1.00

Page 12

5

M_CHB_MAA[0..14][18]

D D

C C

DDR_REF NEED ROUTING

Width/Spacing: 12/12 mils

+1P5V_DUAL

12

NI

NI

NCB4

NCB4

0.1UF/16V

B B

0.1UF/16V

GND

12

I

I

NR11

NR11

1K

1K

1%

1%

12

I

I

NR12

NR12

1K

1K

1%

1%

GND GND GND

12

I

I

NCB115

NCB115

1UF/10V

1UF/10V

mx_c0603

mx_c0603

090420 add by TSL

12

I

I

NCB5

NCB5

0.1UF/16V

0.1UF/16V

MCH_DDR_RPU, MCH_DDR_RPD, MCH_DDR_SPU, MCH_DDR_SPD

NEED ROUTING LESS THEN 1000MIL LENGTH.

WIDTH/SPACING = 10/10 MIL

A A

5

4

M_CHB_WE#[18]

M_CHB_CAS#[18]

M_CHB_RAS#[18]

M_CHB_BA0[18]

M_CHB_BA1[18]

M_CHB_BA2[18]

M_CHB_CS#0[18]

M_CHB_CS#1[18]

NOBOM

NOBOM

M_CHB_CKE0[18]

M_CHB_CKE1[18]

NOBOM

NOBOM

NOBOM

NOBOM

M_CHB_ODT0[18]

M_CHB_ODT1[18]

NOBOM

NOBOM

M_CHB_CLK0[18]

M_CHB_CLK0#[18]

NOBOM

NOBOM

NOBOM

NOBOM

M_CHB_CLK2[18]

M_CHB_CLK2#[18]

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

M_CHA_CS#1[17]

M_CHA_MAA0[17]

M_CHA_WE#[17]

DDR3_DRAM_PWROK[19]

DDR3_DRAMRST#[17,18]

NOBOM

NOBOM

NOBOM

NOBOM

+1P5V_DUAL

1 2

12

I

I

NCB6

NCB6

0.1UF/16V

0.1UF/16V

GND GND

+1P5V_DUAL

1 2

12

I

I

NCB7

NCB7

0.1UF/16V

0.1UF/16V

GND GND

4

I

I

NR13

NR13

80.6

80.6

1%

1%

I

I

NR15

NR15

80.6

80.6

1%

1%

HT25

HT25

1

HT26

HT26

1

HT27

HT27

1

HT29

HT29

1

HT30

HT30

1

HT31

HT31

1

HT32

HT32

1

HT33

HT33

1

HT34

HT34

1

HT35

HT35

1

HT37

HT37

1

HT39

HT39

1

HT40

HT40

1

M_CHB_MAA0

M_CHB_MAA1

M_CHB_MAA2

M_CHB_MAA3

M_CHB_MAA4

M_CHB_MAA5

M_CHB_MAA6

M_CHB_MAA7

M_CHB_MAA8

M_CHB_MAA9

M_CHB_MAA10

M_CHB_MAA11

M_CHB_MAA12

M_CHB_MAA13

M_CHB_MAA14

N27146430

N27146431

N27146432

N27146434

N27146435

N27146436

N27146437

N27146438

N27146439

N27146440

N27146442

N27146445

N27146446

MCH_DDR_RPD

12

I

I

NR14

NR14

80.6

80.6

1%

1%

MCH_DDR_SPD

12

I

I

NR16

NR16

249

249

1%

1%

DDR_VREF

MCH_DDR_RPU

MCH_DDR_SPU

I

I

NU1D

NU1D

False

BD24

SMA_B0

BB23

SMA_B1

BB24

SMA_B2

BD23

SMA_B3

BB22

SMA_B4

BD22

SMA_B5

BC22

SMA_B6

BC20

SMA_B7

BB20

SMA_B8

BD20

SMA_B9

BC26

SMA_B10

BD19

SMA_B11

BB19

SMA_B12

BE38

SMA_B13

BA19

SMA_B14