Page 1

5

4

3

2

1

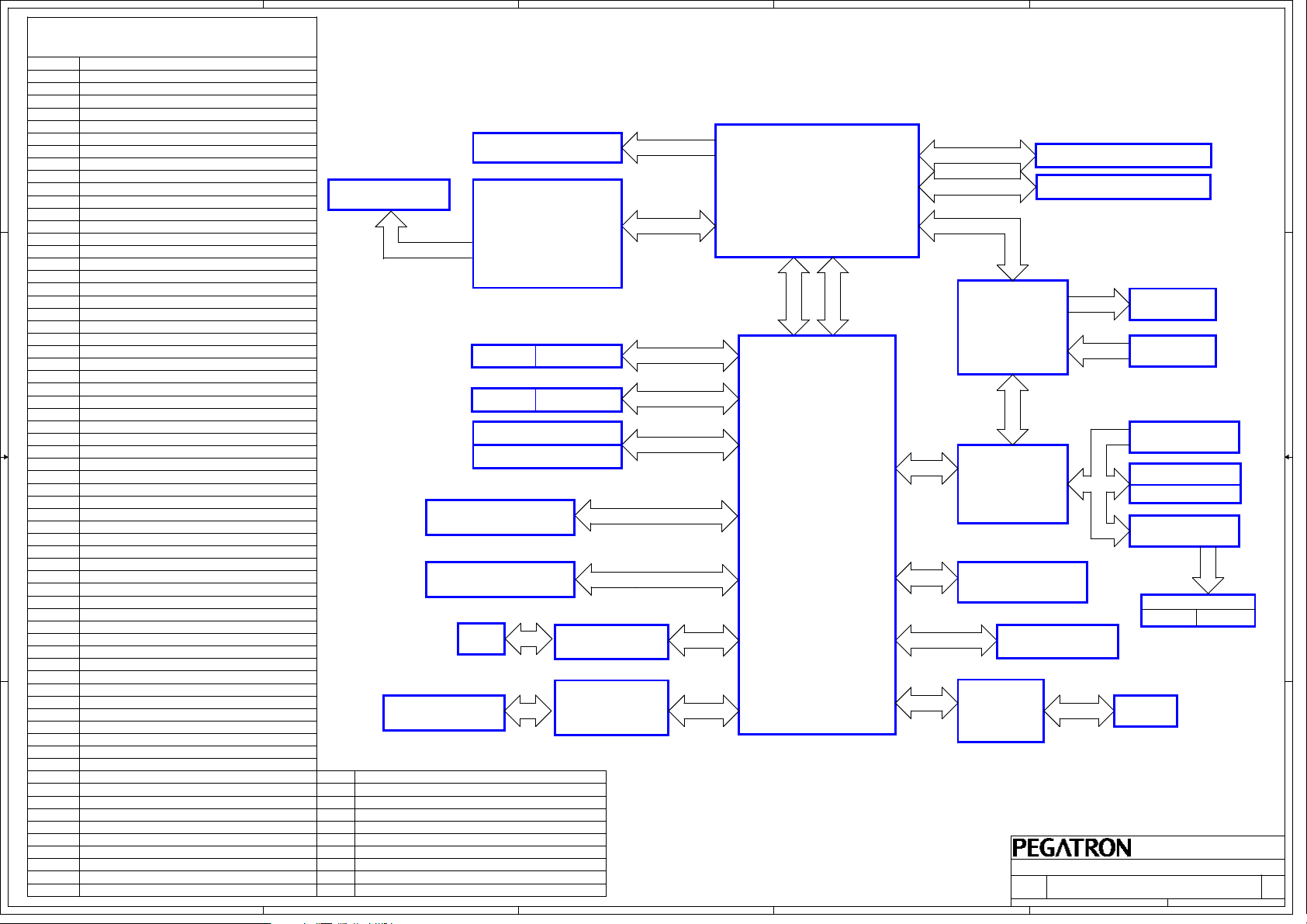

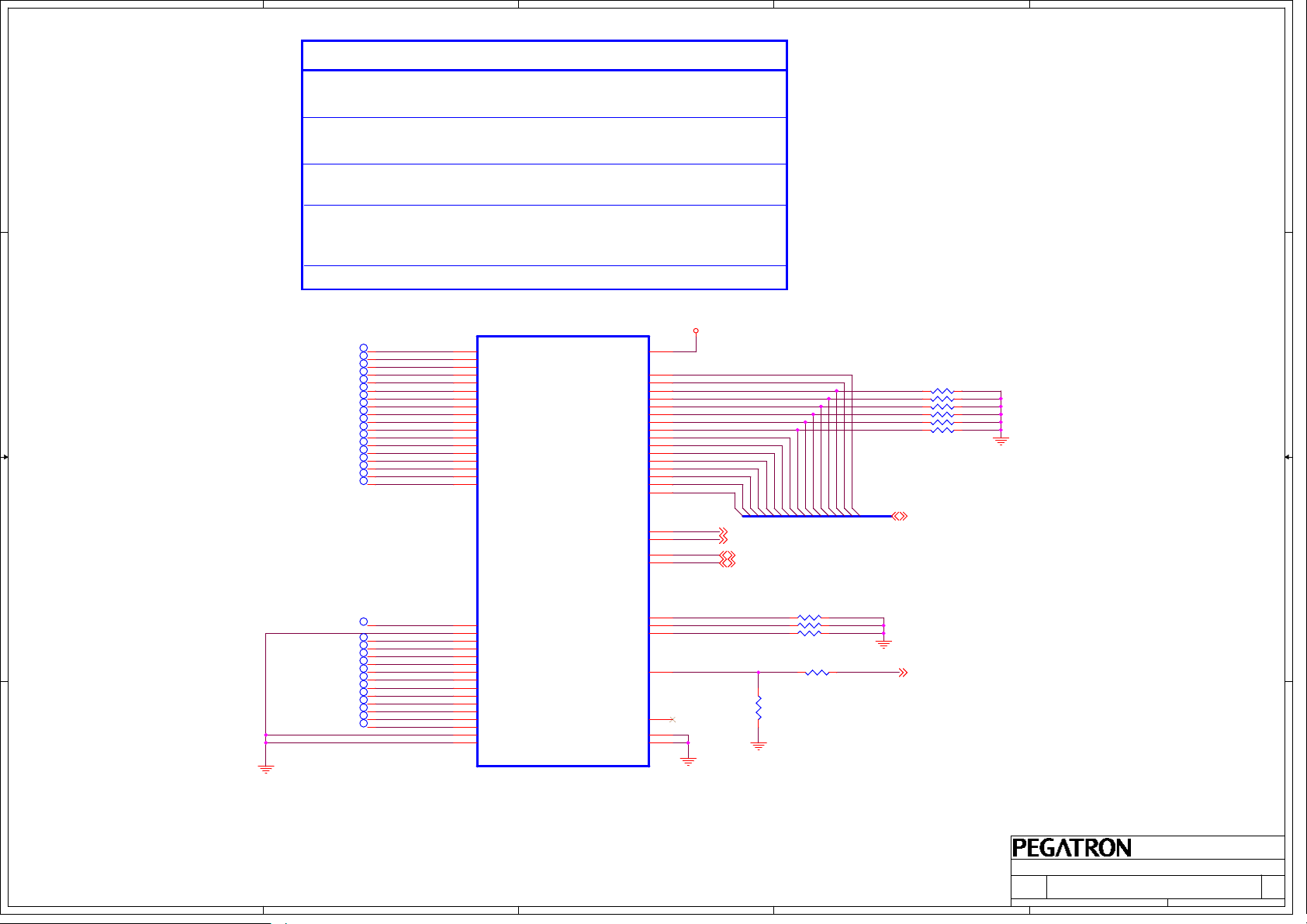

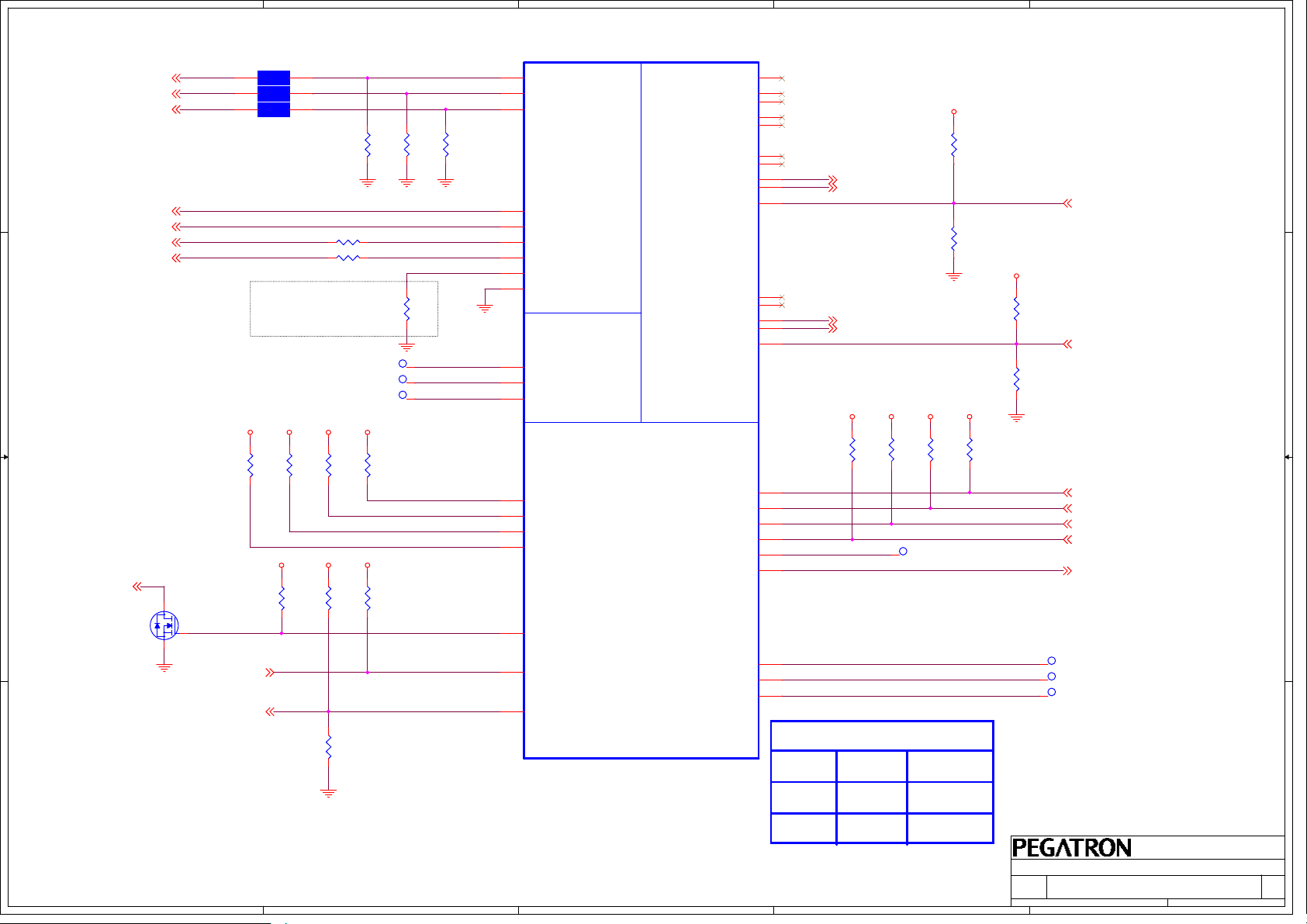

IMPLP-MS

Monster (Shark Bay)

Revision_A00_2013/05/20

PAGE TITLE

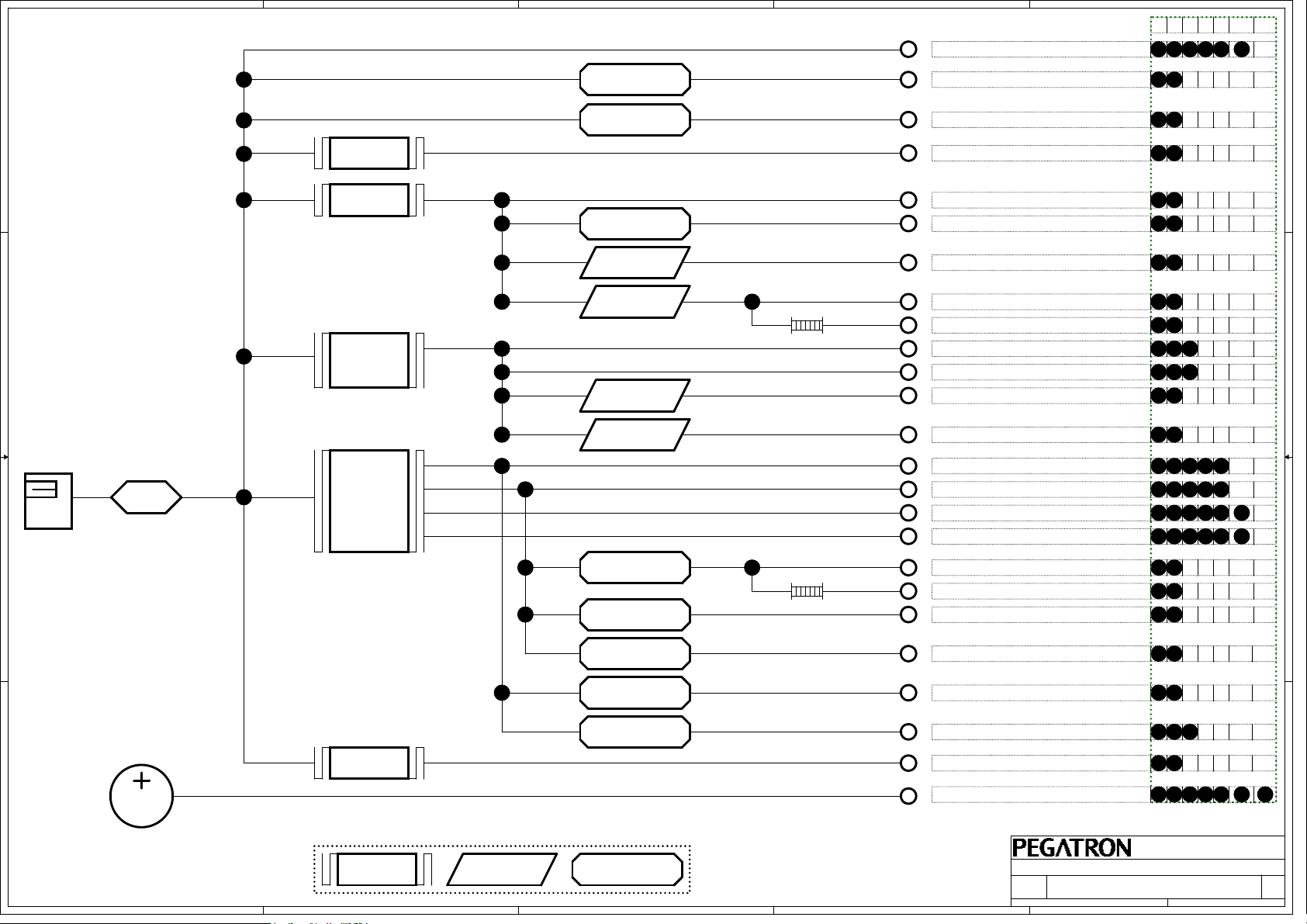

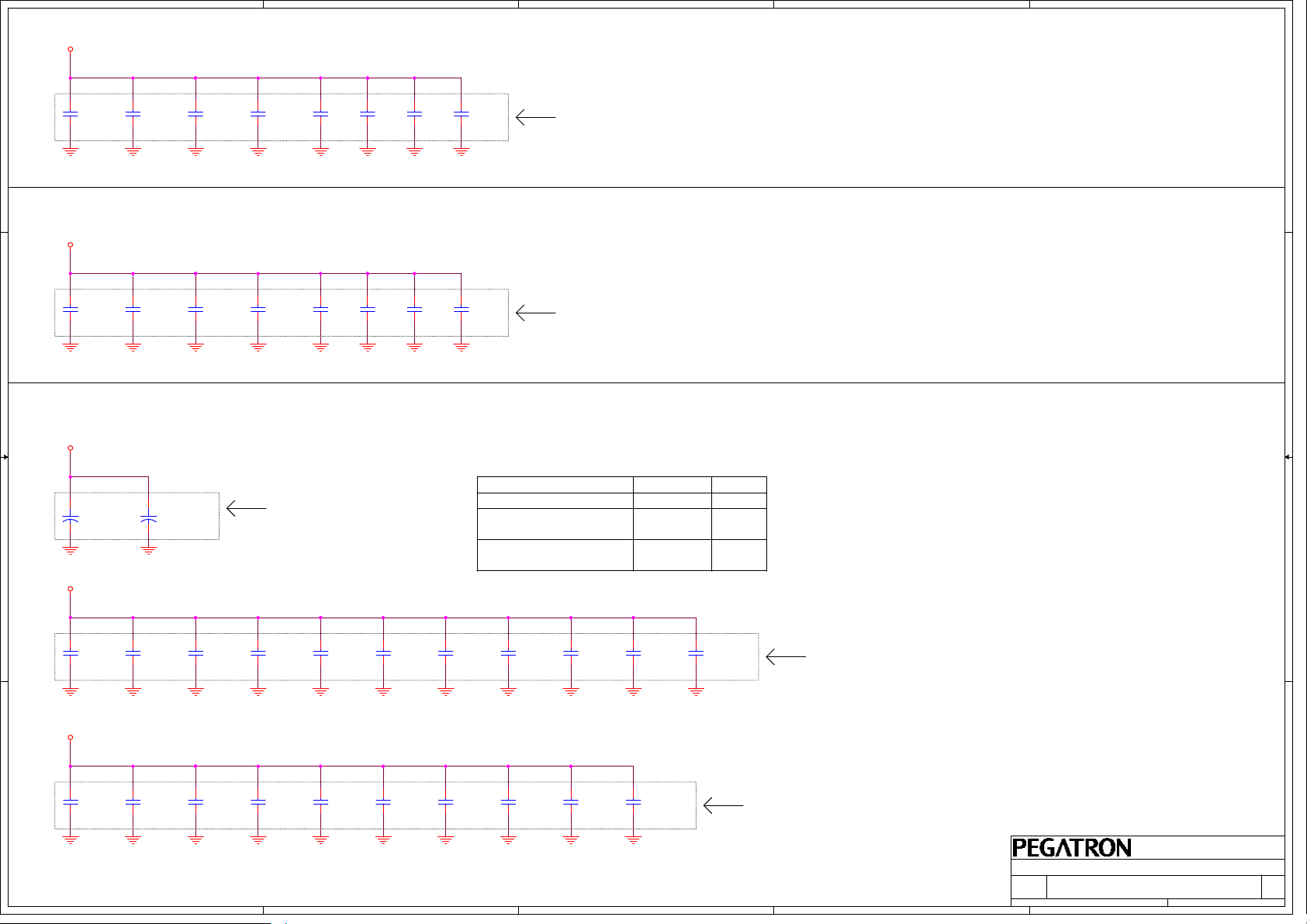

01 BLOCK DIAGRAM

02 CLOCK DISTRIBUTION

03 POWER ON CHART

04 CHANGE HISTORY

D D

05 POWER FLOW

06 POWER DISTRIBUTION

07 POWER SEQUENCE

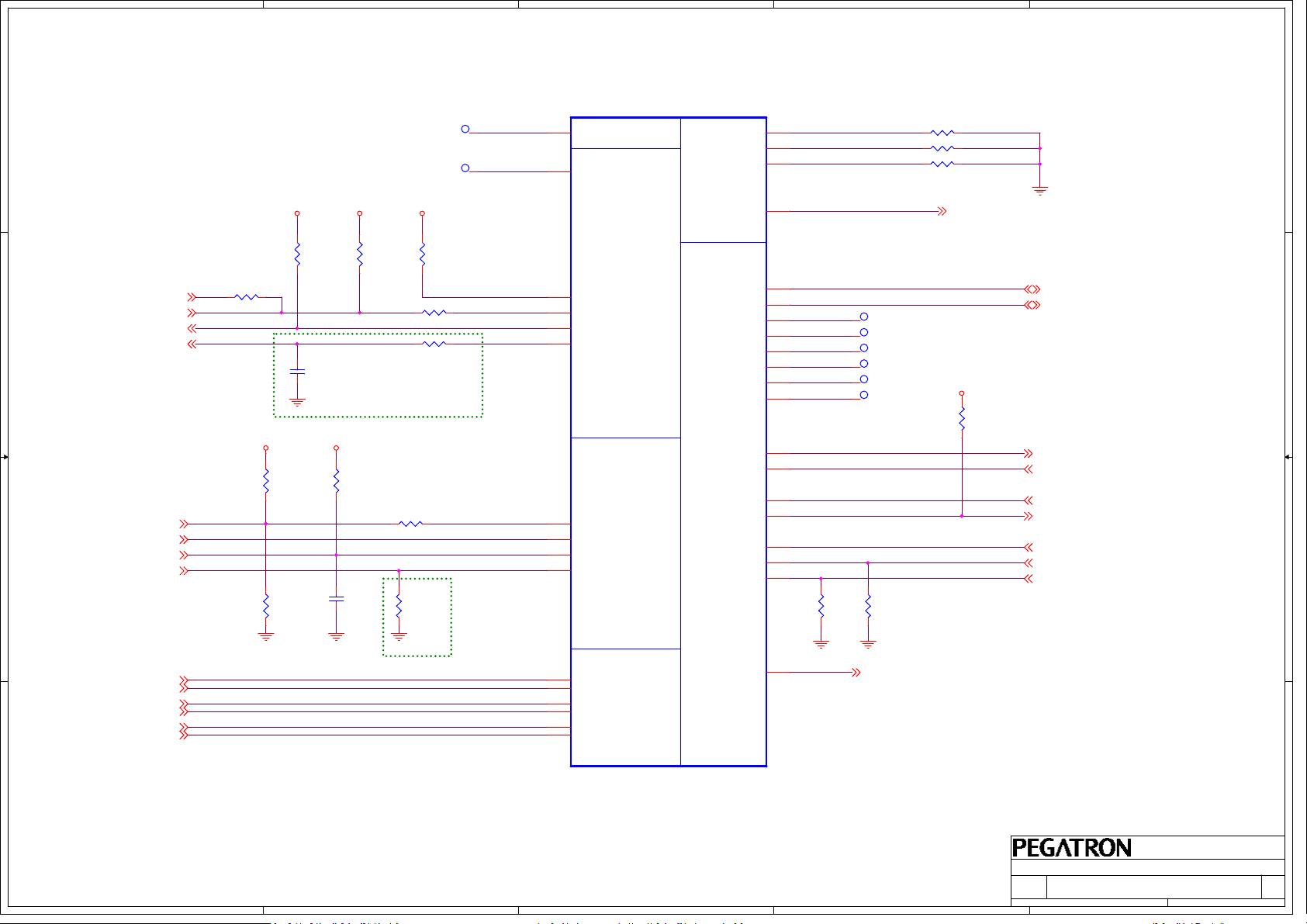

08 CPU DMI,FDI,PEG,DDI

09 CPU CLK,MISC,JTAG,Thermal

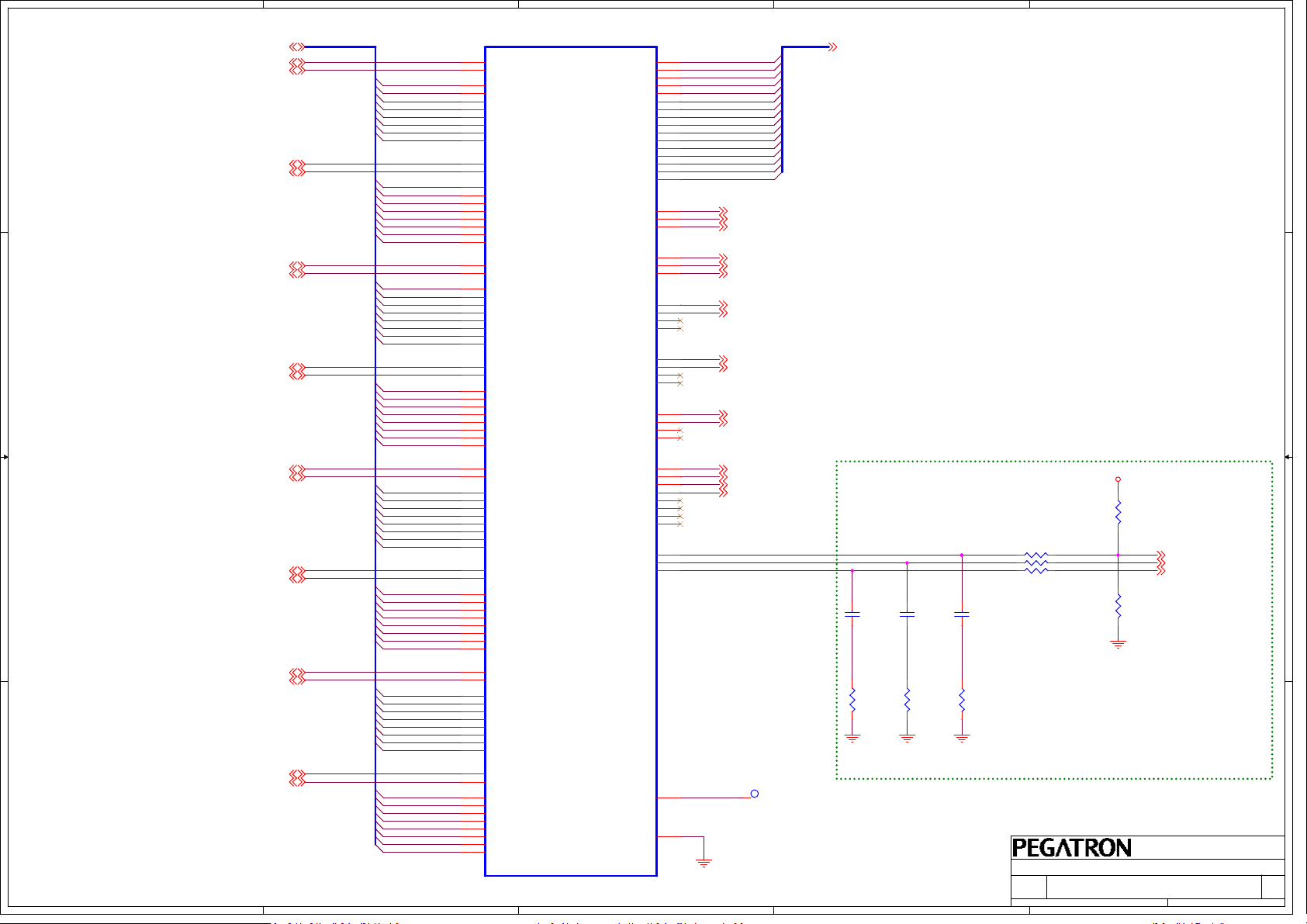

10 CPU DDR3 CHANNEL A

11 CPU DDR3 CHANNEL B

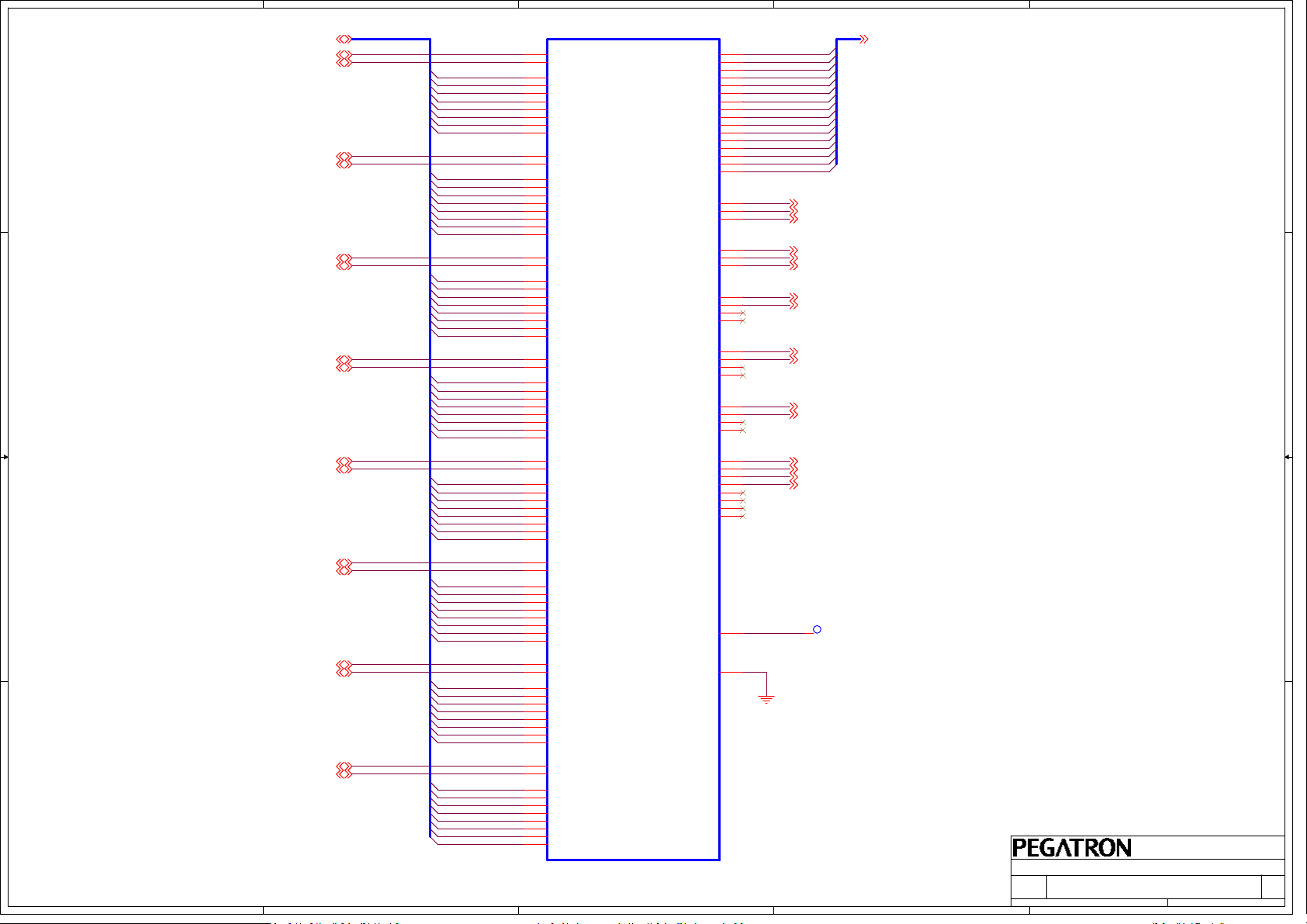

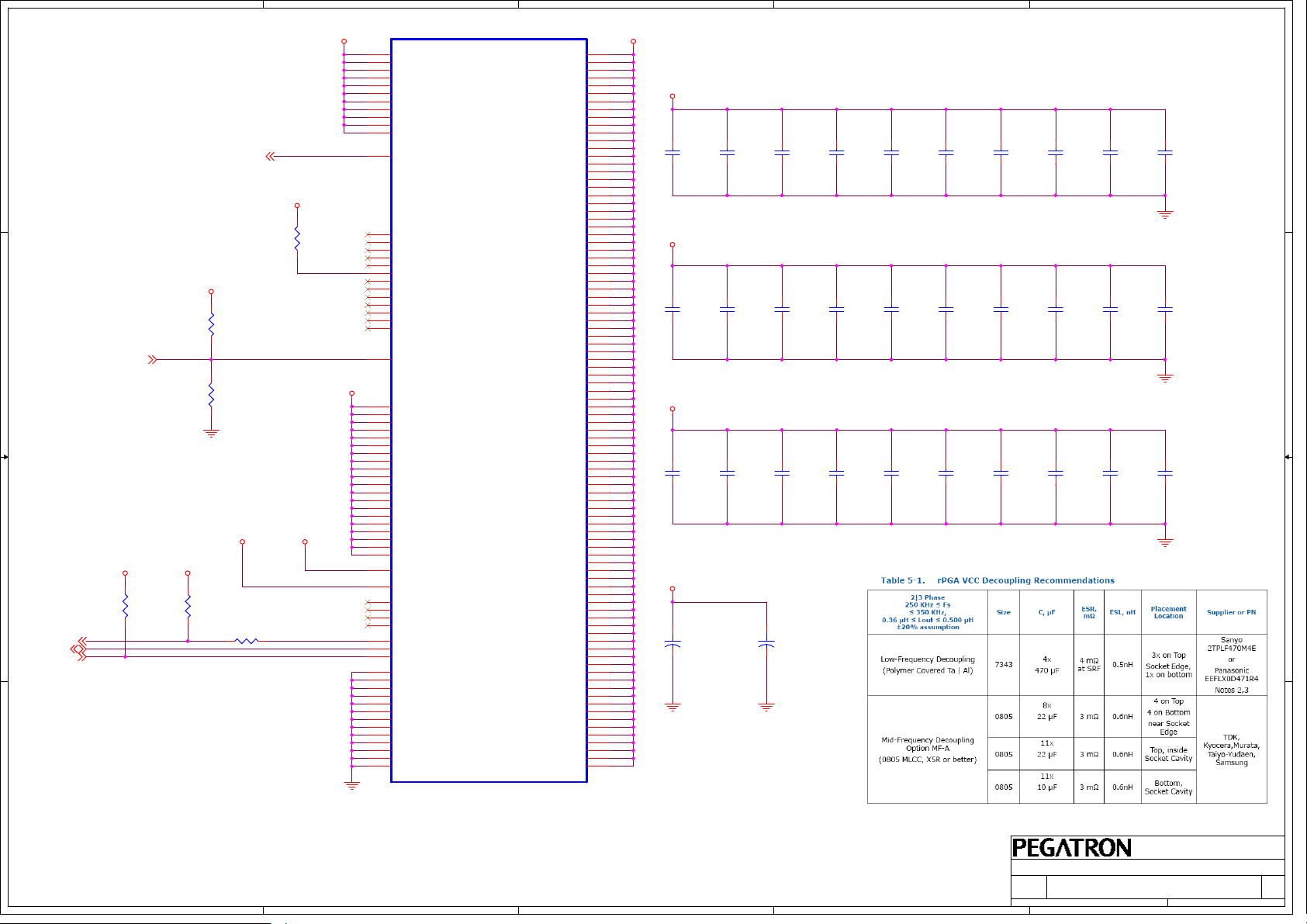

12 CPU POWER

13 CPU CFG

14 CPU GND

15 DDR3 SO-DIMM 0

16 DDR3 SO-DIMM 1

17. PCH SATA,IHDA,RTC,JTAG

18 PCH FDI,DMI,SPM

19 PCH CLOCK

HDMI OUT

2GB GDDR5 AMD SUN-XT 64bit

631 Pin

4.0/5.0 Gbps

23mm x 23mm

TDP 25W

TMDS 1.65Gbps

PCIE X8 Gen3 8.0Gbps

Intel Processor

Haswell

rPGA-947 Pin Socket

TDP 47W/37W

FDI 2.0

DMI 2.0

2.7Gbps 5.0Gbps

Channel A

Channel B

HDMI TMDS 1.65Gbps

20 PCH LPC,SPI,SMBus,Thermal

21 PCH CRT,LVDS,PCI,DISP

22 PCH GPIO,MISC,NCTF

C C

23 PCH PCIE,USB

24 PCH_POWER-1

25 PCH_POWER-2

26

27-28 SCALAR_TSUMU88BDC2

PCHVSS

29 LVDS & DUAL I/O CONNECTOR

30 HDMI IN

31 HDMI OUT

32 HALF MINI-PCIE

33 FULL MINI-PCIE

34 CARDREADER RST5209

35

36 SUPER I/O - F71808A

CARDREADER CONNECTOR

37 LAN RTL8151GD-CG

38 RJ45 CONNECTOR

SIDE

REAR

TOUCH PANEL

WEBCAM

WLAN/BT

Half mini-PCIE Slot

4 ports

2 ports

USB 2.0 & PCIE X1 Gen2 5.0Gbps

USB 3.0 5.0Gbps

USB 2.0 480Mbps

USB 2.0 480Mbps

INTEL

Lynx Point

AZALIA

Mobile PCH

39 USB & AUDIO CONNECTOR

40 LEFT SIDE USB 3.0 CONNECTOR

41 REAR SIDE USB 2.0 CONNECTOR

B B

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

A A

60-63

64

65

66

67

68

69

70

SATA CONNECTOR

AUDIO CODEC ALC3661

AUDIO AMP TPA3110D2

REAR HP-OUT CONN & MUTE

AUDIO MUTE

SM BUS & SPI ROM

RTC & LPC DEBUG & FAN

INTEGRATED VGA PORT

CPU XDP DEBUG CONNECTOR

PCH XDP DEBUG CONNECTOR

LED & PCB & Label & Screw

MARS-S3 PRO PCIE

MARS-S3 PRO IO

MARS-S3 PRO VROM & STRAP

MARS-S3 PRO MEMORY

MARS-S3 PRO POWER

MARS-S3 PRO DP_Power

MARS-S3 PRO GND & TMDS

GDDR5 256M X16bit XCELL

CURRENT LIMIT

Power supply Vin

+19V / 3P3V / 5V / 5V_DUAL

+1P35V_DUAL & +VTTDDR

+1P5V

+3P3GPU

+1P8VMXM & +0P95V_GPU

5

+1P35V_GPU & +VDDCI

71

72

+VDDC controller

73

+VDDC CAP

74

+1P2V & +1P05V_PCH

75

+3VA / 5VA / 3VSB / 5VSB

VCORE CONTROLLER

76

77

VCORE DRIVER 2-1

78

VCORE DRIVER 2-2 & Cout

79

DISCHARGE

80

CARD USB3.0 X2

4

TV TUNER/mSATA

Full mini-PCIE slot

RJ45

CARD READER

SOCKET

USB 2.0/SATA Gen3 6.0Gbps/PCIE X1

LAN

RTL8151GD

CARD READER

RTS5209-GR

Default component footprint is

SMD 0402, Y5V, 5% type.

Difference footprint show on schematics.

Property: BOM

I = Installed Part.

NI = Not Installed Part.

PROTO = PROTO Phase Only.

VP = Virtual Part.

NOBOM = Symbol only.

3

PCIE X1

PCIE X1

HM87

695 Pin

20mm X 20mm

TDP 3W

SPI

SATA Gen3 6.0Gbps

LPC

2

SO-DIMM (Max Memory 16GB)

DDR3L 1600MHz *1

DDR3L 1600MHz *1

MSTAR

Scalar

TSUMU88BDC2-1

LINE IN

REALTEK

AUDIO

ALC3661-CG

QUAD I/O

SPI Flash

Serial ATA Port

FINTEK

SIO

F71808AU

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

(8MB)

LVDS

TMDS

HDMI-IN

AUDIO AMP

TPA3110D2PWPR

FAN

Engineer:

Engineer:

Engineer:

IMPLP-MS

IMPLP-MS

IMPLP-MS

PANEL

DIGITAL MIC

From Webcam

GHS(HP/MIC)

AUDIO OUT

SPEAKER (AVG)

Title :

Title :

Title :

1

R(4W)L(4W)

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Stonko_Chen

Stonko_Chen

Stonko_Chen

1 83Thursday, June 27 , 2013

1 83Thursday, June 27 , 2013

1 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

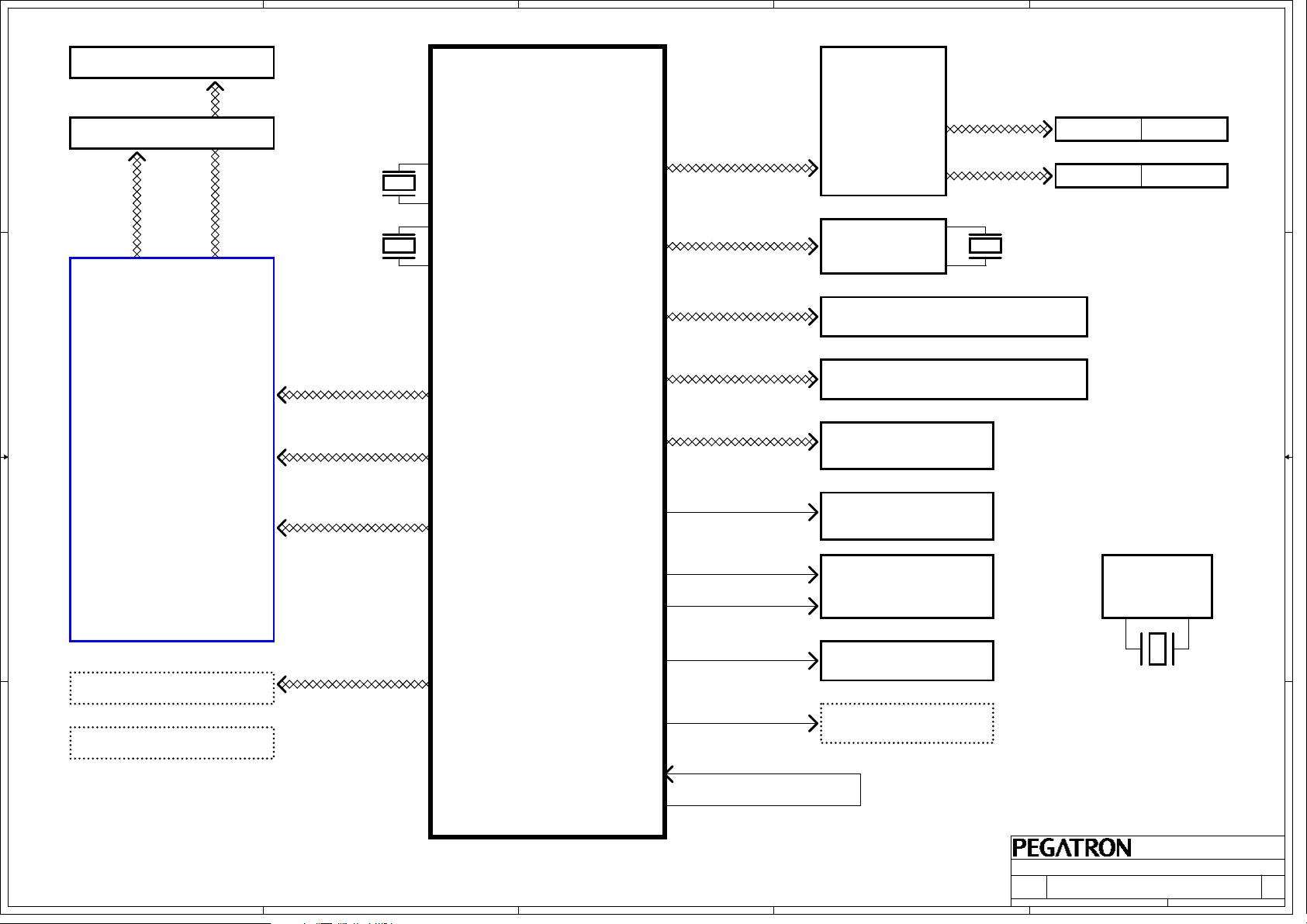

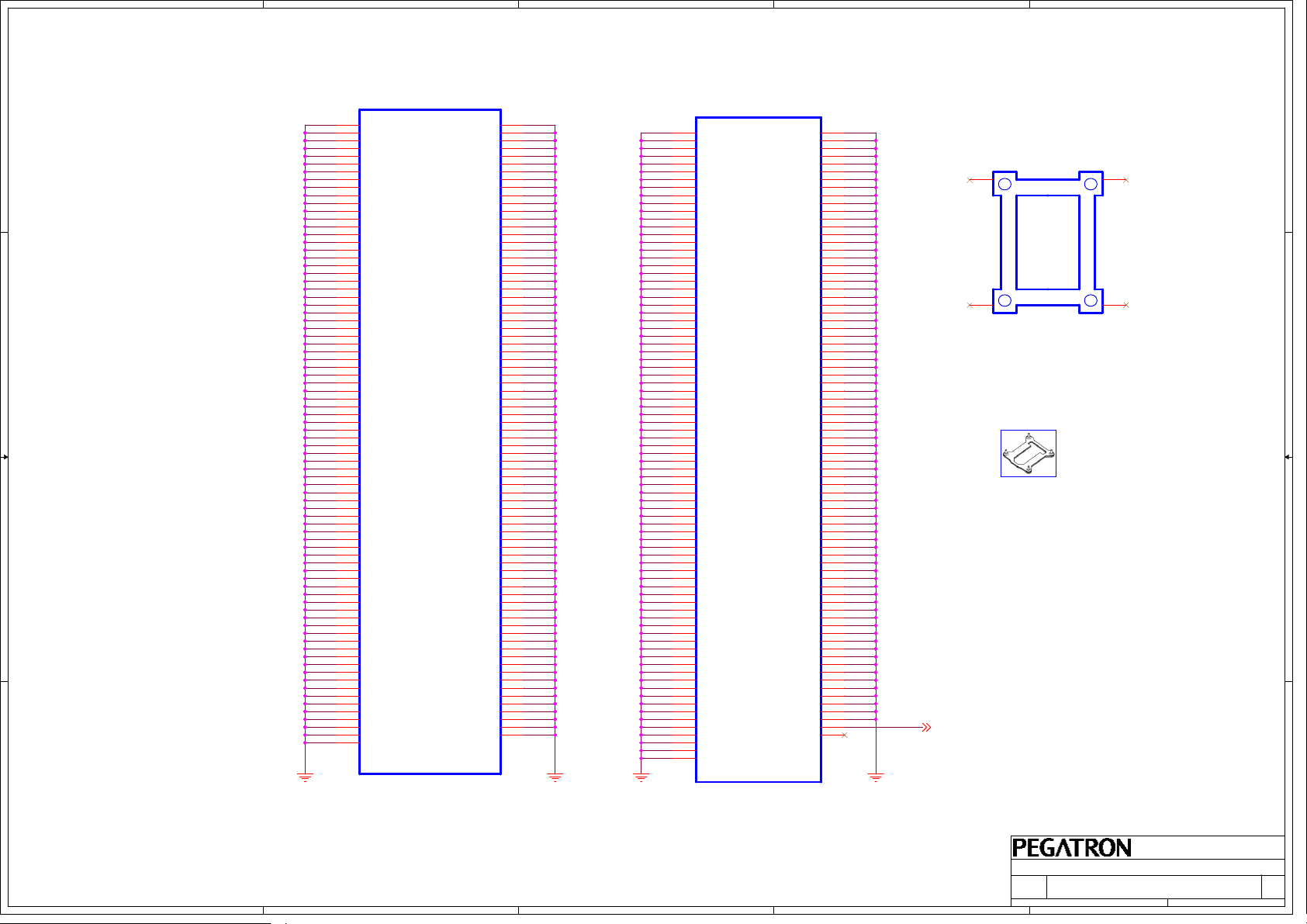

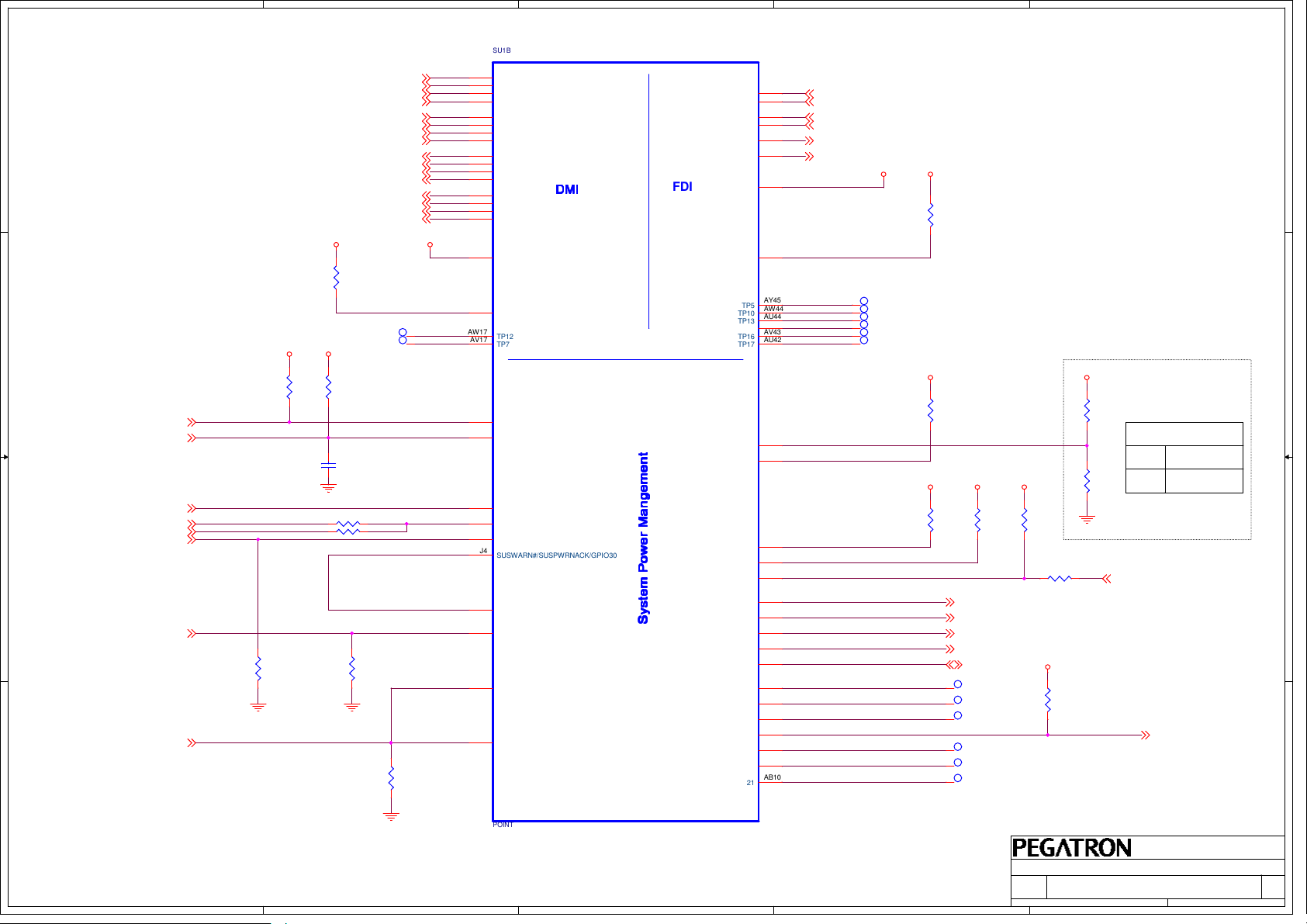

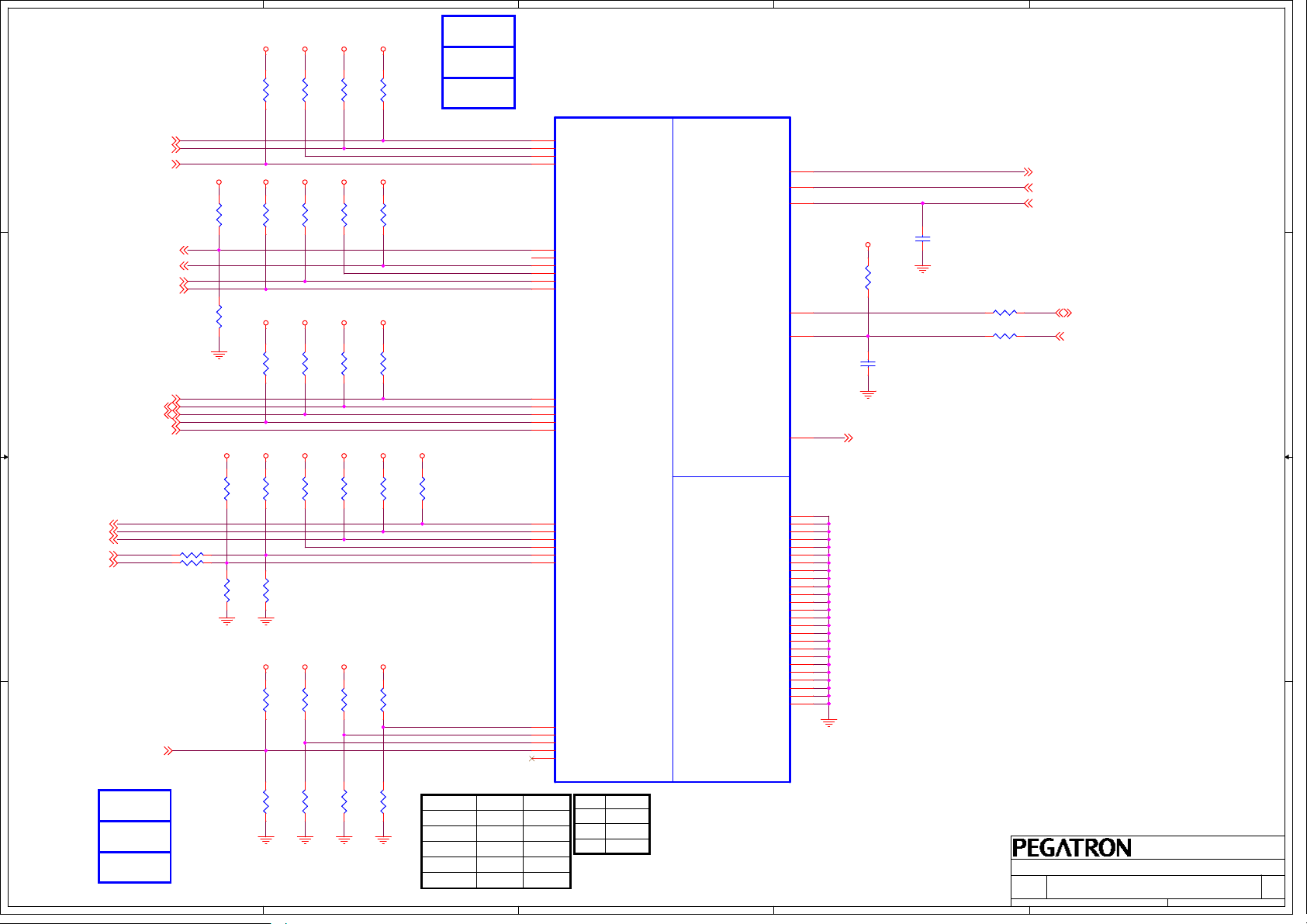

Page 2

5

4

3

2

1

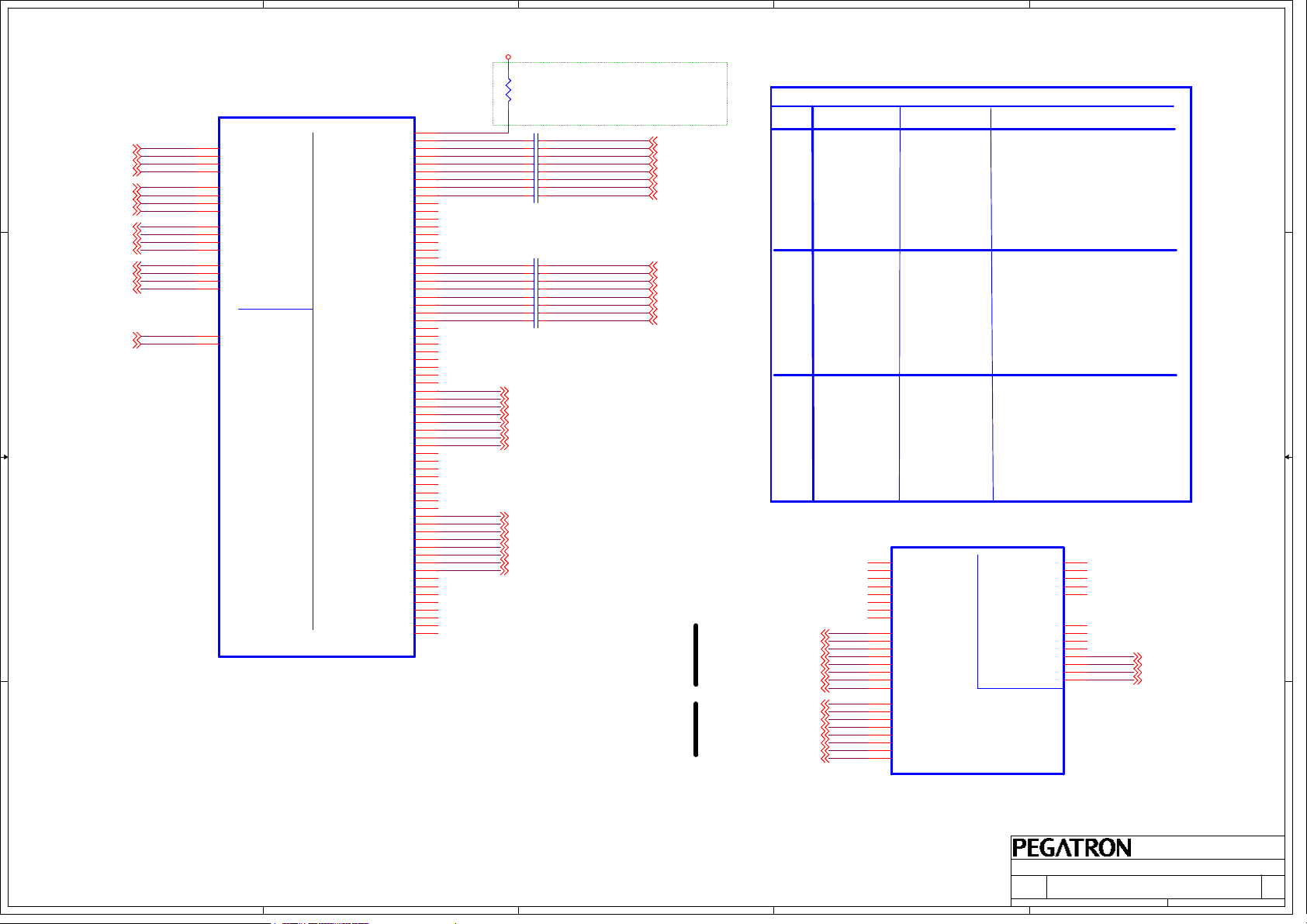

SO-DIMM2

Intel

Platform Controller Hub

D D

SO-DIMM1

32.768KHz

M_CHA[0..1]/#

SA_CK_[0:1]/#

C C

(800MHz)

M_CHB[0..1]/#

SB_CK_[0:1]/#

(800MHz)

25MHz

CLK_DMI/#

BCLK/#

CLK_DP/#

SSC_DPLL_REF_CLK/#

DPLL_REF_CLK/#

CLK_DPNS/#

RTCX

XTAL25_IN

CLKOUT_DMI/#

(100MHz)

CLKOUT_DP/#

(135MHz)

CLKOUT_DPNS/#

Lynx Point

CLKOUT_PEG_A/#

(100MHz)

CLKOUT_PCIE_/#_0

(100MHz)

CLKOUT_PCIE_/#_1

(100MHz)

CLKOUT_PCIE_/#_2

(100MHz)

CLKOUT_PCIE_/#_3

(100MHz)

HDA_BCLK

(24MHz)

CK_100M_PE8/#

CK_100M_LAN/#

CK_100M_PE1/#

CK_100M_PE2/#

CK_100M_PE3/#

AZ_BITCLK

AMD GPU

SUN XT - S3

64Bit

CLKA0/#

(1000~1500MHz)

CLKA1/#

(1000~1500MHz)

REALTEK

RTL8151GD

CLKA0/#

CLKA1/#

GDDR5-1

GDDR5-3

25 MHz

Half mini-PCIE WLAN/BT

Full mini-PCIE TV TUNER/mSATA

CARD READER

Realtek RTS5209-GR

AUDIO

Realtek ALC3661-CG

GDDR5-2

GDDR5-4

(135MHz)

B B

Intel Processor

CLKOUTFLEX3

(48MHz)

CLKOUT_33MHZ2

Hasewell

(33MHz)

SPI_CLK

(20/33/50MHz)

CPU - XDP

CK_100M_CPUXDP/#

CLKOUT_ITPXDP/#

(100MHz)

CLKOUT_33MHZ3

(33MHz)

CK_48M_SIO1

CK_33M_SIO1

SPI_CLK

CK_33M_DEBUG

Super I/O

Fintek F71808AU

SPI ROM

LPC Debug Port

MSTAR

Scalar

TSUMU88BDC2-1

14.318MKHz

PCH - XDP

CLKIN_33MHZILOOPBACK

(33MHz)

A A

CLKOUT_33MHZ1

(33MHz)

5

4

3

CLK_PCI_FB

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

2 83Thursday, June 27 , 2013

2 83Thursday, June 27 , 2013

2 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

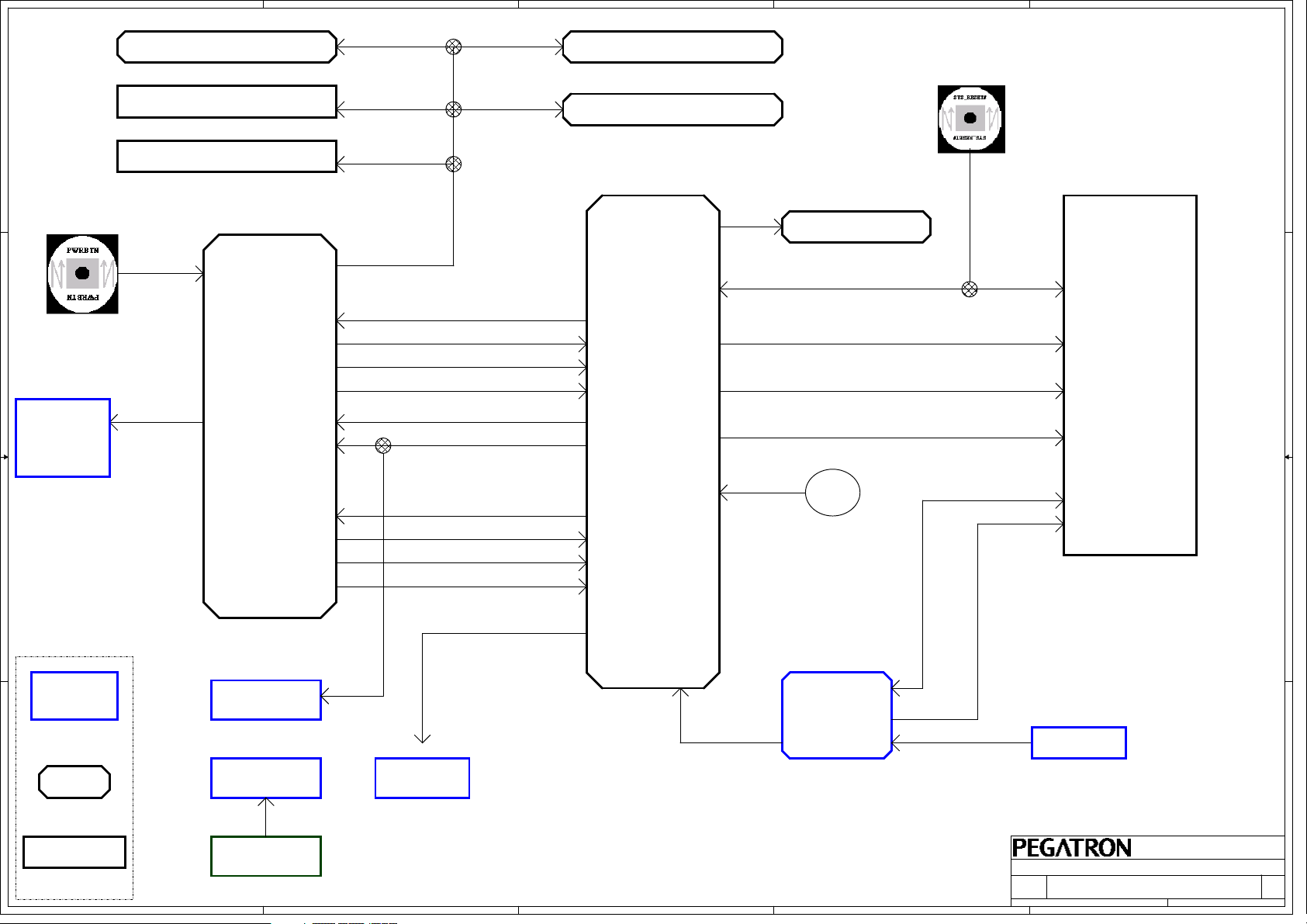

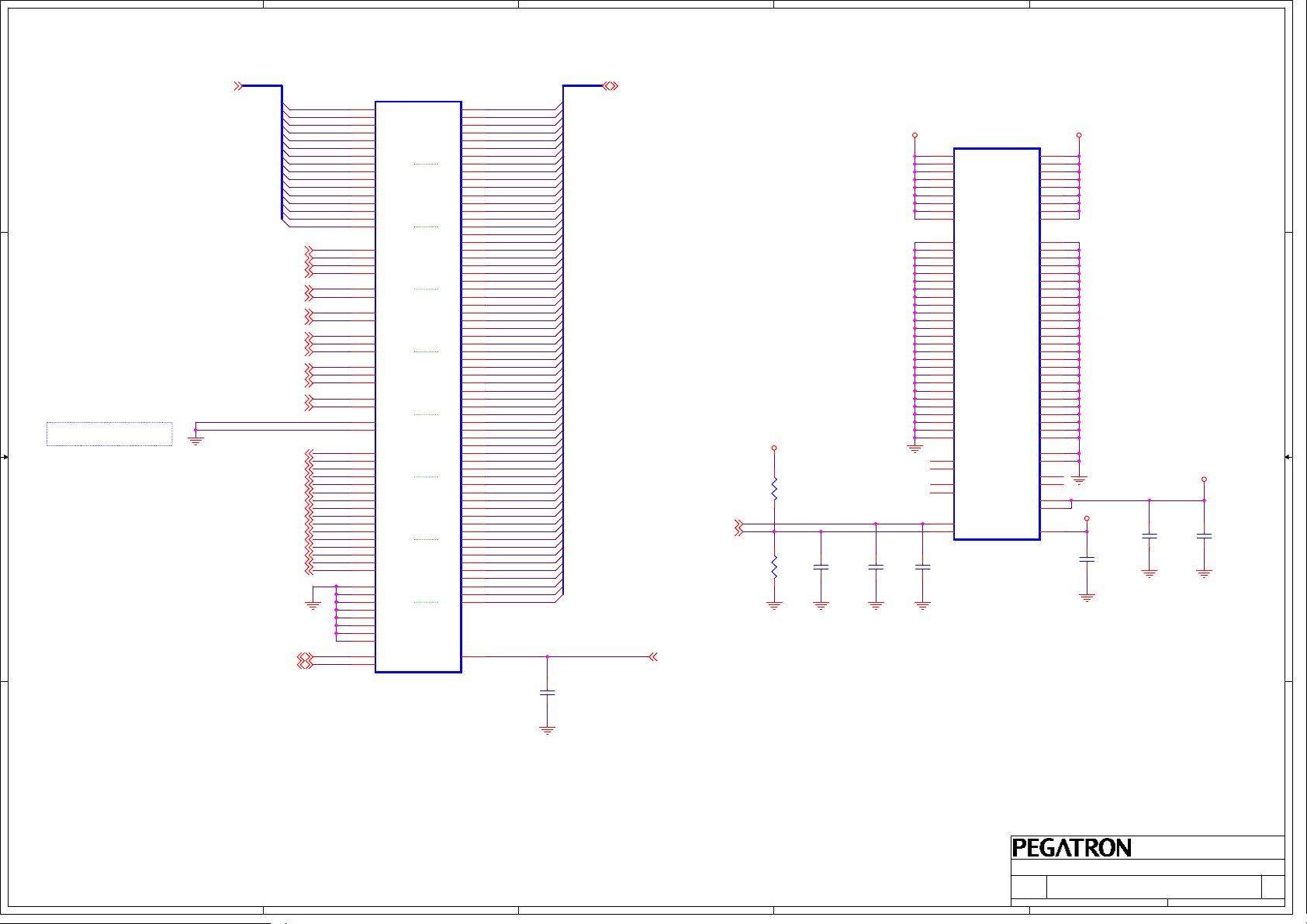

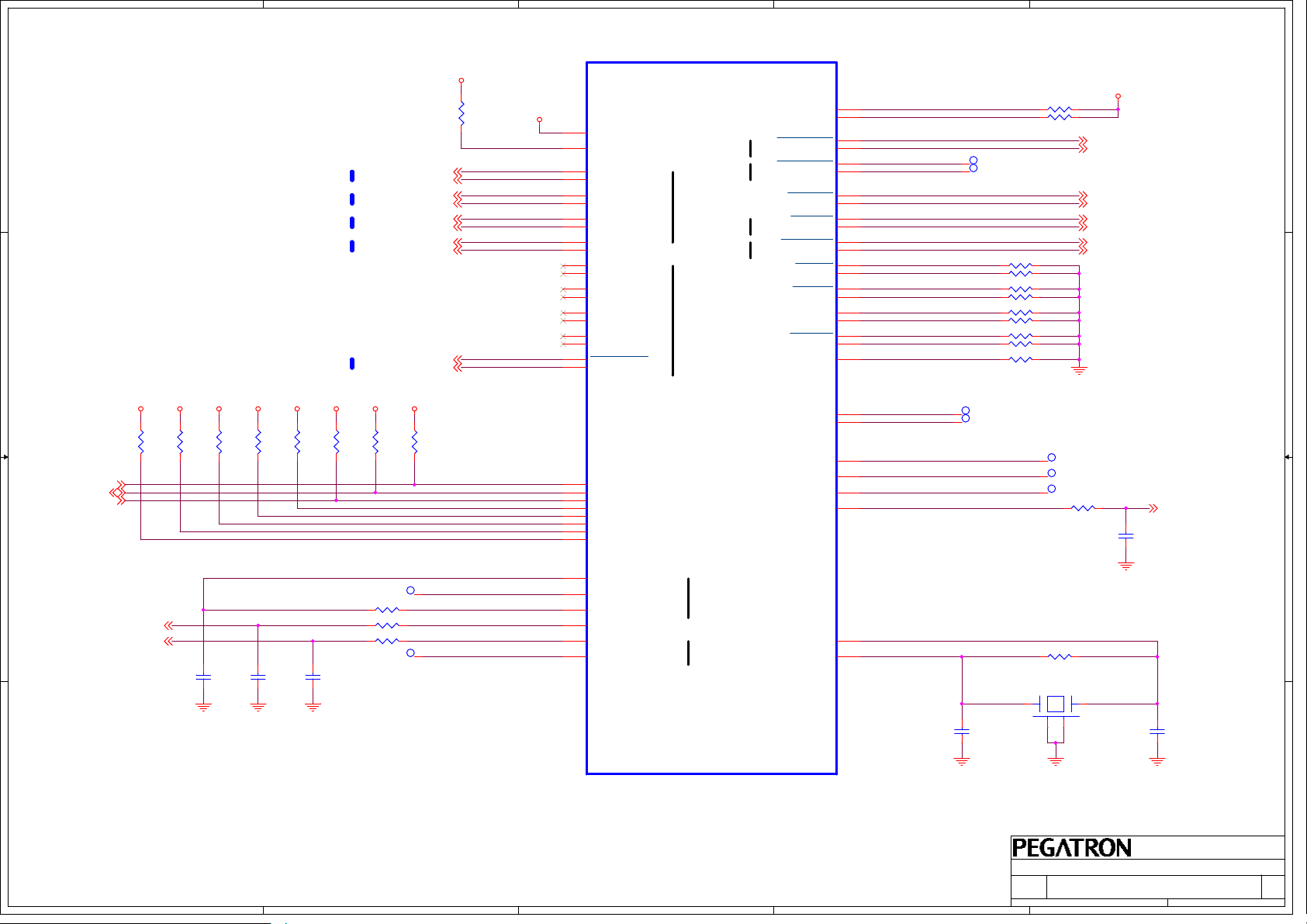

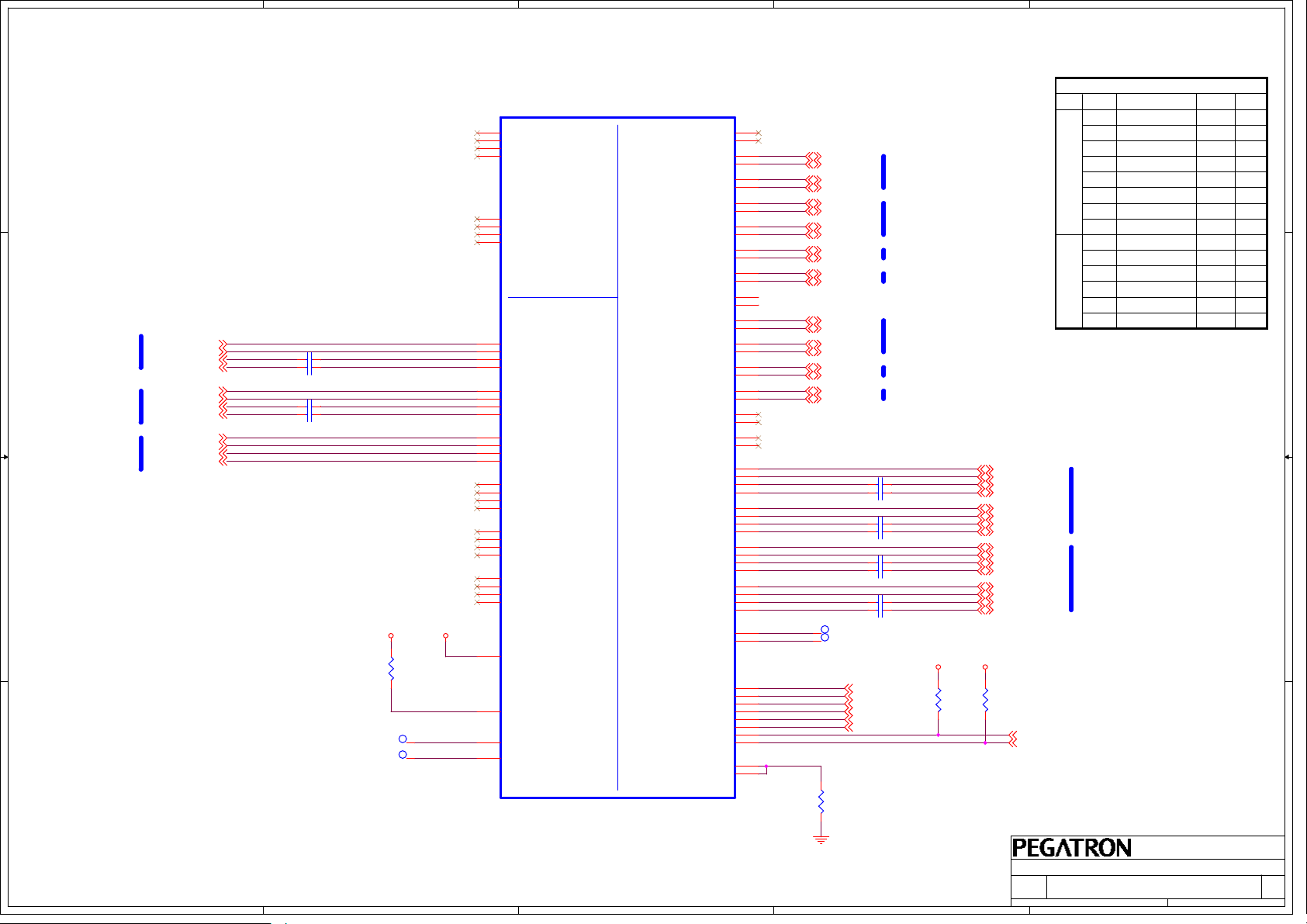

Page 3

5

LAN RTL8151GD-CG

RESET#

4

GPU SUN XT

RESET#

3

2

1

Intel SharkBay and DSW supported

Mini Express x 1 (Half Card)

D D

Mini Express x 1 (Full Card)

PERST#

CARDER READER RTS5209-GR

RESET#

RESET_SWITCH

PERST#

LYNXPOINT PCH

HASWELL PROCESSOR

AUDIO ALC3661-CG

POWER_SWITCH

<5> PWRBTN#

C C

MAIN POWER

+5V

+3P3V

+1P5V

+1P2V

+1P05V

B B

<14> PSON#

Fintek SIO F71808AU

PSIN#

PSON#

PCIRST2#

PCIRST1#

LRESET#

KBRST# RCIN#

RSMRST#

PSOUT# PWRBTN#

S3# SLP_S3#

S4#

SUS_WARN#

SUS_ACK#

DPWROK

PWROK

<23> PCIE_RST#

<22> PLTRST#

<8> RSMRST#

<5> SB_PWRBTN#

<13> SLP_S3#<15> +19V

<11> SLP_S4#

<9> SUS_WARN#

<10> SUS_ACK#

<4> PCH_DPWROK

<16> PWROK

RST_KB#

PLTRST#

RSMRST#

SLP_S4#

SLP_A#

SLP_LAN#

SUS_WARN#

SUS_ACK#

DPWROK

PWROK

DRAMPWROK

PROCPWRGD PWRGOOD

PLTRST_PROC#

RTCRST#

APWROK

<6> SLP_SUS#

SLP_SUS#

AZ_RST#

<1> RTCRST#

RESET#HDA_RST#

SYS_RESET#

<17> PM_DRAM_PWRGD

<18> H_CPUPWRGD

<22> PLTRST_CPU#

BATTERY

<16~18> SVIDs

<19> LOAD SVIDs

DBR#SYS_RESET#

SM_DRAMPWROK

PLTRSTIN#

VIDSOUT/VIDSCLK

VCORE

DUAL POWER

<12> +5V_DUAL

+1P35V_DUAL

ONBOARD POWER

ALWAYS POWER

<3> +5VA

A A

CHIP

+3VA

<2> +19VA

STANDBY POWER

<7> +5VSB

+3VSB

SYS_PWROK

<21> VRM_PWRGD

+19V Adapter PSU

SOCKET or SLOT

5

4

3

Vcore Controller

VDIO/VCLK

VCORE

VR_RDY

TPS51631RSM

EN

<20> +VCORE

<15> +3P3V

2

MAIN POWER

+3P3V

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

POWER ON CHART

POWER ON CHART

POWER ON CHART

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

3 83Thursday, June 27 , 2013

3 83Thursday, June 27 , 2013

3 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

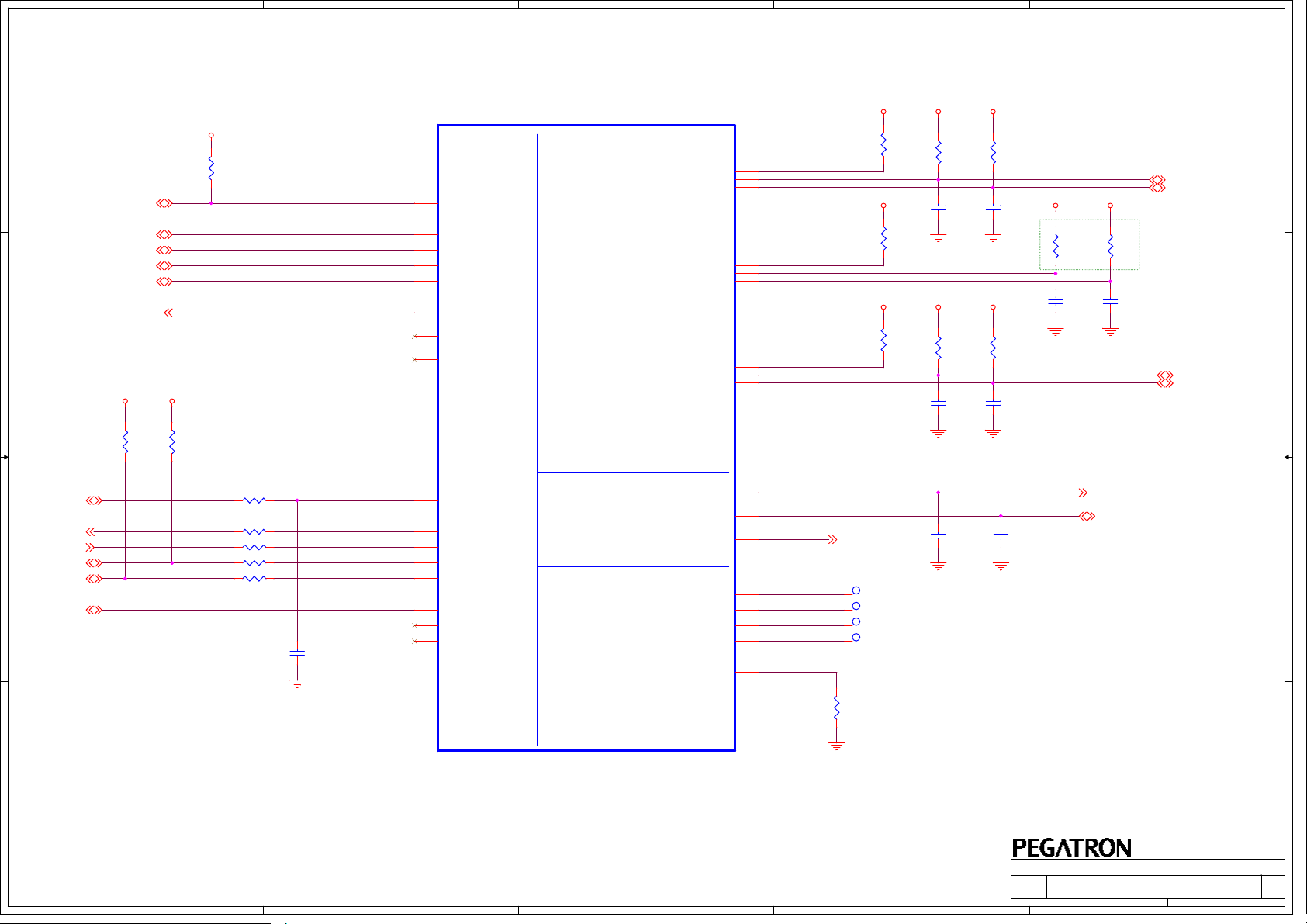

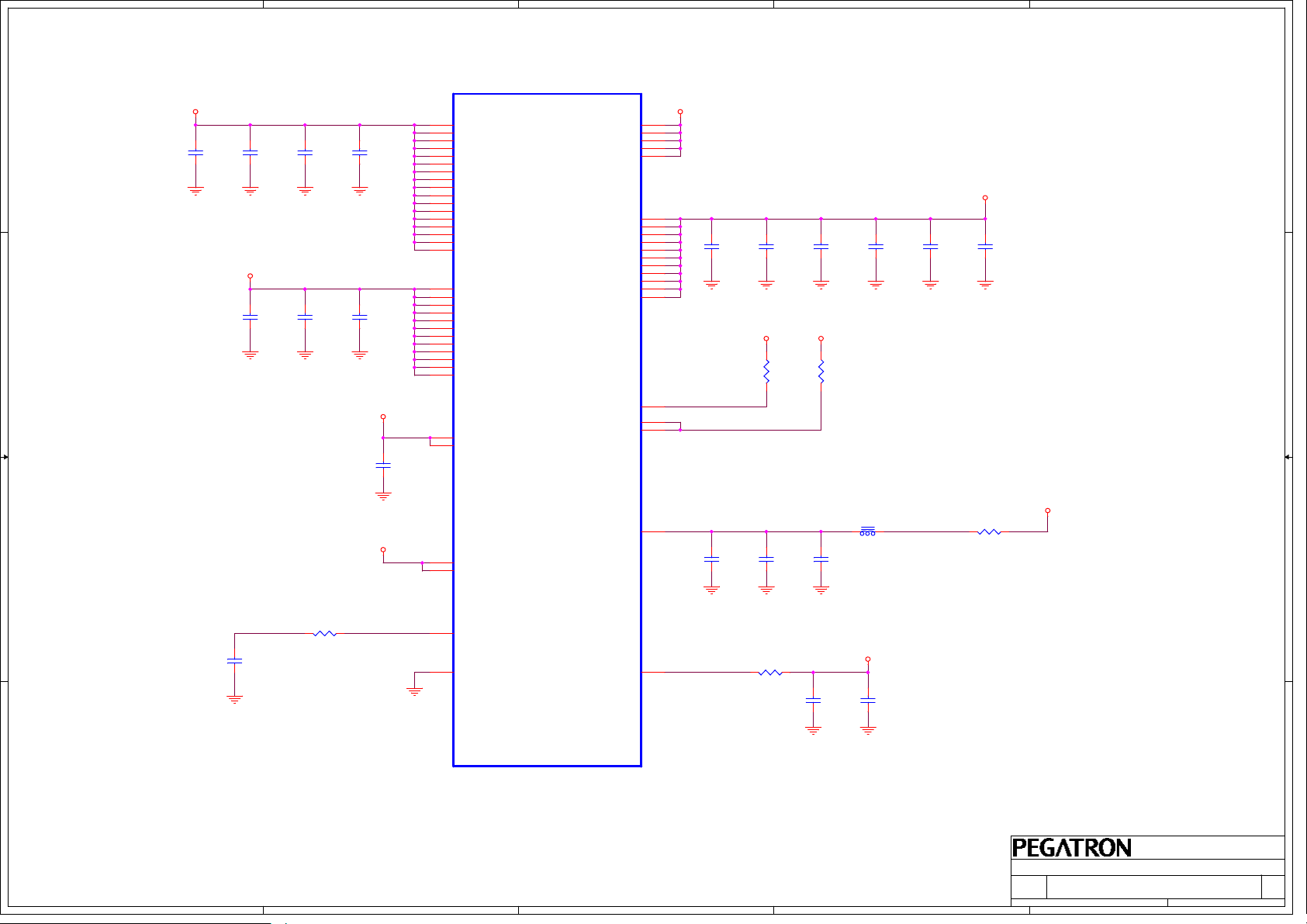

Page 4

5

Schematics Change History

Schematics Change History

Schematics Change HistorySchematics Change History

Version

Version

VersionVersion

1.00

D D

C C

Date

Date

DateDate

Description

Description

DescriptionDescription

4

3

2

Comments

Comments

CommentsComments

1

B B

A A

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

CHANGE HISTORY

CHANGE HISTORY

CHANGE HISTORY

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

4 83Thursday, June 27 , 2013

4 83Thursday, June 27 , 2013

4 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

Page 5

5

4

3

2

1

S0 S1 S3 S4 S5

DS5 G3

+19VSB

MOS - ON/OFF

PAGE. 66

D D

TI-TPS51631

( 3-PHASE )

MOS - ON/OFF

PAGE. 66

+19V_BL Imax=2. 1A/TDC=1.47A

+19V Imax=0.58A /TDC=0.404A

+VCORE Imax=85A /TDC=27A

PAGE. 76,77,78

4

Imax=14.6A

TDC=10.22A

Imax=25.8A

TDC=17.6A

Imax=7.47A

TDC=5.23A

Imax=10.8A

TDC=5.83A

MOS - ON/OFF

PAGE. 71

LM358 + MOS

PAGE. 74

LM358 + MOS

PAGE. 74

LM358 + MOS

PAGE. 71

LM358 + MOS

PAGE. 70

MOS - ON/OFF

PAGE. 66

MOS - ON/OFF

PAGE. 69

MOS - ON/OFF

PAGE. 70

MOS - ON/OFF

PAGE. 66

MOS - ON/OFF

PAGE. 66

3

PAGE. 25

PAGE. 25

+1P5V Imax=1.25 3A/TDC=0.927A

+1P35V_GPU Imax =6.93A/TDC=4.8A

+1P2V Imax=0.5 A/TDC=0.35A

+1P05V_PCH Imax =5.921A/TDC=4.1 447A

+1P05V_ME

+1P35V_DUAL Ima x=9.32A/TDC=6.5 24A

+VTT_DDR Imax= 1.43A/TDC=1A

+VDDCI Imax=9A /TDC=6A

+0P95V_GPU Ima x=6.03A/TDC=4.0 2A

+5VSB Imax=0.5A /TDC=0.35A

+3P3VSB Imax=5. 8944A/TDC=2.476 A

+5VA Imax=0.00 14A /TDC=0.005A

+3VA Imax=0.015 A/TDC=0.011A

+3P3V Imax=2.8 47A/TDC=2.0005A

+3P3V_ME

+3P3V_GPU Imax= 0.086A/TDC=0.06 A

+1P8V_MXM Imax =1.94A/TDC=1.29 A

+5V Imax=1.57A /TDC=1.1A

+5V_DUAL Imax=5 .4A/TDC=3.78A

+VDDC Imax=37.5 A/TDC=25A

+BATT

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

POWER FLOW

POWER FLOW

POWER FLOW

Stonko_Chen

Stonko_Chen

Stonko_Chen

5 83Thursday, June 27 , 2013

5 83Thursday, June 27 , 2013

5 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

TI-TPS51211

( 1-PHASE )

PAGE. 68

C C

TI-TPS51216

( 1-PHASE )

PAGE. 67

+19VA_VIN

+19VSB

19VIN

OVP/UVP

Protection

PAGE. 67

PAGE. 67

B B

A A

BATTERY

TI-TPS51225

( 1-PHASE )

PAGE. 75

RICHTEK

RT8153C

( 1-PHASE )

PAGE. 72, 73

SWITCHING Linear ON / OFF

5

Page 6

5

4

3

2

1

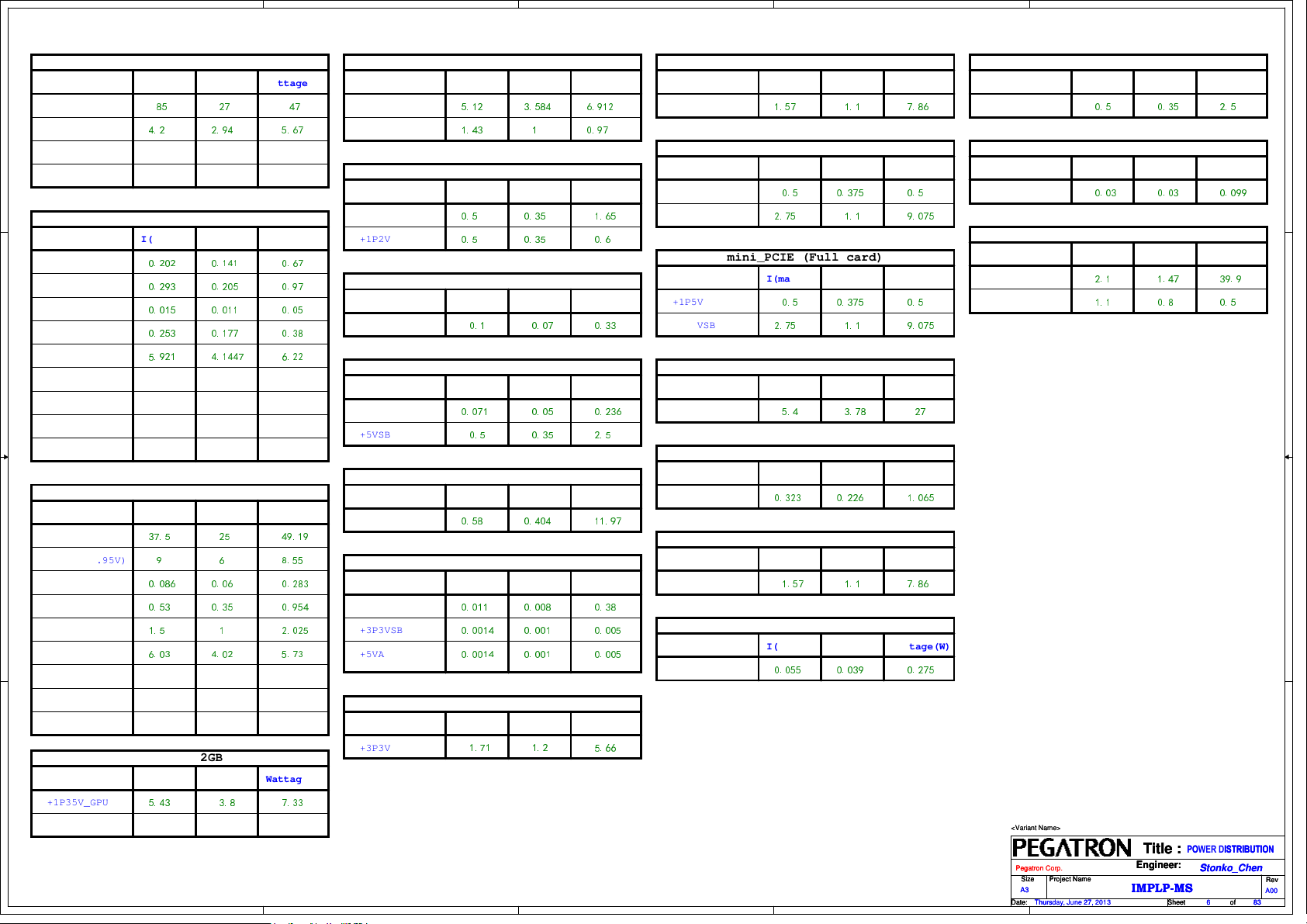

Intel Haswell CPU

Wattage(W)TDC (A)I(max)(A)

+VCORE

D D

+1P35V_DUAL

2785

2.944.2 5.67

47

Intel PCH - Lynx Point HM87

I(max)(A) TDC (A) Wattage(W)

+3P3V

+3P3VSB

+3VA

+1P5V

C C

+1P05V_PCH

0.202 0.141 0.67

0.293 0.970.205

0.015 0.050.011

0.253 0.177 0.38

5.921

6.224.1447

+1P35V_DUAL

+VTT_DDR

+3P3V

+1P2V

+3P3VSB

+3P3V

+5VSB

SO - DIMM x 2 (DDR3L)

Wattage(W)TDC (A)I(max)(A)

5.12 3.584 6.912

11.43 0.97

Scalar - MSTAR TSUMU88BDC2-1

Wattage(W)TDC (A)I(max)(A)

0.5

0.5

0.35

0.35

LOM - Realtek RTL8151GD

Wattage(W)TDC (A)I(max)(A)

0.1 0.07 0.33

Audio - Realtek ALC3661-CG

Wattage(W)TDC (A)I(max)(A)

0.071

0.5

0.05

0.35

1.65

0.6

0.236

2.5

SATA 3.0 (1-Port for 2.5" HDD)

+5V

1.57 1.1 7.86

mini_PCIE (Half card)

+1P5V

+3P3VSB

0.5 0.50.375

2.75 9.0751.1

mini_PCIE (Full card)

I(max)(A) TDC (A) Wattage(W)

+1P5V

+3P3VSB

2.75

0.375 0.50.5

1.1 9.075

USB3.0 ( 6-Ports )

TDC (A) Wattage(W)I(max)(A)

+5V_DUAL

5.4 273.78

FAN

Wattage(W)TDC (A)I(max)(A)

+5V

0.5 2.50.35

TDC (A) Wattage(W)I(max)(A)

SPI

Wattage(W)TDC (A)I(max)(A)

+3P3V

0.03 0.099

TDC (A) Wattage(W)I(max)(A)

0.03

PANEL

Wattage(W)TDC (A)I(max)(A)

+19V_BL

+5V_LCD

2.1 39.91.47

1.1 0.50.8

Webcam

Audio AMP - TPA3110D2PWPR

AMD GPU - SUN-XT (64bit)

I(max)(A) TDC (A) Wattage(W)

+VDDC(1.125V)

+VDDCI(0.95V)

B B

+3P3V_GPU

+1P8V_MXM

0.086 0.06 0.283

0.53 0.35 0.954

+1P35V_GPU

+0P95V_GPU

2537.5 49.19

69 8.55

11.5

2.025

4.026.03 5.73

+19V

+3P3V

+3P3VSB

+5VA

0.58 0.404 11.97

SIO - Fintek F71808AU

0.011

0.0014

0.008

0.001

0.0010.0014 0.005

Wattage(W)TDC (A)I(max)(A)

+3P3V

0.323 1.0650.226

Touch

Wattage(W)TDC (A)I(max)(A)

0.38

0.005

+5V_DUAL

+5V

1.57 7.861.1

HDMI

0.055 0.2750.039

TDC (A) Wattage(W)I(max)(A)

TDC (A) Wattage(W)I(max)(A)

TDC (A) Wattage(W)I(max)(A)

Card Reader - Realtek RTS5209-GR

Wattage(W)TDC (A)I(max)(A)

GDDR5 - 2GB

+3P3V

Wattage(W)TDC (A)I(max)(A)

A A

+1P35V_GPU

5

3.85.43 7.33

4

1.71 1.2 5.66

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

POWER DISTRIBUTION

POWER DISTRIBUTION

POWER DISTRIBUTION

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Engineer:

IMPLP-MS

IMPLP-MS

IMPLP-MS

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

6 83Thursday, June 27 , 2013

6 83Thursday, June 27 , 2013

6 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

Page 7

5

VCCRTC

G3

S5

DSW

t200: >9mS

S5/S4/S3

4

S0

3

2

1

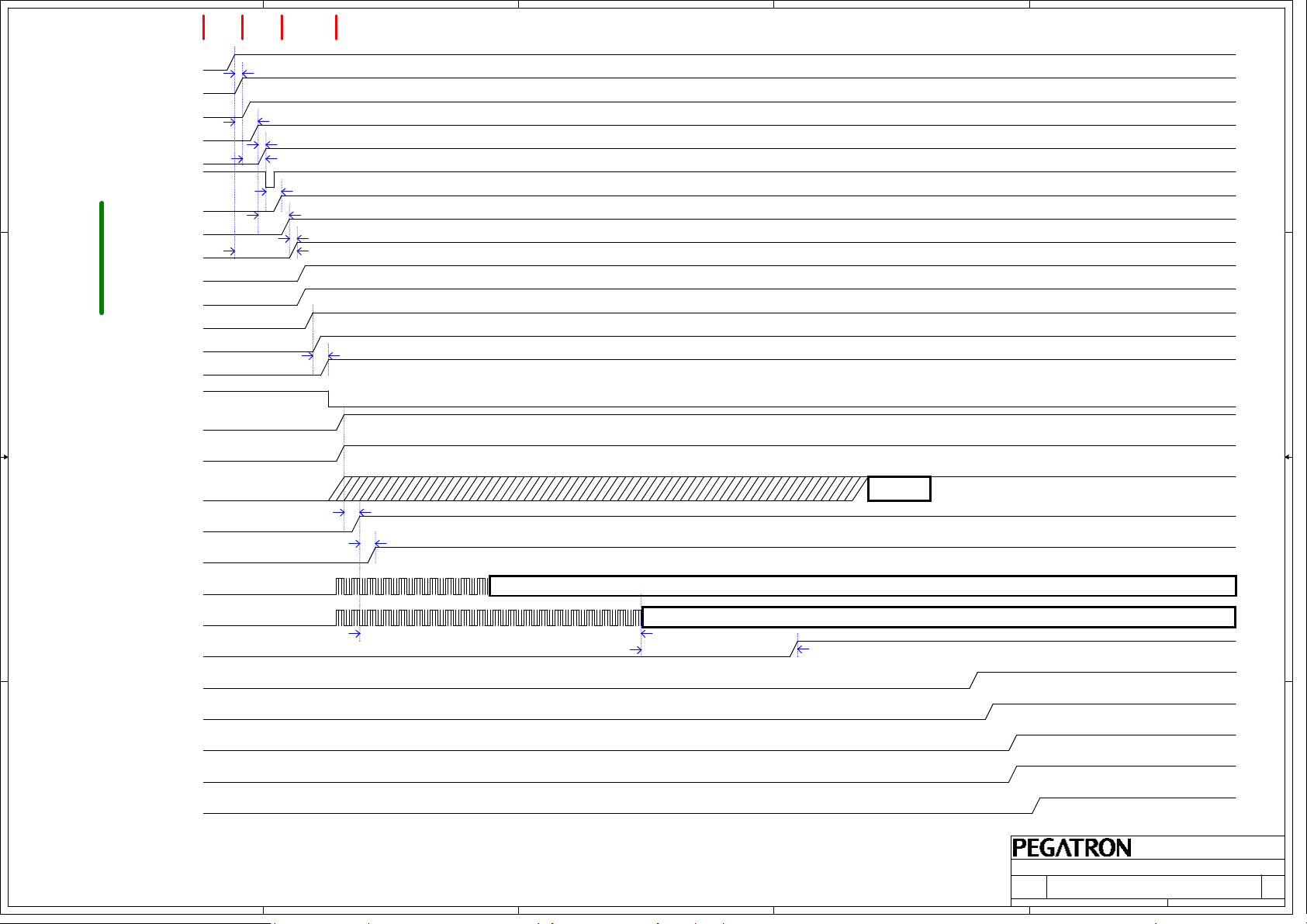

G3 to S0 Power Sequence

RTCRST#

D D

+19VA

+5VA / +3VA

DPWROK

PWRBTN#

SLP_SUS#

+5VSB / +3VSB

DSW exit

RSMRST#

t225: >0mS

t200b: >10mS

t200a: >0mS

t202: >95mS

t200c: >0mS

t201: >10mS

t226: >20nS

SUS_WARN#

SUS_ACK#

SLP_S4#

C C

+5V_DUAL / +1P35V_DUAL

t204: >30uS

SLP_S3#

PSON#

+19V / +5V / +3P3V /

+1P5V / +1P2V / +1P05V

VCORE_EN

VIDSCLK / VIDSOUT

PWROK

t205a: >5mS

t223: >0uS

Serial VID

Load

B B

25MHz CRYSTAL OSC

PCH OUTPUT CLOCKs

DRAMPWROK

PROCPWRGD

25MHz CLK Stable

PCH Output CLK Stable

t208: >1mS

t209: >1mS

+VCORE

VRM_PWRGD

PLTRST_PROC#

PLTRST#

A A

PCIE_RST#

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

POWER SEQUENCE

POWER SEQUENCE

POWER SEQUENCE

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

7 83Thursday, June 27 , 2013

7 83Thursday, June 27 , 2013

7 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

Page 8

5

I

XU1A

D D

DMI_TXN019

DMI_TXN119

DMI_TXN219

DMI_TXN319

DMI_TXP019

DMI_TXP119

DMI_TXP219

DMI_TXP319

DMI_RXN019

DMI_RXN119

DMI_RXN219

DMI_RXN319

DMI_RXP019

DMI_RXP119

DMI_RXP219

DMI_RXP319

FDI_CSYNC19

C C

B B

A A

FDI_INT19

Haswell rPGA

D21

C21

B21

A21

D20

C20

B20

A20

D18

C17

B17

A17

D17

C18

B18

A18

H29

J29

SOCKET_ 947P

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

FDI_CSYNC

DISP_INT

DMI FDI

PEG_RCOMP

PEG_RXN_0

PEG_RXN_1

PEG_RXN_2

PEG_RXN_3

PEG_RXN_4

PEG_RXN_5

PEG_RXN_6

PEG_RXN_7

PEG_RXN_8

PEG_RXN_9

PEG_RXN_10

PEG_RXN_11

PEG_RXN_12

PEG_RXN_13

PEG_RXN_14

PEG_RXN_15

PEG_RXP_0

PEG_RXP_1

PEG_RXP_2

PEG_RXP_3

PEG_RXP_4

PEG_RXP_5

PEG_RXP_6

PEG_RXP_7

PEG_RXP_8

PEG

PEG_RXP_9

PEG_RXP_10

PEG_RXP_11

PEG_RXP_12

PEG_RXP_13

PEG_RXP_14

PEG_RXP_15

PEG_TXN_0

PEG_TXN_1

PEG_TXN_2

PEG_TXN_3

PEG_TXN_4

PEG_TXN_5

PEG_TXN_6

PEG_TXN_7

PEG_TXN_8

PEG_TXN_9

PEG_TXN_10

PEG_TXN_11

PEG_TXN_12

PEG_TXN_13

PEG_TXN_14

PEG_TXN_15

PEG_TXP_0

PEG_TXP_1

PEG_TXP_2

PEG_TXP_3

PEG_TXP_4

PEG_TXP_5

PEG_TXP_6

PEG_TXP_7

PEG_TXP_8

PEG_TXP_9

PEG_TXP_10

PEG_TXP_11

PEG_TXP_12

PEG_TXP_13

PEG_TXP_14

PEG_TXP_15

4

+VCOMP_ OUT

12

I

HR61

24.9

NOTE:

1%

E23

H_PEG_R COMP

M29

PEG_RXN _7

K28

PEG_RXN _6

M31

PEG_RXN _5

L30

PEG_RXN _4

M33

PEG_RXN _3

L32

PEG_RXN _2

M35

PEG_RXN _1

L34

PEG_RXN _0

E29

D28

E31

D30

E35

D34

E33

E32

L29

PEG_RXP _7

L28

PEG_RXP _6

L31

PEG_RXP _5

K30

PEG_RXP _4

L33

PEG_RXP _3

K32

PEG_RXP _2

L35

PEG_RXP _1

K34

PEG_RXP _0

F29

E28

F31

E30

F35

E34

F33

D32

H35

H34

J33

H32

J31

G30

C33

B32

B31

A30

B29

A28

B27

A26

B25

A24

J35

G34

H33

G32

H31

H30

B33

A32

C31

B30

C29

B28

C27

B26

C25

B24

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

I_GPU

W/S=12/15 mil, length<400mil

1 2

HC89 0.22UF/10 V

1 2

HC90 0.22UF/10 V

1 2

HC91 0.22UF/10 V

1 2

HC92 0.22UF/10 V

1 2

HC93 0.22UF/10 V

1 2

HC94 0.22UF/10 V

1 2

HC95 0.22UF/10 V

1 2

HC96 0.22UF/10 V

NOTE:

PCIE X8 Reversed

1 2

HC98 0.22UF/10 V

1 2

HC97 0.22UF/10 V

1 2

HC99 0.22UF/10 V

1 2

HC100 0.22UF/10V

1 2

HC101 0.22UF/10V

1 2

HC102 0.22UF/10V

1 2

HC103 0.22UF/10V

1 2

HC104 0.22UF/10V

EXP_TXN 7 53

EXP_TXN 6 53

EXP_TXN 5 53

EXP_TXN 4 53

EXP_TXN 3 53

EXP_TXN 2 53

EXP_TXN 1 53

EXP_TXN 0 53

EXP_TXP 7 53

EXP_TXP 6 53

EXP_TXP 5 53

EXP_TXP 4 53

EXP_TXP 3 53

EXP_TXP 2 53

EXP_TXP 1 53

EXP_TXP 0 53

3

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

X7R 10%

EXP_RXN 7 53

EXP_RXN 6 53

EXP_RXN 5 53

EXP_RXN 4 53

EXP_RXN 3 53

EXP_RXN 2 53

EXP_RXN 1 53

EXP_RXN 0 53

EXP_RXP 7 53

EXP_RXP 6 53

EXP_RXP 5 53

EXP_RXP 4 53

EXP_RXP 3 53

EXP_RXP 2 53

EXP_RXP 1 53

EXP_RXP 0 53

To Scalar

To HDMI-Out

Connector

2

1

Configuration-wise Mapping of HDMI signals for Processor on DDI ports

DDI

Port

Differential Pairs

DPB_LANE0_P

DPB_LANE0_N

DPB_LANE1_P

DPB_LANE1_N

DPB_LANE2_P

Port B

DPB_LANE2_N

DPB_LANE3_P

DPB_LANE3_N

DDPB_HPD

DDPB_CTRLCLK

DDPB_CTRLDATA

DPC_LANE0_P

DPC_LANE0_N

DPC_LANE1_P

DPC_LANE1_N

DPC_LANE2_P

Port C

Port D

HDMIC_TMD SC_DATA2#28

HDMIC_TMD SC_DATA228

HDMIC_TMD SC_DATA1#28

HDMIC_TMD SC_DATA128

HDMIC_TMD SC_DATA0#28

HDMIC_TMD SC_DATA028

HDMIC_TMD SC_CLK#28

HDMIC_TMD SC_CLK28

HDMID_TMD SD_DATA0#32

HDMID_TMD SD_DATA032

HDMID_TMD SD_DATA1#32

HDMID_TMD SD_DATA132

HDMID_TMD SD_DATA2#32

HDMID_TMD SD_DATA232

HDMID_TMD SD_CLK#32

HDMID_TMD SD_CLK32

DPC_LANE2_N

DPC_LANE3_P

DPC_LANE3_N

DDPC_HPD

DDPC_CTRLCLK

DDPC_CTRLDATA

DPD_LANE0_P

DPD_LANE0_N

DPD_LANE1_P

DPD_LANE1_N

DPD_LANE2_P

DPD_LANE2_N

DPC_LANE3_P

DPC_LANE3_N

DDPD_HPD

DDPD_CTRLCLK

DDPD_CTRLDATA

HDMI

Signals

HDMIB_DATA2_P

HDMIB_DATA2_N

HDMIB_DATA1_P

HDMIB_DATA1_N

HDMIB_DATA0_P

HDMIB_DATA0_N

HDMIB_CK_P

HDMIB_CK_N

DDSP_1_HPD0

DPB_CTRL_CK

DPB_CTRL_DATA

I

XU1H

Haswell rPGA

T28

DDIB_TXBN_0

U28

DDIB_TXBP_0

T30

DDIB_TXBN_1

U30

DDIB_TXBP_1

U29

DDIB_TXBN_2

V29

DDIB_TXBP_2

U31

DDIB_TXBN_3

V31

DDIB_TXBP_3

T34

DDIC_TXCN_0

U34

DDIC_TXCP_0

U35

DDIC_TXCN_1

V35

DDIC_TXCP_1

U32

DDIC_TXCN_2

T32

DDIC_TXCP_2

U33

DDIC_TXCN_3

V33

DDIC_TXCP_3

P29

DDID_TXDN_0

R29

DDID_TXDP_0

N28

DDID_TXDN_1

P28

DDID_TXDP_1

P31

DDID_TXDN_2

R31

DDID_TXDP_2

N30

DDID_TXDN_3

P30

DDID_TXDP_3

SOCKET_ 947P

HDMIC_TX2_DP

HDMIC_TX2_DN

HDMIC_TX1_DP

HDMIC_TX1_DN

HDMIC_TX0_DP

HDMIC_TX0_DN

HDMIC_CLK_DP

HDMIC_CLK_DN

DDSP_2_HPD1

DPC_CTRL_CK

DPC_CTRL_DATA

HDMID_TX2_DP

HDMID_TX2_DN

HDMID_TX1_DP

HDMID_TX1_DN

HDMID_TX0_DP

HDMID_TX0_DN

HDMID_CLK_DP

HDMID_CLK_DN

DDSP_3_HPD2

DPD_CTRL_CK

DPD_CTRL_DATA

DDI

Processor DDI Pins

DDIB_TXP0

DDIB_TXN0

DDIB_TXP1

DDIB_TXBN1

DDIB_TXBP2

DDIB_TXBN2

DDIB_TXBP3

DDIB_TXBN3

Hot plug detect used by HDMI Port B

HDMI DDC lines for Port B

HDMI DDC lines for Port B

DDIC_TXP0

DDIC_TXN0

DDIC_TXP1

DDIC_TXBN1

DDIC_TXBP2

DDIC_TXBN2

DDIC_TXBP3

DDIC_TXBN3

Hot plug detect used by HDMI Port C

HDMI DDC lines for Port C

HDMI DDC lines for Port C

DDID_TXP0

DDID_TXN0

DDID_TXP1

DDID_TXBN1

DDID_TXBP2

DDID_TXBN2

DDID_TXBP3

DDID_TXBN3

Hot plug detect used by HDMI Port D

HDMI DDC lines for Port D

HDMI DDC lines for Port D

EDP_AUXP

EDP_HPD

FDI_TXN_0

FDI_TXP_0

FDI_TXN_1

FDI_TXP_1

M27

N27

P27

E24

R27

P35

R35

N34

P34

P33

R33

N32

P32

EDP_DISP_UTIL

eDP

EDP_AUXN

EDP_RCOMP

EDP_TXN_0

EDP_TXP_0

EDP_TXN_1

EDP_TXP_1

FDI_TXN0 19

FDI_TXP0 19

FDI_TXN1 19

FDI_TXP1 19

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

CPU_DMI,FDI,PEG,DDI

CPU_DMI,FDI,PEG,DDI

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

CPU_DMI,FDI,PEG,DDI

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

8 83Thursday, June 27 , 2013

8 83Thursday, June 27 , 2013

8 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

Page 9

5

D D

+1P05V_ PCH

NI

HR134

0

PROCHOT _SIO#36

PROCHOT #64,76

H_THRMT RIP#23

C C

B B

PECI_SIO23,36

PM_DRAM _PWRGD19

H_PM_SYNC19

PLTRST_ CPU#23,50

H_CPUPW RGD2 3,50

1 2

+1P35V_ DUAL +1V_CPUIOOU T

12

I

HR3

1.8K

12

I

HR4

3.3K

+1V_CPU IOOUT +1P05V_PCH

12

NI

HR126

0

12

NI

HC105

47PF/50V

NPO 5%

GND

12

NI

HR130

4.7K

12

NI

HR128

47PF/50V

NPO 5%

4

12

I

HR1

62

HR2 56

I

HR127 43

I

Close to SIO Side

1 2

12

NOBOM

NOBOM

12

1 2

1 2

I

HR132

0

I

HR6

10K

HT7

HT8

NI

HR125

0

PM_DRAM _PWRGD_R

1

1

H_PROCH OT#_D

AP32

AN32

AK31

AM30

AM35

AR27

AC10

AT28

AT26

AL34

I

XU1B

Haswell rPGA

SKTOCC#

CATERR#

THERMAL

FC1

PROCHOT#

THERMTRIP#

PECI

SM_DRAMPWROK

PM_SYNC

PLTRSTIN#

PWRGOOD

MISC

PWR

3

AP3

SM_RCOMP_0

SM_RCOMP_1

SM_RCOMP_2

AR3

AP2

SM_RCOM P0

SM_RCOM P1

SM_RCOM P2

DDR3

BPM_N_0

BPM_N_1

BPM_N_2

BPM_N_3

BPM_N_4

BPM_N_5

BPM_N_6

BPM_N_7

PRDY#

PREQ#

TDO

TMS

TRST#

TCK

AN3

AR30

AN31

AN29

H_BPM2

AP31

H_BPM3

AP30

H_BPM4

AN28

H_BPM5

AP29

H_BPM6

AP28

H_BPM7

AR29

AT29

AM31

TDI

AL33

AN33

AM33

AM34

1

1

1

1

1

1

12

I

SR133

51

SM_DRAMRST#

JTAG

2

1 2

HR7 100 1%

I

1 2

HR8 75 1 %

I

1 2

HR9 100 1%

I

HT1

NOBOM

HT2

NOBOM

HT3

NOBOM

HT4

NOBOM

HT5

NOBOM

HT6

NOBOM

12

I

SR134

51

SM_DRAM RST# 15,16

+1P05V_ PCH

12

I

SR135

51

1

GND

XDP_BPM 0 50

XDP_BPM 1 50

H_PRDY# 50

H_PREQ# 50

TDI 5 0

TDO 50

TMS 50

TRST# 50

TCK 50

GND GNDGND

CLK_DPN S_N20

CLK_DPN S_P20

CLK_DP_ N20

CLK_DP_ P20

CLK_DMI_N20

CLK_DMI_P20

A A

CRB

G28

DPLL_REF_CLKN

H28

DPLL_REF_CLKP

F27

SSC_DPLL_REF_CLKN

E27

SSC_DPLL_REF_CLKP

D26

BCLKN

E26

BCLKP

SOCKET_ 947P

CLOCK

DBR#

AP33

OD

GND GND

SYS_RESET # 19 ,50,51

PEGATRON DT-MB RESTRICTED SECRET

CPU_CLK,MISC,JTAG

CPU_CLK,MISC,JTAG

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

IMPLP-MS

IMPLP-MS

IMPLP-MS

CPU_CLK,MISC,JTAG

1

Stonko_Chen

Stonko_Chen

Stonko_Chen

9 83Thursday, June 27 , 2013

9 83Thursday, June 27 , 2013

9 83Thursday, June 27 , 2013

Rev

Rev

Rev

A00

A00

A00

Page 10

5

M_CHA_D Q[0..63]15 M_CHA_M AA[0..15] 15

M_CHA_D QS015

M_CHA_D QS0#15

D D

M_CHA_D QS115

M_CHA_D QS1#15

M_CHA_D QS215

M_CHA_D QS2#15

C C

M_CHA_D QS315

M_CHA_D QS3#15

M_CHA_D QS415

M_CHA_D QS4#15

B B

A A

5

M_CHA_D QS515

M_CHA_D QS5#15

M_CHA_D QS615

M_CHA_D QS6#15

M_CHA_D QS715

M_CHA_D QS7#15

4

M_CHA_D QS0

M_CHA_D QS0#

M_CHA_D Q0

M_CHA_D Q1

M_CHA_D Q2

M_CHA_D Q3

M_CHA_D Q4

M_CHA_D Q5

M_CHA_D Q6

M_CHA_D Q7

M_CHA_D QS1

M_CHA_D QS1#

M_CHA_D Q8

M_CHA_D Q9

M_CHA_D Q10

M_CHA_D Q11

M_CHA_D Q12

M_CHA_D Q13

M_CHA_D Q14

M_CHA_D Q15

M_CHA_D QS2

M_CHA_D QS2#

M_CHA_D Q16

M_CHA_D Q17

M_CHA_D Q18

M_CHA_D Q19

M_CHA_D Q20

M_CHA_D Q21

M_CHA_D Q22

M_CHA_D Q23

M_CHA_D QS3

M_CHA_D QS3#

M_CHA_D Q24

M_CHA_D Q25

M_CHA_D Q26

M_CHA_D Q27

M_CHA_D Q28

M_CHA_D Q29

M_CHA_D Q30

M_CHA_D Q31

M_CHA_D QS4

M_CHA_D QS4#

M_CHA_D Q32

M_CHA_D Q33

M_CHA_D Q34

M_CHA_D Q35

M_CHA_D Q36

M_CHA_D Q37

M_CHA_D Q38

M_CHA_D Q39

M_CHA_D QS5

M_CHA_D QS5#

M_CHA_D Q40

M_CHA_D Q41

M_CHA_D Q42

M_CHA_D Q43

M_CHA_D Q44

M_CHA_D Q45

M_CHA_D Q46

M_CHA_D Q47

M_CHA_D QS6

M_CHA_D QS6#

M_CHA_D Q48

M_CHA_D Q49

M_CHA_D Q50

M_CHA_D Q51

M_CHA_D Q52

M_CHA_D Q53

M_CHA_D Q54

M_CHA_D Q55

M_CHA_D QS7

M_CHA_D QS7#

M_CHA_D Q56

M_CHA_D Q57

M_CHA_D Q58

M_CHA_D Q59

M_CHA_D Q60

M_CHA_D Q61

M_CHA_D Q62

M_CHA_D Q63

4

AP14

AP15

AR15

AT14

AM14

AN14

AT15

AR14

AN15

AM15

AP9

AP8

AM9

AN9

AM8

AN8

AR9

AT9

AR8

AT8

AK8

AK9

AK6

AJ10

AK10

AK7

AG3

AF3

AF4

AF5

AF1

AF2

AG4

AG5

AG1

AG2

C12

C11

E12

D12

B11

A11

E11

D11

B12

A12

AJ8

AJ9

AJ6

AJ7

H3

J3

J1

J2

J5

H5

H2

H1

J4

H4

E3

E2

F2

F1

D2

D3

D1

F3

C3

B3

C6

C5

B5

E6

A5

D6

D5

E5

B6

A6

I

XU1C

Haswell rPGA

SA_DQS_P_0

SA_DQS_N_0

SA_DQ_0

SA_DQ_1

SA_DQ_2

SA_DQ_3

SA_DQ_4

SA_DQ_5

SA_DQ_6

SA_DQ_7

SA_DQS_P_1

SA_DQS_N_1

SA_DQ_8

SA_DQ_9

SA_DQ_10

SA_DQ_11

SA_DQ_12

SA_DQ_13

SA_DQ_14

SA_DQ_15

SA_DQS_P_2

SA_DQS_N_2

SA_DQ_16

SA_DQ_17

SA_DQ_18

SA_DQ_19

SA_DQ_20

SA_DQ_21

SA_DQ_22

SA_DQ_23

SA_DQS_P_3

SA_DQS_N_3

SA_DQ_24

SA_DQ_25

SA_DQ_26

SA_DQ_27

SA_DQ_28

SA_DQ_29

SA_DQ_30

SA_DQ_31

SA_DQS_P_4

SA_DQS_N_4

SA_DQ_32

SA_DQ_33

SA_DQ_34

SA_DQ_35

SA_DQ_36

SA_DQ_37

SA_DQ_38

SA_DQ_39

SA_DQS_P_5

SA_DQS_N_5

SA_DQ_40

SA_DQ_41

SA_DQ_42

SA_DQ_43

SA_DQ_44

SA_DQ_45

SA_DQ_46

SA_DQ_47

SA_DQS_P_6

SA_DQS_N_6

SA_DQ_48

SA_DQ_49

SA_DQ_50

SA_DQ_51

SA_DQ_52

SA_DQ_53

SA_DQ_54

SA_DQ_55

SA_DQS_P_7

SA_DQS_N_7

SA_DQ_56

SA_DQ_57

SA_DQ_58

SA_DQ_59

SA_DQ_60

SA_DQ_61

SA_DQ_62

SA_DQ_63

SOCKET_ 947P

SA_MA_0

SA_MA_1

SA_MA_2

SA_MA_3

SA_MA_4

SA_MA_5

SA_MA_6

SA_MA_7

SA_MA_8

SA_MA_9

SA_MA_10

SA_MA_11

SA_MA_12

SA_MA_13

SA_MA_14

SA_MA_15

SA_WE#

SA_CAS#

SA_RAS#

SA_BS_0

SA_BS_1

SA_BS_2

SA_CS_N_0

SA_CS_N_1

SA_CS_N_2

SA_CS_N_3

SA_CKE_0

SA_CKE_1

SA_CKE_2

SA_CKE_3

SA_ODT_0

SA_ODT_1

SA_ODT_2

SA_ODT_3

SA_CK_P_0

SA_CK_N_0

SA_CK_P_1

SA_CK_N_1

SA_CK_P_2

SA_CK_N_2

SA_CK_P_3

SA_CK_N_3

SM_VREF

SA_DIMM_VREFDQ

SB_DIMM_VREFDQ

RSVD_AC7

VSS1

3

V8

AC6

V9

U9

AC5

AC4

AD6

AC3

AD5

AC2

V6

AC1

AD4

V7

AD3

AD2

U7

U8

U6

V5

U5

AD1

M7

L9

M9

M10

AD9

AC9

AD8

AC8

M8

L7

L8

L10

V4

U4

V3

U3

V2

U2

V1

U1

AM3

F16

F13

AC7

V10

3

M_CHA_M AA0

M_CHA_M AA1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

M_CHA_M AA15

M_CHA_W E# 1 5

M_CHA_C AS# 15

M_CHA_R AS# 15

M_CHA_B A0 15

M_CHA_B A1 15

M_CHA_B A2 15

M_CHA_C S#0 1 5

M_CHA_C S#1 1 5

M_CHA_C KE0 15

M_CHA_C KE1 15

M_CHA_O DT0 15

M_CHA_O DT1 15

M_CHA_C LK0 1 5

M_CHA_C LK0# 15

M_CHA_C LK1 1 5

M_CHA_C LK1# 15

CPU_SM_ VREF

CPU_SA_ DIMM_VREFDQ

CPU_SB_ DIMM_VREFDQ

RSVD_AC 7

1

GND

HT9

NOBOM

2

I

D3C13

0.1UF/16V

X7R 10%

I

D3R17

24.9

1%

12

SA_VDQ_RC

12

2

I

D3C14

0.1UF/16V

X7R 10%

I

D3R18

24.9

1%

12

SB_VDQ_RC

12

GND GND GND

1 2

D3R14 0Imx_r0603

1 2

D3R15 0Imx_r0603

1 2

D3R16 0Imx_r0603

12

I

D3C15

0.1UF/16V

SM_VREF_RC

X7R 10%

12

I

D3R19

24.9

1%

Close to DIMM Side

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

+1P35V_ DUAL

12

I

D3R4

1K

1%

12

I

D3R11

1K

1%

GND

IMPLP-MS

IMPLP-MS

IMPLP-MS

1

DIMM_CA_V REF_AB 15,16

DIMM_DQ_V REF_A 15

DIMM_DQ_V REF_B 16

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

CPU_DDR3_A

CPU_DDR3_A

CPU_DDR3_A

Stonko_Chen

Stonko_Chen

Stonko_Chen

10 83Thursday, June 27, 2013

10 83Thursday, June 27, 2013

10 83Thursday, June 27, 2013

Rev

Rev

Rev

A00

A00

A00

Page 11

5

M_CHB_D Q[0..63]16

M_CHB_D QS016

M_CHB_D QS0#16

D D

M_CHB_D QS116

M_CHB_D QS1#16

M_CHB_D QS216

M_CHB_D QS2#16

C C

B B

A A

5

M_CHB_D QS316

M_CHB_D QS3#16

M_CHB_D QS416

M_CHB_D QS4#16

M_CHB_D QS516

M_CHB_D QS5#16

M_CHB_D QS616

M_CHB_D QS6#16

M_CHB_D QS716

M_CHB_D QS7#16

4

I

XU1D

Haswell rPGA

M_CHB_D QS0

M_CHB_D QS0#

M_CHB_D Q0

M_CHB_D Q1

M_CHB_D Q2

M_CHB_D Q3

M_CHB_D Q4

M_CHB_D Q5

M_CHB_D Q6

M_CHB_D Q7

M_CHB_D QS1

M_CHB_D QS1#

M_CHB_D Q8

M_CHB_D Q9

M_CHB_D Q10

M_CHB_D Q11

M_CHB_D Q12

M_CHB_D Q13

M_CHB_D Q14

M_CHB_D Q15

M_CHB_D QS2

M_CHB_D QS2#

M_CHB_D Q16

M_CHB_D Q17

M_CHB_D Q18

M_CHB_D Q19

M_CHB_D Q20

M_CHB_D Q21

M_CHB_D Q22

M_CHB_D Q23

M_CHB_D QS3

M_CHB_D QS3#

M_CHB_D Q24

M_CHB_D Q25

M_CHB_D Q26

M_CHB_D Q27

M_CHB_D Q28

M_CHB_D Q29

M_CHB_D Q30

M_CHB_D Q31

M_CHB_D QS4

M_CHB_D QS4#

M_CHB_D Q32

M_CHB_D Q33

M_CHB_D Q34

M_CHB_D Q35

M_CHB_D Q36

M_CHB_D Q37

M_CHB_D Q38

M_CHB_D Q39

M_CHB_D QS5

M_CHB_D QS5#

M_CHB_D Q40

M_CHB_D Q41

M_CHB_D Q42

M_CHB_D Q43

M_CHB_D Q44

M_CHB_D Q45

M_CHB_D Q46

M_CHB_D Q47

M_CHB_D QS6

M_CHB_D QS6#

M_CHB_D Q48

M_CHB_D Q49

M_CHB_D Q50

M_CHB_D Q51

M_CHB_D Q52

M_CHB_D Q53

M_CHB_D Q54

M_CHB_D Q55

M_CHB_D QS7

M_CHB_D QS7#

M_CHB_D Q56

M_CHB_D Q57

M_CHB_D Q58

M_CHB_D Q59

M_CHB_D Q60

M_CHB_D Q61

M_CHB_D Q62

M_CHB_D Q63

4

AP17

AP18

AR18

AT18

AM17

AM18

AR17

AT17

AN17

AN18

AP12

AP11

AT12

AR12

AN12

AM11

AT11

AR11

AM12

AN11

AP6

AP5

AR5

AR6

AM5

AM6

AT5

AT6

AN5

AN6

AK3

AJ3

AJ4

AK4

AJ1

AJ2

AM1

AN1

AK2

AK1

G10

C15

C14

E15

D15

A15

B15

E14

D14

A14

B14

M3

L3

L2

M2

L4

M4

L1

M1

L5

M5

H8

H9

G7

J8

G8

G9

J7

J9

J10

C9

C8

A8

B8

A9

B9

D8

E8

D9

E9

SB_DQS_P_0

SB_DQS_N_0

SB_DQ_0

SB_DQ_1

SB_DQ_2

SB_DQ_3

SB_DQ_4

SB_DQ_5

SB_DQ_6

SB_DQ_7

SB_DQS_P_1

SB_DQS_N_1

SB_DQ_8

SB_DQ_9

SB_DQ_10

SB_DQ_11

SB_DQ_12

SB_DQ_13

SB_DQ_14

SB_DQ_15

SB_DQS_P_2

SB_DQS_N_2

SB_DQ_16

SB_DQ_17

SB_DQ_18

SB_DQ_19

SB_DQ_20

SB_DQ_21

SB_DQ_22

SB_DQ_23

SB_DQS_P_3

SB_DQS_N_3

SB_DQ_24

SB_DQ_25

SB_DQ_26

SB_DQ_27

SB_DQ_28

SB_DQ_29

SB_DQ_30

SB_DQ_31

SB_DQS_P_4

SB_DQS_N_4

SB_DQ_32

SB_DQ_33

SB_DQ_34

SB_DQ_35

SB_DQ_36

SB_DQ_37

SB_DQ_38

SB_DQ_39

SB_DQS_P_5

SB_DQS_N_5

SB_DQ_40

SB_DQ_41

SB_DQ_42

SB_DQ_43

SB_DQ_44

SB_DQ_45

SB_DQ_46

SB_DQ_47

SB_DQS_P_6

SB_DQS_N_6

SB_DQ_48

SB_DQ_49

SB_DQ_50

SB_DQ_51

SB_DQ_52

SB_DQ_53

SB_DQ_54

SB_DQ_55

SB_DQS_P_7

SB_DQS_N_7

SB_DQ_56

SB_DQ_57

SB_DQ_58

SB_DQ_59

SB_DQ_60

SB_DQ_61

SB_DQ_62

SB_DQ_63

SOCKET_ 947P

3

R8

Y5

Y10

AA5

Y7

AA6

Y6

AA7

Y8

AA10

R9

Y9

AF7

P9

AA8

AG7

P6

P7

R6

R7

P8

AA9

P4

R2

P3

P1

AF10

AG10

AG9

AF9

R4

R3

R1

P2

AA4

Y4

AA3

Y3

AA2

Y2

AA1

Y1

AG8

R10

M_CHB_M AA0

M_CHB_M AA1

M_CHB_M AA2

M_CHB_M AA3

M_CHB_M AA4

M_CHB_M AA5

M_CHB_M AA6

M_CHB_M AA7

M_CHB_M AA8

M_CHB_M AA9

M_CHB_M AA10

M_CHB_M AA11

M_CHB_M AA12

M_CHB_M AA13

M_CHB_M AA14

M_CHB_M AA15

RSVD1

GND

M_CHB_W E# 1 6

M_CHB_C AS# 16

M_CHB_R AS# 16

M_CHB_B A0 16

M_CHB_B A1 16

M_CHB_B A2 16

M_CHB_C S#0 1 6

M_CHB_C S#1 1 6

M_CHB_C KE0 16

M_CHB_C KE1 16

M_CHB_O DT0 16

M_CHB_O DT1 16

M_CHB_C LK0 1 6

M_CHB_C LK0# 16

M_CHB_C LK1 1 6

M_CHB_C LK1# 16

1

HT10

NOBOM

SB_MA_0

SB_MA_1

SB_MA_2

SB_MA_3

SB_MA_4

SB_MA_5

SB_MA_6

SB_MA_7

SB_MA_8

SB_MA_9

SB_MA_10

SB_MA_11

SB_MA_12

SB_MA_13

SB_MA_14

SB_MA_15

SB_WE#

SB_CAS#

SB_RAS#

SB_BS_0

SB_BS_1

SB_BS_2

SB_CS_N_0

SB_CS_N_1

SB_CS_N_2

SB_CS_N_3

SB_CKE_0

SB_CKE_1

SB_CKE_2

SB_CKE_3

SB_ODT_0

SB_ODT_1

SB_ODT_2

SB_ODT_3

SB_CK0

SB_CKN0

SB_CK1

SB_CKN1

SB_CK2

SB_CKN2

SB_CK3

SB_CKN3

RSVD1

VSS2

3

2

M_CHB_M AA[0..15] 16

2

1

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

CPU_DDR3_B

CPU_DDR3_B

CPU_DDR3_B

Stonko_Chen

Stonko_Chen

Stonko_Chen

11 83Thursday, June 27, 2013

11 83Thursday, June 27, 2013

11 83Thursday, June 27, 2013

Rev

Rev

Rev

A00

A00

A00

Page 12

5

+VCORE

D D

VCC_SEN SE76

PIN A23 = FC_A23

+1P05V_ PCH

12

NI

HR131

0

mx_r0805

FC_A23

+1P05V_ PCH

12

I

HR24

150

12

GND

I

HR31

75

1%

12

1%

NI

HR25

10K

+1V_CPU IOOUT

I

HR34

43

1 2

+1P35V_ DUAL

+VCOMP_ OUT

CPU_VIDAL ERT#

C C

B B

A A

XDP_PW R_DEBUG5 0

+1V_CPU IOOUT

VIDALERT#76

VIDSCLK76

VIDSOUT76

12

I

HR30

130

+1V_CPU IOOUT

GND

AB25

AB29

AB26

AA32

AA30

AA34

AA28

AA26

AG32

AG30

AL35

W32

AL16

AL13

AK27

AL27

AB11

AE11

AH11

W11

AN35

AT35

AR35

AR32

AL26

AM28

AM29

AL28

AP35

AP34

AT34

AL22

AT33

AM21

AM25

AM22

AM20

AM24

AL19

AM23

AT32

K26

E17

A23

K27

T27

V27

N26

H27

AB2

AB5

AB8

AE2

AE5

AE8

K11

N11

T11

F22

J27

L27

N8

T2

T5

T8

W2

W5

W8

4

I

XU1E

Haswell rPGA

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCC101

VCC102

VCC103

VCC_SENSE

RSVD30

RSVD29

RSVD28

RSVD27

RSVD26

RSVD25

RSVD24

RSVD23

RSVD22

RSVD21

RSVD20

RSVD19

RSVD18

PWR_DEBUG

VDDQ13

VDDQ12

VDDQ11

VDDQ10

VDDQ9

VDDQ8

VDDQ7

VDDQ6

VDDQ14

VDDQ15

VDDQ5

VDDQ16

VDDQ4

VDDQ17

VDDQ3

VDDQ18

VDDQ2

VDDQ19

VDDQ1

VDDQ20

VCOMP_OUT

VCCIO_OUT

RSVD_TP4

RSVD_TP3

RSVD_TP2

RSVD_TP1

VIDALERT#

VIDSCLK

VIDSOUT

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

SOCKET_ 947P

VCC92

VCC91

VCC90

VCC89

VCC88

VCC87

VCC86

VCC85

VCC84

VCC83

VCC82

VCC81

VCC80

VCC79

VCC78

VCC77

VCC76

VCC75

VCC74

VCC73

VCC72

VCC71

VCC70

VCC69

VCC68

VCC67

VCC66

VCC65

VCC64

VCC63

VCC62

VCC61

VCC60

VCC59

VCC58

VCC57

VCC56

VCC55

VCC54

VCC53

VCC52

VCC51

VCC50

VCC49

VCC48

VCC47

VCC46

VCC45

VCC44

VCC43

VCC42

VCC41

VCC40

VCC39

VCC38

VCC37

VCC36

VCC35

VCC34

VCC33

VCC32

VCC31

VCC30

VCC29

VCC28

VCC27

VCC26

VCC25

VCC24

VCC23

VCC22

VCC21

VCC20

VCC19

VCC18

VCC17

VCC16

VCC15

VCC14

VCC13

VCC12

VCC11

VCC10

VCC9

VCC8

VCC7

VCC6

VCC5

VCC4

VCC3

VCC2

VCC1

AB27

AB28

AB30

AB31

AB33

AB34

AB32

AC26

AB35

AC28

AD25

AC30

AD28

AC32

AD31

AC34

AD34

AD26

AD27

AD29

AD30

AD32

AD33

AD35

AE26

AE32

AE28

AE30

AG28

AG34

AE34

AF25

AF26

AF27

AF28

AF29

AF30

AF31

AF32

AF33

AF34

AF35

AG26

AH26

AH29

AH32

AH35

AH25

AH27

AH28

AH30

AH31

AH33

AH34

AJ25

AJ26

AJ27

AJ28

AJ29

AJ30

AJ31

AJ32

AJ33

AJ34

AJ35

G25

H25

J25

K25

L25

M25

N25

P25

R25

T25

U25

U26

V25

V26

W26

W27

Y25

Y26

Y27

Y28

Y29

Y30

Y31

Y32

Y33

Y34

Y35

+VCORE

3

Output CAP

+VCORE

I

12

+VCORE

12

+VCORE

12

+VCORE

12

GND

+

12

PC294

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC350

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC308

22UF/6.3V

X5R 20%

mx_c0805_ small

I

PCE2

330UF/2.5 V

ESR=9mO hm/Ir=3900mA

I

PC299

22UF/6.3V

X5R 20%

mx_c0805_ small

I

PC352

22UF/6.3V

X5R 20%

mx_c0805_ small

I

PC312

22UF/6.3V

X5R 20%

mx_c0805_ small

12

I

+

PCE3

330UF/2.5 V

ESR=9mO hm/Ir=3900mA

GND

I

12

PC303

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC284

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC314

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC304

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC285

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC342

22UF/6.3V

X5R 20%

mx_c0805_ small

2

I

12

PC305

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC286

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC343

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC306

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC287

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC344

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC307

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC288

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC346

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC309

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC289

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC347

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC310

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC291

22UF/6.3V

X5R 20%

mx_c0805_ small

I

12

PC348

22UF/6.3V

X5R 20%

mx_c0805_ small

1

I

12

PC311

22UF/6.3V

X5R 20%

mx_c0805_ small

GND

I

12

PC292

22UF/6.3V

X5R 20%

mx_c0805_ small

GND

I

12

PC349

22UF/6.3V

X5R 20%

mx_c0805_ small

GND

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

CPU_POWER

CPU_POWER

CPU_POWER

Stonko_Chen

Stonko_Chen

Stonko_Chen

12 83Thursday, June 27, 2013

12 83Thursday, June 27, 2013

12 83Thursday, June 27, 2013

Rev

Rev

Rev

A00

A00

A00

Page 13

5

4

3

2

1

CFG[19:0] (default value of '1' if not terminated on the board.) [our setting = *]

CFG[2]: PCI Express* Static x16 Lane Numbering Reversal.

— 1 = Normal operation (*)

D D

— 0 = Lane numbers reversed

CFG[3]: MSR Privacy Bit Feature

— 1 = Debug capability is determined by IA32_Debug_Interface_MSR (0xC80) bit[0] setting (*)

— 0 = IA32_Debug_Interface_MSR (0xC80) bit[0] default setting overridden

CFG[4]: eDP enable

— 1 = Disabled (*)

— 0 = Enabled

CFG[6:5]: PCI Express* Bifurcation:

— 00 = 1 x8, 2 x4 PCI Express*

— 01 = reserved

— 10 = 2 x8 PCI Express*

— 11 = 1 x16 PCI Express*(*)

CFG[1:0] ; CFG[19:7] Reserved configuration lanes. Need test point

I

XU1I

AR1

D23

D24

C23

C35

AT2

AT1

W29

W28

AL25

W30

W31

E20

E21

B23

B35

A35

A34

Haswell rPGA

RSVD_TP5

RSVD_TP6

RSVD_TP7

RSVD_TP8

RSVD_TP9

RSVD_TP10

RSVD_TP11

RSVD_TP12

RSVD_TP13

RSVD_TP14

RSVD_TP15

RSVD_TP16

RSVD_TP17

RSVD_TP18

RSVD_TP19

RSVD_TP20

RSVD_TP21

RSVD_TP22

VCC104

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_17

CFG_16

CFG_19

CFG_18

C C

B B

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

NOBOM

HT81

HT69

HT68

HT65

HT66

HT67

HT64

HT63

HT78

HT73

HT72

HT70

HT71

HT79

HT77

HT76

HT74

HT75

1

CPU_RSV D_TP5

1

CPU_RSV D_TP6

1

CPU_RSV D_TP7

1

CPU_RSV D_TP8

1

CPU_RSV D_TP9

1

CPU_RSV D_TP10

1

CPU_RSV D_TP11

1

CPU_RSV D_TP12

1

CPU_RSV D_TP13

1

CPU_RSV D_TP14

1

CPU_RSV D_TP15

1

CPU_RSV D_TP16

1

CPU_RSV D_TP17

1

CPU_RSV D_TP18

1

CPU_RSV D_TP19

1

CPU_RSV D_TP20

1

CPU_RSV D_TP21

1

CPU_RSV D_TP22

F25

AT20

AR20

AP20

AP22

AT22

AN22

AT25

AN23

AR24

AT23

AN20

AP24

AP26

AN25

AN26

AP25

AP21

AR21

AP23

AR23

+VCORE

CPU_CFG 0

CPU_CFG 1

CPU_CFG 2

CPU_CFG 3

CPU_CFG 4

CPU_CFG 5

CPU_CFG 6

CPU_CFG 7

CPU_CFG 8

CPU_CFG 9

CPU_CFG 10

CPU_CFG 11

CPU_CFG 12

CPU_CFG 13

CPU_CFG 14

CPU_CFG 15

OBSFN_C 0 5 0

OBSFN_C 1 5 0

OBSFN_D 0 5 0

OBSFN_D 1 5 0

1 2

HR38 1K

NI

1 2

HR39 1K

NI

1 2

HR40 1K

NI

1 2

HR41 1K

NI

1 2

HR42 1K

NI

1 2

HR43 1K

NI

CPU_CFG [0..15] 50

GND

W33, AR26, AP27 = GND

AT31

FC2

NC

H_CFG_R COMP

W34

CPU_TES TLOW2

G26

CPU_TES TLOW1

G6

CPU_FC2 _PWROK

B1

AL31

AL32

GND

1

HT80

NOBOM

HT83

NOBOM

HT84

NOBOM

HT85

NOBOM

HT86

NOBOM

HT87

NOBOM

HT88

NOBOM

HT89

NOBOM

HT90

NOBOM

HT91

NOBOM

HT92

NOBOM

HT93

NOBOM

HT94

NOBOM

GND

A A

CPU_RSV D2

1

CPU_RSV D4

1

CPU_RSV D5

1

CPU_RSV D6

1

CPU_RSV D7

1

CPU_RSV D8

1

CPU_RSV D9

1

CPU_RSV D10

1

CPU_RSV D11

1

CPU_RSV D12

1

CPU_RSV D13

1

CPU_RSV D14

1

CPU_RSV D15

AD10

W33

AL30

AL29

AR33

AM27

AM26

AM2

E18

U10

P10

AP27

AR26

F5

K6

A2

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

SOCKET_ 947P

CFG_RCOMP

TESTLO2

TESTLO1

VSS258

VSS259

1 2

HR56 49.9 1%

I

1 2

HR57 49.9 1%

I

1 2

HR58 49.9 1%

I

1 2

NI

HR59

2K

1%

GND

12

NI

HR60

1K

1%

GND

PWRO K 19,36

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

CPU_CFG

CPU_CFG

CPU_CFG

Stonko_Chen

Stonko_Chen

Stonko_Chen

13 83Thursday, June 27, 2013

13 83Thursday, June 27, 2013

13 83Thursday, June 27, 2013

Rev

Rev

Rev

A00

A00

A00

Page 14

5

D D

C C

B B

A A

A10

A13

A16

A19

A22

A25

A27

A29

A31

A33

AA11

AA25

AA27

AA31

AA29

AB1

AB10

AA33

AA35

AB3

AC25

AC27

AB4

AB6

AB7

AB9

AC11

AD11

AC29

AC31

AC33

AC35

AD7

AE1

AE10

AE25

AE29

AE3

AE27

AE35

AE4

AE6

AE7

AE9

AF11

AF6

AF8

AG11

AG25

AE31

AG31

AE33

AG6

AH1

AH10

AH2

AG27

AG29

AH3

AG33

AG35

AH4

AH5

AH6

AH7

AH8

AH9

AJ11

AJ5

AK11

AK25

AK26

AK28

AK29

AK30

AK32

E19

GND GNDGND GND

I

XU1F

Haswell rPGA

VSS16

VSS127

VSS238

VSS268

VSS279

VSS290

VSS301

VSS312

A3

VSS323

VSS17

VSS28

A4

VSS39

A7

VSS50

VSS61

VSS72

VSS83

VSS94

VSS105

VSS116

VSS128

VSS139

VSS150

VSS161

VSS172

VSS183

VSS194

VSS205

VSS216

VSS227

VSS239

VSS250

VSS260

VSS261

VSS262

VSS263

VSS264

VSS265

VSS266

VSS267

VSS269

VSS270

VSS271

VSS272

VSS273

VSS274

VSS275

VSS276

VSS277

VSS278

VSS280

VSS281

VSS282

VSS283

VSS284

VSS285

VSS286

VSS287

VSS288

VSS289

VSS291

VSS292

VSS293

VSS294

VSS295

VSS296

VSS297

VSS298

VSS299

VSS300

VSS302

VSS303

VSS304

VSS305

VSS306

VSS307

VSS308

VSS309

VSS310

VSS311

VSS313

SOCKET_ 947P

4

AK34

VSS314

AK5

VSS315

AL1

VSS316

AL10

VSS317

AL11

VSS318

AL12

VSS319

AL14

VSS320

AL15

VSS321

AL17

VSS322

AL18

VSS324

AL2

VSS325

AL20

VSS326

AL21

VSS327

AL23

VSS328

E22

VSS329

AL3

VSS330

AL4

VSS331

AL5

VSS332

AL6

VSS333

AL7

VSS18

AL8

VSS19

AL9

VSS20

AM10

VSS21

AM13

VSS22

AM16

VSS23

AM19

VSS24

E25

VSS25

AM32

VSS26

AM4

VSS27

AM7

VSS29

AN10

VSS30

AN13

VSS31

AN16

VSS32

AN19

VSS33

AN2

VSS34

AN21

VSS35

AN24

VSS36

AN27

VSS37

AN30

VSS38

AN34

VSS40

AN4

VSS41

AN7

VSS42

AP1

VSS43

AP10

VSS44

AP13

VSS45

AP16

VSS46

AP19

VSS47

AP4

VSS48

AP7

VSS49

W25

VSS51

AR10

VSS52

AR13

VSS53

AR16

VSS54

AR19

VSS55

AR2

VSS56

AR22

VSS57

AR25

VSS58

AR28

VSS59

AR31

VSS60

AR34

VSS62

AR4

VSS63

AR7

VSS64

AT10

VSS65

AT13

VSS66

AT16

VSS67

AT19

VSS68

AT21

VSS69

AT24

VSS70

AT27

VSS71

AT3

VSS73

AT30

VSS74

AT4

VSS75

AT7

VSS76

B10

VSS77

B13

VSS78

B16

VSS79

B19

VSS80

B2

VSS81

B22

VSS82

3

I

XU1G

Haswell rPGA

B34

B4

B7

C1

C10

C13

C16

C19

C2

C22

C24

C26

C28

C30

C32

C34

C4

C7

D10

D13

D16

D19

D22

D25

D27

D29

D31

D33

D35

D4

D7

E1

E10

E13

E16

E4

E7

F10

F11

F12

F14

F15

F17

F18

F20

F21

F23

F24

F26

F28

F30

F32

F34

F4

F6

F7

F8

F9

G1

G11

G2

G27

G29

G3

G31

G33

G35

G4

G5

H10

H26

H6

H7

J11

J26

J28

J30

J32

J34

J6

K1

SOCKET_ 947P

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS173

VSS_SENSE

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

VSS234

VSS235

VSS236

VSS237

VSS240

VSS241

VSS242

VSS243

VSS244

VSS245

VSS246

VSS247

VSS248

VSS249

VSS251

VSS252

VSS253

VSS254

VSS255

VSS256

VSS257

RSVD31

K10

K2

K29

K3

K31

K33

K35

K4

K5

K7

K8

K9

L11

L26

L6

M11

M26

M28

M30

M32

M34

M6

N1

N10

N2

N29

N3

N31

N33

N35

N4

N5

N6

N7

N9

P11

P26

P5

R11

R26

R28

R30

R32

R34

R5

T1

T10

T29

T3

T31

T33

T35

T4

T6

T7

T9

U11

U27

V11

V28

V30

V32

V34

W1

W10

W3

W35

W4

W6

W7

W9

Y11

H11

AL24

F19

T26

AK35

AK33

2

1

1

VSS_SEN SE 76

NOBOM

H16

C138D13 8N

NOBOM

H18

C138D13 8N

I

X_BP

CPU

NOBOM

H17

C138D13 8N

NOBOM

H19

C138D13 8N

1

1

1

<Variant Name>

<Variant Name>

<Variant Name>

PEGATRON DT-MB RESTRICTED SECRET

Title :

Title :

Title :

Engineer:

Engineer:

Pegatron Corp.

Pegatron Corp.

Pegatron Corp.

Size Project Name

Size Project Name

Size Project Name

A3

A3

A3

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

IMPLP-MS

IMPLP-MS

IMPLP-MS

Engineer:

1

CPU_GND

CPU_GND

CPU_GND

Stonko_Chen

Stonko_Chen

Stonko_Chen

14 83Thursday, June 27, 2013

14 83Thursday, June 27, 2013

14 83Thursday, June 27, 2013

Rev

Rev

Rev

A00

A00

A00

Page 15

5

4

3

2

1

M_CHA_M AA[0..15]10

M_CHA_M AA0

M_CHA_M AA1

D D

C C

SMBus Slave Address: A0H

GND

B B

M_CHA_D QS710

M_CHA_D QS7#10

M_CHA_D QS610

M_CHA_D QS6#10

M_CHA_D QS510

M_CHA_D QS5#10

M_CHA_D QS410

M_CHA_D QS4#10

M_CHA_D QS310

M_CHA_D QS3#10

M_CHA_D QS210

M_CHA_D QS2#10

M_CHA_D QS110

M_CHA_D QS1#10

M_CHA_D QS010

M_CHA_D QS0#10

SMB_CLK _MAIN16,47,50,5 1

SMB_DAT A_MAIN16,47,50,5 1

M_CHA_M AA2

M_CHA_M AA3

M_CHA_M AA4

M_CHA_M AA5

M_CHA_M AA6

M_CHA_M AA7

M_CHA_M AA8

M_CHA_M AA9

M_CHA_M AA10

M_CHA_M AA11

M_CHA_M AA12

M_CHA_M AA13

M_CHA_M AA14

M_CHA_M AA15

M_CHA_C LK110

M_CHA_C LK1#10

M_CHA_C LK010

M_CHA_C LK0#10

M_CHA_C S#110

M_CHA_C S#010

M_CHA_O DT110

M_CHA_O DT010

M_CHA_W E#10

M_CHA_R AS#10

M_CHA_C AS#10

M_CHA_B A210

M_CHA_B A110

M_CHA_B A010

M_CHA_C KE110

M_CHA_C KE010

GND

I

DIMM1A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM _204P

0

1

2

3

4

5

6

7

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

RESET#

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

30

M_CHA_D Q2

M_CHA_D Q7

M_CHA_D Q3

M_CHA_D Q6

M_CHA_D Q1

M_CHA_D Q5

M_CHA_D Q0

M_CHA_D Q4

M_CHA_D Q11

M_CHA_D Q9

M_CHA_D Q14

M_CHA_D Q15

M_CHA_D Q10

M_CHA_D Q8

M_CHA_D Q13

M_CHA_D Q12

M_CHA_D Q21

M_CHA_D Q20

M_CHA_D Q23

M_CHA_D Q19

M_CHA_D Q16

M_CHA_D Q17

M_CHA_D Q18

M_CHA_D Q22

M_CHA_D Q24

M_CHA_D Q28

M_CHA_D Q30

M_CHA_D Q27

M_CHA_D Q25

M_CHA_D Q29

M_CHA_D Q26

M_CHA_D Q31

M_CHA_D Q38

M_CHA_D Q33

M_CHA_D Q37

M_CHA_D Q34

M_CHA_D Q36

M_CHA_D Q32

M_CHA_D Q35

M_CHA_D Q39

M_CHA_D Q46

M_CHA_D Q44

M_CHA_D Q43

M_CHA_D Q45

M_CHA_D Q40

M_CHA_D Q42

M_CHA_D Q47

M_CHA_D Q41

M_CHA_D Q49

M_CHA_D Q51

M_CHA_D Q50

M_CHA_D Q48

M_CHA_D Q52

M_CHA_D Q53

M_CHA_D Q55

M_CHA_D Q54

M_CHA_D Q60

M_CHA_D Q56

M_CHA_D Q62

M_CHA_D Q63

M_CHA_D Q58

M_CHA_D Q59

M_CHA_D Q61

M_CHA_D Q57

12

I

D3C11

0.1UF/16V

X7R 10%

0~7

8~15

16~23

24~31

32~39

40~47

48~55

56~63

M_CHA_D Q[0..63] 1 0

DIMM_CA_V REF_AB10,16

DIMM_DQ_V REF_A10

SM_DRAM RST# 9,16

+1P35V_ DUAL

12

I

D3R1

1K

1%

12

I

D3R2

1K

1%

GND GND

12

I

D3C1

0.1UF/16V

X7R 10%

+1P35V_ DUAL +1P35V_DUAL

GND

12

I

D3C2

0.1UF/16V

X7R 10%

GND

GND

12

I

D3C16

4.7UF/6.3V

X5R 10%

mx_c0603

I

DIMM1B

75

VDD1

81

VDD3

87

VDD5

93

VDD7

99

VDD9

105

VDD11

111

VDD13

117

VDD15

123

VDD17

2

VSS1

8

VSS3

13

VSS5

19

VSS7

25

VSS9

31

VSS11

37

VSS13

43

VSS15

48

VSS17

54

VSS19

60

VSS21

65

VSS23

71

VSS25

127

VSS27

133

VSS29

138

VSS31

144

VSS33

150

VSS35

155

VSS37

161

VSS39

167

VSS41

172

VSS43

178

VSS45

184

VSS47

189

VSS49

195

VSS51

198

EVENT#

125

TEST

77

NC1

122

NC2

126

VREFCA

1

VREFDQ

DDR3_DIMM _204P

VDD2

VDD4

VDD6

VDD8

VDD10

VDD12

VDD14

VDD16

VDD18

VSS2

VSS4

VSS6

VSS8

VSS10

VSS12

VSS14

VSS16

VSS18

VSS20

VSS22

VSS24

VSS26

VSS28

VSS30

VSS32

VSS34

VSS36

VSS38

VSS40

VSS42

VSS44

VSS46

VSS48

VSS50

VSS52

GND1

GND2

NP_NC1

NP_NC2

VTT1

VTT2

VDDSPD

76

82

88

94

100

106

112

118

124

3

9

14

20

26

32

38

44

49

55

61

66

72

128

134

139

145

151

156

162

168

173

179

185

190

196

207

208

205

206

GND

203

204

+3P3V

199

12

NI

D3C3

0.1UF/16V

X7R 10%

GND

+VTT_DD R

12

I

D3C4

0.1UF/16V

X7R 10%