Page 1

5

4

3

2

1

SYSTEM PAGE REF.

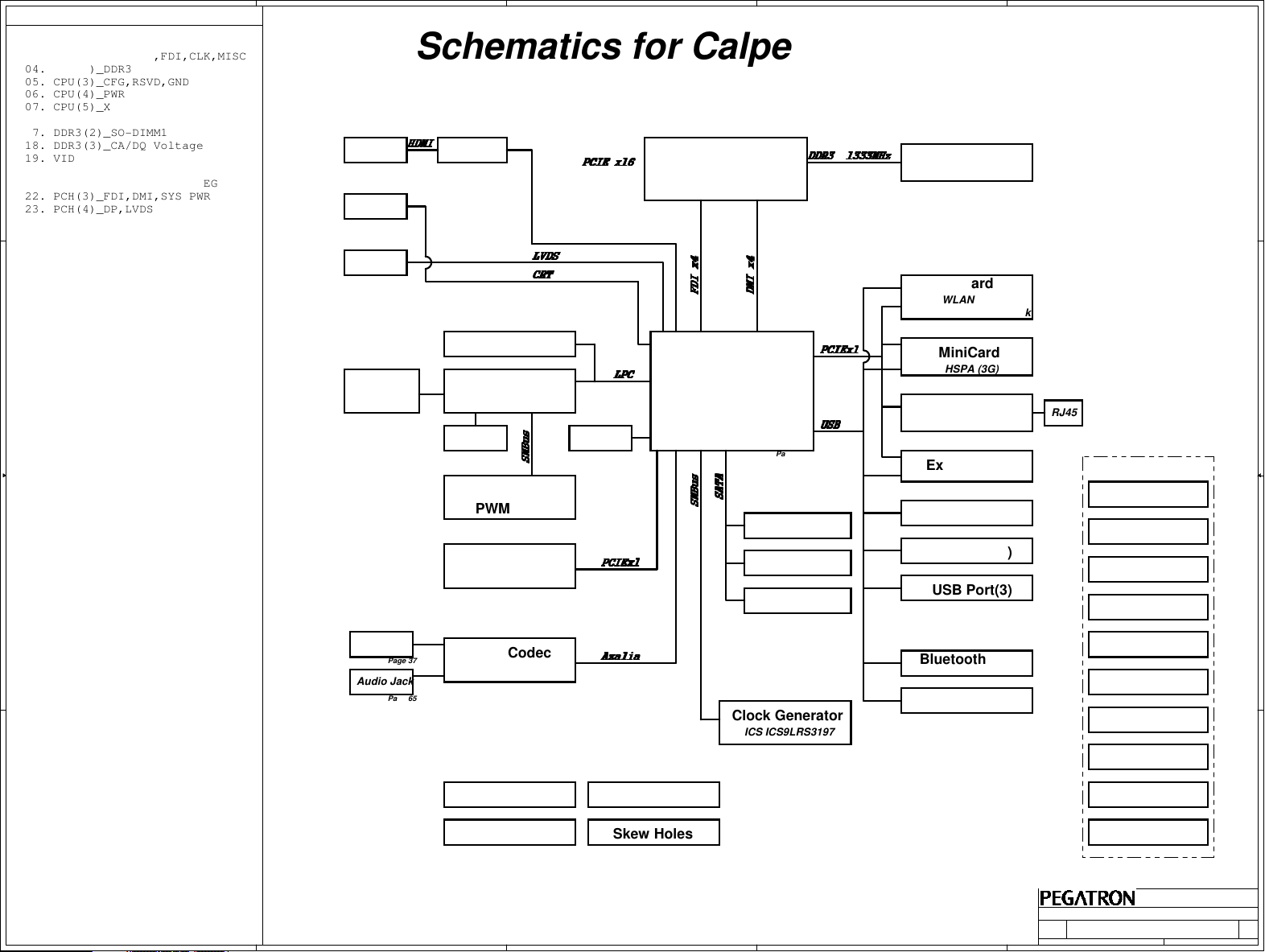

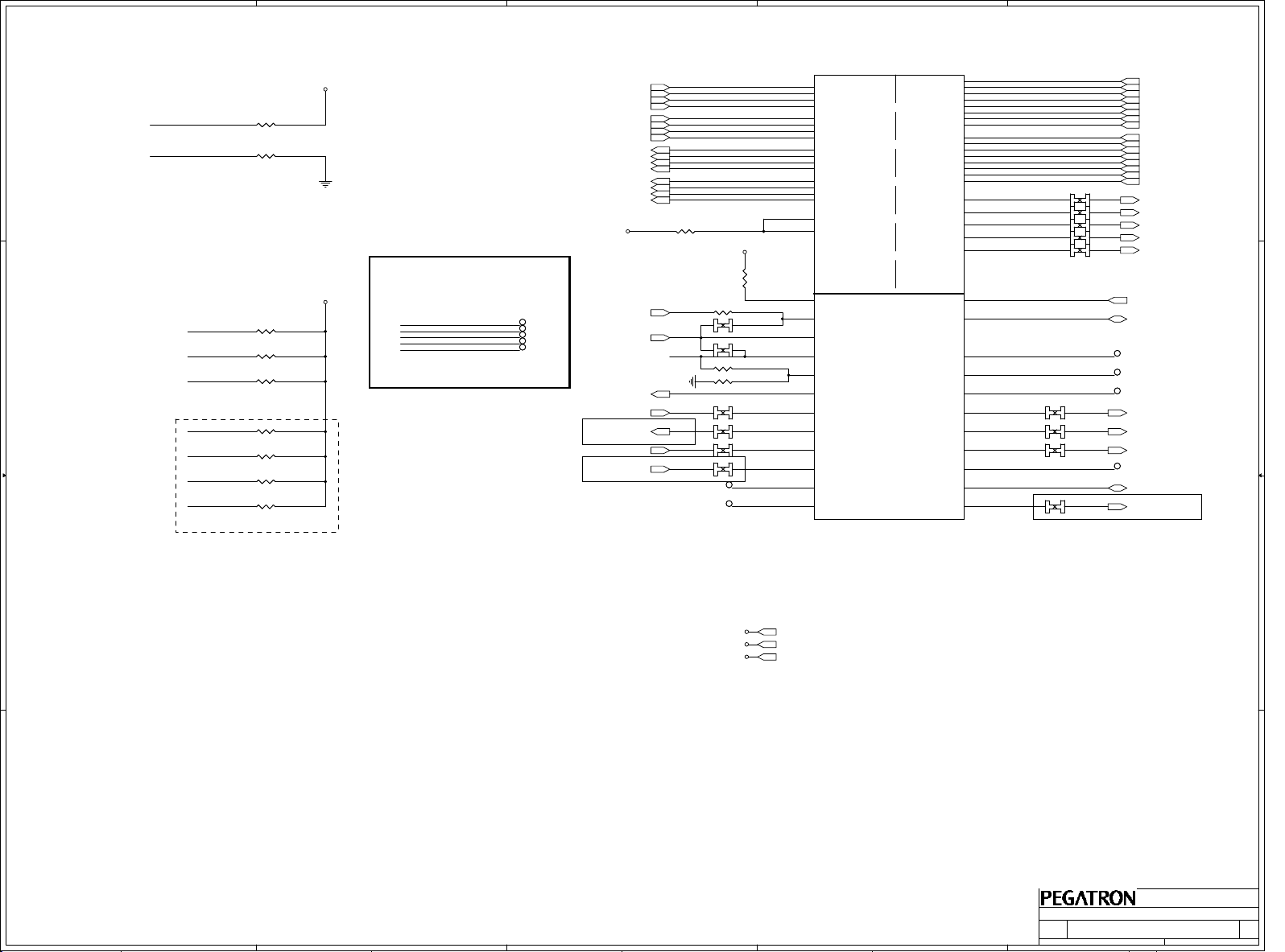

01. Block Diagram

02. System Setting

03. CPU(1)_DMI,PEG,FDI,CLK,MISC

04. CPU(2)_DDR3

05. CPU(3)_CFG,RSVD,GND

06. CPU(4)_PWR

07. CPU(5)_XDP

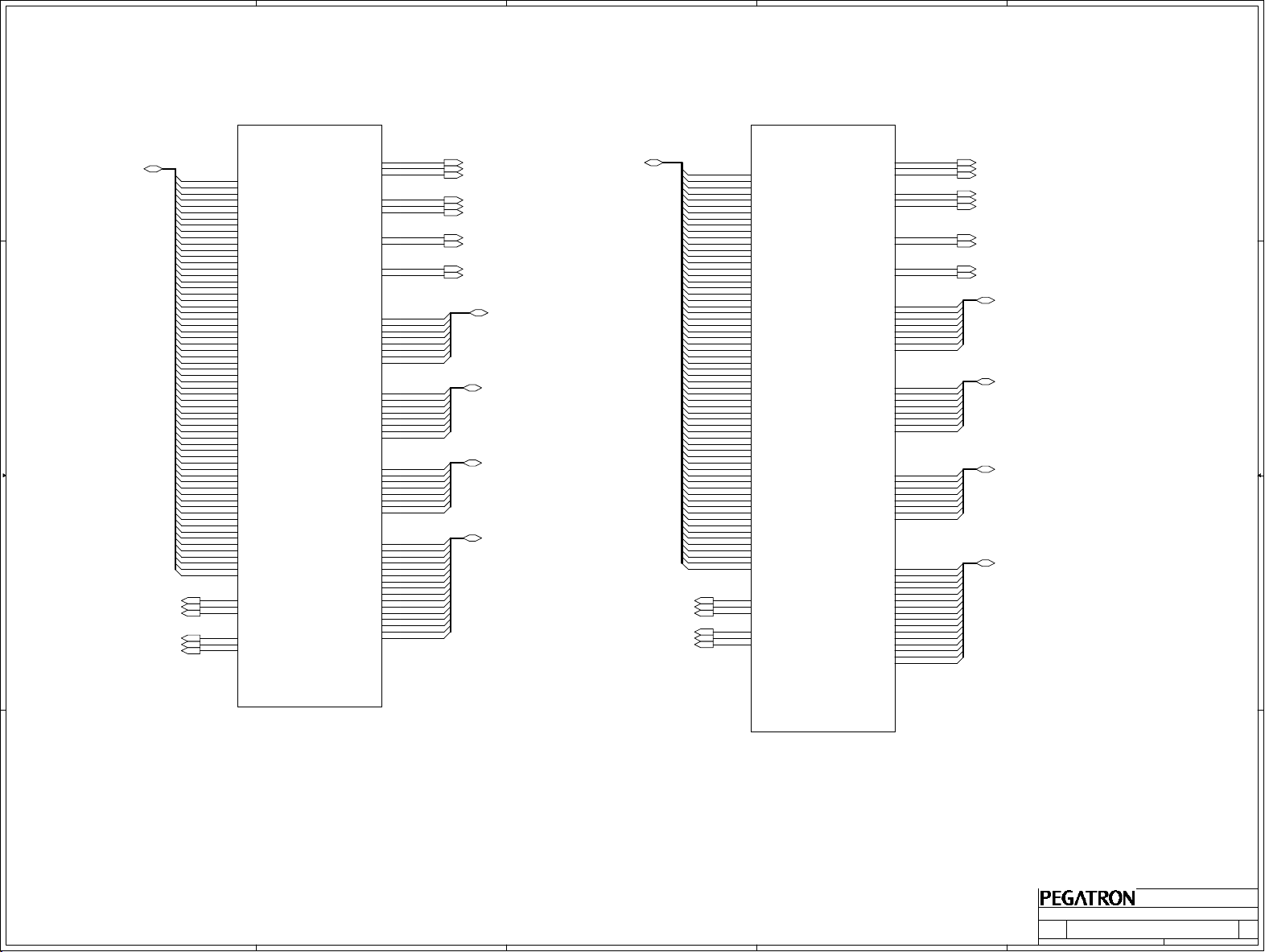

16. DDR3(1)_SO-DIMM0

D D

17. DDR3(2)_SO-DIMM1

18. DDR3(3)_CA/DQ Voltage

19. VID Controller

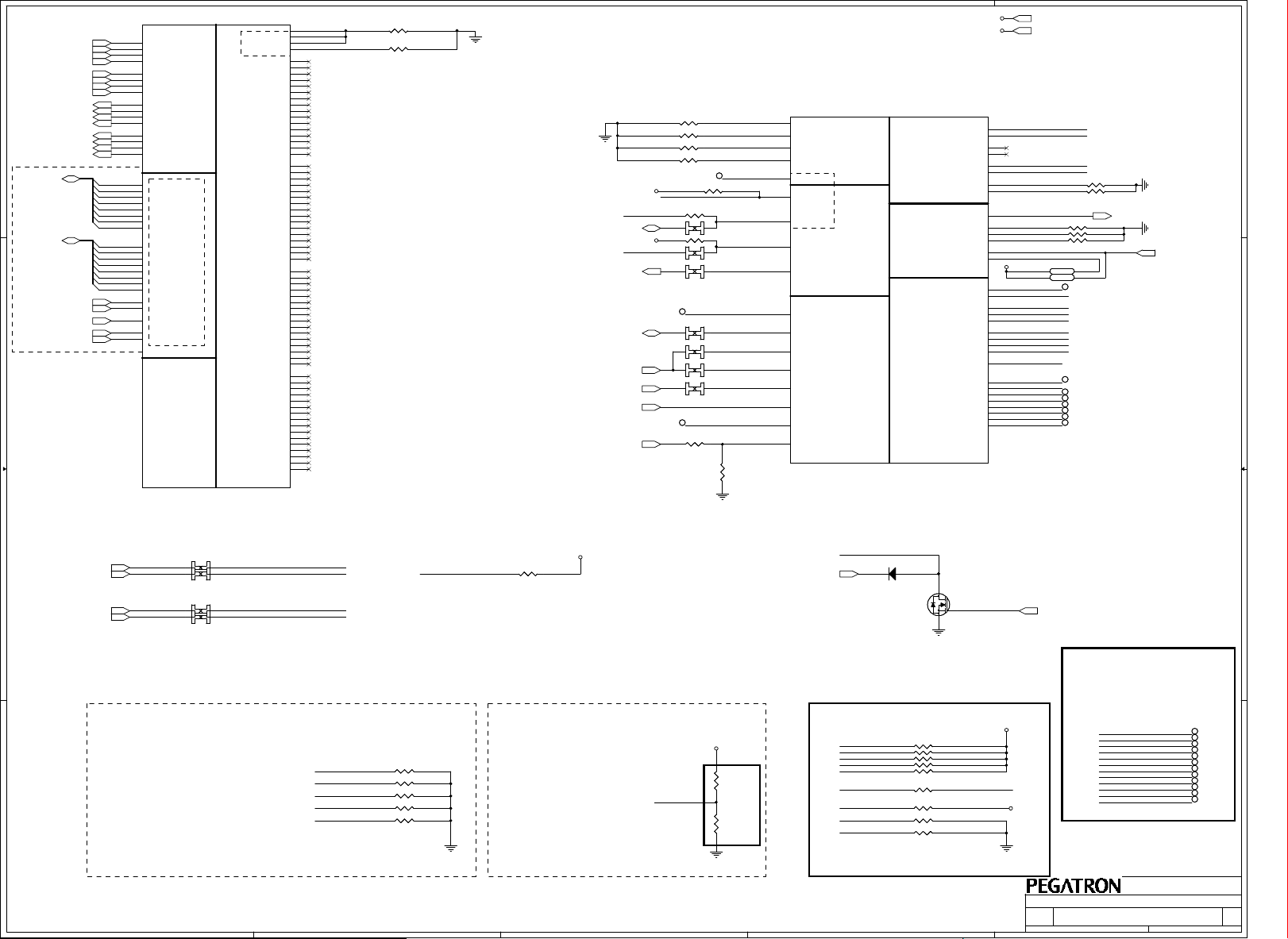

20. PCH(1)_SATA,IHDA,RTC,LPC

21. PCH(2)_PCIE,CLK,SMB,PEG

22. PCH(3)_FDI,DMI,SYS PWR

23. PCH(4)_DP,LVDS,CRT

24. PCH(5)_PCI,NVRAM,USB

25. PCH(6)_CPU,GPIO,MISC

26. PCH(7)_POWER,GND

27. PCH(8)_POWER,GND

28. PCH(9)_SPI,SMB

29. CLK_ICS9LPR362

30. EC_IT8512(1)

31. EC_IT8512(2)KB,TP,FP

32. RST_Reset Circuit

33. LAN_AR8131

34. LAN_RJ45

C C

36. AUD(1)_ALC663VD

37. AUD(2)_AMP,JACK

38. AUD(3)_FM2010

40. CB(1)_R5U230

43. CB(4)_NewCard

44. BUG_Debug

45. CRT(1)_LVDS

46. CRT(2)_D-Sub

47. CRT(3)_Display Port

48. TV(1)_HDMI

50. FAN_Fan,Sensor

51. XDD_HDD,ODD

52. USB_USB Port

53. MINICARD_WLAN

56. LED_Indicator

57. DSG_Discharge

60. DC_DC/BAT CONN

61. BT_Bluetooth

64. TUN_TV Tuner

B B

65. ME_CONN,Skew Hole

66. ESA_ESATA

69. OTH_GAME-LED

70. VGA(1)_MXM Slot

71. VGA(2)_LVDS Switch

80_PWR(1)_VCORE

81_PWR(2)_SYSTEM_+12VSUS

82_PWR(3)_VTT_CPUS & 1.05VS

83_PWR(4)_I/O_DDR & VTT

84_PWR(5)_****

85_PWR(6)_+1.8VS

86_PWR(7)_+VGFX_CORE

88_PWR(9)_CHARGER

90_PWR(11)_DETECT

91_PWR(12)_LOAD SWITCH

92_PWR(13)_PROTECT

93_PWR(14)_SIGNAL

94_PWR(15)_FLOWCHART

A A

95. System History

98. Power On Sequence

99. Power On Timing

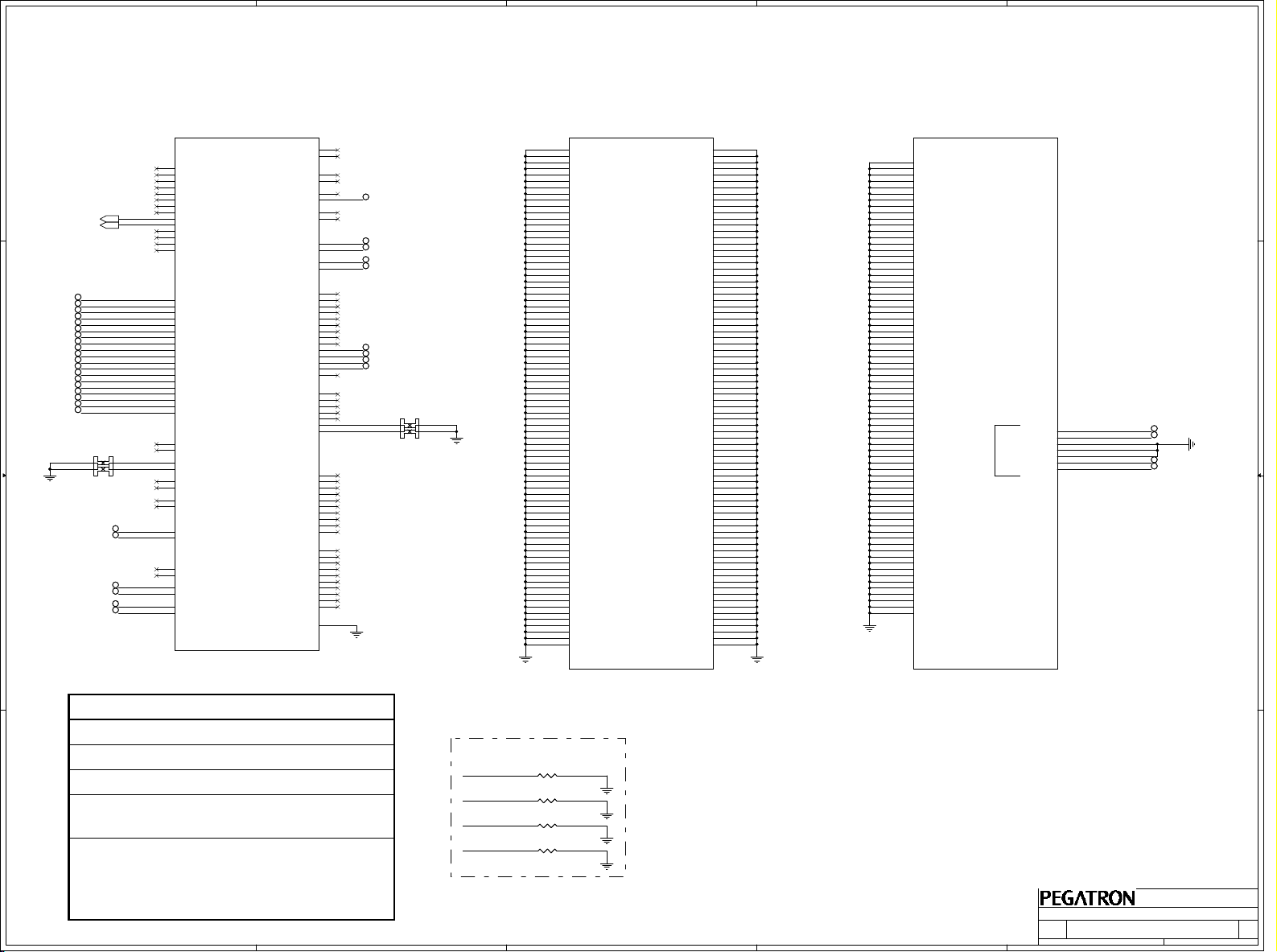

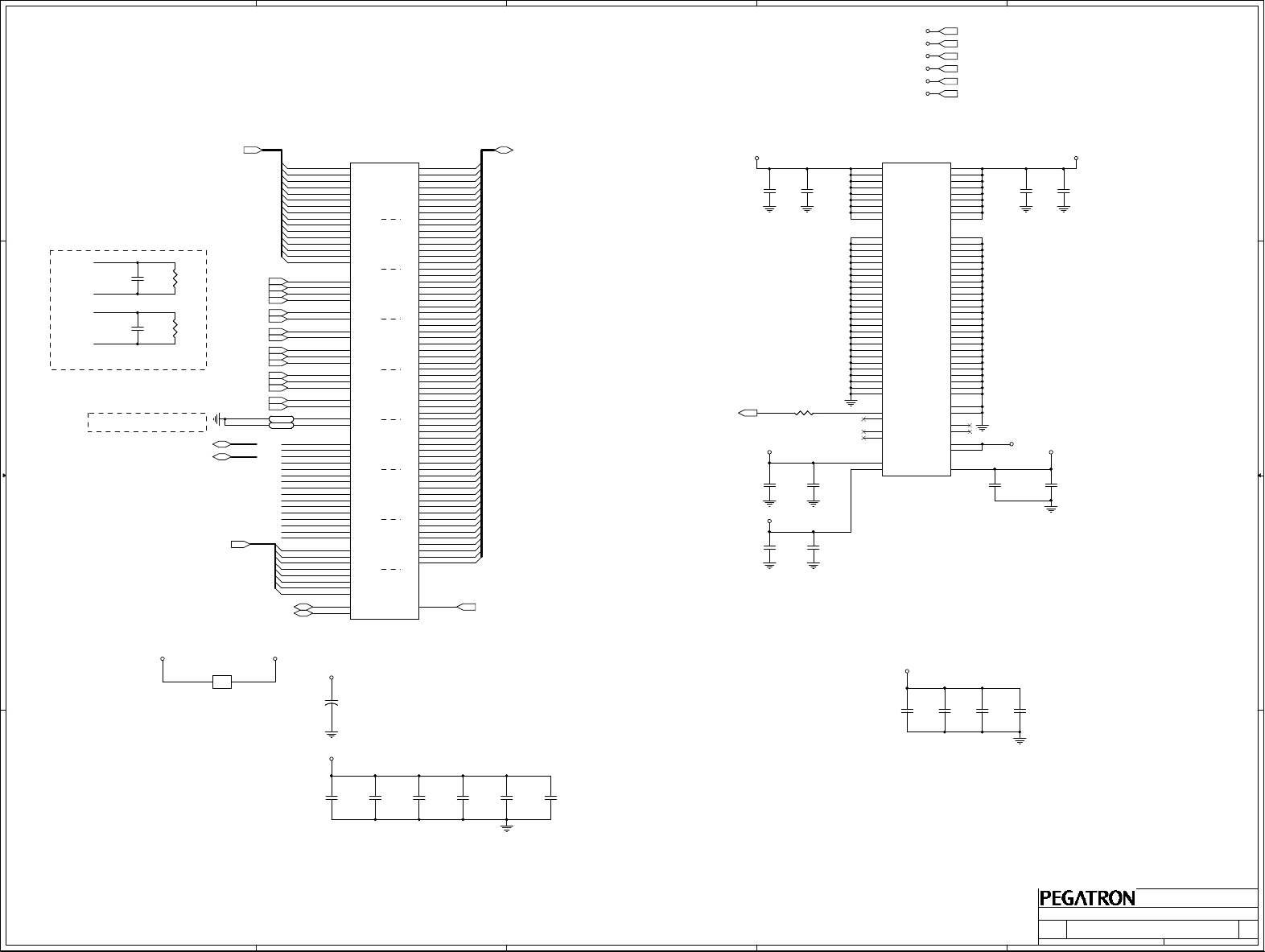

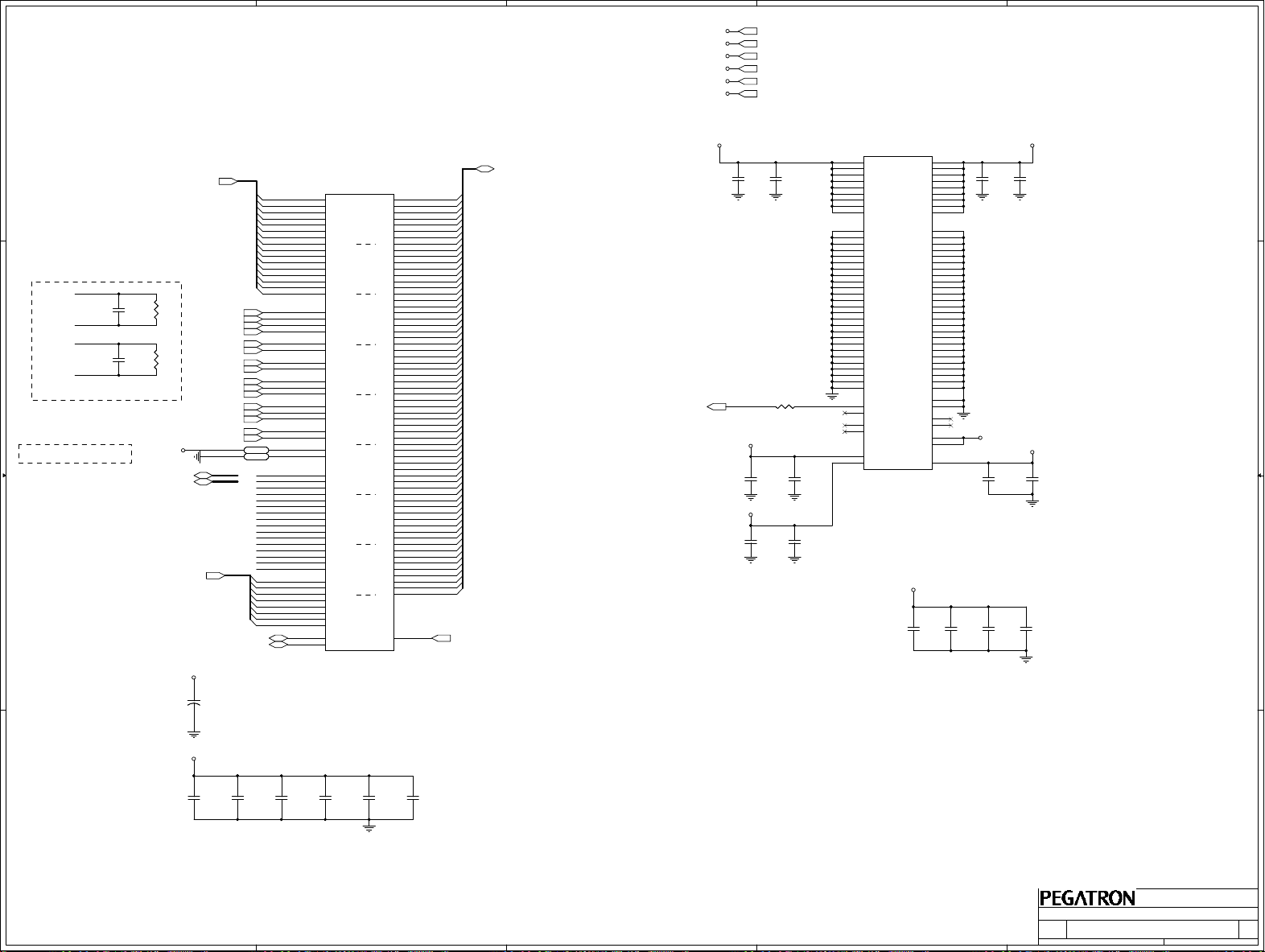

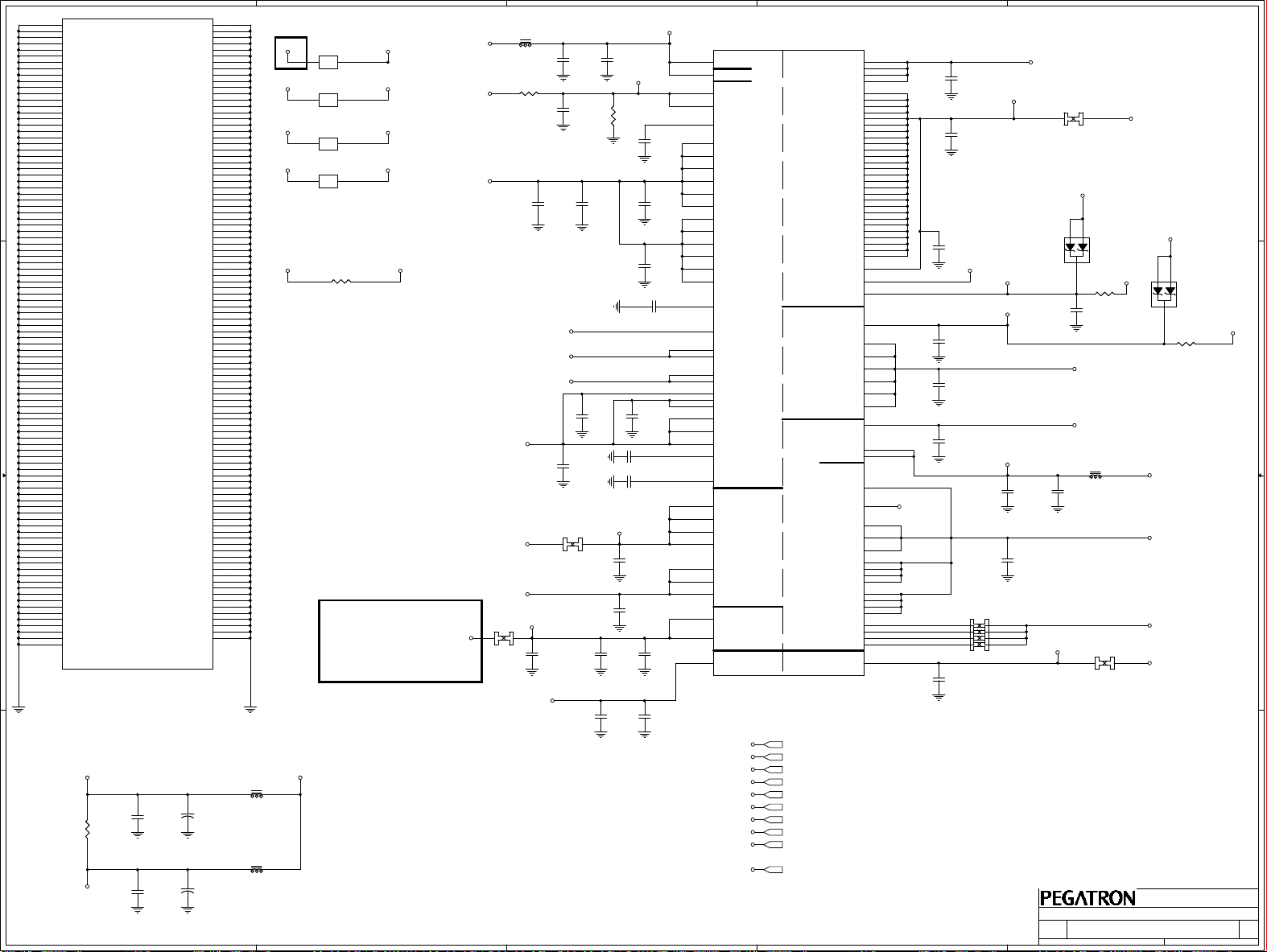

H36Y Schematics for Calpella Platform Rev. 2.2

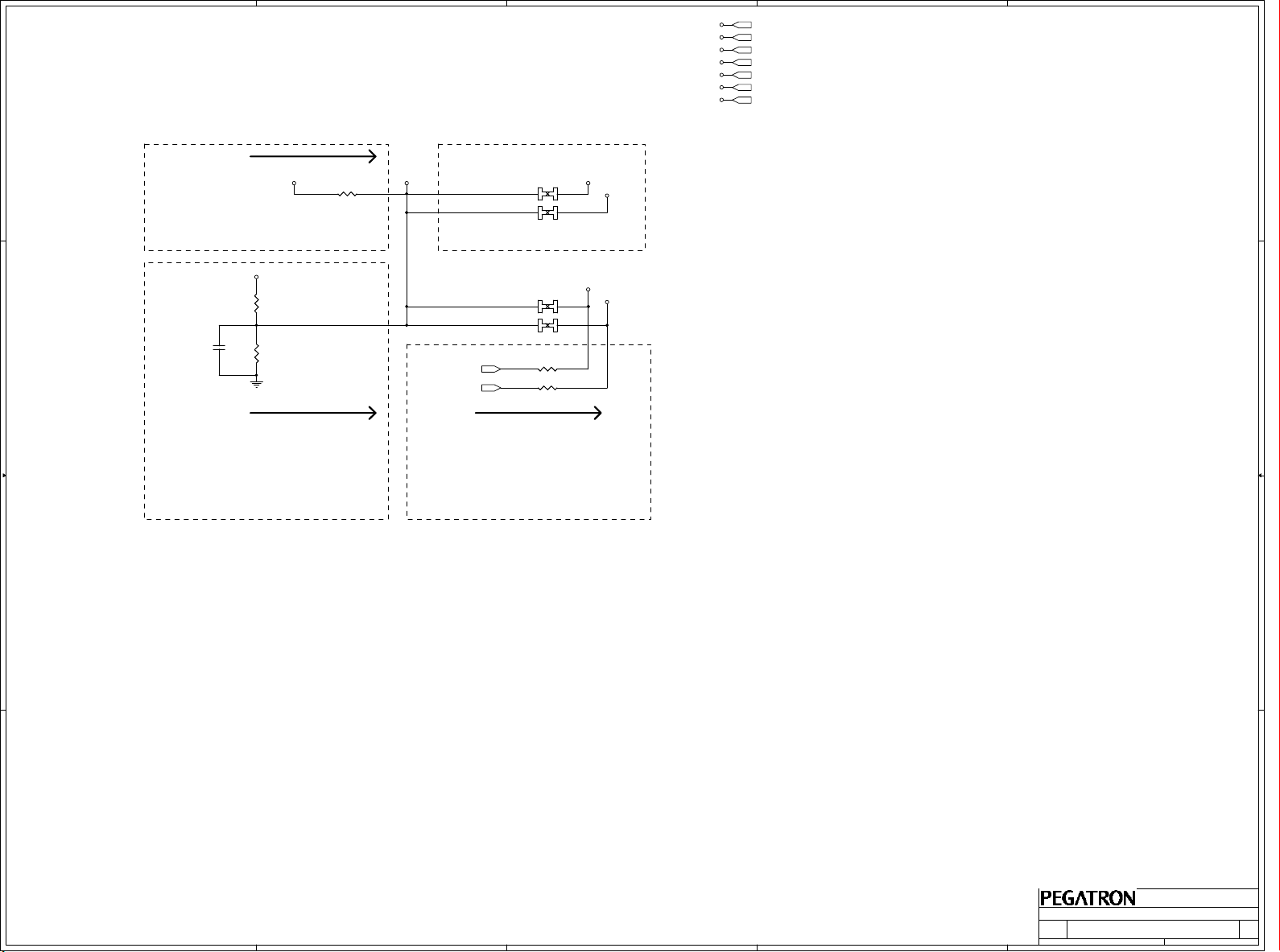

BLOCK DIAGRAM

HDMI

HDMI

Page 48

Page 46

Page 45

Page 37

Page 65

HDMIHDMI

SDVO

SPI ROM

Thermal Sensor

CardReader

Alcor AU4633

Azalia Codec

Discharge Circuit

Reset Circuit

Page 48

LVDS

LVDS

LVDSLVDS

CRT

CRT

CRTCRT

Debug Conn.

EC

ITE IT8512E

s

s

s

s

u

u

u

u

B

B

B

B

M

M

M

M

Page 30

S

S

S

S

PWM Fan

Page 40~41

Realtek ALC269

PCIE x16

PCIE x16

PCIE x16PCIE x16

Page 44

Page 30Page 31

SPI ROM

Page 28

Page 50

PCIEx1

PCIEx1

PCIEx1PCIEx1

Azalia

Azalia

AzaliaAzalia

Page 36

DC & BATT. Conn.

Page 57

Page 32

LPC

LPC

LPCLPC

Skew Holes

CPU

Arrandale

(DC)

4

4

4

4

x

x

x

x

I

I

I

I

D

D

D

D

F

F

F

F

4

4

4

4

x

x

x

x

I

I

I

I

M

M

M

M

D

D

D

D

PCH

Ibex Peak-M

A

A

A

A

s

s

s

s

T

T

T

T

u

u

u

u

A

A

A

A

B

B

B

B

S

S

S

S

M

M

M

M

S

S

S

S

1

0

5

Clock Generator

ICS ICS9LRS3197

Page 60

Page 65

DDR3 1333MHz

DDR3 1333MHz

DDR3 1333MHzDDR3 1333MHz

Page 3~7

Page 20~28

ODD

HDD(1)

eSATA

PCIEx1

PCIEx1

PCIEx1PCIEx1

USB

USB

USBUSB

Page 51

Page 51

Page 66

Page 29

DDR3 SO-DIMM

9

4

5

0

1

2

12

13

MiniCard

2

WLAN

Shirley Peak/ Echo Peak

1

MiniCard

6

3

GigaLAN

ExpressCard

USB Port(1)

USB Port(2)

USB Port(3)

Bluetooth

CMOS Camera

HSPA (3G)

AR8131

Page 16~18

Page 53

Page 64

Page 33~34

Page 43

Page 52

Page 52

Page 52

Page 61

Page 45

RJ45

Page 34

Power

CPU_VCORE

System

+1.8VS

GFX_CORE

Charger

Load Switch

Power Protect

HDMI

CRT

LCD Panel

Touchpad

Keyboard

Speaker

Audio Jack

Page 80

Page 81

VTT

Page 82

DDR

Page 83

Page 85

Page 86

Page 88

Detect

Page 90

Page 91

Page 92

Title :

Title :

Title :

Block Diagram

Block Diagram

Block Diagram

Kuansheng Yang

Kuansheng Yang

Engineer:

Engineer:

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

1

Kuansheng Yang

1 99Monday, May 10, 2010

1 99Monday, May 10, 2010

1 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

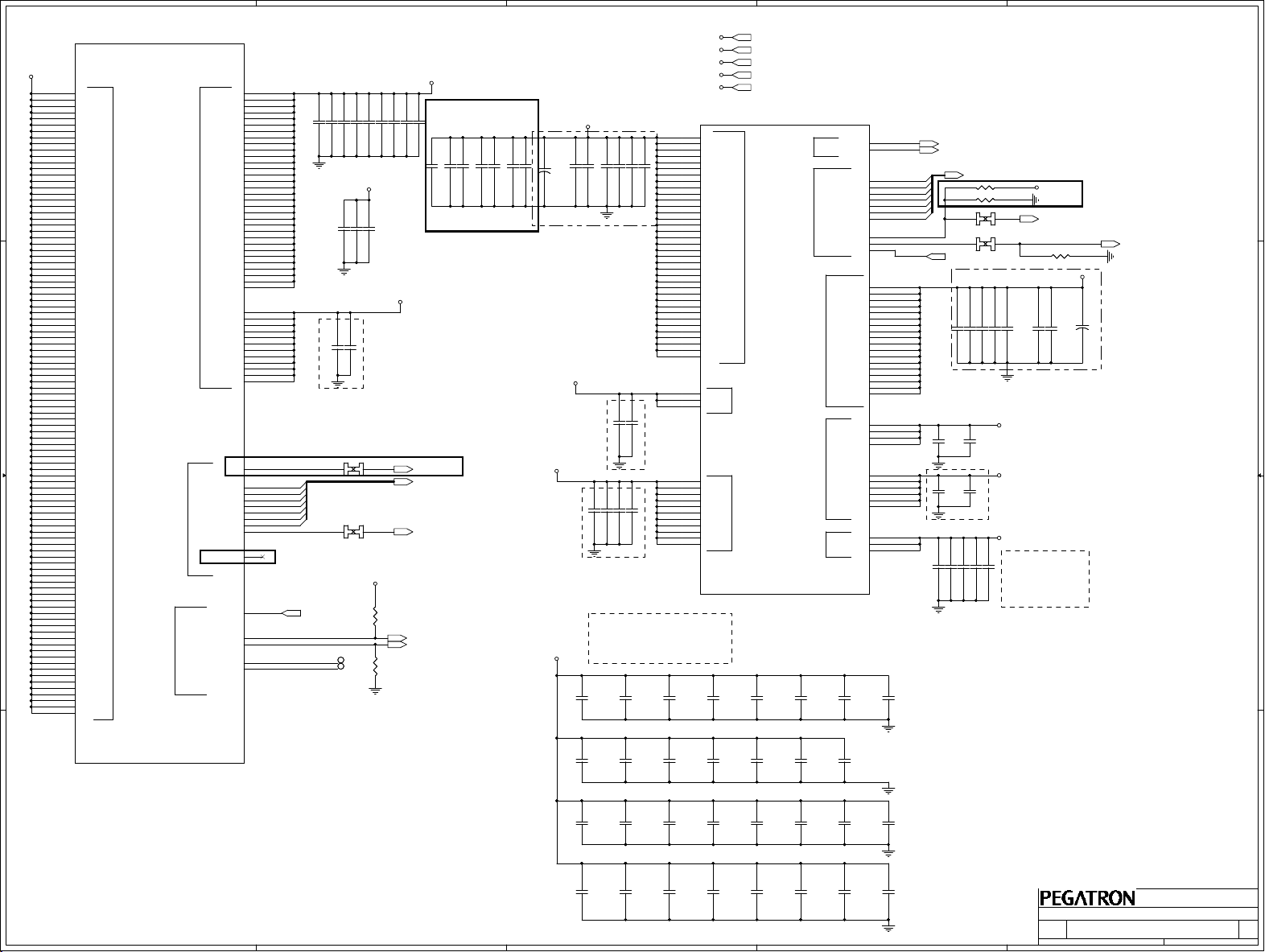

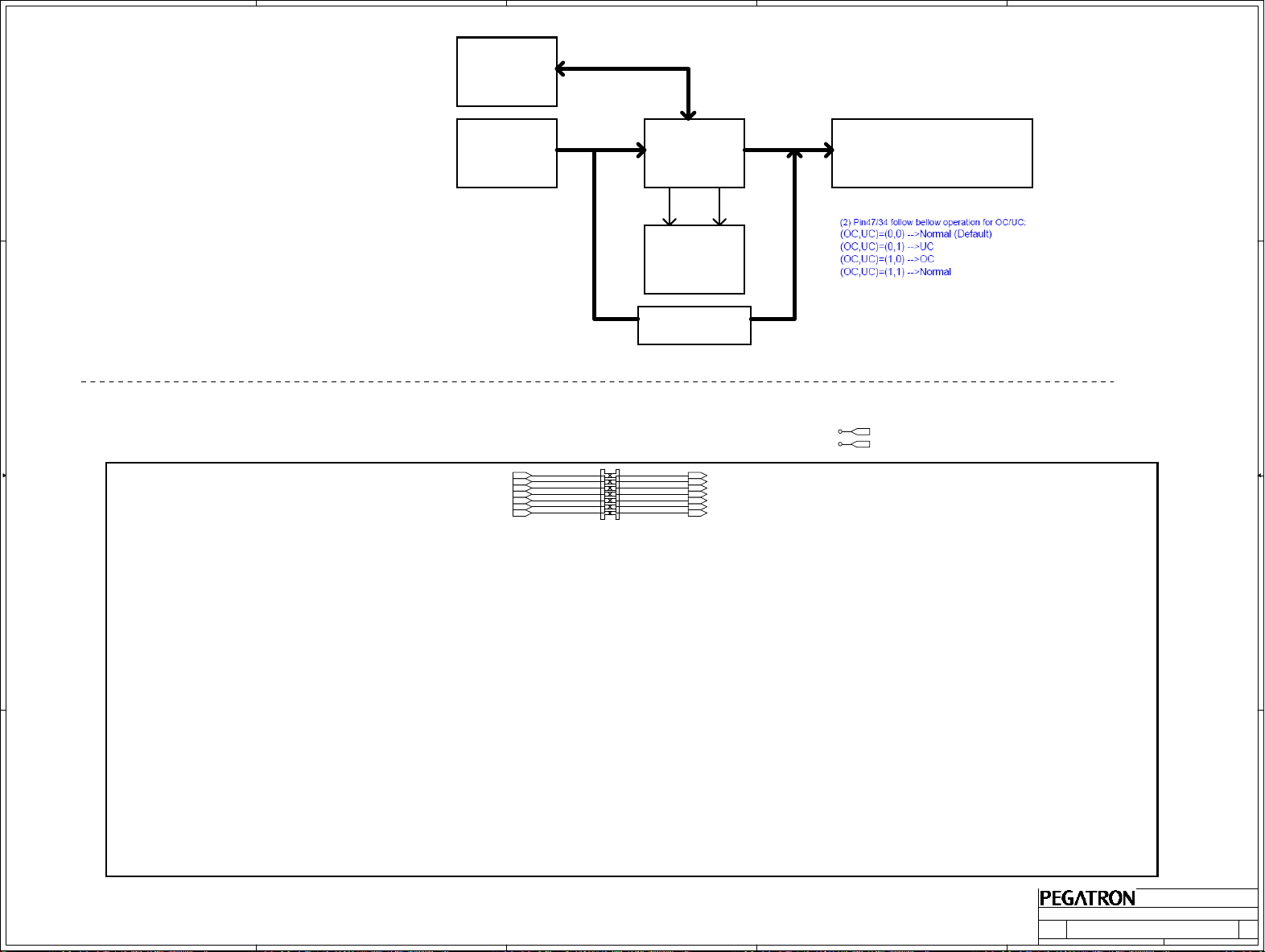

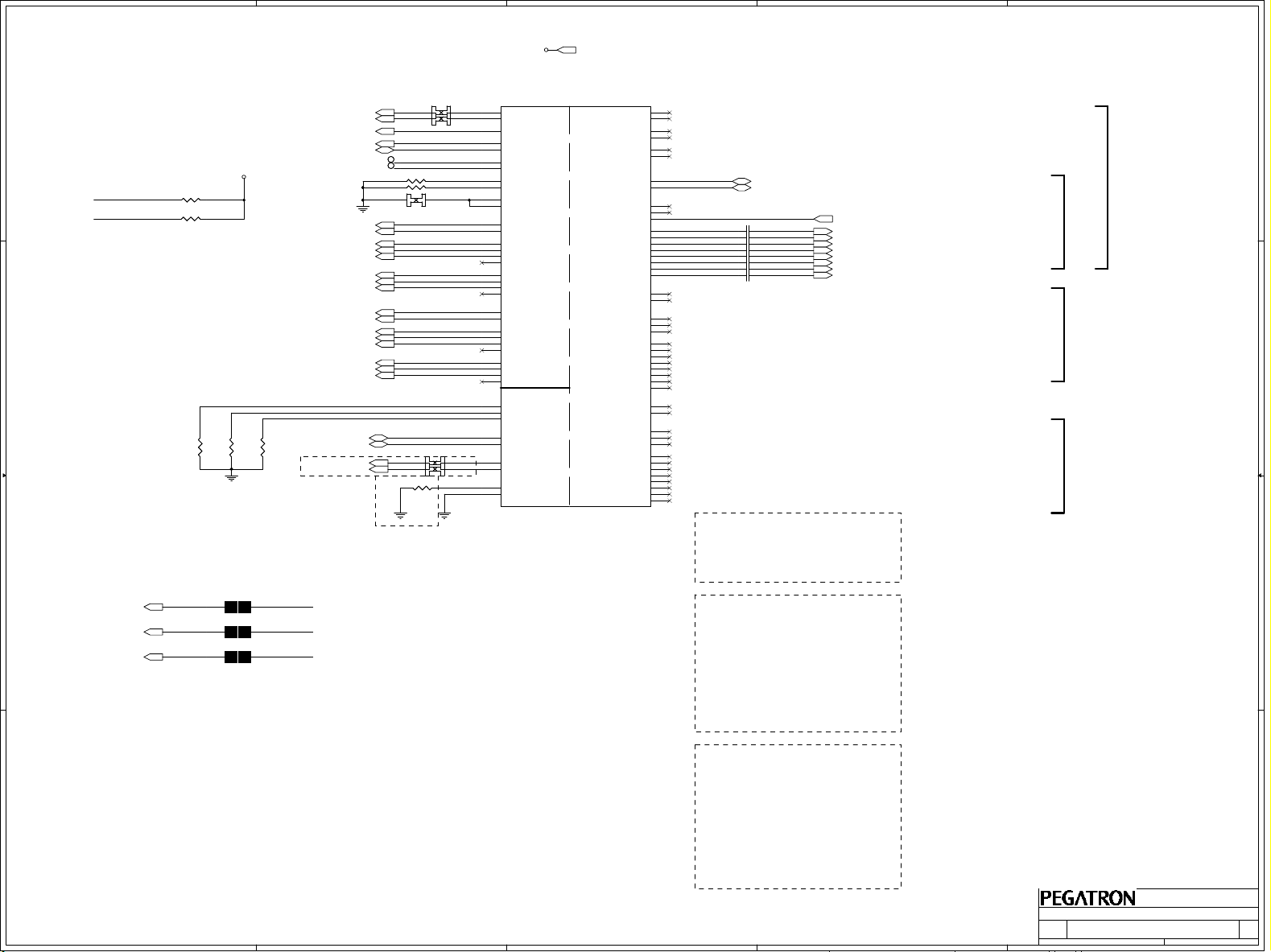

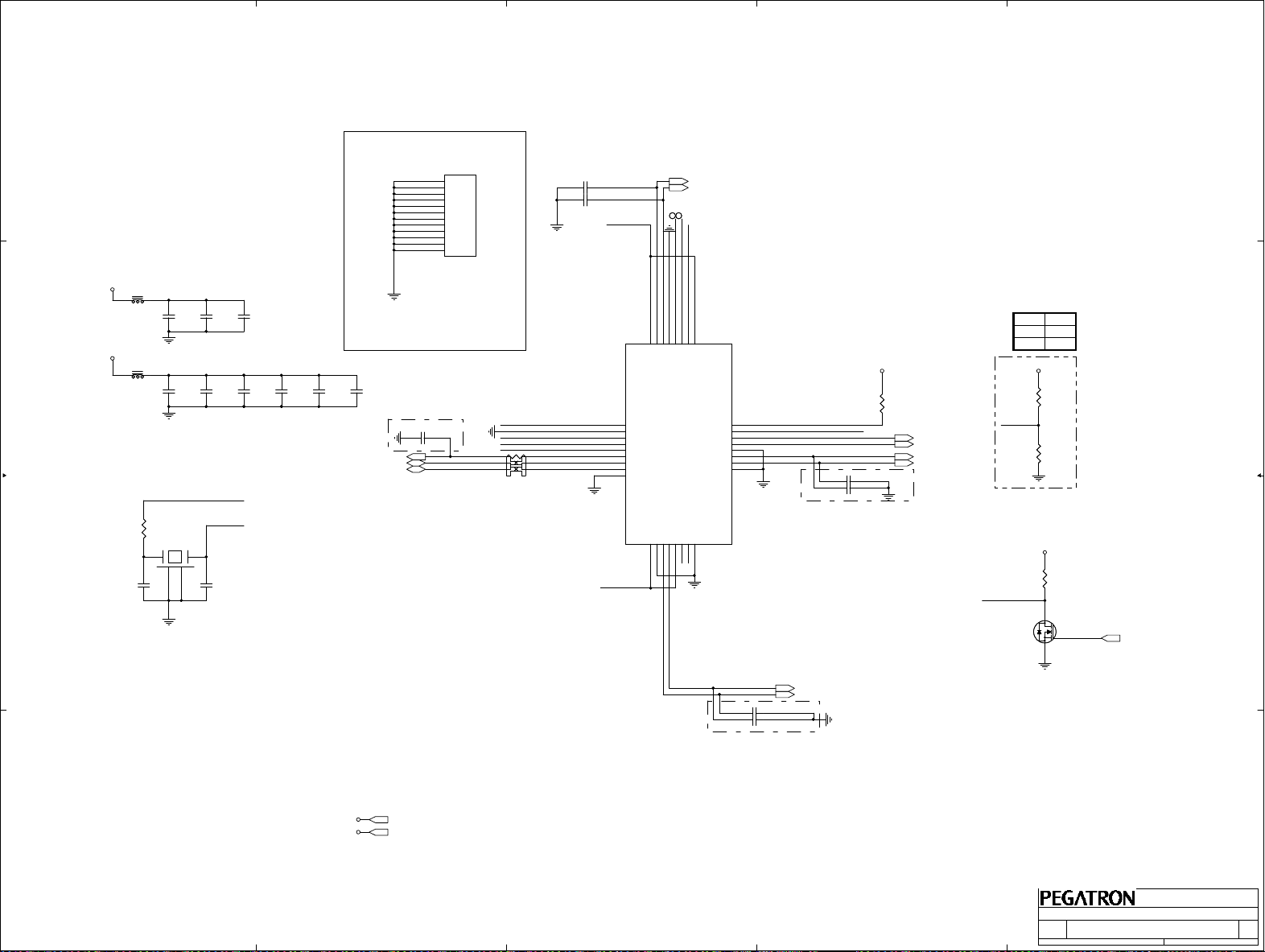

Page 2

PCH_IBEX

5

GPIO

D D

C C

B B

A A

PCH_IBEX

GPIO

GPIO 00

GPIO 01

GPIO [2:5]

GPIO 06

GPIO 07

GPIO 08

GPIO 09

GPIO 10

GPIO 11

GPIO 12

GPIO 13

GPIO 14

GPIO 15

GPIO 16 +3VS

GPIO 17 +3VSGPIO 18 +3VS

GPIO 19 +3VS

GPIO 20 +3VS

GPIO 21

GPIO 22

GPIO 23

GPIO 24 +3VSUS

GPIO 26

GPIO 27

GPIO 28

GPIO 29

GPIO 30

GPIO 31

GPIO 32

GPIO 33

GPIO 34

GPIO 35

GPIO 36

GPIO 37

GPIO 38

GPIO 39 +3VS

GPIO 40

GPIO 41

GPIO 42

GPIO 43

GPIO 44

GPIO 45

GPIO 46

GPIO 47

GPIO 48

GPIO 49

GPIO 50

GPIO 51

GPIO 52

GPIO 53

GPIO 54

GPIO 55

GPIO 56

GPIO 57

GPIO 58

GPIO 59

GPIO 60

GPIO 61

GPIO 62

GPIO 63

GPIO 64

GPIO 65

GPIO 66

GPIO 67

GPIO 72

GPIO 73

GPIO 74

GPIO 75

5

-

-

Native

-

-

GPI

Native

Native USB_OC6#

GPI

-

-

Native

GPO

-

Native

Native

Native

GPO

-

NativeGPIO 25

- CLK_REQ4#

- VRM_EN

GPO

Native ME_PM_SLP_LAN#

Native

Native

Native

Native

Native

GPO CAP_RST#_ICH

-

GPI

GPI

Native

Native

Native

Native

Native

-

-

- CLKREQ_PEG#

GPO

--PCI_REQ1#

-

-

Native

Native

GPO

Native

Native USB_OC0#

-

-

-

-

-

-

-

Native

-

-

-

Native

Signal NameUse As Power

GPIO0

DOCKING_DET#

PCI_INT[E:H]#

DGPU_PWR_EN

XIDE_BAY_IN#

EXT_SMI#

USB_OC5#

EXT_SCI#

PM_LANPHY_EN

DGPU_PWR_EN_R

USB_OC7#

BT_LED

DGPU_HOLD_RST#

DGPU_PWR_OK

CLK_REQ1#

SATA1GP

CLKREQ2_WLAN#

SATA0GP

WLAN_LED

LPC_DRQ#1

OC_LAN_RST#

CLKREQ3_NEWCARD#

WLAN_ON

ME_SUSPWRDNACK

ME_AC_PRESENT

PM_CLKRUN#

HDA_DOCK_EN#

STP_PCI#

DGPU_PWR_EN#

DGPU_PRSNT#

PCB_ID0

PCB_ID1

USB_OC1#

USB_OC2#

USB_OC3#

USB_OC4#

CLK_REQ5_LAN#

CLK_REQ6#

CLK_REQ7#

EMAIL_LED

PCH_TEMP_ALERT#

PCI_GNT1#

PCI_REQ2#PCI_GNT2#

PCI_REQ3#

PCI_GNT3#

CLKREQ_GLAN#_R

BT_ON

SML1_CLK

RTLAN_DSM_EN

PM_SUS_STAT#

SUS_CLK

SLP_S5#

CLK_OUT0

CLK_OUT1

CLK_OUT2

CLK_USB48_CR

PM_BATLOW#

CLK_REQ0#

SML1ALERT#

SML1_DAT

4

Internal &

External

Pull-up/down

-

EXT PU

EXT PU

EXT PU

EXT PU

EXT PU & INT PU

EXT PU

EXT PU

EXT PU

EXT PU

-

EXT PU

INT PD

-

EXT PD & INT TBD

EXT PU(DNI)/PD

-

EXT PU(DNI)/PD

-

EXT PD

-

EXT PU

EXT PU(DNI)/PD

EXT PU(Not used)

INT WEAK PU

EXT PD

EXT PU(DNI)/PD(DNI)

EXT PU

EXT PU

EXT PU

-

EXT PU

EXT PU/PD(DNI)

EXT PU

EXT PU

EXT PD

EXT PD

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PD

-

-

EXT PU (Not used)

INT PU

EXT PU

INT PU

INT PU

INT PU

EXT PU(DNI)/PD

EXT PU(DIODE)

EXT PU

EXT PU (Not used)

EXT PU

-

-

-

INT TBD

INT TBD

INT TBD

INT TBD

EXT PU (Not used)

EXT PU (Not used)

EXT PU (Not used)

EXT PU

4

+3VS

+3VS

+5VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+5VS

+3VS

+5VS

+3VS

+5VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

+3VS

+3VS

+3VS

+3VS

+3VSUS

+3VSUS

+3VSUS

+3VSUS

EC

IT8512

3

EC GPIO

Use As Signal Name

GPA0

GPA1

GPA2

GPA3

GPA4

GPA5

GPA6

GPA7

GPB0

GPB1

GPB2

GPB3

GPB4

GPB5

GPB6

GPB7

GPC0

GPC1

GPC2

GPC3

GPC4

GPC5

GPC6

GPC7

GPD0

GPD1

GPD2

GPD3

GPD4

GPD5

GPD6

GPD7

GPE0

GPE1

GPE2

GPE3

GPE4

GPE5

GPE6

GPE7

GPF0

GPF1

GPF2

GPF3

GPF4

GPF5

GPF6

GPF7

GPG0

GPG1

GPG2

GPG6 GPH0

GPH1

GPH2

GPH3

GPH4

GPH5

GPH6 CAP_LED#

GPI0

GPI1

GPI2

GPI3

GPI4

GPI5

GPI6

GPI7

GPJ0

GPJ1

GPJ2

GPJ4

GPJ5 GFX_VR

PWR_LED#

O

CHG_LED#

O

-

LCD_BL_PWM

O

FAN_PWM

O

-

-

-

-

SMB0_CLK

IO

SMB0_DAT

IO

A20GATE

O

RCIN#

O

PM_RSMRST#

O

SMB1_CLK

IO

SMB1_DAT

IO

PM_PWRBTN#

O

AC_IN_OC#

I

OP_SD#

O

BAT1_IN_OC#

I

RFON_SW#

I

PWRLIMIT#

I

PM_SUSC#

I

BUF_PLT_RST#

I

EXT_SCI#

O

EXT_SMI#

O

LCD_BACKOFF#

O

FAN0_TACH

I

VSUS_ON

O

SUSC_EC#

O

SUSB_EC#

O

O

CPU_VRON

PWR_SW#

I

LID_SW#

I

CAP_ACK#

I

-

-

DISTP#

I

TP_CLK

I

TP_DAT

IO

THRO_CPU

O

ME_AC_PRESENT

O

KB_ID0

O

PM_SUSB#

I

-

PM_CLKRUN#

IO

3G_ON

I

GFX_VR_ON

O

-

-

-

O

PCH_TEMP_ALERT#

I

SUS_PWRGD

I

ALL_SYSTEM_PWRGD

I

VRM_PWRGD

I

ME_PM_SLP_LAN#

I

ME_PM_SLP_M#

I

ME_SUSPWRDNACK

I

CAP_RST#_EC

O

PM_PWROK

O

KB_ID1

O

-GPJ3

TP_LED

O

I

3

2

EC

IT8301

2

1

GPIO0 GPIO1

GPIO2

GPIO3

GPIO4

GPIO5

GPIO6

GPIO7

GPIO8

GPIO9

GPIO10

GPIO11

GPIO12

GPIO13

GPIO14

GPIO15

GPIO16

GPIO17

GPIO18

GPIO19

GPIO20

GPIO21

GPIO22

GPIO23

GPIO24

GPIO25

GPIO26

GPIO27

GPIO28

GPIO29

GPIO30

GPIO31

GPIO32

GPIO33

GPIO34

GPIO35

GPIO36

GPIO37

Signal NameUse AsEC GPIO

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

-

SM_BUS ADDRESS :

SM-Bus Device

Clock Generator

SO-DIMM 0

SO-DIMM 1

CPU Thermal IC(G780)

VGA Thermal IC(G781-1)

VGA Thermal Sensor(NB9E-GE1) 1001111x ( 9Eh )

VID Controller ASM8272 0011011x ( 36h )

PCIE 1

N/A

PCIE 2

Minicard WLAN

PCIE 3

Newcard

PCIE 4

N/A

PCIE 5

N/A

PCIE 6

GLAN

PCIE 7

N/A

PCIE 8

N/A

SATA0

SATA HDD

SATA1

SATA ODD

SATA2

N/A

SATA3

N/A

N/ASATA4

SATA5 eSATA

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

SM-Bus Address

1101001x ( D2h )

1010000x ( A0h )

1010001x ( A4h )

1001100x ( 98h )

1001101x ( 9Ah )

USB 0

USB Port (1)

USB 1

USB Port (2)

USB 2

USB Port (3)

USB 3

N/A

N/A

USB 4

USB 5

Newcard

Card Reader

USB 6

USB 7

3G

N/A

USB 8

WLAN

USB 9

USB 10

N/A

USB 11

N/A

Bluetooth

USB 12

USB 13

CMOS Camera

Engineer:

Engineer:

Engineer:

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

1

Title :

Title :

Title :

System Setting

System Setting

System Setting

Kuansheng Yang

Kuansheng Yang

Kuansheng Yang

2 99Monday, May 10, 2010

2 99Monday, May 10, 2010

2 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

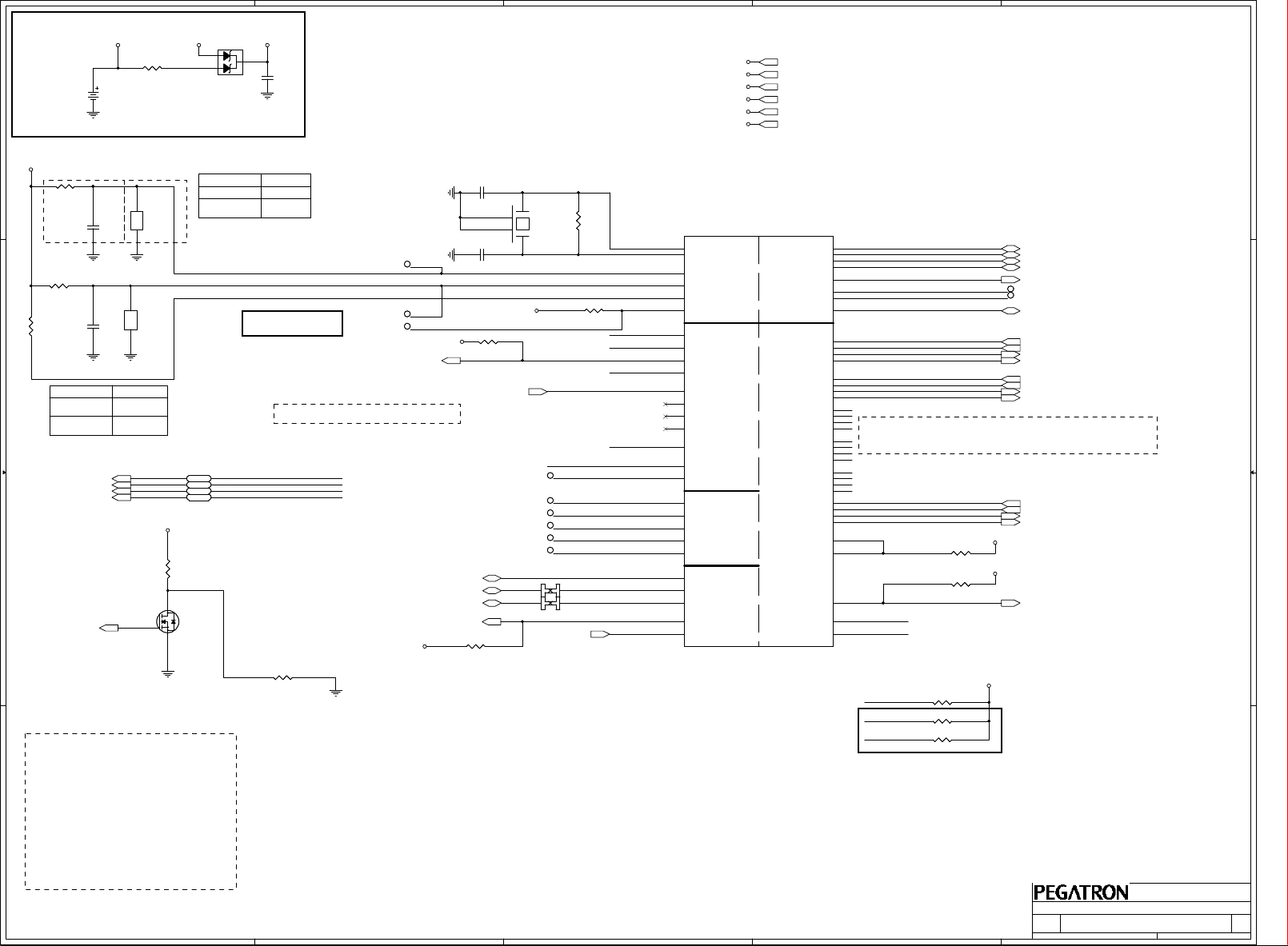

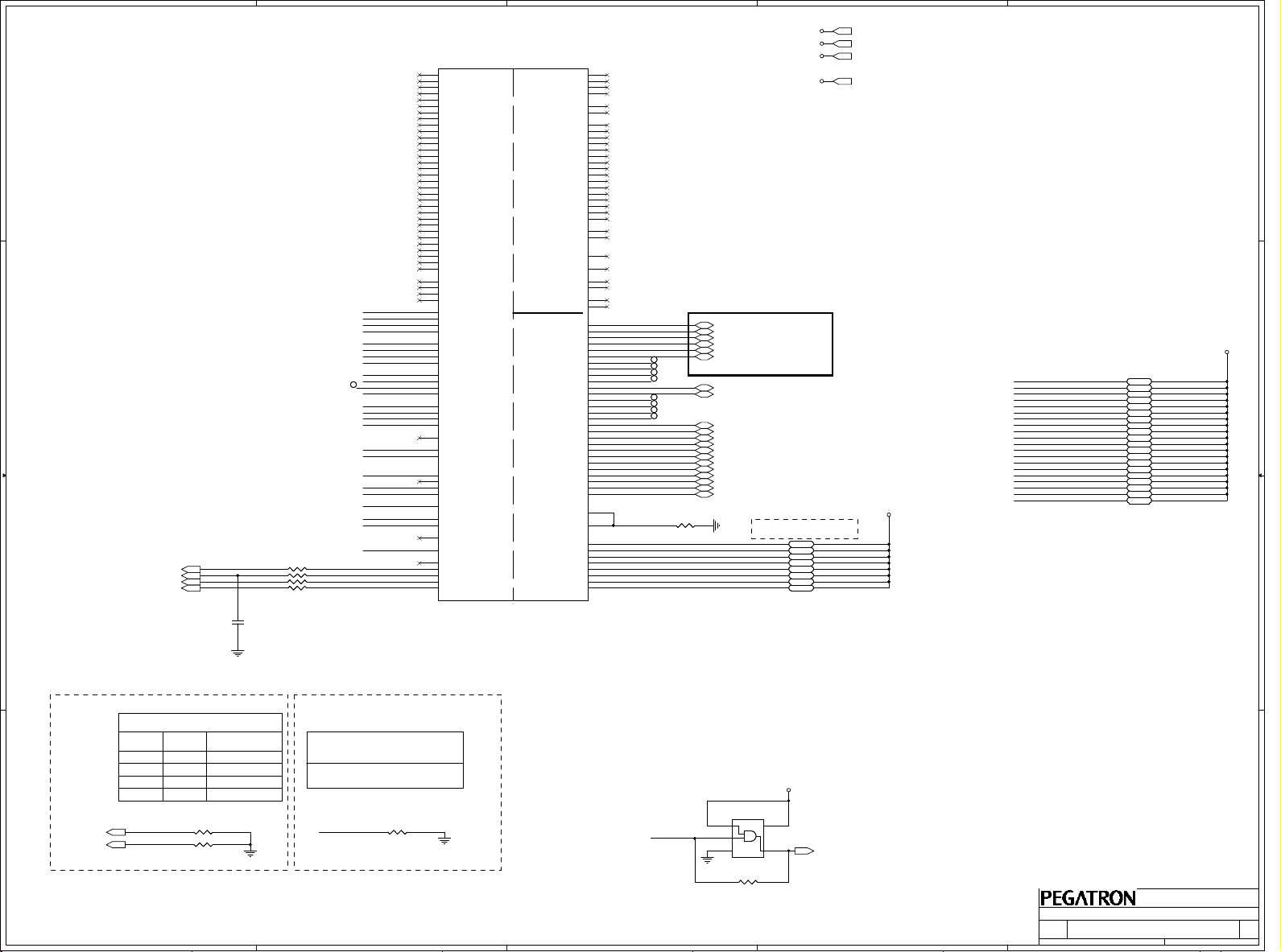

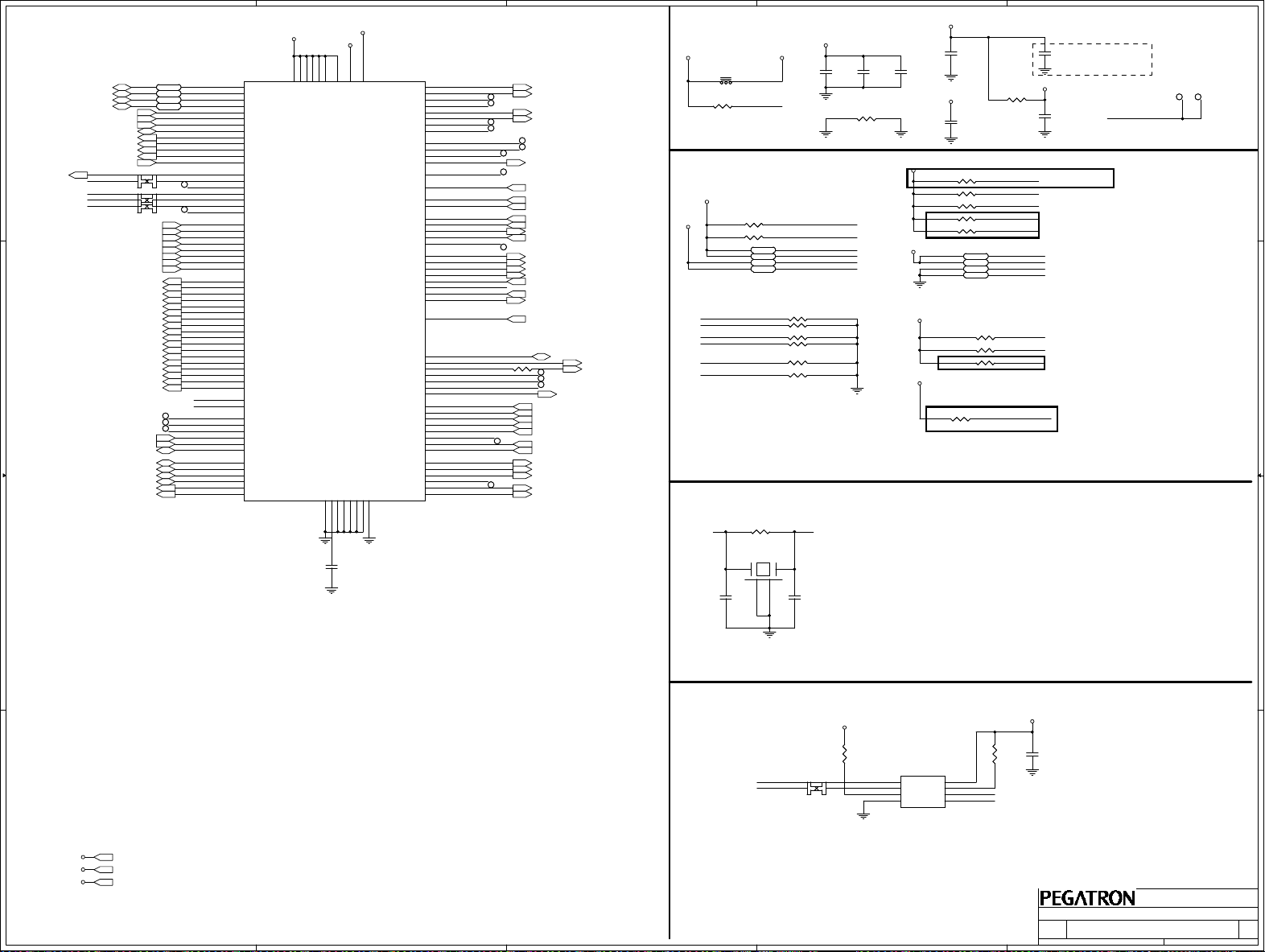

Page 3

5

U0301A

U0301A

FDI_TXN0

FDI_TXN1

FDI_TXN2

FDI_TXN3

FDI_TXN4

FDI_TXN5

FDI_TXN6

FDI_TXN7

FDI_TXP0

FDI_TXP1

FDI_TXP2

FDI_TXP3

FDI_TXP4

FDI_TXP5

FDI_TXP6

FDI_TXP7

A24

DMI_RX#[0]

C23

DMI_RX#[1]

B22

DMI_RX#[2]

A21

DMI_RX#[3]

B24

DMI_RX[0]

D23

DMI_RX[1]

B23

DMI_RX[2]

A22

DMI_RX[3]

D24

DMI_TX#[0]

G24

DMI_TX#[1]

F23

DMI_TX#[2]

H23

DMI_TX#[3]

D25

DMI_TX[0]

F24

DMI_TX[1]

E23

DMI_TX[2]

G23

DMI_TX[3]

E22

FDI_TX#[0]

D21

FDI_TX#[1]

D19

FDI_TX#[2]

D18

FDI_TX#[3]

G21

FDI_TX#[4]

E19

FDI_TX#[5]

F21

FDI_TX#[6]

G18

FDI_TX#[7]

D22

FDI_TX[0]

C21

FDI_TX[1]

D20

FDI_TX[2]

C18

FDI_TX[3]

G22

FDI_TX[4]

E20

FDI_TX[5]

F20

FDI_TX[6]

G19

FDI_TX[7]

F17

FDI_FSYNC[0]

E17

FDI_FSYNC[1]

C17

FDI_INT

F18

FDI_LSYNC[0]

D17

FDI_LSYNC[1]

SOCKET989

SOCKET989

1201-0017000

1201-0017000

DMI_TXN0<22>

DMI_TXN1<22>

DMI_TXN2<22>

DMI_TXN3<22>

DMI_TXP0<22>

DMI_TXP1<22>

DMI_TXP2<22>

DMI_TXP3<22>

DMI_RXN0<22>

DMI_RXN1<22>

DMI_RXN2<22>

D D

C C

DMI_RXN3<22>

DMI_RXP0<22>

DMI_RXP1<22>

DMI_RXP2<22>

DMI_RXP3<22>

FDI_TXN[7:0]<22>

FDI_TXP[7:0]<22>

FDI_FSYNC0<22>

FDI_FSYNC1<22>

FDI_INT<22>

FDI_LSYNC0<22>

FDI_LSYNC1<22>

For Intel GFX display

PEG_ICOMPI

PEG_ICOMPO

PEG_RCOMPO

PEG_RBIAS

PEG_RX#[0]

PEG_RX#[1]

PEG_RX#[2]

DMI Intel(R) FDI

DMI Intel(R) FDI

PEG_RX#[3]

PEG_RX#[4]

PEG_RX#[5]

PEG_RX#[6]

PEG_RX#[7]

PEG_RX#[8]

PEG_RX#[9]

PEG_RX#[10]

PEG_RX#[11]

PEG_RX#[12]

PEG_RX#[13]

PEG_RX#[14]

PEG_RX#[15]

PEG_RX[0]

PEG_RX[1]

PEG_RX[2]

PEG_RX[3]

PEG_RX[4]

PEG_RX[5]

PEG_RX[6]

PEG_RX[7]

PEG_RX[8]

PEG_RX[9]

PEG_RX[10]

PEG_RX[11]

PEG_RX[12]

PEG_RX[13]

PEG_RX[14]

PEG_RX[15]

PEG_TX#[0]

PEG_TX#[1]

PEG_TX#[2]

PEG_TX#[3]

PEG_TX#[4]

PEG_TX#[5]

PEG_TX#[6]

PEG_TX#[7]

PEG_TX#[8]

PEG_TX#[9]

PEG_TX#[10]

PEG_TX#[11]

PEG_TX#[12]

PEG_TX#[13]

PCI EXPRESS -- GRAPHICS

PCI EXPRESS -- GRAPHICS

PEG_TX#[14]

PEG_TX#[15]

PEG_TX[0]

PEG_TX[1]

PEG_TX[2]

PEG_TX[3]

PEG_TX[4]

PEG_TX[5]

PEG_TX[6]

PEG_TX[7]

PEG_TX[8]

PEG_TX[9]

PEG_TX[10]

PEG_TX[11]

PEG_TX[12]

PEG_TX[13]

PEG_TX[14]

PEG_TX[15]

B26

A26

B27

A25

K35

J34

J33

G35

G32

F34

F31

D35

E33

C33

D32

B32

C31

B28

B30

A31

J35

H34

H33

F35

G33

E34

F32

D34

F33

B33

D31

A32

C30

A28

B29

A30

L33

M35

M33

M30

L31

K32

M29

J31

K29

H30

H29

F29

E28

D29

D27

C26

L34

M34

M32

L30

M31

K31

M28

H31

K28

G30

G29

F28

E27

D28

C27

C25

PEG_IRCOMP_R

EXP_RBIAS

4

R0301 49.9Ohm1%R0301 49.9Ohm1%

1 2

R0302 750OHM1%R0302 750OHM1%

1 2

3

SKTOCC#:pulled to ground on processor.

may use to determine if CPU is present

U0301B

AT23

AT24

AT26

AH24

AK14

AT15

AN26

AK15

AP26

AL15

AN14

AN27

AK13

AM15

AM26

AL14

G16

U0301B

COMP3

COMP2

COMP1

COMP0

SKTOCC#

CATERR#

PECI

PROCHOT#

THERMTRIP#

RESET_OBS#

PM_SYNC

VCCPWRGOOD_1

VCCPWRGOOD_0

SM_DRAMPWROK

VTTPWRGOOD

TAPPWRGOOD

RSTIN#

SOCKET989

SOCKET989

H_COMP3

R030320Ohm 1% R030320Ohm 1%

12

H_COMP2

R030420Ohm 1% R030420Ohm 1%

12

H_COMP1

R030549.9Ohm 1% R030549.9Ohm 1%

12

H_COMP0

R030649.9Ohm 1% R030649.9Ohm 1%

12

TP_SKTOCC#

T0301T0301

1

R030749.9Ohm 1% R030749.9Ohm 1%

@

@

R0322

R0322

68Ohm

68Ohm

1

1

R0318

R0318

1.5KOHM

1.5KOHM

12

12

H_PECI_ISO

12

12

H_PROCHOT_S#_R

12

H_THRMTRIP#_R

12

H_CPURST#

PM_SYNC#_R

12

VCCPWRGOOD_1_R

12

VCCPWRGOOD_0_R

12

VDDPWRGOOD_R

12

H_VTTPWRGD_R

H_PWRGD_XDP

PLT_RST#_R

12

R0319

R0319

750OHM

750OHM

+VTT_CPU

H_CATERR#

R0317 0Ohm

R0317 0Ohm

THRO_CPU

H_PECI<25>

SP0301 R0402SP0301 R0402

+VTT_CPU

H_PROCHOT_S#

H_THRMTRIP#<25,32>

PM_SYNC#<22>

H_CPUPWRGD<25>

H_DRAM_PWRGD<22>

H_VTTPWRGD< 92>

BUF_PLT_RST#<24,30,32,33,43,53,54>

SP0302 R0402SP0302 R0402

SP0303 R0402SP0303 R0402

T0303T0303

SP0304 R0402SP0304 R0402

SP0305 R0402SP0305 R0402

SP0306 R0402SP0306 R0402

SP0307 R0402SP0307 R0402

T0302T0302

1 2

2

MISC

MISC

CLOCKS

CLOCKS

THERMAL PWR MANAGEMENT

THERMAL PWR MANAGEMENT

DDR3

MISC

DDR3

MISC

JTAG & MBP

JTAG & MBP

BCLK#

BCLK_ITP

BCLK_ITP#

PEG_CLK

PEG_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

SM_DRAMRST#

SM_RCOMP[0]

SM_RCOMP[1]

SM_RCOMP[2]

PM_EXT_TS#[0]

PM_EXT_TS#[1]

PRDY#

PREQ#

TRST#

TDI_M

TDO_M

BPM#[0]

BPM#[1]

BPM#[2]

BPM#[3]

BPM#[4]

BPM#[5]

BPM#[6]

BPM#[7]

+VTT_CPU

BCLK

TCK

TMS

TDI

TDO

DBR#

+1.5V

A16

B16

AR30

AT30

E16

D16

A18

A17

F6

AL1

AM1

AN1

AN15

AP15

+VTT_CPU

AT28

AP27

AN28

AP28

AT27

AT29

AR27

AR29

AP29

AN25

AJ22

AK22

AK24

AJ24

AJ25

AH22

AK23

AH23

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_EXP_P

CLK_EXP_N

CLKDREF

CLKDREF#

SM_RCOMP0

SM_RCOMP1

SM_RCOMP2

RN0301A

RN0301A

RN0301B

RN0301B

+VTT_CPU <6,25,26,32,57,82>

+1.5V <6,16,57,83>

R0323 0OhmR0323 0Ohm

R0324 0OhmR0324 0Ohm

R0331 100Ohm1%R0331 100Ohm1%

1 2

R0332 24.9Ohm1%R0332 24.9Ohm1%

1 2

R0333 130Ohm1%R0333 130Ohm1%

1 2

PM_EXTTS#1

10KOHM

10KOHM

10KOHM

10KOHM

XDP_PRDY#

1

H_PREQ#

H_TCK

H_TMS

H_TRST#

H_TDI

H_TDO

H_TDI_M

H_TDO_M

H_DBR#

XDP_BPM#0

1

XDP_BPM#1

XDP_BPM#2

1

XDP_BPM#3

1

XDP_BPM#4

1

XDP_BPM#5

1

XDP_BPM#6

1

XDP_BPM#7

1

1 2

1 2

12

34

T0309T0309

T0310T0310

T0311T0311

T0304T0304

T0305T0305

T0306T0306

T0307T0307

T0308T0308

1

CLK selection

M_DRAMRST# <16,17>

120MHz from PCH.

IF NOT USED,

PULL-LOW FOR POWER SAVING.

PM_EXTTS#0 <16,17>

BCLK_CPU_P_PCH<25>

B B

BCLK_CPU_N_PCH<25>

CLK_DMI_PCH<21>

CLK_DMI#_PCH<21>

SP0313 R0402SP0313 R0402

SP0314 R0402SP0314 R0402

SP0315 R0402SP0315 R0402

SP0316 R0402SP0316 R0402

12

12

12

12

FDI disable: (For discrete graphic)

1. NC:

FDI_TX#[0:7],FDI_TX[0:7],FDI_RX#[0:7],FDI_RX[0:7]

VCC_AXGSENSE,VSS_AXGSENSE

2. Pull-down to GND via 1KΩ ± 5% resistor:

FDI_FSYNC[0:1],FDI_LSYNC[0:1],FDI_INT,GFX_IMON

~15mW power saving.(DG R0.8 P.70)

A A

3. Connected to GND:

VCCAXG,DPLL_REF_CLK,DPLL_REF_CLK#

4. Can be connected to GND directly:

DPLL_REF_CLK,DPLL_REF_CLK#

5. Connect to +V1.05S rail:

VCCFDIPLL

5

CLK_CPU_BCLK

CLK_CPU_BCLK#

CLK_EXP_P

CLK_EXP_N

FDI_FSYNC0

FDI_FSYNC1

FDI_LSYNC0

FDI_LSYNC1

FDI_INT

R0364 1KOhm@R0364 1KOhm@

1 2

R0361 1KOhm@R0361 1KOhm@

1 2

R0365 1KOhm@R0365 1KOhm@

1 2

R0362 1KOhm@R0362 1KOhm@

1 2

R0363 1KOhm@R0363 1KOhm@

1 2

4

H_CPURST#

R0313 68Ohm@R0313 68Ohm@

1 2

DRAMPWROK: (WW35 MoW)

Choose either one solution: -->Choose solution 2

1. This pin should have an external pull-up of 1K Ohms

to 10K Ohms to a rail of 1.05/1.1V which is ON in S0-S3

2. Connect this pin through a voltage divider circuit;

recommend 4.75K Ohms pull-up to DDR3 Power Rail

(VDDQ) of +V1.5U and a 12K Ohms pull-down to

ground to convert to processor’s VTT level.

+VTT_CPU

3

VDDPWRGOOD_R

+1.5V

R0320

R0320

1.1KOhm

1.1KOhm

1 2

12

R0321

R0321

3.01KOHM

3.01KOHM

R1.4--1

WW14_2009_WOM

H_PROCHOT_S#

D0301

PWRLIMIT#<30,90>

D0301

RB751V-40

RB751V-40

@

@

Default Strapping When Not Used

XDP_BPM#1

R0328 51Ohm @R0328 51Ohm @

H_PREQ#

R0329 51Ohm /boundary scanR0329 51Ohm /boundary scan

H_TDI

R0330 51Ohm @R0330 51Ohm @

H_TDO

R0336 51Ohm /boundary scanR0336 51Ohm /boundary scan

H_TMS

R0337 51Ohm @R0337 51Ohm @

H_TDO_M

R0314 0Ohm /boundary scanR0314 0Ohm /boundary scan

H_DBR#

R0338 1KOhm @R0338 1KOhm @

H_TCK

R0334 51Ohm @R0334 51Ohm @

H_TRST#

R0335 51Ohm /boundary scanR0335 51Ohm /boundary scan

2

12

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

3

3

D

D

Q0301

Q0301

2N7002

2N7002

1

1

THRO_CPU

G

G

S

S

2

2

+VTT_CPU

H_TDI_M

12

THRO_CPU <30>

Adding layout test point

for boundary sc an

Jervis 2009/1 1/09

CLK_CPU_BCLK

H_VTTPWRGD_R

VCCPWRGOOD_0_R

VCCPWRGOOD_1_R

PLT_RST#_R

H_TRST#

H_TCK

H_TMS

H_TDI

H_TDO

H_TDI_M

+3VS

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

H_TDO_M

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

1

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

CPU(1)_DMI,PEG,FDI,CLK,MISC

T0312T0312

1

T0313T0313

1

T0314T0314

1

T0315T0315

1

T0316T0316

1

T0317T0317

1

T0318T0318

1

T0319T0319

1

T0320T0320

1

T0321T0321

1

T0322T0322

1

T0323T0323

1

Kuansheng Yang

Kuansheng Yang

Kuansheng Yang

3 99Monday, May 10, 2010

3 99Monday, May 10, 2010

3 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

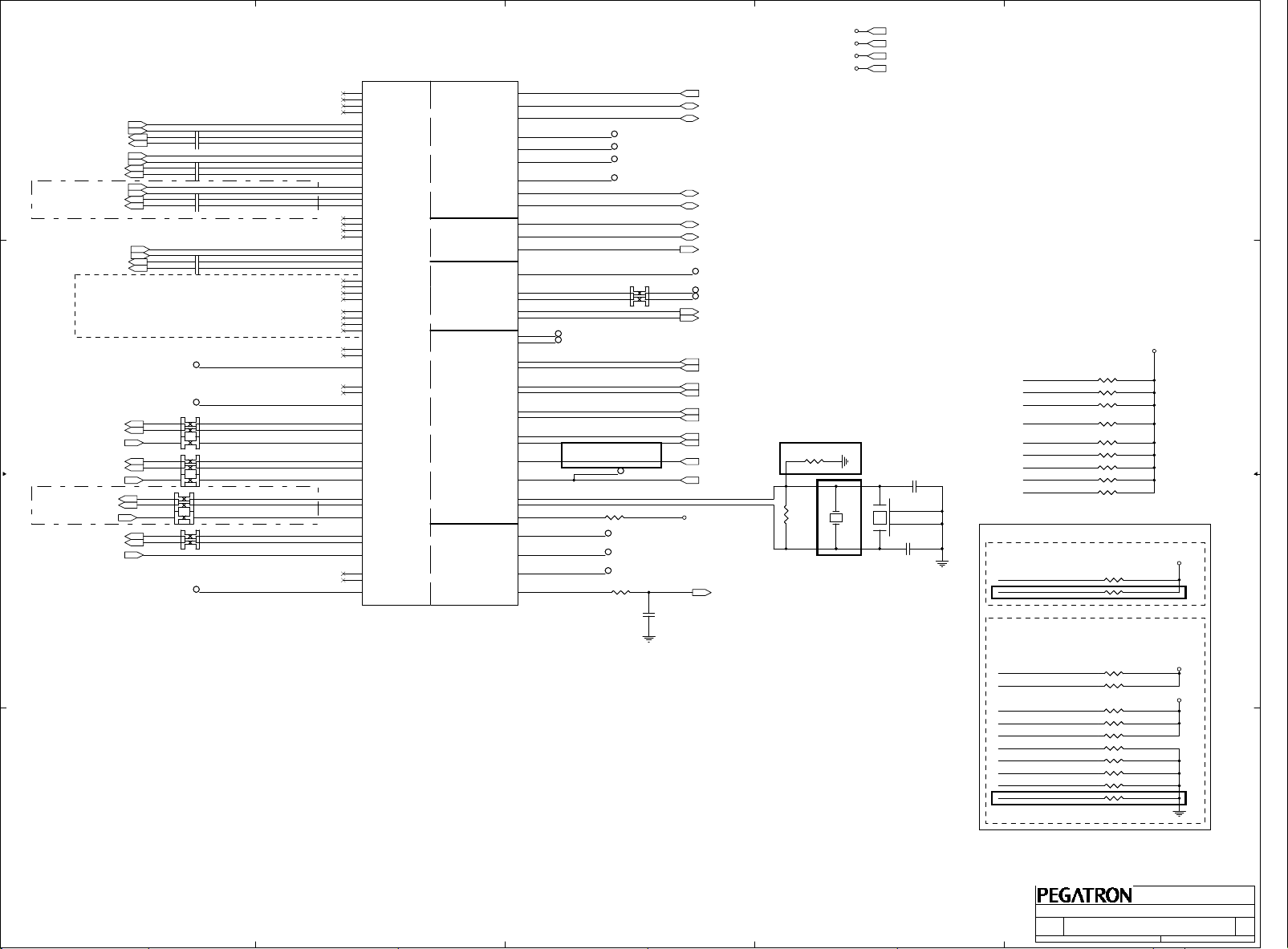

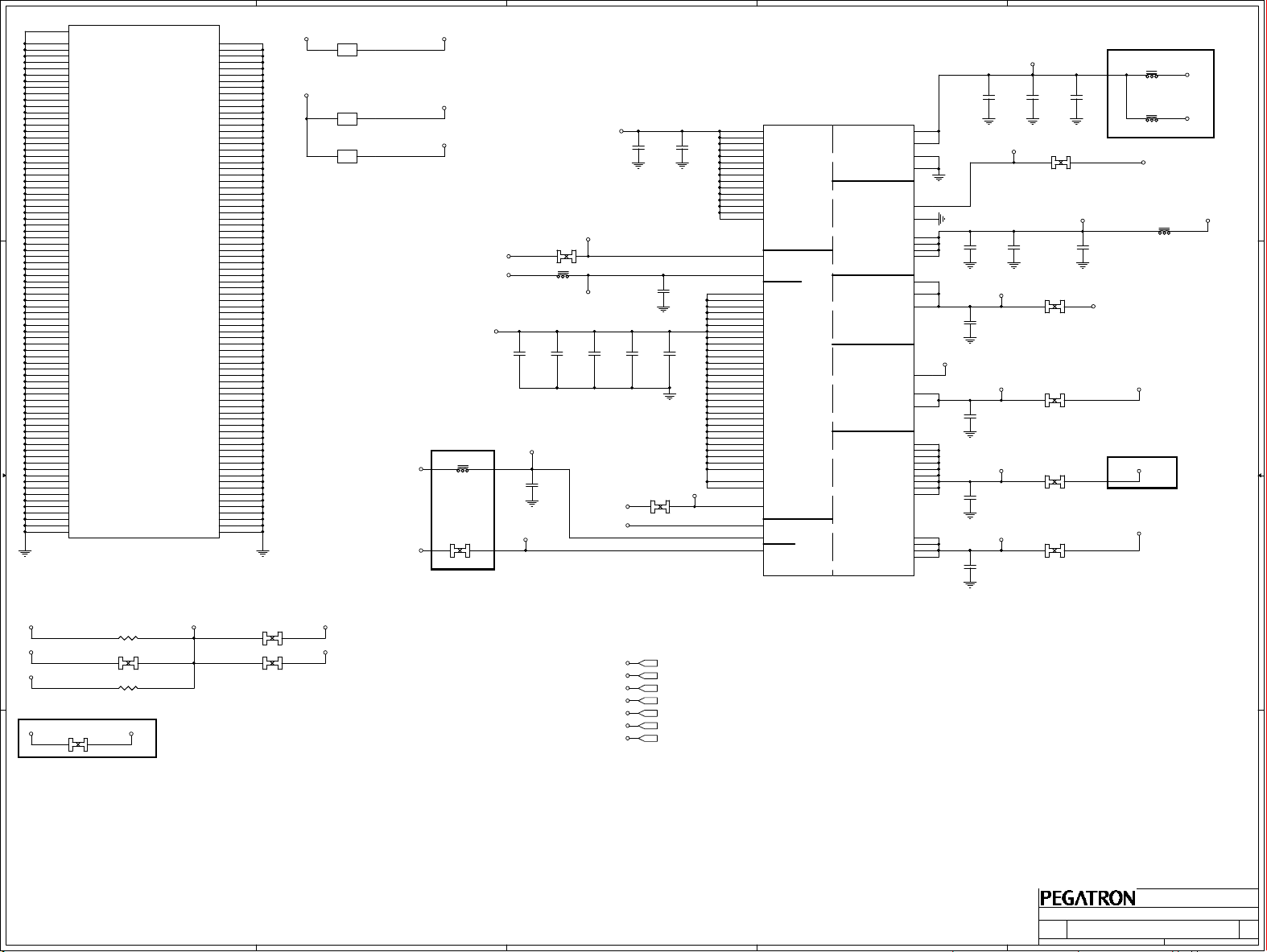

Page 4

5

U0301C

D D

U0301C

4

3

U0301D

U0301D

2

1

AA6

SA_CK[0]

M_A_DQ[63:0]<16>

C C

B B

M_A_DQ0

A10

AK12

AK11

AM10

AR11

AT11

AP12

AM12

AN12

AM13

AT14

AT12

AR14

AP14

AJ10

AL10

AL11

AL13

SA_DQ[0]

C10

SA_DQ[1]

C7

SA_DQ[2]

A7

SA_DQ[3]

B10

SA_DQ[4]

D10

SA_DQ[5]

E10

SA_DQ[6]

A8

SA_DQ[7]

D8

SA_DQ[8]

F10

SA_DQ[9]

E6

SA_DQ[10]

F7

SA_DQ[11]

E9

SA_DQ[12]

B7

SA_DQ[13]

E7

SA_DQ[14]

C6

SA_DQ[15]

H10

SA_DQ[16]

G8

SA_DQ[17]

K7

SA_DQ[18]

J8

SA_DQ[19]

G7

SA_DQ[20]

G10

SA_DQ[21]

J7

SA_DQ[22]

J10

SA_DQ[23]

L7

SA_DQ[24]

M6

SA_DQ[25]

M8

SA_DQ[26]

L9

SA_DQ[27]

L6

SA_DQ[28]

K8

SA_DQ[29]

N8

SA_DQ[30]

P9

SA_DQ[31]

AH5

SA_DQ[32]

AF5

SA_DQ[33]

AK6

SA_DQ[34]

AK7

SA_DQ[35]

AF6

SA_DQ[36]

AG5

SA_DQ[37]

AJ7

SA_DQ[38]

AJ6

SA_DQ[39]

SA_DQ[40]

AJ9

SA_DQ[41]

SA_DQ[42]

SA_DQ[43]

AK8

SA_DQ[44]

AL7

SA_DQ[45]

SA_DQ[46]

AL8

SA_DQ[47]

AN8

SA_DQ[48]

SA_DQ[49]

SA_DQ[50]

SA_DQ[51]

AM9

SA_DQ[52]

AN9

SA_DQ[53]

SA_DQ[54]

SA_DQ[55]

SA_DQ[56]

SA_DQ[57]

SA_DQ[58]

SA_DQ[59]

SA_DQ[60]

SA_DQ[61]

SA_DQ[62]

SA_DQ[63]

AC3

SA_BS[0]

AB2

SA_BS[1]

U7

SA_BS[2]

AE1

SA_CAS#

AB3

SA_RAS#

AE9

SA_WE#

DDR SYSTEM MEMORY A

DDR SYSTEM MEMORY A

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48

M_A_DQ49

M_A_DQ50

M_A_DQ51

M_A_DQ52

M_A_DQ53

M_A_DQ54

M_A_DQ55

M_A_DQ56

M_A_DQ57

M_A_DQ58

M_A_DQ59

M_A_DQ60

M_A_DQ61

M_A_DQ62

M_A_DQ63

M_A_BS0<16>

M_A_BS1<16>

M_A_BS2<16>

M_A_CAS#<16>

M_A_RAS#<16>

M_A_WE#<16>

SA_CK#[0]

SA_CKE[0]

SA_CK[1]

SA_CK#[1]

SA_CKE[1]

SA_CS#[0]

SA_CS#[1]

SA_ODT[0]

SA_ODT[1]

SA_DM[0]

SA_DM[1]

SA_DM[2]

SA_DM[3]

SA_DM[4]

SA_DM[5]

SA_DM[6]

SA_DM[7]

SA_DQS#[0]

SA_DQS#[1]

SA_DQS#[2]

SA_DQS#[3]

SA_DQS#[4]

SA_DQS#[5]

SA_DQS#[6]

SA_DQS#[7]

SA_DQS[0]

SA_DQS[1]

SA_DQS[2]

SA_DQS[3]

SA_DQS[4]

SA_DQS[5]

SA_DQS[6]

SA_DQS[7]

SA_MA[0]

SA_MA[1]

SA_MA[2]

SA_MA[3]

SA_MA[4]

SA_MA[5]

SA_MA[6]

SA_MA[7]

SA_MA[8]

SA_MA[9]

SA_MA[10]

SA_MA[11]

SA_MA[12]

SA_MA[13]

SA_MA[14]

SA_MA[15]

AA7

P7

Y6

Y5

P6

AE2

AE8

AD8

AF9

B9

D7

H7

M7

AG6

AM7

AN10

AN13

C9

F8

J9

N9

AH7

AK9

AP11

AT13

C8

F9

H9

M9

AH8

AK10

AN11

AR13

Y3

W1

AA8

AA3

V1

AA9

V8

T1

Y9

U6

AD4

T2

U3

AG8

T3

V9

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_CLK_DDR0 <16>

M_CLK_DDR#0 <16>

M_CKE0 <16>

M_CLK_DDR1 <16>

M_CLK_DDR#1 <16>

M_CKE1 <16>

M_CS#0 <16>

M_CS#1 <16>

M_ODT0 <16>

M_ODT1 <16>

M_A_DM[7:0] <16>

M_A_DQS#[7:0] <16>

M_A_DQS[7:0] <16>

M_A_A[15:0] <16>

M_B_DQ[63:0]<17>

M_B_DQ0

B5

AR10

AT10

SB_DQ[0]

A5

SB_DQ[1]

C3

SB_DQ[2]

B3

SB_DQ[3]

E4

SB_DQ[4]

A6

SB_DQ[5]

A4

SB_DQ[6]

C4

SB_DQ[7]

D1

SB_DQ[8]

D2

SB_DQ[9]

F2

SB_DQ[10]

F1

SB_DQ[11]

C2

SB_DQ[12]

F5

SB_DQ[13]

F3

SB_DQ[14]

G4

SB_DQ[15]

H6

SB_DQ[16]

G2

SB_DQ[17]

J6

SB_DQ[18]

J3

SB_DQ[19]

G1

SB_DQ[20]

G5

SB_DQ[21]

J2

SB_DQ[22]

J1

SB_DQ[23]

J5

SB_DQ[24]

K2

SB_DQ[25]

L3

SB_DQ[26]

M1

SB_DQ[27]

K5

SB_DQ[28]

K4

SB_DQ[29]

M4

SB_DQ[30]

N5

SB_DQ[31]

AF3

SB_DQ[32]

AG1

SB_DQ[33]

AJ3

SB_DQ[34]

AK1

SB_DQ[35]

AG4

SB_DQ[36]

AG3

SB_DQ[37]

AJ4

SB_DQ[38]

AH4

SB_DQ[39]

AK3

SB_DQ[40]

AK4

SB_DQ[41]

AM6

SB_DQ[42]

AN2

SB_DQ[43]

AK5

SB_DQ[44]

AK2

SB_DQ[45]

AM4

SB_DQ[46]

AM3

SB_DQ[47]

AP3

SB_DQ[48]

AN5

SB_DQ[49]

AT4

SB_DQ[50]

AN6

SB_DQ[51]

AN4

SB_DQ[52]

AN3

SB_DQ[53]

AT5

SB_DQ[54]

AT6

SB_DQ[55]

AN7

SB_DQ[56]

AP6

SB_DQ[57]

AP8

SB_DQ[58]

AT9

SB_DQ[59]

AT7

SB_DQ[60]

AP9

SB_DQ[61]

SB_DQ[62]

SB_DQ[63]

AB1

SB_BS[0]

W5

SB_BS[1]

R7

SB_BS[2]

AC5

SB_CAS#

Y7

SB_RAS#

AC6

SB_WE#

DDR SYSTEM MEMORY - B

DDR SYSTEM MEMORY - B

M_B_DQ1

M_B_DQ2

M_B_DQ3

M_B_DQ4

M_B_DQ5

M_B_DQ6

M_B_DQ7

M_B_DQ8

M_B_DQ9

M_B_DQ10

M_B_DQ11

M_B_DQ12

M_B_DQ13

M_B_DQ14

M_B_DQ15

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ24

M_B_DQ25

M_B_DQ26

M_B_DQ27

M_B_DQ28

M_B_DQ29

M_B_DQ30

M_B_DQ31

M_B_DQ32

M_B_DQ33

M_B_DQ34

M_B_DQ35

M_B_DQ36

M_B_DQ37

M_B_DQ38

M_B_DQ39

M_B_DQ40

M_B_DQ41

M_B_DQ42

M_B_DQ43

M_B_DQ44

M_B_DQ45

M_B_DQ46

M_B_DQ47

M_B_DQ48

M_B_DQ49

M_B_DQ50

M_B_DQ51

M_B_DQ52

M_B_DQ53

M_B_DQ54

M_B_DQ55

M_B_DQ56

M_B_DQ57

M_B_DQ58

M_B_DQ59

M_B_DQ60

M_B_DQ61

M_B_DQ62

M_B_DQ63

M_B_BS0<17>

M_B_BS1<17>

M_B_BS2<17>

M_B_CAS#<17>

M_B_RAS#<17>

M_B_WE#<17>

SB_CK[0]

SB_CK#[0]

SB_CKE[0]

SB_CK[1]

SB_CK#[1]

SB_CKE[1]

SB_CS#[0]

SB_CS#[1]

SB_ODT[0]

SB_ODT[1]

SB_DM[0]

SB_DM[1]

SB_DM[2]

SB_DM[3]

SB_DM[4]

SB_DM[5]

SB_DM[6]

SB_DM[7]

SB_DQS#[0]

SB_DQS#[1]

SB_DQS#[2]

SB_DQS#[3]

SB_DQS#[4]

SB_DQS#[5]

SB_DQS#[6]

SB_DQS#[7]

SB_DQS[0]

SB_DQS[1]

SB_DQS[2]

SB_DQS[3]

SB_DQS[4]

SB_DQS[5]

SB_DQS[6]

SB_DQS[7]

SB_MA[0]

SB_MA[1]

SB_MA[2]

SB_MA[3]

SB_MA[4]

SB_MA[5]

SB_MA[6]

SB_MA[7]

SB_MA[8]

SB_MA[9]

SB_MA[10]

SB_MA[11]

SB_MA[12]

SB_MA[13]

SB_MA[14]

SB_MA[15]

W8

W9

M3

V7

V6

M2

AB8

AD6

AC7

AD1

M_B_DM0

D4

M_B_DM1

E1

M_B_DM2

H3

M_B_DM3

K1

M_B_DM4

AH1

M_B_DM5

AL2

M_B_DM6

AR4

M_B_DM7

AT8

M_B_DQS#0

D5

M_B_DQS#1

F4

M_B_DQS#2

J4

M_B_DQS#3

L4

M_B_DQS#4

AH2

M_B_DQS#5

AL4

M_B_DQS#6

AR5

M_B_DQS#7

AR8

M_B_DQS0

C5

M_B_DQS1

E3

M_B_DQS2

H4

M_B_DQS3

M5

M_B_DQS4

AG2

M_B_DQS5

AL5

M_B_DQS6

AP5

M_B_DQS7

AR7

M_B_A0

U5

M_B_A1

V2

M_B_A2

T5

M_B_A3

V3

M_B_A4

R1

M_B_A5

T8

M_B_A6

R2

M_B_A7

R6

M_B_A8

R4

M_B_A9

R5

M_B_A10

AB5

M_B_A11

P3

M_B_A12

R3

M_B_A13

AF7

M_B_A14

P5

M_B_A15

N1

M_CLK_DDR2 <17>

M_CLK_DDR#2 <17>

M_CKE2 <17>

M_CLK_DDR3 <17>

M_CLK_DDR#3 <17>

M_CKE3 <17>

M_CS#2 <17>

M_CS#3 <17>

M_ODT2 <17>

M_ODT3 <17>

M_B_DM[7:0] <17>

M_B_DQS#[7:0] <17>

M_B_DQS[7:0] <17>

M_B_A[15:0] <17>

SOCKET989

SOCKET989

SOCKET989

SOCKET989

A A

Title :

Title :

Title :

CPU(2)_DDR3

CPU(2)_DDR3

CPU(2)_DDR3

Kuansheng Yang

Kuansheng Yang

Engineer:

Engineer:

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

1

Kuansheng Yang

4 99Monday, May 10, 2010

4 99Monday, May 10, 2010

4 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Page 5

5

4

3

2

1

D D

CFG0

1

CFG1

1

CFG2

1

CFG3

1

CFG4

1

CFG5

1

CFG6

1

CFG7

1

CFG8

1

CFG9

1

CFG10

1

CFG11

1

CFG12

1

CFG13

1

CFG14

1

CFG15

1

CFG16

1

CFG17

1

CFG18

1

SP0501 R0402SP0501 R0402

SP0502 R0402SP0502 R0402

T0513T0513

T0510T0510

T0511T0511

T0512T0512

T0514T0514

T0515T0515

10mil trace

10mil trace

H_RSVD17_R

12

H_RSVD18_R

12

1

1

1

1

1

1

DIMM0_VREF_DQ<18>

DIMM1_VREF_DQ<18>

T0578T0578

T0567T0567

T0566T0566

T0565T0565

T0569T0569

T0568T0568

T0571T0571

T0572T0572

T0574T0574

T0570T0570

C C

B B

T0575T0575

T0573T0573

T0576T0576

T0577T0577

T0592T0592

T0581T0581

T0580T0580

T0579T0579

T0583T0583

AP25

AL25

AL24

AL22

AJ33

AM30

AM28

AP31

AL32

AL30

AM31

AN29

AM32

AK32

AK31

AK28

AJ28

AN30

AN32

AJ32

AJ29

AJ30

AK30

AG9

M27

L28

J17

H17

G25

G17

E31

E30

H16

B19

A19

A20

B20

U9

T9

AC9

AB9

C1

A3

J29

J28

A34

A33

C35

B35

U0301E

U0301E

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

CFG[0]

CFG[1]

CFG[2]

CFG[3]

CFG[4]

CFG[5]

CFG[6]

CFG[7]

CFG[8]

CFG[9]

CFG[10]

CFG[11]

CFG[12]

CFG[13]

CFG[14]

CFG[15]

CFG[16]

CFG[17]

RSVD_TP_86

RSVD15

RSVD16

RSVD17

RSVD18

RSVD19

RSVD20

RSVD21

RSVD22

RSVD_NCTF_23

RSVD_NCTF_24

RSVD26

RSVD27

RSVD_NCTF_28

RSVD_NCTF_29

RSVD_NCTF_30

RSVD_NCTF_31

SOCKET989

SOCKET989

RSVD_NCTF_37

RSVD_NCTF_40

RSVD_NCTF_41

RSVD_NCTF_42

RSVD_NCTF_43

RSVD_NCTF_54

RSVD_NCTF_55

RSVD_NCTF_56

RSVD_NCTF_57

RSVD_TP_59

RSVD_TP_60

RESERVED

RESERVED

RSVD_TP_66

RSVD_TP_67

RSVD_TP_68

RSVD_TP_69

RSVD_TP_70

RSVD_TP_71

RSVD_TP_72

RSVD_TP_73

RSVD_TP_74

RSVD_TP_75

RSVD_TP_76

RSVD_TP_77

RSVD_TP_78

RSVD_TP_79

RSVD_TP_80

RSVD_TP_81

RSVD_TP_82

RSVD_TP_83

RSVD_TP_84

RSVD_TP_85

RSVD32

RSVD33

RSVD34

RSVD35

RSVD36

RSVD38

RSVD39

RSVD45

RSVD46

RSVD47

RSVD48

RSVD49

RSVD50

RSVD51

RSVD52

RSVD53

RSVD58

RSVD62

RSVD63

RSVD64

RSVD65

U0301H

AJ13

AJ12

AH25

AK26

AL26

T0504T0504

AR2

1

AJ26

AJ27

T0501T0501

AP1

1

T0506T0506

AT2

1

T0507T0507

AT3

1

T0503T0503

AR1

1

AL28

AL29

AP30

AP32

AL27

AT31

AT32

AP33

AR33

T0508T0508

1

AT33

T0509T0509

AT34

1

T0502T0502

AP35

1

T0505T0505

AR35

1

AR32

E15

F15

A2

KEY

D15

C15

AJ15

AH15

AA5

AA4

R8

AD3

AD2

AA2

AA1

R9

AG7

AE3

V4

V5

N2

AD5

AD7

W3

W2

N3

AE5

AD9

AP34

VSS

RSVD64_R

RSVD65_R

SP0503 R0402SP0503 R0402

SP0504 R0402SP0504 R0402

12

12

AT20

AT17

AR31

AR28

AR26

AR24

AR23

AR20

AR17

AR15

AR12

AP20

AP17

AP13

AP10

AN34

AN31

AN23

AN20

AN17

AM29

AM27

AM25

AM20

AM17

AM14

AM11

AL34

AL31

AL23

AL20

AL17

AL12

AK29

AK27

AK25

AK20

AK17

AJ31

AJ23

AJ20

AJ17

AJ14

AJ11

AH35

AH34

AH33

AH32

AH31

AH30

AH29

AH28

AH27

AH26

AH20

AH17

AH13

AG10

AE35

AR9

AR6

AR3

AP7

AP4

AP2

AM8

AM5

AM2

AL9

AL6

AL3

AJ8

AJ5

AJ2

AH9

AH6

AH3

AF8

AF4

AF2

U0301H

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VSS53

VSS54

VSS55

VSS56

VSS57

VSS58

VSS59

VSS60

VSS61

VSS62

VSS63

VSS64

VSS65

VSS66

VSS67

VSS68

VSS69

VSS70

VSS71

VSS72

VSS73

VSS74

VSS75

VSS76

VSS77

VSS78

VSS79

VSS80

SOCKET989

SOCKET989

VSS

VSS

VSS81

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

AE34

AE33

AE32

AE31

AE30

AE29

AE28

AE27

AE26

AE6

AD10

AC8

AC4

AC2

AB35

AB34

AB33

AB32

AB31

AB30

AB29

AB28

AB27

AB26

AB6

AA10

Y8

Y4

Y2

W35

W34

W33

W32

W31

W30

W29

W28

W27

W26

W6

V10

U8

U4

U2

T35

T34

T33

T32

T31

T30

T29

T28

T27

T26

T6

R10

P8

P4

P2

N35

N34

N33

N32

N31

N30

N29

N28

N27

N26

N6

M10

L35

L32

L29

L8

L5

L2

K34

K33

K30

K27

K9

K6

K3

J32

J30

J21

J19

H35

H32

H28

H26

H24

H22

H18

H15

H13

H11

H8

H5

H2

G34

G31

G20

G9

G6

G3

F30

F27

F25

F22

F19

F16

E35

E32

E29

E24

E21

E18

E13

E11

E8

E5

E2

D33

D30

D26

D9

D6

D3

C34

C32

C29

C28

C24

C22

C20

C19

C16

B31

B25

B21

B18

B17

B13

B11

B8

B6

B4

A29

A27

A23

A9

U0301I

U0301I

VSS161

VSS162

VSS163

VSS164

VSS165

VSS166

VSS167

VSS168

VSS169

VSS170

VSS171

VSS172

VSS173

VSS174

VSS175

VSS176

VSS177

VSS178

VSS179

VSS180

VSS181

VSS182

VSS183

VSS184

VSS185

VSS186

VSS187

VSS188

VSS189

VSS190

VSS191

VSS192

VSS193

VSS194

VSS195

VSS196

VSS197

VSS198

VSS199

VSS200

VSS201

VSS202

VSS203

VSS204

VSS205

VSS206

VSS207

VSS208

VSS209

VSS210

VSS211

VSS212

VSS213

VSS214

VSS215

VSS216

VSS217

VSS218

VSS219

VSS220

VSS221

VSS222

VSS223

VSS224

VSS225

VSS226

VSS227

VSS228

VSS229

VSS230

VSS231

VSS232

VSS233

SOCKET989

SOCKET989

VSS

VSS

NCTF

NCTF

VSS_NCTF1

VSS_NCTF2

VSS_NCTF3

VSS_NCTF4

VSS_NCTF5

VSS_NCTF6

VSS_NCTF7

TP_MCP_VSS_NCTF1

AT35

TP_MCP_VSS_NCTF2

AT1

AR34

B34

B2

TP_MCP_VSS_NCTF6

B1

TP_MCP_VSS_NCTF7

A35

T0564T0564

1

T0561T0561

1

T0563T0563

1

T0562T0562

1

CFG strapping information:

CFG[1:0]: PCI Express Port Bifurcation:(Clarksfield Only)

- 11 = 1 x 16 PEG (Default)

- 10 = 2 x 8 PEG

CFG[3]: PCIE Static Numbering Lane Reversal.(Auburndale Only)

- 1:Normal Operation (Default)

- 0:Lane Numbers Reversed 15 -> 0, 14 -> 1, ...

CFG[4]: Embedded DisplayPort Detection.(Auburndale Only)

- 1:Disabled - No Physical Display Port attached to Embedded DisplayPort

- 0:Enabled - An external Display Port device is connected to the Embedded Display Port

CFG[7]: Fixed for PCI Express 2.0 jitter specifications.(Clarksfi eld)

Clarksfield (only for early samples pre-ES1) - Connect to GND with 3.01K Ohm /5% resistor

For a common motherboard design (for AUB and CFD),

A A

the pull-down resistor should be used. Does not impact AUB functionality.

Unmount if Intel has fixed this issue.

Note: (Auburndale)Hardware Straps are sampled on

the asserting edge of VCCPWRGOOD_0 and

VCCPWRGOOD_1 and latched inside the processor.

Note: (Clarksfield)Hardware Straps are sampled

after RSTIN# de-assertion.

5

4

CFG0

CFG3

CFG4

CFG7

R0535 3.01KOHM@R0535 3.01KOHM@

R0536 3.01KOHM@R0536 3.01KOHM@

R0537 3.01KOHM@R0537 3.01KOHM@

R0538 3.01KOHM@R0538 3.01KOHM@

12

12

12

12

Title :

Title :

Title :

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

CPU(3)_CFG,RSVD,GND

Kuansheng Yang

Kuansheng Yang

Engineer:

Engineer:

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Engineer:

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

1

Kuansheng Yang

5 99Monday, May 10, 2010

5 99Monday, May 10, 2010

5 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Page 6

5

4

3

2

1

U0301F

U0301F

+VCORE

AG35

VCC1

AG34

VCC2

AG33

VCC3

AG32

VCC4

AG31

VCC5

D D

C C

B B

AG30

AG29

AG28

AG27

AG26

AF35

AF34

AF33

AF32

AF31

AF30

AF29

AF28

AF27

AF26

AD35

AD34

AD33

AD32

AD31

AD30

AD29

AD28

AD27

AD26

AC35

AC34

AC33

AC32

AC31

AC30

AC29

AC28

AC27

AC26

AA35

AA34

AA33

AA32

AA31

AA30

AA29

AA28

AA27

AA26

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

Y35

VCC51

Y34

VCC52

Y33

VCC53

Y32

VCC54

Y31

VCC55

Y30

VCC56

Y29

VCC57

Y28

VCC58

Y27

VCC59

Y26

VCC60

V35

VCC61

V34

VCC62

V33

VCC63

V32

VCC64

V31

VCC65

V30

VCC66

V29

VCC67

V28

VCC68

V27

VCC69

V26

VCC70

U35

VCC71

U34

VCC72

U33

VCC73

U32

VCC74

U31

VCC75

U30

VCC76

U29

VCC77

U28

VCC78

U27

VCC79

U26

VCC80

R35

VCC81

R34

VCC82

R33

VCC83

R32

VCC84

R31

VCC85

R30

VCC86

R29

VCC87

R28

VCC88

R27

VCC89

R26

VCC90

P35

VCC91

P34

VCC92

P33

VCC93

P32

VCC94

P31

VCC95

P30

VCC96

P29

VCC97

P28

VCC98

P27

VCC99

P26

VCC100

1.1V RAIL POWER

1.1V RAIL POWER

CPU CORE SUPPLY

CPU CORE SUPPLY

POWER

POWER

PROC_DPRSLPVR

CPU VIDS

CPU VIDS

VSS_SENSE_VTT

SENSE LINES

SENSE LINES

VTT0_1

VTT0_2

VTT0_3

VTT0_4

VTT0_5

VTT0_6

VTT0_7

VTT0_8

VTT0_9

VTT0_10

VTT0_11

VTT0_12

VTT0_13

VTT0_14

VTT0_15

VTT0_16

VTT0_17

VTT0_18

VTT0_19

VTT0_20

VTT0_21

VTT0_22

VTT0_23

VTT0_24

VTT0_25

VTT0_26

VTT0_27

VTT0_28

VTT0_29

VTT0_30

VTT0_31

VTT0_32

VTT0_33

VTT0_34

VTT0_35

VTT0_36

VTT0_37

VTT0_38

VTT0_39

VTT0_40

VTT0_41

VTT0_42

VTT0_43

VTT0_44

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VTT_SELECT

ISENSE

VCC_SENSE

VSS_SENSE

VTT_SENSE

PSI#

AH14

AH12

AH11

AH10

J14

J13

H14

H12

G14

G13

G12

G11

F14

F13

F12

F11

E14

E12

D14

D13

D12

D11

C14

C13

C12

C11

B14

B12

A14

A13

A12

A11

AF10

AE10

AC10

AB10

Y10

W10

U10

T10

J12

J11

J16

J15

AN33

CPU_VID0

AK35

CPU_VID1

AK33

CPU_VID2

AK34

CPU_VID3

AL35

CPU_VID4

AL33

CPU_VID5

AM33

CPU_VID6

AM35

PM_DPRSLPVR_R

AM34

G15

VTT_TEST TBD

AN35

AJ34

AJ35

B15

A15

I_MON <80>

VCCSENSE

VSSSENSE

VTT_SENSE

TP_VSS_SENSE_VTT

C060410UF/6.3V C060410UF/6.3V

C060110UF/6.3V C060110UF/6.3V

C060210UF/6.3V C060210UF/6.3V

12

12

12

C068710UF/6.3V@C068710UF/6.3V

12

@

12

C061722UF/6.3V C061722UF/6.3V

Intel use 22u

SP0601 R0402SP0601 R0402

SP0602 R0402SP0602 R0402

T0632T0632

1

T0631T0631

1

C060610UF/6.3V C060610UF/6.3V

12

+VTT_CPU

C068810UF/6.3V@C068810UF/6.3V

12

@

12

C061822UF/6.3V C061822UF/6.3V

+VCORE

C060810UF/6.3V C060810UF/6.3V

12

C068910UF/6.3V@C068910UF/6.3V

12

@

12

12

1 2

12

C061110UF/6.3V@C061110UF/6.3V

12

@

R0602

R0602

100Ohm

100Ohm

1%

1%

R0603

R0603

100Ohm

100Ohm

1%

1%

C061510UF/6.3V@C061510UF/6.3V

C061310UF/6.3V@C061310UF/6.3V

12

12

@

@

+VTT_CPU

VCCSENSE <80>

VSSSENSE <80>

+VTT_CPU

C061610UF/6.3V@C061610UF/6.3V

12

@

C0690

C0690

C0691

C0691

12

12

@

@

@

@

1500PF/50V

1500PF/50V

1500PF/50V

1500PF/50V

reserve for emi

R1.4--5

PM_PSI# <80>

CPU_VID[0:6] <19>

PM_DPRSLPVR <80>

+VGFX_CORE

C0693

C0693

C0695

C0692

C0692

C0695

C0694

C0694

C0696

C0696

12

12

12

@

@

@

@

1500PF/50V

1500PF/50V

1500PF/50V

1500PF/50V

1500PF/50V

1500PF/50V

12

12

12

+

+

@

@

@

@

@

@

CE0601

CE0601

330UF/2.5V

330UF/2.5V

1500PF/50V

1500PF/50V

1500PF/50V

1500PF/50V

CE0601

CE0601

12

12

C065022UF/6.3V@C065022UF/6.3V

@

12

12

12

C064922UF/6.3V C 064922UF/6.3V

C061910UF/6.3V C 061910UF/6.3V

C065122UF/6.3V@C065122UF/6.3V

C064822UF/6.3V C 064822UF/6.3V

@

DG R0.8,P368

+VTT_CPU

12

12

C065422UF/6.3V C 065422UF/6.3V

C065522UF/6.3V@C065522UF/6.3V

@

+VTT_CPU

+VCORE

Intel use 22u

12

12

12

12

C065922UF/6.3V@C065922UF/6.3V

C065722UF/6.3V C 065722UF/6.3V

C065622UF/6.3V C 065622UF/6.3V

C065822UF/6.3V@C065822UF/6.3V

@

@

Intel use 22u

Decoupling guide from Intel

VCORE 22uF * 16pcs

10uF * 16pcs

470uF * 6pcs (2 no stuff)

12

12

C0632

C0632

C0633

C0633

22UF/6.3V

22UF/6.3V

10UF/6.3V

10UF/6.3V

+VTT_CPU

+VCORE

+1.8VS

+VGFX_CORE

U0301G

U0301G

AT21

AT19

AT18

AT16

12

C062010UF/6.3V C 062010UF/6.3V

AR21

AR19

AR18

AR16

AP21

AP19

AP18

AP16

AN21

AN19

AN18

AN16

AM21

AM19

AM18

AM16

AL21

AL19

AL18

AL16

AK21

AK19

AK18

AK16

AJ21

AJ19

AJ18

AJ16

AH21

AH19

AH18

AH16

J24

J23

H25

K26

J27

J26

J25

H27

G28

G27

G26

F26

E26

E25

SOCKET989

SOCKET989

12

C0634

C0634

22UF/6.3V

22UF/6.3V

+1.5V

VAXG1

VAXG2

VAXG3

VAXG4

VAXG5

VAXG6

VAXG7

VAXG8

VAXG9

VAXG10

VAXG11

VAXG12

VAXG13

VAXG14

VAXG15

VAXG16

VAXG17

VAXG18

VAXG19

VAXG20

VAXG21

VAXG22

VAXG23

VAXG24

VAXG25

VAXG26

VAXG27

VAXG28

VAXG29

VAXG30

VAXG31

VAXG32

VAXG33

VAXG34

VAXG35

VAXG36

VTT1_45

VTT1_46

VTT1_47

VTT1_48

VTT1_49

VTT1_50

VTT1_51

VTT1_52

VTT1_53

VTT1_54

VTT1_55

VTT1_56

VTT1_57

VTT1_58

12

C0635

C0635

10UF/6.3V

10UF/6.3V

+VTT_CPU <3,25,26,32,57,82>

+1.5V <3,16,57,83>

+VCORE <57,80>

+1.8VS <26,57,85>

+VGFX_CORE <57,86,91>

VSSAXG_SENSE

SENSE

LINES

SENSE

LINES

GRAPHICS

GRAPHICS

GFX_DPRSLPVR

GRAPHICS VIDs

GRAPHICS VIDs

FDI PEG & DMI

FDI PEG & DMI

12

C0636

C0636

22UF/6.3V

22UF/6.3V

DDR3 - 1.5V RAILS

DDR3 - 1.5V RAILS

POWER

POWER

1.1V1.8V

1.1V1.8V

12

C0637

C0637

22UF/6.3V

22UF/6.3V

VAXG_SENSE

GFX_VID[0]

GFX_VID[1]

GFX_VID[2]

GFX_VID[3]

GFX_VID[4]

GFX_VID[5]

GFX_VID[6]

GFX_VR_EN

GFX_IMON

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

VDDQ9

VDDQ10

VDDQ11

VDDQ12

VDDQ13

VDDQ14

VDDQ15

VDDQ16

VDDQ17

VDDQ18

VTT0_59

VTT0_60

VTT0_61

VTT0_62

VTT1_63

VTT1_64

VTT1_65

VTT1_66

VTT1_67

VTT1_68

VCCPLL1

VCCPLL2

VCCPLL3

12

C0638

C0638

22UF/6.3V

22UF/6.3V

AR22

AT22

GVR_VID0

AM22

GVR_VID1

AP22

GVR_VID2

AN22

GVR_VID3

AP23

GVR_VID4

AM23

GVR_VID5

AP24

GVR_VID6

AN24

GFX_VRON_EN

AR25

GFXVR_DPRSLPVR_R

AT25

AM24

AJ1

AF1

AE7

AE4

AC1

AB7

AB4

Y1

W7

W4

U1

T7

T4

P1

N7

N4

L1

H1

P10

N10

L10

K10

J22

J20

J18

H21

H20

H19

L26

L27

M26

12

C0639

C0639

22UF/6.3V

22UF/6.3V

VCC_AXG_SENSE < 86>

VSS_AXG_SENSE <86>

GVR_VID[0:6] <86>

R0618 10KOhmR0618 10KOhm

1 2

R0605 4.7KOhm@R0605 4.7KOhm@

1 2

SP0603 R0402SP0603 R0402

SP0604 R0402SP0604 R0402

GVR_PWR_MON <86>

C06211UF/10V C06211UF/10V

C06221UF/10V C06221UF/10V

12

12

12

12

C0627

C0627

C0626

C0626

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

@

@

12

12

C0664

C0664

C0665

C0665

22UF/6.3V

22UF/6.3V

22UF/6.3V

22UF/6.3V

@

@

Intel use 22u

12

12

12

12

C06291UF/10V@C06291UF/10V

C06672.2UF/10V C 06672.2UF/10V

C06281UF/10V C06281UF/10V

@

@

+VTT_CPU

R1.2--11

12

follow EC Team suggestion 09-14

kurt

12

R0606 4.7KOhmR0606 4.7KOhm

C06241UF/10V@C06241UF/10V

C06231UF/10V C06231UF/10V

12

12

C06684.7UF/6.3V@C06684.7UF/6.3V

C068522UF/6.3V@C068522UF/6.3V

C06251UF/10V@C06251UF/10V

12

12

12

@

@

@

DG R0.8,P367

1xbuck Stuffing option

+VTT_CPU

+VTT_CPU

+1.8VS

Intel 1.8V CAP.

C066622UF/6.3V C 066622UF/6.3V

1u: 2/2

2.2u: 1/1

4.7u: 1/1

330u:1/1

GFX_VR_ON <30,91>

1 2

+1.5V

12

C068622UF/6.3V C068622UF/6.3V

+

12

CE0604330UF/2V+CE0604330UF/2V

GFXVR_DPRSLPVR <86>

12

C0641

C0641

22UF/6.3V

22UF/6.3V

12

C0670

C0670

22UF/6.3V

22UF/6.3V

12

C0678

C0678

22UF/6.3V

22UF/6.3V

3

12

C0642

C0642

22UF/6.3V

22UF/6.3V

@

@

12

C0671

C0671

10UF/6.3V

10UF/6.3V

12

C0679

C0679

22UF/6.3V

22UF/6.3V

12

12

C0643

C0643

22UF/6.3V

22UF/6.3V

C0672

C0672

22UF/6.3V

22UF/6.3V

C0680

C0680

10UF/6.3V

10UF/6.3V

12

12

12

C0644

C0644

10UF/6.3V

10UF/6.3V

C0673

C0673

22UF/6.3V

22UF/6.3V

C0681

C0681

22UF/6.3V

22UF/6.3V

12

C0640

12

12

C0640

22UF/6.3V

22UF/6.3V

C0669

C0669

22UF/6.3V

22UF/6.3V

C0677

C0677

10UF/6.3V

10UF/6.3V

@

@

SOCKET989

SOCKET989

A A

5

4

12

12

12

12

C0645

C0645

22UF/6.3V

22UF/6.3V

C0674

C0674

22UF/6.3V

22UF/6.3V

C0682

C0682

10UF/6.3V

10UF/6.3V

12

12

12

C0647

C0647

10UF/6.3V

10UF/6.3V

C0675

C0675

22UF/6.3V

22UF/6.3V

C0683

C0683

22UF/6.3V

22UF/6.3V

12

C0676

C0676

22UF/6.3V

22UF/6.3V

12

C0684

C0684

10UF/6.3V

10UF/6.3V

@

@

2

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

C

C

C

H36Y_U30X10

H36Y_U30X10

Date: Sheet of

Date: Sheet of

Date: Sheet of

H36Y_U30X10

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

1

CPU(4)_PWR

CPU(4)_PWR

CPU(4)_PWR

Kuansheng Yang

Kuansheng Yang

Kuansheng Yang

6 99Monday, May 10, 2010

6 99Monday, May 10, 2010

6 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Page 7

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

CPU(5)_XDP

CPU(5)_XDP

CPU(5)_XDP

Kuansheng Yang

Kuansheng Yang

Engineer:

Engineer:

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Engineer:

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

1

Kuansheng Yang

7 99Monday, May 10, 2010

7 99Monday, May 10, 2010

7 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Page 8

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

NB(1)_****

NB(1)_****

NB(1)_****

Kuansheng Yang

Kuansheng Yang

1

Kuansheng Yang

8 99Monday, May 10, 2010

8 99Monday, May 10, 2010

8 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Engineer:

Engineer:

BG1\HW 1

BG1\HW 1

BG1\HW 1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

Engineer:

Page 9

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

NB(2)_****

NB(2)_****

NB(2)_****

Kuansheng Yang

Kuansheng Yang

1

Kuansheng Yang

9 99Monday, May 10, 2010

9 99Monday, May 10, 2010

9 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Engineer:

Engineer:

BG1\HW 1

BG1\HW 1

BG1\HW 1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

Engineer:

Page 10

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

NB(3)_****

NB(3)_****

NB(3)_****

Kuansheng Yang

Kuansheng Yang

1

Kuansheng Yang

10 99Monday, May 10, 2010

10 99Monday, May 10, 2010

10 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Engineer:

Engineer:

BG1\HW 1

BG1\HW 1

BG1\HW 1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

Engineer:

Page 11

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

NB(4)_****

NB(4)_****

NB(4)_****

Kuansheng Yang

Kuansheng Yang

1

Kuansheng Yang

11 99Monday, May 10, 2010

11 99Monday, May 10, 2010

11 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Engineer:

Engineer:

BG1\HW 1

BG1\HW 1

BG1\HW 1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

Engineer:

Page 12

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

NB(5)_****

NB(5)_****

NB(5)_****

Kuansheng Yang

Kuansheng Yang

1

Kuansheng Yang

12 99Monday, May 10, 2010

12 99Monday, May 10, 2010

12 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Engineer:

Engineer:

BG1\HW 1

BG1\HW 1

BG1\HW 1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

Engineer:

Page 13

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

NB(6)_****

NB(6)_****

NB(6)_****

Kuansheng Yang

Kuansheng Yang

1

Kuansheng Yang

13 99Monday, May 10, 2010

13 99Monday, May 10, 2010

13 99Monday, May 10, 2010

Rev

Rev

Rev

1.0

1.0

1.0

Engineer:

Engineer:

BG1\HW 1

BG1\HW 1

BG1\HW 1

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

Engineer:

Page 14

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

Engineer:

Engineer:

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

2

Engineer:

NB(7)_****

NB(7)_****

NB(7)_****

Kuansheng Yang

Kuansheng Yang

Kuansheng Yang

14 99Monday, May 10, 2010

14 99Monday, May 10, 2010

14 99Monday, May 10, 2010

1

Rev

Rev

Rev

1.0

1.0

1.0

Page 15

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

Engineer:

Engineer:

BG1\HW1

BG1\HW1

BG1\HW1

Size Project Name

Size Project Name

Size Project Name

A

A

A

Date: Sheet of

Date: Sheet of

5

4

3

Date: Sheet of

H36Y_U30X10

H36Y_U30X10

H36Y_U30X10

2

Engineer:

NB(8)_****

NB(8)_****

NB(8)_****

Kuansheng Yang

Kuansheng Yang

Kuansheng Yang

15 99Monday, May 10, 2010

15 99Monday, May 10, 2010

15 99Monday, May 10, 2010

1

Rev

Rev

Rev

1.0

1.0

1.0

Page 16

5

D D

M_A_A[15:0]<4>

M_CLK_DDR0

M_CLK_DDR#0

M_CLK_DDR1

M_CLK_DDR#1

C C

PLACE CLOSE TO SODIMM

SMBus Slave Address: A0H

B B

12

12

C1621

C1621

10PF/50V

10PF/50V

@

@

C1626

C1626

10PF/50V

10PF/50V

@

@

12

1%

1%

R1603

R1603

150Ohm

150Ohm

12

R1604

R1604

150Ohm

150Ohm

M_A_DQS[7:0]<4>

M_A_DQS#[7:0]<4>

@

@

1%

1%

@

@

M_A_DM[7:0]<4>

M_CLK_DDR1<4>

M_CLK_DDR#1<4>

M_CLK_DDR0<4>

M_CLK_DDR#0<4>

M_A_WE#<4>

M_A_RAS#< 4>

M_A_CAS#< 4>

M_A_BS2<4>

M_A_BS1<4>

M_A_BS0<4>

RN1601A

RN1601A

RN1601B

RN1601B

JP1601

JP1601

3MM_OPEN_5MIL

3MM_OPEN_5MIL

2

112

M_CS#1<4>

M_CS#0<4>

M_ODT1<4>

M_ODT0<4>

M_CKE1<4>

M_CKE0<4>

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

12

10KOHM

10KOHM

34

10KOHM

10KOHM

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

SMB_CLK_S<17,28,29,44,53> M_DRAMRST# <3,17>

SMB_DAT_S<17,28,29,44,53>

+1.5V_DDR3+1.5V

+1.5V_DDR3

12

J1601A

J1601A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM_204P

DDR3_DIMM_204P

1202-002O000

1202-002O000

H:9.2mm

+

+

CE1603

@

CE1603

@

220UF/4V

220UF/4V

ESR=40mOhm/Ir=1.9A

ESR=40mOhm/Ir=1.9A

4

M_A_DQ[63:0] <4>

0

1

2

3

4

5

6

7

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

RESET#

M_A_DQ5

5

DQ0

M_A_DQ1

7

DQ1

M_A_DQ7

15

DQ2

M_A_DQ6

17

DQ3

M_A_DQ0

4

DQ4

M_A_DQ4

6

DQ5

M_A_DQ3

16

DQ6

M_A_DQ2

18

DQ7

M_A_DQ12

21

DQ8

M_A_DQ8

23

DQ9

M_A_DQ10

33

M_A_DQ15

35

M_A_DQ13

22

M_A_DQ9

24

M_A_DQ14

34

M_A_DQ11

36

M_A_DQ16

39

M_A_DQ17

41

M_A_DQ18

51

M_A_DQ22

53

M_A_DQ21

40

M_A_DQ20

42

M_A_DQ23

50

M_A_DQ19

52

M_A_DQ24

57