Page 1

5

4

3

2

1

Power

VCORE

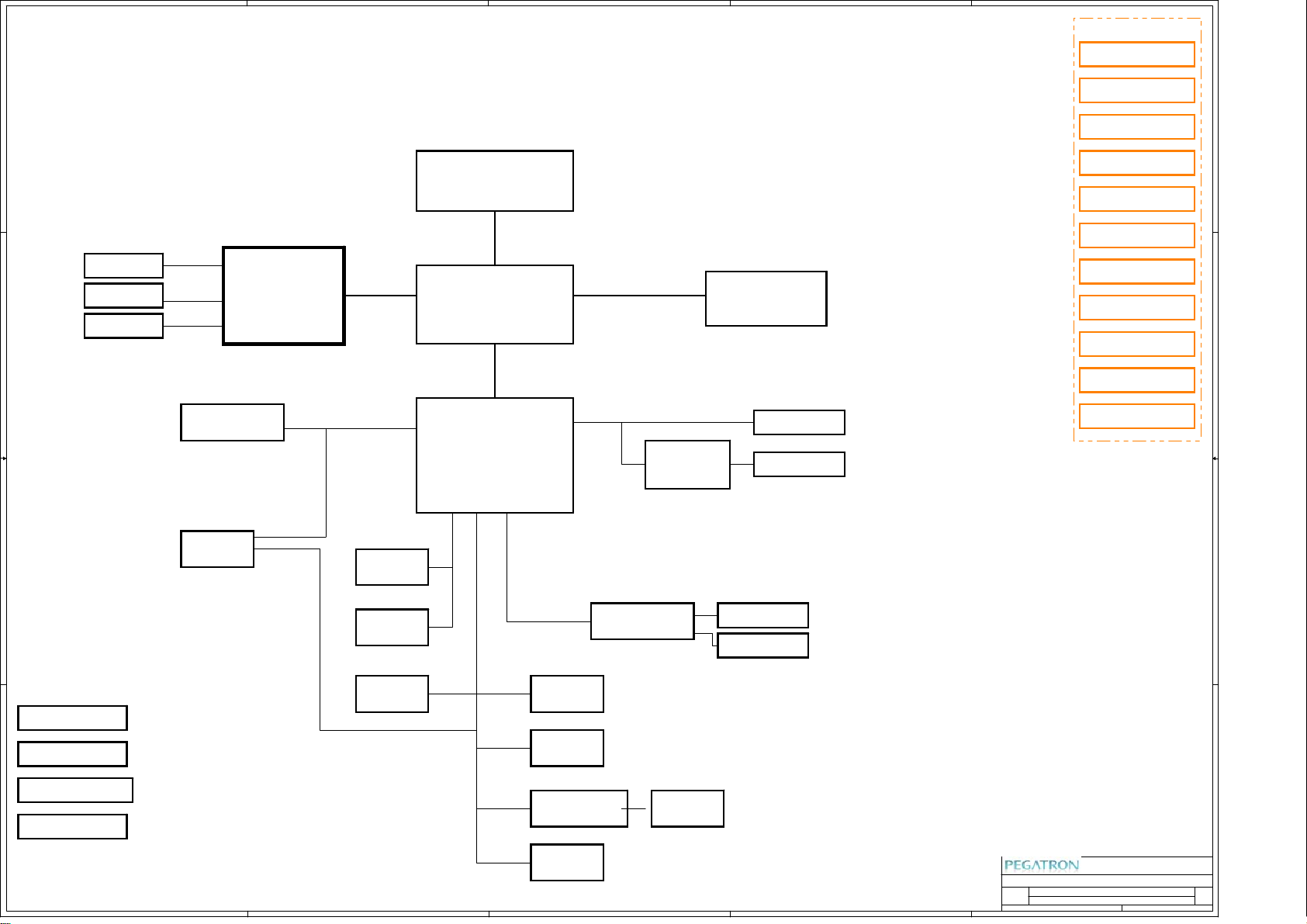

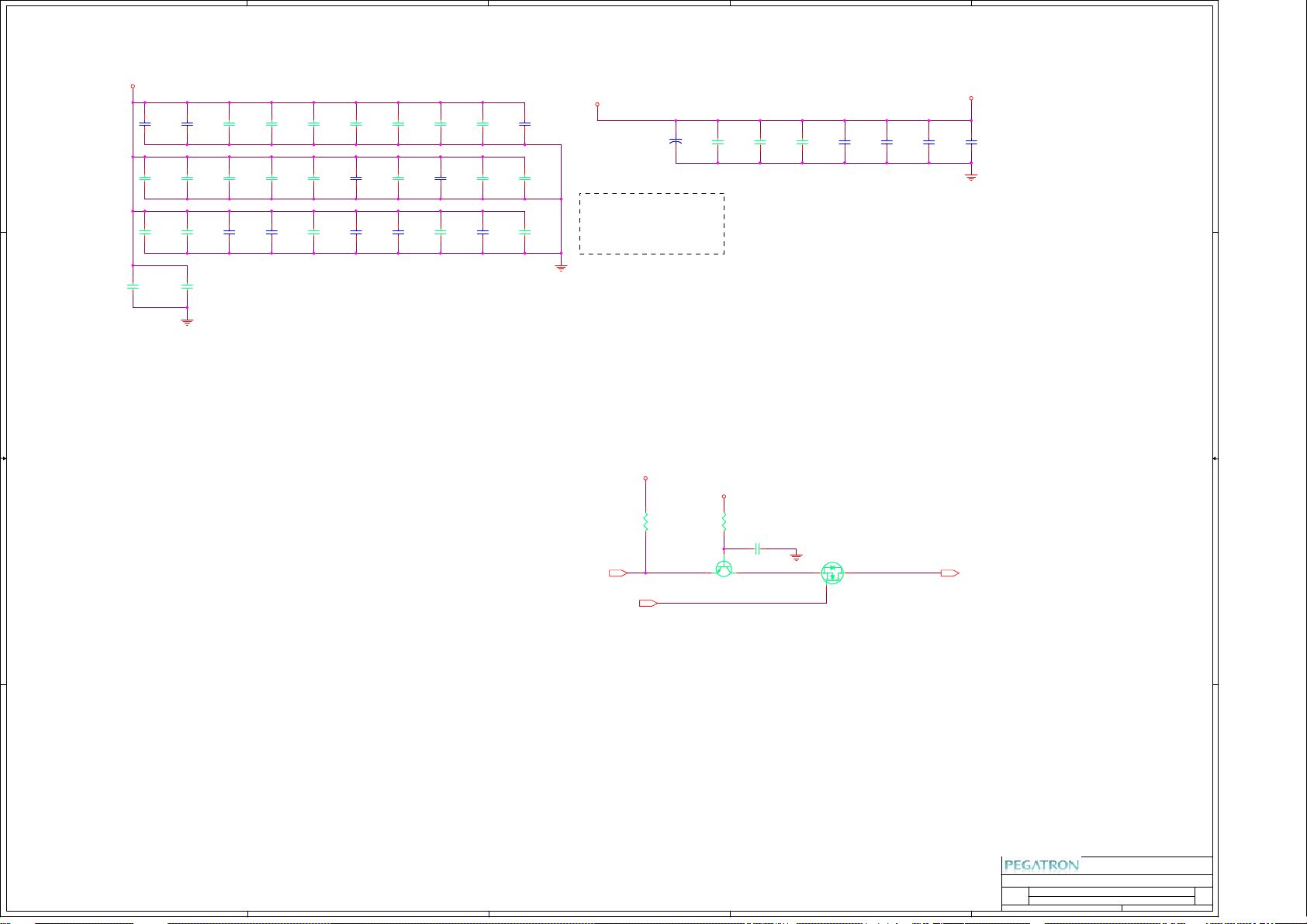

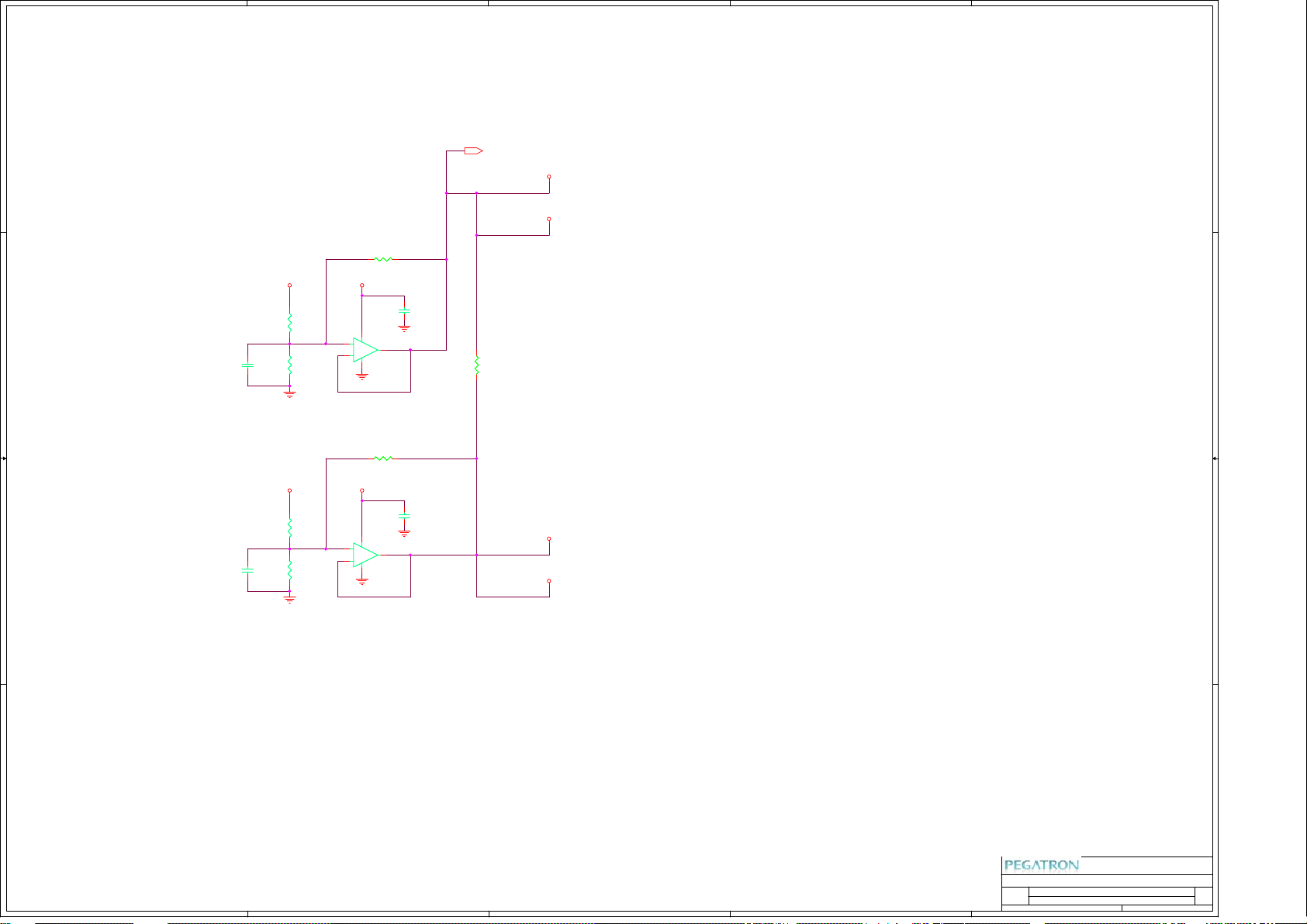

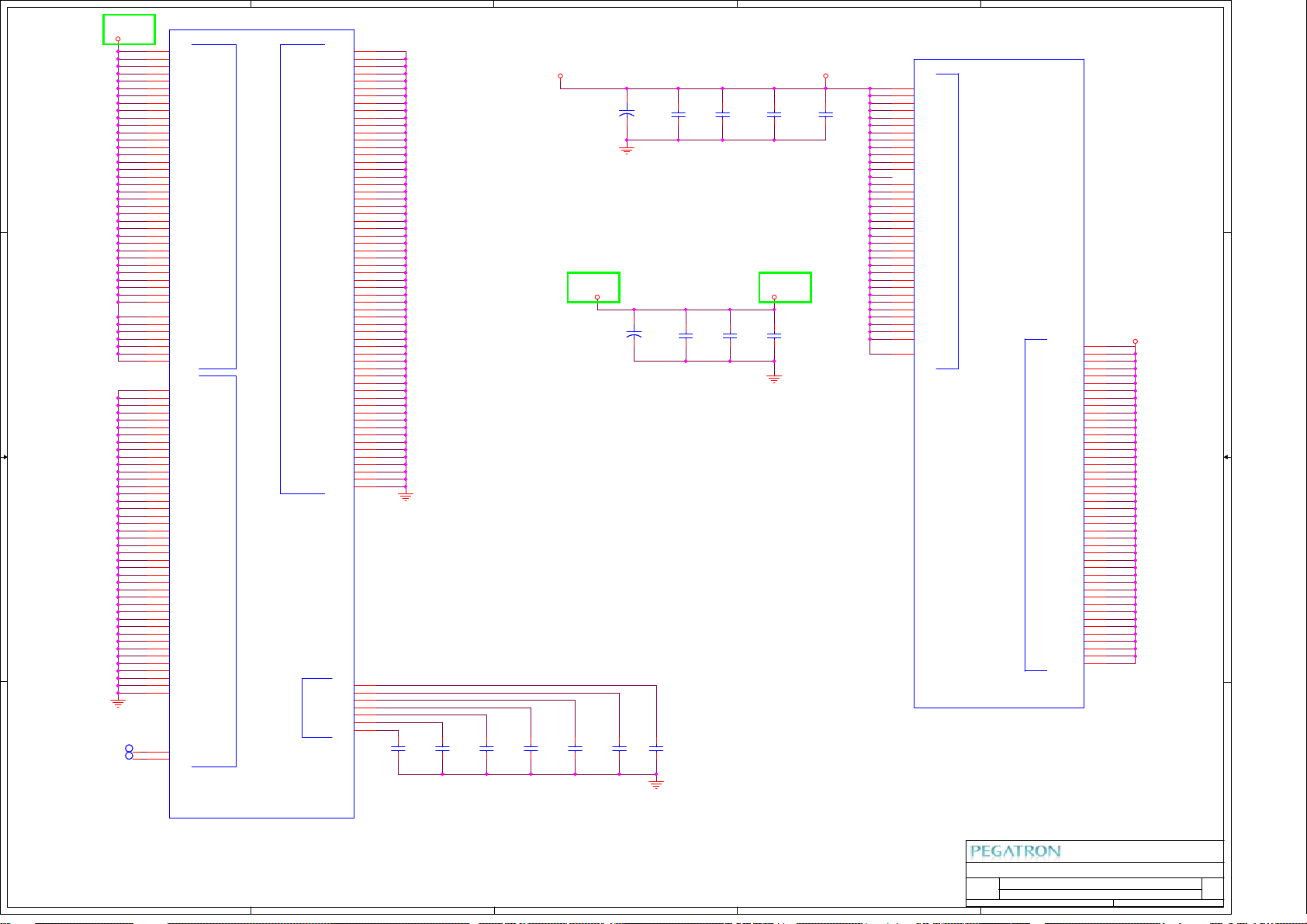

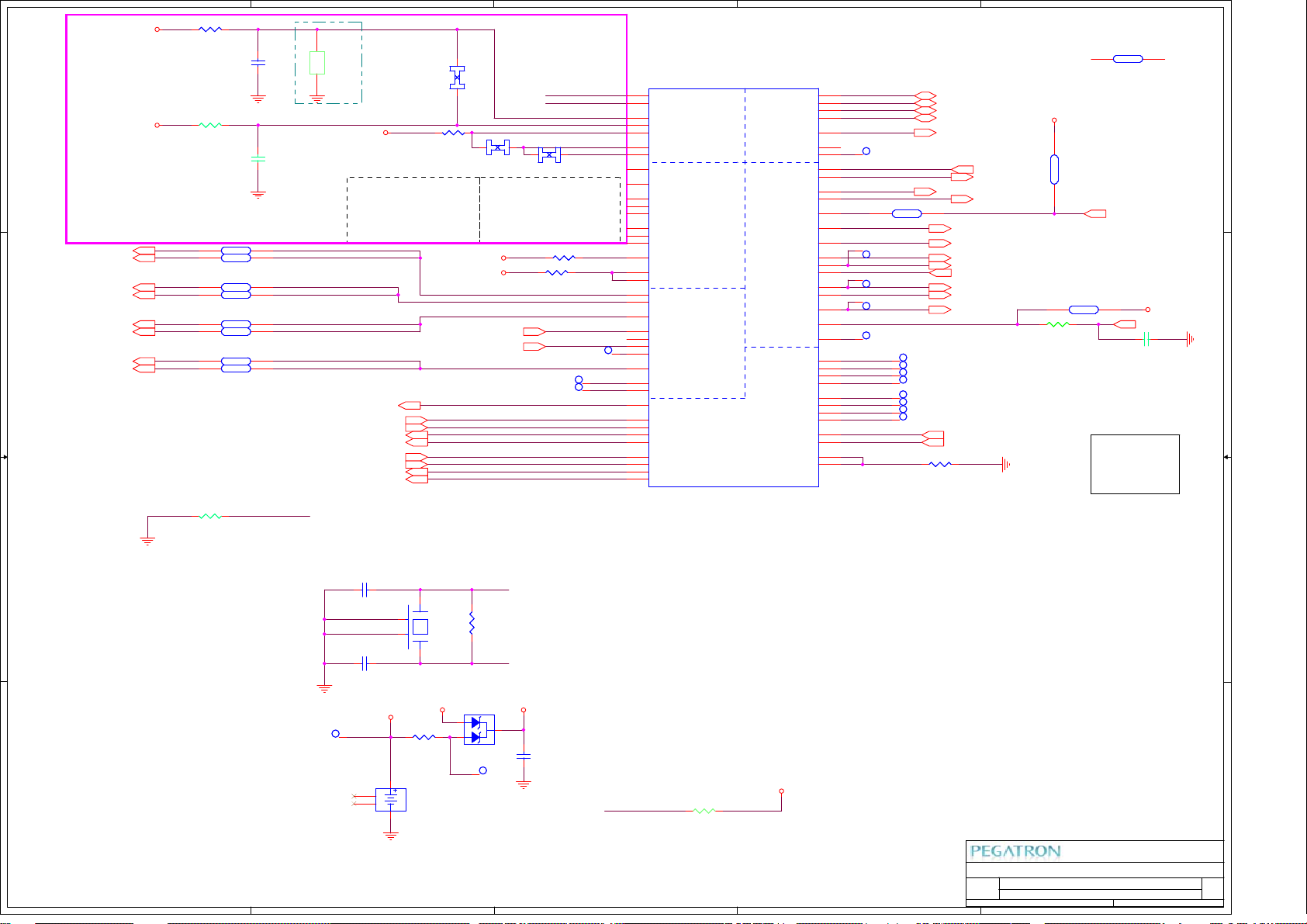

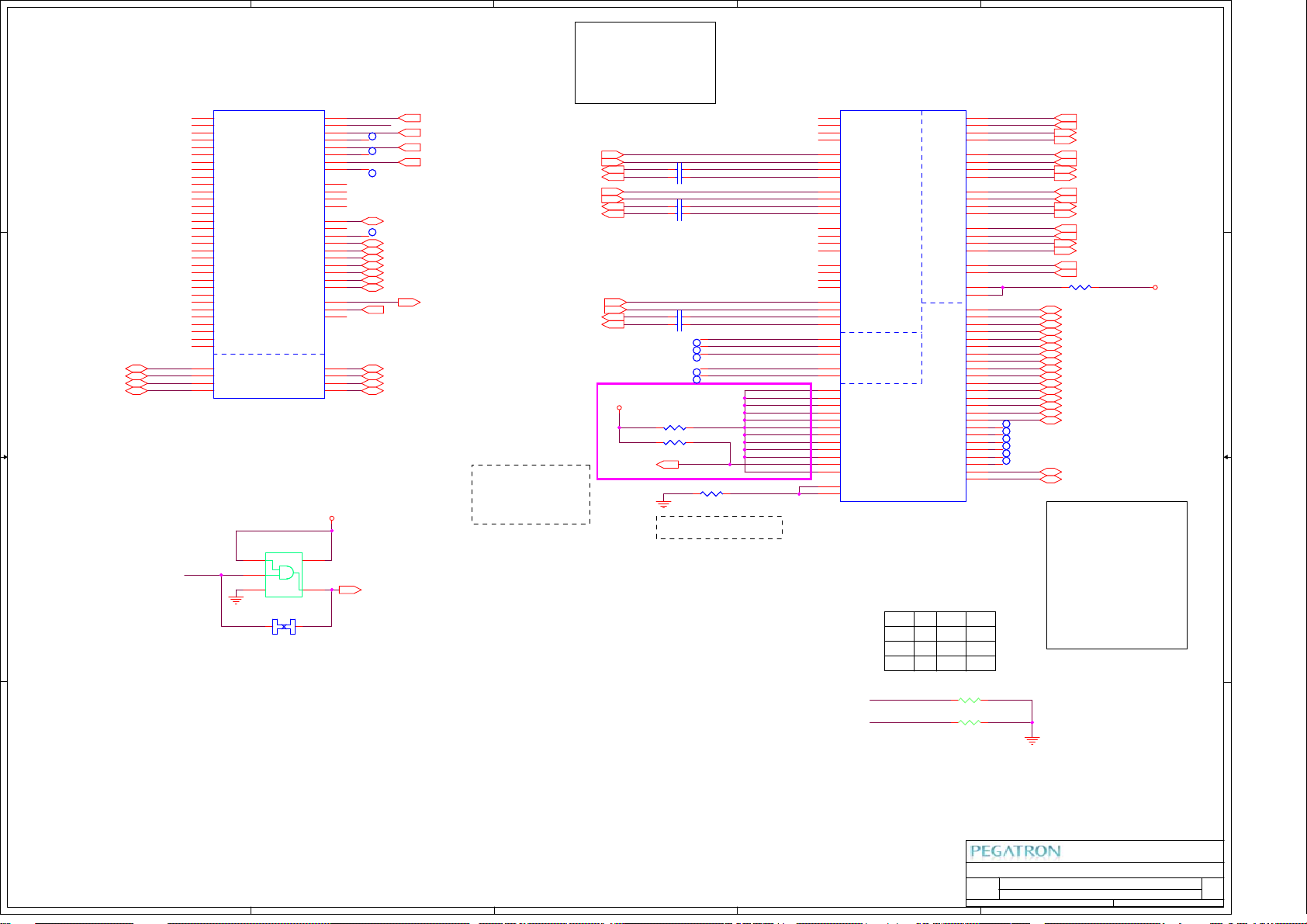

F83Vf MonteVina BLOCK DIAGRAM

D D

CPU

MEROM / PENRYN

Page 3~5

FSB 1066MHz

LVDS

Page 45

CRT

Page 46

HDMI

Page 48

C C

NVIDIA

N10P-GV2

Page 70~79

PCIE x16 DDR3 1066MHz

PM-45

Page 10~15

x4 DMI

Dual Channel DDR3

SO-DIMM X 2

Page 7 ~ 9

System

1.5VS & 1.05VS

DDR & VTT

1.8VS

VGA_VCORE

Charger

Detect

Load Switch

Power Protect

10/100 LAN

PCI-E LAN

AR8132

Page 33 ~ 34

PCI-E

ICH9-M

Page 20 ~ 24

NEWCARD

B B

Page 53

SATA HDD

SATA ODD

USB 2.0

X4

FAN + SENSOR

Page 50

Power On Sequence

Page 02

PWR / EXGATE Switch

A A

Page 55

PWR Discharge

Page 57

5

4

SATA

Page 51

Page 51

USB

Page 52

LPC

33MHz

Azalia

USB CCD

Page 45

BLUE TOOTH

Module

Page 61

Card Reader

Alcor AU6433

Finger Printer

(NO STUFF)

Page 63

RLT ALC269

Page 40

3

Debug Conn.

EC ITE8512 SPI ROM

Page 30 ~ 31

AUDIO AMP

Page 36

AUDIO JACK &

MIC

4 in 1 Card

Reader

Page 40

Page 44

Page 30

Page 37

Page 38

Power Protect

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

2

Date: Sheet

Engineer:

F83Vf

F83Vf

F83Vf

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

Page 80

Page 81

Page 82

Page 83

Page 84

Page 85

Page 88

Page 90

Page 91

Page 92

Page 93

Block Diagram

Block Diagram

Block Diagram

Zack Kuo

Zack Kuo

Zack Kuo

of

of

of

1 100Thursday, July 16, 2009

1 100Thursday, July 16, 2009

1 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

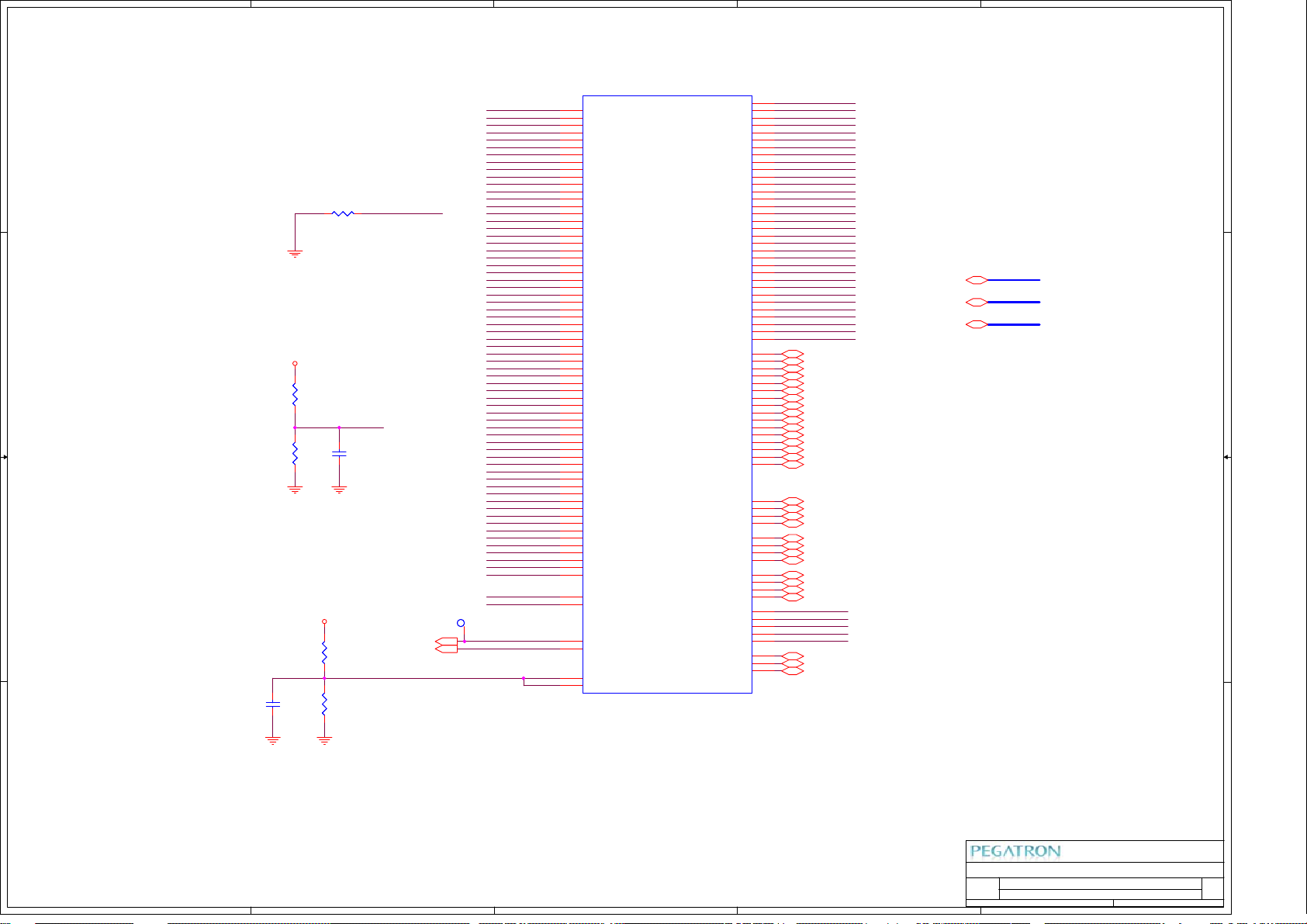

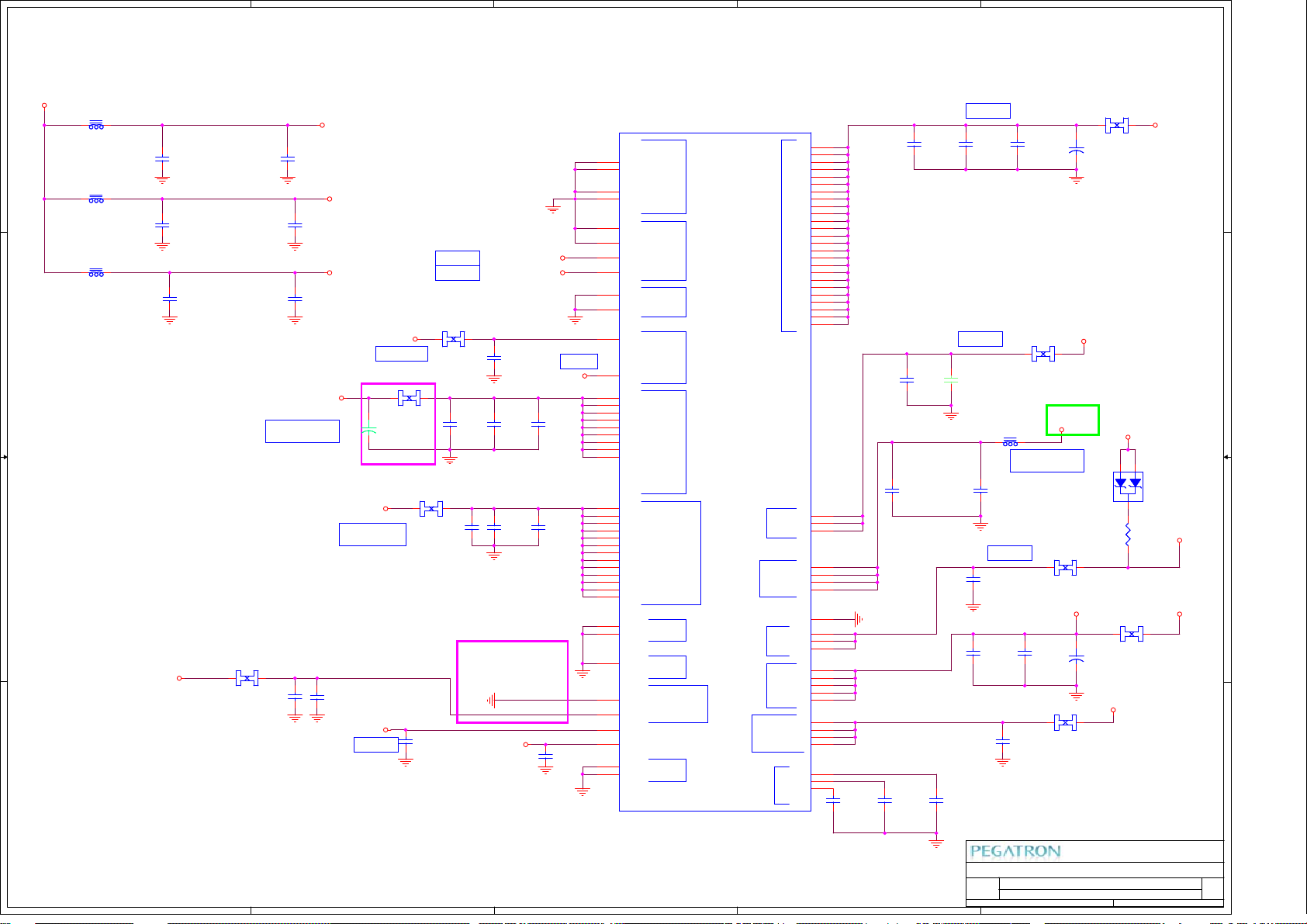

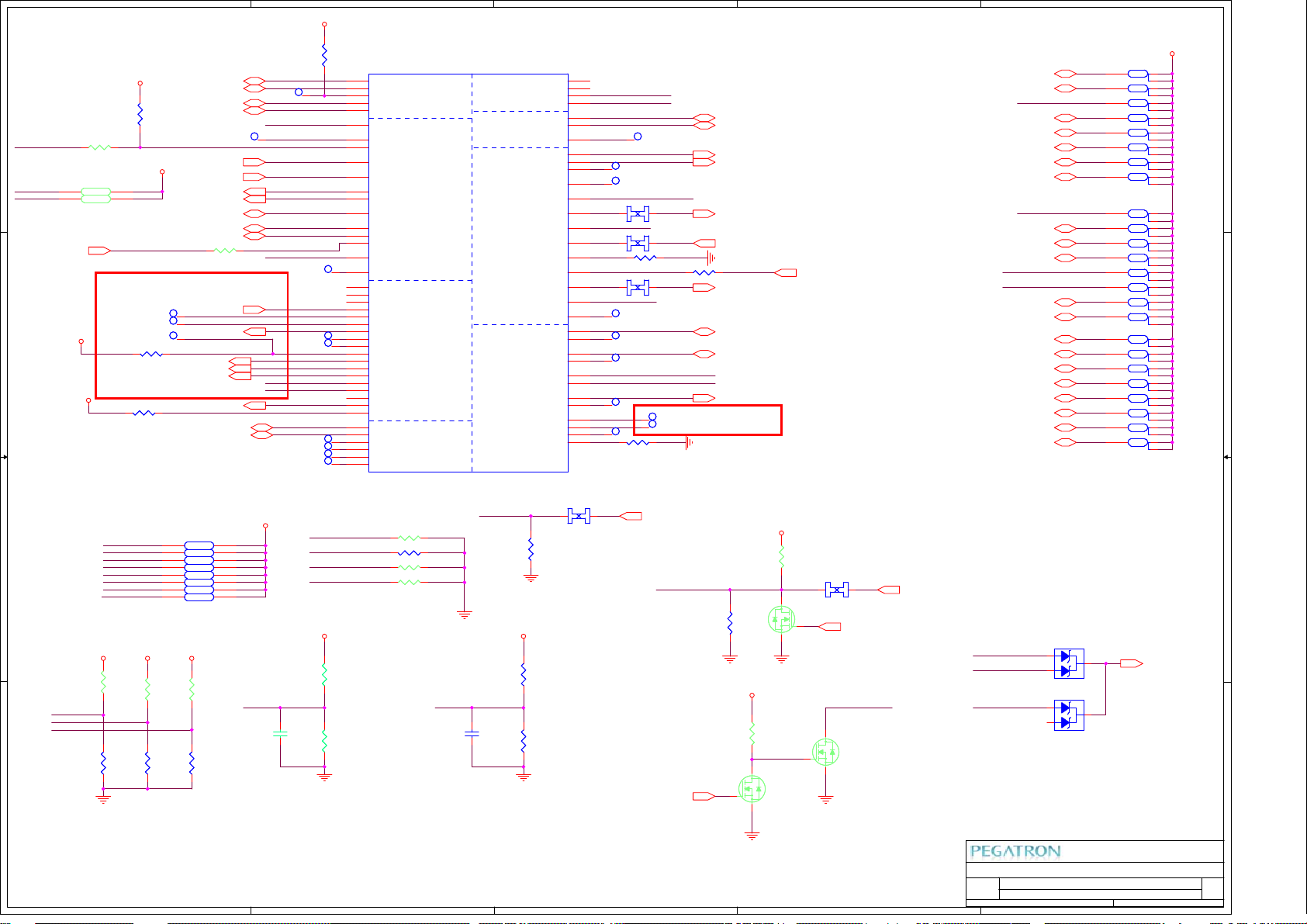

Page 2

5

4

3

2

1

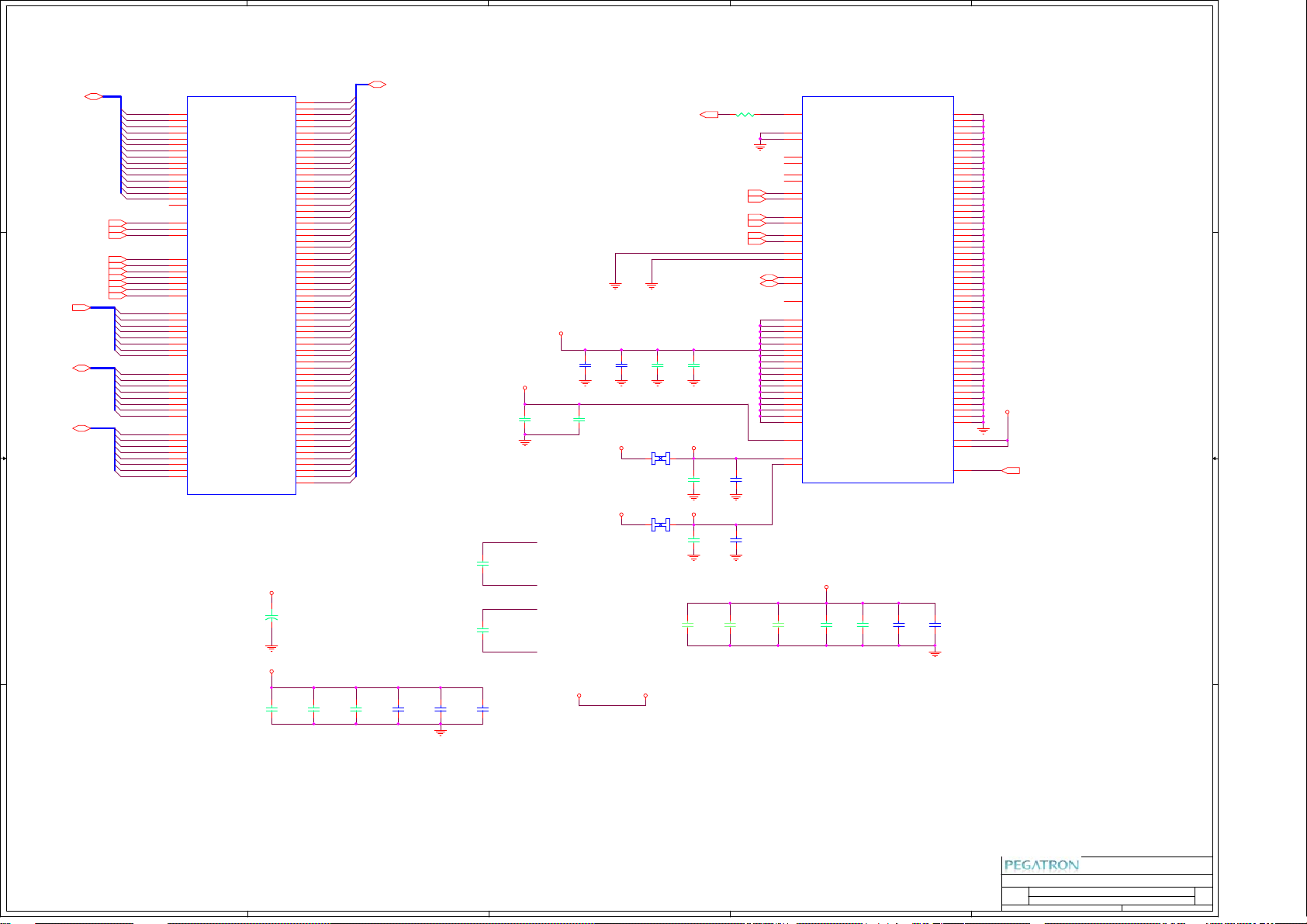

Reset

IC

D D

2

AC_BAT_SYS

+5VA

+3VA

+3VA_EC

+3VSUS

+5VSUS

+12VSUS

1

3

4

+3VA_EC

VSUS_ON

VSUS_GD#

EC

IT8511E

8

C C

B B

SUSC_ON

9

SUSB_ON

+1.5V

+3V

+5V

+12V

+VGA_VCORE

+1.8VS

+1.25VS

+2.5VS

+3VS

+5VS

+12VS

10

ALL_SYSTEM_PWRGD

CPU_PWRGD

12

PWRSW#_EC

7

PM_PWRBTN#

5

PM_RSMRST#

EC_CLK_EN

SUSC_ON

SUSB_ON

15

ICH8_PWROK

13

6

Power On

SWITCH

ICH9

VRMPWRGD

CL_PWROK

PWROK

PM45

CL_PWROK

PWROK

CLK

Gen.

SLP_S4#

SLP_S3#

16

PLT_RST#

17

H_CPURST#

14

CLK_PWRGD

CLK_PWRGD asserted when both

PM_SUSB# and VRM_PWRGD are

high.

To EC

16

H_PWRGD

PENRYN

Delay

99ms

A A

5

11

4

CPU_VRON

+VCORE

Power On Sequence

1

3

2

17

Title :

Title :

Title :

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

Date: Sheet

Engineer:

F83Vf

F83Vf

F83Vf

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

Power Sequence

Power Sequence

Power Sequence

Zack Kuo

Zack Kuo

Zack Kuo

of

of

of

2 100Thursday, July 16, 2009

2 100Thursday, July 16, 2009

2 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

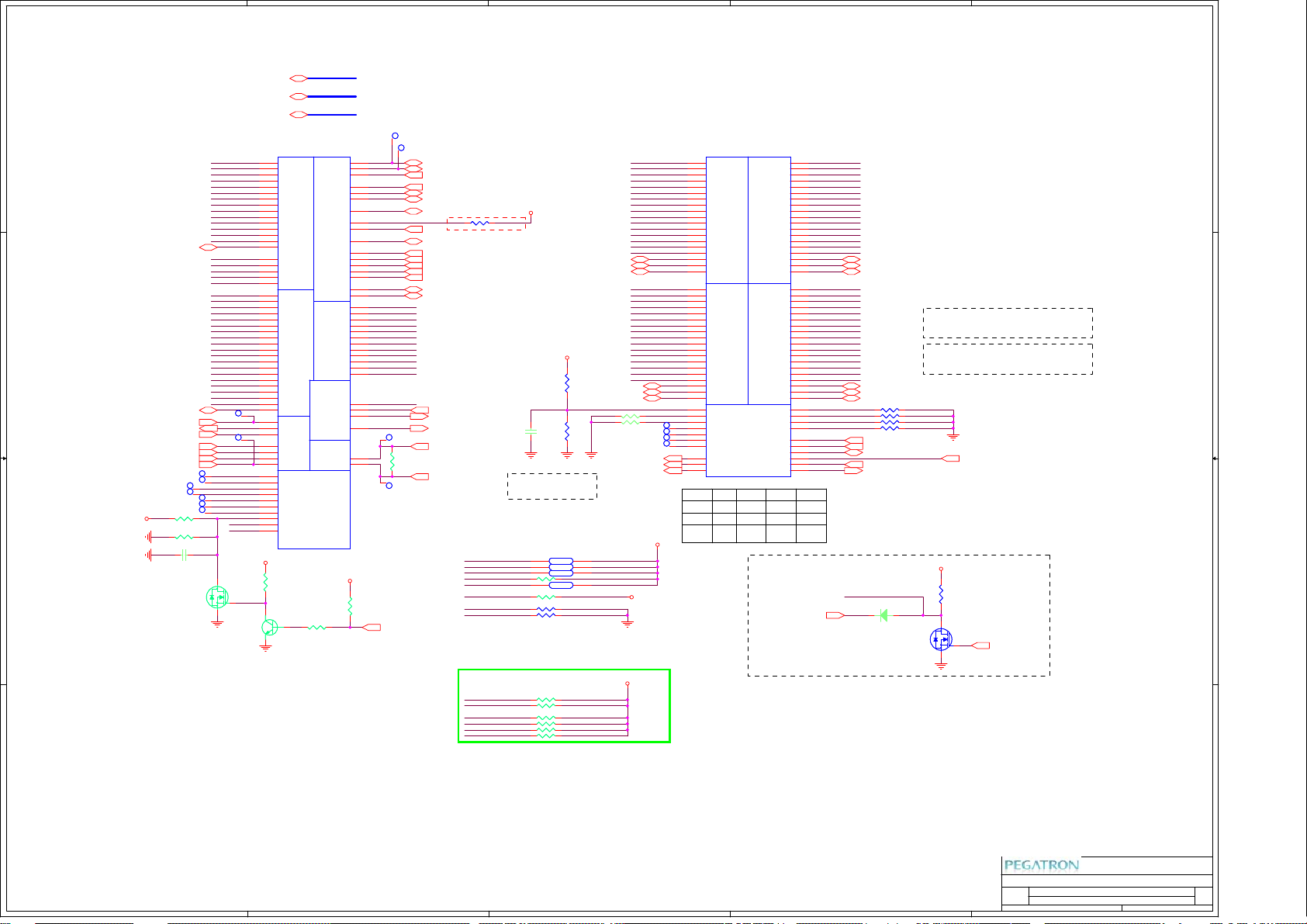

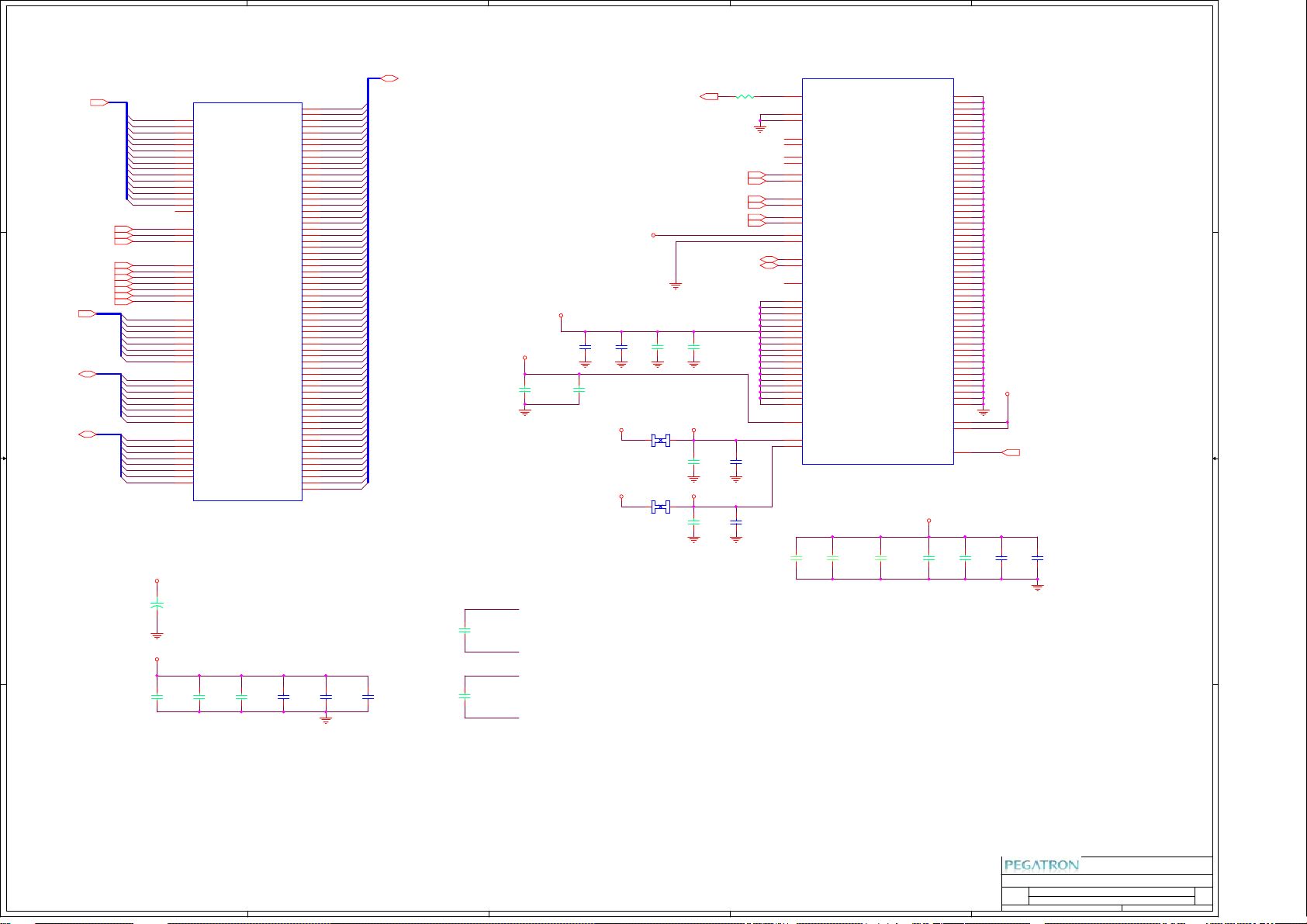

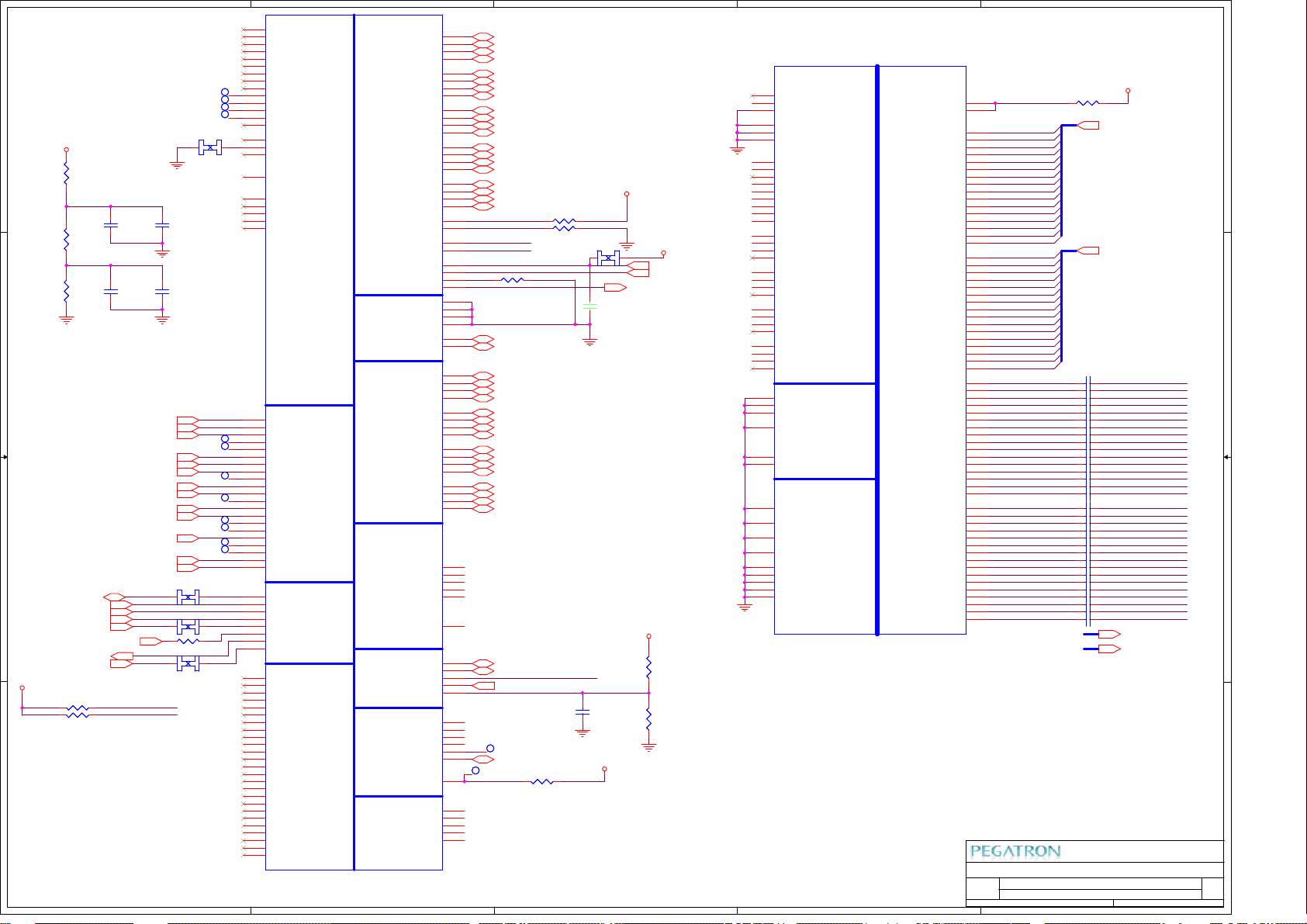

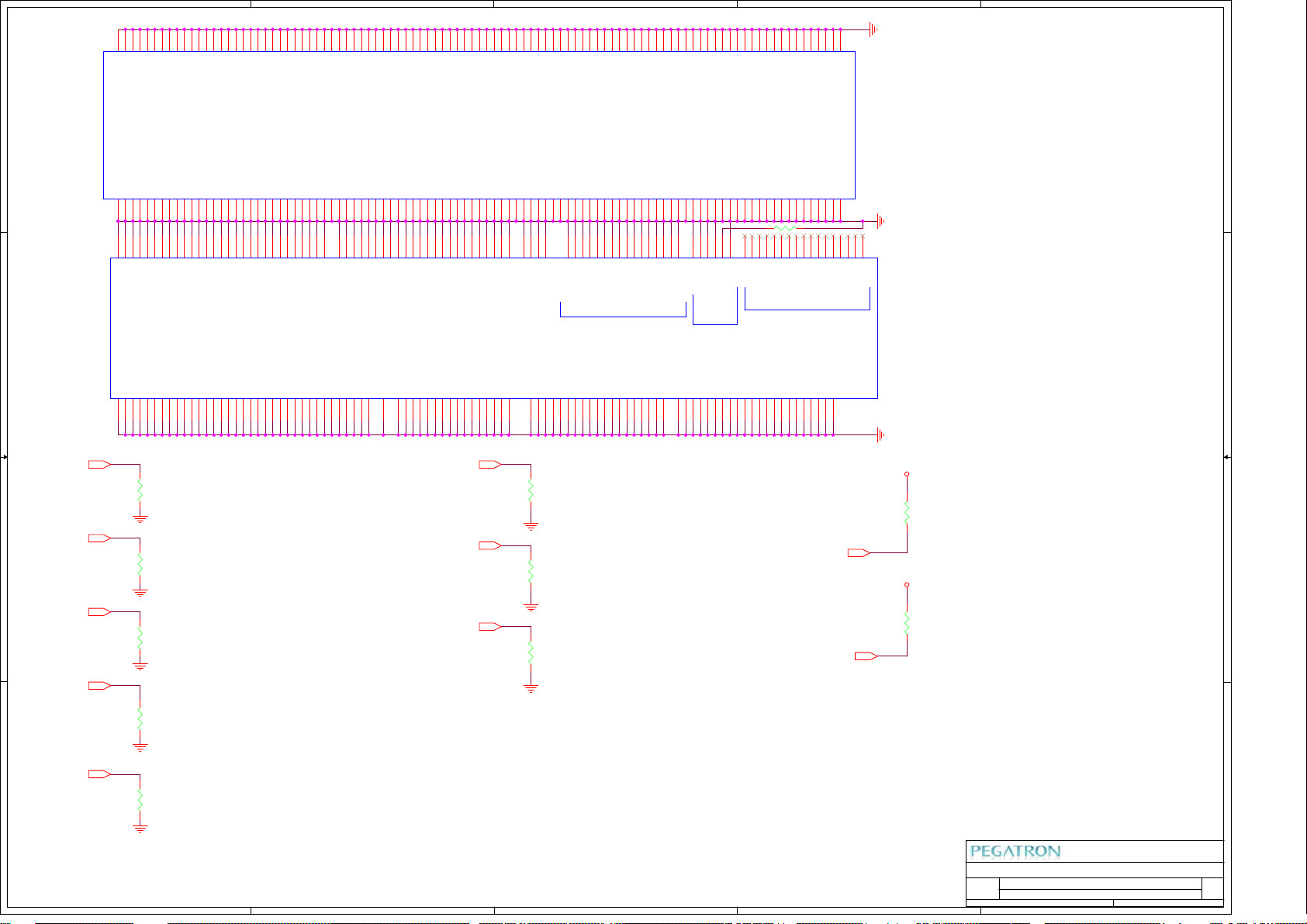

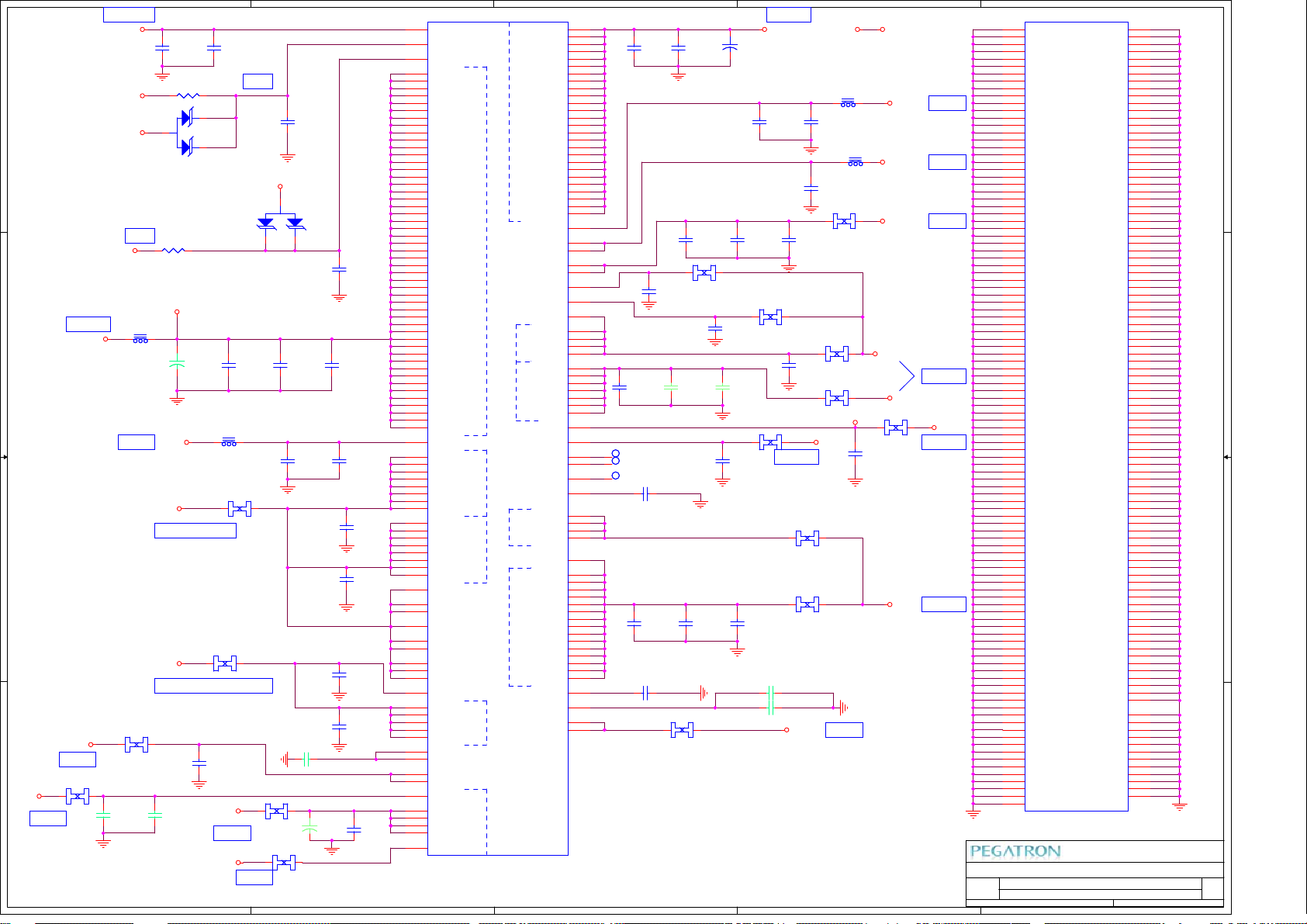

Page 3

5

4

3

2

1

U0301A

U0301A

ADDR GROUP 0 ADDR GROUP 1

ADDR GROUP 0 ADDR GROUP 1

A[3]#

A[4]#

A[5]#

A[6]#

A[7]#

A[8]#

A[9]#

A[10]#

A[11]#

A[12]#

A[13]#

A[14]#

A[15]#

A[16]#

ADSTB[0]#

REQ[0]#

REQ[1]#

REQ[2]#

REQ[3]#

REQ[4]#

A[17]#

A[18]#

A[19]#

A[20]#

A[21]#

A[22]#

A[23]#

A[24]#

A[25]#

A[26]#

A[27]#

A[28]#

A[29]#

A[30]#

A[31]#

A[32]#

A[33]#

A[34]#

A[35]#

ADSTB[1]#

ICH

ICH

A20M#

FERR#

IGNNE#

STPCLK#

LINT0

LINT1

SMI#

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

SOCKET478B

SOCKET478B

B

1

B

1

1 2

R0333 10KOhm

R0333 10KOhm

H_D#[63:0]

H_A#[35:3]

H_REQ#[4:0]

ADS#

BNR#

BPRI#

DEFER#

DRDY#

DBSY#

BR0#

IERR#

INIT#

LOCK#

CONTROL

CONTROL

RESET#

RS[0]#

RS[1]#

RS[2]#

TRDY#

HITM#

BPM[0]#

BPM[1]#

BPM[2]#

BPM[3]#

PRDY#

PREQ#

TRST#

XDP/ITP SIGNALS

XDP/ITP SIGNALS

DBR#

THERMAL

THERMAL

PROCHOT#

THRMDA

THRMDC

THERMTRIP#

H CLK

H CLK

BCLK[0]

BCLK[1]

RESERVED

RESERVED

@

@

HIT#

TCK

TDI

TDO

TMS

+VCCP_CPU

1 2

H1

E2

G5

H5

F21

E1

F1

H_IERR#

D20

B3

H4

C1

F3

F4

G3

G2

G6

E4

AD4

AD3

AD1

AC4

AC2

AC1

AC5

AA6

AB3

AB5

AB6

C20

H_PROCHOT_S#

D21

A24

B25

C7

A22

A21

R0334

R0334

10KOhm

10KOhm

@

@

T0318T0318

T0319T0319

1

1

XDP_BPM#0

XDP_BPM#1

XDP_BPM#2

H_PRDY#

H_PREQ#

H_TCK

H_TDI

H_TDO

H_TMS

H_TRST#

H_DBR#

T0302T0302

1

R0339

R0339

100Ohm

100Ohm

1% @

1% @

1 2

1

T0303T0303

GTLREF_CTRL <4>

H_ADS# <10>

H_BNR# <10>

H_BPRI# <10>

H_DEFER# <10>

H_DRDY# <10>

H_DBSY# <10>

H_BR0# <10>

R0309 49.9OhmR0309 49.9Ohm

1 2

H_INIT# <20>

H_LOCK# <10>

H_CPURST# <10>

H_RS#0 <10>

H_RS#1 <10>

H_RS#2 <10>

H_TRDY# <10>

H_HIT# <10>

H_HITM# <10>

CPU_THRM_DA <50>

CPU_THRM_DC <50>

H_THRMTRIP# <5,11,20,32>

CLK_CPU_BCLK <29>

CLK_CPU_BCLK# <29>

+VCCP_CPU

QC

C0301

C0301

0.1UF/10V

0.1UF/10V

@

@

Zo=55 Ohm, 0.5" max

for GTL_REF

Default Strapping When Not Used

H_PRDY#

H_PREQ#

H_TDI

H_TDO

R0304 54.9Ohm 1%@R0304 54.9Ohm 1%@

H_TMS

H_DBR#

R0306 1KOhm 1%@R0306 1KOhm 1%@

H_TCK

R0307 54.9Ohm 1%R0307 54.9Ohm 1%

H_TRST#

R0308 54.9Ohm 1%R0308 54.9Ohm 1%

Place R0304 & R0306 for XDP function

H_TDI_M

R0337 54.9Ohm 1% @R0337 54.9Ohm 1% @

H_TDO_M

R0338 54.9Ohm 1% @R0338 54.9Ohm 1% @

XDP_BPM#0

R0321 54.9Ohm 1% @R0321 54.9Ohm 1% @

XDP_BPM#1

R0301 54.9Ohm 1% @R0301 54.9Ohm 1% @

XDP_BPM#2

R0322 54.9Ohm 1% @R0322 54.9Ohm 1% @

XDP_BPM#3

R0323 54.9Ohm 1% @R0323 54.9Ohm 1% @

R0315

R0315

1KOhm

1KOhm

1%

1%

12

R0316

R0316

2KOhm

2KOhm

1%

1%

5 6

7 8

3 4

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

+VCCP_CPU

1 2

1 2

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

56Ohm

H_DSTBN#0<10>

H_DSTBP#0<10>

H_DINV#0<10>

R0317 1KOhm1%@R0317 1KOhm1%@

R0318 1KOhm1%@R0318 1KOhm1%@

RN0301C

RN0301C

RN0301D

RN0301D

RN0301B

RN0301B

RN0301A

RN0301A

H_DSTBN#1<10>

H_DSTBP#1<10>

H_DINV#1<10>

+VCCP_CPU

T0304T0304

T0305T0305

T0306T0306

T0307T0307

CPU_BSEL0<29>

CPU_BSEL1<29>

CPU_BSEL2<29>

+VCCP_CPU

+3VS

QC

U0301B

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4H_A#7

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#20

H_D#21

H_D#22XDP_BPM#3

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

GTL_REF

12

12

U0301B

E22

D[0]#

F24

D[1]#

E26

D[2]#

G22

D[3]#

F23

D[4]#

G25

D[5]#

E25

D[6]#

E23

D[7]#

K24

D[8]#

G24

D[9]#

J24

D[10]#

J23

D[11]#

H22

D[12]#

F26

D[13]#

K22

D[14]#

H23

D[15]#

J26

DSTBN[0]#

H26

DSTBP[0]#

H25

DINV[0]#

N22

D[16]#

K25

D[17]#

P26

D[18]#

R23

D[19]#

L23

D[20]#

M24

D[21]#

L22

D[22]#

M23

D[23]#

P25

D[24]#

P23

D[25]#

P22

D[26]#

T24

D[27]#

R24

D[28]#

L25

D[29]#

T25

D[30]#

N25

D[31]#

L26

DSTBN[1]#

M26

DSTBP[1]#

N24

DINV[1]#

AD26

GTLREF

C23

TEST1

D25

TEST2

C24

1

TEST3

AF26

1

TEST4

AF1

1

TEST5

A26

1

TEST6

B22

BSEL[0]

B23

BSEL[1]

C21

BSEL[2]

SOCKET478B

SOCKET478B

BCLK FSB BSEL2 BSEL1 BSEL0

667 L H H

166

800 L H L

200

1067 L L L266

DATA GRP 0

DATA GRP 0

DATA GRP 2DATA GRP 3

DATA GRP 2DATA GRP 3

DSTBN[2]#

DSTBP[2]#

DATA GRP 1

DATA GRP 1

DSTBN[3]#

DSTBP[3]#

MISC

MISC

PWRGOOD

D[32]#

D[33]#

D[34]#

D[35]#

D[36]#

D[37]#

D[38]#

D[39]#

D[40]#

D[41]#

D[42]#

D[43]#

D[44]#

D[45]#

D[46]#

D[47]#

DINV[2]#

D[48]#

D[49]#

D[50]#

D[51]#

D[52]#

D[53]#

D[54]#

D[55]#

D[56]#

D[57]#

D[58]#

D[59]#

D[60]#

D[61]#

D[62]#

D[63]#

DINV[3]#

COMP[0]

COMP[1]

COMP[2]

COMP[3]

DPRSTP#

DPSLP#

DPWR#

SLP#

H_D#32

Y22

H_D#33

AB24

H_D#34

V24

H_D#35

V26

H_D#36

V23

H_D#37

T22

H_D#38

U25

H_D#39

U23

H_D#40

Y25

H_D#41

W22

H_D#42

Y23

H_D#43

W24

H_D#44

W25

H_D#45

AA23

H_D#46

AA24

H_D#47

AB25

Y26

AA26

U22

AE24

AD24

AA21

AB22

AB21

AC26

AD20

AE22

AF23

AC25

AE21

AD21

AC22

AD23

AF22

AC23

AE25

AF24

AC20

R26

U26

AA1

Y1

E5

B5

D24

D6

D7

AE6

PSI#

PWRLIMIT#<30>

H_D#48

H_D#49

H_D#50

H_D#51H_D#19

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_COMP0

R0311 24.9Ohm 1%R0311 24.9Ohm 1%

H_COMP1

R0312 49.9Ohm 1%R0312 49.9Ohm 1%

H_COMP2

R0313 24.9Ohm 1%R0313 24.9Ohm 1%

H_COMP3

R0314 49.9Ohm 1%R0314 49.9Ohm 1%

H_PROCHOT_S#

D0301 RB751V-40

D0301 RB751V-40

H_DSTBN#2 <10>

H_DSTBP#2 <10>

H_DINV#2 <10>

QC

DC

H_DSTBN#3 <10>

H_DSTBP#3 <10>

H_DINV#3 <10>

1 2

1 2

1 2

1 2

H_DPRSTP# <11,20,80>

H_DPSLP# <20>

H_DPWR# <10>

H_CPUSLP# <10>

PM_PSI# <80>

@

@

12

Comp 0,2: Zo=25 Ohm, trace length < 0.5"

Comp 1,3: Z0=50 Ohm, trace length < 0.5"

Comp 0,2: Zo=27.4 Ohm, trace length < 0.5"

Comp 1,3: Z0=55 Ohm, trace length < 0.5"

H_PWRGD <20>

+VCCP_CPU

R0310

R0310

68Ohm

68Ohm

1 2

32

3

3

D

D

Q0301

Q0301

H2N7002

H2N7002

1

1

1

THRO_CPU <30>

G

G

S

S

2

2

H_D#[63:0]<10>

H_A#[35:3]<10>

D D

H_ADSTB#0<10>

C C

H_ADSTB#1<10>

H_A20M#<20>

H_FERR#<20>

H_IGNNE#<20>

H_STPCLK#<20>

H_INTR<20>

H_NMI<20>

H_SMI#<20>

T0308T0308

T0309T0309

CPU_THRM_DA_QC

T310T310

1

CPU_THRM_DC_QC

T311T311

1

T0312T0312

T0313T0313

T0314T0314

1%

1%

+VCCP_CPU

B B

12

R0335 1KOhm

R0335 1KOhm

@

@

1%

1%

12

R0336 1.74KOHM

R0336 1.74KOHM

@

@

12

C0302 0.1UF/10V

C0302 0.1UF/10V

@

@

Q0303

Q0303

2N7002

2N7002

@

@

H_REQ#[4:0]<10>

H_A#3

J4

H_A#4

L5

H_A#5

L4

H_A#6

K5

M3

H_A#8

N2

H_A#9

J1

H_A#10

N3

H_A#11

P5

H_A#12

P2

H_A#13

L2

H_A#14

P4

H_A#15

P1

H_A#16

R1

M1

H_REQ#0

K3

H_REQ#1

H2

H_REQ#2

K2

H_REQ#3

J3

H_REQ#4

L1

H_A#17

Y2

H_A#18

U5

H_A#19

R3

H_A#20

W6

H_A#21

U4

H_A#22

Y5

H_A#23 H_D#23

U1

H_A#24

R4

H_A#25

T5

H_A#26

T3

H_A#27

W2

H_A#28

W5

H_A#29

Y4

H_A#30

U2

H_A#31

V4

H_A#32

W3

H_A#33

AA4

H_A#34

AB2

H_A#35

AA3

BPM_2[1]#

BPM_2[0]#

BPM_2[2]#

GTL_REF2

H_TDO_M

H_TDI_M

1

1

1

G

G

PMBS3904

PMBS3904

Q0302

Q0302

@

@

V1

1

A6

A5

C4

1

D5

C6

B4

A3

M4

N5

T2

V3

B2

C3

D2

D22

D3

F6

+3VS

R0332

R0332

100KOhm

100KOhm

@

@

1 2

3

3

C

C

E

E

2

2

T0320T0320

T0321T0321

1

1

1

1

1

32

3

3

D

D

S

S

2

2

A A

Title :

Title :

Title :

Penryn(1)

Penryn(1)

Penryn(1)

Zack Kuo

Zack Kuo

F83Vf

F83Vf

F83Vf

Zack Kuo

3 100Thursday, July 16, 2009

3 100Thursday, July 16, 2009

3 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

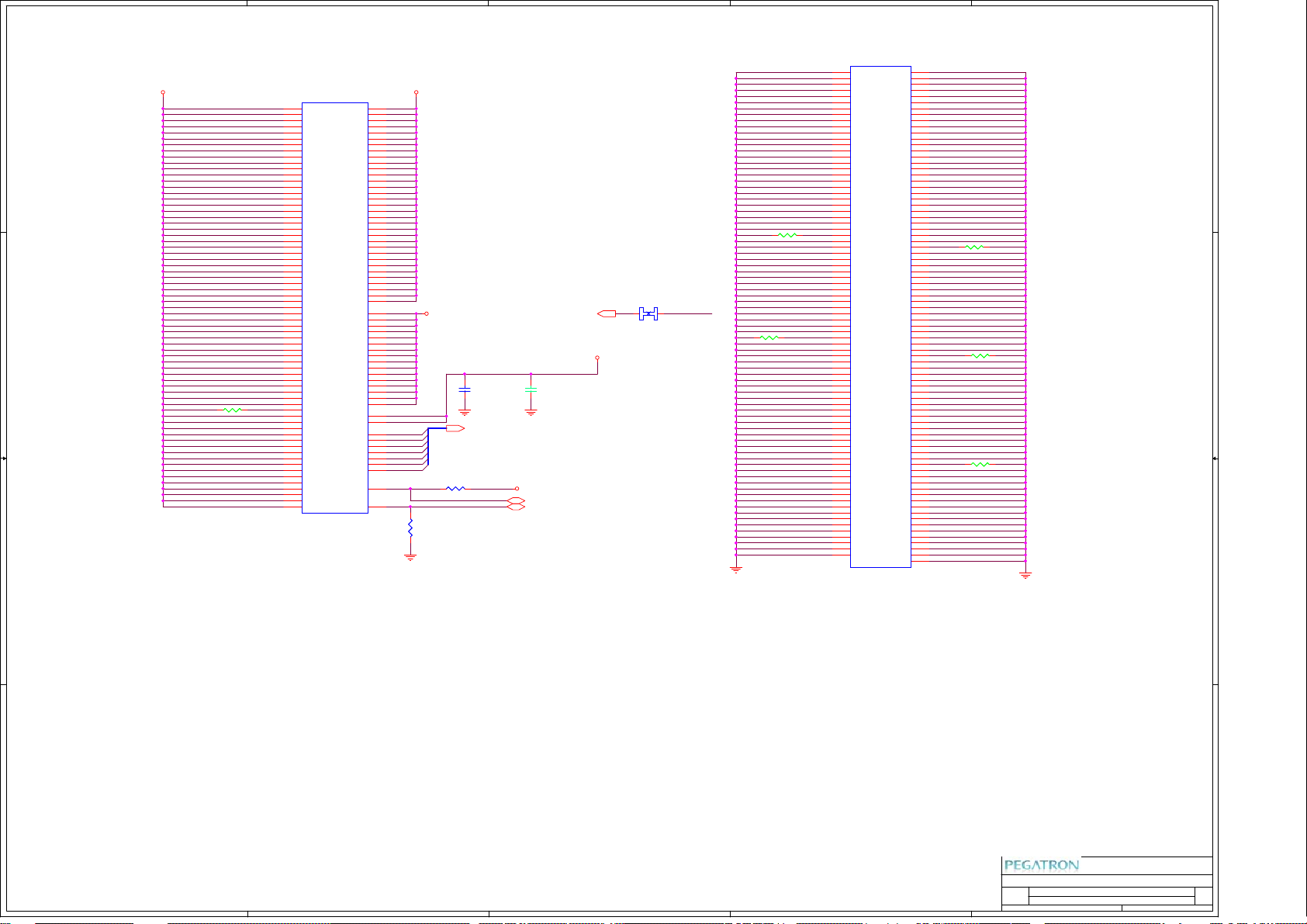

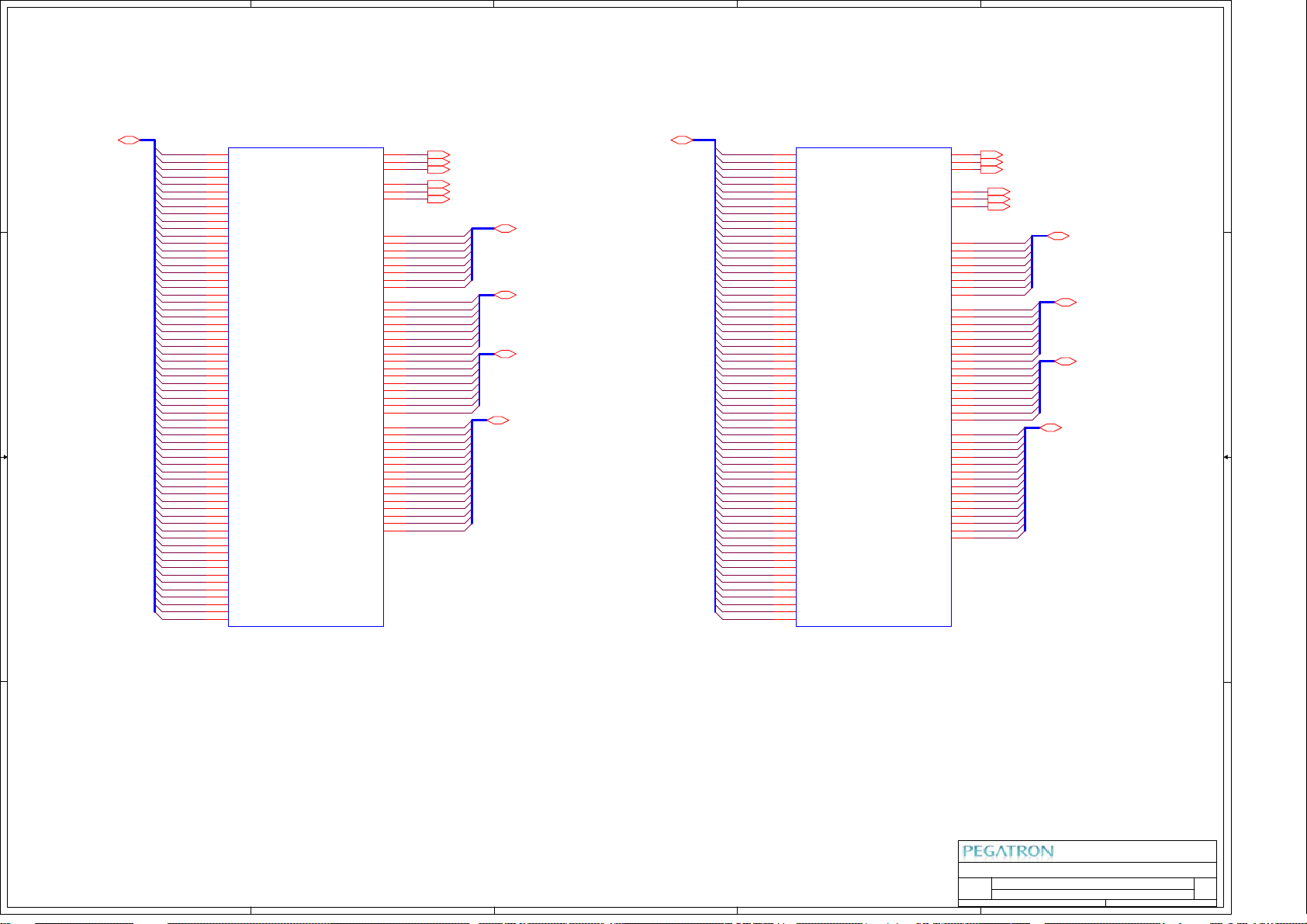

Page 4

5

+VCORE

D D

C C

@

@

1 2

R0409 0Ohm

R0409 0Ohm

B B

AA10

AA12

AA13

AA15

AA17

AA18

AA20

AC10

AB10

AB12

AB14

AB15

AB17

AB18

A10

A12

A13

A15

A17

A18

A20

B10

B12

B14

B15

B17

B18

B20

C10

C12

C13

C15

C17

C18

D10

D12

D14

D15

D17

D18

E10

E12

E13

E15

E17

E18

E20

F10

F12

F14

F15

F17

F18

F20

AA7

AA9

AB9

A7

A9

B7

B9

C9

D9

E7

E9

F7

F9

U0301C

U0301C

VCC1

VCC2

VCC3

VCC4

VCC5

VCC6

VCC7

VCC8

VCC9

VCC10

VCC11

VCC12

VCC13

VCC14

VCC15

VCC16

VCC17

VCC18

VCC19

VCC20

VCC21

VCC22

VCC23

VCC24

VCC25

VCC26

VCC27

VCC28

VCC29

VCC30

VCC31

VCC32

VCC33

VCC34

VCC35

VCC36

VCC37

VCC38

VCC39

VCC40

VCC41

VCC42

VCC43

VCC44

VCC45

VCC46

VCC47

VCC48

VCC49

VCC50

VCC51

VCC52

VCC53

VCC54

VCC55

VCC56

VCC57

VCC58

VCC59

VCC60

VCC61

VCC62

VCC63

VCC64

VCC65

VCC66

VCC67

SOCKET478B

SOCKET478B

VCC68

VCC69

VCC70

VCC71

VCC72

VCC73

VCC74

VCC75

VCC76

VCC77

VCC78

VCC79

VCC80

VCC81

VCC82

VCC83

VCC84

VCC85

VCC86

VCC87

VCC88

VCC89

VCC90

VCC91

VCC92

VCC93

VCC94

VCC95

VCC96

VCC97

VCC98

VCC99

VCC100

VCCP1

VCCP2

VCCP3

VCCP4

VCCP5

VCCP6

VCCP7

VCCP8

VCCP9

VCCP10

VCCP11

VCCP12

VCCP13

VCCP14

VCCP15

VCCP16

VCCA1

VCCA2

VID[0]

VID[1]

VID[2]

VID[3]

VID[4]

VID[5]

VID[6]

VCCSENSE

VSSSENSE

4

+VCORE

AB20

AB7

AC7

AC9

AC12

AC13

AC15

AC17

AC18

AD7

AD9

AD10

AD12

AD14

AD15

AD17

AD18

AE9

AE10

AE12

AE13

AE15

AE17

AE18

AE20

AF9

AF10

AF12

AF14

AF15

AF17

AF18

AF20

G21

V6

J6

K6

M6

J21

K21

M21

N21

N6

R21

R6

T21

T6

V21

W21

B26

C26

VR_VID0

AD6

VR_VID1

AF5

VR_VID2

AE5

VR_VID3

AF4

VR_VID4

AE3

VR_VID5

AF3

VR_VID6

AE2

AF7

AE7

+VCCP_CPU

12

C0402

C0402

0.01UF/16V

0.01UF/16V

VR_VID[0:6] <80>

1 2

R0401 100Ohm 1%R0401 100Ohm 1%

12

R0402

R0402

100Ohm

100Ohm

1%

1%

Max: 130 mA

12

C0401

C0401

10UF/6.3V

10UF/6.3V

@

@

+VCORE

VCCSENSE <80>

VSSSENSE <80>

GTLREF_CTRL<3>

+1.5VS

3

R0403 0Ohm@R0403 0Ohm@

1 2

SL401

SL401

GTLREF_CTRL_R

1 2

R0402

R0402

R0404 0Ohm

R0404 0Ohm

@

@

1 2

GTLREF_CTRL_R

2

U0301D

U0301D

A4

VSS1

A8

VSS2

A11

VSS3

A14

VSS4

A16

VSS5

A19

VSS6

A23

VSS7

AF2

VSS8

B6

VSS9

B8

VSS10

B11

VSS11

B13

VSS12

B16

VSS13

B19

VSS14

B21

VSS15

B24

VSS16

C5

VSS17

C8

VSS18

C11

VSS19

C14

VSS20

C16

VSS21

C19

VSS22

C2

VSS23

C22

VSS24

C25

VSS25

D1

VSS26

D4

VSS27

D8

VSS28

D11

VSS29

D13

VSS30

D16

VSS31

D19

VSS32

D23

VSS33

D26

VSS34

E3

VSS35

E6

VSS36

E8

VSS37

E11

VSS38

E14

VSS39

E16

VSS40

E19

VSS41

E21

VSS42

E24

VSS43

F5

VSS44

F8

VSS45

F11

VSS46

F13

VSS47

F16

VSS48

F19

VSS49

F2

VSS50

F22

VSS51

F25

VSS52

G4

VSS53

G1

VSS54

G23

VSS55

G26

VSS56

H3

VSS57

H6

VSS58

H21

VSS59

H24

VSS60

J2

VSS61

J5

VSS62

J22

VSS63

J25

VSS64

K1

VSS65

K4

VSS66

K23

VSS67

K26

VSS68

L3

VSS69

L6

VSS70

L21

VSS71

L24

VSS72

M2

VSS73

M5

VSS74

M22

VSS75

M25

VSS76

N1

VSS77

N4

VSS78

N23

VSS79

N26

VSS80

VSS81P3VSS162

SOCKET478B

SOCKET478B

VSS82

VSS83

VSS84

VSS85

VSS86

VSS87

VSS88

VSS89

VSS90

VSS91

VSS92

VSS93

VSS94

VSS95

VSS96

VSS97

VSS98

VSS99

VSS100

VSS101

VSS102

VSS103

VSS104

VSS105

VSS106

VSS107

VSS108

VSS109

VSS110

VSS111

VSS112

VSS113

VSS114

VSS115

VSS116

VSS117

VSS118

VSS119

VSS120

VSS121

VSS122

VSS123

VSS124

VSS125

VSS126

VSS127

VSS128

VSS129

VSS130

VSS131

VSS132

VSS133

VSS134

VSS135

VSS136

VSS137

VSS138

VSS139

VSS140

VSS141

VSS142

VSS143

VSS144

VSS145

VSS146

VSS147

VSS148

VSS149

VSS150

VSS151

VSS152

VSS153

VSS154

VSS155

VSS156

VSS157

VSS158

VSS159

VSS160

VSS161

VSS163

P6

P21

P24

R2

R5

R22

R25

T1

T4

T23

T26

U3

U6

U21

U24

V2

V5

V22

V25

W1

W4

W23

W26

Y3

Y6

Y21

Y24

AA2

AA5

AA8

AA11

AA14

AA16

AA19

AA22

AA25

AB1

AB4

AB8

AB11

AB13

AB16

AB19

AB23

AB26

AC3

AC6

AC8

AC11

AC14

AC16

AC19

AC21

AC24

AD2

AD5

AD8

AD11

AD13

AD16

AD19

AD22

AD25

AE1

AE4

AE8

AE11

AE14

AE16

AE19

AE23

AE26

A2

AF6

AF8

AF11

AF13

AF16

AF19

AF21

A25

AF25

R0405 0Ohm@R0405 0Ohm@

1 2

R0406 0Ohm@R0406 0Ohm@

BPM_2[3]#

1 2

R0407

R0407

@

@

1 2

0Ohm

0Ohm

1

A A

Title :

Title :

Title :

Penryn(2)

Penryn(2)

Penryn(2)

Zack Kuo

Zack Kuo

F83Vf

F83Vf

F83Vf

Zack Kuo

4 100Thursday, July 16, 2009

4 100Thursday, July 16, 2009

4 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

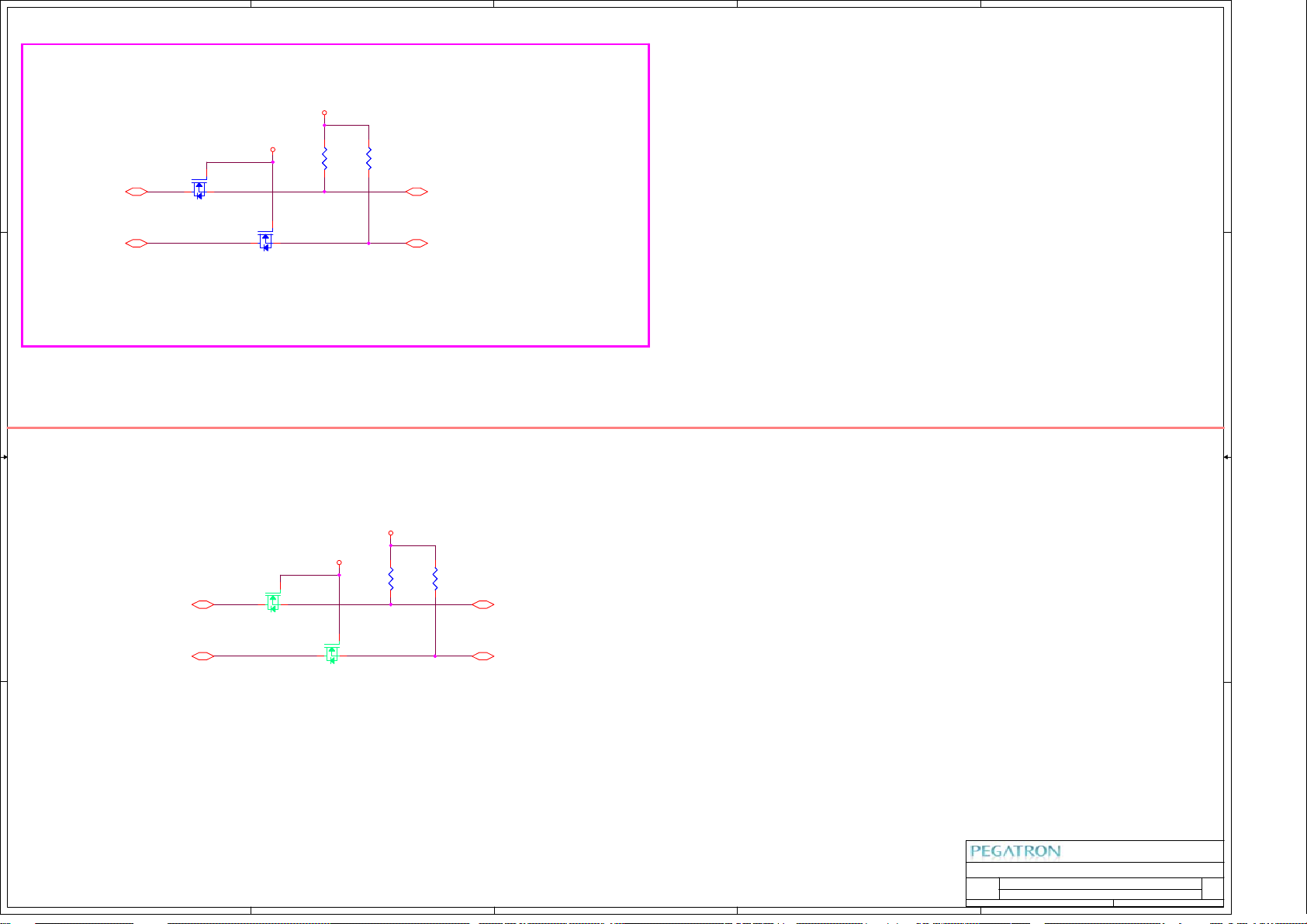

Page 5

5

4

3

2

1

+VCORE

12

C0505

C0505

10UF/6.3V

10UF/6.3V

@

@

12

C0508

C0508

10UF/6.3V

10UF/6.3V

12

C0525

C0525

10UF/6.3V

10UF/6.3V

@

@

12

C0512

C0512

10UF/6.3V

10UF/6.3V

@

@

D D

C C

B B

12

C0531

C0531

10UF/6.3V

10UF/6.3V

12

C0517

C0517

10UF/6.3V

10UF/6.3V

@

@

12

C0539

C0539

10UF/6.3V

10UF/6.3V

@

@

12

C0532

C0532

10UF/6.3V

10UF/6.3V

@

@

12

C0518

C0518

10UF/6.3V

10UF/6.3V

@

@

12

C0524

C0524

10UF/6.3V

10UF/6.3V

@

@

12

C0516

C0516

10UF/6.3V

10UF/6.3V

12

C0515

C0515

10UF/6.3V

10UF/6.3V

@

@

12

C0528

C0528

10UF/6.3V

10UF/6.3V

@

@

12

C0504

C0504

10UF/6.3V

10UF/6.3V

38A for Penryn

12

12

C0523

C0523

10UF/6.3V

10UF/6.3V

@

@

12

12

C0522

C0522

10UF/6.3V

10UF/6.3V

@

@

12

12

C0507

C0507

10UF/6.3V

10UF/6.3V

@

@

C0502

C0502

10UF/6.3V

10UF/6.3V

@

@

C0511

C0511

10UF/6.3V

10UF/6.3V

C0501

C0501

10UF/6.3V

10UF/6.3V

12

C0530

C0530

10UF/6.3V

10UF/6.3V

@

@

12

C0520

C0520

10UF/6.3V

10UF/6.3V

@

@

12

C0506

C0506

10UF/6.3V

10UF/6.3V

12

C0521

C0521

10UF/6.3V

10UF/6.3V

@

@

12

C0503

C0503

10UF/6.3V

10UF/6.3V

12

C0513

C0513

10UF/6.3V

10UF/6.3V

@

@

12

C0519

C0519

10UF/6.3V

10UF/6.3V

@

@

12

C0510

C0510

10UF/6.3V

10UF/6.3V

@

@

12

C0526

C0526

10UF/6.3V

10UF/6.3V

12

C0527

C0527

10UF/6.3V

10UF/6.3V

12

C0509

C0509

10UF/6.3V

10UF/6.3V

@

@

12

C0529

C0529

10UF/6.3V

10UF/6.3V

@

@

+VCCP

Decoupling guide from Intel

VCORE 22uF/10V r 10uF * 32pcs

330uF/2V * 6pcs

VCCP 0.1uF * 6pcs

150uF * 1pcs ?

10uF * 1pcs ?

+VCORE Mid-Frequency Capacitor

Intel: 22UF *32

F83Vf: 10UF*12

+VCCP Decoupling Capacitor

Intel: 270UF *1, 0.1UF *6

F3S: 100UF *1, 0.1UF *3

V1V: ?

+VCCP

12

R0504

R0504

49.9KOhm

49.9KOhm

@

@

H_THRMTRIP#<3,11,20,32>

BUF_PLT_RST#<11,21,30,33,41,53,70>

12

+

+

CE0501

CE0501

100UF/2.5V

100UF/2.5V

+VCCP Decoupling Capacitor

(Place near CPU)

Max: 4500 mA

12

12

C0514

C0514

C0538

C0538

0.1UF/16V

0.1UF/16V

0.1UF/16V

0.1UF/16V

@

@

@

@

+VCCP

12

R0505

R0505

330Ohm

330Ohm

@

@

1 2

C0542 0.1UF/16V

C0542 0.1UF/16V

B

B

@

@

C

C

E12

3

E12

3

Q0502

Q0502

PMBS3904

PMBS3904

@

@

12

C0535

C0535

0.1UF/16V

0.1UF/16V

@

@

2

2

Q0503

Q0503

2N7002

2N7002

S

S

G

G

+VCCP_CPU

12

C0534

C0534

0.1UF/16V

0.1UF/16V

@

@

D

D

FORCE_OFF#

32

3

3

1

1

1

12

C0537

C0537

0.1UF/16V

0.1UF/16V

12

C0536

C0536

0.1UF/16V

0.1UF/16V

12

C0533

C0533

10UF/6.3V

10UF/6.3V

FORCE_OFF# <91,92>

Thermal Trip signal (From CPU to ICH-9M and sequence)

A A

Title :

Title :

Title :

CPU Decouple

CPU Decouple

CPU Decouple

Zack Kuo

Zack Kuo

F83Vf

F83Vf

F83Vf

Zack Kuo

5 100Thursday, July 16, 2009

5 100Thursday, July 16, 2009

5 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

Page 6

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

CPU_***

CPU_***

CPU_***

Zack Kuo

Zack Kuo

F83Vf

F83Vf

F83Vf

Zack Kuo

6 100Thursday, July 16, 2009

6 100Thursday, July 16, 2009

6 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

Page 7

5

4

3

2

1

12

C722

10UF/6.3V

10UF/6.3V

@C722

@

M_A_DQ[63:0] <12>

12

C723

C723

10UF/6.3V

10UF/6.3V

12

C724

C724

10UF/6.3V

10UF/6.3V

1 2

1 2

12

C712

C712

10PF/50V

10PF/50V

@

@

C713

C713

10PF/50V

10PF/50V

@

@

C725

C725

10UF/6.3V

10UF/6.3V

+3VS

12

C706

2.2UF/6.3V

2.2UF/6.3V

M_CLK_DDR0

M_CLK_DDR0#

M_CLK_DDR1

M_CLK_DDR1#

+1.5V_DDR3

12

C702

C702

0.1UF/10V

0.1UF/10V

12

@C706

@

C707

C707

0.1UF/10V

0.1UF/10V

+1.5V_DDR3 +1.5V

RX701

12

12

C705

C705

0.1UF/10V

0.1UF/10V

@

@

12

C708

C708

2.2UF/6.3V

2.2UF/6.3V

12

C710

C710

2.2UF/6.3V

2.2UF/6.3V

C714

C714

10UF/10V

10UF/10V

RX701

0Ohm @

0Ohm @

M_ODT0<11>

M_ODT1<11>

M_A_RAS#<12>

M_DRAMRST#<8,11>

M_CS#0<11>

M_CS#1<11>

SMB_CLK_S<8,24,29,44,53>

SMB_DAT_S<8,24,29,44,53>

12

@

@

C709

C709

0.1UF/10V

0.1UF/10V

12

@

@

C711

C711

0.1UF/10V

0.1UF/10V

12

C715

C715

@

@

10UF/10V

10UF/10V

PM_EXTTS#0<11>

12

12

C703

C703

C704

C704

0.1UF/10V

0.1UF/10V

0.1UF/10V

0.1UF/10V

@

@

@

@

SL701

SL701

1 2

R0603

R0603

SL702

SL702

1 2

R0603

R0603

M_VREFCA_DIMM0

M_VREFDQ_DIMM0

@

@

+0.75V

+0.75V

U701A

M_A_A[14:0]<12>

D D

M_A_BS0<12>

M_A_BS1<12>

M_A_BS2<12>

M_A_CAS#<12>

M_CLK_DDR0#<11>

M_CLK_DDR1#<11>

M_CLK_DDR0<11>

M_CLK_DDR1<11>

M_CKE0<11>

M_A_DM[0:7]<12>

C C

M_A_DQS[0:7]<12>

M_A_DQS#[0:7]<12>

B B

M_CKE1<11>

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

U701A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

109

BA0

108

BA1

79

BA2

115

CAS#

103

CK#0

104

CK#1

101

CK0

102

CK1

73

CKE0

74

CKE1

11

DM0

28

DM1

46

DM2

63

DM3

136

DM4

153

DM5

170

DM6

187

DM7

12

DQS0

29

DQS1

47

DQS2

64

DQS3

137

DQS4

154

DQS5

171

DQS6

188

DQS7

10

DQS#0

27

DQS#1

45

DQS#2

62

DQS#3

135

DQS#4

152

DQS#5

169

DQS#6

186

DQS#7

DDR3_DIMM_204P

DDR3_DIMM_204P

DDR3 DIMM 204P 0.6mm 9.2H REV

DDR3 DIMM 204P 0.6mm 9.2H REV

1202-003V000

1202-003V000

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

+1.5V_DDR3

12

+

+

CE701

CE701

100UF/2V

100UF/2V

@

@

+1.5V_DDR3

12

C701

10UF/6.3V

10UF/6.3V

M_A_DQ5

5

M_A_DQ1

7

M_A_DQ7

15

M_A_DQ6

17

M_A_DQ0

4

M_A_DQ4

6

M_A_DQ2

16

M_A_DQ3

18

M_A_DQ12

21

M_A_DQ8

23

M_A_DQ10

33

M_A_DQ15

35

M_A_DQ13

22

M_A_DQ9

24

M_A_DQ11

34

M_A_DQ14

36

M_A_DQ16

39

M_A_DQ17

41

M_A_DQ19

51

M_A_DQ22

53

M_A_DQ18

40

M_A_DQ20

42

M_A_DQ21

50

M_A_DQ23

52

M_A_DQ28

57

M_A_DQ29

59

M_A_DQ30

67

M_A_DQ31

69

M_A_DQ24

56

M_A_DQ25

58

M_A_DQ27

68

M_A_DQ26

70

M_A_DQ32

129

M_A_DQ37

131

M_A_DQ38

141

M_A_DQ39

143

M_A_DQ33

130

M_A_DQ36

132

M_A_DQ34

140

M_A_DQ35

142

M_A_DQ44

147

M_A_DQ45

149

M_A_DQ47

157

M_A_DQ46

159

M_A_DQ40

146

M_A_DQ41

148

M_A_DQ42

158

M_A_DQ43

160

M_A_DQ53

163

M_A_DQ48

165

M_A_DQ54

175

M_A_DQ52

177

M_A_DQ49

164

M_A_DQ50

166

M_A_DQ51

174

M_A_DQ55

176

M_A_DQ60

181

M_A_DQ61

183

M_A_DQ59

191

M_A_DQ57

193

M_A_DQ56

180

M_A_DQ63

182

M_A_DQ58

192

M_A_DQ62

194

12

@C701

@

C721

@C721

@

10UF/6.3V

10UF/6.3V

U701B

U701B

198

12

EVENT#

207

GND1

208

GND2

77

NC1

122

NC2

205

NP_NC1

206

NP_NC2

116

ODT0

120

ODT1

110

RAS#

30

RESET#

114

S#0

121

S#1

197

SA0

201

SA1

202

SCL

200

SDA

125

TEST

75

VDD1

76

VDD2

81

VDD3

82

VDD4

87

VDD5

88

VDD6

93

VDD7

94

VDD8

99

VDD9

100

VDD10

105

VDD11

106

VDD12

111

VDD13

112

VDD14

117

VDD15

118

VDD16

123

VDD17

124

VDD18

199

VDDSPD

126

VREFCA

1

VREFDQ

DDR3_DIMM_204P

DDR3_DIMM_204P

+0.75V

C716

C716

10UF/10V

10UF/10V

12

C717

1UF/6.3V

1UF/6.3V

@C717

@

12

@

@

12

C718

C718

1UF/6.3V

1UF/6.3V

12

@

C719

C719

@

1UF/6.3V

1UF/6.3V

VSS1

VSS2

VSS3

VSS4

VSS5

VSS6

VSS7

VSS8

VSS9

VSS10

VSS11

VSS12

VSS13

VSS14

VSS15

VSS16

VSS17

VSS18

VSS19

VSS20

VSS21

VSS22

VSS23

VSS24

VSS25

VSS26

VSS27

VSS28

VSS29

VSS30

VSS31

VSS32

VSS33

VSS34

VSS35

VSS36

VSS37

VSS38

VSS39

VSS40

VSS41

VSS42

VSS43

VSS44

VSS45

VSS46

VSS47

VSS48

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

12

WE#

C720

C720

1UF/6.3V

1UF/6.3V

2

3

8

9

13

14

19

20

25

26

31

32

37

38

43

44

48

49

54

55

60

61

65

66

71

72

127

128

133

134

138

139

144

145

150

151

155

156

161

162

167

168

172

173

178

179

184

185

189

+0.75V

190

195

196

203

204

113

M_A_WE# <12>

A A

Title :

Title :

Title :

DIMM0

DIMM0

DIMM0

Zack Kuo

Zack Kuo

F83Vf

F83Vf

F83Vf

Zack Kuo

7 100Thursday, July 16, 2009

7 100Thursday, July 16, 2009

7 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

Page 8

5

U801A

+1.5V_DDR3

12

+

+

CE801

CE801

100UF/2V

100UF/2V

@

@

+1.5V_DDR3

12

C819

C819

10UF/6.3V

10UF/6.3V

@

@

98

97

96

95

92

91

90

86

89

85

107

84

83

119

80

78

109

108

79

115

103

104

101

102

73

74

11

28

46

63

136

153

170

187

12

29

47

64

137

154

171

188

10

27

45

62

135

152

169

186

U801A

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10/AP

A11

A12/BC#

A13

A14

A15

BA0

BA1

BA2

CAS#

CK#0

CK#1

CK0

CK1

CKE0

CKE1

DM0

DM1

DM2

DM3

DM4

DM5

DM6

DM7

DQS0

DQS1

DQS2

DQS3

DQS4

DQS5

DQS6

DQS7

DQS#0

DQS#1

DQS#2

DQS#3

DQS#4

DQS#5

DQS#6

DQS#7

DDR3_DIMM_204P

DDR3_DIMM_204P

DDR3 DIMM 204P 0.6mm 5.2H REV.

DDR3 DIMM 204P 0.6mm 5.2H REV.

1202-003U000

1202-003U000

12

12

C820

C820

C821

C821

10UF/6.3V

10UF/6.3V

10UF/6.3V

10UF/6.3V

@

@

@

@

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

12

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQ8

DQ9

C822

C822

10UF/6.3V

10UF/6.3V

5

7

15

17

4

6

16

18

21

23

33

35

22

24

34

36

39

41

51

53

40

42

50

52

57

59

67

69

56

58

68

70

129

131

141

143

130

132

140

142

147

149

157

159

146

148

158

160

163

165

175

177

164

166

174

176

181

183

191

193

180

182

192

194

M_B_A[0:14]<12>

D D

M_B_BS0<12>

M_B_BS1<12>

M_B_BS2<12>

M_B_CAS#<12>

M_CLK_DDR2#<11>

M_CLK_DDR3#<11>

M_CLK_DDR2<11>

M_CLK_DDR3<11>

M_CKE2<11>

M_B_DM[0:7]<12>

C C

M_B_DQS[0:7]<12>

M_B_DQS#[0:7]<12>

B B

M_CKE3<11>

M_B_A0

M_B_A1

M_B_A2

M_B_A3

M_B_A4

M_B_A5

M_B_A6

M_B_A7

M_B_A8

M_B_A9

M_B_A10

M_B_A11

M_B_A12

M_B_A13

M_B_A14

M_B_DM0

M_B_DM1

M_B_DM2

M_B_DM3

M_B_DM4

M_B_DM5

M_B_DM6

M_B_DM7

M_B_DQS0

M_B_DQS1

M_B_DQS2

M_B_DQS3

M_B_DQS4

M_B_DQS5

M_B_DQS6

M_B_DQS7

M_B_DQS#0

M_B_DQS#1

M_B_DQS#2

M_B_DQS#3

M_B_DQS#4

M_B_DQS#5

M_B_DQS#6

M_B_DQS#7

M_B_DQ4

M_B_DQ1

M_B_DQ7

M_B_DQ3

M_B_DQ5

M_B_DQ0

M_B_DQ2

M_B_DQ6

M_B_DQ9

M_B_DQ8

M_B_DQ14

M_B_DQ15

M_B_DQ13

M_B_DQ12

M_B_DQ11

M_B_DQ10

M_B_DQ20

M_B_DQ21

M_B_DQ22

M_B_DQ23

M_B_DQ16

M_B_DQ17

M_B_DQ18

M_B_DQ19

M_B_DQ28

M_B_DQ29

M_B_DQ26

M_B_DQ30

M_B_DQ24

M_B_DQ25

M_B_DQ27

M_B_DQ31

M_B_DQ32

M_B_DQ36

M_B_DQ34

M_B_DQ39

M_B_DQ37

M_B_DQ33

M_B_DQ38

M_B_DQ35

M_B_DQ41

M_B_DQ44

M_B_DQ47

M_B_DQ42

M_B_DQ40

M_B_DQ45

M_B_DQ43

M_B_DQ46

M_B_DQ48

M_B_DQ53

M_B_DQ55

M_B_DQ49

M_B_DQ50

M_B_DQ52

M_B_DQ51

M_B_DQ54

M_B_DQ60

M_B_DQ61

M_B_DQ63

M_B_DQ57

M_B_DQ56

M_B_DQ58

M_B_DQ59

M_B_DQ62

12

C823

C823

10UF/6.3V

10UF/6.3V

4

12

C824

C824

10UF/6.3V

10UF/6.3V

M_B_DQ[0:63] <12>

1 2

1 2

C801

C801

10PF/50V

10PF/50V

@

@

C825

C825

10PF/50V

10PF/50V

@

@

M_CLK_DDR2

M_CLK_DDR2#

M_CLK_DDR3

M_CLK_DDR3#

+3VS

12

C806

2.2UF/6.3V

2.2UF/6.3V

@C806

@

+1.5V_DDR3

12

12

C802

C802

0.1UF/10V

0.1UF/10V

C807

C807

0.1UF/10V

0.1UF/10V

3

U801B

RX801

12

C805

C805

0.1UF/10V

0.1UF/10V

12

C808

C808

2.2UF/6.3V

2.2UF/6.3V

12

C810

C810

2.2UF/6.3V

2.2UF/6.3V

RX801

0Ohm @

0Ohm @

M_ODT2<11>

M_ODT3<11>

M_B_RAS#<12>

M_DRAMRST#<7,11>

M_CS#2<11>

M_CS#3<11>

SMB_CLK_S<7,24,29,44,53>

SMB_DAT_S<7,24,29,44,53>

@

@

12

C809

C809

0.1UF/10V

0.1UF/10V

@

@

12

C811

C811

0.1UF/10V

0.1UF/10V

@

@

PM_EXTTS#1<11>

+3VS

12

12

C804

C804

C803

C803

0.1UF/10V

0.1UF/10V

0.1UF/10V

0.1UF/10V

@

@

@

@

SL801

SL801

1 2

R0603

R0603

SL802

SL802

1 2

R0603

R0603

M_VREFCA_DIMM1

M_VREFDQ_DIMM1

+0.75V

+0.75V

U801B

198

12

207

208

77

122

205

206

116

120

110

30

114

121

197

201

202

200

125

75

76

81

82

87

88

93

94

99

100

105

106

111

112

117

118

123

124

199

126

1

DDR3_DIMM_204P

DDR3_DIMM_204P

12

C812

C812

@

@

10UF/10V

10UF/10V

EVENT#

GND1

GND2

NC1

NC2

NP_NC1

NP_NC2

ODT0

ODT1

RAS#

RESET#

S#0

S#1

SA0

SA1

SCL

SDA

TEST

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

VDD8

VDD9

VDD10

VDD11

VDD12

VDD13

VDD14

VDD15

VDD16

VDD17

VDD18

VDDSPD

VREFCA

VREFDQ

2

2

VSS1

3

VSS2

8

VSS3

9

VSS4

13

VSS5

14

VSS6

19

VSS7

20

VSS8

25

VSS9

26

VSS10

31

VSS11

32

VSS12

37

VSS13

38

VSS14

43

VSS15

44

VSS16

48

VSS17

49

VSS18

54

VSS19

55

VSS20

60

VSS21

61

VSS22

65

VSS23

66

VSS24

71

VSS25

72

VSS26

127

VSS27

128

VSS28

133

VSS29

134

VSS30

138

VSS31

139

VSS32

144

VSS33

145

VSS34

150

VSS35

151

VSS36

155

VSS37

156

VSS38

161

VSS39

162

VSS40

167

VSS41

168

VSS42

172

VSS43

173

VSS44

178

VSS45

179

VSS46

184

VSS47

185

VSS48

189

VSS49

VSS50

VSS51

VSS52

VTT1

VTT2

WE#

+0.75V

12

@

@

C813

C813

10UF/10V

10UF/10V

12

@

@

C814

C814

10UF/10V

10UF/10V

12

C815

C815

1UF/6.3V

1UF/6.3V

@

@

+0.75V

190

195

196

203

204

12

C817

C817

1UF/6.3V

1UF/6.3V

M_B_WE# <12>

12

C818

C818

1UF/6.3V

1UF/6.3V

113

12

C816

C816

1UF/6.3V

1UF/6.3V

@

@

1

A A

Title :

Title :

Title :

DIMM1

DIMM1

DIMM1

Zack Kuo

Zack Kuo

F83Vf

F83Vf

F83Vf

Zack Kuo

8 100Thursday, July 16, 2009

8 100Thursday, July 16, 2009

8 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

Page 9

5

D D

+1.5V_DDR3 +5V

12

R902

R902

2KOhm

2KOhm

@

@

C C

B B

12

C901

C901

0.1UF/10V

0.1UF/10V

@

@

12

C904

C904

0.1UF/10V

0.1UF/10V

@

@

12

R903

R903

2KOhm

2KOhm

@

@

+1.5V_DDR3 +5V

12

R906

R906

2KOhm

2KOhm

@

@

12

R907

R907

2KOhm

2KOhm

@

@

1

3

1

3

4

R901

R901

1 2

0Ohm

0Ohm

@

@

52

U901

U901

V+

V+

+

+

-

V-

V-

LMV321AS5X_NL

LMV321AS5X_NL

@

@

R905

R905

1 2

0Ohm

0Ohm

@

@

52

U902

U902

V+

V+

+

+

-

V-

V-

LMV321AS5X_NL

LMV321AS5X_NL

@

@

3

M_VREF_MCH <7,8,11>

M_VREFCA_DIMM0

M_VREFCA_DIMM1

12

C902

C902

0.1UF/10V

0.1UF/10V

@

@

4

12

C903

C903

0.1UF/10V

0.1UF/10V

@

@

4

12

R904

R904

0Ohm

0Ohm

@

@

M_VREFDQ_DIMM0

M_VREFDQ_DIMM1

2

1

A A

Title :

Title :

Title :

DIMM_TERM

DIMM_TERM

DIMM_TERM

Zack Kuo

Zack Kuo

F83Vf

F83Vf

F83Vf

Zack Kuo

9 100Thursday, July 16, 2009

9 100Thursday, July 16, 2009

9 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

C

C

C

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

Page 10

5

D D

1 2

C C

B B

+VCCP_GMCH

1 2

1 2

12

C1001

C1001

0.1UF/10V

0.1UF/10V

R1004

R1004

221Ohm

221Ohm

H_SWING

R1005

R1005

75Ohm

75Ohm

1%

1%

+VCCP_GMCH

1 2

1 2

R1001

R1001

16.9Ohm

16.9Ohm

1%

1%

12

C1002

C1002

0.1UF/10V

0.1UF/10V

R1008

R1008

1KOhm

1KOhm

1%

1%

R1007

R1007

2KOhm

2KOhm

1%

1%

4

H_RCOMP

H_CPURST#<3>

H_CPUSLP#<3>

T1001T1001

3

U1001A

H_D#0

H_D#1

H_D#2

H_D#3

H_D#4

H_D#5

H_D#6

H_D#7

H_D#8

H_D#9

H_D#10

H_D#11

H_D#12

H_D#13

H_D#14

H_D#15

H_D#16

H_D#17

H_D#18

H_D#19

H_D#20

H_D#21

H_D#22

H_D#23

H_D#24

H_D#25

H_D#26

H_D#27

H_D#28

H_D#29

H_D#30

H_D#31

H_D#32

H_D#33

H_D#34

H_D#35

H_D#36

H_D#37

H_D#38

H_D#39

H_D#40

H_D#41

H_D#42

H_D#43

H_D#44

H_D#45

H_D#46

H_D#47

H_D#48

H_D#49

H_D#50

H_D#51

H_D#52

H_D#53

H_D#54

H_D#55

H_D#56

H_D#57

H_D#58

H_D#59

H_D#60

H_D#61

H_D#62

H_D#63

H_SWING

H_RCOMP

1

HVREF

U1001A

F2

H_D#_0

G8

H_D#_1

F8

H_D#_2

E6

H_D#_3

G2

H_D#_4

H6

H_D#_5

H2

H_D#_6

F6

H_D#_7

D4

H_D#_8

H3

H_D#_9

M9

H_D#_10

M11

H_D#_11

J1

H_D#_12

J2

H_D#_13

N12

H_D#_14

J6

H_D#_15

P2

H_D#_16

L2

H_D#_17

R2

H_D#_18

N9

H_D#_19

L6

H_D#_20

M5

H_D#_21

J3

H_D#_22

N2

H_D#_23

R1

H_D#_24

N5

H_D#_25

N6

H_D#_26

P13

H_D#_27

N8

H_D#_28

L7

H_D#_29

N10

H_D#_30

M3

H_D#_31

Y3

H_D#_32

AD14

H_D#_33

Y6

H_D#_34

Y10

H_D#_35

Y12

H_D#_36

Y14

H_D#_37

Y7

H_D#_38

W2

H_D#_39

AA8

H_D#_40

Y9

H_D#_41

AA13

H_D#_42

AA9

H_D#_43

AA11

H_D#_44

AD11

H_D#_45

AD10

H_D#_46

AD13

H_D#_47

AE12

H_D#_48

AE9

H_D#_49

AA2

H_D#_50

AD8

H_D#_51

AA3

H_D#_52

AD3

H_D#_53

AD7

H_D#_54

AE14

H_D#_55

AF3

H_D#_56

AC1

H_D#_57

AE3

H_D#_58

AC3

H_D#_59

AE11

H_D#_60

AE8

H_D#_61

AG2

H_D#_62

AD6

H_D#_63

C5

H_SWING

E3

H_RCOMP

C12

H_CPURST#

E11

H_CPUSLP#

A11

H_AVREF

B11

H_DVREF

CANTIGA_CHIPSET

CANTIGA_CHIPSET

HOST

HOST

H_A#_3

H_A#_4

H_A#_5

H_A#_6

H_A#_7

H_A#_8

H_A#_9

H_A#_10

H_A#_11

H_A#_12

H_A#_13

H_A#_14

H_A#_15

H_A#_16

H_A#_17

H_A#_18

H_A#_19

H_A#_20

H_A#_21

H_A#_22

H_A#_23

H_A#_24

H_A#_25

H_A#_26

H_A#_27

H_A#_28

H_A#_29

H_A#_30

H_A#_31

H_A#_32

H_A#_33

H_A#_34

H_A#_35

H_ADS#

H_ADSTB#_0

H_ADSTB#_1

H_BNR#

H_BPRI#

H_BREQ#

H_DEFER#

H_DBSY#

HPLL_CLK

HPLL_CLK#

H_DPWR#

H_DRDY#

H_HIT#

H_HITM#

H_LOCK#

H_TRDY#

H_DINV#_0

H_DINV#_1

H_DINV#_2

H_DINV#_3

H_DSTBN#_0

H_DSTBN#_1

H_DSTBN#_2

H_DSTBN#_3

H_DSTBP#_0

H_DSTBP#_1

H_DSTBP#_2

H_DSTBP#_3

H_REQ#_0

H_REQ#_1

H_REQ#_2

H_REQ#_3

H_REQ#_4

H_RS#_0

H_RS#_1

H_RS#_2

A14

C15

F16

H13

C18

M16

J13

P16

R16

N17

M13

E17

P17

F17

G20

B19

J16

E20

H16

J20

L17

A17

B17

L16

C21

J17

H20

B18

K17

B20

F21

K21

L20

H12

B16

G17

A9

F11

G12

E9

B10

AH7

AH6

J11

F9

H9

E12

H11

C9

J8

L3

Y13

Y1

L10

M7

AA5

AE6

L9

M8

AA6

AE5

B15

K13

F13

B13

B14

B6

F12

C8

H_A#3

H_A#4

H_A#5

H_A#6

H_A#7

H_A#8

H_A#9

H_A#10

H_A#11

H_A#12

H_A#13

H_A#14

H_A#15

H_A#16

H_A#17

H_A#18

H_A#19

H_A#20

H_A#21

H_A#22

H_A#23

H_A#24

H_A#25

H_A#26

H_A#27

H_A#28

H_A#29

H_A#30

H_A#31

H_A#32

H_A#33

H_A#34

H_A#35

H_ADS# <3>

H_ADSTB#0 <3>

H_ADSTB#1 <3>

H_BNR# <3>

H_BPRI# <3>

H_BR0# <3>

H_DEFER# <3>

H_DBSY# <3>

CLK_MCH_BCLK <29>

CLK_MCH_BCLK# <29>

H_DPWR# <3>

H_DRDY# <3>

H_HIT# <3>

H_HITM# <3>

H_LOCK# <3>

H_TRDY# <3>

H_DINV#0 <3>

H_DINV#1 <3>

H_DINV#2 <3>

H_DINV#3 <3>

H_DSTBN#0 <3>

H_DSTBN#1 <3>

H_DSTBN#2 <3>

H_DSTBN#3 <3>

H_DSTBP#0 <3>

H_DSTBP#1 <3>

H_DSTBP#2 <3>

H_DSTBP#3 <3>

H_REQ#0

H_REQ#1

H_REQ#2

H_REQ#3

H_REQ#4

H_RS#0 <3>

H_RS#1 <3>

H_RS#2 <3>

2

H_A#[35:3]<3>

H_REQ#[4:0]<3>

H_D#[63:0]<3>

H_A#[35:3]

H_REQ#[4:0]

H_D#[63:0]

1

Cap 0.1uF within 100 mils from GMCH

A A

Title :

Title :

Title :

Cantiga -- CPU (1)

Cantiga -- CPU (1)

Cantiga -- CPU (1)

Zack Kuo

Zack Kuo

Engineer:

Engineer:

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

P/N

P/N

P/N

Date: Sheet

Date: Sheet

5

4

3

2

Date: Sheet

Engineer:

F83Vf

F83Vf

F83Vf

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

Zack Kuo

Rev

Rev

Rev

1.1

1.1

10 100Thursday, July 16, 2009

10 100Thursday, July 16, 2009

1

10 100Thursday, July 16, 2009

1.1

of

of

of

Page 11

5

T1105T1105

T1116T1116

T1118T1118

D D

+1.5V

R1105

R1105

1KOhm

1KOhm

1%

1%

1 2

SM_RCOMP_VOH

12

C1101

C1101

2.2UF/6.3V

2.2UF/6.3V

R1106

R1106

3.01KOHM

3.01KOHM

1%

1%

1 2

SM_RCOMP_VOL

12

C1103

C1103

R1107

R1107

2.2UF/6.3V

2.2UF/6.3V

1KOhm

1KOhm

1%

1%

1 2

C C

MCH_BSEL0<29>

MCH_BSEL1<29>

MCH_BSEL2<29>

MCH_CFG_5<15>

MCH_CFG_6<15>

MCH_CFG_7<15>

MCH_CFG_9<15>

MCH_CFG_10<15>

MCH_CFG_12<15>

MCH_CFG_13<15>

MCH_CFG_16<15>

MCH_CFG_19<15>

B B

PM_SYNC#<22>

H_DPRSTP#<3,20,80>

PM_EXTTS#0<7>

PM_EXTTS#1<8>

PM_PWROK<22,30>

H_THRMTRIP#<3,5,20,32>

PM_DPRSLPVR<22,80>

+3VS

R1103 10KOhmR1103 10KOhm

R1104 10KOhmR1104 10KOhm

A A

MCH_CFG_20<15>

SL1102 R0402SL1102 R0402

PM_EXTTS#0

PM_EXTTS#1

SL1103 R0402SL1103 R0402

BUF_PLT_RST#<5,21,30,33,41,53,70>

SL1104 R0402SL1104 R0402

PM_EXTTS#0

12

PM_EXTTS#1

12

5

T1119T1119

SL1101

SL1101

1 2

R0402

R0402

12

C1102

C1102

0.01UF/16V

0.01UF/16V

12

C1104

C1104

0.01UF/16V

0.01UF/16V

T1102T1102

T1101T1101

T1115T1115

T1107T1107

T1103T1103

T1108T1108

T1104T1104

T1109T1109

1 2

1 2

1 2

RX1101 100OhmRX1101 100Ohm

1 2

M36

N36

R33

T33

AH9

AH10

AH12

AH13

K12

AL34

1

AK34

1

AN35

1

AM35

1

T24

B31

AJ6

M1

AY21

A47

BG23

BF23

BH18

BF18

T25

R25

P25

P20

1

P24

1

C25

N24

M24

E21

1

C23

C24

N21

1

P21

T21

R20

1

M20

1

L21

H21

1

P29

1

R28

T28

R29

B7

N33

P32

AT40

AT11

T20

R32

BG48

BF48

BD48

BC48

BH47

BG47

BE47

BH46

BF46

BG45

BH44

BH43

BH6

BH5

BG4

BH3

BF3

BH2

BG2

BE2

BG1

BF1

BD1

BC1

F1

CANTIGA_CHIPSET

CANTIGA_CHIPSET

U1001B

U1001B

RSVD1

RSVD2

RSVD3

RSVD4

RSVD5

RSVD6

RSVD7

RSVD8

RSVD9

RSVD10

RSVD11

RSVD12

RSVD13

RSVD14

RSVD15

RSVD16

RSVD17

RSVD20

RSVD21

RSVD22

RSVD23

RSVD24

RSVD25

CFG_0

CFG_1

CFG_2

CFG_3

CFG_4

CFG_5

CFG_6

CFG_7

CFG_8

CFG_9

CFG_10

CFG_11

CFG_12

CFG_13

CFG_14

CFG_15

CFG_16

CFG_17

CFG_18

CFG_19

CFG_20

PM_SYNC#

PM_DPRSTP#

PM_EXT_TS#_0

PM_EXT_TS#_1

PWROK

RSTIN#

THERMTRIP#

DPRSLPVR

NC_1

NC_2

NC_3

NC_4

NC_5

NC_6

NC_7

NC_8

NC_9

NC_10

NC_11

NC_12

NC_13

NC_14

NC_15

NC_16

NC_17

NC_18

NC_19

NC_20

NC_21

NC_22

NC_23

NC_24

NC_25

4

AP24

SA_CK_0

AT21

SA_CK_1

AV24

SB_CK_0

AU20

SB_CK_1

AR24

SA_CK#_0

AR21

SA_CK#_1

AU24

SB_CK#_0

AV20

SB_CK#_1

BC28

SA_CKE_0

AY28

SA_CKE_1

AY36

SB_CKE_0

RSVD

RSVD

SM_RCOMP

SM_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

SM_PWROK

DDR CONTROL/COMPENSATION

DDR CONTROL/COMPENSATION

SM_DRAMRST#

DPLL_REF_CLK

DPLL_REF_CLK#

DPLL_REF_SSCLK

DPLL_REF_SSCLK#

CLK

CLK

CFG

CFG

DMI

DMI

PM

NC

NC

PM

GFX_VR_EN

GRAPHICS VID

GRAPHICS VID

MEHDA

MEHDA

DDPC_CTRLCLK

DDPC_CTRLDATA

SDVO_CTRLCLK

SDVO_CTRLDATA

MISC

MISC

4

SB_CKE_1

SA_CS#_0

SA_CS#_1

SB_CS#_0

SB_CS#_1

SA_ODT_0

SA_ODT_1

SB_ODT_0

SB_ODT_1

SM_VREF

SM_REXT

PEG_CLK

PEG_CLK#

DMI_RXN_0

DMI_RXN_1

DMI_RXN_2

DMI_RXN_3

DMI_RXP_0

DMI_RXP_1

DMI_RXP_2

DMI_RXP_3

DMI_TXN_0

DMI_TXN_1

DMI_TXN_2

DMI_TXN_3

DMI_TXP_0

DMI_TXP_1

DMI_TXP_2

DMI_TXP_3

GFX_VID_0

GFX_VID_1

GFX_VID_2

GFX_VID_3

GFX_VID_4

CL_CLK

CL_DATA

CL_PWROK

CL_RST#

CL_VREF

CLKREQ#

ICH_SYNC#

TSATN#

HDA_BCLK

HDA_RST#

HDA_SDI

HDA_SDO

HDA_SYNC

BB36

BA17

AY16

AV16

AR13

BD17

AY17

BF15

AY13

BG22

BH21

BF28

BH28

AV42

AR36

BF17

BC36

B38

A38

E41

F41

F43

E43

AE41

AE37

AE47

AH39

AE40

AE38

AE48

AH40

AE35

AE43

AE46

AH42

AD35

AE44

AF46

AH43

B33

B32

G33

F33

E33

C34

AH37

AH36

AN36

AJ35

AH34

N28

M28

G36

E36

K36

H36

B12

B28

B30

B29

C29

A28

M_CLK_DDR0 <7>

M_CLK_DDR1 <7>

M_CLK_DDR2 <8>

M_CLK_DDR3 <8>

M_CLK_DDR0# <7>

M_CLK_DDR1# <7>

M_CLK_DDR2# <8>

M_CLK_DDR3# <8>

M_CKE0 <7>

M_CKE1 <7>

M_CKE2 <8>

M_CKE3 <8>

M_CS#0 <7>

M_CS#1 <7>

M_CS#2 <8>

M_CS#3 <8>

M_ODT0 <7>

M_ODT1 <7>

M_ODT2 <8>

M_ODT3 <8>

M_RCOMP

M_RCOMP#

SM_RCOMP_VOH

SM_RCOMP_VOL

1 2

R1121 499Ohm 1%R1121 499Ohm 1%

CLK_MCH_3GPLL <29>

CLK_MCH_3GPLL# <29>

DMI_TXN0 <21>

DMI_TXN1 <21>

DMI_TXN2 <21>

DMI_TXN3 <21>

DMI_TXP0 <21>

DMI_TXP1 <21>

DMI_TXP2 <21>

DMI_TXP3 <21>

DMI_RXN0 <21>

DMI_RXN1 <21>

DMI_RXN2 <21>

DMI_RXN3 <21>

DMI_RXP0 <21>

DMI_RXP1 <21>

DMI_RXP2 <21>

DMI_RXP3 <21>

CL_CLK0 <22>

CL_DATA0 <22>

CL_RST#0 <22>

T1120T1120

1

MCH_ICH_SYNC# <22>

T1117T1117

1

R1112 80.6Ohm 1%R1112 80.6Ohm 1%

1 2

R1117 80.6Ohm 1%R1117 80.6Ohm 1%

1 2

SL1105 R0402SL1105 R0402

1 2

12

C1105

C1105

0.01UF/16V

0.01UF/16V

@

@

PM_PWROK

CL_VREF

12

C1106

C1106

0.1UF/10V

0.1UF/10V

+VCCP_GMCH

R1126 56OHMR1126 56OHM

12

3

+1.5V

M_DRAMRST# <7,8>

+VCCP_GMCH

1 2

1 2

3

+0.75V

M_VREF_MCH <7,8,9>

DDR_PWRGD <83,92>

R1108

R1108

1KOhm

1KOhm

1%

1%

R1102

R1102

499Ohm

499Ohm

1%

1%

U1001C

U1001C

L32

L_BKLT_CTRL

G32

L_BKLT_EN

M32

L_CTRL_CLK

M33

L_CTRL_DATA

K33

L_DDC_CLK

J33

L_DDC_DATA

M29

L_VDD_EN

C44

LVDS_IBG

B43

LVDS_VBG

E37

LVDS_VREFH

E38

LVDS_VREFL

C41

LVDSA_CLK#

C40

LVDSA_CLK

B37

LVDSB_CLK#

A37

LVDSB_CLK

H47

LVDSA_DATA#_0

E46

LVDSA_DATA#_1

G40

LVDSA_DATA#_2

A40

LVDSA_DATA#_3

H48

LVDSA_DATA_0

D45

LVDSA_DATA_1

F40

LVDSA_DATA_2

B40

LVDSA_DATA_3

A41

LVDSB_DATA#_0

H38

LVDSB_DATA#_1

G37

LVDSB_DATA#_2

J37

LVDSB_DATA#_3

B42

LVDSB_DATA_0

G38

LVDSB_DATA_1

F37

LVDSB_DATA_2

K37

LVDSB_DATA_3

F25

TVA_DAC

H25

TVB_DAC

K25

TVC_DAC

H24

TV_RTN

C31

TV_DCONSEL_0

E32

TV_DCONSEL_1

E28

CRT_BLUE

G28

CRT_GREEN

J28

CRT_RED

G29

CRT_IRTN

H32

CRT_DDC_CLK

J32

CRT_DDC_DATA

J29

CRT_HSYNC

E29

CRT_TVO_IREF

L29

CRT_VSYNC

CANTIGA_CHIPSET

CANTIGA_CHIPSET

2

PEGCOMP

PEG_COMPI

PEG_COMPO

PEG_RX#_0

PEG_RX#_1

PEG_RX#_2

PEG_RX#_3

PEG_RX#_4

PEG_RX#_5

PEG_RX#_6

LVDS

LVDS

TV

TV

VGA

VGA

2

PEG_RX#_7

PEG_RX#_8

PEG_RX#_9

PEG_RX#_10

PEG_RX#_11

PEG_RX#_12

PEG_RX#_13

PEG_RX#_14

PEG_RX#_15

PEG_RX_10

PEG_RX_11

PEG_RX_12

PEG_RX_13

PEG_RX_14

PEG_RX_15

PEG_TX#_0

PEG_TX#_1

PEG_TX#_2

PEG_TX#_3

PEG_TX#_4

PEG_TX#_5

PEG_TX#_6

PEG_TX#_7

PEG_TX#_8

PEG_TX#_9

PEG_TX#_10

PEG_TX#_11

PEG_TX#_12

PCI-EXPRESS GRAPHICS

PCI-EXPRESS GRAPHICS

PEG_TX#_13

PEG_TX#_14

PEG_TX#_15

PEG_TX_10

PEG_TX_11

PEG_TX_12

PEG_TX_13

PEG_TX_14

PEG_TX_15

T37

T36

PCIENB_RXN0

H44

PCIENB_RXN1

J46

PCIENB_RXN2

L44

PCIENB_RXN3

L40

PCIENB_RXN4

N41

PCIENB_RXN5

P48

PCIENB_RXN6

N44

PCIENB_RXN7

T43

PCIENB_RXN8

U43

PCIENB_RXN9

Y43

PCIENB_RXN10

Y48

PCIENB_RXN11

Y36

PCIENB_RXN12

AA43

PCIENB_RXN13

AD37

PCIENB_RXN14

AC47

PCIENB_RXN15

AD39

PCIENB_RXP0

H43

PEG_RX_0

PEG_RX_1

PEG_RX_2

PEG_RX_3

PEG_RX_4

PEG_RX_5

PEG_RX_6

PEG_RX_7

PEG_RX_8

PEG_RX_9

PEG_TX_0

PEG_TX_1

PEG_TX_2

PEG_TX_3

PEG_TX_4

PEG_TX_5

PEG_TX_6

PEG_TX_7

PEG_TX_8

PEG_TX_9

PCIENB_RXP1

J44

PCIENB_RXP2

L43

PCIENB_RXP3

L41

PCIENB_RXP4

N40

PCIENB_RXP5

P47

PCIENB_RXP6

N43

PCIENB_RXP7

T42

PCIENB_RXP8

U42

PCIENB_RXP9

Y42

PCIENB_RXP10

W47

PCIENB_RXP11

Y37

PCIENB_RXP12

AA42

PCIENB_RXP13

AD36

PCIENB_RXP14

AC48

PCIENB_RXP15

AD40

PCIENB_TXN0

J41

PCIENB_TXN1

M46

PCIENB_TXN2

M47

PCIENB_TXN3

M40

PCIENB_TXN4

M42

PCIENB_TXN5

R48

PCIENB_TXN6

N38

PCIENB_TXN7

T40

PCIENB_TXN8

U37

PCIENB_TXN9

U40

PCIENB_TXN10

Y40

PCIENB_TXN11

AA46

PCIENB_TXN12

AA37

PCIENB_TXN13

AA40

PCIENB_TXN14

AD43

PCIENB_TXN15

AC46

PCIENB_TXP0

J42

PCIENB_TXP1

L46

PCIENB_TXP2

M48

PCIENB_TXP3

M39

PCIENB_TXP4

M43

PCIENB_TXP5

R47

PCIENB_TXP6

N37

PCIENB_TXP7

T39

PCIENB_TXP8

U36

PCIENB_TXP9

U39

PCIENB_TXP10

Y39

PCIENB_TXP11

Y46

PCIENB_TXP12

AA36

PCIENB_TXP13

AA39

PCIENB_TXP14

AD42

PCIENB_TXP15

AD46

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

PEGATRON COMPUTER INC

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

P/N

P/N

P/N

Date: Sheet

Date: Sheet

Date: Sheet

1

+VCC_PEG

1%

1%

1 2

R1101 49.9Ohm

R1101 49.9Ohm

PCIENB_RXN[15:0] <70>

PCIENB_RXP[15:0] <70>

CX1138 0.1UF/10VCX1138 0.1UF/10V

1 2

CX1121 0.1UF/10VCX1121 0.1UF/10V

1 2

CX1148 0.1UF/10VCX1148 0.1UF/10V

1 2

CX1134 0.1UF/10VCX1134 0.1UF/10V

1 2

CX1147 0.1UF/10VCX1147 0.1UF/10V

1 2

CX1143 0.1UF/10VCX1143 0.1UF/10V

1 2

CX1133 0.1UF/10VCX1133 0.1UF/10V

1 2

CX1144 0.1UF/10VCX1144 0.1UF/10V

1 2

CX1137 0.1UF/10VCX1137 0.1UF/10V

1 2

CX1117 0.1UF/10VCX1117 0.1UF/10V

1 2

CX1118 0.1UF/10VCX1118 0.1UF/10V

1 2

CX1120 0.1UF/10VCX1120 0.1UF/10V

1 2

CX1122 0.1UF/10VCX1122 0.1UF/10V

1 2

CX1146 0.1UF/10VCX1146 0.1UF/10V

1 2

CX1140 0.1UF/10VCX1140 0.1UF/10V

1 2

CX1119 0.1UF/10VCX1119 0.1UF/10V

1 2

CX1127 0.1UF/10VCX1127 0.1UF/10V

1 2

CX1145 0.1UF/10VCX1145 0.1UF/10V

1 2

CX1128 0.1UF/10VCX1128 0.1UF/10V

1 2

CX1142 0.1UF/10VCX1142 0.1UF/10V

1 2

CX1139 0.1UF/10VCX1139 0.1UF/10V

1 2

CX1125 0.1UF/10VCX1125 0.1UF/10V

1 2

CX1123 0.1UF/10VCX1123 0.1UF/10V

1 2

CX1124 0.1UF/10VCX1124 0.1UF/10V

1 2

CX1135 0.1UF/10VCX1135 0.1UF/10V

1 2

CX1126 0.1UF/10VCX1126 0.1UF/10V

1 2

CX1141 0.1UF/10VCX1141 0.1UF/10V

1 2

CX1131 0.1UF/10VCX1131 0.1UF/10V

1 2

CX1129 0.1UF/10VCX1129 0.1UF/10V

1 2

CX1130 0.1UF/10VCX1130 0.1UF/10V

1 2

CX1136 0.1UF/10VCX1136 0.1UF/10V

1 2

CX1132 0.1UF/10VCX1132 0.1UF/10V

1 2

PCIEG_RXN[15:0] <70>

PCIEG_RXP[15:0] <70>

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

F83Vf

F83Vf

F83Vf

<OrgAddr2>

<OrgAddr2>

<OrgAddr2>

1

PCIEG_RXN0

PCIEG_RXN1

PCIEG_RXN2

PCIEG_RXN3

PCIEG_RXN4

PCIEG_RXN5

PCIEG_RXN6

PCIEG_RXN7

PCIEG_RXN8

PCIEG_RXN9

PCIEG_RXN10

PCIEG_RXN11

PCIEG_RXN12

PCIEG_RXN13

PCIEG_RXN14

PCIEG_RXN15

PCIEG_RXP0

PCIEG_RXP1

PCIEG_RXP2

PCIEG_RXP3

PCIEG_RXP4

PCIEG_RXP5

PCIEG_RXP6

PCIEG_RXP7

PCIEG_RXP8

PCIEG_RXP9

PCIEG_RXP10

PCIEG_RXP11

PCIEG_RXP12

PCIEG_RXP13

PCIEG_RXP14

PCIEG_RXP15

Cantiga-DDR2/PEG(2)

Cantiga-DDR2/PEG(2)

Cantiga-DDR2/PEG(2)

Zack Kuo

Zack Kuo

Zack Kuo

11 100Thursday, July 16, 2009

11 100Thursday, July 16, 2009

11 100Thursday, July 16, 2009

Rev

Rev

Rev

1.1

1.1

1.1

of

of

of

Page 12

5

D D

M_A_DQ[0:63]<7> M_B_DQ[0:63]<8>

C C

B B

M_A_DQ0

M_A_DQ1

M_A_DQ2

M_A_DQ3

M_A_DQ4

M_A_DQ5

M_A_DQ6

M_A_DQ7

M_A_DQ8

M_A_DQ9

M_A_DQ10

M_A_DQ11

M_A_DQ12

M_A_DQ13

M_A_DQ14

M_A_DQ15

M_A_DQ16

M_A_DQ17

M_A_DQ18

M_A_DQ19

M_A_DQ20

M_A_DQ21

M_A_DQ22

M_A_DQ23

M_A_DQ24

M_A_DQ25

M_A_DQ26

M_A_DQ27

M_A_DQ28

M_A_DQ29

M_A_DQ30

M_A_DQ31

M_A_DQ32

M_A_DQ33

M_A_DQ34

M_A_DQ35

M_A_DQ36

M_A_DQ37

M_A_DQ38

M_A_DQ39

M_A_DQ40

M_A_DQ41

M_A_DQ42

M_A_DQ43

M_A_DQ44

M_A_DQ45

M_A_DQ46

M_A_DQ47

M_A_DQ48