Page 1

5

4

3

2

1

SYSTEM PAGE REF.

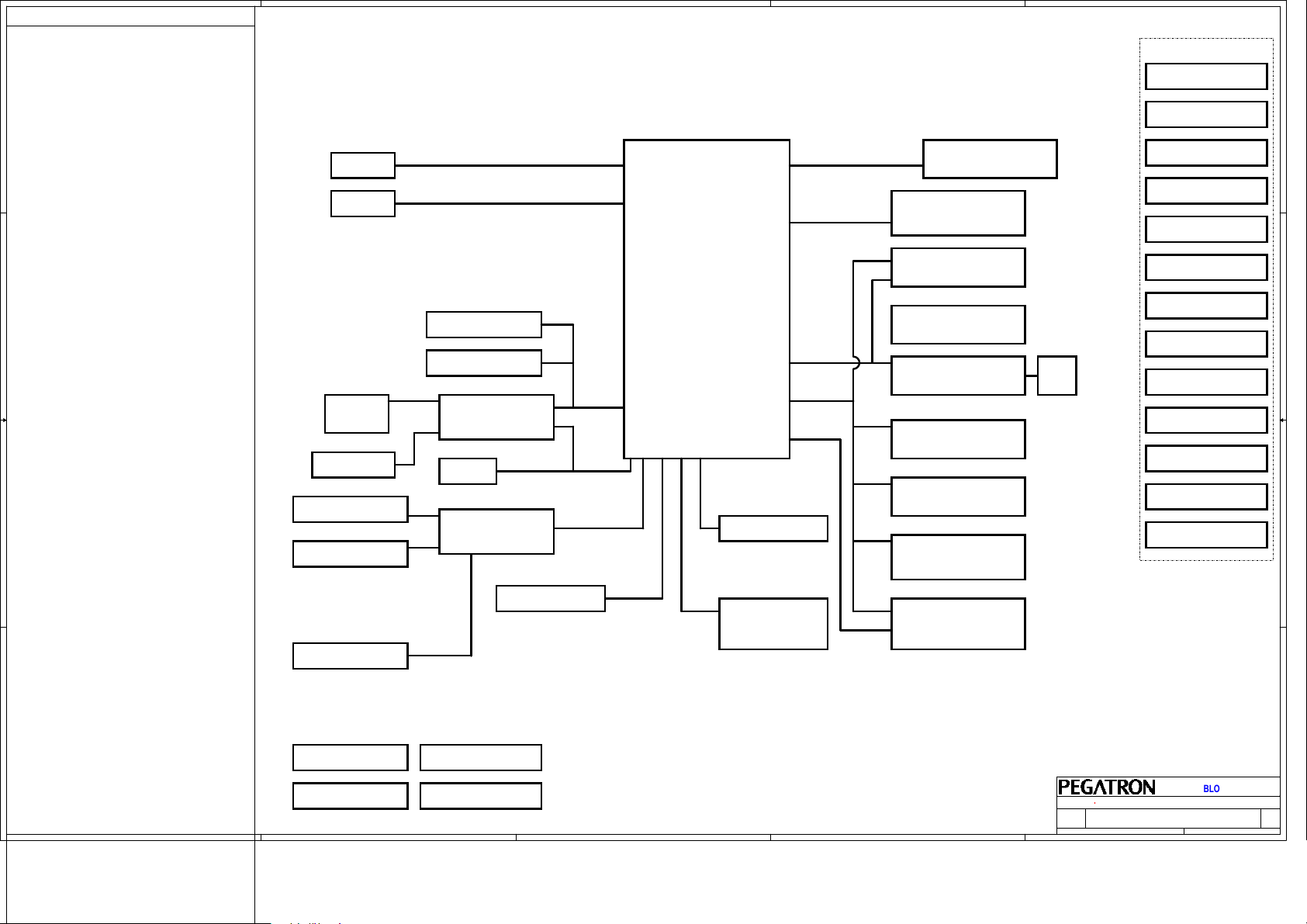

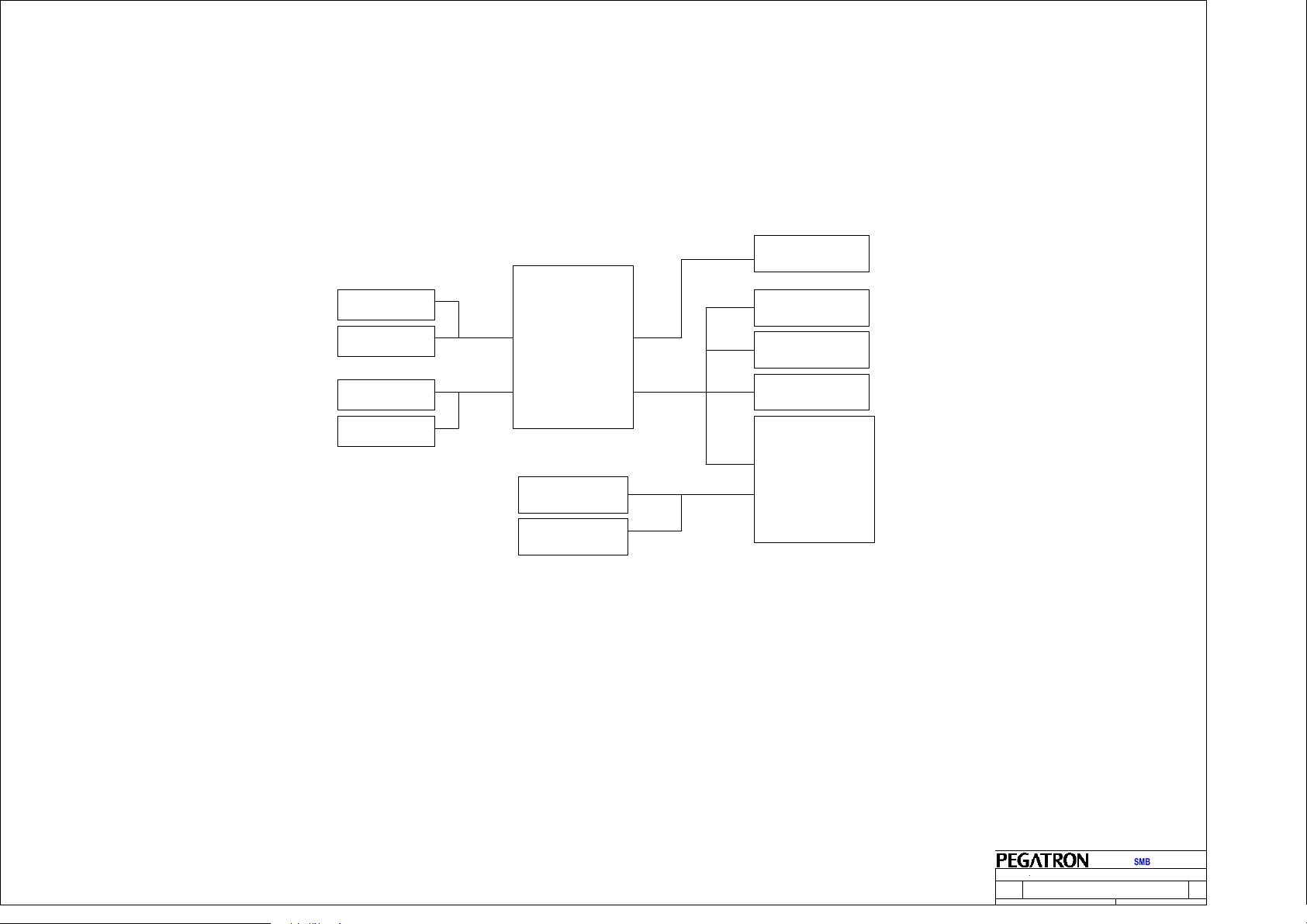

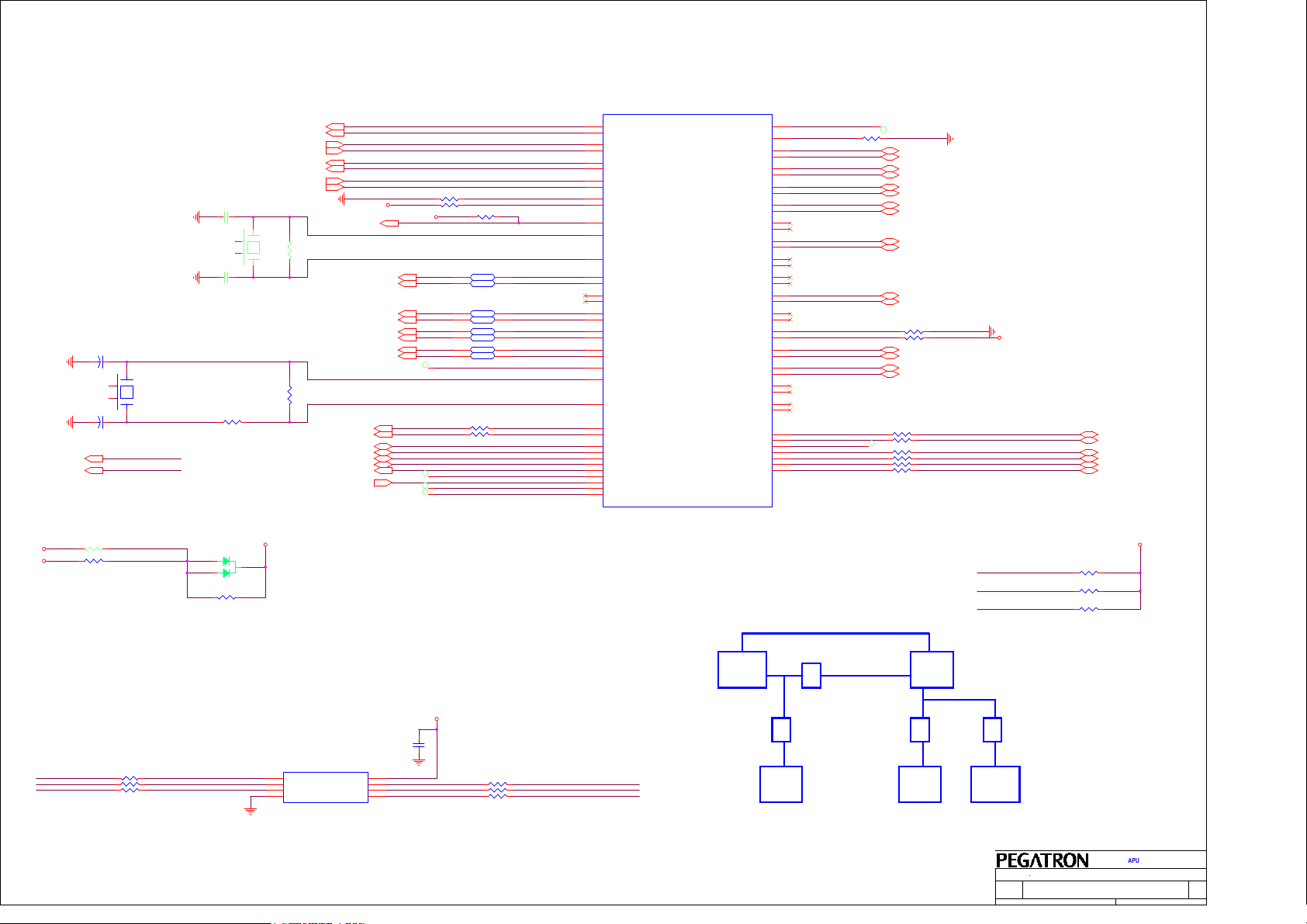

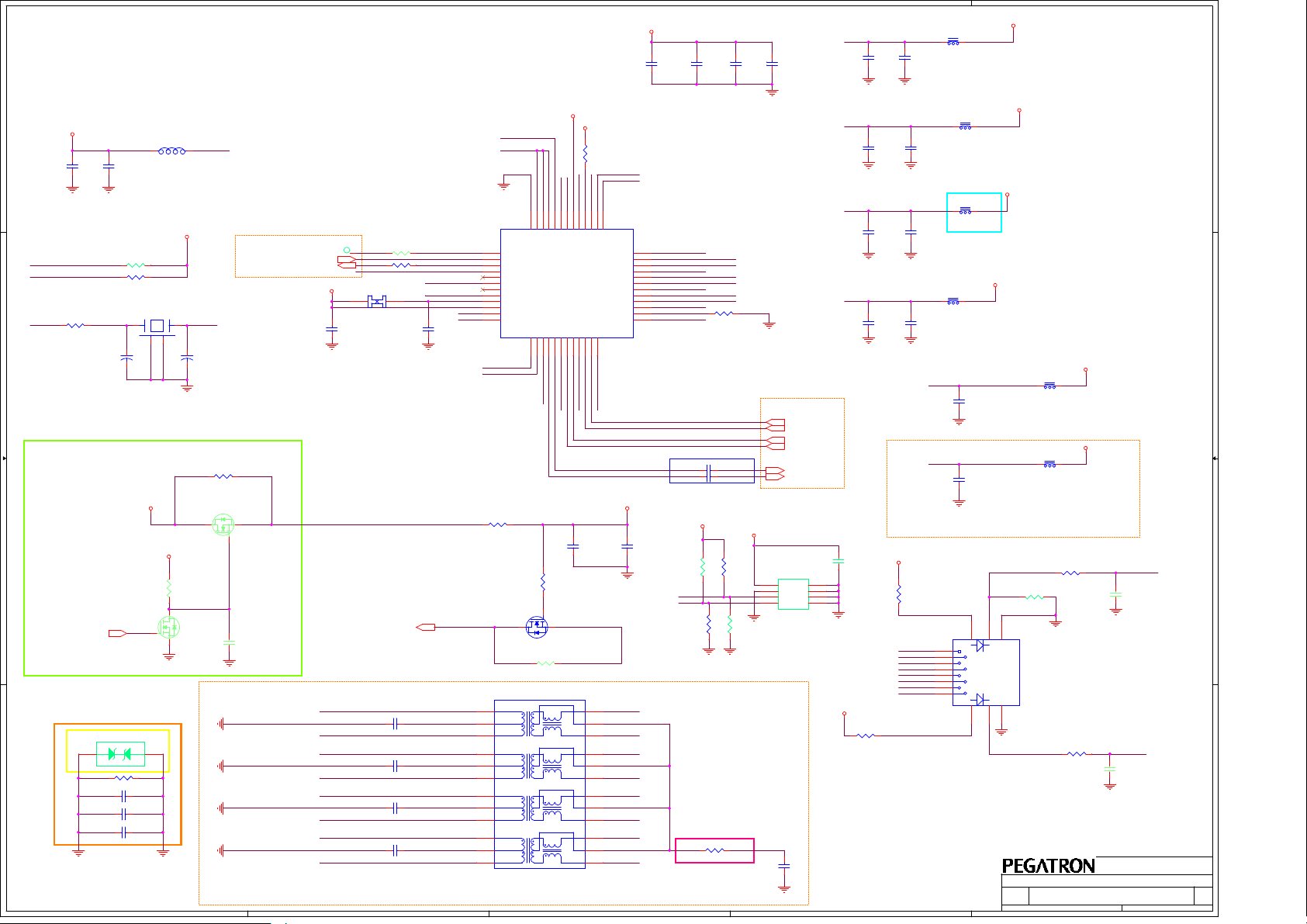

01. Block Diagr am

02. ******

03. POWER DELIV ER CHART

04. POWER SEQUE NCE CHART

05. CLOCK DISTR IBUTION

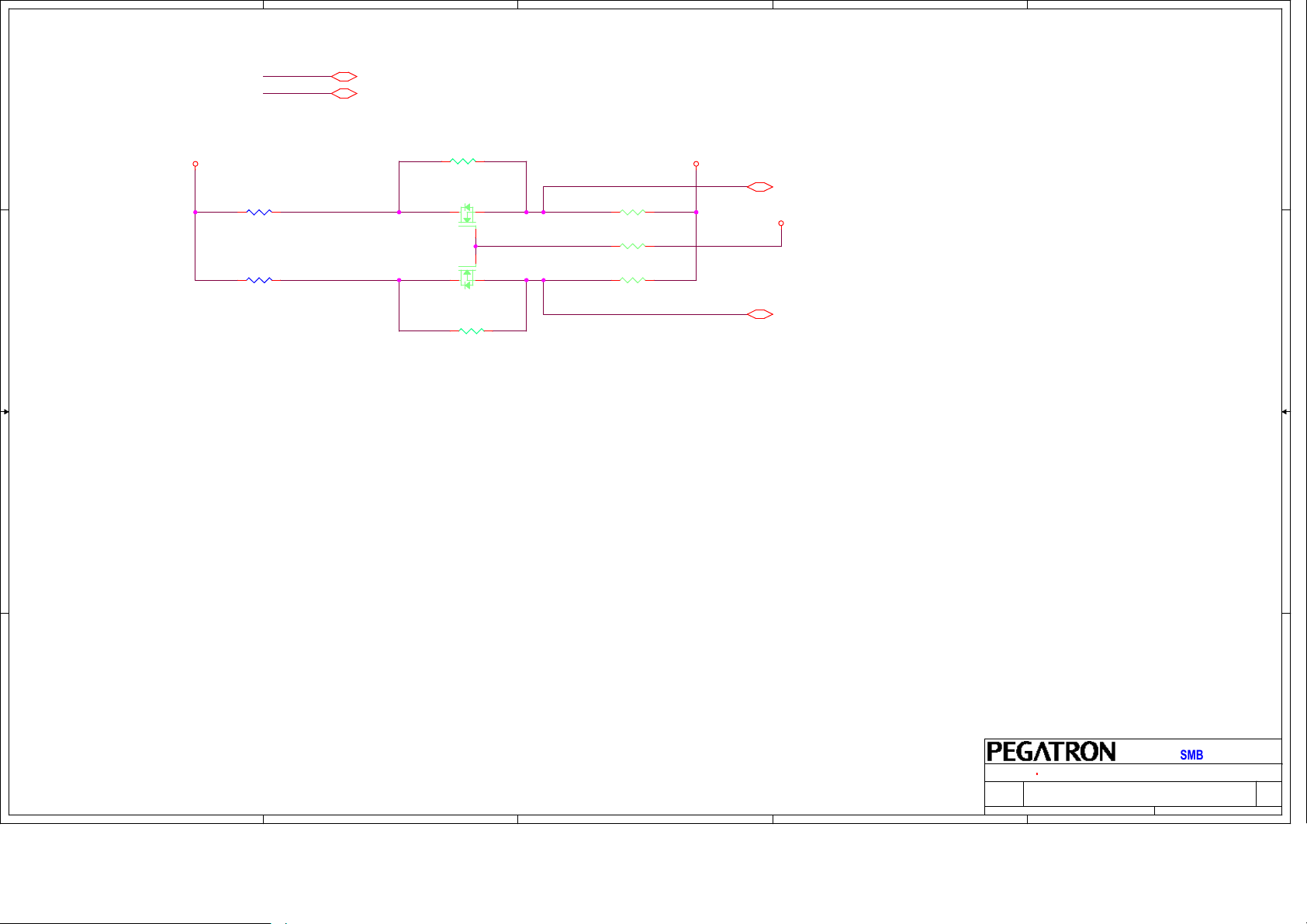

06. SMBUS MAP

07. APU_MEM_&_P CIE_I_F

D D

C C

B B

08. APU_DISPLAY _CLK_MISC

09. APU_GEVENT_ GPIO_SD_AZ

10. APU_SATA_US B_LPC_SPI_C

11. APU_POWER_& _DECOUPLING

12. APU_STRAPS, SOCKET, HS

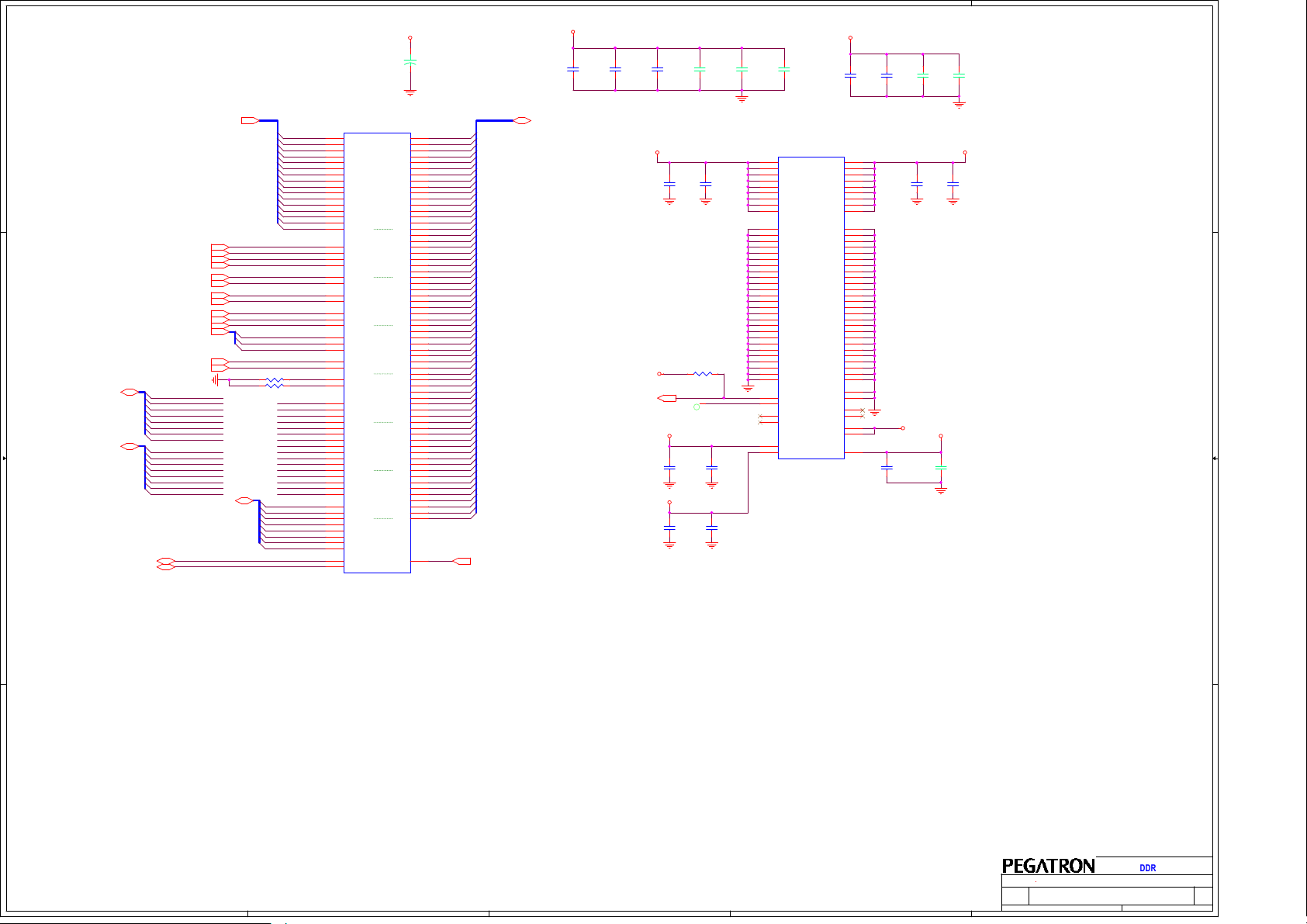

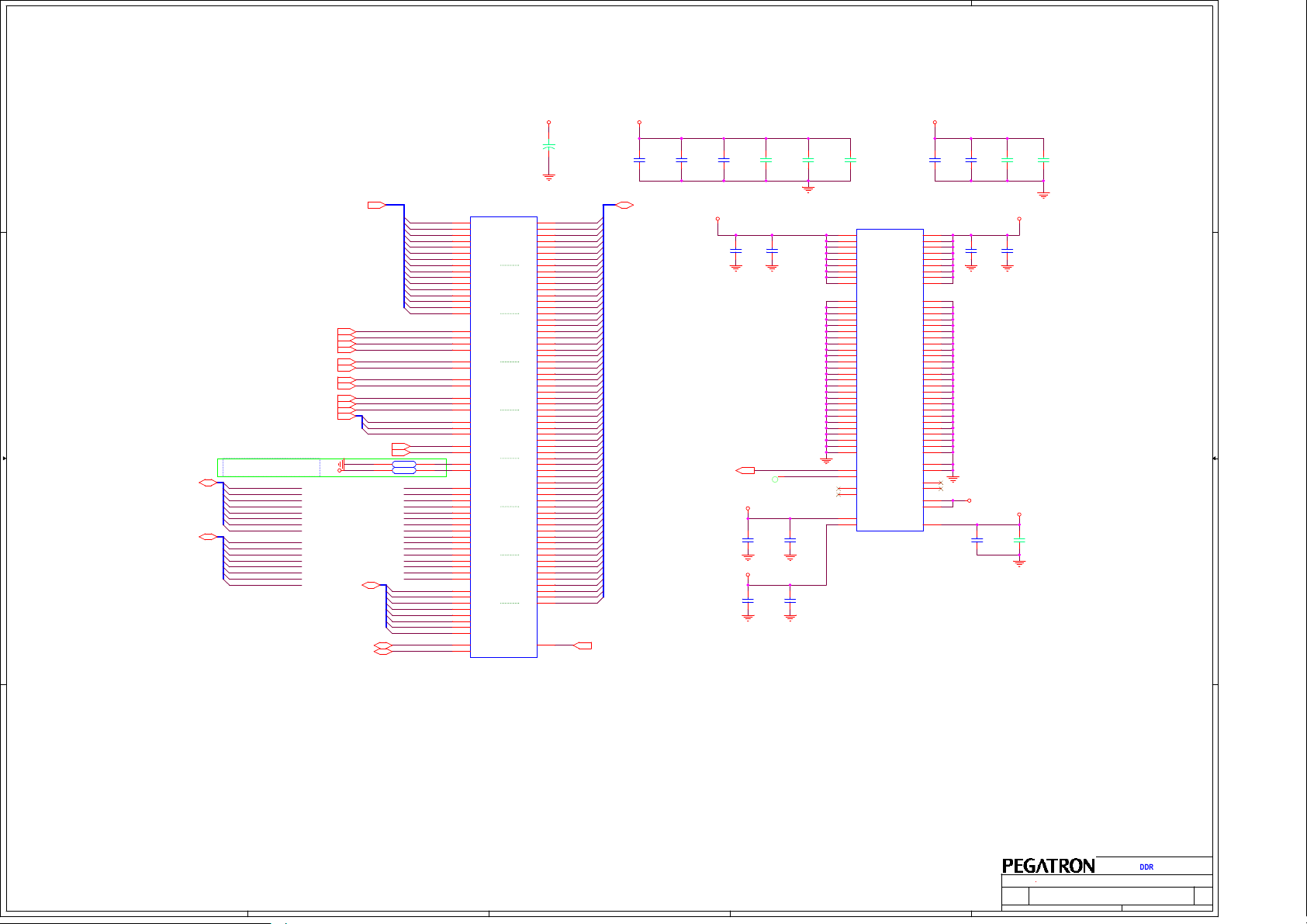

16. DDR3_SO-DIM M0

17. DDR3_SO-DIM M1

18. DDR3_CA/DQ Voltage

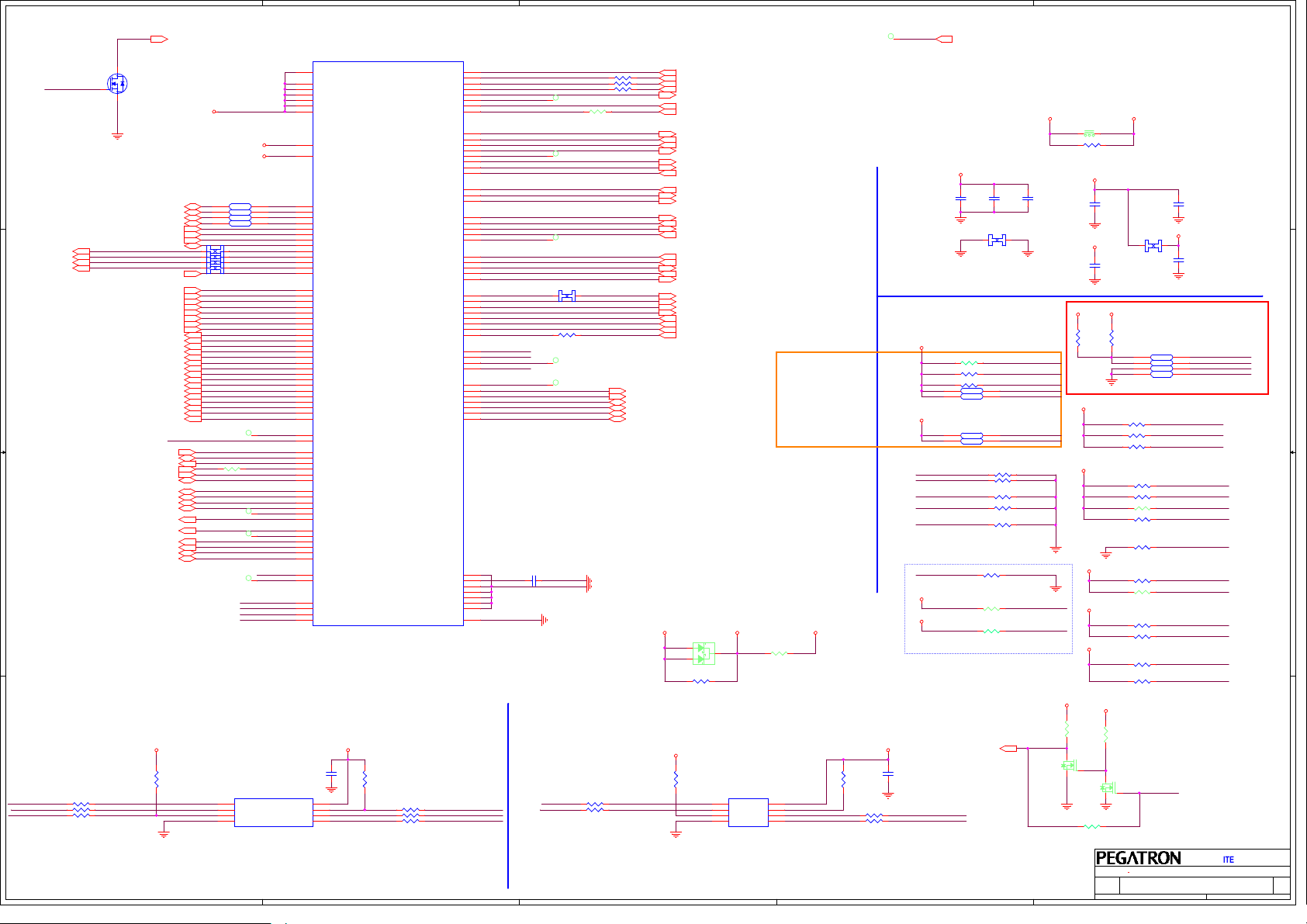

30. EC_IT8528

33. LAN Chip_BC M57780

34. ******

35. ******

36. ******

37. LVDS/eDP CO N

38. RGB_CONN

39. HDMI_CONN

40. Card Reader _RTS5209-GR

41. AUDIO_ALC32 25

42. AUDIO_HP/ M IC JACK

47. RESET CIRCU IT

48. KB/TP CONN

50. FAN/THERMAL SENSOR

55. MINI-PCIE C ARD (WLAN/BT)

60. HDD/ODD

61. USB CONN/ I O/B CONN

63. DC-IN/DISCH ARGE

65. PWR/B CONN/ DEBUG CONN

66. LED/NUT/SCR EW

70. GPU_MARS_PC IE_INTERFACE

71. GPU_MARS_MA IN

72. GPU_MARS_ X TAL

73. GPU_MARS_LV TMDS

74. GPU_MARS_ST RAPS/THERMAL/CT F

75. GPU_MARS_PO WER

76. GPU_MARS_DP _POWER/GND

77. GPU_MARS_ME M_INTERFACE

78. GPU_MARS_DD R3_CH_B

79. GPU_MARS_DD R3_CH_A

80. POWER_VCORE

81. POWER_SYSTE M

82. POWER_+0.95 VSUS

83. POWER_DDR & VTT

84. POWER_+1.8V SUS

85. POWER_+1.5V SUS

86. POWER_+1.5V S

87. POWER_VGA_V DDC

88. POWER_CHARG ER

89. POWER_***** *

90. POWER_DETEC T

91. POWER_LOAD SWITCH

92. POWER_PROTE CT

93. POWER_SIGNA L

94. GPU_MARS_PO WER_SEQUENCE

97. SB_PWR/B

98. SB_TP/B

99. SB_IO/B

CRT

LCD Panel

Touchpad

Keyboard

Page 48

PWM Fan

Speaker

Audio Jack

(IO DB)

RGB

*

eDP

Page 50

Page 38

Page 42

DMIC

*

EG70_KB BLOCK DIAGRAM

DDR3 1333/1600 MHz

DP0

SD

2

AMD FUSION APU

KABINI FT3

TPM

*

Debug Conn.

*

EC

NPCE795L

Page 30

SPI ROM

*

Azalia Codec

ALC3225

Page 41

NFC

LPC

SPI

SATA

Azalia

Page 7~12

SATA

0

HDD

SMB0

*

1

ODD

PCIEx1

USB 2.0

USB 3.0

Page 60

Page 60

0

1

3

8

0

DDR3 SO-DIMM

CardReader

MiniCard

WLAN + BT

1

CARD READER

RTS5209-GR

3

10/100/1000 LAN

BCM57780

USB 2.0

(M/B)

USB 2.0

(S/B)

CMOS Camera

internal MIC

USB3.0

*

Page 55

Page 40

Page 33

*

*

*

*

Page 16, 17

RJ45

*

Power

VCORE

Page 80

SYSTEM

Page 81

+0.95VSUS

Page 82

DDR3 & VTT

Page 83

+1.8VSUS

Page 84

+1.5VSUS

Page 85

VGA_VDDC

Page 87

CHARGER

Page 88

DETECT

Page 90

LOAD SWITCH

Page 91

PROTECT

Page 92

SIGNAL

Page 93

FLOWCHART

Page 94

A A

DISCHARGE

Page 63

RESET CIRCUIT

Page 47

5

DC & BATT. Conn.

SCREW HOLES

4

Page 63

Page 66

Title :

Title :

Title :

BLOCK DIAGRAM

BLOCK DIAGRAM

BLOCK DIAGRAM

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

1

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

3

2

Date: Sheet of

Mike_Chiu

Mike_Chiu

Mike_Chiu

1 99Monday, March 25, 2013

1 99Monday, March 25, 2013

1 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 2

5

D D

C C

4

3

2

1

B B

A A

Title :

Title :

Title :

******

******

******

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

1

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

5

4

3

2

Date: Sheet of

Mike_Chiu

2 99Monday, March 25, 2013

2 99Monday, March 25, 2013

2 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 3

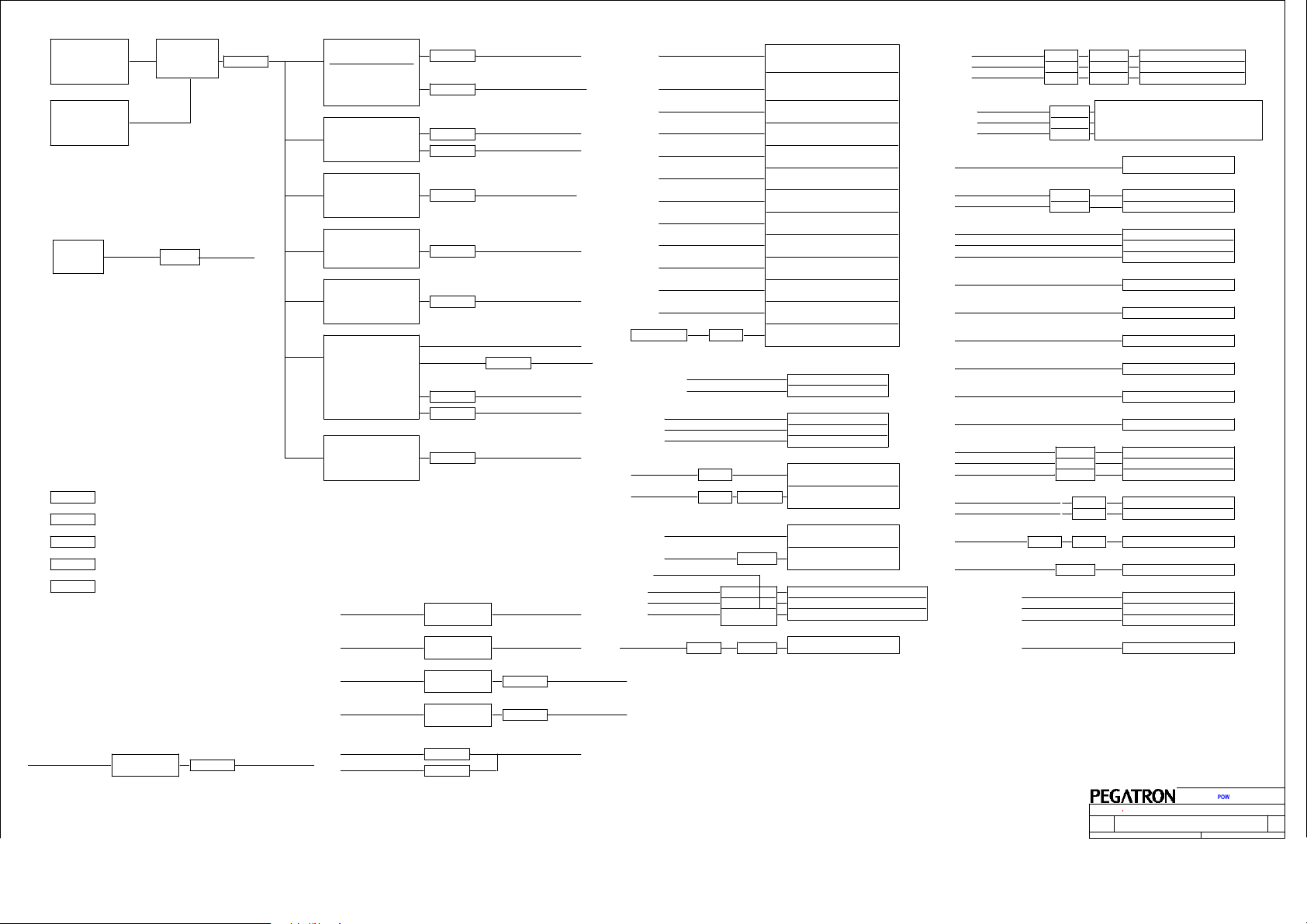

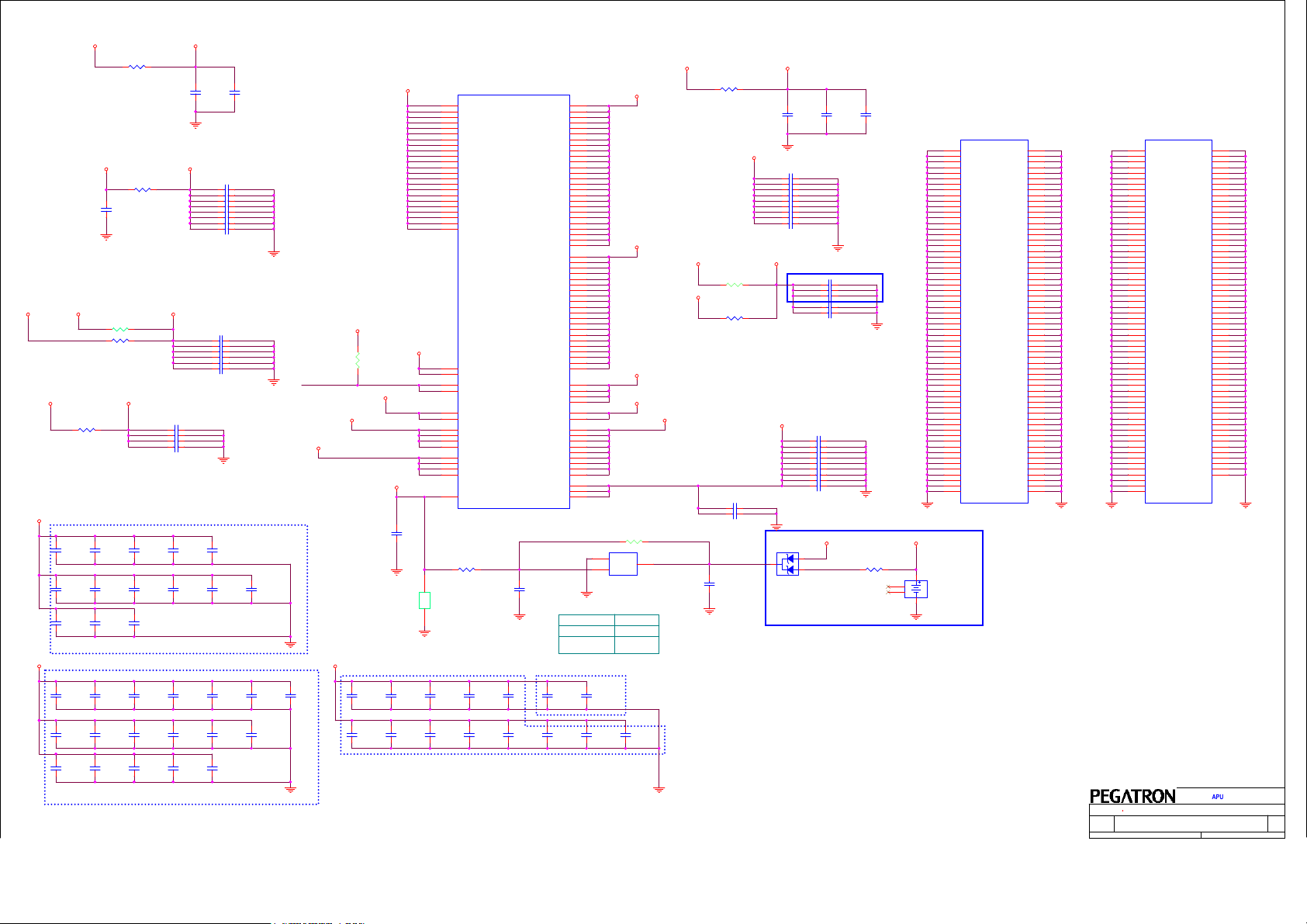

11.1V 65WHr

AC ADAPTER

15-16V 90W

AUXILIARY

AC ADAPTOR

AC ADAPTOR

15-16V 90W

SW

SW

SRJ

SRJ

SRJ

BATTERY

VIN_EXT

CHARGERBATTERY

MAX8731A

MOSFET

SWITCHED

SRJ

VIN_GFX

= FET PWR SW ITCH CONTROLLED BY GPIO

= FET PWR SW ITCH CONTROLLED BY JUMPER OR GPIO

= 1mO SENSE RESISTOR WITH JUMPER (KEVIN)

= 5mO SENSE RESISTOR WITH JUMPER (KEVIN)

= 50mO SENSE RESISTOR WITH JUMPER (KEVIN)

+VIN_ALW

CPU CORE PWM

(single phase)

CPU NB PWM

(single phase)

ISL62771

DDR3 PWM

LDO VTT

MAX8632

+0.95V SW

ISL6269A

+1.5V SW

ISL6269A

+1.8V SW

ISL6269A

+5V LDO

+3V LDO

+5V SW

+3V SW

MAX1533

+12V SW

MAX8792

+5V_ALW

+3.3V_ALW

SRJ

SRJ

SRJ

SRJ

SRJ

SRJ

SRJ

SRJ

SRJ

SRJ

SWITCH

SWITCH

APU_VDD_RUN@15A

APU_VDDNB_RUN@13A

APU_VDDIO_SUS@9A

MEM_VTT_RUN@1A

@8A

+0.95V_ALW

+1.5V_ALW@4A

+1.8V_ALW

@5A

+5V_MAIN

+3.3V_EC

SRJ

+3.3V_ALW@8A

+5V_ALW@8A

+12V_RUN

+5V_RUN

+3.3V_RUN

3V BATT

+1.5V_RUN

+3.3V_ALW

+3.3V_ALW

APU_VDD_RUN

APU_VDDNB_RUN

APU_VDDIO_SUS

+0.95V_RUN

+0.95V_RUN

+1.8_RUN

+1.8V_ALW

+3.3V_RUN

+3.3V_ALW

+1.5V_ALW

+12V_RUN

+3.3V_RUN

+3.3V_ALW

+1.5V_RUN

+3.3V_ALW

MXM_EN

+3.3V_RUN

+5V_RUN

+VIN_GFX

LDO

APU_VDDIO_SUS

MEM_VTT_RUN

SW

SW

Sensor

Resistor

SW

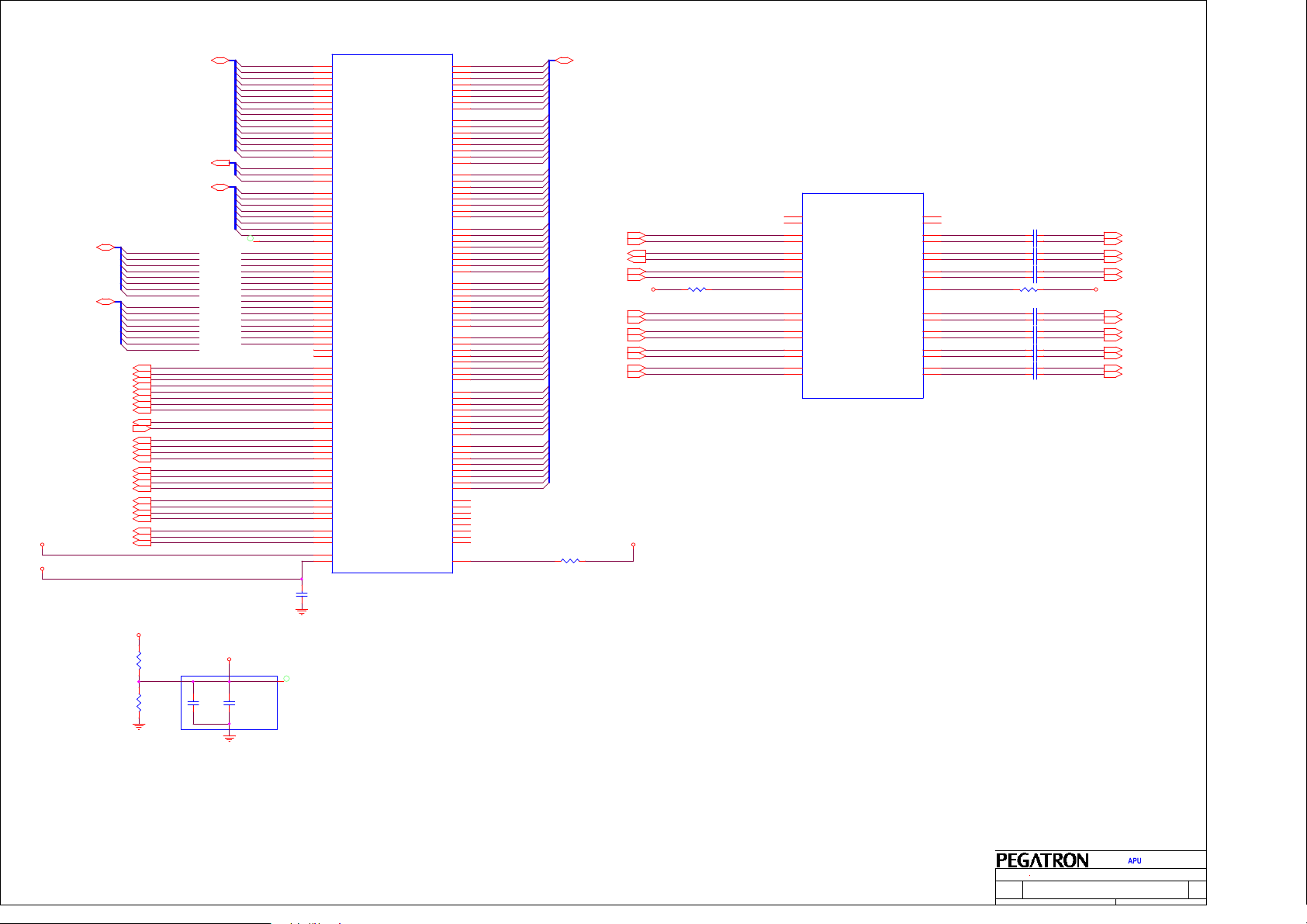

AMD KABINI FT3 APU

VDDCR_CPU

0.3-1.400V 15A

VDDCR_NB

0.7-1.325V @ 13A

VDDIO_MEM_S @ 3A

VDD_0.95 @ 5A

VDD_095_GFX @ 0.6A

VDD_095_USB3_DUAL+0.95V_DUAL

@ 1.0A

VDD_095_ALW @ 0.5A+0.95_ALW

VDD_18 @ 1.5A

VDD_18_ALW @ 0.5A

VDD_33 @ 0.2A

VDD_33_ALW @ 0.2A

VDDIO_AZ_ALW @ 100mA

VDDBT_RTC_G(1.5V)

DDRIII x2 SODIMM

VDD MEM 4A

VTT_MEM 0.5A

DESKTOP x1 PCIE Slot

+12V

+3.3V

+3.3VAux

MINI PCIE SLOT 2

1.5V(S0,S1) 0.5A

each

3.3V(S3,S5) 2.75A

SRJ

each

MINI PCIE SLOT 1(WLAN/BT)

1.5V(S0,S1) 0.5A

each

3.3V(S3,S5) 2.75A

SRJ

each

MXM3.0

SW

SW

BEAD

MXM_VDD_3.3V 1A

MXM_VDD_5V 2.5A

MXM_VDD_MAIN upto 10A

PCIe LAN

3.3V(S3,S5) TBD

+3.3V_RUN

+1.5V_RUN

+1.5V_RUN

+5V_RUN

+3.3V_RUN

+1.5V_ALW

+3.3V_EC

+3.3V_RUN

+5V_RUN

+5V_RUN

VDD_LED_BL_RUN

+VIN_ALW

+5V_ALW

+5V_ALW

+5V_ALW

+5V_ALW

+3.3V_RUN

+3.3V_RUN

+1.5V_RUN

+3.3V_RUN

+3.3V_ALW

+5V_RUN

+3.3V_RUN

+5V_RUN

+3.3V_RUN

SW

+VIN_ALW

+5V_RUN

+3.3V_RUN

+3.3V_RUN

BEAD

SW

SW

BEAD

SW

BEAD

CLOCK GEN

3.3V(S0,S1) 0.1A

1.5V 0.1A

1.5V 0.2A

HD AUDIO CODEC

5V(S0,S1) 22mA+1A(Class D)

BEAD

3.3V(S0,S1) 50mA

BEAD

1.5V(S3,S5) 30mA

BEAD

SMSC1308-EC

3.3V 0.5A

LCD PANEL

SRJ

SRJ

SRJ

3.3V 1.5A

5V 0.5A

BACK LIGHT

+5V

LED_BL

+VDD_MAIN

USB3 x2 REAR

5VDUAL

USB2 x1 MULTITOUCH

5VDUAL

USB2 x1 HDR

5VDUAL

USB TOUCHPAD

5VDUAL

USB WEBCAM/MIC

3.3V(S0,S1)0.2A

USB FINGERPRINT

3.3V(S0,S1)TBD

EXPRESSCARD

1.5V(S0,S1)0.7A

3.3V(S0,S1)1.3A

3.3V(S3,S5)0.3A

SATA HDD

5V(S0,S1) TBD

3.3V(S0,S1) TBD

SATA ODD

5V(S0,S1) TBD

USB BLUETOOTH

3.3V(S0,S1) TBD

MINI-DDI

+VIN_ALW

+5V

+3.3V

SD READER

+3.3V TBD

BEAD

SW

SW

SW

SW

SW

+1.8V_ALW

SPARE

LDO DNI

+1.8V_ALW

+1.5V_ALW

+0.95V_DUAL

SRJ

+0.95V_RUN

+0.95V_ALW

SWITCH

SWITCH

SRJ DNI

SRJ

SRJ

SRJ

+0.95V_DUAL

+1.8V_RUN

+1.5V_RUN

POWER DELIVER CHART

POWER DELIVER CHART

POWER DELIVER CHART

Title :

Title :

Title :

Mike_Chiu

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

3 99Monday, March 25, 2013

3 99Monday, March 25, 2013

3 99Monday, March 25, 2013

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Rev

Rev

Rev

1.2

1.2

1.2

Page 4

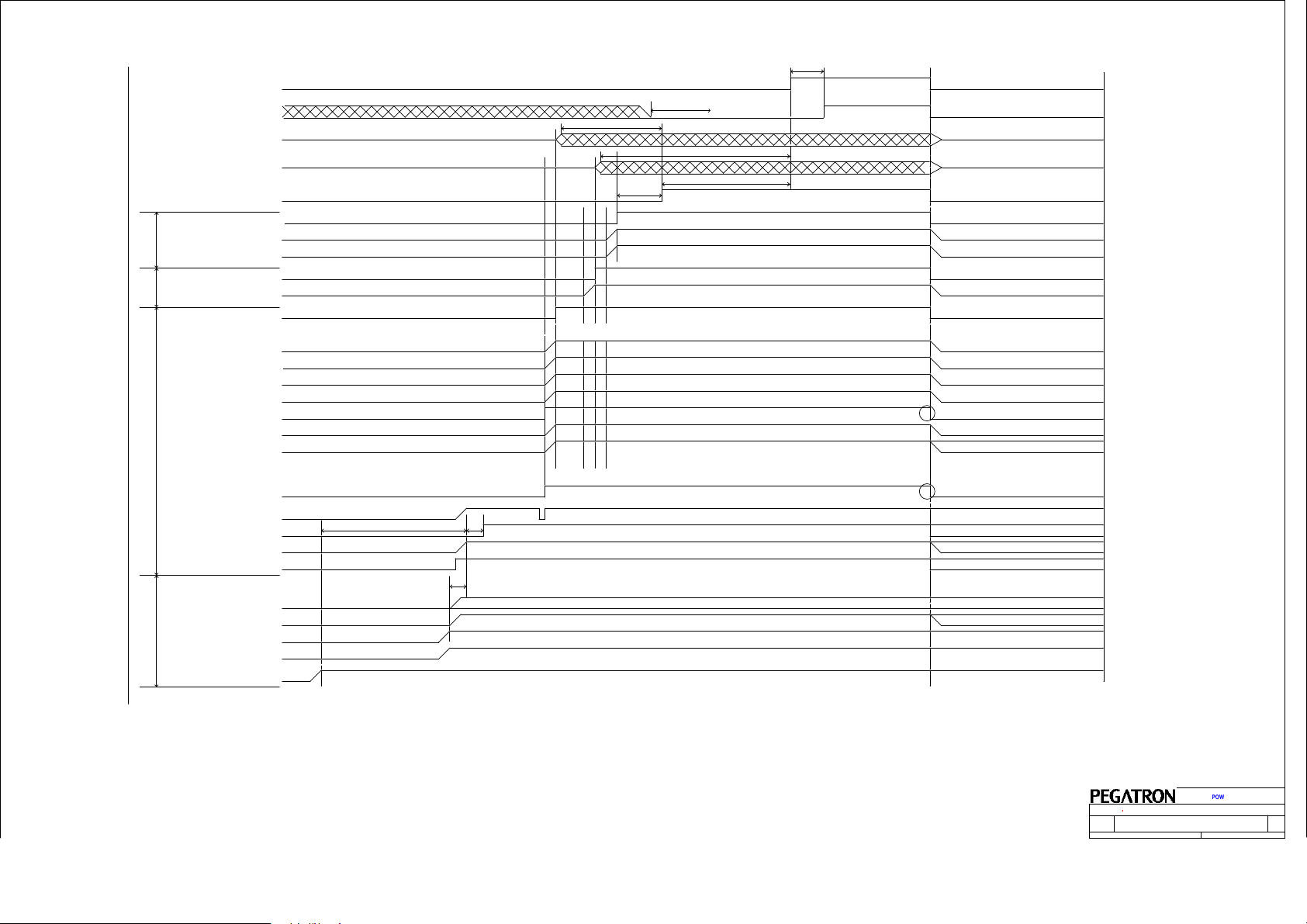

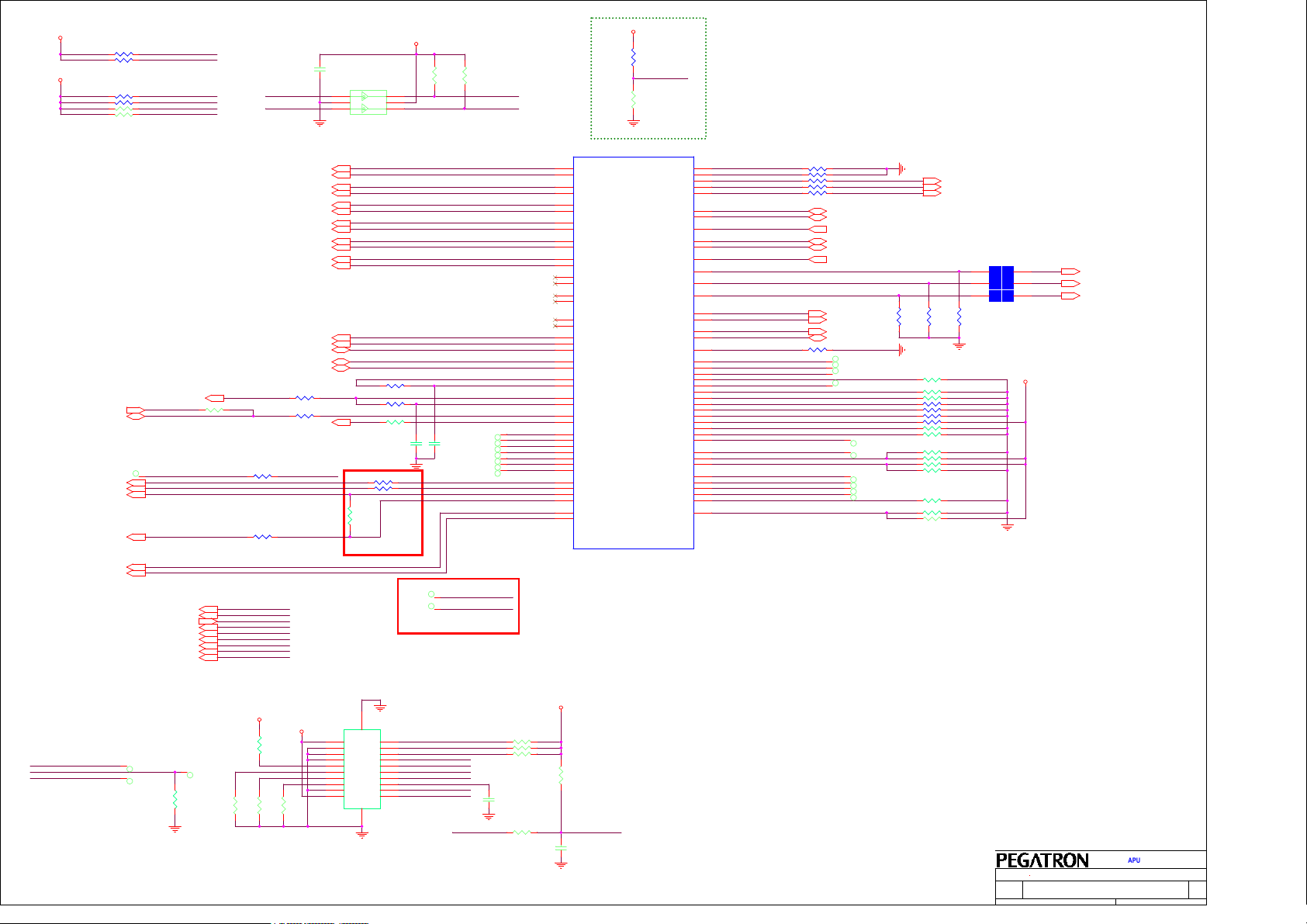

APU_PWRGD (LDT_PWROK)

APU_VDDNB_RUN (VDDCR_NB)

GROUP D

APU_VDD_RUN (VDDCR_CPU)

GROUP C

GROUP B

APU_VDDIO_SUS (VDDIO_MEM_S)

GROUP A

LDT_RST# (LDT_RST#)

APU_CLKIN (EXT)

APU_CLKIN (INT)

SYS_PWRGD

APU_VRM_PWRGD

+0.95V_RUN_PWRGD

+0.95V_RUN (VDD_10)

APU_GB_PG

+1.5V_RUN

+1.8V_RUN (VDD_18)

+3.3V_RUN(VDD_33)

MEM_VTT_RUN

PWR_BTN#_KB

RSM_RST_L

ALWRAILS_KB

EN_KB_ALW

+5V_RUN

SLP_S3#

SLP_S5#

+3.3V_EC

+5V_MAIN

+VIN_ALW

AC_OK

+VBAT

Power-up Sequencing for the KABINI Platform from Mechanic al Off

_ from S3 _

Power button pressed

5S delay

10mS

delay

+5V_ALW/+3.3V_ALW/+1.8V_ALW/+1.5V_ALW/+0.95V_ALW

0S for DT, >0S for NB

delay

Battery inserted/AC IN

31 mS Delay

running

15 mS Delay

AC not present scenario = LOW AC present = high

>1 uS

Req.

Req.

>1 mS

Req.

>1 mS

running

48mS chipset delay

_TO S3_

POWER SEQUENCE CHART

POWER SEQUENCE CHART

POWER SEQUENCE CHART

Title :

Title :

Title :

Mike_Chiu

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

4 99Monday, March 25, 2013

4 99Monday, March 25, 2013

4 99Monday, March 25, 2013

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

Rev

Rev

Rev

1.2

1.2

1.2

Page 5

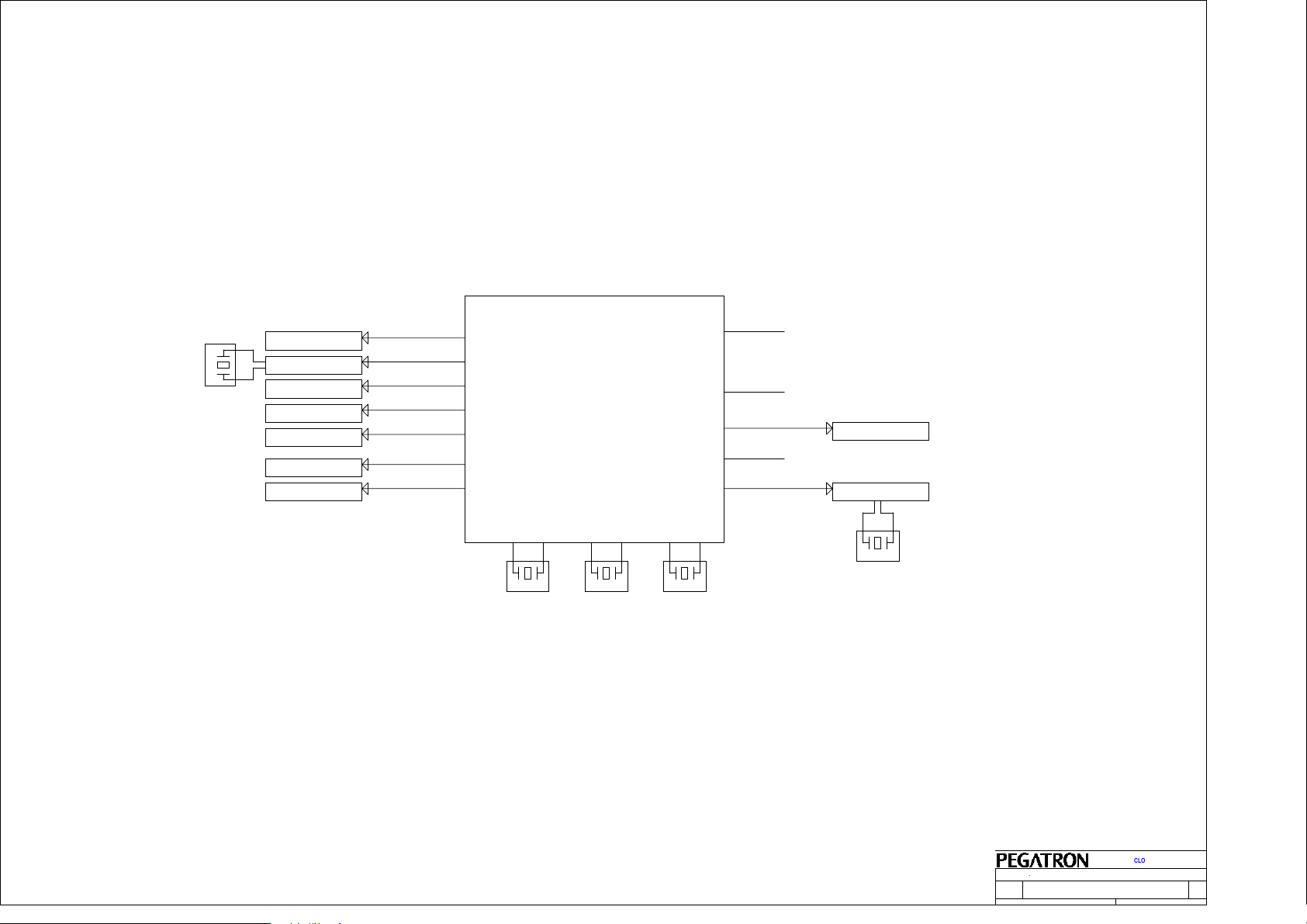

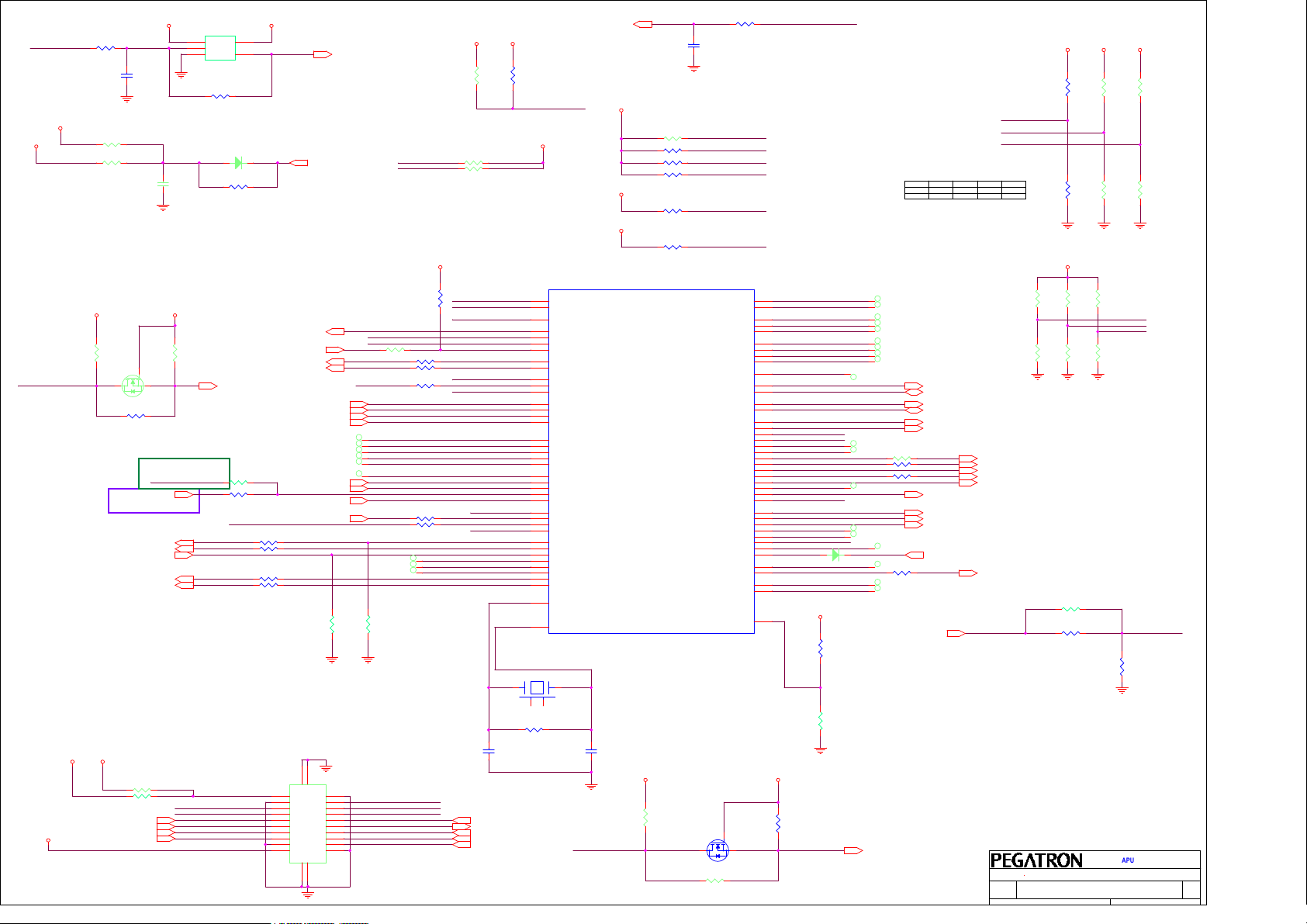

INTERNAL CLOCK MODE

32.768K Hz

EC,LPC HEADER,

LPC TPM

SPI ROM & HEADER

HD AUDIO CODEC, AUDIO DSP

EC

A0_SODIMM

A1_SODIMM

LPC_CLK0

33MHZ

LPC_CLK1

33MHZ

SPI_CLK

xxHZ

HDA_BCLK_R AZ_BITCLK

24MHZ

RTC_CLK

32.768KHZ

M_A_DIM0_CLK0/M_A_DIM0_CLK#0

M_A_DIM0_CLK1/M_A_DIM0_CLK#1

M_A_DIM1_CLK2/M_A_DIM1_CLK#2

M_A_DIM1_CLK3/M_A_DIM1_CLK#3

LPCCLK0

LPCCLK1

SPI_CLK

RTCCLK

AMD FT3 CPU

CLOCK GENERATOR

48M HZ

FOR RTCFOR MASTER

32.768K Hz

GFX_CLKP/N

GPP_CLK0P/N

GPP_CLK1P/N

GPP_CLK2P/N

GPP_CLK3P/N

FOR SATA

25M Hz

NC

NC

CLK_PCIE1_WLAN/CLK_PCIE1_WLAN#

100MHZ

NC

CLK_PCIE3_LAN/CLK_PCIE3_LAN#

100MHZ

WLAN

LAN

25M Hz

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

CLOCK DISTRIBUTION

Title :

Title :

Title :

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Mike_Chiu

5 99Monday, March 25, 2013

5 99Monday, March 25, 2013

5 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 6

WLAN

Touch Pad

AMD

KABINI FT3 U0701

(MASTER)

SDA1

SCL1

SVC

SVD

SVT

ISL62771HRTZ-T

SVC

SVD

APU Core PWR PWM

SVT

GPU

GPU Thermal Sensor

SO-DIMMDDR 3

SDA0

SCL0

SO-DIMMDDR 3

BATTERY

SIC

SID

Plam Reset Thermal Sensor

ITE 8528

U3001

SMB1_DAT

SMB1_CLK

(MASTER)

SMB0_DAT

SMB0_CLK

BATTERY CHARGER

Title :

Title :

Title :

SMBUS MAP

SMBUS MAP

SMBUS MAP

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Mike_Chiu

6 99Monday, March 25, 2013

6 99Monday, March 25, 2013

6 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 7

+V_SM_VREF

+V_VREF_DDR3

M_A_A[15:0]<16,17>

M_A_BS[2:0]<16,17>

M_A_DM[7:0]<16,17>

M_A_DQS[7:0]<16,17>

M_A_DQS#[7:0]<16,17>

M_A_DIM0_CLK0<16>

M_A_DIM0_CLK#0<16>

M_A_DIM0_CLK1<16>

M_A_DIM0_CLK#1<16>

M_A_DIM1_CLK2<17>

M_A_DIM1_CLK#2<17>

M_A_DIM1_CLK3<17>

M_A_DIM1_CLK#3<17>

M_RESET#<16,17>

M_EVENT#<16,17>

M_A_DIM0_CKE0<16>

M_A_DIM0_CKE1<16>

M_A_DIM1_CKE0<17>

M_A_DIM1_CKE1<17>

M_A_DIM0_ODT0<16>

M_A_DIM0_ODT1<16>

M_A_DIM1_ODT0<17>

M_A_DIM1_ODT1<17>

M_A_DIM0_CS#0<16>

M_A_DIM0_CS#1<16>

M_A_DIM1_CS#0<17>

M_A_DIM1_CS#1<17>

M_A_RAS#<16,17>

M_A_CAS#<16,17>

M_A_WE#<16,17>

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

T0701 @

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS0

M_A_BS1

M_A_BS2

M_A_DM0

M_A_DM1

M_A_DM2

M_A_DM3

M_A_DM4

M_A_DM5

M_A_DM6

M_A_DM7

1

M_A_DQS0

M_A_DQS#0

M_A_DQS1

M_A_DQS#1

M_A_DQS2

M_A_DQS#2

M_A_DQS3

M_A_DQS#3

M_A_DQS4

M_A_DQS#4

M_A_DQS5

M_A_DQS#5

M_A_DQS6

M_A_DQS#6

M_A_DQS7

M_A_DQS#7

M_A_DIM0_CLK0

M_A_DIM0_CLK#0

M_A_DIM0_CLK1

M_A_DIM0_CLK#1

M_A_DIM1_CLK2

M_A_DIM1_CLK#2

M_A_DIM1_CLK3

M_A_DIM1_CLK#3

M_RESET#

M_EVENT#

M_A_DIM0_CKE0

M_A_DIM0_CKE1

M_A_DIM1_CKE0

M_A_DIM1_CKE1

M_A_DIM0_ODT0

M_A_DIM0_ODT1

M_A_DIM1_ODT0

M_A_DIM1_ODT1

M_A_DIM0_CS#0

M_A_DIM0_CS#1

M_A_DIM1_CS#0

M_A_DIM1_CS#1

M_A_RAS#

M_A_CAS#

M_A_WE#

U0701A

AG38

M_ADD0

W35

M_ADD1

W38

M_ADD2

W34

M_ADD3

U38

M_ADD4

U37

M_ADD5

U34

M_ADD6

R35

M_ADD7

R38

M_ADD8

N38

M_ADD9

AG34

M_ADD10

R34

M_ADD11

N37

M_ADD12

AN34

M_ADD13

L38

M_ADD14

L35

M_ADD15

AJ38

M_BANK0

AG35

M_BANK1

N34

M_BANK2

B32

M_DM0

B38

M_DM1

G40

M_DM2

N41

M_DM3

AG40

M_DM4

AN41

M_DM5

AY40

M_DM6

AY34

M_DM7

Y40

M_DM8

B33

M_DQS_H0

A33

M_DQS_L0

B40

M_DQS_H1

A40

M_DQS_L1

H41

M_DQS_H2

H40

M_DQS_L2

P41

M_DQS_H3

P40

M_DQS_L3

AH41

M_DQS_H4

AH40

M_DQS_L4

AP41

M_DQS_H5

AP40

M_DQS_L5

BA40

M_DQS_H6

AY41

M_DQS_L6

AY33

M_DQS_H7

BA34

M_DQS_L7

AA40

M_DQS_H8

Y41

M_DQS_L8

AC35

M_CLK_H0

AC34

M_CLK_L0

AA34

M_CLK_H1

AA32

M_CLK_L1

AE38

M_CLK_H2

AE37

M_CLK_L2

AA37

M_CLK_H3

AA38

M_CLK_L3

G38

M_RESET_L

AE34

M_EVENT_L

L34

M0_CKE0

J38

M0_CKE1

J37

M1_CKE0

J34

M1_CKE1

AN38

M0_ODT0

AU38

M0_ODT1

AN37

M1_ODT0

AR37

M1_ODT1

AJ34

M0_CS_L0

AR38

M0_CS_L1

AL38

M1_CS_L0

AN35

M1_CS_L1

AJ37

M_RAS_L

AL34

M_CAS_L

AL35

M_WE_L

AD40

M_VREF

AC38

M_VREFDQ

10369

12

Note: Open the sodlermask for Vias on Mem interface

C0704

1UF/6.3V

MEMORY

M_ZVDDIO_MEM_S

M_DATA0

M_DATA1

M_DATA2

M_DATA3

M_DATA4

M_DATA5

M_DATA6

M_DATA7

M_DATA8

M_DATA9

M_DATA10

M_DATA11

M_DATA12

M_DATA13

M_DATA14

M_DATA15

M_DATA16

M_DATA17

M_DATA18

M_DATA19

M_DATA20

M_DATA21

M_DATA22

M_DATA23

M_DATA24

M_DATA25

M_DATA26

M_DATA27

M_DATA28

M_DATA29

M_DATA30

M_DATA31

M_DATA32

M_DATA33

M_DATA34

M_DATA35

M_DATA36

M_DATA37

M_DATA38

M_DATA39

M_DATA40

M_DATA41

M_DATA42

M_DATA43

M_DATA44

M_DATA45

M_DATA46

M_DATA47

M_DATA48

M_DATA49

M_DATA50

M_DATA51

M_DATA52

M_DATA53

M_DATA54

M_DATA55

M_DATA56

M_DATA57

M_DATA58

M_DATA59

M_DATA60

M_DATA61

M_DATA62

M_DATA63

M_CHECK0

M_CHECK1

M_CHECK2

M_CHECK3

M_CHECK4

M_CHECK5

M_CHECK6

M_CHECK7

B30

A32

B35

A36

B29

A30

A34

B34

B37

A38

D40

D41

B36

A37

B41

C40

F40

F41

K40

K41

E40

E41

J40

J41

M41

N40

T41

U40

L40

M40

R40

T40

AF40

AF41

AK40

AK41

AE40

AE41

AJ40

AJ41

AM41

AN40

AT41

AU40

AL40

AM40

AR40

AT40

AV41

AW40

BA38

AY37

AU41

AV40

AY39

AY38

BA36

AY35

BA32

AY31

BA37

AY36

BA33

AY32

V41

W40

AB40

AC40

U41

V40

AA41

AB41

AD41

M_A_D0

M_A_D1

M_A_D2

M_A_D3

M_A_D4

M_A_D5

M_A_D6

M_A_D7

M_A_D8

M_A_D9

M_A_D10

M_A_D11

M_A_D12

M_A_D13

M_A_D14

M_A_D15

M_A_D16

M_A_D17

M_A_D18

M_A_D19

M_A_D20

M_A_D21

M_A_D22

M_A_D23

M_A_D24

M_A_D25

M_A_D26

M_A_D27

M_A_D28

M_A_D29

M_A_D30

M_A_D31

M_A_D32

M_A_D33

M_A_D34

M_A_D35

M_A_D36

M_A_D37

M_A_D38

M_A_D39

M_A_D40

M_A_D41

M_A_D42

M_A_D43

M_A_D44

M_A_D45

M_A_D46

M_A_D47

M_A_D48

M_A_D49

M_A_D50

M_A_D51

M_A_D52

M_A_D53

M_A_D54

M_A_D55

M_A_D56

M_A_D57

M_A_D58

M_A_D59

M_A_D60

M_A_D61

M_A_D62

M_A_D63

MEM_ZVDDIO

M_A_D[63:0] <16,17>

PCIE_RXP1_WLAN<55>

PCIE_RXN1_WLAN<55>

PCIE_RXP2_CR<40>

PCIE_RXN2_CR<40>

PCIE_RXP3_LAN<33>

PCIE_RXN3_LAN<33>

PEG_RXP0<70>

PEG_RXN0<70>

PEG_RXP1<70>

PEG_RXN1<70>

PEG_RXP2<70>

PEG_RXN2<70>

PEG_RXP3<70>

PEG_RXN3<70>

1 2

R0701 39.2Ohm

1%

R0701 connection to VDDIO_SUS should

be directly to the plane without a long trace

U0701B

R10

P_GPP_RXP0

R8

P_GPP_RXN0

R5

P_GPP_RXP1

R4

P_GPP_RXN1

N5

P_GPP_RXP2

N4

P_GPP_RXN2

N10

P_GPP_RXP3

N8

1 2

R0717 1.69KOhm

+0.95VS +0.95VS

+1.35V_DDR

+P_TX_ZVDD

ROUTE PCIE-LINK DIFF PAIR @ 85 OHM +/- 10%

P_GPP_RXN3

W8

P_TX_ZVDD_095

L5

P_GFX_RXP0

L4

P_GFX_RXN0

J5

P_GFX_RXP1

J4

P_GFX_RXN1

G5

P_GFX_RXP2

G4

P_GFX_RXN2

D7

P_GFX_RXP3

E7

P_GFX_RXN3

10369

PCIE

P_GPP_TXP0

P_GPP_TXN0

P_GPP_TXP1

P_GPP_TXN1

P_GPP_TXP2

P_GPP_TXN2

P_GPP_TXP3

P_GPP_TXN3

P_RX_ZVDD_095

P_GFX_TXP0

P_GFX_TXN0

P_GFX_TXP1

P_GFX_TXN1

P_GFX_TXP2

P_GFX_TXN2

P_GFX_TXP3

P_GFX_TXN3

L2

L1

K2

PCIE_TXP1_WLAN_C

K1

PCIE_TXN1_WLAN_C

J2

PCIE_TXP2_CR_C

J1

PCIE_TXN2_CR_C

H2

PCIE_TXP3_LAN_C

H1

PCIE_TXN3_LAN_C

W7

+P_RX_ZVDD

G2

PEG_TXP0_C

G1

PEG_TXN0_C

F2

PEG_TXP1_C

F1

PEG_TXN1_C

E2

PEG_TXP2_C

E1

PEG_TXN2_C

D2

PEG_TXP3_C

D1

PEG_TXN3_C

1 2

C0709 0.1UF/10V

1 2

C0710 0.1UF/10V

1 2

C0723 0.1UF/10V

1 2

C0724 0.1UF/10V

1 2

C0713 0.1UF/10V

1 2

C0714 0.1UF/10V

1 2

R0718 1KOhm

1 2

C0715 0.1UF/10V /DSC

1 2

C0716 0.1UF/10V /DSC

1 2

C0717 0.1UF/10V /DSC

1 2

C0718 0.1UF/10V /DSC

1 2

C0719 0.1UF/10V /DSC

1 2

C0720 0.1UF/10V /DSC

1 2

C0721 0.1UF/10V /DSC

1 2

C0722 0.1UF/10V /DSC

PCIE_TXP1_WLAN <55>

PCIE_TXN1_WLAN <55>

PCIE_TXP2_CR <40>

PCIE_TXN2_CR <40>

PCIE_TXP3_LAN <33>

PCIE_TXN3_LAN <33>

PEG_TXP0 <70>

PEG_TXN0 <70>

PEG_TXP1 <70>

PEG_TXN1 <70>

PEG_TXP2 <70>

PEG_TXN2 <70>

PEG_TXP3 <70>

PEG_TXN3 <70>

+1.35V_DDR

1 2

1 2

R0702

1KOhm

R0703

1KOhm

12

C0702

0.1UF/10V

+V_SM_VREF

12

C0703

1000PF/50V

Layout: Place within

1000 mils of the APU

socket.

1

T0702@

APU_MEM_&_PCIE_I_F

APU_MEM_&_PCIE_I_F

APU_MEM_&_PCIE_I_F

Title :

Title :

Title :

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Mike_Chiu

7 99Monday, March 25, 2013

7 99Monday, March 25, 2013

7 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 8

+1.8VS

R0801 300Ohm

R0804 300Ohm

+APU_VDD_33

R0803 1KOhm

R0805 1KOhm

R0806 1KOhm@

R0807 1KOhm@

APU_PROCHOT#<9,30>

VDDCR_NB_FB_H<80>

VDDCR_APU_FB_H<80>

VDDIO_SUS_FB_H<83>

VDDCR_APU_FB_L<80>

VDD_095_FB_H<82>

VDD_095_FB_L<82>

To Nano HDT

VR_HOT#<80>

1 2

1 2

1 2

1 2

1 2

1 2

T0850 @

LDT_RST#

APU_PWRGD

APU_ALERT#

PROCHOT#

APU_SIC

APU_SID

VCORE_PWROK<80>

1 2

R0860 0Ohm@

APU_PROCHOT#

1

VDDCR_NB_FB_L VSS_SENSE

VDDCR_NB_FB_H

VDDCR_APU_FB_H

VDDCR_APU_FB_L

APU_TCK<9>

APU_TMS<9>

APU_TDI<9>

APU_TDO<9>

APU_PWRGD_BUF<9>

LDT_RST#_BUF<9>

DBRDY<9>

DBREQ#<9>

APU_TRST#<9>

R0861 0Ohm

R0816 0Ohm

APU_TCK

APU_TMS

APU_TDI

APU_TDO

APU_PWRGD_BUF

LDT_RST#_BUF

DBRDY

DBREQ#

APU_TRST#

LDT_RST#

APU_PWRGD

R0859 0Ohm

R0812 0Ohm

1 2

1 2

HDMI_TXP2_APU<39>

HDMI_TXN2_APU<39>

HDMI_TXP1_APU<39>

HDMI_TXN1_APU<39>

HDMI_TXP0_APU<39>

HDMI_TXN0_APU<39>

HDMI_CLKP_APU<39>

HDMI_CLKN_APU<39>

1 2

1 2

APU_ALERT#<30>

EDP_TXP0<37>

EDP_TXN0<37>

EDP_TXP1<37>

EDP_TXN1<37>

APU_SVT<80>

APU_SVC<80>

APU_SVD<80>

APU_SIC<30,50,71>

APU_SID<30,50,71>

12

C0801

0.1UF/10V

@

1

2

3 4

+1.8VS

U0801

6

A1

Y1

5

VCC

GND

Y2

A2

SN74LVC2G07DCKR

@

DECOUPLING ON MINI-DDI CARD

HDMI_TXP2_APU

HDMI_TXN2_APU

HDMI_TXP1_APU

HDMI_TXN1_APU

HDMI_TXP0_APU

HDMI_TXN0_APU

HDMI_CLKP_APU

HDMI_CLKN_APU

EDP_TXP0

EDP_TXN0

EDP_TXP1

EDP_TXN1

APU_SVT

APU_SVC

APU_SVD

APU_SIC

APU_SID

1 2

R0810 0Ohm

1 2

R0811 0Ohm

PROCHOT#

1 2

R0864 0Ohm@

C0802

150PF/50V

@

1 2

R0813 0Ohm

1 2

R0814 0Ohm

12

R0817

49.9Ohm

@

close to APU

T0802 @

T0803 @

12

12

R0808

1KOhm

@

LDT_RST#

LDTRST_R

APU_PWRGD

LDTPWRGD_R

APU_ALERT#_R

12

C0803

150PF/50V

@

VSS_SENSE

VDD_095_FB_H

VDD_095_FB_L

1

1

close to APU

12

R0809

1KOhm

@

LDT_RST#_BUF

APU_PWRGD_BUF

T0813 @

T0814 @

T0815 @

T0816 @

T0817 @

T0818 @

T0819 @

VDD_095_FB_H

VDD_095_FB_L

1

APU_TDI

1

APU_TDO

1

APU_TCK

1

APU_TMS

1

APU_TRST#

1

DBRDY

1

APU_DBREQ#

VDDCR_NB_SENSE

VDDCR_CPU_SENSE

VDDIO_SUS_FB_HVDDIO_SUS_FB_H

U0701C

A9

TDP1_TXP0

B9

TDP1_TXN0

A10

TDP1_TXP1

B10

TDP1_TXN1

A11

TDP1_TXP2

B11

TDP1_TXN2

A12

TDP1_TXP3

B12

TDP1_TXN3

A4

LTDP0_TXP0

B4

LTDP0_TXN0

A5

LTDP0_TXP1

B5

LTDP0_TXN1

A6

LTDP0_TXP2

B6

LTDP0_TXN2

A7

LTDP0_TXP3

B7

LTDP0_TXN3

K15

DISP_CLKIN_H

H15

DISP_CLKIN_L

G31

SVT

D27

SVC

E29

SVD

B22

SIC

B21

SID

B20

APU_RST_L

A20

LDT_RST_L

B19

APU_PWROK

A19

LDT_PWROK

A22

PROCHOT_L

B18

ALERT_L

D29

TDI

D31

TDO

D35

TCK

D33

TMS

G27

TRST_L

B25

DBRDY

A25

DBREQ_L

D23

VDDCR_NB_SENSE

G23

VDDCR_CPU_SENSE

E25

VDDIO_MEM_S_SENSE

E23

VSS_SENSE

AV33

VDD_095_FB_H

AU33

VDD_095_FB_L

10369

+APU_VDD_33

R0862

1KOhm

1 2

CRT_HSYNC

R0863

1KOhm

@

1 2

DISPLAY/SVI2/JTAG/TEST

DP_150_ZVSS

DIECRACKMON

BYPASSCLK_H

BYPASSCLK_L

GIO_TSTDTM0_SERIALCLK

GIO_TSTDTM0_CLKINIT

M_ANALOGOUT

/DP_STEREOSYNC

DP_2K_ZVSS

DP_BLON

DP_DIGON

DP_VARY_BL

TDP1_AUXP

TDP1_AUXN

TDP1_HPD

LTDP0_AUXP

LTDP0_AUXN

LTDP0_HPD

DAC_RED

DAC_GREEN

DAC_BLUE

DAC_HSYNC

DAC_VSYNC

DAC_SCL

DAC_SDA

DAC_ZVSS

THERMDA

THERMDC

PLLTEST1

PLLTEST0

PLLCHRZ_H

PLLCHRZ_L

M_TEST

FREE_2

USB_ATEST0

USB_ATEST1

M_ANALOGIN

TMON_CAL

HDMI_EN

NOTE: DP_STEREOSYNC & APU_HSYNC PU FOR INTERNAL,

DP_STEREOSYNC & APU_HSYNC PD FOR CUSTOMER

B16

DP_150_ZVSS

A21

DP_2K_ZVSS

B17

ON_BLON_R

A17

ON_DIGON_R

A18

ON_VARY_R

D17

HDMI_DDC_CLK_APU

E17

HDMI_DDC_DATA_APU

H19

HDMI_HPD_APU

D15

EDP_AUXP

E15

EDP_AUXN

H17

EDP_HPD

B14

CRT_R_APU

A14

CRT_G_APU

B15

CRT_B_APU

G19

CRT_HSYNC

E19

CRT_VSYNC

D19

CRT_DDC_CLK

D21

CRT_DDC_DATA

A16

DAC_ZVSS

H27

APU_TEST4_THERMDA

H29

APU_TEST5_THERMDC

D25

APU_TEST6_DIRECRACKMON

A27

BP0

BP1

BP2

BP3

APU_TEST14_BP0

B27

APU_TEST15_BP1

A26

APU_TEST16_BP2

B26

APU_TEST17_BP3

B28

APU_TEST18_PLLTEST1

A28

APU_TEST19_PLLTEST0

B24

APU_TEST25_H_BYPASSCLK

A24

APU_TEST25_L_BYPASSCLK

AV35

APU_TEST28_H_PLLCHARZ

AU35

APU_TEST28_L_PLLCHARZ

E33

APU_TEST31_MEM_TEST

A29

APU_TEST34_L_TSTCLKIN_L

H21

APU_TEST36_GIO_TSTDTM0_SER_CLK

H25

APU_TEST37_GIO_TSTDTM0_CLKINIT

AJ10

USB_ATEST0

AJ8

USB_ATEST1

R32

M_ANALOGIN

N32

M_ANALOGOUT

AP29

TMON_CAL

E21

APU_TEST35_STEREOSYNC

1 2

R0818 150Ohm

1 2

R0819 2KOhm

1 2

R0820 0Ohm

1 2

R0821 0Ohm

1 2

R0822 0Ohm

HDMI_DDC_CLK_APU <39>

HDMI_DDC_DATA_APU <39>

HDMI_HPD_APU <39>

EDP_AUXP <37>

EDP_AUXN <37>

EDP_HPD <37>

CRT_HSYNC <38>

CRT_VSYNC <38>

CRT_DDC_CLK <38>

CRT_DDC_DATA <38>

1 2

R0826 499Ohm

1

T0846@

1

T0847@

1

T0826@

1

T0801@

1

1

1

1

1

1

LCDBL_EN_APU

LCDVDD_EN_APU

LCDBL_PWM_APU

12

R0827 1KOhm@

R0828 1KOhm@

R0829 1KOhm@

R0830 1KOhm

R0831 1KOhm

R0832 510Ohm

R0833 510Ohm

R0841 0Ohm@

R0842 0Ohm@

T0827@

R0836 1KOhm@

R0834 1KOhm@

T0828@

R0835 1KOhm@

R0837 1KOhm@

T0829@

T0830@

T0831@

T0832@

R0840 0Ohm@

R0838 1KOhm@

R0839 1KOhm@

NOTE: DP_STEREOSYNC PU FOR INTERNAL,

DP_STEREOSYNC PD FOR CUSTOMER

R0823

150Ohm

1%

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

LCDBL_EN_APU <37>

LCDVDD_EN_APU <37>

LCDBL_PWM_APU <37>

JP0801 SHORT_PIN

JP0802 SHORT_PIN

JP0803 SHORT_PIN

12

12

R0825

R0824

150Ohm

150Ohm

1%

1%

+1.8VS

12

12

12

CRT_R <38>

CRT_G <38>

CRT_B <38>

Route BYPASSCLK_H/L

and PLLCHARZ_H/L differentially

APU_TEST35_STEREOSYNC

APU_TEST15_BP1

APU_TEST17_BP3

HDT+ header

+1.8VS

+1.8VS

12

R0858

1KOhm

@

12

R0855

10KOhm

@

12

R0856

10KOhm

@

APU_TRST#

12

R0857

10KOhm

@

1

T0843@

1

1

T0845@

T0844@

12

R0853

1KOhm

@

21

J0801 BTOB_CON_20P @

112

334

P_GND1

556

778

9910

111112

131314

151516

171718

191920

P_GND2

22

2

APU_TCK

4

APU_TMS

6

APU_TDI

8

APU_TDO

10

APU_PWRGD_BUF

12

LDT_RST#_BUF

14

DBRDY

16

DBREQ#

18

APU_TEST19_PLLTEST0

20

APU_TEST18_PLLTEST1

R0847 1KOhm@

R0848 1KOhm@

R0849 1KOhm@

12

C0805

0.01UF/25V

@

DBREQ# APU_DBREQ#

R0850 0Ohm@

1 2

1 2

1 2

1 2

+1.8VS

12

12

R0851

1KOhm

@

C0804

1UF/6.3V

@

APU_DISPLAY_CLK_MISC

APU_DISPLAY_CLK_MISC

APU_DISPLAY_CLK_MISC

Title :

Title :

Title :

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet

Date: Sheet of

Date: Sheet of

Mike_Chiu

8 99Monday, March 25, 2013

8 99Monday, March 25, 2013

8 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

of

Page 9

PCIE_RST#_R

+3VSUS

+1.8VSUS

SATA_ODD_PRSNT#_R

+1.8VS

1 2

R0903

33Ohm

150PF/50V

1 2

R0912 47KOhm@

1 2

R0913 47KOhm@

+3VSUS

1 2

+3VS+3VSUS

+3VSUS +3VSUS

PCIE_RST#_U

12

C0901

R0935

10KOhm

@

Q0901

2N7002

@

1

G

3

2

D

S

07V040000001

1 2

R0994 0Ohm

/Zero_ODD

S5 Power Domain

SATA_ODD_DA#_R

CLK_REQ3_LAN#<33>

S0 Power Domain

HDA_BCLK<41>

HDA_SDO<41>

HDA_SDIN0<41>

HDA_SYNC<41>

HDA_RST#<41,42>

1 2

R0957 0Ohm@

1 2

R0956 0Ohm@

APU_TCK<8>

APU_TRST#<8>

DBRDY<8>

DBREQ#<8>

1

2

1 2

R0902 0Ohm

RSMRST#

12

C0903

1UF/6.3V

@

+3VS

R0993

10KOhm

@

1 2

HDA_BCLK

HDA_SDO

HDA_SYNC

HDA_RST#

JTAG_TRST#

JTAG_TDO

APU_TCK

APU_TRST#

DBRDY

DBREQ#

U0901

@

5

A

VCC

B

4

GND3Y

SN74LVC1G08DCKR

D0901

1 2

@

RB751V-40

1 2

R0997 0Ohm

SATA_ODD_PRSNT# <60>

1 2

R0958 0Ohm@

1 2

R0915 0Ohm

SATA_ODD_PRSNT#_R

1 2

R0925 33Ohm

1 2

R0926 33Ohm

1 2

R0927 33Ohm

1 2

R0928 33Ohm

+3V_J0901_1

BUF_PLT_RST# <33,40,47,55,70>

PM_RSMRST# <30>

PM_PWRBTN#<30>

PCIE_WAKE#<30,33>

PM_SUSB#<30>

PM_SUSC#<30>

PM_SUSB#

PM_SUSC#

RC_IN#<30>

A20GATE<30>

EXT_SCI#<30>

EXT_SMI#<30,65>

T0950@

T0951@

T0952@

T0953@

T0956@

T0939@

CLK_REQ1_WLAN#<55>

CLK_REQ2_CR#<40>

CLK_REQG_VGA#<71>

USB_OC#<61>

12

R0901

10KOhm

@

Nano HDT header

23

J0901 BTOB_CON_20P

9

11

13

15

112

SIDE424SIDE3

334

556

778

9

15

171718

191920

SIDE222SIDE1

21

2

4

6

8

10

10

121211

141413

16

16

18

20

@

12

R0963

10KOhm

@

+APU_VDD33_ALW

R0906

100KOhm

/Zero_ODD

1

1

1

1 2

R0910 2.2KOhm@

1 2

R0911 2.2KOhm@

12

LPC_RST#_R

PCIE_RST#_R

RSMRST#

PM_PWRBTN#

SYS_PWRGD

SYS_RST#_D

PCIE_WAKE#_APU

PM_SUSB#_R

PM_SUSC#_R

APU_TEST0

APU_TEST2

RC_IN#

A20GATE

EXT_SCI#

EXT_SMI#

IR_RX0

IR_TX0

IR_TX1

IR_RX1

IR_LED_R

GPIO60

CLK_REQ1_WLAN#

CLK_REQ2_CR#

APU_PCIE_LAN_CLKREQ#_R

CLK_REQG_VGA#

JTAG_TRST#

JTAG_TDI

JTAG_TCK

JTAG_TDO

HDA_BCLK_R

HDA_SDO_R

HDA_SDIN0

GPIO168

GPIO169

GPIO170

HDA_SYNC_R

HDA_RST#_R

APU_TMS <8>

APU_TDI <8>

APU_TDO <8>

APU_PWRGD_BUF <8>

LDT_RST#_BUF <8>

PM_SUSB#

PM_SUSC#

1 2

R0996 0Ohm@

1 2

R0907 0Ohm

1 2

R0908 0Ohm

R0909 0Ohm

1

1

1

1

1

1

R0930 0Ohm

R0905 0Ohm

T0902@

T0903@

T0904@

12

R0919

10KOhm

@

JTAG_TCK

JTAG_TMS

JTAG_TDI

APU_TMS

APU_TDI

APU_TDO

APU_PWRGD_BUF

LDT_RST#_BUF

1 2

1 2

1 2

APU_TEST1 JTAG_TMS

+3VSUS+1.8VSUS

XTAL_32K_IN

XTAL_32K_OUT

12

C0905

15PF/50V

12

R0962

10KOhm

SYS_RST#_D

+3VSUS

U0701D

AY4

LPC_RST_L

AY9

PCIE_RST_L

AY5

RSMRST_L

BA8

PWR_BTN_L

AM19

PWR_GOOD

AY7

SYS_RESET_L/GEVENT19_L

AW11

WAKE_L/GEVENT8_L

AY3

SLP_S3_L

BA5

SLP_S5_L

AU13

TEST0

AY10

TEST1/TMS

AY6

TEST2

AR23

KBRST_L

AR31

GA20IN/GEVENT0_L

AN5

LPC_PME_L/GEVENT3_L

AL7

LPC_SMI_L/GEVENT23_L

AP15

AC_PRES/IR_RX0/GEVENT16_L

AV13

IR_TX0/GEVENT21_L

BA9

IR_TX1/GEVENT6_L

BA10

IR_RX1/GEVENT20_L

AV15

IR_LED_L/LLB_L/GPIO184

AU29

CLK_REQ0_L/SATA_IS0_L/SATA_ZP0_L/GPIO60

AW29

CLK_REQ1_L/GPIO61

AR27

CLK_REQ2_L/GPIO62

AV27

CLK_REQ3_L/SATA_IS1_L/SATA_ZP1_L/GPIO63

AY29

CLK_REQG_L/GPIO65/OSCIN

AY8

USB_OC0_L/SPI_TPM_CS_L/TRST_L/GEVENT12_L

AW1

USB_OC1_L/TDI/GEVENT13_L

AV1

USB_OC2_L/TCK/GEVENT14_L

AY1

USB_OC3_L/TDO/GEVENT15_L

AN2

AZ_BITCLK

AN1

AZ_SDOUT

AK2

AZ_SDIN0/GPIO167

AK1

AZ_SDIN1/GPIO168

AM1

AZ_SDIN2/GPIO169

AL2

AZ_SDIN3/GPIO170

AM2

AZ_SYNC

AL1

AZ_RST_L

AJ2

X32K_X1

AJ1

X32K_X2

10369

X0901 32.768KHZ

1 4

2

3

R0918

1 2

20MOhm

SATA_ODD_DA#_R

12

C0904

15PF/50V

LPC_RST#<30>

LPC_RST#

150PF/50V

+3VS

1 2

R0975 10KOhm@

1 2

R0976 10KOhm

1 2

R0982 2.2KOhm

1 2

R0983 2.2KOhm

+3VA

1 2

R0981 10KOhm

+3VSUS

1 2

R0973 10KOhm

ACPI/SD/AZ/GPIO/RTC/MISC

R0936

10KOhm

@

1 2

C0902

R0995 0Ohm@

1 2

R0904 33Ohm

12

DGPU_PWROK

EDP_ON#

SCLK0_DIMM

SDATA0_DIMM

LID_SW#

USB_OC#

SD_PWR_CTRL

SD_CLK/GPIO73

SD_CMD/GPIO74

SD_CD/GPIO75

SD_WP/GPIO76

SD_DATA0/GPIO77

SD_DATA1/GPIO78

SD_DATA2/GPIO79

SD_DATA3/GPIO80

SD_LED/GPIO45

SCL0/GPIO43

SDA0/GPIO47

SCL1/GPIO227

SDA1/GPIO228

GPIO49

GPIO50

GPIO51

GPIO55

GPIO57

GPIO58

GPIO59

GPIO64

SPKR/GPIO66

GPIO68

GPIO69

GPIO70

GPIO71

GPIO174

GEVENT2_L

GEVENT4_L

GEVENT7_L

GEVENT10_L

GEVENT11_L

GEVENT17_L

BLINK/GEVENT18_L

GEVENT22_L

GENINT1_L/GPIO32

GENINT2_L/GPIO33

FANOUT0/GPIO52

FANIN0/GPIO56

RTCCLK

1

G

3

D

S

/Zero_ODD

1 2

Q0902

2N7002

07V040000001

2

BA23

AY22

AY23

AY20

BA20

BA22

AY21

AY24

BA24

AY25

AU25

AV25

AY11

BA11

AP27

AY28

BA28

AV23

AP21

BA26

AV19

AY27

BA27

AU21

AY26

AV21

AM21

BA3

AV17

BA4

AR15

AP17

AP11

AN8

AU17

BA6

BA29

AP23

AV31

AU31

AV11

LPC_RST#_R

+3VS+3VSUS

R0937

10KOhm

/Zero_ODD

1 2

R0942

10KOhm

R0943

2.2KOhm

@

1

1

1

1

1

1

1

1

1

1

T0925@

1

T0906@

1

T0926@

R0924 0Ohm@

R0944 0Ohm

R0923 0Ohm

1

T0929@

1

T0970@

1

T0971@

1

@

1

R0922 0Ohm

1

1

SATA_ODD_DA# <60>

SD_PWR_CTRL

SD_CLK_GPIO73

SD_CMD_GPIO74

SD_CMD_GPIO75

SD_CMD_GPIO76

SD_CMD_GPIO77

SD_CMD_GPIO78

SD_CMD_GPIO79

SD_CMD_GPIO80

GPIO45

SCLK0_DIMM

SDATA0_DIMM

APU_SCL1

APU_SDA1

SATA_ODD_PWRGT

BT_ON_OFF#

PCB_ID1

PCB_ID2

GPIO57

GPIO58

EDP_ON#_APU

DGPU_HOLD_RST#_APU

APU_SPKR

VGA_PWRON_APU

WLAN_RST#_APU

GPIO70

APU_PROCHOT#

PCB_ID0

WLAN_LED

SPKR_MUTE#

WLAN_ON

GEVENT10_L

GEVENT11_L

SATA_ODD_DA#_R

BLINK_GEVENT18_L

1 2

D0903 RB751V-40

GENINT1_L_GPIO32

DGPU_PWROK_APU

FANOUT0_GPIO52

FANIN0_GPIO56

+3VSUS

1 2

12

PCB_ID1

PCB_ID2

T0913@

T0914@

T0915@

T0916@

T0917@

T0918@

T0919@

T0920@

T0923@

1 2

1 2

1 2

T0982@

T0958@

1 2

T0946@

T0945@

PM_PWROK<30,91>

R1.0 R1.1 R2.0 R2.1

0

0 0

SCLK0_DIMM <16, 17>

SDATA0_DIMM <16,17>

APU_SCL1 <28>

APU_SDA1 <28>

SATA_ODD_PWRGT <60>

BT_ON_OFF# <55>

APU_PROCHOT# <8,30>

WLAN_LED <12,66>

SPKR_MUTE# <42>

WLAN_ON <55>

LID_SW# <30,37,65>

0 1

1

EDP_ON# <30>

DGPU_HOLD_RST# <70>

APU_SPKR <41>

VGA_PWRON <63,91>

WLAN_RST#_APU <55>

DGPU_PWROK <87,92>

PEGATRON UN IHAN CORP.

PEGATRON UN IHAN CORP.

PEGATRON UN IHAN CORP.

Date: Sheet of

Date: Sheet of

Date: Sheet of

PCB_ID0

PCB_ID1

PCB_ID2

11

1 2

1 2

R0992 0Ohm@

R0990 1KOhm

‧

‧

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

+3VSUS

R0920

10KOhm

/DSC

1 2

R0921

10KOhm

/UMA

1 2

+3VSUS

R0955

R0954

1KOhm

1KOhm

@

@

1 2

R0952

R0950

15KOhm

15KOhm

@

@

1 2

1 2

EG70_KB

EG70_KB

EG70_KB

+3VS +3VS

1 2

1 2

R0951

1KOhm

@

1 2

R0953

15KOhm

@

1 2

12

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

R0945

10KOhm

@

R0946

10KOhm

@

APU_TEST0

APU_TEST1

APU_TEST2

R0947

10KOhm

@

1 2

R0948

10KOhm

@

1 2

SYS_PWRGDPM_PWROK

R0991

1.27KOhm

1%

1 2

APU_GEVENT_GPIO_SD_AZ

APU_GEVENT_GPIO_SD_AZ

APU_GEVENT_GPIO_SD_AZ

Mike_Chiu

Mike_Chiu

Mike_Chiu

9 99Monday, March 25, 2013

9 99Monday, March 25, 2013

9 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 10

LPC_CLK0_R<12>

LPC_CLK1_R<12>

1AV200000087

C1011 5.6PF/50V

4

2

C1012 5.6PF/50V

1AV200000087

U0701E

SATA_TXP0<60>

HDD

ODD

C1001

12

12PF/50V

@

4

2

C1002

12

12PF/50V

@

X1002

48MHZ

07V080000033

1 3

XTAL_48M_OUT_R

LPC_CLK0_R

LPC_CLK1_R SPI_WP_L_HSPI

1 2

R1050 0Ohm

SATA_TXN0<60>

SATA_RXN0<60>

SATA_RXP0<60>

SATA_TXP1<60>

SATA_TXN1<60>

SATA_RXN1<60>

SATA_RXP1<60>

R1001

X1001

1MOhm

25MHZ

@

@

1 2

1 3

R1006

1MOhm

1 2

SATA_TXP0

SATA_TXN0

SATA_RXN0

SATA_RXP0

SATA_TXP1

SATA_TXN1

SATA_RXN1

SATA_RXP1

+0.95VS

SATA_LED#<66>

CLK_PCIE0_VGA<70>

CLK_PCIE0_VGA#<70>

CLK_PCIE1_WLAN<55>

CLK_PCIE1_WLAN#<55>

CLK_PCIE2_CR<40>

CLK_PCIE2_CR#<40>

CLK_PCIE3_LAN<33>

CLK_PCIE3_LAN#<33>

X1002

For TV:25MHz (07V080000010)

For KB:48MHz (07V080000025)

LPC_CLK0_DEBUG<65>

LPC_CLK1_EC<30>

LPC_AD0<30,65>

LPC_AD1<30,65>

LPC_AD2<30,65>

LPC_AD3<30,65>

LPC_FRAME#<12,30,65>

LPC_SERIRQ<30,65>

1 2

R1003 1KOhm

1 2

R1004 1KOhm

+3VS

RN1001B

RN1001A

RN1003A

RN1003B

RN1004B

RN1004A

RN1005A

RN1005B

1

T1003@

LPC_CLK0_DEBUG

LPC_CLK1_EC

1

T1002@

1

T1011@

1

T1014@

1 2

R1020 560Ohm

34

0Ohm

12

0Ohm

12

0Ohm

34

0Ohm

34

0Ohm

12

0Ohm

12

0Ohm

34

0Ohm

1 2

R1002 22Ohm

1 2

R1007 22Ohm

LPC_PD_L_GEVENT5_L_SPI_TPM_CS_L

SATA_CALRN

SATA_CALRP

SATA_LED#

XTAL_25M_IN

XTAL_25M_OUT

CLK_PCIE0_VGA_APU

CLK_PCIE0_VGA#_APU

CLK_PCIE1_WLAN_APU

CLK_PCIE1_WLAN#_APU

CLK_PCIE2_CR_APU

CLK_PCIE2_CR#_APU

CLK_PCIE3_LAN_APU

CLK_PCIE3_LAN#_APU

INT_48M_R

XTAL_48M_IN

XTAL_48M_OUT

LPC_CLK0_R

LPC_CLK1_R

LPC_AD0

LPC_AD1

LPC_AD2

LPC_AD3

LPC_FRAME#

LPC_DRQ#0

LPC_SERIRQ

LPC_CLKRUN#_R

BA14

SATA_TX0P

AY14

SATA_TX0N

BA16

SATA_RX0N

AY16

SATA_RX0P

AY19

SATA_TX1P

BA19

SATA_TX1N

AY17

SATA_RX1N

BA17

SATA_RX1P

AR19

SATA_ZVSS

AP19

SATA_ZVDD_095

BA30

SATA_ACT_L/GPIO67

AY12

SATA_X1

BA12

SATA_X2

U4

GFX_CLKP

U5

GFX_CLKN

AC8

GPP_CLK0P

AC10

GPP_CLK0N

AE4

GPP_CLK1P

AE5

GPP_CLK1N

AC4

GPP_CLK2P

AC5

GPP_CLK2N

AA5

GPP_CLK3P

AA4

GPP_CLK3N

AP13

X14M_25M_48M_OSC

N2

X48M_X1

N1

X48M_X2

AY2

LPCCLK0

AW2

LPCCLK1

AT2

LAD0

AT1

LAD1

AR2

LAD2

AR1

LAD3

AP2

LFRAME_L

AP1

LDRQ0_L

AV29

SERIRQ/GPIO48

AP25

LPC_CLKRUN_L

AV2

LPC_PD_L/GEVENT5_L/SPI_TPM_CS_L

10369

CLK/SATA/USB/SPI/LPC

USBCLK/14M_25M_48M_OSC

USB_SS_ZVDD_095_USB3_DUAL

SPI_CS1_L/GPIO165

SPI_CS2_L/GPIO166

SPI_HOLD_L/GEVENT9_L

USB_ZVSS

USB_HSD0P

USB_HSD0N

USB_HSD1P

USB_HSD1N

USB_HSD2P

USB_HSD2N

USB_HSD3P

USB_HSD3N

USB_HSD4P

USB_HSD4N

USB_HSD5P

USB_HSD5N

USB_HSD6P

USB_HSD6N

USB_HSD7P

USB_HSD7N

USB_HSD8P

USB_HSD8N

USB_HSD9P

USB_HSD9N

USB_SS_ZVSS

USB_SS_0TXP

USB_SS_0TXN

USB_SS_0RXP

USB_SS_0RXN

USB_SS_1TXP

USB_SS_1TXN

USB_SS_1RXP

USB_SS_1RXN

SPI_CLK/GPIO162

SPI_DO/GPIO163

SPI_DI/GPIO164

SPI_WP_L/GPIO161

W4

AG4

AL4

AL5

AJ4

AJ5

AG7

AG8

AG1

AG2

AF1

AF2

AE1

AE2

AD1

AD2

AC1

AC2

AB1

AB2

AA1

AA2

AE10

AE8

T2

T1

V2

V1

R1

R2

W1

W2

AU7

AW9

AR4

AR11

AR7

AU11

AU9

USB_RCOMP

INT_48M

R1010 11.8KOHM

USB_PP0

USB_PN0

USB_PP1

USB_PN1

USB_PP2

USB_PN2

USB_PP3

USB_PN3

USB_PP5

USB_PN5

USB_PP8

USB_PN8

USB_SS_ZVSS

USB_SS_ZVDD

USB3_TXP0

USB3_TXN0

USB3_RXP0

USB3_RXN0

SPI_CLK_HSPI

SPI_CS1_L_HSPI

SPI_CS2_L_GPIO166

SPI_DO_HSPI

SPI_DI_HSPI

SPI_HOLD_L_HSPI

1

T1001@

1 2

USB_PP0 <61>

USB_PN0 <61>

USB_PP1 <61>

USB_PN1 <61>

USB_PP2 <55>

USB_PN2 <55>

USB_PP3 <37>

USB_PN3 <37>

USB_PP5 <61>

USB_PN5 <61>

USB_PP8 <61>

USB_PN8 <61>

1 2

R1012 1KOhm

1 2

R1013 1KOhm

USB3_TXP0 <61>

USB3_TXN0 <61>

USB3_RXP0 <61>

USB3_RXN0 <61>

1 2

R1021 0Ohm /SHARE

1 2

R1022 0Ohm /SHARE

1

T1004@

1 2

R1023 0Ohm /SHARE

1 2

R1024 0Ohm /SHARE

1 2

R1025 0Ohm /SHARE

1 2

R1026 0Ohm /SHARE

USB2.0 (MB)

USB2.0 (SB)

WLAN/BT

Camera

USB2.0 (SB) @

USB3.0 (MB)

+VDD_095_USB3_DUAL

USB3.0 (MB)

SPI_CLK_HSPI_R < 30>

SPI_CS1_L_HSPI_R <30>

SPI_DO_HSPI_R <30>

SPI_DI_HSPI_R <30>

SPI_HOLD_L_HSPI_R <30>

SPI_WP_L_HSPI_R <30>

+3VA_EC

+3VSUS

@

R1040 0Ohm

R1041 0Ohm

12

12

+3VM_SPI_R

R1042 0Ohm

+3VM_SPI

D1001

1

3

2

@

1V/0.2A

12

non-Share ROM

0.1UF/16V

/NONSHARE

U1001

SPI_CS1_L_HSPI

SPI_DI_HSPI SPI2_HOLD#

SPI_WP_L_HSPI SPI2_CLK

1 2

R1031 0Ohm /NONSHARE

1 2

R1032 33Ohm /NONSHARE

1 2

R1033 0Ohm /NONSHARE

SPI2_CS#1

SPI2_SO

3VM_SPI2_WP#

1

CS#

2

DO(IO1)

3

WP#(IO2)

4

GND

W25Q32FVSSIQ

05V000000022

HOLD#/RESET#(IO3)

(32Mb)

VCC

CLK

DI(IO0)

/NONSHARE

8

7

6

5

C1030

12

+3VM_SPI

R1035 0Ohm /NONSHARE

R1036 33Ohm /NONSHARE

SPI2_SI

R1037 33Ohm /NONSHARE

1 2

1 2

1 2

SPI_HOLD_L_HSPI

SPI_CLK_HSPI

SPI_DO_HSPI

LPC

APU EC

R

/SHARE

HSPI

FSPI

R R R

4MB

ROM

4MB

ROM

/SHARE/NONSHARE /NONSHARE

/SHARE

SPI_HOLD_L_HSPI

SPI_WP_L_HSPI

SPI_CS1_L_HSPI

1 2

R1027 10KOhm

1 2

R1018 10KOhm

1 2

R1019 10KOhm

/NONSHARE/NONSHARE

128KB

ROM

Title :

Title :

Title :

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

+3VM_SPI

APU_SATA_USB_LPC_SPI_C

APU_SATA_USB_LPC_SPI_C

APU_SATA_USB_LPC_SPI_C

Mike_Chiu

Mike_Chiu

Mike_Chiu

1.2

1.2

1.2

10 99Monday, March 25, 2013

10 99Monday, March 25, 2013

10 99Monday, March 25, 2013

Rev

Rev

Rev

Page 11

S5 DOMAIN S0 DOMAIN

1 2

R1108 0Ohm

+VDDCR_NB

12

C1151

10UF/6.3V

12

C1153

1UF/6.3V

12

C1162

1UF/6.3V

+VDDCR_CPU

12

C1165

10UF/6.3V

12

C1167

1UF/6.3V

12

C1175

1UF/6.3V

+3VSUS +APU_VDD33_ALW

1 2

R1102 0Ohm

12

C1102

1UF/6.3V

+APU_VDD18_ALW+1.8VSUS

12

R11030Ohm

C1105 4.7UF/6.3V

C1106 1UF/6.3V

+VDD_095_USB3_DUAL+0.95VS+0.95VSUS

1 2

1 2

1 2

1 2

C1107 1UF/6.3V

C1108 1UF/6.3V

C1109 1UF/6.3V

C1110 1UF/6.3V

C1111 1UF/6.3V

C1112 180PF/50V

1 2

C1113 10UF/6.3V

1 2

C1114 10UF/6.3V

1 2

C1115 1UF/6.3V

1 2

C1116 1UF/6.3V

1 2

C1117 1UF/6.3V

1 2

C1118 180PF/50V

12

C1104

180PF/50V

1 2

R1106 0Ohm@

1 2

R1107 0Ohm

+VDD_0.95_ALW+0.95VSUS

C1119 1UF/6.3V

C1120 1UF/6.3V

C1121 1UF/6.3V

C1122 1UF/6.3V

Layout Notice : Place on Bottom Layer

12

12

12

C1152

10UF/6.3V

C1154

1UF/6.3V

C1163

1UF/6.3V

12

12

C1157

10UF/6.3V

C1155

1UF/6.3V

C1164

1UF/6.3V

12

C1158

10UF/6.3V

C1159

1UF/6.3V

12

12

12

12

Layout Notice : Place on Bottom Layer

12

12

12

C1166

10UF/6.3V

C1168

1UF/6.3V

C1176

1UF/6.3V

12

12

12

C1171

10UF/6.3V

C1169

1UF/6.3V

C1177

1UF/6.3V

12

12

12

C1170

180PF/50V

C1172

1UF/6.3V

C1179

1UF/6.3V

12

12

12

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

C1156

180PF/50V

C1160

1UF/6.3V

C1196

0.1UF/10V

C1173

1UF/6.3V

C1178

1UF/6.3V

+3VS +APU_VDD_33

12

C1103

1UF/6.3V

+0.95VS

@

+APU_VDD18_ALW

+VDD_095_USB3_DUAL

+VDD_0.95_ALW

PLACE C1194 CLOSE TO PIN

12

C1161

1UF/6.3V

+1.35V_DDR

12

12

C1198

C1197

0.1UF/10V

0.1UF/10V

12

C1174

1UF/6.3V

12

R1105

0Ohm

+APU_VDD33_ALW

+VCC_RTC

C1194

0.22UF/6.3V

+1.35V_DDR

+APU_VDDIO_AZ

12

U0701F

J35

3A 18A/21A

VDDIO_MEM_S_1

L32

VDDIO_MEM_S_2

L37

VDDIO_MEM_S_3

N35

VDDIO_MEM_S_4

R31

VDDIO_MEM_S_5

R37

VDDIO_MEM_S_6

U32

VDDIO_MEM_S_7

U35

VDDIO_MEM_S_8

W31

VDDIO_MEM_S_9

W32

VDDIO_MEM_S_10

W37

VDDIO_MEM_S_11

AA31

VDDIO_MEM_S_12

AA35

VDDIO_MEM_S_13

AC32

VDDIO_MEM_S_14

AC37

VDDIO_MEM_S_15

AE31

VDDIO_MEM_S_16

AE35

VDDIO_MEM_S_17

AG32

VDDIO_MEM_S_18

AG37

VDDIO_MEM_S_19

AJ35

VDDIO_MEM_S_20

AL32

VDDIO_MEM_S_21

AL37

VDDIO_MEM_S_22

AR35

VDDIO_MEM_S_23

AL10

0.1A

VDDIO_AZ_ALW_1

AL11

VDDIO_AZ_ALW_2

B1

0.5A

VDD_18_ALW_1

B2

VDD_18_ALW_2

AL13

0.2A

VDD_33_ALW_1

AM13

VDD_33_ALW_2

AR5

1A

VDD_095_USB3_DUAL_1

AU4

VDD_095_USB3_DUAL_2

AV7

VDD_095_USB3_DUAL_3

AW5

VDD_095_USB3_DUAL_4

AE11

0.5A

VDD_095_ALW_1

AE13

VDD_095_ALW_2

AJ11

VDD_095_ALW_3

AJ13

VDD_095_ALW_4

AN4

VDDBT_RTC_G

10369

1 2

R1115 10KOhm

1

JRST1101

1

2

SGL_JUMP

@

2

Layout Notice : Place on Bottom Layer

12

12

12

C1183

10UF/6.3V

C1189

1UF/6.3V

12

12

C1182

180PF/50V

C1190

1UF/6.3V

12

12

C1180

10UF/6.3V

C1187

1UF/6.3V

12

C1181

10UF/6.3V

C1188

1UF/6.3V

1 2

POWER

12

L21

VDDCR_CPU_1

L23

VDDCR_CPU_2

L25

VDDCR_CPU_3

L27

VDDCR_CPU_4

L29

VDDCR_CPU_5

N21

VDDCR_CPU_6

N23

VDDCR_CPU_7

N27

VDDCR_CPU_8

R21

VDDCR_CPU_9

R23

VDDCR_CPU_10

R27

VDDCR_CPU_11

U21

VDDCR_CPU_12

U23

VDDCR_CPU_13

U27

VDDCR_CPU_14

W21

VDDCR_CPU_15

W23

VDDCR_CPU_16

W27

VDDCR_CPU_17

AA21

VDDCR_CPU_18

AA23

VDDCR_CPU_19

AA27

VDDCR_CPU_20

AC21

VDDCR_CPU_21

AC23

VDDCR_CPU_22

AC27

VDDCR_CPU_23

AE21

VDDCR_CPU_24

AE23

VDDCR_CPU_25

AE27

VDDCR_CPU_26

L13

VDDCR_NB_1

L17

VDDCR_NB_2

N11

VDDCR_NB_3

N13

VDDCR_NB_4

N17

VDDCR_NB_5

R11

VDDCR_NB_6

R13

VDDCR_NB_7

R17

VDDCR_NB_8

U13

VDDCR_NB_9

U17

VDDCR_NB_10

W13

VDDCR_NB_11

W17

VDDCR_NB_12

AA13

VDDCR_NB_13

AA17

VDDCR_NB_14

AC13

VDDCR_NB_15

AC17

VDDCR_NB_16

AE15

VDDCR_NB_17

AE17

VDDCR_NB_18

AE19

VDDCR_NB_19

AG17

VDDCR_NB_20

AG21

VDDCR_NB_21

A2

VDD_18_1

A3

VDD_18_2

B3

VDD_18_3

C3

VDD_18_4

AM15

VDD_33_1

AM17

VDD_33_2

AG23

VDD_095_1

AG27

VDD_095_2

AJ21

VDD_095_3

AJ27

VDD_095_4

AL21

VDD_095_5

AL23

VDD_095_6

AL27

VDD_095_7

AM23

VDD_095_8

AM25

VDD_095_9

U10

VDD_095_GFX_1

W10

VDD_095_GFX_2

AA10

VDD_095_GFX_3

+VCC_RTC_R +RTC_BAT

C1101

1UF/6.3V

CMOS Settings

Clear CMOS

Keep CMOS

+VDDCR_CPU

+VDDCR_NB

15A/17A

+1.8VS

1.5A

+APU_VDD_33

0.2A

5A

0.6A

FOR TV BOARD

+1.1V_CLK will be

1.1V but it will be

0.95V for Kabini.

@

1 2

R1112 1KOhm

U1101

1

GND

3

VIN

2

VOUT

AP2138N-1.5TRG1

06V280000027

JRST1101

Shunt

Open

(Default)

+0.95VS

R1109 0Ohm

+1.5VSUS +APU_VDDIO_AZ

1 2

R1110 0Ohm@

+1.5VS

1 2

R1116 0Ohm

1 2

C1149 1UF/6.3V

1 2

C1150 10UF/6.3V

+VCC_RTC_U

12

C1199

1UF/6.3V

+1.8VS

C1133 10UF/6.3V

C1126 1UF/6.3V

C1127 1UF/6.3V

C1128 1UF/6.3V

C1129 1UF/6.3V

C1130 1UF/6.3V

C1131 1UF/6.3V

C1134 1UF/6.3V

C1132 180PF/50V

+0.95VS

3

D1101

1V/0.2A

Layout Notice : Place C1183 and C1185 close to +1.5V_DDR plane Split

12

12

12

C1184

180PF/50V

12

C1191

1UF/6.3V

12

C1185

180PF/50V

C1192

1UF/6.3V

C1186

180PF/50V

12

C1193

1UF/6.3V

12

C1195

1UF/6.3V

12

12

C1123

1UF/6.3V

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

1 2

PLACE ON TOP LAYER

1 2

C1135 4.7UF/6.3V

1 2

C1137 1UF/6.3V

1 2

C1139 180PF/50V

1 2

C1136 1UF/6.3V

1 2

C1138 1UF/6.3V

1 2

C1140 1UF/6.3V

1 2

C1141 1UF/6.3V

1 2

C1142 1UF/6.3V

1 2

C1143 1UF/6.3V

1 2

C1144 1UF/6.3V

1 2

C1148 10UF/6.3V

1 2

C1147 10UF/6.3V

1 2

C1145 1UF/6.3V

1 2

C1146 180PF/50V

1

2

C1124

1UF/6.3V

12

C1125

180PF/50V

1 2

R11011KOhm

3

4

RTC battery

+RTCBAT+3VA

12

U0701G

A8

VSS_1

A13

VSS_2

A23

VSS_3

A31

VSS_4

A35

VSS_5

A39

VSS_6

B8

VSS_7

B13

VSS_8

B23

VSS_9

B31

VSS_10

B39

VSS_11

C1

VSS_12

C2

VSS_13

C5

VSS_14

C7

VSS_15

C9

VSS_16

C11

VSS_17

C13

VSS_18

C15

VSS_19

C17

VSS_20

C19

VSS_21

C21

VSS_22

C23

VSS_23

C25

VSS_24

C27

VSS_25

C29

VSS_26

C31

VSS_27

C33

VSS_28

C35

VSS_29

C37

VSS_30

C39

VSS_31

C41

VSS_32

D9

VSS_33

D11

VSS_34

D13

VSS_35

E3

VSS_36

E4

VSS_37

E9

VSS_38

E11

VSS_39

E13

VSS_40

E27

VSS_41

E31

VSS_42

E35

VSS_43

E38

VSS_44

E39

VSS_45

G3

VSS_46

G7

VSS_47

G11

VSS_48

G13

VSS_49

G15

VSS_50

G17

VSS_51

G21

VSS_52

G25

VSS_53

G29

VSS_54

G35

VSS_55

G37

VSS_56

G39

VSS_57

G41

VSS_58

H11

VSS_59

H13

VSS_60

H23

VSS_61

H31

VSS_62

10369

J1101

BATT_HOLDER_2P

12V20GBSM000

U0701H

GND

J3

VSS_63

J7

VSS_64

J8

VSS_65

J39

VSS_66

K11

VSS_67

K13

VSS_68

K17

VSS_69

K19

VSS_70

VSS_71

VSS_72

VSS_73

VSS_74

VSS_75

VSS_76

VSS_77

VSS_78

VSS_79

VSS_80

VSS_81

VSS_82

VSS_83

VSS_84

VSS_85

VSS_86

VSS_87

VSS_88

VSS_89

VSS_90

VSS_91

VSS_92

VSS_93

VSS_94

VSS_95

VSS_96

VSS_97

VSS_98

VSS_99

VSS_100

VSS_101

VSS_102

VSS_103

VSS_104

VSS_105

VSS_106

VSS_107

VSS_108

VSS_109

VSS_110

VSS_111

VSS_112

VSS_113

VSS_114

VSS_115

VSS_116

VSS_117

VSS_118

VSS_119

VSS_120

VSS_121

VSS_122

VSS_123

VSS_124

K21

K23

K25

K27

K29

K31

L3

L7

L8

L10

L11

L15

L19

L31

L39

L41

M1

M2

N3

N7

N15

N19

N25

N29

N31

N39

P1

P2

R3

R7

R15

R19

R25

R29

R39

R41

U1

U2

U3

U7

U8

U11

U15

U19

U25

U29

U31

U39

W3

W5

W11

W15

W19

W25

AA11

AA15

AA19

AA25

AA29

AA39

AC11

AC15

AC19

AC25

AC29

AC31

AC39

AC41

AE25

AE29

AE32

AE39

AG10

AG11

AG13

AG15

AG19

AG25

AG29

AG31

AG39

AG41

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

PEGATRON UNIHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

W29

VSS_125

W39

VSS_126

W41

VSS_127

Y1

VSS_128

Y2

VSS_129

AA3

VSS_130

AA7

VSS_131

AA8

VSS_132

VSS_133

VSS_134

VSS_135

VSS_136

VSS_137

VSS_138

AC3

VSS_139

AC7

VSS_140

VSS_141

VSS_142

VSS_143

VSS_144

VSS_145

VSS_146

VSS_147

VSS_148

AE3

VSS_149

AE7

VSS_150

VSS_151

VSS_152

VSS_153

VSS_154

AG3

VSS_155

AG5

VSS_156

VSS_157

VSS_158

VSS_159

VSS_160

VSS_161

VSS_162

VSS_163

VSS_164

VSS_165

VSS_166

AH1

VSS_167

AH2

VSS_168

AJ3

VSS_169

AJ7

VSS_170

AJ15

VSS_171

AJ17

VSS_172

AJ19

VSS_173

AJ23

VSS_174

AJ25

VSS_175

AJ29

VSS_176

AJ31

VSS_177

AJ32

VSS_178

AJ39

VSS_179

AL3

VSS_180

AL8

VSS_181

AL15

VSS_182

AL17

VSS_183

AL19

VSS_184

AL25

VSS_185

AL29

VSS_186

10369

EG70_KB

EG70_KB

EG70_KB

GND

VSS_187

VSS_188

VSS_189

VSS_190

VSS_191

VSS_192

VSS_193

VSS_194

VSS_195

VSS_196

VSS_197

VSS_198

VSS_199

VSS_200

VSS_201

VSS_202

VSS_203

VSS_204

VSS_205

VSS_206

VSS_207

VSS_208

VSS_209

VSS_210

VSS_211

VSS_212

VSS_213

VSS_214

VSS_215

VSS_216

VSS_217

VSS_218

VSS_219

VSS_220

VSS_221

VSS_222

VSS_223

VSS_224

VSS_225

VSS_226

VSS_227

VSS_228

VSS_229

VSS_230

VSS_231

VSS_232

VSS_233

VSS_234

VSS_235

VSS_236

VSS_237

VSS_238

VSS_239

VSS_240

VSS_241

VSS_242

VSSBG_DAC

VBURN

Title :

Title :

Title :

Engineer:

Engineer:

Engineer:

PSEN

AL39

AL41

AM11

AM27

AM31

AN3

AN7

AN39

AP31

AR3

AR13

AR17

AR21

AR25

AR29

AR39

AR41

AU1

AU2

AU3

AU15

AU19

AU23

AU27

AU39

AV9

AW3

AW7

AW13

AW15

AW17

AW19

AW21

AW23

AW25

AW27

AW31

AW33

AW35

AW37

AW39

AW41

AY13

AY15

AY18

AY30

BA2

BA7

BA13

BA15

BA18

BA21

BA25

BA31

BA35

BA39

A15

AL31

AM29

APU_PWR & DECOUPLING

APU_PWR & DECOUPLING

APU_PWR & DECOUPLING

Mike_Chiu

Mike_Chiu

Mike_Chiu

11 99Monday, M arch 25, 2013

11 99Monday, M arch 25, 2013

11 99Monday, M arch 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 12

STRAP PINS

+3VSUS +3VSUS +3VSUS +3VSUS

12

R1206

10KOhm

LPC_CLK1_R<10>

LPC_CLK0_R<10> LPC_FRAME# <10,30,65>

LPC_CLK1_R

LPC_CLK0_R LPC_FRAME#

1 2

R1207 22Ohm

12

R1208

@

10KOhm

12

R1210

2KOhm

12

R1209

10KOhm

12

R1211

@

2.2KOhm

12

R1212

@

10KOhm

WLAN_LED <9,66>

12

R1213

2.2KOhm

OVERLAP COMMON PADS WHERE

POSSIBLE FOR DUAL-OP RESISTORS.

PLACE STRAP RESISTORS DIRECTLY

ON CLK NETS (WITHOUT ST UBS)

LPC_CLK0

BOOT FAIL TIMER

ENABLED

1

BOOT FAIL TIMER CLKGEN

DISABLED

0

(DEFAULT)

LPC_CLK1

CLKGEN

ENABLED

(DEFAULT)

DISABLED

LFRAME_L

SPI ROM

(DEFAULT)

LPC ROM

WLAN_LED

+1.8V SPI ROM

+3.3V SPI ROM

(DEFAULT)

APU_STRAPS, SOCKET, HS

APU_STRAPS, SOCKET, HS

APU_STRAPS, SOCKET, HS

Title :

Title :

Title :

Mike_Chiu

Mike_Chiu

Engineer:

Engineer:

EG70_KB

EG70_KB

EG70_KB

Engineer:

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

PEGATRON UN IHAN CORP.

‧

Size Project Name

Size Project Name

Size Project Name

C

C

C

Date: Sheet of

Date: Sheet of

Date: Sheet of

Mike_Chiu

12 99Monday, March 25, 2013

12 99Monday, March 25, 2013

12 99Monday, March 25, 2013

Rev

Rev

Rev

1.2

1.2

1.2

Page 13

5

4

+1.35V_DDR

12

+

CE1603

220UF/4V

@

+1.35V_DDR

3

Layout Note: Place these caps near SO DIMM 0

12

C1609

10UF/6.3V

12

C1610

10UF/6.3V

12

C1611

10UF/6.3V

12

C1612

10UF/6.3V

@

12

C1613

10UF/6.3V

@

12

C1620

10UF/6.3V

@

2

+0.675VS

12

C1616

1UF/6.3V

12

C1617

1UF/6.3V

12

C1618

1UF/6.3V

@

12

C1619

1UF/6.3V

@

1

0~7

8~15

16~23

24~31

32~39

40~47

48~55

56~63

M_A_D[63:0] <7,17>M_A_A[15:0]<7,17>

+1.35V_DDR +1.35V_DDR

Layout Note: Place these caps near SO DIMM 0

+1.35V_DDR

M_EVENT#<7,17>

+V_VREF_DQ_DIMM0_1

MAX: 2.68A

TDC: 2.68A

12

C1605

0.1UF/10V

1 2

R1603 1KOhm

M_EVENT#

T1601 @

12

C1624

1000PF/16V

12

C1622

1000PF/16V

12

C1606

0.1UF/10V

1

W/S=20/20

12

C1623

0.1UF/10V

W/S=20/20

12

C1625

0.1UF/10V

J1601B

75

VDD1

81

VDD3

87

VDD5

93

VDD7

99

VDD9

105

VDD11

111

VDD13

117

VDD15

123

VDD17

2

VSS1

8

VSS3

13

VSS5

19

VSS7

25

VSS9

31

VSS11

37

VSS13

43

VSS15

48

VSS17

54

VSS19

60

VSS21

65

VSS23

71

VSS25

127

VSS27

133

VSS29

138

VSS31

144

VSS33

150

VSS35

155

VSS37

161

VSS39

167

VSS41

172

VSS43

178

VSS45

184

VSS47

189

VSS49

195

VSS51

198

EVENT#

125

TEST

77

NC1

122

NC2

126

VREFCA

1

VREFDQ

DDR3_DIMM_204P

12V02GIRM001

VDD2

VDD4

VDD6

VDD8

VDD10

VDD12

VDD14

VDD16

VDD18

VSS2

VSS4

VSS6

VSS8

VSS10

VSS12

VSS14

VSS16

VSS18

VSS20

VSS22

VSS24

VSS26

VSS28

VSS30

VSS32

VSS34

VSS36

VSS38

VSS40

VSS42

VSS44

VSS46

VSS48

VSS50

VSS52

GND1

GND2

NP_NC1

NP_NC2

VTT1

VTT2

VDDSPD

76

82

88

94

100

106

112

118

124

3

9

14

20

26

32

38

44

49

55

61

66

72

128

134

139

145

151

156

162

168

173

179

185

190

196

207

208

205

206

203

204

199

MAX: 0.75A

TDC: 0.75A

+0.675VS

12

C1615

0.1UF/10V

12

C1607

0.1UF/10V

+3VS+V_VREF_CA_DIMM0_1

12

12

C1608

0.1UF/10V

C1614

2.2UF/6.3V

@

vx_c0402_small

D D

M_A_DIM0_CLK1<7>

M_A_DIM0_CLK#1<7>

M_A_DIM0_CLK0<7>

M_A_DIM0_CLK#0<7>

M_A_DIM0_CS#1<7>

M_A_DIM0_CS#0<7>

M_A_DIM0_ODT1<7>

M_A_DIM0_ODT0<7>

M_A_WE#<7,17>

M_A_RAS#<7,17>

M_A_CAS#<7,17>

C C

SMBus Slave Address: A0H

M_A_DQS[7:0]<7,17>

M_A_DQS#[7:0]<7,17>

SCLK0_DIMM<9,17>

B B

SDATA0_DIMM<9,17>

M_A_DIM0_CKE1<7>

M_A_DIM0_CKE0<7>

M_A_DQS0

M_A_DQS1

M_A_DQS2

M_A_DQS3

M_A_DQS4

M_A_DQS5

M_A_DQS6

M_A_DQS7

M_A_DQS#0

M_A_DQS#1

M_A_DQS#2

M_A_DQS#3

M_A_DQS#4

M_A_DQS#5

M_A_DQS#6

M_A_DQS#7

M_A_BS[2:0]<7, 17>

R1601 10KOhm

R1602 10KOhm

M_A_DM[7:0]<7,17>

1 2

1 2

M_A_A0

M_A_A1

M_A_A2

M_A_A3

M_A_A4

M_A_A5

M_A_A6

M_A_A7

M_A_A8

M_A_A9

M_A_A10

M_A_A11

M_A_A12

M_A_A13

M_A_A14

M_A_A15

M_A_BS2

M_A_BS1

M_A_BS0

M_A_DQS7

M_A_DQS#7

M_A_DQS6

M_A_DQS#6

M_A_DQS5

M_A_DQS#5

M_A_DQS4

M_A_DQS#4

M_A_DQS3

M_A_DQS#3

M_A_DQS2

M_A_DQS#2

M_A_DQS1

M_A_DQS#1

M_A_DQS0

M_A_DQS#0

M_A_DM7

M_A_DM6

M_A_DM5

M_A_DM4

M_A_DM3

M_A_DM2

M_A_DM1

M_A_DM0

J1601A

98

A0

97

A1

96

A2

95

A3

92

A4

91

A5

90

A6

86

A7

89

A8

85

A9

107

A10/AP

84

A11

83

A12/BC#

119

A13

80

A14

78

A15

102

CK1

104

CK1#

101

CK0

103

CK0#

121

S1#

114

S0#

120

ODT1

116

ODT0

113

WE#

110

RAS#

115

CAS#

79

BA2

108

BA1

109

BA0

74

CKE1

73

CKE0

201

SA1

197

SA0

188

DQS7

186

DQS#7

171

DQS6

169

DQS#6

154

DQS5

152

DQS#5

137

DQS4

135

DQS#4

64

DQS3

62

DQS#3

47

DQS2

45

DQS#2

29

DQS1

27

DQS#1

12

DQS0

10

DQS#0

187

DM7

170

DM6

153

DM5

136

DM4

63

DM3

46

DM2

28

DM1

11

DM0

202

SCL

200

SDA

DDR3_DIMM_204P

12V02GIRM001

M:1202-00EE000

S:1202-00KB000

0

1

2

3

4

5

6

7

DQ10

DQ11