PC Pelser SMT340, SMT360, SMT380 User Manual

Preliminary Page 1 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

SMT340/360/380

User Manual

Preliminary Page 2 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

TABLE OF CONTENTS

Page

1. REVISION HISTORY................................................................................................................................................4

2. RELATED DOCUMENTATION...............................................................................................................................5

2.1 APPLICABLE DOCUMENTS .........................................................................................................................................5

2.2 REFERENCE DOCUMENTS ..........................................................................................................................................5

3. SUPPORTED HARDWARE......................................................................................................................................6

4. SCOPE ........................................................................................................................................................................7

5. TECHNICAL DESCRIPTION...................................................................................................................................8

6. INTERFACES...........................................................................................................................................................10

7. SMT380 SPECIFICATIONS....................................................................................................................................12

8. CONFIGURATION..................................................................................................................................................13

8.1 SMT340/360/360 DIP SWITCH SELECTABLE OPTIONS...............................................................................................13

8.1.1 Clock source selection...................................................................................................................................14

8.1.2 Capture Mode selection.................................................................................................................................14

8.2 LED INDICATORS....................................................................................................................................................15

9. PRECAUTIONS .......................................................................................................................................................16

10. POWER SUPPLY.....................................................................................................................................................17

11. DEMONSTRATION SOFTWARE..........................................................................................................................18

12. APPENDIX A : SAMPLE DATA.............................................................................................................................19

12.1 SMT340 SAMPLE PLOTS.....................................................................................................................................19

12.2 SMT360 SAMPLE PLOTS.....................................................................................................................................20

12.3 SMT380 SAMPLE PLOTS ....................................................................................................................................22

13. APPENDIX B : CROSS-TALK MEASUREMENTS...............................................................................................24

13.1 SMT360 CROSS-TALK........................................................................................................................................24

13.2 SMT380 CROSS-TALK........................................................................................................................................26

14. APPENDIX C : SYSTEM SET-UP FOR EXECUTING TEST PROGRAM..........................................................28

Preliminary Page 3 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

LIST OF FIGURES

Page

Fig. 1 : SMT340/360/380 TIM ADC Block diagram................................................................8

Fig. 2 : Physical Layout of the SMT340/360/380..................................................................10

Fig. 3 : Full scale 1.4MHz filtered input signal sampled at 40MHz.......................................19

Fig. 4 : Full scale 1.4MHz filtered input signal sampled at 65MHz.......................................20

Fig. 5 : Full scale 15MHz unfiltered input signal sampled at 65MHz....................................20

Fig. 6 : Full scale 30MHz unfiltered input signal sampled at 65MHz....................................21

Fig. 7 : Full scale 1.4MHz filtered input signal sampled at 100MHz..................................... 22

Fig. 8 : Full Scale 10 MHz unfiltered input signal sampled at 100 MHz ...............................22

Fig. 9 : Full Scale 25 MHz unfiltered input signal sampled at 100 MHz ...............................23

Fig. 10 : Full Scale 45 MHz unfiltered input signal sampled at 100 MHz..............................23

Fig. 11 : 1.4 MHz cross-talk with unused-input terminated...................................................24

Fig. 12 : 15 MHz cross-talk with unused-input terminated.................................................... 24

Fig. 13 : 30 MHz cross-talk with unused-input terminated.................................................... 25

Fig. 14 : 1.4 MHz cross-talk with unused-input terminated...................................................26

Fig. 15 : 10 MHz cross-talk with unused-input terminated.................................................... 26

Fig. 16 : 25 MHz cross-talk with unused-input terminated.................................................... 27

Fig. 17 : 45 MHz cross-talk with unused-input terminated ................................................... 27

Fig. 18 : SMT340/360/380 Test set-up..................................................................................28

LIST OF TABLES

Page

Table 1 : SMT340/360/380 Specifications.............................................................................12

Table 2 : SMT340/360/380 switch S1 set-up......................................................................... 13

Table 3 : SMT340/360/380 switch S2 set-up......................................................................... 14

Preliminary Page 4 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

1. REVISION HISTORY

Date Description of Changes Revision Issue

25/05/01 Initial release of combined document 01 01

Preliminary Page 5 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

2. RELATED DOCUMENTATION

2.1 Applicable Documents

This document replaces the following documents:

[1] SMT340R2 User Manual,

Petrus Pelser, July 2000

Document No: SMT340R2_User_Manual.doc

[2] SMT360 User Manual,

Petrus Pelser / Marius Vogel, November 2000

Document No: SMT360_User_Manual_Rev01_I2.doc

[3] SMT380 User Manual,

Petrus Pelser / Marius Vogel, November 2000

Document No: SMT380_User_Manual_Rev01_I2.doc

2.2 Reference Documents

[4] Low Distortion Differential ADC Driver,

Analog Devices, 1999

Document No: AD8138_a.pdf

[5] 12-Bit 80MSPS/105MSPS A/D Converter,

Analog Devices, 2000

Document No: AD9432_c.pdf

Preliminary Page 6 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

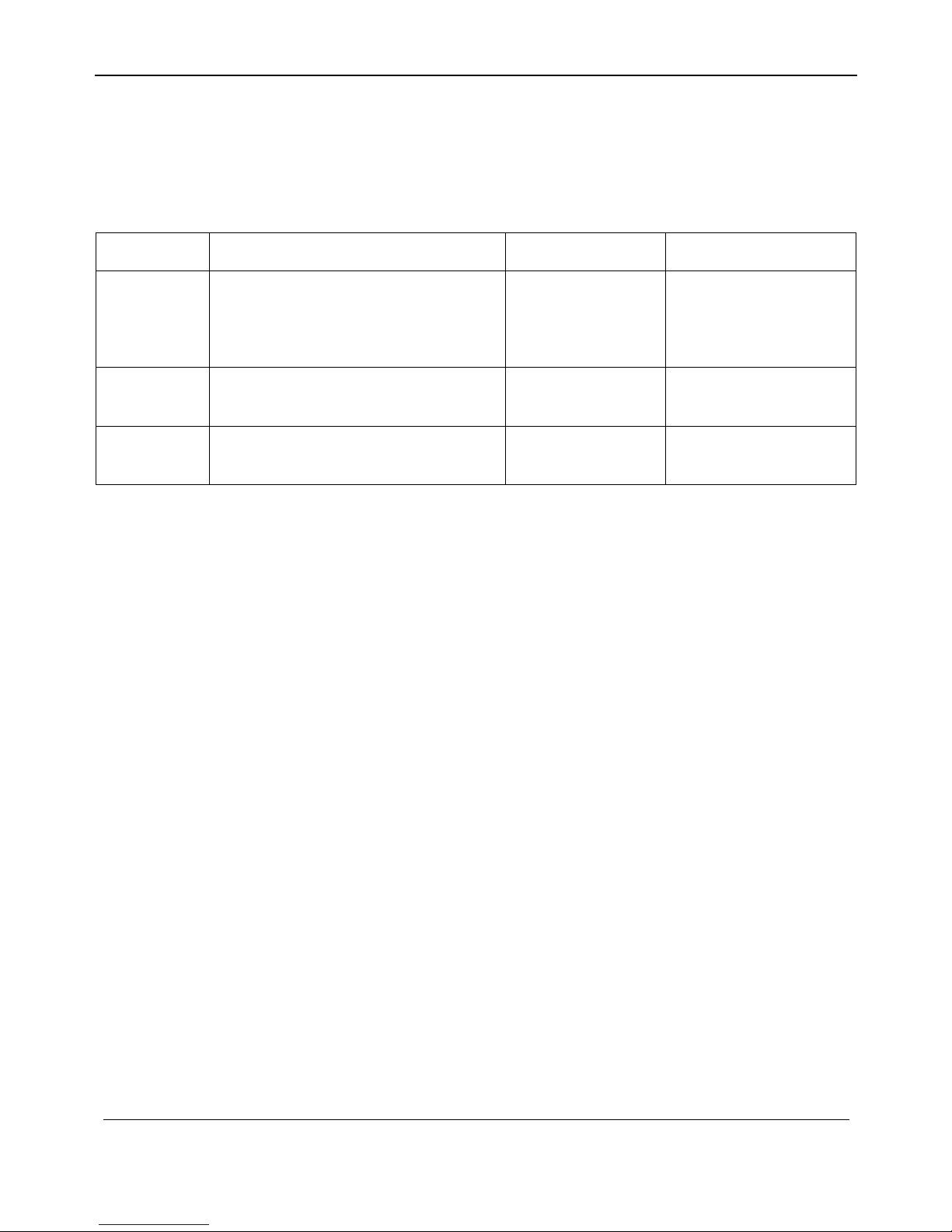

3. SUPPORTED HARDWARE

This User Manual supports the following hardware:

Module PCB Revisions Oscillator On PCB Firmware Revisions

SMT340 SMT340 Revision 02 and higher

PCB labelled as SMT380-02 or

SMT380-03

40 MHz All firmware revisions

SMT360 PCB labelled as SMT380-02 or

SMT380-03

64 MHz All firmware revisions

SMT380 PCB labelled as SMT380-02 or

SMT380-03

105 MHz All firmware revisions

Preliminary Page 7 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

4. SCOPE

This document describes the SMT340, the SMT360 and the SMT380 TIM ADC from a User’s

perspective.

The SMT340 is a single width TIM-40 compliant module consisting of a dual channel 40MHz, 12-Bit

ADC. Data output is via two Sundance Digital Bus Connectors (SDB). An FPGA on the module controls

various modes of Sampling and Data routing.

The SMT360 is a single width TIM-40 compliant module consisting of a dual channel 65MHz, 12-Bit

ADC. Data output is via two Sundance Digital Bus Connectors (SDB). An FPGA on the module controls

various modes of Sampling and Data routing.

The SMT380 is a single width TIM-40 compliant module consisting of a dual channel 105MHz, 12-Bit

ADC. Data output is via four Sundance Digital Bus Connectors (SDB). An FPGA on the module controls

various modes of Sampling and Data routing.

The SMT340/360/380 makes use of the Analog Devices AD9432 ADC to realise a high speed 12-bit

Analogue to Digital Converter. The SMT380 does not implement any filters in the signal paths, the

analogue signal is buffered with a differential buffer (AD8138) before the ADC samples it (For more

information see the AD9432 and AD8138 datasheets as listed above in Reference Documents).

The module is typically suitable for the following applications

• Communications

• Base stations and ‘Zero-IF’ Subsystems

• Wireless Local Loop (WLL)

• Local Multipoint Distribution Service (LMDS)

• HDTV Broadcast Cameras and Film Scanners

Preliminary Page 8 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

5. TECHNICAL DESCRIPTION

Fig. 1 : SMT340/360/380 TIM ADC Block diagram

Fig. 1 shows the block diagram of the SMT340/360/380 TIMADC. The following section describes this

family of TIMADCs from a user’s point of view. Reference is made to the different blocks in Fig. 1.

The ADC section implements a high speed Analogue-to-digital converter (12-bit, maximum 105 MHz,

AD9432). ADC Sampling and clock selection is done under control of the FPGA via the Clock Buffering

circuitry.

The Clock Buffering circuitry consists of high-speed differential ECL devices capable of supplying a

very accurate low Jitter differential clock to the ADC. The Clock Buffering circuitry also selects between

the External Clock and onboard Oscillator as the clock source for the ADC.

An external enable/trigger input is available on the SMT340/360/380. Function selection of this signal

between ADC Enable or ADC trigger is done under DIP switch control. When configured as an enable,

ADC Sampling can be selectively enabled (gated) allowing for accurate user control of the data capturing

Control

ADC A Data ABuffer

Ji5/

Ji6

Input A

ADC B Data BBuffer

Ji7/

Ji8

Input B

Clock

Control

External clock

Ji1/

Ji2

40MHz,

64MHz or

105MHz

Channel A

SDB

Jo3

Channel B

SDB

Jo1

Switch S1

Switch S2

Ji3/

Ji4

External Enable/Trigger

Rev01, Issue 01

SMT3x0_Block_Rev01_Iss01.vsd

SDB

Jo4

SDB

Jo2

Jo2 and Jo4 are only

used on the SMT380

Preliminary Page 9 of 28

Document Name: SMT340_360_380_User_Manual_Rev01_Iss01.doc Revision: 01

Document Number: TBD Original Date: 25 June 2001

Author: PC Pelser / MR Vogel Revision Date: 25 June 2001

Document Title: SMT340/360/380 User Manual

sizes this is especially relevant in burst mode applications. The SMT340/360/380 will capture data for as

long as the external enable signal is active high.

When configured as a trigger ADC sampling for a specified burst size will be performed each time the

trigger is asserted active. The SMT340/60/80 starts to capture N samples once it detects a rising edge on

the external trigger. The amount of samples to be captured per trigger event (N) is determined by DIP

Switch S2, the amount of blocks to be captured during trigger mode is specified with the LSB 7 bits of S2

(Block size is hardwired to 128 samples).

The user can also select a capture mode where the SMT340/60/80 is permanently enabled irrespective of

the external enable/trigger input.

A FPGA serves as the main controller on the SMT340/60/80. The following functions are implemented

in the FPGA:

§ ADC and Clock Control

§ ADC Data Routing to the SDB connectors

The user can select different data formats to be used, 16-bit sign-extended over one SDB, 16-bit signextended over two SDBs (only SMT380), 8-bit packed over one SDB, 8-bit packed over two SDBs (only

SMT380) or test-words. These output formats are DIP switch selectable, for more detail see section 8.1.

Loading...

Loading...