PC Concepts SHG2 DP User Manual

®

Intel

Technical Product Specification

SHG2 DP Server Board

Intel Order Number C11343-001

Revision 1.0

Enterprise Platforms and Services Division

Intel Order Number C11343-001

June 2002

Revision History Intel® SHG2 DP Server Board Technical Product Specification

Revision History

Date Revision

Number

06/05/02 1.0 Final draft.

Modifications

Disclaimers

Information in this document is provided in connection with Intel® products. No license, express

or implied, by estoppels or otherwise, to any intellectual property rig ht s is granted by this

document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel

assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating t o

sale and/or use of Intel products including liability or warranties relating to fitness for a particular

purpose, merchantability, or inf r ingement of any patent, copyright or other intellectual property

right. Intel products ar e not intended for use in medical, lif e saving, or life sustaining

applications.

Intel may make changes to specif icat ions and pr oduct descr ipt ions at any time, without notice.

®

The Intel

cause the product to deviate from published specif icat ions. Current characterized errata will be

available on request.

2

C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the

I

2

C bus/protocol and was developed by Intel Corporation. Implementat ions of the I2C

I

bus/protocol or the SMBus bus/protocol may require licenses from various entities, including

Philips Electronics N.V. and North Am er ic an Philips Cor p or at ion.

SHG2 Server Board may contain design defects or er r or s known as errata that may

®

is a trademark or reg ister ed t r ademark of Intel Corporation or its subsidiaries in the

Intel

United States and other countries.

Copyright © Intel Corporation 2002. *Other nam es and br ands m ay be claimed as the pr oper t y

of others.

ii Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification Table of Contents

Table of Contents

1. Introduction............................................................................................................ 1

1.1 SHG2 Architecture Overview...............................................................................2

1.2 Document Structure and Outline.........................................................................4

2. Processor and Chipset ......................................................................................... 6

2.1 Overview..............................................................................................................6

2.2 Processor Support...............................................................................................6

2.2.1 Processor Bus Termination/Regulation/Power..............................................7

2.2.2 Miscellaneous Processor Subsystem Logic...................................................7

2.2.3 Server Management Registers and Sensors.................................................7

2.2.4 ServerWorks* Grand Champion* LE Chipset ................................................8

2.2.5 CMIC-LE

2.3 Memory Subsystem.............................................................................................9

2.3.1 Chipkill*..........................................................................................................9

2.3.2 Memory Configuration....................................................................................9

2.3.3 CIOB-X2

2.4 CSB5 South Bridge...........................................................................................11

2.4.1 PCI Interface................................................................................................12

2.4.2 PCI Bus Master IDE Interface......................................................................12

2.4.3 USB Interface ..............................................................................................12

2.4.4 BIOS Flash ..................................................................................................12

....................................................................................................8

...................................................................................................11

2.4.5 Compatibility Interrupt Control .....................................................................12

2.4.6 Power Management

2.4.7 General Purpose Input and Output Pins......................................................13

Revision 1.0 Intel Order Number C11343-001

........................................................................................13

iii

Table of Contents Intel® SHG2 DP Server Board Technical Product Specification

2.5 Chipset Support Components...........................................................................14

2.5.1 Legacy I/O (Super I/O) National* PC87417VLA...........................................14

3. Baseboard PCI I/O Subsystem........................................................................... 18

3.1 Overview............................................................................................................18

3.2 64-bit/100MHz PCI-X Subsystem......................................................................18

3.2.1 Device IDs (IDSEL)......................................................................................18

3.2.2 64/100MHz PCI-X Arbitration.......................................................................19

3.2.3 82544GC Gigabit Ethernet Controller..........................................................19

3.3 64-bit/133MHz PCI-X Subsystem......................................................................19

3.3.1 Device IDs (IDSEL)......................................................................................19

3.3.2 64/133MHz Segment Arbitration..................................................................19

3.3.3 Ultra 160 SCSI Controller (Adaptec* AIC- 7899).........................................20

3.4 Modular RAID Capable PCI Slot 6 ....................................................................20

3.5 32-bit/33-MHz PCI Subsystem..........................................................................20

3.5.1 Device IDs (IDSEL)......................................................................................21

3.5.2 32/33 MHz PCI Arbitration...........................................................................21

3.5.3 Network Interface Controller (NIC)...............................................................21

3.5.4 Video Controller...........................................................................................22

3.6 Interrupt Routing................................................................................................23

3.6.1 Serialized IRQ support.................................................................................26

3.6.2 IRQ scan for PCIIRQ ...................................................................................26

4. Clock Generation and Distribution .................................................................... 27

5. Server Management ............................................................................................ 29

5.1 Sahalee Baseboard Management Controller....................................................30

5.2 System Reset Control........................................................................................31

iv

Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification Table of Contents

5.2.1 Power-up Reset...........................................................................................31

5.2.2 Hard Reset...................................................................................................32

5.2.3 Soft Reset....................................................................................................32

5.3 Intelligent Platform Management Buses............................................................33

6. Error Reporting and Handling............................................................................ 35

6.1 Error Sources and Types...................................................................................35

6.2 Handling and Logging System Errors................................................................35

6.2.1 Logging Format Conventions .......................................................................35

6.3 System Management Interrupt (SMI) Handler...................................................37

6.3.1 PCI Bus Error...............................................................................................37

6.3.2 Intel Xeon Processor Bus Error..............................................................37

6.3.3 Memory Bus Error ........................................................................................37

6.3.4 System Limit Error .......................................................................................37

6.3.5 Processor Failure .........................................................................................37

6.3.6 Boot Event...................................................................................................38

6.3.7 Chip Set Failure...........................................................................................38

6.4 Firmware (BMC)................................................................................................38

6.4.1 System Event Log (SEL) Full.......................................................................38

6.4.2 Timestamp Clock.........................................................................................38

6.4.3 Fault Resilient Booting.................................................................................38

6.5 Error Messages and Error Codes......................................................................39

6.5.1 Alert Standard Forum (ASF) Progress Codes..............................................40

6.5.2 Power-On Self Test (POST) Codes.............................................................40

6.5.3 POST Error Codes and Messages ..............................................................44

6.5.4 Liquid Crystal Display (LCD)........................................................................46

Revision 1.0 Intel Order Number C11343-001

v

Table of Contents Intel® SHG2 DP Server Board Technical Product Specification

7. Jumpers ............................................................................................................... 48

7.1 Hardware Configuration.....................................................................................48

8. Connections ......................................................................................................... 50

8.1 Connector Locations .........................................................................................50

8.2 Power Distribution Board Interface Connector..................................................51

8.3 SCSI Connectors...............................................................................................52

8.4 Floppy Connector..............................................................................................53

8.5 IDE Connectors.................................................................................................54

8.6 Front Panel Interface.........................................................................................55

8.7 Processor Connector.........................................................................................56

8.8 System Management Interfaces........................................................................60

8.8.1 ICMB Connector ..........................................................................................60

2

8.8.2 Auxiliary I

C* Connector ..............................................................................60

8.9 Baseboard Fan Connectors...............................................................................61

8.9.1 Fan Connector Pin-out.................................................................................63

8.10 Standard I/O Panel Connectors......................................................................64

8.10.1 Universal Serial Bus (USB) Interface.........................................................65

8.10.2 Mouse and Keyboard Ports.......................................................................66

8.10.3 Serial Ports................................................................................................66

8.10.4 Parallel Port ...............................................................................................67

8.10.5 Video Port..................................................................................................68

8.10.6 Ethernet Connectors..................................................................................68

8.11 Connector Manufacturers and Part Numbers.................................................70

9. General Specifications........................................................................................ 72

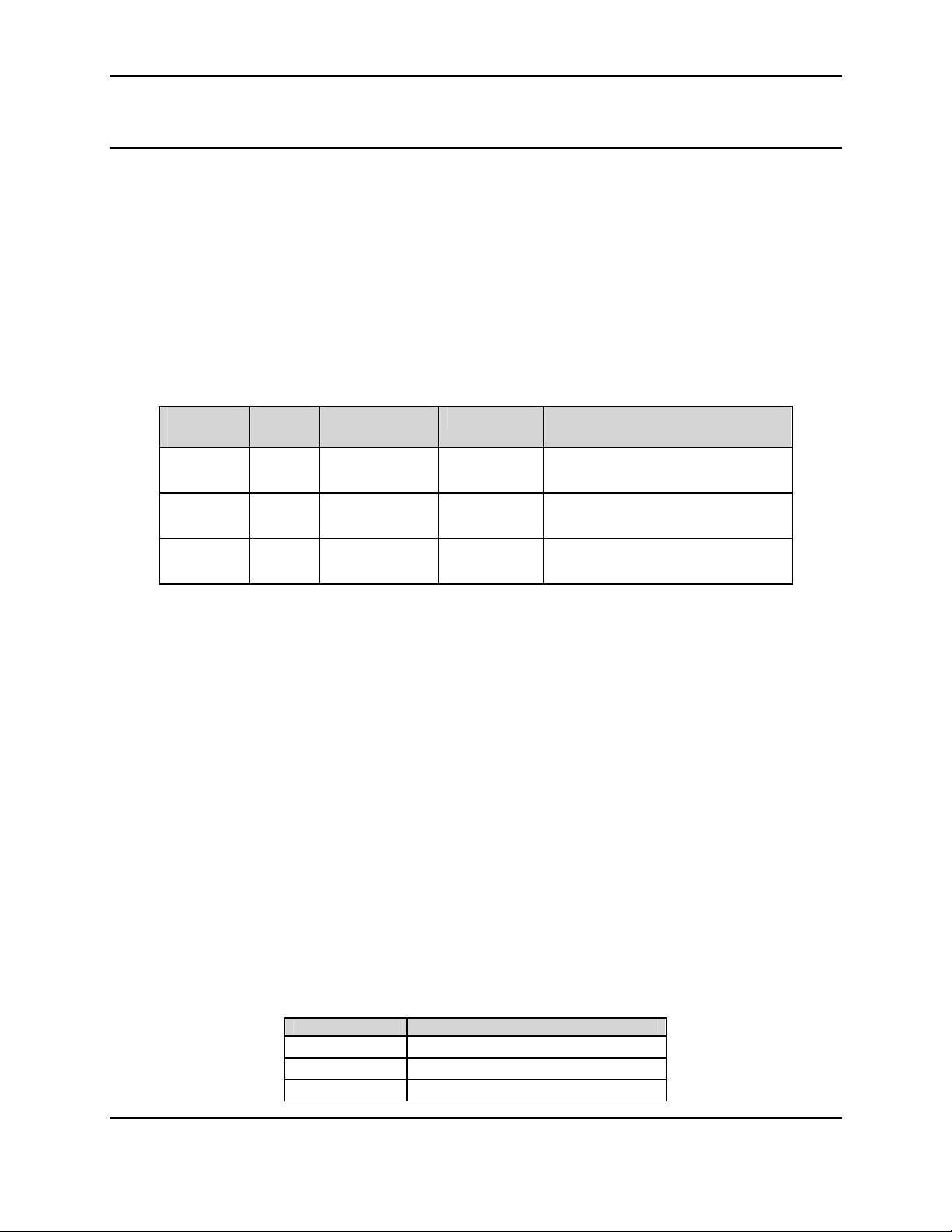

9.1 Absolute Maximum Electrical and Thermal Ratings..........................................72

vi

Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification Table of Contents

9.2 Airflow Specification for CIOB-X2 and CMIC-LE...............................................73

9.3 Electrical Specifications.....................................................................................73

9.3.1 Power Consumption.....................................................................................73

9.3.2 Power Supply Specifications........................................................................74

10. Mechanical Specifications.................................................................................. 78

11. Regulatory and Integration Information ............................................................ 80

11.1 Product Regulatory Compliance.....................................................................80

11.1.1 Product Safety Compliance .......................................................................80

11.1.2 Product EMC Compliance..........................................................................80

11.1.3 Product Regulatory Compliance Markings.................................................80

11.2 Electromagnetic Compatibility Notices ...........................................................80

11.2.1 Europe (CE Declaration of Conformity) .....................................................80

11.2.2 Australian Communications Authority (ACA) (C-Tick Declaration of

Conformity)..............................................................................................................81

11.2.3 Ministry of Economic Development (New Zealand) Declaration of

Conformity...............................................................................................................81

11.2.4 BSMI (Taiwan)...........................................................................................81

11.3 Replacing the Back up Battery.......................................................................81

Appendix A: Glossary.................................................................................................. I

Appendix B: Reference Documents.......................................................................... III

Revision 1.0 Intel Order Number C11343-001

vii

List of Figures Intel® SHG2 DP Server Board Technical Product Specification

List of Figures

Figure 1. Intel® SHG2 Server Board...............................................................................1

Figure 2. SHG2 Server Board Placement Diagram........................................................2

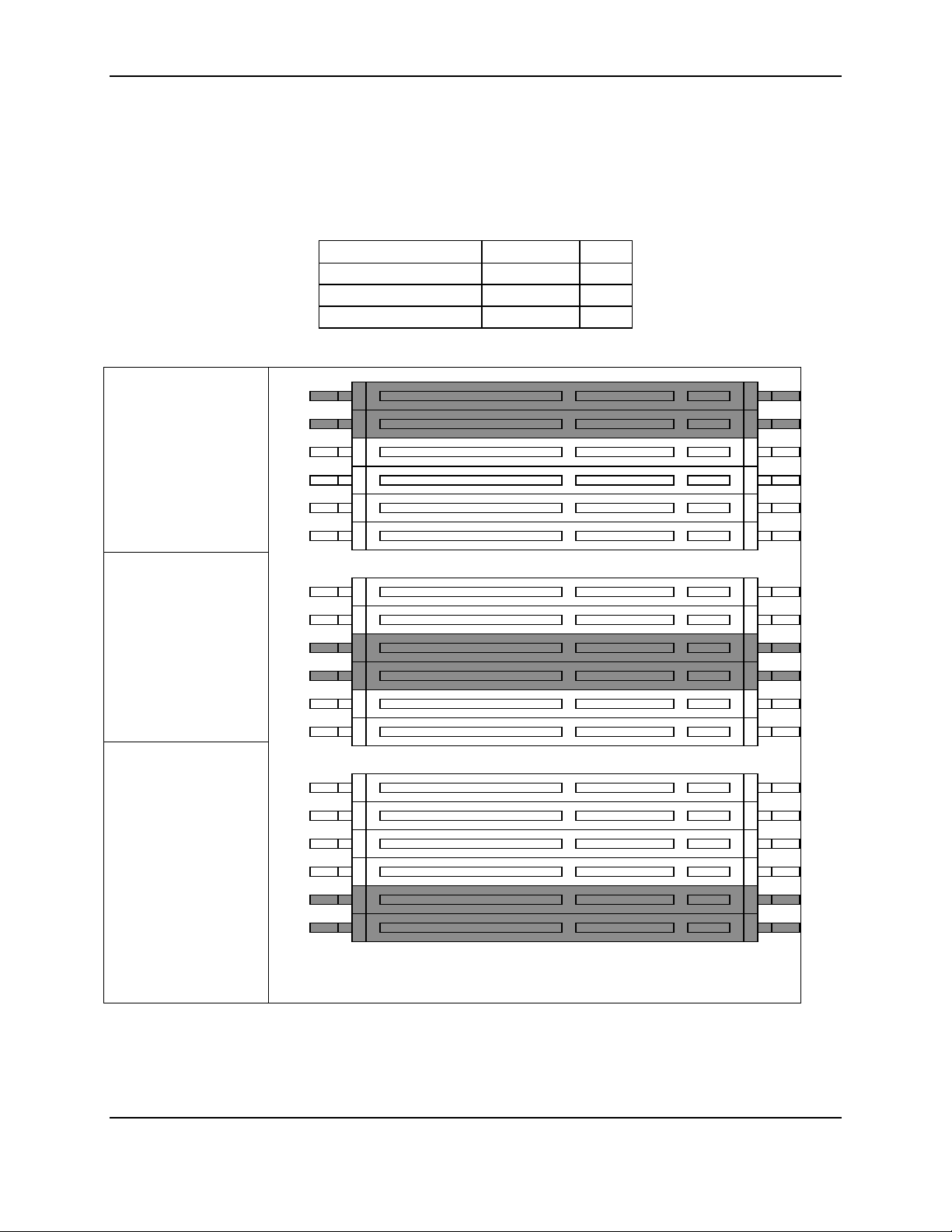

Figure 3. SHG2 Memory Bank Layout..........................................................................10

Figure 4. SHG2 Interrupt Routing (PIC Mode)..............................................................24

Figure 5. SHG2 Interrupt Routing (Symmetric Mode)...................................................25

Figure 6. SHG2 Baseboard Clock Distribution.............................................................28

Figure 7. SHG2 Sahalee BMC Block Diagram.............................................................29

Figure 8. Basic Reset Flow...........................................................................................32

Figure 9. Jumper Location.............................................................................................48

Figure 10. SHG2 Baseboard Connector Identification and Locations...........................50

Figure 11. SHG2 Board Fan Connector Locations........................................................61

Figure 12. SHG2 System Redundant Cooling Fan Support..........................................62

Figure 13. SHG2 I/O Panel Connector Graphical Locations.........................................64

Figure 14. SHG2 I/O Panel Connector Location Dimensions........................................69

Figure 15. Output Voltage Timing..................................................................................75

Figure 16. Turn On/Off Timing ......................................................................................76

Figure 17. SHG2 Baseboard Mechanical Diagram 1.....................................................78

Figure 18. SHG2 Baseboard Mechanical Diagram 2.....................................................79

viii

Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification List of Tables

List of Tables

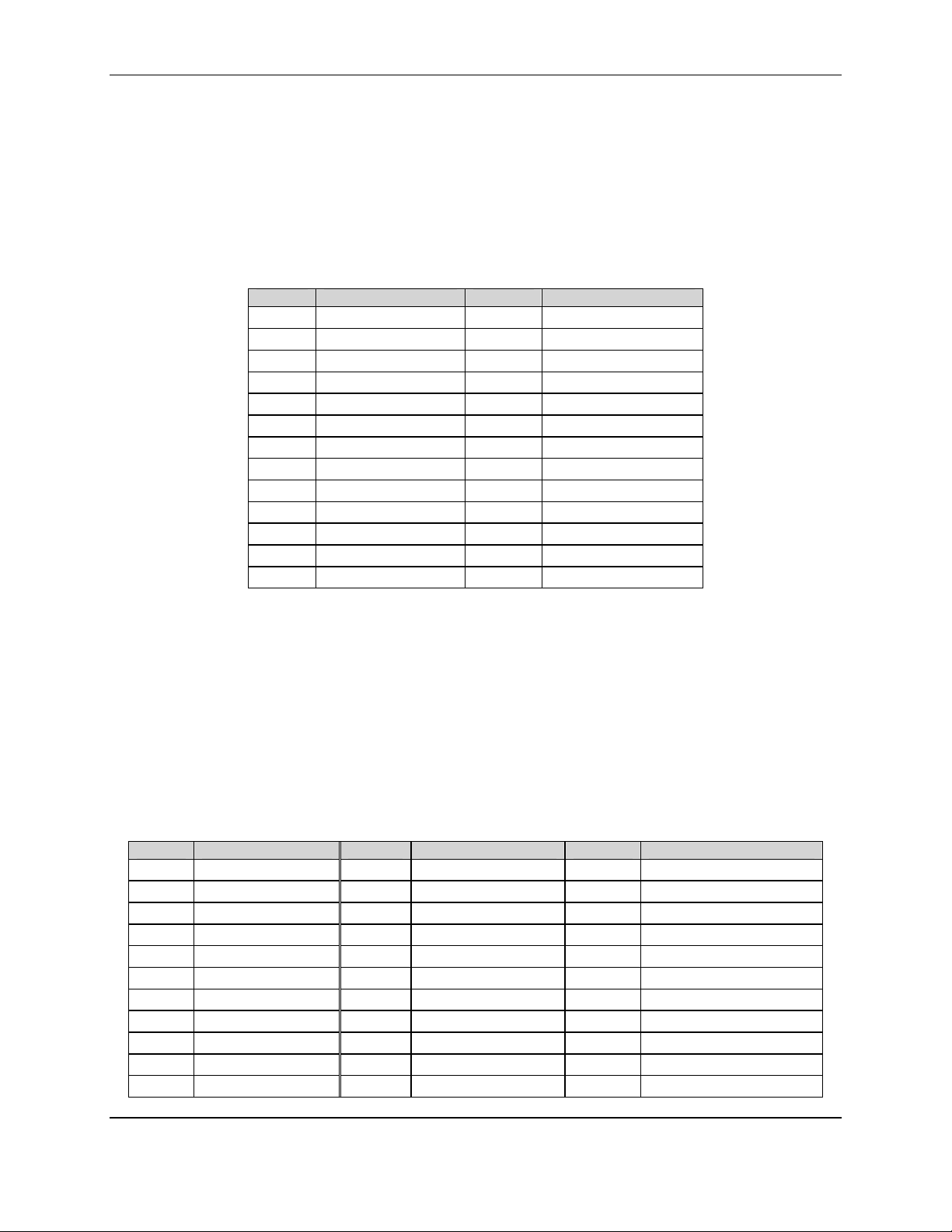

Table 1. Memory DIMM Pairs.......................................................................................10

Table 2. CSB5 GPIO Usage Table...............................................................................13

Table 3. Serial Port Connector Pinout..........................................................................14

Table 4. Parallel Port Connector Pinout.......................................................................15

Table 5. Floppy Port Connector Pinout........................................................................15

Table 6. Keyboard Connector Pinout...........................................................................16

Table 7. Mouse Connector Pinout................................................................................16

Table 8. Super I/O* GPIO Usage Table .......................................................................16

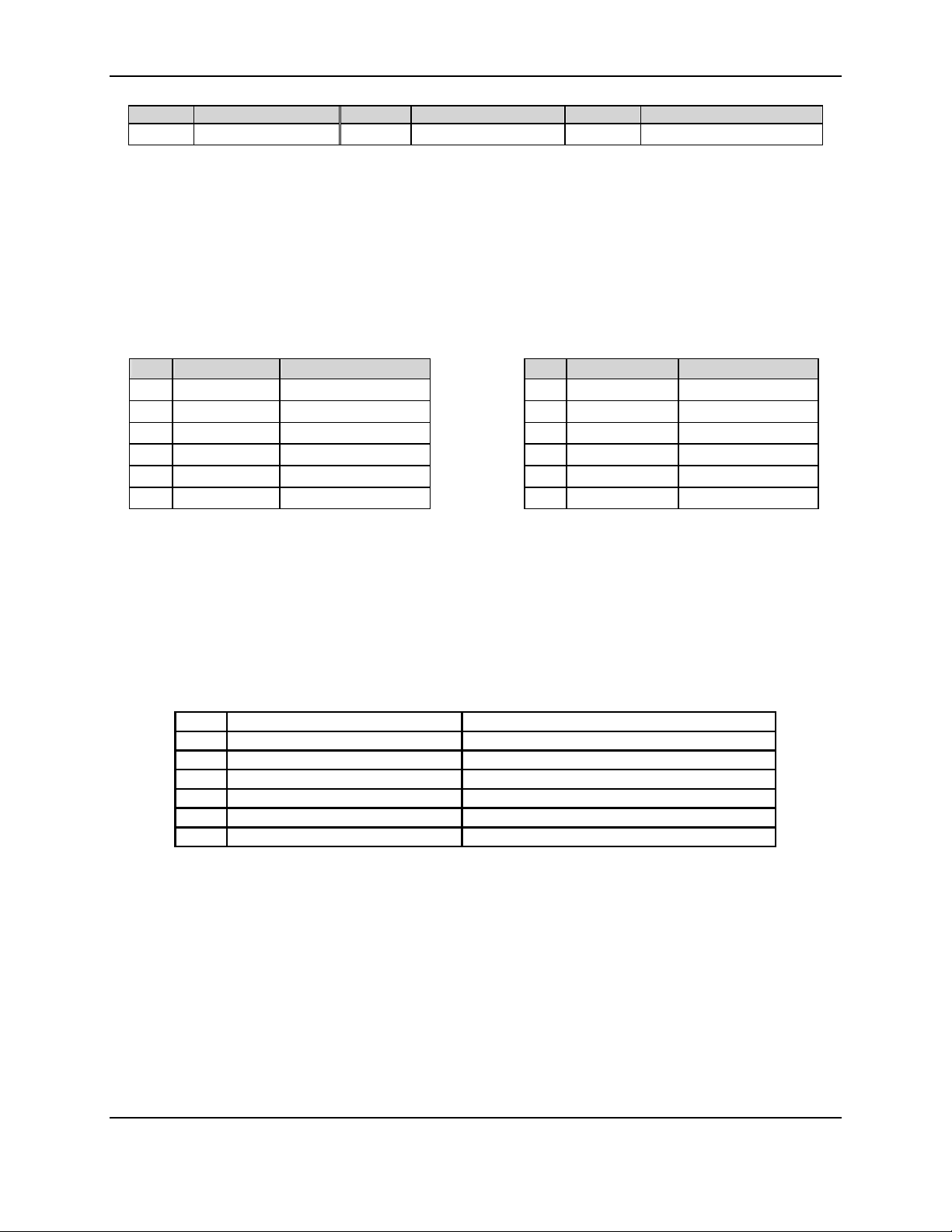

Table 9. PCI(-X) Bus Segment Characteristics............................................................18

Table 10. 64/100MHz Segment Configuration IDs........................................................18

Table 11. 64/100MHz Segment Arbitration Connections ..............................................19

Table 12. 64/133MHz Segment Configuration IDs........................................................19

Table 13. 64/133 MHz Segment Arbitration Connections .............................................20

Table 14. 32/33MHz Segment Configuration IDs..........................................................21

Table 15. 32/33MHz Segment Arbitration Connections ................................................21

Table 16. Standard VGA Modes ...................................................................................22

Table 17. Video Port Connector Pinout.........................................................................23

Table 18. ADM1026* Input Definition............................................................................30

Table 19. Temperature Sensors....................................................................................31

Table 20: IPMB Bus Devices........................................................................................33

Table 21. Private I2C* Bus 1 Devices............................................................................33

2

Table 22: Private I

Table 23: Private I

Table 24: Private I

Table 25: Private I

C* Bus 2 Devices............................................................................33

2

C* Bus 3 Devices............................................................................34

2

C* Bus 4 Devices............................................................................34

2

C* Bus 5 Devices............................................................................34

Table 26. BIOS Logging SEL List..................................................................................36

Table 27. Event Request Message Event Data Field Contents.....................................36

Table 28. Event Request Message Event Data Field Contents.....................................40

Table 29. Port-80h Code Definition...............................................................................40

Table 30. Standard BIOS POST Codes........................................................................41

Revision 1.0 Intel Order Number C11343-001

ix

List of Tables Intel® SHG2 DP Server Board Technical Product Specification

Table 31. Recovery BIOS POST Codes........................................................................44

Table 32. POST Error Messages and Codes................................................................45

Table 33. SHG2 Configuration Jumper Options............................................................49

Table 34. SHG2 Baseboard Connectors.......................................................................50

Table 35. Main Power Connector..................................................................................51

Table 36. +12V Power Connector.................................................................................51

2

Table 37. Power Connector for I

C* Bus.......................................................................52

Table 38. 68-pin SCSI Connector Pin-out.....................................................................52

Table 39. Legacy 34-pin Floppy Connector Pin-out ......................................................53

Table 40. Primary/Secondary IDE 40-pin Connector Pinout .........................................54

Table 41. AT Front Panel Header Pinout......................................................................55

Table 42. Intel

®

Xeon™ Processor Connector Pinout...................................................56

Table 43. ICMB Connector Pin-out................................................................................60

Table 44. IPMB Connector Pinout.................................................................................60

Table 45. SC5200 Fan Implementation........................................................................63

Table 46. Fan Connector Pinout ...................................................................................63

Table 47. I/O Panel Connectors....................................................................................65

Table 48. USB Connector .............................................................................................65

Table 49. Internal USB Connector.................................................................................65

Table 50. Mouse and Keyboard Ports...........................................................................66

Table 51. Serial A Port Connector.................................................................................66

Table 52. Serial B Port Header: COM2/EMP ................................................................67

Table 53. Parallel Port Connector.................................................................................67

Table 54. Video Connector............................................................................................68

Table 55. Ethernet Connectors .....................................................................................68

Table 56. LAN1 10/100 LED Schemes .........................................................................69

Table 57. LAN2 10/100/1000 LED Schemes ................................................................69

Table 58. Baseboard Connector Manufacturer Part Numbers......................................70

Table 59. Absolute Maximum Electrical and Thermal Specifications............................72

Table 60. Thermal Specification for Key Components..................................................72

Table 61. Airflow Specification for Key Components.....................................................73

Table 62. SHG2 Power Budget.....................................................................................73

Table 63. SHG2 DC Power Supply Voltage Specification.............................................74

x

Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification List of Tables

Table 64. SHG2 Ripple and Noise Specification...........................................................74

Table 65. Voltage Timing Parameters...........................................................................74

Table 66. Turn On/Off Timing........................................................................................75

Table 67. Transient Load Requirements.......................................................................77

Revision 1.0 Intel Order Number C11343-001

xi

List of Tables Intel® SHG2 DP Server Board Technical Product Specification

< This page intentionally left blank. >

xii

Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification Introduction

1. Introduction

This chapter provides an architectural overview of the Intel® SHG2 Server Board, including

functional blocks and the electrical r elat ionships.

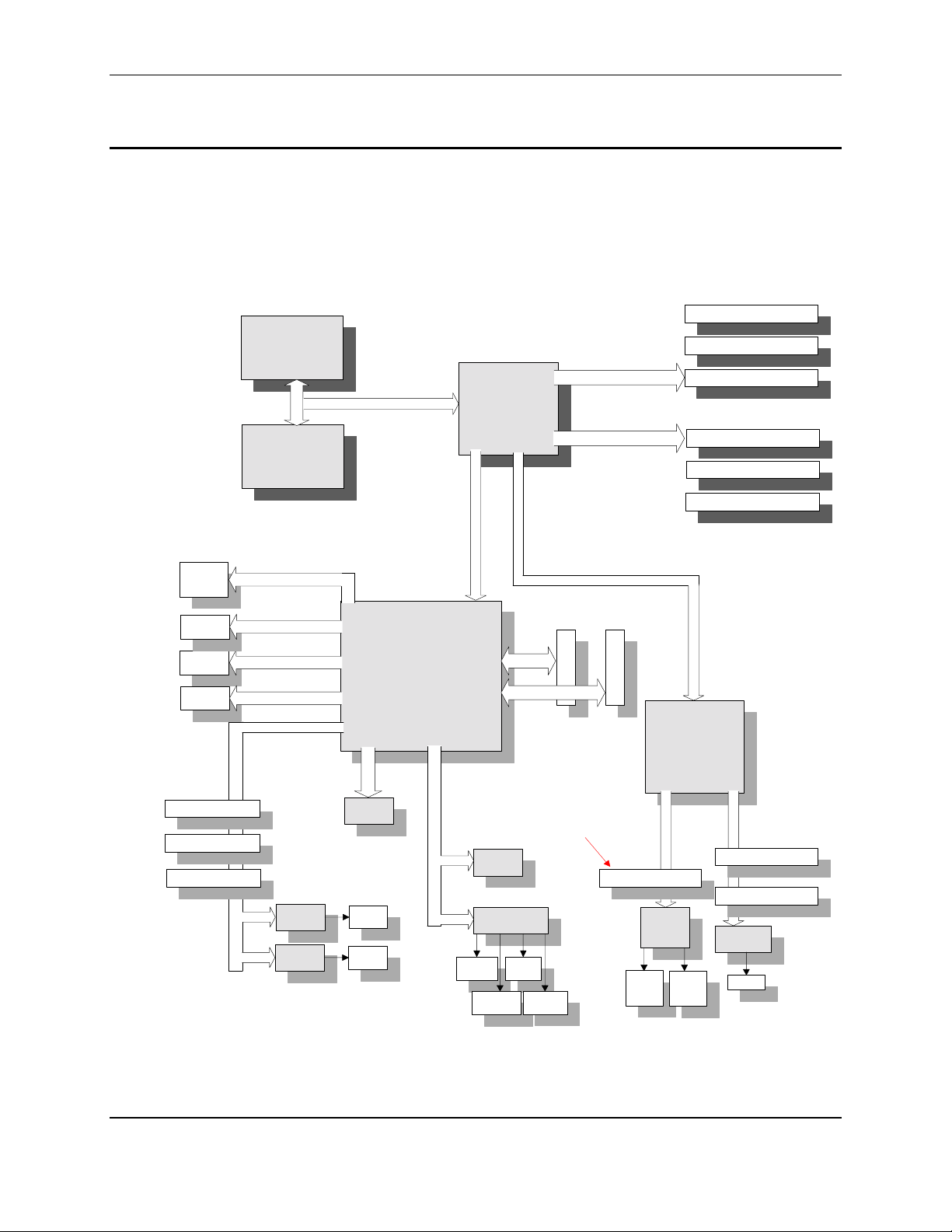

Figure 1 shows the functional blocks of the SHG 2 baseboar d.

DIMM

Front

Panel

USB

Prestonia

Processor

Prestonia

Processor

USB 1.1

400M T/s

100MHz 4x

FSB

400MT/s

200MHz 2x

CMIC-LE

Thin IM B

200M T/s

100MHz 2x

DDR 200 CHA

200M T/s

100MHz 2x

DDR 200 CHB

800MT/s

400MHz 2x

IM B

DIMM

DIMM

DIMM

DIMM

DIMM

12GB DD R 200 EC C

M emory (6 DIM Ms)

2-way interleaved

Rear

USB

Rear

USB

Rear

USB

PCI 32

PCI 32

PCI 32

PCI 32/33

USB 1.1

USB 1.1

USB 1.1

Video

LAN

10/100

Flash

Video

Conn

RJ45

XBUS

CSB5

LPC

Serial

Ports

Parallel

BMC

ATA 100

ATA 100

MRO M B Enabled

SIO

PS/2

Floppy

IDE

IDE

CIOBX2

PCI-X 100

PCI 64

PCI 64

Gbit

LAN

RJ45

PCI 64

U160/

U320

SCSI

Int

SCSI

Conn

PCI-X 133

SCSI

Conn

Int

Figure 1. Intel® SHG2 Server Board

Revision 1.0 Intel Order Number C11343-001

1

Introduction Intel® SHG2 DP Server Board Technical Product Specification

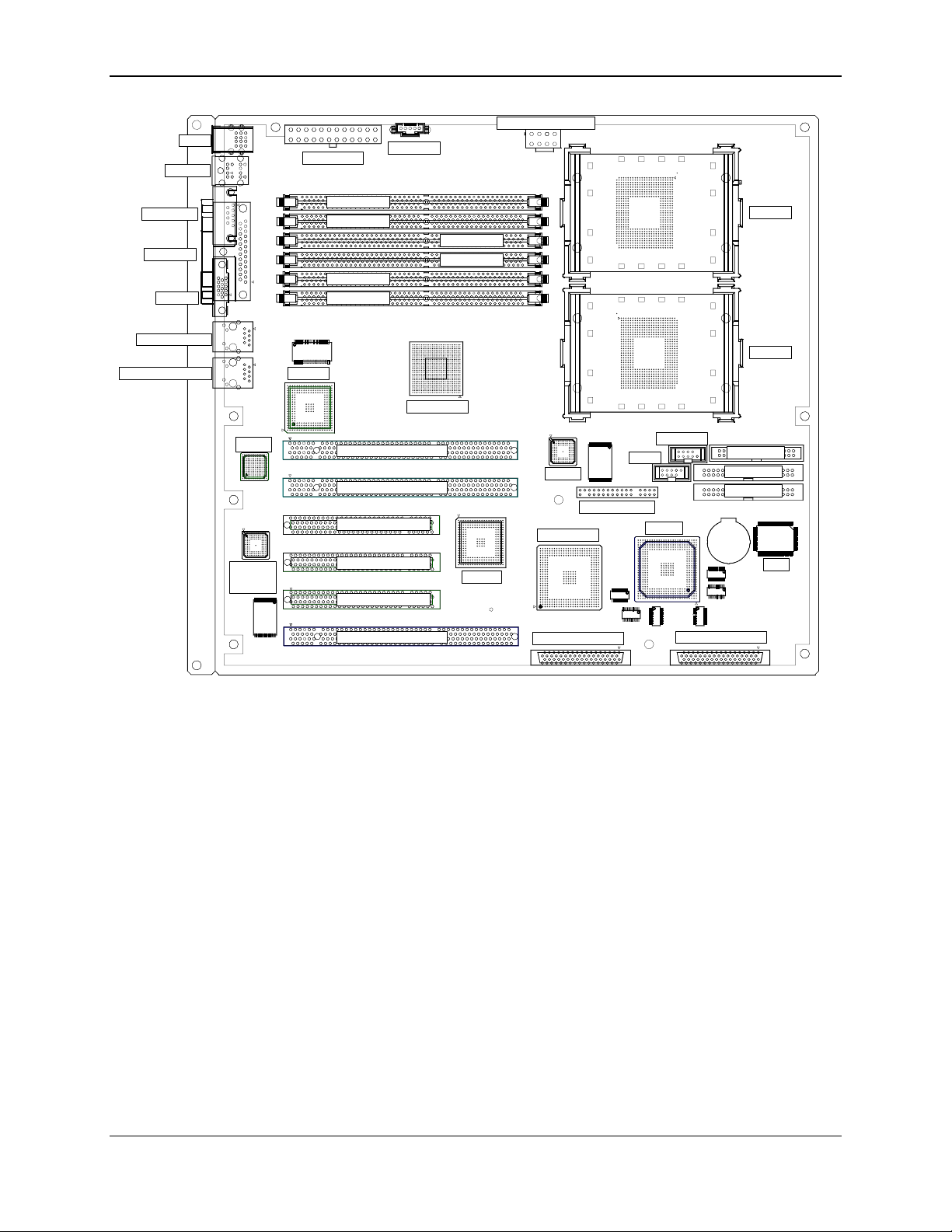

USB

KB/MS

Serial A

Pa ra lle l

Video

NIC2 (Gbit)

NIC1 (10/100)

1

5

86

21

3

5

96

151

0

5

6

1

1

1

10/100

8

6

B

A

C

2513

1

4

7

1

71

Gbit

NIC

1234

1

1

Main Pwr

Aux Sig

DIMM 3B

DIMM 3A

+12V CPU Pwr

Proc 1

DIMM 2B

DIMM 2A

DIMM 1B

1

2

8

2

DIMM 1A

Proc 2

Video

CMIC-LE

PCIX-1 (64/100)

BMC

PCIX-2 (64/100)

USB

Serial B

2

1

1

2

1

1

Floppy

Sec IDE

Prim IDE

4

2

0

0

4

2

0

0

Front Panel

PCI-3 (32/33)

PCI-4 (32/33)

CIOB-X2

CSB5

SCSI

SIO

PCI-5 (32/33)

PCIX-6 (64/133)

LVD SCSI A

3

4

3

7

3

8

6

6

1

2

5

6

3

3

LVD SCSI B

3

4

3

7

3

8

6

6

1

2

5

6

3

3

Figure 2. SHG2 Server Board Placement Diagram

1.1 SHG2 Architecture Overview

The Intel® SHG2 Server Board is designed around the Intel® Xeon™ processor and the

ServerWorks* Grand Champion* LE ServerSet* chipset. This combination provides the basis

for a high performance system with leading edge processor, memory, and I/O per formance.

The SHG2 baseboard architecture provides fo r t wo INT3- com pliant (603 pin) processor sockets

supporting dual processing operation using I nt el Xeon processors. It also contains six industry

standard PCI and PCI-X expansion slots supporting a m ixture of 32-bit/33-MHz, 64-bit/100-MHz

and 64-bit/133-MHz slots.

The processor baseboard provides an array of embedded I/ O devices including a SCSI

controller that provides two independent channels at SCSI bus speeds up to 160MB/sec with

7899 SCSI controller, one embedded 10/100 Network I nterface Controller (NIC), one

10/100/1000 Gigabit Network Inte r face Controller, and a 2D/3D graphics accelerat o r .

2

Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification Introduction

Server management and monitoring har dware are also included. These features, and the

others listed below, make this one of the most highly integrated server boards in this class.

SHG2 supports two interleaved memory channels at 100 MHz, each utilizing the rising edge

and falling edge of t he c lock cycle for 200MT/s per channel (also known as “double pumped” )

for a combined throughput of 400 MT/s. The subsystem was originally intended for PC1600

DDR memory modules (DDR200), however up to 6 DDR200 of DDR266 reg ist er ed memory

modules (PC1600 or PC2100 DIMMs) inserted as pairs may be used. Each DIMM may provide

up to 2 GB of memory capacity, providing up to 12 GB of system memory.

Note: Although the use of DDR266 modules is supported f or upward compatibility, the channel

throughput is fixed at 400 MT/s, and t he use of higher speed DIMMs will not provide additional

bandwidth. Mixed memory is not recommended, all DIMM sites should be populated with the

same speed and, when possible, same manufacturer.

The SHG2 server board provides the following features:

•

Dual Intel Xeon processor support.

- Two processor sockets for installation of one to two identical Intel Xeon processor s .

- Embedded VRMs to support two Xeon processors.

•

ServerWorks Grand Champion LE chipset.

- Champion Memory and I/O Controller-Low End (CMIC-LE).

- Champion South Bridge (CSB5).

- Champion I/O Bridge (CIOBX2).

•

Support for 6 DDR registered ECC Synchronous Dynamic RAM (SDRAM) DIMMs.

- Error Correcting Code (ECC) single-bit correction, and multiple-bit error detection

and memory scrubbing.

- Supports Chipkill* technology

•

32-bit, 33-MHz 5V keyed PCI segment with three expansion connectors and two

embedded devices with external connectors.

- One PCI NIC—Intel 82550PM Fast Ethernet Controller with a dedicated RJ-45

connector at the rear I/O panel

- 3D/2D Graphics Accelerator —ATI* RAGE XL Video Controller with DB15 VGA

connector at the rear I/O panel

•

64-bit, 100-MHz, 3.3V PCI-X segment with two expansion connectors and one

embedded device.

- One PCI-X network interface controller—In t el 82544GC Gigabit Ethernet Controller

with a dedicated RJ-45 connector at the rear I/O panel

•

64-bit, 133-MHz, 3.3V PCI-X segment with one expansion connector and one

embedded device.

- Dual Channel Ultra* 160 SCSI Controller—Adaptec* 7899 SCSI Controller.

Note: W hen t h e 7899 SCSI Cont r oller is enabled, this bus segment will run at 66MHz in

PCI mode. When disabled, the segment is capable of 133MHz PCI-X mode.

•

X-bus segment with one embedded device.

- 8-Mbit flash device for system BIOS.

•

LPC bus segment with two embedded devices.

Revision 1.0 Intel Order Number C11343-001

3

Introduction Intel® SHG2 DP Server Board Technical Product Specification

- Super I/O* controller chip providing all PC-compatible I/ O (floppy, parallel, serial,

keyboard, mouse).

- Sahalee Baseboard Management Controller (BMC) providing monitoring, alerting,

and logging of critical system information obtained from em bedded sensor s on

baseboard.

•

Four Universal Serial Bus (USB) ports.

•

Two 68 pin Ultra SCSI connectors, supporting t wo SCSI U-160 channels

•

Two 40 pin fast ATA (IDE) connector s, suppor t ing two ATA 33/66/100 channels

1.2 Document Structure and Outline

The information contained in this document is organized into 11 chapters. The content of each

chapter is summarized below:

Chapter 1: Int r oduct i on

Architectural overview of the Intel SHG2 Server Board showing functional blocks

and identifying major fe at ur es.

Chapter 2: Processor and Chipset

Detailed description of the chipset and the supported pr ocessor s .

Chapter 3: Baseboard PCI I/O Subsystem

Detailed descriptions of the PCI I/O subsystem. Three PCI buses are detailed,

with specifics on embedded devices and provided slots. Interrupt routing

information is also provided.

Chapter 4: Clock G enerat ion and Distribution

Identification of the clock signals generated and used on the SHG2 server board,

and detailed drawings of their implementation.

Chapter 5: Server Management

Detailed description of the server managem ent hardware integrated on the

SHG2 baseboard. I

2

C* addresses and block diagrams are provided.

Chapter 6: Error Handli ng and Report i ng

Defines how errors are handled by the system BIOS and SHG2 server board.

Chapter 7: Jumpers

Identification and description of all j um p er s used on t he SHG 2 ser ver boar d.

Chapter 8: Connecti ons

Identification of all connect or s on the SHG2 server board, by ‘CN’ number and

manufacturer's part num b er . I nt er facing specifics are identified where applicable.

Chapter 9: General Specifications

Description of operational parameter s and consider at ions, and other hardware

specifications.

Chapter 10: Mechanical Specifications

Mechanical drawings of the Intel SHG2 Server Board.

4

Intel Order Number C11343-001 Revision 1.0

Intel® SHG2 DP Server Board Technical Product Specification Introduction

Chapter 11 Regulatory and Integration Information

Revision 1.0 Intel Order Number C11343-001

5

Processor and Chipset Intel® SHG2 DP Server Board Technical Product Specification

2. Processor and Chipset

2.1 Overview

The Intel SHG2 Server Board consists of one to two identical Intel Xeon processors, the Grand

Champion LE chipset, and support circuitry. The baseboar d houses t wo surf ace mount zero

insertion force (ZIF) processor sockets and one embedded processor voltage regulator module

(VRMs) to power one or both processors. The ServerWorks* Grand Champion LE chipset

provides the 36-bit address/64-bit data processor host bus int er face, operating at 100 MHz in

the AGTL+ signaling environment . The Grand Champion Memory and I/O Controller (CMIC-LE)

provides an integrated memory controller, a high-speed I/O connection (IMB) to the PCI-X

bridge (CIOB-X2) and a connection ( Thin IMB) to the south bridge (CSB5) for legacy devices

and the PCI segment. The server boar d suppor t s up to 12 GB of ECC memory, using 2GB

DDR-registered PC1600 or PC2100 SDRAM DIMMs.

Additional descriptions and features include the f ollowing:

•

ServerWorks Grand Champion LE chipset providing an integrated I/O bridge and

memory controller, and a flexible I/O subsystem core (PCI) optimized for multiprocessor

systems and standard high-volume (SHV) servers.

•

Dual (603 pin) processor sockets that accept t he I nt el Xeon processors.

•

Processor host bus AGTL+ supported circuit r y, including t er mination power supply.

•

Integrated APIC signals suppor t .

•

Miscellaneous logic for reset configurat ion, pr ocessor pr esence det ect ion, I TP port, and

server management.

2.2 Processor Support

SHG2 specifically supports Intel Xeon processors from 1.8 G Hz to 2.6 G Hz, with 512 KB of L2

advanced transfer cache.

The processor is packaged in a 603-pin micr o- Pin- G r id Ar r ay (PGA) and pr ovides an integrated

heat spreader (IHS) for heat sink attachment.

The Intel Xeon processor socket t hat conforms to the 603-pin Socket Design Guidelines is a

surface mount technology (SMT); ZIF socket using soldered ball attachment (BG A) t o t he

platform.

®

As with previous versions of Intel

interface is designed to be DP-ready. Each pr ocessor cont ains a local advanced

programmable interrupt cont r oller (APIC) section for interr upt handling. When t wo processors

are installed, both processors must be of identical revision, core voltage, cache voltage, and

bus/core speeds.

Note: W hen using only one processor in the system, install the processor into the pr im ar y

socket (PROC1, closest t o the corner of the board). This will enable on-die termination on the

end-agent processor the for system to function proper ly. The BMC will not allow DC power to

Intel Order Number C11343-001 Revision 1.0

6

Pentium® Pro processors, the Intel Xeon processor extern al

Intel® SHG2 DP Server Board Technical Product Specification Processor and Chipset

be applied to the system unless primary slot is populated with a processor, unless used in f ault

resilient booting (FRB) mode (details in Section 5).

When using t wo processors, not ice t hat t he pr ocessor pins ar e physically 180 degrees out - ofphase. Improper processor installation may permanent ly damage pr ocessor pins.

2.2.1 Processor Bus Termination/Regulation/Power

The termination circuitry required by the Intel Xeon processor bus (AGT L+) signaling

environment, and the circuitry to set the AGTL+ reference voltage, are implemented directly on

the processors. The baseboard provides 1.5 V AGTL+ termination power (VTT), and VRM 9.1compliant DC-to-DC converters to provide processor power (VCC_P) at each socket. The

baseboard provides two embedded VRMs to power the processors, which derive power from

the +5 V and 12 V supplies. Both processors share the same VRM to power their core.

2.2.2 Miscellaneous Processor Subsystem Logic

In addition to the circuitry described above, the processor subsystem cont ains t he following:

•

Reset configuration logic.

•

Processor presence detection circuitry.

•

Server management registers and sensors.

2.2.2.1 Reset Configuration Logic

On the SHG2 platform , t he BMC is responsible for configuring the pr ocessor speeds. The BMC

uses the processor speed information (d er ived f r om the Intel Xeon processor SECC FRU

devices) to determine the appropriate speed to program into the speed-setting device (I

2

C-

based EEPROM Mux).

The processor information is r ead at every system power-on. T he EEMUX is set t o cor r espond

to the speed of the slowest processor.

2.2.2.2 Processor Presence Detection

Logic is provided on the baseboard to detect the presence and identity a proper ly installed

processor. This prevents system power on if an empty socket in t he pr imary section is detected

in the primary processor socket (labeled Proc1, locat ed closest t o the edge of the server

board), thus preventing operation of t he system with an impr oper ly term inated AGTL+

processor bus. The BMC checks th is logic and will not turn on the system DC power until the

bus is terminated properly with a processor in the primary socket .

2.2.2.3 APIC Bus

Interrupt notification and generation for the processors is done using a front side bus (FSB)

between local APIC, in each processor, and the I/O APIC in the CSB5 located on the

baseboard.

2.2.3 Server Management Registers and Sensors

The BMC manages registers and sensors associated with the processor/mem or y subsystem.

Revision 1.0 Intel Order Number C11343-001

7

Processor and Chipset Intel® SHG2 DP Server Board Technical Product Specification

2.2.4 ServerWorks* Grand Champion* LE Chipset

The CMIC-LE, CIOB-X2, and CSB5 chips provide the pathway between processor and I/O

systems. The CMIC-LE is responsible for accepting access requests from the host (processor)

bus, and directing all I/O accesses to one of the PCI buses or legacy I/O locations. If the cycle

is directed to one of the 64-bit PCI segments, the CMIC-LE communicates with the CIOB-X2

through a private interface called t he I MB bus. If the cycle is directed to the 32-bit PCI segment

or to the CSB5, the cycle is output on the private interface between the CMIC-LE and the CSB5

called the Thin-IMB bus. The CIOB-X2 translates the IMB bus operation to a 64-bit PCI-X

signaling environment, operating at 100 MHz or 133 MHz (PCI Local Bus Specification 2.2 and

PCI-X Specification 1.0a com pliant ) .

The IMB bus consists of two data paths, one upstream (to the CMIC-LE from the CIOB-X2) and

one downstream (from the CMIC-LE to the CI OB-X2). The interf ace is 16 bits wide and

operates at 400 MHz with double-pumped data, providing over 1.6 GB per second of bandwidth

in each direction, or 3.2 GB per second of bandwidth in both directions concurrently.

All I/O for the SHG2 server board, including PCI-X, is directed through the CMIC-LE and then

through either the CIOB- X2 or the CSB5-provided 32-bit/33-MHz PCI bus.

•

The CSB5 provides a 32-bit/33-MHz PCI bus.

•

The CIOB-X2 provides a 64-bit/100- MHz PCI-X bus and t he 64- bit / 133- MHz PCI-X bus.

This independent bus structure allows all three PCI buses to oper at e concur r ent ly and provides

1.2 GB per second of I/O bandwidth.

2.2.5 CMIC-LE

The Champion Memory and I/O Controller (CMIC-LE) is t he fourth generation product in

ServerWorks* Champion ServerSet Technology. The CMIC-LE is built on t o p of the proven

components of previous generations lik e t he I nt el® Pent ium® Pro Bus interface unit, the I MB

interface unit, and the DDR SDRAM memor y inter face unit.

The CMIC-LE integrates two main functional units: 1) an integrated high per formance main

memory subsystem, and 2) an IMB bus interface that pr ovides a high- per formance data flow

path between the processor bus and the I/O subsystem. In addit ion to t he above-mentioned

units, the CMIC-LE incorporates a Thin-Int r a Module Bus (T hin- I MB) Int er face.

Other features provided by the CMIC-LE include the following:

•

Full support of processor bus protocol with multiprocessor suppor t.

•

Full support of ECC on the memory interface.

•

An in-order queue (twelve deep).

•

Full support of register ed DDR ECC SDRAM DIMMs.

•

Addressing support for 12 GB of 2-way interleaved SDRAM with 6 DIMMs sockets.

•

Memory scrubbing.

•

Multiple-bit error detection and Multiple-bit error correction fo r 1- 4 bit s on one DRAM

within the same DIMM module (Chipkill*).

Intel Order Number C11343-001 Revision 1.0

8

Intel® SHG2 DP Server Board Technical Product Specification Processor and Chipset

2.3 Memory Subsystem

Features provided in the SHG2 server board memory subsystem include the following:

•

Six DIMM sockets, supporting three pairs of PC1600 (DDR200) , upward compatible with

PC2100 (DDR266) DIMMs.

•

Memory can be implemented with either single-sided (one row) or double-sided ( t wo

row) DIMMs.

•

Minimum me mory capacity of 256 MB (2 x 128MB DIMMs).

•

Maximum memory capacity of 12 GB (6 x 2GB DIMMs).

•

The DIMM organization is x72, which includes 8 ECC check bits.

•

Supports memory scrubbing, ECC sing le bit error correction, and multiple bit er r or

detection.

•

ECC from the DIMMs is passed through to the processor FSB.

•

Supports Chipkill* multiple bit er r o r det ection and multiple bit error correct ion.

•

Support for 2-way interleaved DDR SDRAM.

•

The DDR SDRAM interface is comprised of 2 channels running at a frequency of 200

MHz each for for a total interleaved transfer rate of 400MT /s.

Note: Memory interleaving is a way to increase memory performance by allowing the system to

access multiple memory modules simultaneously, rat her than sequentially, in a similar fashion

to hard-drive striping. Inter leaving can only tak e place bet ween identical mem or y modules.

Note: Although the use of DDR266 modules is supported f or upward compatibility, the channel

throughput is fixed at 400 MT/s, and t he use of higher speed DIMMs will not provide additional

bandwidth. Mixed memory is not recommended, all DIMM sites should be populated with the

same speed and, when possible, same manufacturer.

2.3.1 Chipkill*

The CMIC-LE chipset supports Chipkill memory technology, which allows the system to recover

when a multi-bit error is encountered within a single DDR SDRAM device on the same DIMM

module. Chipkill memory technolog y provides prot ec t ion up t o, and inc luding, a complete failure

of a single DRAM device. The Chipkill technology incorporated in the CMIC-LE does not

require any layout requirements on t he memory boards. CMIC-LE contains the Chipkill

algorithm and perform s all the data correction logic required.

Chipkill memory technology works by re-ord er ing the data from the DDR SDRAMs so that if one

DDR SDRAM device within a module should fail, the check bit algorithm pr ovides suf ficient

information to recover from the multi-bit data err or . The correctable errors are t hen writt en t o

the system error log (SEL) for evaluation at a later time.

2.3.2 Memory Configuration

Memory configuration requirements are as follows:

•

DDR200 or DDR266 SDRAM-registered DIMM modules

•

DIMM organization: x72 ECC

•

Pin count: 184

Revision 1.0 Intel Order Number C11343-001

9

Processor and Chipset Intel® SHG2 DP Server Board Technical Product Specification

•

DIMM capacity (in pairs): 128 MB, 256 MB, 512 MB, 1 GB and 2 GB

•

Serial PD: JEDEC Rev 2.0

•

Voltage Options: 2.5 V (VDD/ VDDQ )

•

DIMMs must be populated in pairs for a x144 wide memory data path

Table 1. Memory DIMM Pairs

Memory DIMM DIMM PAIR Row

DIMM 1A, DIMM 1B 1 1, 2

DIMM 2A, DIMM 2B 2 3, 4

DIMM 3A, DIMM 3B 3 5, 6

DIMM Pair 3A/B

DIMM Pair 2A/B

DIMM Pair 1A/B

Figure 3. SHG2 Memory Bank Layout

Intel Order Number C11343-001 Revision 1.0

10

Intel® SHG2 DP Server Board Technical Product Specification Processor and Chipset

2.3.3 CIOB-X2

The Champion I/O Bridge ( CI O B- X2) provides an integrated I/O br idge that provides a highperformance data flow path between the IMB and the 64-bit I / O subsystem . This subsystem

supports 2 peer 64-bit PCI (-X) segments. Having two PCI (-X) interfaces, the CIOB-X2 is able

to provide large and efficient I/O configurations. The CIOB-X2 functions as the bridg e bet ween

IMB and the two 64-bit PCI (-X) I/O seg m ent s or peer s.

•

The IMB interface is capable of supporting 1.6 GB/s of data bandwidth in both the

upstream and downstream direction simultaneously.

•

The internal PCI (-X) ar bit er implements the least-recently used algorit hm to grant

access to requesting masters.

•

The CIOB-X2 is a 352-pin ball-g rid array (BGA) device.

2.3.3.1 64/100MHz I/O Subsystem

The 64/100MHz subsystem supports the following embedded devices and connectors:

•

One PCI-X network interface controller—Intel 82544GC G ig abit Ethernet Controller with

a dedicated RJ-45 connector.

•

Two 184-pin, 3.3 V keyed, 64-bit PCI expansion slot connectors, num ber ed PCI X-1 and

PCIX-2, supporting 100-MHz 3.3V-compliant PCI- X adapters, and both 66-MHz and 33MHz 3.3V-compliant PCI adapters.

2.3.3.2 64/133 MHz I/O Subsystem

The 64/133 MHz subsystem supports the following embedded device and connector:

•

Dual Channel Ultra 160 SCSI Controller—Adaptec 7899 SCSI Cont r oller. Note: When

the 7899 is enabled, the PCI expansion slot connector would only be capable of running

at 66 MHz PCI mode.

•

One 184-pin, 3.3 V keyed, 64-bit PCI expansion slot connecto r , num ber ed PCI X-6

(64/133), supporting 133-MHz 3.3V PCI-X-com pliant PCI-X adapters, and MROMB

SCSI adapters.

2.4 CSB5 South Bridge

CSB5 is a multi-function PCI device, housed in a 256-pin BGA device, pr oviding a PCI -to-LPC

bridge, PCI IDE interface, PCI USB controller, and power management controller. Each

function within the CSB5 has its own set of config ur at ion r egisters. Once configured, each

appears to the system as a distinct hardware controller sharing t he sam e PCI bus int er face.

In the SHG2 server board implementation, the CSB5’s primary role is to provide the gateway to

all PC-compatible I/O devices and features. The SHG2 uses the following CSB5 features:

•

PCI bus interface

•

LPC bus interface

•

IDE interface, with dual channel Ultra DMA 100 capability

Revision 1.0 Intel Order Number C11343-001

11

Processor and Chipset Intel® SHG2 DP Server Board Technical Product Specification

•

Four port USB interface

•

PCI-compatible timer/counter and DMA controller s

•

APIC and legacy 8259 interrupt controller

•

Power management

•

General purpose I/O

The following are descriptions of how each supported feature is implemented in SHG2.

2.4.1 PCI Interface

The CSB5 fully implements a 32-bit PCI master/slave interface, in accordance with the PCI

Local Bus Specification, Revision 2.2. On the SHG2 baseboar d, t he PCI interface operates at

33 MHz, using the 5V-signaling environment.

2.4.2 PCI Bus Master IDE Interface

The CSB5 acts as a PCI-based fast IDE cont r oller t hat suppor t s pr ogrammed I/O transfers and

bus master IDE transfers. The CSB5 supports two fast ATA-100 IDE channels, support ing t wo

drives per channel. Two IDE connectors, primary and secondary, feat ur ing 40 pins each (2 x

20), are provided on the baseboard.

The SHG2 ATA interface suppor t s Ultra DMA 33/66/100 synchronous DMA mode transfers.

2.4.3 USB Interface

The CSB5 contains a USB controller and USB hub. T he USB cont r oller m oves data bet ween

main memory and the four USB connector s pr ovided.

The SHG2 baseboard provides three external USB connector inter faces on the rear I/O panel.

All ports function identically and support the sam e bandwidth. The external connector is defined

by the USB Specification, Revision 1.1. The SHG2 baseboard also provides a proprietary 10pin internal USB header, as the fourt h USB por t r outable to an external location such as a front

panel (see the Section 8, Connections, for int e r face specifics on all connectors).

2.4.4 BIOS Flash

The SHG2 baseboard incorporates a Fujitsu*

The 29LV800TA-90PFTN is a high-per formance 8-Mbit memory organized as 1 MB of 8 bits

each. There are 16 64-KB blocks within this device.

The 8-bit flash memory provides 1024K x 8 of BIO S and non- volatile st or age space. The flash

device is directly addressed as 20-bit XBUS memory.

29LV800TA-90PFTN

flash memory component.

2.4.5 Compatibility Interrupt Control

The CSB5 provides the functionality of two legacy 8259 programmable interrupt controller ( PI C)

devices, for ISA-compatible interr upt handling.

Intel Order Number C11343-001 Revision 1.0

12

Intel® SHG2 DP Server Board Technical Product Specification Processor and Chipset

2.4.6 Power Management

One of the embedded funct ions of CSB5 is a power management controller. The SHG2 server

board uses this to implement ACPI-com pliant power management features. T he SHG 2

supports four sleep states: S0, S1, S4, and S5.

2.4.7 General Purpose Input and Output Pins

The CSB5 provides a number of general- pur pose input ( GPI) and general-purpose output

(GPO) pins. Many of these pins have alternate functions, and thus all are not available. Table 2

lists the GPI and GPO pins used on the SHG2 baseboard and gives a brief description of their

function.

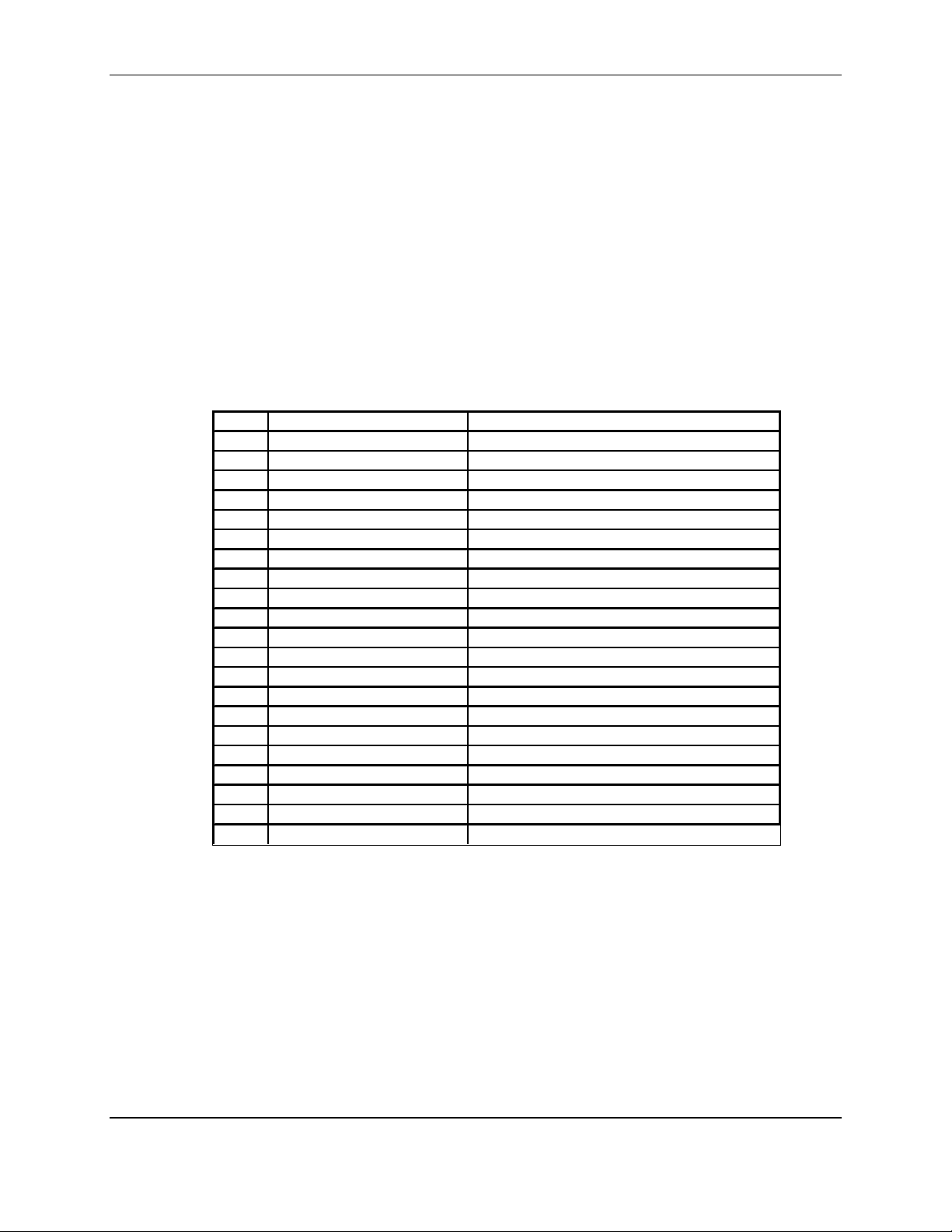

Table 2. CSB5 GPIO Usage Table

Pad Usage Description

V3 CMIC_FATALN CMIC fatal error condition

W2 CMIC_ALERTN CMIC error condition

W3 SCSI_IDSEL_EN SCSI ID select enable

W4 CIOB1_ALERTN CIOB error condition

Y4 CSB5_NMI CSB5 NMI condition

Y1 BMC_IRQ_SMI-10 BMC SMI condition

Y2 LAN1_IDSEL_EN LAN1 ID select enable

Y19 NVRAMCLR Non-volatile RAM clear status

V17 PASSDIS-00 Allows password to be disabled

U16 CMOSCLR-00 CMOS clear status

V15 VENDER_SEL Monitor PCIRST# signal

T20 F3SETUPEN-00 Enable Inspection Mode for factory use

T19 BMC_SCI-10 BMC system control interrupt status

T18 BMCISPMD-00 Reserved

Y16 SIDE_A+000 Secondary IDE addressbit 0

V12 SIDE_A+001 Secondary IDE address bit 1

U12 SIDE_A+002 Secondary IDE address bit 2

V19 LAN2_IDSEL_EN LAN2 ID select enable

W20 VGA_IDSEL_EN Video ID select enable

U14 FRWPN Enable Frimware Write Protect Mode

Y20 ROM_CSN BIOS flash chip select

Revision 1.0 Intel Order Number C11343-001

13

Processor and Chipset Intel® SHG2 DP Server Board Technical Product Specification

2.5 Chipset Support Components

2.5.1 Legacy I/O (Super I/O) National* PC87417VLA

The National* PC87417VLA is integrated on the SHG2 baseboar d as t he Super I/O controller

(SIO). The SIO is a Plug and Play-compatible device with ACPI-compliant controller/extender.

The SIO provides support for t he following features:

•

The system real-time clock (RTC)

•

Two serial ports

•

One parallel port

•

Floppy disk controller

•

PS/2-compatible keyboard and mouse controller

•

Gereral purpose I/O (GPIO) pins

•

Plug and Play functions

•

Power management controller

The SHG2 baseboard provides the connector interface for the floppy, dual serial ports, par allel

port, PS/2 mouse, and the PS/2 k eyboard. See Sect ion 8 ( Connect ions) for connector pinout

information. Upon reset, t he SI O reads the values on GPO pins to determine its boot-up

address configuration.

2.5.1.1 Serial Ports

One 9-pin connector in a D-Sub housing is provided for serial port A, while serial port B is

optional via cable to the rear of the chassis through a 9- pin connect or . Both ports are

compatible with 16450 and 16550A modes, and both are re-locatable. Each serial port can be

set to one of four different COM-x ports, and each can be enabled separately. When enabled,

each port can be programmed to generate edge- or level-sensitive interrupts. When disabled,

serial port interrupts are available to add-in cards. The serial port pinout is shown in Table 3.

Table 3. Serial Port Connector Pinout

Pin Name Description

1 DCD Data Carrier Detected

2 RXD Receive Data

3 TXD Transmit Data

4 DTR Data Terminal Ready

5 GND Ground

6 DSR Data Set Ready

7 RTS Request to Send

8 CTS Clear to Send

9 RIA Ring Indication Active

Intel Order Number C11343-001 Revision 1.0

14

Intel® SHG2 DP Server Board Technical Product Specification Processor and Chipset

2.5.1.2 Parallel Port

The SHG2 baseboard provides a 25-pin parallel port connect or . The SIO provides an IEEE

1284-compliant, 25-pin bi-directional par allel por t . BIOS programming of the SIO registers

enables the parallel port and determines the port addr ess and int er r upt . When disabled, t he

interrupt is available to add in adapters. Parallel port pinouts are shown in Table 4.

Table 4. Parallel Port Connector Pinout

Pin Name Pin Name

1 STROBE_L 14 AUFDXT_L

2 D0 15 ERROR_L

3 D1 16 INIT_L

4 D2 17 SLCTIN_L

5 D3 18 GND

6 D4 19 GND

7 D5 20 GND

8 D6 21 GND

9 D7 22 GND

10 ACK_L 23 GND

11 BUSY 24 GND

12 PE 25 GND

13 SLCT

2.5.1.3 Floppy Port

The Floppy Disk Controller (FDC) is located in t he t h e Super I / O controller (SIO). T he SI O is

software compatible with the PC8477, which contains a superset of the FDC functions in the

uDP8473, NEC uPD765A, and N82077. The baseboard provides the 48-MHz clock,

termination resistors, and chip selects. All other FDC functions are integrated into the SIO ,

including analog data separator and 16-byte FIFO . The FDC connector pinouts are shown

below in Table 5.

Table 5. Floppy Port Connector Pinout

Pin Name Pin Name Pin Name

1 GND 13 GND 25 GND

2 FD_DENSEL 14 FD_DR0_L 26 FD_TRK0_L

3 GND 15 GND 27 FD_MSEN0

4 N/C 16 FD_MTR1_L 28 FD_WPROT_L

5 Key 17 FD_MSEN1 29 GND

6 FD_DRATE0 18 FD_DIR_L 30 FD_RDATA_L

7 GND 19 GND 31 GND

8 FD_INDEX_L 20 FD_STEP_L 32 FD_HDSEL_L

9 GND 21 GND 33 GND

10 FD_MTR0_L 22 FD_WDATA_L 34 FD_DSKCHG_L

11 GND 23 GND

Revision 1.0 Intel Order Number C11343-001

15

Processor and Chipset Intel® SHG2 DP Server Board Technical Product Specification

Pin Name Pin Name Pin Name

12 FD_DR1_L 24 FD_WGATE_L

2.5.1.4 Keyboard and Mouse Connectors

The PS/2-compatible keyboard and mouse connector s ar e m ounted within a single stacked

housing. The mouse connector is stack ed over the keyboard connector. External to the board,

they appear as two connectors. The keyboard contr o ller is functionally compatible with the

8042AH and PC87911. The keyboard and mouse connector pinouts are shown in Table 6 and

Table 7

Table 6. Keyboard Connector Pinout

Pin Signal Description

1 KEYDAT Keyboard Data

2 (NC)

3 GND Ground

4 FUSED_VCC +5 V, fused

5 KEYCLK Keyboard Clock

6 (NC)

Table 7. Mouse Connector Pinout

Pin Signal Description

1 MSEDAT Mouse Data

2 (NC)

3 GND Ground

4 FUSED_VCC +5 V, fused

5 MSECLK Mouse Clock

6 (NC)

2.5.1.5 GPIO

The PC PC87417VLA provides several of the GPIO pins th at t he SHG 2 ser ver board ut ilizes.

Table 8 identifies the pin, the signal name specified in the schematic, and a brief descript ion of

its usage.

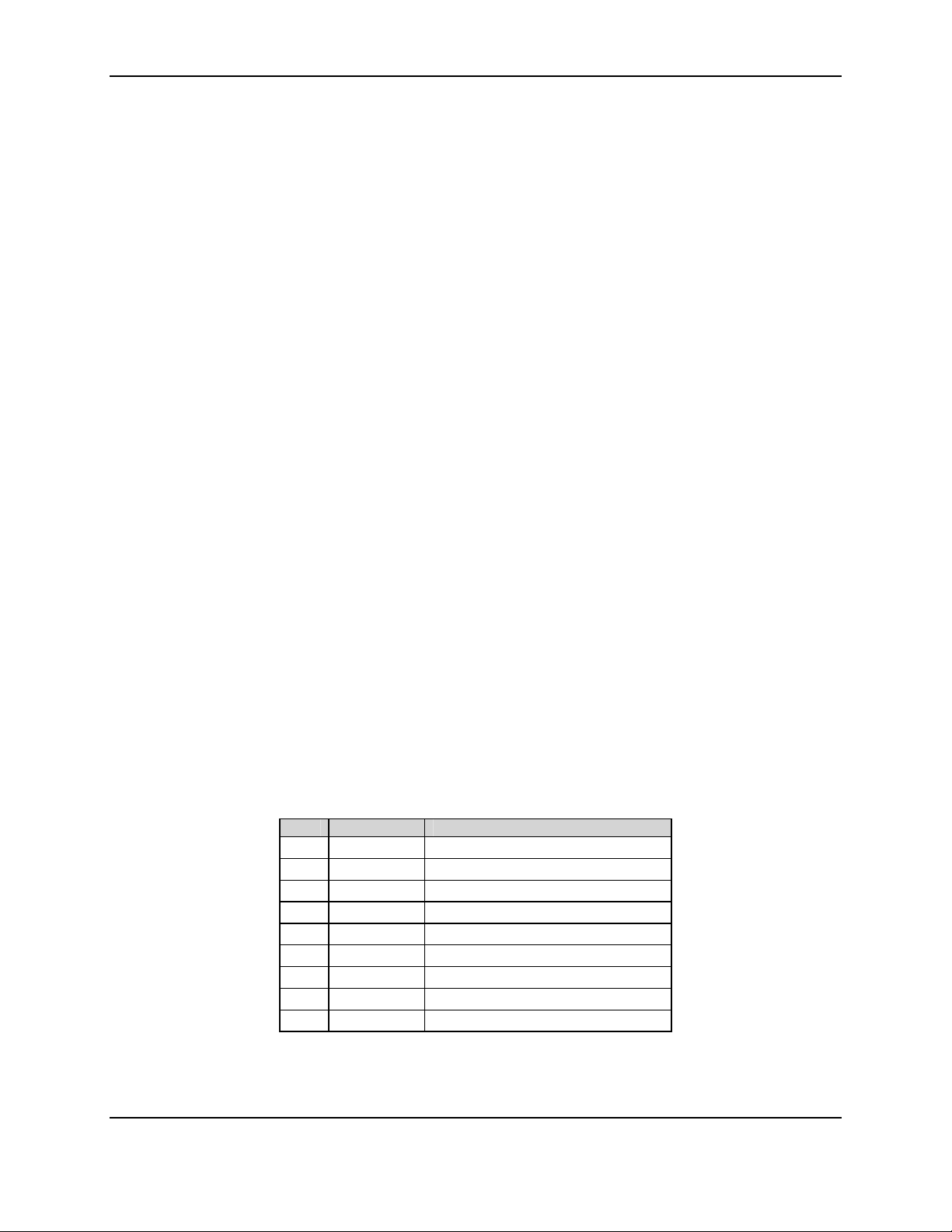

Table 8. Super I/O* GPIO Usage Table

Pin Usage Descritpion

1,2,3 PKG_SELECT<1-3> PKG ID

5 PCIXCAP1+SW To enable/disable pcix mode to slot6

49 PCIX_PME-10 Power Management Event from PCIX bus

52 PCI33_PME-10 Power Management Event from PCI bus

51 FP_PWR_LED+00 Front Panel LED control

50 PCI66_PME-10 Power Management Event from PCI 66bus

2.5.1.6 Real-time Clock

The PC97417VLA contains a DS1287, MC146818, and PC87911-compatible RTC with external

battery backup. The device also contains 242 bytes of general pur pose battery-backed CMOS

RAM.

2.5.1.7 Power Management Controller

The PC87417VLA contains functionality that allows various events to control the power state of

the system (power-up or power-down). This functionality can be controlled from PCI power

Intel Order Number C11343-001 Revision 1.0

16

Intel® SHG2 DP Server Board Technical Product Specification Processor and Chipset

management events, the BMC, or the f r ont panel. This circuitry is powered from stand-by

voltage, which is present anytime the system is plugged int o an AC out let .

Revision 1.0 Intel Order Number C11343-001

17

Baseboard PCI I/O Subsystem Intel® SHG2 DP Server Board Technical Product Specification

3. Baseboard PCI I/O Subsystem

3.1 Overview

The I/O buses for t he I nt el SHG 2 ser ver board ar e bot h PCI - X and PCI, with one PCI and two

PCI-X bus segments or peers. All the PCI (-X) buses comply with the PCI Local Bus

Specification, Revision 2.2 and PCI-X Specification, Revision 1. 0a. All three 64-bit slots on

SHG2 are capable of supporting PCI - X mode (note: the 7899 on-board SCSI adapter must be

disabled in BIOS Setup to enable PCIX-6 support of PCI-X mode). Table 9 lists the

characteristics of the three PCI (-X) bus segments.

Table 9. PCI(-X) Bus Segment Characteristics

PCI Bus

Segment

64/100MHz 64 bit 100MHz PCI-X 2 slots (64-bit/100-MHz)

64/133MHz 64 bit 133 MHz PCI-X 1 slots (64-bit/133-MHz)

32/33MHz 32 bit 33 MHz

Width Speed Type Add-in PCI Slot Support,

Total Eight Slots

Full-length cards supported

Full-length cards supported

PCI 3 slots (32-bit 33-MHz)

Full-length cards supported

3.2 64-bit/100MHz PCI-X Subsystem

64/100 MHz segment supports these embedded devices and connectors:

•

Two 184-pin, 3.3 V, 64-bit PCI (-X ) expansion connector s, numbered PCIX-1 (64/100)

and PCIX-2 (64/100).

•

One embedded 82544GC Gigabit Ethernet Controller.

3.2.1 Device IDs (IDSEL)

All slots on this segment support PCI ( X ) and conform to the PCI-X Specificat ion, Revision

1.0a. Each device under the PCI-X host bridg e has it s I DSEL signal connected to one bit of

AD[31::16], which acts as a chip select on the PCI(-X) bus segment. This determines a unique

PCI (-X) device ID value for use in conf iguration cycles. Table 10 shows both the bit to which

each IDSEL signal is attached for 64/100MHz devices, and the corresponding device number.

Table 10. 64/100MHz Segment Configuration IDs

IDSEL Value Device

25 PCI (X) Slot #1, PCIX-1 (64/100)

24 PCI (X) Slot #2, PCIX-2 (64/100)

20 82544GC Gigabit Ethernet Controller

Intel Order Number C11343-001 Revision 1.0

18

Loading...

Loading...