Panasonic MN63112S Datasheet

EEPROMs

MN63112S

2K-Bit EEPROM

Overview

The MN63112S is a 2K-bit EEPROM supporting serial I/O and operating on a single power supply with a

voltage between 1.8 and 5.5 V. It provides the following

pins for easy interfacing to microprocessors or

microcontrollers: chip select (CS), serial clock (SK), data

input (DI), and data output (DO). It includes a built-in

timer for use in automatically erasing and writing data

during data update operations.

The ORG pin provides a choice of two memory organizations: 256 × 8 bits when ORG is connected to ground

and 128 × 16 bits when ORG is connected to V

CC

. An

internal pull-up resistor makes the latter the default configuration.

Conversion of peripheral circuits to CMOS realizes

great reductions in power consumption. Use of floating

gate memory cells and a built-in error correction circuit

ensures reliable operation for 10

5

write cycles.

Features

Choice of memory organizations: 256 × 8 bits and

128 × 16 bits

Floating gate memory cells

Function blocking erroneous writes

Low power consumption

- Reads: max. 6.6 mW for V

- Standby: max. 66 µW for V

Built-in self-timer for use in automatically erasing

and writing

Built-in error correction circuit that guarantees 10

write cycles

10-year data preservation period

= 3.3 V

CC

= 3.3 V

CC

5

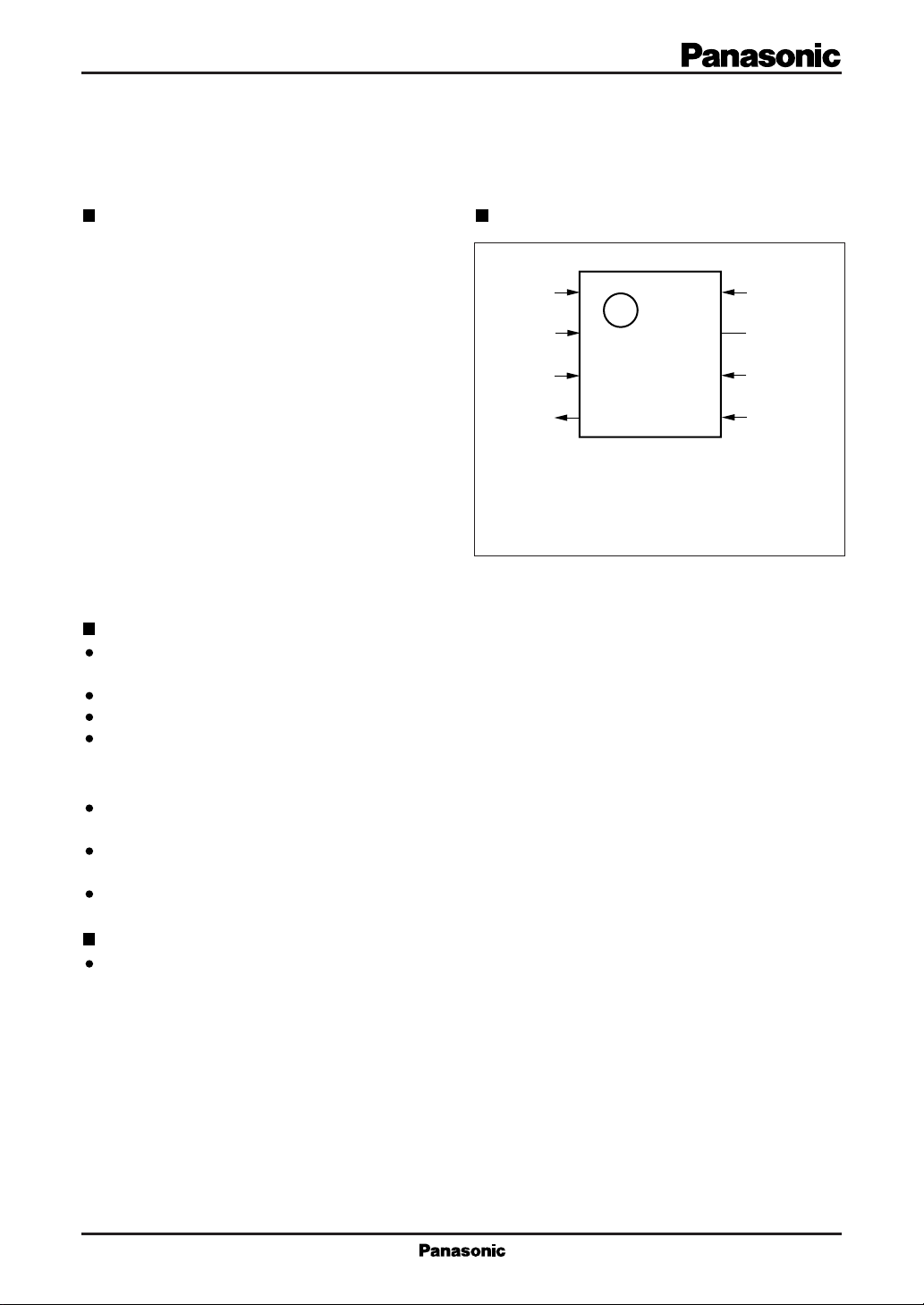

Pin Assignment

1

CS

2

SK

3

DI

4

DO

SOP008-P-0225

( TOP VIEW )

8

V

CC

N.C.

7

ORG

6

GND

5

Applications

Keyless entry systems, cordless telephones, storage for

recognition and adjustment data for terminals, etc.

1

MN63112S EEPROMs

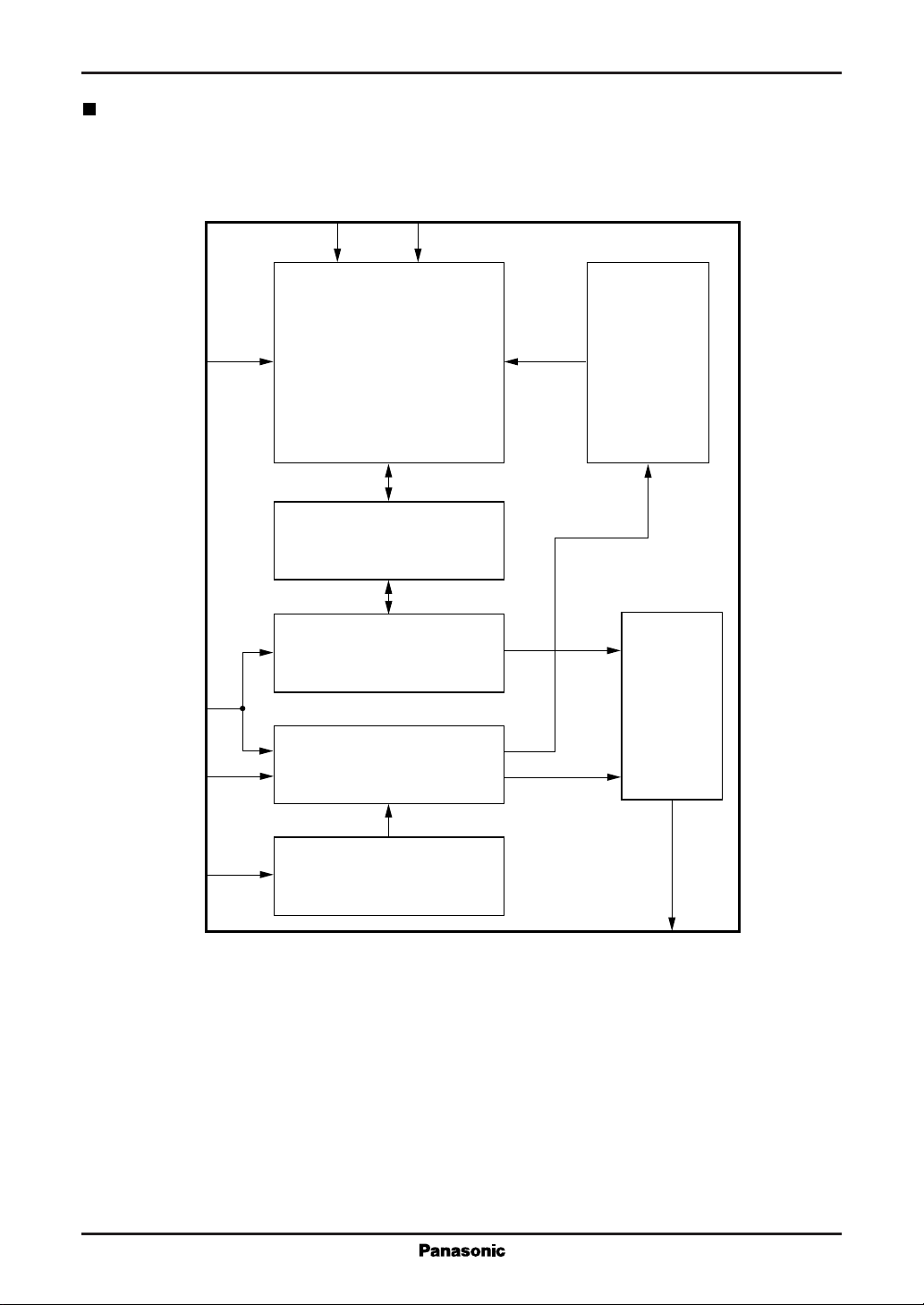

Block Diagram

CC

V

8

Memory array

GND

5

ORG

DI

CS

SK

6

3

1

2

128 × 16

or

256 × 8

Error correction circuit

Data register

Mode decode logic

Clock generator

Address

decoder

Output buffer

4

DO

2

Loading...

Loading...