Panasonic MN6153UC Datasheet

For Communications Equipment

MN6153UC

PLL LSI with Built-In Prescaler

Overview

The MN6153UC is a CMOS LSI for a phase-locked

loop (PLL) frequency synthesizer with serial data input.

It consists of a two-coefficient prescaler, variable

frequency divider, phase comparator, and charge pump.

It offers high-speed operation on a low power supply

voltage (1.0 to 1.4 V) and low power consumption (0.5

mW for V

=1.03 V, FIN= 60 MHz).

DD

Other features include intermittent operation by the

power save (PS) control signal and high-speed pull-in that

rapidly corrects the phase differences occurring at the start

of operation.

Features

Low power supply voltage: VDD=1.0 to 1.4V

Low power consumption: 0.5mW (VDD=V1.03V,

F

=60MHz)

IN

High-speed operation: FIN=60MHz

(V

=1.03V)

DD

Frequency dividing ratios in reference frequency

dividing stage: 5 to 131,071

Frequency dividing ratios in comparator stage:

272 to 262,143

Lock detector output pin

Two types of phase comparator output

- Internal charge pump output

- Output for external charge pump

Output monitor pins for both comparator and reference

frequency dividing stages

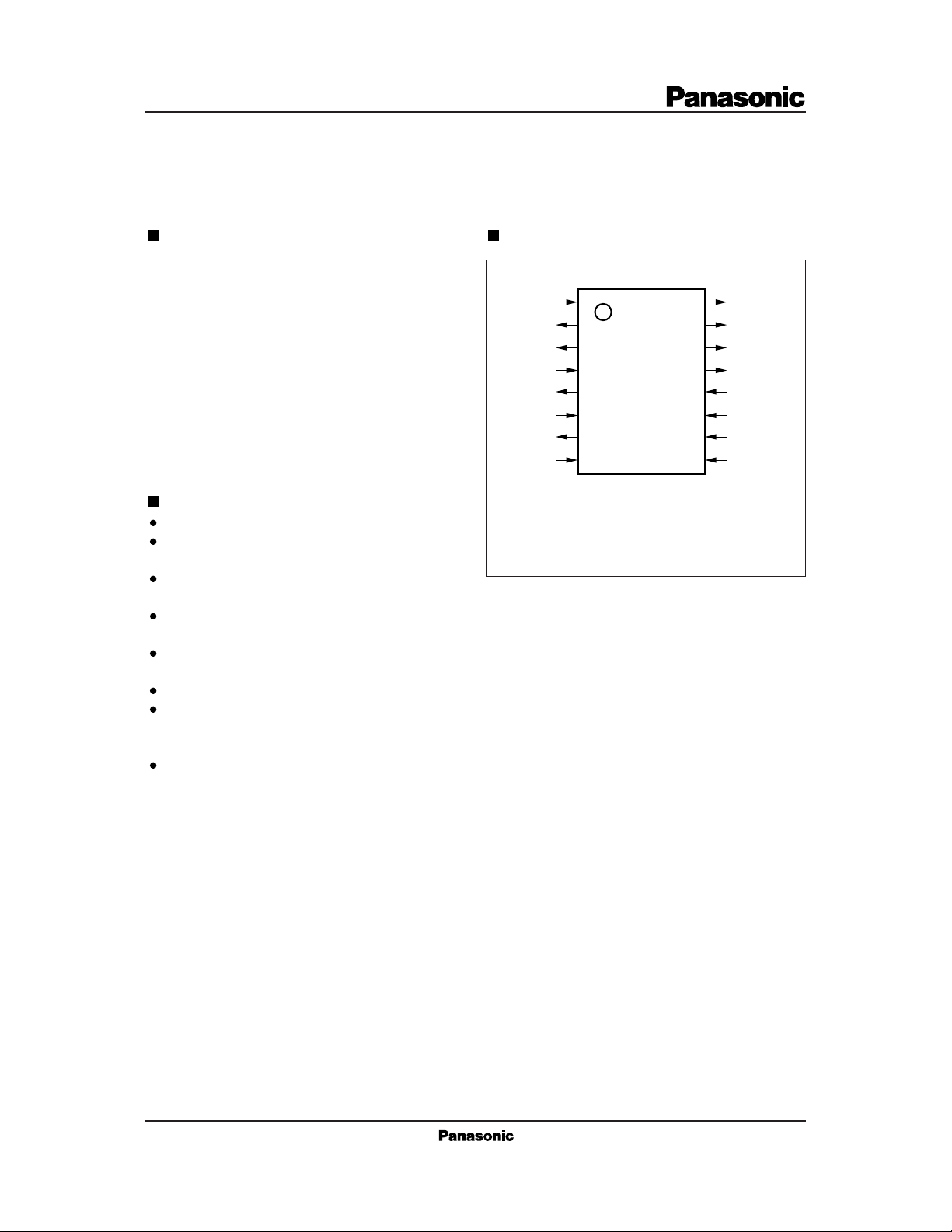

Pin Assignment

X

X

OUT

FV

V

D

V

V

F

DD

1

IN

2

3

4

5

OP

6

SS

7

CP

8

IN

SSOP016-P-0225

(TOP VIEW)

OR

16

OV

15

LC

14

FR

13

PS

12

LE

11

DATA

10

CLK

9

MN6153UC For Communications Equipment

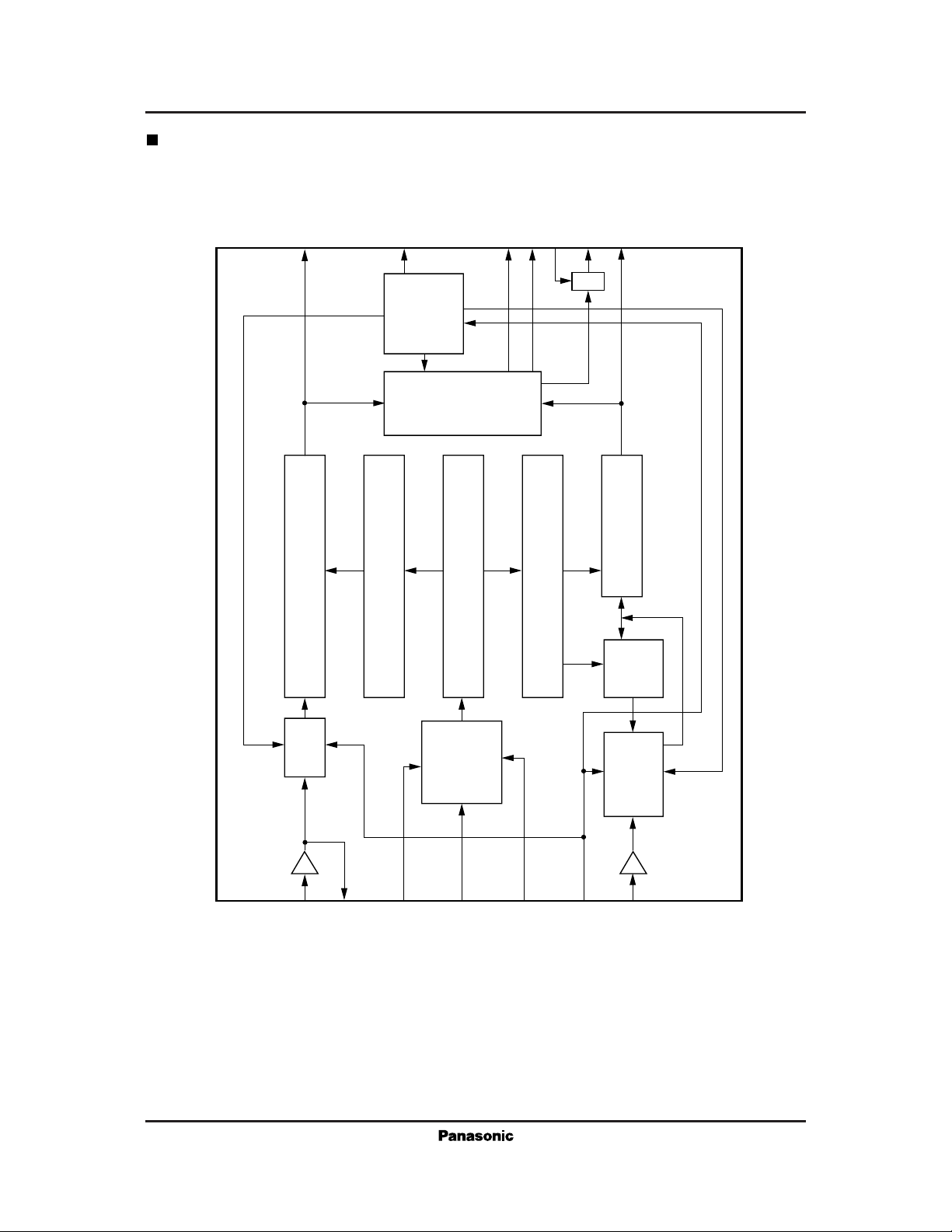

Block Diagram

FR

13

LC

14

Phase comparator

17-bit latch

17-bit programmable counter

Control

18-bit shift register

OVORV

15

16

CPDOP

7

5

18-bit latch

FV

3

14-bit programmable

counter

Phase

matching

1

IN

X

Swallow

counter

Data control

Prescaler and

phase matching

2

OUT

X

9

CLK

10

DATA

PS

8

IN

F

11

12

LE

For Communications Equipment MN6153UC

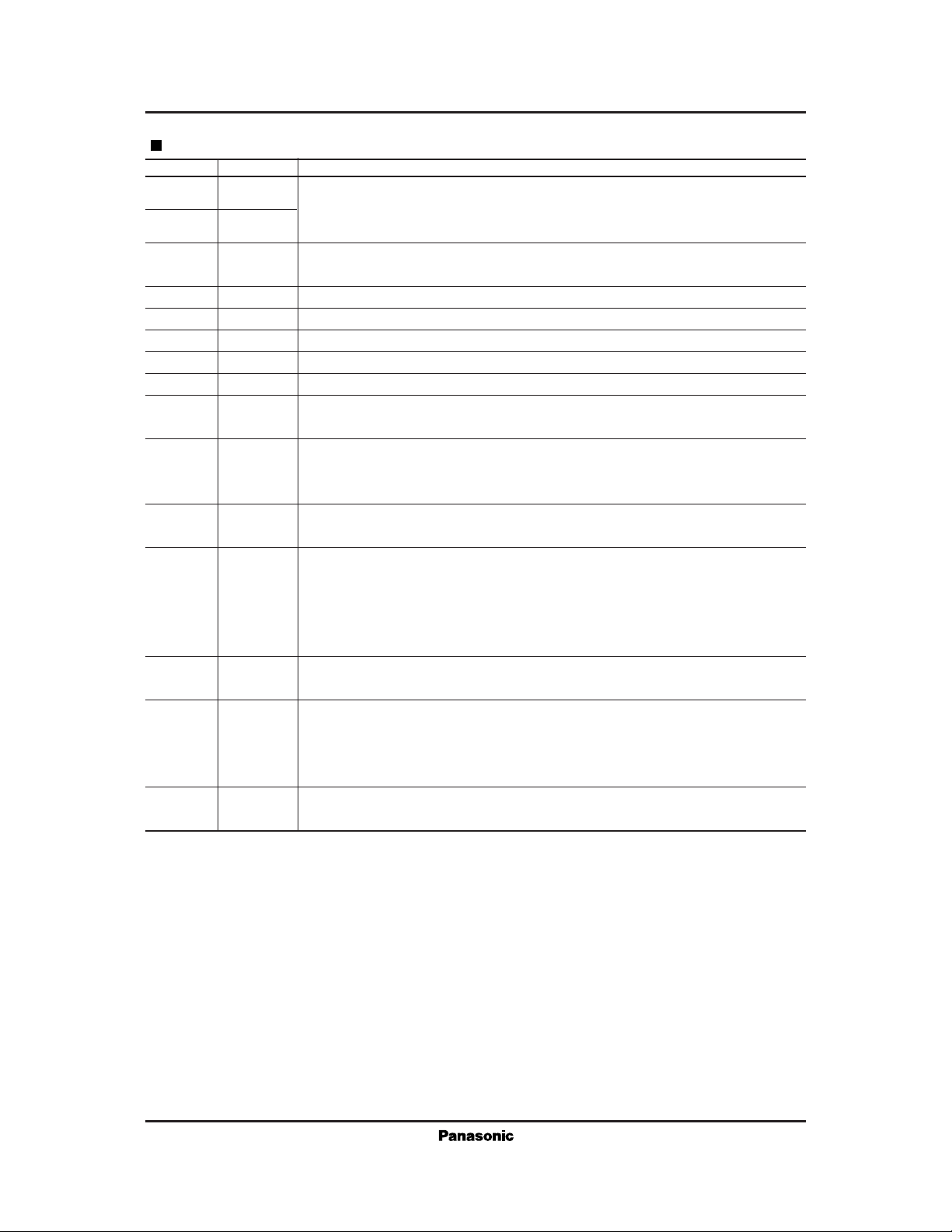

Pin Descriptions

Pin No. Symbol Function Description

1X

2X

IN

OUT

3 FV Frequency divider output signal in comparator stage.

4VDDPower supply

5DOPLow-pass filter connection pin. Use a passive filter.

6VSSGround

7VCPPower supply pin for built-in charge pump

8FINFrequency divider input pin in comparator stage.

9 CLK Shift register clock input pin.

10 DATA Shift register data input pin.

11 LE Load enable signal input pin.

12 PS Power save control signal input pin.

13 FR Reference frequency divider output signal.

14 LC Charge pump control signal output pin.

15 OV Phase comparator output pin for external charge pump.

16 OR (OR provides N-channel open drain output.)

Crystal oscillator connection pins:

XIN =Oscillator circuit input pin;

X

=Oscillator circuit output pin.

OUT

Phase comparator input monitor.

The chip latches data at the rising edge of the CLK signal.

The final two bits in the data select the write latch:

"11" for R-latch; "01" for N-latch.

This is the latch-write-enable signal. It is at "H" level for write.

"H" level input starts the frequency divider and places the chip in operational mode.

"L" level input places the chip in standby mode, which saves power.

The chip switches the internal charge pump output to the H-z state and the loop

is opened.

Phase comparator input monitor.

When frequency divider operation is stopped, this pin is at "L" level,

the internal charge pump output is in the high-impedance state, and the loop is

opened.

Loading...

Loading...