Panasonic AN78M05R, AN7805R, AN78M12R, AN78M09R, AN78M08R Datasheet

...

AN7800R/AN78M00R Series

Positive Output Voltage Regulators with

Reset pin (1A/500mA Type)

■ Overview

The AN7800R and the AN78M00R series are the fix ed

positive output voltage regulators with reset pin. Stabilized fixed output voltage is obtained from unstable DC

input voltage without using any external components.

Three types of output voltage, 5V, 9V and 12V, are available for the AN7800R series, and four types, 5V, 8V, 9V

and 12V, are available for the AN78M00R series. They

can be used in power circuits with current capacitance

1A/500mA. ON/OFF of output voltage can be controlled

by the reset pin.

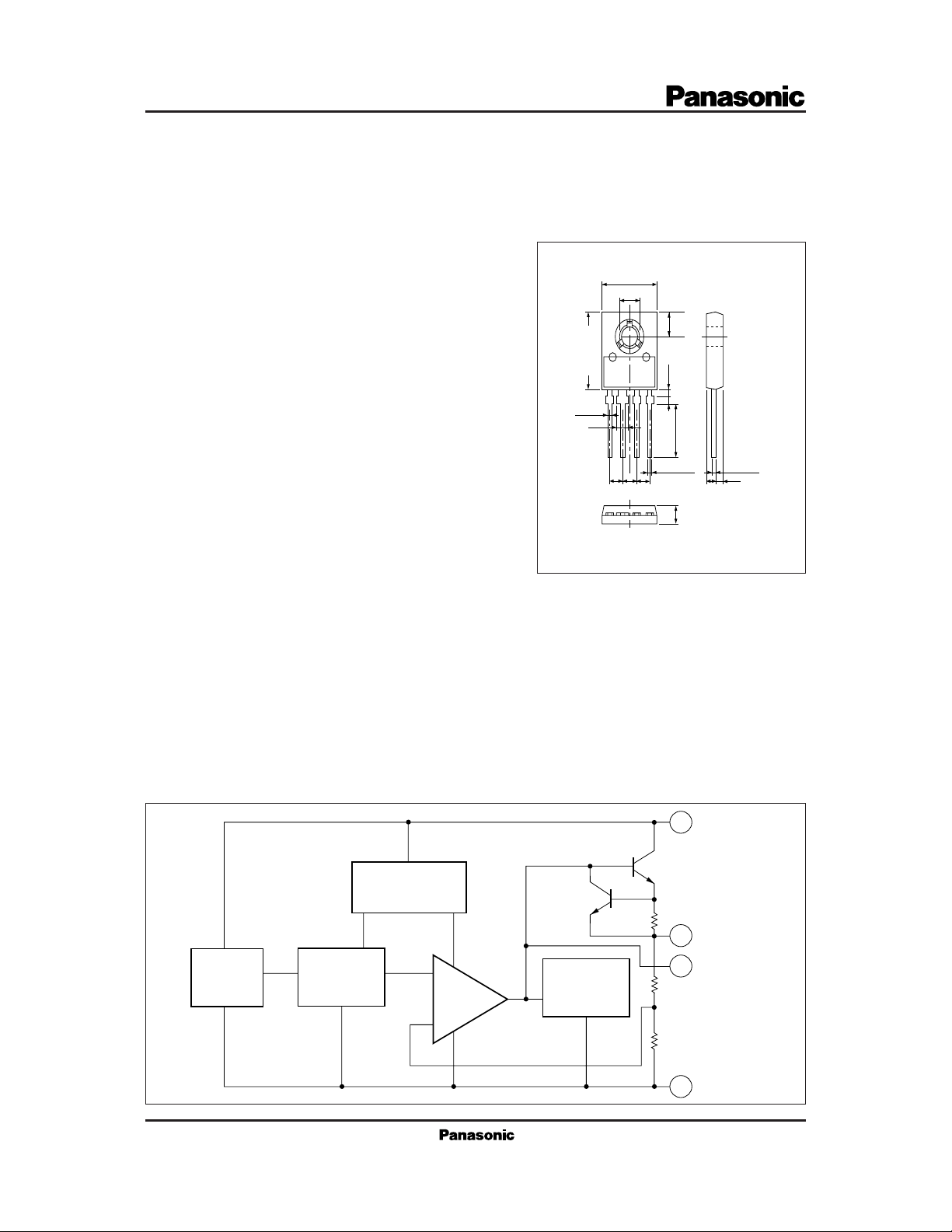

3–1.0

12.5max.

1.8

9.6

+ 0.5

– 0.1

ø 3.1

2.3 1.5 1.32.32.3

Unit:mm

4.0

2.0

9.0min.

0.7±0.2 0.5±0.1

■ Features

• No external components

• Maximum output current :1A (AN7800R)

500mA (AN78M00R)

• Output voltage :5V, 9V, 12V (AN7800R)

:8V (AN78M08R)

• Short-circuit current limiting built-in

• Thermal overload protection built-in

• Output transistor safe area compensation

• ON/OFF of output voltage can be controlled by reset

pin.

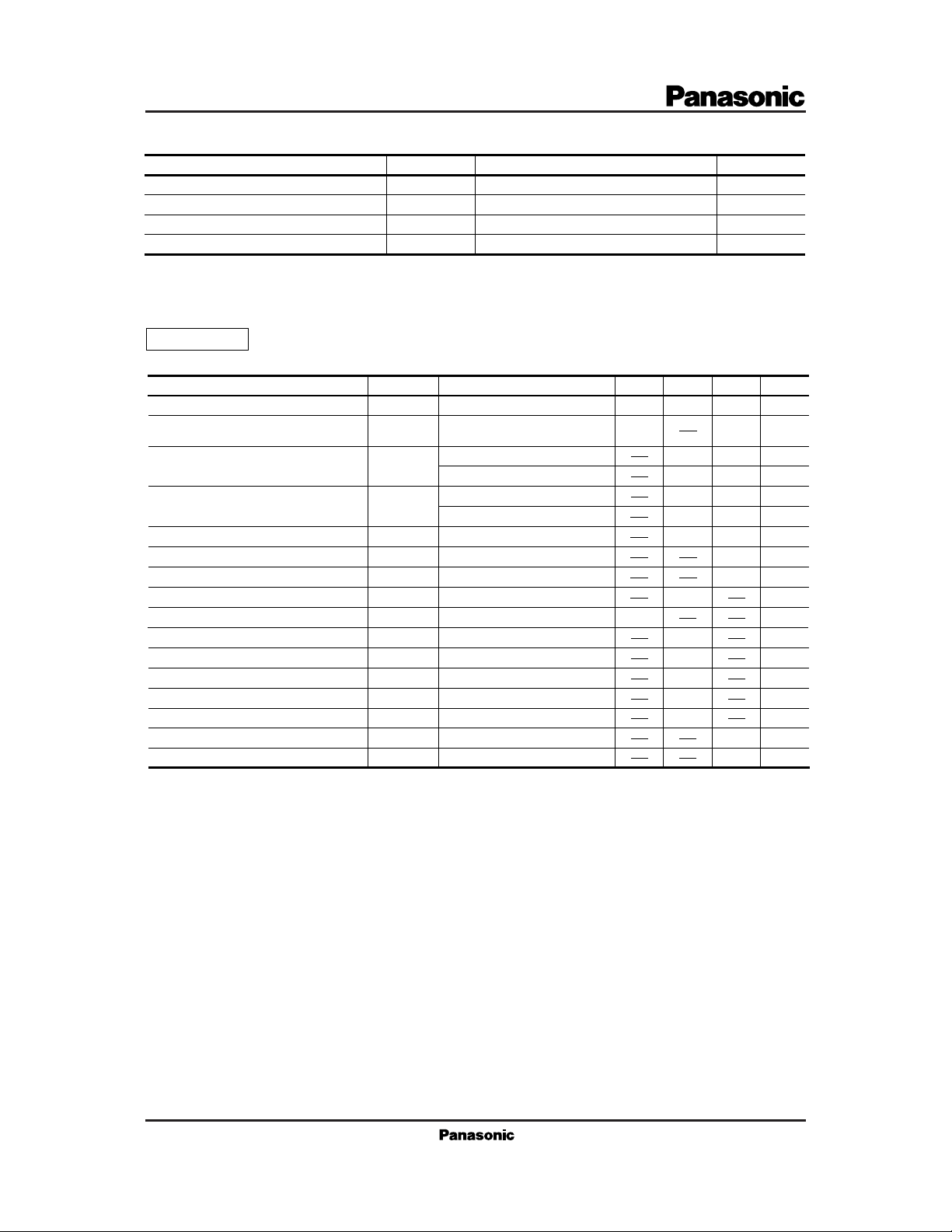

■ Block Diagram

Current

Source

Starter

Voltage

Reference

+

Error Amp.

–

3.3max.

4-pin SIL Plastic Package with Fin (SSIP004-P-0000)

Input

1

Pass Tr

Q

1

Current

Limiter

Thermal

Protection

R

SC

Output

3

Reset

4

R

2

R

1

2

Common

■ Absolute Maximum Ratings (Ta=25˚C)

Parameter Symbol Rating Unit

Input voltage

Power dissipation

Operating ambient temperature

Storage temperature

*

1 Follow the derating curve. When Tj exceeds 150˚C, the internal circuit cuts off the output.

V

I

P

D

T

opr

T

stg

35

1

*

10

–20 to + 80

–55 to + 150

V

W

˚C

˚C

■ Electrical Characteristics (Ta=25˚C)

AN7800R Series

AN7805R (1A, 5V Type)

·

Parameter Symbol Condition min typ max Unit

Output voltage

Output voltage tolerance

Line regulation

Load regulation

Bias current

Input bias current fluctuation

Load bias current fluctuation

Output noise voltage

Ripple rejection ratio

Minimum input/output voltage difference

Output impedance

Output short circuit current

Peak output current

Output voltage temperature coefficient

Output voltage at reset

Reset input current

V

V

REG

REG

I

bias

∆I

bias (IN)

∆I

bias (L)

V

RR

V

DIF (min.)

I

O (Short)

I

O (Peak)

∆VO/Ta

O (Reset)

I (Reset)

O

O

no

O

Note 1) The specified condition Tj=25˚C means that the test should be carried out with the test time so short (within 10ms) that the

drift in characteristic value due to the rise in chip junction temperature can be ignored.

Note 2) When not specified, VI=10V, IO=100mA, CI=0.33µF, CO=0.1µF, Tj=0 to 125˚C

=25˚C

T

j

=8 to 20V, IO=5mA to 1A,

V

I

=0 to 125˚C, P

T

j

=7.5 to 25V, Tj=25˚C

V

I

IN

=8 to 12V, Tj=25˚C

V

I

=5mA to 1.5A, Tj=25˚C

I

O

L

=250 to 750mA, Tj=25˚C

I

O

=25˚C

T

j

=7.5 to 25V, Tj=25˚C

V

I

=5mA to 1A, Tj=25˚C

I

O

f=10Hz to 100kHz

VI=8 to 18V, IO=100mA, f=120Hz

=1A, Tj=25˚C

I

O

f=1kHz

=35V, Tj=25˚C

V

I

Tj=25˚C

IO=5mA, Tj=0 to 125˚C

Tj=25˚C, I

I (Reset)

Tj=25˚C

<

D

=

=1mA

15W

4.8

4.75

5.2 V5

5.25

100 mV3

1

100

5

1.3

0.5

mV

50

mV15

mV

50

mA3.9

8

mA

mA

62

mΩ17Z

mA700

mV/˚C– 0.3

mA1I

V

µV40

dB

V2

A2

V1V

Loading...

Loading...