Oxford Semiconductor Ltd.

A

OXFW911

IEEE1394 to ATA/ATAPI Native Bridge

FEATURES

• S400 (50 Mbytes/s) compliant 1394-1995 Link and

Transaction layers

• Compatible with 1394-1995 and 1394A Phys.

• Microsoft Win98-Second Edition, Win2000 and Apple

MacOS generic driver support

• SBP-2 Target Revision 4 compliant interface

• Fully ATA-5 compliant (see T13-1321D)

• Support for UDMA5 (ATA100)

• Sustained data transfer of 35 MB/s

• Supports PIO modes 0 to 4, DMA modes 0 to 2 and

Ultra DMA modes 0 to 5

• ORB co-processor to accelerate translation of ORBs

to ATAPI commands

• Supports ORB chaining for increased performance

DESCRIPTION

The OXFW911 is a high-performance 1394 to

ATA/ATAPI (IDE) native bridge with an integrated target

Serial Bus Protocol (SBP-2 ) controller. By supporting

the SBP-2 protocol, the device can use generic SBP-2

drivers available in the Microsoft Windows 98SE, Microsoft

Windows 2000, Microsoft Millennium and Apple MacOS

(8.4 to 9.04) operating systems. MacOS support also

includes booting from Firewire disk.

The device is ideally suited for smart-cable or tailgate

interface applications for removable-media drives, compact

flash card readers, CD-ROM, CD-R, CD-RW, DVD-ROM,

DVD-RAM and hard disk drives, allowing IDE drives to be

connected to a 1394 serial bus in a plug-and-play fashion.

Both ATA and ATAPI devices are supported using the

same firmware.

This highly integrated device offers a two-chip solution to

native bridge applications using an external 1394 PHY. The

device is compatible with both 1394-1995 and 1394A

PHYs.

The LINK controller complies with 1394-1995 and 1394A

specifications. The 1394 transaction layer and SBP-2

protocol is implemented using a combination of the

ARM7TDMI (low-power 32-bit RISC processor), an ORB

(Operational Request Block) hardware co-processor and a

high performance buffer manager.

The buffer manager has a RAM bandwidth of 800Mbps. It

provides storage for 1394 and ATA/ATAPI packets,

Data Sheet

• High performance ATA command translation in

firmware using Reduced Block Command (RBC) set

• Integrated 32-bit RISC processor (ARM7TDMI) with

on-chip scratch RAM

• Optional External Serial ROM interface for

configuration data, user serial number, etc.

• Integrated 512kb Flash memory

• Blank Flash memory programming feature via 1394

bus

• Firmware and Flash Programming Utilities supplied by

Oxford Semiconductor

• 3.3 Volts operation

• Low Power CMOS

• Ultra-thin 128-TQFP package (14 x 14 x 1 mm)

automatically storing them and passing them to the

appropriate destinations, without any intervention from the

processor. It also provides storage and manages the

sequencing of ORB fetching to reduce latency and improve

data throughput.

The configuration data including the IEEE OUI

(Organisational Unique Identifier) and device serial number

is stored in the Flash ROM which may be uploaded from

the 1394 bus, even when blank. The device also facilitates

firmware uploads from the 1394 bus.

The ORB co-processor translates ORBs as defined in the

SBP-2 protocol into ATA/ATAPI commands, and

automatically stores error/status messages at an address

specified by the host.

Concurrent operation of the ATA/ATAPI and 1394

interfaces are facilitated using the high throughput buffer

manager where LINK, ATAPI manager and ARM7TDMI

can perform interleaved accesses to the on-chip RAM

buffer. The high performance processor ensures that no

significant latency is incurred. The ATA command

translation is performed in firmware to meet RBC (Reduced

Block Commands) standard, T10-1228D. The ATA/ATAPI

Manager supports PIO modes 0 to 4, DMA modes 0 to 2

and Ultra DMA mode 0 to 5 and provides the interface to

the IDE bus. It is compliant with T13-1321D, ATA-5

specification, as well as support for ATA100.

25 Milton Park, Abingdon, Oxon, OX14 4SH, UK

Tel: +44 (0)1235 824900 Fax: +44(0)1235 821141

OXFW911 Data Sheet Revision 1.1 – Mar 2001

Oxford Semiconductor 2001

Part No. OXFW911-TQ-

OXFORD SEMICONDUCTOR LTD.

OXFW911

CONTENTS

FEATURES........................................................................................................................................1

DESCRIPTION...................................................................................................................................1

CONTENTS........................................................................................................................................2

1 BLOCK DIAGRAM.......................................................................................................................3

2 PIN INFORMATION .....................................................................................................................4

3 PIN DESCRIPTIONS....................................................................................................................5

4 OPERATING CONDITIONS..........................................................................................................7

5 DC ELECTRICAL CHARACTERISTICS ........................................................................................7

5.1 I/O BUFFERS ........................................................................................................................................................................7

6 AC ELECTRICAL CHARACTERISTICS ........................................................................................8

6.1 IDE INTERFACE ...................................................................................................................................................................8

6.2 1394 LINK-PHY INTERFACE.............................................................................................................................................11

6.3 EXTERNAL PROCESSOR INTERFACE............................................................................................................................13

7 TIMING WAVEFORMS ...............................................................................................................14

8 PACKAGE INFORMATION ........................................................................................................ 29

9 ORDERING INFORMATION....................................................................................................... 29

NOTES............................................................................................................................................ 31

CONTACT DETAILS......................................................................................................................... 32

DISCLAIMER................................................................................................................................... 32

Data Sheet Rev 1.1 Page 2

OXFORD SEMICONDUCTOR LTD.

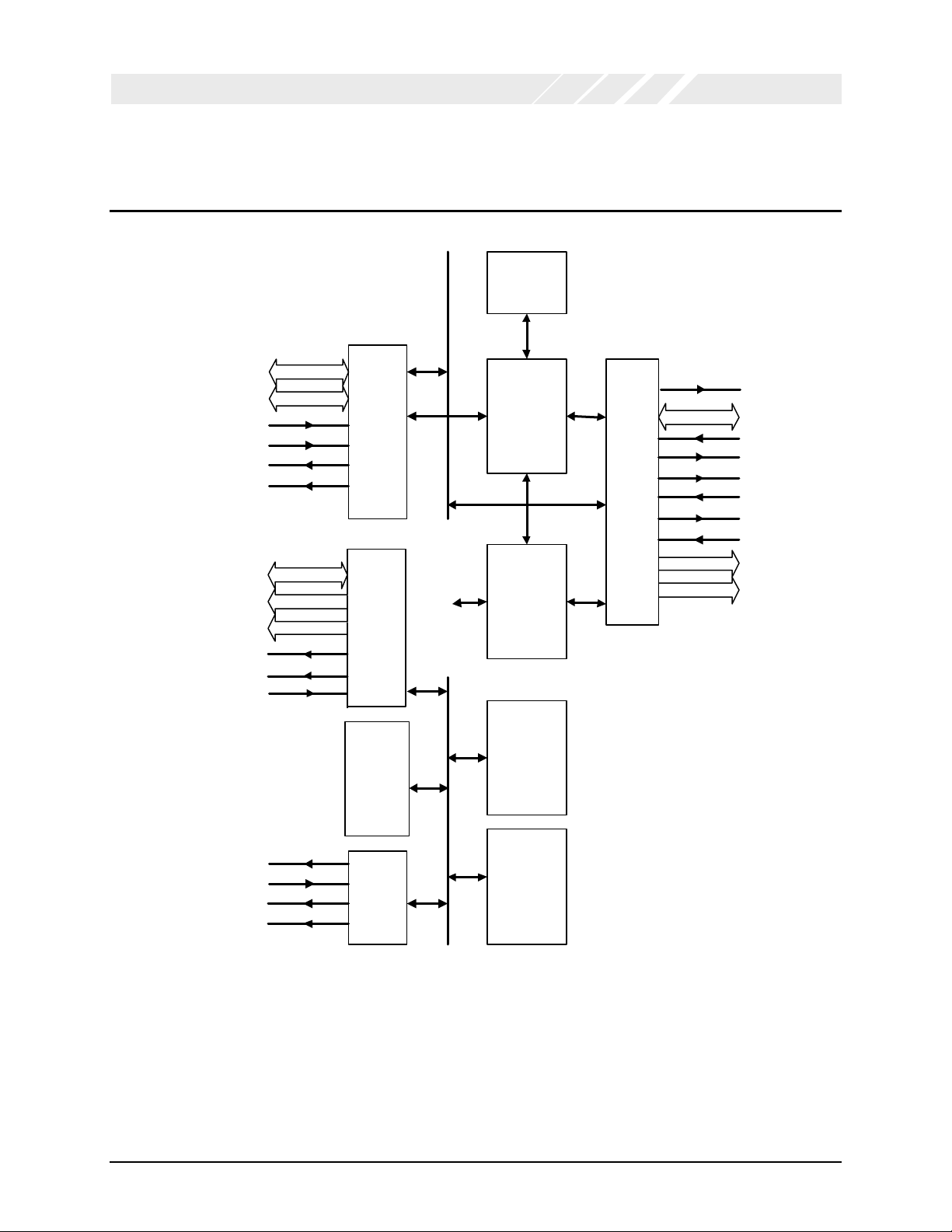

1 BLOCK DIAGRAM

PD[7:0]

CTL[1:0]

PHY_CLK

LINK_ON

LPS

LREQ

D[15:0]

A[16:0]

CS#[3:0]

OE#

WE#

INT#

Link-Phy

interface

External

Device

interface

Buffer RAM

RAM

Manager

ORB Co-

processor

Internal ARM7TDMI bus

ATA/

ATAPI

manager

OXFW911

IDE_OE#

ID[15:0]

DMARQ

DIOW#

DIOR#

IORDY

DMACK#

INTRQ#

IA[2:0]

ICS#[1:0]

Internal

FLASH

EE_DO

EE_DI GPIO /

EE_CK

EE_CS

EEPROM

interface

ARM7TDMI

SCRATCH

RAM

Figure 1: OXFW911 Block Diagram

Data Sheet Rev 1.1 Page 3

OXFORD SEMICONDUCTOR LTD.

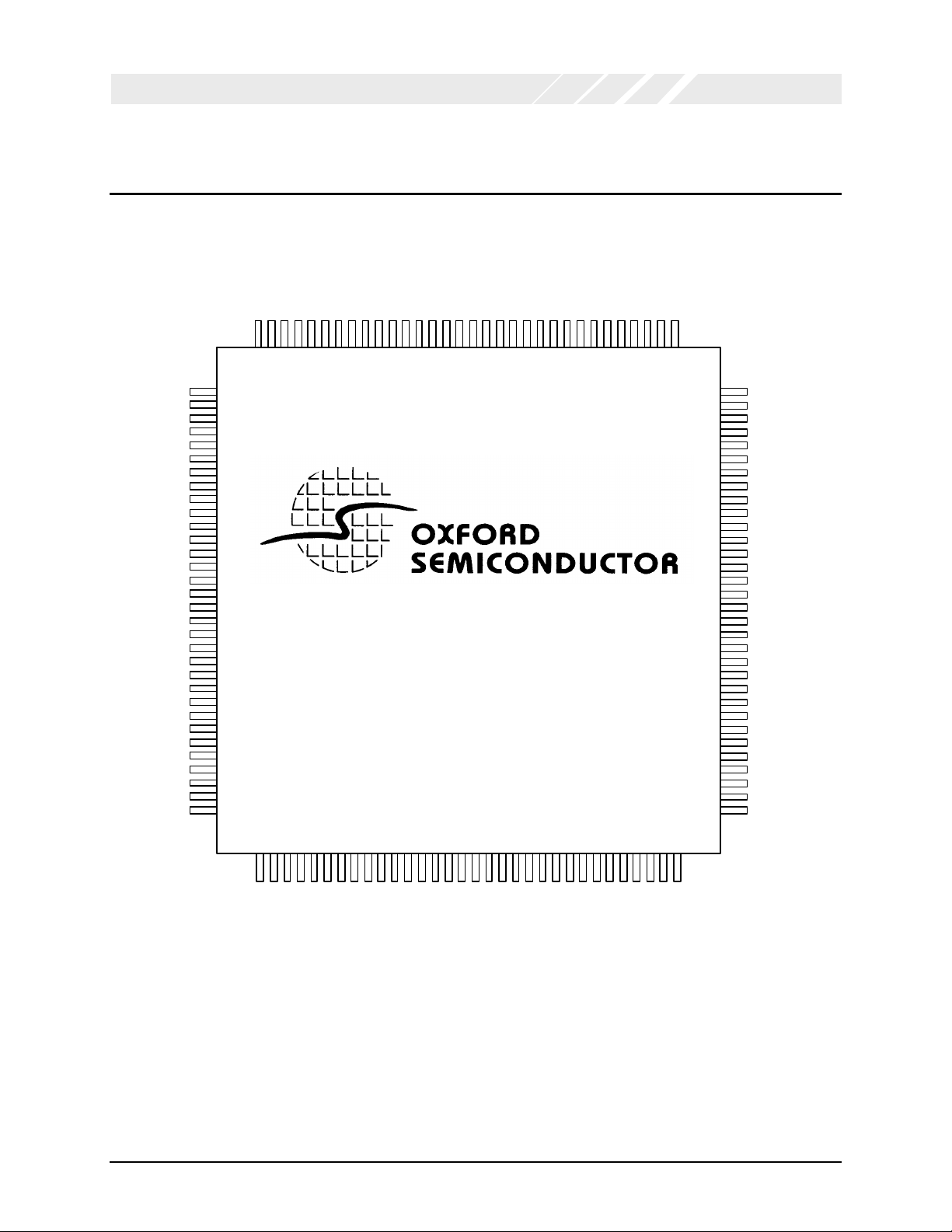

2 PIN INFORMATION

OXFW911

IA1

IA0

IA2

ICS0#

ICS1#

LINKON

LPS

PD7

PD6

GND

VDD

PD5

PD4

PD3

PD2

GND

VDD

PD1

PD0

CTL1

CTL0

GND

PHYCLK

VDD

LREQ

NC

CS3#

CS2#

GPO1

GPO2

GPO3

CKOUT

DMACK#

GND

IORDY

DIOR#

DIOW#

DMARQ

VDD

GND

ID15

ID0

VDD

GND

ID14

ID1

VDD

GND

96959493929190898887868584838281807877767574737271706968676665

97

98

99

100

101

102

103

104

105

106

107

108

109

110

111

112

113

114

115

116

117

OXFW911-TQ-A

118

119

120

121

122

123

124

125

126

127

128

ID13

ID2

79

ID12

ID3

VDD

GND

ID11

ID4

ID10

ID5

ID9

ID6

VDD

GND

ID8

ID7

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

IRESET

IDE_OE#

INTRQ

INT#

A0

VDD

GPI

UIF

RESET#

GND

A1

A2

A3

A4

A5

A6

VDD

GND

A7

A8

A9

A10

A11

A12

VDD

GND

A13

A14

A15

A16

WE#

CS0#

12345678910111213141516171920212223242526272829303132

D9D8D7

NC

D15

D14

D13

D12

D11

VDD

GND

D10

D6

GND

VDD

D5

D4

18

D3

D2

D1

VDD

D0

VDD

GND

TEST_SEL

GND

OE#

CS1#

VDD

GND

TEST0

TEST1

Figure 2: Pinout (package = 128 TQFP)

Data Sheet Rev 1.1 Page 4

OXFORD SEMICONDUCTOR LTD.

OXFW911

3 PIN DESCRIPTIONS

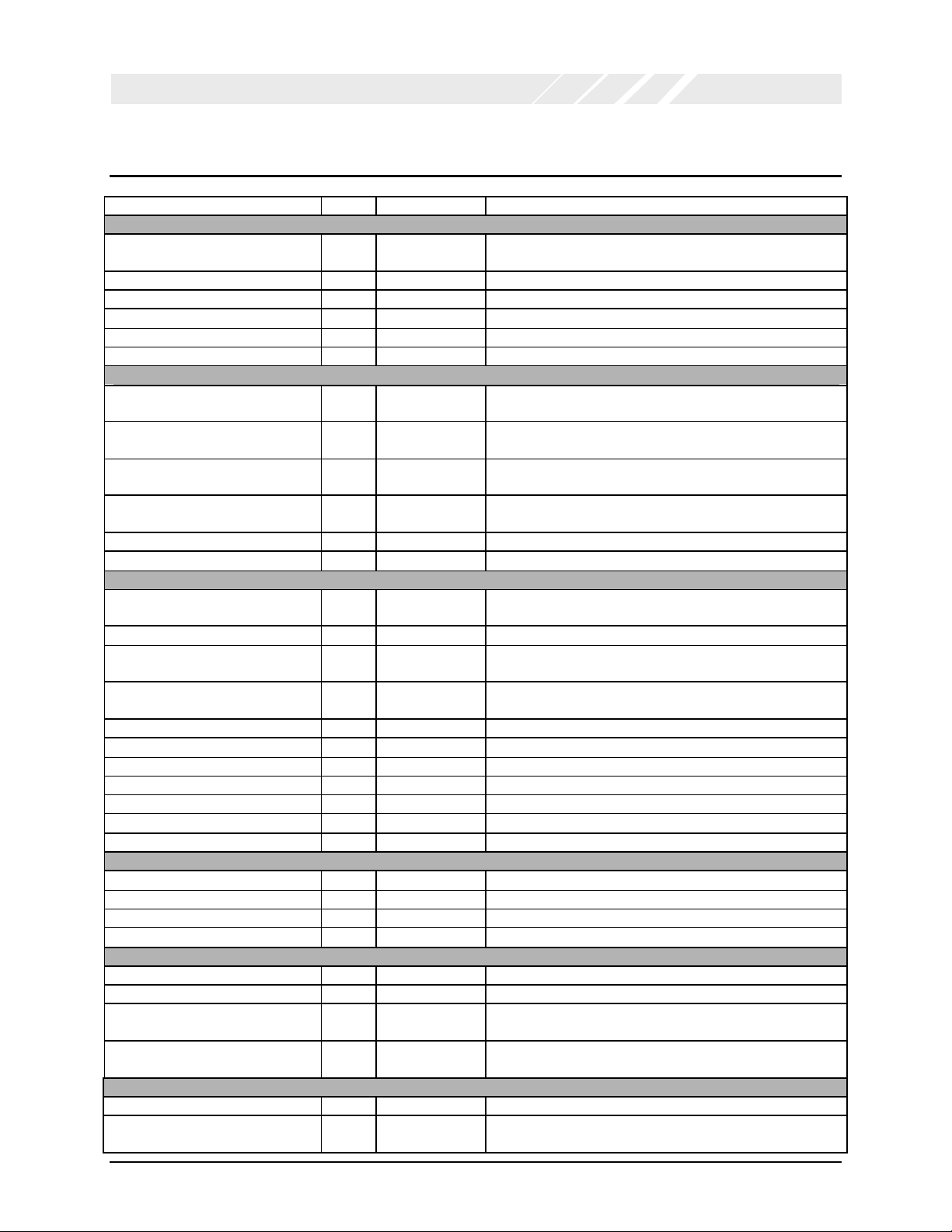

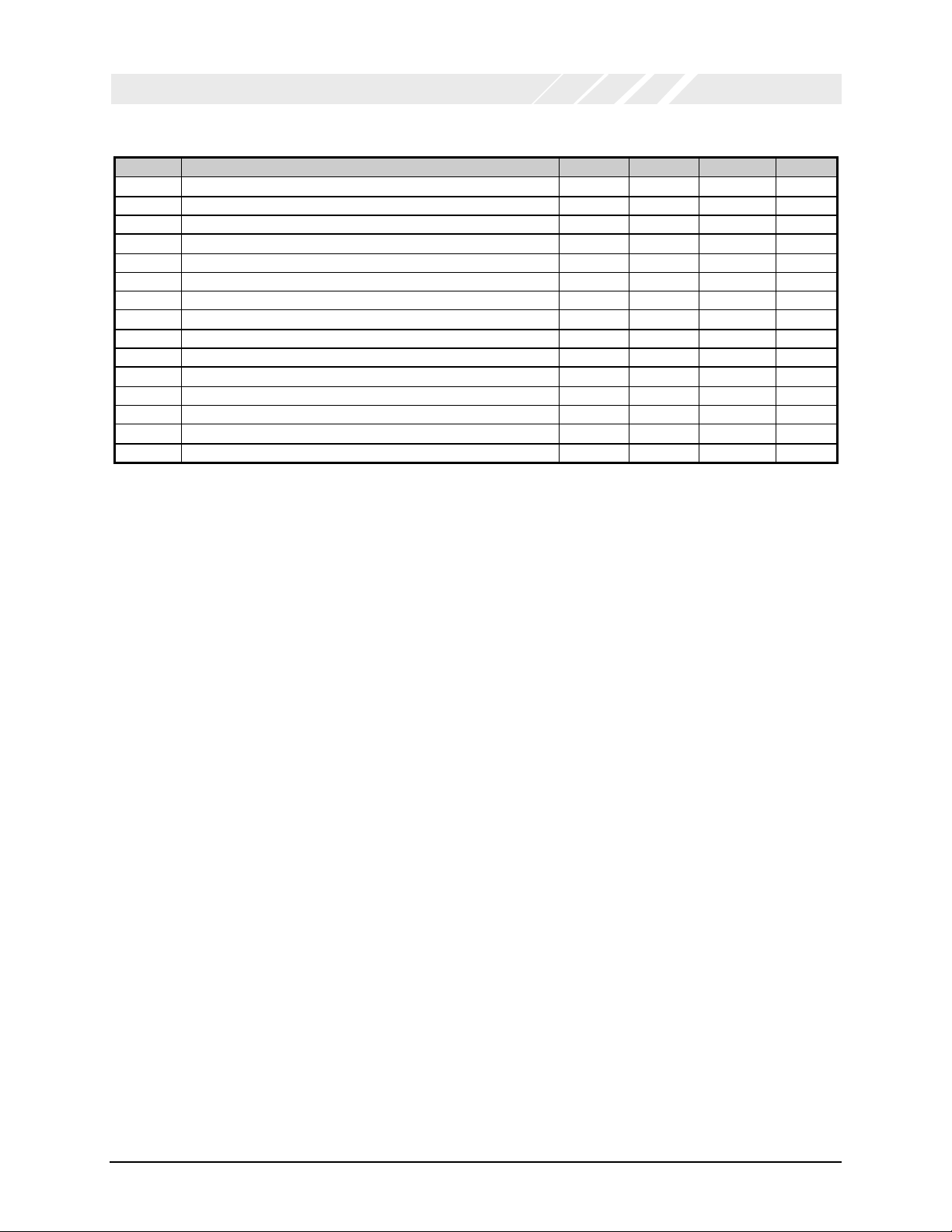

Dir1 Name Description

1394 PHY-LINK interface

104, 105, 108, 109, 110, 111, 114,

115

116,117 I/O CTL[1:0] Phy-Link Control Bus

119 I PHYCLK 49.152 MHz clock sourced by PHY

121 O LREQ Link Request

102 IU LINKON Requests link to power up when in a low power mode

103 O LPS Indicates to phy that link is powered and ready

ARM external interface

2, 3, 4, 5, 6, 9, 10, 11, 12, 13, 16,

17, 18, 19, 20, 24

35, 36, 37, 38, 41, 42, 43, 44, 45,

46, 49, 50, 51, 52, 53, 54, 60

123, 124, 27, 33 T_O CS#[3:0] ARM external chip selects. CS0# is always used for program

28 T_O OE# ARM external output enable. Active when reading data from

34 T_O WE# Write Enable. Active when writing to external devices

61 T_IU INT# External ARM interrupt

IDE interface

86, 82, 80, 78, 74, 72, 70, 66, 65,

69, 71, 73, 77, 79, 81, 85

99, 97, 98 T_O IA[2:0] IDE address bus

101, 100 T_O ICS#[1:0] IDE chip select. Used to select the Command Block or

63 T_O IDE_OE# IDE output enable. Only used when external buffering is

64 T_O IRESET IDE interface reset

89 T_I DMARQ

90 T_O DIOW# IDE interface write strobe

91 T_O DIOR# IDE interface read strobe

92 T_O IORDY

95 T_O DMACK#

62 T_I INTRQ

EEPROM interface

125 O GPO1 General Purpose Output 1

126 O GPO2 General Purpose Output 2

127 O GPO3 General Purpose Output 3

58 T_IU GPI General Purpose Input

Miscellaneous Pins

56 IU RESET# Global reset for the OXFW911. Active Low.

128 T_O CKOUT Clock output. 49.152 MHz clock output.

22, 32, 31 I TEST_SEL,

57 IU UIF Leave unconnected to use internal Flash, tie low to use only

Power and ground2

15, 8, 40, 48, 59, 76, 94, 107, 113 VDD AC VDD Supplies power to output buffers in switching (AC) state

30, 21, 23, 68, 84, 88, 120 VDD DC VDD Power supply. Supplies power to core logic, input buffers

I/O PD[7:0] Phy-Link Data Bus

T_I/O D[15:0] ARM external data bus

T_O A[16:0] ARM external address bus

ROM.

external devices including program ROM

T_I/O ID[15:0] IDE data bus

Control Block registers.

required to drive IDE data bus

‘100’ = NORMAL OPERATION. Other settings are for

TEST[1:0]

foundry test purposes only.

external device

and output buffers in steady state

Data Sheet Rev 1.1 Page 5

OXFORD SEMICONDUCTOR LTD.

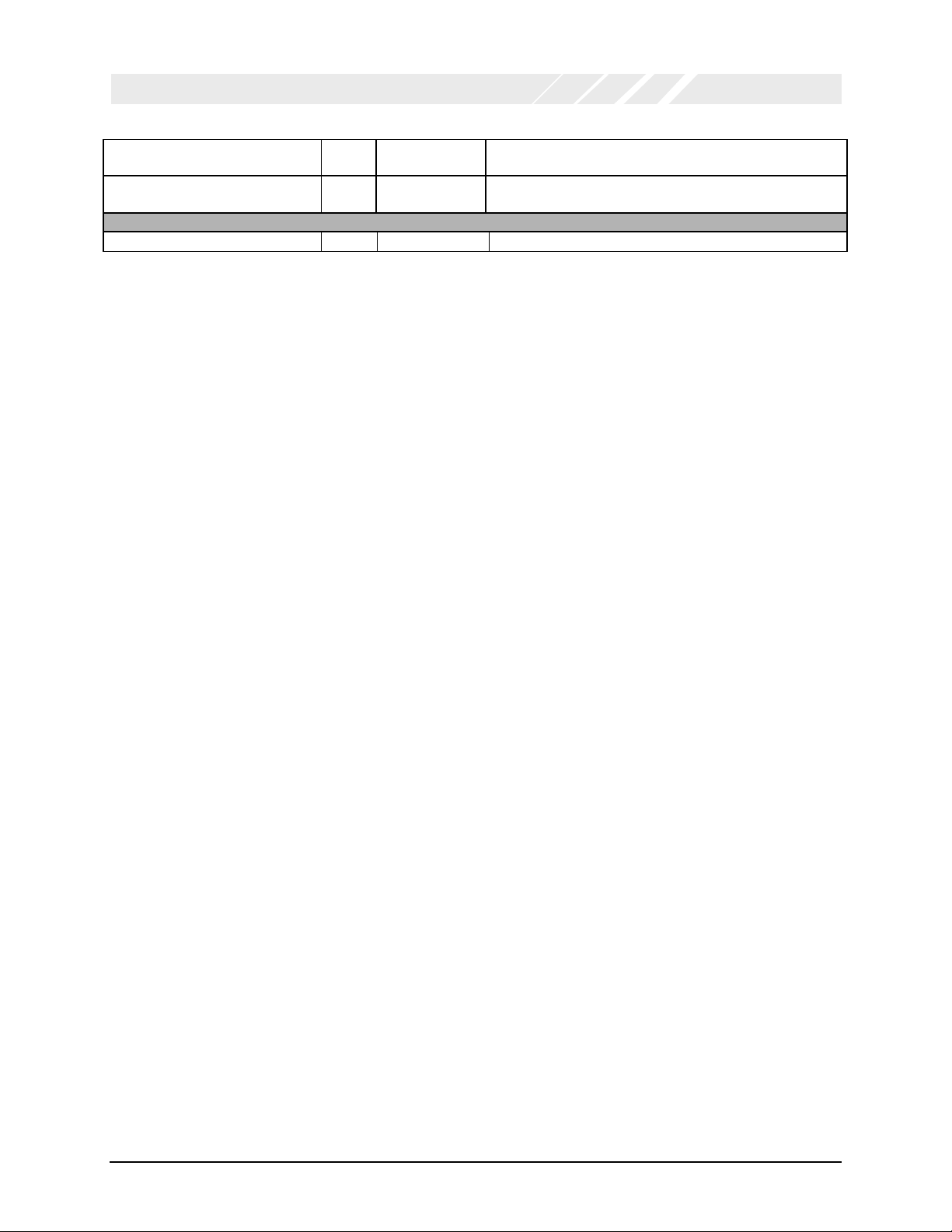

14, 7, 39, 47, 55, 67, 75, 93, 96,

106, 112,

29, 25, 26, 83, 87, 118 GND DC GND Ground (0 volts). Supplies GND to core logic, input buffers

Other

1, 122 NC No Connect

Note 1: Direction key:

I Input

IU Input with internal pull-up

ID Input with external pull-down

O Output

I/O Bi-directional

T_I 5V tolerant input

Note 2: Power & Ground

There are two GND and two VDD rails internally. One set of rails supply power and ground to output buffers while in switching

state (called AC power) and another rail supply the core logic, input buffers and output buffers in steady-state (called DC rail).

The rails are not connected internally. This precaution reduces the effects of simultaneous switching outputs and undesirable RF

radiation from the chip.

GND AC GND Supplies GND to output buffers in switching (AC) state

and output buffers in steady state

Table 1: Pin Descriptions

T_O 5V tolerant output

T_I/O 5V tolerant bi-directional

GND Ground

VDD 3.3V power

NC No Connect

OXFW911

Data Sheet Rev 1.1 Page 6

OXFORD SEMICONDUCTOR LTD.

Configuration & Operation

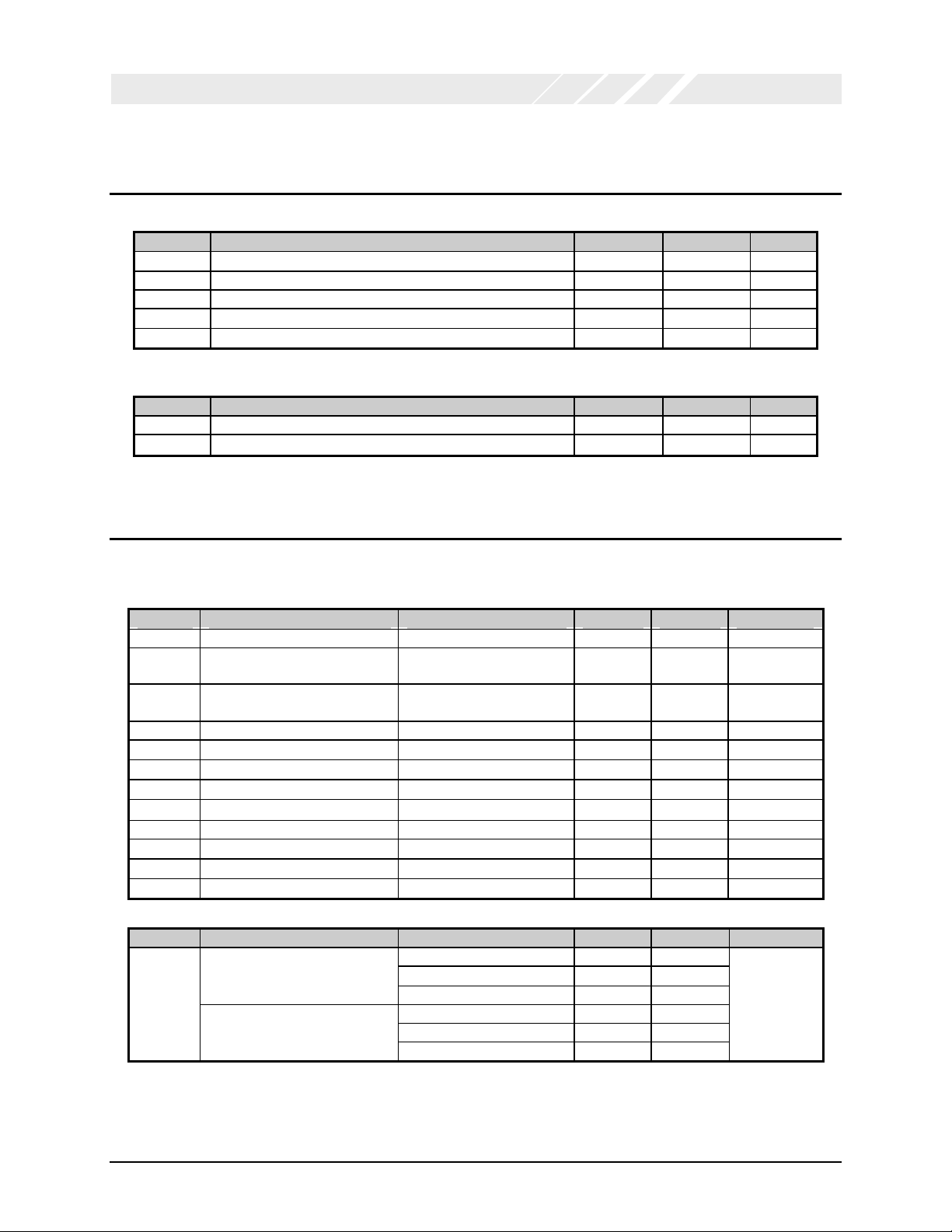

4 OPERATING CONDITIONS

Symbol Parameter Min Max Units

VDD DC supply voltage -0.3 3.8 V

VIN DC input voltage (3.3V IO) -0.3 VDD + 0.3 V

VIN DC input voltage (5V tolerant IO) -0.3 5.5 V

IIN DC input current +/- 10 mA

T

Storage temperature -40 125

STG

Table 2: Absolute maximum ratings

Symbol Parameter Min Max Units

VDD DC supply voltage 3.15 3.6 V

TC Temperature 0 70

Table 3: Recommended operating conditions

5 DC ELECTRICAL CHARACTERISTICS

OXFW911

°C

°C

5.1 I/O Buffers

Symbol Parameter Condition Min Max Units

VDD Supply voltage Commercial 3.0 3.6 V

V

VIL Input low voltage CMOS Interface 1

CIL Cap of input buffers 4.0 pF

COL Cap of output buffers 4.0 pF

IIH Input high leakage current Vin = VDD -10 10

IIL Input low leakage current Vin = VSS -10 10

VOH Output high voltage

VOH Output high voltage IOH = -1mA to –24mA 2.4 V

VOL Output low voltage

VOL Output low voltage IOL = 1mA to 24mA 0.4 V

IOZ 3-state output leakage current -10 10

Symbol Parameter Condition Typical Max Units

ICC

Input high voltage CMOS Interface

IH

Operating supply current in

normal mode

Operating supply current in

Power-down mode

2.0

CMOS Schmitt trig

CMOS Schmitt trig

IOH = -1 µA

IOL = 1 µA

VDD = 3.3V 85 TBD

T=25°C

2.0

0.8

VDD – 0.05

0.05 V

V

0.8

V

V

µA

µA

µA

mA

Table 4: Characteristics of OXFW911 I/O buffers

Data Sheet Rev 1.1 Page 7

OXFORD SEMICONDUCTOR LTD.

OXFW911

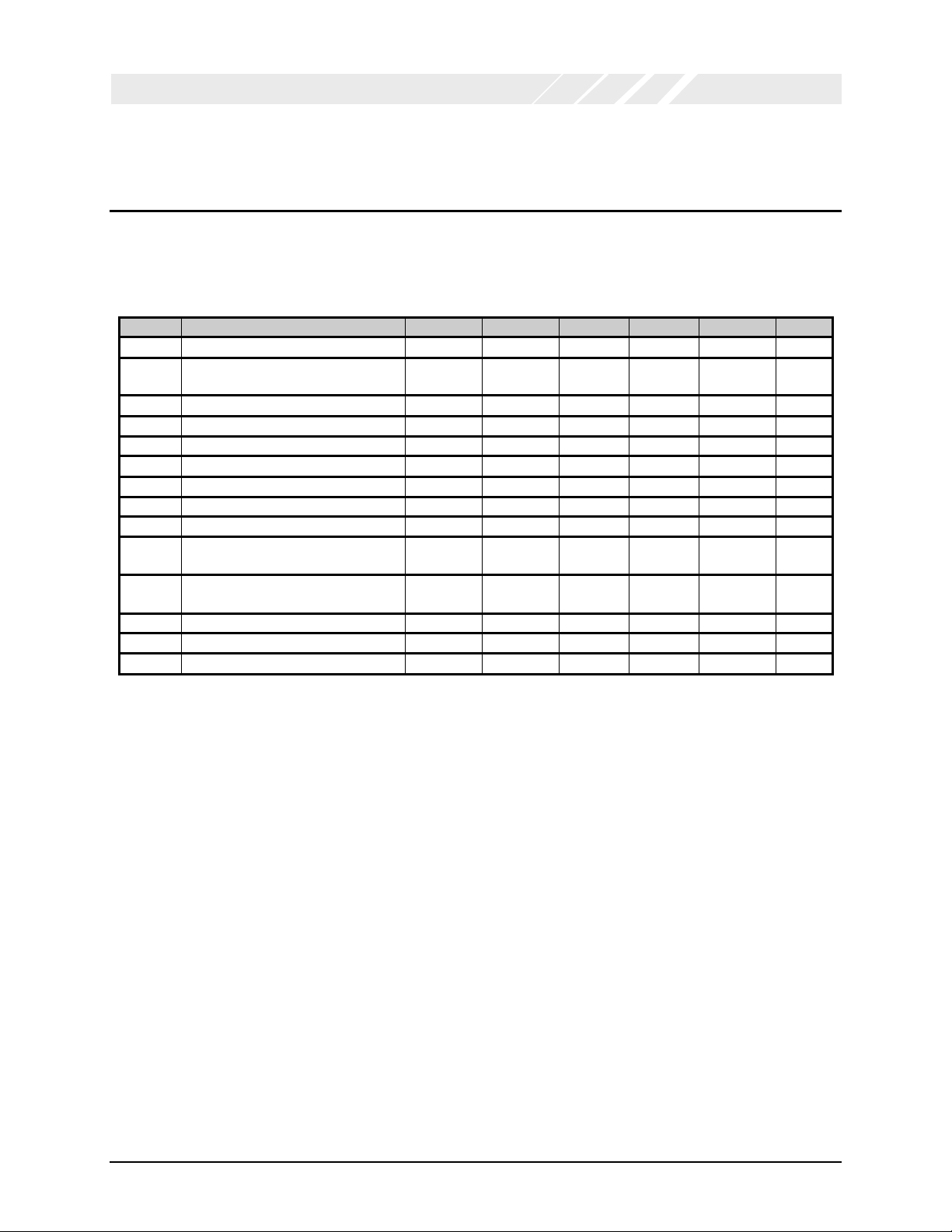

6 AC ELECTRICAL CHARACTERISTICS

6.1 IDE interface

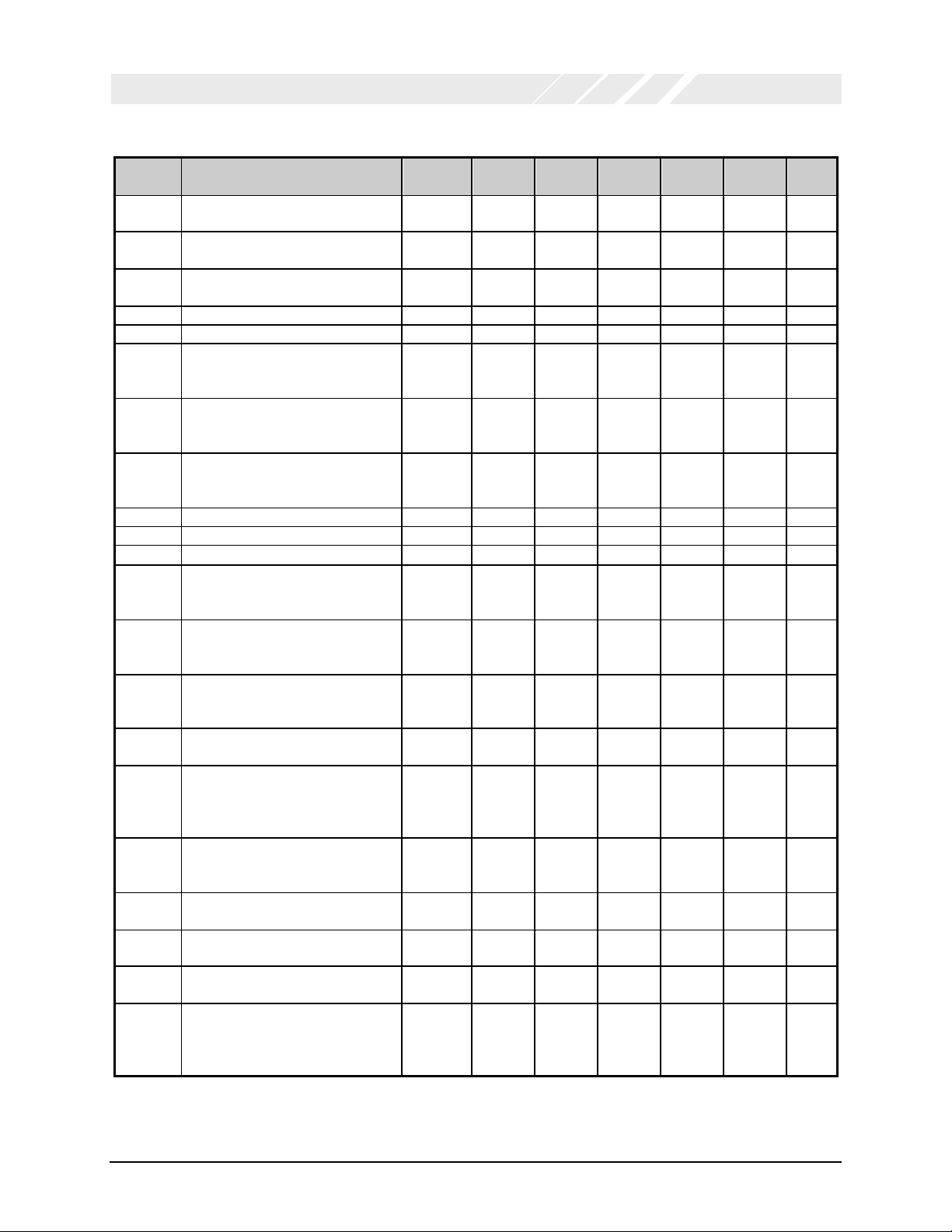

Symbol Parameter Mode 0 Mode 1 Mode 2 Mode 3 Mode 4 Units

t0 Cycle Time 600 400 360 200 120 ns

t1 Address Valid to DIOR# / DIOW#

setup

t2 DIOR# / DIOW# pulse width 320 320 320 80 80 ns

t2i DIOR# / DIOW# recovery time - - - 80 40 ns

t3 DIOW# data setup (min ) 60 45 30 30 20 ns

t4 DIOW# data hold 40 40 40 40 40 ns

t5 DIOR# data setup ( min ) 50 35 20 20 20 ns

t6 DIOR# data hold ( min ) 5 5 5 5 5 ns

t6z DIOR# data tristate (max ) 30 30 30 30 30 ns

t9 DIOR# / DIOW# to address valid

hold

tRD Read Data Valid to IORDY active if

IORDY initially low after tA

tA IORDY Setup time 35 35 35 35 35 ns

tB IORDY Pulse Width ( max ) 1250 1250 1250 1250 1250 ns

tA IORDY assertion to release 5 5 5 5 5 ns

80 80 40 40 40 ns

40 40 40 40 40 ns

0 0 0 0 0 ns

Table 5: OXFW911 IDE PIO / Register Transfers

Data Sheet Rev 1.1 Page 8

OXFORD SEMICONDUCTOR LTD.

Symbol Parameter Mode 0 Mode 1 Mode 2 Units

t0 Cycle time 480 160 120 ns

tD DIOR# / DIOW# 240 80 80 ns

tE DIOR# data access ( max ) 150 60 50 ns

tF DIOR# data hold ( min ) 5 5 5 ns

tG DIOR# / DIOW# data setup 100 30 20 ns

tH DIOW# data hold 20 15 10 ns

tI DMACK to DIOR# / DIOW# setup ( min ) 0 0 0 ns

tJ DIOR# / DIOW# to DMACK hold ( min ) 20 5 5 ns

tKr DIOR# negated pulse width 80 80 40 ns

tKw DIOW# negated pulse width 240 80 40 ns

tLr DIOR# to DMARQ delay ( max ) 120 40 35 ns

tLw DIOW# to DMARQ delay ( max ) 40 40 35 ns

tM IDCS[1:0] valid to DIOR# / DIOW# 80 40 40 ns

tN IDCS[1:0] hold 40 40 40 ns

tZ DMACK to tristate ( max ) 20 25 25 ns

Table 6: OXFW911 Multiword DMA timings

OXFW911

Data Sheet Rev 1.1 Page 9

OXFORD SEMICONDUCTOR LTD.

Symbol Parameter Mode 0

t2cyc Typical sustained average two

cycle time

tcyc Cycle time allowing for clock

variations ( refer to ATA spec)

t2cyc Two cycle time allowing for clock

variations ( refer to ATA spec )

tds Data setup time at recipient 15 10 7 ns

tdh Data hold time at recipient 5 5 5 ns

tdvs Data valid setup time at sender

(from data bus being valid until

STROBE edge )

tdvh Data valid hold time at sender (from

STROBE edge until data may

become invalid

tfs First STROBE time (for device to

first negate DSTROBE from STOP

during a data-in burst)

tli Limited interlock time 0 150 0 150 0 150 ns

tmli Interlock time with minimum 20 20 20 ns

tui Unlimited interlock time 0 0 0 ns

taz Maximum time allowed for output

drivers to release (from being

asserted or negated)

tzah

tzad

tenv Envelope time ( from DMACK# to

tsr STROBE to DMARDY time ( refer

trfs Ready-to-final-STROBE time ( no

trp Ready-to-pause time ( time that

tiordyz Pull-up time before allowing IORDY

tziordy Minimum time a device shall wait

tack Setup and hold times for DMACK#

tss Time from STROBE edge to

Minimum delay time required for

output drivers to assert or negate

(from released state)

STOP and HDMARDY# during

data-out burst initiation

to ATA spec

STROBE edges shall be sent this

long after the negation of

DDMARDY#

recipient shall wait to initiate pause

after negating DMARDY# )

to be released

before driving IORDY

(before assertion or negation )

negation of DMARQ or assertion of

STOP (when sender terminates a

burst )

Mode 0

min

240 160 120 ns

112 75 55 ns

230 156 117 ns

70 48 34 ns

6 6 6 ns

0 230 0 200 0 170 ns

10 10 10 ns

20

0

20 70 20 70 20 70 ns

50 30 20 ns

75 70 60 ns

160 125 100 ns

20 20 20 ns

0 0 0 ns

20 20 20 ns

50 50 50 ns

max

Mode 1

min

20

0

Mode1

max

20

Mode 2

min

0

OXFW911

Mode 2

max

Units

ns

Table 7: OXFW911 Ultra DMA timings

Data Sheet Rev 1.1 Page 10

Loading...

Loading...