OXFORD OX9162 Datasheet

Oxford Semiconductor Ltd.

October 1999

OX9162

Integrated Parallel Port/Local

EATURE

F

8 bit pass-through local bus

•

• IEEE1284 SPP/EPP/ECP parallel port

• Single function target PCI controller, fully PCI 2.2 and

PCI Power Management 1.0 compliant

ESCRIPTION

D

The OX9162 is a single chip solution for PCI-based parallel

expansion add-in cards, or local bus bridges. It is a single

function PCI device, where function 0 offers either an 8 bit

Local Bus or a bi-directional parallel port.

For legacy applications the PCI resources are arranged so

that the parallel port can be located at standard I/O

addresses.

The efficient 32-bit, 33MHz target-only PCI interface is

compliant with version 2.2 of the PCI Bus Specification and

version 1.0 of PCI Power Management Specification. For

Bus and PCI interface

• 2 multi-purpose IO pins which can be configured as

interrupt input pins

• Can be reconfigured using optional non-volatile

configuration memory (EEPROM)

5.0V operation

•

• 128 TQFP package

full flexibility, all the default register values can be

overwritten using an optional MicrowireTM serial EEPROM.

Bridging applications can be realised using the 8-bit passthrough Local Bus function. The addressable space can be

increased up to 256 bytes for each chip-select region.

The OX9162 alternatively provides an IEEE1284 EPP/ECP

parallel port which fully supports the existing Centronics

interface. The parallel port can be enabled in place of the

Local Bus.

69 Milton Park, Abingdon, Oxon, OX14 4RX, UK

Tel: +44 (0)1235 824900 Fax: +44(0)1235 821141

OX9162 1.0 PRELIMINARY –

Oxford Semiconductor 1999

Part No. OX9162-TQC-A

OX9162

OXFORD SEMICONDUCTOR LTD.

CONTENTS

1 PIN INFORMATION...................................3

2 PIN DESCRIPTIONS .................................4

3 CONFIGURATION & OPERATION............ 8

4 PCI TARGET CONTROLLER....................9

4.1 OPERATION............................................................ 9

4.2 CONFIGURATION SPACE ....................................9

4.2.1 PCI CONFIGURATION SPACE REGISTER

MAP 10

4.3 ACCESSING LOGICAL FUNCTIONS.................11

4.3.1 PCI ACCESS TO 8-BIT LOCAL BUS ..............11

4.3.2 PCI ACCESS TO PARALLEL PORT...............11

4.4 ACCESSING LOCAL CONFIGURATION

REGISTERS ........................................................................12

4.4.1 LOCAL CONFIGURATION AND CONTROL

REGISTER ‘LCC’ (OFFSET 0X00) ....................................12

4.4.2 MULTI-PURPOSE I/O CONFIGURATION

REGISTER ‘MIC’ (OFFSET 0X04).....................................13

4.4.3 LOCAL BUS TIMING PARAMETER REGISTER

1 ‘LT1’ (OFFSET 0X08): .....................................................13

4.4.4 LOCAL BUS TIMING PARAMETER/BAR

SIZING REGISTER 2 ‘LT2’ (OFFSET 0X0C):...................15

4.4.5 GLOBAL INTERRUPT STATUS AND

CONTROL REGISTER ‘GIS’ (OFFSET 0X10).................16

4.5 PCI INTERRUPTS................................................. 17

4.6 POWER MANAGEMENT......................................18

4.6.1 POWER MANAGEMENT USING MIO ............18

5 LOCAL BUS ...........................................19

5.1 OVERVIEW............................................................19

5.2 OPERATION.......................................................... 19

5.3 CONFIGURATION & PROGRAMMING ..............20

6 BI-DIRECTIONAL PARALLEL PORT...... 21

6.1 OPERATION AND MODE SELECTION..............21

6.1.1 SPP MODE........................................................21

6.1.2 PS2 MODE ........................................................21

6.1.3 EPP MODE........................................................21

6.1.4 ECP MODE........................................................21

6.2 PARALLEL PORT INTERRUPT ..........................21

6.3 REGISTER DESCRIPTION.................................. 22

6.3.1 PARALLEL PORT DATA REGISTER ‘PDR’... 22

6.3.2 ECP FIFO ADDRESS / RLE............................ 22

6.3.3 DEVICE STATUS REGISTER ‘DSR’ .............. 22

6.3.4 DEVICE CONTROL REGISTER ‘DCR’........... 23

6.3.5 EPP ADDRESS REGISTER ‘EPPA’ ...............23

6.3.6 EPP DATA REGISTERS ‘EPPD1-4’ ...............23

6.3.7 ECP DATA FIFO............................................... 23

6.3.8 TEST FIFO........................................................ 23

6.3.9 CONFIGURATION A REGISTER.................... 23

6.3.10 CONFIGURATION B REGISTER.................... 24

6.3.11 EXTENDED CONTROL REGISTER ‘ECR’ ....24

7 SERIAL EEPROM ................................... 25

7.1 SPECIFICATION................................................... 25

7.2 EEPROM DATA ORGANISATION...................... 25

7.2.1 ZONE0: HEADER............................................. 25

7.2.2 ZONE1: LOCAL CONFIGURATION

REGISTERS........................................................................ 27

7.2.3 ZONE2: IDENTIFICATION REGISTERS........ 28

7.2.4 ZONE3: PCI CONFIGURATION REGISTERS28

7.2.5 ZONE4: FUNCTION ACCESS......................... 28

8 OPERATING CONDITIONS.....................30

9 DC ELECTRICAL CHARACTERISTICS ..30

9.1 NON-PCI I/O BUFFERS....................................... 30

9.2 PCI I/O BUFFERS................................................. 31

10 AC ELECTRICAL CHARACTERISTICS

32

10.1 PCI BUS ................................................................ 32

10.2 LOCAL BUS.......................................................... 32

11 TIMING WAVEFORMS ........................34

12 ERRATA 1 – IMMEDIATE POWER

DOWN FILTERING.........................................39

Data Sheet Revision 1.1 PRELIMINARY Page 2

OX9162

OXFORD SEMICONDUCTOR LTD.

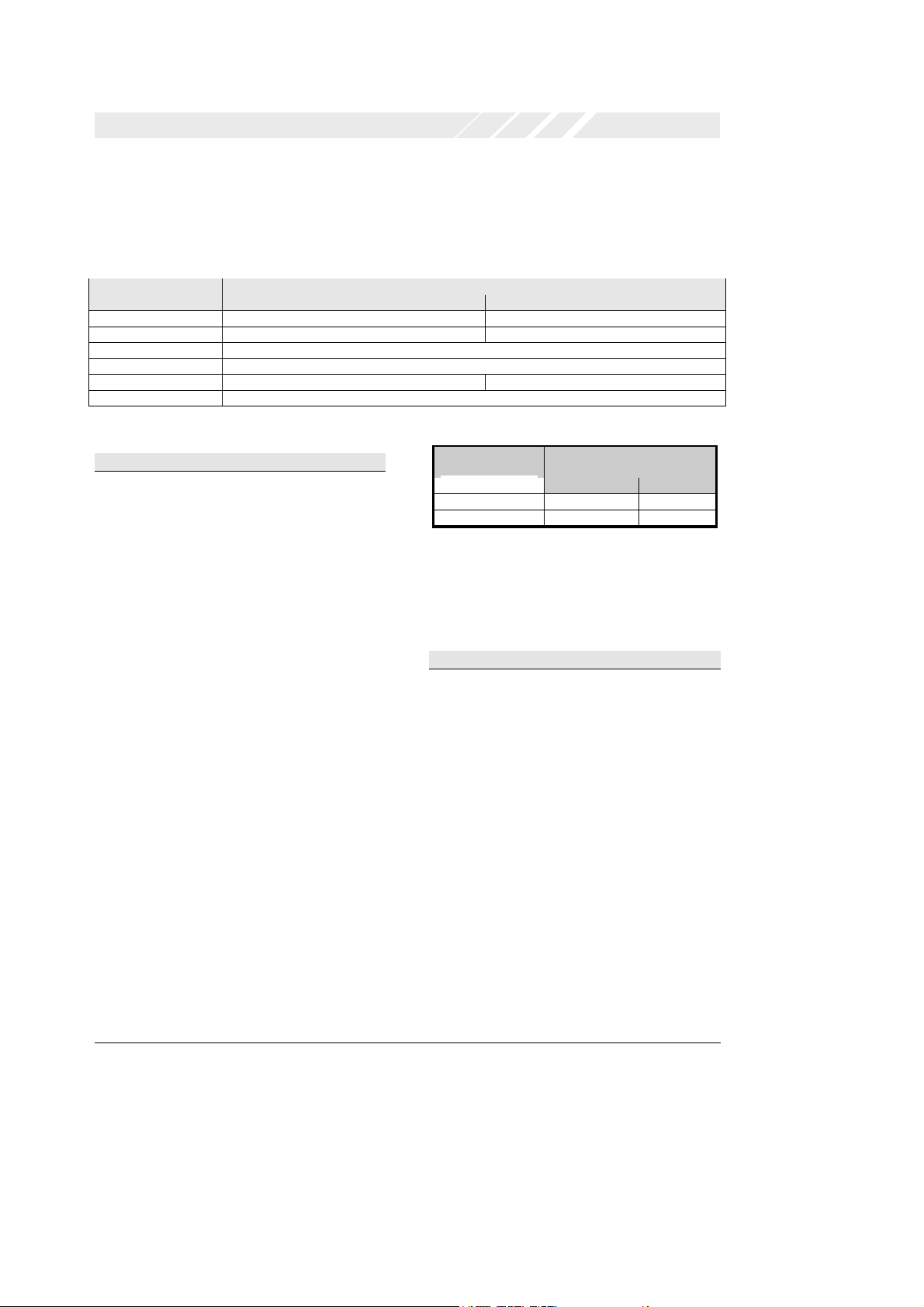

GND ac

AD10

148121620242832

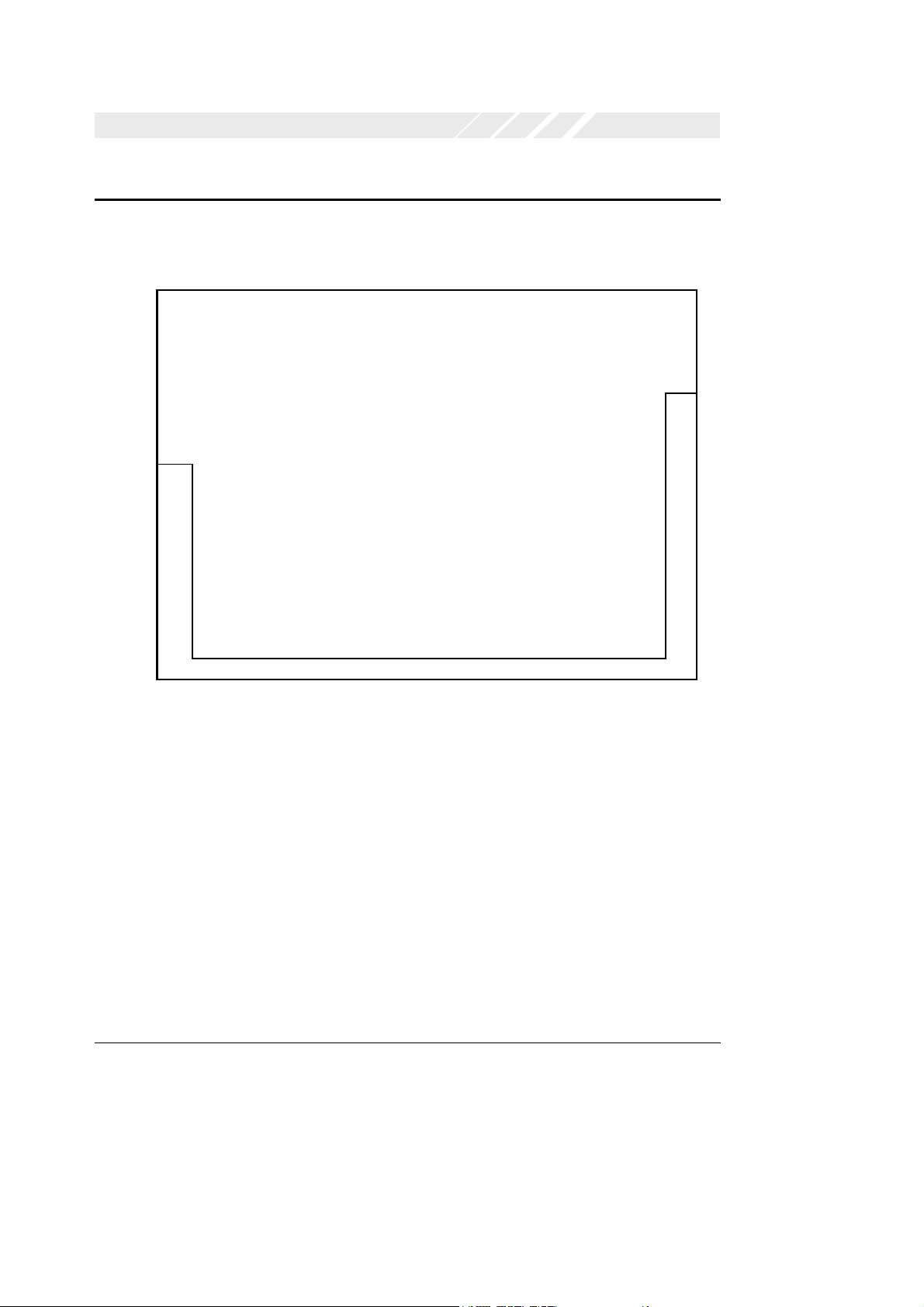

1 PIN INFORMATION

128 pin TQFP

EE_DO

IDSEL

EE_CS

AD23

TEST

AD22

GND ac

LBCS0

AD21

LBA0-STB

LBA1-AFD#

AD20

GND ac

LBA2-INIT#

LBA3-SLIN#

AD19

VDD ac

EE_DI

96 92 88 84 80 76 72 68 65

97 64

NC

EE_SK LBWR

LBCS1 LBRST

NC

LBCLK 60 NC

MODE VDD dc

Z_INTA

Z_RESET NC

GND dc AD4

PCI_CLK

VDD dc

Z_PME VDD ac

GND ac Z_CBE0

VDD ac

Z_CBE3 AD12

100

NC AD0

NC AD1

104

MIO1

NC

NC AD3

108

NC

112

AD31 AD6

116

NC

AD30

AD29 NC

120

AD28

AD27

AD26 AD9

124

AD25

AD24 AD11

NC 128 33 NC

NC

NC

GND ac

LBRD - ACK#

AD18

AD17

NC

AD16

DATA_EN

LBA4-ERR#

Z_CBE2

Z_FRAME

VDD dc

GND dc

VDD dc

GND dc

LBA5-SLCT

LBA6-BUSY

Z_IRDY

Z_TRDY

LBA7-PE

LBD0-PD0

GND ac

Z_DEVSEL

GND ac

LBD1-PD1

Z_STOP

Z_PERR

LBD2-PD2

LBD3-PD3

PAR

Z_SERR

VDD ac

LBD4-PD4

AD15

Z_CBE1

GND ac

LBD5-PD5

AD14

AD13

LBD6-PD6

LBD7-PD7

VDD ac

GND ac

MIO0

NC

NC

LBRST#

GND ac

56

AD2

GND dc

52

NC

AD5

48

GND ac

AD7

44

NC

AD8

40

GND ac

NC

36

NC

Data Sheet Revision 1.1 PRELIMINARY Page 3

OX9162

OXFORD SEMICONDUCTOR LTD.

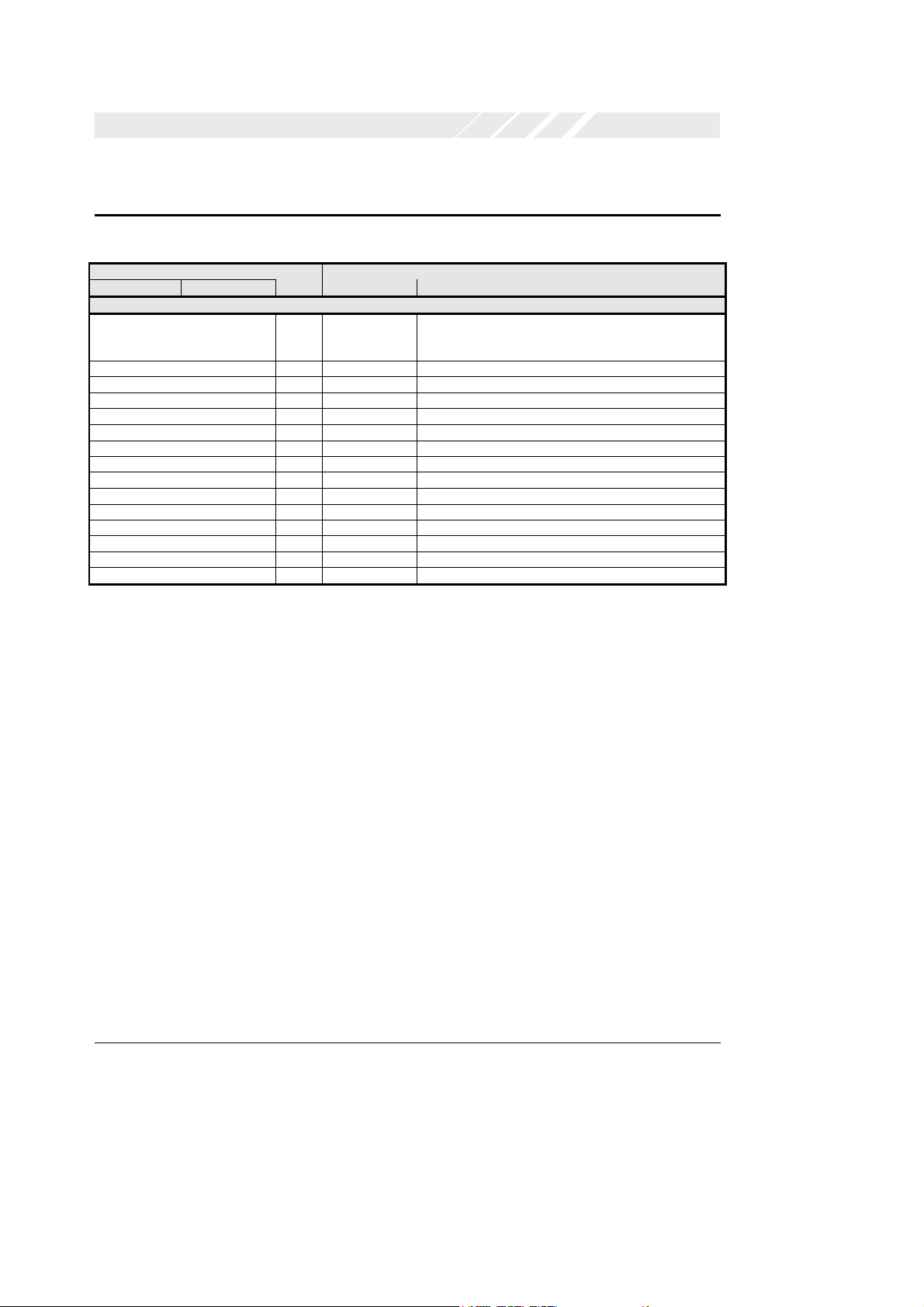

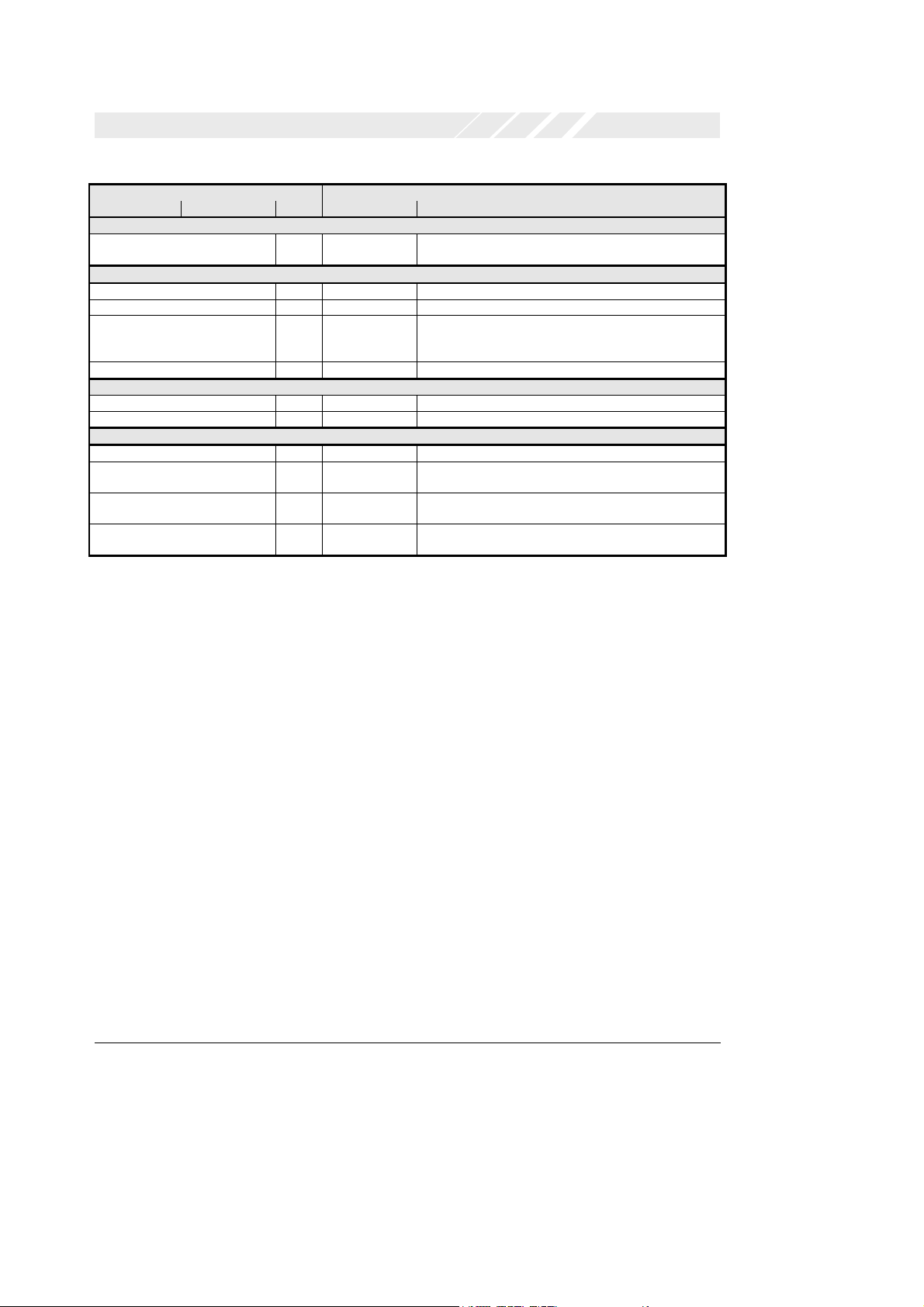

2 PIN DESCRIPTIONS

Mode

Parallel Local Bus

PCI interface

115,117,118,120,121,122,125,126,

3,5,6,7,10,11,12,13,27,28,29,34,35

,38,39,41,45,46,49,50,55,56,58,59

127, 14, 26 ,42 P_I C/BE[3:0]# PCI Command/Byte enable

112 P_I CLK PCI system clock

15 P_I FRAME# Cycle Frame

20 P_O DEVSEL# Device Select

18 P_I IRDY# Initiator ready

19 P_O TRDY# Target ready

22 P_O STOP# Target Stop request

25 P_I/O PAR Parity

24 P_O SERR# System error

23 P_I/O PERR# Parity error

2 P_I IDSEL Initialisation device select

110 P_I RST# PCI system reset

109 P_OD INTA# PCI interrupt

114 P_OD PME# Power management event

Dir1 Name Description

P_I/O AD[31:0] Multiplexed PCI Address/Data bus

Data Sheet Revision 1.1 PRELIMINARY Page 4

OX9162

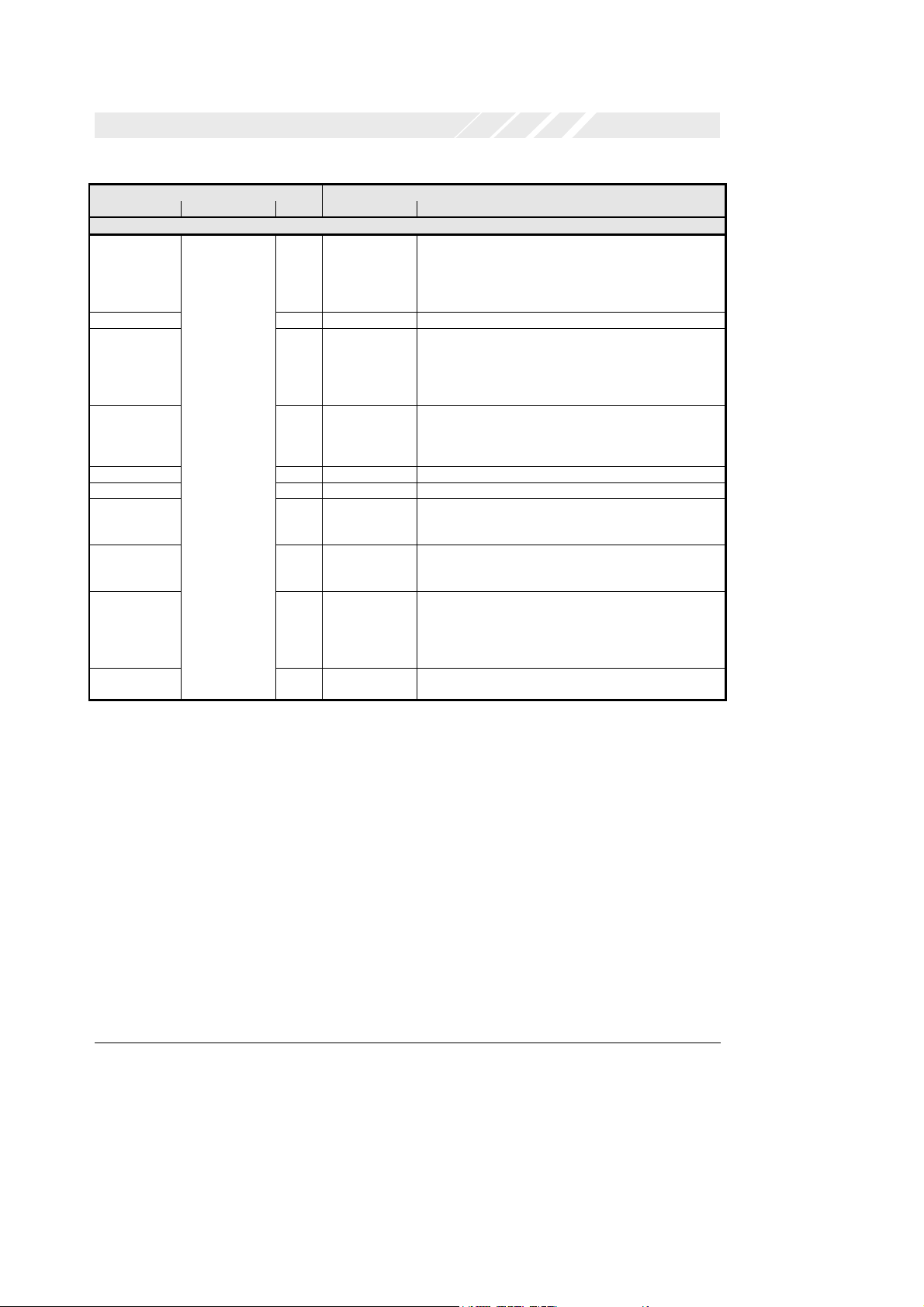

OXFORD SEMICONDUCTOR LTD.

Mode

Parallel Local Bus

Local Bus

N/A

77,78,79,82,

87,88,89,90

66,67,68,71,

72,73,74,76

Dir1 Name Description

62 O LBRST Local bus active-high reset

61 O LBRST# Local bus active-low reset

83 O LBDOUT Local bus data out enable. This pin can be used by external

101 O LBCLK Buffered PCI clock. Can be enabled / disabled by software

99, 91 O

63 O

85 O

LBCS[1:0]#

O

LBDS[1:0]#

LBWR#

O

LBRDWR#

LBRD#

O

Hi

O LBA[7:0] Local bus address signals

I/O LBD[7:0] Local bus data signals

transceivers; it is high when LBD[7:0] are in output mode and

low when they are in input mode.

Local bus active-low Chip-Select (Intel mode)

Local bus active-low Data-Strobe (Motorola mode)

Local Bus active-low write-strobe (Intel mode)

Local Bus Read-not-Write control (Motorola mode)

Local Bus active-low read-strobe (Intel mode)

Permanent high (Motorola mode)

Data Sheet Revision 1.1 PRELIMINARY Page 5

OX9162

OXFORD SEMICONDUCTOR LTD.

Mode

Parallel Local Bus

Parallel port

85 I

77 I PE Paper Empty. Activated by printer when it runs out of paper.

78 I

87 OD

79 I SLCT Peripheral selected. Asserted by peripheral when selected.

82 I ERR# Error. Held low by the peripheral during an error condition.

88 OD

89 OD

90 OD

66,67,68,71,

72,73,74,76

N/A

Dir1 Name Description

ACK#

I

INTR#

BUSY

I

WAIT#

SLIN#

O

ADDRSTB#

INIT#

O

INIT#

AFD#

O

DATASTB#

STB#

O

WRITE#

I/O PD[7:0] Parallel data bus

Acknowledge (SPP mode). ACK# is asserted (low) by the

peripheral to indicate that a successful data transfer has

taken place.

Identical function to ACK# (EPP mode).

Busy (SPP mode). BUSY is asserted (high) by the peripheral

when it is not ready to accept data

Wait (EPP mode). Handshake signal for interlocked IEEE

1284 compliant EPP cycles.

Select (SPP mode). Asserted by host to select the peripheral

Address strobe (EPP mode) provides address read and write

strobe

Initialise (SPP mode). Commands the peripheral to initialise.

Initialise (EPP mode). Identical function to SPP mode.

Auto Feed (SPP mode, open-drain)

Data strobe (EPP mode) provides data read and write strobe

Strobe (SPP mode). Used by peripheral to latch data

currently available on PD[7:0]

Write (EPP mode). Indicates a write cycle when low and a

read cycle when high

Data Sheet Revision 1.1 PRELIMINARY Page 6

OX9162

OXFORD SEMICONDUCTOR LTD.

Mode

Parallel Local Bus

Multi-purpose & External interrupt pins

104, 65 I/O MIO[1:0] Multi-purpose I/O pins. Can drive high or low, or assert a PCI

EEPROM pins

98 O EE_CK EEPROM clock

94 O EE_CS EEPROM active-high Chip Select

96 IU EE_DI EEPROM data in. When the serial EEPROM is connected,

95 O EE_DO EEPROM data out.

Miscellaneous pins

107 ID MODE Mode selection: Parallel Port (0) or Local Bus (1)

93 I TEST Test Pin : should be held low at all times

Power and ground2

9, 31, 47, 70, 124 V AC VDD Supplies power to output buffers in switching (AC) state

17, 54, 81, 113 V DC VDD Power supply. Supplies power to core logic, input buffers

4, 8, 21, 30, 40, 48, 57,

69, 75, 86, 119, 123

16, 53, 80, 111 G DC GND Ground (0 volts). Supplies GND to core logic, input buffers

Note 1: Direction key:

I Input

ID Input with internal pull-down

O Output

I/O Bi-directional

OD Open drain

NC No connect

Z High impedance

Note 2: Power & Ground

There are two GND and two VDD rails internally. One set of rails supply power and ground to output buffers while in switching

state (called AC power) and another rail supply the core logic, input buffers and output buffers in steady-state (called DC rail).

The rails are not connected internally. This precaution reduces the effects of simultaneous switching outputs and undesirable RF

radiation from the chip. Further precaution is taken by segmenting the GND and VDD AC rails to isolate the PCI and Local Bus

pins.

Dir1 Name Description

interrupt

this pin should be pulled up using 1-10k resistor. When the

EEPROM is not used the internal pull-up is sufficient.

and output buffers in steady state

G AC GND Supplies GND to output buffers in switching (AC) state

and output buffers in steady state

Table 1: Pin Descriptions

P_I PCI input

P_O PCI output

P_I/O PCI bi-directional

P_OD PCI open drain

G Ground

V 5.0V power

Data Sheet Revision 1.1 PRELIMINARY Page 7

OX9162

OXFORD SEMICONDUCTOR LTD.

3 CONFIGURATION & OPERATION

The OX9162 is a single function, target-only PCI device,

compliant with the PCI Local Bus Specification, Revision

2.2 and PCI Power Management Specification, Revision

1.0.

The function selected is configured by the Mode pin. It

should be tied low for parallel port operation, or tied high

for local bus operation.

The OX9162 is configured by system start-up software

during the bootstrap process that follows bus reset. The

system scans the bus and reads the vendor and device

identification codes from any devices it finds. It then loads

device-driver software according to this information and

configures the I/O, memory and interrupt resources. Device

drivers can then access the functions at the assigned

addresses in the usual fashion, with the improved data

throughput provided by PCI.

There are a set of Local configuration registers that can be

used to enable signals and interrupts, and configure local

bus timings. These can be set up by drivers or from the

EEPROM.

All registers default after reset to suitable values for typical

applications. However, all identification, control and timing

registers can be redefined using an optional serial

EEPROM. As an additional enhancement, the EEPROM

can be used to program the parallel port or local bus,

allowing pre-configuration, without requiring driver

changes.

Data Sheet Revision 1.1 PRELIMINARY Page 8

OX9162

OXFORD SEMICONDUCTOR LTD.

4 PCI TARGET CONTROLLER

4.1 Operation

The OX9162 responds to the following PCI transactions:-

• Configuration access: The OX9162 responds to type 0

configuration reads and writes if the IDSEL signal is

asserted and the bus address is selecting the

configuration registers for function 0. The device will

respond to the configuration transaction by asserting

DEVSEL#. Data transfer then follows. Any other

configuration transaction will be ignored by the

OX9162.

• IO reads/writes: The address is compared with the

addresses reserved in the I/O Base Address Registers

(BARs). If the address falls within one of the assigned

ranges, the device will respond to the IO transaction

by asserting DEVSEL#. Data transfer follows this

address phase. For all modes, only byte accesses are

possible to the function BARs (excluding the local

configuration registers for which WORD, DWORD

access is supported). For IO accesses to these

regions, the controller compares AD[1:0] with the byteenable signals as defined in the PCI specification. The

access is always completed; however if the correct BE

signal is not present the transaction will have no

effect.

• Memory reads/writes: These are treated in the same

way as I/O transactions, except that the memory

ranges are used. Memory access to single-byte

regions is always expanded to DWORDs in the

OX9162. In other words, OX9162 reserves a DWORD

per byte in single-byte regions. The device allows the

user to define the active byte lane using LCC[4:3] so

that in Big-Endian systems the hardware can swap the

byte lane automatically. For Memory mapped access

in single-byte regions, the OX9162 compares the

asserted byte-enable with the selected byte-lane in

LCC[4:3] and completes the operation if a match

occurs, otherwise the access will complete normally

on the PCI bus, but it will have no effect on either the

parallel port or the local bus controller.

• All other cycles (64-bit, special cycles, reserved

encoding etc.) are ignored.

The OX9162 will complete all transactions as disconnectwith-data, i.e. the device will assert the STOP# signal

alongside TRDY#, to ensure that the Bus Master does not

continue with a burst access. The exception to this is Retry,

which will be signalled in response to any access while the

OX9162 is reading from the serial EEPROM.

The OX9162 performs medium-speed address decoding as

defined by the PCI specification. It asserts the DEVSEL#

bus signal two clocks after FRAME# is first sampled low on

all bus transaction frames which address the chip. Fast

back-to-back transactions are supported by the OX9162 as

a target, so a bus master can perform faster sequences of

write transactions to the parallel port or local bus when an

inter-frame turn-around cycle is not required.

The device supports any combination of byte-enables to

the PCI Configuration Registers and the Local

Configuration registers (see Base Address 2 and 3). If a

byte-enable is not asserted, that byte is unaffected by a

write operation and undefined data is returned upon a read.

The OX9162 performs parity generation and checking on

all PCI bus transactions as defined by the standard. If a

parity error occurs during the PCI bus address phase, the

device will report the error in the standard way by asserting

the SERR# bus signal. However if that address/command

combination is decoded as a valid access, it will still

complete the transaction as though the parity check was

correct.

The OX9162 does not support any kind of caching or data

buffering, other than that in the parallel port. In general,

registers on the local bus can not be pre-fetched because

there may be side-effects on read.

4.2 Configuration space

The OX9162 is a single function device, with one

configuration space. All required fields in the standard

header are implemented, plus the Power Management

Extended Capability register set. The format of the

configuration space is shown in Table 2 overleaf.

In general, writes to any registers that are not implemented

are ignored, and all reads from unimplemented registers

return 0.

Data Sheet Revision 1.1 PRELIMINARY Page 9

OX9162

OXFORD SEMICONDUCTOR LTD.

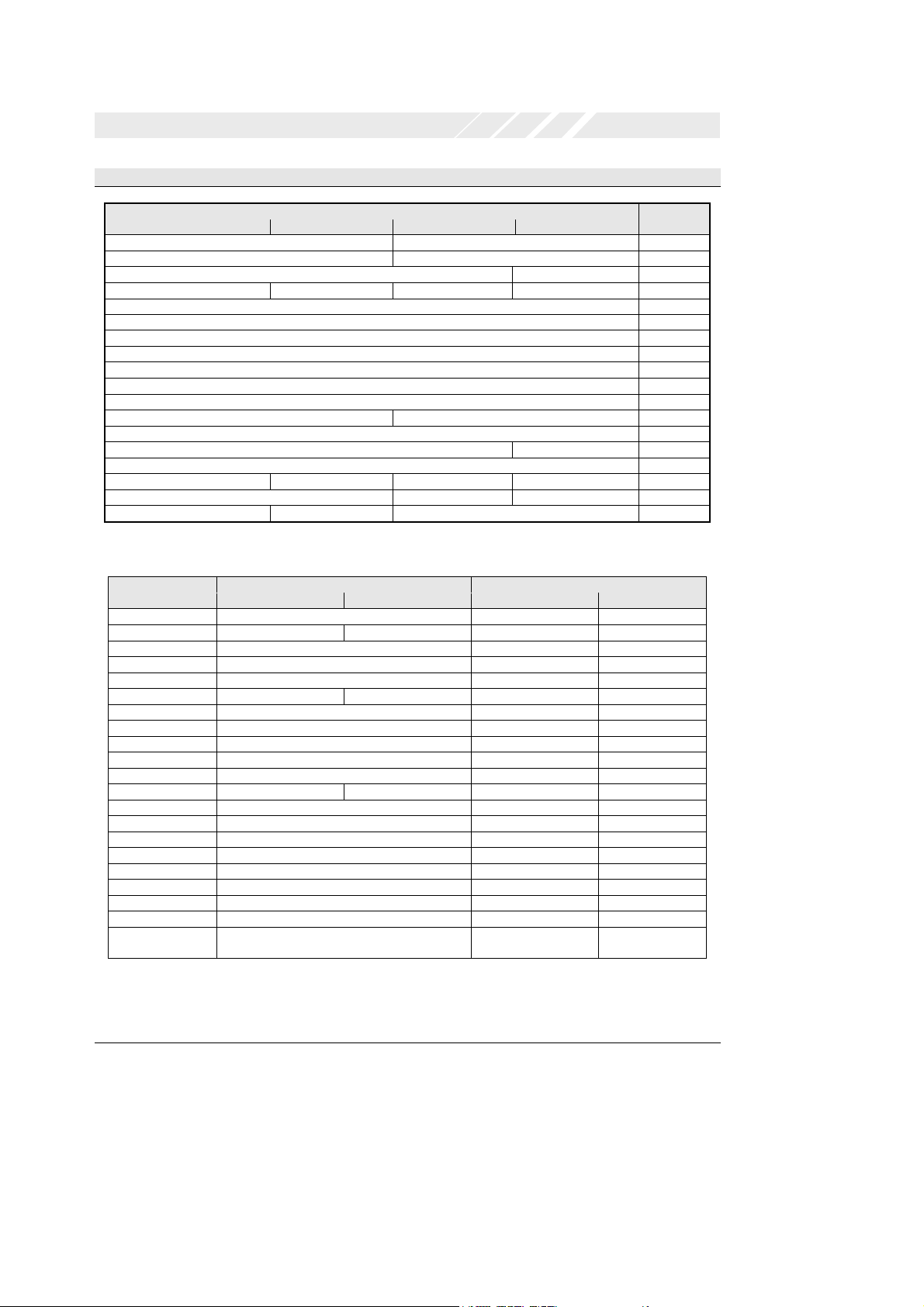

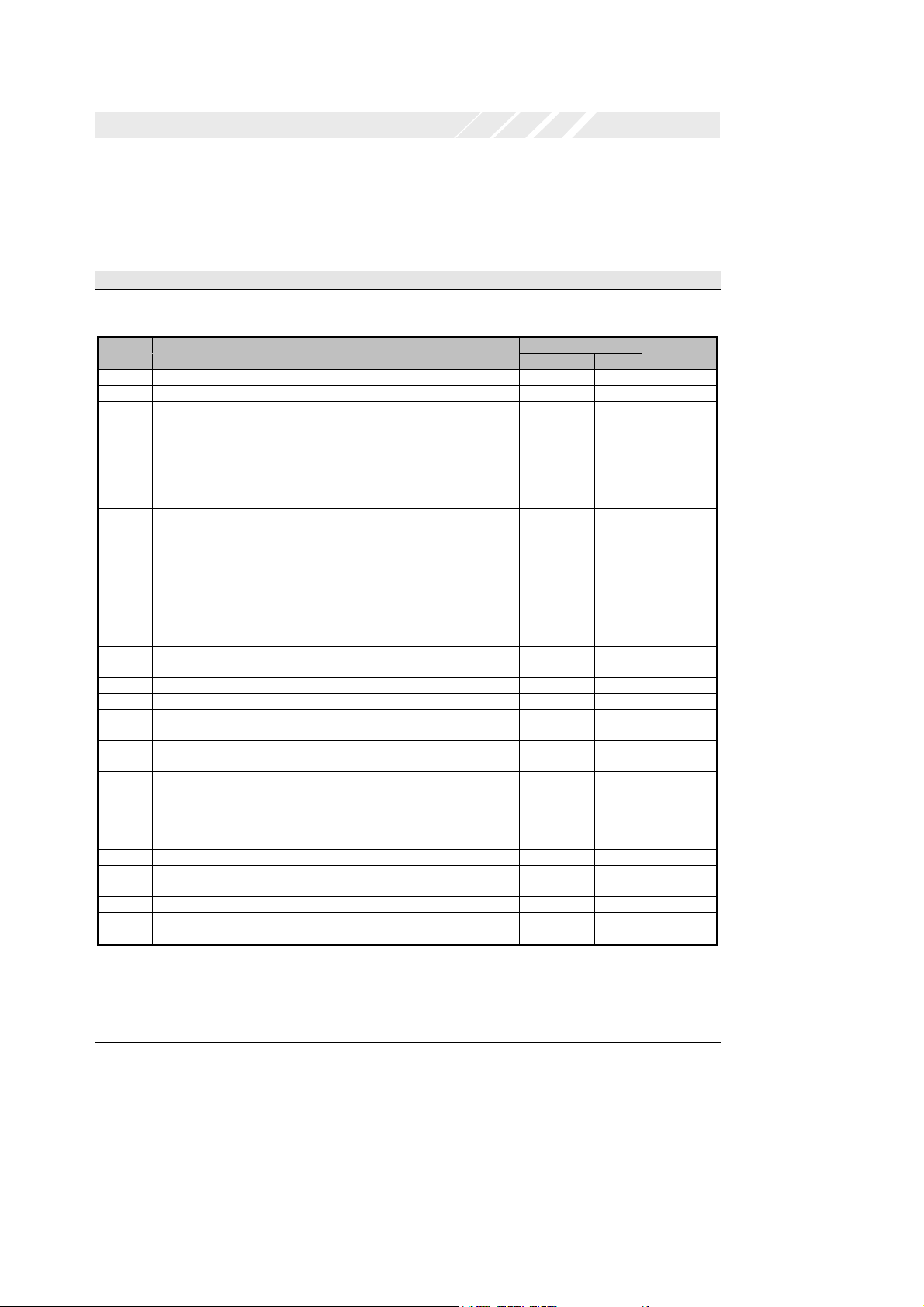

4.2.1 PCI Configuration Space Register map

31 16 15 0

Device ID Vendor ID 00h

Status Command 04h

BIST1 Header Type Reserved Reserved 0Ch

Base Address Register 1 (BAR 1) - Function in I/O space 14h

Base Address Register 2 (BAR 2) – Local Configuration Registers in IO space 18h

Base Address Register 3 (BAR3) – Local Configuration Registers in Memory space 1Ch

Base Address Register 4 (BAR4) – Function in Memory Space 20h

Subsystem ID Subsystem Vendor ID 2Ch

Reserved Reserved Interrupt Pin Interrupt Line 3Ch

Power Management Capabilities (PMC) Next Ptr Cap_ID 40h

Reserved Reserved PMC Control/Status Register (PMCSR) 44h

Vendor ID 0x1415 W R

Device ID 0x8401 0x8403 W R

Command 0x0000 - R/W

Status 0x0290 W(bit 4) R/W

Revision ID 0x00 - R

Class code 0x068000 0x070103 W R

Header type 0x00 - R

BAR 0 0x00000001 - R/W

BAR 1 0x00000001 - R/W

BAR 2 0x00000001 - R/W

BAR 3 0x00000000 - R/W

BAR 4 0x00000000 Reserved - R/W

Subsystem VID 0x1415 W R

Subsystem ID 0x0001 W R

Cap ptr. 0x40 - R

Interrupt line 0x00 - R/W

Interrupt pin 0x01 W R

Cap ID 0x01 - R

Next ptr. 0x00 - R

PM capabilities 0x6C01 W R

PMC control/

status register

Configuration Register Description Offset

Class Code Revision ID 08h

Base Address Register 0 (BAR0) - Function in I/O space 10h

Reserved 24h

Reserved 28h

Reserved 30h

Reserved Cap_Ptr 34h

Reserved 38h

Table 2: PCI Configuration space

Reset value Program read/write Register name

Local Bus Parallel Port

0x0000 - R/W

Table 3: PCI configuration space default values

Address

Data Sheet Revision 1.1 PRELIMINARY Page 10

OX9162

OXFORD SEMICONDUCTOR LTD.

Chip-Select

4.3 Accessing logical functions

Access to the local bus and parallel port is achieved via standard I/O and memory mapping, at addresses defined by the Base

Address Registers (BARs) in configuration space. The BARs are configured by the system to allocate blocks of I/O and memory

space to the logical function, according to the size required by the function. The addresses allocated can then be used to access

the function. The mapping of these BARs is shown in Table 4.

Function 0 BAR

Local Bus Parallel Port

0 CS0 (I/O mapped) Parallel port base registers (I/O mapped)

1 CS1 (I/O mapped) Parallel port extended registers (I/O mapped)

2 Local configuration registers (I/O mapped

3 Local configuration registers (memory mapped)

4 All CS (memory mapped Unused

5 Unused

4.3.1 PCI access to 8-bit local bus

When the local bus is enabled (Mode 1), the function

reserves two blocks of I/O space (BAR0 for chip select 0,

BAR1 for chip select 1) and a block of memory space

(BAR4 for chip selects 0 and 1). Each I/O block size is user

definable in the range of 4 to 256 bytes; the memory range

is fixed at 4K bytes.

I/O space

In order to minimise the usage of IO space, the block sizes

for BAR0 and BAR1 are user definable in the range of 4 to

256 bytes.

The 8-bit Local Bus has eight address lines (LBA[7:0])

which correspond to the maximum IO address space. If the

maximum allowable block size is allocated to the IO space

(i.e. 256 bytes), then as access in IO space is byte aligned,

LBA[7:0] equal PCI AD[7:0] respectively. When the user

selects an address range which is less than 256 bytes, the

corresponding upper address lines will be set to logic zero.

Memory Space:

The memory base address registers have an allocated

fixed size of 4K bytes in the address space. Since the

Local Bus has 8 address lines and the OX9162 only

implements DWORD aligned accesses in memory space,

the 256 bytes of addressable space per chip select is

expanded to 1K. Unlike an I/O access (where access to

BAR0, BAR1 determines chip-select decoding) for a

memory access the internal chip-select decoding logic

uses the field PCI AD[10] to decode into 2 chip-select

regions. When the Local Bus is accessed in memory

space, A[9:2] are asserted on LBA[7:0]. The chip-select

regions are defined below.

Table 4: Base Address Register definition

Local Bus

LBCS0# (LBDS0#) 000h 3FCh

LBCS1# (LBDS1#) 400h 7FCh

Table 5: PCI address map for local bus (memory)

Note: The description given for I/O and memory accesses

is for an Intel-type configuration for the Local Bus. For

Motorola-type configuration, the chip select pins are

redefined to data strobe pins. In this mode the Local Bus

offers up to 8 address lines and two data-strobe pins.

4.3.2 PCI access to parallel port

When the parallel port is enabled (Mode 0), access to the

port works via BAR definitions as usual with two I/O BARs

corresponding to the two sets of registers defined to

operate an IEEE1284 ECP/EPP and bi-directional Parallel

Port.

The user can change the I/O space block size of BAR0 or

BAR1 as for the local bus mode by over-writing the default

values using the serial EEPROM (see section 4.4).

Legacy parallel ports expect the upper register set to be

mapped 0x400 above the base block, therefore if the BARs

are fixed with this relationship, generic parallel port drivers

can be used to operate the device in all modes.

Example: BAR0 = 0x00000379 (8 bytes at address 0x378)

BAR1 = 0x00000779 (8 bytes at address 0x778)

If this relationship is not used, custom drivers will be

needed.

PCI Offset from BAR 1 in

Function1 (Memory space)

Lower Address Upper Limit

Data Sheet Revision 1.1 PRELIMINARY Page 11

OX9162

OXFORD SEMICONDUCTOR LTD.

4.4 Accessing Local configuration registers

The local configuration registers are a set of device specific registers which can always be accessed. They are mapped to the

I/O and memory addresses set up in BAR2 and BAR3, with the offsets defined for each register. I/O or memory accesses can be

byte, word or dword accessed, however on little-endian systems such as Intel 80x86 the byte order will be reversed.

4.4.1 Local Configuration and Control register ‘LCC’ (Offset 0x00)

This register defines control of ancillary functions such as Power Management, endian selection and the serial EEPROM. The

individual bits are described below.

Bits Description Read/Write Reset

0 Mode. This bit returns the state of the Mode pin. - R X

2:1 Reserved 00

4:3 Endian Byte-Lane Select for memory access to 8-bit peripherals.

7:5 Power-down filter time. These bits define a value of an internal filter time

000 = power-down request disabled

10:8 Reserved: Power management test bits. The device driver must write

22:11 Reserved. - R 0000h

23 Parallel port Input (glitch) filters. Enabled when ‘1’ W RW 0

24 EEPROM Clock. For PCI read or write to the EEPROM , toggle this bit to

25 EEPROM Chip Select. When 1 the EEPROM chip-select pin EE_CS is

26 EEPROM Data Out. For writes to the EEPROM, this output bit is the

27 EEPROM Data In. For reads from the EEPROM, this input bit is the

28 EEPROM Valid. A 1 indicates that a valid EEPROM program is present - R X

29 Reload configuration from EEPROM. Writing a 1 to this bit re-loads the

30 Reserved - R 0

31 Reserved - R 0

00 = Select Data[7:0] 10 = Select Data[23:16]

01 = Select Data[15:8] 11 = Select Data[31:24]

Memory access to OX9162 is always DWORD aligned. When accessing

8-bit regions this option selects the active byte lane. As both PCI and PC

architectures are little endian, the default value will be used by systems,

however, some non-PC architectures may need to select the byte lane.

for power-down interrupt request in power management circuitry in

Function0. Once Function0 is ready to go into power down mode,

OX9162 will wait for the specified filter time and if Function0 is still in

power-down request mode, it can assert a PCI interrupt (see section

4.6).

001 = 4 seconds

zero to these bits

generate an EEPROM clock (EE_CK pin).

activated (high). When 0 EE_CS is de-active (low).

input-data of the EEPROM. This bit is output on EE_DO and clocked into

the EEPROM by EE_CK.

output-data of the EEPROM connected to EE_DI pin.

configuration from EEPROM. This bit is self-clearing after EEPROM read

010 = 129 seconds

011 = 518 seconds

1XX = Immediate

EEPROM

W RW 00

W RW 000

- R 000

- RW 0

- RW 0

- RW 0

- R X

- RW 0

PCI

Data Sheet Revision 1.1 PRELIMINARY Page 12

OX9162

OXFORD SEMICONDUCTOR LTD.

4.4.2 Multi-purpose I/O Configuration register ‘MIC’ (Offset 0x04)

This register configures the operation of the multi-purpose I/O pins ‘MIO[1:0] as follows.

Bits Description Read/Write Reset

1:0 MIO0 Configuration Register

EEPROM

PCI

W RW 00

00 -> MIO0 is a non-inverting input pin

01 -> MIO0 is an inverting input pin

10 -> MIO0 is an output pin driving ‘0’

11 -> MIO0 is an output pin driving ‘1’

3:2 MIO1 Configuration Register

W RW 00

00 -> MIO1 is a non-inverting input pin

01 -> MIO1 is an inverting input pin

10 -> MIO1 is an output pin driving ‘0’

11 -> MIO1 is an output pin driving ‘1’

4 MIO0_PME Enable. A value of ‘1’ enables MIO0 pin to set the

W RW 0

PME_Status in PMCSR register, and hence assert the PME# pin if

enabled. A value of ‘0’ disables MIO0 from setting the PME_Status bit.

5 MIO1_PME Enable. A value of ‘1’ enables MIO1 pin to set the

W RW 0

PME_Status in PMCSR register, and hence assert the PME# pin if

enabled. A value of ‘0’ disables MIO1 from setting the PME_Status bit.

6 MIO0 Power Down Request: A ‘1’ enables MIO0 to control the power

W RW 0

down request filter.

7 MIO1 Power Down Request: A ‘1’ enables MIO1 to control the power

W RW 0

down request filter.

31:8 Reserved - R 00

4.4.3 Local Bus Timing Parameter register 1 ‘LT1’ (Offset 0x08):

The Local Bus Timing Parameter registers (LT1 and LT2) define the operation and timing parameters used by the Local Bus.

The timing parameters are programmed in 4-bit registers to define the assertion/de-assertion of the Local Bus control signals.

The value programmed in these registers defines the number of PCI clock cycles after a Reference Cycle when the events

occur, where the reference Cycle is defined as two clock cycles after the master asserts the IRDY# signal. The following

arrangement provides a flexible approach for users to define the desired bus timing of their peripheral devices. The timings refer

to I/O or Memory mapped accesses.

Bits Description Read/Write Reset

3:0 Read Chip-select Assertion (Intel-type interface). Defines the number of

clock cycles after the Reference Cycle when the LBCS[1:0]# pins are

asserted (low) during a read operation from the Local Bus.

1

These bits are unused in Motorola-type interface.

7:4 Read Chip-select De-assertion (Intel-type interface). Defines the number

of clock cycles after the Reference Cycle when the LBCS[1:0]# pins are

de-asserted (high) during a read from the Local Bus.

1

These bits are unused in Motorola-type interface.

11:8 Write Chip-select Assertion (Intel-type interface). Defines the number of

clock cycles after the Reference Cycle when the LBCS[1:0]# pins are

asserted (low) during a write operation to the Local Bus. 1

EEPROM

PCI

W RW 0h

W RW 3h

W RW 0h

(2h for

parallel port)

Data Sheet Revision 1.1 PRELIMINARY Page 13

Loading...

Loading...