OXFORD OX16C954-PCC60-B, OX16C954-TQC60-B Datasheet

OX16C954 rev B

FEATURES

High Performance Quad UART with 128-byte FIFOs

Intel / Motorola Bus Interface

• Four independent full-duplex asynchronous 16C950

high performance UART channels

• 128-byte deep FIFO per transmitter and receiver

• UARTs fully software compatible with industry

standard 16C55x type UARTs

• Pin compatible with TL16C554 and ST16C654

• Baud rates up to 15 Mbps in normal mode and

60Mbps in external 1x clock (isochronous) mode

• Readable FIFO levels

• Flexible clock prescaler from 1 to 31.875

• Automated in-band flow control using programmable

Xon/Xoff characters, in both directions

• Automated out-of-band flow control using CTS#/RTS#

and/or DSR#/DTR#

• Arbitrary trigger levels for receiver and transmitter

FIFO interrupts and automatic in-band and out-ofband flow control

• Readable in-band and out-of-band flow control status

• Programmable special character detection

• Infra-red (IrDA) receiver and transmitter option

• 5, 6, 7, 8 and 9-bits data framing

• Detection of bad data in the receiver FIFO

• Independent channel reset by software

• Transmitter and receiver can be disabled

• Transmitter idle interrupt

• RS-485 buffer enable signals

• Four byte device ID

• Sleep mode (low operating current)

• System clock up to 60 MHz at 5V, 50 MHz at 3.3V

• 5.0 volt or 3.3v operation*

• 68pin PLCC and 80pin TQFP package options.

*Only the 80pin TQFP package supports operation at 5v or 3.3v.

REV B ENHANCEMENTS

The OX16C954B is an enhanced, backward-compatible revision of the OX16C954 rev A. It uses the newer core as in the

OX16C950 rev B. The chief enhancements are as follows –

• All known errata fixed

• Full TCR range from 4-16

• Enhanced controls for sleep-mode sensitivity, ability to read FCR and Good Data Status

• 3.3V operation with 80 pin TQFP

• Enhanced isochronous clocking options (optional inversions, DTR/DSR)

Hereafter OX16C954 rev B is simply referred to as OX16C954.

Oxford Semiconductor Ltd. Oxford Semiconductor 2001

25 Milton Park, Abingdon, Oxon, OX14 4SH, UK OX16C954 rev B Data Sheet R1.0 – November 2001

Tel: +44 (0)1235 824900 Fax: +44 (0)1235 821141 Part Nos. OX16C954-PCC60-B / OX16C954_TQC60_B

ESCRIPTION

D

The OX16C954 is a single chip solution for 4 channel serial

add-in cards.

Each UART channel in the OX16C954 offers data rates up

to 15Mbps and 128-byte deep transmitter and receiver

FIFOs. Deep FIFOs reduce CPU overhead and allow

utilisation of higher data rates.

Each UART channel is software compatible with the widely

used industry-standard 16C550 devices and compatibles,

as well as the OX16C95x family of high performance

UARTs. It is pin-compatible with the TL16C554, ST16C654

devices.

In addition to increased performance and FIFO size, the

UARTs also provide the full set of OX16C95x enhanced

features. These include improved flow controls such as

automated software flow control using Xon/Xoff and

automated hardware flow control using CTS#/RTS# and

DSR#/DTR# to prevent FIFO over-run.

Flow control and interrupt thresholds are fully

programmable and readable, enabling programmers to

fine-tune the performance of their system. FIFO levels are

readable to facilitate fast driver applications.

The addition of software reset enables recovery from

unforeseen error conditions allowing drivers to restart

gracefully. The OX16C954 supports 9-bit data frames used

in multi-drop industrial protocols. It also offers multiple

external clock options for isochronous applications, e.g.

ISDN, xDSL.

The OX16C954 is ideally suited to PC applications, such

as high-speed multi-port add-in cards that enable PC users

to take advantage of the maximum performance of

analogue modems or ISDN terminal adapters. It is also

suitable for any equipment requiring high speed

RS232/RS422/RS485 interfaces.

Fabricated in 0.6µm process, OX16C954 also has a low

operating current and sleep mode for battery powered

applications.

Oxford Semiconductor Ltd. Oxford Semiconductor 2001

25 Milton Park, Abingdon, Oxon, OX14 4SH, UK OX16C954 rev B Data Sheet R1.0 – November 2001

Tel: +44 (0)1235 824900 Fax: +44 (0)1235 821141 Part Nos. OX16C954-PCC60-B / OX16C954_TQC60_B

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

ONTENTS

C

FEATURES.................................................................................................................................................................................................1

REV B ENHANCEMENTS.........................................................................................................................................................................1

DESCRIPTION............................................................................................................................................................................................2

CONTENTS.................................................................................................................................................................................................3

1 PERFORMANCE COMPARISON......................................................................................................................................................5

2 BLOCK DIAGRAM...............................................................................................................................................................................7

3 PIN INFORMATION.............................................................................................................................................................................8

4 PIN DESCRIPTIONS .........................................................................................................................................................................10

4.1 Further Pin Information...........................................................................................................................................................15

5 MODE SELECTION...........................................................................................................................................................................16

5.1 450 Mode....................................................................................................................................................................................16

5.2 550 Mode....................................................................................................................................................................................16

5.3 Extended 550 Mode..................................................................................................................................................................16

5.4 750 Mode....................................................................................................................................................................................16

5.5 650 Mode....................................................................................................................................................................................16

5.6 950 Mode....................................................................................................................................................................................17

6 REGISTER DESCRIPTION TABLES...............................................................................................................................................18

7 RESET CONFIGURATION................................................................................................................................................................22

7.1 Hardware Reset.........................................................................................................................................................................22

7.2 Software Reset..........................................................................................................................................................................22

8 TRANSMITTER AND RECEIVER FIFOS........................................................................................................................................23

8.1 FIFO Control Register ‘FCR’...................................................................................................................................................23

9 LINE CONTROL & STATUS.............................................................................................................................................................24

9.1 False Start Bit Detection..........................................................................................................................................................24

9.2 Line Control Register ‘LCR’....................................................................................................................................................24

9.3 Line Status Register ‘LSR’......................................................................................................................................................25

10 INTERRUPTS & SLEEP MODE.......................................................................................................................................................26

10.1 Interrupt Enable Register ‘IER’...............................................................................................................................................26

10.2 Interrupt Status Register ‘ISR’................................................................................................................................................27

10.3 Interrupt Description................................................................................................................................................................27

10.4 Sleep Mode.................................................................................................................................................................................28

11 MODEM INTERFACE........................................................................................................................................................................28

11.1 Modem Control Register ‘MCR’..............................................................................................................................................28

11.2 Modem Status Register ‘MSR’................................................................................................................................................29

12 OTHER STANDARD REGISTERS...................................................................................................................................................30

12.1 Divisor Latch Registers ‘DLL & DLM’....................................................................................................................................30

12.2 Scratch Pad Register ‘SPR’.....................................................................................................................................................30

13 AUTOMATIC FLOW CONTROL.......................................................................................................................................................31

13.1 Enhanced Features Register ‘EFR’........................................................................................................................................31

13.2 Special Character Detection...................................................................................................................................................32

13.3 Automatic In-band Flow Control............................................................................................................................................32

13.4 Automatic Out-of-band Flow Control....................................................................................................................................32

14 BAUD RATE GENERATION.............................................................................................................................................................33

14.1 General Operation.....................................................................................................................................................................33

14.2 Clock Prescaler Register ‘CPR’..............................................................................................................................................34

14.3 Times Clock Register ‘TCR’....................................................................................................................................................34

14.4 Input Clock Options..................................................................................................................................................................36

Data Sheet Revision 1.0 Page 3

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

14.5 TTL Clock Mode........................................................................................................................................................................36

14.6 External 1x Clock Mode...........................................................................................................................................................36

14.7 Crystal Oscillator Circuit.........................................................................................................................................................36

15 ADDITIONAL FEATURES................................................................................................................................................................37

15.1 Additional Status Register ‘ASR’...........................................................................................................................................37

15.2 FIFO Fill levels ‘TFL & RFL’.....................................................................................................................................................37

15.3 Additional Control Register ‘ACR’.........................................................................................................................................37

15.4 Transmitter Trigger Level ‘TTL’..............................................................................................................................................39

15.5 Receiver Interrupt. Trigger Level ‘RTL’.................................................................................................................................39

15.6 Flow Control Levels ‘FCL’ & ‘FCH’........................................................................................................................................39

15.7 Device Identification Registers..............................................................................................................................................39

15.8 Clock Select Register ‘CKS’....................................................................................................................................................40

15.9 Nine-bit Mode Register ‘NMR’.................................................................................................................................................40

15.10 Modem Disable Mask ‘MDM’..............................................................................................................................................41

15.11 Readable FCR ‘RFC’............................................................................................................................................................41

15.12 Good-data status register ‘GDS’.......................................................................................................................................41

15.13 DMA Status Register ‘DMS’................................................................................................................................................42

15.14 Port Index Register ‘PIX’.....................................................................................................................................................42

15.15 Clock Alteration Register ‘CKA’........................................................................................................................................42

16 OPERATING CONDITIONS..............................................................................................................................................................43

17 DC ELECTRICAL CHARACTERISTICS.........................................................................................................................................44

17.1 5V Operation..............................................................................................................................................................................44

17.2 3.3V Operation...........................................................................................................................................................................45

18 AC ELECTRICAL CHARACTERISTICS.........................................................................................................................................46

18.1 5V Operation..............................................................................................................................................................................46

18.2 3.3V Operation...........................................................................................................................................................................47

19 TIMING WAVEFORMS......................................................................................................................................................................48

20 PACKAGE INFORMATION...............................................................................................................................................................50

21 ORDERING INFORMATION.............................................................................................................................................................52

NOTES......................................................................................................................................................................................................53

CONTACT DETAILS................................................................................................................................................................................54

Data Sheet Revision 1.0 Page 4

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

1 P

ERFORMANCE COMPARISON

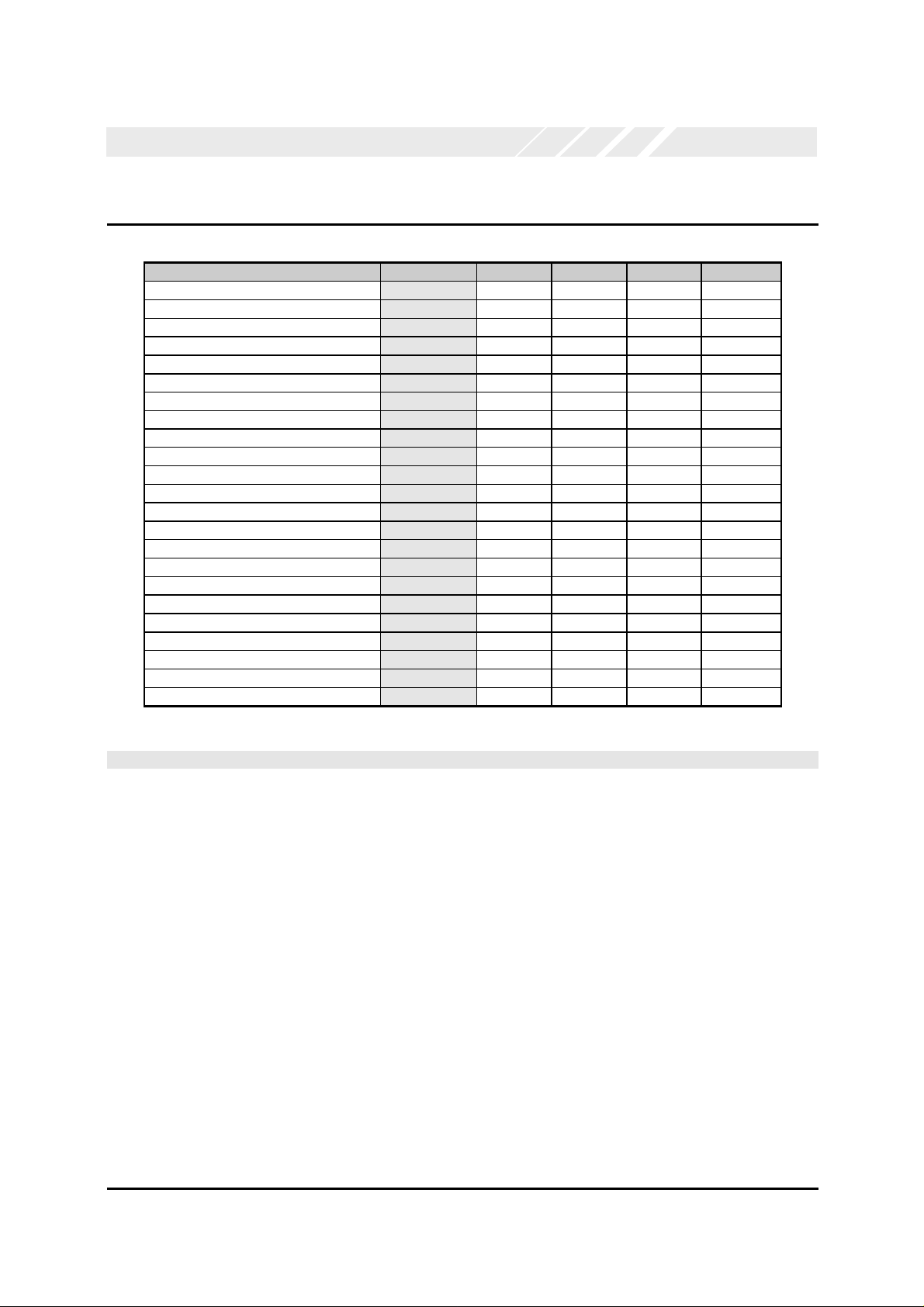

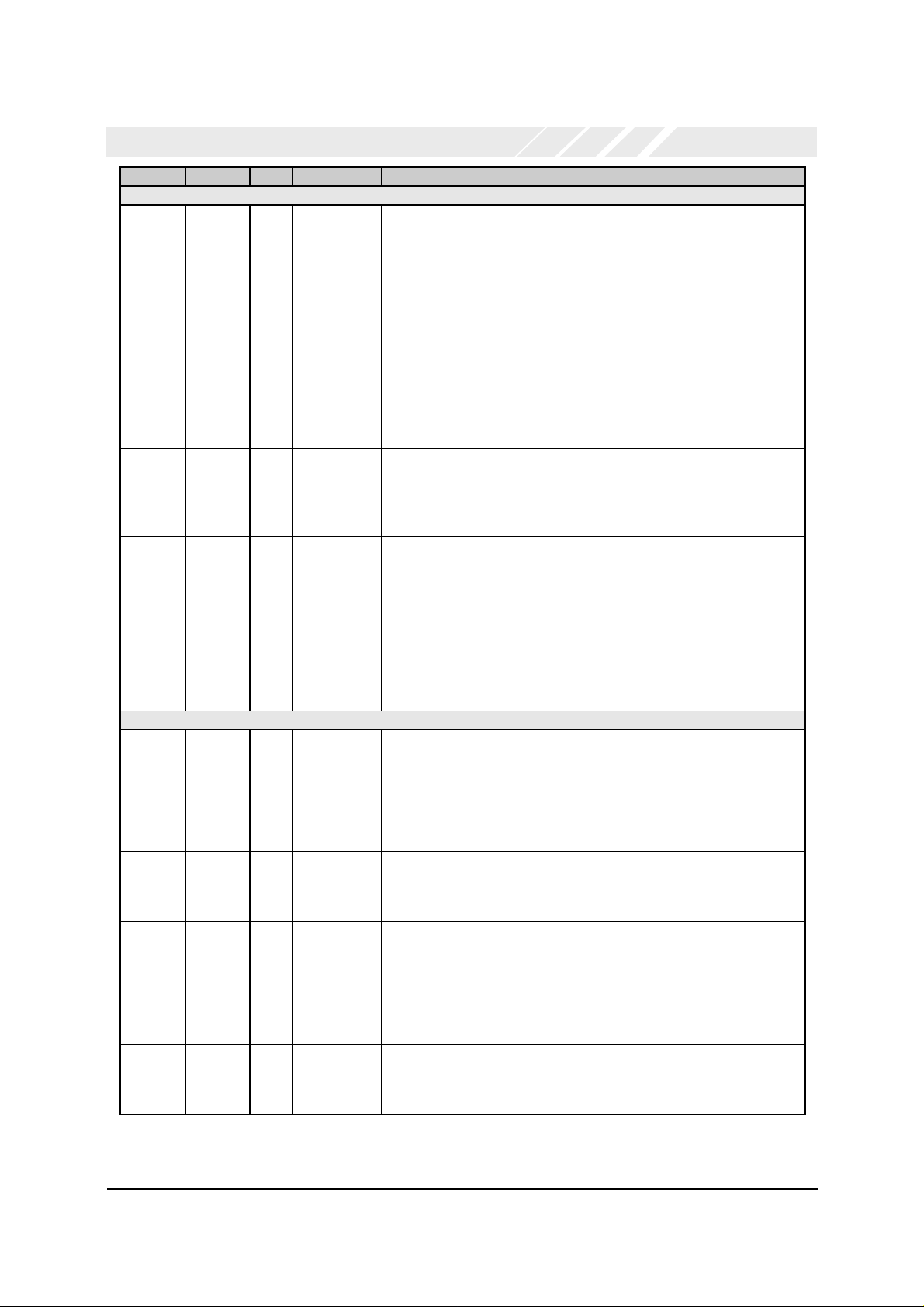

Feature OX16C954 16C454 16C554 16C654 16C750

Integrated Serial channels 4 4 4 4 1

Good-Data status Yes No No No No

External 1x baud rate clock Yes No No No No

Max baud rate in normal mode 15 Mbps 115 kbps 115 kbps 1.5 Mbps 1 Mbps

Max baud rate in 1x clock mode 60 Mbps n/a n/a n/a n/a

FIFO depth 128 1 16 64 64

Sleep mode Yes No No Yes Yes

Auto Xon/Xoff flow Yes No No Yes No

Auto CTS#/RTS# flow Yes No No Yes Yes

Auto DSR#/DTR# flow Yes No No No No

No. of Rx interrupt thresholds 128 1 4 4 4

No. of Tx interrupt thresholds 128 1 1 4 1

No. of flow control thresholds 128 n/a n/a 4 n/a

Transmitter empty interrupt Yes No No No No

Readable status of flow control Yes n/a No No No

Readable FIFO levels Yes n/a No No No

Clock prescaler options 248 n/a n/a 2 n/a

Rx/Tx disable Yes No No No No

Software reset Yes No No No No

Device ID Yes No No No No

9-bit data frames Yes No No No No

RS485 buffer enable Yes No No No No

Infra-red (IrDA) Yes No No Yes No

Table 1 OX16C954 performance compared with 16C454, 16C554, 16C654 and 16C750 devices

Improvements of the OX16C954 over previous generations of PC UARTs:

Deeper FIFOs:

The OX16C954 offers 128-byte deep FIFOs for the

transmitter and receiver.

Higher data rates:

Transmission and reception baud rates up to 15Mbps. A

flexible clock prescaler offers division ratios of 1 to 31 7/8

in steps of 1/8 using a divide-by-“M N/8” circuitry. The

flexible prescaler allows users to select from a wide variety

of input clock frequencies as well as access to higher baud

rates whilst maintaining compatibility with existing software

drivers (see section 14.2).

External clock option:

The receiver can accept an external clock on the DSR#

input. The transmitter can accept a 1x clock on the RI#

input and/or assert its own (Nx) clock on the DTR# output.

In 1x mode, asynchronous data may be transmitted and

received at speeds up to 60 Mbps (see section 14.6).

Automatic flow control:

The UART automatically handles either or both in-band

(software) flow control (transmitting and receiving Xon/Xoff

characters) and out-of-band (hardware) flow control using

the RTS#/CTS# or DSR#/DTR# modem control lines.

Special character detection:

The receiver can be programmed to generate an interrupt

upon reception of a particular character value.

Power-down:

The device can be placed in ‘sleep mode’ to conserve

power

Readable FIFO levels:

Driver efficiency can be improved by using readable FIFO

levels.

Selectable trigger levels:

The receiver FIFO threshold can be arbitrarily

programmed. The transmitter FIFO threshold and

Data Sheet Revision 1.0 Page 5

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

thresholds for automatic flow control can be programmed

to operate at a variety of trigger levels.

TX/RX Disable:

The transmitter and receiver can be independently

disabled.

Additional status:

Software drivers are able to read the status of in-band and

out-of-band automatic flow control, and distinguish

between XOFF and special character received interrupts.

Software reset:

The software driver may reset the device to recover from

unforeseen or unusual error conditions.

Transmitter empty interrupt:

The transmitter can generate an interrupt when the FIFO

and shift register are both empty.

RS485 buffer enable:

The function of the DTR# pin may be re-assigned to bufferenable signal for RS485 line driver in half-duplex mode

(see ACR[4:3] in section 15.3).

Device ID:

Four bytes of device ID are available to identify the

OX16C954 device to software drivers.

Infrared ‘IrDA’ interface:

The UART contains an IrDA compliant modulator and

demodulator.

9-bit data framing

The UART may be configured for use in 9-bit character

framing for multi-drop protocols, where a tag ID (9th bit)

differentiates address and data characters.

Dual Voltage Operation(TQFP)

The 80pin TQFP package option can operate with supply

voltages of either 5.0v or 3.3v, thereby reducing inventory

controls. The VDETECT pin will need to be set according

to the voltage environment.

Data Sheet Revision 1.0 Page 6

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

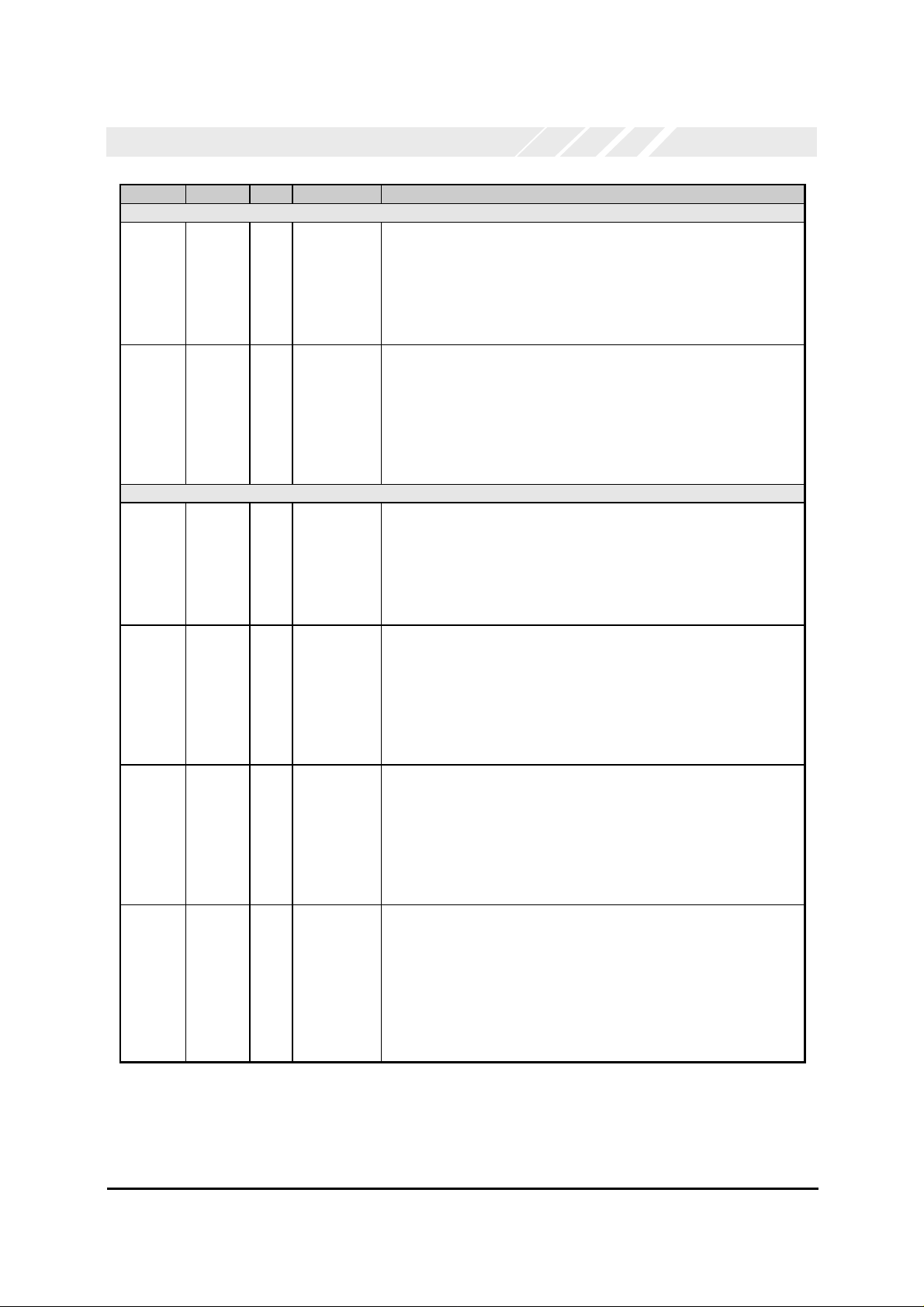

2 B

LOCK DIAGRAM

CS0# / CS#

CS1# / A[3]

CS2# / A[4]

IOW# / R/W#

FIFOSEL

RESET / RESET#

RXRDY#

TXRDY#

CLKSEL

A[2:0]

D[7:0]

CS3#

I/M#

IOR#

VDD

GND

XTLI

XTLO

2

4

Intel &

Motorola

Bus

Interface

Power

supply

Control

and DMA

Interface

Clock &

Baud Rate

Generator

Internal Data Bus

Internal Control Bus

SERIAL CHANNEL n ( 1 of 4 shown )

Transmitter

128 Byte

FIFO

Receiver

128 Byte

FIFO

Control

and

Status

Registers

Modem

Control

Interface

Interrupt

Control

Logic

SOUTn

SINn

RTSn#

DTRn#

OUT1n

OUT2n

CTSn#

DSRn#

DCDn#

RIn#

INTn

INTEN#

VDETECT*

Data Sheet Revision 1.0 Page 7

5v / 3.3v

IO Buffer Control

Figure 1: OX16C954 Block Diagram

NOTE : VDETECT pin is only available on the 80pin TQFP package option

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

IN

FIF

60

59

58

57

56

55

54

53

52

51

50

CS2# / A4

49

48

47

46

45

44

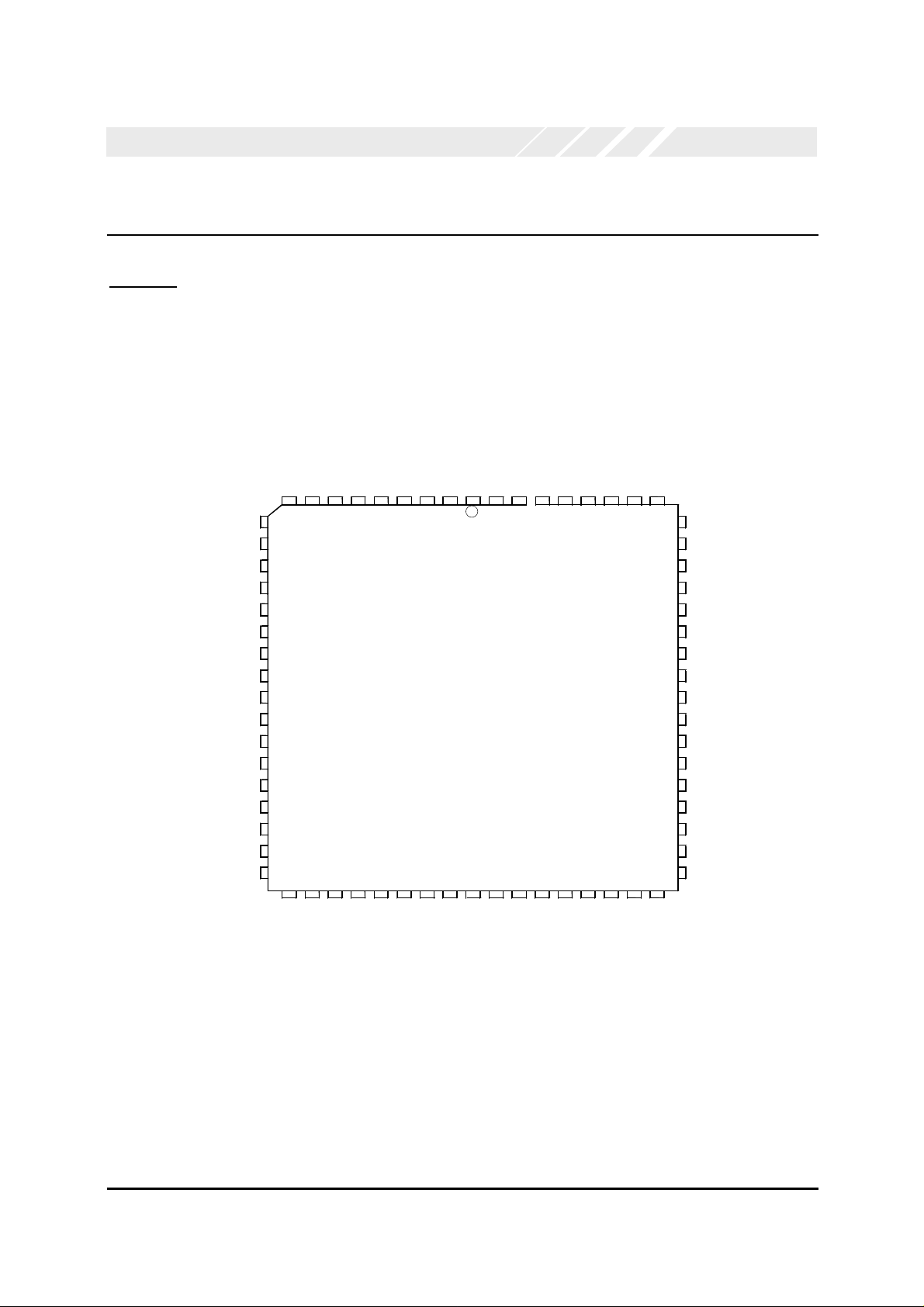

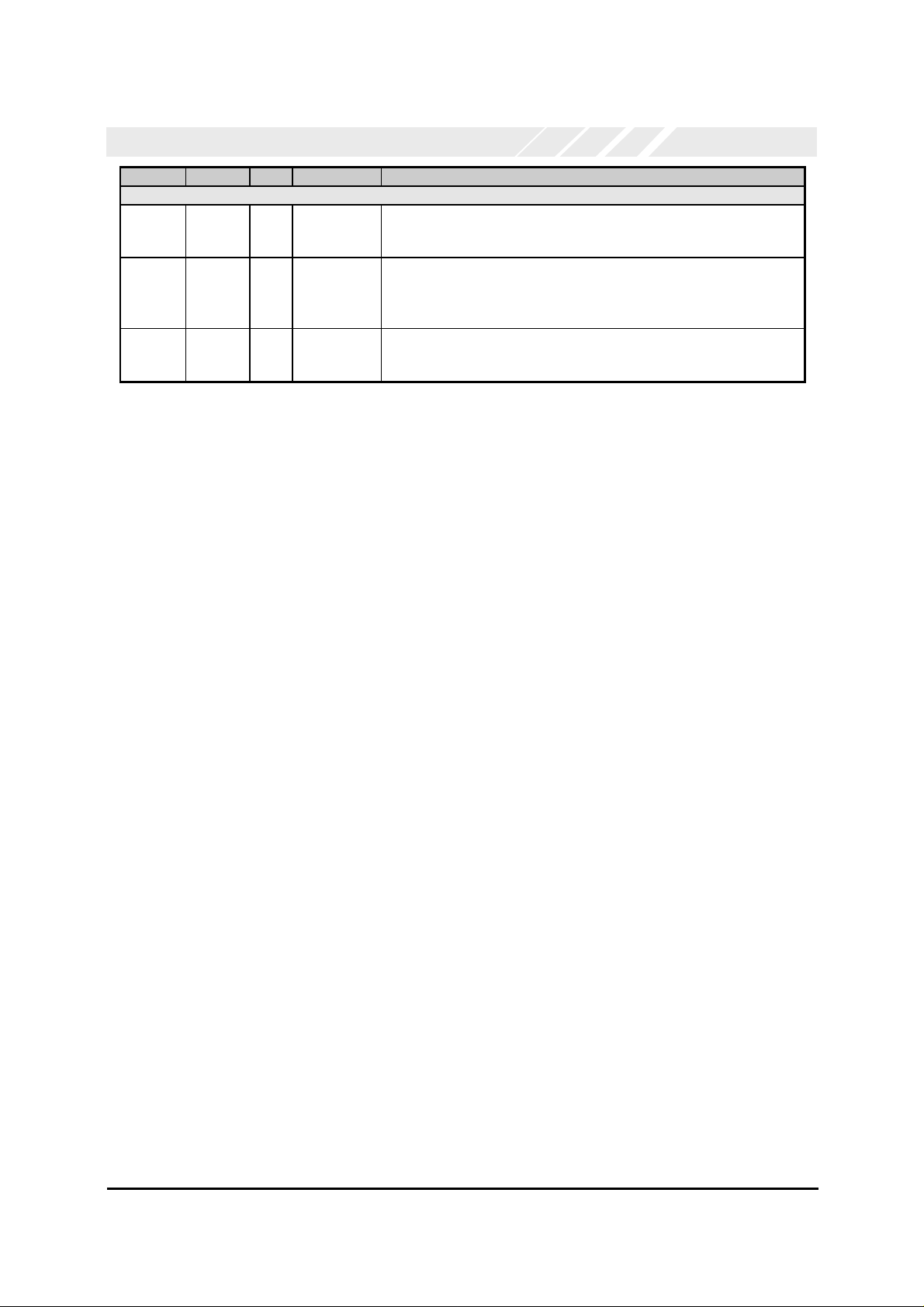

3 PIN INFORMATION

68pin PLCC

DC

D0

#

OS

TS

SI

GN

RI

0#

DB

DB

DB

DB

DB

DB

N0

D

7

6

5

4

DB

3

2

1

DB

0

EL

EL

#

#

DC

D3

SI

RI

#

N3

3#

DSR0#

CTS0#

DTR0#

VDD

RTS0#

INT0 / IRQ#

CS0# / DS#

SOUT0

IOW# / R/W#

SOUT1

CS1# / A3

INT1

RTS1#

GND

DTR1#

CTS1#

DSR1#

9 8 7 6 5 4 3 2 1 68 67 66 65 64 63 62 61

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43

DC

D1

#

CL

SI

RI

KS

1#

N1

EL

OX16C954-PCC60-B

I/M

A2 A1 A0

#

RE

RX

TX

SE

XT

XT

LI

RD

T /

LO

Y#

RE

SE

T#

RD

Y#

GN

D

SI

N2

DSR3#

CTS3#

DTR3#

GND

RTS3#

INT3

CS3#

SOUT3

IOR#

SOUT2

INT2

RTS2#

VDD

DTR2#

CTS2#

DSR2#

DC

RI

D2

2#

#

Data Sheet Revision 1.0 Page 8

OX16C954-PCC60-B (Rev B) is pin compatible with the previous part OX16C954-PCC60-A (Rev A).

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

IOW# / R/R#

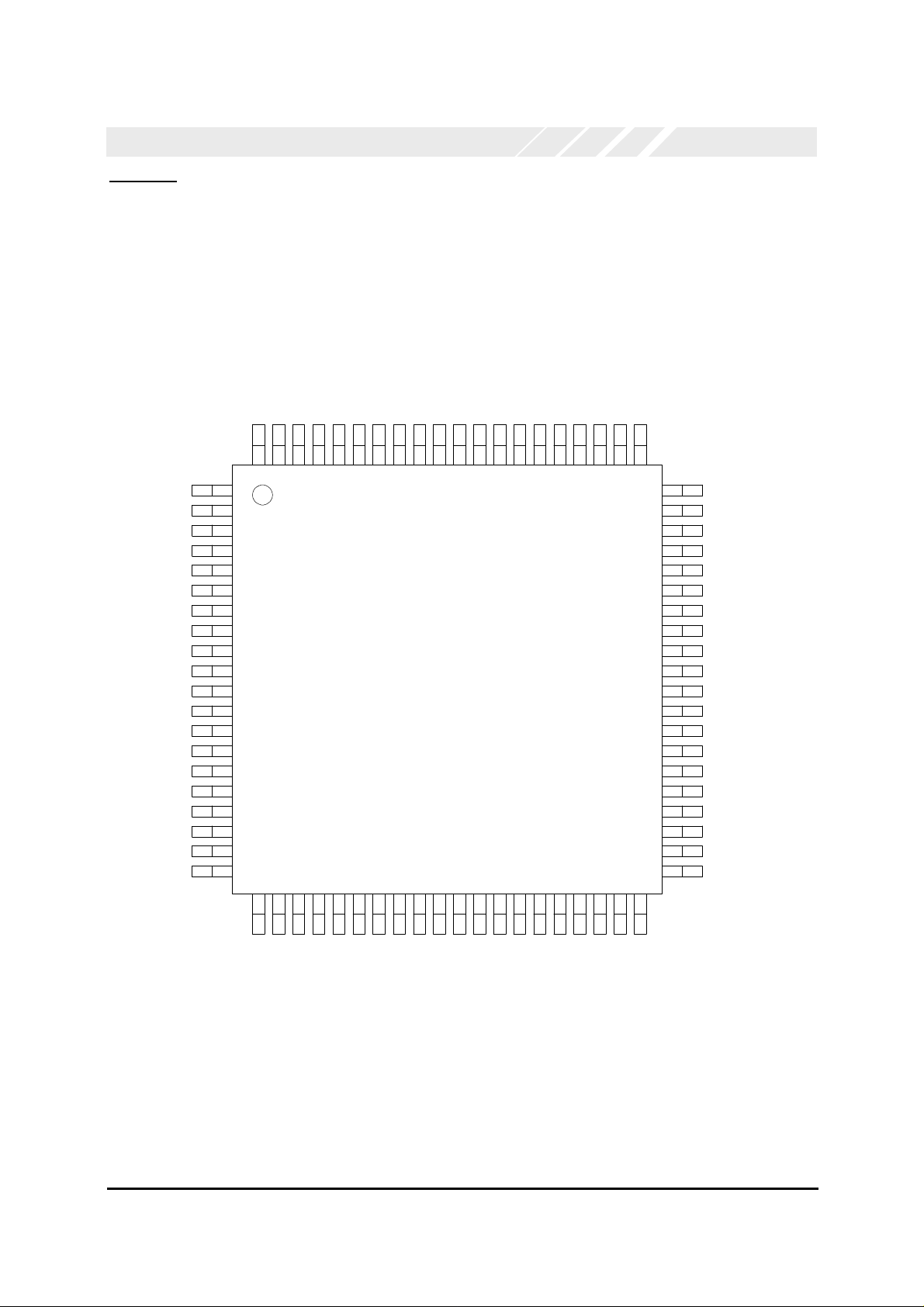

80pin TQFP

TXRDY3#

DCD3#

RI3#

SIN3

FIFOSEL#

INTSEL#

DB0

DB1

DB2

NC

DB3

DB4

DB5

DB6

DB7

GND

SIN0

RI0#

DCD0#

RXRDY0#

RXRDY3#

DSR3#

CTS3#

DTR3#

GND

Z_RTS3

767779 78 717275 74 73 70 666769 68 616265 64 6380

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21 252422 23 302926 27 28 31 353432 33 403936 37 38

SOUT3

CS3#

INT3

OX16C954_TQC60_B

NC

IOR#

SOUT2

CS2# / A4

INT2

RTS2#

VDD

DTR2#

CTS2#

TXRDY2#

DSR2#

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

RXRDY2#

DCD2#

RI2#

SIN2

GND

TXRDY#

RXRDY#

RESET/RESET#

VDETECT

XTLO

XTLI

I/M#

A0

A1

A2

CLKSEL

SIN1

RI1#

DCD1#

TXRDY1#

Data Sheet Revision 1.0 Page 9

DSR0#

TXRDY0#

CTS0#

DTR0#

VDD

RTS0#

SOUT0

CS0# / DS#

INT0 / IRQ#

NC

SOUT1

CS1# / A3

INT1

GND

RTS1#

CTS1#

DTR1#

DSR1#

RXRDY1#

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

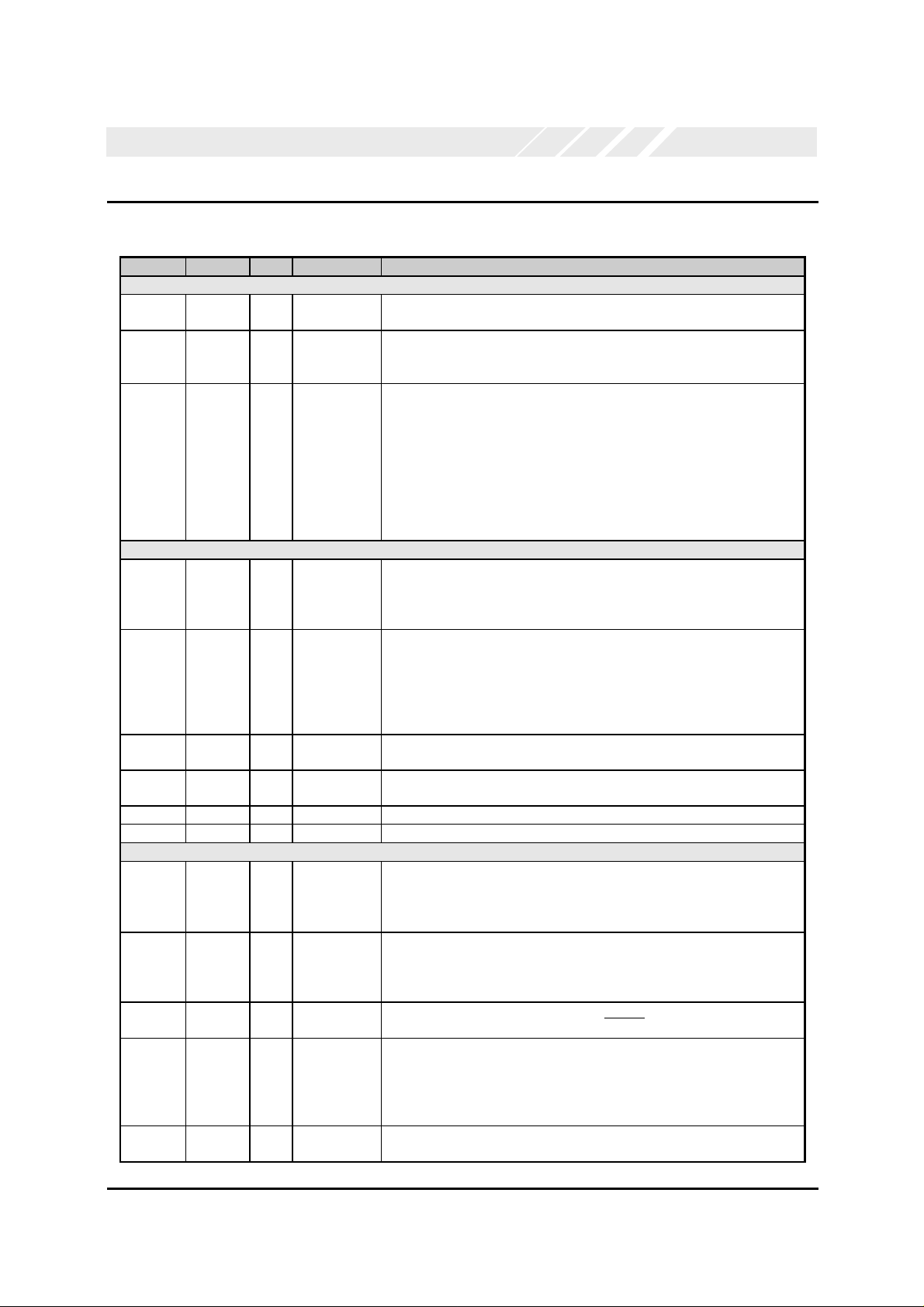

4 PIN DESCRIPTIONS

Please refer to Section 3 for actual Signal Name to Pin Number assignments, for the selected package.

TQFP PLCC Dir1 Name Description

Clock

50 35 I XTLI Crystal oscillator input or external clock pin, for the UART channels.

Crystal oscillator frequency maximum 60MHz

51 36 O XTLO Crystal oscillator output.

Not used when an alternative TTL level clock is applied to XTLI and can

be left unconnected

45 30 I CLKSEL This pin is provided to select an internal clock prescaler on power up. In

16C554 devices this pin is a VDD. When CLKSEL pin is high the internal

prescaler is bypassed (a 1.8432MHz clock is assumed). Connect this pin

to GND to enable the internal clock prescaler. The complement of this pin

is loaded in bit 7 of the MCR register after a hardware reset.

This pin can also be used as an alternative external clock pin under

software control (replacing XTLI and thus reducing noise/power due to

XTLO) for embedded applications.

Processor Interface Pins in Intel Mode (I/M# = ‘1’)

53 37 I

73

68

33

28

46 to 48 32 to 34 I A[2:0] Address lines to select the Uart (channel) registers.

15 to 11

9 to 7

31 18 I IOW# Active-low write strobe in Intel bus mode.

70 52 I IOR# Active-low read strobe in Intel bus mode.

Processor Interface Pins in Motorola Mode (I/M# = ‘0’)

53 37 I RESET# Active-low Hardware Reset. The configuration of OX16C954 after a

28 16 I DS# Active-low Data-Strobe.

70

73

68

33

46 to 48 32 to 34 I A[2:0] Address lines to select the UART (channel) registers.

54

50

20

16

5 to 1

68 to 66

52

54

50

20

RESET Active-high Hardware Reset. The configuration of OX16C954 after a

I

CS[3]#

I

CS[2]#

I

CS[1]#

I

CS[0]#

I/O DB[7:0] Eight-bit 3-state data bus.

I

UNUSED In Motorola bus mode these pins are unused and must be connected to

I

I

A4

I

A3

hardware reset is described in section 7.1. This pin exhibits a small

hysteresis to provide noise immunity. This pin must be tied inactive when

not in use.

Active-low Chip-Selects for each Uart channel, in Intel bus mode.

CS3# - Chip select for Uart 3

CS2# - Chip select for Uart 2

CS1# - Chip select for Uart 1

CS0# - Chip select for Uart 0

hardware reset is described in section 7.1. This pin exhibits a small

hysteresis to provide noise immunity. This pin must be tied inactive when

not in use.

(In Motorola bus mode, individual registers are accessed using DS#,

R/W# and A[4:0])

VDD or GND.

The A[4:3] combination selects individual channels as follows:

00 = UART 0 selected

01 = UART 1 selected

10 = UART 2 selected

11 = UART 3 selected

Data Sheet Revision 1.0 Page 10

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

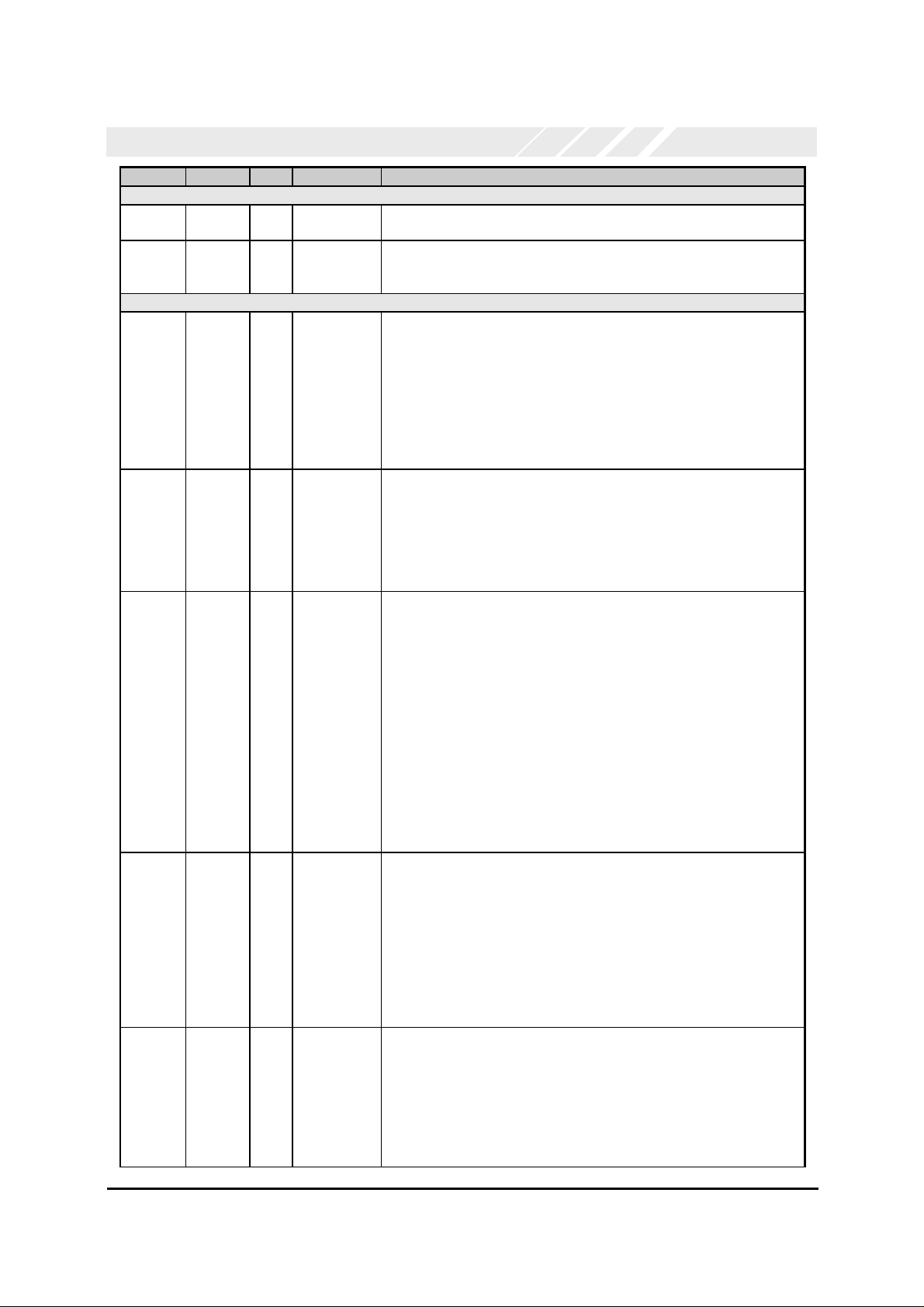

TQFP PLCC Dir1 Name Description

Processor Interface Pins in Motorola Mode (I/M# = ‘0’) Contd.

15 to 11

9 to 7

31 18 I R/W# Read-not-write signal. This signal should be high during read cycles and

Serial Port Pins

72

69

32

29

72

69

32

29

75

66

35

26

77

64

37

24

77

64

37

24

77

64

37

24

4

57

44

17

4

57

44

17

78

63

38

23

5 to 1

68 to 66

53

51

19

17

53

51

19

17

56

48

22

14

58

46

24

12

58

46

24

12

58

46

24

12

63

41

29

7

63

41

29

7

59

45

25

11

I/O DB[7:0] Eight-bit 3-state data bus.

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

O

I

I

I

I

I

I

I

I

I

I

I

I

SOUT[3]

SOUT[2]

SOUT[1]

SOUT[0]

IrDA_Out[3]

IrDA_Out[2]

IrDA_Out[1]

IrDA_Out[0]

RTS[3]#

RTS[2]#

RTS[1]#

RTS[0]#

DTR[3]#

DTR[2]#

DTR[1]#

DTR[0]#

485_En[3]

485_En[2]

485_En[1]

485_En[0]

TxClkOut[3]

TxClkOut[2]

TxClkOut[1]

TxClkOut[0]

SIN[3]

SIN[2]

SIN[1]

SIN[0]

IrDA_In[0:3]

IrDA_In[0:3]

IrDA_In[0:3]

IrDA_In[0:3]

CTS[3]#

CTS[2]#

CTS[1]#

CTS[0]#

low during write cycles.

Serial data output, Uart 3

Serial data output, Uart 2

Serial data output, Uart 1

Serial data output, Uart 0

UART IrDA data outputs, each Uart, respectively.

Serial data output pins are redefined as IrDA data outputs when MCR[6]

of the corresponding UART channel is set in enhanced mode

Active-low Request-To-Send output, for each uart respectively.

Whenever the automated RTS# flow control is enabled for the

corresponding channel, the RTS# pin is de-asserted and re-asserted if the

receiver FIFO reaches or falls below a pair of programmed flow control

thresholds, respectively. The state is controlled by bit 1 of the MCR.

RTS may also be used as a general-purpose output.

Active-low modem “data-terminal-ready output”, for each uart respectively.

If automated DTR# flow control is enabled for the corresponding UART

channel, the DTR# pin is asserted and deasserted if the receiver FIFO

reaches or falls below the channel’s programmed thresholds, respectively.

The state is set by bit 0 of the MCR. DTR may also be used as a general

purpose output.

In RS485 half-duplex mode, the DTR# pin of each UART channel may be

programmed to reflect the state of the channel’s transmitter empty bit (or

its inverse) to automatically control the direction of the RS485 transceiver

buffer (see register ACR[4:3])

Transmitter 1x (or baud rate generator output) clock. For isochronous

applications, the 1x (or Nx) transmitter clock may be asserted on the

uart’s DTR# pin (see CKS[5:4]).

Serial data input, UART 3.

Serial data input, UART 2.

Serial data input, UART 1.

Serial data input, UART 0.

UART IrDA data inputs, for each uart respectively.

Serial data input pins redefined as IrDA data inputs when MCR[6] of the

corresponding UART channel is set in enhanced mode

Active-low modem “clear-to-send” input, for each uart respectively.

If automated CTS# flow control is enabled for the corresponding UART

channel, upon deassertion of the CTS# pin, the channel’s transmitter will

complete the current character and enter the idle mode until the CTS# pin

is reasserted. Note: flow control characters are transmitted regardless of

the state of the CTS# pin. The state of this pin is reflected in bit 4 of the

MSR.

It can also be used as a general-purpose input.

Data Sheet Revision 1.0 Page 11

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

TQFP PLCC Dir1 Name Description

Serial Port Pins Contd.

79

62

39

22

79

62

39

22

2

59

42

19

3

58

43

18

3

58

43

18

Interrupt & DMA Pins

1

61

41

21

55

80

60

40

20

54 38 O RXRDY# Signal for DMA transfer of received data.

60

44

26

10

60

44

26

10

61

43

27

9

62

42

28

8

62

42

28

8

No pin

No pin

No pin

No pin

39

No pin

No pin

No pin

No pin

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

I

O

O

O

O

O TXRDY# Signal for the DMA transfer of transmitter data.

O

O

O

O

DSR[3]#

DSR[2]#

DSR[1]#

DSR[0]#

RxClkIn[3]

RxClkIn[2]

RxClkIn[1]

RxClkIn[0]

DCD[3]#

DCD[2]#

DCD[1]#

DCD[0]#

RI[3]#

RI[2]#

RI[1]#

RI[0]#

Ext_CK[3]

Ext_CK[2]

Ext_CK[1]

Ext_CK[0]

TXRDY3#

TXRDY2#

TXRDY1#

TXRDY0#

RXRDY3#

RXRDY2#

RXRDY1#

RXRDY0#

Active-low modem “data-set-ready” input, for each uart respectively.

If automated DSR# flow control is enabled for the corresponding UART

channel, upon deassertion of the channel’s DSR# pin, the transmitter will

complete the current character and enter the idle mode until the DSR# pin

is reasserted. Note: flow control characters are transmitted regardless of

the state of the DSR# pin. The state of this pin is reflected in bit 5 of the

MSR.

It can also be used as a general-purpose input.

External receiver clock for isochronous applications for each uart

respectively. Selected when CKS[1:0] = ‘01’.

Active-low modem Data-Carrier-Detect input, for each uart respectively.

The state of this pin is reflected in bit 7 of the MSR. It can also be used

as a general-purpose input.

Active-low modem Ring-Indicator input, for each uart respectively.

The state of this pin is reflected in bit 6 of the MSR. It can also be used

as a general-purpose input. RI can be configured as tx and rx for a 1x

clock in isochronous operation.

External transmitter clock for each uart respectively. This clock can be

used by the transmitter (and by the receiver indirectly) when CKS[6] = ‘1’.

Signal for the DMA transfer of transmitter data, for Uart 3.

Signal for the DMA transfer of transmitter data, for Uart 2.

Signal for the DMA transfer of transmitter data, for Uart 1.

Signal for the DMA transfer of transmitter data, for Uart 0.

There are two modes of DMA signalling described in section 8.1

This pin is the wire ”OR-ed” function of the TXRDY# signals of all

channels.

Signal for the DMA transfer of receiver data, for Uart 3.

Signal for the DMA transfer of receiver data, for Uart 2.

Signal for the DMA transfer of receiver data, for Uart 1.

Signal for the DMA transfer of receiver data, for Uart 0.

There are two modes of DMA signalling described in section 8.1

This pin is the wire ”OR-ed” function of the RXRDY# signals of all

channels.

Data Sheet Revision 1.0 Page 12

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

TQFP PLCC Dir1 Name Description

Interrupt & DMA Pins Contd.

74

67

34

27

27

Miscellaneous Pins

6 65 ID INTSEL# Active-low Interrupt enable.

49 31

5 64 I FIFOSEL# FIFO SIZE select.

52 No pin ID VDETECT 3.3v or 5.0v I/O buffer selection.

55

49

21

15

15

O

O

O

O

OD

IU I/M# Intel or Motorola bus interface select.

INT[3]

INT[2]

INT[1]

INT0

IRQ#

Interrupt pin for Uart channel 3 (Intel Bus mode)

Interrupt pin for Uart channel 2 (Intel Bus mode)

Interrupt pin for Uart channel 1 (Intel Bus mode)

Each of these serial channels have a 3-state interrupt output (enabled by

MCR[3] and INTSEL# pin) which goes active (high) when an interrupt

condition occurs. The interrupt is disabled after a hardware reset.

Interrupt pin for Uart channel 0, in Intel bus mode.

This serial channel has a 3-state interrupt output (enabled by MCR[3] and

INTSEL# pin) which goes active (high) when an interrupt condition occurs.

The interrupt is disabled after a hardware reset.

Device interrupt pin (for all uart channels) in Motorola bus mode.

This pin goes active (low) when the interrupt signal from any of the 4

channels is asserted. Otherwise it is in the high-impedance state.

When this pin is left open or connected to GND, the three-state interrupts

that are available on INT[3:0] are enabled according to the setting of

MCR[3]. If this pin is high interrupts are enabled regardless of the state of

MCR[3].

This pin is ignored in Motorola bus mode.

When this pin is tied high or left open, the Intel bus interface is selected.

When this pin is tied low, the Motorola bus interface is selected where

RESET, IOW#, CS0#, CS1# are CS2# are re-assigned and CS3#, IOR#

and INTSEL# are unused. In Motorola mode, all the interrupt lines of the

internal uart channels are wired “OR-ed” onto the IRQ# pin.

In 16C554 this pin is unconnected.

For backward compatibility with 16C554, 16C654 and 16C754 devices the

FIFO depth is 16 when FIFOSEL# is high and 128 when FIFOSEL# is

low. The unlatched state of this pin is readable by software. The FIFO size

may be set to 128 by writing a 1 in FCR[5] when LCR[7] is set or by

putting the device into Enhanced mode, thus overriding the state of the

FIFOSEL# pin. Pin 64 is a VDD in 16C554 and 16C654 devices (PLCC).

This pin must be tied according to the voltage supply used to power the

TQFP package option.

For 5v supply voltage : Vdetect must be tied low.

For 3.3v supply voltage : Vdetect must be tied high.

NOTE : The PLCC package option does not bond-out this pin, which is

internally pulled down to gnd. So the PLCC is suitable for 5v operation

only.

Data Sheet Revision 1.0 Page 13

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

TQFP PLCC Dir1 Name Description

Power, Ground, No Connects

16, 36,

56, 76

6, 23,

40, 57

GND Ground pin.

All GND pins must be tied to ground.

25, 65 13, 47 VDD Power pin.

PLCC : All VDD pins must be tied to 5 Volts.

TQFP : All VDD pins must be tied to 5v or 3.3v. (Note that the VDETECT

pin must be set according to the selected voltage environment).

10, 30,

71

-

NC No Connects

These pins are not connected to any pads within the device, and can be

left open.

Table 2: Pin Descriptions

Direction key:

I, Input

IU Input with pull-up

ID Input with pull-down

O Output

I/O Bi-directional

OD Open drain

Note: All unused signal input pins should be tied to VDD or GND as applicable and must not be left floating. For high speed operation (XTAL >

10MHz), card designers are recommended to follow the guidelines for high-speed digital design such as maintaining PCB tracks as short

as possible, using a multi-layer PCB with separate power and ground planes, and using good-quality de-coupling capacitors.

Attention should be given to high frequency decoupling of power and ground pins due to the high frequency internal switching that occurs

under normal operation

Data Sheet Revision 1.0 Page 14

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

Additional address

4.1 Further Pin Information

Pin Description Action when used Action when not used

I/M# Intel / Motorola Mode Tie high for Intel™ style bus mode Leave unconnected (Internal pull-up)

CS0#-CS3# Chip selects Connect direct to active low channel select

I/M# Intel / Motorola Mode Tie low for Motorola ™ style bus mode n/a

DS# (CS0#) Data Strobe Connect direct to data strobe generator logic n/a

A3-4 (CS1-2#)

IRQ# (INT0) Global interrupt Interrupt for all channels. Connect to an

CS3# Unused n/a Tie high

INT1-3 Unused n/a Leave unconnected

INTSEL

RXRDY# DMA Control signal

TXRDY# DMA Control signal

SOUT Serial data output Connect to a suitable line driver

SIN Serial data input Connect to a suitable line receiver

RTS# Request- To-Send

CTS# Clear-To-Send

DTR# Data-Terminal-Ready

DSR# Data-Set-Ready

DCD# Data-Carrier-Detect

RI# Ring-Indicator

INT Interrupt Output Connect to an available processor interrupt

Intel ™ Mode Bus Interface Pins

n/a

signals for UART channels 0-3 respectively

Motorola™ Mode Bus Interface Pins

Must be tied low for Motorola mode

lines

Connect direct to channel selection logic

A[4:3] = 00 = ch. 1, 01 = ch. 2 etc.

n/a

Leave unconnected

available processor interrupt line

(Interrupts can not be used)

Control Pins

Interrupt Control

Mode (used in Intel

mode only)

Tie high to keep the interrupt pins

permanently enabled.

Tie low or leave unconnected to allow

software enable/disable of the

interrupt pin.

DMA Pins

Connect direct to DMA control circuitry Leave unconnected

output

Connect direct to DMA control circuitry Leave unconnected

output

Common Channel Pins

Leave unconnected

(Serial data can not be transmitted)

Leave unconnected

Connect to a suitable line driver

Modem signal output

Modem signal input

Connect to a suitable line receiver

Connect to a suitable line driver

Modem signal output

Modem signal input

Connect to a suitable line receiver

Connect to a suitable line receiver

Modem signal input

Connect to a suitable line receiver

Modem signal input

(Serial data can not be received)

Leave unconnected

Tie high

Leave unconnected

Tie high

Tie high

Tie high

Leave unconnected

line

(Interrupts can not be used)

Data Sheet Revision 1.0 Page 15

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

5 MODE SELECTION

The OX16C954 device is a four-channel device backward compatible with the 16C454, 16C554, 16C654 and 16C750 UARTs.

Each of the four channels are identical and independent in terms of functionality, with the exception of some shared pins (for

example, CLKSEL, FIFOSEL#, CLK and RESET). The remainder of this document therefore discusses the operation of a single

channel only.

The operation of each Uart Channel depends on a number of mode settings, which are referred to throughout this section. The

modes, conditions and corresponding FIFO depth are tabulated below:

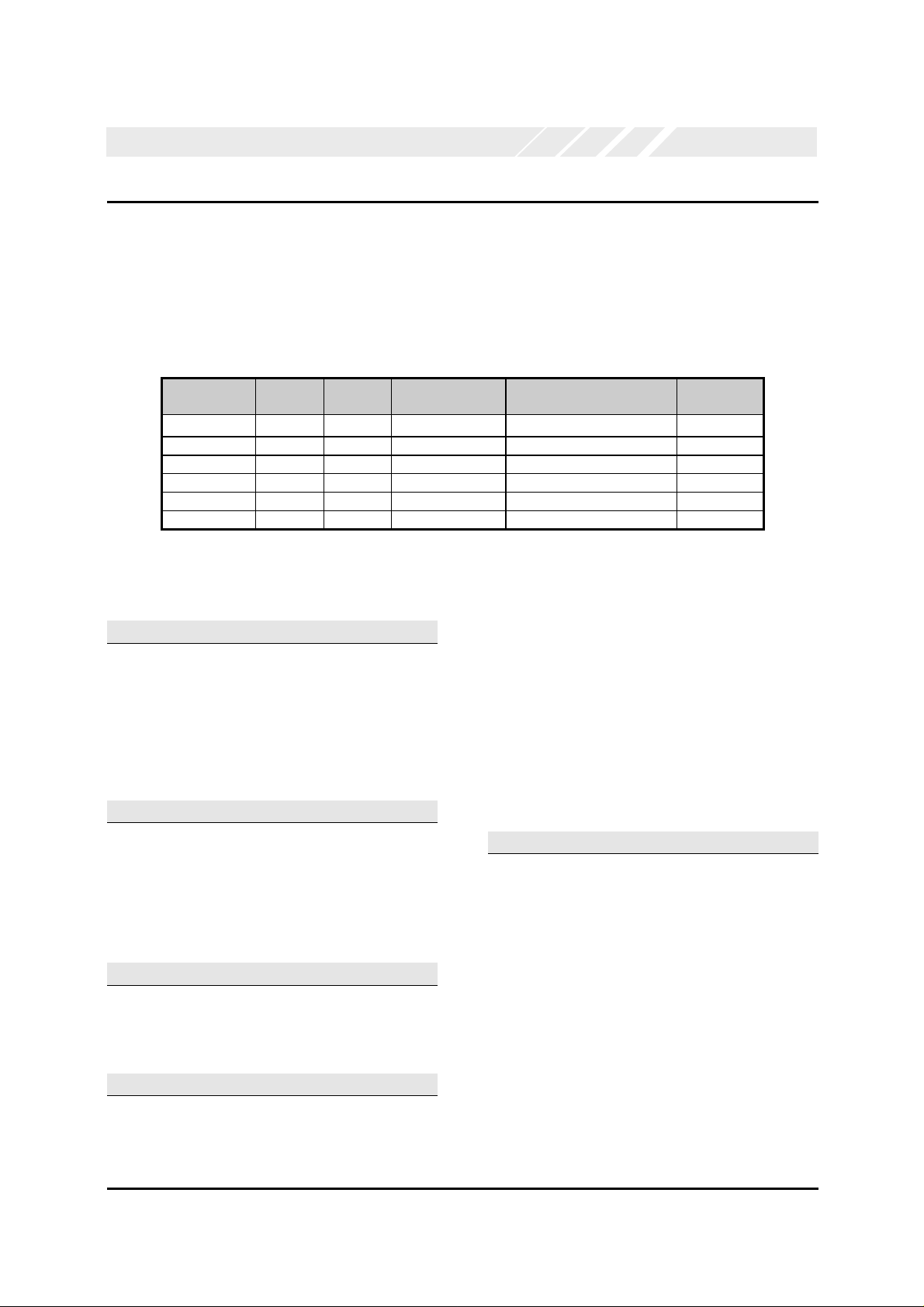

UART Mode FIFO

size

450 1 0 X X X

550 16 1 0 0 1

Extended 550 128 1 0 X 0

650 128 1 1 X X

750 128 1 0 1 1

9501 128 1 1 X X

Note 1: 950 mode configuration is identical to 650 configuration

5.1 450 Mode

After a hardware reset, bit 0 of the FIFO Control Register

(‘FCR’) is cleared, hence the UART is compatible with the

16C450. The transmitter and receiver FIFOs (referred to as

the ‘Transmit Holding Register’ and ‘Receiver Holding

Register’ respectively) have a depth of one. This is referred

to as ‘Byte mode’. When FCR[0] is cleared, all other mode

selection parameters are ignored.

5.2 550 Mode

Connect FIFOSEL# to VDD. After a hardware reset, writing

a 1 to FCR[0] will increase the FIFO size to 16, providing

compatibility with 16C550 devices. Since this pin is VDD in

16C554 devices, replacing a 16C554 with OX16C954

would result in a 550 compatible device with 16 byte deep

FIFOs.

5.3 Extended 550 Mode

Connect FIFOSEL# to GND. Writing a 1 to FCR[0] will now

increase the FIFO size to 128, thus providing a 550 device

with 128 deep FIFOs.

5.4 750 Mode

Writing a 1 to FCR[0] will increase the FIFO size to 16. In a

similar fashion to 16C750, the FIFO size can be further

increased to 128 by writing a 1 to FCR[5]. Note that access

to FCR[5] is protected by LCR[7]. i.e., to set FCR[5],

FCR[0] Enhanced mode

(EFR[4]=1)

Table 3: UART Mode Configuration

software should first set LCR[7] to temporarily remove the

guard. Once FCR[5] is set, the software should clear

LCR[7] for normal operation.

The 16C750 additional features are available as long as

the UART is not put into Enhanced mode; i.e. ensure

EFR[4] = ‘0’. These features are:

• Deeper FIFOs

• Automatic RTS/CTS out-of-band flow control

• Sleep mode

5.5 650 Mode

The OX16C954 UART is compatible with the 16C650 when

EFR[4] is set, i.e. the device is in Enhanced mode. As 650

software drivers usually put the device in Enhanced mode,

running 650 drivers on the one of the UART channels will

result in 650 compatibility with 128 deep FIFOs, as long as

FCR[0] is set. Note that the 650 emulation mode of the

OX16C954 provides 128-deep FIFOs whereas the

standard 16C650 has only 32 byte FIFOs.

650 mode has the same enhancements as the 16C750

over the 16C550, but these are enabled using different

registers.

There are also additional enhancements over those of the

16C750 in this mode. These are -

1. Automatic in-band flow control

2. Special character detection

FCR[5]

(guarded with LCR[7] = 1)

FIFOSEL#

Pin

Data Sheet Revision 1.0 Page 16

OX16C954 rev B

OXFORD SEMICONDUCTOR LTD.

3. Infra-red “IrDA-format” transmit and receive mode

4. Transmit trigger levels

5. Optional clock prescaler

5.6 950 Mode

The additional features offered in 950 mode generally only

apply when the UART is in Enhanced mode (EFR[4]=’1’).

Provided FCR[0] is set, in Enhanced mode the FIFO size is

128 regardless of the state of FIFOSEL#.

Note that 950 mode configuration is identical to that of 650

mode, however additional 950 specific features are

enabled using the Additional Control Register ‘ACR’ (see

section 15.3). In addition to larger FIFOs and higher baud

rates, the enhancements of the 950 mode over 650

emulation mode are:

Selectable arbitrary trigger levels for the receiver and

•

transmitter FIFO interrupts

• Improved automatic flow control using selectable

arbitrary thresholds

• DSR#/DTR# automatic flow control

• Transmitter and receiver can be optionally disabled

• Software reset of device

• Readable FIFO fill levels

• Optional generation of an RS-485 buffer enable signal

Four-byte device identification (0x16C95404)

•

• Readable status for automatic in-band and out-of-

band flow control

• External 1x clock modes (see section14.4)

• Flexible “M+N/8” clock prescaler (see section 14.2)

• Programmable sample clock to allow data rates up to

15 Mbps (see section 14.3).

• 9-bit data mode

The 950 trigger levels are enabled when ACR[5] is set (bits

4 to 7 of FCR are ignored). Then arbitrary trigger levels can

be defined in RTL, TTL, FCL and FCH registers (see

section 15). The Additional Status Register (‘ASR’) offers

flow control status for the local and remote transmitters.

FIFO levels are readable using RFL and TFL registers.

The UART has a flexible prescaler capable of dividing the

system clock by any value between 1 and 31.875 in steps

of 0.125. It divides the system clock by an arbitrary value in

“M+N/8” format, where M and N are 5- and 3-bit binary

numbers programmed in CPR[7:3] and CPR[2:0]

respectively. This arrangement offers a great deal of

flexibility when choosing an input clock frequency to

synthesise arbitrary baud rates. The default division value

is 4 to provide backward compatibility with 16C650

devices.

The user may apply an external 1x (or Nx) clock for the

transmitter and receiver to the RI# and DSR# pin

respectively. The transmitter clock may instead be asserted

on the DTR# pin. The external clock options are selected

through the CKS register (offset 0x02 of ICR).

It is also possible to define the over-sampling rate used by

the transmitter and receiver clocks. The 16C450/16C550

and compatible devices employ 16 times over-sampling,

where there are 16 clock cycles per bit. However the 950

UART can employ any over-sampling rate from 4 to 16 by

programming the TCR register. This allows the data rates

to be increased to 460.8 Kbps using a 1.8432MHz clock, or

15 Mbps using a 60 MHz clock. The default value after a

reset for this register is 0x00, which corresponds to a 16

cycle sampling clock. Writing 0x01, 0x02 or 0x03 will also

result in a 16 cycle sampling clock. To program the value to

any value from 4 to 15 it is necessary to write this value

into the TCR i.e. to set the device to a 13 cycle sampling

clock it would be necessary to write 0x0D to TCR. For

further information see section 14.3.

The UART also offers 9-bit data frames for multi-drop

industrial applications.

Data Sheet Revision 1.0 Page 17

Loading...

Loading...