OXFORD OX12PCI840 Datasheet

Oxford Semiconductor Ltd.

Oxford Semiconductor 1999

A

OX12PCI840

EATURE

F

Integrated Parallel Port

and PCI interface

• IEEE1284 SPP/EPP/ECP parallel port

• Single function target PCI controller, fully PCI 2.2 and

PCI Power Management 1.0 compliant

• 2 multi-purpose IO pins which can be configured as

interrupt input pins

DESCRIPTION

The OX12PCI840 is a single chip solution for PCI-based

parallel expansion add-in cards. It is a single function PCI

device.

For legacy applications the PCI resources are arranged so

that the parallel port can be located at standard I/O

addresses.

The efficient 32-bit, 33MHz target-only PCI interface is

compliant with version 2.2 of the PCI Bus Specification and

• Can be reconfigured using optional non-volatile

configuration memory (EEPROM)

• 5.0V operation

• 100 pin PQFP package

version 1.0 of PCI Power Management Specification. For

full flexibility, all the default register values can be

overwritten using an optional MicrowireTM serial EEPROM.

The OX12PCI840 provides an IEEE1284 EPP/ECP parallel

port which fully supports the existing Centronics interface.

25 Milton Park, Abingdon, Oxon, OX14 4SH, UK

Tel: +44 (0)1235 824900 Fax: +44(0)1235 821141

OX12PCI840 1.2 – Dec 2001

Part No. OX12PCI840-PQC-

OXFORD SEMICONDUCTOR LTD.

OX12PCI840

CONTENTS

1 PIN INFORMATION .....................................................................................................................4

2 PIN DESCRIPTIONS ....................................................................................................................5

3 CONFIGURATION & OPERATION...............................................................................................8

4 PCI TARGET CONTROLLER .......................................................................................................9

4.1 OPERATION..........................................................................................................................................................................9

4.2 CONFIGURATION SPACE...................................................................................................................................................9

4.2.1 PCI CONFIGURATION SPACE REGISTER MAP .........................................................................................................10

4.3 ACCESSING LOGICAL FUNCTIONS................................................................................................................................11

4.3.1 PCI ACCESS TO PARALLEL PORT..............................................................................................................................11

4.4 ACCESSING LOCAL CONFIGURATION REGISTERS ....................................................................................................12

4.4.1 LOCAL CONFIGURATION AND CONTROL REGISTER ‘LCC’ (OFFSET 0X00) .........................................................12

4.4.2 MULTI-PURPOSE I/O CONFIGURATION REGISTER ‘MIC’ (OFFSET 0X04)............................................................. 13

4.4.3 LOCAL BUS TIMING PARAMETER REGISTER 1 ‘LT1’ (OFFSET 0X08): ...................................................................13

4.4.4 LOCAL BUS TIMING PARAMETER/BAR SIZING REGISTER 2 ‘LT2’ (OFFSET 0X0C):.............................................14

4.4.5

4.5 PCI INTERRUPTS ...............................................................................................................................................................16

4.6 POWER MANAGEMENT....................................................................................................................................................17

4.6.1 POWER MANAGEMENT USING MIO............................................................................................................................ 17

GLOB AL INTERRUPT STATUS AND CONTROL REGISTER ‘GIS’ (OFFSET 0X10)................................................. 15

5 BI-DIRECTIONAL PARALLEL PORT..........................................................................................18

5.1 OPERATION AND MODE SELECTION............................................................................................................................. 18

5.1.1 SPP MODE......................................................................................................................................................................18

5.1.2 PS2 MODE......................................................................................................................................................................18

5.1.3 EPP MODE......................................................................................................................................................................18

5.1.4 ECP MODE......................................................................................................................................................................18

5.2 PARALLEL PORT INTERRUPT .........................................................................................................................................18

5.3 REGISTER DESCRIPTION.................................................................................................................................................19

5.3.1 PARALLEL PORT DATA REGISTER ‘PDR’...................................................................................................................19

5.3.2 ECP FIFO ADDRESS / RLE...........................................................................................................................................19

5.3.3 DEVICE STATUS REGISTER ‘DSR’..............................................................................................................................19

5.3.4 DEVICE CONTROL REGISTER ‘DCR’ ..........................................................................................................................20

5.3.5

5.3.6 EPP DATA REGISTERS ‘EPPD1-4’ ...............................................................................................................................20

5.3.7 ECP DATA FIFO............................................................................................................................................................. 20

5.3.8 TEST FIFO......................................................................................................................................................................20

5.3.9 CONFIGURATION A REGISTER ...................................................................................................................................20

5.3.10 CONFIGURATION B REGISTER ...................................................................................................................................21

5.3.11 EXTENDED CONTROL REGISTER ‘ECR’....................................................................................................................21

EPP ADDRESS REGISTER ‘EPPA’ ...............................................................................................................................20

6 SERIAL EEPROM......................................................................................................................22

6.1 SPECIFICATION .................................................................................................................................................................22

6.2 EEPROM DATA ORGANISATION ..................................................................................................................................... 22

6.2.1 ZONE0: HEADER............................................................................................................................................................ 22

6.2.2 ZONE1: LOCAL CONFIGURATION REGISTERS .........................................................................................................23

6.2.3 ZONE2: IDENTIFICATION REGISTERS........................................................................................................................23

6.2.4 ZONE3: PCI CONFIGURATION REGISTERS ...............................................................................................................23

6.2.5 ZONE4: FUNCTION ACCESS........................................................................................................................................ 25

7 OPERATING CONDITIONS ........................................................................................................26

Data Sheet Revision 1.2 Page 2

OXFORD SEMICONDUCTOR LTD.

OX12PCI840

8 DC ELECTRICAL CHARACTERISTICS ......................................................................................26

8.1 NON-PCI I/O BUFFERS ...................................................................................................................................................... 26

8.2 PCI I/O BUFFERS ...............................................................................................................................................................27

9 AC ELECTRICAL CHARACTERISTICS ......................................................................................28

9.1 PCI BUS...............................................................................................................................................................................28

10 TIMING WAVEFORMS............................................................................................................29

11 PACKAGE DETAILS ..............................................................................................................30

12 NOTES..................................................................................................................................31

13 CONTACT DETAILS...............................................................................................................32

Data Sheet Revision 1.2 Page 3

80 75 70 65 60 55 51 EE_SK

81 50

AD0 MIO1 AD1 Z_INTA

GND ac

Z_RESET

AD2

AD30 90 GND ac

AD29 40 VDD ac

GND ac

AD6 AD28 AD7 AD27 Z_CBE0

AD26

AD8 GND ac

GND ac

1 5 10 15 20 25 30

OXFORD SEMICONDUCTOR LTD.

1 PIN INFORMATION

100 pin QFP

OX12PCI840

GND dc 85

PCI_CLK

VDD dc

Z_PME

AD31

VDD ac

AD25

AD24

Z_CBE3

100

STB

AFD#

INIT#

SLIN#

VDD ac

GND ac

EE_DI

95

IDSEL

TEST

EE_DO EE_CS

AD23

AD22 AD21 AD20

GND ac

NC

ACK#

GND ac

AD19 AD18 AD17 AD16

PD_EN

ERR#

VDD dc GND dc

Z_CBE2

Z_FRAME

GND dc

SLCT

BUSY

VDD dc

Z_IRDY

PE

PD0

Z_TRDY

Z_DEVSEL

PD1 PD2 PD3 PD4

GND ac

GND ac

Z_STOP Z_PERR Z_SERR

VDD ac GND ac

PAR

Z_CBE1

PD5 PD6 PD7

AD15 AD14 AD13

MIO0

VDD ac

GND ac

AD3

45 VDD dc

GND dc

AD4

AD5

35

AD9

AD10

AD11

31 AD12

Data Sheet Revision 1.2 Page 4

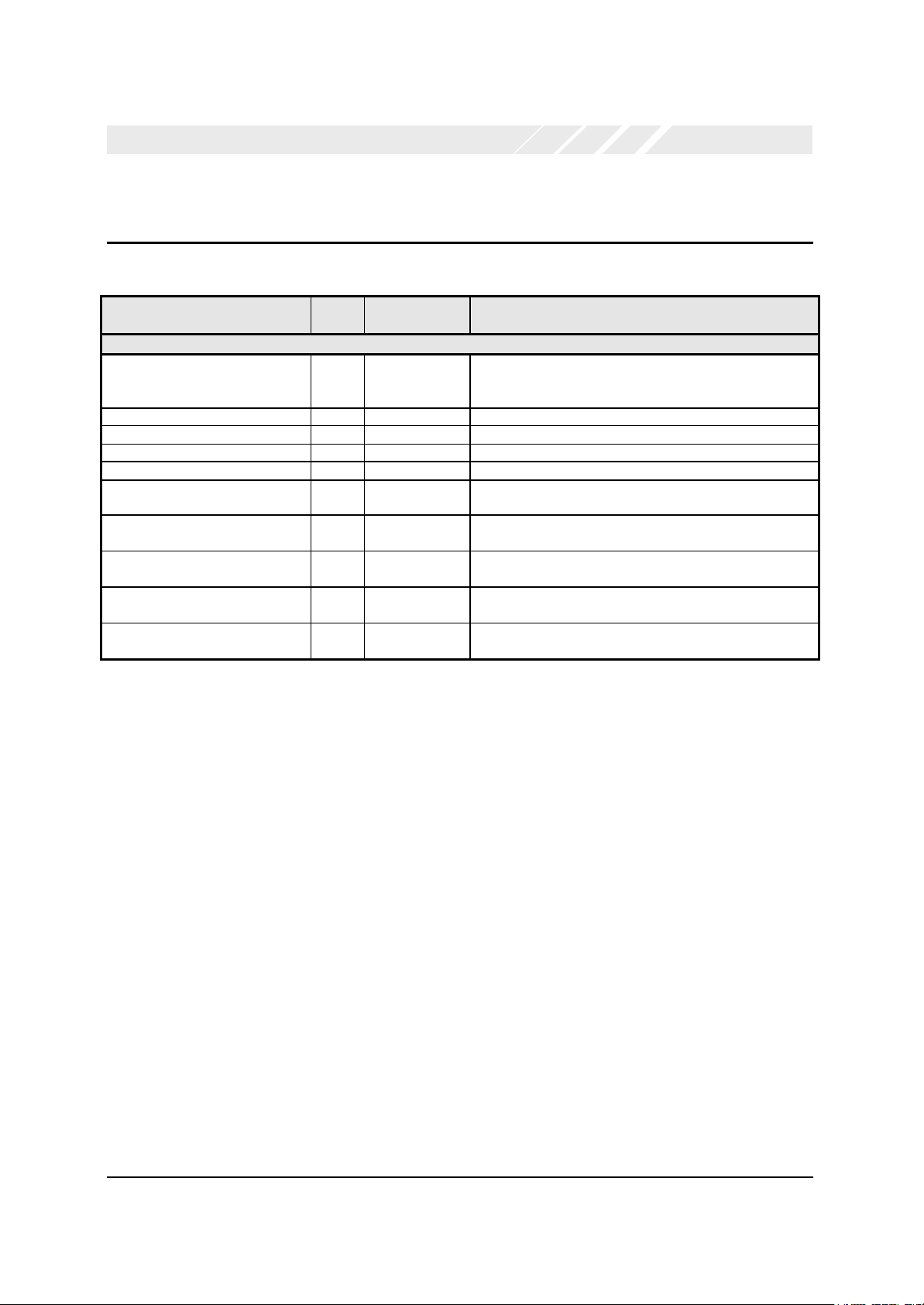

OXFORD SEMICONDUCTOR LTD.

2 PIN DESCRIPTIONS

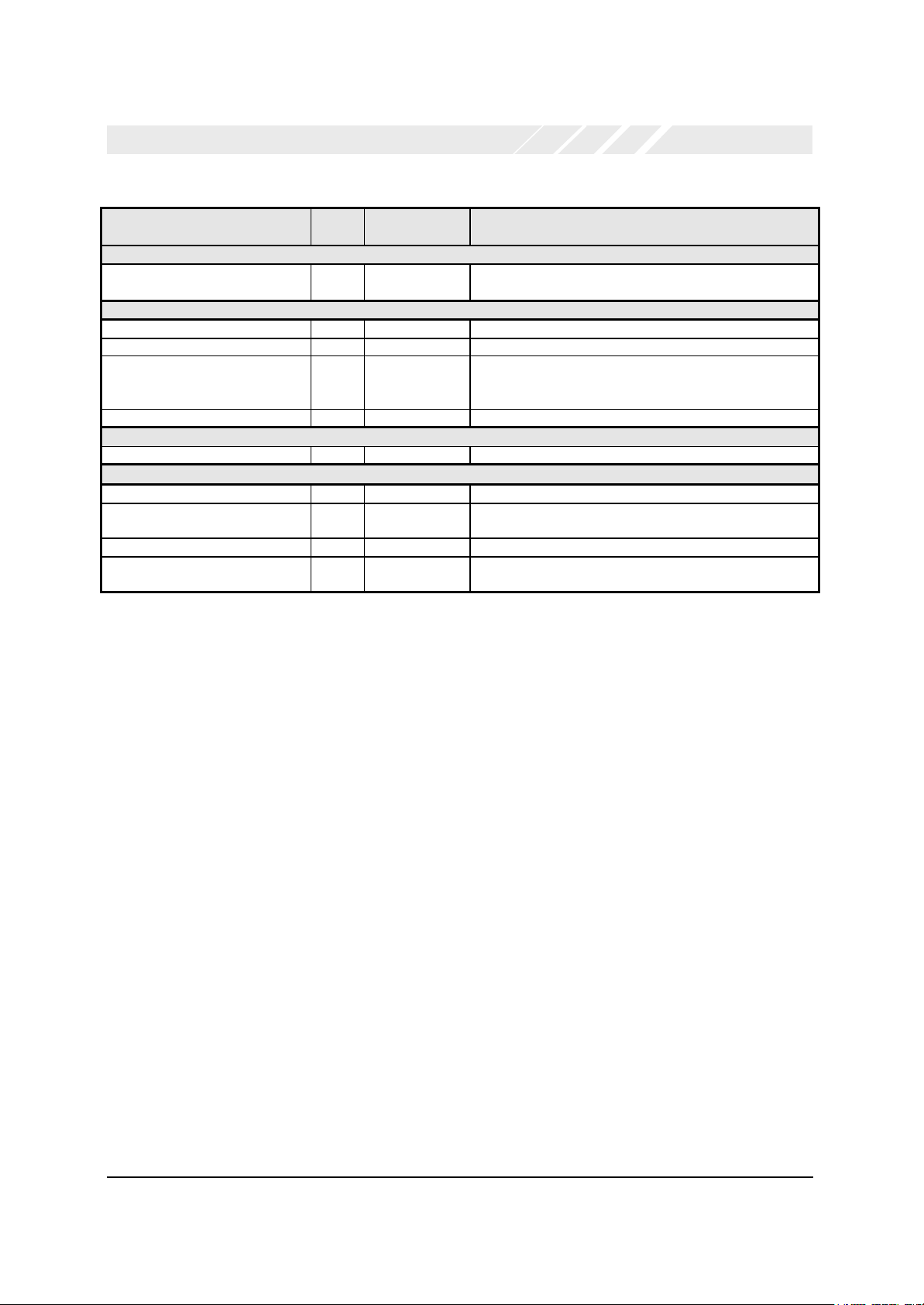

Pin Numbers Dir1 Name Description

PCI interface

89,90,91,93,94,95,98,99,2,4,5,6,9,

10,11,12,26,27,28,31,32,33,34,36,

38,39,42,43,46,47,49,50

100,13,25,37 P_I C/BE[3:0]# PCI Command/Byte enable

86 P_I CLK PCI system clock

14 P_I FRAME# Cycle Frame

19 P_O DEVSEL# Device Select

17 P_I IRDY# Initiator ready

18 P_O TRDY# Target ready

21 P_O STOP# Target Stop request

24 P_I/O PAR Parity

23 P_O SERR# System error

22 P_I/O PERR# Parity error

1 P_I IDSEL Initialisation device select

84 P_I RST# PCI system reset

83 P_OD INTA# PCI interrupt

88 P_OD PME# Power management event

OX12PCI840

P_I/O AD[31:0] Multiplexed PCI Address/Data bus

Data Sheet Revision 1.2 Page 5

OXFORD SEMICONDUCTOR LTD.

Pin Numbers Dir1 Name Description

Parallel port

71 I

63 I PE Paper Empty. Activated by printer when it runs out of paper.

64 I

73 OD

65 I SLCT Peripheral selected. Asserted by peripheral when selected.

68 I ERR# Error. Held low by the peripheral during an error condition.

74 OD

75 OD

76 OD

52,53,54,57,

58,59,60,62

ACK#

I

INTR#

BUSY

I

WAIT#

SLIN#

O

ADDRSTB#

INIT#

O

INIT#

AFD#

O

DATASTB#

STB#

O

WRITE#

I/O PD[7:0] Parallel data bus

Acknowledge (SPP mode). ACK# is asserted (low) by the

peripheral to indicate that a successful data transfer has

taken place.

Identical function to ACK# (EPP mode).

Busy (SPP mode). BUSY is asserted (high) by the peripheral

when it is not ready to accept data

Wait (EPP mode). Handshake signal for interlocked IEEE

1284 compliant EPP cycles.

Select (SPP mode). Asserted by host to select the peripheral

Address strobe (EPP mode) provides address read and write

strobe

Initialise (SPP mode). Commands the peripheral to initialise.

Initialise (EPP mode). Identical function to SPP mode.

Auto Feed (SPP mode, open-drain)

Data strobe (EPP mode) provides data read and write strobe

Strobe (SPP mode). Used by peripheral to latch data

currently available on PD[7:0]

Write (EPP mode). Indicates a write cycle when low and a

read cycle when high

OX12PCI840

Data Sheet Revision 1.2 Page 6

OXFORD SEMICONDUCTOR LTD.

Pin Numbers Dir1 Name Description

Multi-purpose & External interrupt pins

82, 51 I/O MIO[1:0] Multi -purpose I/O pins. Can drive high or low, or assert a PCI

interrupt

EEPROM pins

81 O EE_CK EEPROM clock

78 O EE_CS EEPROM active-high Chip Select

80 IU EE_DI EEPROM data in. When the serial EEPROM is connected,

this pin should be pulled up using 1-10k resistor. When the

EEPROM is not used the internal pull-up is sufficient.

79 O EE_DO EEPROM data out.

Miscellaneous pins

77 I TEST Test Pin : should be held low at all times

Power and ground2

8,30,40,56,97 V AC VDD Supplies power to output buffers in switching (AC) state

16,45,67,87 V DC VDD Power supply. Supplies power to core logic, input buffers

and output buffers in steady state

3,7,20,29,35,41,48,55,61,72,92,96 G AC GND Supplies GND to output buffers in switching (AC) state

15,44,66,85 G DC GND Ground (0 volts). Supplies GND to core logic, input buffers

and output buffers in steady state

OX12PCI840

Table 1: Pin Descriptions

Note 1: Direction key:

I Input

ID Input with internal pull-down

O Output

I/O Bi-directional

OD Open drain

NC No connect

Z High impedance

Note 2: Power & Ground

There are two GND and two VDD rails internally. One set of rails supply power and ground to output buffers while in switching

state (called AC power) and another rail supply the core logic, input buffers and output buffers in steady-state (called DC rail).

The rails are not connected internally. This precaution reduces the effects of simultaneous switching outputs and undesirable RF

radiation from the chip. Further precaution is taken by segmenting the GND and VDD AC rails to isolate the PCI and Local Bus

pins.

P_I PCI input

P_O PCI output

P_I/O PCI bi-directional

P_OD PCI open drain

G Ground

V 5.0V power

Data Sheet Revision 1.2 Page 7

OXFORD SEMICONDUCTOR LTD.

3 CONFIGURATION & OPERATION

OX12PCI840

The OX12PCI840 is a single function, target-only PCI

device, compliant with the PCI Local Bus Specification,

Revision 2.2 and PCI Power Management Specification,

Revision 1.0.

The OX12PCI840 is configured by system start-up

software during the bootstrap process that follows bus

reset. The system scans the bus and reads the vendor and

device identification codes from any devices it finds. It then

loads device-driver software according to this information

and configures the I/O, memory and interrupt resources.

Device drivers can then access the functions at the

assigned addresses in the usual fashion, with the improved

data throughput provided by PCI.

There are a set of Local configuration registers that can be

used to enable signals and interrupts, and configure

timings. These can be set up by drivers or from the

EEPROM.

All registers default after reset to suitable values for typical

applications. However, all identification, control and timing

registers can be redefined using an optional serial

EEPROM. As an additional enhancement, the EEPROM

can be used to program the parallel port, allowing preconfiguration, without requiring driver changes.

Data Sheet Revision 1.2 Page 8

OXFORD SEMICONDUCTOR LTD.

4 PCI TARGET CONTROLLER

OX12PCI840

4.1 Operation

The OX12PCI840 responds to the following PCI

transactions:-

• Configuration access: The OX12PCI840 responds to

type 0 configuration reads and writes if the IDSEL

signal is asserted and the bus address is selecting the

configuration registers for function 0. The device will

respond to the configuration transaction by asserting

DEVSEL#. Data transfer then follows. Any other

configuration transaction will be ignored by the

OX12PCI840.

• IO reads/writes: The address is compared with the

addresses reserved in the I/O Base Address Registers

(BARs). If the address falls within one of the assigned

ranges, the device will respond to the IO transaction

by asserting DEVSEL#. Data transfer follows this

address phase. Only byte accesses are possible to

the function BARs (excluding the local configuration

registers for which WORD, DWORD access is

supported). For IO accesses to these regions, the

controller compares AD[1:0] with the byte-enable

signals as defined in the PCI specification. The access

is always completed; however if the correct BE signal

is not present the transaction will have no effect.

• Memory reads/writes: These are treated in the same

way as I/O transactions, except that the memory

ranges are used. Memory access to single-byte

regions is always expanded to DWORDs in the

OX12PCI840. In other words, OX12PCI840 reserves

a DWORD per byte in single-byte regions. The device

allows the user to define the active byte lane using

LCC[4:3] so that in Big-Endian systems the hardware

can swap the byte lane automatically. For Memory

mapped access in single-byte regions, the

OX12PCI840 compares the asserted byte-enable with

the selected byte-lane in LCC[4:3] and completes the

operation if a match occurs, otherwise the access will

complete normally on the PCI bus, but it will have no

effect on either the parallel port or the local bus

controller.

• All other cycles (64-bit, special cycles, reserved

encoding etc.) are ignored.

The OX12PCI840 will complete all transactions as

disconnect-with-data, i.e. the device will assert the STOP#

signal alongside TRDY#, to ensure that the Bus Master

does not continue with a burst access. The exception to

this is Retry, which will be signalled in response to any

access while the OX12PCI840 is reading from the serial

EEPROM.

The OX12PCI840 performs medium-speed address

decoding as defined by the PCI specification. It asserts the

DEVSEL# bus signal two clocks after FRAME# is first

sampled low on all bus transaction frames which address

the chip. Fast back-to-back transactions are supported by

the OX12PCI840 as a target, so a bus master can perform

faster sequences of write transactions to the parallel port

when an inter-frame turn-around cycle is not required.

The device supports any combination of byte-enables to

the PCI Configuration Registers and the Local

Configuration registers (see Base Address 2 and 3). If a

byte-enable is not asserted, that byte is unaffected by a

write operation and undefined data is returned upon a read.

The OX12PCI840 performs parity generation and checking

on all PCI bus transactions as defined by the standard. If a

parity error occurs during the PCI bus address phase, the

device will report the error in the standard way by asserting

the SERR# bus signal. However if that address/command

combination is decoded as a valid access, it will still

complete the transaction as though the parity check was

correct.

The OX12PCI840 does not support any kind of caching or

data buffering, other than that in the parallel port interface

itself.

4.2 Configuration space

The OX12PCI840 is a single function device, with one

configuration space. All required fields in the standard

header are implemented, plus the Power Management

Extended Capability register set. The format of the

configuration space is shown in Table 2 overleaf.

In general, writes to any registers that are not implemented

are ignored, and all reads from unimplemented registers

return 0.

Data Sheet Revision 1.2 Page 9

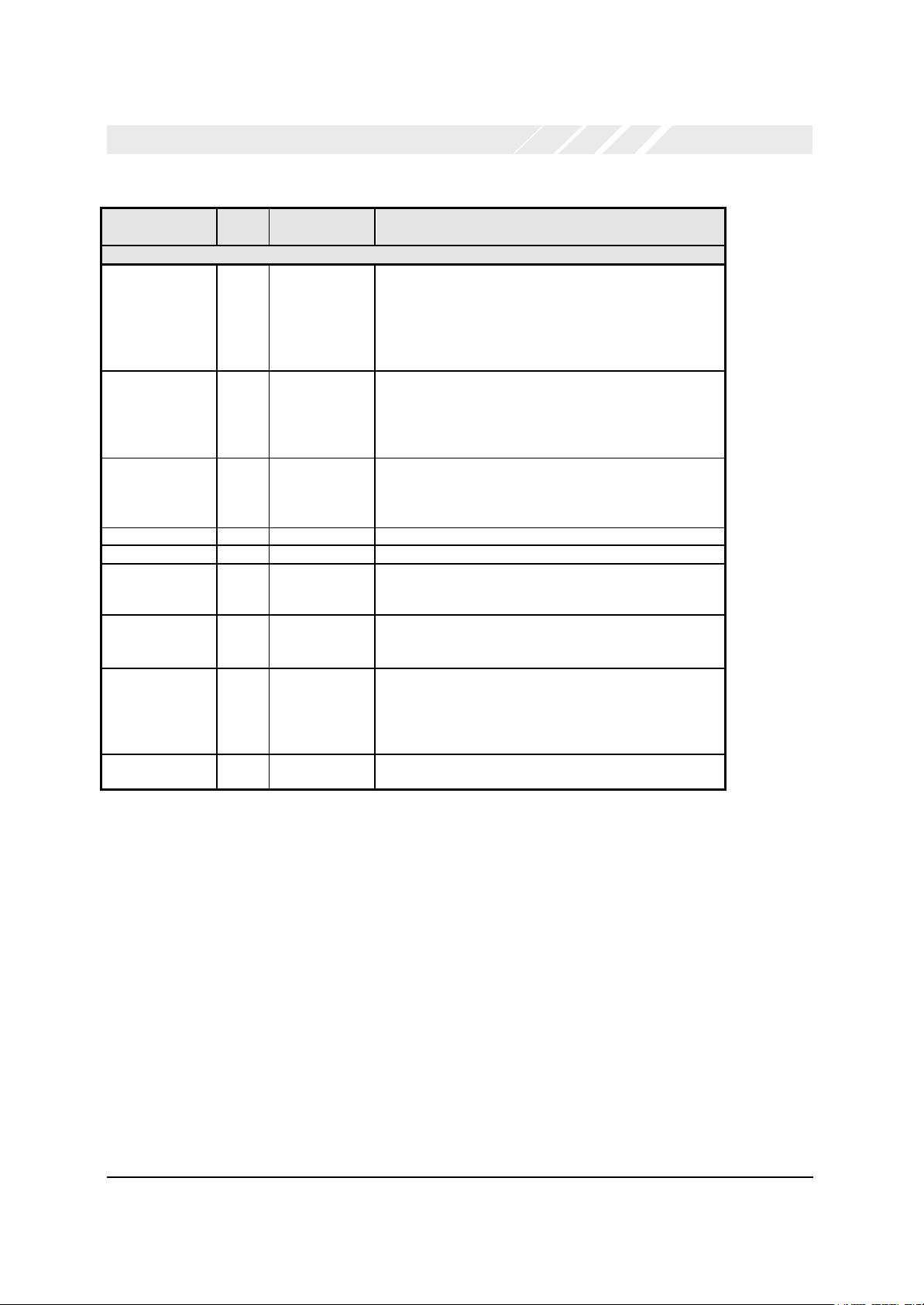

OXFORD SEMICONDUCTOR LTD.

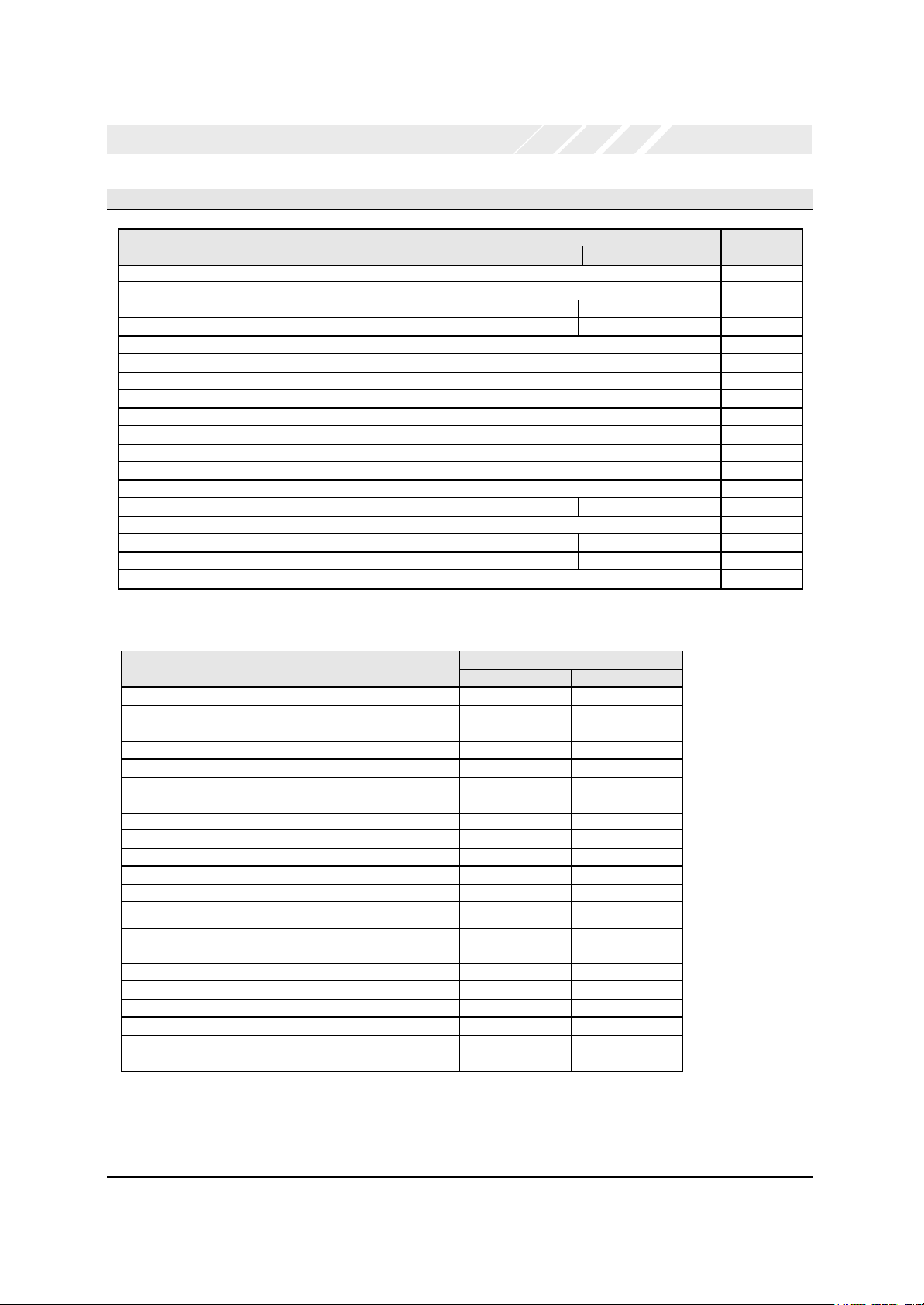

4.2.1 PCI Configuration Space Register map

31 16 15 0

Device ID Vendor ID 00h

Status Command 04h

BIST1 Header Type Rese rved Reserved 0Ch

Base Address Register 0 (BAR0) - Function in I/O space 10h

Base Address Register 1 (BAR 1) - Function in I/O space 14h

Base Address Register 2 (BAR 2) – Local Configuration Registers in IO space 18h

Base Address Register 3 (BAR3) – Local Configuration Registers in Memory space 1Ch

Base Address Register 4 (BAR4) – Function in Memory Space 20h

Subsystem ID Subsystem Vendor ID 2Ch

Reserved Reserved Interrupt Pin Interrupt Line 3Ch

Power Management Capabilities (PMC) Next Ptr Cap_ID 40h

Reserved Reserved PMC Control/Status Register (PMCSR) 44h

Configuration Register Description Offset

Class Code Revision ID 08h

Reserved 24h

Reserved 28h

Reserved 30h

Reserved Cap_Ptr 34h

Reserved 38h

OX12PCI840

Address

Table 2: PCI Configuration space

Program read/write Register name Reset value

EEPROM PCI

Vendor ID 0x1415 W R

Device ID 0x8403 W R

Command 0x0000 - R/W

Status 0x0290 W(bit 4) R/W

Revision ID 0x00 - R

Class code 0x070103 W R

Header type 0x00 - R

BAR 0 0x00000001 - R/W

BAR 1 0x00000001 - R/W

BAR 2 0x00000001 - R/W

BAR 3 0x00000000 - R/W

BAR 4 Reserved - R/W

Subsystem VID 0x1415 W R

Subsystem ID 0x0001 W R

Cap ptr. 0x40 - R

Interrupt line 0x00 - R/W

Interrupt pin 0x01 W R

Cap ID 0x01 - R

Next ptr. 0x00 - R

PM capabilities 0x6C01 W R

PMC control/ status register 0x0000 - R/W

Table 3: PCI configuration space default values

Data Sheet Revision 1.2 Page 10

Loading...

Loading...