NCP9003

Compact Backlight LED

Boost Driver

The NCP9003 is a high efficiency boost converter operating in

current loop, based on a PFM mode, to drive White LED. The current

mode regulation allows a uniform brightness of the LEDs. The chip

has been optimized for small ceramic capacitors, capable to supply

up to 1.0 W output power.

Features

• 2.7 to 5.5 V Input Voltage Range

• V

to 24 V Output Compliance Allows up to 5 LEDs Drive in

out

Series

• Built−in Overvoltage Protection

• Full EMI Immunity

• Inductor Based Converter brings up to 90% Efficiency

• Constant Output Current Regulation

• 0.3 mA Standby Quiescent Current

• Includes Dimming Function (PWM)

• Enable Function Driven Directly from Low Battery Voltage Source

• Automatic LEDs Current Matching

• Thermal Shutdown Protection

• All Pins are Fully ESD Protected

• Low EMI Radiation

• Pb−Free Package is Available

http://onsemi.com

TSOP−5

5

SN SUFFIX

CASE 483

1

DBN = Specific Device Code

A = Assembly Location

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

PIN CONNECTIONS

1

V

out

2GND

FB

3EN

5

4

MARKING

DIAGRAM

5

DBNAYWG

G

1

V

bat

Typical Applications

• LED Display Back Light Control

• Keyboard Back Light

• High Efficiency Step Up Converter

(Top View)

ORDERING INFORMATION

Device Package Shipping†

NCP9003SNT1G TSOP−5

(Pb−Free)

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

3000 Tape & Reel

© Semiconductor Components Industries, LLC, 2006

August, 2006 − Rev. 1

1 Publication Order Number:

NCP9003/D

NCP9003

GND

R1

15 W

V

bat

U1

4

EN

V

bat

V

bat

5

22 mH

2

GNDGND

3

FB

1

V

out

NCP9003

D6

LWT67CD5LWT67CD4LWT67CD3LWT67CD2LWT67C

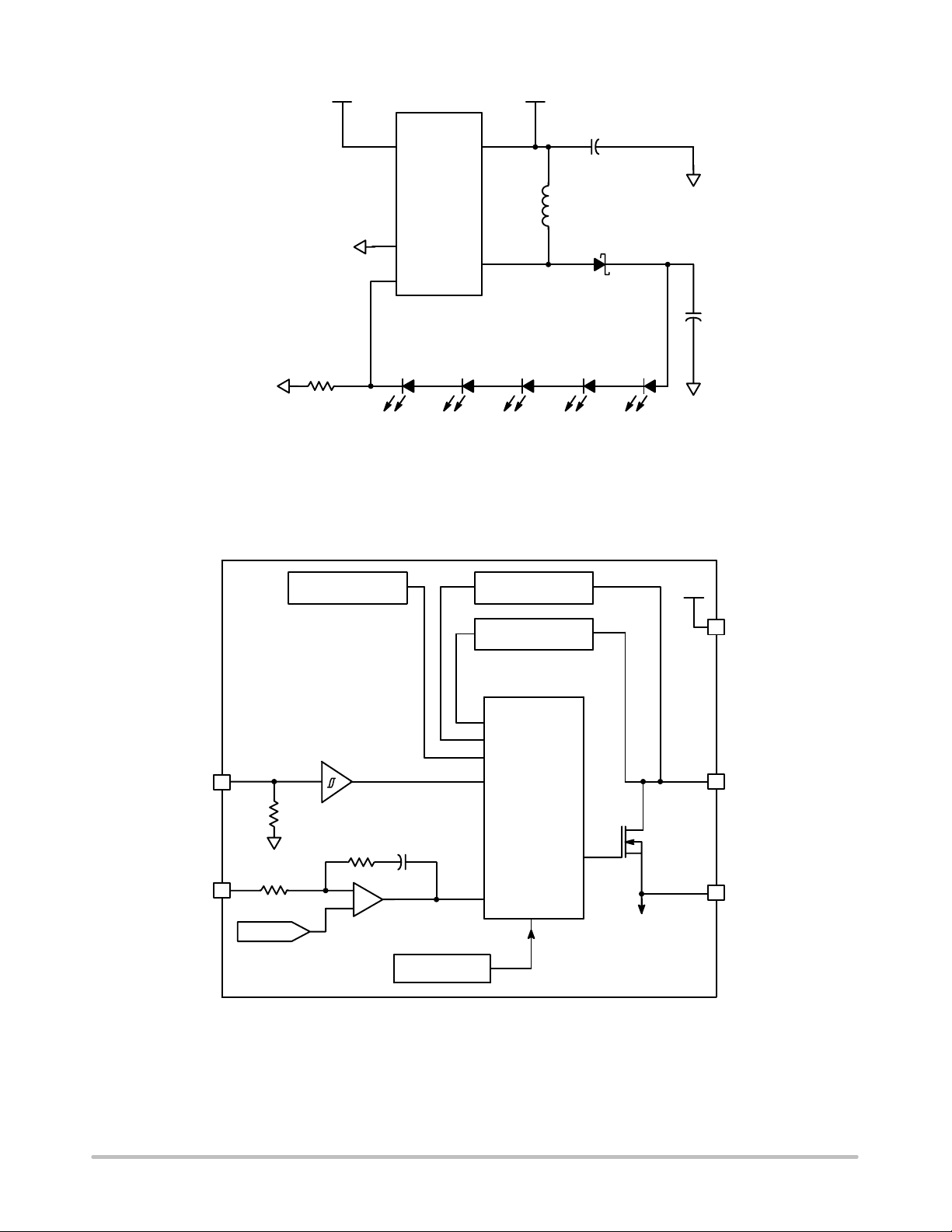

Figure 1. Typical Application

C1

4.7 mF

L1

D1

MBR0530

GND

C2

1.0 mF

GND

EN

FB

4

3

GND

300 k

+200 mV

Thermal Shutdown Current Sense

V

sense

100 k

CONTROLLER

−

+

Band Gap

Figure 2. Block Diagram

GND

Q1

V

bat

5

V

bat

1

V

out

2

GND

http://onsemi.com

2

NCP9003

PIN FUNCTION DESCRIPTION

Pin Pin Name Type Description

1 V

2 GND POWER This pin is the system ground for the NCP9003 and carries both the power and

3 FB ANALOG INPUT This pin provides the output current range adjustment by means of a sense

4 EN DIGITAL INPUT This is an Active−High logic input which enables the boost converter. The built−in

5 V

out

bat

POWER This pin is the power side of the external inductor and must be connected to the

POWER The external voltage supply is connected to this pin. A high quality reservoir

external Schottky diode. It provides the output current to the load. Since the boost

converter operates in a current loop mode, the output voltage can range up to

+24 V but shall not extend this limit. However, if the voltage on this pin is higher

than the Over Voltage Protection threshold (OVP) the device comes back to

shutdown mode. To restart the chip, one must either send a Low to High

sequence on Pin EN, or switch off the V

the output voltage to avoid false triggering of the OVP circuit. This capacitor

should be 1.0 mF minimum. Ceramic type, (ESR <100 mW), is mandatory to

achieve the high end efficiency. This capacitor limits the noise created by the fast

transients present in this circuitry. In order to limit the inrush current and to

operate with an acceptable start−up time, it is recommended to use any value

between 1.0 mF and 8.2 mF capacitor maximum. Care must be observed to avoid

EMI through the PCB copper tracks connected to this pin.

the analog signals. High quality ground must be provided to avoid spikes and/or

uncontrolled operation. Care must be observed to avoid high−density current flow

in a limited PCB copper track. Ground plane technique is recommended.

resistor connected to the analog control or with a PWM control. The dimming

function can be achieved by applying a PWM voltage technique to this pin (see

Figure 29). The current output tolerance depends upon the accuracy of this

resistor. Using a "5% metal film resistor or better, yields a good enough output

current accuracy.

Note: A built−in comparator switch OFF the DC/DC converter if the voltage

sensed across this pin and ground is higher than 700 mV (typical).

pull down resistor disables the device when the EN pin is left open. The LED

brightness can be controlled by applying a pulse width modulated signal to the

enable pin (see Figure 31).

capacitor must be connected across Pin 1 and Ground to achieve the specified

output voltage parameters. A 4.7 mF/6.3 V, low ESR capacitor must be connected

as close as possible across Pin 5 and ground Pin 2. The X5R or X7R ceramic

MURATA types are recommended. The return side of the external inductor shall

be connected to this pin. Typical application will use a 22 mH, size 1008, to handle

the 1.0 to 100 mA max output current range. On the other hand, when the desired

output current is above 20 mA, the inductor shall have an ESR < 1.5 W to achieve

a good efficiency over the V

bat

range.

supply. A capacitor must be used on

bat

http://onsemi.com

3

NCP9003

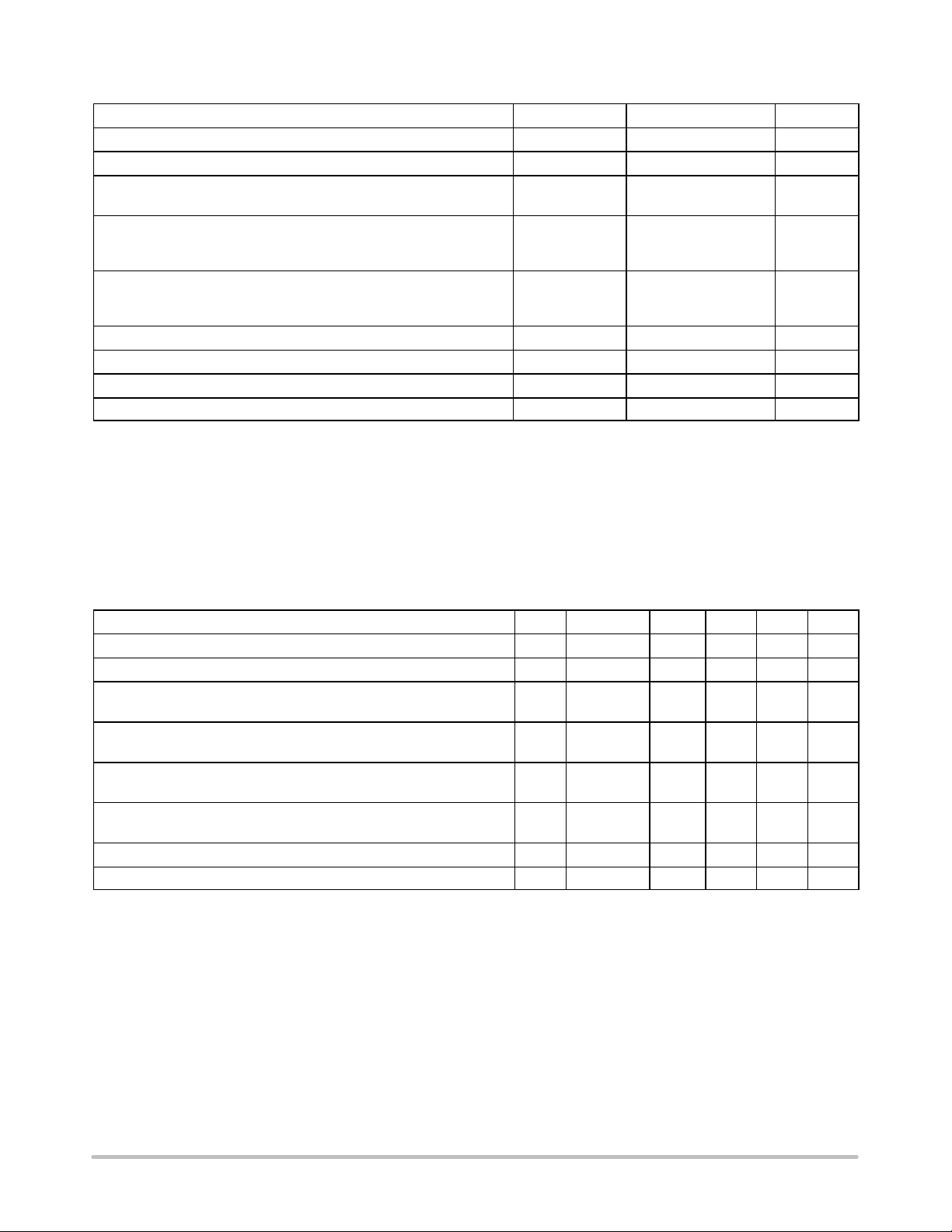

MAXIMUM RATINGS

Rating Symbol Value Unit

Power Supply V

Output Power Supply Voltage Compliance V

Digital Input Voltage

bat

out

EN −0.3 < Vin < V

Digital Input Current

ESD Capability (Note 1)

V

ESD

Human Body Model (HBM)

Machine Model (MM)

TSOP−5 Package

Power Dissipation @ T

Thermal Resistance, Junction−to−Air

Operating Ambient Temperature Range T

Operating Junction Temperature Range T

Maximum Junction Temperature T

Storage Temperature Range T

= +85°C (Note 2)

A

P

R

Jmax

q

stg

D

JA

A

J

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the

Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

device reliability.

1. This device series contains ESD protection and exceeds the following tests:

Human Body Model (HBM) "2.0 kV per JEDEC standard: JESD22−A114

Machine Model (MM) "200 V per JEDEC standard: JESD22−A115

2. The maximum package power dissipation limit must not be exceeded.

3. Latch−up current maximum rating: "100 mA per JEDEC standard: JESD78.

4. Moisture Sensivity Level (MSL): 1 per IPC/JEDEC standard: J−STD−020A.

6.0 V

28 V

+ 0.3

bat

1.0

2.0

mA

kV

200

160

250

mW

°C/W

−25 to +85 °C

−25 to +125 °C

+150 °C

−65 to +150 °C

V

V

POWER SUPPLY SECTION (Typical values are referenced to T

= +25°C, Min & Max values are referenced −25°C to +85°C ambient

A

temperature, unless otherwise noted.)

Rating Pin Symbol Min Typ Max Unit

Power Supply 4 V

Output Load Voltage Compliance 5 V

Continuous DC Current in the Load @ V

ESR < 1.5 W, V

Stand By Current, @ I

Stand By Current, @ I

Inductor Discharging Time @ V

I

= 10 mA

out

= 3.60 V

bat

= 0 mA, EN = L, V

out

= 0 mA, EN = L, V

out

= 3.6 V, L = 22 mH, 3xLED,

bat

= 3xLED, L = 22 mH,

out

= 3.6 V 4 I

bat

= 5.5 V 4 I

bat

5 I

4 Toffmax − 320 − ns

Thermal Shutdown Protection − T

Thermal Shutdown Protection Hysteresis − T

bat

out

out

stdb

stdb

SD

SDH

2.7 − 5.5 V

21 24 − V

50 − − mA

− 0.3 − mA

− 0.8 3.0 mA

− 160 − °C

− 30 − °C

http://onsemi.com

4

NCP9003

ANALOG SECTION (Typical values are referenced to T

temperature, unless otherwise noted.)

Rating Pin Symbol Min Typ Max Unit

High Level Input Voltage

Low Level Input Voltage

EN Pull Down Resistor 4 R

Feedback Voltage Threshold 3 FB 185 200 225 mV

Output Current Stabilization Time Delay following a DC/DC Start−up,

@ V

= 3.60 V, L = 22 mH, I

bat

Internal Switch ON Resistor @ Tamb = +25°C 1 QR

5. The overall tolerance depends upon the accuracy of the external resistor.

= 20 mA

out

= +25°C, Min & Max values are referenced −25°C to +85°C ambient

A

4 EN 1.3

EN

1 I

outdly

DSON

−

− 100 − kW

− 100 − ms

− 1.7 − W

−

−

−

0.4

ESD PROTECTION

The NCP9003 includes silicon devices to protect the pins

against the ESD spikes voltages. To cope with the different

ESD voltages developed in the applications, the built−in

structures have been designed to handle "2.0 kVin Human

Body Model (HBM) and "200 V in Machine Model (MM)

on each pin.

means of a current loop, the output voltage will varies

depending upon the dynamic impedance presented by the

load.

Considering high intensity LED, the output voltage can

range from a low 6.40 V (two LED in series biased with a

low current), up to 21 V, the voltage compliance the chip

can sustain continuously.

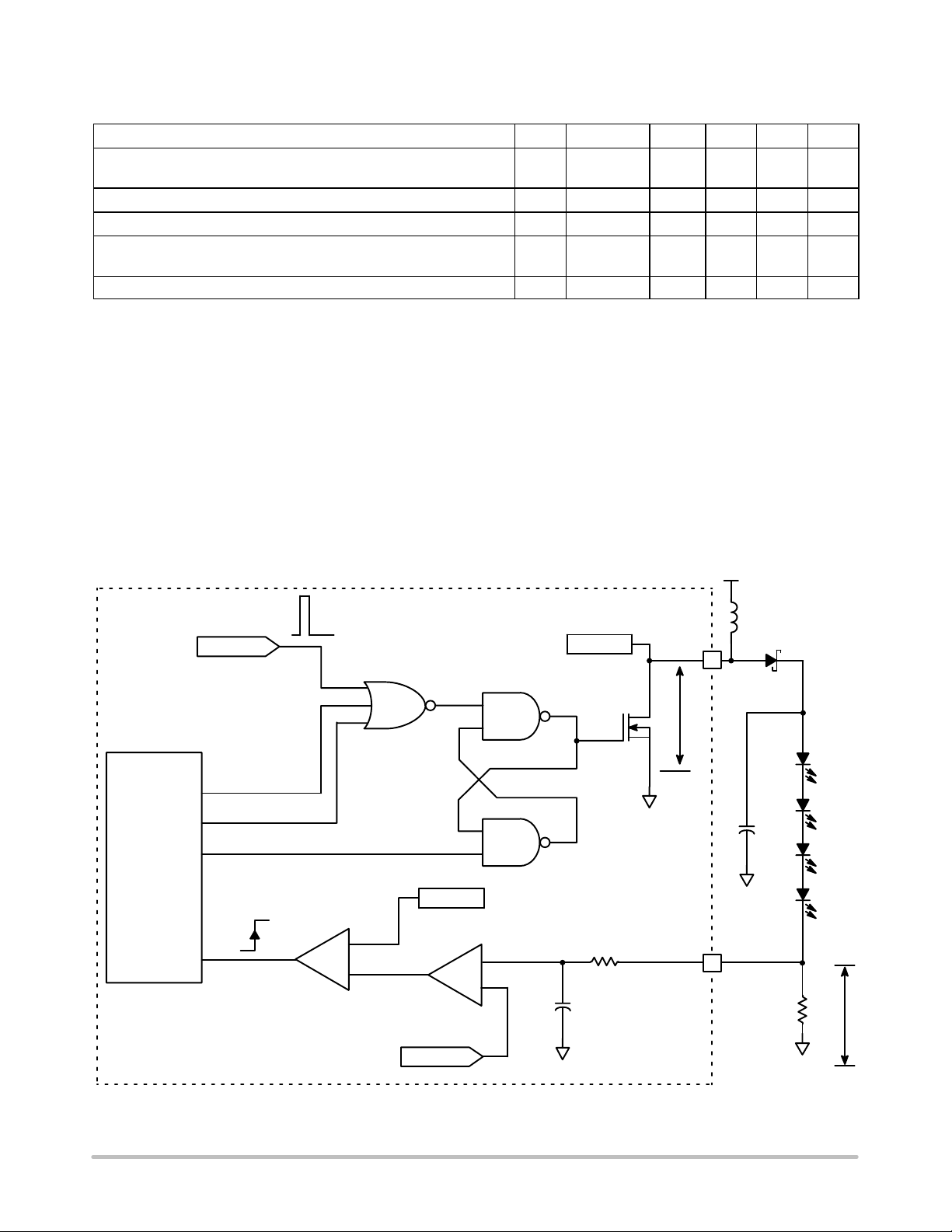

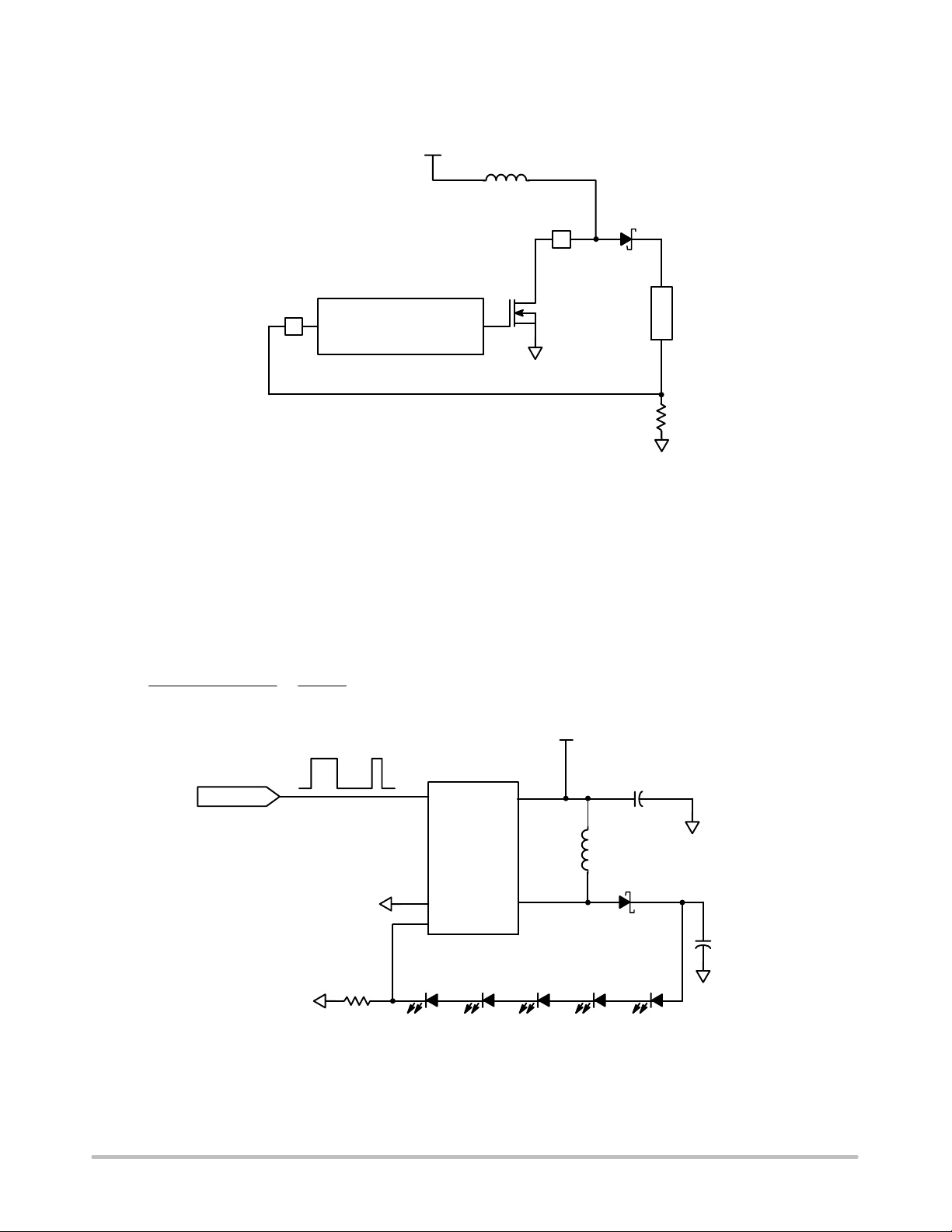

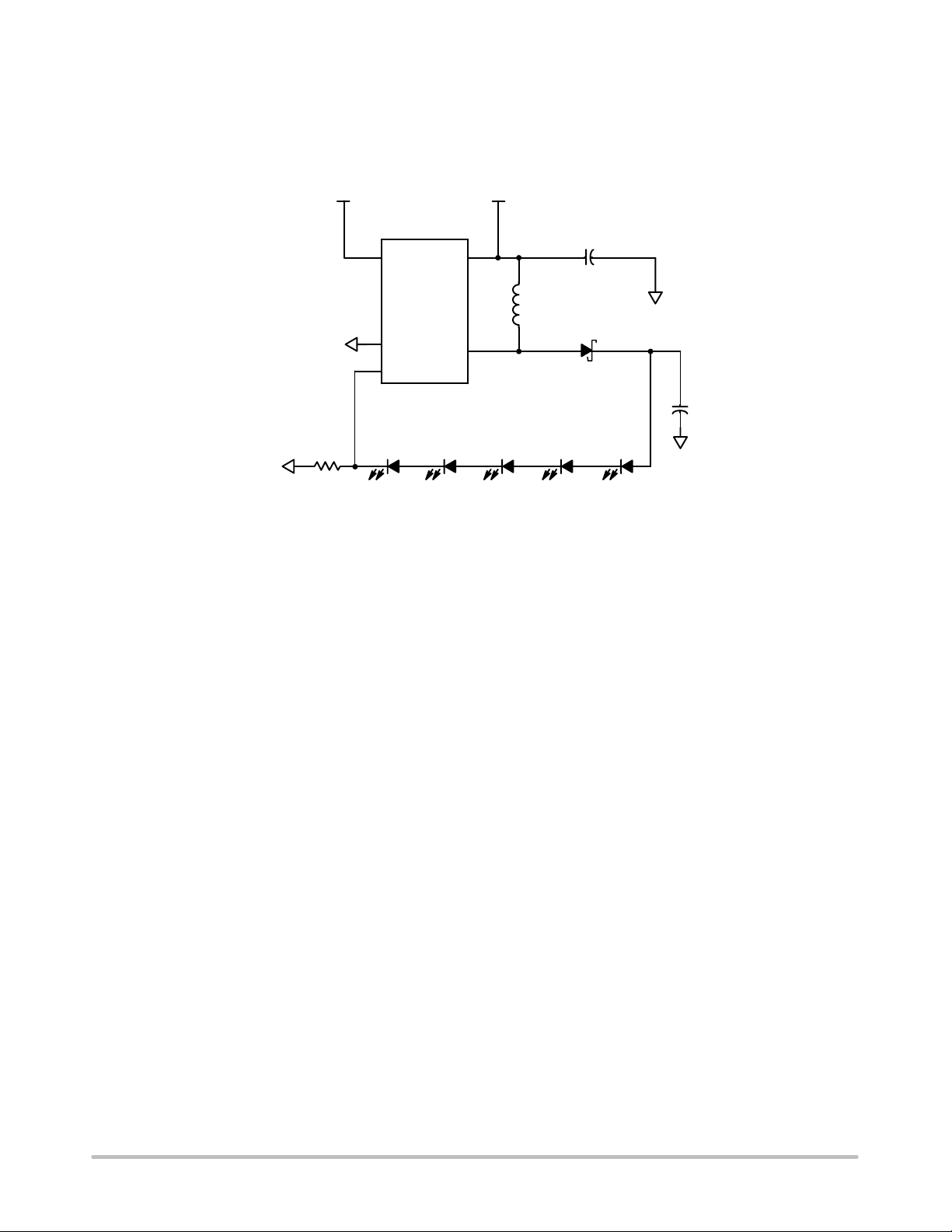

DC/DC OPERATION

The DC/DC converter is designed to supply a constant

current to the external load, the circuit being powered from

a standard battery supply. Since the regulation is made by

The basic DC/DC structure is depicted in Figure 3. With

a 28 V maximum rating voltage capability, the power

device can accommodate high voltage source without any

leakage current downgrading.

V

bat

V

V

LOGIC

CONTROL

POR

TIME_OUT

ZERO_CROSSING

RESET

L1

22 mH

Vd

sense

Q1

GND

Vd

sense

+

V(Ipeak)

−

−

+

C2

Vref

R1

GND

Vds

1

D1

1.0 mF

C1

GND

3

R2

xR

D5 D4 D3 D2

Vs

GND

Figure 3. Basic DC/DC Converter Structure

http://onsemi.com

5

NCP9003

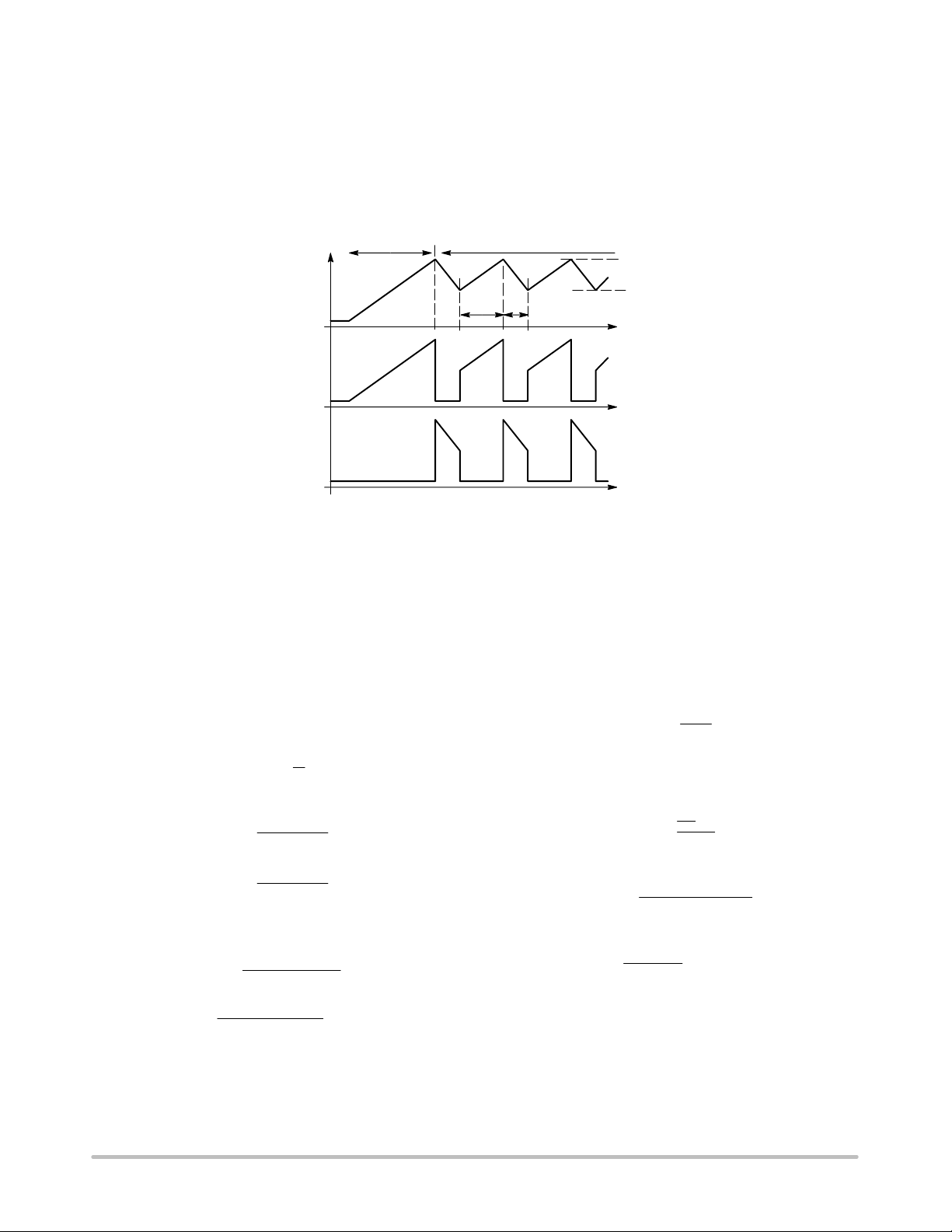

Basically, the chip operates with two cycles:

Cycle #1: time t1, the energy is stored into the inductor

Cycle #2: time t2, the energy is dumped to the load

The POR signal sets the flip−flop and the first cycle takes

place. When the current hits the peak value, defined by the

First Start−Up Normal Operation

I

L

0 mA

Ids

0 mA

Io

0 mA

Figure 4. Basic DC−DC Operation

error amplifier associated to the loop regulation, the

flip−flop resets, the NMOS is deactivated and the current

is dumped into the load. Since the timings depend on the

environment, the internal timer limits the toff cycle to

320 ns (typical), making sure the system operates in a

continuous mode to maximize the energy transfer.

Ipeak

Iv

t1 t2

t

t

t

Based on the data sheet, the current flowing into the

inductor is bounded by two limits:

• Ipeak Value: Internally fixed to 350 mA typical

• Iv Value: Limited by the fixed Toff time built in the

chip (320 ns typical)

The system operates in a continuous mode as depicted in

Figure 4 and t1 and t2 times can be derived from basic

equations. (Note: The equations are for theoretical analysis

only, they do not include the losses.)

dI

dt

(Ip * Iv) * L

V

bat

(Ip * Iv) * L

Vo * V

bat

Let V

= E, then:

bat

L + E*

t1 +

t2 +

Since t2 = 320 ns typical and Vo = 21 V maximum, then

(assuming a typical V

DImax +

= 3.0 V):

bat

t2 * (Vo * V

DI +

320 ns * (21−3.0)

L

22 mH

bat)

+ 261 mA

Of course, from a practical stand point, the inductor must

be sized to cope with the peak current present in the circuit

(eq. 1)

(eq. 2)

(eq. 3)

(eq. 4)

to avoid saturation of the core. On top of that, the ferrite

material shall be capable to operate at high frequency

(1.0 MHz) to minimize the Foucault’s losses developed

during the cycles.

The operating frequency can be derived from the

electrical parameters. Let V = Vo − V

, rearranging

bat

Equation 1:

ton +

dI * L

E

(eq. 5)

Since toff is nearly constant (according to the 320 ns

typical time), the dI is constant for a given load and

inductance value. Rearranging Equation 5 yields:

V*dt

*L

Let E = V

ton +

, and Vopk = output peak voltage, then:

bat

ton +

L

E

(Vopk * V

V

bat

bat

)*dt

(eq. 6)

(eq. 7)

Finally, the operating frequency is:

f +

1

ton ) toff

(eq. 8)

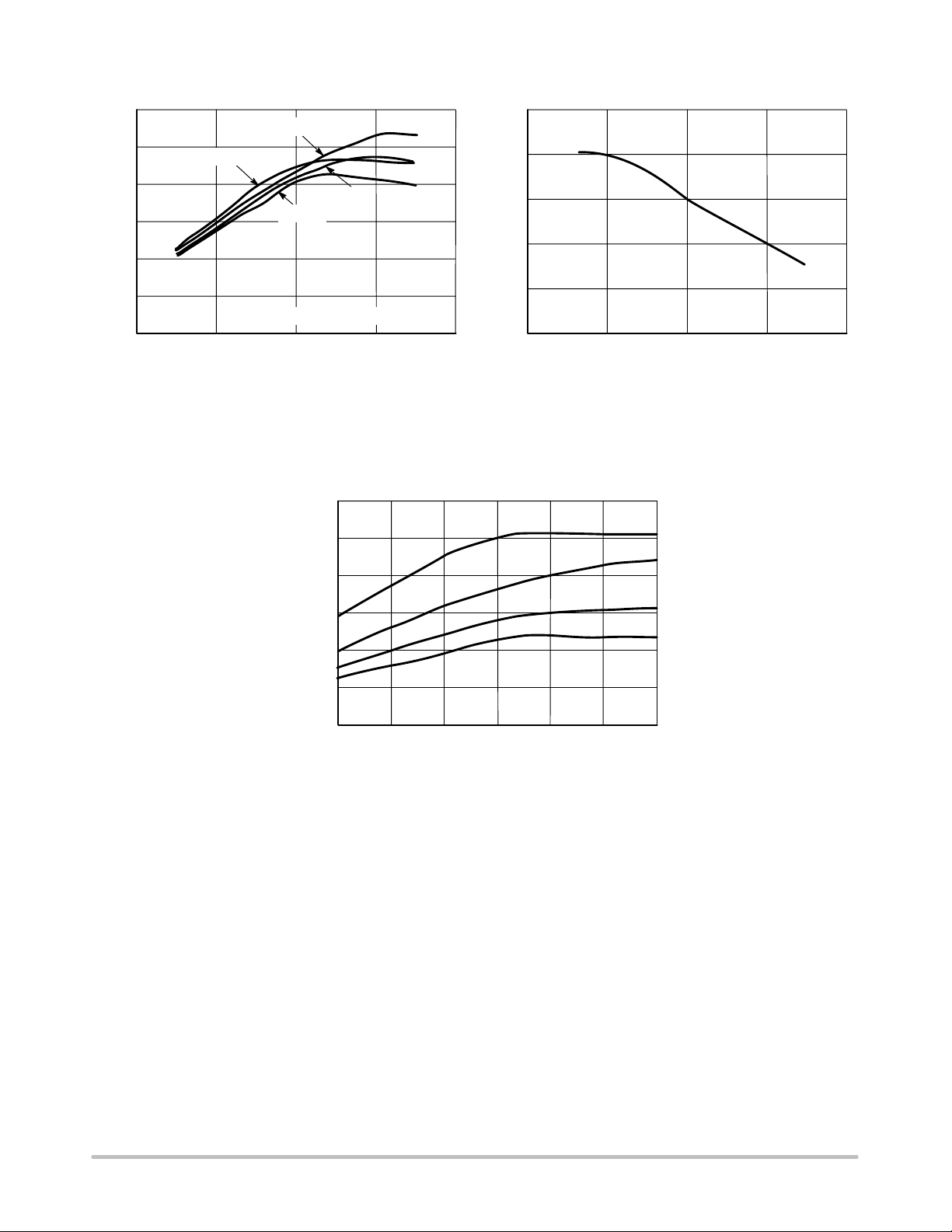

The output power supplied by the NCP9003 is limited to

one watt: Figure 5 shows the maximum power that can be

delivered by the chip as a function of the output voltage.

http://onsemi.com

6

1200

1000

P

out

2 LED

= f(V

NCP9003

) @ Rs = 2.0 W I

bat

400

3 LED

350

peak

= f(V

bat

) @ L

= 22 mH

out

800

600

(mW)

out

P

5 LED

4 LED

400

200

P

= f(V

bat

(V)

bat

) @ R

0

24

out

V

sense

= 2.0 W

53

Figure 5. Maximum Output Power as a Function of

the Battery Supply Voltage

120

100

80

60

(mA)

out

I

40

6

300

250

Ipeak (mA)

200

150

Test conditions: L = 22 mH, R

Figure 6. Typical Inductor Peak Current as a

2 LED

3 LED

4 LED

5 LED

V

bat

Function of V

432

(V)

= 10 W, Tamb = +20°C

sense

Voltage

bat

5

6

20

0

3.0 4.0 5.02.5 3.5 4.5 5.5

V

(V)

bat

Test conditions: L = 22 mH, R

= 2.0 W, Tamb = +25°C

sense

Figure 7. Maximum Output Current as a Function of V

bat

http://onsemi.com

7

NCP9003

Output Current Range Set−Up

The current regulation is achieved by means of an external sense resistor connected in series with the LED string.

V

bat

L1

22 mH

V

out

1

D1

FB

3

CONTROLLER

Figure 8. Output Current Feedback

The current flowing through the LED creates a voltage

drop across the sense resistor R1. The voltage drop is

constantly monitored internally, and maximum peak

current allowed in the inductor is set accordingly in order

to keep constant this voltage drop (and thus the current

flowing through the LED). For example, should one need

a 10 mA output current, the sense resistor should be sized

according to the following equation:

Feedback Threshold

R1+

I

out

200 mV

+

10 mA

+ 20 W

(eq. 9)

Q1

GND

Load

R1

xW

GND

A standard 5% tolerance resistor, 22 W SMD device,

yields 9.09 mA, good enough to fulfill the back light

demand. The typical application schematic diagram is

provided in Figure 9.

V

bat

Pulse

GND

U1

5

V

bat

V

out

GND

R1

22 W

4

EN

2 1

GND

3

FB

NCP9003

D6 D5 D4 D3

LWT67C LWT67C LWT67C LWT67C LWT67C

Figure 9. Basic Schematic Diagram

http://onsemi.com

8

4.7 mF

L1

22 mH

MBR0530

C1

D1

D2

GND

C2

1.0 mF

GND

NCP9003

Output Load Drive

In order to optimize the built−in Boost capabilities, one

shall operate the NCP9003 in the continuous output current

mode. Such a mode is achieved by using and external

reservoir capacitor (see Table 1) across the LED.

At this point, the peak current flowing into the LED

diodes shall be within the maximum ratings specified for

these devices. Of course, pulsed operation can be achieved,

due to the EN signal Pin 4, to force high current into the

LED when necessary.

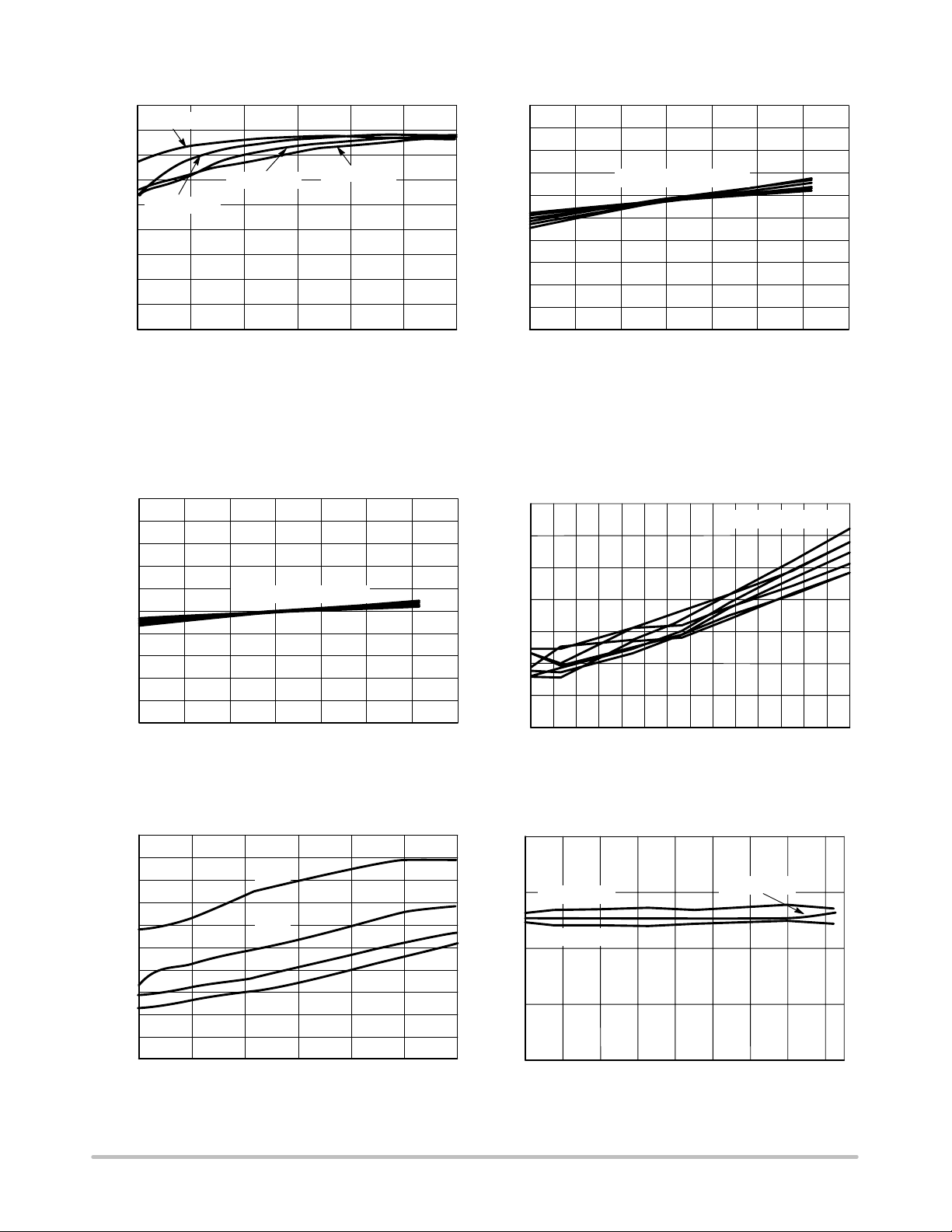

TYPICAL OPERATING CHARACTERISTICS

Yield = f(V

100

90

80

5 LED/4 mA

70

60

50

40

YIELD (%)

30

20

10

0

2.50 3.00 3.50 4.00 4.50 5.00 5.50

Figure 10. Overall Efficiency vs. Power Supply @

) @ I

bat

3 LED/4 mA

I

out

= 4.0 mA/L

out

4 LED/4 mA

2 LED/4 mA

V

(V) V

bat

= 4.0 mA, L = 22 mH

= 22 mH Yield = f(V

out

The Schottky diode D1, associated with capacitor C2

(see Figure 9), provides a rectification and filtering

function.

When a pulse−operating mode is acceptable:

• A PWM mode control can be used to adjust the output

current range by means of a resistor and a capacitor

connected across FB pin. On the other hand, the

Schottky diode can be removed and replaced by at

least one LED diode, keeping in mind such LED shall

sustain the large pulsed peak current during the

operation.

) @ I

100

90

80

70

2 LED/10 mA

60

50

40

YIELD (%)

30

20

10

0

2.50 3.00 3.50 4.00 4.50 5.00 5.50

bat

4 LED/10 mA

Figure 11. Overall Efficiency vs. Power Supply @

I

= 10 mA, L = 22 mH

out

= 10 mA/L

out

5 LED/10 mA

(V)

bat

= 22 mH

out

3 LED/10 mA

100

Yield = f(V

3 LED/15 mA

90

80

70

60

4 LED/15 mA

50

40

YIELD (%)

30

20

10

0

2.50 3.00 3.50 4.00 4.50

) @ I

bat

5 LED/15 mA

= 15 mA/L

out

Vbat (V)

= 22 mH Yield = f(V

out

2 LED/15 mA

Figure 12. Overall Efficiency vs. Power Supply @

= 15 mA, L = 22 mH

I

out

5.00

5.50

http://onsemi.com

) @ I

100

3 LED/20 mA

90

80

70

4 LED/20 mA

60

50

40

YIELD (%)

30

20

10

0

2.50 3.00 3.50 4.00 4.50 5.00 5.50

bat

5 LED/20 mA

= 20 mA/L

out

Vbat (V)

out

2 LED/20 mA

Figure 13. Overall Efficiency vs. Power Supply @

I

= 20 mA, L = 22 mH

out

9

= 22 mH

NCP9003

Yield = f(V

100

2 LED/40 mA

90

80

70

60

3 LED/40 mA

50

40

YIELD (%)

30

20

10

0

2.50 3.00 3.50 4.00 4.50 5.00 5.50

All curve conditions: L = 22 mH, Cin = 4.7 mF, C

) @ I

bat

4 LED/40 mA

Typical curve @ T° = +25°C

= 40 mA/L

out

V

(V)

bat

5 LED/40 mA

= 22 mH

out

= 1.0 mF,

out

Figure 14. Overall Efficiency vs. Power Supply @

= 40 mA, L = 22 mH

I

out

Feedback Variation vs. Nominal

= 3.0 V, 6.0 V, T = 255C)

(V

5

4

3

2

1

0

−1

−2

−3

FEEDBACK VARIATION (%)

−4

−5

−40 40−20 60 80

bat

V

= 3.1 V thru 5.5 V

bat

0 20 100

TEMPERATURE (°C)

Figure 16. Feedback Voltage Variation

Feedback Variation vs. Temperature

205

204

203

202

201

200

199

198

197

FEEDBACK VOLTAGE (mV)

196

195

−40 40−20 60 80

V

= 3.1 V thru 5.5 V

bat

0 20 100

TEMPERATURE (°C)

Figure 15. Feedback Voltage Stability

1.4

Standby Current vs. V

1.2

1.0

0.8

0.6

IStby (mA)

0.4

0.2

0.0

2.7

3.3 3.9 4.5 5.1

V

(V)

bat

bat

−40°C thru 125°C

Figure 17. Standby Current

5.5

Frequency = f(V

2.5

2.0

1.5

f (mHz)

1.0

0.5

0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

bat

2 LED

3 LED

4 LED

5 LED

) @ I

V

= 20 mA−L

out

(V)

bat

out

Figure 18. Typical Operating Frequency

= 22 mH OVP vs. Temperature

26

V

V

V

= 2.7 V

bat

= 5.5 V

bat

0 100

25

24

23

OVERVOLTAGE PROTECTION (V)

22

−40

40 80

20 130−20 60 120

TEMPERATURE (°C)

bat

Figure 19. Overvoltage Protection

http://onsemi.com

10

= 3.6 V

NCP9003

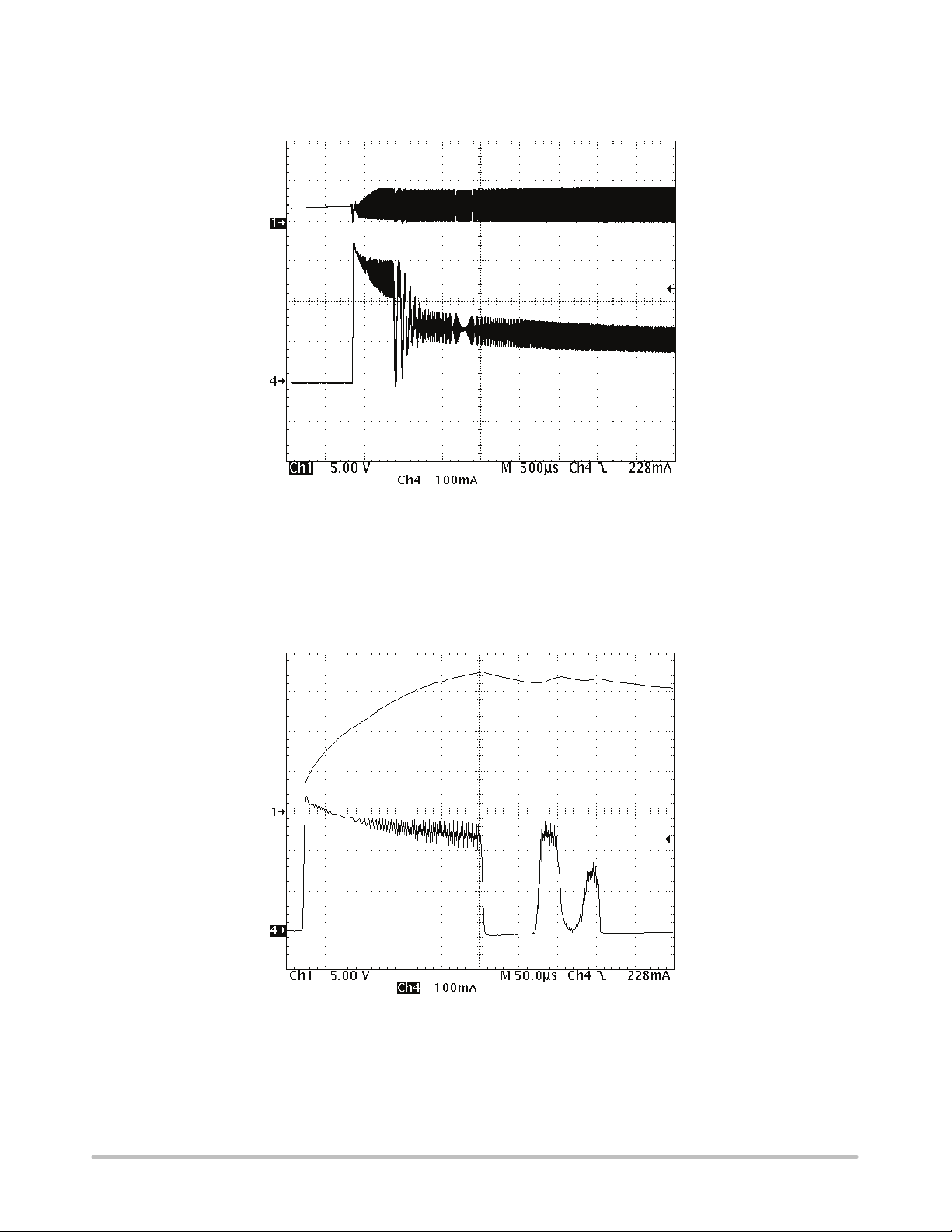

TYPICAL OPERATING WAVEFORMS

V

out

Inductor

Current

Conditions: V

= 3.6 V, L

bat

= 22 mH, 5 LED, I

out

Figure 20. Typical Power Up Response

V

load

Inductor

Current

= 15 mA

out

Conditions: V

= 3.6 V, L

bat

= 22 mH, 5 LED, I

out

= 15 mA

out

Figure 21. Typical Start−Up Inductor Current and Output Voltage

http://onsemi.com

11

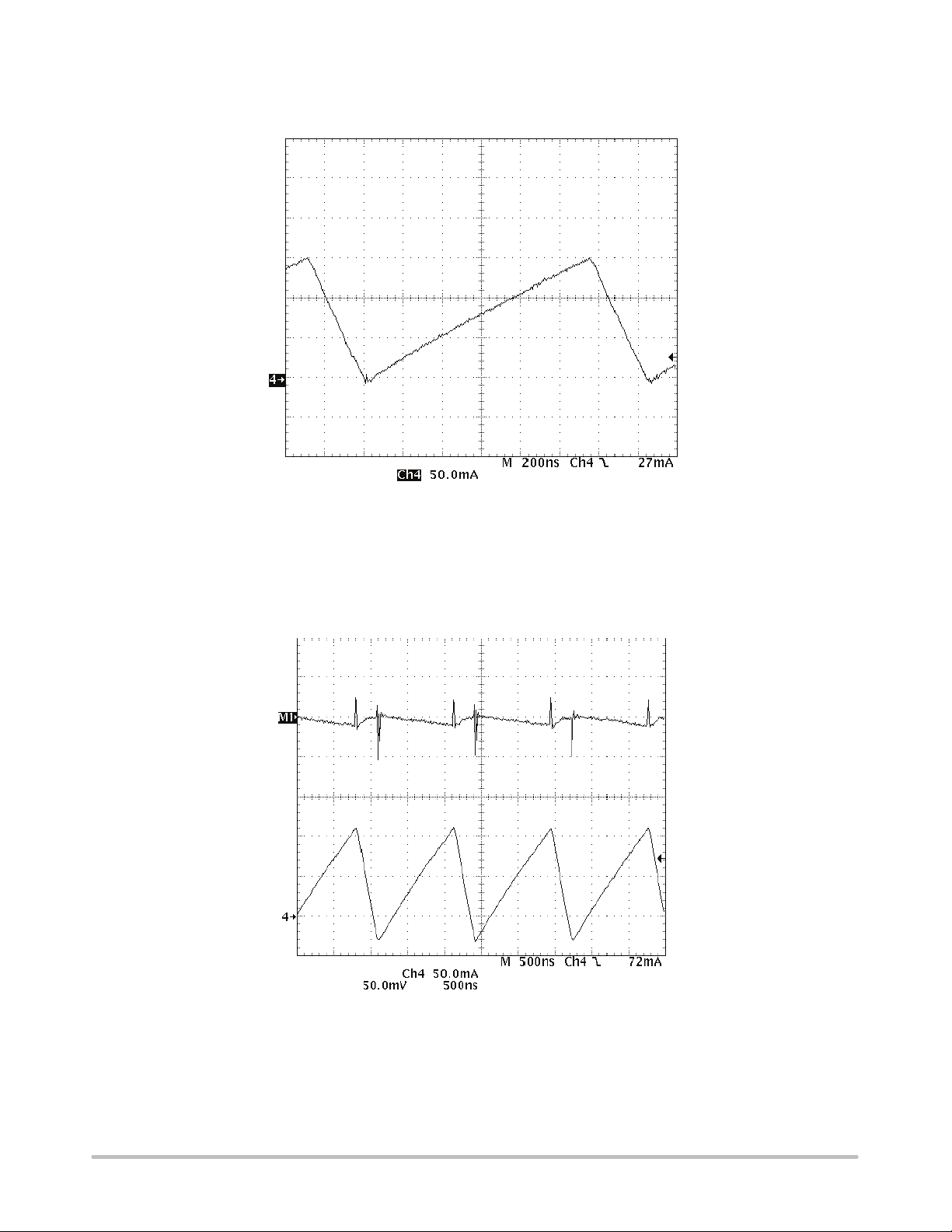

NCP9003

TYPICAL OPERATING WAVEFORMS

Inductor

Current

Conditions: V

= 3.6 V, L

bat

= 22 mH, 5 LED, I

out

Figure 22. Typical Inductor Current

= 15 mA

out

V

Ripple

load

50 mV/div

Inductor

Current

Conditions: V

= 3.6 V, L

bat

= 22 mH, 5 LED, I

out

= 15 mA

out

Figure 23. Typical Output Load Voltage Ripple

http://onsemi.com

12

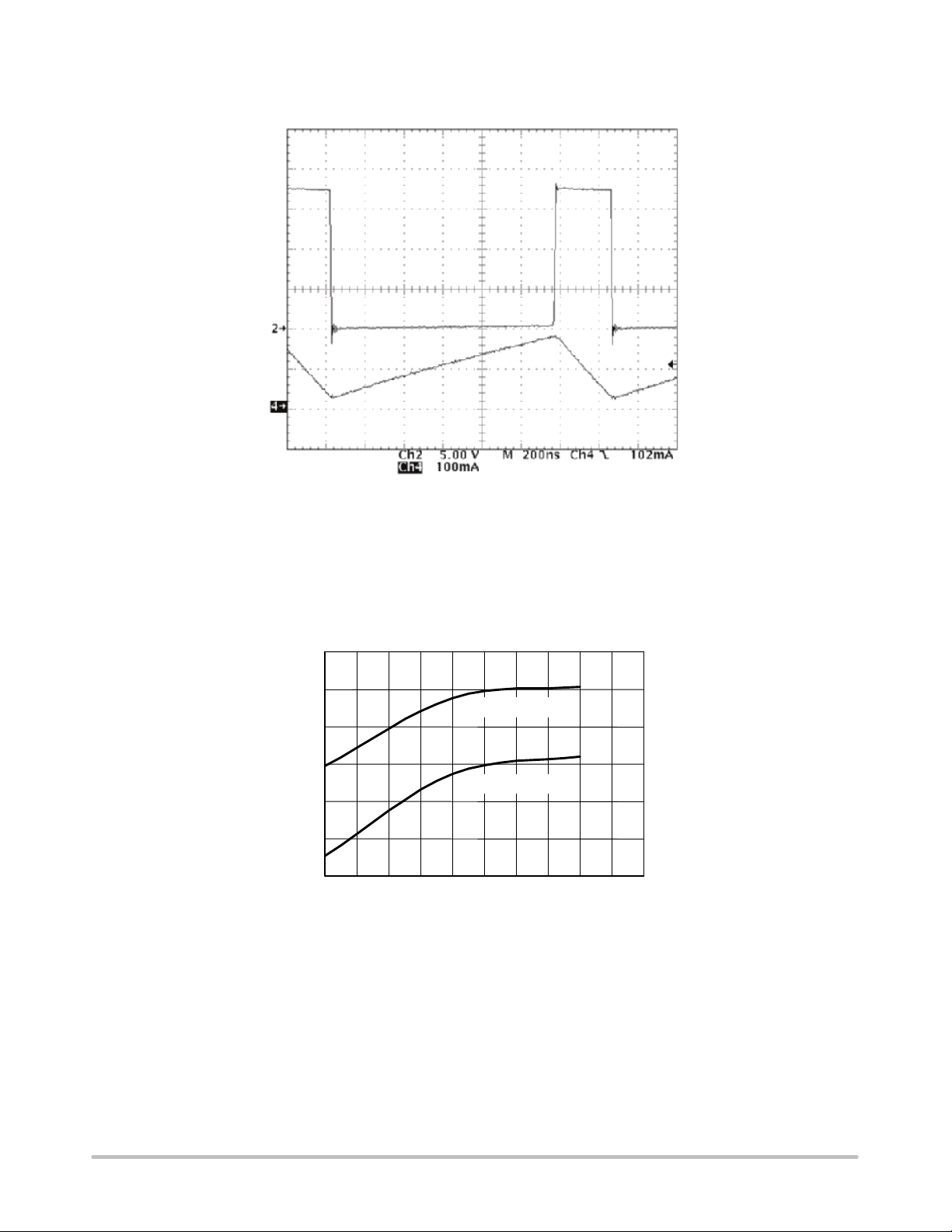

NCP9003

TYPICAL OPERATING WAVEFORMS

Output Voltage

Inductor Current

Test Conditions: L = 22 mH, I

= 15 mA, V

out

= 3.6 V, Ambient Temperature

bat

Figure 24. Typical Output Peak Voltage

92.00

90.00

88.00

86.00

84.00

EFFICIENCY (%)

82.00

80.00

78.00

3 3.5 4 4.5 5 5.5

NCP9003: Efficiency = f(ESR) @ 5 LED, ILed = 20 mA

ESR = 0.3 W

ESR = 1.3 W

V

(V)

bat

Figure 25. Efficiency as a Function of V

http://onsemi.com

13

and Inductor ESR

bat

10.00

1.00

0.10

NOISE (mV/SQR/Hz)

NCP9003

0.01

10001001010.1

FREQUENCY (MHz)

Figure 26. Noise Returned to the Battery

Test Conditions: V

= 3.6 V, I

bat

= 20 mA, string of 3 LED (OSRAM LWT67C)

out

Figure 27. Relative EMI Over 100 kHz − 30 MHz Bandwidth

http://onsemi.com

14

TYPICAL APPLICATIONS CIRCUITS

Standard Feedback

The standard feedback provides a constant current to the

LED, independently of the V

supply and number of LED

bat

NCP9003

associated in series. Figure 28 depicts a typical application

to supply 13 mA to the load.

V

bat

U1

4

GND

GND

R1

15 W

EN

2

GND

3

FB

NCP9003

D6 D5 D4 D3

LWT67C

V

V

LWT67C LWT67C LWT67C LWT67C

Figure 28. Basic DC Current Mode Operation with Analog Feedback

PWM Operation

The analog feedback Pin 3 provides a way to dim the

LED by means of an external PWM signal as depicted in

Figure 29. By optimizing the internal high impedance

presented by the FB pin, one can set up a simple R/C

network to accommodate such a dimming function. Two

modes of operation can be considered:

• Pulsed mode, with no filtering

• Averaged mode with filtering capacitor

Although the pulsed mode will provide a good dimming

function, from a human eye standpoint, it will continuously

bat

out

V

bat

5

L1

22 mH

1

C1

4.7 mF

D1

MBR0530

D2

GND

C2

1.0 mF

GND

start and stop the converter, yielding high transients . These

transients might generate spikes difficult to filter out in the

rest of the application, a situation not recommended. The

output current depends upon the duty cycle of the signal

presented to the node Pin 3: this is very similar to the digital

control discussed in Figure 31.

The average mode yields a noise free operation since the

converter operates continuously, together with a very good

dimming function. The cost is an extra resistor and one

extra capacitor, both being low cost parts.

http://onsemi.com

15

NCP9003

V

bat

Average Network

R2

PWM

150 k

C3

100 nF

GND

GND

NOTE: RC filter R2 and C3 is optional (see text)

R3

10 k

GND GND

R4

5.6 k

R1

10 W

Figure 29. Basic DC Current Mode Operation with PWM Control

To implement such a function, let consider the feedback

input as an operational amplifier with a high impedance

input (reference schematic Figure 29). The analog loop

will keep going to balance the current flowing through the

sense resistor R1 until the feedback voltage is 200 mV. An

extra resistor (R4) isolates the FB node from low resistance

to ground, making possible to add an external voltage to

this pin.

The time constant R2/C3 generates the voltage across C3,

added to the node Pin 1, while R2/R3/R4/R1/C3 create the

discharge time constant. In order to minimize the pick up

noise at FB node, the resistors shall have relative medium

V

bat

U1

4

EN

2

3

FB

NCP9003

D6 D5 D4 D3 D2

LWT67C LWT67C LWT67C LWT67C LWT67C

Sense Resistor

5

V

bat

L1

22 mH

1

V

out

C1

4.7 mF

D1

MBR0530

GND

value, preferably well below 1.0 MW. Consequently, let R2 =

150 k, R3 = 10 k and R4 = 5.6 k. On the other hand, the

feedback delay to control the luminosity of the LED shall be

acceptable by the user, 10 ms or less being a good

compromise. The time constant can now be calculated based

on a 400 mV offset voltage at the C3/R2/R3 node to force

zero current to the LED. Assuming the PWM signal comes

from a standard gate powered by a 3.0 V supply, running at

10 kHz, then a full dimming of the LED can be achieved with

a 95% span of the Duty Cycle signal. Figure 30 depicts the

behavior under such PWM analog mode.

C2

1.0 mF

GND

Figure 30. Operation with Analog PWM, f = 10 kHz, DC = 25%

http://onsemi.com

16

PWM

VFB

VPWM

NCP9003

Digital Control

Due to the EN pin, a digitally controlled luminosity can

be implemented by providing a PWM signal to this pin (see

Figure 31). The output current depends upon the Duty

U1

Pulse

GND

R1

GND

22 W

NOTE: Pulse width and frequency depends upon the application constraints.

Figure 31. Typical Semi−Pulsed Mode of Operation

4

EN

2

GND

3

FB

NCP9003

D6 D5 D4 D3 D2

LWT67C LWT67C LWT67C LWT67C LWT67C

Cycle, but care must be observed as the DC/DC converter

is continuously pulsed ON/OFF and noise are likely to be

generated.

V

bat

5

V

bat

L1

22 mH

1

V

out

C1

4.7 mF

D1

MBR0530

GND

V

load

C2

1.0 mF

GND

The PWM operation, using the EN pin as a digital

control, is depicted in Figures 32 and 33. The tests have

Figure 32. Operation @ PWM = 10 kHz, DC = 10%

been carried out at room temperature with V

L = 22 mH, five LEDs in series, RFB = 22 W.

PWM

V

load

VFB

VPWM

= 3.60 V,

bat

http://onsemi.com

17

NCP9003

Figure 33. Operation @ PWM = 10 kHz, DC = 25%

PWM

V

load

VFB

PWR CLK

Figure 34. Magnified View of Operation @ PWM = 10 kHz, DC = 25%

PWM

V

load

PWR CLK

http://onsemi.com

18

NCP9003

10.00

9.00

8.00

7.00

6.00

5.00

(mA)

out

I

4.00

3.00

2.00

1.00

0.00

0 20 40 60 80 100 120

NCP9003 I

Digital EN

= f(PWM) @ f = 10 kHz

out

Analog PWM

DC (%)

Figure 35. Output Current as a Function of the Operating Condition

Table 1. Recommended Passive Parts

Part Manufacturer Description Part Number

Ceramic Capacitor 1.0 mF/16 V MURATA GRM42 − X7R GRM42−6X7R−105K16

Ceramic Capacitor 1.0 mF/25 V MURATA GRM42 – X5R GRM

Ceramic Capacitor 4.7 mF/6.3 V MURATA GRM40 – X5R GRM40−X5R−475K6.3

Inductor 22 mH CoilCraft 1008PS − Shielded 1008PS−223MC

Inductor 22 mH CoilCraft Power Wafer LPQ4812−223KXC

Inductor 22 mH WURTH Power Choke 744031220

Inductor 22 mH TDK Power Inductor VLP4614T−220MR40

http://onsemi.com

19

NCP9003

Typical LEDs Load Mapping

Since the output power is voltage battery limited (see

Figure 5), one shall arrange the LED to cope with a specific

need. In particular, since the power cannot extend 600 mW

under realistic battery supply, powering ten LED can be

achieved by a series/parallel combination as depicted in

Figure 36.

Load

50 mA

D1

LED

D2

LED

D3

14 V (Typ.)

Sense

Resistor

Test conditions: V

LED

D4

LED

GND

R1

3.9 W

bat

L

out

C

out

D5

LED

D6

LED

D7

LED

D8

LED

= 3.6 V

= 22 mH

= 1.0 mF

Load

Load

75 mA

7.0 V (Typ.)

60 mA

10.5 V (Typ.)

D1

LED

D2

LED

Resistor

D1

LED

D2

LED

D3

LED

Sense

D3

LED

D4

LED

D4

LED

D5

LED

D6

LED

GND

D5

LED

D6

LED

R1

2.7 W

D7

LED

D8

LED

D9

LED

D7

LED

D8

LED

D10

LED

D11

LED

D12

LED

D9

LED

D10

LED

D13

LED

D14

LED

D15

LED

Sense

Resistor

Figure 36. Examples of Possible LED Arrangements

R1

3.3 W

GND

http://onsemi.com

20

S1

3

2

1

ENABLE

J1

VBAT

J2

GROUND

V

bat

GND

EN

GND

TP2

FB

GND

1 mF/10 V

GND

C1

FB

NCP9003

U1

4

EN

V

2

GND

3

V

FB

NCP9003

bat

out

V

bat

JP1

Isense

C3

GND

1 mF/6.3 V

5

L1

22 mH

V

1

out

D1

MBR0530

TP3

V

out

I

out

1 mF/25 V

C2

TP4

V

SW

GND

LW E67CD3LW E67CD4LW E67CD5LW E67C

D2

GND

Z1

GND

R1

51R

Note: Use Jumper JP2 to JP3 to adjust the number of LED in the operating string

Figure 37. NCP9003 Demo Board Schematic Diagram

2

JP2

JUMP_6

1

2

JP3

JUMP_6

1

http://onsemi.com

21

0.05 (0.002)

S

H

D

54

123

L

G

A

NCP9003

PACKAGE DIMENSIONS

TSOP−5

SN SUFFIX

CASE 483−02

ISSUE C

B

C

K

NOTES:

1. DIMENSIONING AND TOLERANCING PER

ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. MAXIMUM LEAD THICKNESS INCLUDES

LEAD FINISH THICKNESS. MINIMUM LEAD

THICKNESS IS THE MINIMUM THICKNESS

OF BASE MATERIAL.

4. A AND B DIMENSIONS DO NOT INCLUDE

MOLD FLASH, PROTRUSIONS, OR GATE

BURRS.

DIM MIN MAX MIN MAX

A 2.90 3.10 0.1142 0.1220

B 1.30 1.70 0.0512 0.0669

J

M

C 0.90 1.10 0.0354 0.0433

D 0.25 0.50 0.0098 0.0197

G 0.85 1.05 0.0335 0.0413

H 0.013 0.100 0.0005 0.0040

J 0.10 0.26 0.0040 0.0102

K 0.20 0.60 0.0079 0.0236

L 1.25 1.55 0.0493 0.0610

M 0 10 0 10

__ _ _

S 2.50 3.00 0.0985 0.1181

INCHESMILLIMETERS

SOLDERING FOOTPRINT*

1.9

0.95

0.037

1.0

0.039

*For additional information on our Pb−Free strategy and soldering

details, please download the ON Semiconductor Soldering and

Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice

to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any

liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental

damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over

time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under

its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body,

or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death

may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees,

subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of

personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part.

SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

0.074

0.028

0.7

2.4

0.094

SCALE 10:1

mm

ǒ

inches

Ǔ

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada

Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800−282−9855 Toll Free

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81−3−5773−3850

http://onsemi.com

22

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative

NCP9003/D

Loading...

Loading...