NB7V33MMNGEVB

NB7V33MMNG

Evaluation Board

User's Manual

Introduction

ON Semiconductor has developed the QFN16EVB

evaluation board for its high-performance devices packaged

in the 16-pin QFN. This evaluation board was designed to

provide a flexible and convenient platform to quickly

evaluate, characterize and verify the operation of various

ON Semiconductor products. Many QFN16EVBs are

dedicated with a device already installed, and can be ordered

from www.onsemi.com at the specific device web page.

This evaluation board manual contains:

Information on 16-lead QFN Evaluation Board

Assembly Instructions

Appropriate Lab Setup

Bill of Materials

This user’s manual provides detailed information on

board contents, layout and its use. It should be used in

conjunction with an appropriate ON Semiconductor device

datasheet located at www.onsemi.com. The datasheet

contains the technical device specifications.

http://onsemi.com

EVAL BOARD USER’S MANUAL

Board Layout

The QFN16 Evaluation Board provides a high bandwidth,

50 W controlled impedance environment and is

implemented in four layers. The first layer or primary trace

layer is 0.008 thick Rogers RO4003 material, and is

designed to have equal electrical length on all signal traces

from the device under test (DUT) pins to the SMA

connectors. The second layer is the 1.0 oz copper ground

plane and is primarily dedicated for the SMA connector

ground plane. FR4 dielectric material is placed between the

second and third layers and between third and fourth layers.

The third layer is also 1.0 oz copper plane. A portion of this

layer is designated for the device V

planes. The fourth layer is the secondary trace layer.

and DUTGND power

CC

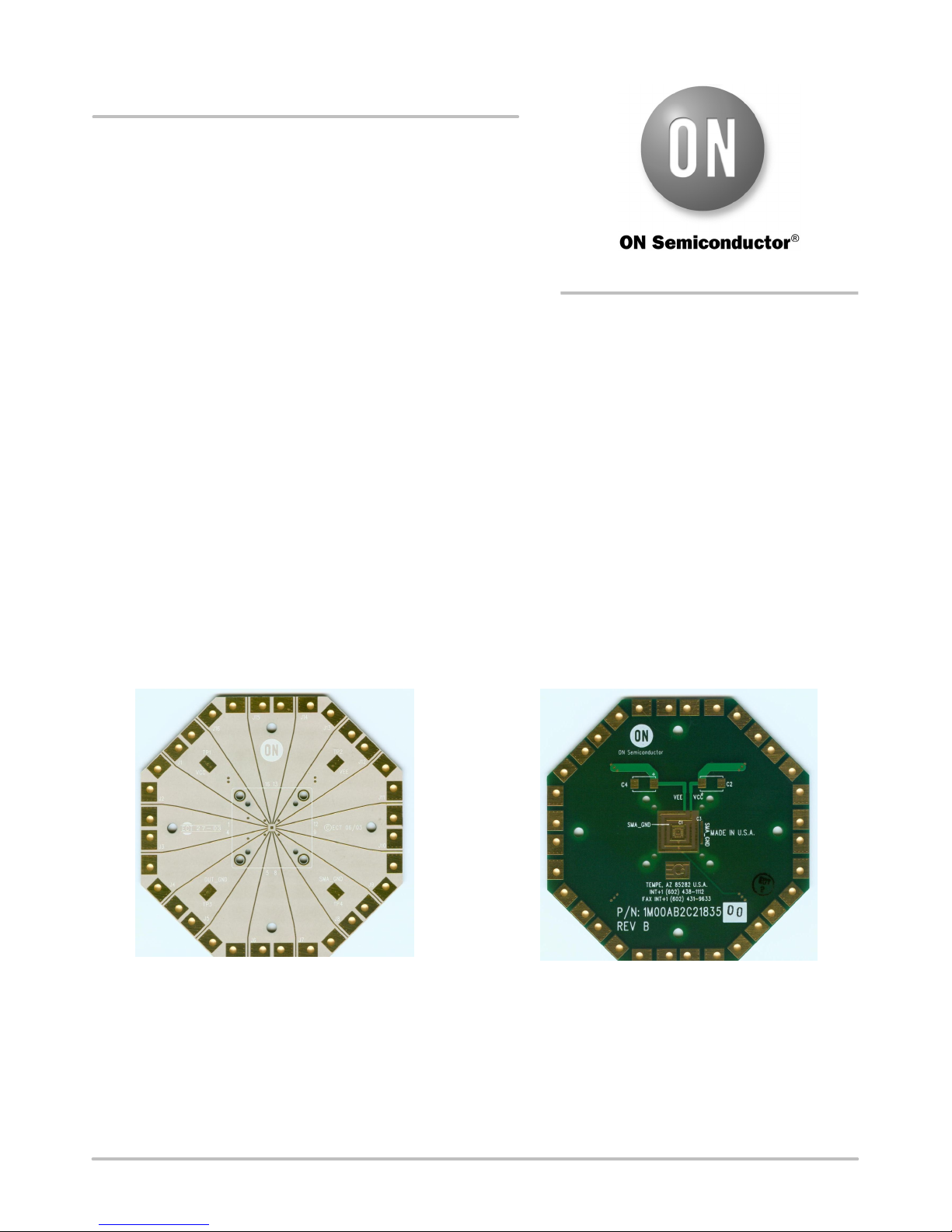

Top View Bottom View

Figure 1. Top and Bottom View of the 16 QFN Evaluation Board

Semiconductor Components Industries, LLC, 2013

May, 2013 − Rev. 0

1 Publication Order Number:

EVBUM2187/D

NB7V33MMNGEVB

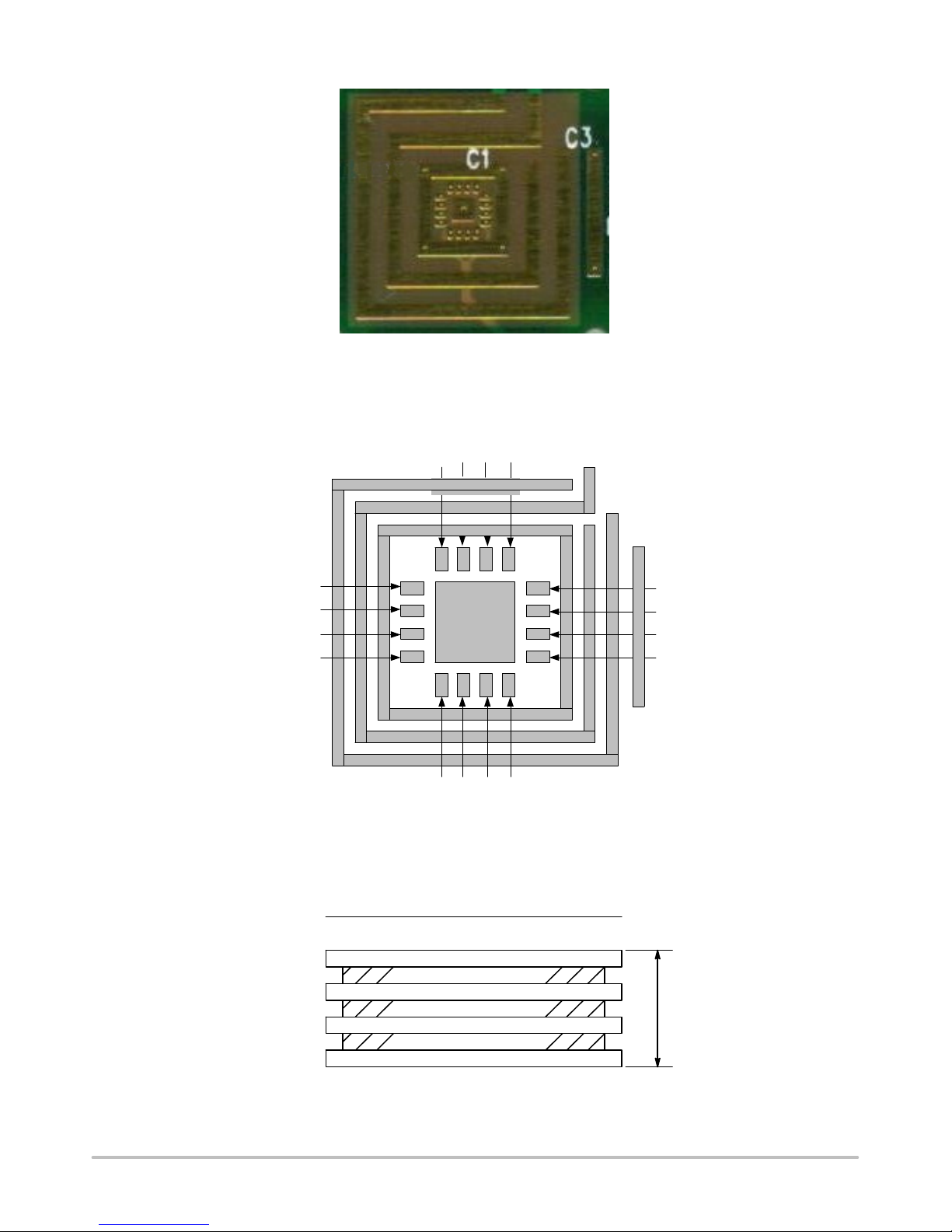

Figure 2. Enlarged Bottom View

Pin 13

Pin 14

Pin 15

Pin 16

VEE/DUTGND

VCC

SMA_GND

Pin 12

Pin 11

Pin 10

Pin 9

DUT_GND

Pin 8

Pin 7

Pin 6

Pin 5

Figure 3. Enlarged Bottom View of the Evaluation Board

SILKSCREEN (TOP SIDE)

LAYER 1 (TOP SIDE) 1 OZ

ROGERS 4003 0.008 in

LAYER 2 (GROUND PLANE P1) 1 OZ

LAYER 3 (GROUND, VCC & VEE, PLANE P2) 1 OZ

LAYER 4 (BOTTOM SIDE) 1 OZ

FR−4 0.020 in

FR−4 0.025 in

Pin 1

Pin 2

Pin 3

SMA_GND

Pin 4

0.062 0.007

Figure 4. Evaluation Board Layout, 4 Layer

http://onsemi.com

2

NB7V33MMNGEVB

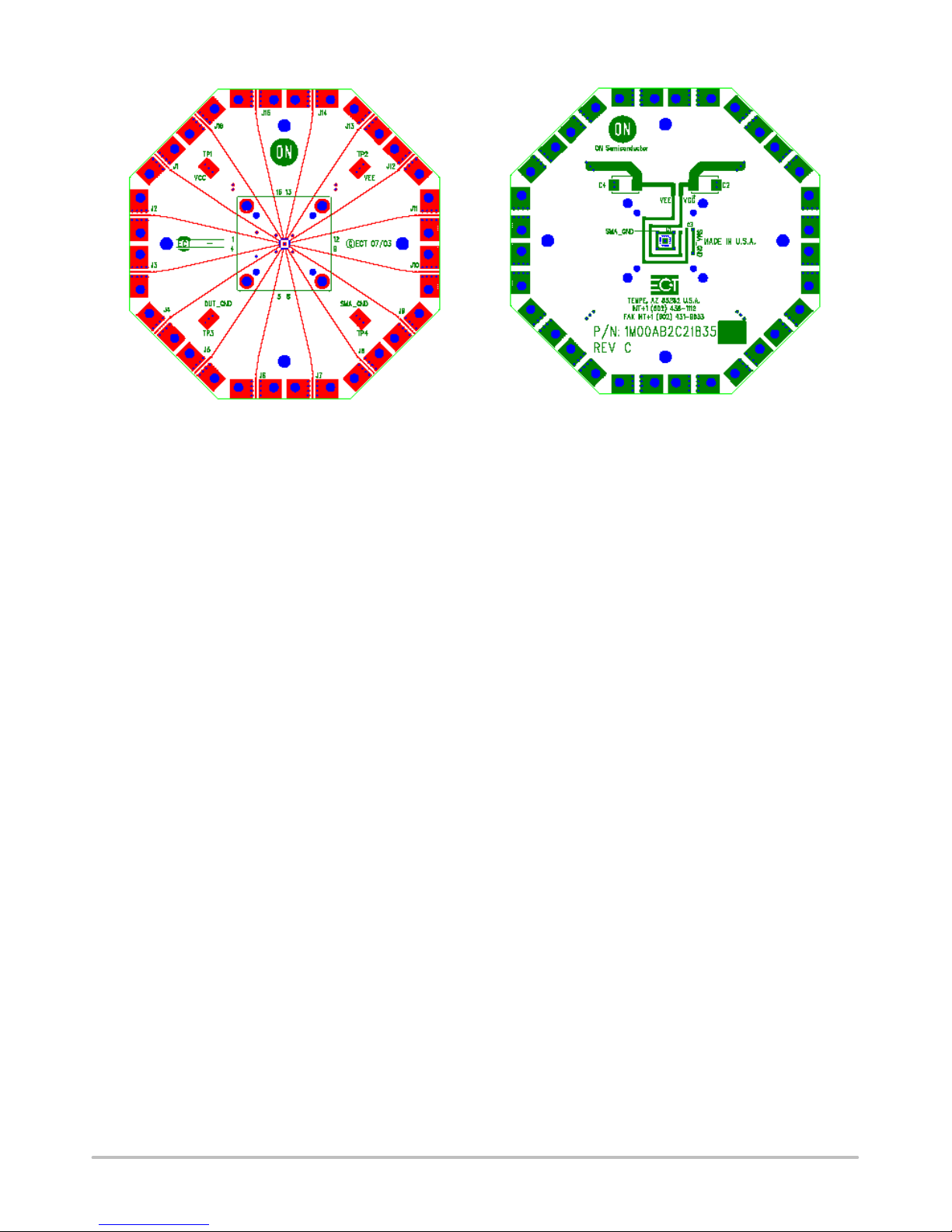

Figure 5. Evaluation Board Layout

Bottom ViewTop View

Evaluation Board Assembly Instructions

The QFN−16 evaluation board is designed for

characterizing devices in a 50 W laboratory environment

using high bandwidth equipment. Each signal trace on the

board has a via at the DUT pin, which provides an option of

placing a termination resistor on the board bottom,

depending on the input/output configuration (see Table 1,

Configuration for Device: NB7V33M). Table 4 contains the

Bill of Materials for this evaluation board.

The QFN16EVB was designed to accommodate a custom

QFN−16 socket. Therefore, some external components are

installed on the bottom side of the board.

Solder the Device on the Evaluation Board

The soldering of a device to the evaluation board can be

accomplished by hand soldering or solder reflow techniques

using solder paste. Make sure pin 1 of the device is located

properly and all the pins are aligned to the footprint pads.

Solder the QFN−16 device to the evaluation board. As

mentioned earlier, many QFN16EVBs are dedicated with a

device already installed, and can be ordered from

onsemi.com at the specific device web page.

Connecting Power and Ground

On the top side of the evaluation board, solder the four

surface mount test point clips (anvils) to the pads labeled

V

, VEE/DUTGND, SMAGND, and ExPad. ExPad is

CC

connected to the exposed flag of the QFN package. For

proper operation, the exposed flag is typically

recommended to be tied to V

/DUTGND, the negative

EE

supply of the device.

The positive power supply connector is labeled V

CC

Depending on the device, the negative power supply

nomenclature is labeled either GND or V

. To help avoid

EE

confusion with the use of this board, the negative supply

connector is labeled V

/DUTGND. SMAGND is the

EE

ground for the SMA connectors and is not to be confused

with the device ground, V

/DUTGND. SMAGND and

EE

DUTGND can be connected in single-supply applications.

The power pin layout and typical connection of the

evaluation board is shown in Figure 6.

It is recommended to add bypass capacitors to reduce

unwanted noise from the power supplies. Connect 0.1 mF

capacitors from V

Output Loading/Termination

ECL/PECL/LVPECL

and VEE/DUTGND to SMA_GND.

CC

Outputs

Most ECL outputs are open emitter and need to be DC

loaded and AC terminated to V

− 2.0 V via a 50 W resistor.

CC

If no internal resistors are provided on the device, 0402 chip

resistor pads are provided on the bottom side of the

evaluation board to terminate the ECL driver. Solder the

chip resistors to the bottom side of the board between the

appropriate input device pads and the ground pads. If

internal resistors are provided, the VT pins should be wired

to SMAGND. (More information on termination is provided

in AND8020).

For standard ECL lab setup and test, a split (dual) power

supply is recommended enabling the 50 W internal

impedance in the oscilloscope, or other measuring

instrument, to be used as an ECL output load/termination.

By offsetting V

(SMAGND is the system ground, 0V); V

V

/DUTGND is −3.0 V, −1.3 V or −0.5 V; see Table 2,

.

EE

Power Supply Levels).

= +2.0 V, SMAGND = VCC − 2.0 V,

CC

CC

is 2.0 V, and

http://onsemi.com

3

NB7V33MMNGEVB

CML Outputs

Likewise, CML outputs need to be terminated to VCC via

a 50 W resistor. If no internal resistors are provided on the

device, 0402 chip resistor pads are provided on the bottom

side of the evaluation board to terminate the CML driver. If

internal resistors are provided, the V

to V

.

CC

pins should be wired

T

For CML lab setup and test, operation with negative

supply voltages is recommended to enable the 50 W internal

impedance in the oscilloscope, or other measuring

instrument, to be used as a CML output termination; (V

CC

= 0 V, SMAGND = 0 V, and VEE/DUTGND = −5.0 V,

−3.3 V, −2.5 V, or −1.8 V).

LVDS Outputs

LVDS outputs are typically terminated with 100 W across

the Q/Q

output pair. The 100 W can be added on the

QFN16EVB, but it is not provided on the board, since there

are several user dependent LVDS output measurement

techniques.

For LVDS lab setup and test, a single supply is typically

used, ie. V

= 3.3 V and DUTGND = 0 V.

CC

Installing the SMA Connectors

Each configuration indicates the number of SMA

connectors needed to populate an evaluation board for a

given device. Each input and output requires one SMA

connector. Install all the required SMA connectors onto the

board and solder the center signal conductor pin to the board

on J1 through J16. Please note that the alignment of the

signal connector pin of the SMA connector to the metal trace

on the board can influence lab results. The launch and

reflection of the signals are largely influenced by imperfect

alignment and soldering of the SMA connector.

Validating the Assembled Board

After assembling the evaluation board, it is recommended

to perform continuity checks on all soldered areas before

commencing with the evaluation process. Time Domain

Reflectometry (TDR) is another highly recommended

validation test.

http://onsemi.com

4

NB7V33MMNGEVB

NB7V33MMNGEVB ASSEMBLY

Table 1. CONFIGURATION FOR DEVICE: NB7V33M

J1 J2 J3 J4 J5 J6 J7 J8 J9 J10 J11 J12 J13 J14 J15 J16

Device Pin # 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16

SMA

Connector

Wire No No No No No GND GND GND V

NOTE: DUTGND/VEE = Exposed Pad and must be tied to DUTGND/VEE.

Yes Ye s Yes Yes No No No No No Yes Yes No No No Ye s No

No No V

CC

CCVCCVCC

No V

CONFIGURATIONS

J15 J14

J16

J13

CC

DUTGND/VEE

12

11

ExPad

10

9

8765

VCC

SMAGND

16151413

1

2

3

4

SMAGND

J1

V

CC

J2

J3

Exposed Pad

J4

J5

J6 J7

Top View

Polarity of 22 mF:

+ C4 − + C2 −

DUTGND/V

DUT

SMAGND

J8

J12

EE

J11

J10

J9

Bottom View

Figure 6. Power Supply Configuration for Device NB7V33M

Install 0.1 mF Decoupling

Capacitors here and at

package pins

http://onsemi.com

5

NB7V33MMNGEVB

NB7V33MMNGEVB TEST

Power Supply

V

CCVEE

/DUTGND

Differential

Signal

Generator

V

Out

Out

Trigger

1. Connect appropriate power supplies to V

2. Connect a signal generator to the input SMA connectors. Setup input signal according to the device data sheet.

3. Connect a test measurement device to the device’s output SMA connectors.

CC

DUT

ExPad SMAGND

VEE/

DUTGND

Power Supply

, VEE/DUTGND, SMAGND, and ExPad (see Table 2).

CC

DUTGND/

V

EE

GND (0 V)

Test Measuring

Equipment

Channel 1

Channel 2

Trigger

NOTE: The test measurement device must contain 50 W termination.

Figure 7. Basic Lab Setup (Typical)

Table 2. POWER SUPPLY LEVELS

Outputs Power Supply V

CML 2.5 V 0 V −2.5 V 0 V VEE/DUTGND

CML 1.8 V 0 V −1.8 V 0 V VEE/DUTGND

CC

Table 3. NB7xxxM, CML OUTPUTS “SPLIT” POWER

VEE/DUTGND SMAGND ExPad (typ)

Dual Power Supplies

SUPPLY CONFIGURATION

Device Pin Power

Supply Convertor

V

CC

SMAGND VTT = 0 V

DUTGND DUTGND = −2.5 V or −1.8 V

“Spilt” Power Supply

VCC = 0.0 V

Offset / “Split” Power Supply Configuration

+0.0 V +2.5 V

V

CC

SMAGND

−+ −+

DUTGND

+2.5 V

Figure 8. “Split” or Dual Power Supply Connections

http://onsemi.com

6

NB7V33MMNGEVB

Table 4. BILL OF MATERIALS

Components Manufacturer Description Part Number Qty Web Site

SMA Connector Rosenberger SMA Connector, Side

Surface Mount

Test Points

Chip Capacitor AVC Corporation*

Chip Resistor Panasonic*

Evaluation Board ON Semiconductor QFN 16 Evaluation

Device Samples ON Semiconductor QFN 16 Package

*Components are available through most distributors, i.e. www.newark.com, www.digikey.com

Keystone* SMT Miniature Test

Launch, Gold Plated

Point

0603 0.01 mF 10%

0603 0.1 mF 10%

0402 50 W 1%

Precision Thick Film

Chip Resistor

Board

Device

32K243−40ME3 7 http://www.rosenberger.de

5015 4 http://www.keyelco.com

06035C103KAT2A na

0603C104KAT2A 2

ERJ−2RKF49R9X na http://www.panasonic.com

QFN16EVB 1 http://www.onsemi.com

NB7V33MMNG 1 http://www.onsemi.com

http://www.rosenbergerna.com

http://www.avxcorp.com

http://onsemi.com

7

NB7V33MMNGEVB

Top Layer

Second Layer (SMA_GND Plane)

Figure 9. Gerber Files

http://onsemi.com

8

NB7V33MMNGEVB

Third Layer (DUT_GND Trace)

Bottom Layer

Figure 10. Gerber Files

http://onsemi.com

9

NB7V33MMNGEVB

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks,

copyrights, trade secrets, and other intellectual property. A listing of SCILLC’s product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent−Marking.pdf. SCILLC

reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any

particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without

limitation special, consequential or incidental damages. “Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications

and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC

does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for

surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where

personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and

its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly,

any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture

of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

PUBLICATION ORDERING INFORMATION

LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada

Fax: 303−675−2176 or 800−344−3867 Toll Free USA/Canada

Email: orderlit@onsemi.com

N. American Technical Support: 800−282−9855 Toll Free

USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81−3−5817−1050

http://onsemi.com

10

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local

Sales Representative

EVBUM2187/D

Loading...

Loading...