Page 1

Low Power &

f

High-Resolution Audio

Processing System SoC for

Portable Sound Solution

LC823455

Description

LC823455 is an audio processing System−on−Chip (SoC) for

recording and playback, with High−Resolution 32−bit & 192 kHz

audio processing capability that provides the key functions required

for portable audio solutions.

It has a Dual CPU configuration and a DSP providing intensive

processing capability, 4316 KB of internal SRAM that supports the

implementation of large-scale programs for WLAN applications, and

multiple interfaces for increased extensibility. Its features an extensive

range of functions including SBC/AAC codec and Active Noise

Canceller by the DSP, UART and ASRC − applicable for wearable

audio applications. The highly integrated implementation of this rich

set of analog functions results in a miniature footprint with ultra− low

power consumption. This, along with its high performance, makes the

LC823455 suitable for portable audio markets such as Wireless

headsets.

This document describes features, basic functions, electrical

specifications, characteristics, application diagrams and package

dimension of this SoC.

Features

• Ultra Low Power Consumption

®

• Arm

• Proprietary 32−bit DSP Core (LPDSP32)

• Internal Large−Scale Size SRAM : 4316 KB (4 MB + 220 KB)

• High−Resolution 32−bit & 192 kHz Audio Processing Capability

• Several DSP Codes Available for Audio Functions

• Hard−Wired Audio Functions Built−In:

• Analog Blocks Built−in:

• USB2.0 Device with an Integrated PHY, eMMC and SD Card I/F,

Cortex®−M3 Dual Core

MP3 decoder, MP3 encoder,

6 band Equalizer

Synchronous SRC, Asynchronous SRC, etc.

System PLL, Audio PLL,

16−bit DAC, Class−D amp, etc.

Serial Flash I/F(Quad) with Cache Memory,

SPI, UART, I2C, etc.

www.onsemi.com

WLCSP120, 4.086x4.086x0.62

CASE 567WG

LFBGA136, 11.0x11.0

CASE 566GB

ORDERING INFORMATION

See detailed ordering and shipping information on page 104 o

this data sheet.

Typical Applications

• Wearable Earbuds

• Wearable Headphone

• Wireless Speaker

• IC Recorder

© Semiconductor Components Industries, LLC, 2017

April, 2021 − Rev. 3

NOTE:

LC823455RB−2H is under planning.

LC823455RB−2H : Package Code = RB

1 Publication Order Number:

LC823455/D

Page 2

LC823455

Table of Contents

Abstract 3................................................................................................

Terminal Function 21......................................................................................

Pin Assignment 36........................................................................................

Input/Output Circuit 45.....................................................................................

Electrical Specification 55..................................................................................

AC Characteristics 69.....................................................................................

www.onsemi.com

2

Page 3

ABSTRACT

LC823455

Features

• Cortex−M3 Dual Core, AMBA

♦ Internal SRAM (4 M-byte)

♦ Internal ROM (256 k-byte). Boot code, Standard

®

(AHB/APB) system

Functions

♦ DMA Controller (8 ch)

♦ Interrupt Controller (External 90 ch, Internal 83 ch)

♦ SPI (2 ch)

♦ Serial Flash I/F (1 ch)

♦ Quad SPI, cache memory (16 k-byte, 4way set

associative, 128 line) function available

♦ UART (3ch)

UART1, UART2: w/flow control (CTS, RTS)

UART0: w/o flow control

♦ I2C (2ch) Single Master, Full/Standard

♦ GPIO (90 ch)

♦ Pin multiplex function (I2C:2 ch, SPI:2 ch, UAR T:3

ch, MTM:2 ch, DMIC:2 ch x 2)

♦ Plain Timer w/ Watch Dog Timer (1 ch×3)

♦ Multiple Timer (2 ch×4)

♦ 12 bit ADC (8 ch)

♦ SD Card I/F (3 ch)

eSD/eMMC, UHS−I, w/o CPRM

−SD0: eSD/eMMC boot supported (Internal ROM

Boot function)

− SD1: 1.8 V/3.3 V dedicated power supply

− SD2 :

♦ USB2.0 Device (HS/FS) Controller,

Integrated PHY.

Xtal (XT1) is required for USB function, 12, 19.2,

24 MHz for device w/o OTG function.

♦ Real Time Clock

2 modes below are available

− General RTC mode : RTC w/o key input

− KeyInt RTC mode : RTC w/ key input which

enables power on function

♦ SWD (Serial Wire Debug) is supported as the debug

interface

SWV (Serial Wire Viewer) is supported as the trace

interfaceOnly one of Cortex−M3 Dual Core can be

traced

Availability of features explained here depends on

products.

• MP3 hard wired encoder/decoder

♦ MP3 MPEG1, MPEG2, MPEG2.5

− Sampling rate: 8 kHz,11.025 kHz,12 kHz,

16 kHz, 22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz,

48 kHz

− Bit rate: 8 Kbps to 320 Kbps (Decoder−VBR

supported)

• LPDSP32 system

♦ Internal SRAM (220 kbyte)

♦ Audio codec

− MP3

− WMA

− AAC

− SBC

− FLAC, etc.

♦ Audio function

− Active Noise Canceller

− 1−mic/2−mic Noise Canceller for Recorder

− 2−mic Noise Canceller for Hands Free

− Echo Canceller

− Variable Speed Control playback etc.

♦ JTAG ICE

1

MPEG Layer−3 audio coding technology licensed from Fraunhofer IIS and Thomson. Supply of this product does not convey license nor

imply any right to distribute content created with this product in revenue−generating broadcast systems (terrestrial, satellite, cable and/or

other distribution channels), streaming applications (via Internet, intranets and/or networks), other content distribution systems (pay−au-

dio or audio−on−demand applications and the like) or on physical media (compact discs, digital versatile discs, semiconductor chips,

hard drives, memory cards and the like). For details, please visit http://mp3licensing.com/

Supply of this product does not convey license under the relevant intellectual property of Thomson and/or Fraunhofer Gesellschaft nor

imply any right to use this product in any finished end user or ready−to−use final product. An independent license for such use is required.

For details, please visit http://mp3licensing.com/

2

This product contain technology of Microsoft company ownership, and you cannot distribute or use without getting license from Microsoft

Licensing Company.

www.onsemi.com

3

Page 4

LC823455

• Bluetooth Protocol Stack available

• Audio

♦ MP3 hard wired encoder/decoder, MP3 MPEG1,

MPEG2, MPEG2.5

− Sampling rate: 8 kHz,11.025 kHz,12 kHz,16 kHz,

22.05 kHz, 24 kHz, 32 kHz, 44.1 kHz, 48kHz

− Bit rate :8 Kbps to 320 Kbps

(Decoder−VBR supported)

♦ Other audio functions available

− 6 band Equalizer (EQ3)

− Hardware Mixer

− Volume, Mute

− Level Meter

− Audio Timer w/ interrupt generation

− 16/24/32 bit 192 kHz PCM I/F (2ch×2).

Master/slave, I2S

− SSRC (Synchronous Sampling Rate Converter)

0.25 to 64 conversion capable

− ASRC (Asynchronous Sampling Rate Converter)

Jitter reducing function supporting USB audio

class and Bluetooth streaming

− Beep generator

− Digital Microphone I/F (2ch x2), Sampling rate :

up to 48 kHz, Support up to 4 PDM Digital

Microphones

− 16 bit Audio DAC (2 ch)

w/ Class−D Amplifier for Head Phone (2 ch).

Requires external LC LPF

• Audio clock generation

♦ Dedicated PLL for audio

♦ Selectable PLL reference clock

XT1 (12, 19.2, 24 MHz Main xtal)

XTRTC (32.768 kHz RTC xtal)

PCM I/F MCLK0 (/MCLK1), BCK0, BCK1

• Power supply

♦ Typical voltage

− LOGIC(Vdd1),XT1(VddXT1),

PLL1(AVddPLL1), PLL2(AVddPLL2) = 1.0 V

− RTC(VddRTC) = 1.0 V

− I/O(Vdd2) = 1.8 V or 3.3 V

− SD1(VddSD1) = 1.8 V or 3.3 V

− ADC(AVddADC) = 1.8V

− USB PHY(DVddUSBPHY1) = 1.0 V,

(AVddUSBPHY2) = 3.3 V,

(AVddUSBPHY18) = 1.8 V

− Class−D Amplifier

(AVddDAMPL,AVddDAMPR) = 1.5 V

3

The product name for which Bluetooth Protocol Stack is available is determined. Please contact our representative for license fee for the

Stack.

Copyright 1999−2014 OpenSynergy GmbH

All rights reserved. All unpublished rights reserved.

www.onsemi.com

4

Page 5

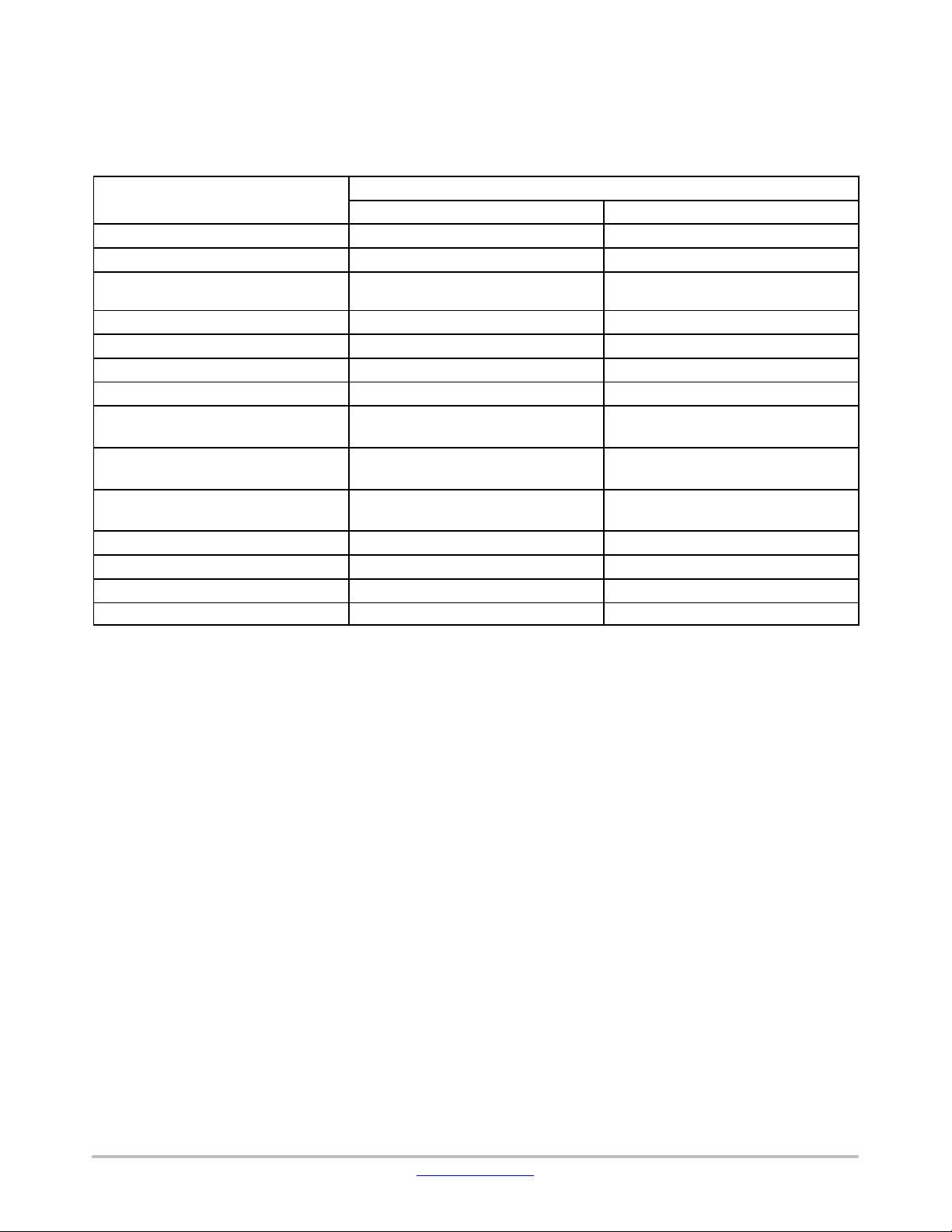

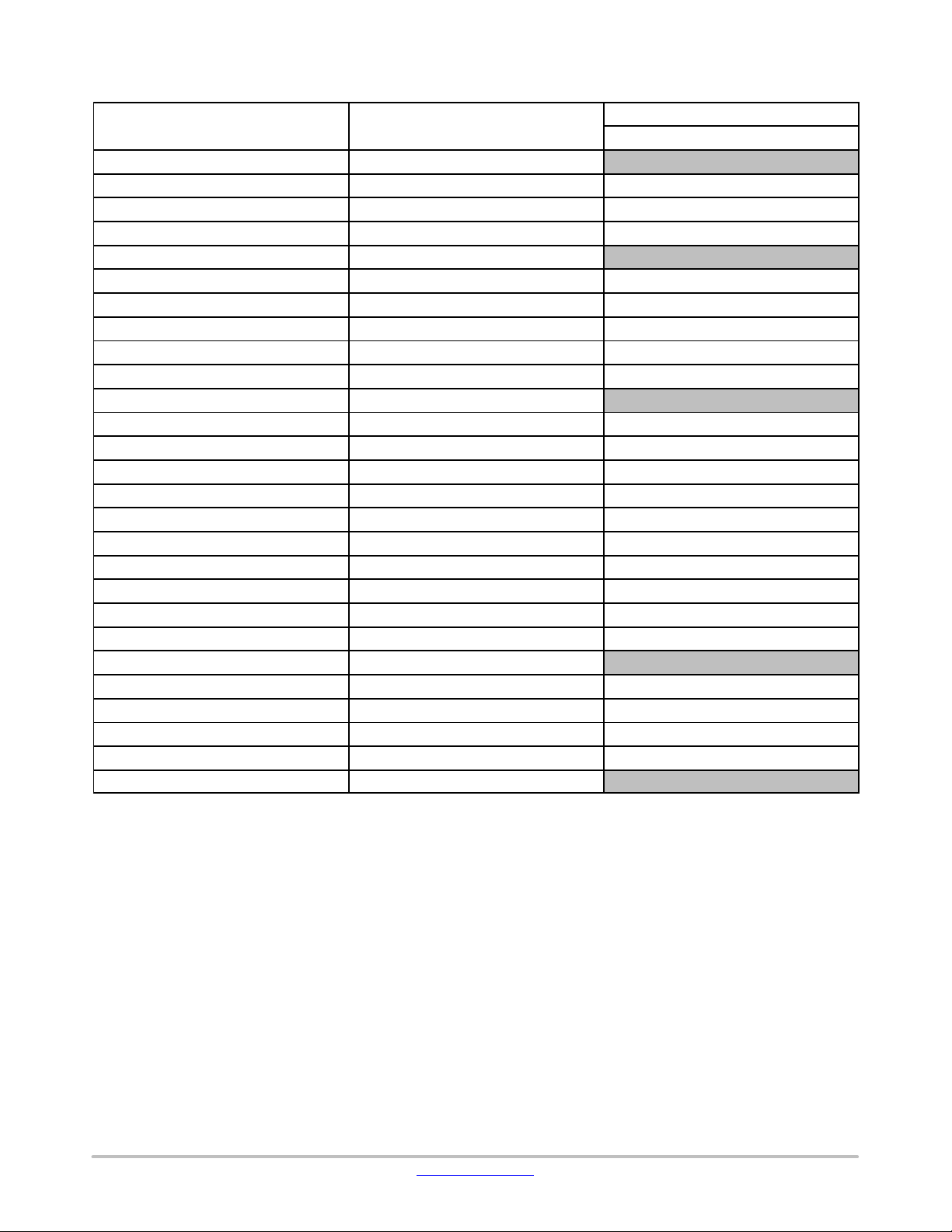

Package Codes and Functional Differences

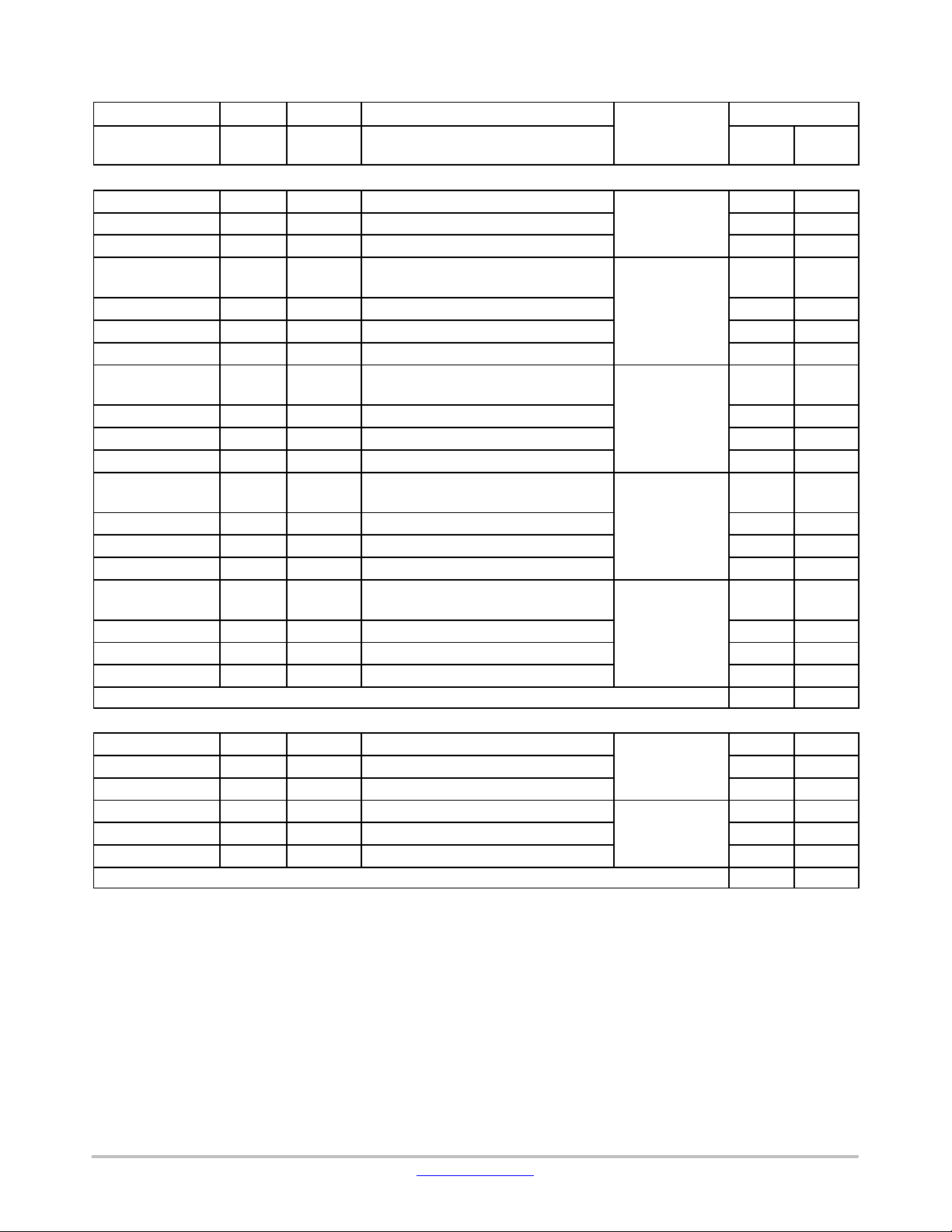

Table 1. FUNCTIONAL DIFFERENCES

Package Code

XA

RB

Package

WLP120

BGA136

SDRAM Controller

−

−

External Memory

−

−

SD0

Shared pins with S−Flash function

Dedicated

P−SRAM−−

USB2.0

HS/FS Device

HS/FS Device

12 bit ADC

3ch

8ch

PLL1

Only Internal Loop Filter

Only Internal Loop Filter

XTALINFO[1:0] input

“00”

“00”

RTCMODE input

“0”

Available

BACKUPB input

Connected with VDET internally

Available

KEYINT input

2ch

2ch

External Interrupt

52 ch

53 ch

GPIO

52 ch

53 ch

The product with Package Code = “RB” is under planning.

Function

Controller

PLL2

LC823455

(24 MHz)

(KEYINT RTC mode)

(24 MHz)

www.onsemi.com

5

Page 6

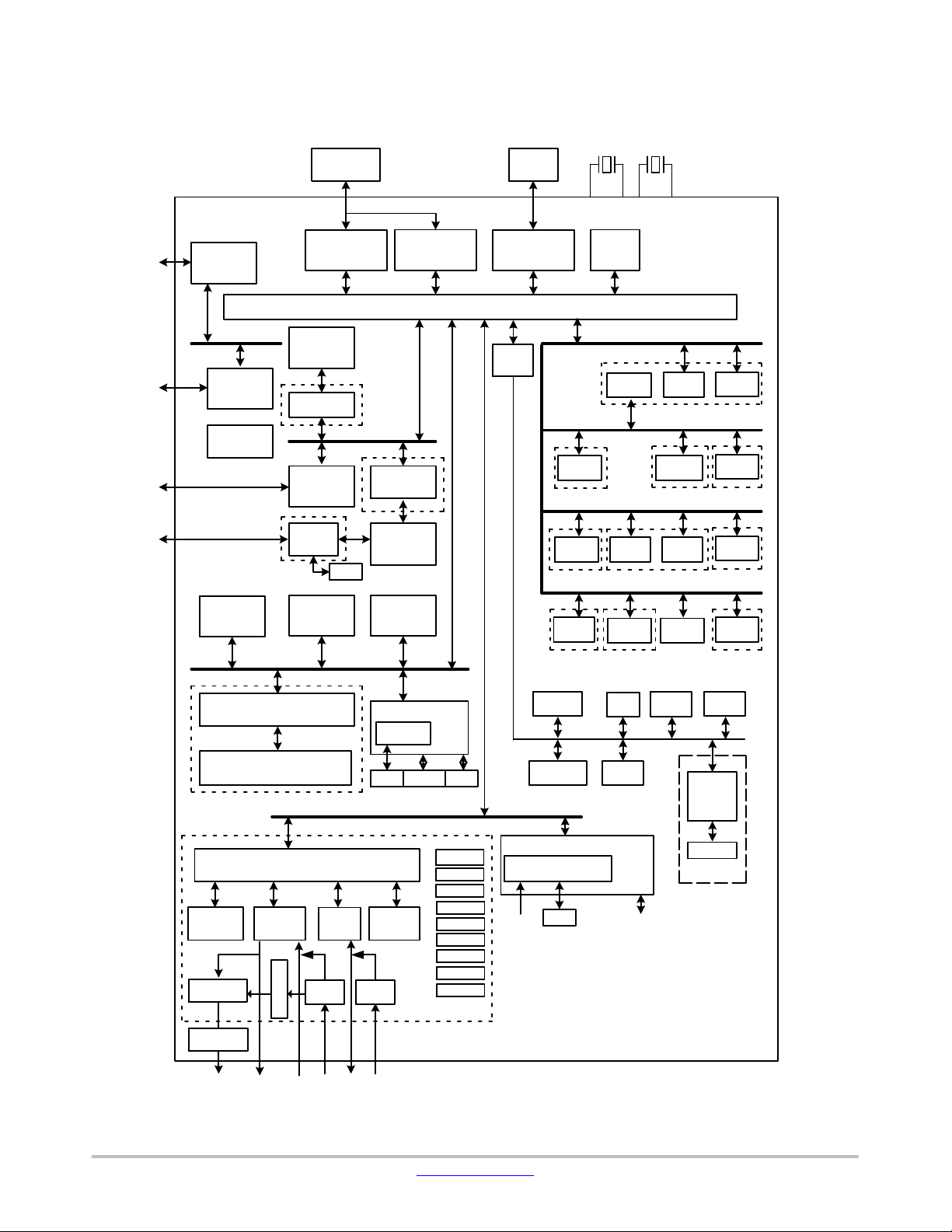

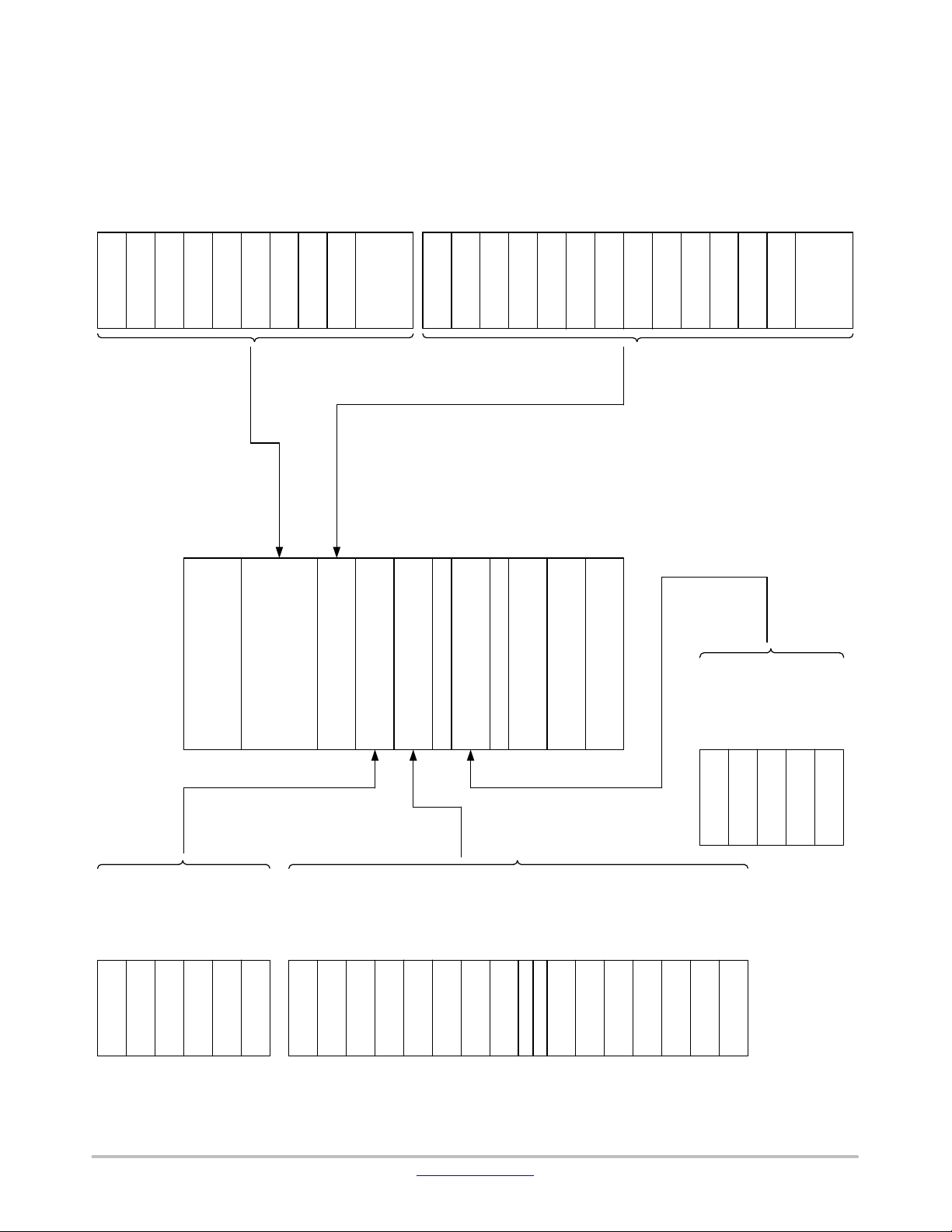

Block Diagram

SWD/SWV

ICE

LC823455

JTAG

ICE

12MHz,

19.2MHz,

32.768kHz

24MHz

XT 1 XTRTC

PSRAM I/F

(1ch

EXT4

SDRAM

CTRL

Controller

USB2.0

Main

Module

Manager

)

Reset

PD -J

(512 byte×3)

BUF

SD I/F

(3ch

ARM Cortex-M3

S-Flash I/F

(1ch)

Cache

(16 Kbyte)

External

Memory

Controller

USB

PHY

Plain

Timer

(1ch×

PD -H

)

PD -G

PD -E

XT1

3)

ARM Cortex-M3

Multilayer Bus

BASIC

BUF

(16 Kbyte)

USB2.0

Device

Multiple

Timer

(2ch×

4)

EXT1

OSC

System

PLL

XT1 RC

XTRTC

EXT3

LPDSP32

APB

Bridge

SRAM S7B

(224Kbyte)

PD -9

SRAM S5A

(384Kbyte)

PD -6

SRAM S1

(256Kbyte)

PD -3

12 bit ADC

(8ch )

PORT0~4

(80 I/O)

DMAC

(8ch)

SRAM S7A

(256Kbyte)

SRAM S4

(256Kbyte)

SRAM S0B

(128Kbyte)

PD -2

SPI

(2ch )

PORT5

(10 I/O)

(1536Kbyte)

PD -5

UART

(3ch )

SRAM S9

(220Kbyte)

PD -10

SRAM S6

PD -8

SRAM S3

(256Kbyte)

SRAM S0A

(128Kbyte)

RTC

SRAM S8

(32Kbyte)

SRAM S5B

(384Kbyte)

PD -7

SRAM S2

(256Kbyte)

PD -4

ROM

(256Kbyte)

PD -1

I2C

(2ch )

MP3

Decoder

16bit Audio

DAC

Class-D

AMP

Audio Buffer

(256 Kbyte)

PCM

I/F

A

N

C

*

Digital

Mic

ATM

BEEP

VOLUME

PCM

I/F

MP3

Encoder

EQ3

METER

MUTE

BCK0/1

MCLK0/1

(PCM I/F)

SSRC

ASRC

Digital

Mic

MIXER

PD -A

Figure 1. T op−Level Block Diagram

www.onsemi.com

6

OSC

Audio PLL

XT1

AHB CLK

(HCLK)

XTRTC

PD -RTC

Page 7

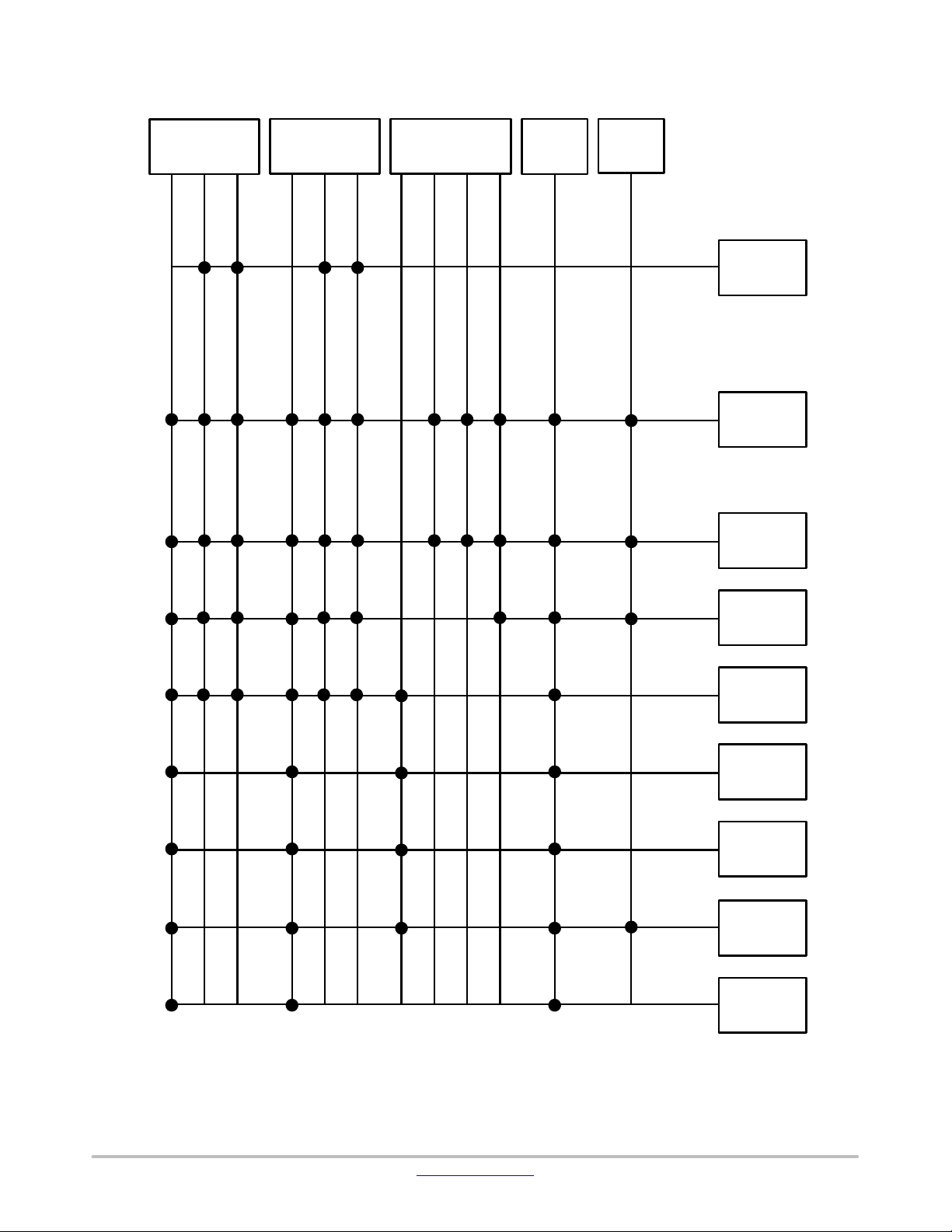

Bus Matrix

LC823455

ARM Cortex−M3

System−Bus

I−Bus

D−Bus

ARM Cortex−M3 LPDSP32

System−Bus

I−Bus

D−Bus

DMIO

DMA

DMB

PM

DMAC

(8ch)

USB2.0

System

ROM

SRAM

(Seg 0)

・・・

SRAM

(Seg 8)

Figure 2. Bus Matrix

SRAM

(Seg 9)

BASIC

Peripheral

EXT1

Peripheral

EXT3

Peripheral

EXT4

Peripheral

APB

Peripheral

www.onsemi.com

7

Page 8

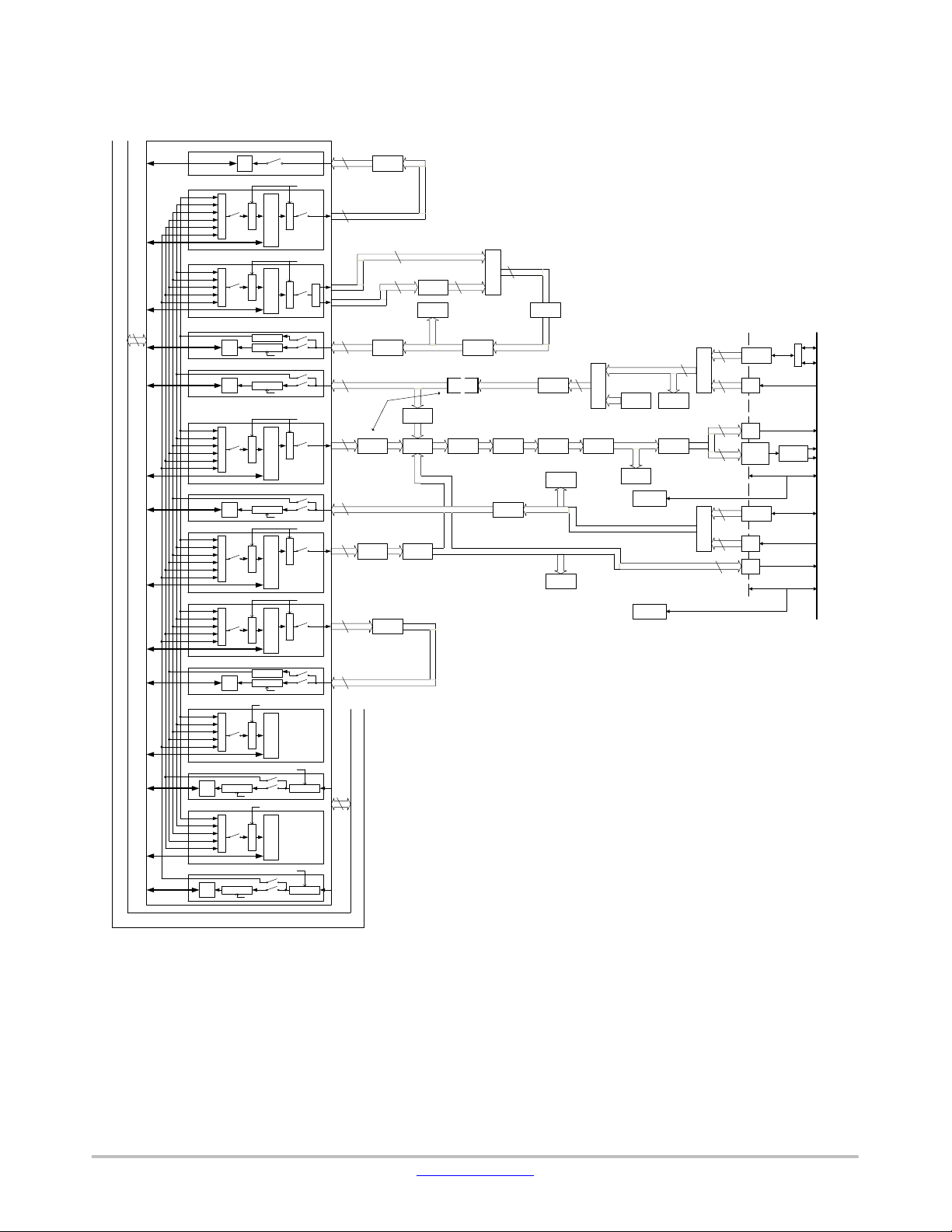

Audio

Internal

Bus

LC823455

256KB SRAM divided into

A

~ N Audio Buffers

by register settings

A buffer

RAM

RAM

Bit conv

RAM

Bit conv

32 Bit conv

Bit conv

RAM

Bit conv

BIT1-0、

BIT1-0、

BIT1-0、

Bit conv

BIT1-0、

Bit conv

MONO

MONO

BIT1-0、

Bit conv

B buffer

D

redirect

E

redirect

G

redirect

J

redirect

L

redirect

N

redirect

C buffer

E

redirect

G

redirect

J

redirect

L

redirect

N

redirect

32

D buffer

RAM

E buffer

RAM Bit conv

F buffer

D

redirect

E

redirect

G

redirect

J

redirect

L

redirect

N

redirect

G buffer

H buffer

D

redirect

E

redirect

G

redirect

J

redirect

L

redirect

N

redirect

I buffer

D

redirect

E

redirect

G

redirect

L

redirect

N

redirect

J buffer

K buffer

D

redirect

E

redirect

G

redirect

J

redirect

N

redirect

L buffer

RAM Bit conv

M buffer

D

redirect

E

redirect

G

redirect

J

redirect

L

redirect

N buffer

RAM Bit conv

RAM Bit conv

RAM Bit conv

BIT1-0、

BIT1-0、

RAM

Bit conv

RAM

Bit conv

32 Bit conv

BIT1-0、

RAM

Bit conv

CBIT1-0、

MONO

BIT1-0、

RAM

Bit conv

CBIT1-0、

MONO

BIT1-0、

BIT1-0、

MONO

CMONO

MONO

CMONO

MONO

BIT1-0、

Bit conv

BIT1-0、

Bit conv

MONO

32 Bit conv

32 Bit conv

MONO

MONO

MONO

MONO

MONO

8

MP3

Encoder

16

24

8

MP3

Decoder

METER

(DEC)

24

VOLUME

(DEC)

32

VOLUME

(AMB)

32

EQ3

32

32

24

DWNMIX

(PS

VOLUME

1)

1)

(PS

ASRC

16

EQ3

DWNMIX

(PS

0

D

E

24

C

S

E

L

1

MUTE

(DEC)

DMCKO0A

SSRC

0

S

I

32

VOLUME

(SP

VOLUME

BTLMIXER

0)

VOLUME

(PS

1)

(SP

0)

0)

METER

(SP

METER

(PS

N

S

E

L

1

MUTE

0)

(PS

1)

SINGEN

METER

(PS

AudioTimer0

METER

0)

(SP

BEEP

0)

LRCK0

1)

LRCK1

AudioTimer1

24

Digtal

1

P

C

32

M

S

E

32

PCM

L

0

SP0

32

PCM

PS0

16 bit

24

Audio

DAC

24

P

C

M

1

S

E

L

Digtal

1

32

PCM

0

SP1

32

PCM

PS1

S

DMDIN0A

E

Mic0

PCM input

PCM output

Mic1

PCM input

PCM output

Class−D

AMP

DMCKO0B

L

DMDIN0B

DIN0

(PCM input)

DOUT0

(PCM output)

LOUT

ROUT

MCLK0/

BCK0/

LRCK0

DMCKO1

DMDIN1

DIN1

(PCM input)

DOUT1

(PCM output)

MCLK1/

BCK1/

LRCK1

24

32

Figure 3. Audio

www.onsemi.com

8

Page 9

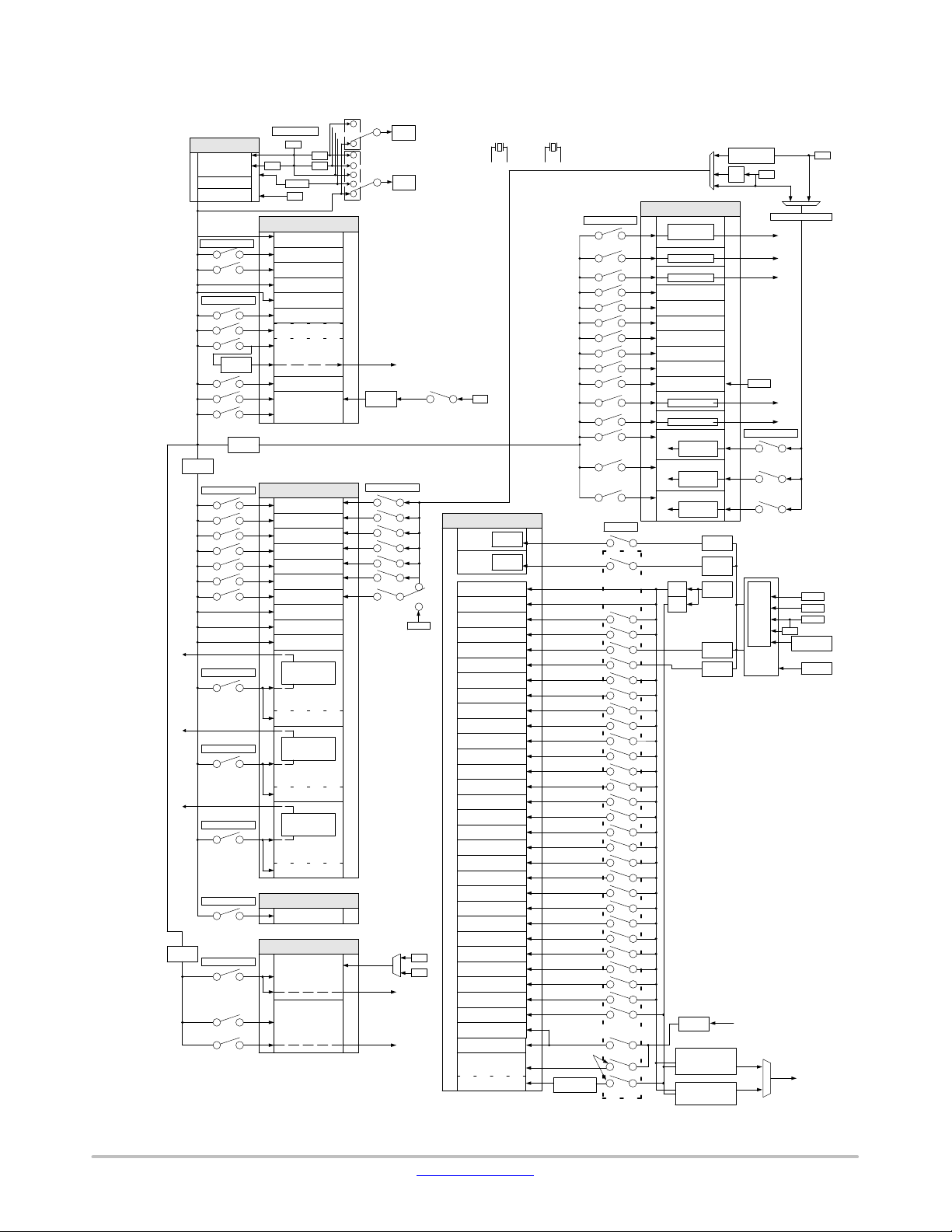

Clock Hierarchy

LC823455

1/(1~64)

1/(1~64)

AHB CLK

(EXT4 only)

Oscillation System

SYSTEM PLL

(PLL1)

1/2、1/4

1/1、1/{(1~63)×2}

BASIC CLK

CORECNT

MCLKCNTBASIC

1/1、1/2、

1/4、1/8

1/(1~64)

AHB CLK(HCLK)

MCLKCNTEXT 1

SDCLK0

MCLKCNTEXT 1

SDCLK1

MCLKCNTEXT 1

SDCLK2

MCLKCNTEXT 1

MCLKCNTEXT 3

MCLKCNTEXT 4

FCLKCNT

XT1

1/4

XTRTC

RC

BASIC

M3Core0

M3Core1

LPDSP32

SRAM/ROM

INTC

DMAC

Cache

S-Flash I/F

External Memory

Controller(XMC)

USB2.0 Device

APB CLK (PCLK )

AHB EXT1

Plain Timer 0

Plain Timer 1

Plain Timer 2

Multiple Timer 0

Multiple Timer 1

Multiple Timer 2

Multiple Timer 3

Audio PLL

System PLL

OSC System

1/1、1/2、1/4、1/8、

1/16、1/32、1/64、

1/128 、1/256 、1/512

SD0(Main Function)

SD0(Card Detect)

1/1、1/2、1/4、1/8、

1/16、1/32、1/64、

1/128 、1/256 、1/512

SD1(Main Function)

SD1(Card Detect)

1/1、1/2、1/4、1/8、

1/16、1/32、1/64、

1/128 、1/256 、1/512

SD2(Main Function)

SD2(Card Detect)

AHB EXT3

AUDIO BUFFER

AHB EXT4

PSRAM I/F

SDRAM CTRL

PHI1 pin

・・・

・・・

1/4

1/2

PHI0 pin

[Note]

- M3Core 0, M3Core 1 and LPDSP 32 has additional clock gating

switch enabled by the execution of a dedicated operation.

SFCK

USB PHY

MCLKCNTEXT 1

XTRTC

PLL1

PSM_SCK

SDRCLK

Figure 4. Clock Hierarchy

12MHz

19.2MHz

24MHz

XT1

(XIN1/XOUT 1 pin)

32.768kHz

XTRTC

(XIN32K/XOUT 32K pin )

MCLKCNTAPB

APB

ADC

1/2、1/4、1/8、

1/16、1/32、1/64

SPI0

1/{(2~256 )×4}

SPI1

1/{(2~256 )×4}

1/1、1/2、1/4、

1/8、1/16

1/4

ADCCLK

(Internal)

PLL1

XT1

1/{(1~8) + (0~63)/64}

SCK0

SCK1

PORT 0

PORT 1

PORT 2

PORT 3

PORT 4

PORT 5

1/2、1/4、

1/8

1/4、1/8、

1/16

1/1、1/2、

1/4

1/1、1/2、

1/4、1/8

1/1、1/2、

1/4、1/8

XTRTC

SCL0

SCL1

MCLKCNTAPB

AUDIO

PLL

(PLL2)

1/4

MCLK 0/MCLK 1

BCK0

BCK1

XT1

(input)

AHB CLK

(HCLK )

XT1

AUDIO Block

MP3DEC

MP3ENC

AUDIO Control

VOLUME DEC

MIXER

EQ3

BEEP

SSRC

ASRC

1/2

1/1、1/2、

1/4

CLOCKEN

FS384

FS192

FS256

RTC

I2C0

1/{(2~65535)×8}

I2C1

1/{(2~65535)×8}

UART0

1/{(8~16)×

(1~65536)}

UART1

1/{(8~16)×

(1~65536)}

UART2

1/{(8~16)×

(1~65536)}

DECCLK

ENCCLK

AUDCLK

1/3

1/2

FS384

SSRCFCLK

ASRCFCLK

FS768

VOLUME SP 0

VOLUME PS0

VOLUME SP 1

VOLUME PS1

VOLUME AMB

METER DEC

METER SP0

METER PS0

METER SP1

METER PS1

[Note]

- Regarding the initial value of switches described in this figure,

refer to the appropriate documents.

- Regarding the frequency of SSRCFCLK and ASRCFCLK,

refer to the SSRC and ASRC Programmer’s Model documents.

- ENCCLK frequency should be192 * FS

while FS is Sampling Frequency of MPEG1 mode of MP3.

ex.) ENCCLK should be8.4672MHz to make all of MP 3 data

44.1/22.05/11.025 KHz (MPEG1/MPEG2/MPEG2.5).

- DECCLK frequency should be384 * FS

while FS is Sampling Frequency of MPEG1 mode of MP3.

ex.) DECCLK should be16.9344MHz to make all of MP 3 data

44.1/22.05/11.025 KHz (MPEG1/MPEG2/MPEG2.5).

MUTE DEC

MUTE PS0

PCMPS0

PCMSP0

PCMPS1

PCMSP1

AudioTimer 0

AudioTimer 1

XT1

SINGEN

DigitalMIC0

DigitalMIC1

PCKGEN

Damp CTL

Class -D AMP

16bit Audio

DAC(Noise Shaping )

DAC(Main)

FCEDAC

1/1, 1/2, 1/4

1/8, 1/16

[Note]

- Class-D AMP has additional clock source and gating switch

for being used as GPO.

1/1, 1/2,

1/4

1/1, 1/2, 1/4, 1/8,

1/1, 1/21/4, 1/8,

1/16, 1/32

1/16, 1/32

FS384

MCLK0/MCLK1

(output )

www.onsemi.com

9

Page 10

Memory Map

All Areas (Cortex−M3)

0x4000 1000

0x4000 0000

0x4000 2000

0x4000 3000

0x4000 4000

0x4000 5000

0x4000 6000

0x4000 7000

0x4001 0000

0x4002 0000

LC823455

0x4004 0000

0x4003 FFFF

0x4004 1000

0x4004 2000

0x4004 3000

0x4004 4000

0x4004 5000

0x4004 6000

0x4004 7000

0x4004 A000

0x4004 9000

0x4004 8000

0x4004 B000

0x4004 C000

0x4004 D000

0x4005 FFFF

S-Flash I/F

MEM CTL

External

USB2.0 CTL

INTC

0x0000 0000

external memory

MUTEX REG

DSP CMDIF

DMAC

peripherals

BASIC

0x4000 0000

SRAM memories

BASIC peripherals

USB2.0 FIFO

reserved

0x4004 0000

0x4006 0000

AHB EXT1 peripherals

reserved

0x4008 0000

AHB EXT3 peripherals

APB peripherals

System

OSC

0x400A 0000

0x6000 0000

reserved

System PLL

Audio PLL

Timer0

0x6402 0000

0xE000 0000

AHB EXT4 peripherals

reserved

Multiple

Multiple

Timer1

0xE004 0000

Private peripheral bus - External

Private peripheral bus - Internal

Multiple

Timer2

0xE010 0000

Multiple

Timer3

Timer0

peripherals

System

Timer1

Plain

AHB EXT1

Timer2

Plain

Plain

0x6000 0000

SD1

SD0

0x6400 0000

0x6200 0000

SD2

peripherals

AHB EXT4

0x6400 2000

0x6400 1000

reserved

0x6401 FFFF

0x4006 1000

0x4006 0000

0x4006 2000

Audio Buffer

Functions

Audio

peripherals

AHB EXT3

0x4006 3000

MP3 Decoder

MP3 Encoder

0x4007 FFFF

0x4006 5000

0x4006 4000

Controles

reserved

Audio

0x4008 1000

System

PORT0

0x4008 2000

0x4008 0000

Controller

peripherals

APB

0x4008 3000

0x4008 4000

0x4008 5000

0x4008 6000

0x4008 7000

0x4008 8000

0x4008 8800

PORT3

PORT4

PORT1

PORT2

PORT5

ADC

SPI0

SPI1

Figure 5. All Areas (Cortex−M3)

www.onsemi.com

10

0x4008 9000

0x4008 A000

I2C0

I2C1

0x4008 B000

0x4008 C000

UART0

UART1

Memory Area

SDRAM

0x4008 D000

0x4008 E000

0x4008 F000

UART2

RTC

SDRAM CTRL

reserved

0x4009 FFFF

reserved

PSRAM I/F

reserved

Page 11

Code Area (Cortex−M3)

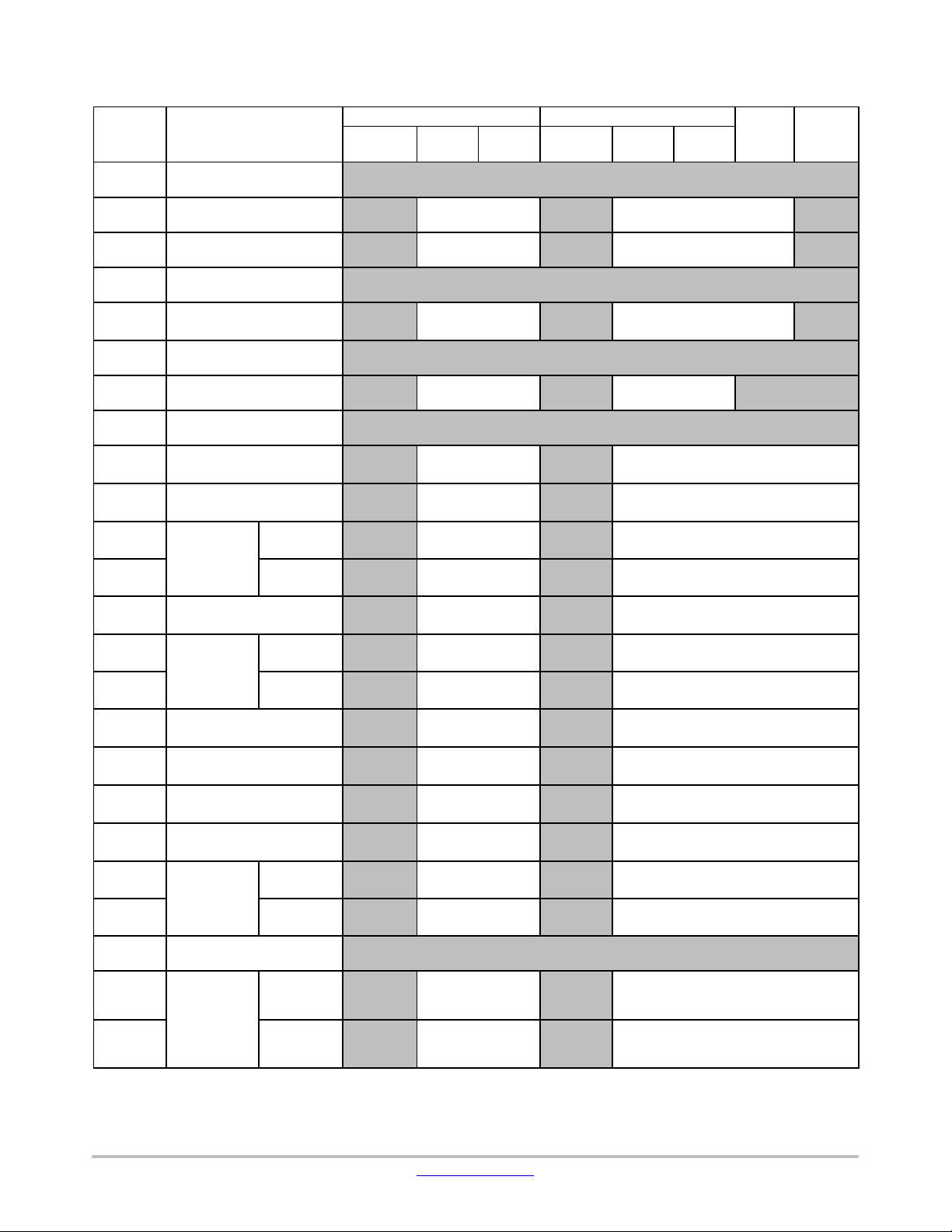

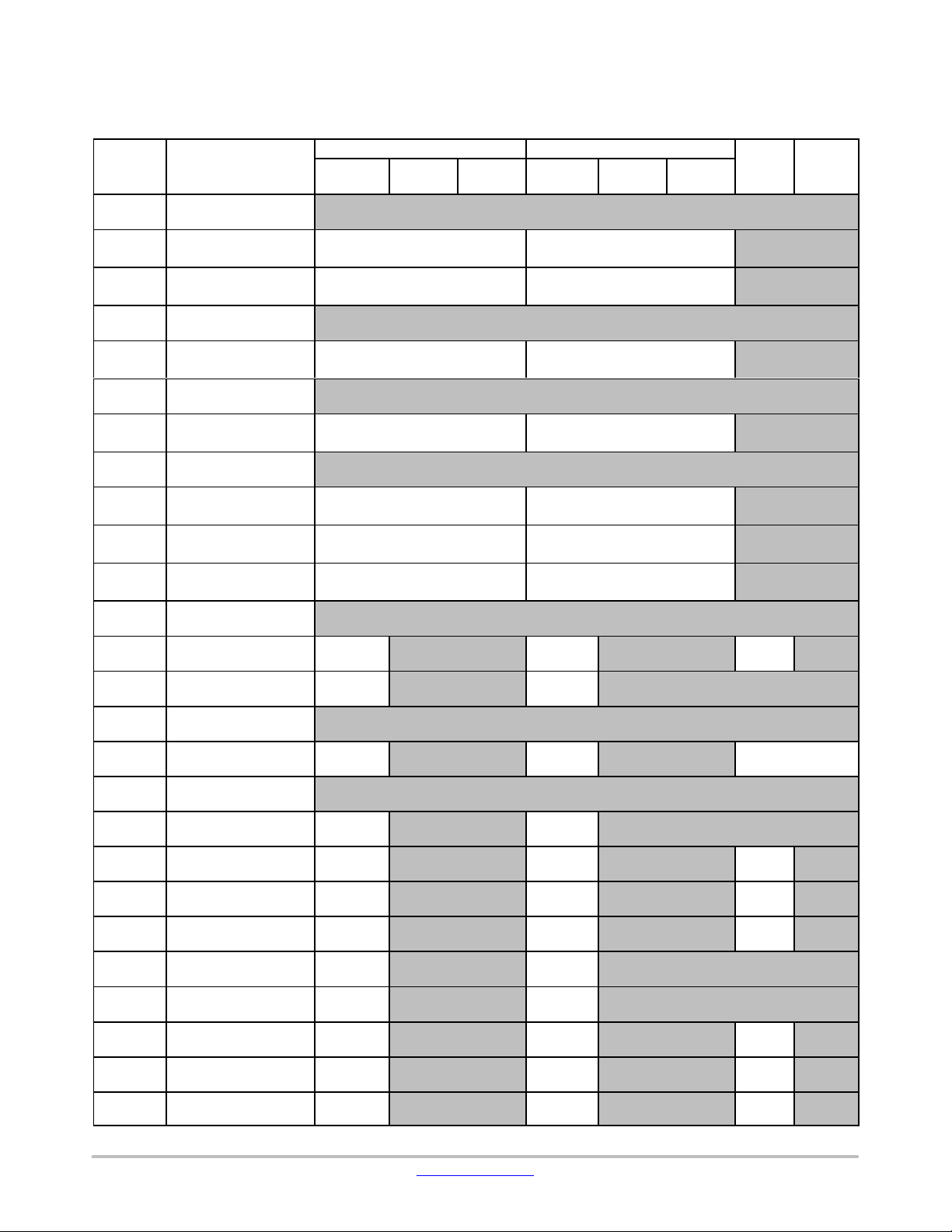

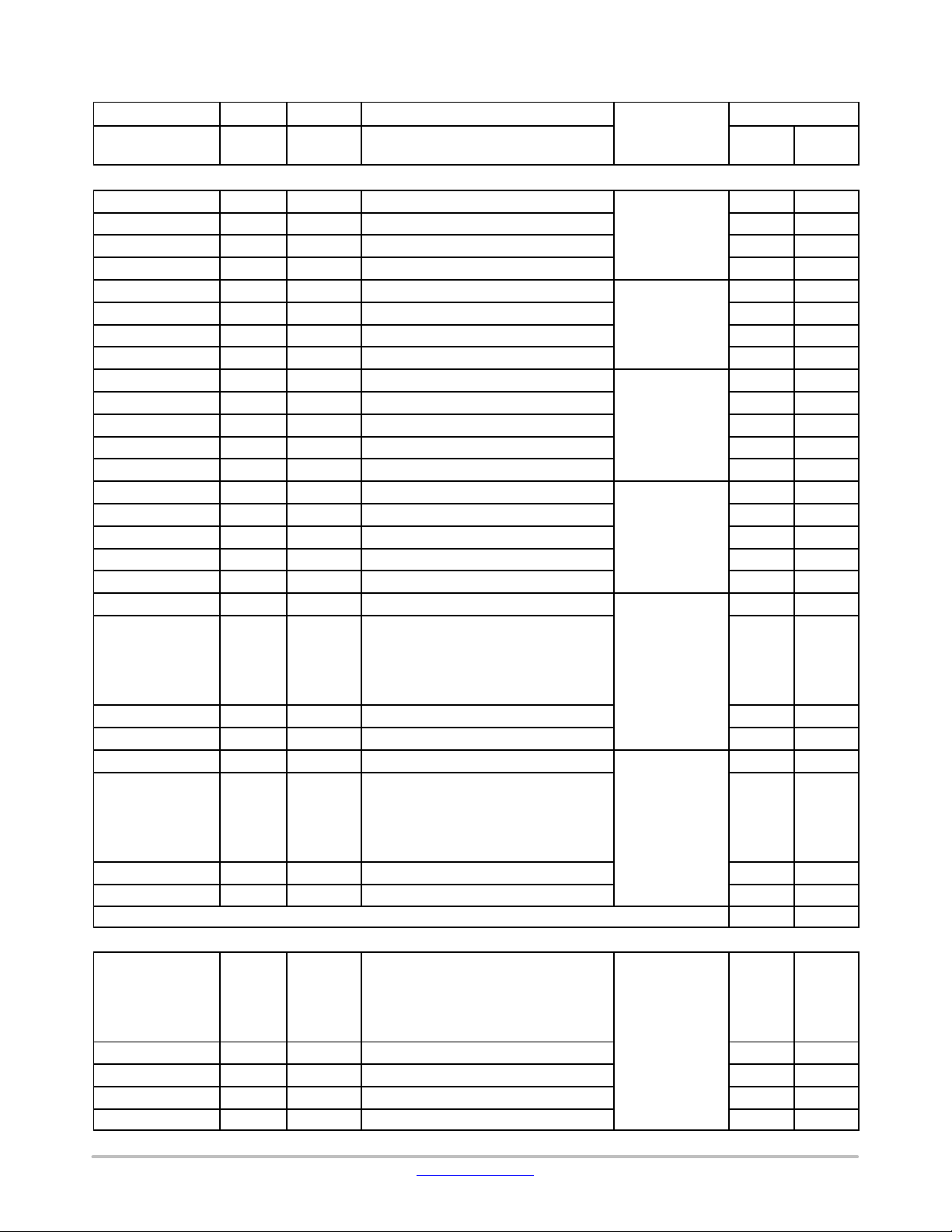

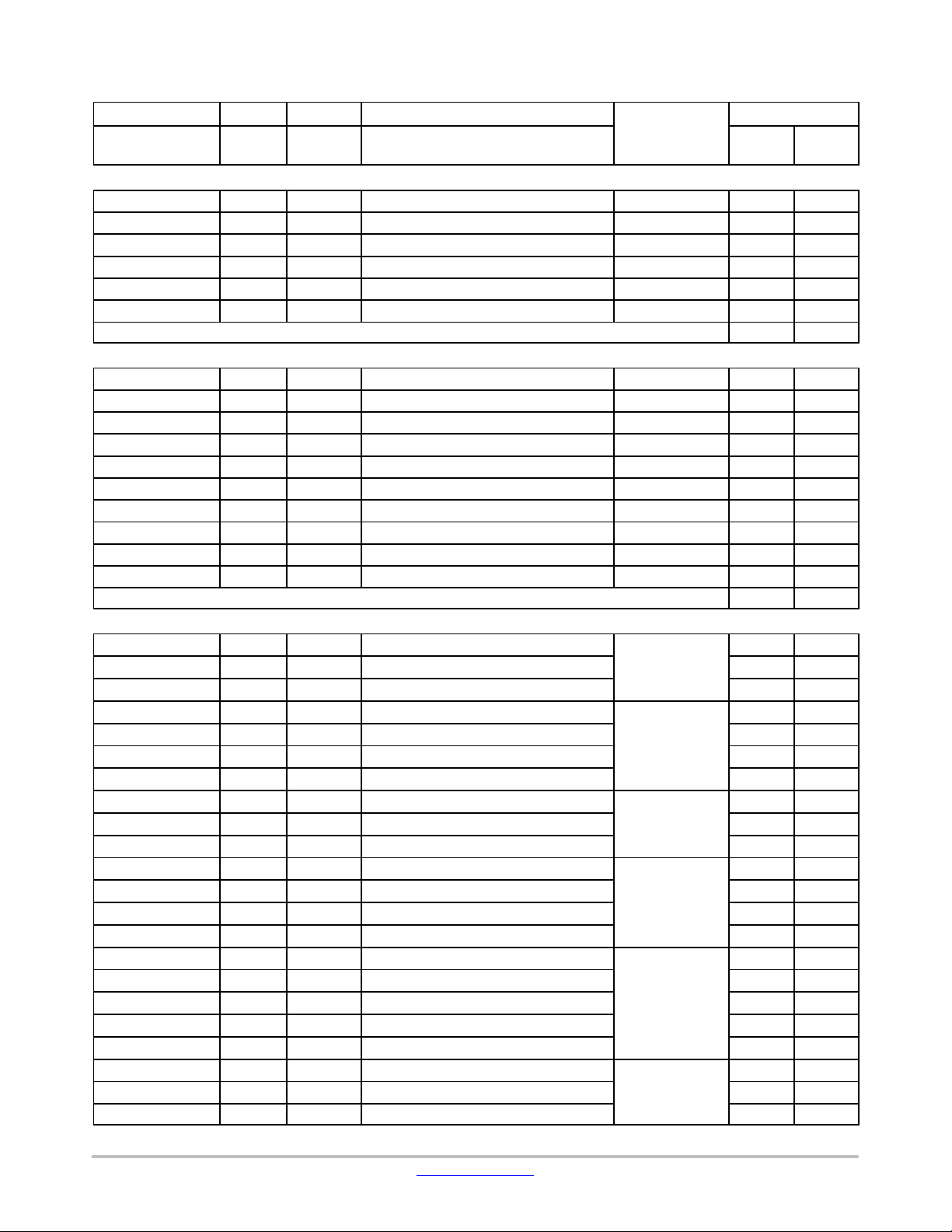

Table 2. CODE AREA (CORTEX−M3) − UNREMAPPED (AFTER RESET)

Cortex−M3−0

Cortex−M3−1

System−

I−Bus

D−Bus

System−

I−Bus

D−Bus

0x1C00

Reserved

0x1A00

External memory 1

0x1800

External memory 0

0x0600

Reserved

0x0500

S−Flash I/F

0x0254

Reserved

0x0250

256 KB Internal ROM

0x0243

Reserved

0x0240

220 KB Internal SRAM

0x023F

32 KB Internal SRAM

0x023C

224 KB

0x0238

256KB

0x0220

1536 KB Internal SRAM

0x021A

384 KB

0x0214

384 KB

0x0210

256 KB Internal SRAM

0x020C

256 KB Internal SRAM

0x0208

256 KB Internal SRAM

0x0204

256 KB Internal SRAM

0x0202

128 KB

0x0200

128 KB

0x0004

Reserved

0x0000

256 KB Internal ROM

LC823455

Address Master / Slave

0000

0000

0000

0000

0000

0000

0000

7000

0000

8000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

(Memory, Cache)

(seg 9)

(seg 8)

480 KB

Internal

SRAM

(seg 7)

(seg 6)

768 KB

Internal

SRAM

(seg 5)

(seg 4)

(seg 3)

(seg 2)

(seg 1)

256 KB

Internal

SRAM

(seg 0)

(seg 7−B)

(seg 7−A)

(seg 5−B)

(seg 5−A)

(seg 0−B)

(seg 0−A)

Bus

Bus

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

DMAC USB20

0000

0000

Shadow Area

www.onsemi.com

d d

11

Page 12

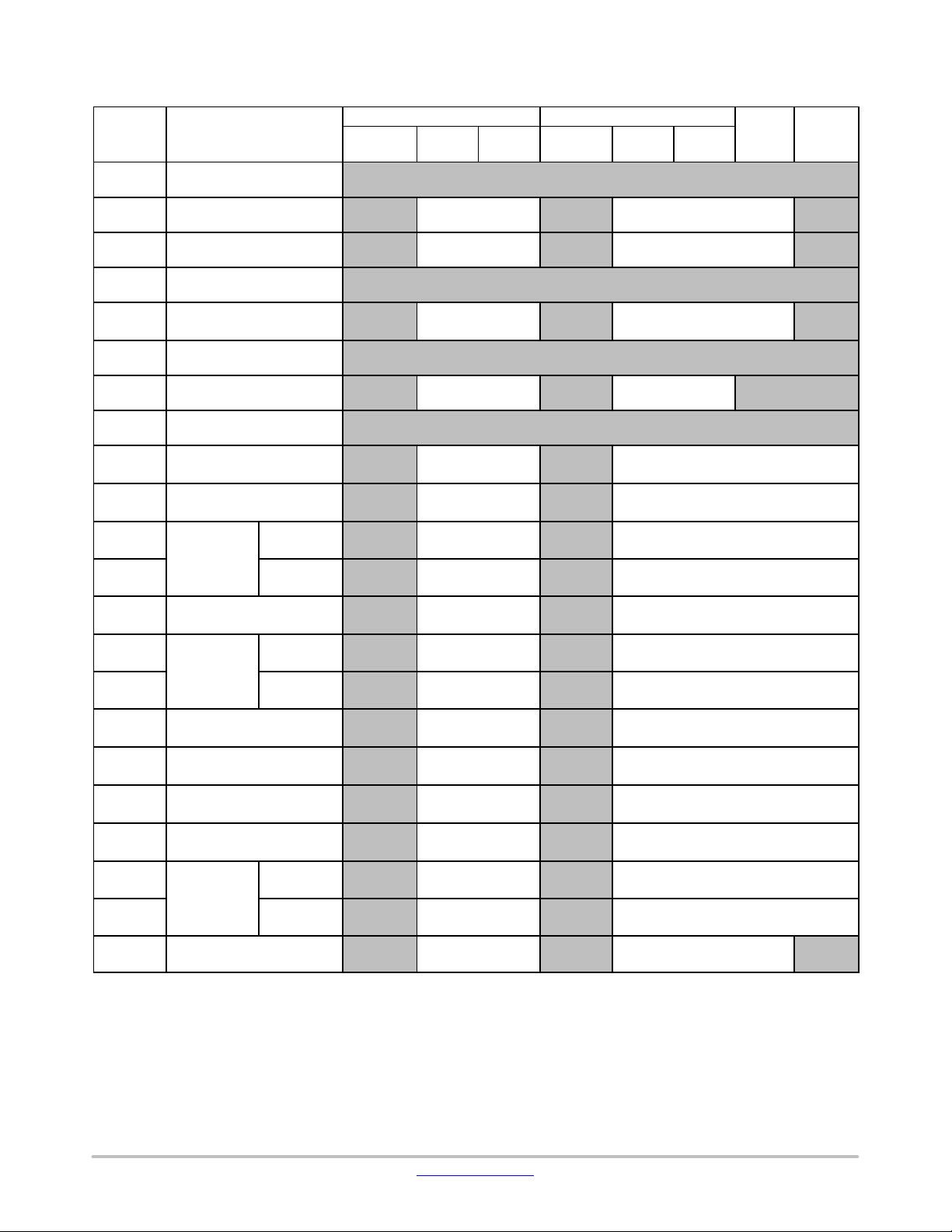

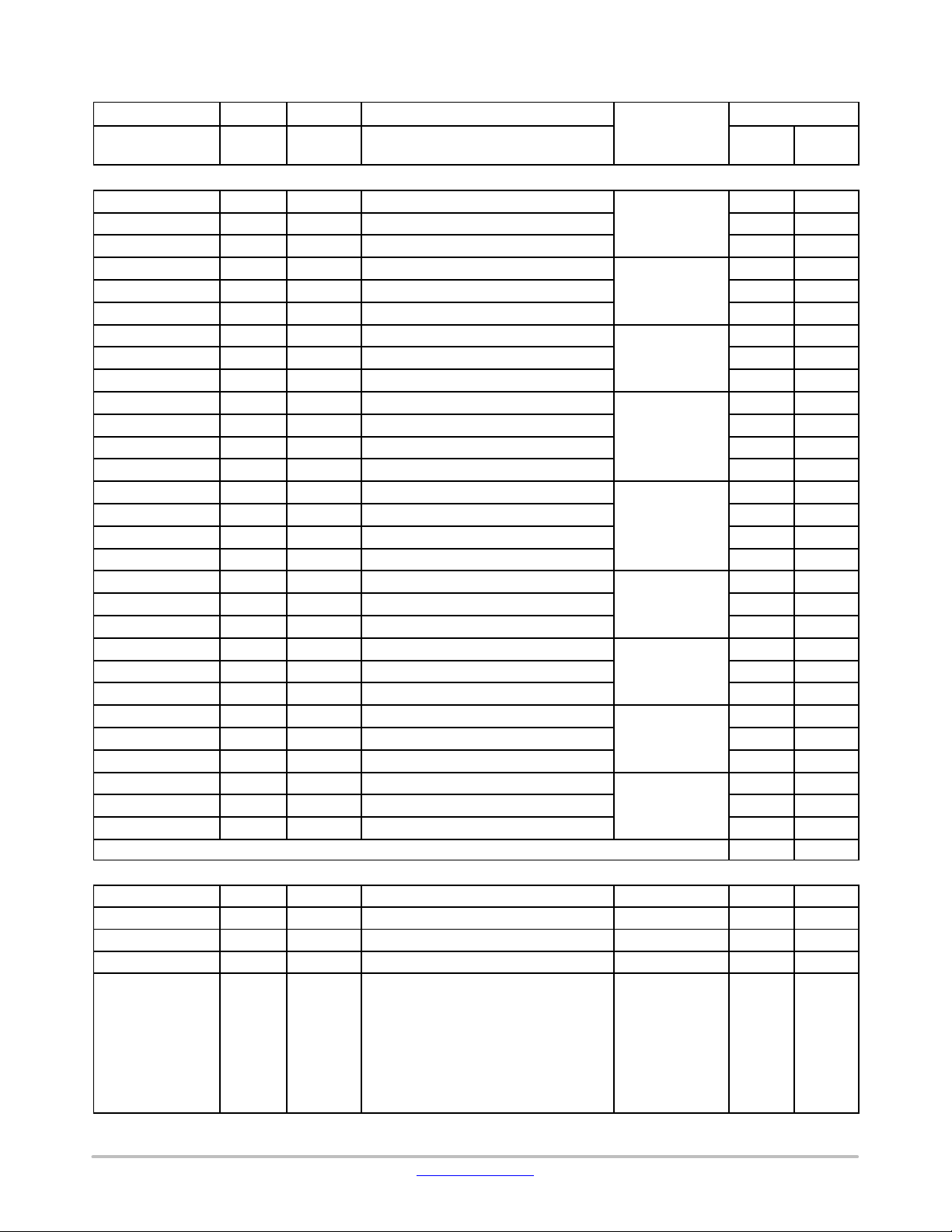

LC823455

Table 3. CODE AREA (CORTEX−M3) − REMAPPED (REMAP[1:0]=2’B01)

Cortex−M3−0

Cortex−M3−1

System−

I−Bus

D−Bus

System−

I−Bus

D−Bus

0x1C00

Reserved

0x1A00

External memory 1

0x1800

External memory 0

0x0600

Reserved

0x0500

S−Flash I/F

0x0254

Reserved

0x0250

256 KB Internal ROM

0x0243

Reserved

0x0240

220 KB Internal SRAM

0x023F

32 KB Internal SRAM

0x023C

224 KB

0x0238

256 KB

0x0220

1536 KB Internal SRAM

0x021A

384 KB

0x0214

384 KB

0x0210

256 KB Internal SRAM

0x020C

256 KB Internal SRAM

0x0208

256 KB Internal SRAM

0x0204

256 KB Internal SRAM

0x0202

128 KB

0x0200

128 KB

0x0004

Reserved

0x0002

128 KB

0x0000

128 KB

Address Master / Slave

0000

0000

0000

0000

0000

0000

0000

7000

0000

8000

0000

0000

(Memory, Cache)

(seg 9)

(seg 8)

480 KB

Internal

SRAM

(seg 7)

(seg 7−B)

(seg 7−A)

Bus

Bus

d d

d d

d d

d d

d d

d d

d d

d d

DMAC USB20

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

768 KB

Internal

SRAM

(seg 5)

256 KB

Internal

SRAM

(seg 0)

256 KB

Internal

SRAM

(seg 0)

Shadow

Area

(seg 6)

(seg 4)

(seg 3)

(seg 2)

(seg 1)

(seg 5−B)

(seg 5−A)

(seg 0−B)

(seg 0−A)

(seg 0−B)

(seg 0−A)

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

12

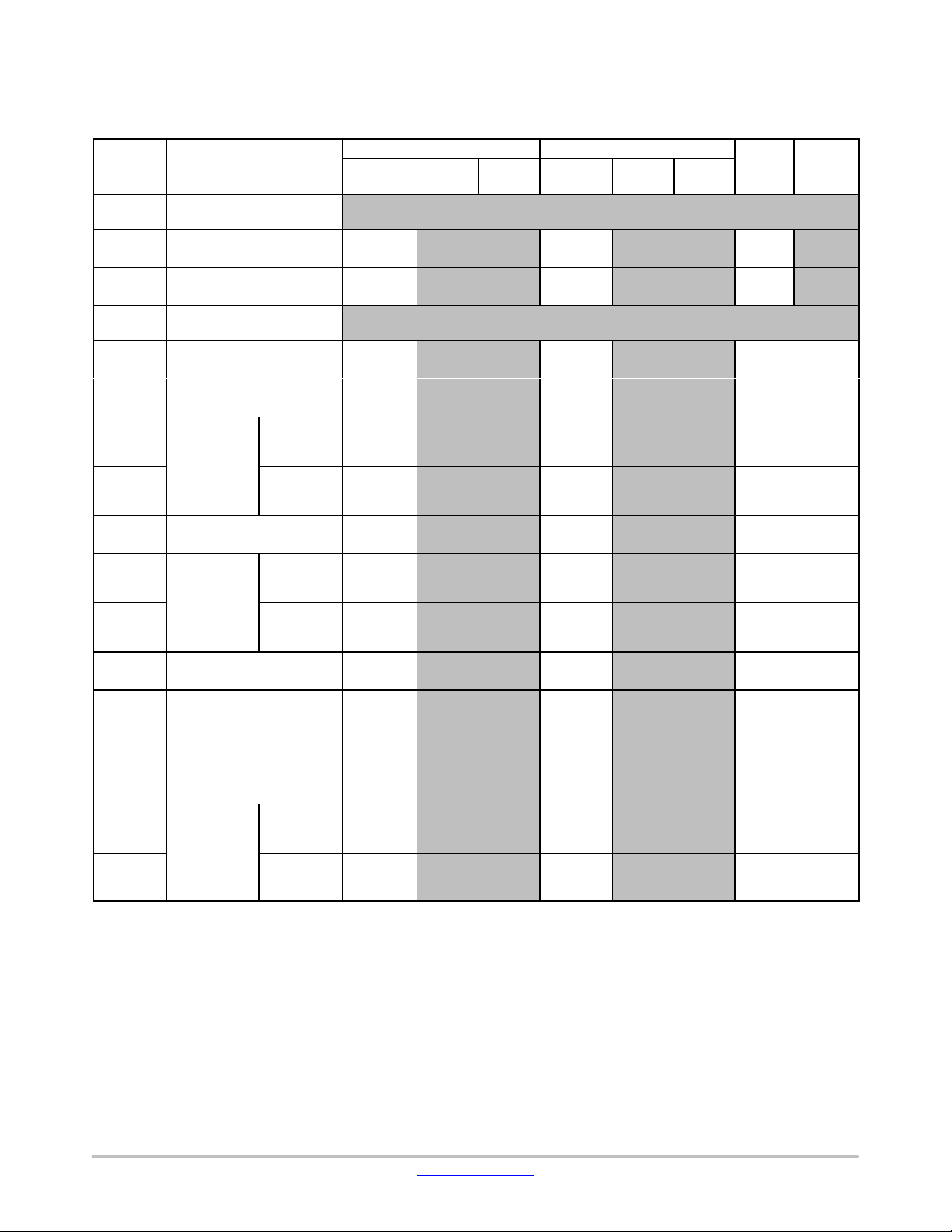

Page 13

LC823455

Table 4. CODE AREA (CORTEX−M3) − REMAPPED (REMAP[1:0]=2’B11)

Cortex−M3−0

Cortex−M3−1

System−

I−Bus

D−Bus

System−

I−Bus

D−Bus

0x1C00

Reserved

0x1A00

External memory 1

0x1800

External memory 0

0x0600

Reserved

0x0500

S−Flash I/F

0x0254

Reserved

0x0250

256 KB Internal ROM

0x0243

Reserved

0x0240

220 KB Internal SRAM

0x023F

32 KB Internal SRAM

0x023C

224 KB

0x0238

256 KB

0x0220

1536KB Internal SRAM

0x021A

384 KB

0x0214

384 KB

0x0210

256KB Internal SRAM

0x020C

256KB Internal SRAM

0x0208

256KB Internal SRAM

0x0204

256KB Internal SRAM

0x0202

128 KB

0x0200

128 KB

0x0000

External memory 0

Address Master / Slave

0000

0000

0000

0000

0000

0000

0000

7000

0000

8000

0000

0000

(Memory, Cache)

(seg 9)

(seg 8)

480 KB

Internal

SRAM

(seg 7)

(seg 7−B)

(seg 7−A)

Bus

Bus

d d

d d

d d

d d

d d

d d

d d

d d

DMAC USB20

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

768 KB

Internal

SRAM

(seg 5)

256 KB

Internal

SRAM

(seg 0)

Shadow Area

(seg 6)

(seg 4)

(seg 3)

(seg 2)

(seg 1)

(seg 5−B)

(seg 5−A)

(seg 0−B)

(seg 0−A)

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

13

Page 14

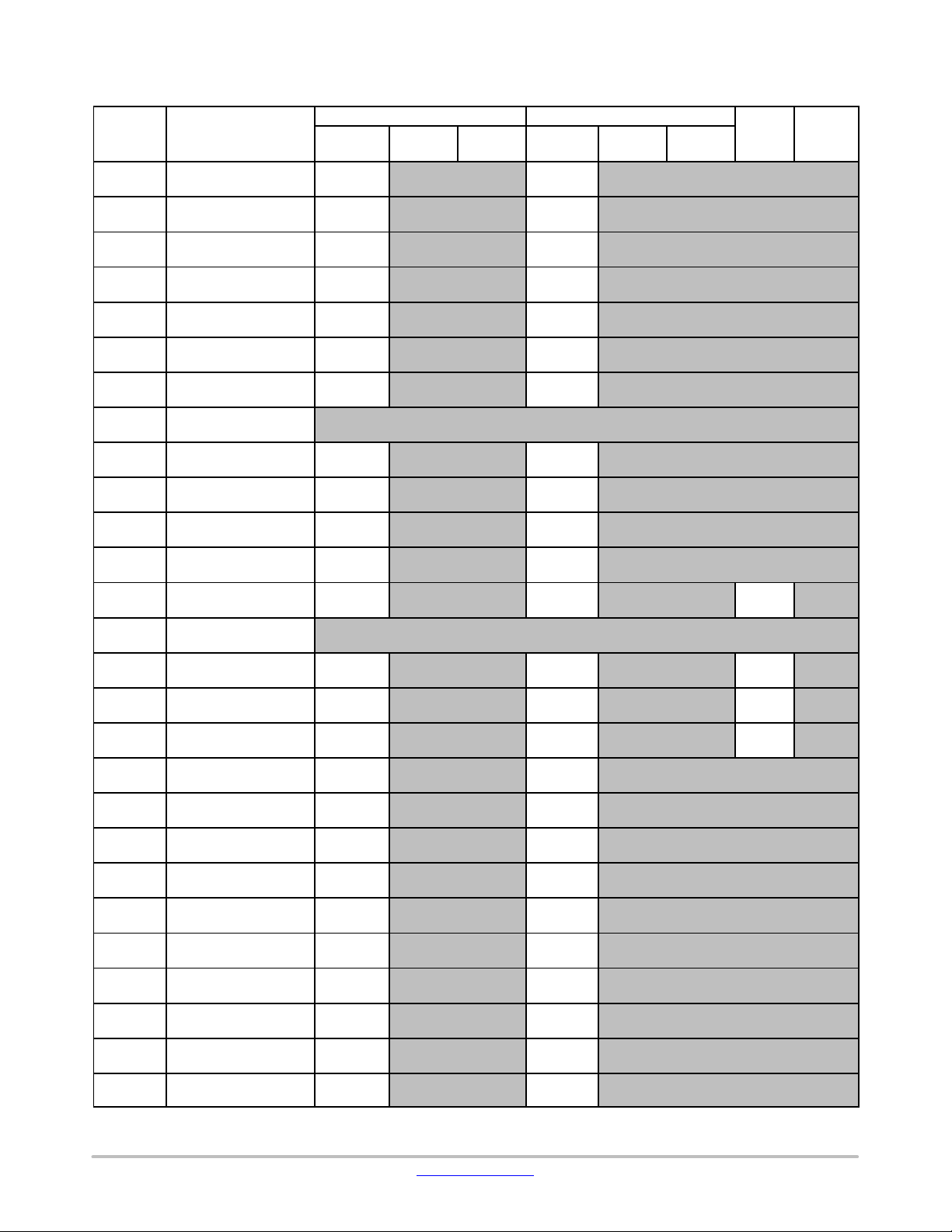

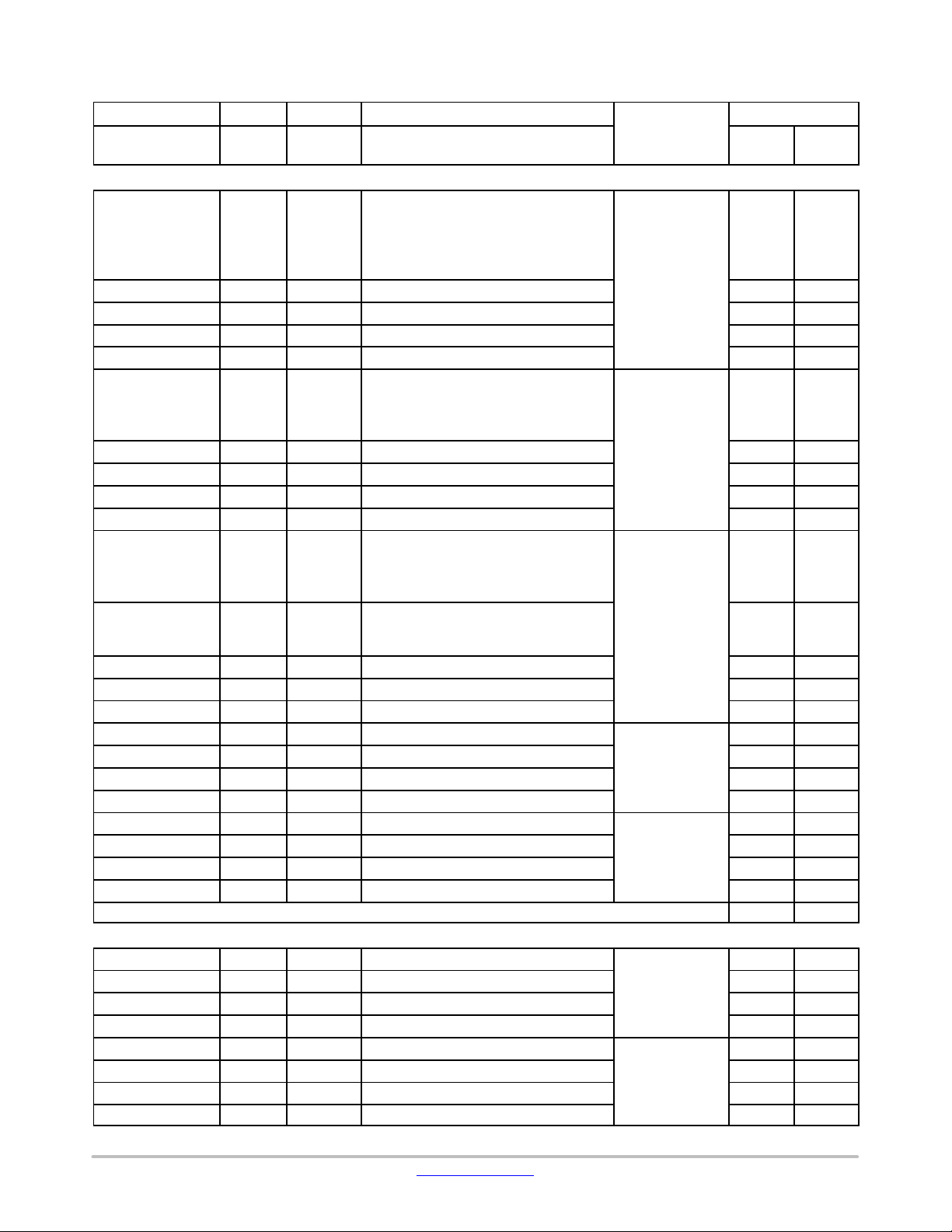

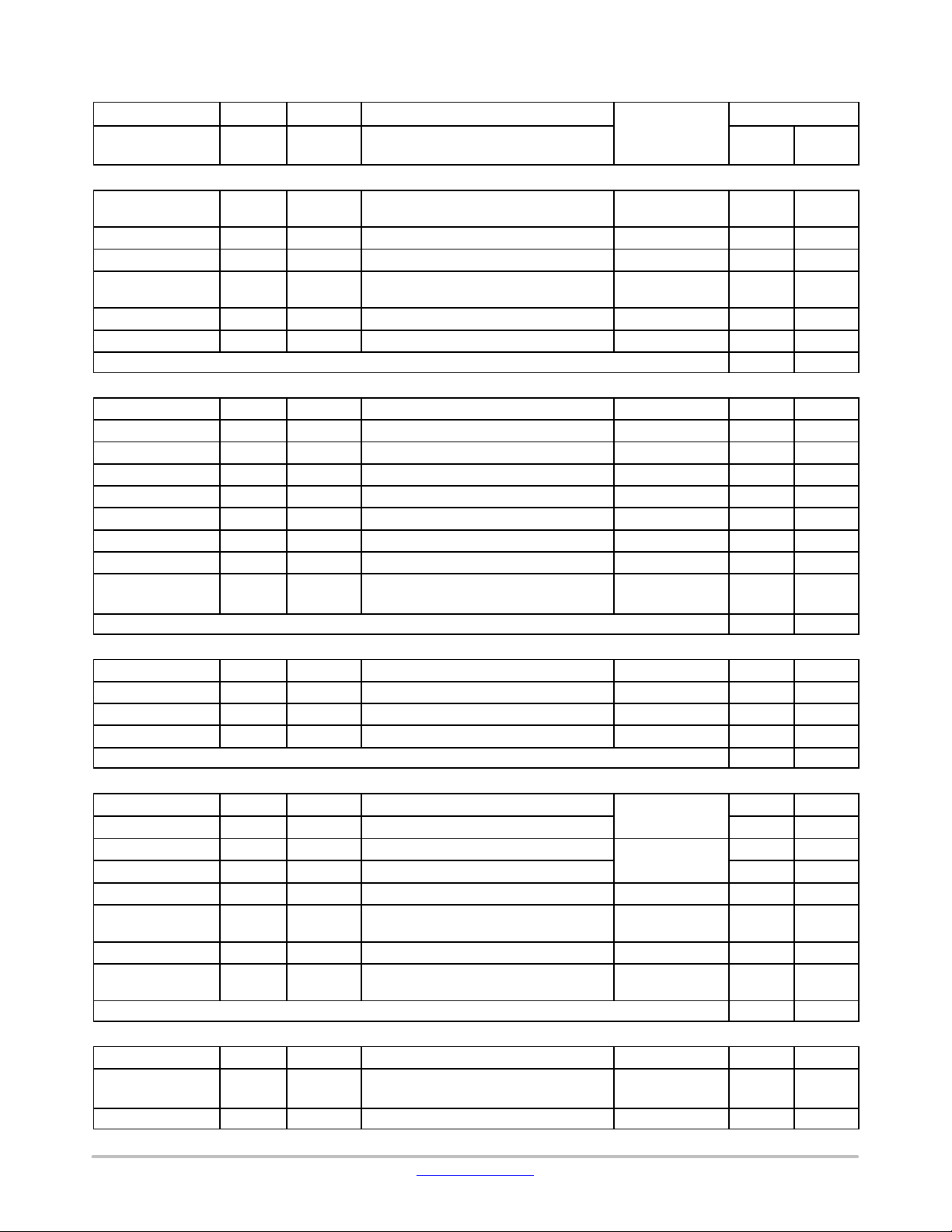

SRAM Area (Cortex−M3)

Table 5. SRAM AREA (CORTEX−M3)

Cortex−M3−0

Cortex−M3−1

System−

I−Bus

D−Bus

System−

I−Bus

D−Bus

0x2600

Reserved

0x2500

S−Flash I/F

0x2400

S−Flash I/F

0x2043

Reserved

0x2040

220 KB Internal SRAM

0x203F

32 KB Internal SRAM

0x203C

224 KB

0x2038

256 KB

0x2020

1536 KB Internal SRAM

0x201A

384 KB

0x2014

384 KB

0x2010

256 KB Internal SRAM

0x200C

256 KB Internal SRAM

0x2008

256 KB Internal SRAM

0x2004

256 KB Internal SRAM

0x2002

128 KB

0x2000

128 KB

LC823455

Address Master / Slave

0000

0000

0000

7000

0000

8000

0000

0000

0000

0000

0000

(Memory, Cache)

(Memory, No Cache)

(seg 9) Shadow area

(seg 8) Shadow area

480 KB

Internal

SRAM

(seg 7)

Shadow

area

(seg 6) Shadow area

768 KB

Internal

SRAM

(seg 5)

Shadow

area

(seg 7−B)

(seg 7−A)

(seg 5−B)

(seg 5−A)

Bus

d d d

d d d

d d d

d d d

d d d

d d d

d d d

d d d

d d d

Bus

DMAC USB20

0000

0000

0000

0000

0000

0000

(seg 4) Shadow area

(seg 3) Shadow area

(seg 2) Shadow area

(seg 1) Shadow area

256 KB

Internal

SRAM

(seg 0)

Shadow

area

(seg 0−B)

(seg 0−A)

d d d

d d d

d d d

d d d

d d d

d d d

www.onsemi.com

14

Page 15

Other Areas (Cortex−M3)

Table 6. OTHER AREAs (CORTEX−M3)

Cortex−M3−0

Cortex−M3−1

System−

I−Bus

D−Bus

System−

I−Bus

D−Bus

0xE010

Reserved

0xE00F

ROM table

0xE00F

CORE REG

0xE004

Reserved

0xE004

TPIU

0xE000

Reserved

0xE000

NVIC

0xE000

Reserved

0xE000

FPB

0xE000

DWT

0xE000

ITM

0x6400

Reserved

0x6400

PSRAM I/F

0x6400

SDRAM CTRL

0x6200

Reserved

0x6000

SDRAM Memory area

0x4008

Reserved

0x4008

RTC

0x4008

UART2

0x4008

UART1

0x4008

UART0

0x4008

I2C1

0x4008

I2C0

0x4008

SPI1

0x4008

SPI0

0x4008

ADC

LC823455

Address Master / Slave

0000

F000

E000

1000

0000

F000

E000

3000

2000

1000

0000

2000

1000

0000

Bus

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

d d d

d d

Bus

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

d

(Note 1)

DMAC USB20

0000

0000

F000

E000

D000

C000

B000

A000

9000

8800

8000

7000

d d d

d d

d d d

d d d

d d d

d d

d d

d d d

d d d

d d d

www.onsemi.com

15

Page 16

LC823455

0x4008

PORT5

0x4008

PORT4

0x4008

PORT3

0x4008

PORT2

0x4008

PORT1

0x4008

PORT0

0x4008

System Controller

0x4006

Reserved

0x4006

Audio Controls

0x4006

MP3 Encoder

0x4006

MP3 Decoder

0x4006

Audio Functions

0x4006

Audio Buffer

0x4004

Reserved

0x4004

SD2

0x4004

SD1

0x4004

SD0

0x4004

Plain Timer2

0x4004

Plain Timer1

0x4004

Plain Timer0

0x4004

Multiple Timer3

0x4004

Multiple Timer2

0x4004

Multiple Timer1

0x4004

Multiple Timer0

0x4004

Audio PLL

0x4004

System PLL

0x4004

OSC System

Table 6. OTHER AREAs (CORTEX−M3) (continued)

Cortex−M3−1Cortex−M3−0

System−

Address USB20DMAC

6000

5000

4000

3000

2000

1000

0000

5000

4000

3000

2000

1000

0000

Master / Slave

Bus

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d d

D−BusI−Bus

System−

Bus

D−BusI−Bus

D000

C000

B000

A000

9000

8000

7000

6000

5000

4000

3000

2000

1000

0000

d d d

d d d

d d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

16

Page 17

LC823455

0x4002

Reserved

0x4001

USB2.0 FIFO

0x4000

Reserved

0x4000

DSP CMDIF

0x4000

MUTEX REG

0x4000

DMAC

0x4000

INTC

0x4000

USB2.0 CTL

0x4000

S−Flash I/F

0x4000

External MEM CTL

Table 6. OTHER AREAs (CORTEX−M3) (continued)

Cortex−M3−1Cortex−M3−0

System−

Address USB20DMAC

0000

0000

7000

6000

5000

4000

3000

2000

1000

0000

1. Access from internal peripheral bus(AHB/APB)

Master / Slave

Bus

d d

d d

d d

d d

d d

d d

d d

d d

D−BusI−Bus

System−

Bus

D−BusI−Bus

www.onsemi.com

17

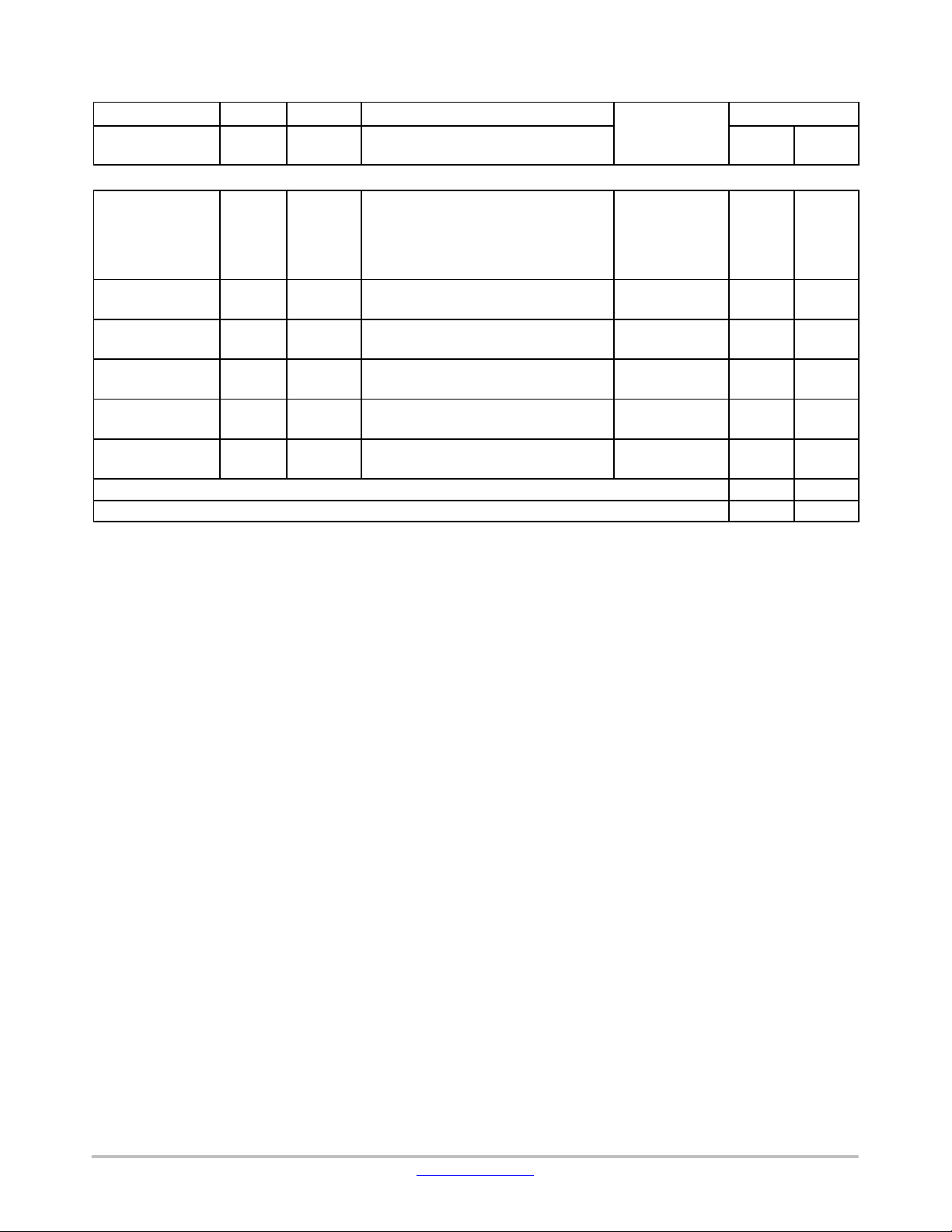

Page 18

LPDSP32

Table 7. LPDSP32 − DMA

LPDSP32

DMA

0x40 0000

Reserved

0x3F 8000

32 KB Internal SRAM (seg 8)

0x3C 0000

224 KB (seg 7−B)

0x38 0000

256 KB (seg 7−A)

0x20 0000

1536 KB Internal SRAM (seg 6)

0x1A 0000

384 KB (seg 5−B)

0x14 0000

384 KB (seg 5−A)

0x10 0000

256 KB Internal SRAM (seg 4)

0x0C 0000

256 KB Internal SRAM (seg 3)

0x08 0000

256 KB Internal SRAM (seg 2)

0x04 0000

256 KB Internal SRAM (seg 1)

0x02 0000

128 KB (seg 0−B)

0x00 0000

128 KB (seg 0−A)

Table 8. LPDSP32 – DMB

LPDSP32

DMB

0xC0 0000

Reserved

0xBF 8000

32 KB Internal SRAM (seg 8)

0xBC 0000

224 KB (seg 7−B)

0xB8 0000

256 KB (seg 7−A)

0xA0 0000

1536 KB Internal SRAM (seg 6)

0x9A 0000

384 KB (seg 5−B)

0x94 0000

384 KB (seg 5−A)

0x90 0000

256 KB Internal SRAM (seg 4)

0x8C 0000

256 KB Internal SRAM (seg 3)

0x88 0000

256 KB Internal SRAM (seg 2)

0x84 0000

256 KB Internal SRAM (seg 1)

0x82 0000

128 KB (seg 0−B)

0x80 0000

128 KB (seg 0−A)

LC823455

Address Master / Slave

480 KB Internal SRAM (seg 7)

768 KB Internal SRAM (seg 5)

256 KB Internal SRAM (seg 0)

d

d

d

d

d

d

d

d

d

d

d

d

Address Master / Slave

480 KB Internal SRAM (seg 7)

768 KB Internal SRAM (seg 5)

256 KB Internal SRAM (seg 0)

d

d

d

d

d

d

d

d

d

d

d

d

www.onsemi.com

18

Page 19

LC823455

Table 9. LPDSP32 − DMIO

LPDSP32

DMIO

0xF0 2000

Reserved

0xF0 1000

PSRAM I/F

0xF0 0000

SDRAM CTRL

0xD0 0000

SDRAM Memory Area

0xC6 5000

Reserved

0xC6 4000

Audio Controls

0xC6 3000

MP3 Encoder

0xC6 2000

MP3 Decoder

0xC6 1000

Audio Functions

0xC6 0000

Audio Buffer

0xC4 A000

Reserved

0xC4 9000

Plain Timer2

0xC4 8000

Plain Timer1

0xC4 7000

Plain Timer0

0xC4 6000

Multiple Timer3

0xC4 5000

Multiple Timer2

0xC4 4000

Multiple Timer1

0xC4 3000

Multiple Timer0

0xC4 2000

Audio PLL

0xC4 1000

System PLL

0xC4 0000

OSC System

0xC0 7000

Reserved

0xC0 6000

DSP CMDIF

0xC0 5000

MUTEX REG

0xC0 4000

DMAC

0xC0 3000

INTC

0xC0 0000

Reserved

Address Master / Slave

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

d

www.onsemi.com

19

Page 20

LC823455

Table 10. LPDSP32 − PM

LPDSP32

PM

0x50 3332

Reserved

0x50 0000

32 KB Internal SRAM (seg 8)

0x4B 0000

Reserved

224 KB (seg 7−B)

256 KB (seg 7−A)

0x41 9998

Reserved

0x38 0000

1536 KB Internal SRAM (seg 6)

0x34 CCCC

Reserved

384 KB (seg 5−B)

384 KB (seg 5−A)

0x29 9998

Reserved

0x28 0000

256 KB Internal SRAM (seg 4)

0x21 9998

Reserved

0x20 0000

256 KB Internal SRAM (seg 3)

0x19 9998

Reserved

0x18 0000

256 KB Internal SRAM (seg 2)

0x11 9998

Reserved

0x10 0000

256 KB Internal SRAM (seg 1)

0x09 9998

Reserved

128 KB (seg 0−B)

128 KB (seg 0−A)

0x01 6000

Reserved

0x00 0000

220 KB Internal SRAM (seg 9)

Address Master / Slave

0x48 0000 480 KB Internal SRAM (seg 7)

0x30 0000 768 KB Internal SRAM (seg 5)

d

d

d

0x08 0000 256 KB Internal SRAM (seg 0)

2. PM of LPDSP32 cannot access internal SRAM seg5, 6, and 7.

d

d

d

d

d

www.onsemi.com

20

Page 21

LC823455

Table 11. TERMINAL FUNCTIONS

Terminal Name

Polarity

Direction

Function

Available(d)

Multiplexed

XA

RB

JTAG/SWD

TDO

−OJTAG test data output

SDWP1

Pos

I

SD I/F Ch1 write protect

GPIO21

−BGPIO

EXTINT21

−IExternal Interrupt 2−bit1

TDI

−IJTAG test data input

SDCD1

Neg

I

SD I/F Ch1 detect

SWO

−Oserial wire view data

GPIO20

−BGPIO

EXTINT20

−IExternal Interrupt 2−bit0

TMS

−IJTAG test data select

SDWP2

Pos

I

SD I/F Ch2 write protect

GPIO28

−BGPIO

EXTINT28

−IExternal Interrupt 2−bit8

TCK

Pos

I

JTAG test clock

SDCD2

Neg

I

SD I/F Ch2 detect

GPIO29

−BGPIO

EXTINT29

−IExternal Interrupt 2−bit9

SWDCLK

Pos

I

Serial wire clock

DMCKO0B

−ODigital Mic Ch0 Clock B Output

GPIO58

−BGPIO

EXTINT58

−IExternal Interrupt 5−bit8

SWDIO

−BSerial wire Data

DMDIN0B

−IDigital Mic Ch0 Data B Input

GPIO59

−BGPIO

EXTINT59

−IExternal Interrupt 5−bit9

Sum

6

6

RTC

XIN32K

Pos

I

32.768KHz XTAL Input (XTRTC)

VddRTC

XOUT32K

−O32.768KHzXTAL Output (XTRTC)

VddRTC

VDET

Neg

I

RTC power detect Input

VddRTC

RTCINT

Neg

O

RTC Interrupt Output (Normal: Hiz, Inter-

VddRTC

BACKUPB

Neg

I

RTC backup mode input

VddRTC

KEYINT[2]

−IRTC KEY input can be used when KeyInt

VddRTC

KEYINT[1:0]

−IRTC KEY input can be used when KeyInt

VddRTC

TERMINAL FUNCTIONS

XA: Package Code = “XA”, RB: Package Code = “RB”, (RB is under planning).

Function

IO POWER

VddSD1

VddSD1

Vdd2

Vdd2

Vdd2

Vdd2

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

rupt enabled:Low Output)

d

Bonded with VDET internally for “XA”

RTC mode

d d

RTC mode

www.onsemi.com

21

Page 22

Table 11. TERMINAL FUNCTIONS

Terminal Name

RTCMODE

−IRTC mode input (Note 3)

VddRTC

VddRTC

−PRTC power supply

VssRTC

−PRTC ground

Sum

8

10

EXTERNAL INTERRUPT/GPIO

SDRADDR12

−OSDRAM address

GPIO2A

−BGPIO

EXTINT2A

−IExternal Interrupt 2−bit10

SCL1

−OI2C ch1 Clock (open drain output )

GPIO2B

−BGPIO

EXTINT2B

−IExternal Interrupt 2−bit11

SDA1

−BI2C ch1 Data (open drain output )

GPIO2C

−BGPIO

EXTINT2C

−IExternal Interrupt 2−bit12

SDRADDR11

−OSDRAM address

DMCKO0A

−ODigital Mic Ch0 Clock A Output

GPIO2D

−BGPIO

EXTINT2D

−IExternal Interrupt 2−bit13

EXTINT2E

−IExternal Interrupt 2−bit14

GPIO2E

−BGPIO

EXTINT2F

−IExternal Interrupt 2−bit15

GPIO2F

−BGPIO

Sum

5

5

SPI (SERIAL I/F CH0)

SCK0

Neg

B

Serial I/F Ch0 Clock

GPIO1D

−BGPIO

EXTINT1D

−IExternal Interrupt 1−bit13

SDI0

−ISerial I/F Ch0 Data Input

GPIO1E

−BGPIO

EXTINT1E

−IExternal Interrupt 1−bit14

SDO0

−OSerial I/F Ch0 Data Output

GPIO1F

−BGPIO

EXTINT1F

−IExternal Interrupt 1−bit15

Sum

3

3

S−FLASH I/F / SD I/F CH0 (Note 4)

SFCK

Neg

O

Serial Flash I/F Clock

Multiplexed

Function

RTC

(continued)

Set General or KeyInt RTC mode

RTCMODE =

“0” : KeyInt RTC mode

“1” : General RTC mode

Bonded to “0” internally for “XA”

LC823455

FunctionDirectionPolarity

Available(d)

IO POWER

d d d

d d d

Vdd2

RBXA

d

* During Internal ROM boot, this terminal

is used as the boot monitor signal.

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

(QSPI Clock)

www.onsemi.com

22

Vdd2

d d

Page 23

Table 11. TERMINAL FUNCTIONS

Terminal Name

GPIO0D

−BGPIO

EXTINT0D

−IExternal Interrupt 0−bit13

SDCLK0

−OSD I/F Ch0 Clock Output

SFDI(QIO0)

−

I(B)

Serial Flash I/F Data input

GPIO0E

−BGPIO

EXTINT0E

−IExternal Interrupt 0−bit14

SDAT00

−BSD I/F Ch0 Data0

SFDO(QIO1)

−

O(B)

Serial Flash I/F Data output

GPIO0F

−BGPIO

EXTINT0F

−IExternal Interrupt 0−bit15

SDAT01

−BSD I/F Ch0 Data1

SFWP(QIO2)

Neg

O(B)

Serial Flash I/F write protect

GPIO11

−BGPIO

EXTINT11

−IExternal Interrupt 1−bit1

SDAT02

−BSD I/F Ch0 Data2

SFHOLD(QIO3)

Neg

O(B)

Serial Flash I/F hold

GPIO12

−BGPIO

EXTINT12

−IExternal Interrupt 1−bit2

SDAT03

−BSD I/F Ch0 Data3

Sum

5

5

I2C

SCL0

−OI2C ch0 Clock (open drain output )

GPIO07

−BGPIO

EXTINT07

−IExternal Interrupt 0−bit7

SDA0

−BI2C ch0 Data (open drain output )

GPIO08

−BGPIO

EXTINT08

−IExternal Interrupt 0−bit8

Sum

2

2

Multiplexed

Function

S−FLASH I/F / SD I/F CH0 (Note 4)

(continued)

(QSPI Data 0)

(QSPI Data 1)

(QSPI Data 2)

(QSPI Data 3)

LC823455

FunctionDirectionPolarity

IO POWER

Vdd2

Vdd2

Vdd2

Vdd2

Available(d)

RBXA

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

23

Vdd2

Vdd2

d d

d d

d d

d d

d d

d d

Page 24

Table 11. TERMINAL FUNCTIONS

Terminal Name

UART

TXD1

−OUART Ch1 transmit Data

SDAT20

−BSD I/F Ch2 Data 0

GPIO04

−BGPIO

EXTINT04

−IExternal Interrupt 0−bit4

RXD1

−IUART Ch1 receive Data

SDAT21

−BSD I/F Ch2 Data 1

GPIO05

−BGPIO

EXTINT05

−IExternal Interrupt 0−bit5

CTS1

Neg

I

UART Ch1 clear to send

SDAT22

−BSD I/F Ch2 Data 2

RXD0

−IUART Ch0 receive Data

GPIO56

−BGPIO

EXTINT56

−IExternal Interrupt 5−bit6

RTS1

Neg

O

UART Ch1 request to send

SDAT23

−BSD I/F Ch2 Data 3

TXD0

−OUART Ch0 transmit Data

GPIO57

−BGPIO

EXTINT57

−IExternal Interrupt 5−bit7

TXD2

−OUART Ch2 transmit Data

TIOCA10

−BMTM1 Ch0A

GPIO0B

−BGPIO

EXTINT0B

−IExternal Interrupt 0−bit11

RXD2

−IUART Ch2 receive Data

TIOCA11

−BMTM1 Ch1A

GPIO0C

−BGPIO

EXTINT0C

−IExternal Interrupt 0−bit12

Sum

6

6

TIMER

TIOCA00

−BMTM0 Ch0A

SDCLK2

−OSD I/F Ch2 Clock Output

PHI0

−OSystem Clock Output 0

GPIO09

−BGPIO

EXTINT09

−IExternal Interrupt 0−bit9

Multiplexed

Function

(continued)

LC823455

FunctionDirectionPolarity

IO POWER

Available(d)

RBXA

− target signal of pulse−length−reader

function

− output of sentinel−inform−function

− output of PWM output

− target signal of pulse−length−reader

function

− output of sentinel−inform−function

− output of PWM output

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

− target signal of pulse−length−reader

function

− output of sentinel−inform−function

− output of PWM output

www.onsemi.com

24

Vdd2

d d

d d

d d

d d

d d

Page 25

Table 11. TERMINAL FUNCTIONS

Terminal Name

TIOCA01

−BMTM0 Ch1A

SDCMD2

−BSD I/F Ch2 command line

PHI1

−OSystem Clock Output 1

GPIO0A

−BGPIO

EXTINT0A

−IExternal Interrupt 0−bit10

TIOCB00

−BMTM0 Ch0B

DIN1

−IPCM1 Data Input

DMDIN0A

−IDigital Mic Ch0 Data A Input

GPIO02

−BGPIO

EXTINT02

−IExternal Interrupt 0−bit2

TIOCB01

−BMTM0 Ch1B

SFQSCS

Neg

O

Serial Flash I/F QSPI chip select

GPIO03

−BGPIO

EXTINT03

−IExternal Interrupt 0−bit3

SDCMD0

−BSD I/F Ch0 command line

TCLKA0

−IMTM0 external Clock A

BCK1

−BPCM1 bit Clock

GPIO00

−BGPIO

EXTINT00

−IExternal Interrupt 0−bit0

TCLKB0

−IMTM0 external Clock B

LRCK1

−BPCM1 LR Clock

GPIO01

−BGPIO

EXTINT01

−IExternal Interrupt 0−bit1

Sum

6

6

PCM I/F

MCLK0

Pos

B

PCM0 maser Clock

MCLK1

Pos

B

PCM1 master Clock

GPIO18

−BGPIO

EXTINT18

−IExternal Interrupt 1−bit8

BCK0

−BPCM0 bit Clock

DMCKO0B

−

O

Digital Mic Ch0 Clock B Output

GPIO19

−BGPIO

EXTINT19

−IExternal Interrupt 1−bit9

Multiplexed

Function

TIMER

(continued)

− target signal of pulse−length−reader

− output of sentinel−inform−function

− output of PWM output

− target signal of pulse−length−reader

− output of sentinel−inform−function

− target signal of pulse−length−reader

− output of sentinel−inform−function

During Serial Flash Boot, this is used as

chip select of Serial Flash

function

function

function

LC823455

FunctionDirectionPolarity

IO POWER

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Available(d)

RBXA

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

25

Vdd2

Vdd2

d d

d d

d d

d d

d d

d d

d d

d d

Page 26

Table 11. TERMINAL FUNCTIONS

Terminal Name

LRCK0

−BPCM0 LR Clock

DMDIN0B

−IDigital Mic Ch0 Data B Input

GPIO1A

−BGPIO

EXTINT1A

−IExternal Interrupt 1−bit10

DIN0

−IPCM0 Data Input

DMDIN0A

−IDigital Mic Ch0 Data A Input

GPIO1B

−BGPIO

EXTINT1B

−IExternal Interrupt 1−bit11

DOUT0

−OPCM0 Data Output

DMCKO0A

−ODigital Mic Ch0 Clock A Output

GPIO1C

−BGPIO

EXTINT1C

−IExternal Interrupt 1−bit12

BCK1

−BPCM1 bit Clock

GPIO13

−BGPIO

EXTINT13

−IExternal Interrupt 1−bit3

LRCK1

−BPCM1 LR Clock

GPIO14

−BGPIO

EXTINT14

−IExternal Interrupt 1−bit4

DOUT1

−OPCM1 Data Output

GPIO15

−BGPIO

EXTINT15

−IExternal Interrupt 1−bit5

Sum

8

8

SD IF

SDCLK0

−OSD I/F Ch0 Clock Output

Vdd2

SDCMD0

−BSD I/F Ch0 command line

Vdd2

SDAT0[3:0]

−BSD I/F Ch0 Data

Vdd2

SDCLK1

−OSD I/F Ch1 Clock Output

GPIO22

−BGPIO

EXTINT22

−IExternal Interrupt 2−bit2

SDCMD1

−BSD I/F Ch1 command line

GPIO23

−BGPIO

EXTINT23

−IExternal Interrupt 2−bit3

SDAT1[3:0]

−BSD I/F Ch1 Data

GPIO2[7:4]

−BGPIO

EXTINT2[7:4]

−IExternal Interrupt 2−bit7 to bit4

Sum

6

12

Multiplexed

Function

PCM I/F

(continued)

LC823455

FunctionDirectionPolarity

IO POWER

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Available(d)

RBXA

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

VddSD1

VddSD1

VddSD1

d

d

d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

26

Page 27

Table 11. TERMINAL FUNCTIONS

Terminal Name

PSEUDO SRAM

PSM_SCK

−OP−SRAM I/F Clock Output

Vdd2

PSM_CS

Neg

O

P−SRAM I/F chip select Output

Vdd2

PSM_SDI(DAT0)

−

I(B)

P−SRAM I/F Data input(QPI Data0)

Vdd2

PSM_SDO(DAT1)

−

O(B)

P−SRAM I/F Data output(QPI Data1)

Vdd2

PSM_DAT2

−BP−SRAM I/F QPI Data 2

Vdd2

PSM_DAT3

−BP−SRAM I/F QPI Data 3

Vdd2

Sum

0

0

SDRAM I/F

SDRCLK

Neg

O

SDRAM Clock Output

Vdd2

SDRCKE

Pos

O

SDRAM Clock enable Output

Vdd2

SDRCS

Neg

O

SDRAM chip select Output

Vdd2

SDRWE

Neg

O

SDRAM write enable Output

Vdd2

SDRCAS

Neg

O

SDRAM CAS Output

Vdd2

SDRRAS

Neg

O

SDRAM RAS Output

Vdd2

SDRDQM[1:0]

Pos

O

SDRAM Data mask byte lane select

Vdd2

SDRADDR[10:0]

−OSDRAM address (Note 5)

Vdd2

SDRBA[1:0]

−OSDRAM bank select

Vdd2

SDRDATA[15:0]

−BSDRAM Data

Vdd2

Sum

0

0

EXTERNAL MEMORY I/F

NCS0

Neg

O

chip select0

GPIO06

−BGPIO

EXTINT06

−−IExternal Interrupt 0−bit6

NCS1

Neg

O

chip select1

(Note 6)

(Note 6)

RXD0

−IUART Ch0 receive Data

GPIO10

−BGPIO

EXTINT10

−IExternal Interrupt 1−bit0

NRD

Neg

O

read enable

(Note 6)

(Note 6)

GPIO17

−BGPIO

EXTINT17

−IExternal Interrupt 1−bit7

NWRENWRL

Neg

O

write enable, write enable low

(Note 6)

(Note 6)

DIN0

−IPCM0 Data Input

GPIO30

−BGPIO

EXTINT30

−IExternal Interrupt 3−bit0

NHBNWRH

Neg

O

high byte select, write enable high

(Note 6)

(Note 6)

TXD0

−OUART Ch0 transmit Data

DOUT0

−OPCM0 Data Output

GPIO31

−BGPIO

EXTINT31

−IExternal Interrupt 3−bit1

NLBEXA0

−Olow byte select, address0

(Note 6)

(Note 6)

GPIO16

−BGPIO

EXTINT16

−IExternal Interrupt 1−bit6

Multiplexed

Function

(continued)

LC823455

FunctionDirectionPolarity

IO POWER

Available(d)

RBXA

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

27

Page 28

Table 11. TERMINAL FUNCTIONS

Terminal Name

EXA[20:15]

−Oaddress

GPIO4[5:0]

−BGPIO

EXTINT4[5:0]

−IExternal Interrupt 4−bit5 to bit0

EXA[14:9]

−Oaddress

GPIO3[F:A]

−BGPIO

EXTINT3[F:A]

−IExternal Interrupt 3−bit15 to bit10

EXA[8:5]

−Oaddress

GPIO3[9:6]

−BGPIO

EXTINT3[9:6]

−IExternal Interrupt 3−bit9 to bit6

EXA4

−Oaddress

DOUT1

−OPCM1 Data Output

GPIO35

−BGPIO

EXTINT35

−IExternal Interrupt 3−bit5

EXA3

−Oaddress

(Note 6)

DIN1

−IPCM1 Data Input

GPIO34

−BGPIO

EXTINT34

−IExternal Interrupt 3−bit4

EXA[2:1]

−Oaddress

GPIO3[3:2]

−BGPIO

EXTINT3[3:2]

−IExternal Interrupt 3−bit3 to bit2

EXD[7:0]

−BData

GPIO4[D:6]

−BGPIO

EXTINT4[D:6]

−IExternal Interrupt 4−bit13 to bit6

EXD[15:10]

−BData

GPIO5[5:0]

−BGPIO

EXTINT5[5:0]

−IExternal Interrupt 5−bit5 to bit0

EXD[9:8]

−BData

GPIO4[F:E]

−BGPIO

EXTINT4[F:E]

−IExternal Interrupt 4−bit15 to bit14

Sum

5

6

XTAL, PLL

XIN1

−IXTAL input (XT1)

VddXT1

XOUT1

−OXTAL output (XT1)

VddXT1

VddXT1

−PXTAL power supply (XT1)

−

VssXT1

−PXTAL ground (XT1)

−

XTALINFO[1: 0]

−BXTALINFO[1: 0] =

Vdd2

Multiplexed

Function

EXTERNAL MEMORY I/F

(continued)

LC823455

FunctionDirectionPolarity

IO POWER

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Vdd2

Available(d)

RBXA

d

d

d

Vdd2

Vdd2

Vdd2

d d

d d

d d

d d

“00” : 24 MHz

“01” : 12 MHz

“10” : 19.2 MHz

“11” : reserved

Used for determining clock frequency set-

ting during internal ROM boot.

Bonding “00” internally.

www.onsemi.com

28

Page 29

Table 11. TERMINAL FUNCTIONS

Terminal Name

VCNT1

−OPLL1 VCO control

AVddPLL1

AVddPLL1

−PPLL1 analog power supply

−

AVssPLL1

−PPLL1 analog power ground

−

VCNT2

−OPLL2 VCO control

AVddPLL2

AVddPLL2

−PPLL2 analog power supply

−

AVssPLL2

−PPLL2 analog power ground

−

Sum

8

8

USB−PHY

USBDP

−BUSB D+

AVddUSBPHY2

USBDM

−BUSB D−

AVddUSBPHY2

USBEXT02

−BUSB reference resistor

AVddUSBPHY18

USBVBUS

−IUSB 5V VBUS detection

−

USBID

−BUSB identifier

AVddUSBPHY18

DVddUSBPHY1

−PUSB−PHY 1.0V digital power supply

−

AVddUSBPHY2

−PUSB−PHY 3.3V analog power supply

−

AVddUSBPHY18

−PUSB−PHY 1.8V analog power supply

−

AVssUSBPHY

−PUSB−PHY ground

−

Sum

10

10

12 BIT ADC

SIN[7: 3]

−IADC input ch7−3

AVddADC

SIN[2: 0]

−IADC input ch2−0

AVddADC

AVddADC

−PADC analog power supply

−

AVssADC

−PADC analog power ground

−

Sum

5

10

CLASS−D AMP

LOUT

−OLch Class D AMP Output

GPLOUT

−OGeneral purpose Output (GPO)

ROUT

−ORch Class D AMP Output

GPROUT

−OGeneral purpose Output (GPO)

AVddDAMPL

−PLch Class D AMP analog power supply

−

AVddDAMPR

−PRch Class D AMP analog

−

AVssDAMPL

−PLch Class D AMP analog power ground

−

AVssDAMPR

−PRch Class D AMP analog

−

Sum

6

6

OTHER, POWER

BMODE[1: 0]

−BBoot mode select

Vdd2

TEST

Pos

I

test mode

VddRTC

NRES

Neg

I

SoC reset input

Vdd2

Multiplexed

Function

XTAL, PLL

(continued)

Only internal loop filter.

Only internal loop filter.

LC823455

FunctionDirectionPolarity

IO POWER

Available(d)

RBXA

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d

2

d

2

power supply

power ground

Connect to ground.

AVddDAMPL

AVddDAMPR

d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

d d

www.onsemi.com

29

Page 30

Table 11. TERMINAL FUNCTIONS

Terminal Name

IO18V

−I1.8 V IO range select for I/O of Vdd2

Vdd1

Vdd1

−PDigital core power supply

−

Vdd2

−PDigital IO power supply

−

VddSD1

−PDigital IO power supply(SDI/F ch1)

−

Vss1

−PDigital core power ground

−

Vss2

−PDigital IO power ground

−

Sum

31

33

All Sum

120

136

Multiplexed

Function

OTHER, POWER

(continued)

“0” : 3.3 V IO operation

“1” : 1.8 V IO operation

When setting “1”, don’t supply any voltage

over the 1.8 V voltage range to Vdd2.

LC823455

FunctionDirectionPolarity

IO POWER

Available(d)

RBXA

d d

d

6

d

6

d

1

d

6

d

7

d

6

d

7

d

1

d

6

d

8

3. Set according to the General RTC mode or KeyInt RTC mode.

4. S−Flash I/F / SD I/F Ch0 includes SFQSCS / SDCMD0 in Timer.

5. SDRAM address bit is 13 bit including SDRADDR [12:11].

6. This function is not available.

www.onsemi.com

30

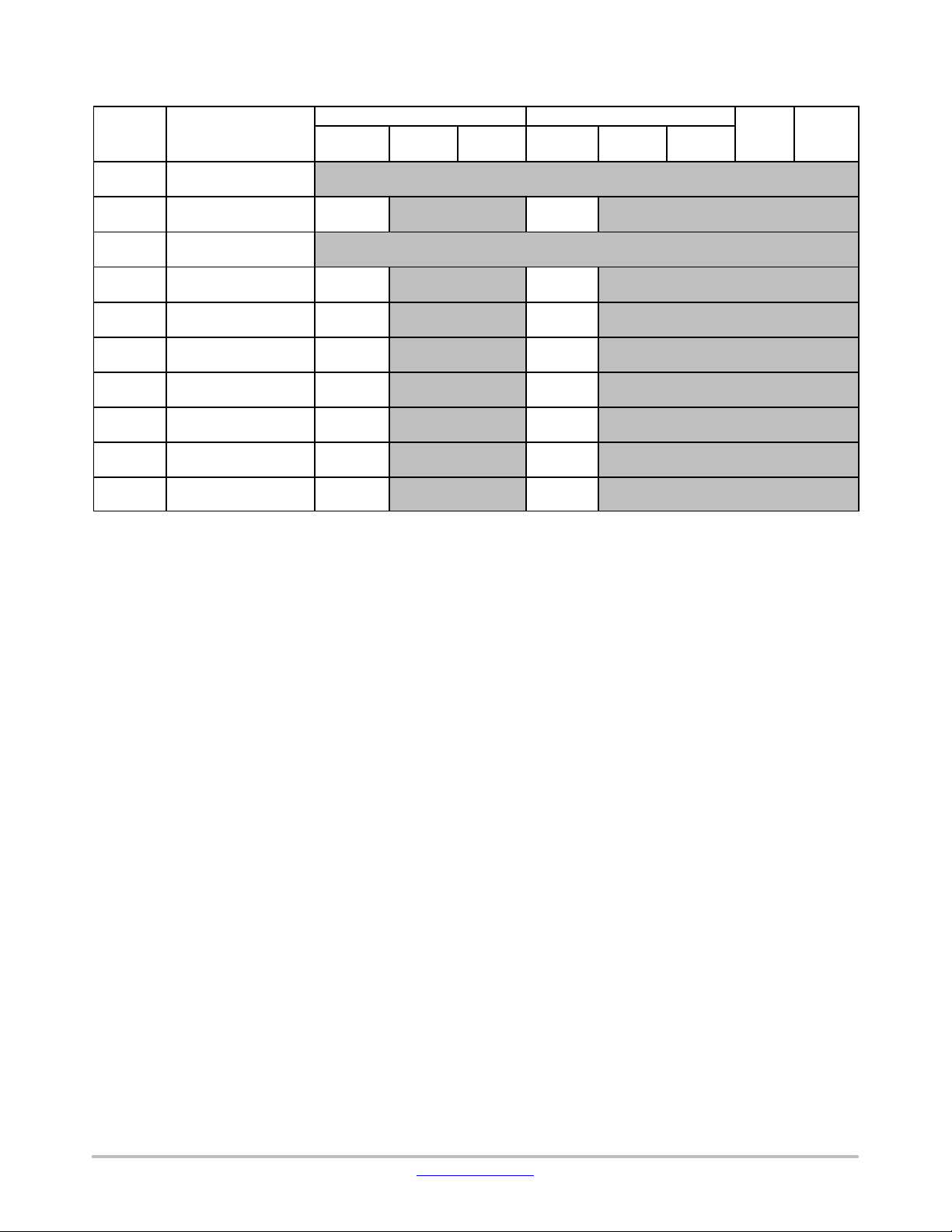

Page 31

LC823455

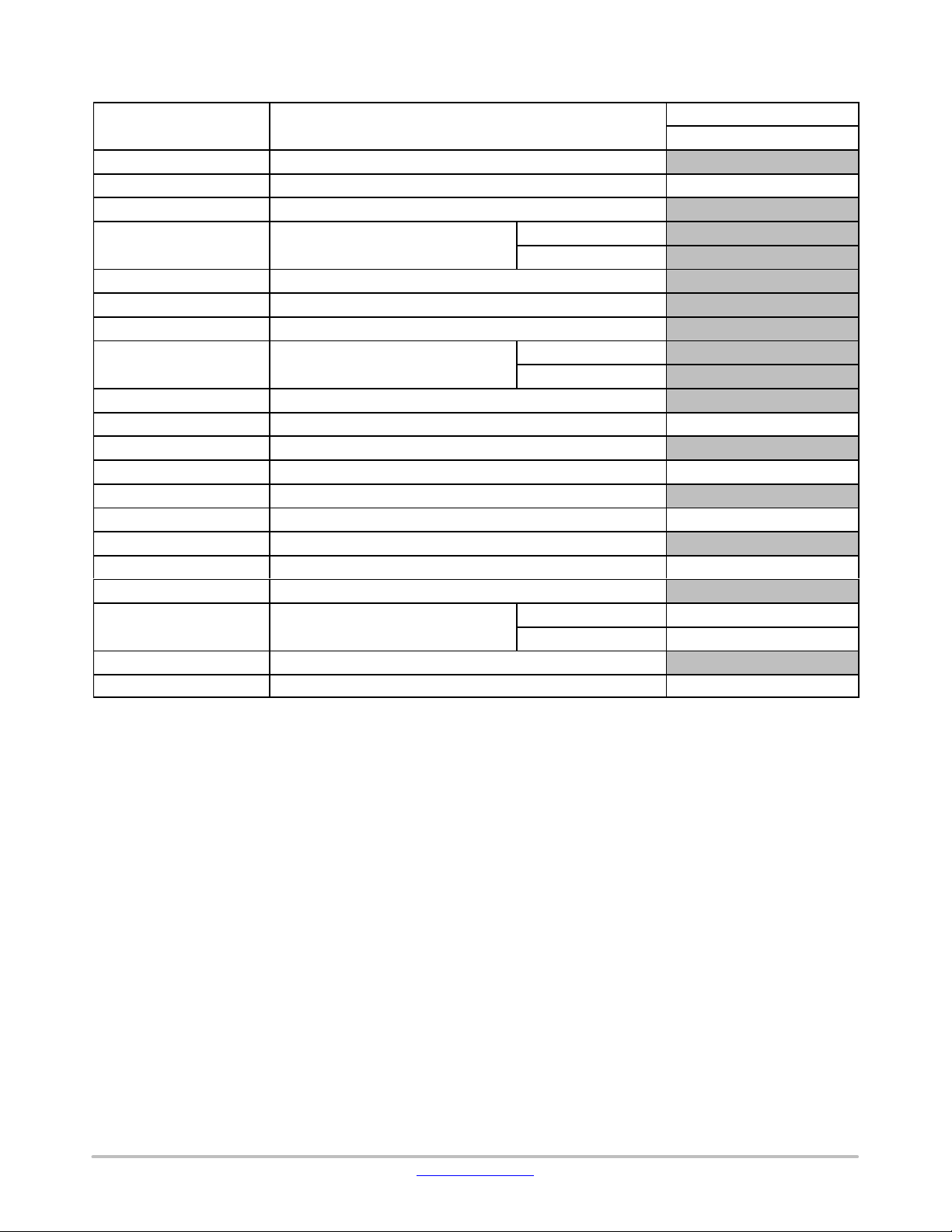

Table 12. PIN MULTIPLEX FUNCTIONS

Number

Module name

Signal name

Function

Assigned GPIO

0

SCL0

I2C ch0 Clock

1

SDA0

I2C ch0 Data

2

SCL1

I2C ch1 Clock

3

SDA1

I2C ch1 Data

4

SCK0

Serial I/F Ch0 Clock

5

SDI0

Serial I/F Ch0 Data Input

6

SDO0

Serial I/F Ch0 Data Output

7

SCK1

Serial I/F Ch1 Clock

8

SDI1

Serial I/F Ch1 Data Input

9

SDO1

Serial I/F Ch1 Data Output

10

TCLKA0

MTM0 external Clock A

11

TCLKB0

MTM0 external Clock B

12

TIOCA00

MTM0 Ch0A

13

TIOCA01

MTM0 Ch1A

14

TIOCB00

MTM0 Ch0B

15

TIOCB01

MTM0 Ch1B

16

TCLKA1

MTM1 external Clock A

17

TCLKB1

MTM1 external Clock B

18

TIOCA10

MTM1 Ch0A

19

TIOCA11

MTM1 Ch1A

20

TIOCB10

MTM1 Ch0B

21

TIOCB11

MTM1 Ch1B

22

RXD0

UART Ch0 receive Data

23

TXD0

UART Ch0 transmit Data

24

RXD1

UART Ch1 receive Data

25

TXD1

UART Ch1 transmit Data

26

CTS1

UART Ch1 clear to send

27

RTS1

UART Ch1 request to send

28

RXD2

UART Ch2 receive Data

29

TXD2

UART Ch2 transmit Data

30

CTS2

UART Ch2 clear to send

31

RTS2

UART Ch2 request to send

32

DMCKO0

Digital Mic Ch0 Clock Output

33

DMDIN0

Digital Mic Ch0 Data Input

34

DMCKO1

Digital Mic Ch1 Clock Output

35

DMDIN1

Digital Mic Ch1 Data Input

36

OSC

WICPOWERDOWN

Power control for WIC Sleep

37

Reserved

Reserved

Reserved

Signals Handled by Pin Multiplex Function

The pin multiplex function can be used to assign

low−speed signals to any of GPIOs. The table below shows

the signal functions that can be multiplexed and the GPIOs

that can be assigned.

I2C0

I2C1

SPI0

SPI1

MTM0

MTM1

GPIO00 to 0F

GPIO10 to 1F

GPIO20 to 2F

GPIO30 to 3F

GPIO40 to 4F

GPIO50 to 59

UART0

UART1

UART2

DMIC0

DMIC1

www.onsemi.com

31

Page 32

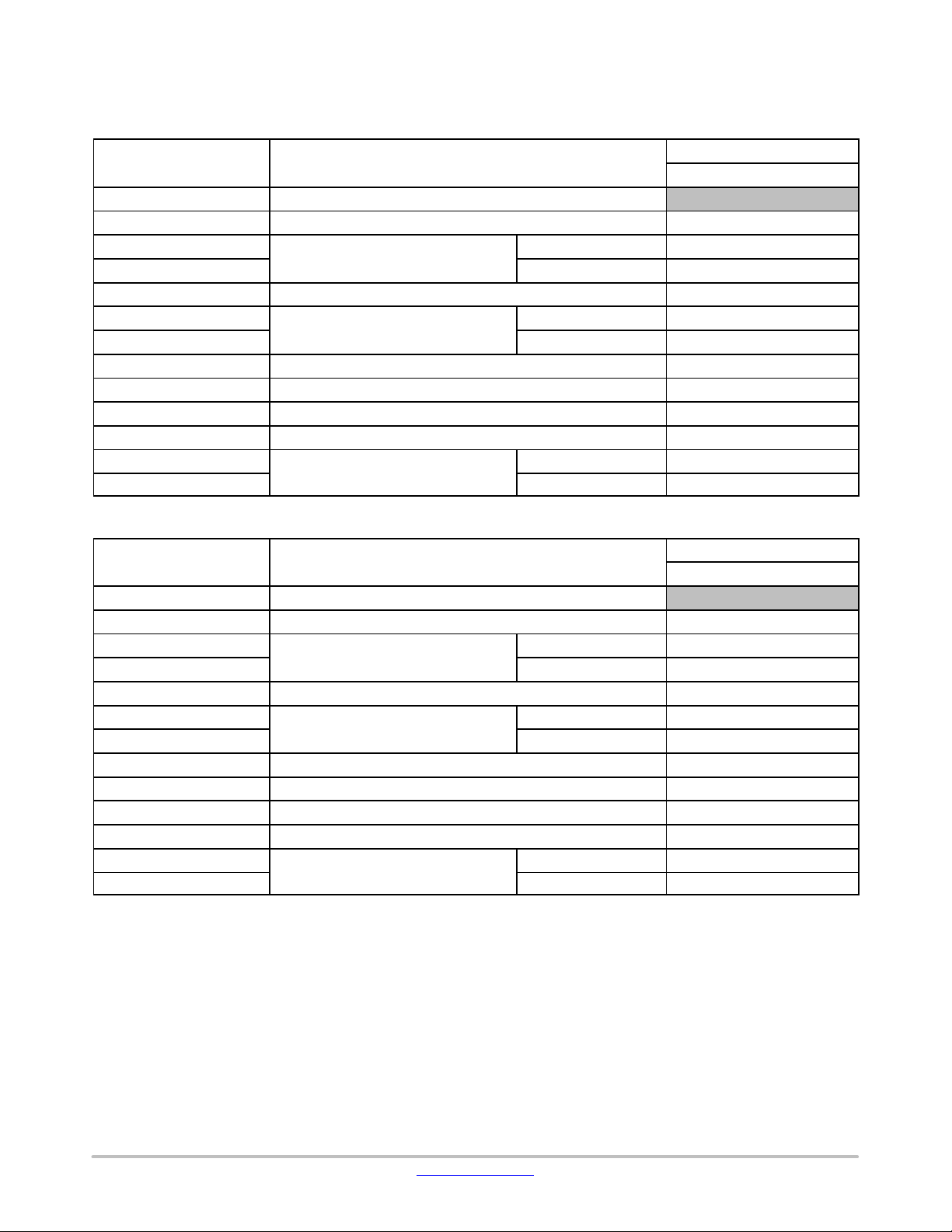

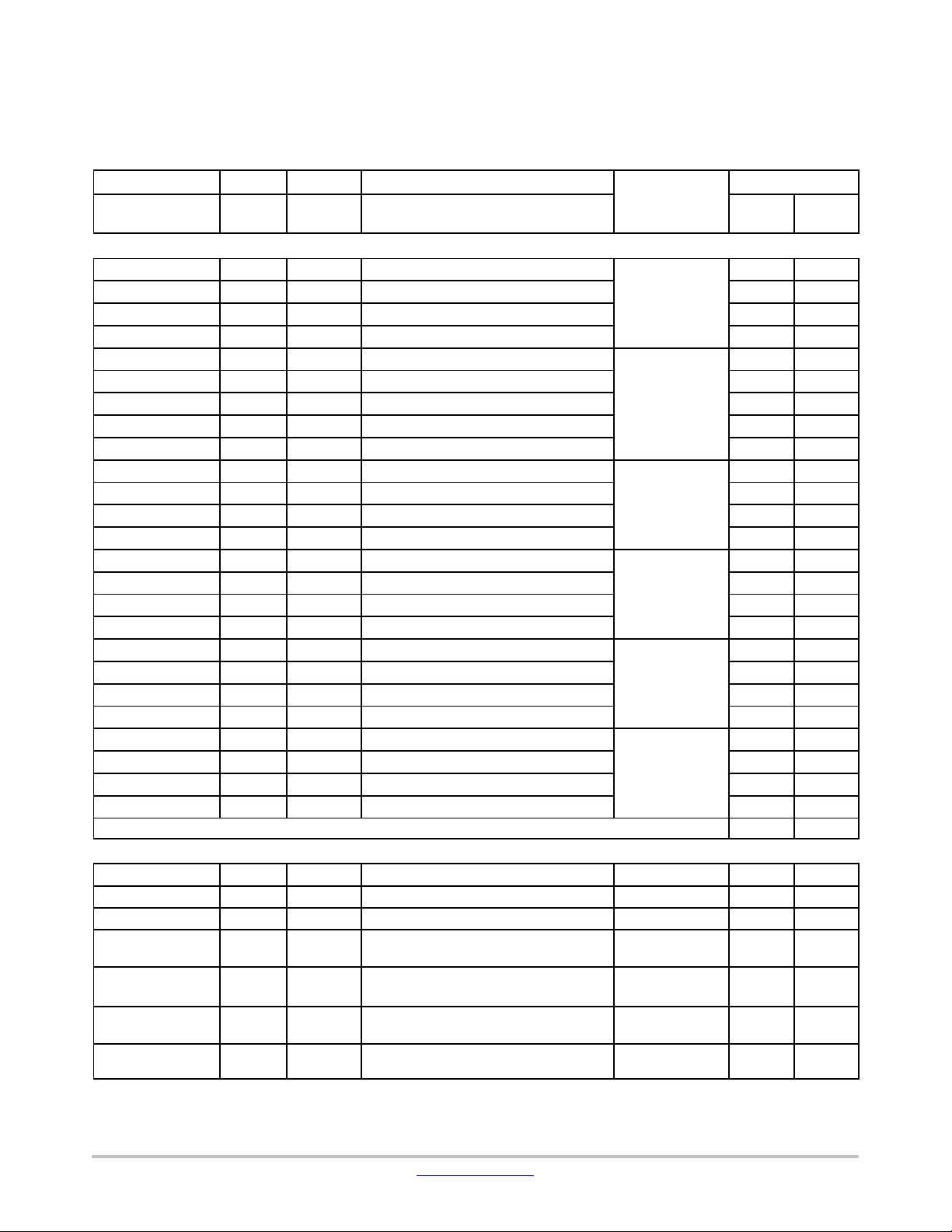

Boot Mode

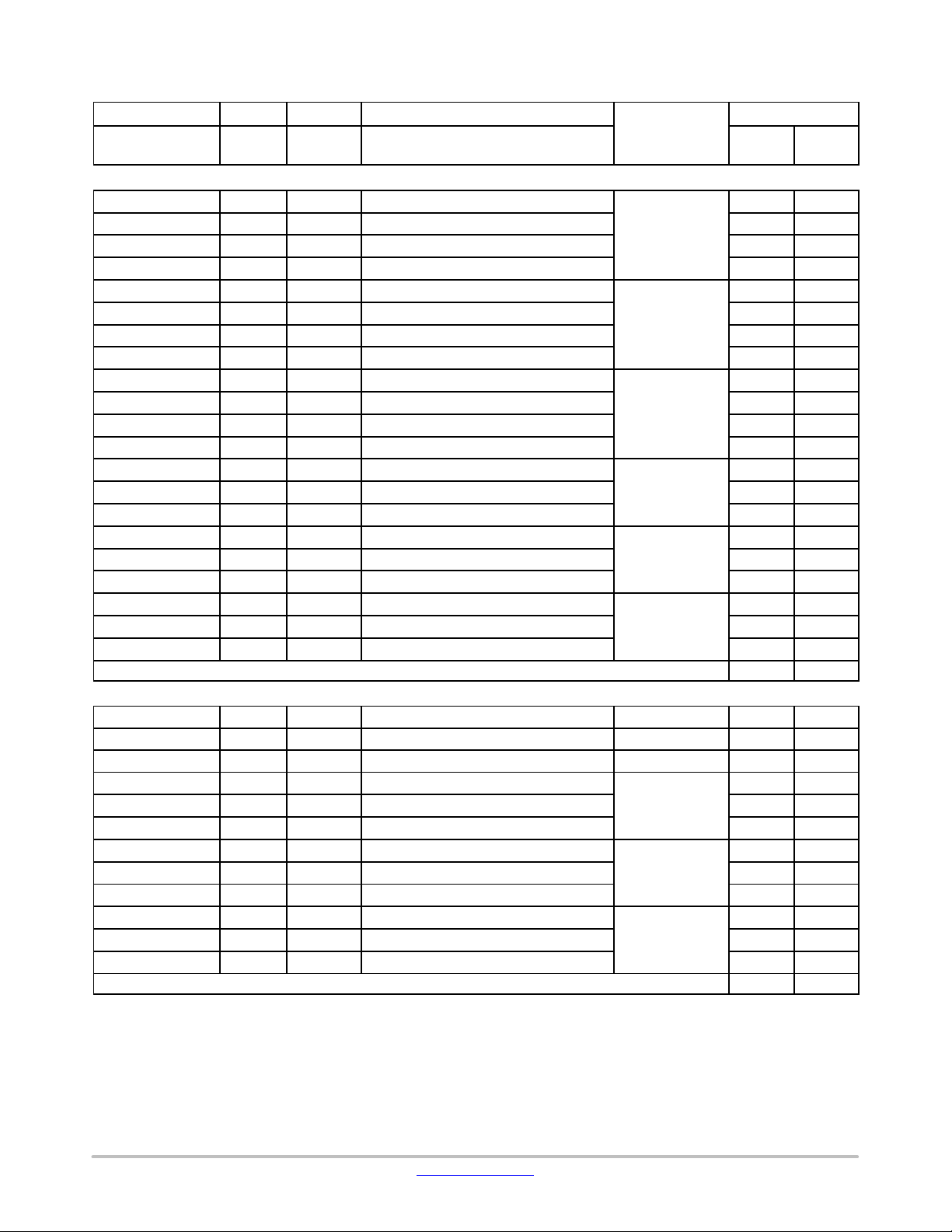

Table 13. BOOT MODE

IPL mode

BMODE1

BMODE0

Explanation

Internal ROM boot (EMMC Physical Boot with USB download)

IPL2 is transferred to boot partition1 area of eMMC via USB from PC.

Internal ROM boot (EMMC Physical Boot with SD Ch1 download)

IPL2 is transferred to boot partition1 area of eMMC from SDCH1.

Internal ROM boot (User Area Boot with USB download)

IPL2 is transferred to user area of eMMC via USB from PC.

Internal ROM boot (User Area Boot with SD Ch1 download)

IPL2 is transferred to user area of eMMC from SDCH1.

Internal ROM boot (External Serial Flash SPI Boot with USB download)

IPL2 is transferred to user area of S−FLASH via USB from PC.

Internal ROM boot (External Serial Flash SPI Boot with SD Ch1 download)

IPL2 is transferred to user area of S−FLASH from SDCH1.

Internal ROM boot

The IPL supports the direct write of the program using the DD command from USB.

The available boot modes are determined by the values on

the BMODE[1:0] terminal.

LC823455

Physical

Boot

USB

Physical

Boot

SD

User Area

Boot

USB

User Area

Boot

SD

SPI Boot

USB

PD

470 k

PD

470 k

PD

1 k

PU

470 k

PU

470 k

PD

470 k

PU

470 k

PU or PD

470 k

PD

1 k

PU

470 k

(SD card I/F Ch0 + USB Device + EXTINT2F)

Using Boot operation mode of eMMC, IPL2(program) is copied to internal SRAM

from boot partition1 area of eMMC connected to SDCH0 and is executed.

XT1 must be connected in this mode to boot the ROM.

The connection of XTRTC is arbitrary.

(SD card I/F Ch0 + SD card I/F Ch1 + EXTINT2F)

Using Boot operation mode of eMMC, IPL2(program) is copied to internal SRAM

from boot partition1 area of eMMC connected to SDCH0 and is executed.

Either XT1 or XTRTC is required to boot the ROM.

(SD card I/F Ch0 + USB Device + EXTINT2F)

IPL2(program) is copied to internal SRAM from user area of eMMC connected to

SDCH0 and is executed.

XT1 must be connected in this mode to boot the ROM.

The connection of XTRTC is arbitrary.

(SD card I/F Ch0 + SD card I/F Ch1 + EXTINT2F)

IPL2(program) is copied to internal SRAM from user area of eMMC connected to

SDCH0 and is executed.

Either XT1 or XTRTC is required to boot the ROM.

(S−FLASH I/F + USB Device + EXTINT2F )

IPL2(program) is copied to internal SRAM from user area of S−FLASH and is

executed.

XT1 must be connected in this mode to boot the ROM.

The connection of XTRTC is arbitrary.

SPI Boot

SD

QSPI Boot

USB

PD

470 k

PU

1 k

PU

1 k

PU

470 k

(S−FLASH I/F + SDcard I/F Ch1 + EXTINT2F)

IPL2(program) is copied to internal SRAM from user area of S−FLASH and is

executed.

Either XT1 or XTRTC is required to boot the ROM.

(External Serial Flash QSPI Boot with USB download)

(S−Flash I/F(QSPI) + USB Device + EXTINT2F)

In this mode, the CPU fetches Serial Flash connected to S/Flash IF directly.

XT1 must be connected in this mode to boot the ROM.

The connection of XTRTC is arbitrary.

www.onsemi.com

32

Page 33

Table 13. BOOT MODE (continued)

Internal ROM boot

IPL2 is transferred to S−FLASH from SDCH1.

Internal ROM boot (User Area IPL2 deletion)

It comes to be able to write IPL2 again at User Area Boot.

Internal ROM boot (Partition Area IPL2 deletion)

It comes to be able to write IPL2 again at eMMC Physical Boot.

Internal ROM boot (All external Serial Flash SPI area deletion)

All of Serial Flash is deleted.

Internal ROM boot (All area deletion )

All of eMMC is deleted. The partition area is also erased, which takes time. When

Internal ROM boot (All external Serial Flash QSPI area deletion)

All of Serial Flash is deleted.

N/A

N/A

Hi−z

PU

PU

External memory I/F terminal are Hiz

IPL mode ExplanationBMODE0BMODE1

QSPI Boot

SD

User Area

Delete

Partition

Delete

SPI All

Erase

SDCH0 All

Erase

PU

1 k

PD

1 k

PD

470 k

PU

470 k

PD

1 k

PD

470 k

PU

1 k

PD

1 k

PU

1 k

PD

1 k

LC823455

(External Serial Flash QSPI Boot with SD Ch1 download)

(S−Flash I/F(QSPI) + SD card I/F Ch1 + EXTINT2F)

In this mode, the CPU fetches from Serial Flash connected to S/Flash IF directly.

Either XT1 or XTRTC is required to boot the ROM.

( SD card I/F Ch0 + EXTINT2F)

Either XT1 or XTRTC is necessary to boot the ROM.

(SD card I/F Ch0 + EXTINT2F)

Either XT1 or XTRTC is necessary to boot the ROM.

( S−Flash I/F, + EXTINT2F )

Please select it when you use Serial Flash with SPI.

Either XT1 or XTRTC is required to boot the ROM.

(SD card I/F Ch0 + EXTINT2F)

eMMC corresponds to Trim, Trim is done.

Either XT1 or XTRTC is required to boot the ROM.

QSPI All

Erase

External

ROM Boot

PU

1 k

PU

470 k

1 k

PD

1 k

PD

470 k

1 k

(S−Flash I/F(QSPI) + EXTINT2F)

Please use it when you use Serial Flash in the fetch mode of QSPI.

Either XT1 or XTRTC is required to boot the ROM.

EXA[20:1], EXD[15:0], NCS[1:0], NRD, NWRENWRL, NHBNWRH, NLBEXA0

SD card I/F Ch0 terminal are Hiz

SDCLK0, SDCMD0, SDAT0[3:0]

S−Flash(QSPI) terminal are Hiz

SFQSCS, SFCK, SFDI(QIO0), SFDO(QIO1), SFWP(QIO2), SFHOLD(QIO3)

Either XT1 or XTRTC is required to boot the ROM.

Boot Port

The ports used while booting are described below.

• There is no dedicated SDCH0 pin in the WLP package.

Therefore, when booting from eMMC, the terminals

SFCK, SFQSCS, SFDO, SFDI, SFWP, and SFHOLD

must be switched to SDCLK0, SDCMD0, SDAT00,

SDAT01, SDAT02, and SDAT03. The target is Physical

Boot USB · Physical Boot SD · User Area Boot USB ·

User Area Boot SD · User Area Delete, Partition

Delete, SDCH 0 All Erase

• SD Card SDCH1 uses only CMD, DATA, and CLK.

The terminals CD and WP are not used. These three

terminals are controlled only when writing IPL2 from

SDCH1

• SPI Boot / SPI All Erase uses only SFCK, SFDO, SFDI

and SFQSCS switched from TIOCB01. SFHOLD and

SFWP (The function is different according to the

device) are not used

• QSPI Boot / QSPI All Erase uses SFCK, SFDO, SFDI,

SFHOLD, SFWP and SFQSCS switched from

TIOCB01

www.onsemi.com

33

Page 34

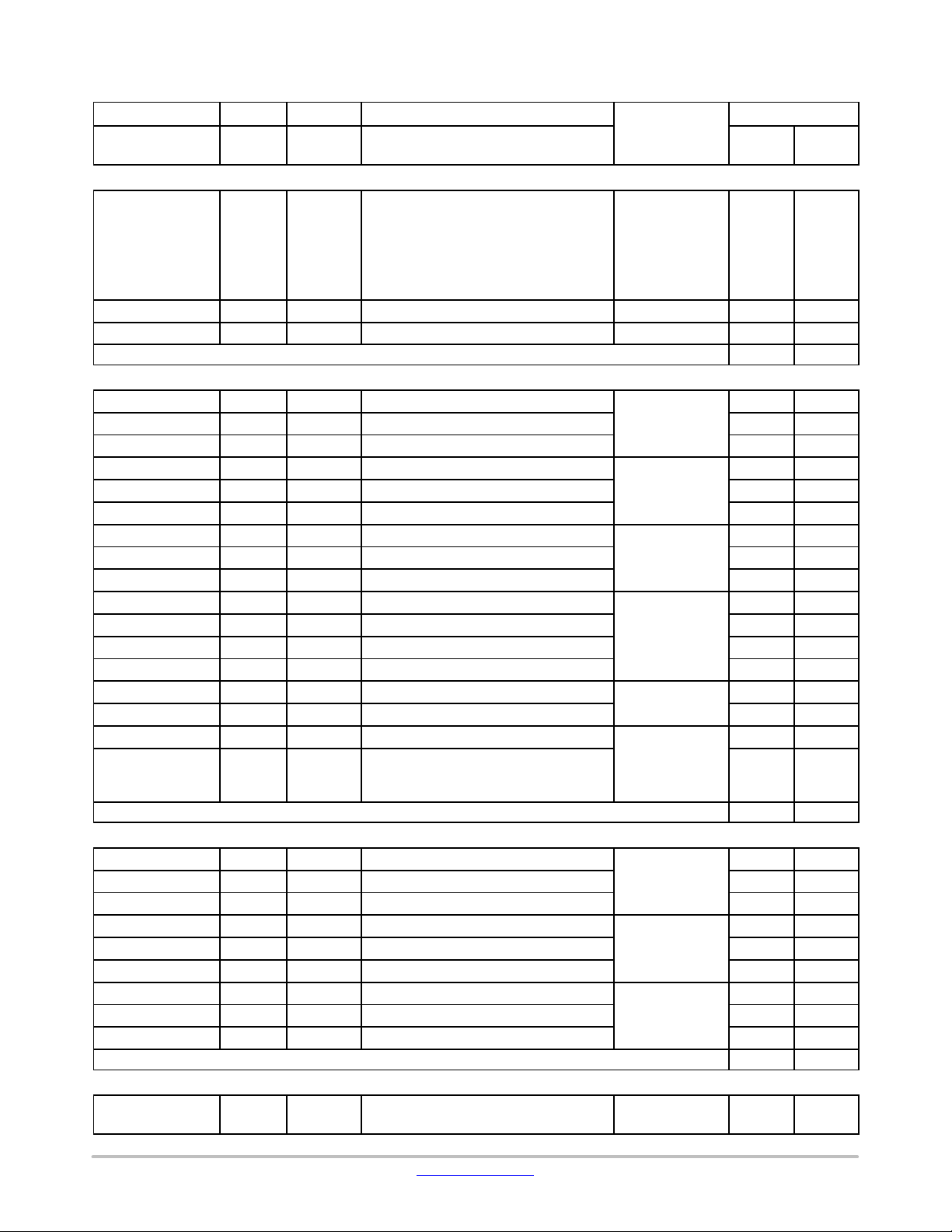

Table 14. GPIOs USED DURING IPL

(RB is under planning.)

SDCH0

Shared (for XA)

Dedicated (for RB)

Physical Boot USB

P2F(error notification)

P2F(error notification)

Physical Boot SD

P2F(error notification),

P2F(error notification)

User Area Boot USB

P2F(error notification),

P2F(error notification)

User Area Boot SD

P2F(error notification)

P2F(error notification)

SPI Boot USB

P2F(error notification)

P2F(error notification)

SPI Boot SD

P2F(error notification),

P2F(error notification)

QSPI Boot USB

P2F(error notification),

P2F(error notification)

QSPI Boot SD

P2F(error notification)

P2F(error notification)

UserArea Delete

P2F(error notification),

P2F(error notification)

Partition Delete

P2F(error notification),

P2F(error notification)

SPI Erase

P2F(error notification),

P2F(error notification),

SDCH0 All Erase

P2F(error notification),

P2F(error notification)

QSPI All Erase

P2F(error notification),

P2F(error notification),

External ROM Boot

N/A

N/A

HI−z

SDCLK0 is set to the Hi−z input.

IPL mode

LC823455

P0D(SDCLK0), P0E(SDAT00), P0F(SDAT01),

P11(SDAT02), P12(SDAT03), P03(SCMD0)

P22(SDCLK1), P23(SDCMD1), P24(SDDATA10),

P25(SDDATA11), P26(SDDATA12),

P27(SDDATA13), P0D(SDCLK0), P0E(SDAT00),

P0F(SDAT01), P11(SDAT02), P12(SDAT03)

P03(SCMD0)

P0D(SDCLK0), P0E(SDAT00), P0F(SDAT01),

P11(SDAT02), P12(SDAT03), P03(SCMD0)

P0D(SDCLK0), P0E(SDAT00), P0F(SDAT01),

P11(SDAT02), P12(SDAT03), P03(SCMD0),

P22(SDCLK1), P23(SDCMD1), P24(SDDATA10),

P25(SDDATA11),

P26(SDDATA12), P27(SDDATA13)

P0D(SFCK), P03(SFQSCS), P0F(SFDO),

P0E(SFDI)

P0D(SFCK), P03(SFQSCS) P0F(SFDO),

P0E(SFDI), P22(SDCLK1), P23(SDCMD1),

P24(SDDATA10), P25(SDDATA11),

P26(SDDATA12), P27(SDDATA13)

P0D(SFCK), P03(SFQSCS), P0F(SFDO),

P0E(SFDI), P11(SFWP), P12(SFHOLD)

,

P22(SDCLK1), P23(SDCMD1),

P24(SDDATA10), P25(SDDATA11),

P26(SDDATA12), P27(SDDATA13)

,

P22(SDCLK1), P23(SDCMD1),

P24(SDDATA10), P25(SDDATA11),

P26(SDDATA12), P27(SDDATA13)

,

P0D(SFCK), P03(SFQSCS), P0F(SFDO), P0E(SFDI)

,

P0D(SFCK), P03(SFQSCS) P0F(SFDO), P0E(SFDI),

P22(SDCLK1), P23(SDCMD1), P24(SDDATA10),

P25(SDDATA11),

P26(SDDATA12), P27(SDDATA13)

,

P0D(SFCK), P03(SFQSCS), P0F(SFDO), P0E(SFDI),

P11(SFWP), P12(SFHOLD)

7. In this table, “Pxx” means “GPIOxx”. For example “P2F” means “GPIO2F”.

P0D(SFCK), P03(SFQSCS), P0F(SFDO),

P0E(SFDI), P011(SFWP), P12(SFHOLD),

P22(SDCLK1), P23(SDCMD1), P24(SDDATA10),

P25(SDDATA11), P26(SDDATA12),

P27(SDDATA13)

P0D(SDCLK0), P0E(SDAT00), P0F(SDAT01),

P11(SDAT02), P12(SDAT03), P03(SCMD0)

P0D(SDCLK0), P0E(SDAT00), P0F(SDAT01),

P11(SDAT02), P12(SDAT03), P03(SCMD0)

P0D(SFCK), P03(SFQSCS), P0F(SPIOUT),

P0E(SFDI)

P0D(SDCLK0), P0E(SDAT00), P0F(SDAT01),

P11(SDAT02), P12(SDAT03), P03(SCMD0)

P0D(SFCK), P03(SFQSCS), P0F(SFDO),

P0E(SFDI), P11(SFWP), P12(SFHOLD)

www.onsemi.com

34

P0D(SFCK), P03(SFQSCS), P0F(SFDO), P0E(SFDI),

P011(SFWP), P12(SFHOLD), P22(SDCLK1), P23(SDCMD1),

P24(SDDATA10), P25(SDDATA11),

P26(SDDATA12), P27(SDDATA13)

P0D(SFCK), P03(SFQSCS), P0F(SPIOUT), P0E(SFDI)

P0D(SFCK), P03(SFQSCS), P0F(SFDO), P0E(SFDI),

P11(SFWP), P12(SFHOLD)

Page 35

LC823455

SDIF PullUp

If using the SDIF port during boot mode, internal PullUp

resistors are used (SDCMD0, SDAT0[3:0] / SDCMD1,

SDAT1[3:0]). Therefore, external PullUp resistors are not

required on the board.

SFQSCS PullUp

If using SFQSCS during boot mode, the initial condition

for terminal P03 relative to SFQSCS is Pull−Up. After

terminal P03 is switched to SFQSCS, the Pull−Up is

released.

GPIO2F

During boot mode, GPIO2F provides notification of the

beginning of USB connection, notification of the

termination of USB connection, as well as error notification

with High/Low of the terminal.

When errors occur during boot sequences, for example

writing of IPL2, GPIO2F reports the sort of error. Moreover,

GPIO2F can indicate the status of USB connection and the

completion of USB file transfer. Additionally, Delete Mode,

completion of Erase, and status of Erase can also be reported

through a sequence of Low/High.

For more d e t a i l a b o u t t h e behavior of this port used during

boot, refer to the “IPL detail” chapter in the “LC823455

Sample Software Reference”

.

www.onsemi.com

35

Page 36

LC823455

Table 15. PIN ASSIGNMENT

I/O

I

Input

O

Output

B

Bidirectional

P

Power

G

Ground

T able 16.

RB

XA

No.

Ball

No.

Ball

−−−−Vdd2

P

−−−−Vss2

G

−−−−EXD0/

B/

Schmitt

3−State

2/4/8 mAPDVdd2

3ISD/3T2

−−−−EXA1/

O/

Schmitt

3−State

2/4/8 mAPDVdd2

3ISD/3T2

−−−−EXA11/

O/

Schmitt

3−State

2/4/8 mAPDVdd2

3ISD/3T2

−−−−EXA12/

O/

Schmitt

3−State

2/4/8 mAPDVdd2

3ISD/3T2

−−−−EXA13/

O/

Schmitt

3−State

2/4/8 mAPDVdd2