ON NUP4103FC Schematic [ru]

NUP4103FC

Four Channel ESD Array

This integrated transient voltage suppressor device (TVS) is

designed for applications requiring transient overvoltage protection. It

is intended for use in sensitive portable equipment and other

applications. Its integrated design provides very effective and reliable

protection for four (4) separate lines using only one package. These

devices are ideal for situations where board space is a premium.

http://onsemi.com

Features

• Unidirectional, Quad ESD Protection

• Ultra−small Flip−Chip Packaging (0.95 mm x 1.33 mm)

• Compliance with IEC61000−4−2 (Level 4) Requirements

• Maximum Leakage Current of 100 nA at 3.3 V

• Pb−Free Package is Available*

Benefits

• Protects Four Data Lines from ESD while Reducing Component

Count

• Small Package Saves on PCB Real Estate

• Provides Protection for ESD Industry Standards, IEC 61000,

HBM and MM

• Low Leakage Capability Minimizes Power Loss in the System

Applications

• ESD Protection for Portable Equipment

• Cell Phones

• MP3 Players

• PDAs

MAXIMUM RATINGS

Rating Symbol Value Unit

ESD Discharge IEC61000−4−2,

− Air Discharge

− Contact Discharge

Human Body Model

Machine Model

Junction Temperature T

Operating Ambient Temperature Range T

Storage Temperature Range T

Stresses exceeding Maximum Ratings may damage the device. Maximum

Ratings are stress ratings only. Functional operation above the Recommended

Operating Conditions is not implied. Extended exposure to stresses above the

Recommended Operating Conditions may affect device reliability.

*For additional information on our Pb−Free strategy and soldering details, please

download the ON Semiconductor Soldering and Mounting Techniques

Reference Manual, SOLDERRM/D.

V

PP

J

A

STG

30

kV

30

16

1.6

150 °C

−40 to +85 °C

−55 to +150 °C

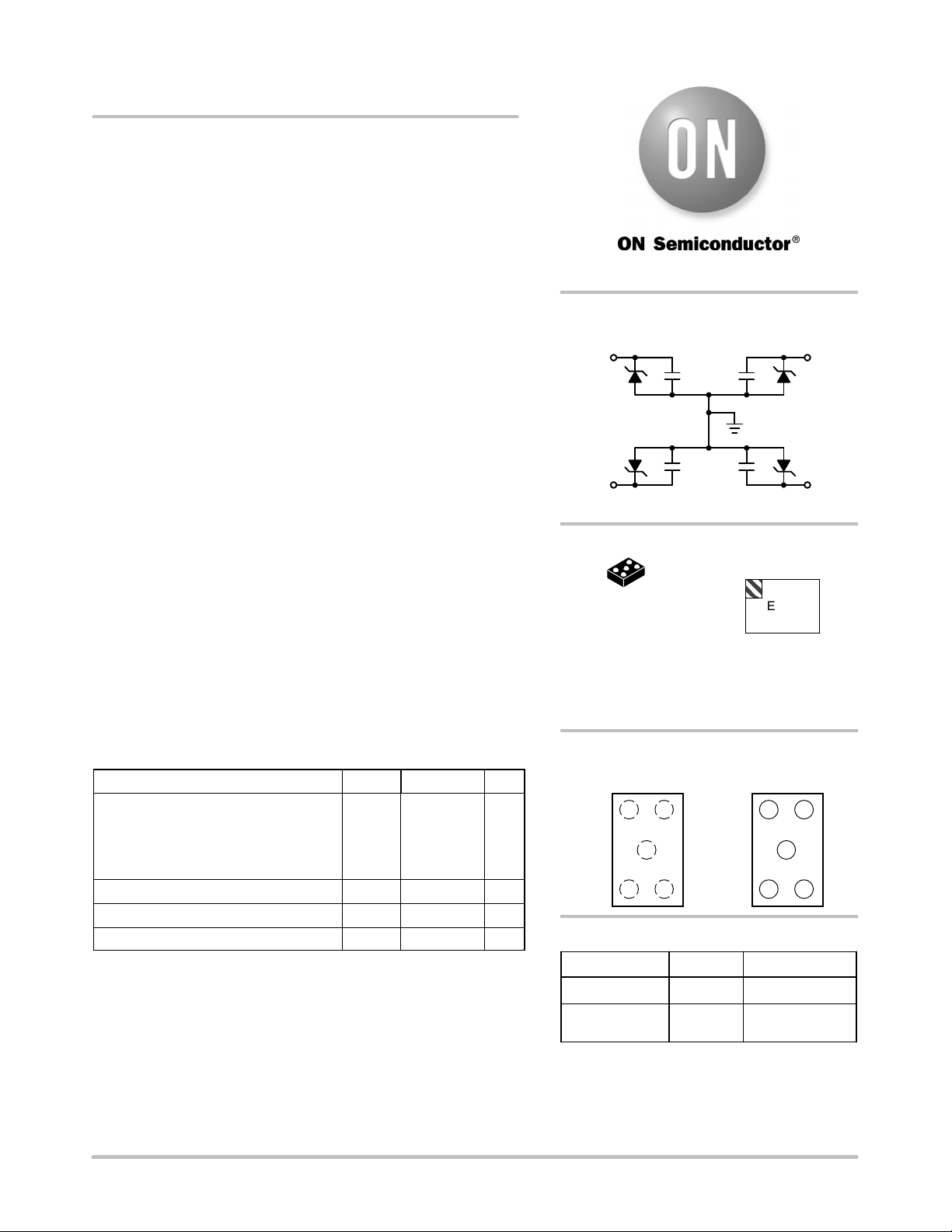

CIRCUIT DESCRIPTION

A1 C1

B2

A3 C3

MARKING

1

5−PIN FLIP−CHIP CSP

PLASTIC

CASE 766AB

E = Specific Device Code

M = Date Code

G = Pb−Free Package

(Note: Microdot may be in either location)

TOP VIEW

(Bumps Down)

12 12

33

A

B

C

DIAGRAM

E M G

G

BOTTOM VIEW

(Bumps Up)

A

B

C

ORDERING INFORMATION

Device Package

NUP4103FCT1 Flip−Chip 3000/Tape & Reel

NUP4103FCT1G Flip−Chip

(Pb−Free)

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specifications

Brochure, BRD8011/D.

Shipping

3000/Tape & Reel

†

© Semiconductor Components Industries, LLC, 2006

March, 2006 − Rev. 1

1 Publication Order Number:

NUP4103FC/D

NUP4103FC

ELECTRICAL CHARACTERISTICS (T

Parameter

Reverse Stand−Off Voltage V

Breakdown Voltage V

Leakage Current I

Junction Capacitance C

= 25°C unless otherwise specified)

J

Symbol Conditions Min Typ Max Unit

I

RWM

BR

R

J

= 10 mA (Note 1)

RWM

IT = 1.0 mA (Note 2) 6.0 7.0 8.0 V

VRM = 3.3 V per line 100 nA

VR = 2.5 V, f = 1 MHz 30 pF

1. TVS devices are normally selected according to the working peak reverse voltage (V

or continuous peak operating voltage level.

2. VBR is measured at pulse test current IT.

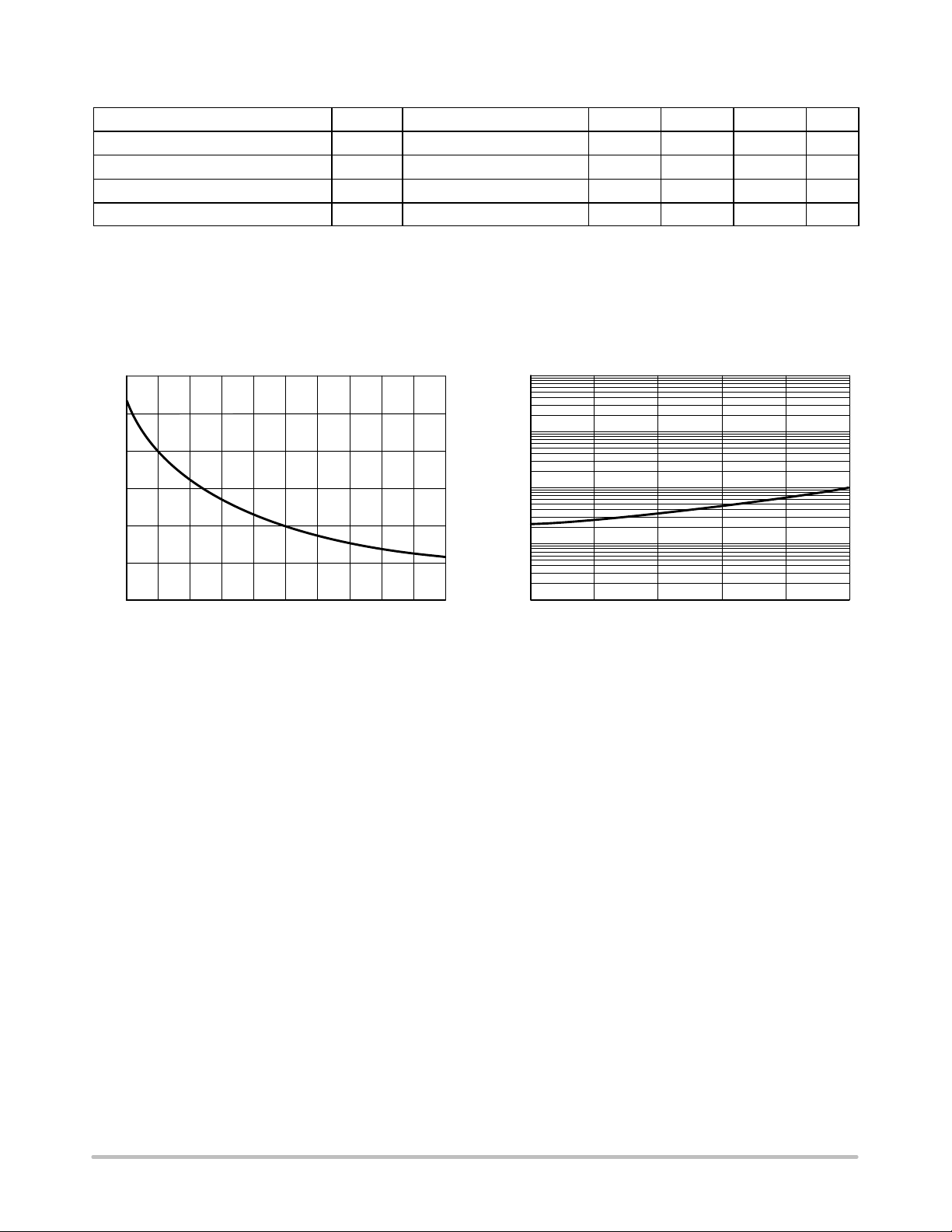

TYPICAL PERFORMANCE CURVES

(TJ = 25°C unless otherwise specified)

50

45

40

35

30

C, Capacitance (pF)

25

100.0E−9

10.0E−9

1.0E−9

, Leakage Current (A)

100.0E−12

R

I

5.5 V

) which should be equal or greater than the DC

RWM

20

0

12345

VR, Reverse Voltage (V)

Figure 1. Reverse Voltage vs Junction Capacitance

10.0E−12

−40

−15

10

35 60 85

T, Temperature (°C)

Figure 2. Reverse Leakage Current

vs Junction Temperature

http://onsemi.com

2

Loading...

Loading...