ON NCP5901DR2G, NCP5901MNTBG Schematic [ru]

NCP5901

VR12 Compatible

Synchronous Buck MOSFET

Drivers

The NCP5901 is a high performance dual MOSFET gate driver

optimized to drive the gates of both high−side and low−side power

MOSFETs in a synchronous buck converter. It can drive up to 3 nF

load with a 25 ns propagation delay and 20 ns transition time.

Adaptive anti−cross−conduction and power saving operation

circuit can provide a low switching loss and high efficiency solution

for notebook and desktop systems. Bidirectional EN pin can provide

a fault signal to controller when the gate driver fault detect under

OVP, UVLO occur. Also, an under−voltage lockout function

guarantees the outputs are low when supply voltage is low.

Features

• Faster Rise and Fall Times

• Adaptive Anti−Cross−Conduction Circuit

• Pre OV function

• ZCD Detect

• Floating Top Driver Accommodates Boost Voltages of up to 35 V

• Output Disable Control Turns Off Both MOSFETs

• Under−voltage Lockout

• Power Saving Operation Under Light Load Conditions

• Direct Interface to NCP6151 and Other Compatible PWM

Controllers

• Thermally Enhanced Package

• These are Pb−Free Devices

Typical Applications

• Power Solutions for Desktop Systems

http://onsemi.com

8

1

SOIC−8 NB

D SUFFIX

CASE 751

MARKING DIAGRAMS

8

N5901

ALYW

1

N5901 = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

1

AJMG

AJ = Specific Device Code

M = Date Code

G = Pb−Free Device

DFN8

MN SUFFIX

CASE 506AA

G

G

1

© Semiconductor Components Industries, LLC, 2013

June, 2013 − Rev. 2

ORDERING INFORMATION

Device Package Shipping

NCP5901MNTBG DFN8

(Pb−Free)

NCP5901DR2G SOIC−8

(Pb−Free)

†For information on tape and reel specifications,

including part orientation and tape sizes, please

refer to our Tape and Reel Packaging Specification

Brochure, BRD8011/D.

1 Publication Order Number:

3000 / Tape & Reel

2500 / Tape & Reel

†

NCP5901/D

NCP5901

VCC

PWM

BST

1

PWM

EN

VCC

(Top View)

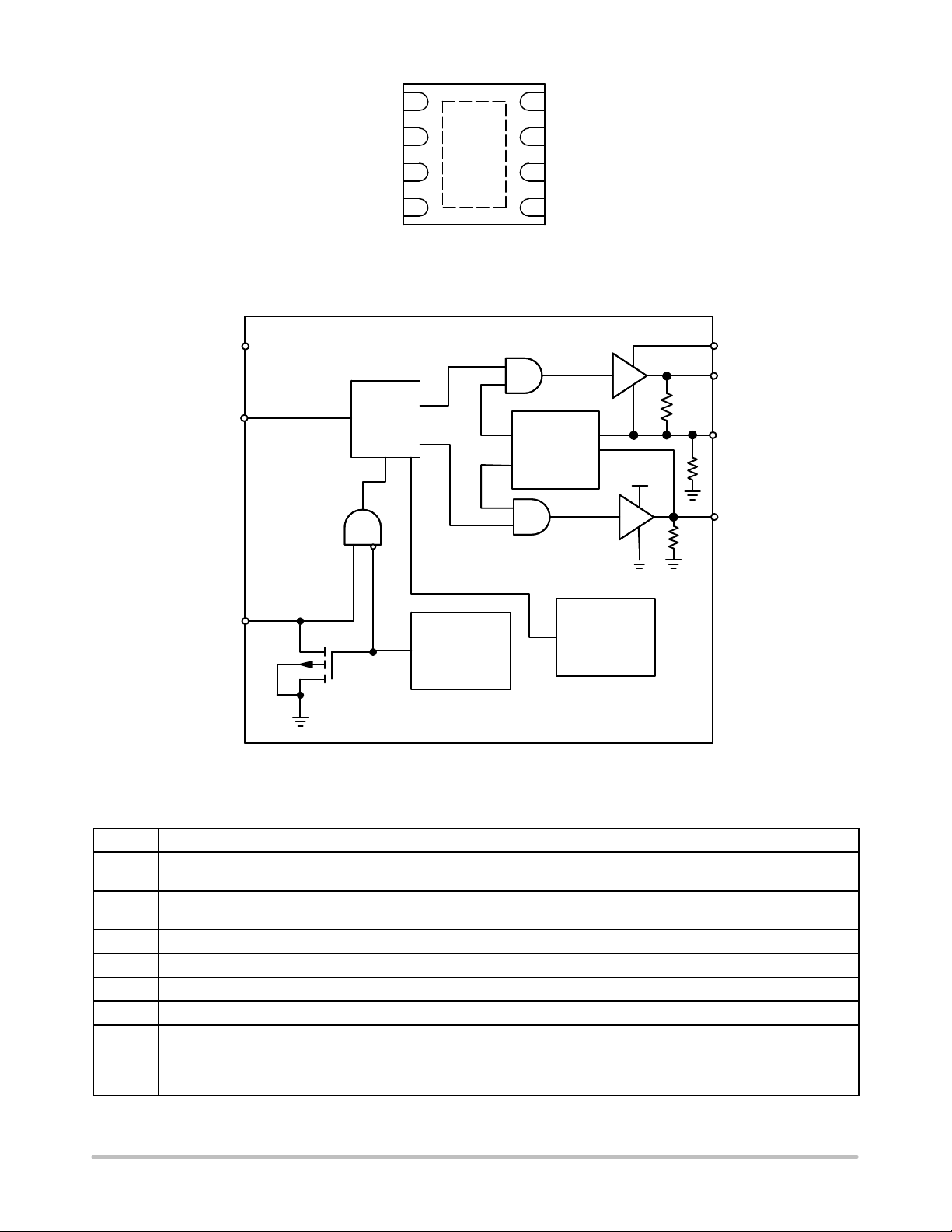

Figure 1. Pin Diagram

Logic

FLAG

9

DRVH

SW

GND

DRVL

Anti−Cross

Conduction

BST

DRVH

SW

VCC

DRVL

EN

Fault

UVLO

Pre−OV

ZCD

Detection

Figure 2. Block Diagram

Table 1. Pin Descriptions

Pin No. Symbol Description

1 BST Floating bootstrap supply pin for high side gate driver. Connect the bootstrap capacitor between this pin

2 PWM Control input. The PWM signal has three distinctive states: Low = Low Side FET Enabled, Mid = Diode

3 EN Logic input. A logic high to enable the part and a logic low to disable the part.

4 VCC Power supply input. Connect a bypass capacitor (0.1 mF) from this pin to ground.

5 DRVL Low side gate drive output. Connect to the gate of low side MOSFET.

6 GND Bias and reference ground. All signals are referenced to this node (QFN Flag).

7 SW Switch node. Connect this pin to the source of the high side MOSFET and drain of the low side MOSFET.

8 DRVH High side gate drive output. Connect to the gate of high side MOSFET.

9 FLAG Thermal flag. There is no electrical connection to the IC. Connect to ground plane.

and the SW pin.

Emulation Enabled, High = High Side FET Enabled.

http://onsemi.com

2

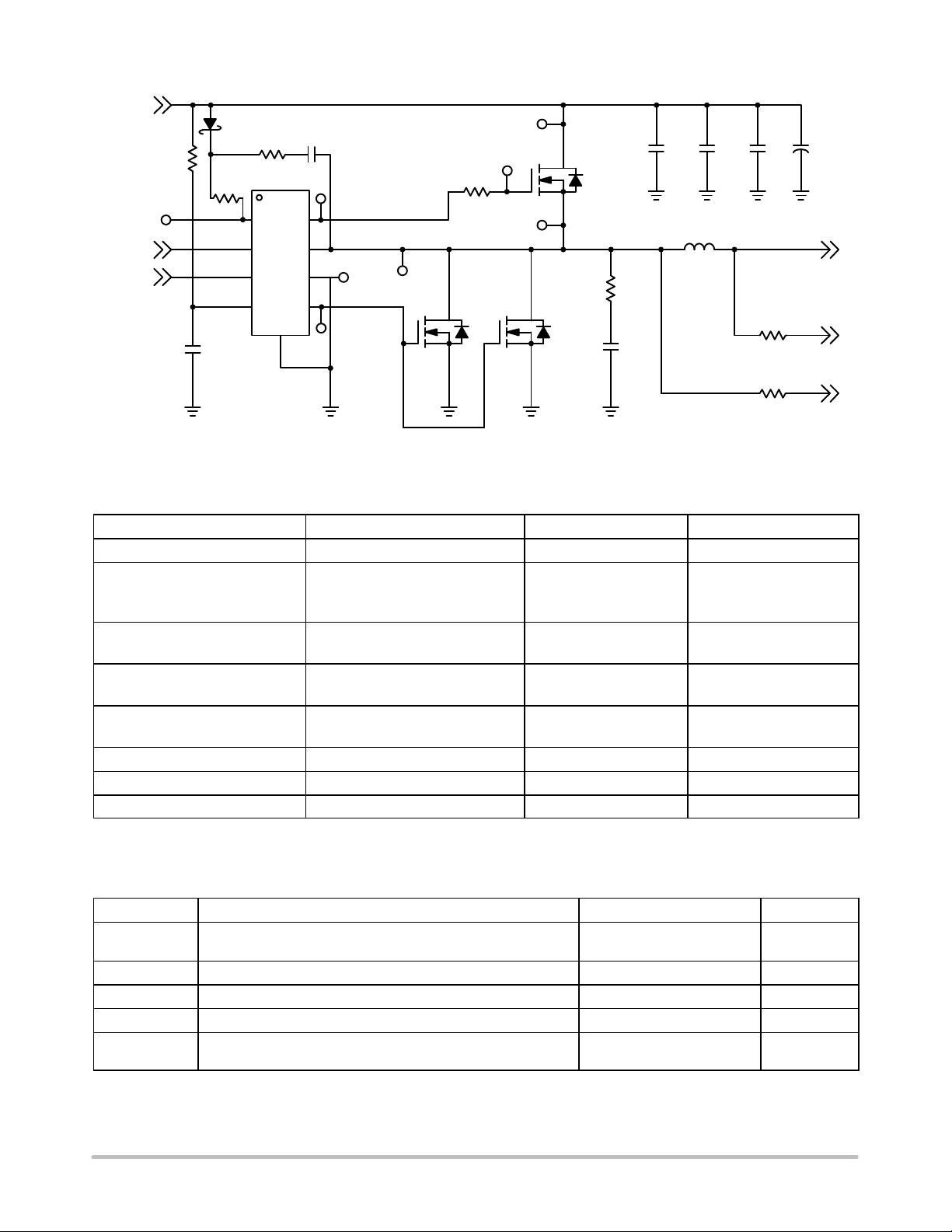

12V_POWER

TP4

PWM

DRON

R1

1.02

C5

1uF

CR1

MMSD4148

R143

0.0

R164

0.0

NCP5901

BST

PWM

EN

VCC

PAD

HG

SW

GND

LG

C4

0.027uF

TP3

VREG_SW1_HG

VREG_SW1_OUT

VREG_SW1_LG

TP8

NCP5901

R142

0.0

TP6

TP7

Q9 Q10

NTMFS4851N NTMFS4851N

Figure 3. Application Circuit

TP2

TP1

TP5

Q1

NTMFS4821N

R3

2.2

C6

2700pF

C1 C2 C3 CE9

4.7uF 4.7uF 4.7uF 390uF

L

+

VCCP

235nH

JP13_ETCH

JP14_ETCH

CSN11

CSP11

Table 2. ABSOLUTE MAXIMUM RATINGS

Pin Symbol Pin Name V

MAX

VCC Main Supply Voltage Input 15 V −0.3 V

BST Bootstrap Supply Voltage 35 V wrt/ GND

40 V ≤ 50 ns wrt/ GND

15 V wrt/ SW

SW Switching Node

(Bootstrap Supply Return)

35 V

40 V ≤ 50 ns

DRVH High Side Driver Output BST+0.3 V −0.3 V wrt/SW

−2 V (<200 ns) wrt/SW

DRVL Low Side Driver Output VCC+0.3 V −0.3 V DC

PWM DRVH and DRVL Control Input 6.5 V −0.3 V

EN Enable Pin 6.5 V −0.3 V

GND Ground 0 V 0 V

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the

Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

device reliability.

V

MIN

−0.3 V wrt/SW

−5 V

−10 V (200 ns)

−5 V (<200 ns)

Table 3. THERMAL INFORMATION (All signals referenced to AGND unless noted otherwise)

Symbol Parameter Value Unit

R

q

JA

T

J

T

A

T

STG

MSL Moisture Sensitivity Level SOIC Package

* The maximum package power dissipation must be observed.

1. I in2 Cu, 1 oz thickness.

2. Operation at −40°C to −10°C guaranteed by design, not production tested.

Thermal Characteristic SOIC Package (Note 1)

DFN Package (Note 1)

123

74

°C/W

Operating Junction Temperature Range (Note 2) 0 to 150 °C

Operating Ambient Temperature Range −10 to +125 °C

Maximum Storage Temperature Range −55 to +150 °C

1

DFN Package

1

http://onsemi.com

3

Loading...

Loading...