ON MC74VHC1GT50DF, MC74VHC1GT50DT Schematic [ru]

MC74VHC1GT50

Noninverting Buffer /

CMOS Logic Level Shifter

TTL−Compatible Inputs

The MC74VHC1GT50 is a single gate noninverting buffer

fabricated with silicon gate CMOS technology. It achieves high speed

operation similar to equivalent Bipolar Schottky TTL while

maintaining CMOS low power dissipation.

The internal circuit is composed of three stages, including a buffer

output which provides high noise immunity and stable output.

The device input is compatible with TTL−type input thresholds and

the output has a f ull 5 V C MOS l evel o utput s wing. T he input p rotection

circuitry on this device allows overvoltage tolerance on the input,

allowing the device to be used as a logic−level translator from 3 V

CMOS logic to 5 V CMOS Logic or from 1.8 V CMOS logic to 3 V

CMOS Logic while operating at the high−voltage power supply.

The MC74VHC1GT50 input structure provides protection when

voltages up to 7 V are applied, regardless of the supply voltage. This

allows the MC74VHC1GT50 to be used to interface high voltage to

low voltage circuits. The output structures also provide protection

when V

device destruction caused by supply voltage − input/output voltage

mismatch, battery backup, hot insertion, etc.

= 0 V. These input and output structures help prevent

CC

http://onsemi.com

5

1

SC−88A/SOT−353/SC−70

DF SUFFIX

CASE 419A

5

1

TSOP−5/SOT−23/SC−59

DT SUFFIX

CASE 483

MARKING

DIAGRAMS

5

M

VL M G

G

1

5

VL M G

G

1

Features

• Designed for 1.65 V to 5.5 V

• High Speed: t

= 3.5 ns (Typ) at VCC = 5 V

PD

• Low Power Dissipation: I

• TTL−Compatible Inputs: V

• CMOS−Compatible Outputs: V

Operation

CC

= 1 mA (Max) at TA = 25°C

CC

= 0.8 V; VIH = 2.0 V, VCC = 5 V

IL

> 0.8 VCC; VOL < 0.1 VCC @Load

OH

• Power Down Protection Provided on Inputs and Outputs

• Balanced Propagation Delays

• Pin and Function Compatible with Other Standard Logic Families

• Chip Complexity: FETs = 104; Equivalent Gates = 26

• Pb−Free Packages are Available

5

NC

1

2

IN A

34

Figure 1. Pinout (Top View)

V

CC

OUT YGND

VL = Device Code

M = Date Code*

G = Pb−Free Package

(Note: Microdot may be in either location)

*Date Code orientation and/or position may vary

depending upon manufacturing location.

PIN ASSIGNMENT

1

2

3 GND

4

5V

FUNCTION TABLE

A Input Y Output

L

H

NC

IN A

OUT Y

CC

L

H

IN A

Figure 2. Logic Symbol

© Semiconductor Components Industries, LLC, 2007

February, 2007 − Rev. 13

1

OUT Y

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 4 of this data sheet.

1 Publication Order Number:

MC74VHC1GT50/D

MC74VHC1GT50

MAXIMUM RATINGS

Symbol Characteristics Value Unit

V

V

V

I

I

OUT

I

q

T

V

I

Latchup

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the

Recommended Opera t i n g Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect

device reliability.

1. Tested to EIA/JESD22−A114−A

2. Tested to EIA/JESD22−A115−A

3. Tested to JESD22−C101−A

4. Tested to EIA/JESD78

DC Supply Voltage −0.5 to +7.0 V

CC

DC Input Voltage −0.5 to +7.0 V

IN

DC Output Voltage VCC = 0

OUT

I

Input Diode Current −20 mA

IK

Output Diode Current V

OK

High or Low State

< GND; V

OUT

OUT

> V

CC

−0.5 to 7.0

−0.5 to V

CC

+20 mA

DC Output Current, per Pin +25 mA

DC Supply Current, VCC and GND +50 mA

CC

P

Power dissipation in still air SC−88A, TSOP−5 200 mW

D

Thermal resistance SC−88A, TSOP−5 333 °C/W

JA

T

Lead temperature, 1 mm from case for 10 secs 260 °C

L

T

Junction temperature under bias +150 °C

J

Storage temperature −65 to +150 °C

stg

ESD Withstand Voltage Human Body Model (Note 1)

ESD

Machine Model (Note 2)

Charged Device Model (Note 3)

> 2000

> 200

N/A

Latchup Performance Above VCC and Below GND at 125°C (Note 4) ±500 mA

+ 0.5

V

V

RECOMMENDED OPERATING CONDITIONS

Symbol Characteristics Min Max Unit

V

V

V

t

DC Supply Voltage 1.65 5.5 V

CC

DC Input Voltage 0.0 5.5 V

IN

DC Output Voltage VCC = 0

OUT

T

Operating Temperature Range −55 +125 °C

A

, tfInput Rise and Fall Time VCC = 3.3 V ± 0.3 V

r

High or Low State

V

= 5.0 V ± 0.5 V

CC

0.0

0.0

0

0

5.5

V

100

20

CC

ns/V

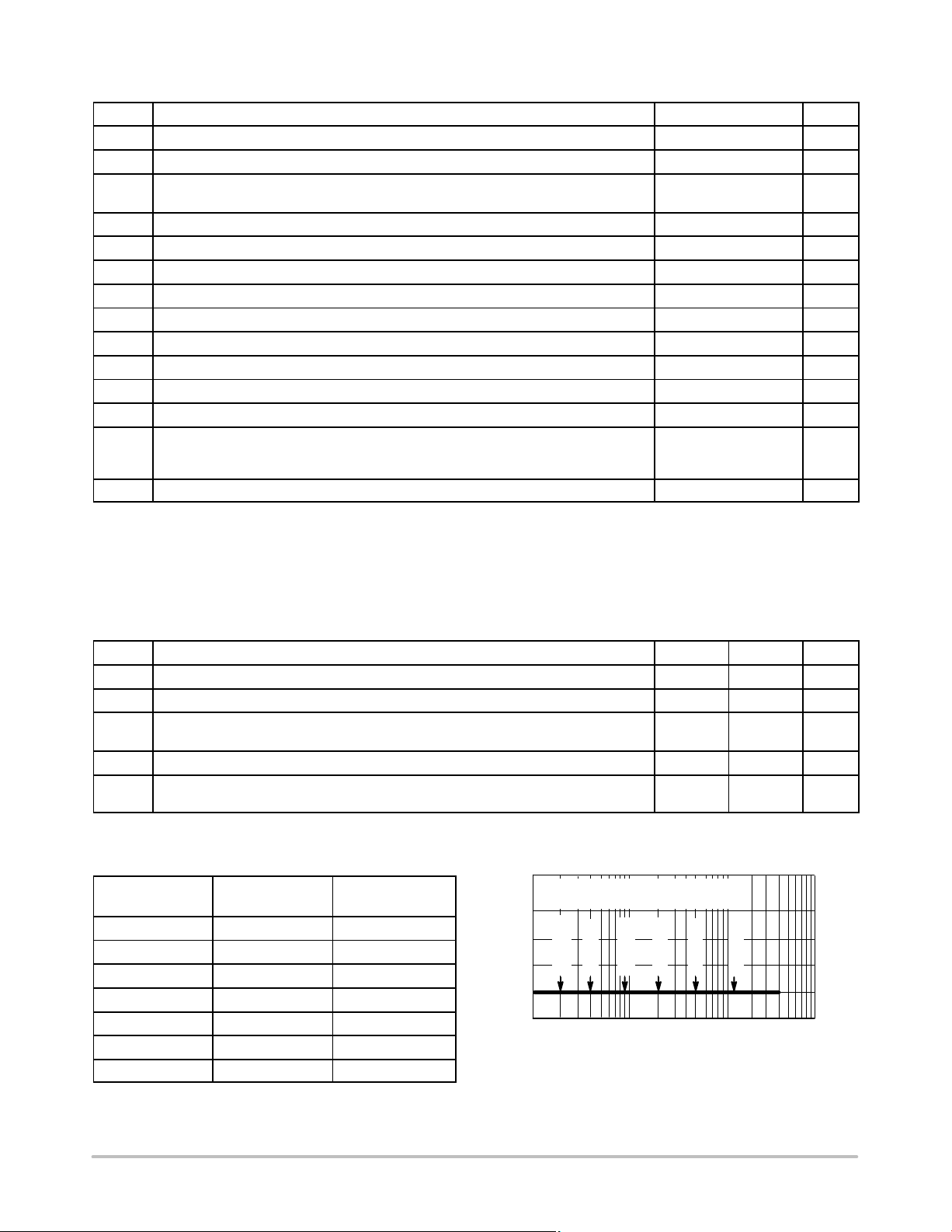

Device Junction Temperature versus

Time to 0.1% Bond Failures

Junction

Temperature °C

Time, Hours Time, Years

80 1,032,200 117.8

90 419,300 47.9

100 178,700 20.4

110 79,600 9.4

120 37,000 4.2

130 17,800 2.0

140 8,900 1.0

Figure 3. Failure Rate vs. Time Junction Temperature

FAILURE RATE OF PLASTIC = CERAMIC

UNTIL INTERMETALLICS OCCUR

= 130 C°

J

T

J

J

T

T

= 110 C°

= 120 C°

1

NORMALIZED FAILURE RATE

1 10 100

TIME, YEARS

C°

C°

= 80

= 90

= 100 C°

J

T

J

J

T

T

1000

V

http://onsemi.com

2

MC74VHC1GT50

Î

l

Î

Î

DC ELECTRICAL CHARACTERISTICS

V

CC

Symbol Parameter Test Conditions (V) Min Typ Max Min Max Min Max Unit

V

IH

Minimum

High−Level

Input Voltage

1.65 to 2.29

2.3 to 2.99

3.0

4.5

5.5

V

IL

Maximum

Low−Level

Input Voltage

1.65 to 2.29

2.3 to 2.99

3.0

4.5

5.5

OH

OL

I

IN

Minimum

High−Level

Output

Voltage

Maximum

Low−Level

Output

Voltage

Maximum

Input

Leakage

V

= V

IN

IH

IOH = −50 mA

1.65 to 2.99

3.0

4.5

V

= VIH

IN

I

= −4 mA

OH

= −8 mA

I

OH

VIN = V

IL

IOL = 50 mA

3.0

4.5

1.65 to 2.99

3.0

4.5

V

= V

IN

IL

IOL = 4 mA

= 8 mA

I

OL

3.0

4.5

VIN = 5.5 V or GND 0 to

5.5

V

V

Current

Maximum

I

CC

Quiescent

VIN = VCC or GND 5.5 1.0 20 40

Supply

Current

I

CCT

Quiescent

Supply

Input: VIN = 3.4 V 5.5 1.35 1.50 1.65 mA

Current

I

OPD

Output

Leakage

V

= 5.5 V 0.0 0.5 5.0 10

OUT

Current

TA = 25°C TA ≤ 85°C −55 ≤ TA ≤ 125°C

0.50 V

CC

0.45 V

CC

1.4

2.0

2.0

VCC − 0.1

2.9

4.4

2.58

3.94

3.0

4.5

0.0

0.0

0.10 V

0.15 V

0.53

0.8

0.8

0.1

0.1

0.1

0.36

0.36

CC

CC

0.50 V

CC

0.45 V

CC

1.4

2.0

2.0

VCC − 0.1

2.9

4.4

2.48

3.80

0.10 V

0.15 V

0.53

0.8

0.8

0.1

0.1

0.1

0.44

0.44

CC

CC

VCC − 0.1

$0.1 $1.0 $1.0

0.50 V

0.45 V

1.4

2.0

2.0

2.9

4.4

2.34

3.66

CC

CC

0.10 V

0.15 V

0.53

0.8

0.8

0.1

0.1

0.1

0.52

0.52

CC

CC

V

V

V

V

V

V

mA

mA

mA

= 50 pF

= 50 pF

= 50 pF

= 3.0 ns

f

Min

TA = 25°C

Typ

4.5

6.3

3.5

4.3

Max

13.3

19.5

10.0

13.5

6.7

7.7

TA ≤ 85°C

Min

−55 ≤ TA ≤ 125°C

Max

14.5

22.0

11.0

15.0

7.5

8.5

Min

Max

17.5

25.5

13.0

17.5

8.5

9.5

5 10 10 10 pF

Unit

ns

ns

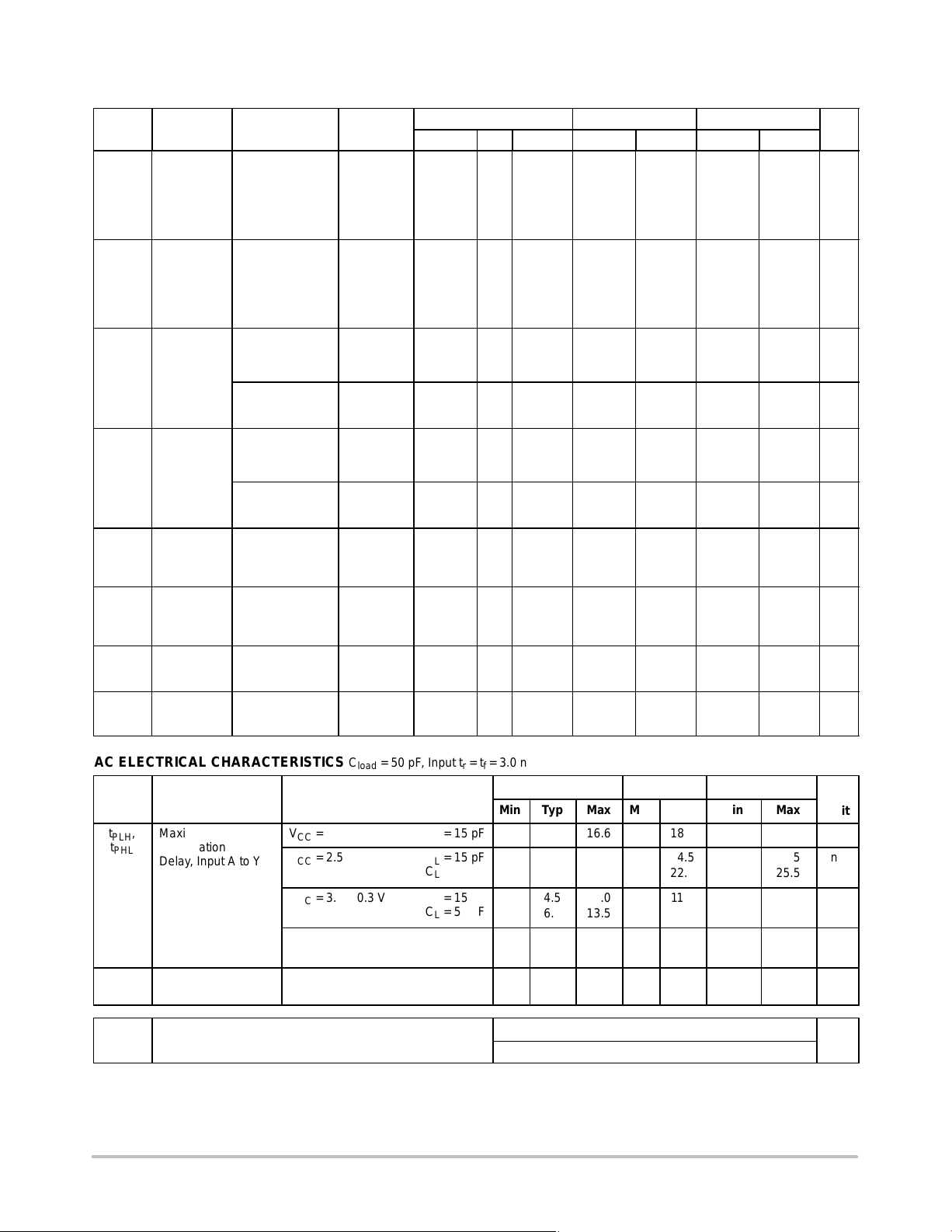

AC ELECTRICAL CHARACTERISTICS C

ÎÎ

Symbo

t

PLH

t

PHL

C

ÎÎÎÎ

,

Maximum

Propagation

Delay, Input A to Y

Maximum Input

IN

Capacitance

Parameter

ОООООООО

Test Conditions

VCC = 1.8 ± 0.15 V CL = 15 pF 16.6 18.0 22.0 ns

VCC = 2.5 ± 0.2 V CL = 15 pF

VCC = 3.3 ± 0.3 V CL = 15 pF

VCC = 5.0 ± 0.5 V CL = 15 pF

= 50 pF, Input tr = t

load

C

C

C

L

L

L

Typical @ 25°C, VCC = 5.0 V

C

Power Dissipation Capacitance (Note 5)

PD

12

pF

5. CPD is defined as the value of the internal equivalent capacitance which is calculated from the operating current consumption without load.

Average operating current can be obtained by the equation: I

power consumption; P

= CPD V

D

2

fin + ICC VCC.

CC

= CPD VCC fin + ICC. CPD is used to determine the no−load dynamic

)

CC(OPR

http://onsemi.com

3

Loading...

Loading...