Page 1

MC68000"SI

NG

LE

BOARD-

COM

PUTE'R,

USER'S

MANUAL

.

01·

OMNISvTE

.

Page 2

OB68K1A

MC68000

SINGLE

BOARD

COMPUTER

USER'S

MANUAL

[]I

OMNIBYTE

The information in this document has been carefully checked and is believed to

be

entirely

reliable. However, no responsibility is assumed for inaccuracies. Furthermore, Omnibyte reserves

the right to make changes

to

any products herein to improve reliability, function, or design.

Omnibyte does not assume any liability arising out

of

the application or useofany product or cir-

cuit

described herein; neither doesitconvey any license under its patent rights nor the rights

of

others.

The technical information contained herein is provided for reference, evaluation and repair pur-

poses only and is copyrighted. It may not

be

copied or duplicated in part or in whole for any pur-

pose without the express written permission

of

Omnibyte Corporation.

VERSAbug &MACSbug are trademarksofMotorola, Inc.

MULTIBUS is a trademark

of

Intel Corporation

OB68K1

& OB68K1A are trademarks of Omnibyte Corporation

OMNIBYTE CORP •

245

West Roosevelt Road • West Chicago,

Illinois

60185 • 312/231-6880

© COPYRIGHT 1983

BY

OMNIBYTE CORPORATION

Page 3

TABLE

OF

CONTENTS

Page

1.0 Introduction I Installation . . . . .. .. . . . . . . . . . . . .. . . . . . . . .. . . . . . . . . . . .

..

4

1.1

Introduction......................................................

4

1.2

Unpacking Instructions. . . .. . . . .. .. . . . . . . . . . . . . . .. . . . . . .. . . . . . . . . .

..

4

1.3

Inspection 4

1.4

Compatibility With Multibus

Products.

. .. .. . . . . . .. .. . . . . . . . .. .. .. . .

..

4

1.5

Factory Standard Configuration

5-6

2.0

Overviewofthe Computer Board. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

..

7

2.1

SummaryofFeatures . .. .. . . . . . .. .. . . . . . . . . . . . . . . . . . . .. .. . . . . . . . .

..

7

2.2

Power Requirements. . . .. .. . . . . .. . . . . . . . . . . . . . .. . . . . . . .. . . . . . . . . .

..

7

3.0

General Description of 0

B6SK

1A 9

3.1

Serial Interface 9

3.2

Timer 9

3.3

Parallel Interface . . . . . . .. .. . . . . . . .. .. . . . . . . . .. . . . . . . . .. .. . . . . . . . .

..

9

3.4

Bus Arbitration. . . . . . . . . . . . . . . . . .... . . . . . . . . . .. . . . . . .. . . . . . . . . . . .

..

9

3.5

On-board Memory

10

3.5.1

On-board

Read

Only Memory

10

3.5.2 On-board Dynamic

RAM

10-11

3.6

Address Decoding and Memory Mapping

11

3.6.1

ROM

Address Selection

(SW-3)

12

3.6.2

RAM

Address Selection

(SW-1)

12

3.6.3

I/O

Base Address Selection

(SW-2)

12

3.6.4 External

RAM

Access Address

(SW-4)

12-13

3.6.5 Operational Considerations

13

3.6.6 Undecoded Addresses

13

3.7

Transfer Acknowledge and Bus Errors

13-14

3.8

Function Codes

14

3.9

Clocks

14

3.9.1

Processor Clock

15

3.9.2 Baud Rate Clock

15

3.9.3 Bus Clockand Constant Clock

15

3.9.4 The EClock

15

3.10 Interrupts

15

3.11

Status Indicators :

16

3.12

Single-Step Mode

16

Page 4

3.13 Restart Vector Accessing

16

3.14 Front Panel Connector

16

4.0

User Definable

Options.

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

17

4.1

Serial Port Configuration (K25,

K26)

19

4.1.1

Transparent Mode

(K10)

19

4.1.2 Baud Rate Selection (K18,

K19)

21

4.1.2.1

Manual Baud Rate Selection

21

4.1.2.2 Software Baud Rate Selection

22

4.2

Bus Error Jumper

(K6)

23

4.3 DTACK Select (K20,

K21)

24

4.4 Interrupt Priority

(K2)

26

4.5

CCLK and BCLK (K14,

K4)

27

4.6

Bus Arbitration(K5,

K7, K8,

K9)

27

4.7 Initialize

(K3)

29

4.8

ROM

Socket Configuration

(K22)

:

29

4.8.1

ROM

Size JumperConfiguration

30

4.9 Timer(K16,

K17)

33

4.10 External

RAM

Access(K12,

K27)

34

4.11

Watchdog Timer

for

External

RAM

Access

(K23)

35

4.12 Optional Front Panel

(K1)

35

4.13 Miscellaneous Jumper Identification

37

4.14 System Configuration

42

5.0 Connector Pinouts

42

5.1

MultibusP1andP2Connectors

42

5.2 PIA and ACIA Connectors

45

5.3 Compatible Cable End Connectors

47

6.0 Memory Decoding

48

6.1

Memory Maps

48

6.2 I/O Address Assignments

53

6.3

Motorola MEX68KDM Compatibilty

55

6.4 OB68K1/0B68K1A Compatibility/Enhancements

55-56

6.5 68000 Memory Organization

56

6.6 OB68K1A Schematic Diagrams

58

7.0 Terminal

Monitor

Programs

65

8.0

Warranty Information

66

9.0

Ordering Information

67

10.0 Appendix(DATA SHEETS)

67

Page 5

Figure

1.0

Figure

1.1

Table

1.5

Figure

2.0

Table

4.0

Figure

4.0

Figure

4.1

Figure

4.1.1

Figure

4.1.2

Table

4.1.2.1

Table

4.3

Figure

4.3

Figure

4.4

Figure

4.6

Figure

4.7

Figure

4.8.1

Figure

4.8.2

Figure

4.8.3

Figure 4.8.4

Figure

4.9

Figure

4.10

Figure

4.12(A)

Figure

4.12(B)

Figure

4.13

Table

5.1.1

Table

5.1.2

Table

5.2.1

Table

5.2.2

Table

5.2.3

Figure

6.1.1

Figure 6.1.2

Figure 6.1.3

Figure 6.1.4

Table

6.2

Figure

6.6(A)

Figure 6.6(8)

Figure

6.6(C)

Tabl,e

6.6

LIST

OF

FIGURES AND TABLES

Photographofthe

OB68K1

A . . . . . . . . . . . . . . . . . . .. .. .. . . . . . . .

..

1

OB68K1A Parts Location

Diagram.

. . . . . . . . .. .. . . . . . . . . . . . . .

..

2

Factory JumperConfiguration 5

Block Diagram. . . . . . . . . . . . . . . . . . . . .. . . . . . . . . . . . .. .. . . . . . .

..

8

JumperOptions

17

LocationofJumperOptions

18

Serial Port JumperOptions

20

Tranparentllndep. Mode Jumper Location

21

Serial Port Baud Rate Jumpers

22

Baud Rate Selection

23

ROM

DTACKdeiays

25

ROM

DTACKdelay Jumpers

25

Interrupt Jumpers

26

Bus Arbitration JumperConfiguration

28

Reset JumperConfiguration

29

ROM

Size Jumper Configuration and Location

30

ROM

Configuration Plug Layouts

31

ROM

Socket Configuration

32

ROM

Chip Pinout Configuration

32

TimerOption Pin Identification and Location

33

External

RAM

Access Size Jumpers

34

Optional Front Panel -Connector

35

Optional Front Panel -Circuit

36

Miscellaneous Jumper Locations

37-41

IEEE-796P1Connector Pinout

43

IEEE-796P2Connector Pinout

44

PIA Connector Pinout.

45

ACIA Port 0 Connector Pinout

46

ACIA Port 1Connector Pinout

46

Memory Map (Factory Standard) 32KVersion

49

Memory Map (FactoryStandard) 128KVersion

50

Memory MapOption (MAP0)32K Version

51

Memory Map Option (MAP0)128K Version

52

Onboard I/O Address Assignments

54

OB68K1A Schematic -

CPU,

Decoding and Buffers

59

OB68K1A Schematic

-I/O

60

OB68K1

A Schematic -Memory

61

OB68K1

A Parts List

62-64

Page 6

Page 7

o

aJ

0')

co

"

.....

:I>

"'0

:I>

,,::D

_

....

C)cn

c:

....

::DO

mo

.....

:1>

.....

.....

-

o

z

c

i>

C)

::D

:I>

3:

UJ4

b'

K24

K34D

UJ2

~K231

....

R19

rn

0 0

N

I

u

5~

UJ5

C26

U60

U64

Page 8

3

Page 9

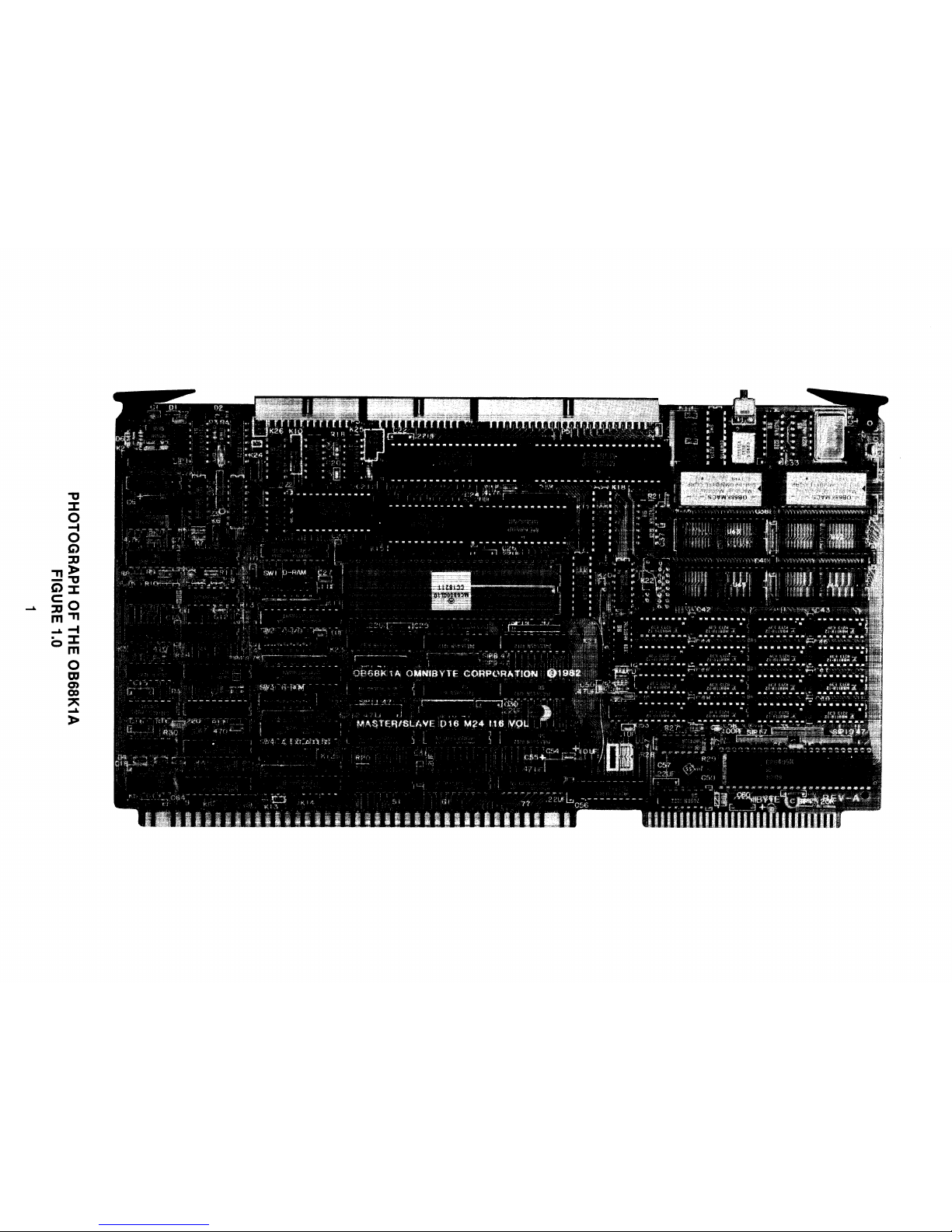

1.0 INTRODUCTION I INSTALLATION

The OMNIBYTE OB68K1A 68000 Single Board Computer has been carefully

de-

signed to

fulfill

a varietyofprocessing applications ranging from extremely small

one board dedicated instruments

to

extremely large multi-processing systems

utilizing several processor boards with shared memory and I/O. Figure

1.0

is a

photograph

of

this board and Figure

1.1

is the parts location diagram.

1.1

Introduction

This chapter provides the unpacking, inspection and configuration instructions

for the OB68K1A Single Board Computer.

1.2 Unpacking Instructions

IF THE SHIPPING CARTON

IS

DAMAGED

UPON

RECEIPT,

REQUEST THAT CARRIER'S AGENT

BE

PRESENT WHILE

THE ITEMS

ARE

BEING UNPACKED AND INSPECTED.

Unpack the OB68K1A Single Board Computer from its shipping carton. Save the

packing material for storing and reshipping the items in case this becomes

necessary.

1.3 Inspection

The OB68K1A Single Board Computer should

be

inspected upon receipt for

broken, damaged, or missing parts, and for physical damage to the printed circuit

board or connectors.

1.4 Compatibility

with

Multibus Products

The OB68K1A Single Board Computer has been carefully designed

to

meet the

most current IEEE

796

bus specifications. It is advised that you become familiar

with these specifications and how they compare with the original and current

Multibus specifications. The OB68K1A implements full address and bus arbitra-

tion for single and multi-processor systems and has been designed for com-

patibility with existing Multibus products. Omnibyte assumes no liability for

non-compatibility

of

certain products which do not meet published IEEE

796

specifications.

4

Page 10

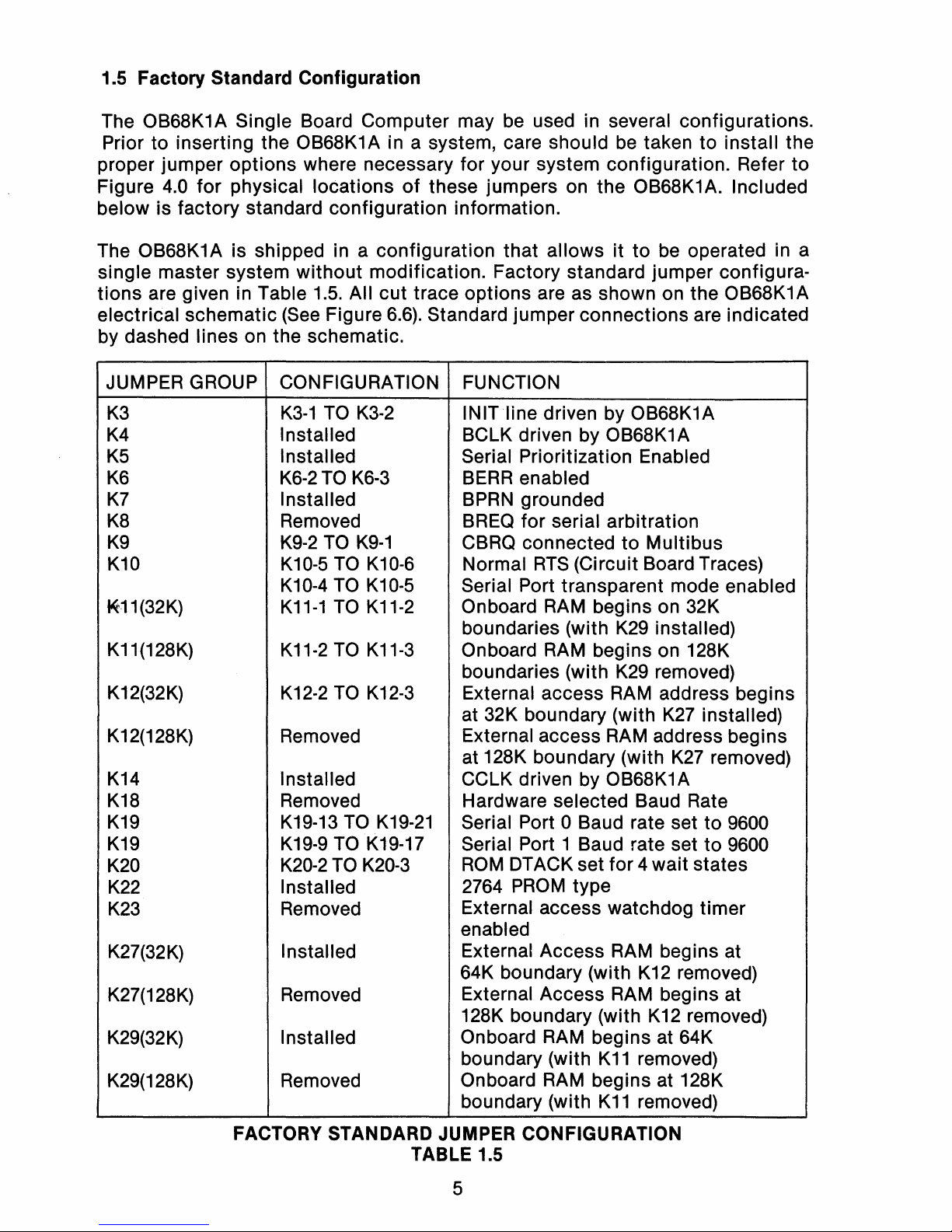

1.5 Factory Standard Configuration

The OB68K1A Single Board Computer may be used in several configurations.

Prior to inserting the OB68K1A in a system, care should be taken to install the

proper jumper

options

where necessary for your system configuration. Refer

to

Figure 4.0

for

physical locations

of

these jumpers on the OB68K1A. Included

below is factory standard configuration information.

The OB68K1A is shipped in a configuration

that

allowsitto

be operated in a

single master system

without

modification. Factory standard jumper configura-

tions

are given in Table

1.5.

All

cut

trace

options

are as shown on the OB68K1A

electrical

schematic

(See Figure

6.6).

Standard jumper connections are indicated

by dashed lines on the schematic.

JUMPER GROUP CONFIGURATION FUNCTION

K3

K3-1

TO

K3-2

INITline

driven by OB68K1A

K4

Installed

BCLK driven by OB68K1A

K5

Installed

Serial Prioritization Enabled

K6

K6-2TO

K6-3

BERR

enabled

K7

Installed BPRN grounded

K8

Removed

BREQ

for serial arbitration

K9

K9-2

TO

K9-1

CBRQ connected

to

Multibus

K10

K10-5

TO

K10-6

Normal

RTS

(Circuit Board Traces)

K10-4

TO

K10-5

Serial Port transparent mode enabled

K11(32K)

K11-1

TO

K11-2

Onboard RAM begins on 32K

boundaries (with

K29

installed)

K11(128K)

K11-2

TO

K11-3

Onboard RAM begins on 128K

boundaries (with K29 removed)

K12(32K)

K12-2

TO

K12-3

External access

RAM

address begins

at 32K boundary (with

K27

installed)

K12(128K) Removed External access RAM address begins

at 128K boundary (with

K27

removed)

K14

Installed CCLK driven by OB68K1A

K18

Removed

Hardware selected Baud Rate

K19

K19-13

TO

K19-21

Serial Port 0 Baud rate setto9600

K19

K19-9

TO

K19-17

Serial Port 1 Baud rate setto9600

K20

K20-2

TO

K20-3

ROM

DTACK set

for

4 wait states

K22

Installed

2764

PROM

type

K23

Removed

External access watchdog

timer

enabled

K27(32K)

Installed

External Access RAM begins at

64K boundary (with

K12

removed)

K27(128K) Removed

External Access RAM begins at

128K boundary (with

K12

removed)

K29(32K)

Installed

Onboard RAM begins at 64K

boundary (with

K11

removed)

K29(128K) Removed

Onboard RAM begins at 128K

boundary (with

K11

removed)

FACTORY STANDARD JUMPER CONFIGURATION

TABLE 1.5

5

Page 11

The

OB68K1

A is configured at the factory to operate in the following way;

a)

BUS

The Bus Clock (BCLK), Constant Clock (CCLK) and Reset line (INIT) are driven

off

the board. On-board power-on reset enabled and the bus error jumper

(K6)

is in-

stalled so that bus error exception processing will

be

executed,ifa bus error is

encountered.

b)

INTERRUPTS

No interrupts are connected.

c)

RAM

On-board

RAM

begins at

$000000

(HEX).

Contiguous

RAM

continues

to

$007FFF

(HEX)

in the 32K version and to $01 FFFF

(HEX)

in the 128K version.

d)

ROM

All on-board

ROM

sockets are configured for 2764-type (8Kx8) 5 volt only

EPROM

and the memory map is configured to MAP 1 (for

2764).

ROM

address begins at

$FEOOOO

(HEX)

and continues to $FEFFFF

(HEX).

The

ROM

DTACK is factory

preset for

350

ns (access time)

ROM

chips.

e)

ON-BOARD SERIAL 1/0

PORTS

On-board 1/0 begins at address $FFFEOO

(HEX).

See table

6.2

for specific device

address assignments. Serial Port 0 is configured as a modem for direct connection to a

RS232C

terminal. Serial Port 1 is configured as a terminal for direct con-

nection to a

RS232C

modem or another computer. The baud rates are set to 9600

BPS

at the factory for testing.

f)

OFF-BOARD 1/0

Off-board 1/0 begins at address $FFOOOO

(HEX)

and continues to $FFFDFF.

g)

TRANSPARENT MODE

Transparent mode is enabled.

Please note that the above is the configuration

of

the OB68K1A as shipped from

the factory and

it

does not include setting-up the board in a different configura-

tion

if

desired before power-up_ A detailed listofthe factory installed jumper con-

figurations is given in Table

1.5.

Factory standard configuration is compatible

with Omnibyte's optional

PROM

based terminal monitor routines that provide the

functionality

of

Motorola's MACSbug/VERSAbug/VMEbug/TUTOR programs.

6

Page 12

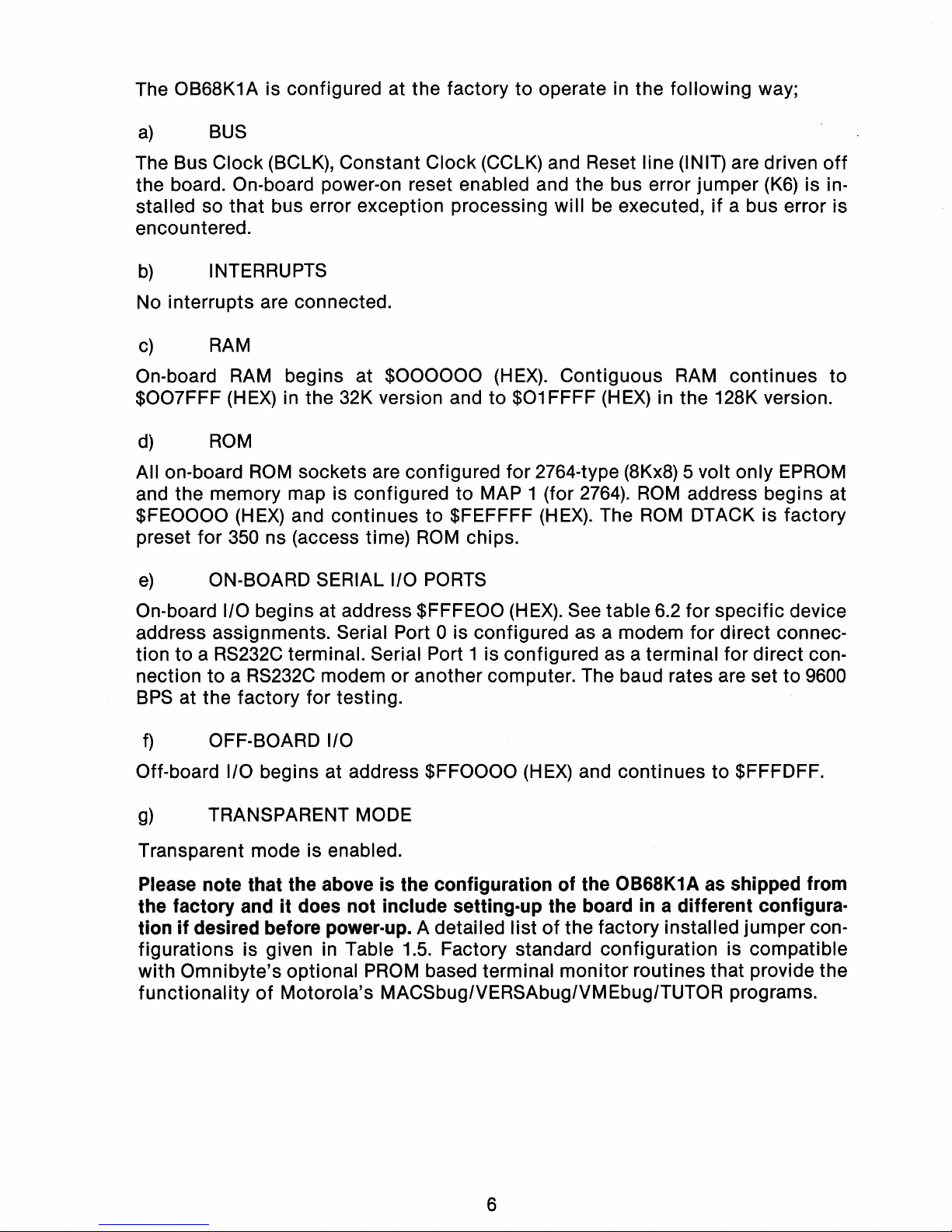

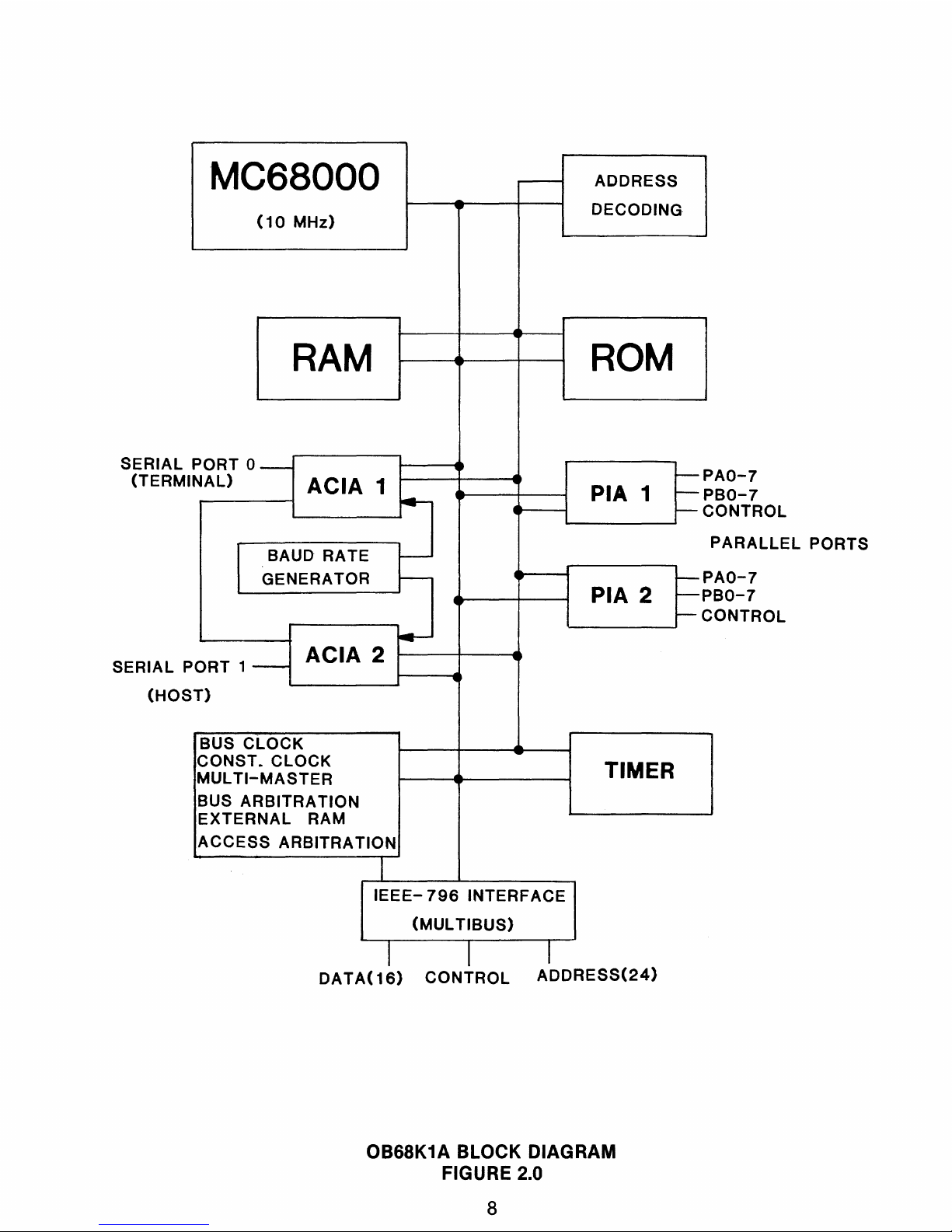

2.0 OVERVIEW OF THE COMPUTER BOARD

This

section

describes the

major

features

of

the OB68K1A. A

block

diagram

of

this

single

board

computer

is shown in Figure 2.0.

2.1

SummaryofFeatures

The OB68K1A

computer

board provides the

following

features:

a.

10MHz processor &

clock

b.

IEEE 796 (Multibus) Compatible (MASTER

D16

M24

116

VOUSLAVE M24

D16)

c. Single step

circuitry

d. Dual Ported on-board RAM (32K byteor128K byte)

e.

Zero

wait

states

for on-board RAM accesses

f.

LSI

Hardware memory refresh

circuit

g.

On-board

ROM

(up

to

192K bytes)

h.

Two asynchronous serial

ports

(RS232C)

i.

Hardware

or

software programmable baud rate generator

j. Two programmable 16-bit parallel I/O ports

k.

Three 16-bit programmable

timers

I.

16

Megabyte (24-bit)

direct

memory addressing

m.

Independantly

Switch

Selectable RAM, ROM,

EXT.

RAM ACCESS, and

I/O base addresses

n.

Multi-Master

bus

arbitration

o.

Motorola

MEX68KDM

software

compatibility

2.2 Power Requirements

The

computer

receives

its

power through the

Multibus

motherboard. Typical

power requirements are as follows:

+

5V

- ±

50/0

+ 12V - ±

5%

-12V-

± 5

%

32K VERSION 128 K VERSION

@ 3.0A @ 3.25A

@

O.05A

@ 0.05A

@

O.05A

@

O.05A

Note: Single 5 volt operation is possible

with

the OB68K1 Aifthe RS232C

ports

are

not

used.

7

Page 13

MC68000

(10

MHz)

RAM

SERIAL

PORT

0-

(TERMI

NAL)

ACIA 1

~

BAUD RATE

~

GENERATOR

I-----

~

SERIAL P

ORT

1-

ACIA 2

~

(HOS

T)

BUS

CLOCK

CONST.CLOCK

MUL

TI-MASTER

BUS

ARBITRATION

EXTERNAL

RAM

ACCESS

ARBITRATION

I

ADDRESS

DECODING-

ROM

-PAO-7

PIA 1

-PBO-7

-CONTROL

1...-

__

---1

PARALLEL

PORTS

t--PAO-7

PIA 2

~PBO-7

~CONTROL

'------I

TIMER

IEEE-

796

INTERFACE

(MULTIBUS)

I I 1

DATA(16)

CONTROL

ADDRESS(24)

OB68K1A BLOCK DIAGRAM

FIGURE 2.0

8

Page 14

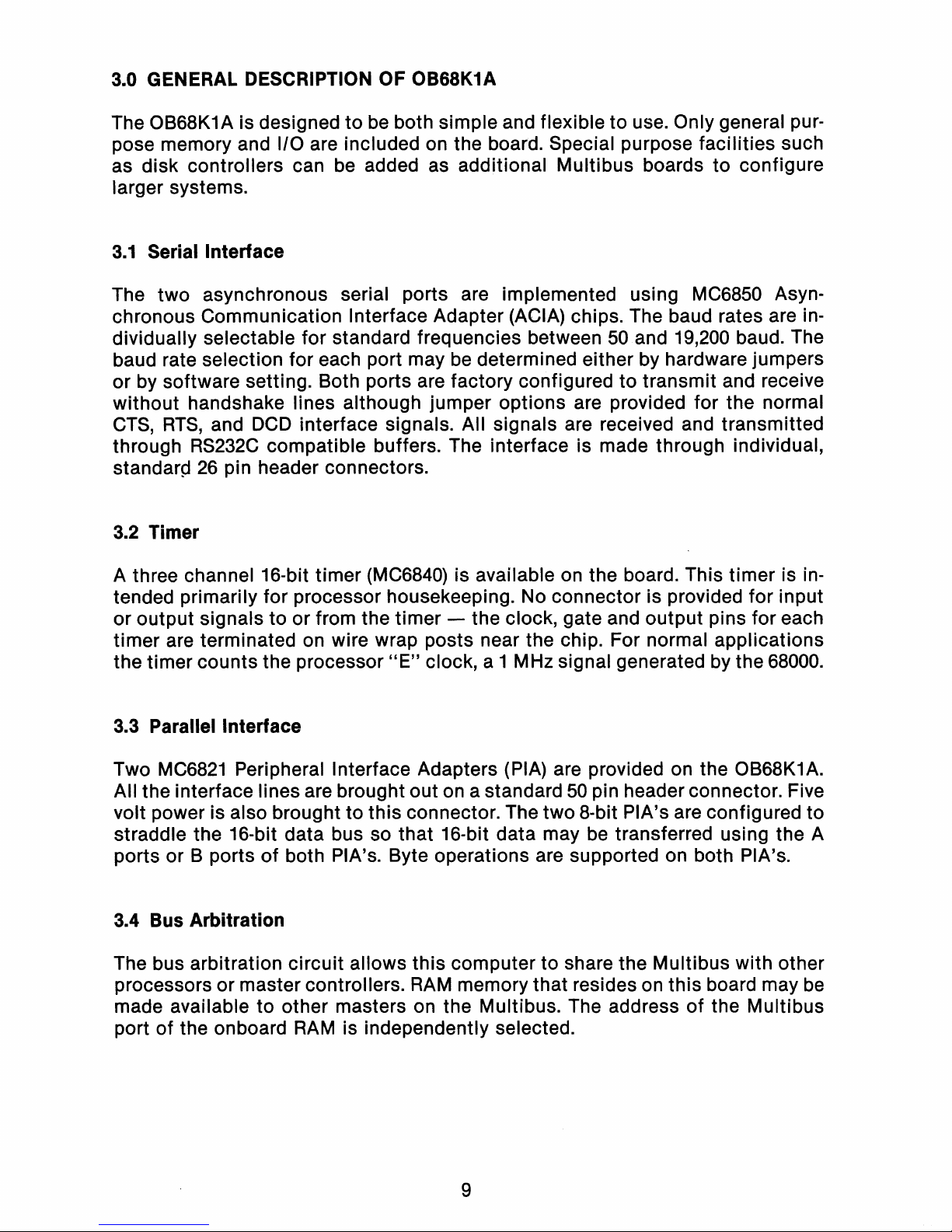

3.0 GENERAL DESCRIPTION OF OB68K1A

The OB68K1A is designed

to

be both simple and flexible to use. Only general purpose memory and I/O are included on the board. Special purpose facilities such

as disk controllers can

be

added as additional Multibus boards to configure

larger systems.

3.1

Serial Interface

The two asynchronous serial ports are implemented using MC6850 Asyn-

chronous Communication Interface Adapter (ACIA) chips. The baud rates are individually selectable for standard frequencies between

50

and 19,200 baud. The

baud rate selection for each port may be determined either by hardware jumpers

or by software setting. Both ports are factory configured

to

transmit and receive

without handshake lines although jumper options are provided for the normal

CTS,

RTS,

and

DCD

interface signals. All signals are received and transmitted

through

RS232C

compatible buffers. The interface is made through individual,

standarp

26

pin header connectors.

3.2

Timer

A three channel 16-bit timer (MC6840) is available on the board. This timer is in-

tended primarily for processor housekeeping. No connector is provided for input

or output signals to or from the timer - the clock, gate and output pins for each

timer are terminated on wire wrap posts near the chip. For normal applications

the timer counts the processor

"E"

clock, a 1 MHz signal generated by the 68000.

3.3 Parallel Interface

Two

MC6821

Peripheral Interface Adapters (PIA) are provided on the OB68K1A.

All the interface lines are brought outon a standard

50

pin header connector. Five

volt power is also brought to this connector. The

two

8-bit PIA's are configured to

straddle the 16-bit data bus so that 16-bit data may be transferred using the A

ports or B ports

of

both PIA's. Byte operations are supported on both PIA's.

3.4 Bus Arbitration

The bus arbitration circuit allows this computer to share the Multibus with other

processors or mastercontrollers.

RAM

memory that resides on this board may

be

made available

to

other masters on the Multibus. The address

of

the Multibus

port

of

the onboard

RAM

is independently selected.

9

Page 15

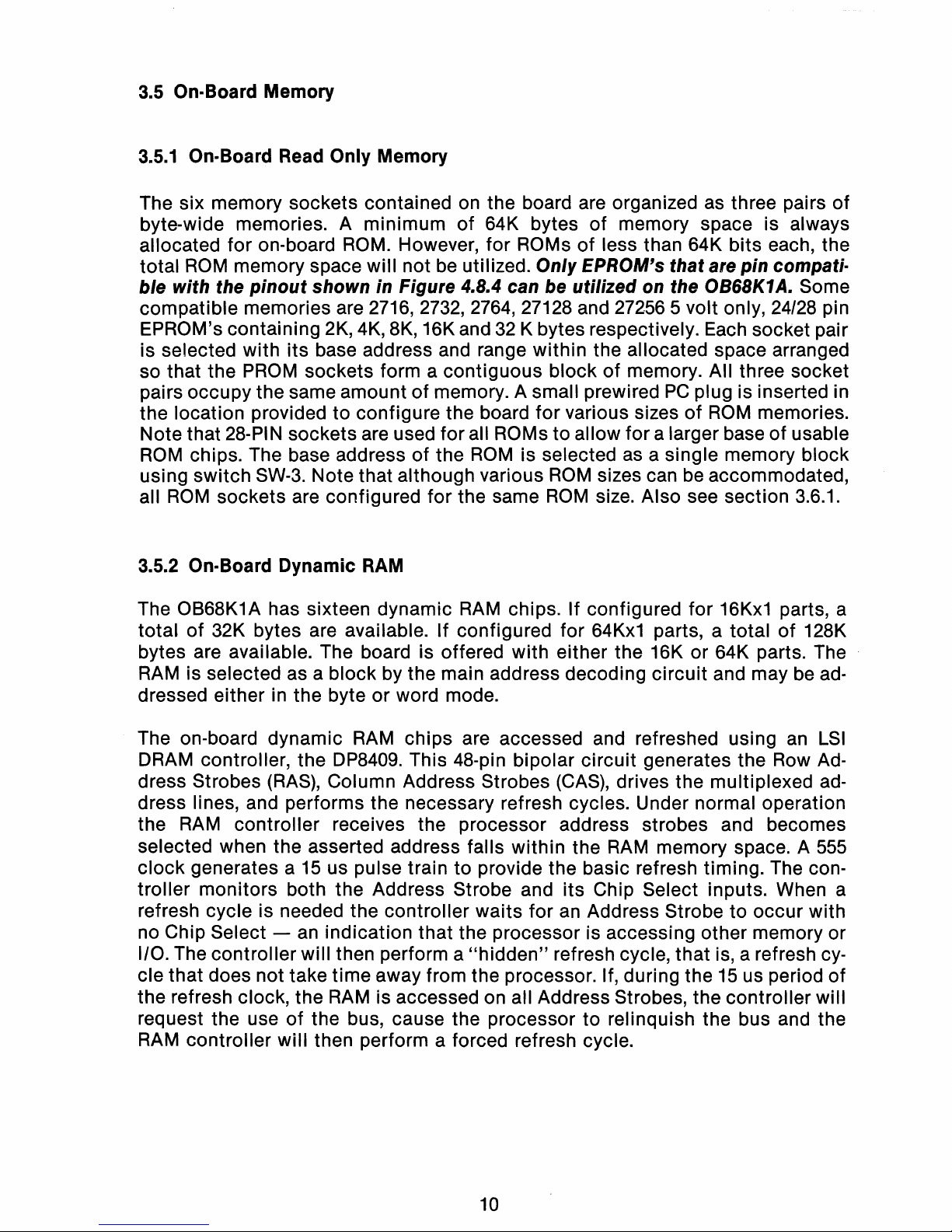

3.5 On-Board Memory

3.5.1

On-Board Read Only Memory

The six memory sockets contained on the board are organized as three pairs

of

byte-wide memories. A

minimum

of

64K bytes

of

memory space is always

allocated

for

on-board ROM. However,

for

ROMs

of

less than 64K

bits

each, the

total

ROM

memory space

will

not

be utilized. OnlyEPROM's that are pin compati-

ble with the

pinout

shown in Figure 4.8.4 can be utilized on the OB68K1

A.

Some

compatible

memories are 2716,2732,2764,27128 and 272565 volt only, 24/28 pin

EPROM's containing 2K, 4K, 8K, 16Kand

32

K bytes respectively. Each socket pair

is selected

with

its

base address and range

within

the allocated space arranged

so that the PROM sockets form a

contiguous

blockofmemory. All three socket

pairs

occupy

the same amountofmemory. A small prewired

PC

plug is inserted in

the location provided

to

configure the board

for

various sizesofROM

memories.

Note that 28-PIN sockets are used

for

all ROMstoallow

for

a largerbaseofusable

ROM

chips. The base addressofthe

ROM

is selected as a single memory

block

using

switch

SW-3. Note that although various

ROM

sizes can be accommodated,

all

ROM

sockets

are configured

for

the same

ROM

size. Also see section 3.6.1.

3.5.2 On-Board Dynamic RAM

The OB68K1A has sixteen dynamic RAM chips.

If

configured for 16Kx1 parts, a

total

of

32K bytes are available.Ifconfigured for 64Kx1 parts, a

total

of

128K

bytes are available. The board is offered

with

either the 16K

or

64K parts. The

RAM is selected as a

block

by the main address decoding

circuit

and may be ad-

dressed either in the byte

or

word mode.

The on-board

dynamic

RAM

chips

are accessed and refreshed using

an

LSI

DRAM controller, the DP8409. This 48-pin bipolar

circuit

generates the Row Address Strobes (RAS), Column Address Strobes (CAS), drives the multiplexed address lines, and performs the necessary refresh cycles. Under normal operation

the RAM

controller

receives the processor address strobes and becomes

selected when the asserted address falls

within

the RAM memory space. A

555

clock

generates a

15

us pulse traintoprovide the basic refresh timing. The con-

troller

monitors

both

the

Address Strobe and

its

Chip Select inputs. When a

refresh cycle is needed the

controller

waits

for

an Address Strobetooccur

with

no Chip Select - an

indication

that

the processor is accessing other memory or

I/O. The

controller

will

then perform a

"hidden"

refresh cycle,

that

is, a refresh cy-

cle

that

does not take

time

away from the processor.

If,

during the

15

us period

of

the refresh clock, the RAM is accessed on all Address Strobes, the

controller

will

request the use

of

the bus, cause the processor

to

relinquish the bus and the

RAM

controllerwiII

then perform a forced refresh cycle.

10

Page 16

The duration

of

forced refresh cycle is about

500

ns. Under most conditions the

refresh overhead

of

the OB68K1A will

be

very low. Note that because the entire

RAM

refresh task is implemented in hardware no processor code-execution

cycles are wasted to perform

RAM

refresh by software.

When the processor performs a Multibus cycle, the duration

of

the cycle will

depend on the availabilityofthe bus and the response timeofthe addressed device.

During these offboard cycles, no address strobes are applied to the

RAM

con-

troller

and forced refreshes are then implemented when needed. The XACK signal

output

by

the OB68K1A signals the external master that data from the onboard

RAM has been placed on the Multibus

or

the datatobe

written has been stored.

Shortly thereafter the external master should terminate the cycle by removing the

read or write command. If the cycle is not terminated afterseveral microseconds,

data in the dynamic

RAM

could

be

lost. A timeout circuit is included on the

OB68K1A that interrupts the external access so a refresh can occur. The offboard

master is not required to wait for the completion

of

an

instruction. The LOCK

feature

of

Multibus is implemented so

an

offboard master may do a test-and-set

operation to the onboard

RAM.

Also see sections 3.6.2 and 3.6.4.

3.6

Address Decoding and Memory Mapping

The OB68K1A has been designed so that the memory mapping is switch selectable by the user. No fusible link devices are needed to change the memory map.

Four separate address decoders are included on the board to individually select

the base address

of

onboard

RAM,

onboard

ROM,

I/O and the Multibus access to

the onboard

RAM.

For eachofthese four blocks, the base address is selected by

the setting

of

an

8-bit

DIP

switch. The dip switches have been socketed so that

dip jumpers can

be

used to fix addressing for production purposes, these dip

jumpers are available through OMNIBYTE.

See

section

9.0

for ordering information. The switch setting is compared with the upper address lines to determine

when the various blocks are being selected (SWITCH BIT 1

= L.S.B., SWITCH BIT

o = M.S.B.;

ON

=

0,

OFF =

1).

Much

of

the random logic associated with address decoding and strobe timing has been consolidated into Programmable Array Logic (PAL)* chips. These circuits are programmed

at

the factory andcannot

be

changed

by

the user.

* PAL

is

a trademarkofMonolithic Memories, Inc.

11

Page 17

3.6.1

ROM

Address Selection

(SW-3)

The 8-bit

DIP

switch

(SW-3)

is used to select the base address

of

the onboard

ROM.

Address lines

A16-23

are compared with the switch setting resulting in a

minimum

ROM

block size

of

64K bytes. The minimum block size will accom-

modate memories through 8K bytes per chip. For larger

ROM

chips, larger

memory block sizes

of

128K and 256K bytes may

be

selected by removing

A16

and

A

17

from the comparator inputs, respectively. All the necessary connections are

made by inserting pre-wired plugs in the location provided. Various jumper

models are available from the factory. Note

that

within the

ROM

block, there are

addresses for which no memory exists. For example, using 8K byte PROMs, the

six sockets provided will occupy 48K

of

the minimum 64K byte block size. The

re-

mainder of

this

block is not accessable and cannot

be

assigned to other memory

or devices.

3.6.2

RAM

Address Selection

(SW-1)

The 8-bit

DIP

switch

(SW-1)

is used to select the base address of the onboard

RAM. Jumpers and cut traces at

A15

and A16 are factory configured for either 32K

or 128K RAM. For 32K

RAM

switch

SW-1

selects base addresses on the lower 32K

block

of

64K byte boundary. For 128K

RAM

switch

(SW-1)

selects base address on

128K byte blocks. For 128K

RAM,

BIT 1ofSW-1

is a

"don't

care" bit, since pins

13

and

14

on

U28

are tied together and the cut trace option at A16is opened.

3.6.3 I/O Base Address Selection

(SW-2)

Because the 68000 accesses I/O the same

as

memory, a 64K byte block

of

memory space is decoded and assigned to the I/O space defined in the IEEE

796

bus specification. No options exist on the boardtochange the sizeofthe I/O

address space, but the base address may be located at any 64K byte boundary

within the available

16

megabyte address range. The onboard I/O devices occupy

the uppermost

512

bytesofthe I/O space; all other addresses within the block

default

to

offboard I/O. Table

6.2

gives the addresses of the onboard I/O devices.

3.6.4 EXTERNAL

RAM

Access Address

(SW-4)

A separate 8-bit DIP switch and comparator are used to determine the base

address

of

the onboard

RAM

when that

RAM

is accessed by another Multibus

master. The

RAM

is then accessed at independently selected addresses chosen

to satisfy requirements

of

both the offboard master and the

OB68K1A.Address

line

A15

can

be

used to gate the comparator in order to decode a 32K byte block

size and jumper options allow the block size to

be

increased. Notice that it is

possible to

limit

the amount

of

memory that can

be

accessed from offboard.

12

Page 18

A 128K byte OB68K1A may allow offboard masters to access 32K, 64K or all 128K

bytes

of

its

onboard RAM. This feature allows portions of the onboard

RAM

to

be

protected from otheroffboard masters. Although limiting blocksofRAM

from offboard access is possible, this option has not been implemented by the factory

and should

be

selected by the userifdesired. Also note that in addition to the

jumper and cut trace option on

A16,

pins

13

and

14

on

U31

have been jumpered

and bit 1

of

SW-4

is a

"don't

care" bit.

(See

Section

3.6.2).

3.6.5 Operational Considerations

When the user is setting the base address switches

of

the OB68K1A care must

be

exercised to avoid overlap of the onboard memory spacesofRAM

ROM,

and 1/0.

The offboard access to the dual-ported

RAM

may arbitrarily overlap any

or

all

of

the onboard RAM,

ROM,

or 1/0 space.

In systems that use multiple OB68K1A computers, the onboard base address

selections may

be

the same for all boards.

The external access to the OB68K1A dual-ported

RAM

appears as a simple

RAM

boardtoan

external Multibus Master. Therefore, the base addressofthe external

access

(SW4)must be selected to avoid overlapofthe dual-ported memory space

with any other memory space on the Multibus. External access spaces

of

Multiple

OB68K1A boards must not overlap. The OB68K1A is protected from accessing

its

own

RAM

via the Multibus by negating onboard access while performing offboard

accesses.

3.6.6 Undecoded Addresses

The

OB68K1

A is designed so that all memory accesses default to offboard

Multibus accesses unless the address that is asserted falls within the onboard

RAM,

ROM

or onboard 1/0 space.

3.7

Transfer Acknowledge and Bus Errors

The 68000's data transfers are asynchronous - A Data Transfer ACKnowledge

(DTACK) signal is required to complete

an

access. For Multibus cycles this signal

is provided naturally by the Multibus Transfer ACKnowledge (XACK). For onboard

ROM

cycles, a DTACK generator is provided to terminate the cycle a fixed

time after

an

on-board memory access is started. The delay time is selectable to

match the access time

of

the on-board

ROM

memory chips.

(See

Section

4.3).

The DTACK signal for onboard

RAM

access cycles is also provided

by

the

ROM

DTACK generator and has also been optimzed for the RAM. The OB68K1A must

generate

an

XACK signal when other Multibus masters access the onboard RAM.

This signal serves to terminate the bus cycle for the offboard master. A tap

on

the

ROM

DTACK generator is used to generate this signal at a delayed time that has

been optimized for the offboard

RAM

access time and no user adjustment is per-

mitted.

13

Page 19

When the OB68K1A accesses external Multibus memory or 1/0, the cycle is terminated by the XACK signal returned by the board that was addressed.

In

the eventthat unimplemented off-board memory is accessed, no DTACK will

be

generated.

An

on-board

"watchdog"

timer is included

to

detect a lack

of

response, and a pulse is generated that may be jumperedtothe 68000 Bus Error

input pin. A signal asserted on this pin will initiate bus error exception processing

and a user-supplied routine is executed

to

allow the systemtoanalyze the report

or recover from this condition.

Notice that the 68000 itself will patiently wait forever,

~f

desired, for a DTACK

response to come. No restriction is placed on the speed

of

response

of

the ad-

dressed memory or device. The watchdog timer delay is user determined and its

implementation is optional.

It is included

to

keep the system from hanging up

if

no response is received.

Conditions that will cause a bus error are:

a)

Accesstooff-board memory addresses that have no responding memory (not

plugged in, or not working).

b)

Access

to

oft-board I/O addresses that have no responsing device (not

plugged in, or not working).

An

access to

an

on-board memory address will not cause a bus error evenifa

memory chip is not installed. On-board I/O uses the 68000 synchronous transfer

capability and no DTACK is required.

3.8

Function Codes

The

68000

processor outputs three function code bits,

FCO,

FC1,

and

FC2

that

allow external circuitryto know the internal operating mode

of

the processor. The

~tate

of

these outputsindicates whetherthe processor is in the supervisoror user

state, whether the present access is a program or data reference, or

if

the pro-

cessor is responding to

an

interrupt. The standard configurationofthe OB68K1A

makes use

of

various function code values only to recognize interrupt

acknowledge cycles.

3.9

Clocks

Four clocks are generated on-board.

14

Page 20

3.9.1

Processor Clock

A

10

MHz crystal oscillator provides the processor clock. It connects directly to

the 68000 clock input pin. The

10

MHz clock is also used as the time base for the

DT

ACK generator.

3.9.2 Baud Rate Clock

A 5.0688 MHzcrystal and a COM8116 comprise the baud rate generator. This

baud rate selection can

be

done by setting four jumpers for each serial port, or by

storing the baud rate setting in the COM8116 chip under software control. These

jumper options allow the processor to dynamically control the baud rate

of

either

one or both serial ports.

3.9.3 Bus Clock and Constant Clock

The

10

MHz processor

clock

may

be

used

as

the Multibus BCLK and CCLK.

Because only one card in a Multibussystem can assert these signals,jumpers are

provided

to

remove these clocks from the bus. With these jumpers removed, the

card uses the BCLK and CCLK generated by another master in the Multibus bin.

3.9.4 The E Clock

The

68000

outputs

an

E clock that is one-tenth the processor clock frequency.

Synchronous transfers to the on-board Motorola peripherals are made using this

1MHz clock. Accordingly, it is connected to the enable input

of

the

PIA,

ACIA and

timer chips. This frequency is used by the timer chip when it is configured

to

count the E clock.

3.10

Interrupts

The 68000 provides for seven levels

of

prioritized auto-vectored interrupts. A

74148

priority encoder is included for inputting low active interrupts. The output

of

the 74148 directly connectstothe

IPLO,

IPL1,IPL2 inputsofthe processor.

Interrupts outputs from the on-board peripherals and the Multibus interrupt lines

must be connected to the priority encoder by the user. Wire wrap pins are provided for each interrupt source.

The 68000 feature

of

reading

an

interrupt vector number from the interrupting

device has not been implemented on this board.

15

Page 21

3.11

Status Indicators

Two

LED

indicator lights are included to show when the processor is in the reset

mode (YELLOW) and when the processor is halted

(RED).

312

Single-Step Mode

Circuitry is included on the OB68K1A to implement single step and halt operations. These functions are activated by

an

external momentary contact switch

(for single stepping the processor) and

an

SPST

switch to select the Single Step

or

Run

mode. A 10-pin header on the board may

be

used to connect these switches. Additional signals included on this header are a Reset input, a Non-Maskable

Interrupt input and connections to

LED

drivers for Halt and Reset indicators. This

group

of

signals may be connected to a front panelifdesired.

3.13 Restart Vector Accessing

When a power-on or manual reset

of

the procesor occurs, the processor begins

operation by accessing memory location zero in Supervisory Program space to

load the restart vector and the Supervisor stack pointer. These two vectors must

be

stored in

PROM

because thecontentsofRAM

are unknown at restart time. The

OB68K1A causes the first four memory accesses following a restart to

be

uncon-

ditionally directed to the location 0 through 7

of

the first

ROM

socket pair (IC60

and

IC61).

The access to these

PROM

locations is independent

of

the switch-

selected location

of

ROM

in the address mapofthe OB68K1A. For proper opera-

tion, after restart some memory must exist at location

$000000

in order to have

memory at the addresses where the processor expects to find exception vectors.

This may be either

RAM

or

PROM

and, can

be

in offboard memory.Inany case,

ROM

chips must

be

present in the first two

ROM

sockets, to supply the initial pro-

gram counter and stack pointer values at restart.

3.14 Front Panel Connector

The OB68K1A has a provision for connecting a front panel board that includes

RESET,

SINGLE-STEP, and RUN-STOP switches, HALT and

RESET

LEOS

and a

Software Abort button that asserts NMI, the level

7 interrupt.

An

optional front

panel box and interconnecting cable is available. See Section

9.0

for ordering

information.

16

Page 22

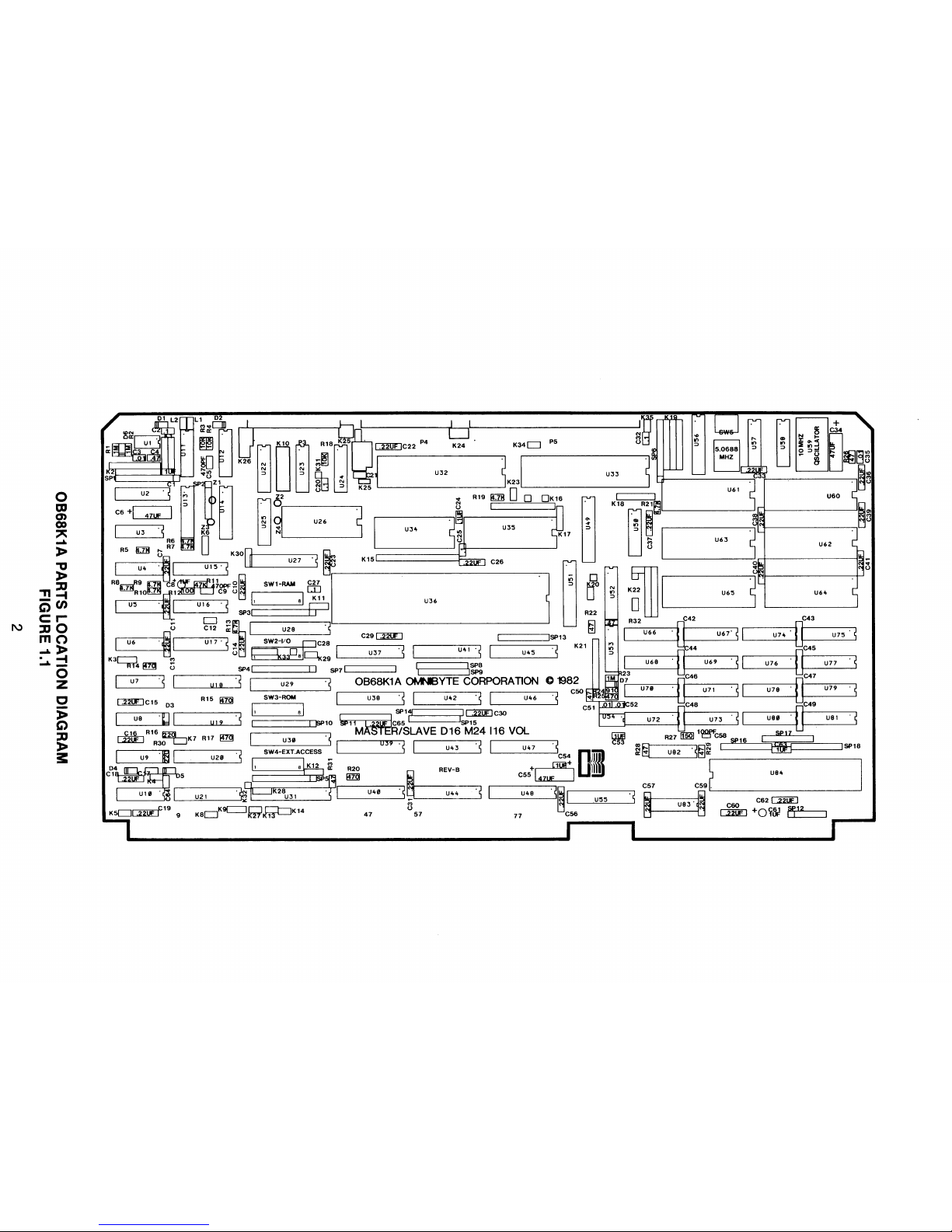

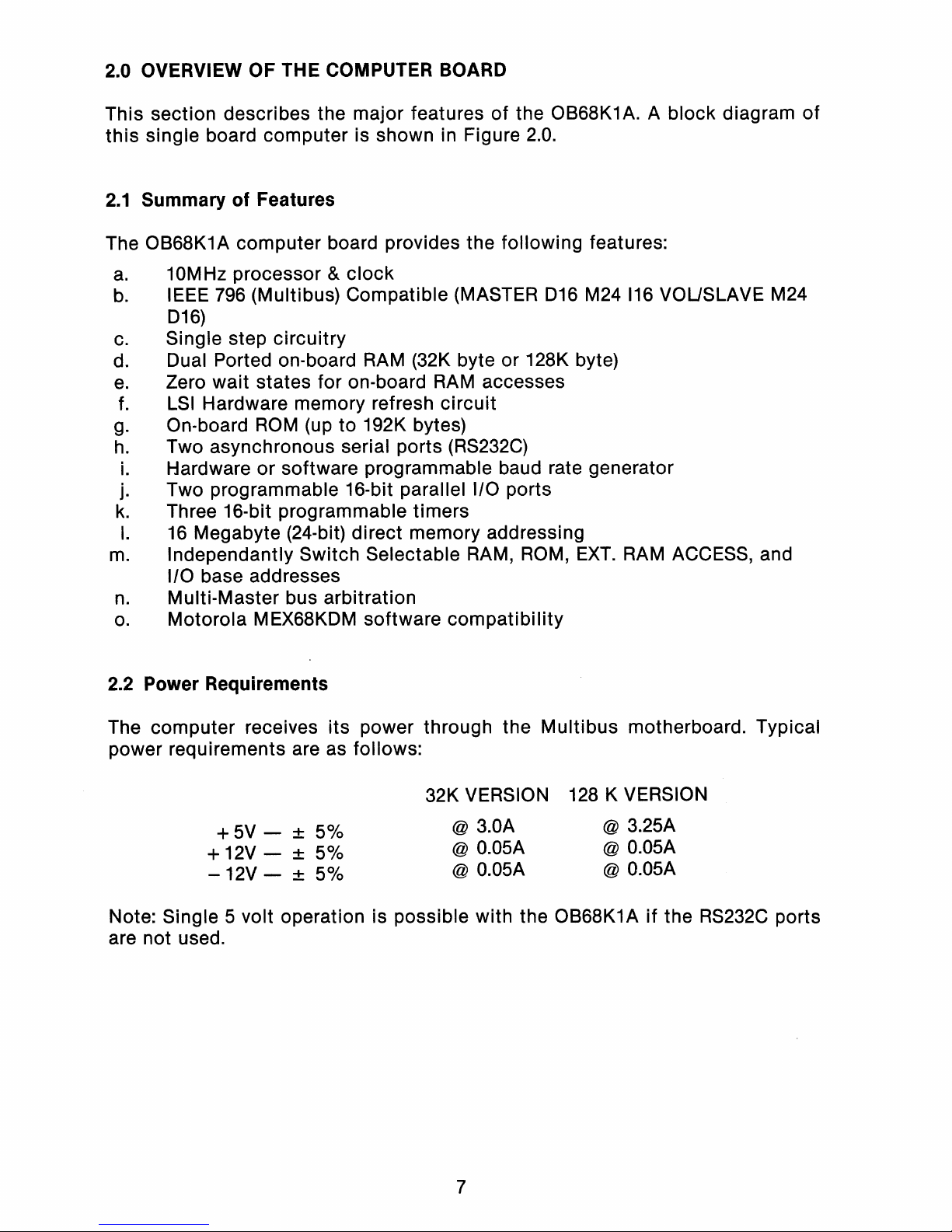

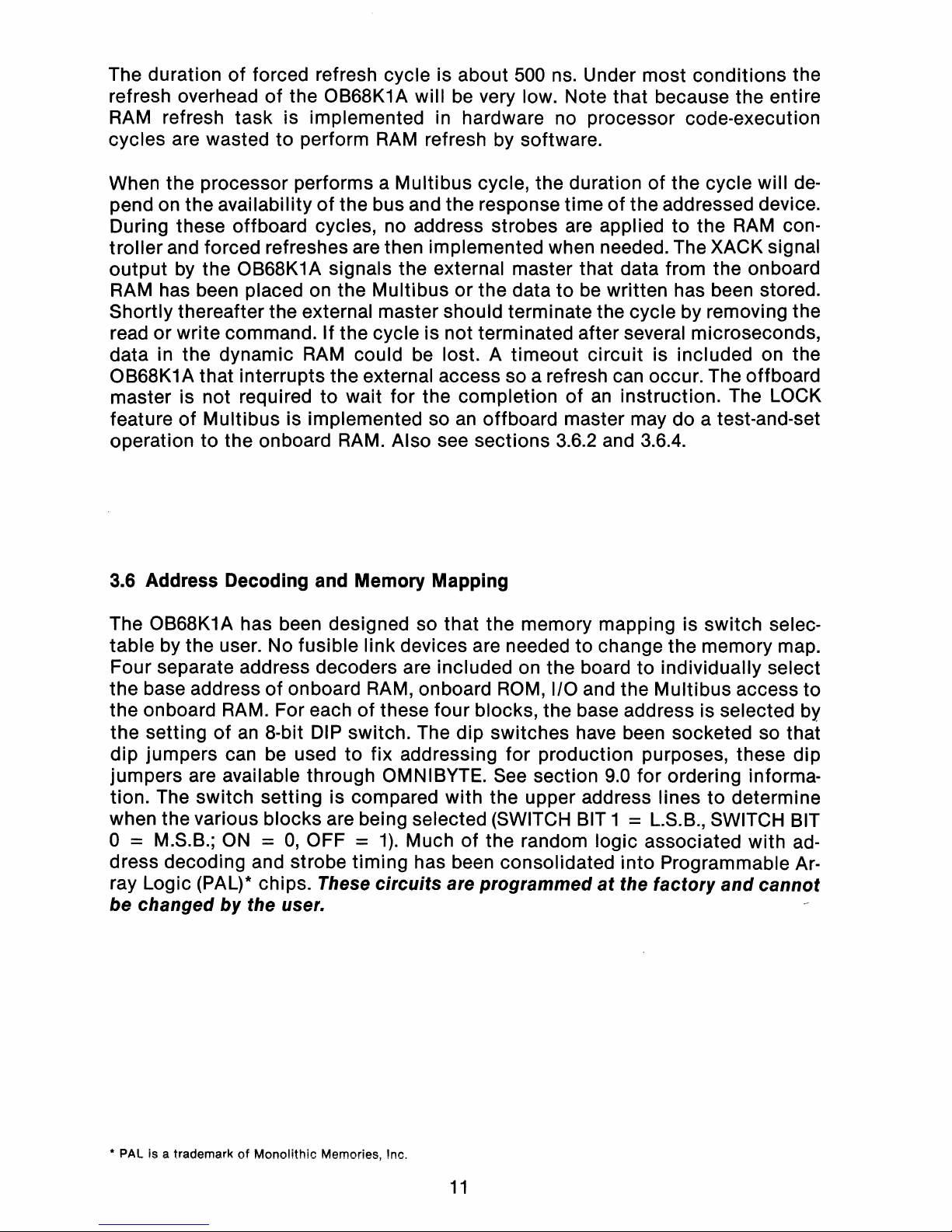

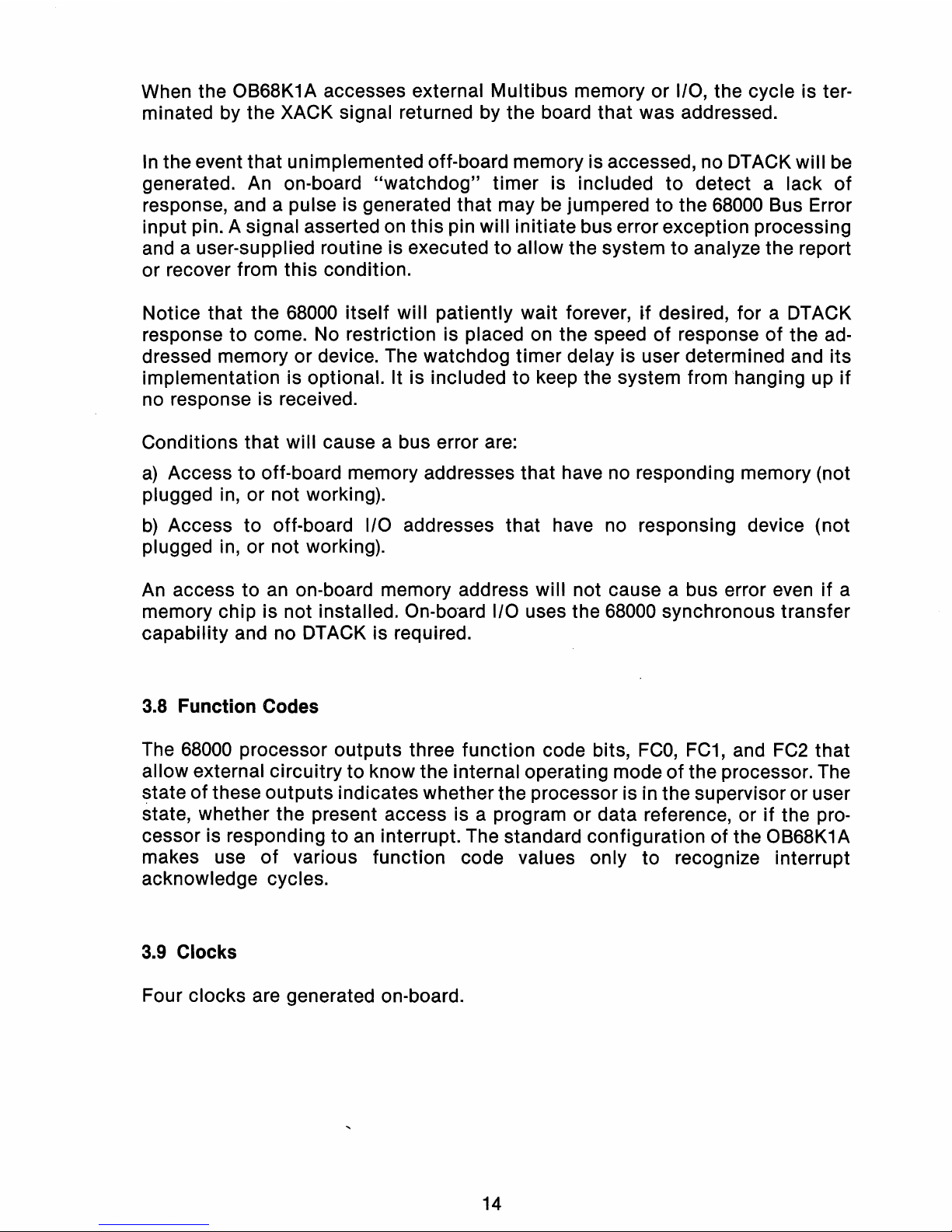

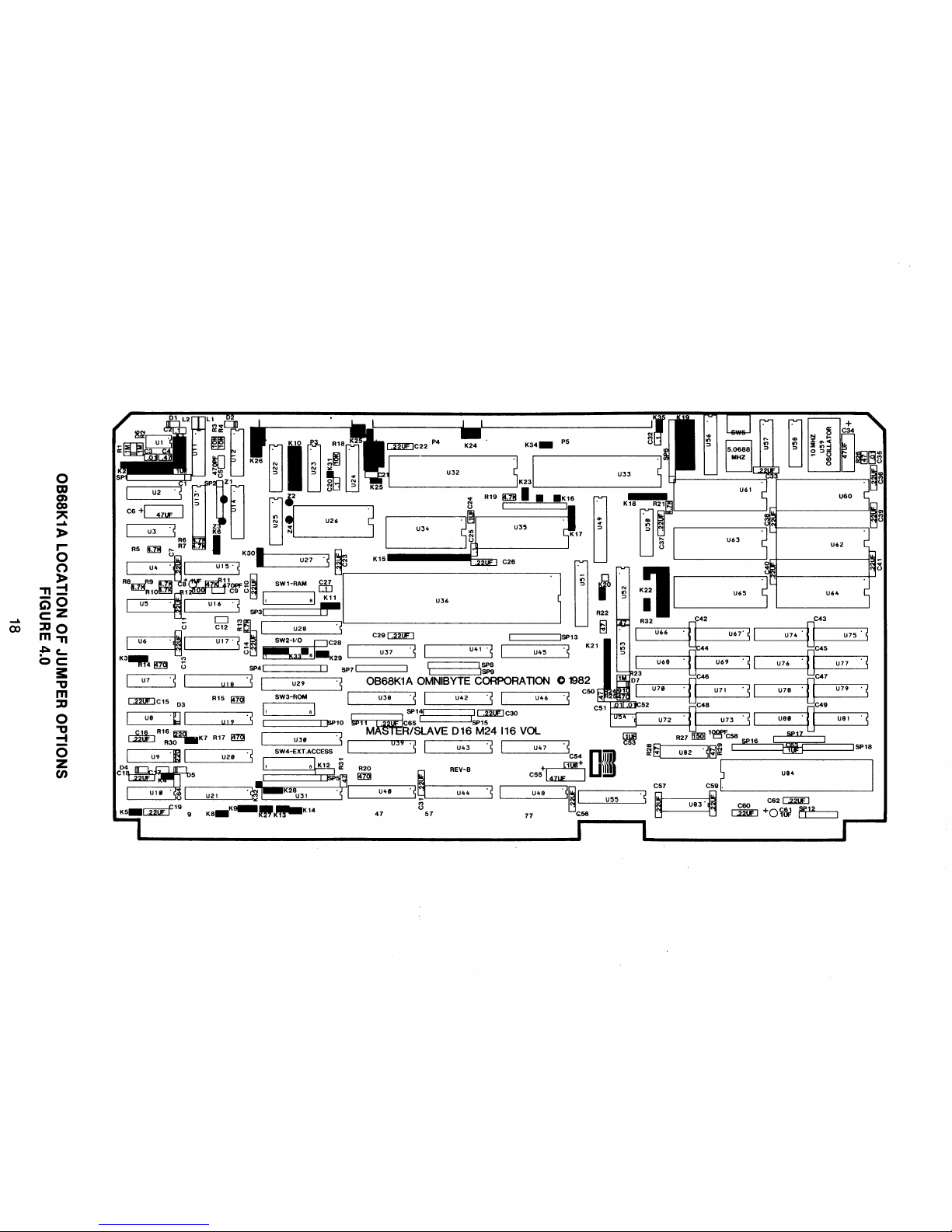

4.0 USER DEFINABLE OPTIONS

This section describes the jumpers and options included on the board. Table

4.0

is a summaryofall the user definable jumpers. The location

of

the jumpers are

shown in Figure

4.0.

JUMPER NO.

NO.

OF PINS

FUNCTION

K1

10

Front Panel Connector

K2

15

Interrupt Jumpers

K3

3

INIT Jumpers

K4

2

BClK

to

Multibus

K5

2

BPRO

to Multibus

K6

3

BERR

Enable

K7

2

BPRN

Enable

K8

2

BREQ

for parallel Arbitration

K9

3

CBRQ Enable/Disable

KlO

7

Serial Port Transparent/Independent Mode

Enable

K11

3

Onboard

RAM

Size Select

K12

3

Ext.

RAM

access,

Upper/lower

32K select

K13

2

Future

RAM

Enhancement

K14

2

CClK

to

Multibus

K15

13

ACIA IRQ, Handshake Configuration; Test points

K16

10

Timer 2 &3,ClK,

Gate, Output; Timer

IRQ,

PIA 0

IRQ's

K17

4

Timer

1;

ClK,

gate, output

K18

6

SW

Baud Rate strobe; PIA1,IRQ

K19

24

Hardware/Software Baud Rate Jumpers

K20

3

ROM

Delay (JumpertoK21)

K21

8

ROM

DTACK Delay Select 100ns/tap

K22

21

Rom

Socket Sizing

K23

2 External access watchdog timer enable

K24

4 ± 12V

TO

Port 0 (For External Circuitry)

K25

20

Port 0 ACIA Configuration

K26

10

Port 1 ACIA Configuration

K27

2

A16 64/128K

EXT.

RAM

Access

limit

K28

2

Future

RAM

Enhancement

K29

2

A16

Onboard

RAM

Size

K30

3

DTR

Normal/Invert (Port

1)

K31

1

Spare

RS232

Receiver Buffer Output

K33

4 Future

RAM

Enhancement

K34

2

5V

for PIA 0

K35

2

5V

for PIA 1

JUMPER OPTIONS

TABLE

4.0

17

Page 23

U64

C43

U74 ' 0

U75

' 5

U76

"0

045

U77 ' 5

0

041

U78

U79

.

5

0

04

•

U8.

U81

' 5

tiE

ISP18

U84

U65

U69 ' 5

L-I

_..::.........:._

U71

. 5

1-1

_

Ll

•

MVCID

.r

l

----J

+

iii

[l

,

Kl0,

R18,K

c;:nm:]C22

P4

K24

K34_

P5

!!!

...

~

~

EJ

~

~g~

LJ

(]

.,.

N

";

.'5

C

__

U_J2

~.,.Ir-----U-JJ--~·.,"'--------1

r---"'-~--~----,"

i:

O

v

R19

IU8 I -

_K16

~

U61

U60

c.

+1

.;l

u"

J

L_~.~()

I

I·...

K18

~R~[5J

~~

UJ

'~R6

1~6:l~'--

---.JJ

UJ4

~~

UJ5

K17:;

~

EJ();

I-----------:..".,~------.....,~()

R5 m ti R7 .

K301

~

1,.If----------.J

,., .

U6J

U62

~I

U""l

U27

"l

Et

.,5

C,.

~

.~m:':.s~~Jb'r'~~

5W1-RAM

ffi.1

'J

~~K~122

I

U5

' 1

U16'

~

'!1

sl

Kll

UJ6

I

••

u

~

~~5Pi

U28

"l

§

••

,

------==---

I

U6

'~.I

U17'

~:!

SW2-I/O

pC28

.--_C_2_9_',_22_UF_1 ISP13 U66

U67'

~

1-1

_

K3.

t3

M

()

•

Ii

K33-sl-K29

1

UJ7

.~

I

U41

'~

U45

'5

K21

4

rn

U SP4J I 1

SP7

1

";1

======:=:-:,

SP=8

1

U7

' 5

lUI

8 . 5 I

U29

. 5 OB68K1A OMNIBYTE CORPoRATION 0

1}82

~C15

03

R15

(tlg

SW3-ROM I

UJ8'5

1 U42

'5

1 U46

'5

U8

lJ

1

'51

I-l

__

~sl

.

SPl~

Icm£JC30

~.10

IffiL

U"

I I

""~;

ISP1M~isSL,WE

D1~5PM24

116

VOL

L22l.EJ

R3~K7

R17

Elm

I

UJ'

~

I1EIl~C58

~-u-9-'mg-IL-

u_2'_.....J'5 SW4-EXT.ACCESS 1

039

'5

1

U4J'5

I

u47'5

[]I~J

~§

.~:,

"~~rl.....lSPZ!:..!.!16L-....!::::~:!rF'=::::L_----.

~~5

L;.!l

...::..s~i

m REV-B

C55+~

111

l

~

[--U2-'--~'~'~,-1

;;;_-=;';_K;;;_28;;=u-J~,~~~~~~--,~..lrJrL..I-_-_-_-_-_U-4~'~~~--,"l~t---u-4-4---"5

1 U48

'5~L..I_--=u:.::.55=--_..J'5

C~5t-7

C59

....

1.------

_

K5_~19

9

K8_K~_-"K14

°

57

~

U8J'~

C60

C62~

Rn"~

47

77

<;;56

1J

C2MJ

+O~~

Ii"M~1

......

2_~

...

-

....

o

m

en

co

"

...A.

»

....

o

o

»

,,::::!

-0

~z

::DO

m"

~c..

oc:

s:

."

m

::D

o

."

::::!

o

z

en

Page 24

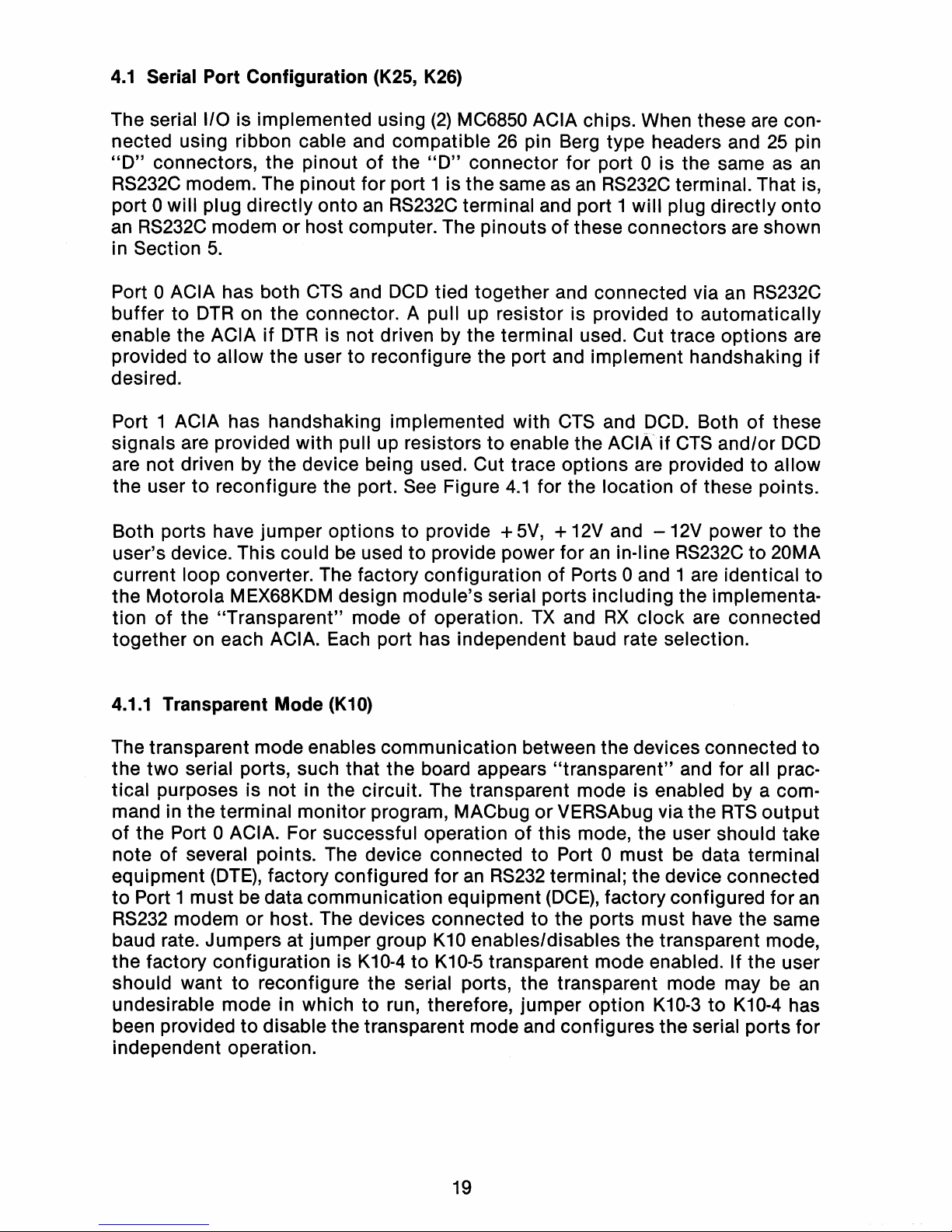

4.1

Serial Port Configuration (K25,

K26)

The serial I/O is implemented using

(2)

MC6850 ACIA chips. When these

are

con-

nected using ribbon cable and compatible

26

pin Berg type headers and

25

pin

"0"

connectors, the pinout

of

the

"D"

connector for port 0 is the same

as

an

RS232C

modem. The pinout for port 1 is the same as

an

RS232C

terminal. That is,

port 0 will plug directly onto

an

RS232C

terminal and port 1 will plug directly onto

an

RS232C

modem or host computer. The pinoutsofthese connectors are shown

in Section

5.

Port 0 ACIA has both

CTS

and

DCD

tied together and connected via

an

RS232C

buffer to

DTR

on the connector. A pull up resistor is provided to automatically

enable the ACIA

if

DTR

is not driven by the terminal used. Cut trace options are

provided

to

allow the user to reconfigure the port and implement handshaking

if

desired.

Port 1 ACIA has handshaking implemented with

CTS

and

DCD.

Both

of

these

signals are provided with pUll up resistors

to

enable the

ACIAif

CTS

and/or

DCD

are not driven by the device being used. Cut trace options are provided

to

allow

the user

to

reconfigure the port.

See

Figure

4.1

for the locationofthese points.

Both ports have jumper options to provide

+

5V,+12V

and -

12V

power to the

user's device. This could

be

used to provide power for

an

in-line

RS232C

to 20MA

current loop converter. The factory configuration

of

Ports 0 and 1 are identical to

the Motorola MEX68KDM design module's serial ports including the implementation of the "Transparent" mode

of

operation.

TX

and

RX

clock

are connected

together on each ACIA. Each port has independent baud rate selection.

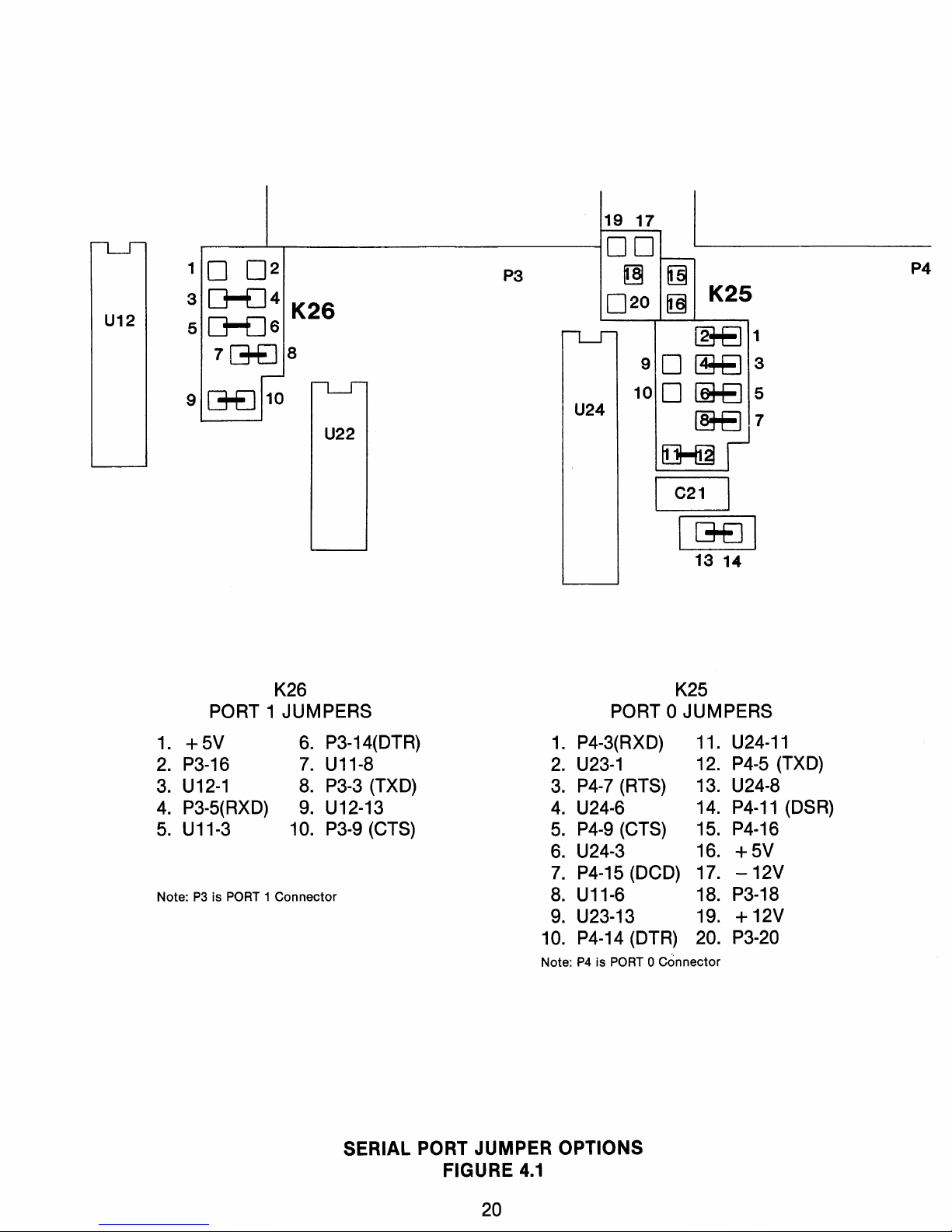

4.1.1

Transparent Mode

(K10)

The transparent mode enables communication between the devices connected

to

the two serial ports, such that the board appears "transparent" and for all practical purposes is not in the circuit. The transparent mode is enabled by a command in the terminal monitor program, MACbug or VERSAbug via the

RTS

output

of

the Port 0 ACIA. For successful operation

of

this mode, the user should take

note

of

several points. The device connected to Port 0 must

be

data terminal

equipment

(DTE),

factory configured foranRS232

terminal; the device connected

to

Port 1 mustbedata communication equipment

(DCE),

factory configured for

an

RS232

modem or host. The devices connected to the ports must have the same

baud rate. Jumpers at jumper group

K10

enables/disables the transparent mode,

the factory configuration is

K10-4toK10-5

transparent mode enabled.Ifthe user

should want to reconfigure the serial ports, the transparent mode may

be

an

undesirable mode in which to run, therefore, jumper option

K10-3

to

K10-4

has

been provided

to

disable the transparent mode and configures the serial ports for

independent operation.

19

Page 25

P4

U24

P3

U22

19

17

r-----L---,----------i

0 0

~

[§]

0

20

[§I

K25

[g3-E]

1

90~3

100

~

5

~7

~

I C21 I

I G£J I

13

14

10

0

2

3

[H]4

K26

5

[H]6

7

G-EJ

8

9

G-EJ

10

U12

K26

PORT 1 JUMPERS

1.

+ 5V

6.

P3-14(DTR)

2.

P3-16

7.

U11-8

3.U12-1

8.

P3-3 (TXD)

4.

P3-5(RXD)

9.

U12-13

5.

U11-3 10. P3-9 (CTS)

Note:P3is

PORT

1 Connector

K25

PORT 0 JUMPERS

1.

P4-3(RXD) 11.

U24-11

2.

U23-1

12. P4-5 (TXD)

3.

P4-7

(RTS) 13. U24-8

4.

U24-6 14.

P4-11

(DSR)

5.

P4-9 (CTS) 15. P4-16

6.

U24-3 16. + 5V

7.

P4-15 (DCD) 17.

-12V

8.

U11-6 18. P3-18

9.

U23-13 19. + 12V

10. P4-14 (DTR) 20. P3-20

Note:P4is

PORT

0 Connector

SERIAL PORT JUMPER OPTIONS

FIGURE

4.1

20

Page 26

U22

K10

1~2

3D

:~6

07

U23

K10

1.

U12-4

2.

P3-15(DCD)

3.

GND

4.

U22-13

5.

U27-6

6.

U24-5

7.

U27-5

OPTIONS

4-5

TRANSPARENT MODE ENABLED

3-4

TRANSPARENT MODE DISABLED

5-6

NORMAL

RTS

6-7

INVERTED

RTS

1-2

DCD

TO

PORT

1

NOTE: CHIPS U12 AND U23 ARE RS232 RECEIVERS

CHIPS

U11

AND U24 ARE RS232 DRIVERS

TRANSPARENT IINDEP. MODE JUMPER LOCATION

FIGURE

4.1.1

4.1.2 Baud Rate Selection (K18,

K19)

Jumper group

K19

selects the serial baud rate for both Port 0 and Port1.K19

is a

group

of

24

pins arranged in three columns as shown in Figure 4.1.2. The center

row

of

pins connect

to

the baud-rate-setting pins

of

the COM8116 baud rate

generator. The baud rate may

be

set manually or by software.

4.1.2.1

Manual Baud Rate Setting

The center row of pins in jumper group

K19

are pulled up so thatifa particular pin

is not jumpered to ground,

it

will be pulled to a logic1.To select a logiczero, a pin

must

be

jumperedtoground

by

connecting

to

the corresponding pin in the right

hand column. The baud rates corresponding to the possible values

of

the 0,C,B,

and A signals are given in table 4.1.2.1.

21

Page 27

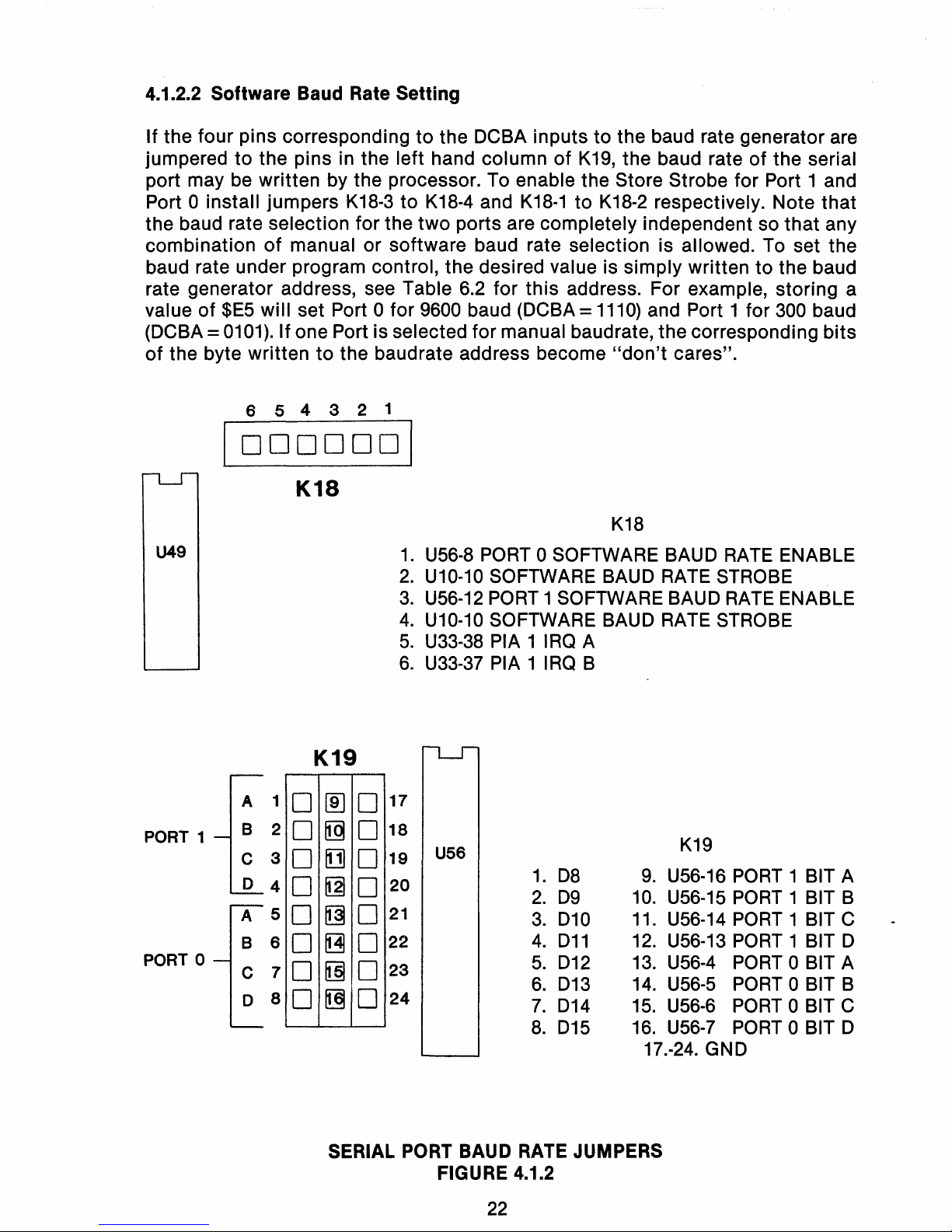

4.1.2.2

Software

Baud Rate

Setting

If the

four

pins

correspondingtothe

DCBA

inputstothe

baud rate generator are

jumpered

to

the

pins

in the

left

hand

column

of

K19,

the

baud rateofthe serial

port may be

written

by

the processor. To enable the Store Strobe

for

Port 1 and

Port 0

install

jumpers

K18-3

to

K18-4 and

K18-1

to

K18-2 respectively. Note

that

the baud rate

selection

for

the

two

ports

are

completely

independent so

that

any

combination

of

manual

or

software

baud rate selection is allowed. To set

the

baud rate under program control,

the

desired value is

simply

writtentothe baud

rate generator address, see Table 6.2

for

this

address. For example,

storing

a

value

of

$E5

will

set Port 0

for

9600 baud (DCBA = 1110) and Port 1

for

300 baud

(DCBA

=0101). If one Port is selected

for

manual baudrate,

the

corresponding

bits

of

the byte

written

to

the baudrate address become

"don't

cares".

6 5 4 3 2 1

10

0

0

000

I

K18

U49

K19

K18

1.

U56-8 PORT 0 SOFTWARE BAUD RATE ENABLE

2.

U10-10 SOFTWARE BAUD RATE STROBE

3.

U56-12 PORT 1 SOFTWARE BAUD RATE ENABLE

4.

U10-10 SOFTWARE BAUD RATE STROBE

5.

U33-38 PIA 1 IRQ A

6.

U33-37 PIA 1 IRQ B

A

1

PORT 1

B

2

C

3

0

4

A

5

B

6

PORT 0

C

7

0

8

0

[[J

0

0

[g

0

0

~

0

0

[g]

0

0

~

0

0

~

0

0

[§]

0

0

~

0

17

18

19

U56

20

21

22

23

24

1.

D8

2.

D9

3.

D10

4.

D11

5.

D12

6.

D13

7.

D14

8.

D15

K19

9.

U56-16 PORT 1 BIT A

10. U56-15 PORT 1 BIT B

11. U56-14 PORT 1 BIT C

12. U56-13 PORT 1 BIT D

13. U56-4 PORT 0 BIT A

14. U56-5 PORT 0 BIT B

15. U56-6 PORT 0 BIT C

16. U56-7 PORT 0 BIT D

17.-24. GND

SERIAL PORT BAUD RATE JUMPERS

FIGURE 4.1.2

22

Page 28

U56

K19

1 0 9

17

2 0

[g

0

18

3 0

~

0

19

4 0 [gl 0

20

A 5 0 21

B 6

0

~

0

22

C 7 0

~

0

23

o 8 0

~

0

24

PORT 1

PORT 0

EXAMPLE ABOVE ILLUSTRATES HARDWARE

BAUD RATE OF 9600 FOR BOTH PORTS

(FACTORY STANDARD).

INSTALLED JUMPERS

= 0

REMOVED JUMPERS

= 1

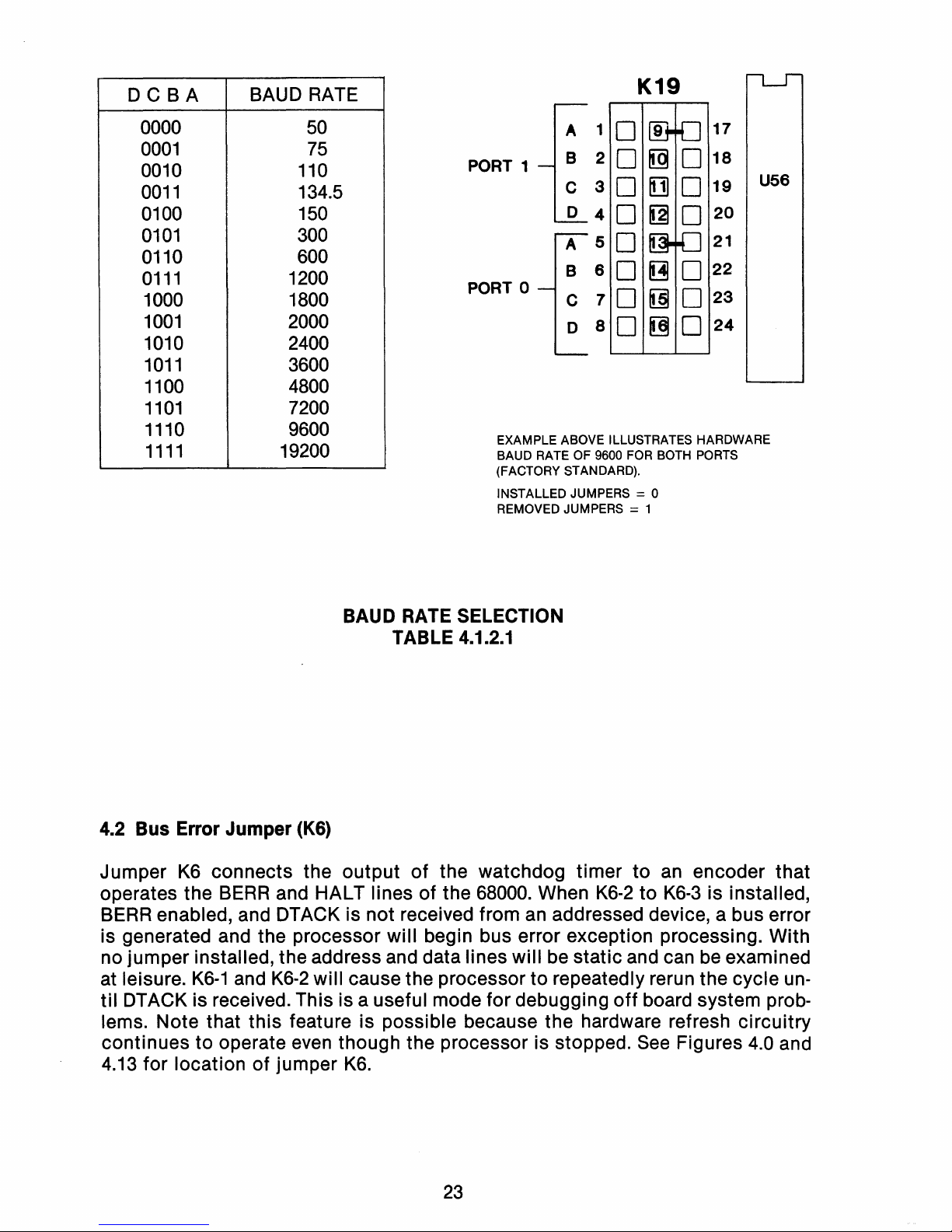

DCBA

BAUD RATE

0000 50

0001

75

0010 110

0011

134.5

0100

150

0101

300

0110

600

0111

1200

1000 1800

1001

2000

1010 2400

1011

3600

1100

4800

1101

7200

1110 9600

1111

19200

BAUD RATE SELECTION

TABLE 4.1.2.1

4.2

Bus

Error

Jumper

(K6)

Jumper

K6

connects

the

output

of

the

watchdog

timer

to

an

encoder

that

operates the BERR and HALT linesofthe 68000. When

K6-2

to

K6-3isinstalled,

BERR enabled, and DTACK

is

not

received from an addressed device, a bus error

is generated and the processor

will

begin bus error exception processing.

With

no

jumper

installed, theaddress and data lines

will

be

static

and can be examined

at leisure.

K6-1

and

K6-2

will

cause the processortorepeatedly rerun the cycle un-

til

DTACK is received. Thisisa useful mode

for

debugging

off

board system prob-

lems.

Note

that

this

featureispossible because the hardware refresh

circuitry

continues

to

operate even

though

the processor is stopped. See Figures 4.0 and

4.13

for

locationofjumper

K6.

23

Page 29

4.3

DTACK Select (K20,K21)

The DTACK generator

for

the

ROM

consistsofa74164

shift

register that is held in

its

cleared state until either LDS or

UDS

is asserted. Logic ones are clocked

through the

shift

register by the 10MHz (processor) oscillator, and DTACK

timing

is selected by choosing the stageofthe

shift

register connectedtothe DTACK in-

put pin. DTACK is factory

set

for

350ns ROM chips.

If

faster ROM

is

used, the

DTACK

jumper

can be moved

to

provide a

shorter

DTACK delay. Each

jumper

represents

an

incrementof100ns.,

K21-1

being the shortest and

K21-5

being the

longest DTACK delay. (See Figure

4.3)

Notice that the DTACK

timer

is active only

for

on-board

ROM

access. For off-board accesses DTACK is derived from the

Multibus

XACK signal. For on-board

RAM

accesses DTACK is derived from the

RAM

controller

circuitry. Normal onboard

RAM

access will incur no wait states.

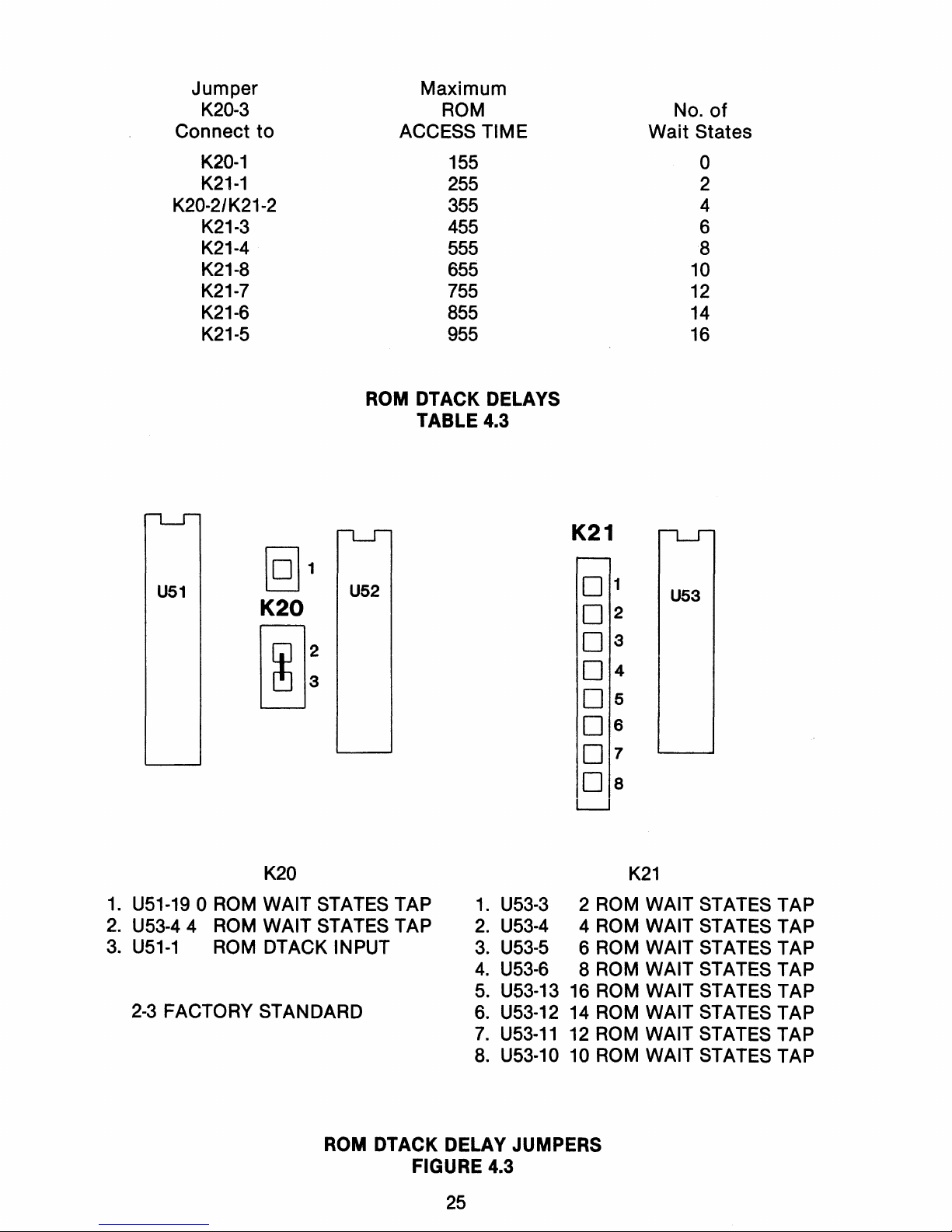

See Table 4.3 below. Jumper K20-3 is the

ROM

delay input pin. This pin may be

connectedtovarious delayed

outputsofthe DTACK generator via the

K21

jumper

group. For convenience,

K21-2

is routedtoK20-2

to

become the factory standard

ROM

DTACK delay. A jumperconnecting

K20-2

and

K20-3

provides a

ROM

DTACK

to operate

with

350ns ROMS. For

other

ROM

speeds

K20-3

may be connected

to

other DTACK generator

outputsatK21

accordingtothe delay time given in Table

4.3.If150ns

or

faster ROMS are used, no wait states are required. For zero wait

state operation

for

ROM

memory accesses, connect

K20-3

to

K20-1.

?A

Page 30

Jumper

Maximum

K20-3

ROM

No.

of

Connect

to

ACCESS TIME

Wait

States

K20-1

155

0

K21-1

255 2

K20-2/K21-2

355

4

K21-3 455

6

K21-4

555

8

K21-8

655

10

K21-7

755

12

K21-6

855

14

K21-5

955

16

ROM DTACK DELAYS

TABLE

4.3

K21

U51

[g]1

U52

0

1

U53

K20

0

2

00:

0

3

0

4

0

5

0

6

0

7

0

8

L-----'

K20

1.

U51-190

ROM

WAIT STATES TAP

2.

U53-44

ROM

WAIT STATES TAP

3.

U51-1

ROM

DTACK INPUT

2-3

FACTORY STANDARD

K21

1.

U53-3

2

ROM

WAIT STATES TAP

2.

U53-4

4 ROM WAIT STATES TAP

3.

U53-5 6 ROM WAIT STATES TAP

4.

U53-6 8

ROM

WAIT STATES TAP

5.

U53-13

16

ROM

WAIT STATES TAP

6.

U53-12

14

ROM

WAIT STATES TAP

7.

U53·11

12

ROM

WAIT STATES TAP

8.

U53-10 10 ROM WAIT STATES TAP

ROM DTACK DELAY JUMPERS

FIGURE 4.3

25

Page 31

4.4 Interrupt Priority (K2)

Interrupts foron-board peripheral chips are terminated on wire wrap posts so that

the user may select the interrupts

to

be

used and the priority level

of

each inter-

rupt. The following interrupts from the onboard peripheral chips are available:

INTERRUPT SOURCE

Port 0 ACIA

Port 1 ACIA

Timer IRQ

PIA 0 IRQ A

PIA 0 IRQ B

PIA 1

IRQ

A

PIA 1 IRQ B

JUMPER

PIN

NO.

K15-11

K15-12

K16-8

K16-9

K16-10

K18-5

K18-6

Because Motorola

IRQ

lines are open drain connections, the interrupt requests

from several chips may

be

wire

ORedtooccupy a single priority level.

The Multibus interrupt lines

(8)

are brought

to

on-board wire wrap posts. These

may also be wire

ORed

and connected

to

the priority encoder inputs'. Both the

Multibus interrupts and the inputs to the priority encoder are located in jumper

group

K2.

See Figure

4.4.

Priority encoder input seven is the highest priority; one is the lowest. Interrupt

requests are not latched on-board. These interrupt requests must be held active until

serviced when they are reset by the processorduring executionofthe interrupt

service routine

as

indicated

by

the IEEE-796 specification.

U1

K2

87654321

00000000

0000000

15

14

13 12

11

10 9

U2

£

K2

P1

CONNECTOR

PROCESSOR

(BACKPLANE) (INT PRIORITY CHIP)

1.

P1-37

INT

4~,

,.,--9.

U2-1

LEVEL 4 IN

PUT

2.

P1-38

INT 5 i

;1{).

U2-2

LEVEL 5 INPUT

3.

P1-35

INT 6

~):~1.U2-3

LEVEL 6 INPUT

4.

P1-36

INT 7;{12.

U2-4

LEVEL 7 INPUT

5.

P1-40

INT 3

1

• (NMI)

6.

P1-39

INT i

1'3.

U2-13

LEVEL 3 INPUT

7.

P1-42

INT

l'

14.

U2-12

LEVEL 2 INPUT

8.·

P1-41

INT 0

15.

U2-11

LEVEL 1 INPUT

INTERRUPT JUMPERS

FIGURE 4.4

26

Page 32

4.5 CCLK and BCLK (K14,

K4)

Jumpers

K14

and

K4

connect the on-board

10

MHz oscillator to the Multibus

CCLK and BCLK lines, respectively. For a single processor system these jumpers

should

be

left in place. For multi-processor systems, only one master should

drive the Multibus

clock

lines. Removing these jumpers will remove the CCLK and

BCLK signals from the bus.

See

Figures

4.0

and

4.13

for

locationofK14

and

K4.

4.6 Bus Arbitration (K5,

K7,

K8,

Kg)

Four jumpers are associated with the bus priority logic.

K5

connects the output

of

the bus arbitration logictothe Multibus

BPRO:k

signal. The trace at

K7

connects

the BPRN* line

to

ground.Ina system with a single bus master,

K7

should be in

place.

In

a Multibus system using serial priority, BPRN* is driven

by

the BPRO*

signal from the master with the next highest priority. For serial operation,

K5

should

be

installed and

K7

should

be

installed for single master or highest priori-

ty

board in a multimaster configuration.

Common Bus Request

(CBRQ)

is a signal that alerts a Multibus Master that

another Master needs

to

use the bus. As shown in Figure

4.6,ifK9

is jumpered

to

connect

K9-1toK9-2,

CBRQ will

be

implemented by the bus arbitration circuitry.

In

this

mode, the OB68K1A will retain ownershipofthe bus until it is forcedtoar-

bitrate with a higher priority user or until a lower priority user asserts CBRQ.

If

another Multibus is not capableofasserting CBRQ the OB68K1A, will relinquish

the bus upon the negation

of

BPRN

and completionofthe present bus cycle. This

allows the OB68K1A to maintain increased

off

board throughput using its CBRQ

feature.

If

K9-2

and

K9-3

are connected, the OB68K1A will relinquish the bus

be-

tween each cycle.

When parallel arbitration is used the

OB68K1

A requests the use of the bus by

asserting

BREQ.

For this modeofarbitration,

K8

should

be

installed.

K8

should

be removed for serial arbitration.

* indicates low active

27

Page 33

U21

2 1

K8~

U10 S I U19 S

2 1 2 1

I

G-£J

I I C19 I I

G-£J

IK7

K5

U20 S

K5 K8

1.

P1-16 (BPRO)

2.

U3-8

JUMPER IN: SERIAL MULTIMASTER

PRIORITIZATION

JUMPER OUT:

PARALLEL MULTIMASTER

PRIORITIZATION

K7

1.

GND

2.

P1-15 (BPRN)

JUMPER IN: SINGLE MASTER

OR

HIGHEST PRIORITY

BOARD IN MULTIMASTER

SYSTEM WITH SERIAL

ARBITRATION

JUMPER OUT:

ALL

OTHER

CONFIGURATIONS

1.

P1-1

(BREQ)

2.

U21-15

JUMPER IN: PARALLEL ARBITRATION

JUMPER OUT: SERIAL ARBITRATION

Kg

1.

P1-29 (CBRQ)

2.

U21-3

3. GND

1-2:

BOARD

MAINTAINS

BUS

CONTROL UNTIL ANOTHER

MASTER REQUEST BUS

2-3:

BOARD RELEASES BUS CONTROL

AFTER EACH TRANSFER

BUS ARBITRATION JUMPER CONFIGURATION

FIGURE

4.6

28

Page 34

4.7 Initialize (K3)

The

master

in a single master system should drive

the

Multibus

INIT line. For

this

type

of

operation

K3-1

should

be

connected

to

K3-2

(See Figure

4.7).

Both the

power-on reset and software generated resets

will

drive the

Multibus

INIT line

(Factory Standard).

For a Multi-Master system,

it

may

be

desirable for INIT

to

be an

input

to

the

OB68K1A board. This is done by connecting

K3-2toK3-3

so

that

the

INIT signal

wi

II

trigger

the

onboard reset generator.

For some

applicationsitmay be necessary for

the

OB68K1Atobe reset

directly

by

the

INIT signal in order

to

synchronize

the

restart sequence

of

multiple

pro-

cessors. To use INIT directly,

cut

the

two

traces Z1-Z3 and Z2-Z4. Connect Pin

K3-2

to

both Z3 and

Z4.

(See Figure

4.13).

This

modification

disables

the

onboard

reset generator and the RESET push button

will

not be operative. The Master driv-

ing INIT

must

meet

the

power-on

timing

requirements

of

the 68000 processor in

order

to

insure a valid restart sequence.

_1J6_S

3 2 1

K31

OG-El I

I

U7

K3

1:

U4-8

RESET OUTPUT

2.

P1-14

INIT

3.

U1-2

RESET GENERATOR INPUT

1-2:

PROCESSOR AND ONBOARD

INIT CIRCUITRY DRIVE

MULTIBUS INIT.

2-3:

MULTIBUS INIT TRIGGERS

ONBOARD INIT CIRCUITRY.

RESET JUMPER CONFIGURATION

FIGURE 4.7

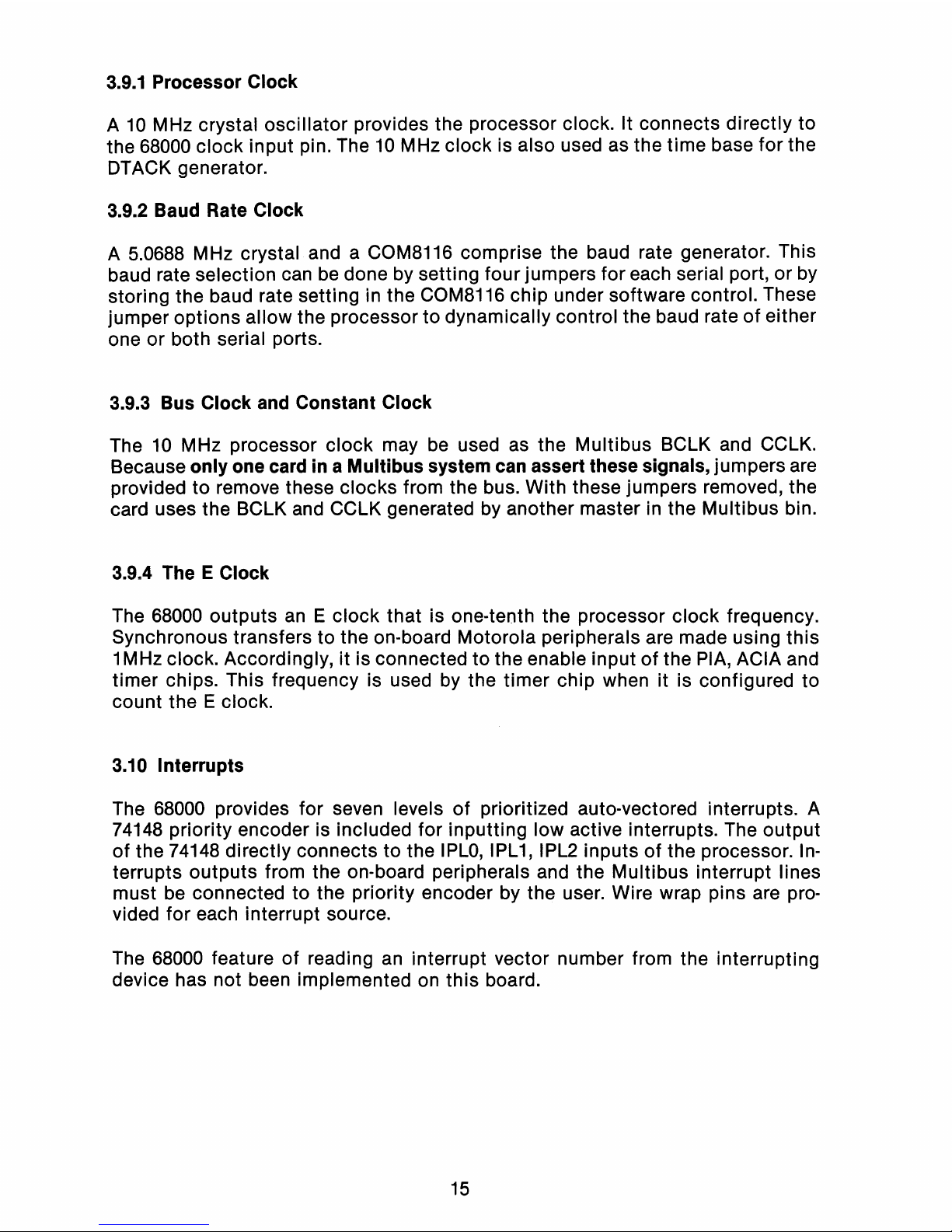

4.8 ROM Socket

Configuration

(K22)

Jumper

area

K22

configures the

ROM

sockets for the

ROM

size

that

is chosen.

Rather than wire wrapping

this

group

of

pins, a small

configurator

board is

plugged in

to

make all the connections simultaneously. The OB68K1A is shipped

withaconfigurator

for

8K(2764's) byte PROMs, but

other

configuration boards are

available from the factory.

29

Page 35

4.8.1

ROM Size

Jumper

Configuration

Figure

4.8.1

shows

the

jumper

group K22 and

identifies

eachofthe pins. The user

may choose

to

wire wrap K22tofield

modify

the

sizeortypeofROM used on

the

OB68K1A.

Normally

the

user

will

use the

factory

supplied

configuration

plugtointerconnect

the K22

jumper

pins. If a

different

PROM type

is

to

be used, the user may

reconnect K22 as shown in Figure 4.8.2. This figure

shows

the

printed

circuit

artwork

for

the

factory

supplied plugs. The user may

choosetofabricate

plugs

or

purchase

them

from Omnibyte. The ROM

sockets

used on

the

OB68K1A have 28

pins.

Thisisto

provide

for

operation

with

certain typesof32K and 64K

ROM

chips.

For operating

with

the24pin devices, ROM's MUST be

installed

with

the unused

pinsonthe

right

sideofthe socket (left justified). See Figure 4.8.3

for

ROM

socket

configuration

and Figure 4.8.4

for

compatible

chip

pinout

configuration.

See sec-

tion

9.0

for

ordering information.

U65

1

2

3

4

5

6

7

8

18 17

DO

[[]

0

~

[g

0

~

0

22

~

0

~

~.

0

~

0

OC§]

0

~

0

K

20

21

19

U52

K22

1.

A 18

2.

A 17

3.

A 16

4.

A 15

5.

A 14

6.

A 13

7.

A 12

8.

A

11

9.

GND

10.

ROM PIN

22

11.

ROM PIN

27

12.

+5V

13. U52-2

14.

U52-1

15.

ROM PIN 2 -A

IL

16. ROM PIN

21

17.

ROM

PIN 26 -

fli]

18.

ROM

PIN

23

19. GND

20.

U30-3

r-

.4

I b

5";<;,)

-)

21.

U30·13 -

.0:;

i 7

NOTE: SEE FIGURE 4.8.2 FOR FACTORY CONFIGURATION

ROM SIZE JUMPER CONFIGURATION

AND

LOCATION

FIGURE

4.8.1

30

Page 36

OBK1A/K22-2716

OBK1A/K22-27128

OBK1A/K22-2732

K22

...

oBK1

AI

K22-27256

K22

0-0

OBK1A/K22-2764

(FACTORY STANDARD)

..

%%%

000-0

0-0

0-0

0-0

000-0

000-0

K22

88

OBK1A/K22-UD

(USER DEFINABLE)

ROM CONFIGURATION PLUGS LAYOUTS

FIGURE

4.8.2

31

Page 37

ODD

BYTE

EVEN

BYTE

IC61

pno

IC60

LOWEST

ADDRESS

IC63

pn1

IC62

IC65

PR2

IC64

HIGHEST

1ADDRESS

ROM SOCKET CONFIGURATION

FIGURE

4.8.3

27256

27128

2764

2732

2716

Vee

Vee

Vee

Al4

PGi

PGi

Al3

Al!

N/C

Vee

Vee

PB

PB

PB

PB

PB

A9

A9

A9

A9

A9

All

All

All

All

Vpp

OE OE OE

OE/Vpp

OE

.-

AlO

AlO

AlO

AlO AlO

CE CE

CE

CE

CE

07

07

07

07 07

(X)

(X)

(X)

(X)

(X)

05

05

05 05

05

ex. ex.

ex.

ex.

04

03

03

03

03

03

PIN

28

27

26

25

24

23

22

21

20

19

18

17

16

15

PIN

27256

27128

2764

2732 2716

Vpp

Vpp

Vpp

Al2

Al2

Al2

AJ AJ

AJ AJ

AJ

NJ NJ

NJ NJ

NJ

AS

AS

AS

AS

AS

M M

M

M

M

A3

A3

A3 A3

A3

lQ

Xl.

lQ

Xl. Xl.

Al Al

Al

Al

Al

NJ

NJ

NJ NJ NJ

00 00

00

00

00

01

01

01

01

01

02

02

02

02

02

God

Gnd

Gnd

Qui