OKI MSM7716GS-K, MSM7716TS-K Datasheet

E2U0043-28-82

¡ Semiconductor MSM7716

¡ Semiconductor

This version: Aug. 1998

Previous version: Nov. 1996

MSM7716

Single Rail Linear CODEC

GENERAL DESCRIPTION

The MSM7716 is a single-channel CODEC CMOS IC for voice signals that contains filters for

linear A/D and D/A conversion.

Designed especially for a single-power supply and low-power applications, the device is

optimized for applications for the analog interfaces of audio signal processing DSPs and digital

wireless systems.

The analog output signal can directly drive a ceramic type handset receiver. In addition, levels

for analog outputs can be set by external control.

FEATURES

• Single power supply : +2.7 V to +3.6 V

• Low power consumption

Operating mode : 24 mW Typ.

Power down mode : 0.05 mW Typ.

• Digital signal input/output interface : 14-bit serial code in 2's complement format

• Sampling frequency(fs) : 4 to 16 kHz

• Transmission clock frequency : fs ¥ 14 min., 2048 kHz max.

• Filter characteristics : when fs = 8 kHz, complies with ITU-T Recommen-

dation G. 714

• Built-in PLL eliminates a master clock

• Two input circuits in transmit section

• Two output circuits in receive section

• Transmit gain adjustable using an external resistor

• Receive gain adjustable by external control 8 steps, 4 dB/step

• Transmit mic-amp is eliminated by the gain setting of a maximum of 36 dB.

• Analog outputs can drive a load of a minimum of 1 kW ; an amplitude of a maximum of 4.0 V

with push-pull driving.

• Built-in reference voltage supply

• Package options:

32-pin plastic TSOP (TSOPI32-P-814-0.50-1K) (Product name : MSM7716TS-K)

30-pin plastic SSOP (SSOP30-P-56-0.65-K) (Product name : MSM7716GS-K)

PP

1/22

¡ Semiconductor MSM7716

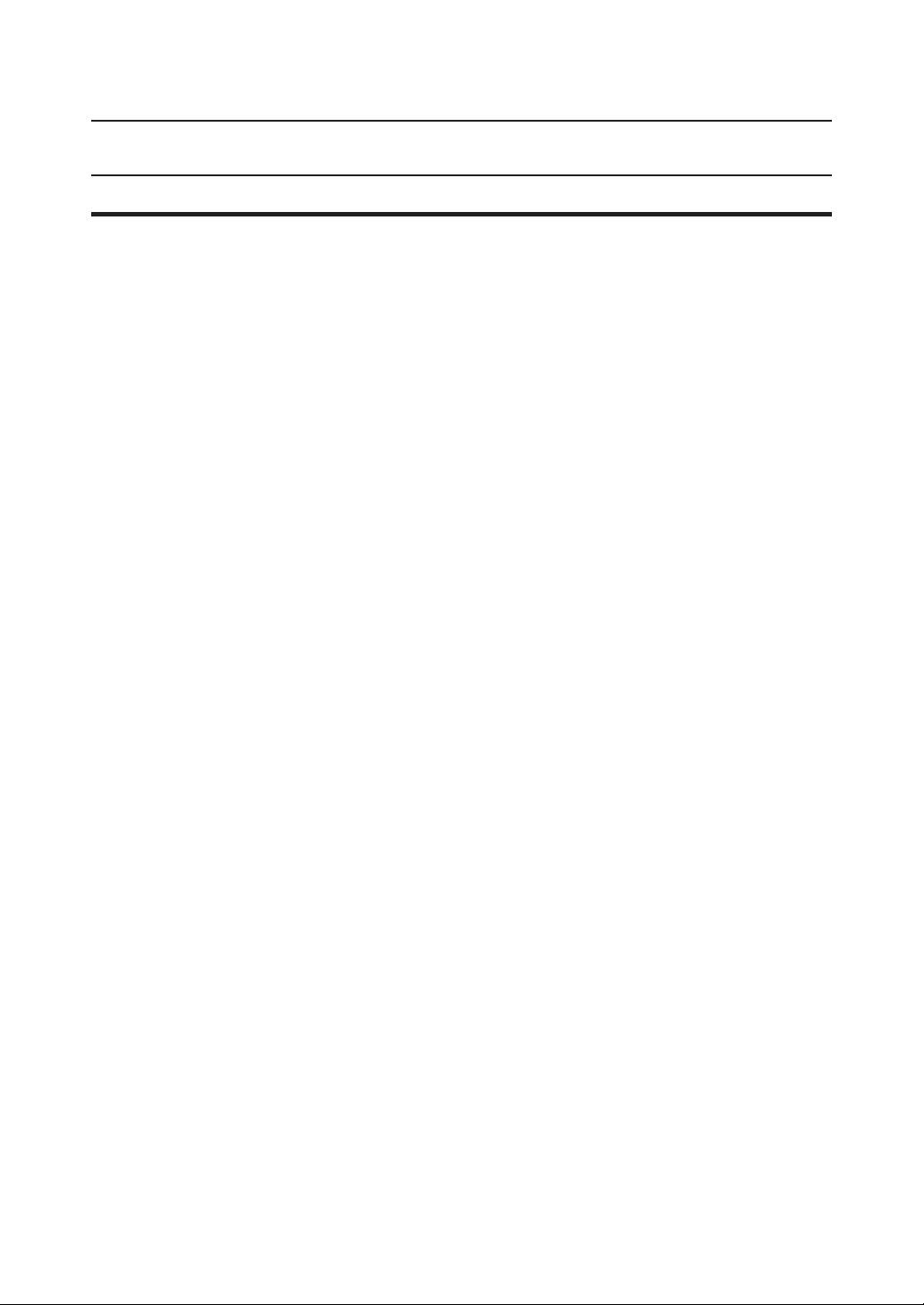

BLOCK DIAGRAM

MAO

MAIN

PBO

PBIN

–

+

–

+

SW 1

SW 2

RC

LPF

8th

BPF

14 BIT

ADCONV

AUTO

ZERO

TCONT

PLL

PCMOUT

SYNC

SW 4

–

+

–

+

SG

GEN

SW 4

SGC SG

VFO

AUXO

PWI

AOUT–

AOUT+

SW 3

VOL

–

+

SW 3

VR

GEN

RC

LPF

5th

LPF

14 BIT

DACONV

PWD

SW

CONT

VOL

CONT

RTIM

RCONT

PWD logic

CONT

Logic

BCLK

PCMIN

PDN

DEN

CDIN

DCLK

V

DD

AG

DG

2/22

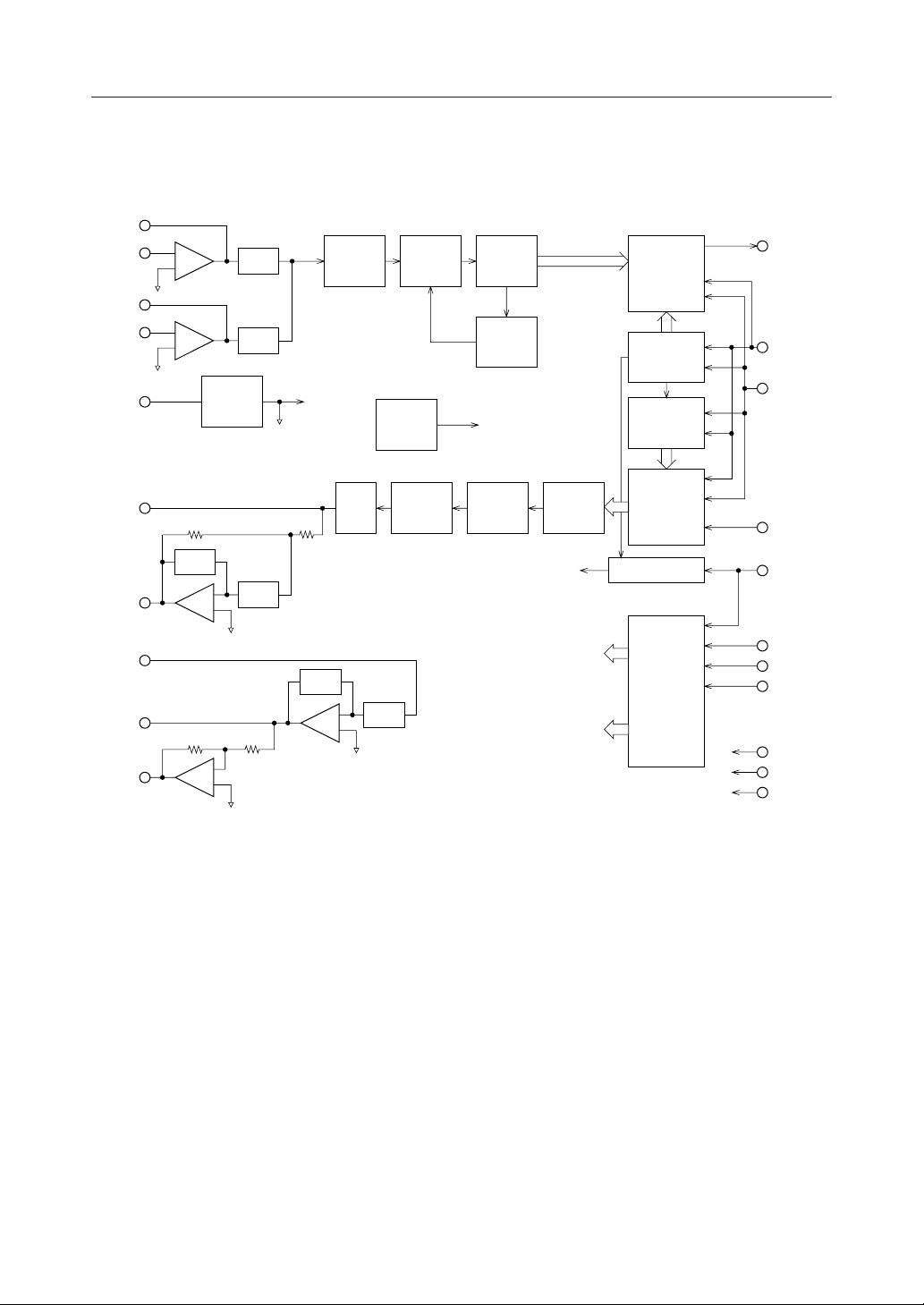

¡ Semiconductor MSM7716

PIN CONFIGURATION (TOP VIEW)

1

MAIN

2

MAO

3

NC

4

NC

5

PBO

6

PBIN

7

NC

8

SGC

9

AG

10

AUXO

AOUT+

AOUT–

AOUT+

AOUT–

11

12

13

NC

14

NC

15

PWI

16 17

VFO V

NC : No connect pin

32-Pin Plastic TSOP

1

AG

2

AUXO

3

4

5

PWI

6

VFO

7

NC

8

NC

9

NC

10

V

DD

11

DCLK

12

NC

13

CDIN

14

DEN

15 16

DG PCMIN

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

30

29

28

27

26

25

24

23

22

21

20

19

18

17

PDN

SYNC

NC

NC

NC

BCLK

PCMOUT

PCMIN

DG

DEN

CDIN

NC

NC

NC

DCLK

DD

SGC

PBIN

PBO

NC

NC

MAO

MAIN

NC

NC

PDN

SYNC

NC

BCLK

PCMOUT

NC : No connect pin

30-Pin Plastic SSOP

3/22

¡ Semiconductor MSM7716

PIN AND FUNCTIONAL DESCRIPTIONS

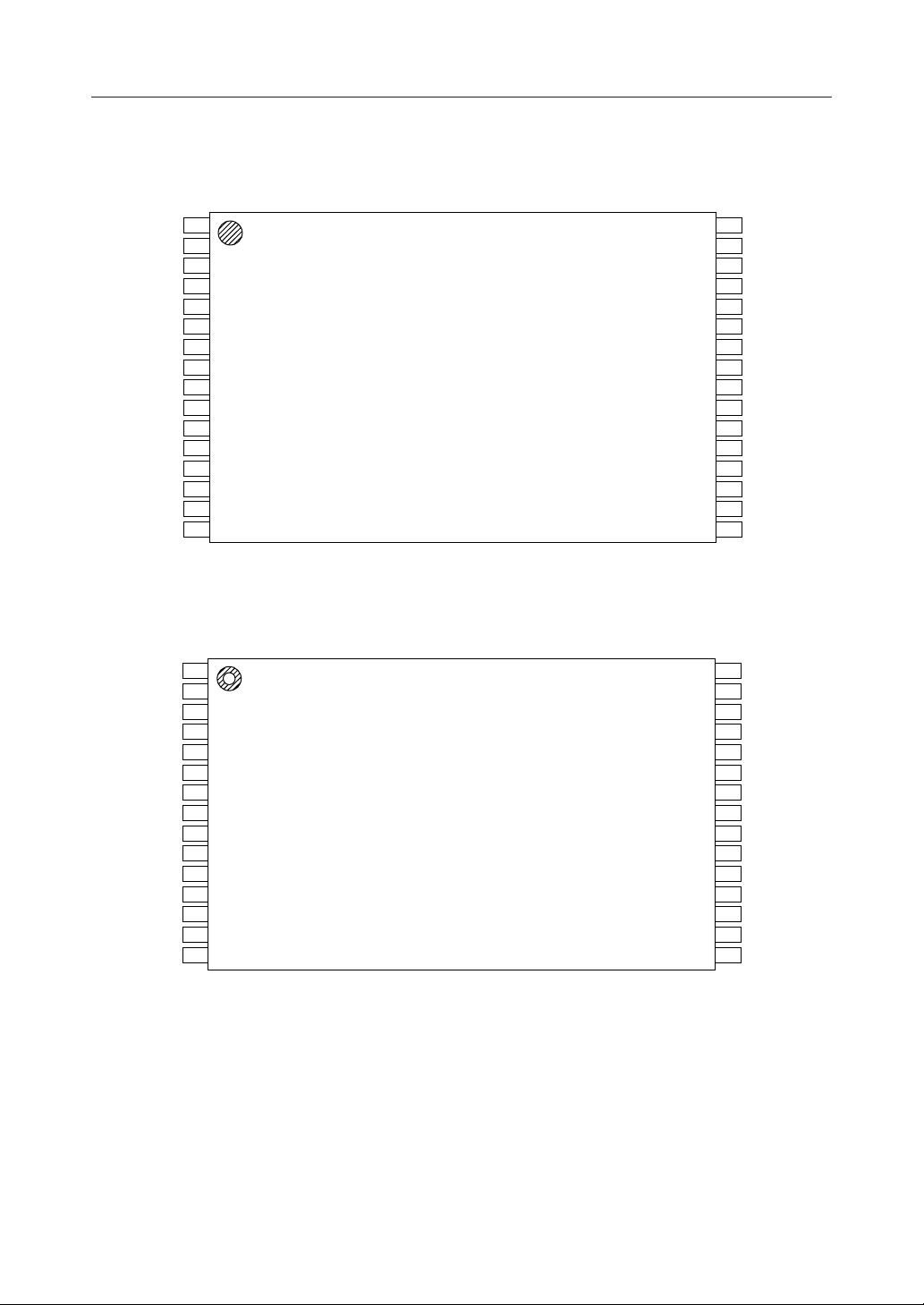

MAIN, MAO

Transmit microphone input and the level adjustment.

MAIN is connected to the noninverting input of the op-amp, and MAO is connected to the output

of the op-amp. The level adjustment should be configured as shown below.

During power saving and power down modes, the MAO output is in high impedance state.

R1 : variable

R2 > 20 kW

C1 > 1/(2 ¥ 3.14 ¥ 30 ¥ R1) (F)

Gain = R2/R1 < 63

Microphone input

C1

R1

R2

MAO

MAIN

–

+

SG

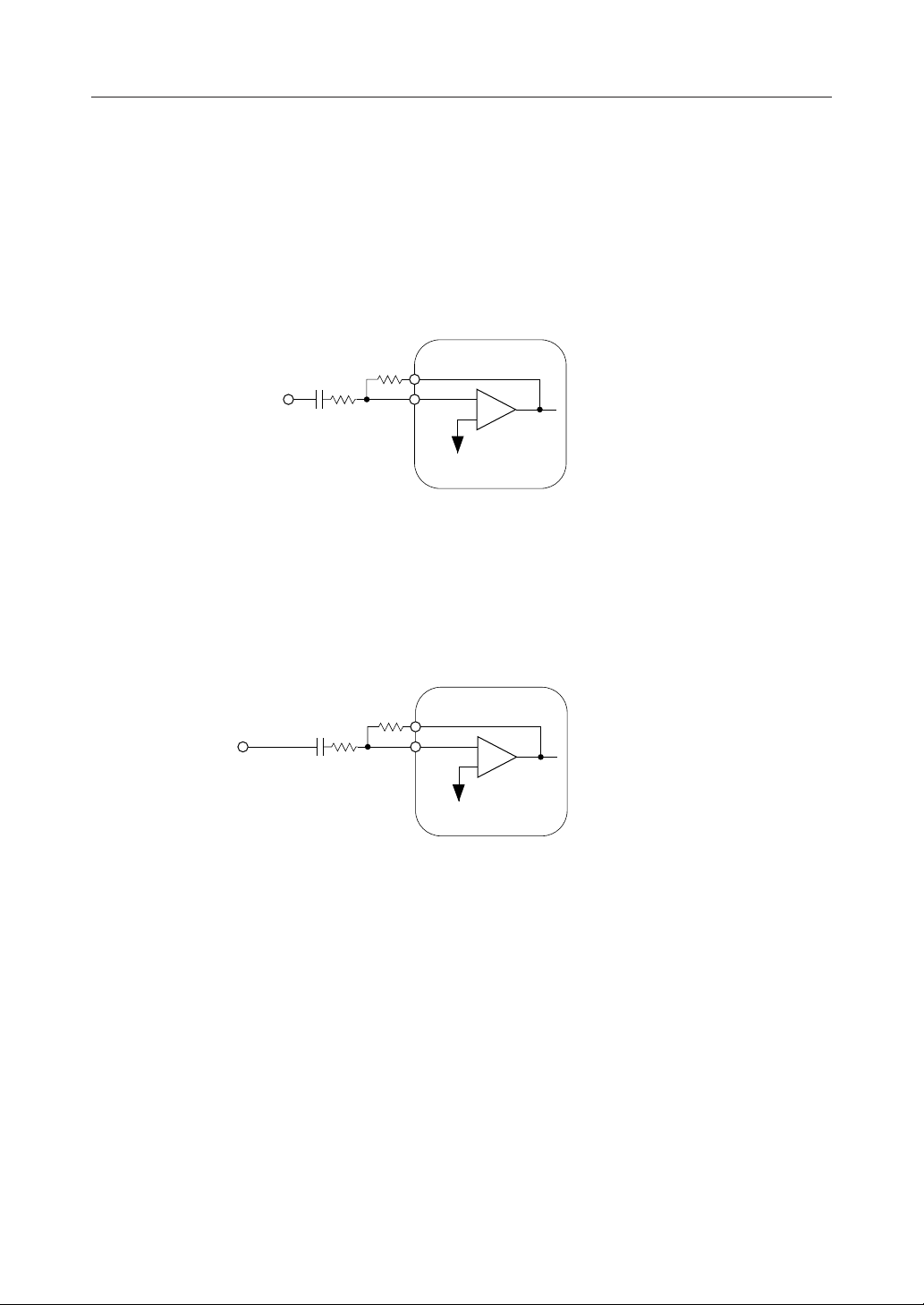

PBIN, PBO

Transmit handset input and the level adjustment.

PBIN is connected to the noninverting input of the op-amp, and PBO is connected to the output

of the op-amp. The level adjustment should be configured as shown below.

During power saving and power down, the PBO output is in high impedance state.

Handset

microphone input

V

DD

C2

R3

R4

PBO

PBIN

–

+

SG

R3 : variable

R4 > 20 kW

C2 > 1/(2 ¥ 3.14 ¥ 30 ¥ R3) (F)

Gain = R4/R3 < 63

Power supply pin for +2.7 to 3.6 V (Typically 3.0 V).

AG

Analog signal ground.

DG

Ground pin for the digital signal circuits.

This ground is separated from the analog signal ground in this device. The DG pin must be

connected to the AG pin on the printed circuit board.

4/22

¡ Semiconductor MSM7716

VFO

Receive filter output.

The output signal has an amplitude of 2.0 VPP above and below the signal ground voltage when

the digital signal of +3 dBm0 is input to PCMIN. VFO can drive a load of 20 kW or more.

This output can be externally controlled in the level range of 0 to –28 dB in 4 dB increments.

During power saving or power down, VFO output is at the voltage level (VDD/2) of SG with a

high impedance state.

PWI, AOUT+, AOUT–

PWI is connected to the inverting input of the receive driver.

The receive driver output is connected to the AOUT– pin. Thus, a receive level can be adjusted

with the pins PWI, AOUT–, and VFO described above.

The output of AOUT+ is inverted with respect to the output of AOUT– with a gain of 1.

The output signal amplitudes are a maximum of 2.0 VPP.

These outputs, above and below the signal ground voltage (VDD/2), can drive a load of a

minimum of 1 kW with push-pull driving (a load connected between AOUT+ and AOUT–).

The output amplitudes are 4 VPP maximum during push-pull driving. These outputs can be

mute controlled externally. These outputs are operational during power saving and output the

SG voltage (VDD/2) in the high impedance state.

AUXO

Auxiliary receive filter output.

The output signal is inverted with respect to the VFO output with a gain of 1. The output signal

swings above and below the SG voltage (VDD/2), and can drive a minimum load of 0.5 kW with

respect to the SG voltage.

The output can be mute controlled externally.

During power saving and power down, AUXO outputs the SG voltage (VDD/2) in the high

impedance state.

BCLK

Shift clock signal input for PCMIN and PCMOUT.

The frequency is equal to the data rate. Setting this signal to logic "1" or "0" drives both transmit

and receive circuits to the power-saving state.

5/22

¡ Semiconductor MSM7716

SYNC

Synchronizing signal input.

In the transmit section, the PCM output signal from the PCMOUT pin is output synchronously

with this synchronizing signal. This synchronizing signal triggers the PLL and synchronizes all

timing signals of the transmit section.

In the receive section, 14 bits required are selected from serial input of PCM signals on the PCMIN

pin by the synchronizing signal.

Signals in the receive section are synchronized by this synchronizing signal. This signal must be

synchronized in phase with the BCLK.

When this signal frequency is 8 kHz, the transmit and receive section have the frequency

characteristics specified by ITU-T G. 714. The frequency characteristics for 8 kHz are specified in

this data sheet.

For different frequencies of the SYNC signal, the frequency values in this data sheet should be

translated according to the following equation:

Frequency values described in the data sheet

8 kHz

Setting this signal to logic "1" or "0" drives the device to power-saving state.

PCMIN

PCM signal input.

A serial PCM signal input to this pin is converted to an analog signal synchronously with the

SYNC signal and BCLK signal.

The data rate of the PCM signal is equal to the frequency of the BCLK signal.

The PCM signal is shifted at a falling edge of the BCLK signal. The PCM signal is latched into the

internal register when shifted by 14 bits.

The top of the data (MSD) is identified at the rising edge of SYNC.

The input signal should be input in the 14-bit 2's complement format.

The MSD bit represents the polarity of the signal with respect to the signal ground.

¥ the SYNC frequency values to be actually used

6/22

¡ Semiconductor MSM7716

PCMOUT

PCM signal output.

The PCM output signal is output from MSD in sequential order, synchronously with the rising

edge of the BCLK signal.

MSD may be output at the rising edge of the SYNC signal, depending on the timing between

BCLK and SYNC.

This pin is in high impedance state except during 14-bit PCM output. It is also high impedance

during power saving or power down mode.

A pull-up resistor must be connected to this pin, because its output is configured as an open

drain.

The output coding format is in 14-bit 2's complement.

The MSD represents a polarity of the signal with respect to the signal ground.

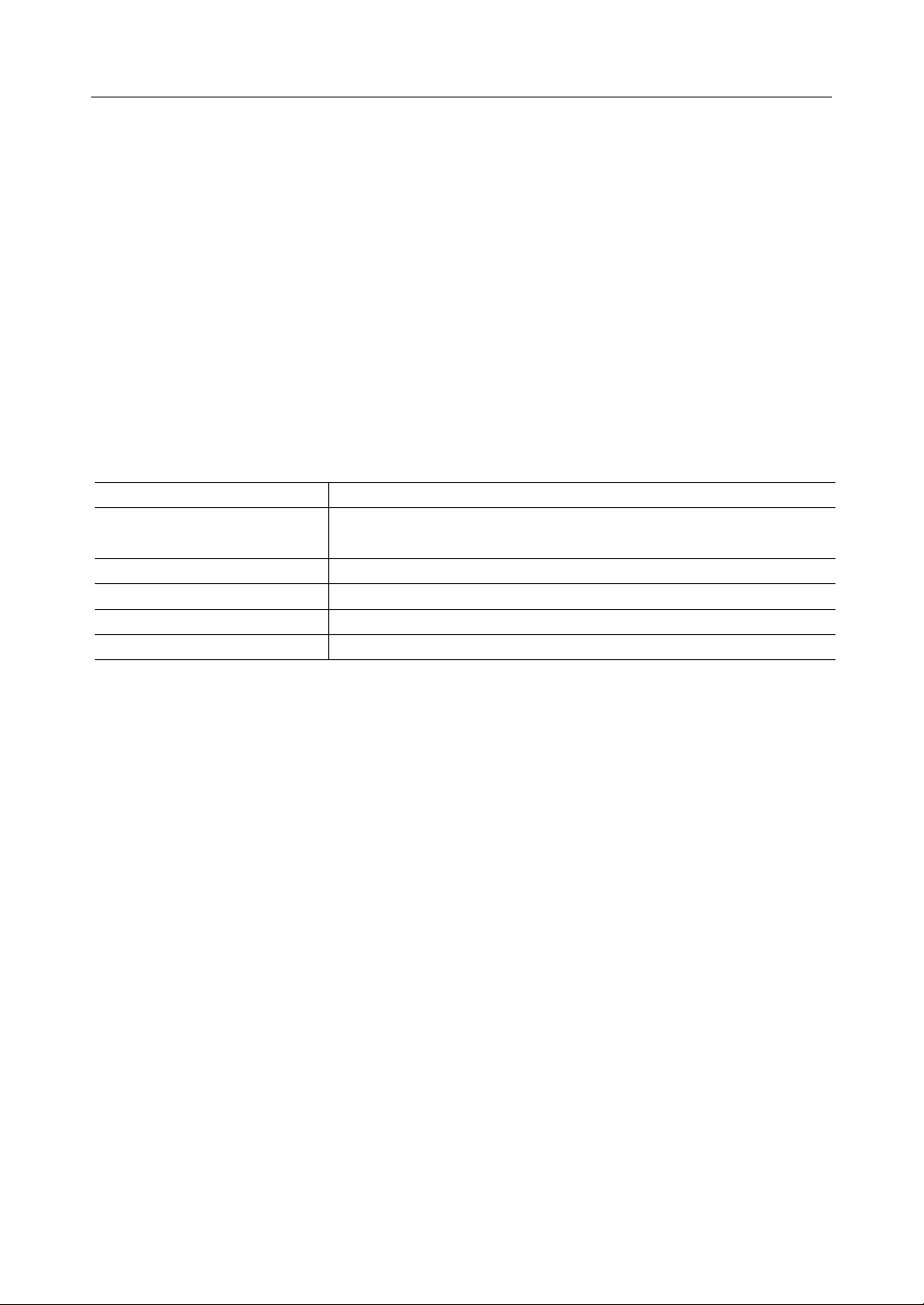

Table 1

Input/Output Level

+Full scale

+1

0

–1 1111 1111 1111 11

–Full scale

MSD

0111 1111 1111 11

0000 0000 0000 01

0000 0000 0000 00

1000 0000 0000 00

PCMIN/PCMOUT

PDN

Power down control signal input.

A digital "L" level drives both transmit and receive circuits to a power down state.

The control registers are set to the initial state.

SGC

Connection of a bypass capacitor for generating the signal ground voltage level.

Connect a 0.1 mF capacitor with excellent high frequency characteristics between the AG pin and

the SGC pin.

7/22

Loading...

Loading...