MSM7712

Wireless LAN Baseband Controller

DESCRIPTION

The MSM7712 is the first release in a series of wireless LAN baseband controllers, designated .XI (a suffix

of the IEEE P802.11 protocol). The MSM7712 integrates the baseband physical layer and the lower MAC

layers into a single IC that supports specific draft standards of the P802.11 specification. The architecture

targets optimum integration with maximum user flexibility, providing a migration path to low-cost module handsets and access points. In accordance with all three P802.11 media, the MSM7712 directly supports frequency hopping (FH), spread spectrum, direct-sequence spread spectrum, and infrared

protocols., A board-level system contains the MSM7712, a radio, a 16-bit processor, and buffer memory

ICs.

The MSM7712 provides a seamless interface to the radio, hoist, processor, and memory subsystems. The

device directly interfaces with the PCMCIA R2.1 and ISA bus, with support for 16-bit data transfers. The

device can control antenna select, synthesizer programming, and power-save modes. The MSM7712 provides FH PLPC framing, with the FH modem on-board. A bypass mode allows support for other standards. MSM7712 firmware is available from Oki Semiconductor.

Portable handheld systems inherently require minimal current dissipation during operation and standby

modes. The MSM7712 offers low power consumption via its implementation of a 3-V core. Either 3-V or

5-V I/O are available for optimal RF and host-interface design.

The MSM7712 wireless LAN baseband controller is manufactured in Oki’s advanced Si-gate 0.5 µ m

CMOS process for the best possible low-power performance.

FEATURES

• Support for specific IEEE P802.11 wireless LAN

draft standards

• Suitable for low-cost stations and access points

• PCMCIA compliant (version 2.1) interface

supporting 16-bit data transfers

• On-chip radio modem for high-throughput

data transfers

• Interface to radio providing antenna select,

power control, synthesizer programming

• Processor interface support for 80C86, 80C186,

V33, and V53A

• On-chip multi-port memory controller on chip

for local shared memory and simplified design

construction

2

•E

PROM interface to download host interface

configuration data and provide non-volatile

card parameter storage

• Low-power mode to minimize power

dissipation in batter applications.

• 5-V external and 3.3-V core operation

• 144-pin LQFP package, suitable for PCMCIA

Type II Cards (LQFP144-P-2020-0.50-K)

1Oki Semiconductor

■

MSM7712 ■ –––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––

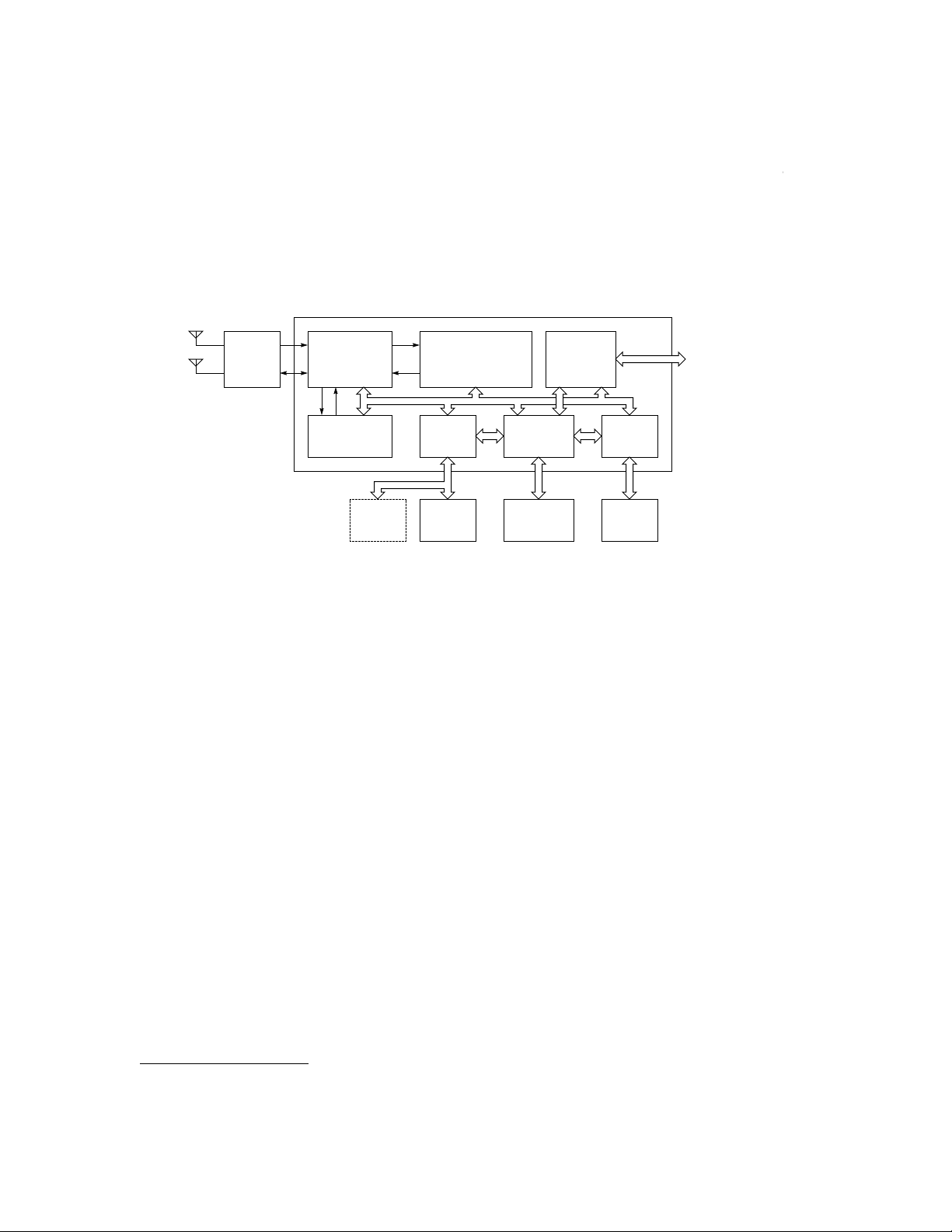

BLOCK DIAGRAM

Figure 1 shows a typical WLAN card. The MSM7712 provides a direct connection to a host interface, pro-

cessor, radio, shared memory, and configuration E

2

PROM. Optional additions are a RAM for processor

code.

MSM7712GS-K

Radio

PHY Layer,

Radio Interface

Combined 1 & 2

Mbps Modem

Processor

RAM

(optional)

802.3 MAC Protocol

Controller

Processor

Interface

Processor

Memory

Controller

Shared RAM

(32k~128kx16)

PCMCIA

Interface

E2PROM

Interface

E2PROM

Host

Computer

Figure 1. MSM7712 Block Diagram & Typical WLAN Card

2 Oki Semiconductor

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– ■ MSM7712 ■

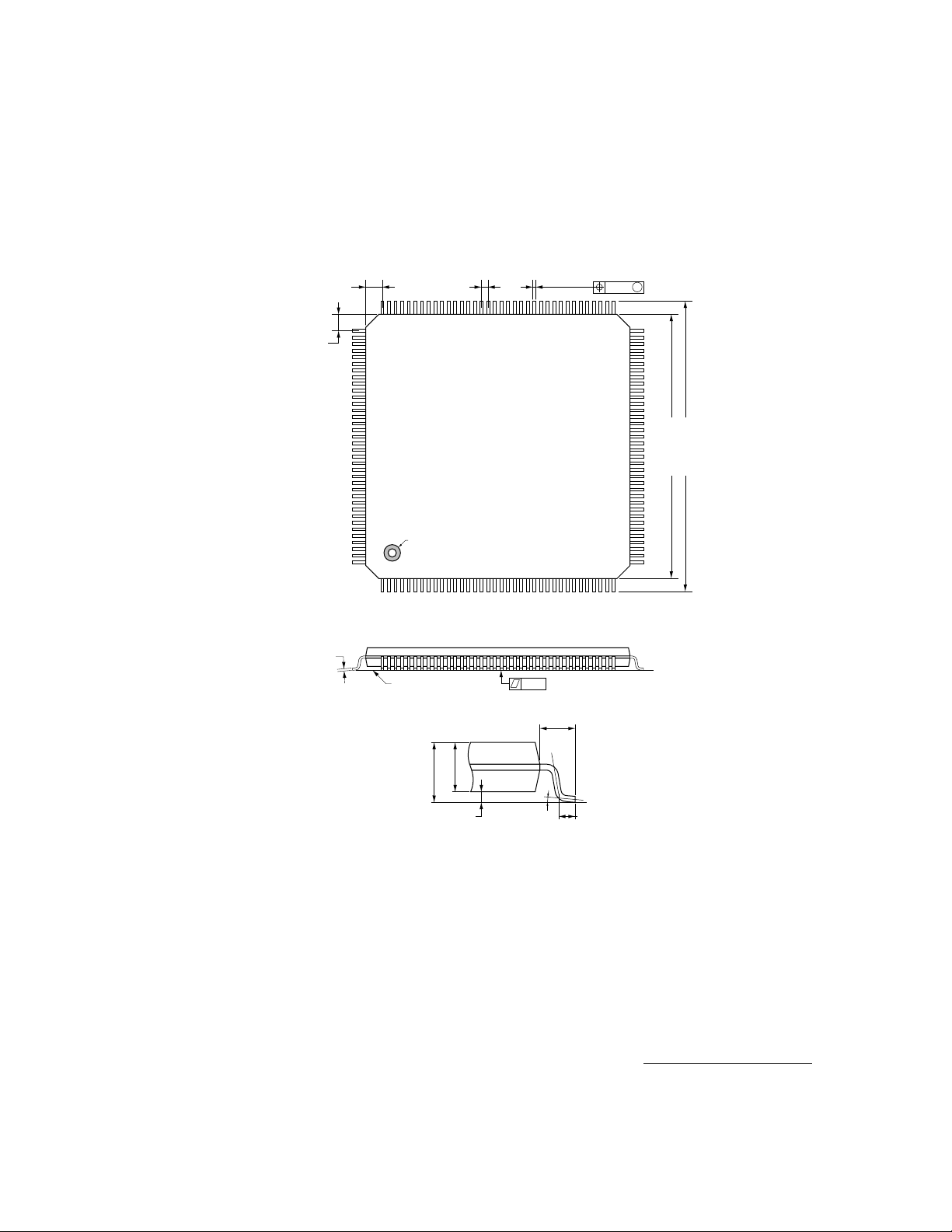

PACKAGE DRAWING

1.25 TYP 0.5

108

109

1.25 TYP

144

1 36

0.17 ±0.05

Seating Plane

LQFP144-P-2-2-0.50-K

PIN 1 INDEX

(Mirror Finish)

0.10

0.22 ±0.05

1.0 ±0.2

0.10

M

73

72

22.0 ±0.2 SQ

20.0 ±0.1 SQ

37

1.4 ±0.05

1.7 Max

0~0.25 0.5 TYP

Dimensions in millimeters

0~10°

3Oki Semiconductor

■

MSM7712 ■ –––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––

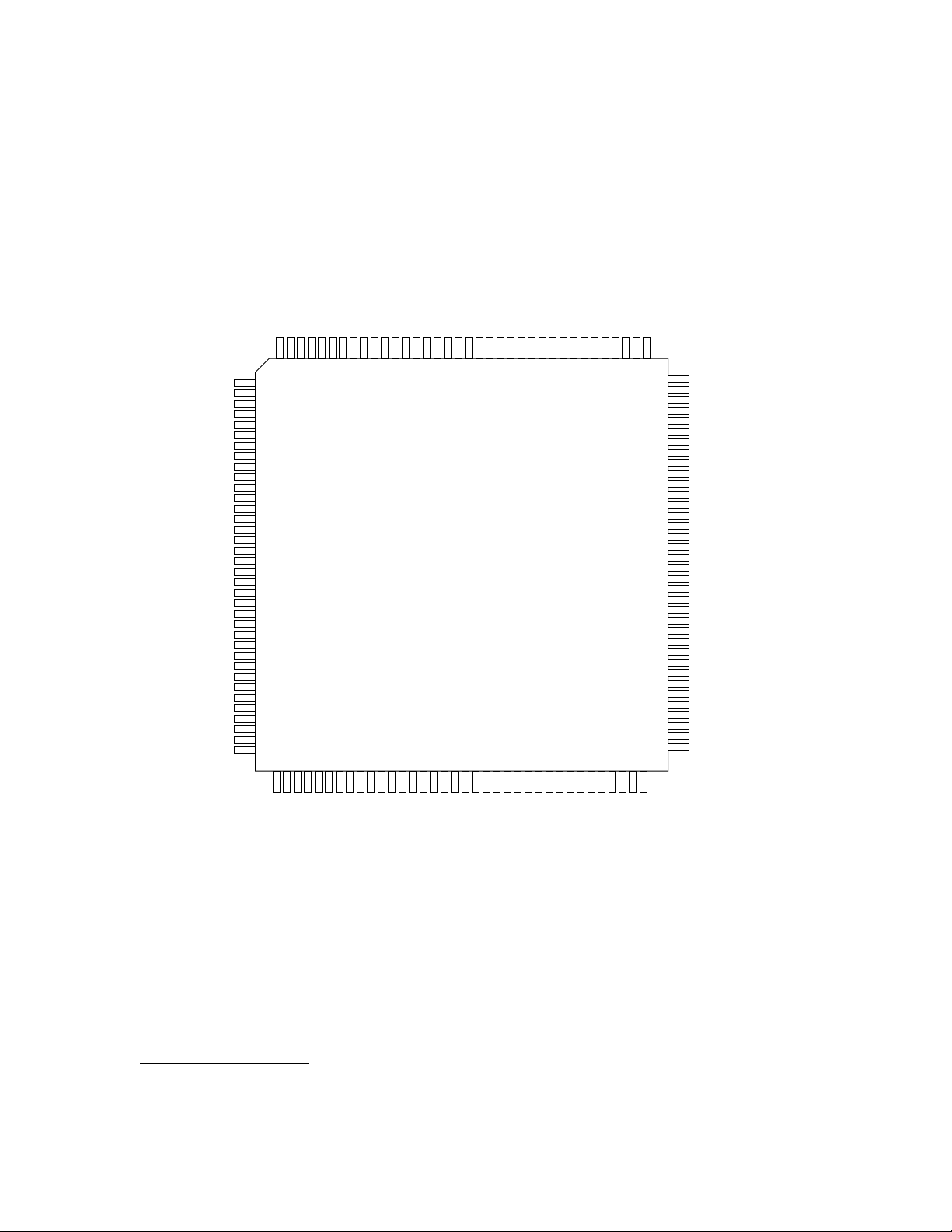

PIN CONFIGURATION

RA15144

RA16143

DIAG6142

DIAG5141

DIAG4140

DIAG3139

DIAG2138

DIAG1137

DIAG0136

RXD135

VSSO134

VDDO133

IFD5132

IFD4/SLICE131

IFD3130

IFD2129

IFD1128

IFD0127

RSSITN126

ANT125

RADPWR124

TXC2123

TXC1122

RXC1121

LKDET120

SYNLEN119

EECS118

SYNDAT/EEDIO117

SYNCLK/EESK116

DACEN115

RCK114

VSSO113

VDDO112

PST0111

PST1110

PST2109

RA14 1

RA13 2

RA12 3

RA11 4

RA10 5

RA9 6

RA8 7

RA7 8

RA6 9

RA5 10

RA4 11

RA3 12

RA2 13

RA1 14

RA0 15

SCK 16

VDDO 17

VSSO 18

RWRN 19

RCELN 20

RCEHN 21

RD0 22

RD1 23

RD2 24

RD3 25

RD4 26

RD5 27

RD6 28

RD7 29

RD8 30

RD9 31

RD10 32

VDDO 33

VSSO 34

RD11 35

RD12 36

PCLK108

PRESETN107

PINTN106

PCLKOUT105

PUBE104

PCSN103

PREAD102

PREADYN101

PD17100

PD1699

PD1598

PD1497

PD1396

PD1295

PD1194

PD1093

PD992

PD891

PD790

PD689

PD588

PD487

VSSO86

VDDO85

PD384

PD283

PD182

PD081

HD380

HD1179

HD478

HD1277

HD576

HD1375

HD674

HD1473

HA0 47

HA1 48

HA2 50

HD2 42

HD9 43

HD1 44

HD8 45

RD13 37

RD14 38

RD15 39

HD10 41

HIOIS16N 40

HD0 46

HA3 52

VDDC 53

HREG 49

HPACKN 51

HA4 58

HA5 60

HA6 61

HA7 62

VSSC 54

HRST 59

VSSO 55

VDDO 56

HWAITN 57

HA8 66

HWEN 64

HIREQN 63

HIORDN 67

HIOWRN 65

HD7 72

HD15 71

HOEN 68

HCE2N 69

HCE1N 70

4 Oki Semiconductor

Figure 2. 144-Pin Plastic TQFP Pin Assignment

–––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––– ■ MSM7712 ■

INTERFACE DESCRIPTIONS

Processor Interface

Most applications (e.g. PC add-in cards) require a local processor to handle the higher layers of the IEEE

802.11 protocol. The host computer typically runs a NDIS or ODI driver that communicates to the local

processor via shared memory and interrupts. The local processor performs the higher layers of the IEEE

802.11 MAC protocol while the MSM7712GS-K performs the lower layers of MAC and the PHY under

control of the local processor.

The MSM7712 can be configured to operate with 80C80 (V30) and 80C186 processor types. The processor

configuration P_CONF is determined from the level of the PD lines during the MSM7712 reset. Designers

should consult the appropriate processor datasheets and this section to understand how the processor

interface works.

No external circuitry is required between the processor and the MSM7712. Table 1 specifies the connection of various processor signals to the MSM7712.

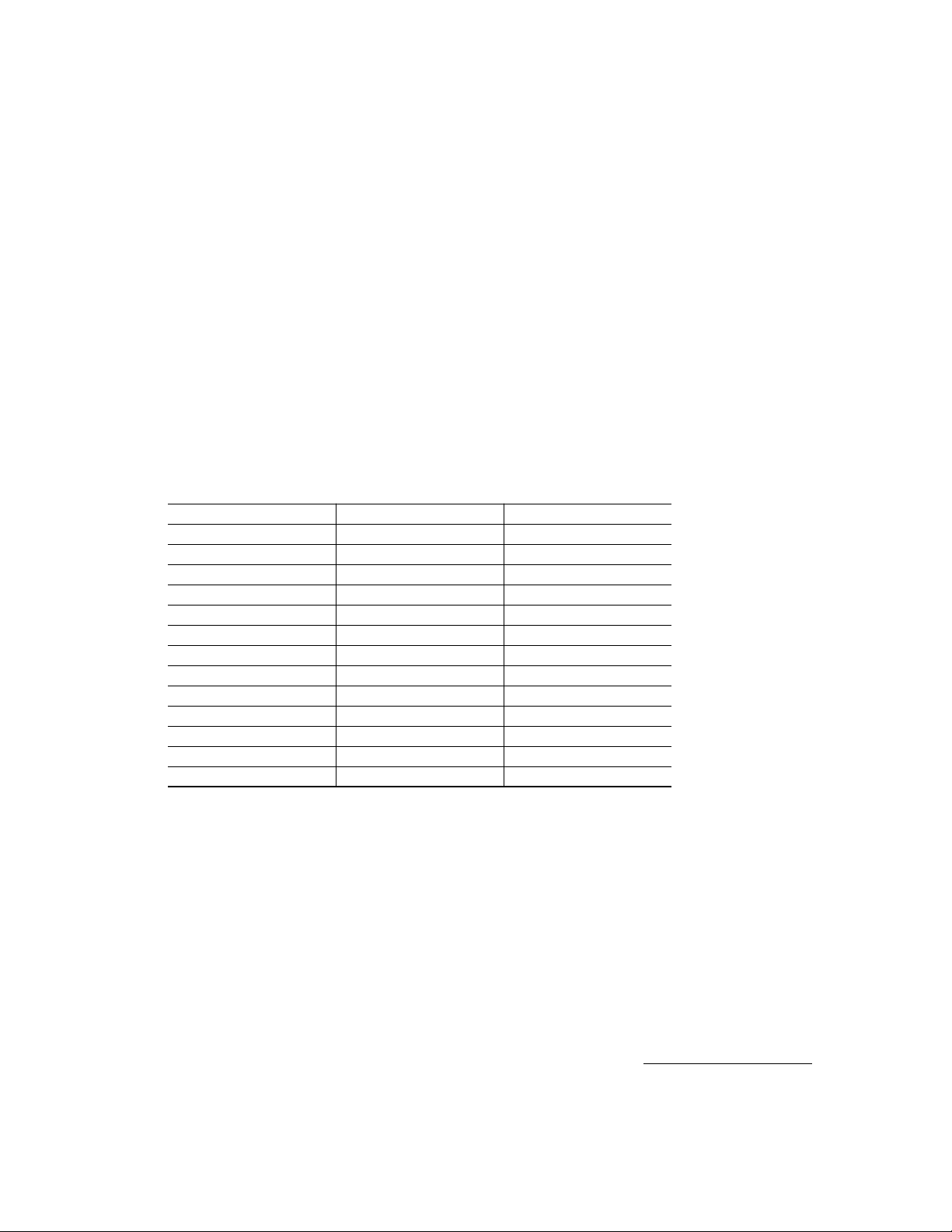

Processor Options

MSM7712GS-K 80C86, V30 (Max mode) 80C186

P_CONF 1 2

PA[17:16] A[17:16] AD[17:16]

PD[15:0] AD[15:0] AD[15:0]

PST2 BS2 S2

PST1 BS1 S1

PST0 BS0 S0

PREAD - PUBE UBE BHE

PCLKOUT - CLKOUT

PREADYN READY SRDY

PINTN INT INT0

PRESETN RESET RES

PCLK CLK X1

The output signal PREADYN, PINTN, PRESETN are active low or high to suit the different processor

requirements

P_CONF option 1 provides an interface to the 80C86 or V30 processor. The processor must be set to maximum mode and a device with a 50% mark/space clock ratio at 16MHz and must be used (assuming a

CSCK of 32 MHz).

P_CONF option 2 provides an interface to the 80C186 processor family with a 32 Mhz oscillator input.

All other values of P_CONF are reserved and should not be used.

5Oki Semiconductor

■

MSM7712 ■ –––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––––

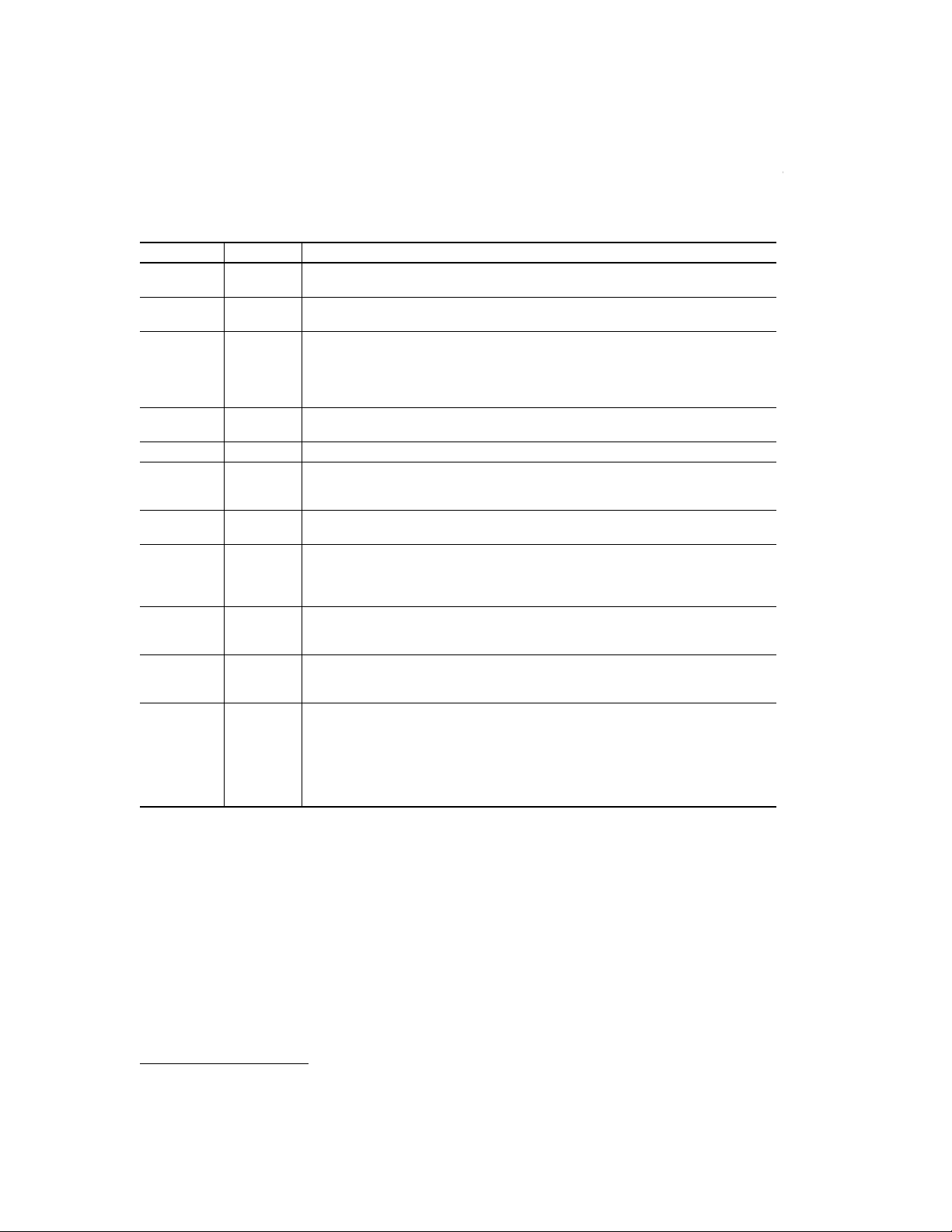

Processor Interface Signal Descriptions

Pin Name Direction Description

PA[17:16] Input Provides the high address pins to the MSM7712. The usage depends on the shared memory size. The address

PCSN Input Provides a processor chip select to the MSM7712. From reset, this pin is ignored and all processor accesses

PD[15:0] Bidirectional Provides the data bus and low addresses. The 80C86 and 80C186 processors have a multiplexed address/

PST[2:0] Input Provides Processor Status to the MSM7712. Typically this differentiates between memory and I/O reads and

PREAD This pin is reserved for future product enhancements.

PUBE Input In conjunction with PD[0], this signal provides a decode of even byte, odd byte, or word accesses by the pro-

PCLKOUT Input Within a 80C186 processor-based system, CLKOUT should be connected to PCLKOUT pin. This is required

PREADYN Input This pin signals the processor that the bus cycle is complete. The only accesses that potentially require wait

PINTN Output One interrupt is provided from the MSM7712 to the processor. A fixed interrupt vector is provided on the data

PRESETN Output The processor is reset via the host computer with this signal. From card reset, the processor is typically held

PCLK Output The processor clock is provided by the MSM7712. From power up PCLK is set at SCK divided by 8. A register

space usage of the MSM7712 is 256 kbytes comprising MSM7712 registers and shared RAM.

use the MSM7712. The pin can then be configured by software to be active high or active low.

data bus and are connected directly to PD [15:0]. The MSM7712 configuration is provided on these pins during reset. During reset (HRST asserted), the processor is reset and these pins are configured as input pins.

The configuration is set by weak pull-up and pull-down resistors on PD [7:0]. Following reset and when the

processor is not reset, the bus operates normally. See the Configuration Section for detailed options.

writes.

cessor. The MSM7712 registers are accessed as words and the processor and shared RAMs can be accessed

as bytes or words.

such that PREADYN timing requirements relative to CLKOUT are met.

states are those to the shared RAM. The shared RAM is accessed by the MSM7712 host (via PCMCIA) and

processor on a priority basis. This means the shared RAM may be busy when the processor requests an access and hence wait states are inserted until the shared RAM is available.

bus for interrupt acknowledge cycles. Although described as active low (by the xxxN convention), the pin state

is active high or low depending on the processor selected.

in reset until the program code is downloaded from the host. Although described as active low (by the xxxN

convention) the pin state is active high or low depending on the processor selected.

programs PCLK to be from SCK to SCK divided by 8. The PCLK frequency selection allows a processor to operate at either low power or maximum performance. Within a 80C186 system, the processor is synchronized

to the MSM7712 by monitoring the processor CLKOUT signal and skipping PCLK periods if necessary. All processor types must use this clock. The MSM7712 expects the processor bus interface timing to be synchronized with this clock signal.

Note: SCLK is typically 16 MHz or 32 MHz depending on which modem and processor is being used.

6 Oki Semiconductor

Loading...

Loading...