OKI MSM7661BGS-BK Datasheet

E2F0009-18-62

Preliminary

¡ Semiconductor MSM7661B

This version: Jun. 1998

¡ Semiconductor

MSM7661B

NTSC/PAL Digital Video Decoder

GENERAL DESCRIPTION

The MSM7661B is an LSI device which converts digitally sampled NTSC or PAL video signals

to 8-bit format based on ITU-RBT601.

The input video signals available are composite video signals and S video signals.

The composite video signals are converted to YUV data via a 2-dimensional Y/C separation

circuit.

The A-to-D converted data is data sampled at pixel clock frequency or double pixel clock

frequency (the built-in decimation filter is used). Input signal synchronization can lock

synchronization and color burst at high speed through internal digital processing.

The MSM7661B is upward compatible with the MSM7661. It provides additional features which

are added to the MSM7661 indicated by the mark n and is superior to the MSM7661 in picture

quality and synchronization stability. The device, which includes an additional register added

to the MSM7661, has electrical characteristics which are nearly equal to those of the MSM7661.

The MSM7661B allows a pin-for-pin replacement with the MSM7661.

FEATURES (• indicates a new feature compared with MSM7660. n indicates a

new feature compared with MSM7661.)

• Input video signals include the following two types of digital data that are A-to-D converted

at pixel frequency or double pixel frequency :

NTSC/PAL composite video signal

NTSC/PAL S video signal

8-bit Y/8-bit C (CbCr) output (conforms to ITU-RBT601)

°

YCbCr 4 : 2 : 2

YCbC4 : 1 : 1

n YCbCr 8-bit multiplex output (27 MHz) (not including SAV and EAV)

• 2-dimensional Y/C separation using adaptive comb filter (this filter is bypassed for S video

signal input)

NTSC: 3 lines/2 lines

PAL: 2 lines (3 virtual lines)

• Input signal synchronization can lock synchronization and color burst at high speed through

internal digital processing.

Sampling frequency

°

13.5 MHz (ITU-R601)

12.27 MHz (NTSC Square Pixel)

14.31818 MHz (NTSC 4Fsc)

14.75 MHz (PAL Square Pixel)

• Internal AGC/ACC circuit

Switchable between AGC and MGC (fixed gain)

n Switchable between ACC and MCC (fixed gain)

• Built-in decimation filter located in the input stage allows easy configuration of an external

filter circuit (located ahead of A/D converter).

• Automatic NTSC/PAL recognition (only for ITU-RBT.601)

• Sleep mode

1/42

¡ Semiconductor MSM7661B

• Multiplex signal recognition (Teletext)

Data during vertical blanking is output in 8 bits in Through mode.

I2C-bus interface

°

• 3.3 V single power supply (each I/O pin is 5 V tolerable)

• Package:

64-pin plastic QFP (QFP64-P-1414-0.80-BK) (Product name: MSM7661B GS-BK)

2/42

¡ Semiconductor MSM7661B

3/42

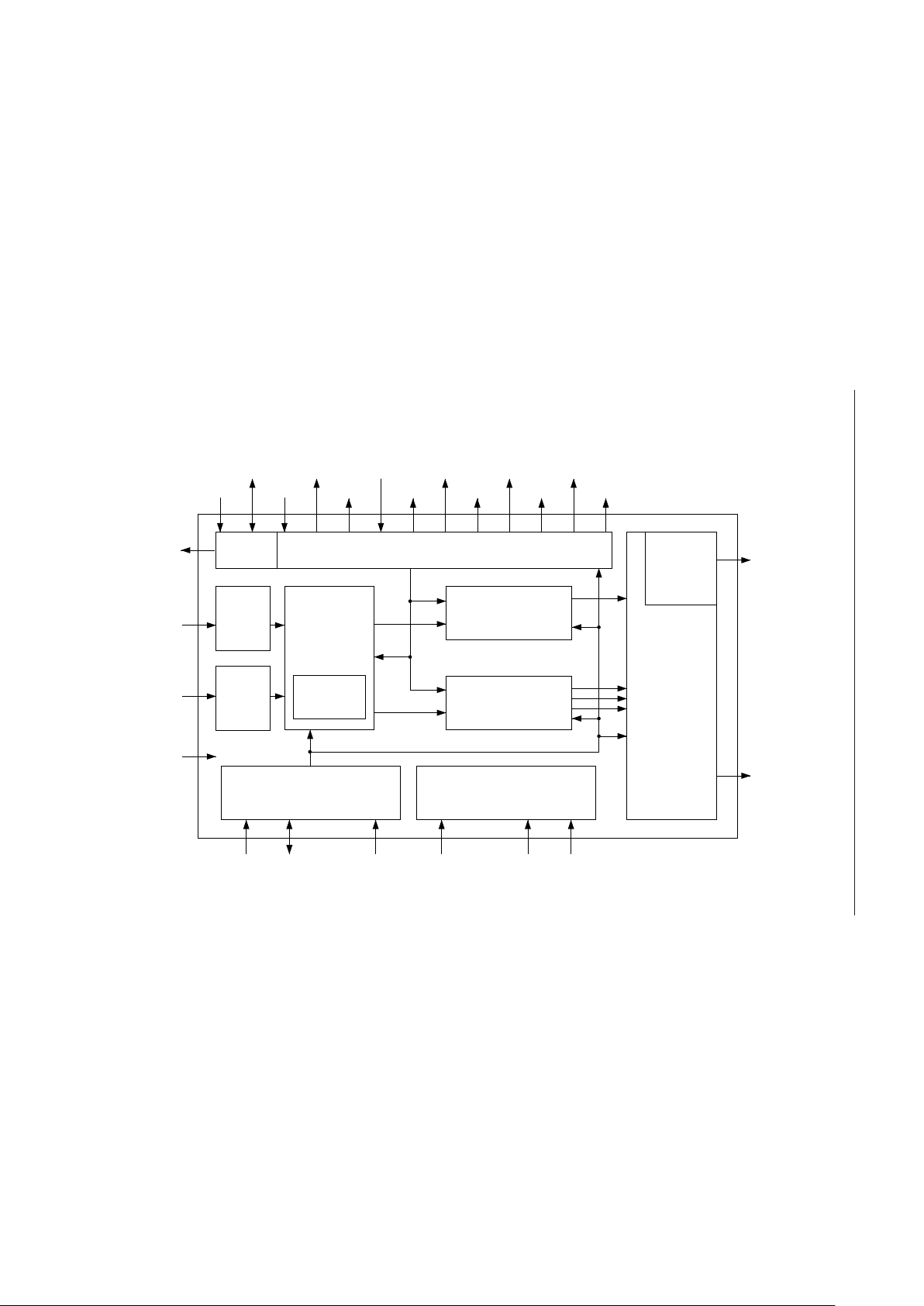

BLOCK DIAGRAM

SCL

Synchronization Block

Luminance Block

(AGC + LPF)

Prologue Block

lum.

chr.

Decimation

Filter

Line Memory

(1kbyte) ¥ 2

(2Dim. Y/C separate)

Chrominance Block

(ACC + LPF)

I2C-bus Control Logic Test Control Logic

Epilogue

Block

(Output Formatter)

SDA RESET_L TE TEST1 TEST2

(SLEEP)

ODDCLKX2PLLSEL

VVALID

HVALID

VSYNC_L

HSYNC_L

HSYCLKX2O

SYSSEL

CLKSEL

CLKXO

MODE[3:0]

YD[7:0]

VCO_CP

CD[7:0]

Y[7:0]

8 bits

(YCbCr)

C[7:0]

SYNC

(CSYNC_L)

Decimation

Filter

¡ Semiconductor MSM7661B

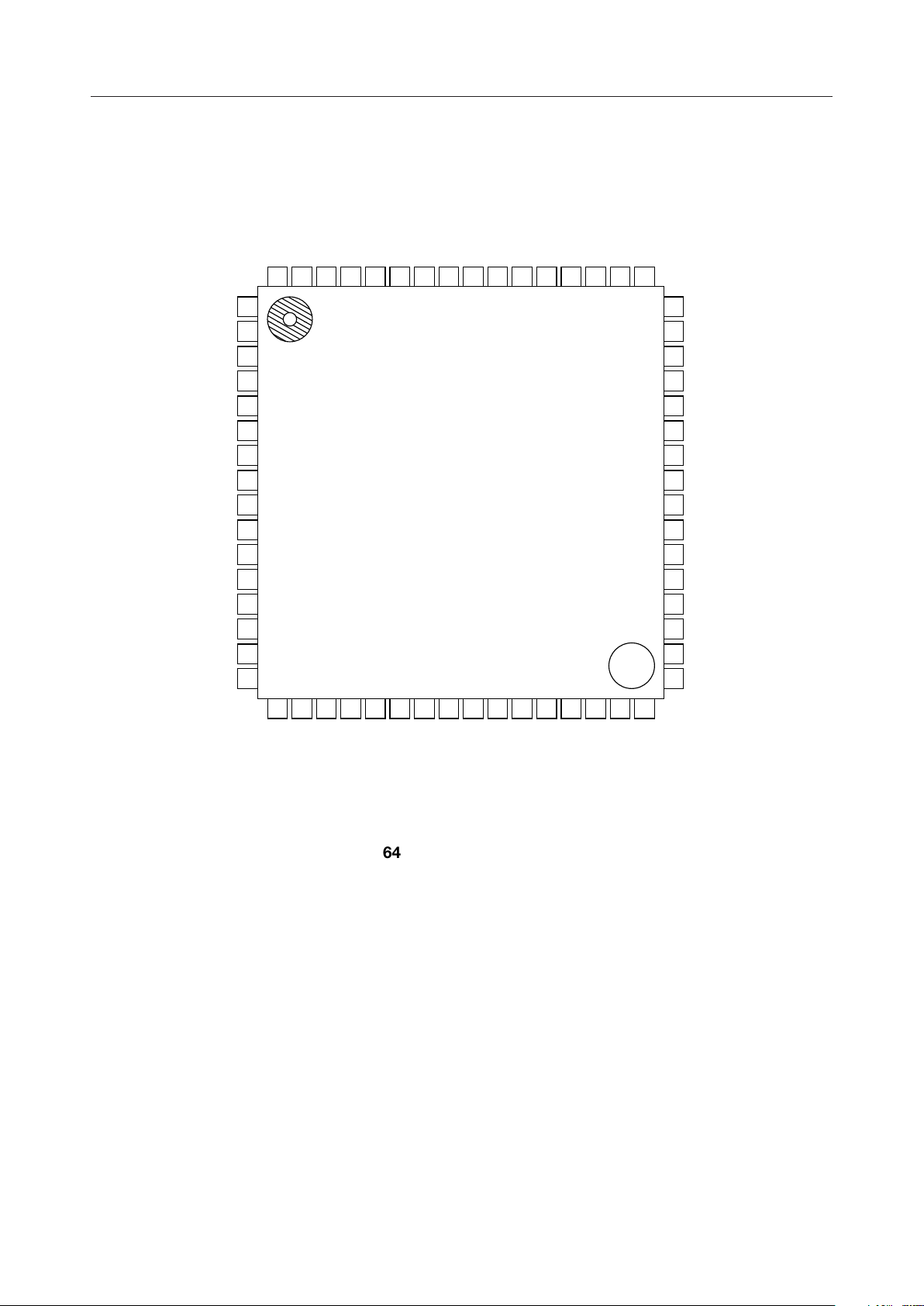

PIN CONFIGURATION (TOP VIEW)

CD[0]

CD[1]

CD[2]

CD[3]

CD[4]

CD[5]

CD[6]

CD[7]

CVBS[0]

CVBS[1]

CVBS[2]

CVBS[3]

CVBS[4]

CVBS[5]

CVBS[6]

CVBS[7]

10

11

12

13

14

15

16

1

2

3

4

5

6

7

8

9

VDDGND

644963

CLKX2

HSY

62

61

SYNC

60

VCO_CP

CLKX2O

59

58

SYSSEL

CLKXO

57

56

HSYNC_L

VSYNC_L

HVALID

55

54

53

VVALID

ODD

52

51

GND

50

V

DD

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

C[0]

C[1]

C[2]

C[3]

C[4]

C[5]

C[6]

C[7]

Y[0]

Y[1]

Y[2]

Y[3]

Y[4]

Y[5]

Y[6]

Y[7]

173218

DD

V

GND

19

SCL

20

21

22

23

24

SDA

MODE[0]

MODE[1]

MODE[2]

MODE[3]

64-Pin Plastic QFP

25

26

PLLSEL

RESET_L

27

28

TEST1

CLKSEL

29

30

TE

SLEEP

31

GND

V

DD

4/42

¡ Semiconductor MSM7661B

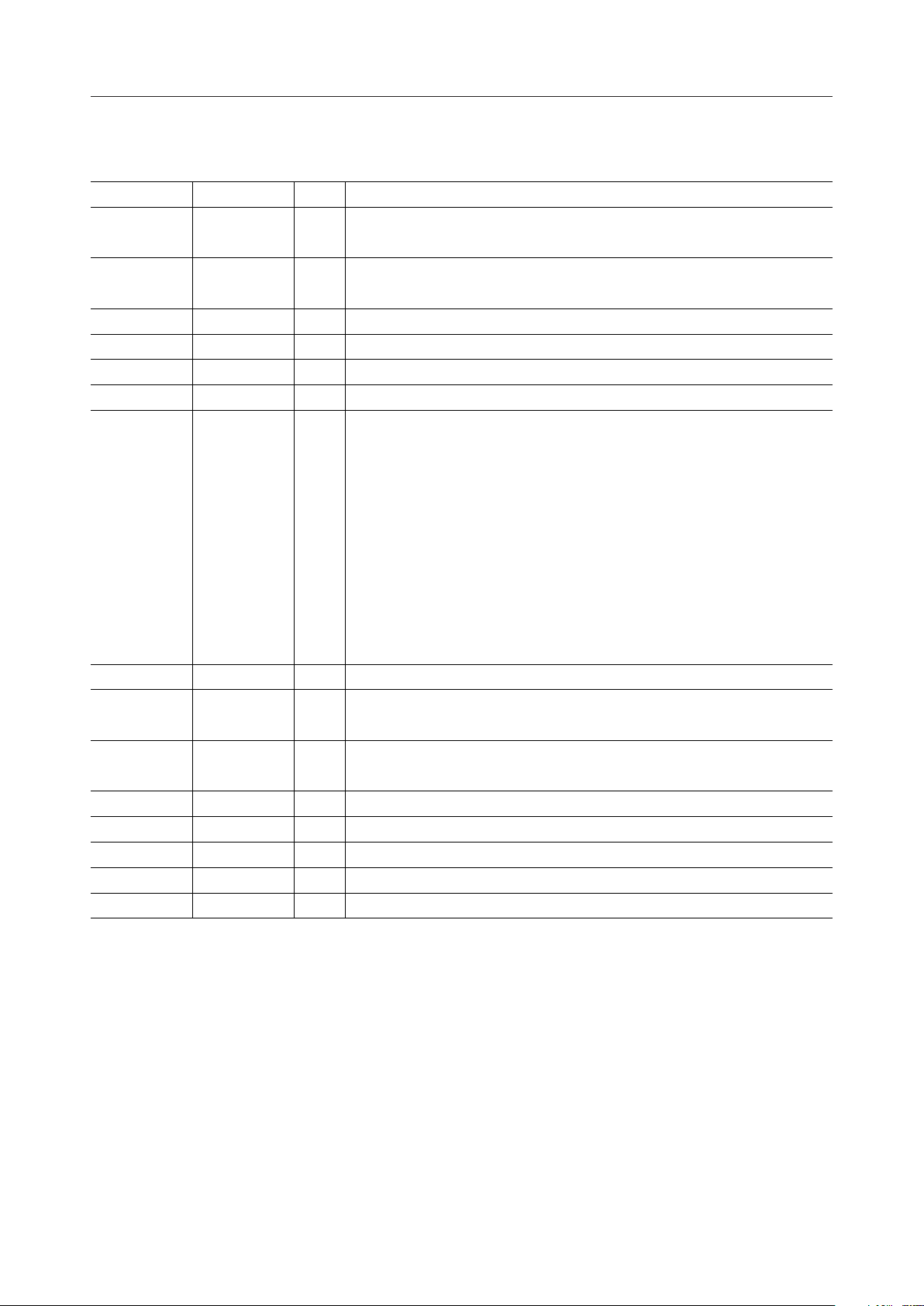

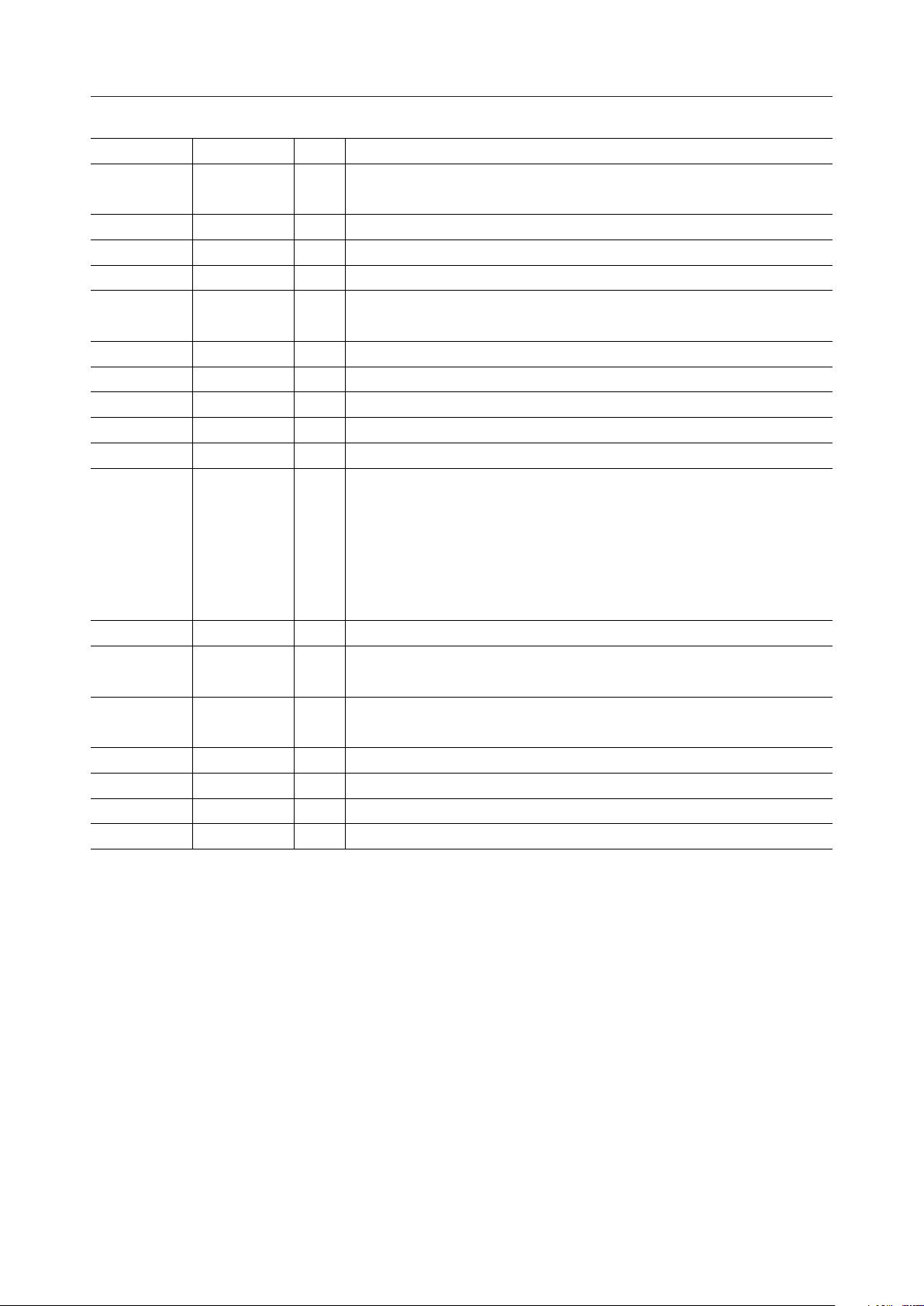

PIN DESCRIPTIONS

Pin

1 to 8

Symbol

CD[0 to 7]

Type

I

Chrominance signal input pin (valid only for S video input)

Description

Set each pin to "L" level at composite signal input.

9 to 16

CVBS[0 to 7]

Composite signal input pin

I

Luminance signal is input for S video input.

17

18

19

20

21 to 24

V

DD

GND

SCL

SDA

MODE[0 to 3]

2

I

C-bus clock pin

I

2

C-bus data pin

I

I/O

Mode input pins. These pins are internally pulled-down.

I

MODE[3] 0: composite

MODE[2] 0: NTSC

1: S video

MODE[1:0] 00: ITU-R601

01: Square Pixel

10: 4Fsc (only for NTSC)

11: none

If ITU-R signals are input when registers are set to automatic NTSC/PAL

recognition mode, NTSC/PAL is automatically recognized irrespective of

MODE2 setting.

25 IRESET_L

26

PLLSEL

System reset pin (active at "L")

Unused.

I

Fixed to "H" externally.

27

CLKSEL

Clock select input pin.

I

"L" Æ double-speed 27 MHz, "H" Æ ordinary 13.5 MHz

28

29

TEST1

SLEEP

Input pin for testing. Normally "L". Internally pulled down.

I

Sleep mode setting pin. Normally "L". Internally pulled down.

I

30 ITE Input pin for testing. Normally "L". Internally pulled down.

31 GND

32 V

DD

1: PAL

5/42

¡ Semiconductor MSM7661B

Pin

33 to 40

41 to 48

49

50

51

52

53

54

55

56

57

58

59

64

Symbol

Y[7 to 0]

C[7 to 0]

V

DD

GND

ODD

VVALID

HVALID

VSYNC_L

HSYNC_L

CLKXO

SYSSEL

CLKX2O

VCO_CP

SYNC I/O60

GND63

V

DD

Type

O

O

O

O

O

O

O

O

O

O

O

Description

Chrominance signal output pins

YCbCr 8-bit multiplex output pins

Luminance signal output pins

Field display output pin

Outputs "H" for odd field.

Vertical valid line timing output pin

Horizontal valid pixel timing output pin

V sync output pin

H sync output pin

Internal operation clock output pin

Display select output pin for NTSC-PAL detect / multiplex signal detect /

HLOCK sync detect.

Selection by register. (Default : NTSC-PAL detect)

NTSC mode : "L", PAL mode : "H"

Multiplex signal detect : "H"

HLOCK sync detect : "H"

Clock output pin

Unused.

Open normally.

Composite sync output.

Unused as input pin.

Clamp signal timing output pin for A/D converterHSY O61

Clock input pinCLKX2 I62

6/42

¡ Semiconductor MSM7661B

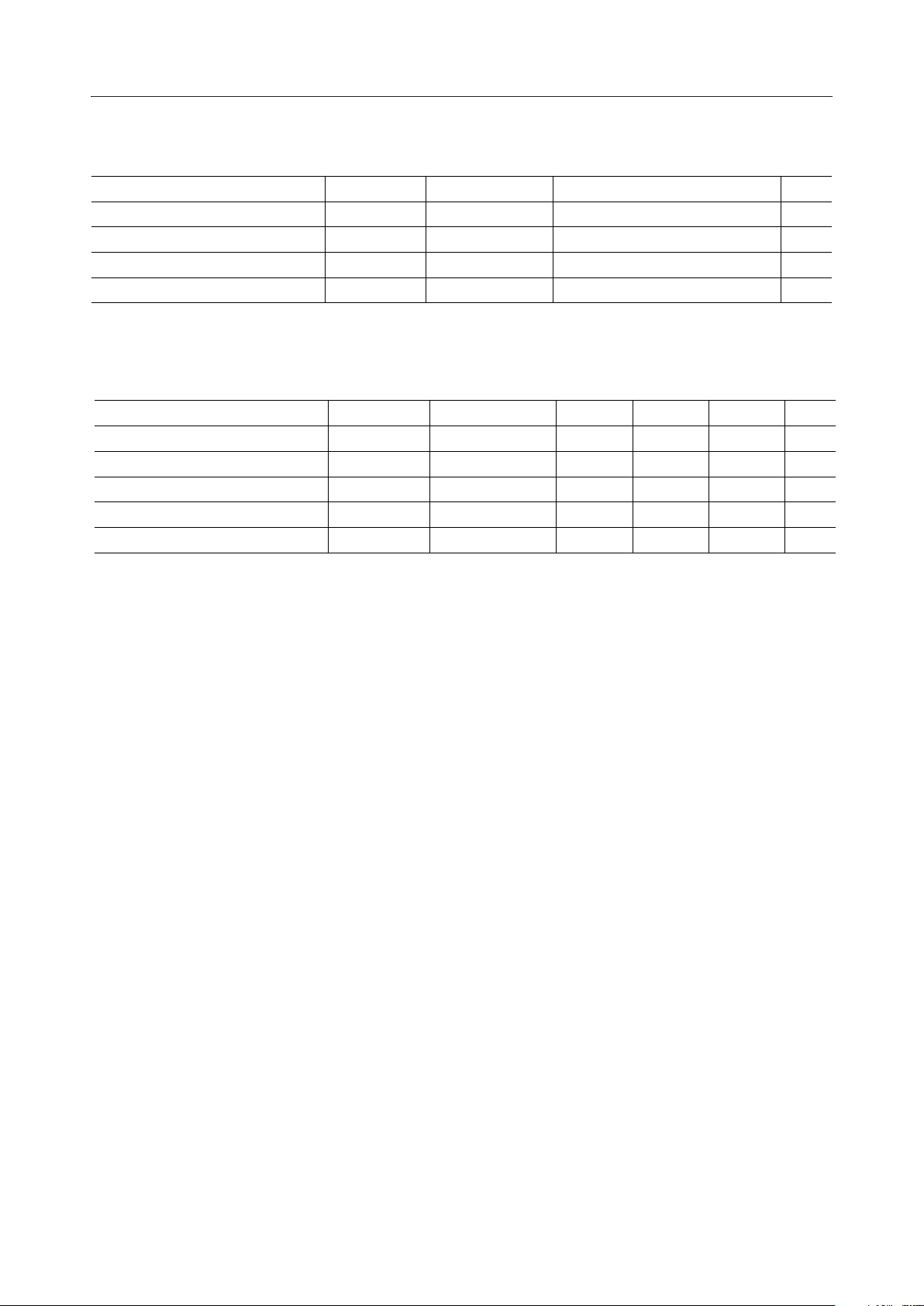

ABSOLUTE MAXIMUM RATINGS

Parameter

Power Supply Voltage

Input Voltage

Power Consumption

Storage Temperature

Symbol

V

DD

V

I

P

W

T

STG

Condition

—

—

—

—

Rating

–0.3 to +4.5

–0.3 to +5.5

800

–55 to +150

RECOMMENDED OPERATING CONDITIONS

Parameter

Power Supply Voltage

Power Supply Voltage

"H" Level Input Voltage

"L" Level Input Voltage

Symbol

V

DD

GND

V

IH

V

IL

Condition

—

—

—

—

Operating Temperature Ta — 25 °C

Min.

3.0

—

2.2

0

0

Typ.

3.3

0

—

—

Max.

3.6

—

V

DD

0.8

70

Unit

V

V

mW

°C

Unit

V

V

V

V

7/42

¡ Semiconductor MSM7661B

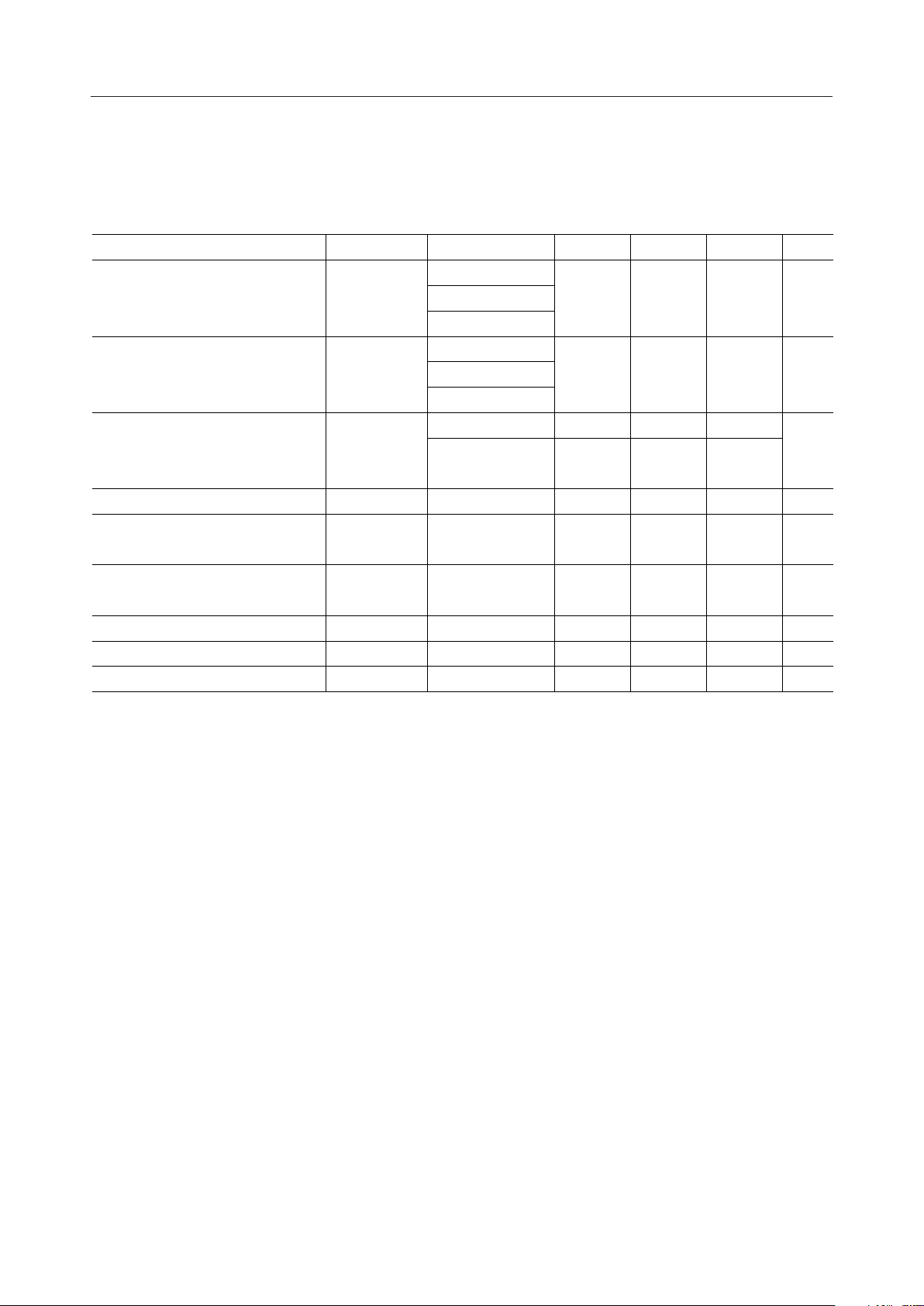

ELECTRICAL CHARACTERISTICS

DC Characteristics

(Ta = 0 to 70°C, VDD = 3.3 V ±0.3 V)

Parameter Symbol

Condition

Min.

Typ.

IOH = –4 mA (*1)

DD

0.7 V

DD

—

–10 +10

—

—V

—

—20 250

"H" Level Output Voltage V

"L" Level Output Voltage V

Input Leak Current I

V

OH

OL

I

IOH = –6 mA (*2)

= –8 mA (*3)

I

OH

= 4 mA (*1)

I

OL

= 6 mA (*2)

I

OL

I

= 8 mA (*3)

OL

VI =

GND to V

R

pull-down

=

50 kW (*4)

Output Leak Current I

Power Supply Current (operating)

I

DDO

O

VI =

CLK

V

GND to V

=

27 MHz

=

3.3 V

DD

DD

— mA–10 +10

155 mA— 190

CLK = 13.5 MHz

Power Supply Current (operating)

Power Supply Current (SLEEP) I

DDO2

DDS

SDA Output Voltage SDAV

SDA Output Current SDAI

=

3.3 V

V

DD

SLEEP ON 1 mA—5

L

O

——V0 0.4

——mA3—

125 mA— 160I

Max.

—

0.4

Unit

mA

*1: HSYNC_L, VSYNC_L, SYSSEL

*2: Y[7:0], C[7:0], HSY, HVALID, VVALID, ODD, CLKXO

*3: CLKX2O

*4: MODE[3:0], SLEEP, TEST1, TE

8/42

¡ Semiconductor MSM7661B

(

)

(

)

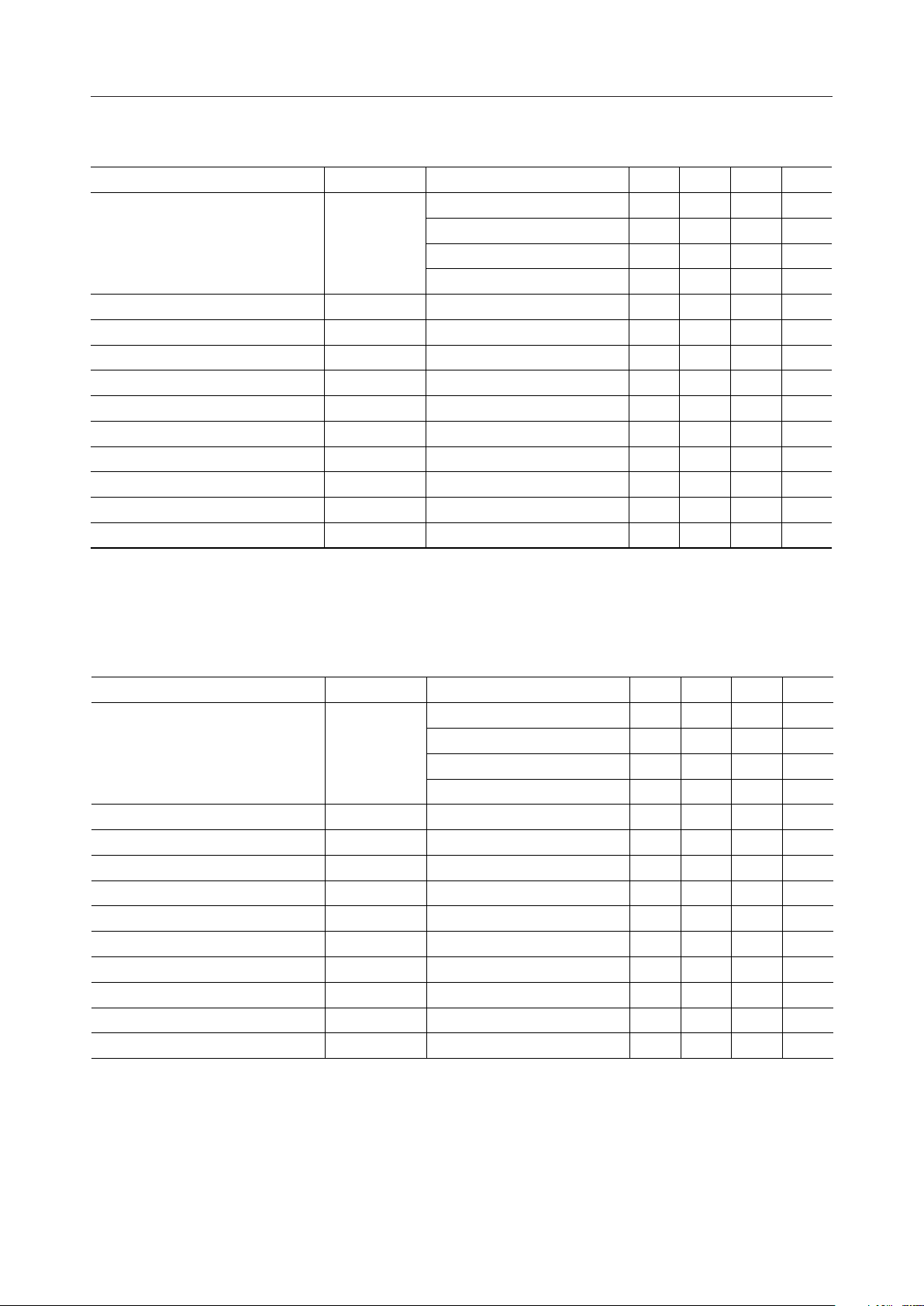

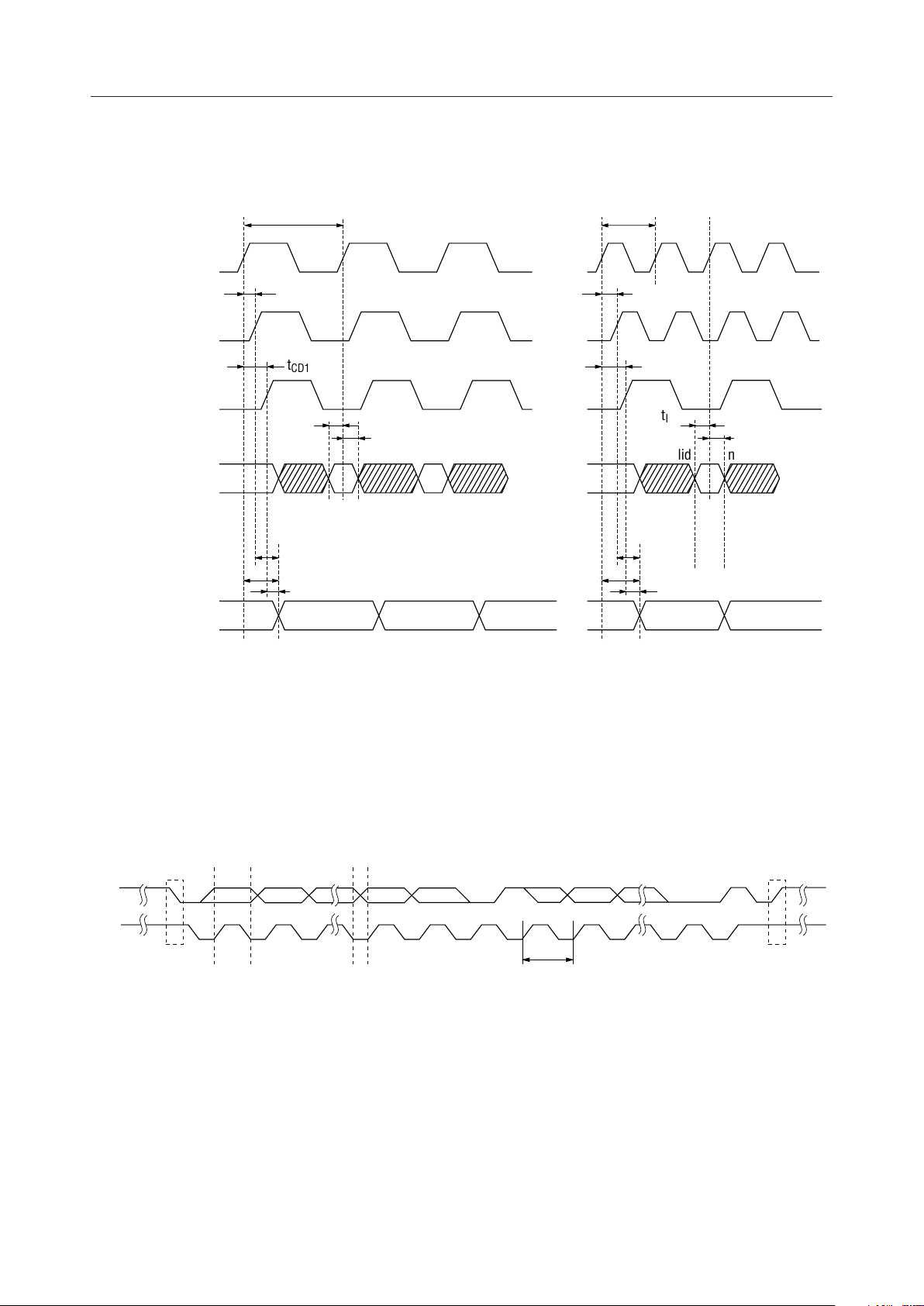

AC Characteristics (Single Speed Mode)

Parameter Symbol Condition Min. Typ. Max. Unit

CLKX2 Cycle Time t

CLKX2 Duty t

Input Data Setup Time t

Input Data Hold Time t

Output Data Delay Time 1 (*) t

Output Data Delay Time 2 (*) t

Output Data Delay Time 3 (*) t

Output Clock Delay Time (*) (External)

Output Clock Delay Time (*) (Internal)

SCL Clock Cycle Time t

Low Level Cycle t

CLKX1

D_D1

IS1

IH1

ODX1

OD2X1

OD1

t

CXD1

t

CD1

C_SCL

L_SCL

(Ta = 0 to 70°C, VDD = 3.3 V ±0.3 V)

ITU-R601 — 74.07 — ns

NTSC 4Fsc — 69.84 — ns

NTSC Square Pixel — 81.5 — ns

PAL Square Pixel — 67.8 — ns

— 40—60%

CLKSEL : H 0 — — ns

CLKSEL : H 30 — — ns

CLKSEL : H 2 — 8 ns

CLKSEL : H 2 — 7 ns

CLKSEL : H 9 — 25 ns

CLKSEL : H 7 — 17 ns

CLKSEL : H 7 — 18 ns

Rpull_up = 4.7 kW 200 — — ns

Rpull_up = 4.7 kW 100 — — ns

*output load 40 pF

AC Characteristics (Double Speed Mode)

Parameter Symbol Condition Min. Typ. Max. Unit

CLKX2 Cycle Time t

CLKX2 Duty t

Input Data Setup Time t

Input Data Hold Time t

Output Data Delay Time 1 (*) t

Output Data Delay Time 2 (*) t

Output Data Delay Time 3 (*) t

Output Clock Delay Time (*) (External)

Output Clock Delay Time (*) (Internal)

SCL Clock Cycle Time t

Low Level Cycle t

CLKX2

D_D2

IS2

IH2

ODX2

OD2X2

OD2

t

CXD2

t

CD2

C_SCL

L_SCL

(Ta = 0 to 70°C, VDD = 3.3 V ±0.3 V)

ITU-R601 — 37.05 — ns

NTSC 4Fsc — 34.9 — ns

NTSC Square Pixel — 40.75 — ns

PAL Square Pixel — 33.9 — ns

— 40—60%

CLKSEL : L 5 — — ns

CLKSEL : L 15 — — ns

CLKSEL : L 2 — 7 ns

CLKSEL : L 2 — 6 ns

CLKSEL : L 9 — 24 ns

CLKSEL : L 7 — 17 ns

CLKSEL : L 7 — 18 ns

Rpull_up = 4.7 kW 200 — — ns

Rpull_up = 4.7 kW 100 — — ns

*output load 40 pF

9/42

¡ Semiconductor MSM7661B

Input and Output Timing

CLKX2

CLKX2O

CLKXO

CVBS

CD

RESET_L

HSY,

HVALID, VVALID,

ODD, SYSSEL,

Y,C,

HSYNC_L,

VSYNC_L

t

OD1

CLKSEL:H

t

CLKX1

t

CXD1

t

CD1

t

IS1

t

IH1

not valid not valid

t

OD2X1

t

ODX1

t

OD2

CLKSEL:L

t

CLKX2

t

CXD2

t

CD2

t

IS2

not valid not valid

t

OD2X2

t

ODX2

t

IH2

I2C-bus Interface Input/Output Timing

The basic input/output timing of the I2C-bus interface is as follows.

SDA

SCL

S

Start Condition

Data Line Stable: Data Valid Change of Data Allowed

MSB

12 789

ACK

12

t

C_SCL

I2C-bus Basic Input/Output Timing

3-8

9

ACK

P

Stop Condition

10/42

¡ Semiconductor MSM7661B

BLOCK DESCRIPTION

1. Prologue Block

The prologue block performs Y/C separation by inputting data.

Data can be input either at ordinary pixel frequency (ITU-R : 13.5 MHz) or at double pixel

frequency (ITU-R: 27 MHz).

When the double pixel frequency is used, data is processed after changing to the ordinary pixel

frequency via a decimeter circuit.

By changing the register setting, the decimeter circuit can be bypassed irrespective of whether

data is input at ordinary pixel frequency or at double pixel frequency.

The prologue block performs Y/C separation using a 2-dimensional adaptive comb filter when

composite signals (CVBS) are input.

The following operation modes can be changed via the I2C-bus. The * mark indicates a default.

The default is a state that is selected when reset.

1) Video input mode select

Composite video input *

S video input

2) Video input mode select

Auto NTSC/PAL select* (Only for ITU-R601)

Dependent on Operation mode selected

When ITU-R601 is selected, the video input mode is automatically determined by the number

of lines per field.

3) Operation mode select

NTSC CCIR601 13.5 MHz*

MTSC Square Pixel 12.27 MHz

NTSC 4Fsc 14.31818 MHz

PAL CCIR601 13.5 MHz

PAL Square Pixel 14.75 MHz

4) Decimeter circuit pass/bypass select

Decimeter circuit is passed. *

Decimeter circuit is bypassed.

5) Y/C separation mode select

Adaptive comb filter is used. *

Unadaptive comb filter is used.

Trap filter is used.

The adaptive comb filter detects the correlation up to 3 lines between continuous lines. The Y/

C is separated by the comb filter according to the way of correlation if theses lines are correlated.

The Y/C is separated by the trap filter if these lines are not correlated (only 2 lines in the case of

PAL).

In the unadaptive comb filter, the Y/C is always separated by removing the luminance

component based on the average of preceding and following lines (when there is the correlation

between 3 lines).

11/42

¡ Semiconductor MSM7661B

If the comb filter is not used, the Y/C is separated by the trap filter.

The Y/C separation circuit is bypassed by S video signal input.

In adittion, the functions of this block work only when lines are valid as image information.

The processing of CVBS signals is not made during V-blanking.

2. Luminance Block

The luminance block removes synchronous signals from the signals containing luminance

components after Y/C separation. The signals are corrected and output as luminance signals.

The luminance signal output level gain control functions include three selectable modes such as

AGC (Auto Gain Control), MGC (manual Gain Control) + No Clamp, and MGC + Pedestal

Clamp.

In the AGC mode, the luminance level amplification is determined by comparing the depth of

SYNC with the reference value. The default is 40IRE which can be changed by the register. The

input is a sync chip clamp type.

In the MGC + No Clamp mode, the luminance signal output level is not affected by the input, and

the amplification and black level are controlled by setting the register.

In the MGC + Pedestal Clamp mode, the signal output level is clamped to the pedestal level of

the input. The signal amplification and black level are controllable from the clamped point by

setting the register.

This block can select the follwing operation modes.

1) Use of prefilter and sharp filter

Used*

Not used

These filters are used for enhancing the edges of luminance component signals.

2) Selection of aperture bandpass filter coefficient

Middle range*

High range

3) Coring range select

off*

±4LBS

±5LBS

±7LBS

4) Aperture weighting factor select

0*

0.25

0.75

1.5

The profile of these signals can be corrected by coring and aperture correction.

5) Use of pixel position correction circuit

Used*

Not used

6) AGC loop filter time constant select

Slow Factor value 1/1024n

12/42

¡ Semiconductor MSM7661B

Medium 1/64n*

Fast 1/n

Fixed 0

7) Parameter for AGC reference level fine adjustment

8) Parameter for sync separation level fine adjustment

The black level is controlled. When the default is specified, the depestal position is output as a

black level (=16).

9) Pedestral clamp selecton

Pedestral clamp is not used.*

Pedestral clamp is used. (AGC will not operate)

3. Chrominance Block

This is a chroma signal processing block.

The following modes can be selected.

1) Use of color bandpass filter

Used*

Not used

2) ACC loop filter time constant select

Slow Factor value 1/1024n

Medium 1/64n*

Fast 1/n

Fixed 0

3) ACC reference level fine adjustment

4) Parameter for burst level fine adjustment

The threshold level for valid chroma amplitude is selected based on a color burst ratio.

0.5

0.25*

0.125

off

5) Color killer mode select

Auto color killer mode*

Forcible color killer

6) Parameter for color subcarrier phase fine adjustment

In this block, chroma signals pass through the chroma bandpass filter to cut an unnecessary

band. To maintain a constant chroma level, UV demodulation is performed on these signals

via the ACC correction circuit. (This filter can be bypassed.)

If the demodulation result does not reach a specified level, color killer signals are generated

to fix the ACC gain. This functions as an auto color killer control circuit.

The UV demodulation result is output as chrominance signals via a low pass filter.

13/42

Loading...

Loading...