OKI MSM7564-01JS, MSM7564-01GS-K Datasheet

Preliminary

¡ Semiconductor MSM7564-01

¡ Semiconductor

MSM7564-01

A Single Chip 14.4 kbps Data & Fax Modem

GENERAL DESCRIPTION

The MSM 7564-01 is a highly integrated single-chip modem IC which provides the functions needed

to construct 14.4 kbps full-duplex and half-duplex modems. This device is compliant with the

following data communication formats : ITU-T Recommendation V.32bis, V.32, V.22bis, V.21 and

Bell standard Bell 212A and Bell103 modes, and facsimile communication formats : ITU-T

Recommendation V.17, V29, V.27ter, V.21 ch2.

This device contains fundamental functions : high speed DSP, analog front end, and digital logic

circuit. It also provides additional circuits such as test functions, synchronous-asynchronous

conversion circuit, DTMF generator/detector, programmable tone generator/detector, voice output

function and sleep mode. The MSM7564-01 is designed to provide a microprocessor peripheral to

interface with popular single-chip microprocessors for the control of modem functions through its

8-bit multiplexed address/data bus.

FEATURES

• Data mode : ITU-T Recommendation V.32bis, V.32, V.22bis, V.22, V.21

Bell standard Bell 212A, Bell103

• Fax mode : ITU-T Recommendation V.17, V.29, V.27ter, V.21 ch2

• Synchronous/Asynchronous conversion

• Scrambler/Descrambler

• DTMF, answer tone, and guard tone generator

• Programmable transmit attenuation (15 dB, 1 dB steps)

• Call progress, answer tone, DTMF, and carrier detector

• Receiving signal quality monitor

• Independent adaptive line equalization for transmit and receive

• Carrier detection level selectable (4 steps)

• Echo canceler

• Jitter canceler

• Programmable tone generator/detector

• Voice output function

• Test mode : Local analog loop (internal/external)

Remote digital loop

511PN pattern generator for error test

1:1 pattern generator for error test

Error counter

• Sleep mode

• Single +5 V DC supply

• CMOS technology for low power consumption

Operation mode : 500 mW Typ. @ +5 V

Sleep mode : < 10 mW @ +5 V

• Package options:

144-pin plastic TQFP (TQFP144-P-2020-K) (Product name : MSM7564-01GS-K)

84-pin plastic QFJ (QFJ84-P-S115) (Product name : MSM7564-01JS)

1

MSM7564-01 ¡ Semiconductor

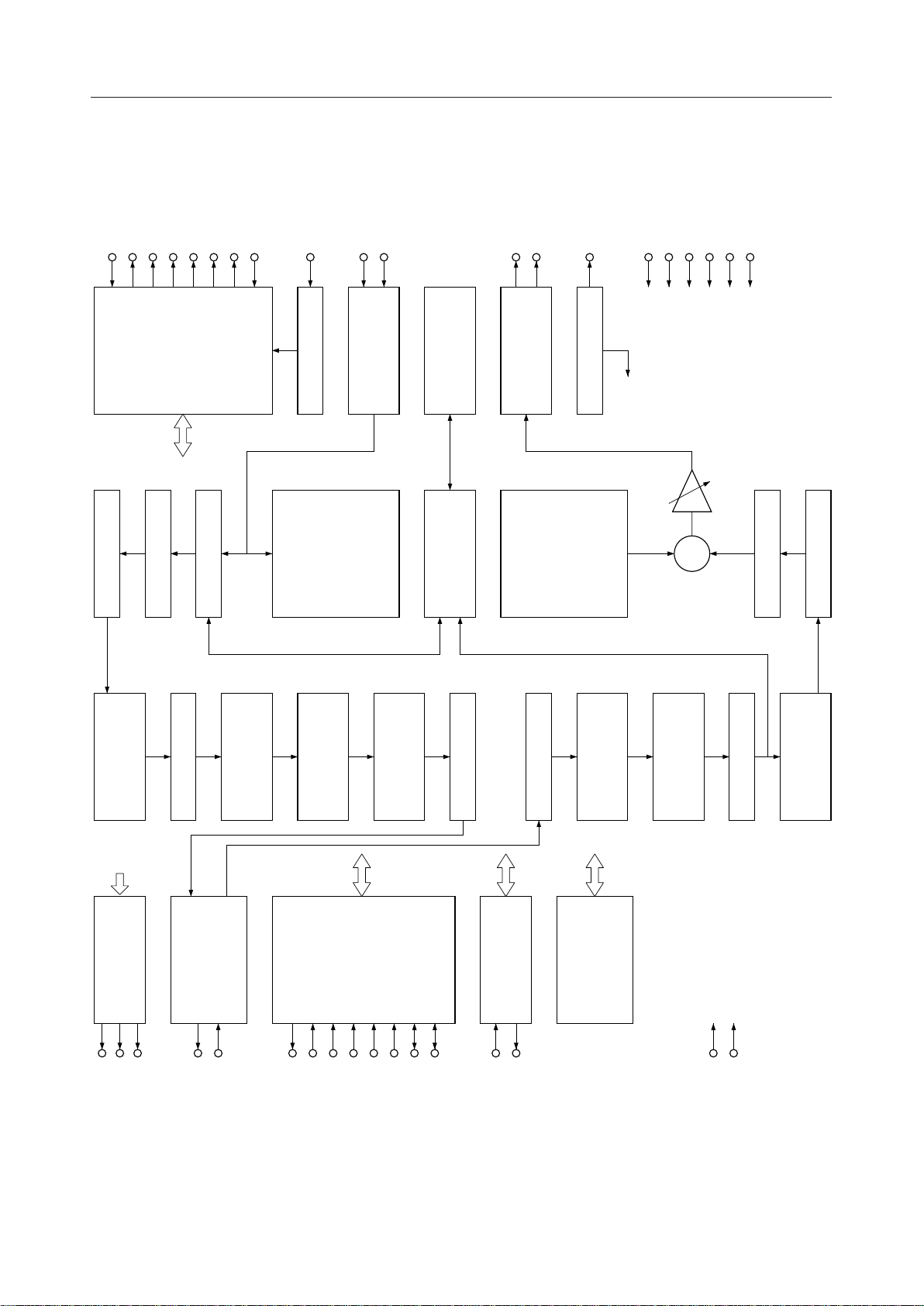

BLOCK DIAGRAM

1 - 5

A

ST1

ST2RTRBTM

SBTM

CPUCLK

GACLK

CKOEN

MCK

AINP

AINN

AOUTP

AOUTN

SG

DD

V

GND1 - 5

DD

V

P

DD

GNDA

V

GNDP

Clock

AGC

Demodulator

Filter

Roll Off

Generator

Filter

Equalizer

PLL

Carrier

Tone

Detector

PLL

(Answer)

Viterbi

Decorder

ADC

(DTMF)

(Calling)

(Program)

Decoder

Differential

Bulk

Delay RAM

Echo

Canceler

Descrambler

DAC

Tone

Generator

Scrambler

VREF

(DTMF)

(Guard)

(Answer)

Differential

(Program)

Encoder

+

Trellis

Encoder

Atten

Mapping

Filter

Modulator

Filter

Roll Off

2

Eye

XYCK

SOM

Monitor

SYCR

I/F

Serial

SRD

STD

STCHG

CPUTYPE

Parallel

CS0, 1

ALEWRRD

I/F

ADA7 - 0

AOD7 - 0

I/F

Test

TI0 - 9, BTD

TO0 - 13, BRD

Test

Circuit

V54 & V22

RST

SLEEP

¡ Semiconductor MSM7564-01

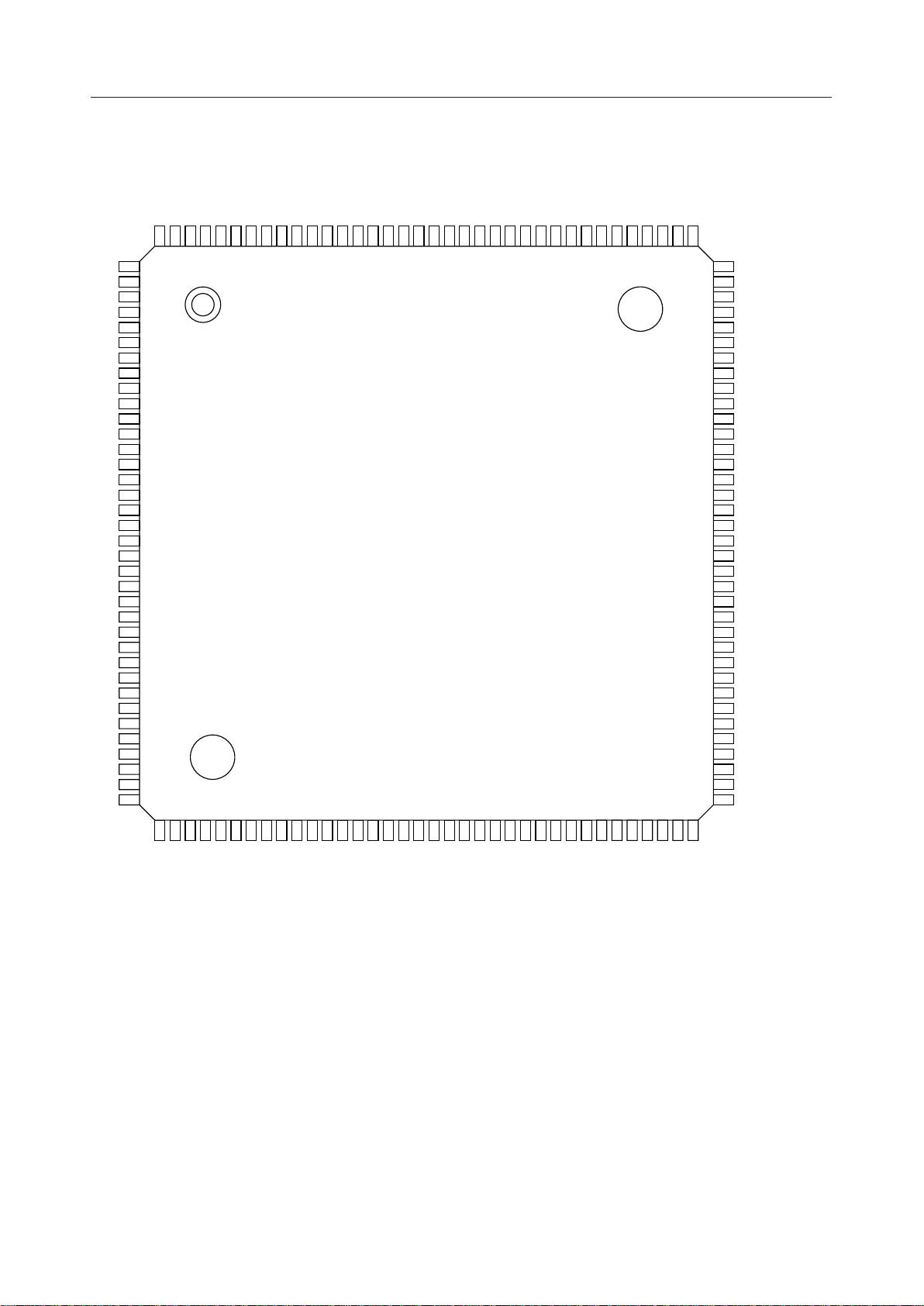

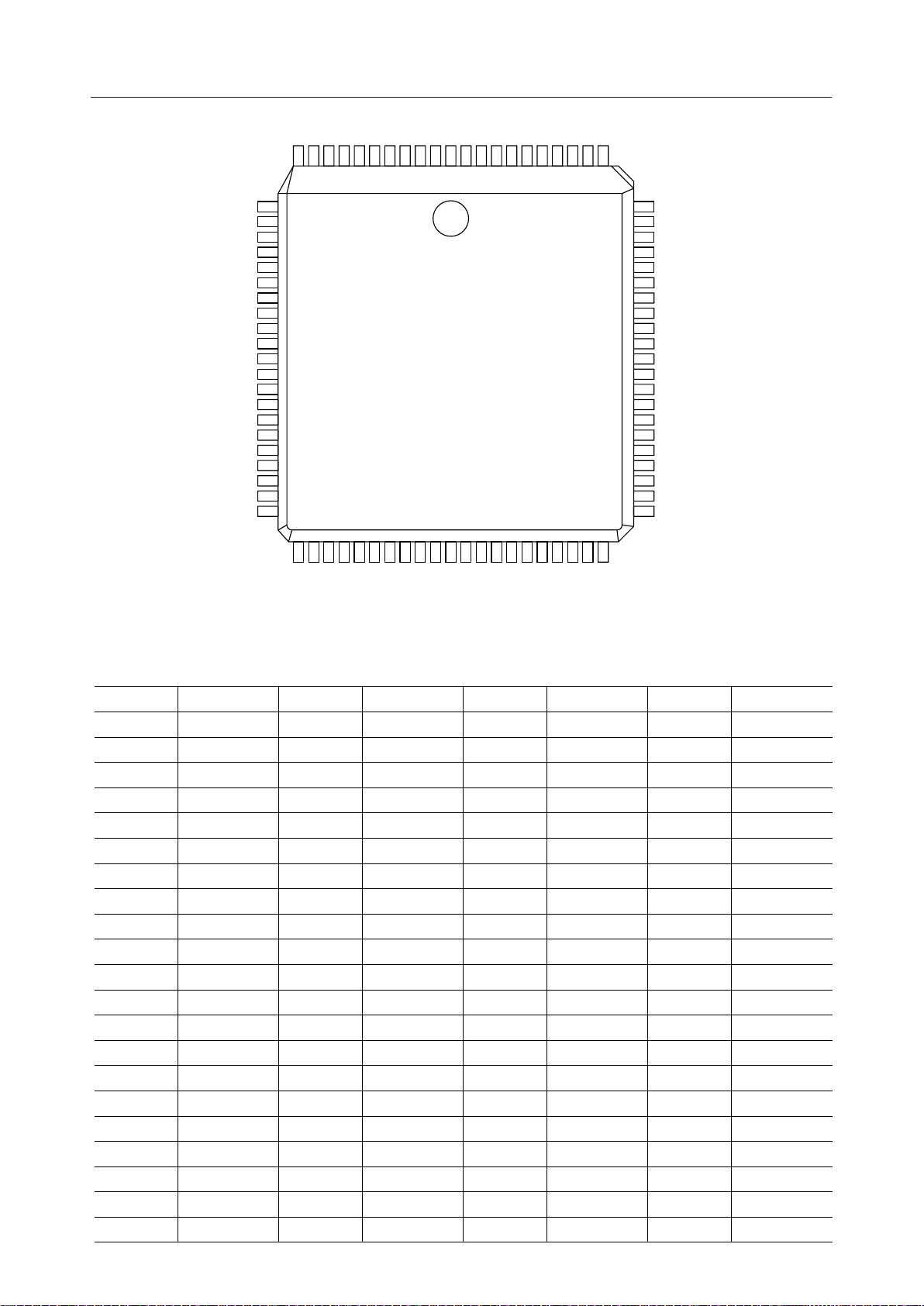

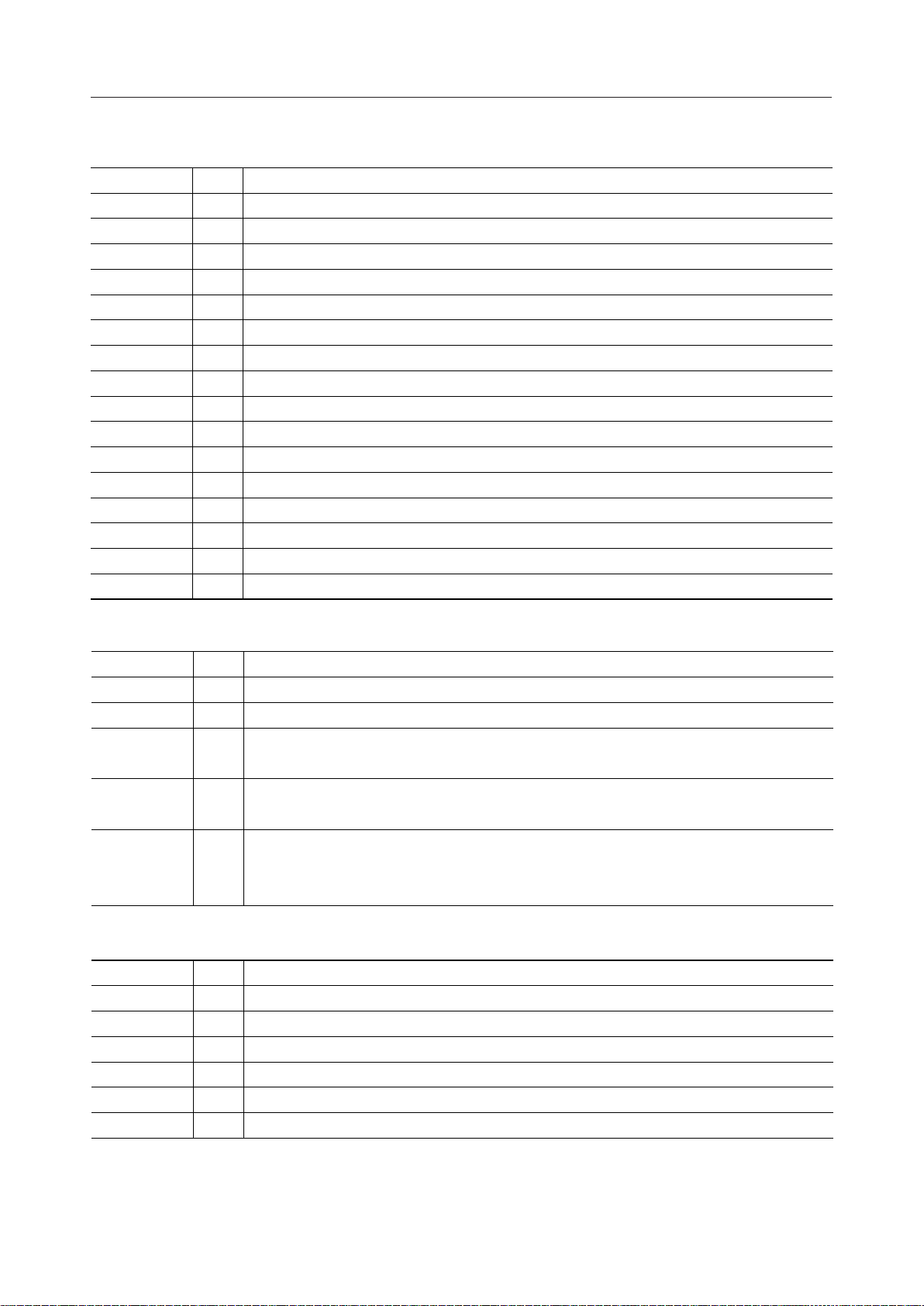

PIN CONFIGURATION (TOP VIEW)

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

108

107

106

105

104

103

102

101

100

99

98

97

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

3738394041424344454647484950515253545556575859606162636465666768697071

144-Pin Plastic TQFP

72

3

MSM7564-01 ¡ Semiconductor

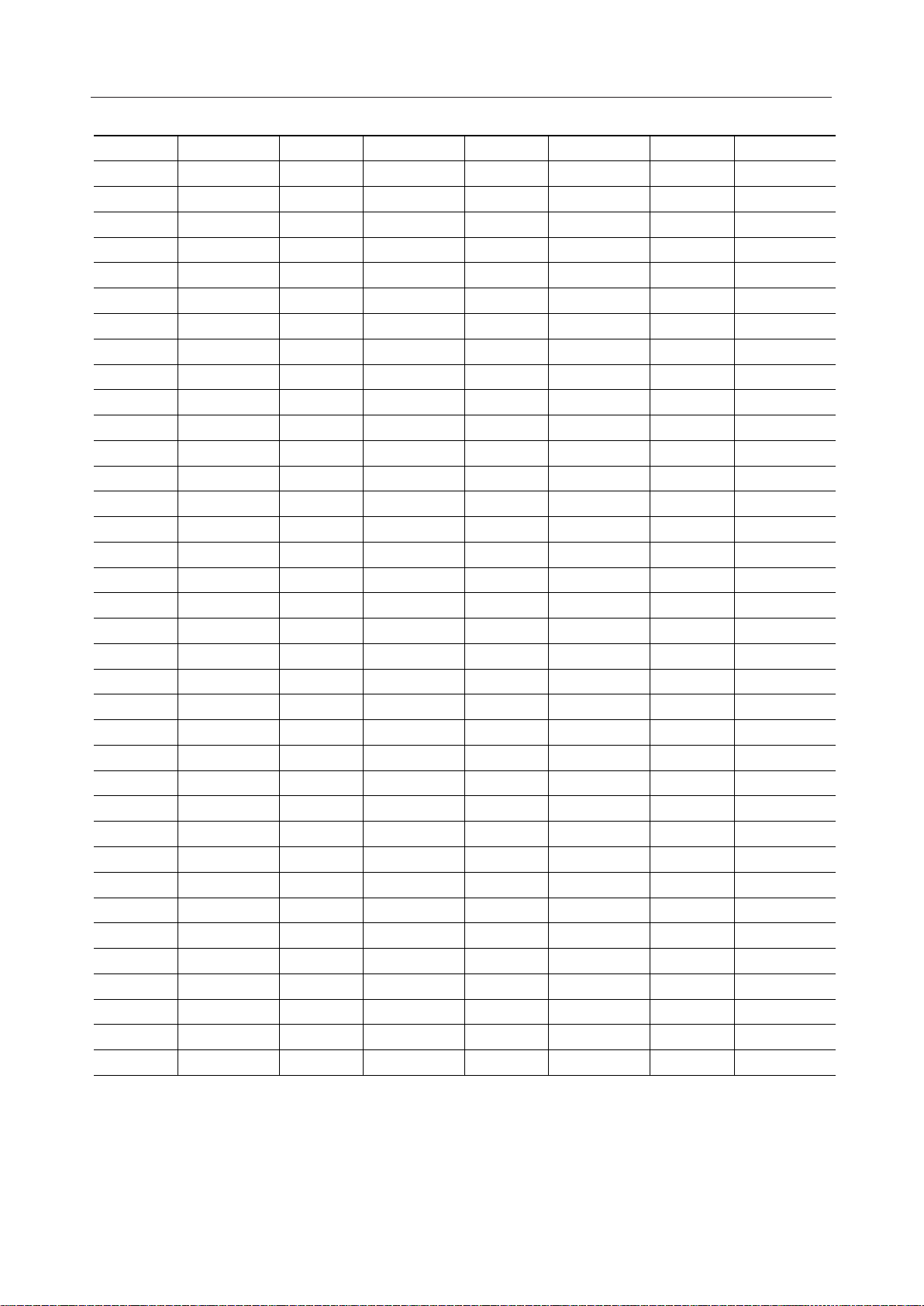

Pin Symbol

1 AINN

2NC

3 AINP

4 AOUTN

5NC

6NC

7 AOUTP

8V

DD

A

9 GND1

10 NC

11 TI2

12 NC

13 STD

14 NC

15 V

DD

1

16 NC

17 ST1

18 NC

19 WR

20 NC

21 BTD

22 NC

23 RD

24 NC

25 CS1

26 GND2

27 NC

28 RST

29 NC

30 CS0

31 NC

32 CKOEN

33 NC

34 SBTM

35 SLEEP

36 RBTM

Pin Symbol

37 NC

38 NC

39 TI4

40 TI3

41 NC

42 TI5

43 NC

44 TO4

45 NC

46 CPUTYPE

47 GND3

48 NC

49 BRD

50 ALE

51 NC

52 SOM

53 NC

54 V

DD

2

55 SYCR

56 NC

57 ST2

58 NC

59 XYCK

60 NC

61 SRD

62 STCHG

63 NC

64 TO2

65 NC

66 TO0

67 TO3

68 RT

69 NC

70 CPUCLK

71 GACLK

72 NC

Pin Symbol

73 TO1

74 ADA6

75 ADA4

76 ADA3

77 V

DD

3

78 NC

79 ADA2

80 NC

81 ADA0

82 NC

83 AOD7

84 NC

85 AOD6

86 NC

87 NC

88 AOD5

89 NC

90 GND4

91 NC

92 AOD4

93 NC

94 AOD3

95 NC

96 AOD2

97 NC

98 NC

99 AOD1

100 NC

101 V

DD

4

102 AOD0

103 ADA5

104 NC

105 NC

106 ADA1

107 ADA7

108 TI8

Pin Symbol

109 NC

110 TO10

111 TO6

112 NC

113 TO13

114 TO12

115 NC

116 TO11

117 TO7

118 NC

119 TO9

120 NC

121 TO8

122 NC

123 TI6

124 TI7

125 NC

126 V

DD

5

127 TI1

128 NC

129 TI0

130 NC

131 TI9

132 GND5

133 V

DD

P

134 MCK

135 NC

136 NC

137 TO5

138 GNDP

139 GNDA

140 NC

141 NC

142 NC

143 SG

144 NC

NC : No connect pin

4

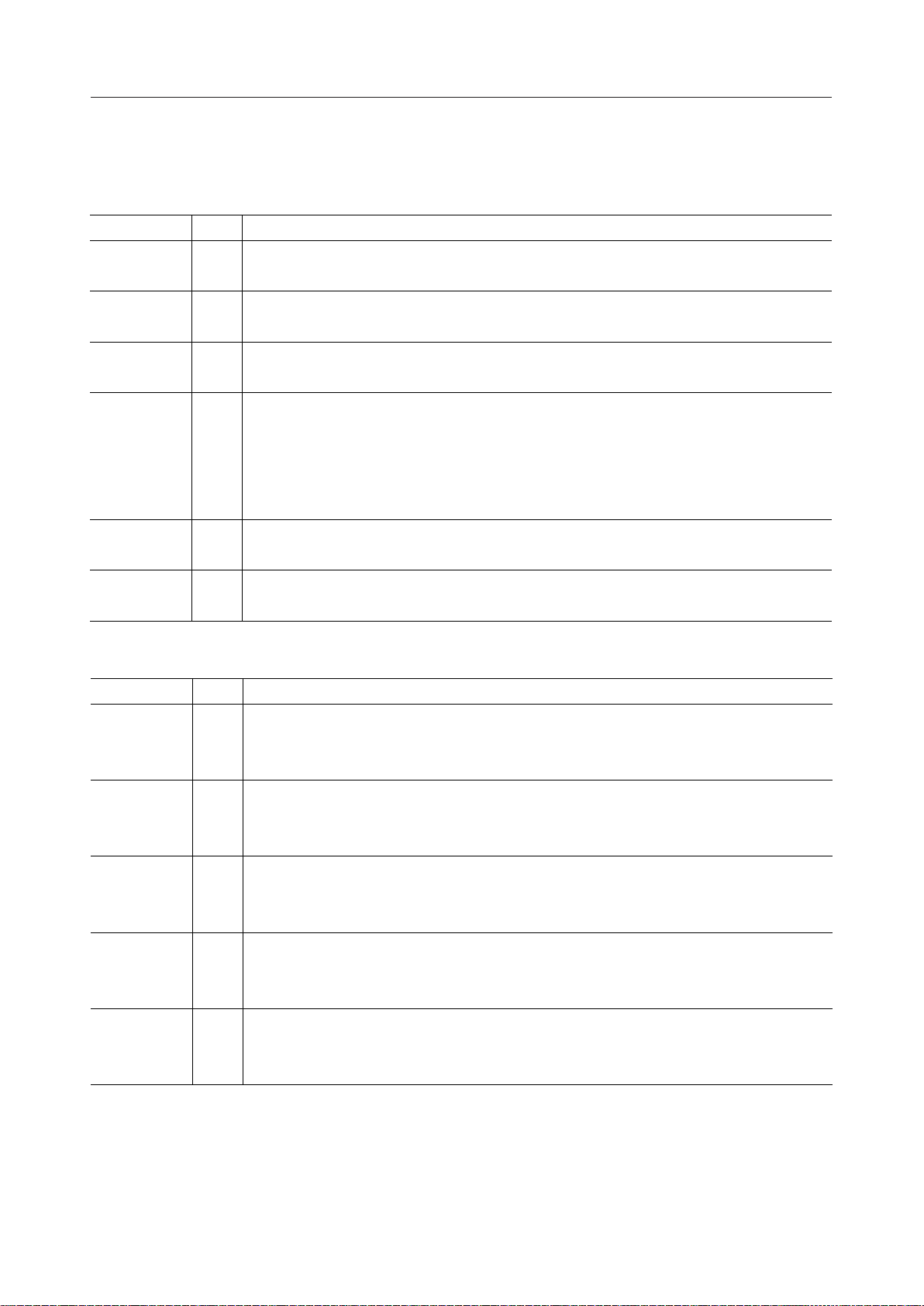

¡ Semiconductor MSM7564-01

987654321

11

10

848382818079787776

75

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

333435363738394041424344454647484950515253

84-Pin Plastic QFJ

74

73

72

71

70

69

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

Pin Symbol

1 GND4

2 AOD4

3 AOD3

4 AOD2

5 AOD1

6V

DD

4

7 AOD0

8ADA5

9ADA1

10 ADA7

11 TI8

12 TO10

13 TO6

14 TO13

15 TO12

16 TO11

17 TO7

18 TO9

19 TO8

20 TI6

21 TI7

Pin Symbol

22 V

DD

5

23 TI1

24 TI0

25 TI9

26 GND5

27 V

DD

P

28 MCK

29 TO5

30 GNDP

31 GNDA

32 SG

33 AINN

34 AINP

35 AOUTN

36 AOUTP

37 V

DD

A

38 GND1

39 TI2

40 STD

41 V

DD

1

42 ST1

Pin Symbol

43 WR

44 BTD

45 RD

46 CS1

47 GND2

48 RST

49 CS0

50 CKOEN

51 SBTM

52 SLEEP

53 RBTM

54 TI4

55 TI3

56 TI5

57 TO4

58 CPUTYPE

59 GND3

60 BRD

61 ALE

62 SOM

63 V

DD

2

Pin Symbol

64 SYCR

65 ST2

66 XYCK

67 SRD

68 STCHG

69 TO2

70 TO0

71 TO3

72 RT

73 CPUCLK

74 GACLK

75 TO1

76 ADA6

77 ADA4

78 ADA3

79 V

DD

3

80 ADA2

81 ADA0

82 AOD7

83 AOD6

84 AOD5

5

MSM7564-01 ¡ Semiconductor

PIN DESCRIPTIONS

System and Clock

Symbol

MCK

RST

SLEEP

CKOEN

CPUCLK

GACLK

Type

I

I

I

I

O

O

Master Clock Input

Frequency of 3.888 MHz ±100 ppm, with a duty ratio of between 45 and 55%.

Reset Input

'0' : reset state, '1' : normal operation

Sleep Input

'0' : sleep state, '1' : normal operation

Clock Output Enable

'0' : CPUCLK and GACLK pins are enabled to output.

(Internal PLL operates normally in sleep state.)

'1' : CPUCLK and GACLK pins are disabled to output.

(Internal PLL turns to be power down in sleep state.)

CPU Clock Output

CPUCLK outputs a 15.552 MHz clock for external CPU.

Gate Array Clock Output

GACLK outputs a 13.824 MHz clock for external gate array.

Modem Digital Interface

Description

Symbol

ST1

ST2

RT

STD

SRD

Type

I

O

O

I

O

Description

External Transmit Clock Input

An external transmit clock provided to input to ST1. The clock frequency of 300 to

14400 Hz is supplied by the local DTE.

Internal Transmit Clock Output

ST2 outputs the transmitting data clock of between 300 and 14400 Hz selected by

modem mode.

Internal Receive Clock Output

RT outputs the receiving data clock of between 300 and 14400 Hz selected by modem

mode.

Transmit Data Serial Input

STD inputs the transmit serial data synchronized with either internal timing selected by

modem mode or ST1 / ST2.

Received Data Serial Output

SRD outputs the received serial data synchronized with either internal timing selected

by modem mode or RT.

6

¡ Semiconductor MSM7564-01

CPU Interfaces

Symbol

CPUTYPE

STCHG

CS0, 1

ALE

RD

WR I

ADA7 - 0 I/O

AOD7 - 0 I/O

Type

O

CPU Type Select

I

CPUTYPE selects CPU bus type of ADA7 - 0 and AOD7 - 0.

'1' : 80 mode (multiplexed address and data bus for Intel-compatible)

'0' : 68 mode (separated address and data bus for Motorola-compatible)

Status Change Output

When interface memory registers (0C, 0D, 1E, 1F) change, STCHG is set to "0". When

the registers are read by external CPU, this pin is set to '1'.

Chip Select Input 0 and 1

I

When CS0 and CS1 are set to '1', this chip is selected for microprocessor operation.

Address Latch Enable Input

I

ALE allows the microprocessor to latch the address bus (ADA7 - 0) when CPUTYPE is

80 mode. Address bus is latched at the falling edge of ALE.

Read Enable

I

RD is active LOW and is used to read from internal memory register via 8-bit address

data input/output pins selected by CPUTYPE pin. CS0 and CS1 must be high.

Write Enable

WR is active Low and is used to write the data at the rising edge via data input/output

pins selected by CPUTYPE pin into internal memory registers. CS0 and CS1 must be

high.

8 bit Address and Data Bus 1

8 lines provide 2 modes of bus type which are selected by CPUTYPE pin. AD7 to 0 are

controlled by ALE, RD and WR.

80 mode : (I/O) address input and data input/output

68 mode : (I) address input

8 bit Address and Data Bus 2

8 lines provide 2 modes of bus type which are selected by CPUTYPE pin. AD7 to 0 are

controlled by ALE, RD and WR.

80 mode : (O) address output (outputs latched address by ALE)

68 mode : (I/O) address input/output

Description

7

MSM7564-01 ¡ Semiconductor

Other Interfaces

Symbol

RBTM

SBTM

SOM

XYCK

SYCR O

Type

Receive Baud Rate Timing Clock Output

O

RBTM outputs receive baud rate timing clock of between 600 and 2400 Hz selected by

modem mode.

Transmit Baud Rate Timing Clock Output

O

RBTM outputs transmit baud rate timing clock of between 600 and 2400 Hz selected

by modem mode.

Serial Eye Pattern X/Y Output

O

SOM outputs serial pattern containing two 16 bit words (X, Y references), synchronized

with the falling edge of XYCK.

Serial Eye Pattern Clock Output

O

XYCK outputs a 1152 Hz clock for SOM timing.

Serial Eye Pattern Timing Output

SYCR outputs synchronous timing for SOM output.

SYCR outputs two clocks of SOM clocks.

Description

8

¡ Semiconductor MSM7564-01

Test Interface

Symbol Type Description

TI0 I TEST PIN. Connect to ground.

TI1 I TEST PIN. Connect to ground.

TI2 - 4 I TEST PIN. Connect to ground.

TI5, 6 I TEST PIN. Connect to ground.

TI7 I TEST PIN. Connect to ground.

TI8 I TEST PIN. Connect to ground.

TI9 I TEST PIN. Connect to V

BTD I TEST PIN. Connect to V

TO0 I/O TEST PIN. Leave "OPEN".

TO1 I/O TEST PIN. Leave "OPEN".

TO2 I/O TEST PIN. Leave "OPEN".

TO3 I/O TEST PIN. Connect to ground.

TO4 I/O TEST PIN. Leave "OPEN".

TO5 O TEST PIN. Leave "OPEN".

TO6 - 13 I/O TEST PIN. Leave "OPEN".

BRD O TEST PIN. Leave "OPEN".

DD

DD

.

.

Analog Interface

Symbol

AINP

AINN

AOUTP

AOUTN

SG

Type

O

O

O

Power Supply

Symbol

1 - 5

V

DD

GND1 - 5

P

V

DD

GNDP

V

A

DD

GNDA

Type

Description

I

Analog Input (positive)

I

Analog Input (negative)

Analog Output (positive)

AOUTP is in high impedance state when CKOEN is '1' state and in sleep mode.

Analog Output (negative)

AOUTN is in high impedance state when CKOEN is in '1' state and in sleep mode.

Signal Ground for Analog

The SG level is about +2.4 V. Connect bypass capacitor between SG and GNDA when

CKOEN is in '1' state and in sleep mode.

Description

DD

DD

.

DD

.

.

I

Digital V

Digital Ground.

I

PLL V

I

PLL Ground.

I

Analog V

I

I

Analog Ground.

9

Loading...

Loading...