Page 1

¡

OKIPAGE4w

LED Page Printer

Troubleshooting Manual

with Component Parts List

(ODA/OEL/INT)

1997.12.10 Rev. 2

All specifications are subject to change without notice.

Page 2

CONTENTS

1. OUTLINE..................................................................................................... 1

2. TOOLS........................................................................................................ 1

3. CIRCUIT DESCRIPTION............................................................................ 2

4. TROUBLESHOOTING.............................................................................. 21

5. CIRCUIT DIAGRAM.................................................................................. 27

6. COMPONENT PARTS LIST

Page 3

1. OUTLINE

This manual has been written to provide guidance for troubleshooting of the OKIPAGE4w Printer

(primarily for its printed circuit boards), on an assumption that the reader is knowledgeable of the

printer. Read the maintenance manual for this printer P/N M-521426 if necessary.

Note:

1. High voltage power supply board and power supply unit containing a high voltage power

supply is dangerous. From the viewpoint of the safety standards, the local repairing of a

defective board is not allowed. Thus, the objects to be locally repaired as a result of

troubleshooting are switches and fuses.

2. TOOLS

For troubleshooting the printer, the tools listed below may be needed in addition to general

maintenance tools.

Oscilloscope Frequency response 100 MHz or higher

Soldering iron A slender tip type, 15-20 watts

Ectension code kit P/N : 40105501

Tool Remarks

- 1 -

Page 4

3. CIRCUIT DESCRIPTION

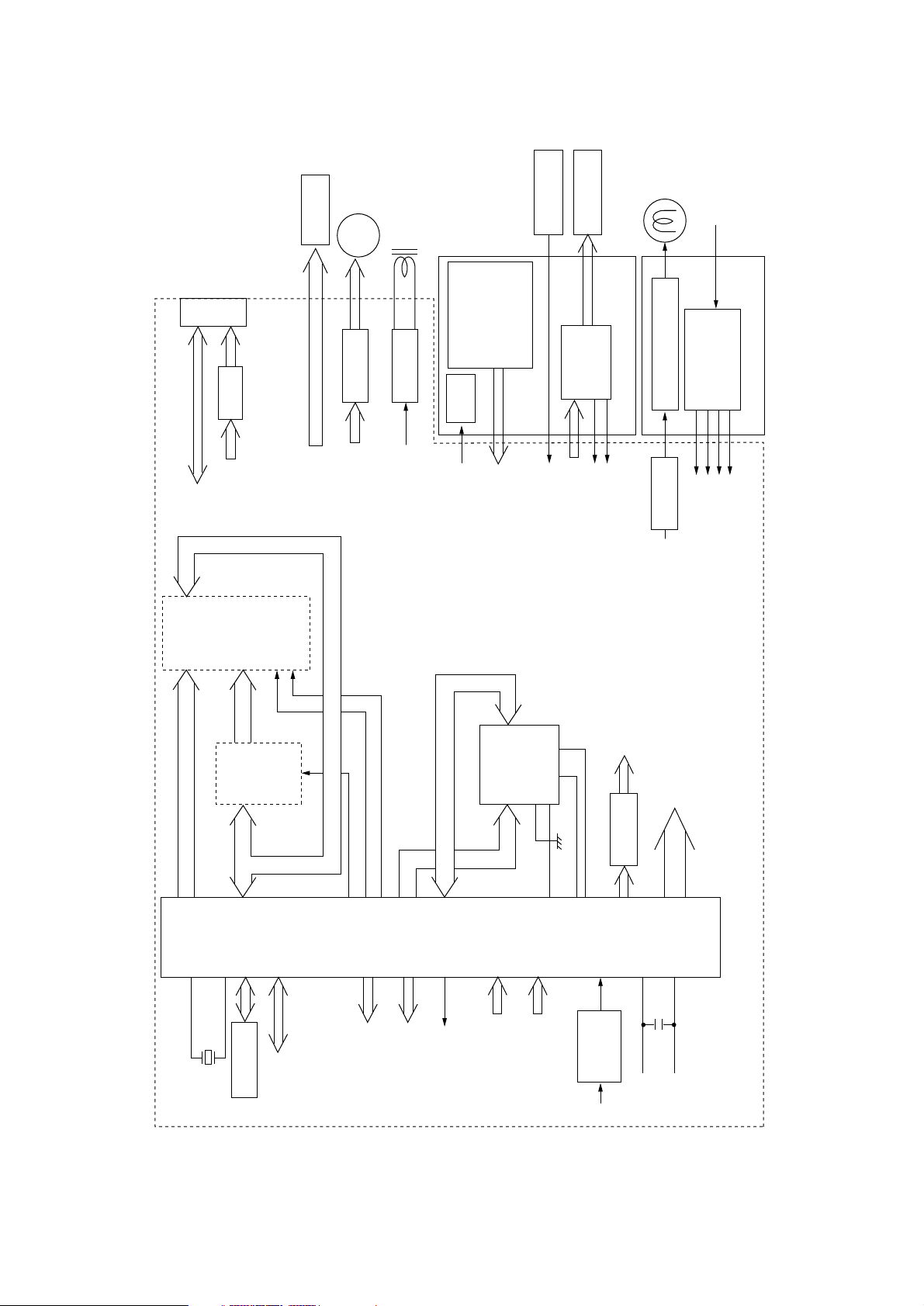

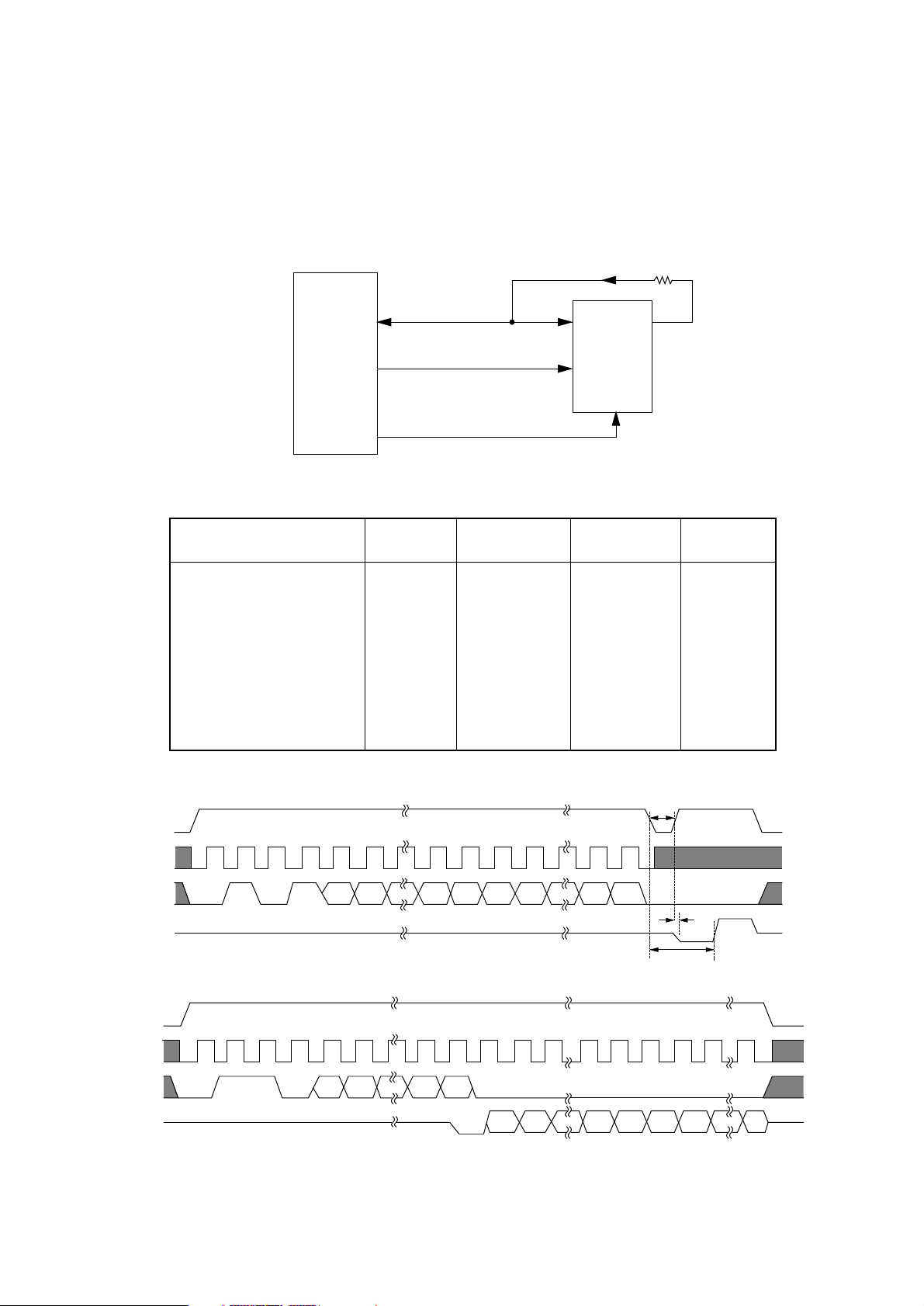

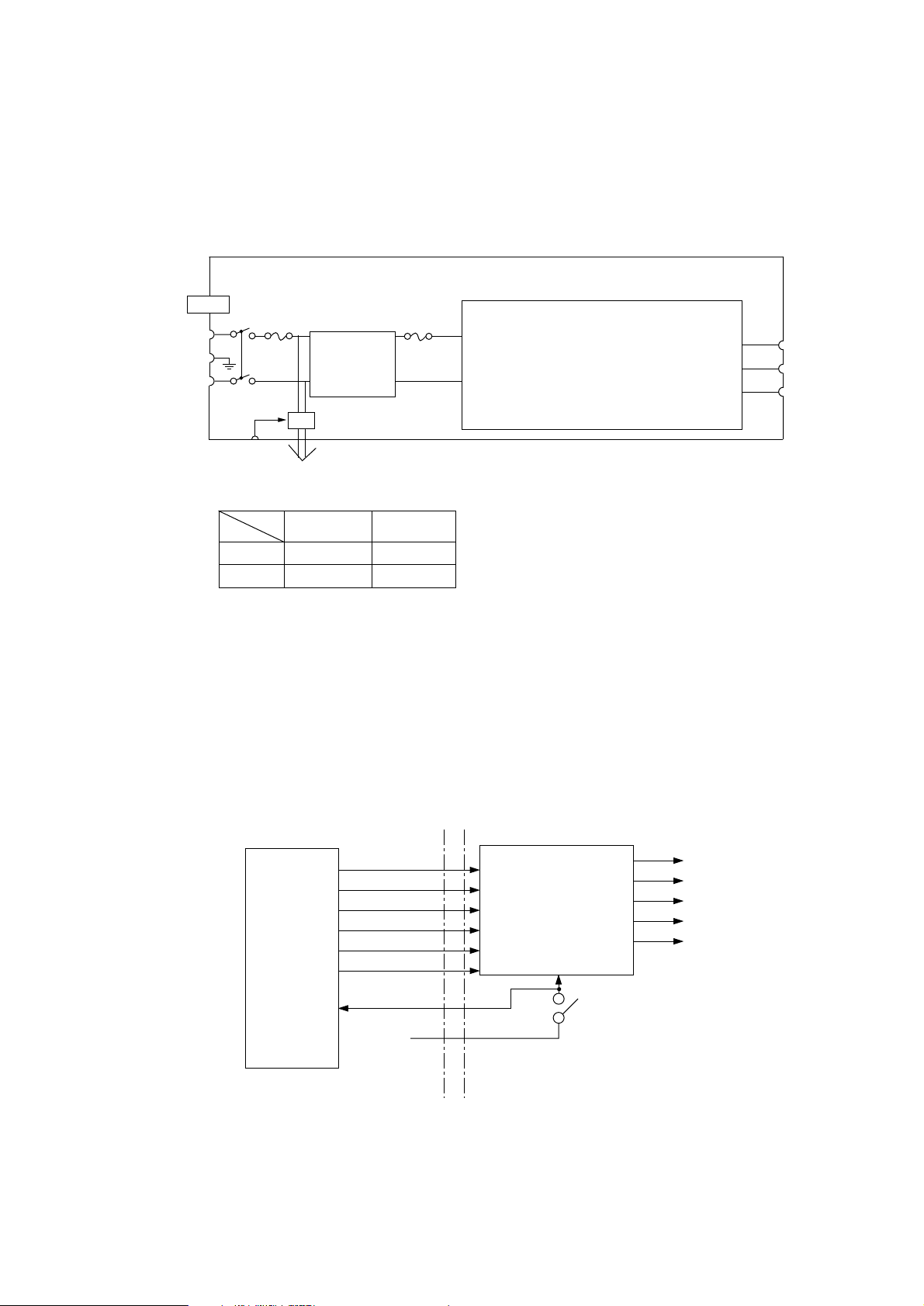

3.1 Outline

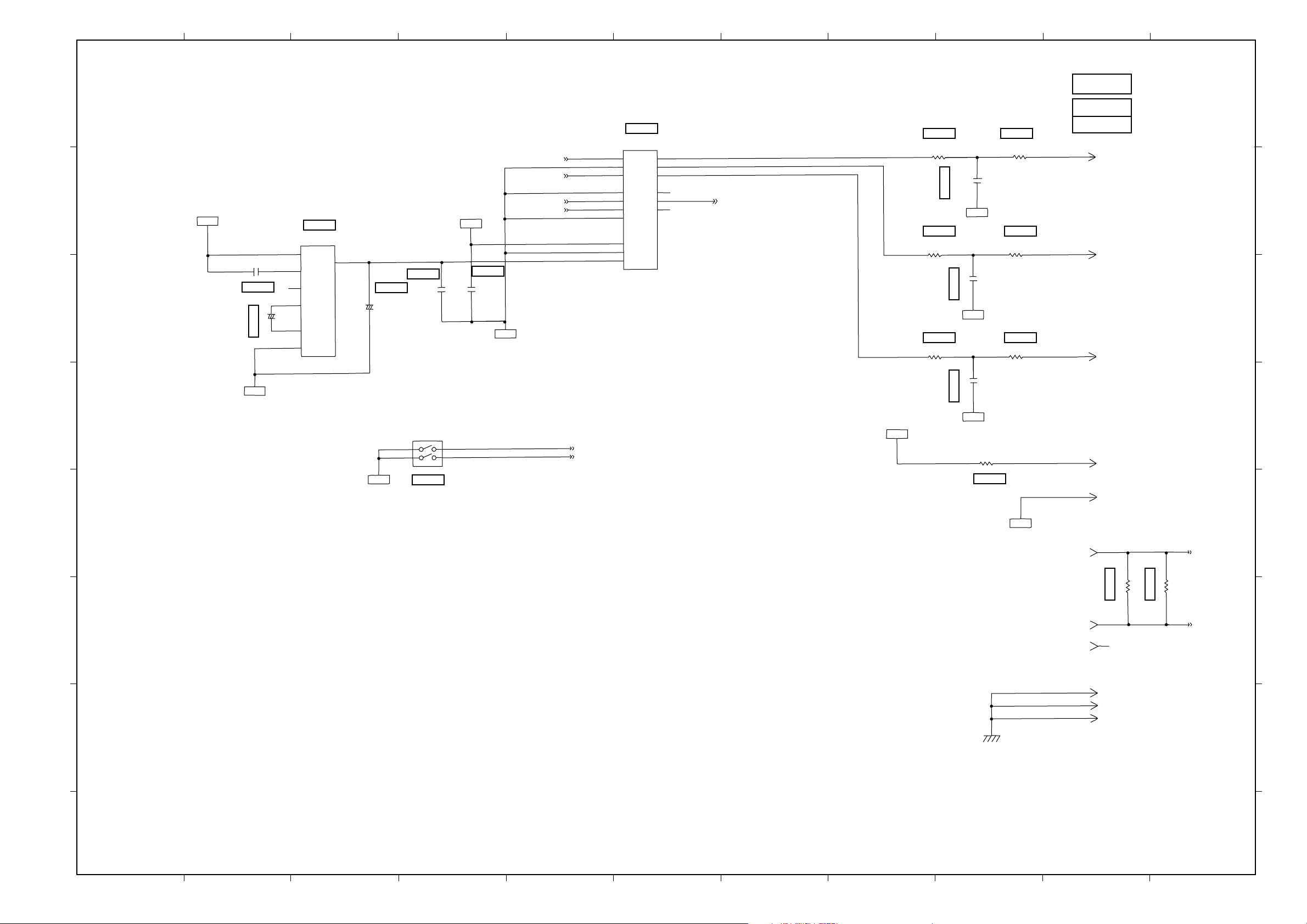

The circuit of OKIPAGE4w consists of a main control board, a high voltage power supply board

and a power supply unit. The block diagram is shown in Fig. 3-1. The main control board controls

the reception and transmission of data with a host I/f and processes command analysis, bit image

development, raster buffer read. It also controls the engine and high voltage outputs.

(1) Reception and transmission control

The main control board has one parallel I/F port which is compliant to the IEEE 1284

specification.

An interface task stores all data received from the host into a receive buffer first, and returns

the printer status upon request of the host.

(2) Command analysis processing

The OKIPAGE4w printer has the following emulation mode.

Hiper-W: OKI original

An edit task fetches data from the receive buffer, analizes commands, and sets I/O registers.

(3) Raster data processing

The decompression circuit in the CPU expands the compressed data and stores the data into

the raster buffer.

(4) Raster data transfer

The LED head control circuit in the CPU sends the data stored in the raster buffer to the LED

head.

(5) High voltage control

The high voltage control circuit in the CPU.

The high voltage power supply board generates high voltage outputs, and have sensors, LED for

display.

The power supply unit generates +24VDC output, +5DC output.

- 2 -

Page 5

CN

I/F

Parallel

LS07

Main motor

M

Electromagnetic

Driver

Driver

clutch

Manual feed sensor

Paper sensor

Outlet sensor

Toner sensor

Cover open switch

LED

Thermistor

EP cartridge

power

HIgh voltage

Heater

(Halogen lamp)

AC

(120 V/230 V)

supply

<High-voltage Power Supply Board>

Switching

AC output ON/OFF

power supply

<Power Supply Unit>

I/F

Parallel

D0 ~ D7

EPROM

(64 KByte)

A8 ~ A15

A0 ~ A7

latch

Address

AD0 ~ AD7

LED head LED head

Main motor

Electromagnetic

clutch

LED

D0 ~ D3

Sensors

D-RAM

(128 KByte)

A0 ~ A10

TEMP

power

High-voltage

TR-ISEN

TR-VSEN

Driver

HEAT ON

High-voltage power I/F

LED

Driver

+5V

0VL

0VP

+24V

<Main Control Board>

HEAT ON

10MHz

CPU

(MSM65917)

EEPROM

I/F

Parallel

LED head

clutch

Main motor

Electromagnetic

Sensors

Figure 3-1 OKIPAGE4w Block Diagram

- 3 -

TEMP

TR-VSEN

TR-ISEN

Reset

circuit

5V

5V

0VL

Page 6

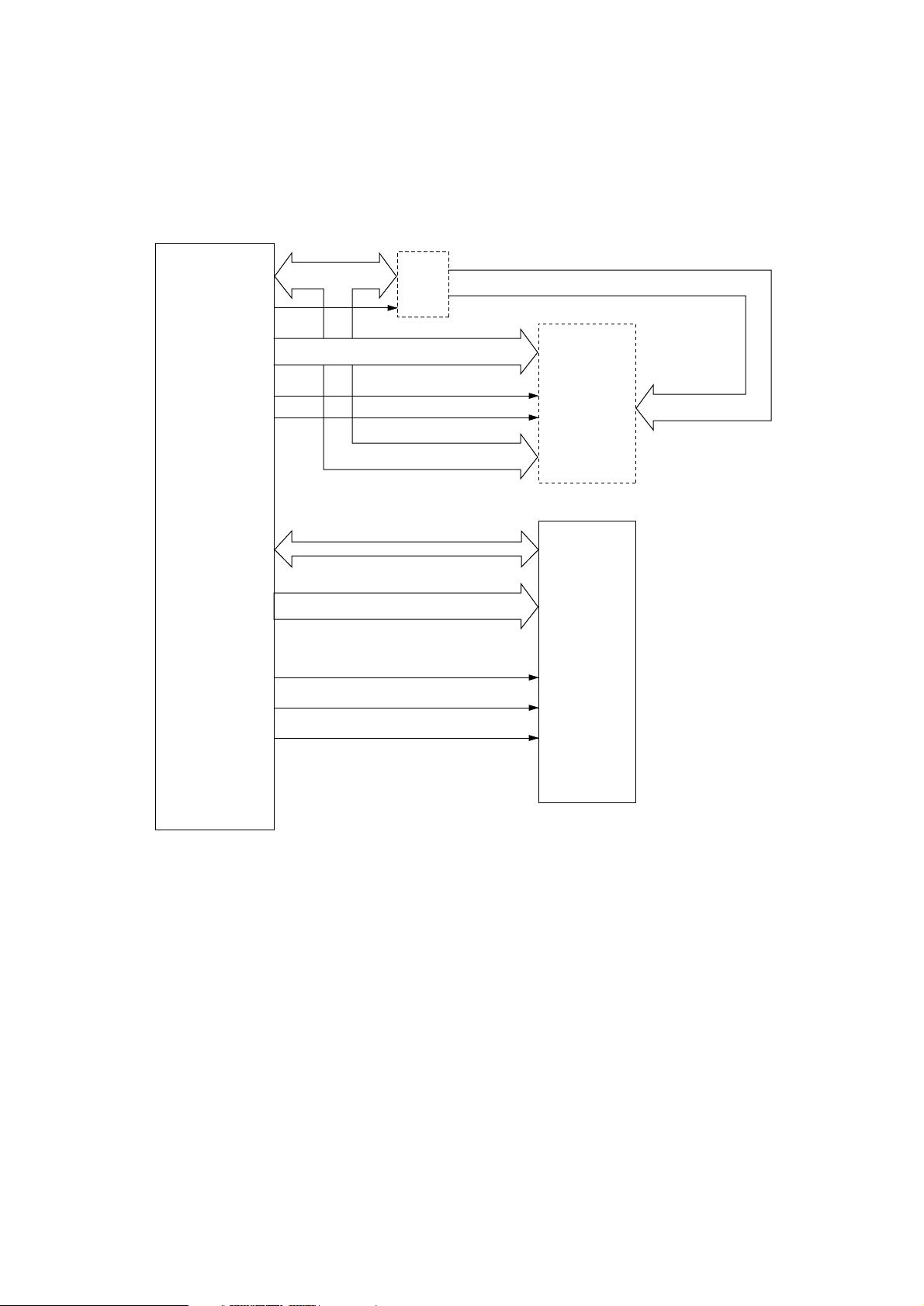

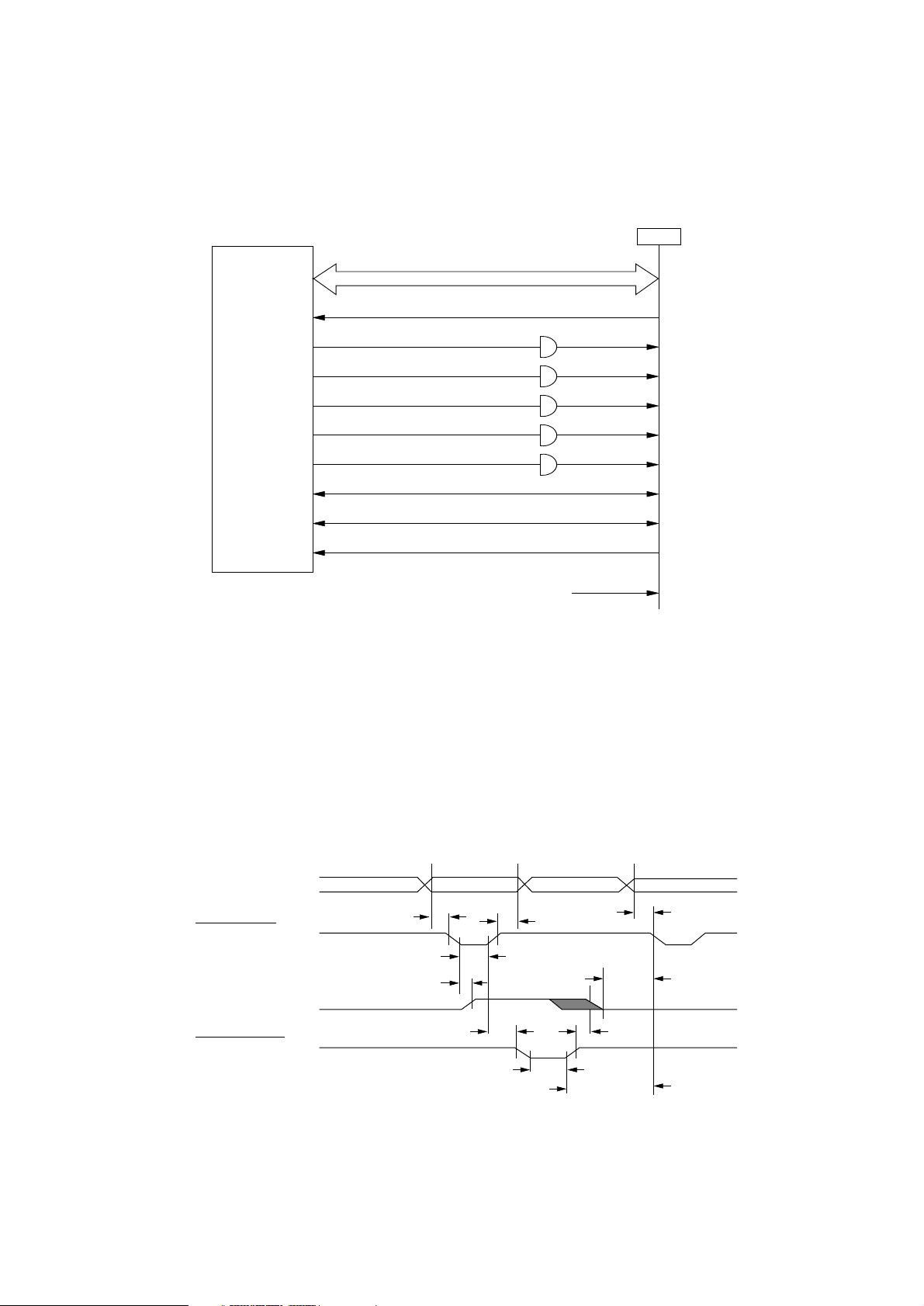

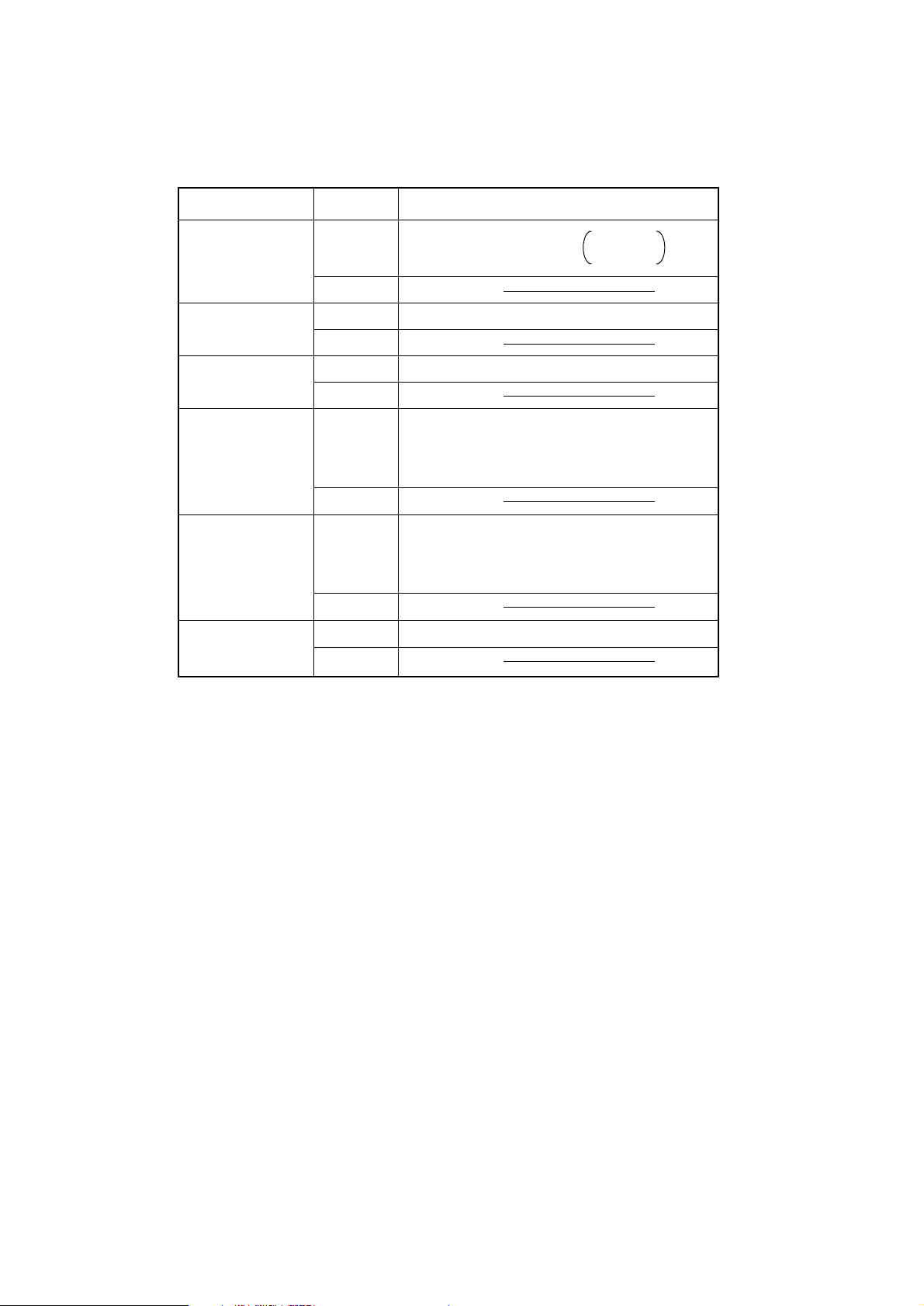

3.2 CPU and Memory

(1) CPU (MSM65917)

CPU core nX-8

CPU clock 10 MHz

Data bus width External 8 bits, Internal 8 bits

(2) Program ROM

ROM capacity 64k-bytes (512-kbit EPROM)

ROM type 512 kbits (64k x 8 bits)

Access time 150 nsec

When mask ROM in the CPU is valid, the EPROM is not mounted.

(3) Resident RAM

RAM capacity 128k bytes (256k x 4 bits D-RAM one piece)

RAM type 1M bits (256k x 4 bits)

Access time 70 ns

The block diagram of CPU and memory circuit is shown in Fig. 3-2.

- 4 -

Page 7

CPU

IC 6

ALE

RDN

ROCS

DA10

DWR

CAS

AD00 to AD07

LS373

IC3

A08 to A15

DD00 to DD03

DA00 to DA09

A00 to A07

IC2

EPROM

(64k x 8 bits)

IC11

DRAM

(256k x 4 bits)

RAS0

RAS1

RAS2

Main Control Board

Figure 3-2 Block Diagram of CPU & Memory in OKIPAGE4w

- 5 -

Page 8

3.3 Reset Control

When power is turned on, RST-N signal is generated by IC5.

+5V+5V

+5V

Power ON

IC5

1

3

2

Power OFF

63

CPU

RSTN

RST-N

- 6 -

Page 9

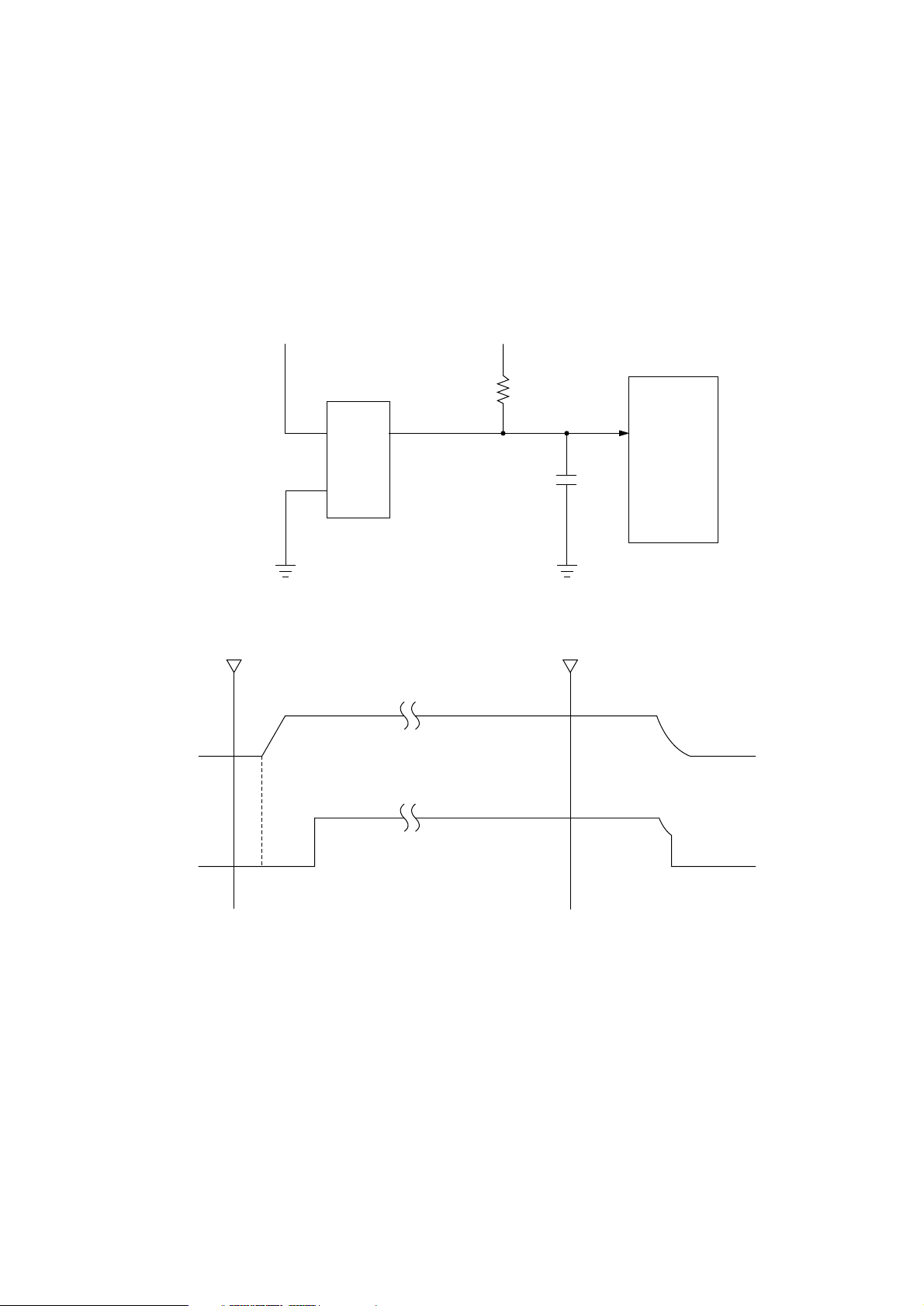

3.4 EEPROM Control

The BR93LC46A on the main control board is an electrical erasable/programmable ROM of 64bit x 16-bit configuration. Data input to and output from the ROM are bidirectionally transferred

in units of 16 bits through I/O port (EEPRMDT-P) in serial transmission synchronized with a clock

signal from the CPU.

The EEPROM operates in the following instruction modes.

Instruction Start bit Operation Address Data

Read (READ) 1 10 A5 to A0

Write Enabled (WEN) 1 00 11XXXX

Write (WRITE) 1 01 A5 to A0 D15 to D0

CPU

39

38

37

EEPRMDT-P

EEPRMCS-P

EEPRMCLK-P

code

3

DI DO

EEPROM

1

CS

IC4

4

SK

2

Write All Address (WRAL) 1 00 01XXXX D15 to D0

Write Disabled (WDS) 1 00 00XXXX

Erase 1 11 A5 to A0

Chip Erasable (ERAL) 1 00 10XXXX

Write cycle timing (WRITE)

Min. 450 ns

CS

SK

DI

DO

1 2 4 9 10 25

10 1

HIGH-Z

A5 A4 A1 A0 D15

D14

D1 D0

Max. 10 ms

Read cycle timing (READ)

CS

SK

DI

12

110

4

A5 A4 A1 A0

910

25 26

STATUS

Max. 500 ns

BUSY READY

DO

HIGH-Z

D15 D14 D1 D00 D15 D14

- 7 -

Page 10

3.5 Parallel Interface

Parallel data is received from a host system via parallel interface which is compliant to the

IEEE1284 specification.

CPU

65 to 68, 71 to 74

64

78

77

79

80

81

82

83

84

PDATA1-P to PDATA8-P

PSTB-N

BUSY-P

ACK-N

PE-P

SEL-P

FAULT-N

IPRIME-N

SELIN-N

AUTOFD-N

IC7

2 to 9

CN4

DATA8-P

to

DATA1-P

STB-N

1

10

12

13

32

31

36

14

BUSY-P

ACK-N

PE-P

SEL-P

FAULT-N

IPRIME-N

SELIN-N

AUTOFEED-N

11

+5V

+5V

18

Compatible mode

The CPU sets a BUSY-P signal to ON at the same time when it reads the parallel data (PDATA1P to PDATA 8-P) from the parallel port at the fall of PSTB-N signal. Furthermore, it makes the

store processing of received data into a receive buffer terminate within a certain fixed time and

outputs an ACK-N signal, setting the BUSY-P signal to OFF.

PARALLEL DATA

(DATA BITs 1 to 8)

0.5 µs min.

DATA STROBE

0.5 µs min.

0.5 µs max.

BUSY

0 min.

ACKNOWLEDGE

0.5 µs to 10 µs

0.5 µs min.

0.5 µs min.

0 min.

0 min.

0 min.

- 8 -

Page 11

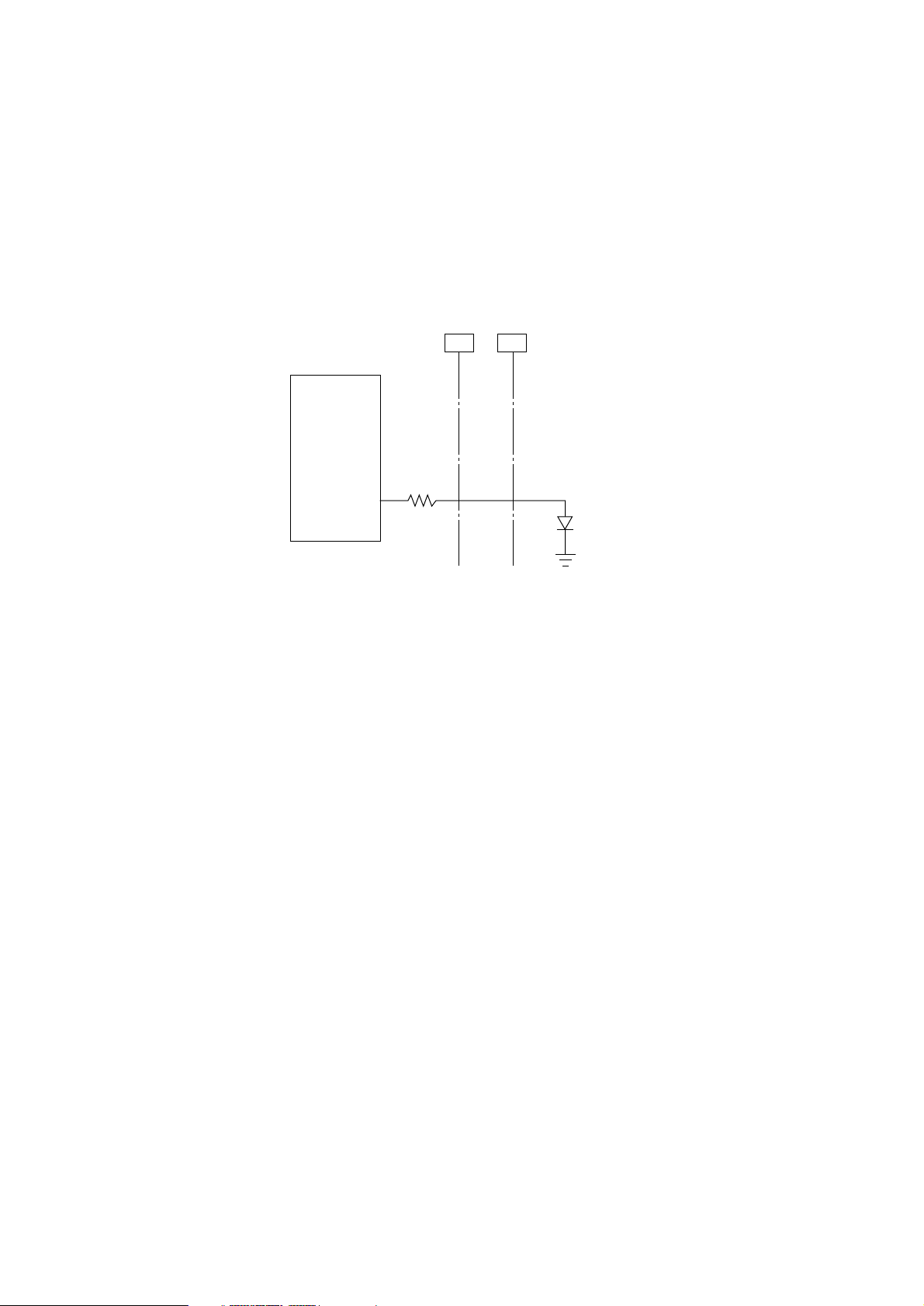

3.6 LED Lamp Control

There is an LED lamp on the high voltage power supply board which is connected to and controled

by the CPU on the main control board.

The light from the LED lamp can be seen on the Lens Cover through the LED Lens.

CN1

main control board high voltage power supply board

CPU

LED-P

41

CN1

- 9 -

Page 12

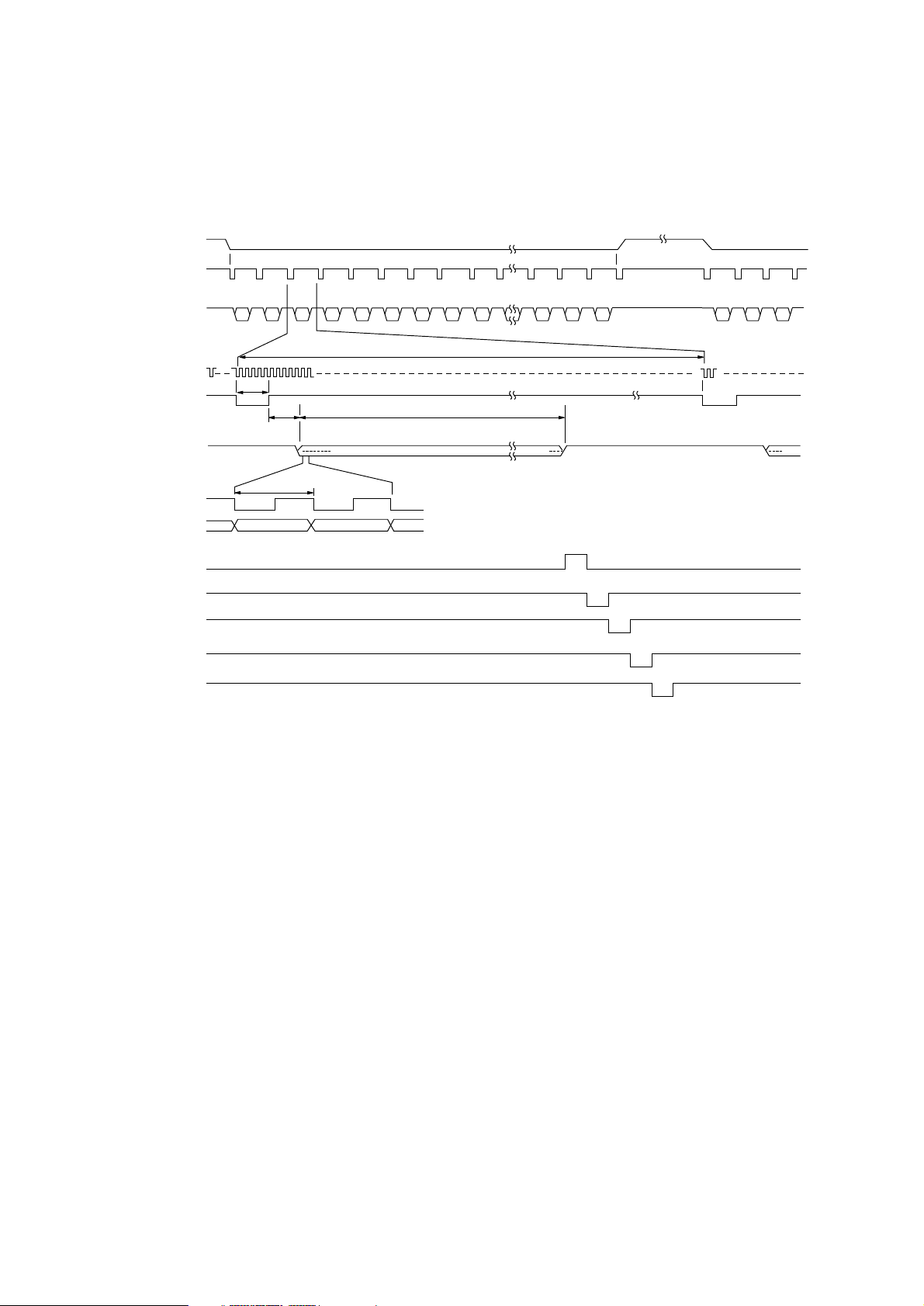

3.7 LED Head Control

When a paper form is made to arrive at the data write position on print start, the sending of data

to the LED head starts as synchronized with the page synchronous signal/line synchronous signal

(CPU internal signal).

Bit image data developed on the raster buffer in the CPU are DMA-transferred to the register of

a video interface controller (CPU built-in) and then sent to the shift register of the LED head in a

serial transmission synchronized with the VCLK-P signal by the VD0-P signal.

When 1-dot line data (2560 bits) is completely shifted, it is latched by means of the VLD-P signal,

causing LEDs to be driven by the VSTB1-N through VSTB4-N signals in different timing for each

signal.

Some of LED heads have 2496 dots rather than 2560 dots. The controls regarding the number

of dots are adjusted to the LED head installed when the printer is shipped from the factory.

Main control board

CPU

CN6 CN1

LED Head

VCLK-P

VD0-P

VLD-P

VSTB 1-N

VSTB 2-N

VSTB 3-N

VSTB 4-N

+5V

0V

90

89

91

92

93

94

95

Chip 40

64 bit shift REG

LATCH

Bit 2560

Chip 1

1 to 640 bits

641 to 1280

1281 to 1920

1921 to 2560

Bit 1

- 10 -

Page 13

Page

synchronous

signal*

Line

synchronous

signal*

VDT-P

3.33 msec

VCLK-P

VDT-P

VCLK-P

VDT-P

VLD-P

VSTB1-N

VSTB2-N

VSTB3-N

VSTB4-N

* CPU internal signal

8 bits

8 bits

0.2 µs

2560 bits

- 11 -

Page 14

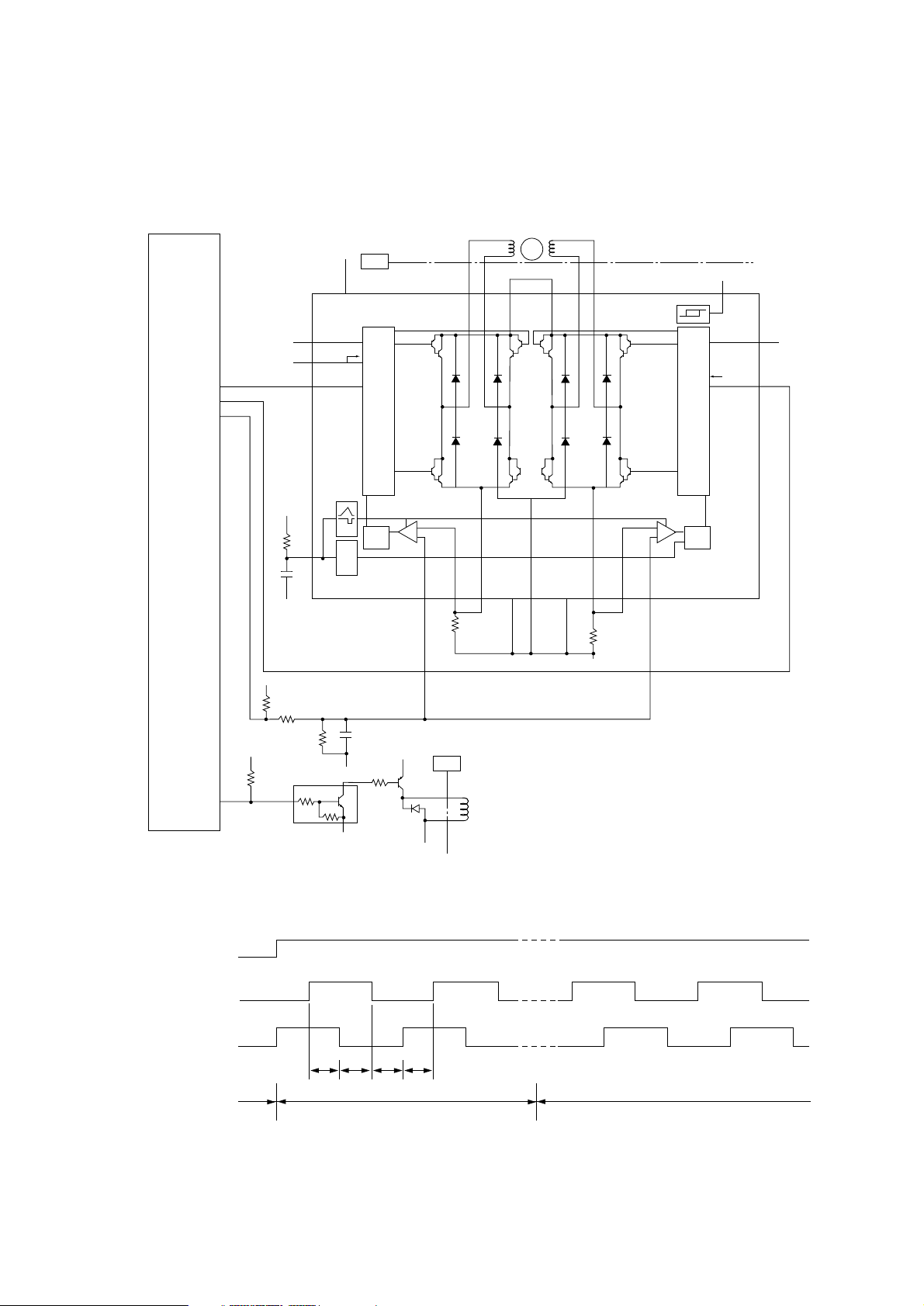

3.8 Motor and clutch control

The electromagnetic clutch is driven by a control signal from the CPU and the drive circuit shown

below.

The main motor is driven by the control signals from the CPU and the driver IC.

CPU

DMP1

DMP2

DMP3

0V 0V

+5V

96

97

98

+5V

IC10

27

18

26

19

ENA A

To Out3, 4Logic

DECAY

PHASE A PHASE B

CN7

GATE CIRCUIT

M

Main Motor

+24V OPEN

37 1 1412 24

Out2 Out3

Out1

SW1 SW3

SW1 SW3

8

Out4Vmm A Vmm B

ALARM

120

140

ENA B

GATE CIRCUIT

Signal of

DECACY

16

17

+5V

+5V +24V

RMON

99

(1) Main motor

+5V

0V

25

BRUNK

0V

0V

SW4SW2

Current

-

Q

R

+

S

Sensor

OSC

Vref A Vref B

Vs A Vs BRs A Rs BLG A PG LG B

23 22 28 15 10 21 20TAB5

CN8

Electromagnetic clutch

0VP

0V

SW4SW2

Current

Sensor

RQ

+

S

DMON-P

DMPH1-P

DMPH2-P

Rotation

T0 T1 T2 T3

Forward rotation

Reverse rotationStop

Operation at normal speed: T0 to T3 = 1.515 ms

- 12 -

Page 15

(2) Motor drive control

Time T0 to T3 determines the motor speed, while the phase different direction between

phase signals DMPH1-P and DMPH2-P determines the rotation direction. DMON-P signal

control a motor coil current. According to the polarity of the phase signal, the coil current flow

as follows:

1) +24V → SW1 → motor coil → SW4 → resistor → earth, or,

2) +24V → SW3 → motor coil → SW2 → resistor → earth

The drop voltage across the resistor is input to comparator, where it is compared with a

reference voltage. If an overcurrent flows, a limiter operates to maintain it within a certain

fixed current.

(3) Electromagnetic clutch control

Mechanical operation mode is switched by the combination of the clutch status and the

direction of motor rotation.

clutch status

off

off

on

on

rotation direction

Forward

Reverse

Forward

Reverse

operation mode

cleaning

Hopping from manual

feed slot

illegal operation

Hopping from tray

- 13 -

Page 16

3.9 Fuser Temperature Control

The temperature change in a heat controller is converted into the electric potential TEMP

corresponding to the change in the resistance value of a thermistor, and the resultant potential

is fed back to the control circuit. The CPU performs ON/OFF control of the HEATON-P signal to

keep the heat roller temperature constant in accordance with the state at which the thermistor

voltage (TEMP) is read into directly by the AD converter of the CPU.

THCHK-N signal is fixed to “0”.

When the paper thickness is set on the menu of the host, the temperature is adjusted to the

targeted thickness accordingly.

Main Control Board

CPU

TEMP

27

AI4

(A/D)

THCHK-N

34

85

HEATON-P

High voltage power

supply board

IC20

5

+

6

-

7

+5V +5V

IC20

3

+

2

-

1

+5V

Ther-

mistor

HEATON-N

Heater

Thermostat

Heat Roller

+5V

ACIN

Power supply unit

- 14 -

Page 17

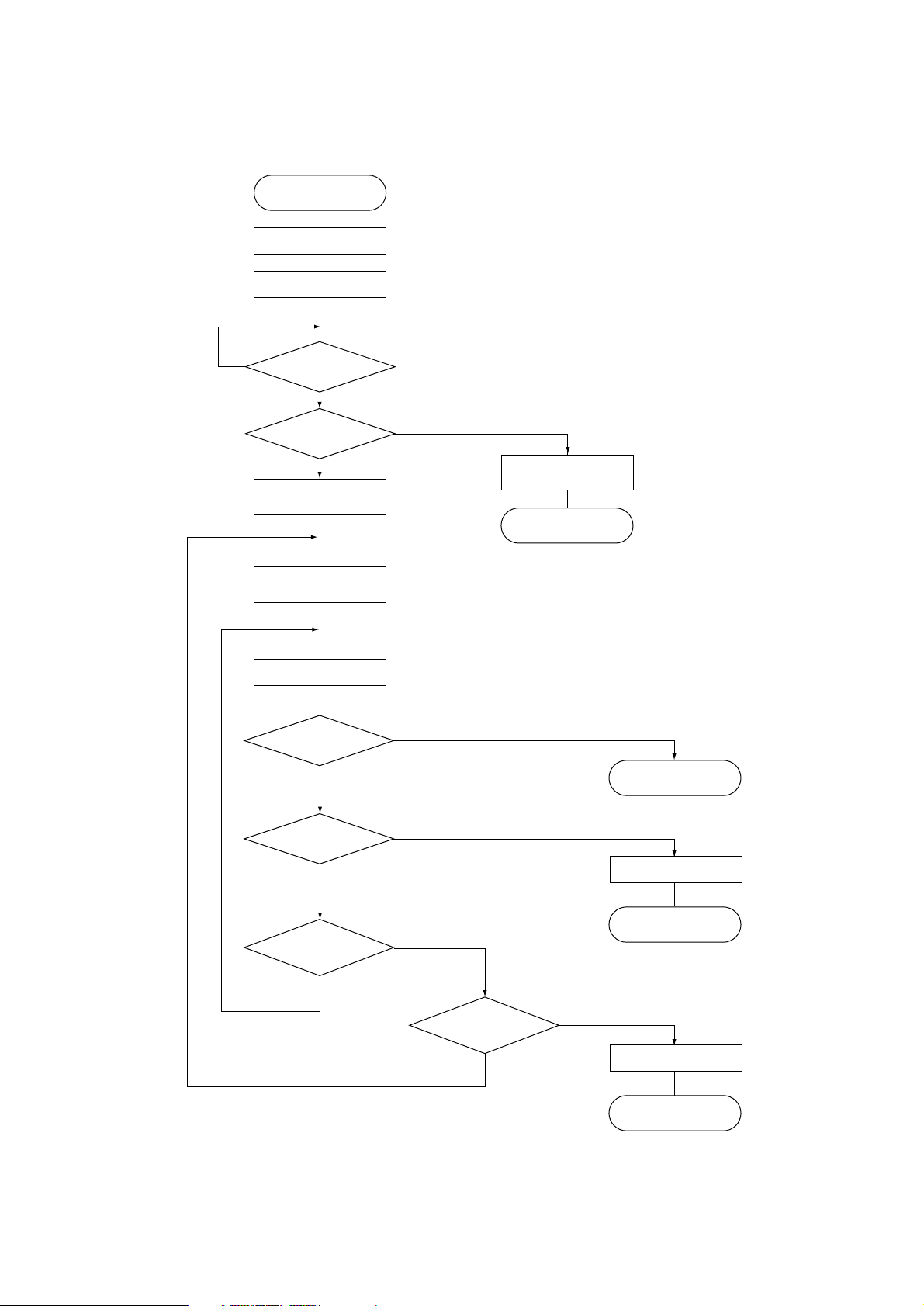

Flowchart of Thermistor Circuit Check

START

HEATER OFF

Short check timer(t16)set

No

Time-out ?

Short error TEMP ?

Thermistor error check

timer (t2) set

Thermistor disconnection

check timer (t35) set

Heater On

Temperature > Tn

No

No

Yes

Yes

Yes

Tn...T0 =

T2 =

T4 =

Thermistor short error

End

Light

Medium

Heavy

To constant

temperature control

Thermistor

error check timer (t2)

within time

Yes

Thermistor

disconnection check timer

(t35) within time

Yes

t2 =

t16 =

t35 =

90 sec

520 msec

10 sec

No

No

Time-out

A/D value changed?

Yes

- 15 -

No

Fuser error

End

Thermistor disconnection

error

End

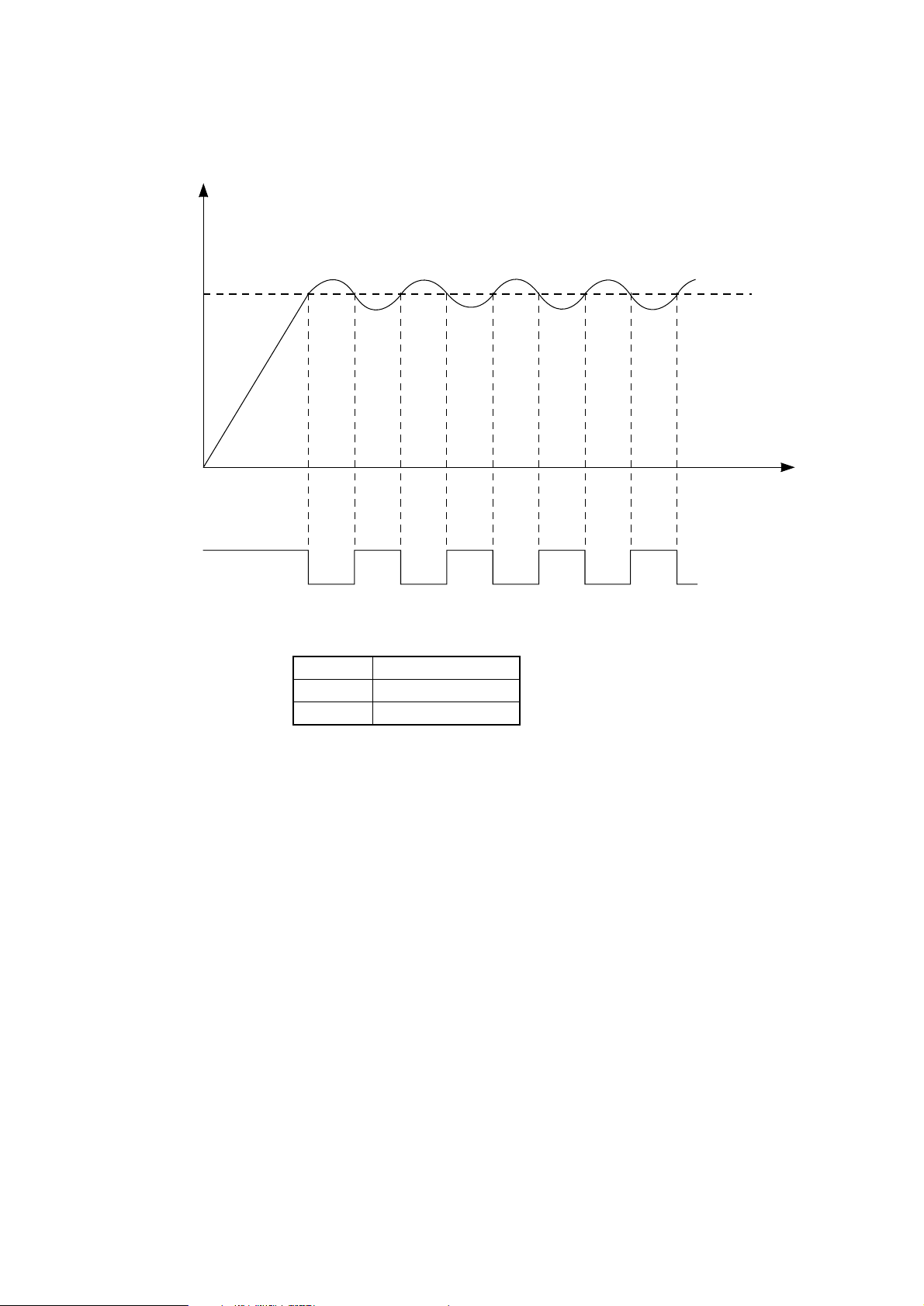

Page 18

Temperature

Controlled

Temperature

T

HEATER ON

OFF

Time

Temperature table

THCHK-N

O

Z

Heater control mode

Normal operation

Not used

T

135˚C:

140˚C:

150˚C:

155˚C:

155˚C:

Paper Thickness

light

medium light

medium

medium heavy

heavy

- 16 -

Page 19

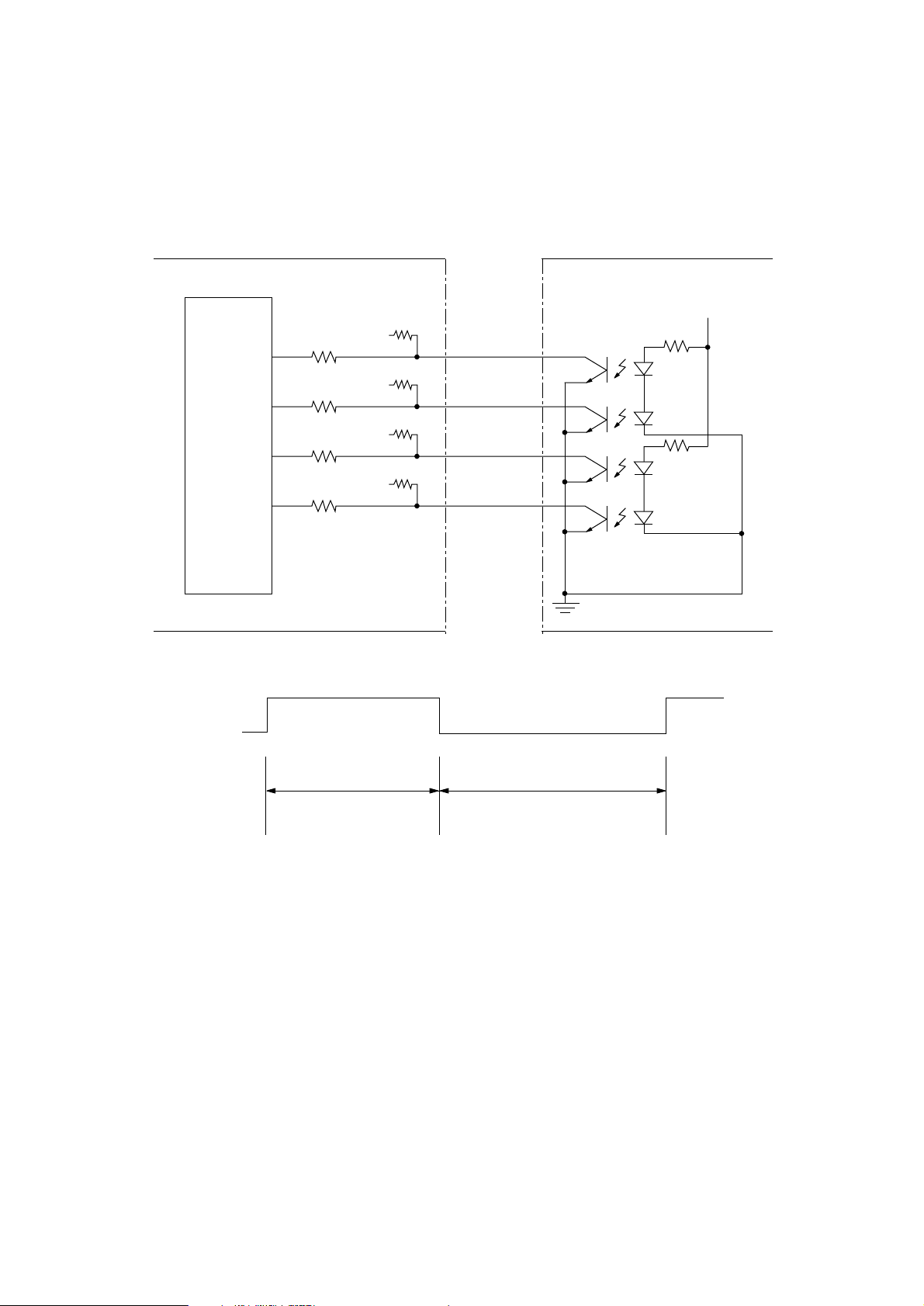

3.10 Sensor Control

The CPU supervises the state of each sensor every 40 ms.

Main Control Board High Voltage Power Supply Board

CN1 CN1

+5V

CPU

Sensor

signal

47

44

46

48

OFF

+5V

+5V

+5V

+5V

TNRSNS-N

PSIN-N

PSOUT-N

WRSNS-N

TransparentShield

PS1

PS2

PS3

PS4

ON

- 17 -

Page 20

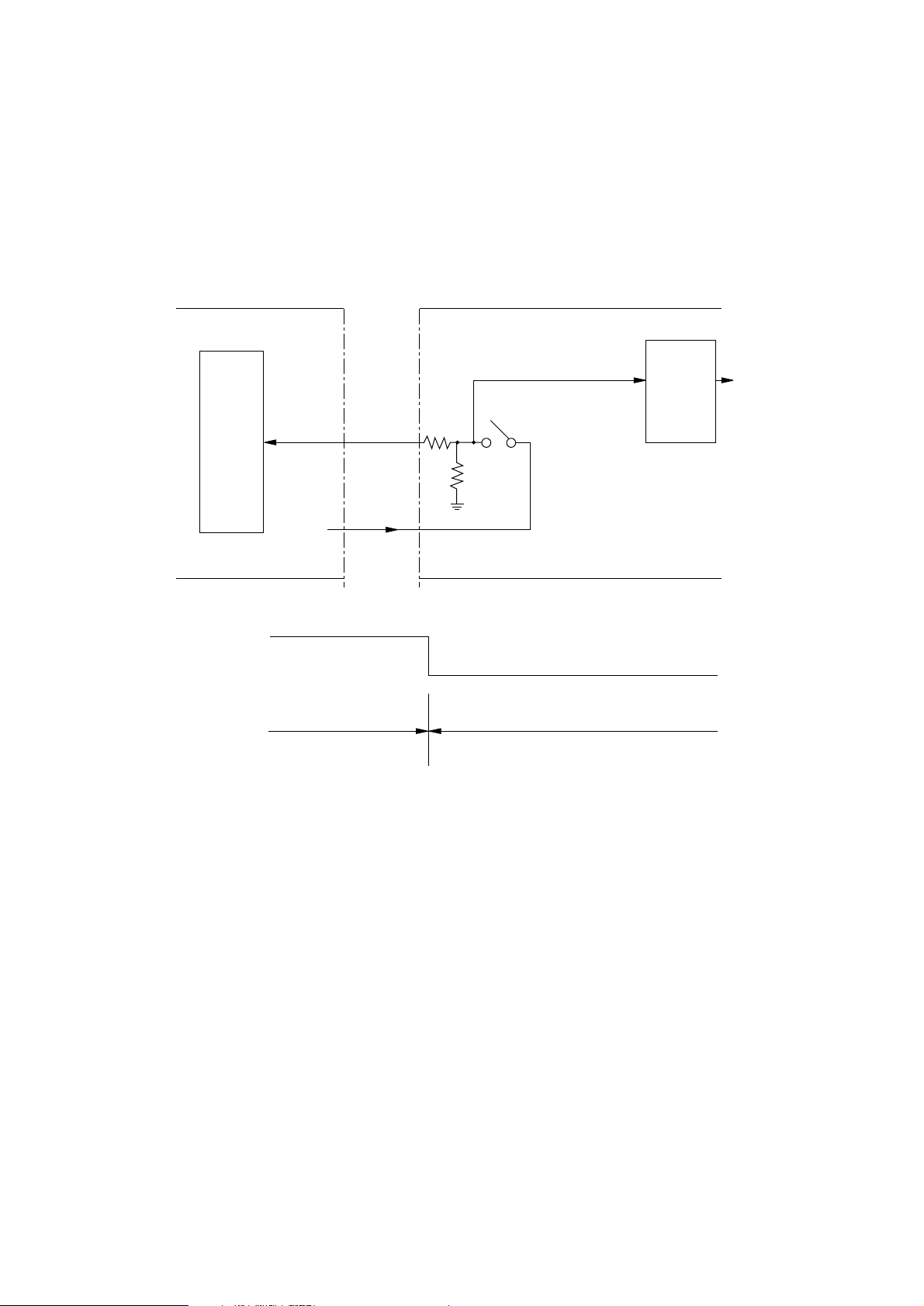

3.11 Cover Open

When the cover is opened, a cover open microswitch is opened. This makes a CVOPN-N signal

low, thereby the CPU detects that cover is open. Furthermore, opening the cover stops applying

a +5V power to the high voltage power supply part, resulting in stopping all high voltage outputs.

CN1 CN1

Main Control Board

CVOPN-N

CPU

+5V

0V

45

Cover close Cover open

CVOPN-N

Cover

Open

Microswitch

+5V

High Voltage Power Supply Board

High

Voltage

Power

Supply

+5V

Part

High

voltage

output

- 18 -

Page 21

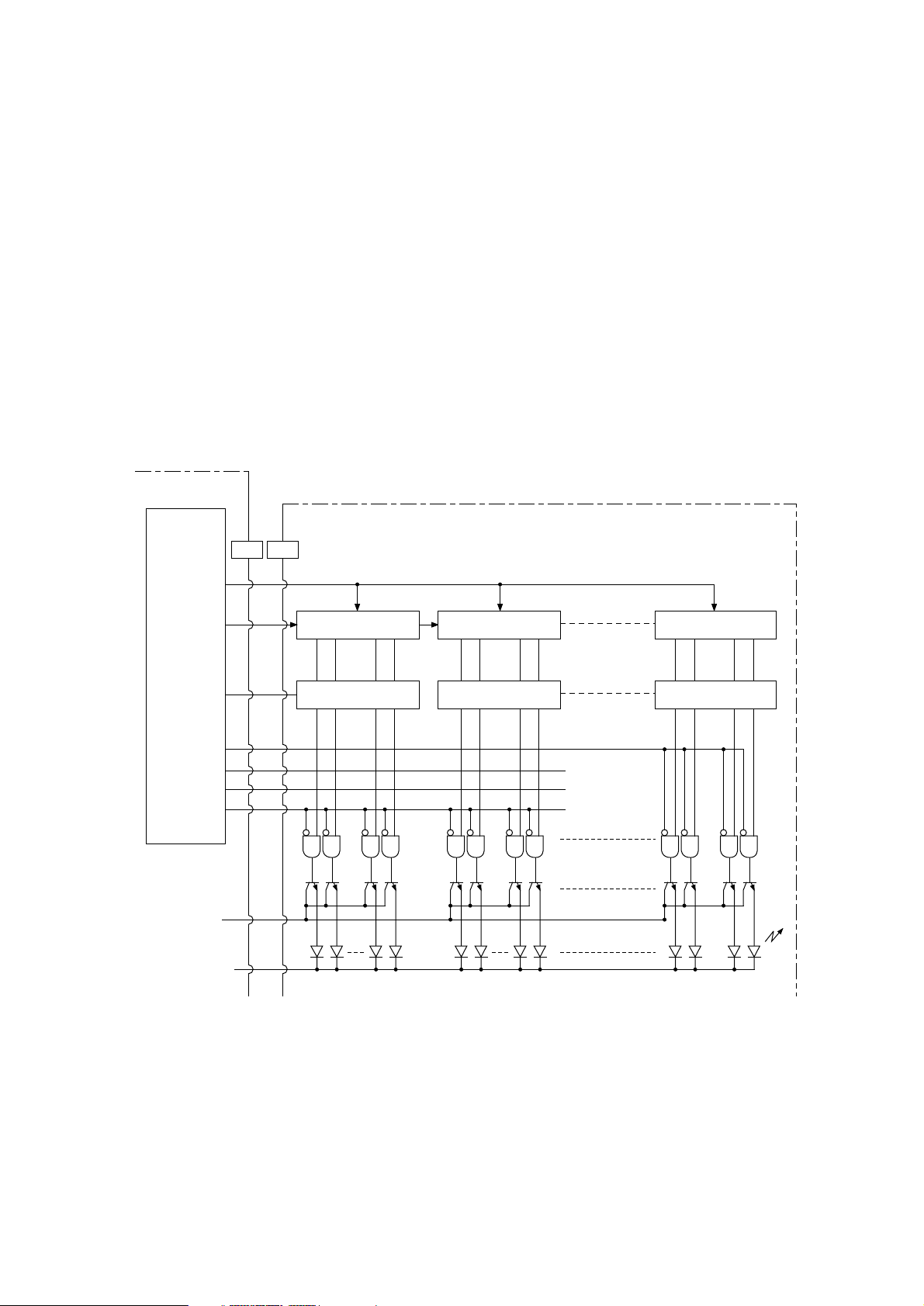

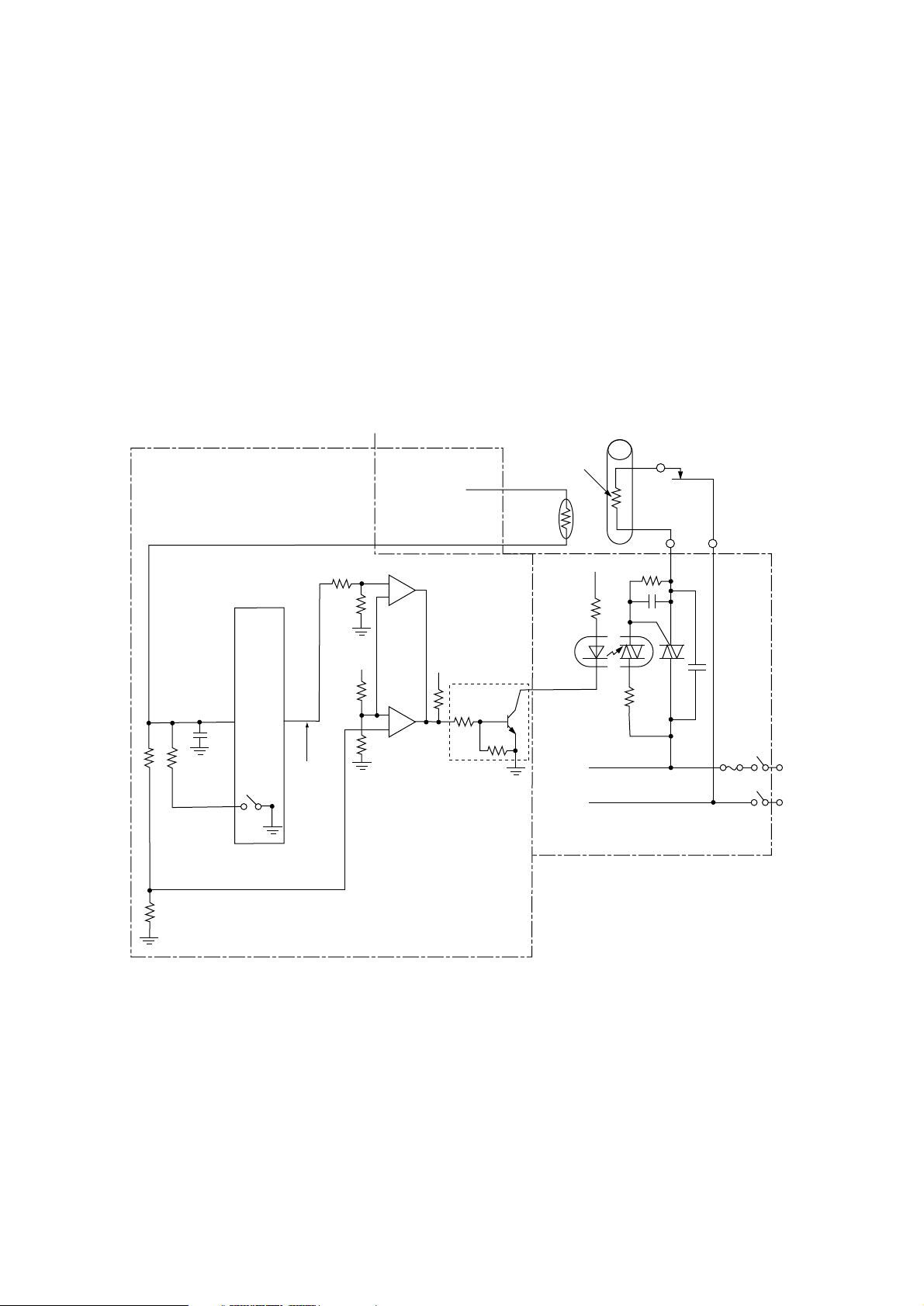

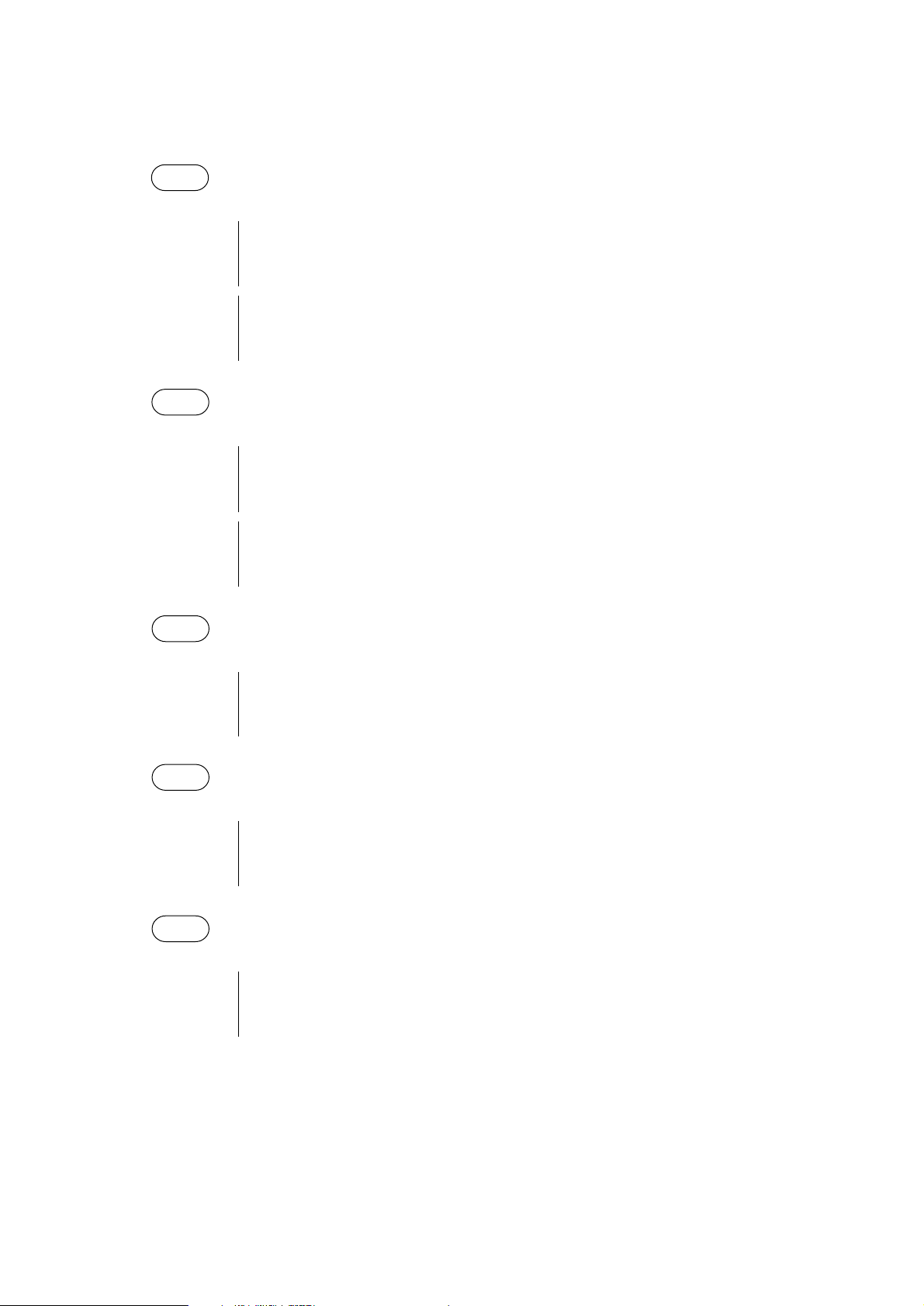

3.12 Power Supply Part

(1) Power supply unit

An AC power from an inlet is input to Switching Reg. part .AC power is converted to a +24

VDC output and +5 VDC output.

ACIN

F1 F2L

FG

N

Filter

Circuit

Power supply unit

+24V

+5V

0V

HEATER

Switching Reg. Part

CONTROLER

HEATON-N

to AC output

Fuse Ratings

AC Input

Fuse

F1

F2

230 V

250 V 6.3 A

250 V 2 A

120 V

125 V 10 A

250 V 2 A

(2) High voltage power supply board

The +5 VDC power supplied to the high voltage power supply part via the cover open

microswitch as source voltage. The high voltage power supply part supplies necessary

voltage for electro-photography print to output terminals CH, DB, SB, TR, and CB according

to a control signal from the CPU. The table on the next page shows the relationship between

control signals and high voltage outputs.

CN1

MainControl Board High Voltage Power Supply Board

TR1PWM-P

55

TR2PWM-P

59

CHPWM-P

56

SDB1-P

53

CPU

52

54

45

SDB2-P

DBPWM-P

CVOPN-N

+5V

CN1

High Voltage

Power Supply

Part

CH

DB

SB

TR

CB

Cover Open

Microswitch

- 19 -

Page 22

Control Signals and High Voltage Outputs

Control signal name Level Function

TR1PWM-P

TR2PWM-P

CHPWM-P

SDB1-P

SDB2-P

DBPWM-P

H/L

(PWM)

L

H/L(PWM)

L

H/L(PWM)

L

H

L

H

L

H/L(PWM)

L

Makes the part put out a power to TR.

+3 to 5 µA

+0.5 to 4 KV

Makes the part put out a -750V power to TR.

Makes the part put out a -1.35 KV power to CH.

Makes the part put out the following power:

+450V or 0V power to SB

+300V power to DB

Makes the part put out the following power:

-450V power to SB

-300V power to DB

+400V power to CB

Makes the part put out the power to SB, DB, CB.

- 20 -

Page 23

4. TROUBLESHOOTING

4.1 Troubleshooting Table

(A) High Voltage Power Supply Board

Note: A malfunction of the power supply is not repaired by an agency. The abnormality to be

treated here is that of sensors only.

Failure PC Display Message

A paper input jams occur frequently.

PAPER

Flowchart

No.

A - 1

INPUT JAM

A paper feed jams occur frequently.

PAPER

A - 2

FEED JAM

A paper-exit jams occur frequently.

PAPER

A - 3

EXIT JAM

A paper size errors occur frequently. A - 4

PAPER

SIZE ERROR

Paper can not be fed from the manual feed slot . A - 5

The message "COVER OPEN" remains displayed on

the PC display.

COVER OPEN

A - 6

The message "TONERLOW" remains displayed on

the PC display.

The message "TONERSNS" remains displayed on

the PC display.

TONER LOW

TONER SENSOR

- 21 -

A - 7

A - 8

Page 24

(B) Main Control Board

Failure PC Display Message

Initialization error and not restored

INITIALIZATION

Flowchart

No.

B - 1

ERROR

Program ROM error

ROM CHECK

B - 2

ERROR

Resident RAM error

RAM CHECK

B - 3

ERROR

EEPROM error B - 4

EEPROM CHECK

ERROR

Fuser error B - 5

Watchdog timer timeout occurs frequently. B - 6

FUSER ERROR

WATCHDOG

Data sent through the Parallel I/F cannot

be received.

TIMER ERROR

INITIALIZATION

ERROR

B - 7

- 22 -

Page 25

4.2 Troubleshooting Flowchart

A-1 Paper input jams occur frequently.

• Is PS4 (Write Sensor ) operating normally?

• No Replace PS4.

▼

• Yes Is Pin1 of CN8 in main control board operating normally?

• No Replace Q4 or Q5 in main control board.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

A-2 A paper feed jams occur frequently.

• Is PS4 (Write Sensor ) operating normally?

• No Replace PS4.

▼

• Yes Is PS3 (Outlet Sensor ) operating normally?

• No Replace PS3.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

A-3 A paper exit jams occur frequently.

• Is PS3 (Outlet Sensor) operating normally?

• No Replace PS3.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

A-4 A paper size errors occur frequently.

• Is PS4 (Write Sensor ) operating normally?

• No Replace PS4.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

A-5 Paper can not be fed from manual feed slot.

• Is PS2 (Manual Feed Sensor) operating normally?

• No Replace PS2.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

- 23 -

Page 26

A-6 The message “COVER OPEN” remains displayed on the PC display.

• Is CVSW (Cover Open Switch) operating normally?

• No Replace CVSW.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

A-7 The message “TONERLOW” remains displayed on the PC display.

• Is PS1 (Toner Sensor) operating normally?

• No Replace PS1.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

A-8 The message “TONERSNS” remains displayed on the PC display.

• Is PS1 (Toner Sensor) operating normally?

• No Replace PS1.

▼

• Yes Failure of IC6 (MSM65917) in main control board.

- 24 -

Page 27

B-1 Initialization error and not restored

• Replace IC2.

▼

• OK?

▼

• No Is the 10-MHz clock signal being put out to pin 3 of OCS1?

• No Replace OSC1 (CST 10.0MTW).

▼

• Yes Failure of IC6 (MSM65917)

B-2 Program ROM error

• Replace IC2.

B-3 Resident RAM error

• Are negative pulses being put out to Pin 4 , 23 (RAS0-N , CSA-N) of IC11?

• No Failure of IC6 (MSM65917)

▼

• Yes Are the signals at pins, 9 TO 12 , 14 TO 18 , 5

(DA00-P to DA09-P) of IC11 being changed?

• No Failure of IC6 (MSM65917)

▼

• Yes Replace IC11.

B-4 EEPROM error

• Replace IC4.

▼

• OK?

▼

• No Failure of IC6 (MSM65917)

B-5 Fuser error

• Is the heater on?

▼

• No Is the voltage at Pin 40 (HEATON-P) of IC6(MSM65917) 5V?

• Yes Replace Q3 or IC20

▼

• No Failure of IC6 (MSM65917)

B-6 Watchdog timer timeout occurs frequently.

• Replace IC2.

▼

• OK?

▼

• No Failure of IC6 (MSM65917)

- 25 -

Page 28

B-7 Data sent through the Parallel I/F cannot be received.

• Is the signal at Pin 11 (BUSY-P) of CN4 being at low level?

• No Is the signal at Pin 13 (BUSY-P) of IC7 (7407) changed as shown

below, at data reception?

ON-LINE OFF-LINE

BUSY-P Low High

• No Failure of IC6 (MSM65917)

▼

• Yes Replace IC7 (7407).

▼

• Yes Is the level of the signal at Pin 1 (STB-N) of CN4 changed at data reception?

• No Make sure of the connection of I/F cable or the operation of the h ost

computer.

▼

• Yes Are the signals at Pin 1 (ACK-N), Pin 9 (FAULT-N) of IC7 (7407) being

respectively at low level and high level in on-line mode?

• No Replace IC7 (7407).

• OK?

▼

▼

• Yes Failure of IC6 (MSM65917)

• No

- 26 -

Page 29

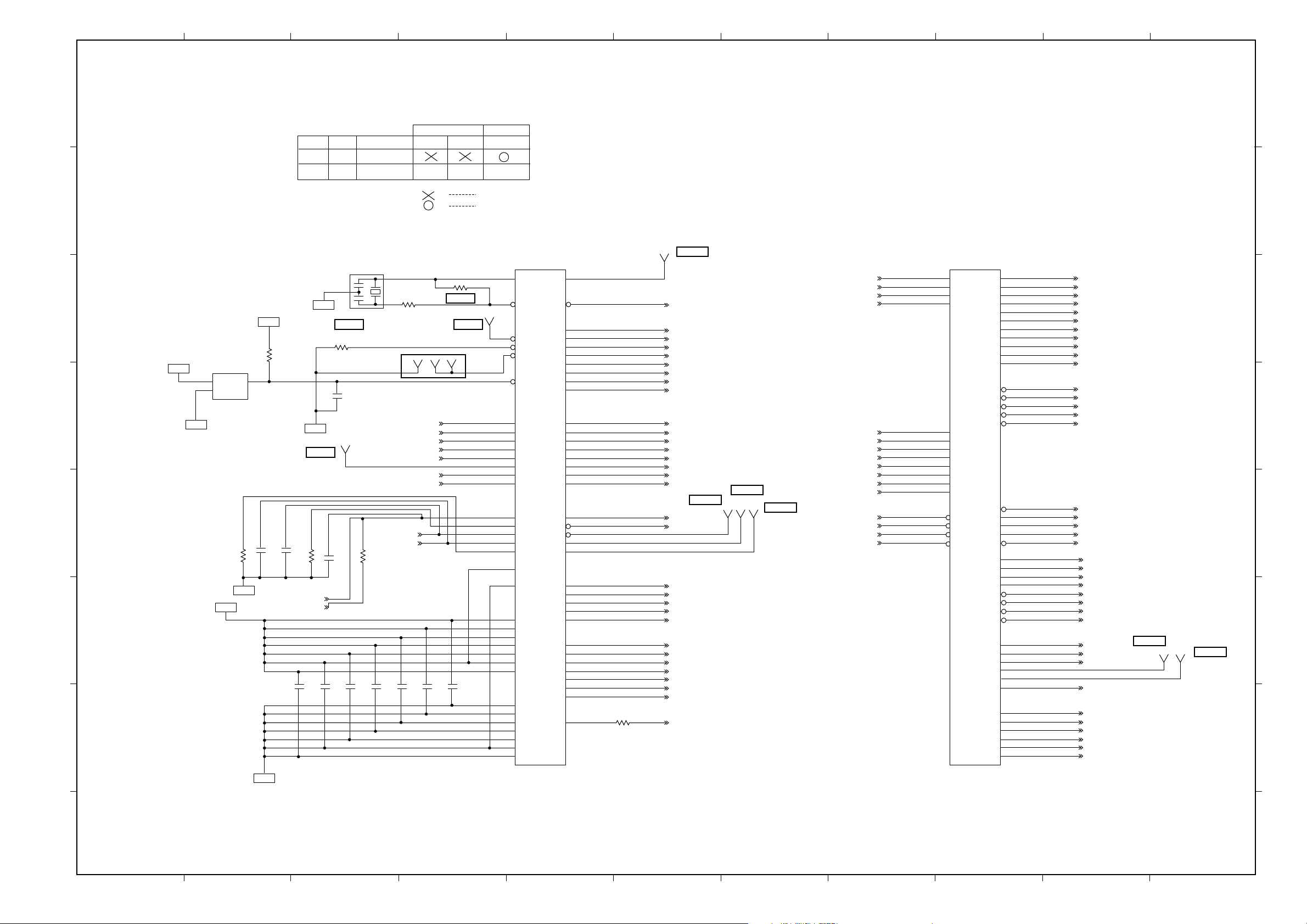

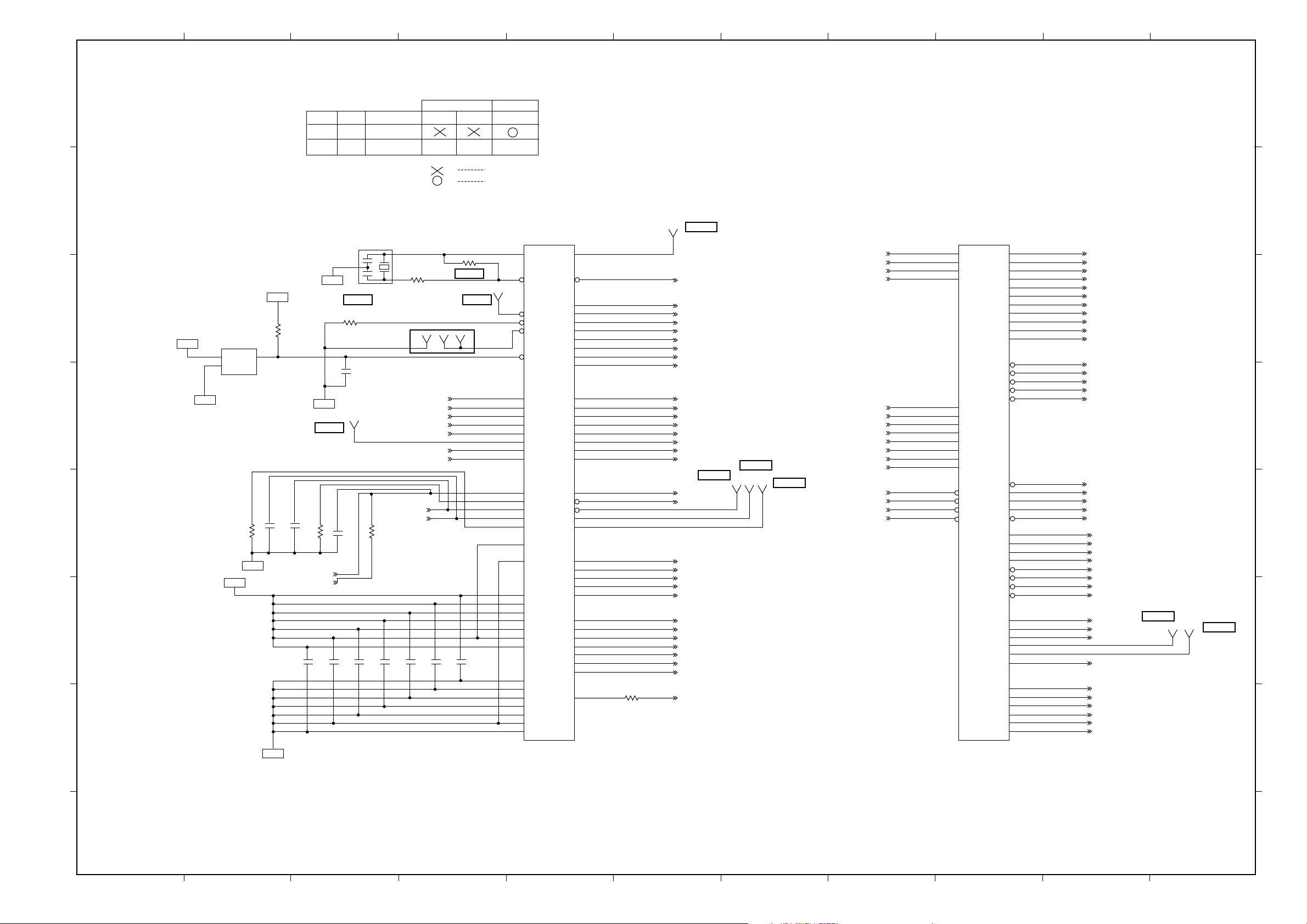

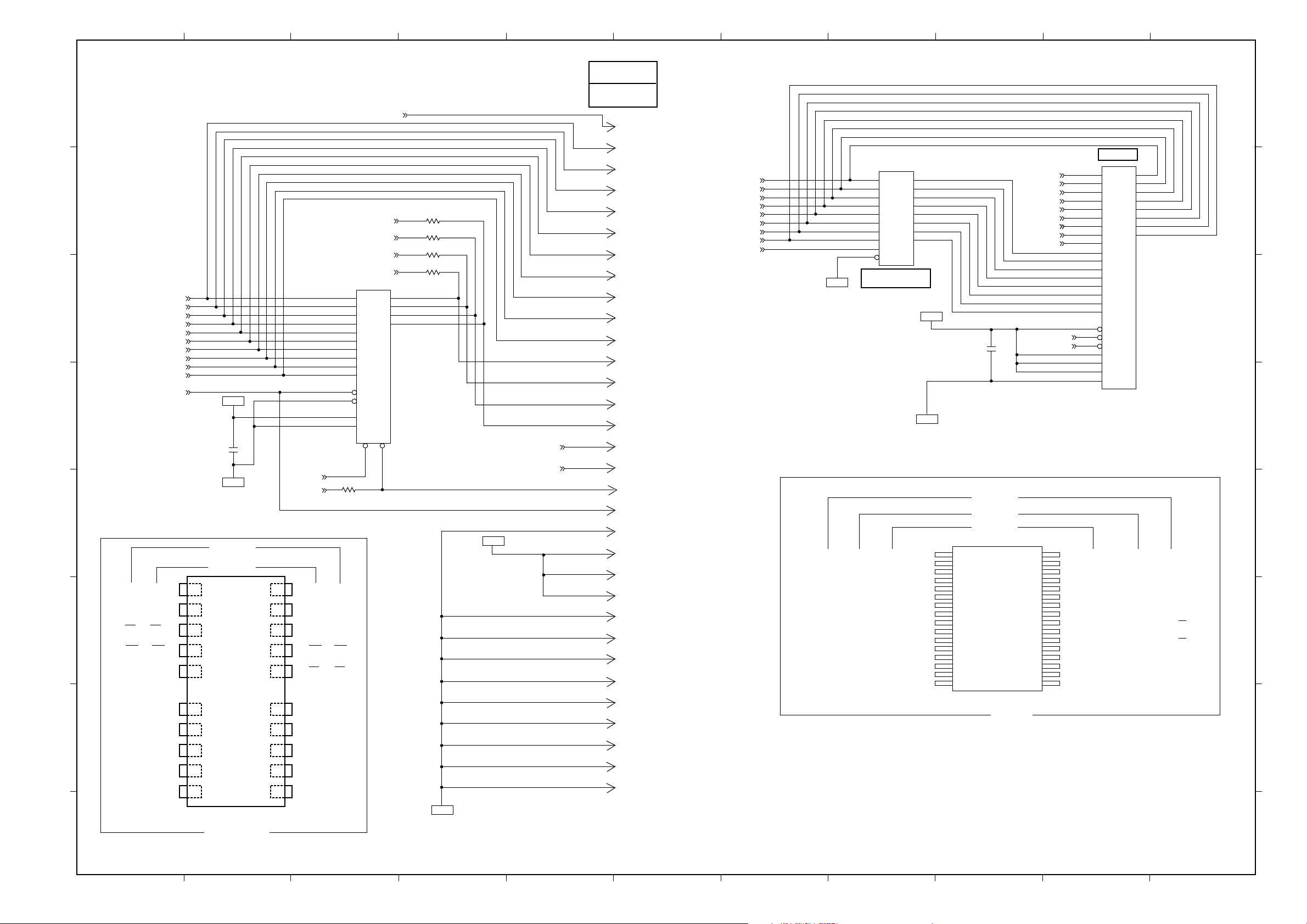

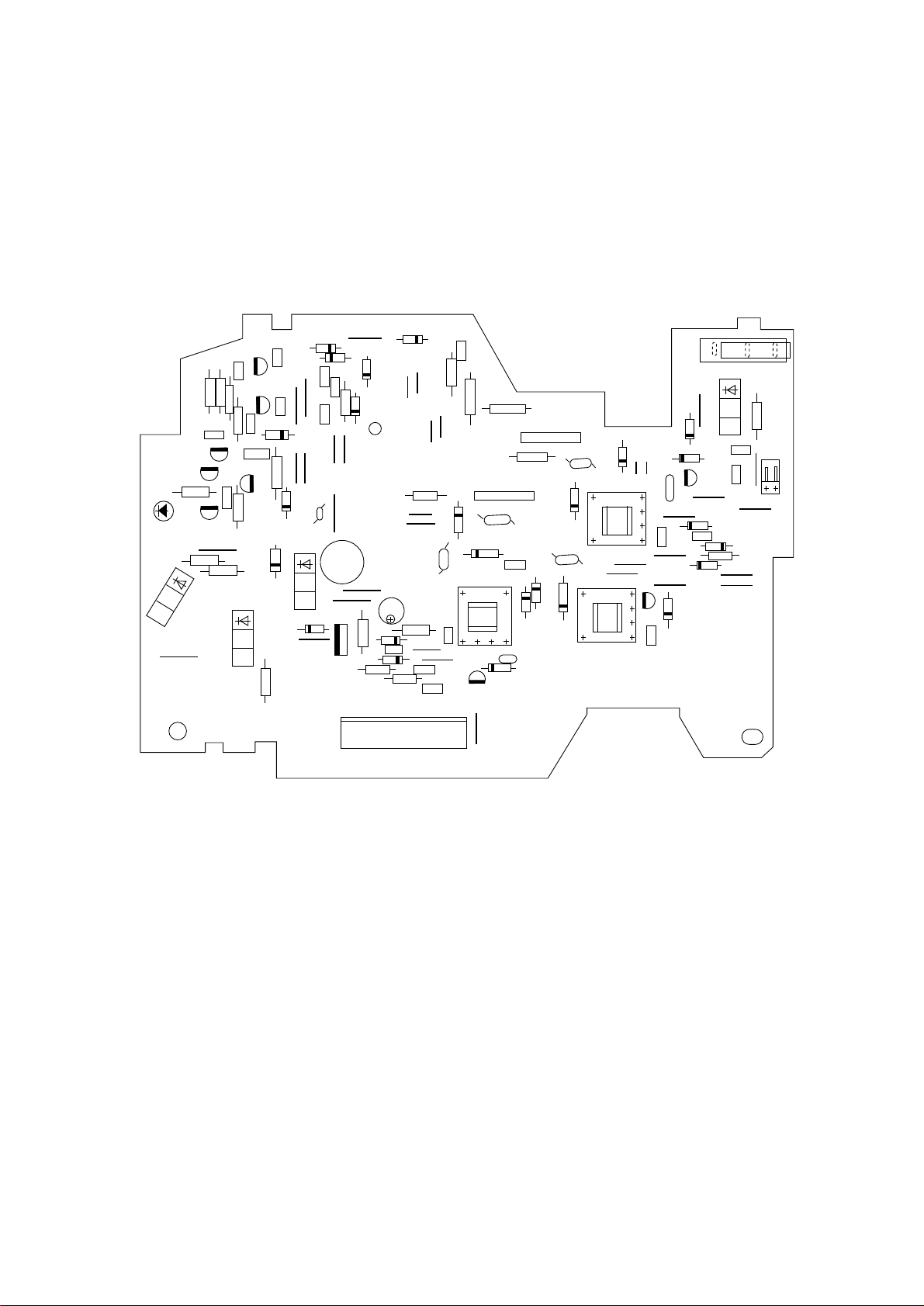

5. CIRCUIT DIAGRAM

Figure 5-1 ~ 5-7 Main Control PCB (HBMC-) Circuit Diagram (Rev. 2)

Figure 5-8 ~ 5-14 Main Control PCB (HBMC-) Circuit Diagram (Rev. 3)

Figure 5-15 High voltage Power Supply PCB (OLHV-) Circuit Diagram (Rev.6 ,7 )

(TLHV-) Circuit Diagram (Rev.2 )

- 27 -

Page 30

1

+5V

+5V

IC5

Not Mounted (HIGH-LEVEL)

MOunted (LOW-LEVEL)

0V

0V

0V

CH1

0V

0V

+5V

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

SIGNAL

OPEN

EAN

Pin-No Short-Wire

MSM65917 Mode change

Tool not connected

Tool connected

Internal ROM Enternal ROM Enternal ROM

61 R121

SP1 B Side A Side A Side62

OSC1

R510

R53

1

1

0

2

2

13

2

1

1

1

2

R533

C15

0.1µ 50

5.1K 0.1

1

1

2

R52

0

0

12

R51

3.6K 0.1

12

R50

12

2

C14

0.1µ 50

1

2

C12

0.1µ 50

1

2

C13

0.1µ 50

1

2

C509

0.1µ 50

1

2

C503

0.1µ 50

1

2

C511

0.1µ 50

1

2

C510

0.1µ 50

2

1

C514

0.1µ 50

1

2

C504

0.1µ 50

2

1

C513

0.1µ 50

1

2

R511

12

3

3

14

18

24

23

17

20

19

21

22

13

12

11

10

15

16

35

36

37

38

39

43

49

34

42

40

85

86

41

105

102

9

7

6

5

8

87

1

111

CH5

CH4CH6CH7

11

CH2 CH3

2

4

1

60

61

62

63

45

47

46

48

27

28

29

30

31

26

32

76

70

58

51

25

75

69

57

50

33

44

106

104

103

108

107

PST592

VCC

GND

OUT

CST10.0MTW

CST

0

R526

12

150 0.1

10K 0.1

CH8

SP1 (Short-plug)

SP1 SP1 SP1

123

AB

(074G) CVOPN-N

(075F) TNRSNS-N

(075G) WRSNS-N

(075G) PSOUT-N

(075F) PSIN-N

(065D) DIPSW2

(065D) DIPSW1

(075F) TEMP

(016F) THCHK-N

(075E) TR-VSEN

(075E) TR-ISEN

GND1

GND2

GND3

GND4

GND5 PU00

P40

P41

P42

P43

P44

P45

P46

P20

P21

P24

P25

P27

INT0

INT1

WRN

RDN

ALE

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

A8

A9

A10

A11

A12

A13

A14

A15

ROCS

CPCK

65917

(1/2)

GND6

GND7

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

AGND

AVDD

AI0

AI1

AI2

AI3

AI4

P30

P31

P32

P33

P34

P35

P36

P37

RSTN

EAN

CPEN

TEST

OSC0

OSC1

IC6

CHPW

DBPW

T2PW

T1PW

SDB2

SDB1

RMON

RMP1

RMP2

DMON

DMP1

DMP2

VSB4

VSB3

VSB2

VSB1

VLDP

VCLK

VD0P

VD1P

FLTN

SELP

PEP

BSYP

ACKN

DWRN

CASN

RAS0

RAS1

RAS2

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

DA10

DA9

DA8

65917

(2/2)

PSBN

AFXN

SLIN

IPRN

PDT2

PDT1

PDT3

PDT4

PDT5

PDT6

PDT7

PDT8

DD0

DD3

DD2

DD1

IC6

LED-P (074F)

XCLK-P (065B)

HEATON-P (075D)

FANALM-N (03XG)

EEPRMDT-P (047A)

EEPRMCS-P (047B)

EEPRMCLK-P (048C)

AD00-P (027B)

AD01-P (027B)

AD02-P (027B)

AD03-P (027B)

AD04-P (027B)

AD05-P (027B)

AD06-P (027B)

AD07-P (027B)

A08-P (02XB)

A09-P (02XB)

A10-P (02XB)

A11-P (02XB)

A12-P (02XB)

A13-P (02XB)

A14-P (02XB)

A15-P (02XB)

ROMCS-N (02XC)

RD-N (02XC)

ALE-P (027C)

FANON-P (037E)

DCLED-P (071F)

THCHK-N (013E)

TXD-P (065B)

BANK (02XB)

RXD-P (065B)

53

52

55

59

54

56

99

100

101

98

96

97

92

93

94

95

91

90

89

88

81

80

79

78

77

120

125

126

127

128

119

118

117

116

115

114

113

112

111

110

109

123

124

121

122

74

73

72

71

68

67

66

65

82

83

84

64

(024B) DD01-P

(024B) DD00-P

(024C) DD03-P

(024C) DD02-P

(054B) PDATA8-P

(054B) PDATA7-P

(054B) PDATA6-P

(054C) PDATA5-P

(054C) PDATA4-P

(054C) PDATA3-P

(054C) PDATA2-P

(054C) PDATA1-P

(054E) IPRIME-N

(054F) SELIN-N

(054G) AUTOFD-N

(054E) PSTB-N

DA10-P (024A)

DA09-P (022C)

DA08-P (022C)

DA07-P (022C)

DA06-P (022C)

DA05-P (022C)

DA04-P (022C)

DA03-P (022C)

DA02-P (022D)

DA01-P (022D)

DA00-P (022D)

RAS2-N (025D)

RAS1-N (025E)

RAS0-N (023E)

CAS-N (023E)

DWR-N (022D)

ACK-N (057E)

BUSY-P (057D)

PE-P (057E)

SEL-P (057F)

FAULT-N (057F)

VD1-P (041B)

VD0-P (041B)

VCLK-P (041B)

VLD-P (041C)

VSTB4-N (041D)

VSTB3-N (041D)

VSTB2-N (041C)

VSTB1-N (041C)

PJON-P (037B)

CHPWM-P (071D)

DBPWM-P (072C)

TR2PWM-P (071E)

TR1PWM-P (071C)

SDB2-P (071B)

SDB1-P (071A)

DMPH1-P (032C)

DMON-P (031D)

DMPH2-P (033C)

23 456 87 9X

Y

A

B

C

D

E

F

G

H

1

2

3456 87 9X

Figure 5-1 Main controller PCB

(HBMC-1/7) Rev. 2

Cicuit Diagram

A

B

C

D

E

F

G

H

- 28 -

Y

Page 31

1

+5V

+5V

+5V

0V

0V

0V

0V

CN9

Option-RAM

(01XB) DA10-P

(018B) DD00-P

(01XB) DA09-P

(01XC) DA08-P

(01XC) DA07-P

(01XC) DA06-P

(01XC) DA05-P

(01XC) DA04-P

(01XC) DA03-P

(01XC) DA02-P

(01XC) DA01-P

(01XC) DA00-P

(01XD) DWR-N

(018B) DD01-P

(018C) DD02-P

(018C) DD03-P

DRAM-A10

DRAM-A09

DRAM-A08

DRAM-A07

DRAM-A06

DRAM-A05

DRAM-A04

DRAM-A03

DRAM-A02

DRAM-A01

DRAM-A00

DRAM-D03

DRAM-D02

DRAM-D01

DRAM-D00

RAS2N

RAS1N

CASN

DRAM-WRN

OE

VCC

VCC

VCC

GND

GND

GND

GND

GND

GND

GND

GND

GND

CN9

24

CN9

25

CN9

26

CN9

27

CN9

28

CN9

29

CN9

30

CN9

12

CN9

11

21

CN9

10

CN9

9

CN9

3

CN9

2

CN9

7

CN9

6

CN9

8

CN9

1

CN9

4

CN9

5

CN9

19

CN9

17

CN9

18

CN9

13

CN9

14

CN9

15

CN9

16

CN9

20

CN9

22

CN9

23

CN9

31

CN9

32

CN9

R548

1

2

0

R546

1

2

0

R549

1

2

0

R550

1

2

0

IC11

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

WE

OE

VCC

VSS

RAS CAS

I/O4

3

22

13

423

1

2

24

25

26

5

18

17

16

15

14

12

11

10

9

I/O3

I/O2

I/O1

514400J

C520

0.1µ 50

1

2

R547

0

12

(01XD) RAS0-N

(01XD)CAS-N

(01XC) RAS2-N

(01XC) RAS1-N

<512>

<256>

DQ1DQ1

DQ2DQ2

WEWE

RASRAS

NCA9

A0A0

A1A1

A2A2

A3A3

Vcc

1

2

3

4

5

9

10

11

12

13

26

25

24

23

22

18

17

16

15

14Vcc

VssVss

DQ4DQ4

DQ3DQ3

CASCAS

OEOE

A8A8

A7A7

A6A6

A5A5

A4A4

IC11

1M Mask

27C1001

27512

IC2

1

2

3 (1)

4 (2)

5 (3)

6 (4)

7 (5)

8 (6)

9 (7)

10 (8)

11 (9)

12 (10)

13 (11)

14 (12)

15 (13)

16 (14)

NC

A16

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

GND

VPP

A16

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DO

D1

D2

GND

-

-

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DO

D1

D2

GND

-

-

VCC

A14

A13

A8

A9

A11

OE/VPP

A10

CE

D7

D6

D5

D4

D3

VCC

PGM

NC

A14

A13

A8

A9

A11

OE

A10

CE

D7

D6

D5

D4

D3

VCC

NC

NC

A14

A13

A8

A9

A11

OE/OE

A10

CE/CE

D7

D6

D5

D4

D3

32

31

(28) 30

(27) 29

(26) 28

(25) 27

(24) 26

(23) 25

(22) 24

(21) 23

(20) 22

(19) 21

(18) 20

(17) 19

(16) 18

(15) 17

GND

VCC

NC

VPP

CE

OE

PGM

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16 Q7

21

31

24

22

1

30

32

16

2

3

29

28

4

25

23

26

27

5

6

7

8

9

10

11

12

20

19

18

17

15

14

13

Q6

Q5

Q4

Q3

Q2

Q1

Q0

(016E) RD-N

C501

0.1µ 50

1

2

(016C) ROMCS-N

Vcc=+5V, Ground=0V

SOCKET

IC2

IC3

27C1001

74LS373

1D

2Q

3Q

4Q

5Q

6Q

7Q

8Q

1Q

2D

3D

4D

5D

6D

7D

8D

EN

OC

2

1

11

18

17

14

13

8

7

4

3

5

6

9

12

15

16

19

(016D) AD07-P

(016F) BANK

(016C) A15-P

(016C) A14-P

(016C) A13-P

(016C) A12-P

(016C) A11-P

(016C) A10-P

(016C) A09-P

(016C) A08-P

(016D) AD06-P

(016D) AD05-P

(016D) AD04-P

(016D) AD03-P

(016D) AD02-P

(016D) AD01-P

(016D) AD00-P

(016E) ALE-P

23 456 87 9X

Y

A

B

C

D

E

F

G

H

1

2

3456 87 9X

Figure 5-2 Main controller PCB

(HBMC-2/7) Rev. 2

Cicuit Diagram

- 29 -

A

B

C

D

E

F

G

H

Y

Page 32

1

23 456 87 9X

Y

A

B

+5V

C

R542

12

(01XF) DMON-P

D

E

2

R541

1

1K 0.1

0.1

22K

A

2

R540

1

0.1

4.3K

0V

22K 0.1

2

1

C523

0.1µ 50

(01XF) DMPH1-P

0V

(01XF) DMPH2-P

R543

12

B

1

C524

0V

2

C

ZA21

NOMOUNT

50

2200p

0V

1

ZA20

1

CH10CH9

11

+5V

C525

12

0.1µ 50

+24V

+

C4

21

47µ 50

D

NOMOUNT

MIN_W:1.27

MIN_W:1.27

MIN_W:1.27mm

0Vp

26

27

17

16

25

23

22

20

21

18

19

28

15

1

14

29

30

MTD2005F

PHAA

NENA

PHAB

NENB

CR

REFA

VSA

REFB

VSB

DCAY

VCC

LGA

LGB

VMM1

VMM2

GND1

GND2

IC10

OUT1

OUT2

OUT3

OUT4

NALM

RSA

RSB

NC1

NC2

NC3

NC4

NC5

NC6

3

7

8

12

24

5

10

2

4

6

9

11

13

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

E

4M-DMOTOR

CN7

CN7

CN7

CN7

IM=0.38A

2

R1

1

2 0.5

CN7

DMPH1-P

1

DMPH1-N

2

DMPH2-P

3

DMPH2-N

4

2

R2

1

2 0.5

MIN_W:0.635mm

0Vp

(01XF) PJON-P

(01GE) FANON-P

R54

1

1K

NOMOUNT

0.1

+24V

+5V

2

R55

1

Q5

22K

2

Q502

22K

2

22K

22K

1

0V

3

1

0V

NOMOUNT

R502

3

1

10K 0.1

10K

2

0.1

Q501

2

3

2SA1338

Q4

3

2SA1338

+24V

MIN_W:0.635

1

2

1

MIN_W:0.635

1

2

D3

1

OVP

NOMOUNT

MIN_W:0.635mm

NOMOUNT

D501

3

SS100MA80VACP

MIN_W:0.635mm

MIN_W:0.635

2

3

SS100MA80VACP

MIN_W:0.635

2

CN8

CN8

NOMOUNT

2M-Fan

CN3

1

CN3

2

CN8

2M-PJ

1

2

CN3

FANPOW

0VP

PJON

OVP

+5V

2

R5011

NOMOUNT

10K 0.1

A

B

C

D

E

F

G

H

1

2

0VP

FANALM-N FANALM-N (01GF)

CN3

3

Figure 5-3 Main controller PCB

(HBMC-3/7) Rev. 2

Cicuit Diagram

- 30 -

3456 87 9X

F

G

H

Y

Page 33

1

23 456 87 9X

Y

A

(01XE) VD0-P

B

C

D

(01XE) VD1-P

(01XE) VCLK-P

(01XE) VLD-P

(01XF) VSTB1-N

(01XE) VSTB2-N

(01XE) VSTB3-N

(01XE) VSTB4-N

+5V

SS100MA80VKCP SS100MA80VKCP

R520

12

0

R519

12

0

R513

12

0

R512

12

0

1

SS100MA80VACP SS100MA80VACP

3

1

D4

3

2

D1 D2

NOMOUNT NOMOUNT

2

A

(01GE) EEPRMDT-P

CN6

3

1

2

NOMOUNTNOMOUNT

D5

1

2

3

CN6

CN6

CN6

CN6

CN6

CN6

CN6

CN6

14F-LED

6

7

8

9

10

11

12

13

HDDT0-P

HDDT1-P

HDCLK-P

HDLD-P

STB1-N

STB2-N

STB3-N

STB4-N

(01GE) EEPRMCS-P

2

R537

1

0V

5.1K 0.1

+5V

2

1

C522

0.1µ 50

(01GE) EEPRMCLK-P

R539

12

IC4

3

DI

6

NC1

1

C8

8

VCC

5

GND1

7

NC2

DO

2

4

R538

12

0V

10K 0.1

B

C

5.1K 0.1

D

E

F

G

H

0V

+5V

C526

0V

0VP

FG1

FG2

2

1

1

1

MIN_W:1.27mm

50

0.1µ

MIN_W:1.27mm

MIN_W:1.27mm

FG

1+

C1

2

10

3300µ

C16

12

0.01µ 250

MIN_W:1.27mm

C8

12

0.01µ 250

MIN_W:1.27mm

MIN_W:1.27mm

MIN_W:1.27mm

MIN_W:1.27mm

MIN_W:1.27mm

CN6

CN6

CN6

CN6

CN6

CN6

E

5V

3

5V

4

F

0V

5

0VP

1

G

0VP

2

FG

14

Figure 5-4 Main controller PCB

(HBMC-4/7) Rev. 2

Cicuit Diagram

H

- 31 -

1

2

3456 87 9X

Y

Page 34

1

A

CN4

36F-Centro

B

C

PDATA8-P

PDATA7-P

PDATA6-P

PDATA5-P

PDATA4-P

PDATA3-P

PDATA2-P

PDATA1-P

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

+5V

21

9

22 0.1

21

8

22 0.1

21

7

22 0.1

21

22 0.1

6

21

5

22 0.1

21

4

22 0.1

21

3

22 0.1

21

2

22 0.1

R30

R31

R29

R28

R25

R26

R27

R24

23 456 87 9X

CN4

36F-Centro

CN4

SG

16

CN4

SG

19

R516

R509

R507

21

3.3K 0.1

R508

21

21

3.3K 0.1

3.3K 0.1

R517

R518

21

3.3K 0.1

R524

21

21

21

3.3K 0.1

3.3K 0.1

R523

21

3.3K 0.1

3.3K 0.1

PDATA8-P(018D)

PDATA7-P (018D)

PDATA6-P(018D)

PDATA5-P (018D)

PDATA4-P(018D)

PDATA3-P (018D)

PDATA2-P(018D)

PDATA1-P (018D)

0V

+5V

2

1

C505

0.1µ 50

0V

+5V

1

12

12

12

12

12

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

SG

20

SG

21

SG

22

SG

23

SG

24

SG

25

SG

26

SG

27

SG

28

SG

29

SG

30

SG

33

N/C

15

N/C

34

Y

A

B

C

D

CN4

STB-N

E

IPRIME-N

F

G

H

SELIN-N

AUTOFEED-P

CN4

CN4

CN4

31

36

14

R37

R35

R36

R43

R38

2

3.3K 0.1

3.3K 0.1

3.3K 0.1

+5V

(01XE) BUSY-P

2

R506

1K 0.1

1

1

R504

R528

12

100 0.1

1K 0.1

12

R514

21

1K 0.1

R505

12

3.3K 0.1

R521

12

10K 0.1

R515

12

3.3K 0.1

R522

1

10K 0.1

+5V

+5V

2

C515

1

0V

560p 50

R527

21

1K 0.1

C506

0V

2

C507

1

0V

2

C508

1

0V

560p 50

560p 50

NOMOUNTNOMOUNT

PSTB-N (018E)

IPRIME-N (018E)

2

1

1000p 50

SELIN-N (018E)

AUTOFD-N (018E)

Vcc=+5V , Ground=0V

IC7

56

OC

07

(01XE) ACK-N

(01XE) PE-P

(01XE) SEL-P

(01XE) FAULT-N

FG

Vcc=+5V , Ground=0V

Vcc=+5V , Ground=0V

Vcc=+5V , Ground=0V

Vcc=+5V , Ground=0V

Vcc=+5V , Ground=0V

IC7

13 12

OC

07

IC7

12

OC

07

IC7

34

OC

07

IC7

11 10

OC

07

IC7

98

OC

07

250

C7

12

0.01µ

0V

+5V

C17

12

12

250

0.01µ

3.3K 0.1

3.3K 0.1

R42

0

R44

3.3K 0.1

CN4

HILEVEL

35

CN4

BUSY-P

11

CN4

ACK-N

10

CN4

PE-P

12

CN4

SEL-P

13

CN4

FAULT-N

32

MIN_W:1.27mm

MIN_W:1.27mm

CN4

CN4

CN4

CN4

5V

18

FG

17

FG

37

FG

38

Figure 5-5 Main controller PCB

(HBMC-5/7) Rev. 2

D

E

F

G

Cicuit Diagram

H

1

2

- 32 -

3456 87 9X

Y

Page 35

1

+5V

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNTNOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

IC9

OSC

VOUT

LV

CAP+

CAPGND

V+

C512

21

1000p 50

8

7

5

6

2

4

3

C6

10µ 16

21+

C5

C516

10µ

0.1µ 50

16

2

2

1

1

C517

0.1µ 50

21

+

0V

0V

0V

SW1

2

1

342

1

DIPSW2 (014D)

DIPSW1 (014D)

+5V

RXD-P (01GF)

R525

12

20 0.1

R532

12

20 0.1

R534

12

20 0.1

R530

12

20 0.1

(01GF) TXD-P

(016F) XCLK-P

(06YE) RXD+

(06YF) RXD-

2

IC8

3

4

12

15

14

13

5

6

7

11

10

9

16

8

1

7660

DS8925

DIN1

DIN2

RIN1RIN2+

RIN2RIN3+

VCC

GND

VEE

DEN1

DOUT1+

DOUT1DOUT2-

ROUT1

ROUT2

ROUT3

0V

0V

0V

0V

C521

150p 50

1

2

C518

150p 50

1

2

C519

150p 50

1

2

CN5

TCS7187-01-201

CN5

6

TXD+

CN5

3

TXD-

R529

12

20 0.1

R544

12

0

R536

12

0.1200

200

R535

12

0.1

R531

12

20 0.1

CN5

1

XCLK-N

CN5

7

+5V

CN5

4

CN5

8

SG

+5V

RXD+

CN5

5

RXD-

CN5

2

CN5

FG

FG

FG

FG

9

CN5

10

CN5

11

HSK-IN

RXD+ (065B)

RXD- (065B)

23 456 87 9X

Y

A

B

C

D

E

A

B

C

D

E

F

G

H

1

F

G

Figure 5-6 Main controller PCB

(HBMC-6/7) Rev. 2

Cicuit Diagram

H

- 33 -

2

3456 87 9X

Y

Page 36

1

23 456 87 9X

Y

A

(01XG) SDB1-P

(01XG) SDB2-P

B

(01XG) DBPWM-P

C

(01XG) TR1PWM-P

D

(01XF) CHPWM-P

E

(01XG) TR2PWM-P

NOMOUNT NOMOUNT

F

(016F) DCLED

Q2

22K

2

G

H

C18

1

0.022µ 50

R32

0.1300

C19

2

0.022µ 50

R33

22K

R5

12

0

R39

1122

1K 0.1

R40

1

2

0.11K

C11

2

0.022µ 50

R41

C10

2

1

0.022µ 50

R34

12

0.1220

2

21

IC1

OC

LS07

NOMOUNT

R3

12

0

IC1

34

OC

LS07

NOMOUNT

1

1256

0.1220

R7

12

0

IC1

OC

LS07

NOMOUNT

R9

12

0

IC1

98

OC

LS07

NOMOUNT

R13

12

0

IC1

11 10

OC

LS07

NOMOUNT

R11

1

21

0.1300

12

0

IC1

13 12

OC

LS07

NOMOUNT

Vcc=+5V , Ground=0V

Q1

1

3

12

2

2SA1338

NOMOUNT

10K

R22

0.1

3

1

0V

+5V

R6

12

3.3K 0.1

R4

12

R8

12

3.3K 0.1

+5V

R10

12

510 0.1

R14

12

510 0.1

NOMOUNT NOMOUNT

R12

12

NOMOUNT

510 0.1

+24V

(016G) LED-P LED-P

+5V

C9

12

0.1µ 50

0V

CN1

High-voltage

NOMOUNT

CN1

SDB1-P

18

NOMOUNT

3.3K 0.1

CN1

SDB2-P

20

NOMOUNT

CN1

DBPWM-P

14

CN1

TR1PWM-P

8

(016F) HEATON-P

CN1

CHPWM-P

2

CN1

TR2PWM-P

4

TR-ISEN

CN1

CN1

12

3

TR-VSEN (014E) TR-VSEN

TR-ISEN (014E)

+5V

CN1

22

CN1

DCLED-P

6

CN1

TEMP TEMP (013E)

TNRSNS-N

PSIN-N

WRSNS-N

PSOUT-N PSOUT-N (014D)

CVOPN-N

CN1

CN1

CN1

CN1

CN1

CN1

CN1

13

CN1

21

CN1

19

CN1

16

CN1

1

CN1

23

5V

15

5V

17

0V

5

0V

7

0V

9

0V

10

0V

11

R16

R15

12

10K 0.1

CVOPN-N (014D)

R18

R17

12

12

10K 0.1

10K 0.1

12

10K 0.1

R19

12

100K 0.1

TNRSNS-N (014D)

PSIN-N (014D)

WRSNS-N (014D)

R545

12

4.7K 0.1

R503

12

10K 0.1

0V

R56

21

200K 0.1

+5V

R21

21

1K 0.1

R20

21

1.2K 0.1

0V

IC20

5

6

IC20

3

2

A

24V

CN2

Power

CN2

+24V

6

12+

C2

0VP

CN2

47µ 50

5

B

0VP

CN2

5V

1

+5V

CN2

NC

5V

2

CN2

0V

3

CN2

0V

4

CN2

7

2

C502

1

12+

C3

0.1µ 50

47µ 16

1

0V

+5V

8

+

-

393

7

4

C

D

0V

+5V

+5V

2

8

+

-

393

1

4

R23

1

1K 0.1

Q3

22K

2

3

22K

CN2

8

HEATON-N

E

1

0V

0V

F

G

Figure 5-7 Main controller PCB

(HBMC-7/7) Rev. 2

Cicuit Diagram

H

- 34 -

1

2

3456 87 9X

Y

Page 37

1

+5V

+5V

IC5

0V

0V

0V

CH1

0V

0V

+5V

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

OSC1

R510

R53

1

1

0

2

2

13

2

1

1

1

2

R533

C15

0.1µ 50

5.1K 0.1

1

1

2

R52

0

0

12

R51

3.6K 0.1

12

R50

12

2

C14

0.1µ 50

1

2

C12

0.1µ 50

1

2

C13

0.1µ 50

1

2

C509

0.1µ 50

1

2

C503

0.1µ 50

1

2

C511

0.1µ 50

1

2

C510

0.1µ 50

2

1

C514

0.1µ 50

1

2

C504

0.1µ 50

2

1

C513

0.1µ 50

1

2

R511

12

3

3

14

18

24

23

17

20

19

21

22

13

12

11

10

15

16

35

36

37

38

39

43

49

34

42

40

85

86

41

105

102

9

7

6

5

8

87

1

111

CH5

CH4CH6CH7

11

CH2 CH3

2

4

1

60

61

62

63

45

47

46

48

27

28

29

30

31

26

32

76

70

58

51

25

75

69

57

50

33

44

106

104

103

108

107

PST592

VCC

GND

OUT

CST10.0MTW

CST

0

R526

12

150 0.1

10K 0.1

CH8

SP1 (Short-plug)

SP1 SP1 SP1

123

AB

(074G) CVOPN-N

(075F) TNRSNS-N

(075G) WRSNS-N

(075G) PSOUT-N

(075F) PSIN-N

(065D) DIPSW2

(065D) DIPSW1

(075F) TEMP

(016F) THCHK-N

(075E) TR-VSEN

(075E) TR-ISEN

GND1

GND2

GND3

GND4

GND5 PU00

P40

P41

P42

P43

P44

P45

P46

P20

P21

P24

P25

P27

INT0

INT1

WRN

RDN

ALE

AD0

AD1

AD2

AD3

AD4

AD5

AD6

AD7

A8

A9

A10

A11

A12

A13

A14

A15

ROCS

CPCK

65917

(1/2)

GND6

GND7

VDD1

VDD2

VDD3

VDD4

VDD5

VDD6

VDD7

AGND

AVDD

AI0

AI1

AI2

AI3

AI4

P30

P31

P32

P33

P34

P35

P36

P37

RSTN

EAN

CPEN

TEST

OSC0

OSC1

IC6

CHPW

DBPW

T2PW

T1PW

SDB2

SDB1

RMON

RMP1

RMP2

DMON

DMP1

DMP2

VSB4

VSB3

VSB2

VSB1

VLDP

VCLK

VD0P

VD1P

FLTN

SELP

PEP

BSYP

ACKN

DWRN

CASN

RAS0

RAS1

RAS2

DA7

DA6

DA5

DA4

DA3

DA2

DA1

DA0

DA10

DA9

DA8

65917

(2/2)

PSBN

AFXN

SLIN

IPRN

PDT2

PDT1

PDT3

PDT4

PDT5

PDT6

PDT7

PDT8

DD0

DD3

DD2

DD1

IC6

LED-P (074F)

XCLK-P (065B)

HEATON-P (075D)

FANALM-N (03XG)

EEPRMDT-P (047A)

EEPRMCS-P (047B)

EEPRMCLK-P (048C)

AD00-P (027B)

AD01-P (027B)

AD02-P (027B)

AD03-P (027B)

AD04-P (027B)

AD05-P (027B)

AD06-P (027B)

AD07-P (027B)

A08-P (02XB)

A09-P (02XB)

A10-P (02XB)

A11-P (02XB)

A12-P (02XB)

A13-P (02XB)

A14-P (02XB)

A15-P (02XB)

ROMCS-N (02XC)

RD-N (02XC)

ALE-P (027C)

FANON-P (037E)

DCLED-P (071F)

THCHK-N (013E)

TXD-P (065B)

BANK (02XB)

RXD-P (065B)

53

52

55

59

54

56

99

100

101

98

96

97

92

93

94

95

91

90

89

88

81

80

79

78

77

120

125

126

127

128

119

118

117

116

115

114

113

112

111

110

109

123

124

121

122

74

73

72

71

68

67

66

65

82

83

84

64

(024B) DD01-P

(024B) DD00-P

(024C) DD03-P

(024C) DD02-P

(054B) PDATA8-P

(054B) PDATA7-P

(054B) PDATA6-P

(054C) PDATA5-P

(054C) PDATA4-P

(054C) PDATA3-P

(054C) PDATA2-P

(054C) PDATA1-P

(054E) IPRIME-N

(054F) SELIN-N

(054G) AUTOFD-N

(054E) PSTB-N

DA10-P (024A)

DA09-P (022C)

DA08-P (022C)

DA07-P (022C)

DA06-P (022C)

DA05-P (022C)

DA04-P (022C)

DA03-P (022C)

DA02-P (022D)

DA01-P (022D)

DA00-P (022D)

RAS2-N (025D)

RAS1-N (025E)

RAS0-N (023E)

CAS-N (023E)

DWR-N (022D)

ACK-N (057E)

BUSY-P (057D)

PE-P (057E)

SEL-P (057F)

FAULT-N (057F)

VD1-P (041B)

VD0-P (041B)

VCLK-P (041B)

VLD-P (041C)

VSTB4-N (041D)

VSTB3-N (041D)

VSTB2-N (041C)

VSTB1-N (041C)

PJON-P (037B)

CHPWM-P (071D)

DBPWM-P (072C)

TR2PWM-P (071E)

TR1PWM-P (071C)

SDB2-P (071B)

SDB1-P (071A)

DMPH1-P (032C)

DMON-P (031D)

DMPH2-P (033C)

Not Mounted (HIGH-LEVEL)

MOunted (LOW-LEVEL)

SIGNAL

OPEN

EAN

Pin-No Short-Wire

MSM65917 Mode change

Tool not connected

Tool connected

Internal ROM Enternal ROM Enternal ROM

61 R53

SP1 B Side A Side A Side62

23 456 87 9X

Y

A

B

C

D

E

F

G

H

1

2

Figure 5-8 Main controller PCB

(HBMC-1/7) Rev. 3

Cicuit Diagram

- 35 -

3456 87 9X

A

B

C

D

E

F

G

H

Y

Page 38

1

+5V

+5V

+5V

0V

0V

0V

0V

CN9

Option-RAM

(01XB) DA10-P

(018B) DD00-P

(01XB) DA09-P

(01XC) DA08-P

(01XC) DA07-P

(01XC) DA06-P

(01XC) DA05-P

(01XC) DA04-P

(01XC) DA03-P

(01XC) DA02-P

(01XC) DA01-P

(01XC) DA00-P

(01XD) DWR-N

(018B) DD01-P

(018C) DD02-P

(018C) DD03-P

DRAM-A10

DRAM-A09

DRAM-A08

DRAM-A07

DRAM-A06

DRAM-A05

DRAM-A04

DRAM-A03

DRAM-A02

DRAM-A01

DRAM-A00

DRAM-D03

DRAM-D02

DRAM-D01

DRAM-D00

RAS2N

RAS1N

CASN

DRAM-WRN

OE

VCC

VCC

VCC

GND

GND

GND

GND

GND

GND

GND

GND

GND

CN9

24

CN9

25

CN9

26

CN9

27

CN9

28

CN9

29

CN9

30

CN9

12

CN9

11

21

CN9

10

CN9

9

CN9

3

CN9

2

CN9

7

CN9

6

CN9

8

CN9

1

CN9

4

CN9

5

CN9

19

CN9

17

CN9

18

CN9

13

CN9

14

CN9

15

CN9

16

CN9

20

CN9

22

CN9

23

CN9

31

CN9

32

CN9

R548

1

2

0

R546

1

2

0

R549

1

2

0

R550

1

2

0

IC11

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

WE

OE

VCC

VSS

RAS CAS

I/O4

3

22

13

423

1

2

24

25

26

5

18

17

16

15

14

12

11

10

9

I/O3

I/O2

I/O1

514400J

C520

0.1µ 50

1

2

R547

0

12

(01XD) RAS0-N

(01XD)CAS-N

(01XC) RAS2-N

(01XC) RAS1-N

<512>

<256>

DQ1DQ1

DQ2DQ2

WEWE

RASRAS

NCA9

A0A0

A1A1

A2A2

A3A3

Vcc

1

2

3

4

5

9

10

11

12

13

26

25

24

23

22

18

17

16

15

14Vcc

VssVss

DQ4DQ4

DQ3DQ3

CASCAS

OEOE

A8A8

A7A7

A6A6

A5A5

A4A4

IC11

1M Mask

27C1001

27512

IC2

1

2

3 (1)

4 (2)

5 (3)

6 (4)

7 (5)

8 (6)

9 (7)

10 (8)

11 (9)

12 (10)

13 (11)

14 (12)

15 (13)

16 (14)

NC

A16

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

D0

D1

D2

GND

VPP

A16

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DO

D1

D2

GND

-

-

A15

A12

A7

A6

A5

A4

A3

A2

A1

A0

DO

D1

D2

GND

-

-

VCC

A14

A13

A8

A9

A11

OE/VPP

A10

CE

D7

D6

D5

D4

D3

VCC

PGM

NC

A14

A13

A8

A9

A11

OE

A10

CE

D7

D6

D5

D4

D3

VCC

NC

NC

A14

A13

A8

A9

A11

OE/OE

A10

CE/CE

D7

D6

D5

D4

D3

32

31

(28) 30

(27) 29

(26) 28

(25) 27

(24) 26

(23) 25

(22) 24

(21) 23

(20) 22

(19) 21

(18) 20

(17) 19

(16) 18

(15) 17

GND

VCC

NC

VPP

CE

OE

PGM

A0

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

A14

A15

A16 Q7

21

31

24

22

1

30

32

16

2

3

29

28

4

25

23

26

27

5

6

7

8

9

10

11

12

20

19

18

17

15

14

13

Q6

Q5

Q4

Q3

Q2

Q1

Q0

(016E) RD-N

C501

0.1µ 50

1

2

(016C) ROMCS-N

Vcc=+5V, Ground=0V

SOCKET

IC2

IC3

27C1001

74LS373

1D

2Q

3Q

4Q

5Q

6Q

7Q

8Q

1Q

2D

3D

4D

5D

6D

7D

8D

EN

OC

2

1

11

18

17

14

13

8

7

4

3

5

6

9

12

15

16

19

(016D) AD07-P

(016F) BANK

(016C) A15-P

(016C) A14-P

(016C) A13-P

(016C) A12-P

(016C) A11-P

(016C) A10-P

(016C) A09-P

(016C) A08-P

(016D) AD06-P

(016D) AD05-P

(016D) AD04-P

(016D) AD03-P

(016D) AD02-P

(016D) AD01-P

(016D) AD00-P

(016E) ALE-P

23 456 87 9X

Y

A

B

C

D

E

F

G

H

1

2

3456 87 9X

Figure 5-9 Main controller PCB

(HBMC-2/7) Rev. 3

Cicuit Diagram

- 36 -

A

B

C

D

E

F

G

H

Y

Page 39

1

A

B

+5V

C

(01XF) DMON-P

D

E

R542

12

1K 0.1

2

0.1

R541

1

22K

A

2

R540

1

0.1

4.3K

0V

22K 0.1

2

1

C523

0.1µ 50

23 456 87 9X

+24V

+5V

R54

1

(01XF) DMPH1-P

0V

(01XF) DMPH2-P

R543

12

B

1

C524

0V

2

C

ZA21

NOMOUNT

50

2200p

0V

1

ZA20

CH10CH9

11

C525

12

0.1µ 50

+24V

+

C4

21

47µ 50

1

D

NOMOUNT

+5V

MIN_W:1.27

MIN_W:1.27

MIN_W:1.27mm

0Vp

26

27

17

16

25

23

22

20

21

18

19

28

15

1

14

29

30

MTD2005F

PHAA

NENA

PHAB

NENB

CR

REFA

VSA

REFB

VSB

DCAY

VCC

LGA

LGB

VMM1

VMM2

GND1

GND2

IC10

OUT1

OUT2

OUT3

OUT4

NALM

RSA

RSB

NC1

NC2

NC3

NC4

NC5

NC6

3

7

8

12

24

5

10

2

4

6

9

11

13

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

MIN_W:0.635mm

E

4M-DMOTOR

CN7

CN7

CN7

CN7

IM=0.38A

2

R1

1

2 0.5

CN7

DMPH1-P

1

DMPH1-N

2

DMPH2-P

3

DMPH2-N

4

2

R2

1

2 0.5

MIN_W:0.635mm

0Vp

(01XF) PJON-P

(01GE) FANON-P

1K

NOMOUNT

0.1

2

R55

1

Q5

22K

2

Q502

22K

2

22K

22K

1

0V

3

1

0V

NOMOUNT

R502

3

1

10K 0.1

6.2K

2

0.1

Q501

2

3

2SA1338

Q4

3

2SA1338

+24V

MIN_W:0.635

1

2

1

MIN_W:0.635

1

2

D3

1

OVP

NOMOUNT

MIN_W:0.635mm

NOMOUNT

D501

3

SS100MA80VACP

MIN_W:0.635mm

MIN_W:0.635

2

3

SS100MA80VACP

MIN_W:0.635

2

CN8

CN8

NOMOUNT

2M-Fan

CN3

1

CN3

2

CN8

2M-PJ

1

2

CN3

FANPOW

0VP

PJON

OVP

+5V

2

R5011

NOMOUNT

10K 0.1

Y

A

B

C

D

E

F

G

H

1

2

0VP

FANALM-N FANALM-N (01GF)

CN3

3

Figure 5-10 Main controller PCB

(HBMC-3/7) Rev. 3

Cicuit Diagram

- 37 -

3456 87 9X

F

G

H

Y

Page 40

1

A

(01XE) VD0-P

B

(01XE) VD1-P

(01XE) VCLK-P

23 456 87 9X

SS100MA80VKCP SS100MA80VKCP

R520

12

330

R519

12

R513

12

NOMOUNT

0

330

+5V

3

1

2

D1 D2

NOMOUNT

1

NOMOUNT

Y

(01GE) EEPRMDT-P

CN6

3

2

CN6

CN6

CN6

14F-LED

6

7

8

HDDT0-P

HDDT1-P

HDCLK-P

(01GE) EEPRMCS-P

2

R537

1

5.1K 0.1

+5V

2

1

C522

R539

12

IC4

3

DI

6

NC1

1

C8

8

VCC

5

GND1

7

NC2

0.1µ 50

4

DO

2

10K 0.1

A

B

(01XE) VLD-P

C

(01XF) VSTB1-N

(01XE) VSTB2-N

(01XE) VSTB3-N

D

(01XE) VSTB4-N

E

R512

12

0

D4

1

SS100MA80VACP SS100MA80VACP

2

3

0V

+5V

CN6

CN6

CN6

CN6

CN6

NOMOUNTNOMOUNT

D5

1

2

3

MIN_W:1.27mm

CN6

HDLD-P

9

STB1-N

10

STB2-N

11

STB3-N

12

STB4-N

13

5V

3

0V

(01GE) EEPRMCLK-P

R538

12

5.1K 0.1

0V

C

D

E

F

G

H

1

MIN_W:1.27mm

2

50

C526

1

0.1µ

MIN_W:1.27mm

0V

MIN_W:1.27mm

0VP

FG1

1

FG2

1

FG

2

1+

C1

2

10

3300µ

C16

12

0.01µ 250

MIN_W:1.27mm

C8

12

0.01µ 250

MIN_W:1.27mm

MIN_W:1.27mm

MIN_W:1.27mm

MIN_W:1.27mm

CN6

CN6

CN6

CN6

CN6

5V

4

0V

5

0VP

1

0VP

2

FG

14

Figure 5-11 Main controller PCB

(HBMC-4/7) Rev. 3

Cicuit Diagram

- 38 -

3456 87 9X

F

G

H

Y

Page 41

1

23 456 87 9X

Y

A

CN4

36F-Centro

B

STB-N

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

PDATA8-P

PDATA7-P

PDATA6-P

PDATA5-P

C

D

E

F

G

H

PDATA4-P

PDATA3-P

PDATA2-P

PDATA1-P

IPRIME-N

SELIN-N

AUTOFEED-P

+5V

9

8

7

6

5

4

3

2

2

R506

1

1

31

36

14

R30

21

22 0.1

R31

21

22 0.1

R29

21

22 0.1

R28

21

22 0.1

R25

21

22 0.1

R26

21

22 0.1

R27

21

22 0.1

R24

21

22 0.1

+5V

1K 0.1

12

100 0.1

R504

1K 0.1

12

21

1K 0.1

R505

12

3.3K 0.1

12

10K 0.1

R515

12

3.3K 0.1

10K 0.1

R528

R514

1

+5V

R521

+5V

R522

R516

R509

R507

21

21

21

3.3K 0.1

3.3K 0.1

3.3K 0.1

R527

21

1K 0.1

2

C515

1

560p 50

0V

C507

NOMOUNTNOMOUNT

C508

R508

R517

R518

21

21

21

3.3K 0.1

3.3K 0.1

3.3K 0.1

2

C506

1

1000p 50

0V

2

1

560p 50

0V

2

1

560p 50

0V

R524

R523

21

21

3.3K 0.1

3.3K 0.1

PDATA8-P(018D)

PDATA7-P (018D)

PDATA6-P(018D)

PDATA5-P (018D)

PDATA4-P(018D)

PDATA3-P (018D)

PDATA2-P(018D)

PDATA1-P (018D)

Vcc=+5V , Ground=0V

IC7

56

OC

07

PSTB-N (018E)

IPRIME-N (018E)

SELIN-N (018E)

AUTOFD-N (018E)

(01XE) BUSY-P

(01XE) ACK-N

(01XE) PE-P

(01XE) SEL-P

(01XE) FAULT-N

FG

IC7

13 12

OC

07

Vcc=+5V , Ground=0V

IC7

12

OC

07

Vcc=+5V , Ground=0V

IC7

34

OC

07

Vcc=+5V , Ground=0V

IC7

11 10

OC

07

Vcc=+5V , Ground=0V

IC7

98

OC

07

Vcc=+5V , Ground=0V

250

C7

12

0.01µ

0V

+5V

2

1

C505

0V

CN4

36F-Centro

CN4

SG

16

CN4

SG

19

0V

0.1µ 50

+5V

1

12

12

12

12

12

R37

R35

R36

R43

3.3K 0.1

R42

0

3.3K 0.1

R44

3.3K 0.1

MIN_W:1.27mm

MIN_W:1.27mm

+5V

R38

2

C17

12

3.3K 0.1

250

0.01µ

3.3K 0.1

3.3K 0.1

12

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

CN4

SG

20

SG

21

SG

22

SG

23

SG

24

SG

25

SG

26

SG

27

SG

28

SG

29

SG

30

SG

33

N/C

15

N/C

34

HILEVEL

35

BUSY-P

11

ACK-N

10

PE-P

12

SEL-P

13

FAULT-N

32

5V

18

FG

17

FG

37

FG

38

A

B

C

D

E

F

G

Figure 5-12 Main controller PCB

(HBMC-5/7) Rev. 3

Cicuit Diagram

H

1

2

- 39 -

3456 87 9X

Y

Page 42

1

+5V

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNTNOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

NOMOUNT

IC9

OSC

VOUT

LV

CAP+

CAPGND

V+

C512

21

1000p 50

8

7

5

6

2

4

3

C6

10µ 16

21+

C5

C516

10µ

0.1µ 50

16

2

2

1

1

C517

0.1µ 50

21

+

0V

0V

0V

SW1

2

1

342

1

DIPSW2 (014D)

DIPSW1 (014D)

+5V

RXD-P (01GF)

R525

12

20 0.1

R532

12

20 0.1

R534

12

20 0.1

R530

12

20 0.1

(01GF) TXD-P

(016F) XCLK-P

(06YE) RXD+

(06YF) RXD-

2

IC8

3

4

12

15

14

13

5

6

7

11

10

9

16

8

1

7660

DS8925

DIN1

DIN2

RIN1RIN2+

RIN2RIN3+

VCC

GND

VEE

DEN1

DOUT1+

DOUT1DOUT2-

ROUT1

ROUT2

ROUT3

0V

0V

0V

0V

C521

150p 50

1

2

C518

150p 50

1

2

C519

150p 50

1

2

CN5

TCS7187-01-201

CN5

6

TXD+

CN5

3

TXD-

R529

12

20 0.1

R544

12

0

R536

12

0.1200

200

R535

12

0.1

R531

12

20 0.1

CN5

1

XCLK-N

CN5

7

+5V

CN5

4

CN5

8

SG

+5V

RXD+

CN5

5

RXD-

CN5

2

CN5

FG

FG

FG

FG

9

CN5

10

CN5

11

HSK-IN

RXD+ (065B)

RXD- (065B)

23 456 87 9X

Y

A

B

C

D

E

A

B

C

D

E

F

G

H

1

F

G

Figure 5-13 Main controller PCB

(HBMC-6/7) Rev. 3

Cicuit Diagram

H

- 40 -

2

3456 87 9X

Y

Page 43

1

23 456 87 9X

+5V

CN1

Y

A

(01XG) SDB1-P

(01XG) SDB2-P

B

(01XG) DBPWM-P

C

(01XG) TR1PWM-P

D

0.022µ 50

(01XF) CHPWM-P

E

(01XG) TR2PWM-P

NOMOUNT NOMOUNT

Q2