O2Micro OZ968G Datasheet

SMBus Smart Inverter Controller

FEATURES

• Single-stage power conversion

• Constant frequency design eliminates inter-

ference with LCDs

• Built-in open-lamp protection and shortcircuit protection

• Reliable 2-winding transformer design eliminates arcing failures and the need for foldback wiring

• 32-level dimming and 256-level contrast

control via SMBus

• High efficiency, 90% typical

• Supports both floating secondary and

grounded secondary designs

ORDERING INFORMATION

OZ968G - 16-pin plastic SOP

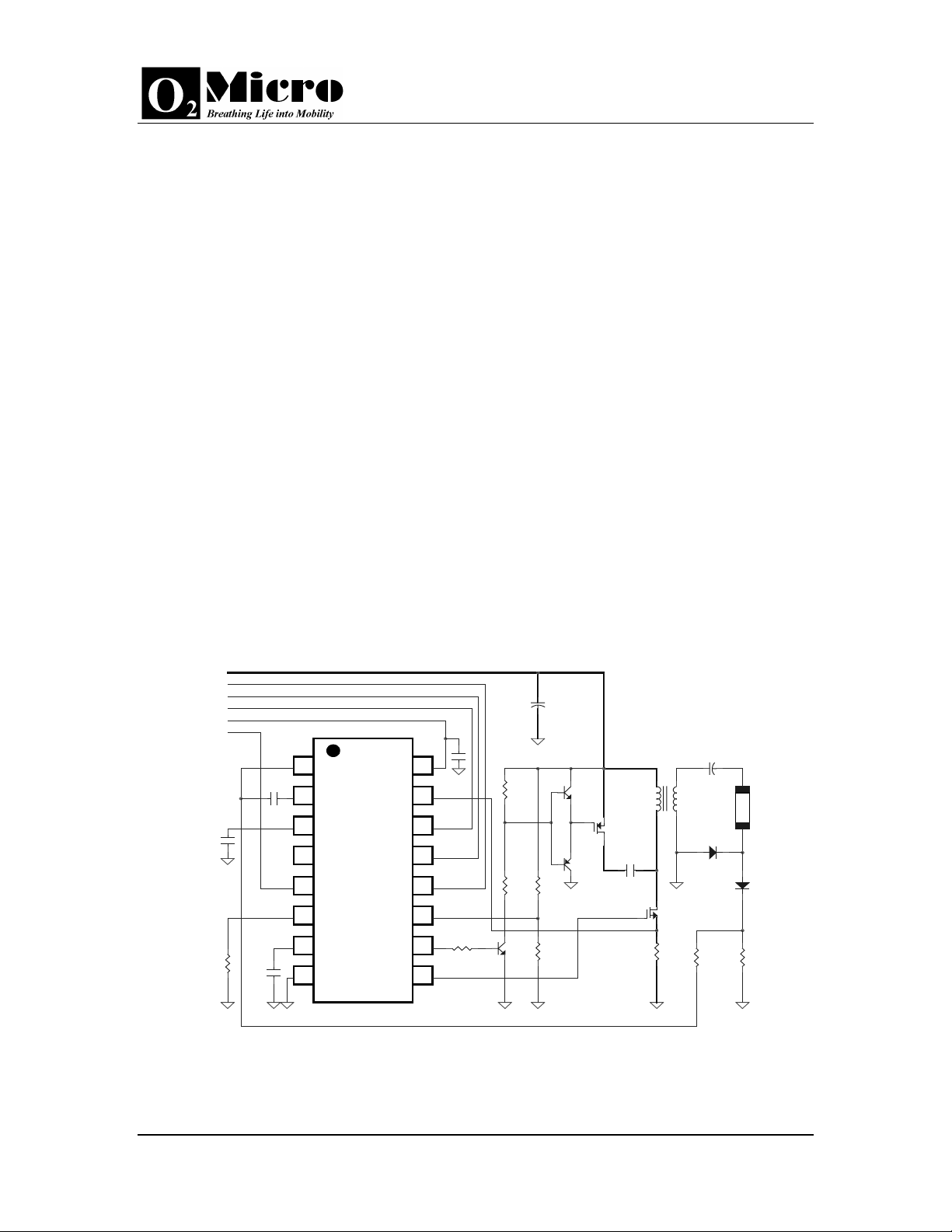

TYPICAL APPLICATION CIRCUIT

20V

SMBCLCK

SMBDATA

ENABLE

5V

CONTRAST

0.47u

1

C2

2

0.1u

C3

R2

120k

C4

220p

CMP

3

SST

4

ADJ

5

CNT

6

RT

7

CT

89

GND NDR

OZ968

VDD

SCP

VSEQ

SMBD

SMBC

OVP

PDR

C5

0.1u

16FB

15

14

13

12

11

R8

10

10k

OZ968

GENERAL DESCRIPTION

The OZ968 is a unique single-stage, highefficiency, CCFL backlight controller. It drives a

zero-voltage-switching circuit and provides a

near sinusoidal output voltage and current waveforms for a CCFL backlight. Typical operating

frequency ranges from 30KHz to 100KHz. These

advances drive the OZ968 beyond comparable

conventional inverter designs with two power

conversion stages (one operates at a variable

frequency, the other at a constant frequency).

Operating in a PWM push-pull drive, the transformer in an OZ968 backlight inverter requires

only one primary winding and one secondary

winding. The secondary winding requires no foldback treatment.

The OZ968 supports a bi-directional, two-wire

bus, data transmission protocol to control dimming (32 levels) and contrast (256 levels). Supply current is 1mA in active mode, 150µA in

standby mode.

The OZ968 is available in a 16-pin SOP package. It is specified over the commercial temperature range 0oC to +70oC.

C1

47u/

25v

C6

1:40

Q1

Si4559EY/

R7

0.1ohm

22p/3KV

CCFL

D1

1N4148

N

D2

1N4148

R10

R9

100k

1k

R3

3.3k

R6

2.2k

Q5

3904

Q4

3904

Q2

Si4559EY/P

Q3

3906

R4

200k

R5

10k

C7

4.7u

Figure 1. Typical Application Circuit

06/15/00 OZ968-SF-1.5 Page 1

Copyright 1999 by O

Micro All Rights Reserved U.S. Patent #5,619,402

2

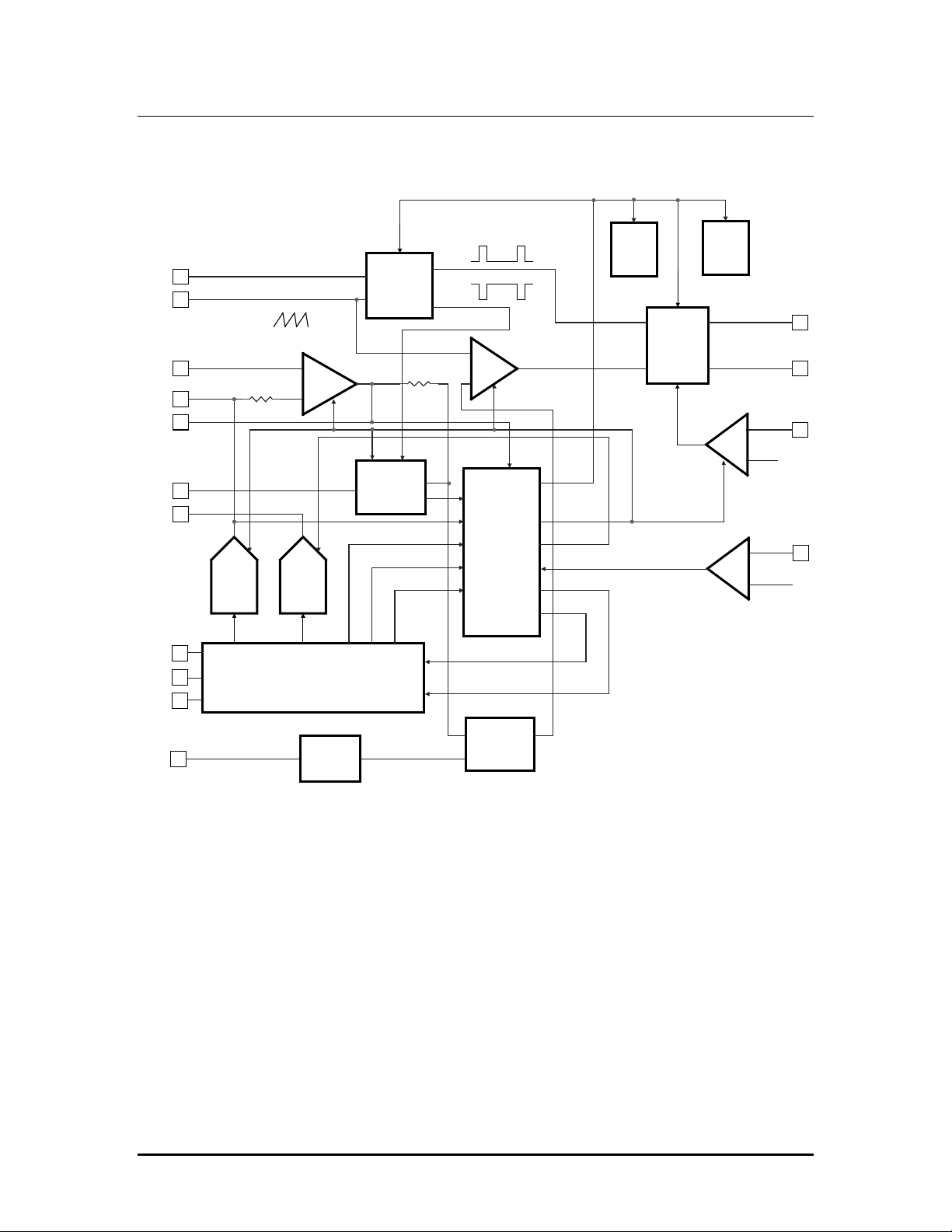

FUNCTIONAL BLOCK DIAGRAM

OZ968

RT

CT

FB

ADJ

CMP

SST

CNT

SMBC

SMBD

VSEQ

Brightness

DAC

5bit

data

ramp

40K

Contrast

DAC

8bit

data

SMB INTERFACE

clki

OSC

-

EA

160K

clk

Reset

Comparator

+

-

IBIAS REF

set

reset

Break

Before

Make

F/F

Qp

Qn

PDR

NDR

+

Slow

Start

lcd_susp

csusp

bsusp

+

OVP

-

SCP

+

See P.8,

Section 9

vd

iss

Protections

poff

pofbr

pofcnt

-

xolp_ok

xscp_ok

OVP

SCP

0.5V

CLAMP

OVP

OVP

Figure 2. Functional Block Diagram

OZ968-SF-1.5 Page 2

Loading...

Loading...