High-Efficiency Inverter Controller

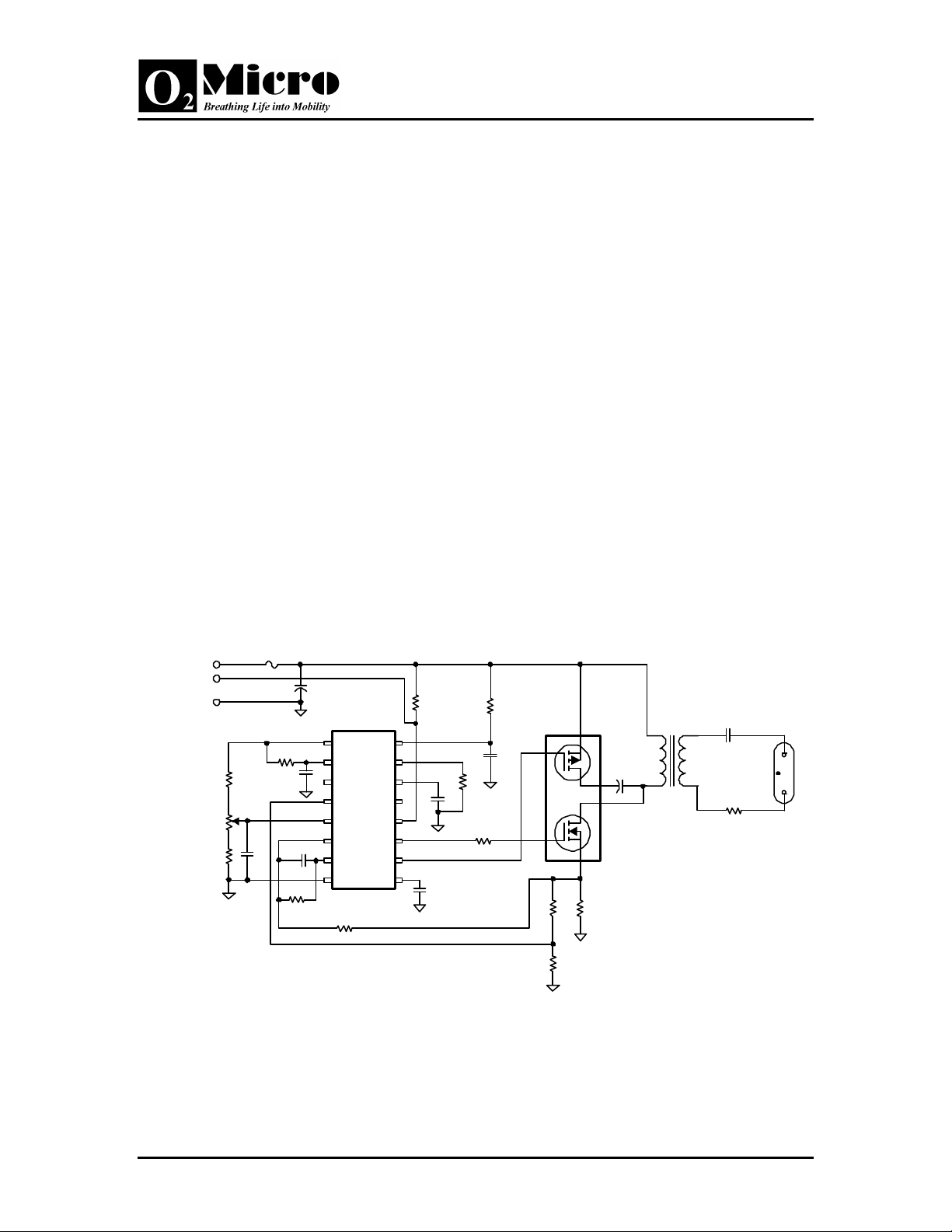

Figure 1. Typical Floating Secondary Application

FEATURES

• Single-stage power conversion, input voltage

range of 5V to 18V

• Reduces the number of components and board

size by 30% compared with conventional design

• Supports both floating and grounded secondary

designs

• 90% efficiency vs. typical 75% efficiency of

conventional designs

• Internal open-lamp and short-circuit protections

• Wide dimming range

• Supports synchronization among multiple

inverter modules

• Reliable 2-winding transformer design,

eliminates arcing problems

• Constant frequency, symmetrical, sinusoidal

drive

ORDERING INFORMATION

OZ962R - 16 lead TSSOP

OZ962G - 16-pin plastic SOP

TYPICAL APPLICATION CIRCUIT

VDD (+12V)

ENA

GND

CN1

R2

10K

R3

5.1K

F1

1A Fast Fuse

R9

R1

220K

200K

C2

0.1u

C9

.01u

R11

+

-

C3

330p

1M

C1

22u

25V

R5

RT

CT

SST

10K

16

15

14

C5

13

220p

12

11

10

9

0.1u

REF

OVP

NC

SCP

ADJ

FB

CMP

GND

R4

15K

OZ962G

U1

VDD

CLK

ENA

NDR

PDR

1

2

3

4

5

6

7

8

R7

100K

R6

30

C4

OZ962

GENERAL DESCRIPTION

The OZ962 is a unique high-efficiency, CCFL

backlight controller. It generates symmetrical,

near sinusoidal output voltage and current

waveforms for driving a CCFL backlight. The

OZ962 operates in a single, constant frequency,

pulse-width-modulation (PWM) mode. Typical

operating frequency ranges between 30 KHz to

100 KHz, depending on the CCFL and the

transformer’s characteristics.

Operating in a PWM push-pull manner, the

transformer in the OZ962 backlight inverter

requires only one primary winding and one

secondary winding, with the secondary winding

requiring no fold-back treatment.

The OZ962 is available in both 16-pin SOIC and

TSSOP packages. It is specified over the

commercial temperature range: 0 oC to +70 oC.

R10

100

C7

68p

2200T33T

3KV

3.5W

R14

1.0K

C8

0.22u

4

SI4559EY

2

R12

750

3 U2

Q2

Q1

1

R8

0.5

5,6

7,8

C6 2.2u

50V

+-

* *

03/01/00 OZ962-SF -2.7 Page 1

Copyright 1999 by O2Micro All Rights Reserved U.S. Patent #5,619,402

R13

100

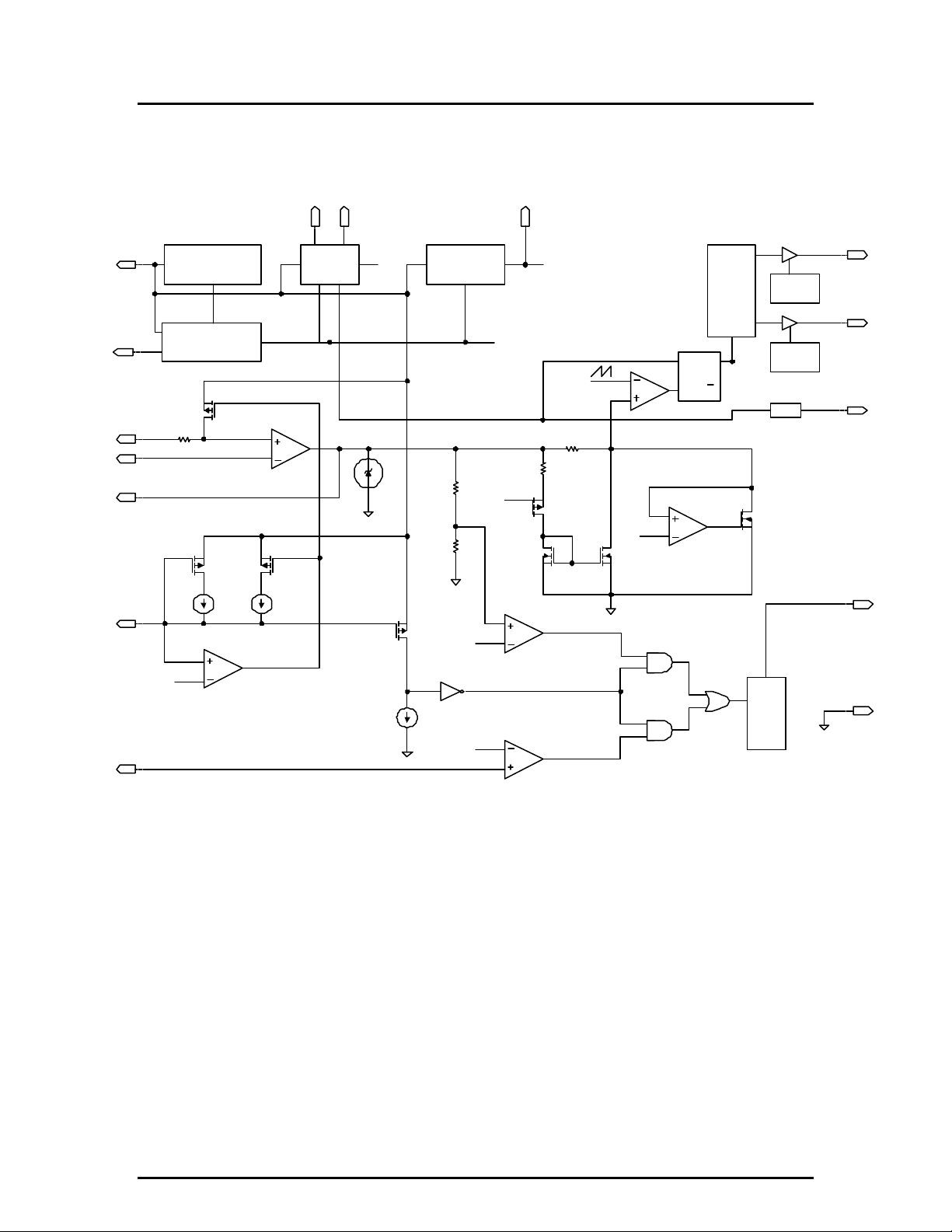

FUNCTIONAL BLOCK DIAGRAM

Note:

UVL – Under Voltage Lockout

OZ962

VDD(16)

REF(1)

ADJ(5)

FB(6)

CMP(7)

SST(9)

Under Voltage

Lockout

Band Gap

Reference

40k

3µA

10µA

Ct(14) Rt(15)

Error

Amp.

OSC

Vcmp

Vdd

SST

RAMP

3V

OVP Voltage

Generator

1k

9k

OVP

OVP(2)

OVP

OVP=Vref-(Vdd - 1)(12.5/150)

D=1.1(OVP)/2.5 - 0.2

Vref (2.5V)

RAMP

30k

SST

60k

OSC

Ve

Ve=Vcmp-2*(Vcmp-SST-Vgs)

OVP

SQRQ

Break

Before

Make

P-Clamp

Dmax

Clamp

N-Clamp

1/2F

NDR(11)

PDR(10)

CLK(13)

ENA(12)

2.0v

SCP(4)

OVP – Over Voltage Protection

SCP – Short-Circuit Protection

2µA

SCP & OVP inhibited during

start-up

ADJ

Figure 2. Functional Block Diagram

OVP

SCP

UVL

shut

down

latch

GND(8)

OZ962-SF -2.7 Page 2

Loading...

Loading...