FEATURES

• ACPI-PCI Bus Power Management Interface

Specification Rev 1.1 Compliant

• Supports OnNow LAN wakeup, OnNow Ring Indicate,

PCI CLKRUN#, PME#, and CardBus CCLKRUN#

• Compliant with PCI specification v2.2, 2000 PC Card

Standard 7.1

• Yenta™ PCI to PCMCIA CardBus Bridge register

compatible

• ExCA (Exchangeable Card Architecture) compatible

registers mappable in memory and I/O space

• Intel

• Supports PCMCIA_ATA Specification

• Supports 5V/3.3V PC Cards and 3.3V CardBus cards

• Supports two PC Card or CardBus slots with hot

• Supports multiple FIFOs for PCI/CardBus data transfer

• Supports Direct Memory Access for PC/PCI and

• Programmable interrupt protocol: PCI, PCI+ISA,

• Win’98 IRQ and PC-98/99 compliant

• Supports parallel or serial interface for socket power

• Zoomed Video Support; Zoomed Video Buffer Enable

• D3

• 3.3Vaux Power Support

• Integrated PC 98/99 -Subsystem Vendor ID support,

• LED Activity Pins

ORDERING INFORMATION

OZ6933T – 208 pin TQFP

OZ6933B – 208 pin Mini-BGA

GENERAL DESCRIPTION

The OZ6933 is an ACPI and PC98/99 logo certified, high

performance, dual slot PC Card controller with a synchronous 32-bit bus master/target PCI interface. This PC Card

to PCI bridge host controller is compliant with the 2000 PC

Card Standard. This standard incorporates the new 32-bit

TM

82365SL PCIC Register Compatible

insertion and removal

PCI/Way on PC Card socket

PCI/Way, or PC/PCI interrupt signaling modes

control including devices from Micrel and TI

Pins

state PME# wakeup support

cold

with auto lock bit

OZ6933

ACPI CardBus Controller

CardBus while retaining the 16-bit PC Card specification as

defined by PCMCIA release 2.1. CardBus is intended to

support “temporal” add-in functions on PC Cards, such as

Memory cards, Network interfaces, FAX/Modems and other

wireless communication cards, etc. The high performance

and capability of the CardBus interface will enable the new

development of many new functions and applications.

The OZ6933 CardBus controller is compliant with the latest

ACPI-PCI Bus Power Management Interface Specification.

It supports all four power states and the PME# function for

maximum power savings and ACPI compliance. Additional

compliance to OnNow Power Management includes D3

state support, paving the way for low sleep state power

consumption and minimized resume times. To allow host

software to reduce power consumption further, the OZ6933

provides a power-down mode in which internal clock

distribution and the PC Card socket clocks are stopped. An

advanced CMOS process is also used to minimize system

power consumption.

The OZ6933 dual PCMCIA socket supports two 3.3V/5V

8/16-bit PC Card R2 cards or 32-bit CardBus R3 cards. The

R2 card support is compatible with the Intel 82365SL PCIC

controller, and the R3 card support is fully compliant with

the 2000 PC Card Standard CardBus specification. The

OZ6933 is a stand alone device, which means that it does

not require an additional buffer chip for the PC Card socket

interface. In addition, the OZ6933 supports dynamic PC

Card hot insertion and removal, with auto configuration

capabilities.

The OZ6933 is fully compliant with the 33Mhz PCI Bus

specification, v2.2. It supports a master device with internal CardBus direct data transfer. The OZ6933 implements a

FIFO data buffer architecture between the PCI bus and

CardBus socket interface to enhance data transfers to

CardBus devices. The bi-directional FIFO buffer permits the

OZ6933 to accept data from a target bus (PCI or CardBus

interface) while simultaneously transferring data. This

architecture not only speeds up data transfers but also

prevents system deadlocks.

The OZ6933 is a PCMCIA R2/CardBus controller, providing

the most advanced design flexibility for PC Cards that interface with advanced notebook designs.

cold

07/20/00 OZ6933-SF-1.7 Page 1

Copyright 2000 by O2Micro All Rights Reserved

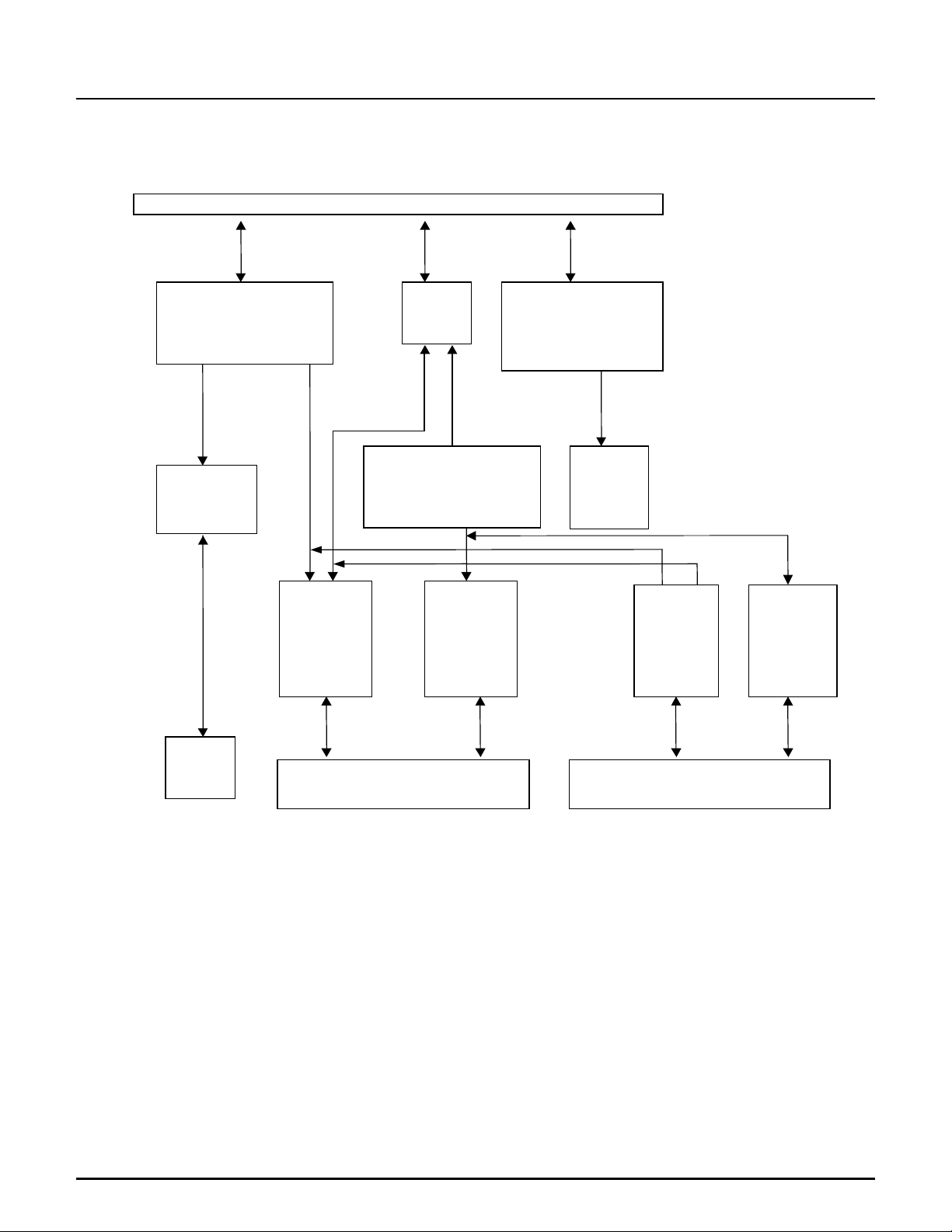

FUNCTIONAL BLOCK DIAGRAM

PCI Interface

OZ6933

PCI Configuration/

Function Control Registers

Power Switch

Control

PCI

Function Control

Configuration/

Registers

Power

Contro

Switch

l

PC Card

Machine

EXCA

8/16-Bit

16-

PC

Bit

Machin

Card

State

e

PCI

PCI

Arbite

Arbiter

r

CardBus FIFO

CardBu

Data Buffering

s

CardBus

PC Card

State

Machine

and

Arbiter

FIFO

ACPI/ OnNow

Power Management

for PC99

Interrupt

Subsystem

Interrup

t

EXCA

8/16 Bit

PC Card

State

Machine

CardBus

PC Card

State

Machine

and

Arbiter

Powe

Power

Switc

r

Switch

h

Interface

Socket A PC Card Interface

PC Card

Interface

Socket B PC Card Interface

OZ6933-SF-1.7 Page 2

OZ6933

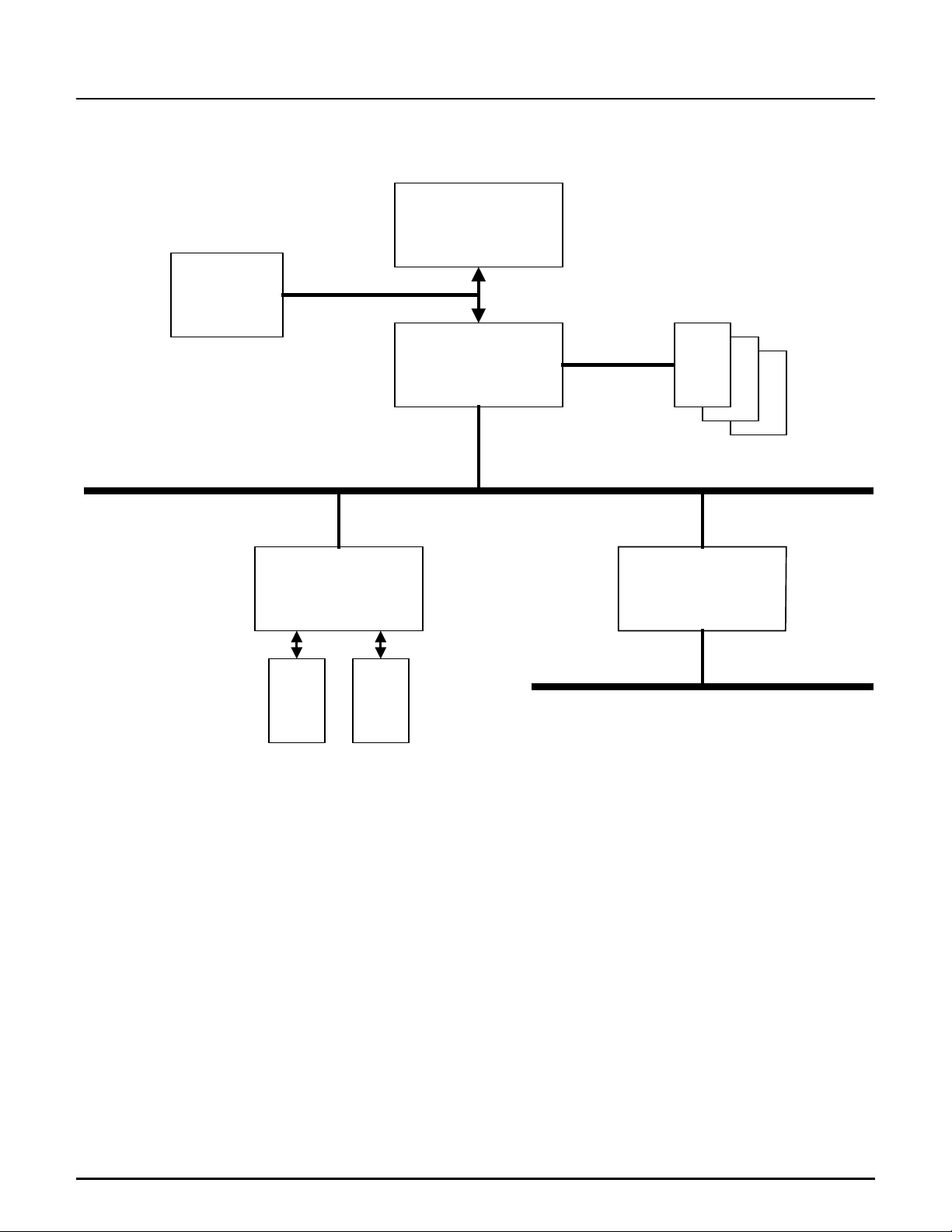

SYSTEM BLOCK DIAGRAM

The following diagram is a typical system block diagram utilizing the OZ6933 ACPI CardBus controller with other related

chipsets.

CPU

PCI Bus

VGA

AGP

OZ6933

CardBus

Controller

PC

Card

PC

Card

Memory

North Bridge

South Bridge

ISA

OZ6933-SF-1.7 Page 3

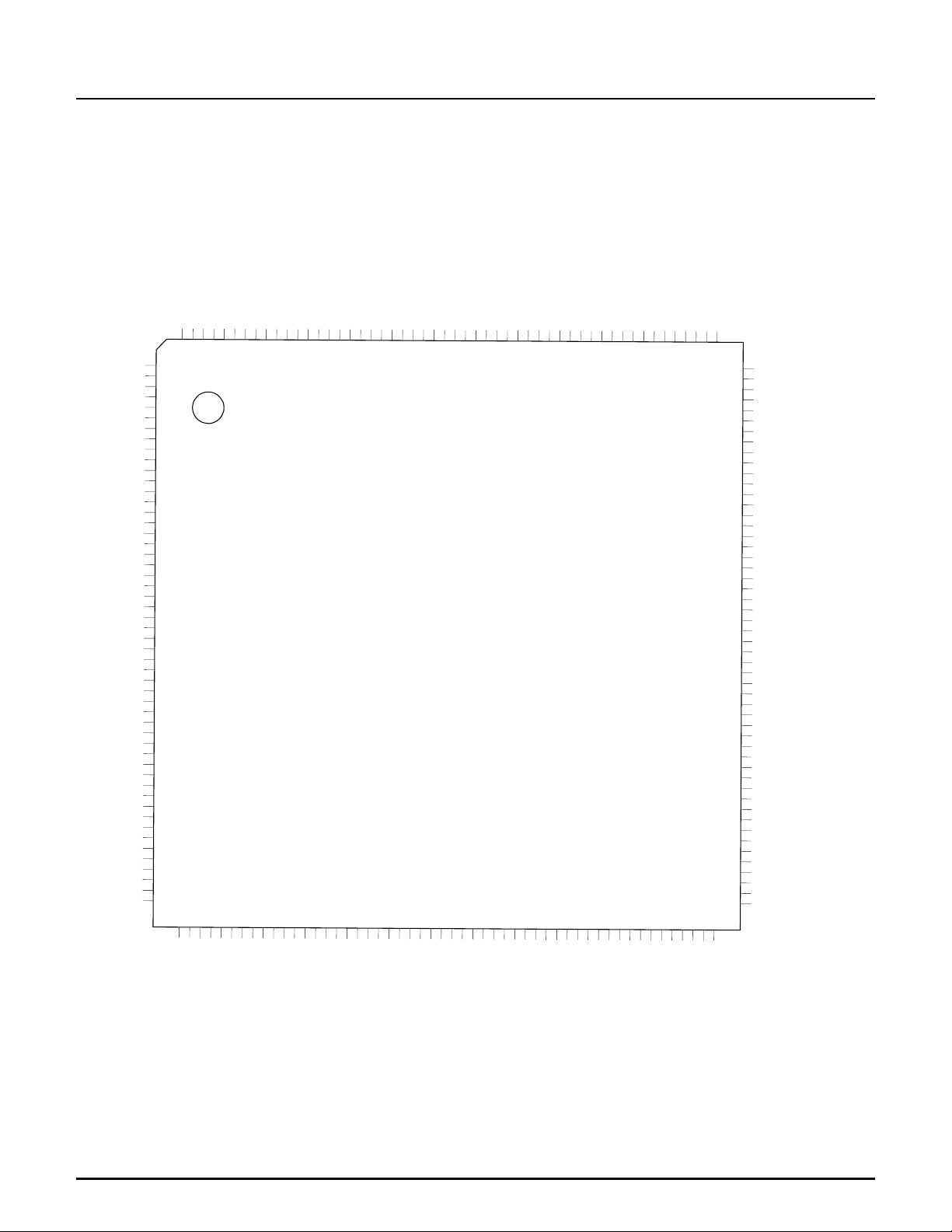

PIN DIAGRAM - 208 PIN TQFP

OZ6933

IRQ7/SIN#/B_VPP_PGM

B_RESET/CRESET#

B_WP/CCLKRUN#

IRQ14/CLKRUN#

IRQ5/SERIRQ

RST#

2

2

2

2

0

0

0

P

C

I

C

K

_

L

P

C

N

G

#

I

T

_

P

E

C

Q

R

I

_

#

1

3

A

D

0

3

A

D

P

C

C

V

I

C

_

A

D

9

2

A

D

8

2

A

D

7

2

A

D

6

2

5

2

A

D

4

2

A

D

C

/

#

B

E

3

C

R

G

O

E

_

N

D

I

D

S

E

L

A

D

3

2

A

D

2

2

A

D

1

2

A

D

0

2

A

D

9

1

P

C

V

I

C

_

C

A

8

1

D

7

1

A

D

1

A

D

6

C

/

#

B

E

2

C

R

O

E

_

D

N

G

R

F

A

M

E

#

C

N

R

G

O

E

_

D

I

R

D

Y

#

Y

T

R

D

#

E

D

V

#

S

E

L

S

P

#

T

O

P

E

R

R

#

S

E

R

R

#

P

A

R

C

/

B

#

E

1

P

C

V

I

C

_

C

A

D

5

1

A

D

1

4

A

D

3

1

2

1

A

D

1

1

A

D

1

A

D

0

C

R

G

O

E

_

N

D

A

D

9

A

D

8

C

/

B

#

E

0

A

D

7

6

A

D

P

C

V

I

C

_

C

A

D

5

4

A

D

0

1

2

3

4

5

6

7

8

9

1

1

1

1

1

1

1

1

1

1

2

2

2

2

2

2

2

2

2

2

3

3

3

3

3

3

3

3

3

9

3

0

4

1

4

2

4

3

4

4

4

5

4

6

4

7

4

4

8

9

4

0

5

1

5

2

5

5

6

7

8

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

9

0

1

2

3

4

5

6

7

8

5

5

5

5

3

4

6

5

B_SOCKET_VCC

B_CD2#/CCD2#

IRQ4/INTB#

2

0

4

5

7

B_D10/CAD31

B_D2/RFU

INTA#

2

0

3

5

5

8

9

1

1

2

2

2

0

0

0

9

9

0

1

2

8

9

6

6

6

6

3

2

1

0

IRQ11/SKTB_ACTV

B_BVD1/CSTCHG

B_D0/CAD27

B_D8/CAD28

B_D1/CAD29

B_D9/CAD30

1

1

9

9

7

6

6

6

4

5

B_A0/CAD26

1

1

1

1

1

9

9

9

9

9

2

3

4

5

1

6

6

6

7

6

6

9

8

7

0

B_INPACK#/CREQ#

B_WAIT#/CSERR#

B_REG#/CC_BE3#

B_BVD2/CAUDIO

B_A2/CAD224

B_A3/CAD23

B_A1/CAD25

1

1

1

1

1

1

8

8

7

4

8

8

7

6

O2M

7

7

6

5

8

5

O

1

8

4

i

Z

7

7

8

7

9

8

0

9

7

7

7

1

2

3

B_VS2/CVS2

B_A6/CAD20

B_A5/CAD21

B_A4/CAD22

CORE_VCC

GND

1

1

1

1

1

1

8

8

2

3

c

r

o

6

9

8

7

9

0

1

8

8

7

7

7

0

1

9

8

7

,

I

n

c

.

3

3

8

8

8

8

4

1

3

2

B_A23/CFRAME#

B_A12/CCBE2#

B_A24/CAD17

B_A25/CAD19

B_A7/CAD18

1

1

1

1

1

7

7

7

7

7

4

2

5

6

3

8

8

8

8

8

6

5

9

8

7

B_RDY_IREQ#/CINT#

B_A21/CDEVSEL#

B_A20/CSTOP#

B_A22/CTRDY#

B_A15/CIRDY#

1

1

7

7

0

1

9

9

9

1

0

2

B_WE#/CGNT#

B_A16/CCLK

1

1

1

1

1

6

6

6

6

6

9

8

7

5

6

9

9

9

9

3

4

5

6

B_SOCKET_VCC

B_A19/CBLOCK#

B_A14/CPERR#

IRQ12/PME#

1

1

1

6

6

6

2

3

4

9

9

9

9

8

7

B_A8/CCBE1#

B_A17/CAD16

B_A13/CPAR

B_A18/RFU

1

1

1

1

1

6

5

5

6

5

5

1

6

I

W

B

O

_

/

C

#

A

R

D

5

1

8

9

0

7

5

5

1

5

1

5

1

1

5

5

1

5

1

4

1

1

4

4

1

4

1

4

1

4

1

4

1

4

1

4

1

4

1

3

1

3

1

1

3

3

1

3

1

3

1

3

1

3

1

3

1

3

1

2

1

2

1

2

1

1

2

2

1

2

1

2

1

1

2

2

1

2

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

1

0

1

1

0

0

1

1

1

1

1

1

0

1

0

0

0

0

0

3

2

1

0

4

A

B

_

4

B

I

O

_

3

A

B

_

2

V

B

_

1

O

B

_

0

B

C

_

9

A

B

_

8

D

B

_

7

B

_

C

6

V

B

_

5

D

B

_

4

D

B

_

3

B

S

_

2

D

B

_

1

D

B

_

0

D

B

_

9

B

D

_

8

D

B

_

7

D

B

_

6

B

_

C

5

B

D

_

4

R

O

C

3

E

D

L

2

S

C

L

1

S

D

A

0

A

S

L

9

C

R

O

8

S

P

K

7

X

A

U

6

C

A

_

5

W

A

_

4

A

D

_

3

D

A

_

2

D

A

_

1

A

_

D

0

A

D

_

9

D

A

_

8

B

V

A

_

7

_

G

R

6

A

0

A

_

5

V

P

A

_

4

B

A

_

3

2

1

0

9

8

7

6

5

V

A

A

1

_

R

A

_

A

A

2

_

I

A

_

N

A

A

3

_

W

A

_

A

4

A

_

A

_

R

E

A

5

A

_

1

/

4

9

C

1

A

D

R

D

/

C

#

A

D

3

1

/

C

1

1

A

D

2

1

S

/

1

C

V

S

1

/

E

#

C

A

D

1

1

/

C

#

E

2

A

D

0

1

/

0

1

C

A

D

9

1

A

D

/

C

5

8

/

C

#

E

1

C

#

B

E

0

V

P

P

_

C

C

4

1

U

F

/

R

A

D

/

C

7

7

K

E

C

O

V

C

_

T

C

/

C

3

1

A

D

6

/

6

A

D

C

5

/

C

2

A

1

D

4

/

C

5

A

D

3

/

C

1

1

A

D

2

4

/

C

A

D

1

/

D

#

C

C

1

D

#

1

A

/

C

3

D

0

E

_

C

V

C

U

/

O

T

S

_

K

A

C

_

T

I

T

V

I

Y

K

/

V

C

A

_

A

T

/

B

V

_

C

T

H

/

B

_

N

G

D

E

_

U

O

_

R

T

V

C

_

C

D

/

#

C

C

2

P

/

C

C

K

L

A

/

C

0

1

D

/

R

2

U

F

9

A

D

/

C

3

A

D

/

C

2

1

/

C

8

A

D

2

/

C

0

A

D

2

D

/

S

1

T

S

S

#

T

/

C

A

D

6

2

P

V

C

_

C

A

D

/

C

2

/

C

A

D

5

2

#

E

G

/

C

C

/

4

C

2

A

D

K

#

P

A

C

/

C

A

D

3

2

A

I

T

/

C

#

S

/

C

A

D

2

2

S

E

/

T

C

/

C

A

1

2

D

T

C

#

5

#

3

C

C

V

C

#

5

C

_

#

D

2

#

R

#

U

N

1

3

0

9

8

7

C

H

G

U

D

I

O

B

E

3

#

R

/

#

E

C

Q

E

R

R

#

E

S

E

#

T

R

AD0

AD3

AD2

AD1

CORE_GND

LOCK#

A_D3/CAD0

A_SOCKET_VCC

A_CD1#/CCD1#

A_D4/CAD1

A_D11/CAD2

A_D5/CAD3

A_D12/CAD4

A_D6/CAD5

A_D13/CAD6

A_D7/CAD7

A_D14/RFU

A_CE1#/CCBE0#

A_D15/CAD8

IRQ15/RING_OUT

A_A10/CAD9

A_CE2#/CAD10

A_OE#/CAD11

A_VS1/CVS1

A_A11/CAD12

A_IORD#/CAD13

CORE_VCC

A_A9/CAD14

A_IOWR/CAD15

A_A8/CCBE1#

A_A17/CAD16

A_A13/CPAR

A_A18/RFU

A_A14/CPERR#

IRQ3/VCC3#

A_A19/CBLOCK#

A_WE#/CGNT#

A_A20/CSTOP#

A_RDY_IREQ#/CINT#

A_A21/CDEVSEL#

A_A16/CCLK

A_A22/CTRDY#

A_A15/CIRDY#

A_A23/CFRAME#

A_A12/CCBE2#

SOCKET_VCC

A_A24/CAD17

A_A7/CAD18

GND

A_A25/CAD19

A_A6/CAD20

A_VS2/CVS2

OZ6933-SF-1.7 Page 4

PIN LIST

Bold Text = Normal Default Pin Name

PCI Bus Interface Pins

Pin Name Description

AD[31:0]

C/BE[3:0]#

FRAME#

IRDY#

TRDY#

STOP#

IDSEL

DEVSEL#

PERR#

PCI Bus Address Input/Data: These

pins connect to PCI bus signals AD[31:0].

A Bus transaction c onsists of an address

phase followed by one or more data

phases.

PCI Bus Command/Byte Enable: The

command signali ng and byte enables are

multiplexed on the same pins . During the

address phase of a transaction,

C/BE[3:0]# are interpreted as the bus

commands. During the data phase,

C/BE[3:0]# are interpreted as byte

enables. The byte enables are to be val id

for the entirety of each data phase, and

they indicate which bytes in t he 32-bit data

path are to carry meaningful dat a for the

current data phase.

Cycle Frame: This input indicates to the

OZ6933 that a bus transaction is

beginning. While FRAME# is asserted,

data transfers continue. When FRAME#

is de-asserted, the transaction is in its final

phases.

Initiator Ready: This input indicates the

initiating agent’s ability to complete the

current data phase of the transaction.

IRDY# is used in conjunction with TRDY#.

Target Ready: This output indicates

target Agent’s the OZ6933’s ability to

complete the current data phase of the

transaction. TRDY# is used in conjunction

with IRDY#.

Stop: This output indicates the current

target is requesting the m aster to s top the

current transaction.

Initialization Device Select: This input is

used as chip select during configuration

read and write transactions. This is a

point-to-point signal. IDS EL can be used

as a chip selec t during configuration read

and write transactions.

Device Select: This output is driven

active LOW when the PCI address is

recognized as supported, thereby acting

as the target for the current PCI cycle.

The Target must respond before timeout

occurs or the cycle will terminate.

Parity Error: The output is driven active

LOW when a dat a parity error is detected

during a write phase.

OZ6933

Pin Number

TQFP BGA

4-5, 7-12, 1620, 22-24, 3843, 45-46, 48-

49, 51-56

13, 25, 36, 47 G1, K3, M3, R1 TTL I/O 4 -

27 K6 TTL I/O 4

29 L1 TTL I/O 4 -

30 L2 TTL I/O 4 PCI Spec

32 L5 TTL I/O 4 PCI Spec

15 H5 TTL I 4 -

31 L3 TTL I/O 4 PCI Spec

33 L6 - TO 4 PCI Spec

E1, E2, F3, F1,

G5, H6, G3,

G2, H2, H1, J1,

J2, J3, J6, K1,

K2, M5, N2,

N1, N3, N6, P1,

P3, N5, P6, R2,

R3, T1, W4,

R6, U5, P7

Input Type

TTL I/O 4 PCI Spec

Power

Rail

Drive

-

OZ6933-SF-1.7 Page 5

Loading...

Loading...