Page 1

MPC5777C Reference Manual

Addendum

Supports maskset 2N45H

Document Number: MPC5777CRMAD

Rev. 1, 12/2015

Page 2

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

2 Freescale Semiconductor, Inc.

Page 3

Contents

Section number Title Page

Chapter 1

Preface

1.1 Overview...........................................................................................................................................................................7

1.2 Device versions.................................................................................................................................................................7

1.3 Audience...........................................................................................................................................................................8

1.4 Document organization.....................................................................................................................................................8

1.5 Conventions......................................................................................................................................................................8

1.5.1 Numbering systems..............................................................................................................................................8

1.5.2 Typographic notation...........................................................................................................................................9

1.5.3 Special terms........................................................................................................................................................9

1.6 References.........................................................................................................................................................................10

Chapter 2

Platform Configuration Module (PCM)

2.1 PCM memory map and register descriptions....................................................................................................................11

2.1.1 FEC Burst Optimization Master Control Register (PCM_FBOMCR)................................................................12

2.1.2 Bus Bridge Configuration Register 1 (PCM_IAHB_BE1)..................................................................................13

2.1.3 Bus Bridge Configuration Register 2 (PCM_IAHB_BE2)..................................................................................16

Chapter 3

Modular CAN (M_CAN)

3.1 Chip-specific M_CAN information..................................................................................................................................19

3.1.1 M_CAN Message RAM allocation......................................................................................................................19

3.1.2 Introduction..........................................................................................................................................................19

3.1.3 Functional Description.........................................................................................................................................20

3.1.4 External Signals...................................................................................................................................................22

3.2 Overview...........................................................................................................................................................................23

3.2.1 Features................................................................................................................................................................23

3.2.2 Block Diagram.....................................................................................................................................................24

3.2.3 Dual Clock Sources..............................................................................................................................................26

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 3

Page 4

Section number Title Page

3.2.4 Dual Interrupt Lines.............................................................................................................................................26

3.3 Memory Map and Register Description............................................................................................................................27

3.3.1 Core Release Register (M_CAN_CREL)............................................................................................................28

3.3.2 Endian Register (M_CAN_ENDN).....................................................................................................................29

3.3.3 Fast Bit Timing and Prescaler Register (M_CAN_FBTP)..................................................................................30

3.3.4 Test Register (M_CAN_TEST)...........................................................................................................................32

3.3.5 RAM Watchdog Register (M_CAN_RWD)........................................................................................................33

3.3.6 CC Control Register (M_CAN_CCCR)..............................................................................................................34

3.3.7 Bit Timing and Prescaler Register (M_CAN_BTP)............................................................................................36

3.3.8 Timestamp Counter Configuration Register (M_CAN_TSCC)..........................................................................38

3.3.9 Timestamp Counter Value Register (M_CAN_TSCV).......................................................................................38

3.3.10 Timeout Counter Configuration Register (M_CAN_TOCC)..............................................................................39

3.3.11 Timeout Counter Value Register (M_CAN_TOCV)...........................................................................................40

3.3.12 Error Counter Register (M_CAN_ECR)..............................................................................................................41

3.3.13 Protocol Status Register (M_CAN_PSR)............................................................................................................42

3.3.14 Interrupt Register (M_CAN_IR)..........................................................................................................................45

3.3.15 Interrupt Enable Register (M_CAN_IE)..............................................................................................................49

3.3.16 Interrupt Line Select Register (M_CAN_ILS).....................................................................................................52

3.3.17 Interrupt Line Enable Register (M_CAN_ILE)...................................................................................................55

3.3.18 Global Filter Configuration Register (M_CAN_GFC)........................................................................................56

3.3.19 Standard ID Filter Configuration Register (M_CAN_SIDFC)............................................................................57

3.3.20 Extended ID Filter Configuration Register (M_CAN_XIDFC)..........................................................................58

3.3.21 Extended ID and Mask Register (M_CAN_XIDAM).........................................................................................59

3.3.22 High Priority Message Status Register (M_CAN_HPMS)..................................................................................59

3.3.23 New Data 1 Register (M_CAN_NDAT1)...........................................................................................................60

3.3.24 New Data 2 Register (M_CAN_NDAT2)...........................................................................................................61

3.3.25 Rx FIFO 0 Configuration Register (M_CAN_RXF0C)......................................................................................61

3.3.26 Rx FIFO 0 Status Register (M_CAN_RXF0S)....................................................................................................62

3.3.27 Rx FIFO 0 Acknowledge Register (M_CAN_RXF0A)......................................................................................63

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

4 Freescale Semiconductor, Inc.

Page 5

Section number Title Page

3.3.28 Rx Buffer Configuration Register (M_CAN_RXBC).........................................................................................64

3.3.29 Rx FIFO 1 Configuration Register (M_CAN_RXF1C)......................................................................................64

3.3.30 Rx FIFO 1 Status Register (M_CAN_RXF1S)....................................................................................................65

3.3.31 Rx FIFO 1 Acknowledge Register (M_CAN_RXF1A)......................................................................................66

3.3.32 Rx Buffer / FIFO Element Size Configuration Register (M_CAN_RXESC).....................................................67

3.3.33 Tx Buffer Configuration Register (M_CAN_TXBC)..........................................................................................69

3.3.34 Tx FIFO/Queue Status Register (M_CAN_TXFQS)...........................................................................................70

3.3.35 Tx Buffer Element Size Configuration (M_CAN_TXESC)................................................................................71

3.3.36 Tx Buffer Request Pending Register (M_CAN_TXBRP)...................................................................................72

3.3.37 Tx Buffer Add Request Register (M_CAN_TXBAR)........................................................................................73

3.3.38 Tx Buffer Cancellation Request Register (M_CAN_TXBCR)...........................................................................73

3.3.39 Tx Buffer Transmission Occurred Register (M_CAN_TXBTO)........................................................................74

3.3.40 Tx Buffer Cancellation Finished Register (M_CAN_TXBCF)...........................................................................74

3.3.41 Tx Buffer Transmission Interrupt Enable Register (M_CAN_TXBTIE)............................................................75

3.3.42 Tx Buffer Cancellation Finished Interrupt Enable Register (M_CAN_TXBCIE)..............................................75

3.3.43 Tx Event FIFO Configuration Register (M_CAN_TXEFC)...............................................................................76

3.3.44 Tx Event FIFO Status Register (M_CAN_TXEFS)............................................................................................77

3.3.45 Tx Event FIFO Acknowledge Register (M_CAN_TXEFA)...............................................................................78

3.4 Message RAM..................................................................................................................................................................78

3.4.1 Rx Buffer and FIFO Element...............................................................................................................................79

3.4.2 Tx Buffer Element...............................................................................................................................................81

3.4.3 Tx Event FIFO Element.......................................................................................................................................83

3.4.4 Standard Message ID Filter Element...................................................................................................................84

3.4.5 Extended Message ID Filter Element..................................................................................................................85

3.5 Functional Description......................................................................................................................................................87

3.5.1 Operating Modes..................................................................................................................................................87

3.5.2 Timestamp Generation.........................................................................................................................................96

3.5.3 Timeout Counter..................................................................................................................................................97

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 5

Page 6

Section number Title Page

3.5.4 Rx Handling.........................................................................................................................................................97

3.5.5 Tx Handling.........................................................................................................................................................108

3.5.6 FIFO Acknowledge Handling..............................................................................................................................114

3.5.7 Interface to DMA Controller................................................................................................................................114

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

6 Freescale Semiconductor, Inc.

Page 7

Chapter 1

Preface

1.1 Overview

For users of maskset 2N45H, this addendum supplements—and must be used in

conjunction with—the latest version of the MPC5777C Reference Manual. The primary

objective of this document is to define the major differences in functionality of maskset

2N45H from maskset 3N45H for software and hardware developers.

The information in this document is subject to change. As with any technical

documentation, it is the reader’s responsibility to ensure he or she is using the most recent

version of the documentation.

To locate any published errata or updates for this document, visit the Freescale Web site

at http://www.freescale.com.

1.2 Device versions

This document is necessary for users of maskset 2N45H. It describes the functionality

and programming model of maskset 2N45H that differ from maskset 3N45H.

For 2N45H, the body chapters in this addendum replace the corresponding chapters of the

latest MPC5777C Reference Manual (document number MPC5777CRM). Other chapters

in the latest MPC5777C Reference Manual accurately describe 2N45H.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 7

Page 8

Audience

1.3 Audience

This addendum is intended for system software and hardware developers and applications

programmers who want to develop products with maskset 2N45H of the MPC5777C. It is

assumed that the reader understands operating systems, microprocessor system design,

basic principles of software and hardware, and basic details of the Power Architecture®

developed by Freescale.

1.4 Document organization

This document contains two chapters whose content differs from the corresponding

chapters of the MPC5777C Reference Manual:

• Platform Configuration Module (PCM)

• Modular CAN (M_CAN)

These addendum chapters describe the indicated modules for maskset 2N45H. The

corresponding chapters of the MPC5777C Reference Manual describe the indicated

modules for maskset 3N45H.

1.5

Conventions

1.5.1 Numbering systems

The following suffixes identify different numbering systems:

This suffix Identifies a

b Binary number. For example, the binary equivalent of the number 5 is written 101b. In some cases,

binary numbers are shown with the prefix 0b.

d Decimal number. Decimal numbers are followed by this suffix only when the possibility of confusion

exists. In general, decimal numbers are shown without a suffix.

h Hexadecimal number. For example, the hexadecimal equivalent of the number 60 is written 3Ch. In

some cases, hexadecimal numbers are shown with the prefix 0x.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

8 Freescale Semiconductor, Inc.

Page 9

Chapter 1 Preface

1.5.2 Typographic notation

The following typographic notation is used throughout this document:

Example Description

placeholder, x Items in italics are placeholders for information that you provide. Italicized text is also used for

the titles of publications and for emphasis. Plain lowercase letters are also used as

placeholders for single letters and numbers.

code

SR[SCM] A mnemonic in brackets represents a named field in a register. This example refers to the

REVNO[6:4], XAD[7:0] Numbers in brackets and separated by a colon represent either:

Fixed-width type indicates text that must be typed exactly as shown. It is used for instruction

mnemonics, directives, symbols, subcommands, parameters, and operators. Fixed-width type

is also used for example code. Instruction mnemonics and directives in text and tables are

shown in all caps; for example, BSR.

Scaling Mode (SCM) field in the Status Register (SR).

• A subset of a register's named field

For example, REVNO[6:4] refers to bits 6–4 that are part of the COREREV field that

occupies bits 6–0 of the REVNO register.

• A continuous range of individual signals of a bus

For example, XAD[7:0] refers to signals 7–0 of the XAD bus.

1.5.3 Special terms

The following terms have special meanings:

Term Meaning

asserted Refers to the state of a signal as follows:

• An active-high signal is asserted when high (1).

• An active-low signal is asserted when low (0).

deasserted Refers to the state of a signal as follows:

• An active-high signal is deasserted when low (0).

• An active-low signal is deasserted when high (1).

In some cases, deasserted signals are described as negated.

reserved Refers to a memory space, register, field, or programming setting. Writes to a reserved location can

result in unpredictable functionality or behavior.

• Do not modify the default value of a reserved programming setting, such as the reset value of

a reserved register field.

• Consider undefined locations in memory to be reserved.

w1c Write 1 to clear: Refers to a register bitfield that must be written as 1 to be "cleared."

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 9

Page 10

References

1.6 References

This addendum must be used in conjunction with the latest version of the MPC5777C

Reference Manual (document number MPC5777CRM).

In addition, the following documents provide information about the operation of the

MPC5777C:

• MPC5777C Data Sheet (document number MPC5777C)

• e200z759n3 Core Reference Manual (document number e200z759n3CRM),

available at www.freescale.com

• Safety Manual for MPC5777C (document number MPC5777CSM)

• IEEE-ISTO 5001-2003 Standard for a Global Embedded Processor Interface (Nexus)

• IEEE 1149.1-2001 standard - IEEE Standard Test Access Port and Boundary-Scan

Architecture

• Power Architecture Book E V1.0, available at www.freescale.com: http://

www.freescale.com/files/32bit/doc/user_guide/BOOK_EUM.pdf

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

10 Freescale Semiconductor, Inc.

Page 11

Chapter 2

Platform Configuration Module (PCM)

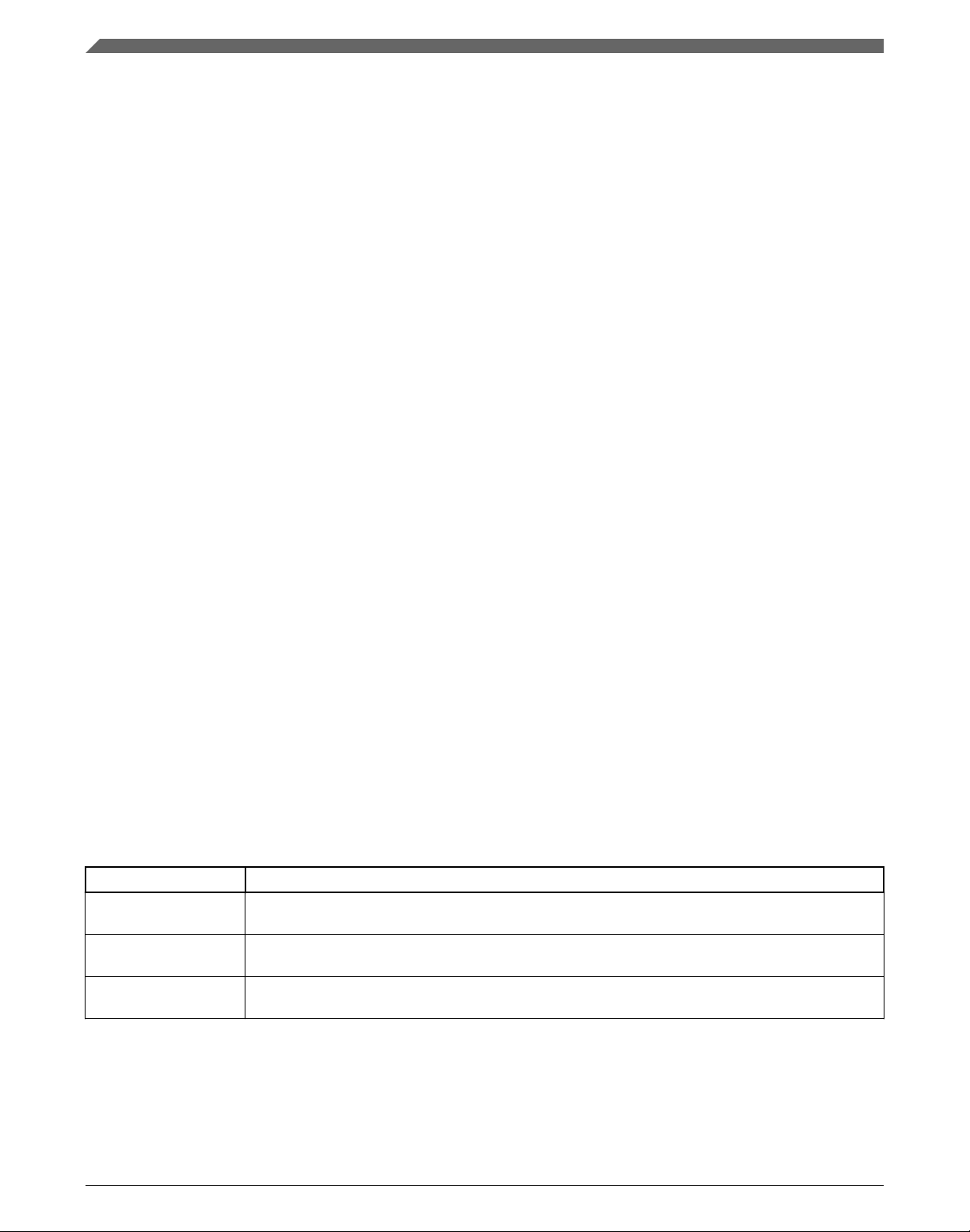

2.1 PCM memory map and register descriptions

The Platform Configuration Module contains three miscellaneous configuration registers

for the chip. Currently, the configuration registers are related to the operation of the FEC

and intelligent bus bridging gasket. The module is mapped to AIPS_0 (PBRIDGE_B) onplatform slot 27 with a base address of FFF6_C000h.

NOTE

These registers can be accessed only in supervisor mode.

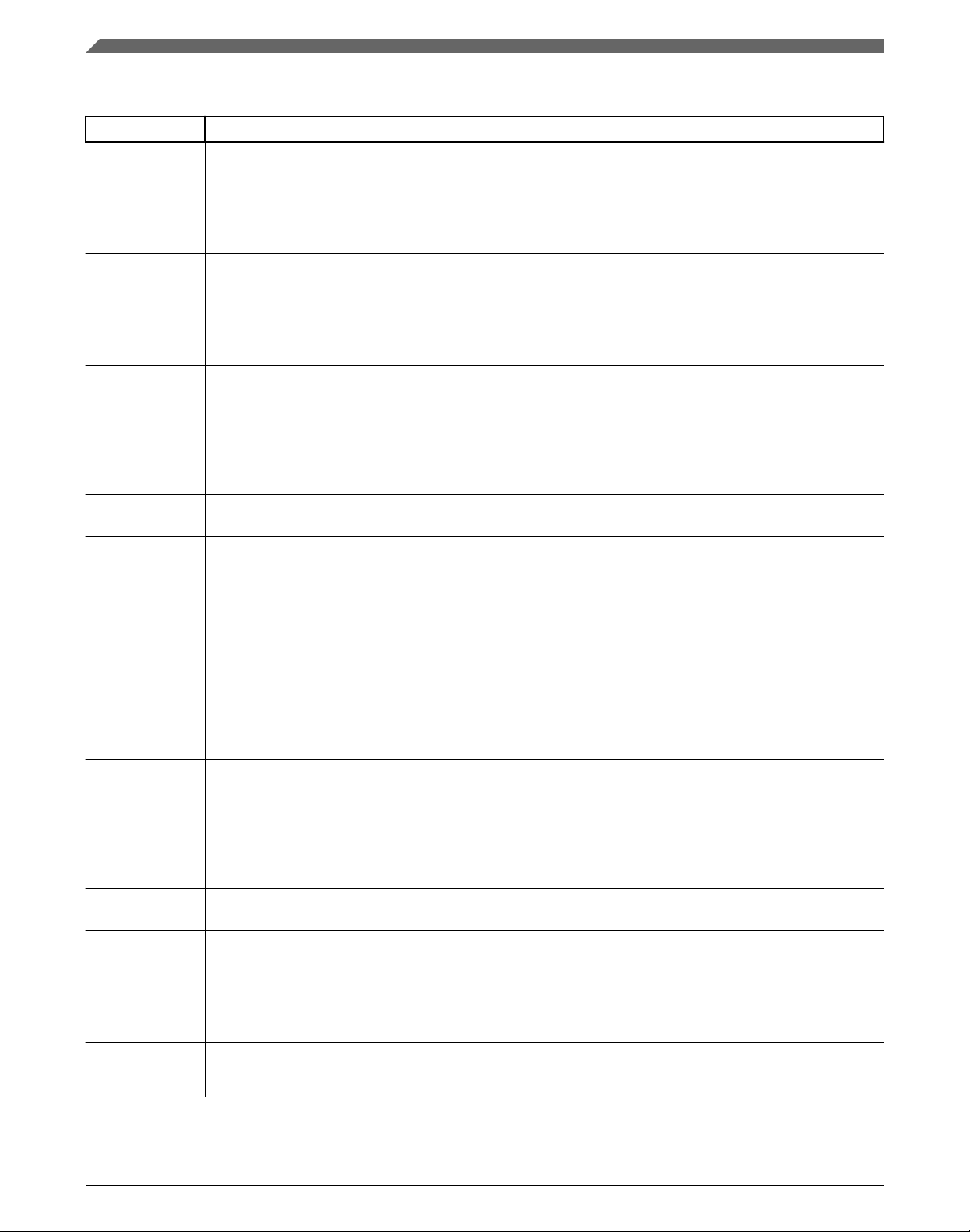

PCM memory map

Address

offset (hex)

0

4 Bus Bridge Configuration Register 1 (PCM_IAHB_BE1) 32 R/W 0707_0707h 2.1.2/13

8 Bus Bridge Configuration Register 2 (PCM_IAHB_BE2) 32 R/W 0707_0707h 2.1.3/16

FEC Burst Optimization Master Control Register

(PCM_FBOMCR)

Register name

Width

(in bits)

Access Reset value

32 R/W 0000_0000h 2.1.1/12

Section/

page

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 11

Page 12

PCM memory map and register descriptions

2.1.1 FEC Burst Optimization Master Control Register

(PCM_FBOMCR)

This register controls FEC burst optimization behavior on the system bus.

Address: 0h base + 0h offset = 0h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

W

Reset

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Bit

R

W

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

RBEN FXSBE[7:0]

WBEN

ACCERR

PCM_FBOMCR field descriptions

Field Description

0–20

Reserved

21

ACCERR

This field is reserved.

This read-only field is reserved and always has the value 0.

Accumulate Error

This field determines whether an error response for the first half of the write burst is accumulated to the

second half of the write burst or discarded. To complete the burst, the FEC interface to the system bus

responds by indicating that the first half of the burst completed without error before it actually writes the

data so that it can fetch the second half of the write data from the FIFO. When actually written onto the

system bus, the first half of the write burst can have an error. Because this half initially responded without

an error to the FIFO, the error is discarded or accumulated with the error response for the second half of

the burst.

0

0 Any error to the first half of the write burst is discarded.

1 Any actual error response to the first half of the write burst is accumulated in the second half's

response. In other words, an error response to the first half is seen in the response to the second half,

even if the second half does not contain an error.

22

WBEN

23

RBEN

Global write burst enable to XBAR slave port designated by FXSBEn

0 Write bursting to all XBAR slave ports is disabled.

1 Write bursting is enabled to any XBAR slave port whose FXSBEn bit is 1.

Global read burst enable from XBAR slave port designated by FXSBEn

0 Read bursting from all XBAR slave ports is disabled.

1 Read bursting is enabled from any XBAR slave port whose FXSBEn bit is 1.

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

12 Freescale Semiconductor, Inc.

Page 13

PCM_FBOMCR field descriptions (continued)

Field Description

24–31

FXSBE[7:0]

FEC XBAR slave burst enable

This field enables bursting by the FEC interface to the XBAR slave port controlled by each FXSBEn bit.

• When a particular FXSBEn bit is 1, the XBAR slave port enabled by that bit can support the bursts

allowed by RBEN and WBEN. RBEN enables read bursts from the XBAR slave port, and WBEN

enables write bursts to the XBAR slave port.

• When a particular FXSBEn bit is 0, the FEC interface does not burst to the XBAR slave port

controlled by that FXSBEn bit.

FXSBEn assignments to XBAR slave ports are as follows:

FXSBE0 = Flash memory

FXSBE1 = EBI

FXSBE2 = RAM

FXSBE3 = reserved

FXSBE4 = reserved

FXSBE5 = reserved

FXSBE6 = AIPS_1 (PBRIDGE_A)

FXSBE7 = AIPS_0 (PBRIDGE_B)

Chapter 2 Platform Configuration Module (PCM)

2.1.2 Bus Bridge Configuration Register 1 (PCM_IAHB_BE1)

Address: 0h base + 4h offset = 4h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

W

Reset

Reset

0 0 0 0 0 1 1 1 0 0 0 0 0 1 1 1

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Bit

R

W

0 0 0 0 0 1 1 1 0 0 0 0 0 1 1 1

Field Description

0–4

Reserved

0

D

D

D

PRE_CORE1_

BRE_CORE1_

BWE_CORE1_

0

D

D

D

PRE_CORE0_

BRE_CORE0_

BWE_CORE0_

PCM_IAHB_BE1 field descriptions

This field is reserved.

This read-only field is reserved and always has the value 0.

0

PRE_CORE1_I

0

PRE_CORE0_I

I

BWE_CORE1_

BRE_CORE1_I

I

BWE_CORE0_

BRE_CORE0_I

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 13

Page 14

PCM memory map and register descriptions

PCM_IAHB_BE1 field descriptions (continued)

Field Description

5

PRE_CORE1_D

6

BRE_CORE1_D

7

BWE_CORE1_D

8–12

Reserved

13

PRE_CORE1_I

Pending Read Enable Core1 Data

This bit controls the bus gasket’s handling of pending read transactions.

0 Pending reads are disabled.

1 Pending reads are enabled.

Burst Read Enable Core1 Data

This bit controls the bus gasket’s handling of burst read transactions.

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

Burst Write Enable Core1 Data

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

This field is reserved.

This read-only field is reserved and always has the value 0.

Pending Read Enable Core1 Instruction

This bit controls the bus gasket’s handling of pending read transactions.

14

BRE_CORE1_I

15

BWE_CORE1_I

16–20

Reserved

21

PRE_CORE0_D

22

BRE_CORE0_D

0 Pending reads are disabled.

1 Pending reads are enabled.

Burst Read Enable Core1 Instruction

This bit controls the bus gasket’s handling of burst read transactions.

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

Burst Write Enable Core1 Instruction

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

This field is reserved.

This read-only field is reserved and always has the value 0.

Pending Read Enable Core0 Data

This bit controls the bus gasket’s handling of pending read transactions.

0 Pending reads are disabled

1 Pending reads are enabled.

Burst Read Enable Core0 Data

This bit controls the bus gasket’s handling of burst read transactions.

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

14 Freescale Semiconductor, Inc.

Page 15

PCM_IAHB_BE1 field descriptions (continued)

Field Description

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

23

BWE_CORE0_D

24–28

Reserved

29

PRE_CORE0_I

30

BRE_CORE0_I

Burst Write Enable Core0 Data

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

This field is reserved.

This read-only field is reserved and always has the value 0.

Pending Read Enable Core0 Instruction

This bit controls the bus gasket’s handling of pending read transactions.

0 Pending reads are disabled.

1 Pending reads are enabled.

Burst Read Enable Core0 Instruction

This bit controls the bus gasket’s handling of burst read transactions.

Chapter 2 Platform Configuration Module (PCM)

31

BWE_CORE0_I

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

Burst Write Enable Core0 Instruction

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 15

Page 16

PCM memory map and register descriptions

2.1.3 Bus Bridge Configuration Register 2 (PCM_IAHB_BE2)

Address: 0h base + 8h offset = 8h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Reset

Bit

Reset

R

W

0 0 0 0 0 1 1 1 0 0 0 0 0 1 1 1

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

0 0 0 0 0 1 1 1 0 0 0 0 0 1 1 1

0

PRE_

BRE_

FEC

FEC

BWE_FEC

0

PRE_DMA_B

BRE_DMA_B

BWE_DMA_B

PCM_IAHB_BE2 field descriptions

Field Description

0–4

Reserved

5

PRE_FEC

6

BRE_FEC

This field is reserved.

This read-only field is reserved and always has the value 0.

Pending Read Enable FEC

This bit controls the bus gasket’s handling of pending read transactions.

0 Pending reads are disabled.

1 Pending reads are enabled.

Burst Read Enable FEC

This bit controls the bus gasket’s handling of burst read transactions.

0

PRE_

M6

BRE_M6

BWE_M6

0

PRE_DMA_A

BRE_DMA_A

BWE_DMA_A

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

7

Burst Write Enable FEC

BWE_FEC

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

8–12

Reserved

13

This field is reserved.

This read-only field is reserved and always has the value 0.

Pending Read Enable Master Port 6 Concentrator

PRE_M6

This bit controls the bus gasket’s handling of pending read transactions.

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

16 Freescale Semiconductor, Inc.

Page 17

PCM_IAHB_BE2 field descriptions (continued)

Field Description

0 Pending reads are disabled.

1 Pending reads are enabled.

14

BRE_M6

15

BWE_M6

16–20

Reserved

21

PRE_DMA_B

Burst Read Enable Master Port 6 Concentrator

This bit controls the bus gasket’s handling of burst read transactions.

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

Burst Write Enable Master Port 6 Concentrator

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

This field is reserved.

This read-only field is reserved and always has the value 0.

Pending Read Enable eDMA_B

This bit controls the bus gasket’s handling of pending read transactions.

Chapter 2 Platform Configuration Module (PCM)

22

BRE_DMA_B

23

BWE_DMA_B

24–28

Reserved

29

PRE_DMA_A

30

BRE_DMA_A

0 Pending reads are disabled

1 Pending reads are enabled.

Burst Read Enable eDMA_B

This bit controls the bus gasket’s handling of burst read transactions.

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

Burst Write Enable eDMA_B

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

This field is reserved.

This read-only field is reserved and always has the value 0.

Pending Read Enable eDMA_A

This bit controls the bus gasket’s handling of pending read transactions.

0 Pending reads are disabled.

1 Pending reads are enabled.

Burst Read Enable eDMA_A

This bit controls the bus gasket’s handling of burst read transactions.

0 Burst reads are converted into a series of single transactions on the slave side of the gasket.

1 Burst reads are optimized for best system performance.

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 17

Page 18

PCM memory map and register descriptions

PCM_IAHB_BE2 field descriptions (continued)

Field Description

31

BWE_DMA_A

Burst Write Enable eDMA_A

This bit controls the bus gasket’s handling of burst write transactions.

0 Burst writes are converted into a series of single transactions on the slave side of the gasket.

1 Burst writes are optimized for best system performance. Note this setting treats writes as “imprecise”

such that an error response on any beat of the burst is reported on the last beat.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

18 Freescale Semiconductor, Inc.

Page 19

Chapter 3

Modular CAN (M_CAN)

3.1 Chip-specific M_CAN information

3.1.1 M_CAN Message RAM allocation

On this chip, each M_CAN instance can address 1216 words in the Message RAM.

As a result, the Message RAM shared by the two M_CAN instances supports 2432

words, or 9.5 KB.

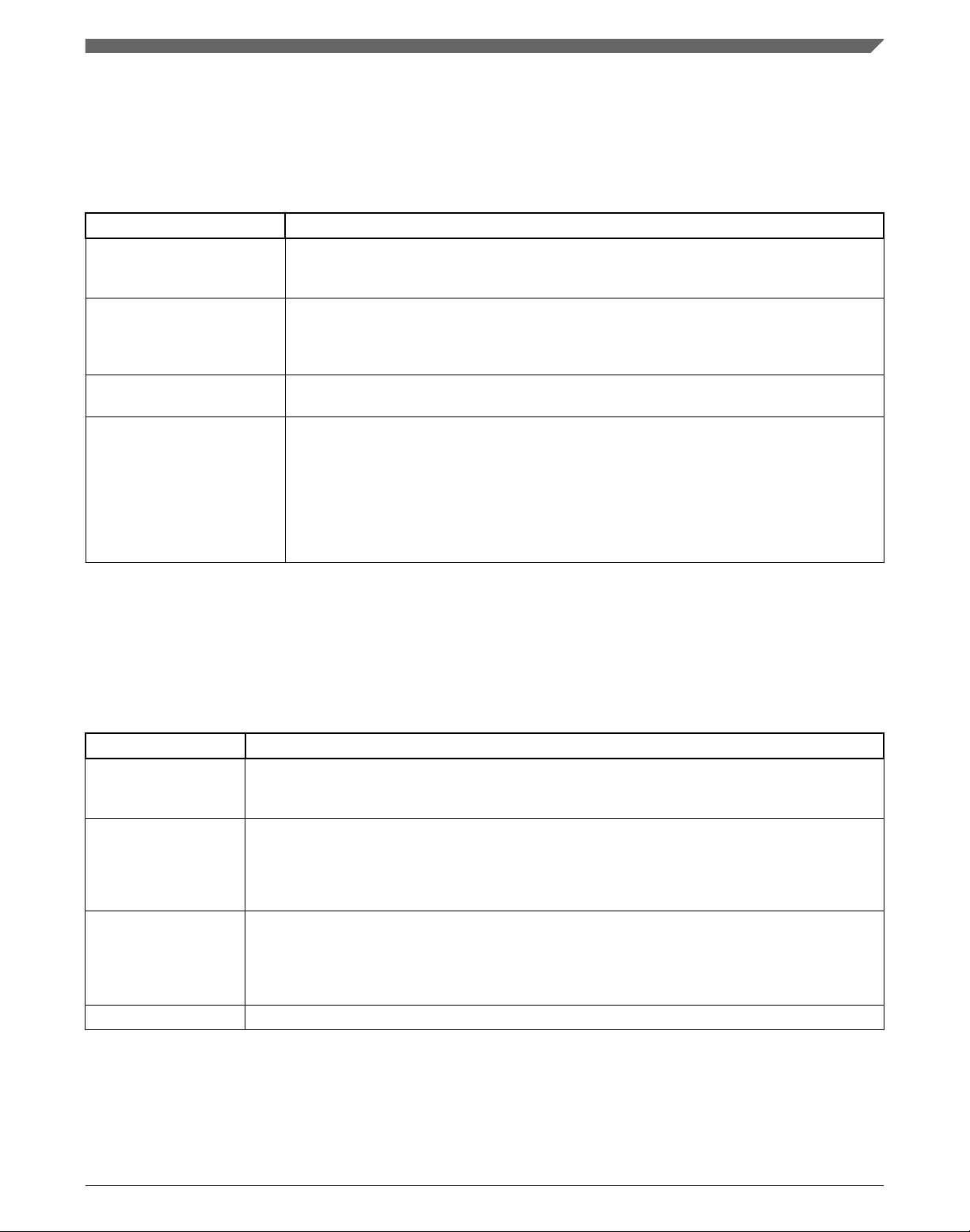

3.1.2 Introduction

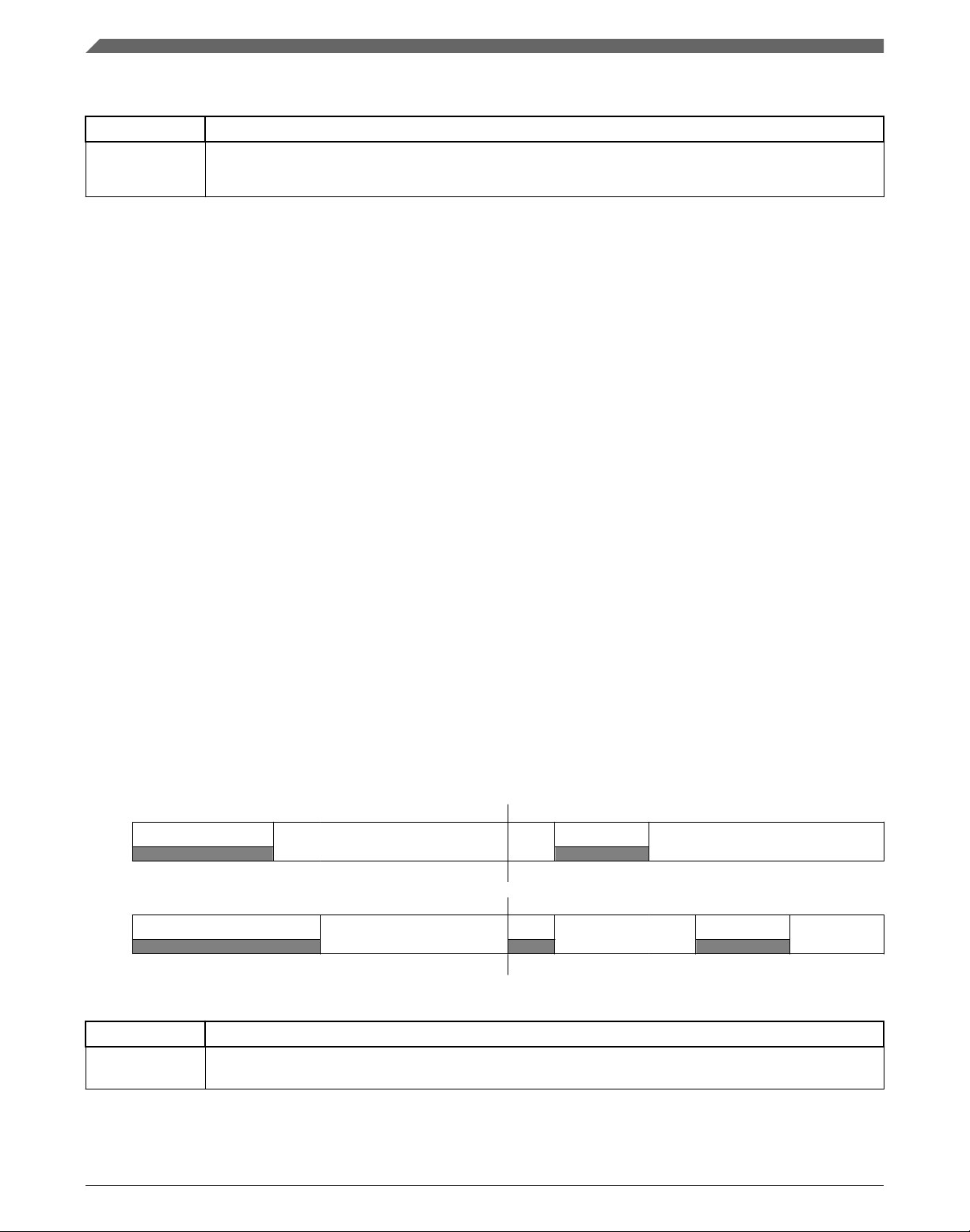

The M_CAN subsystem includes:

• Two M_CAN modules

• A Message RAM controller

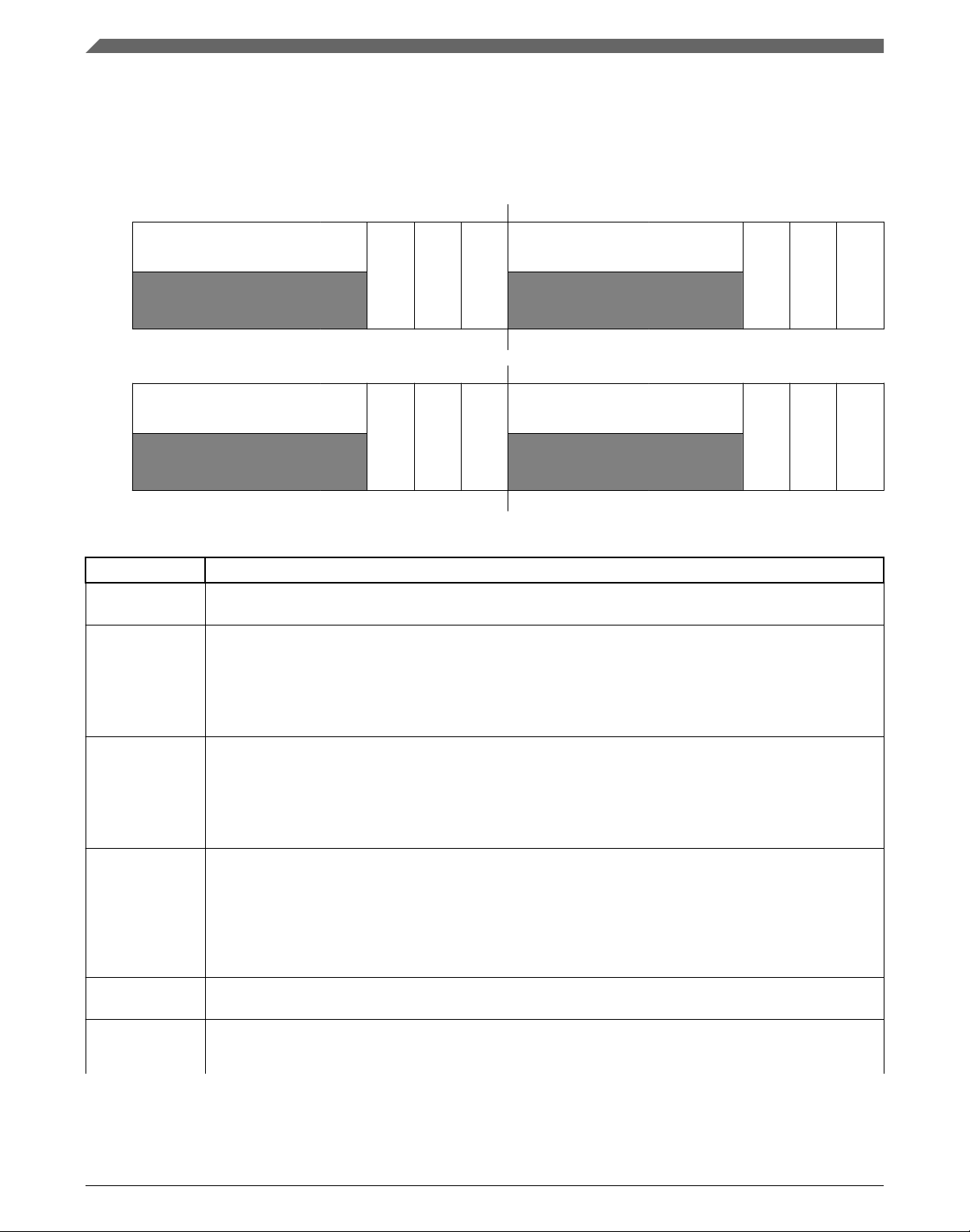

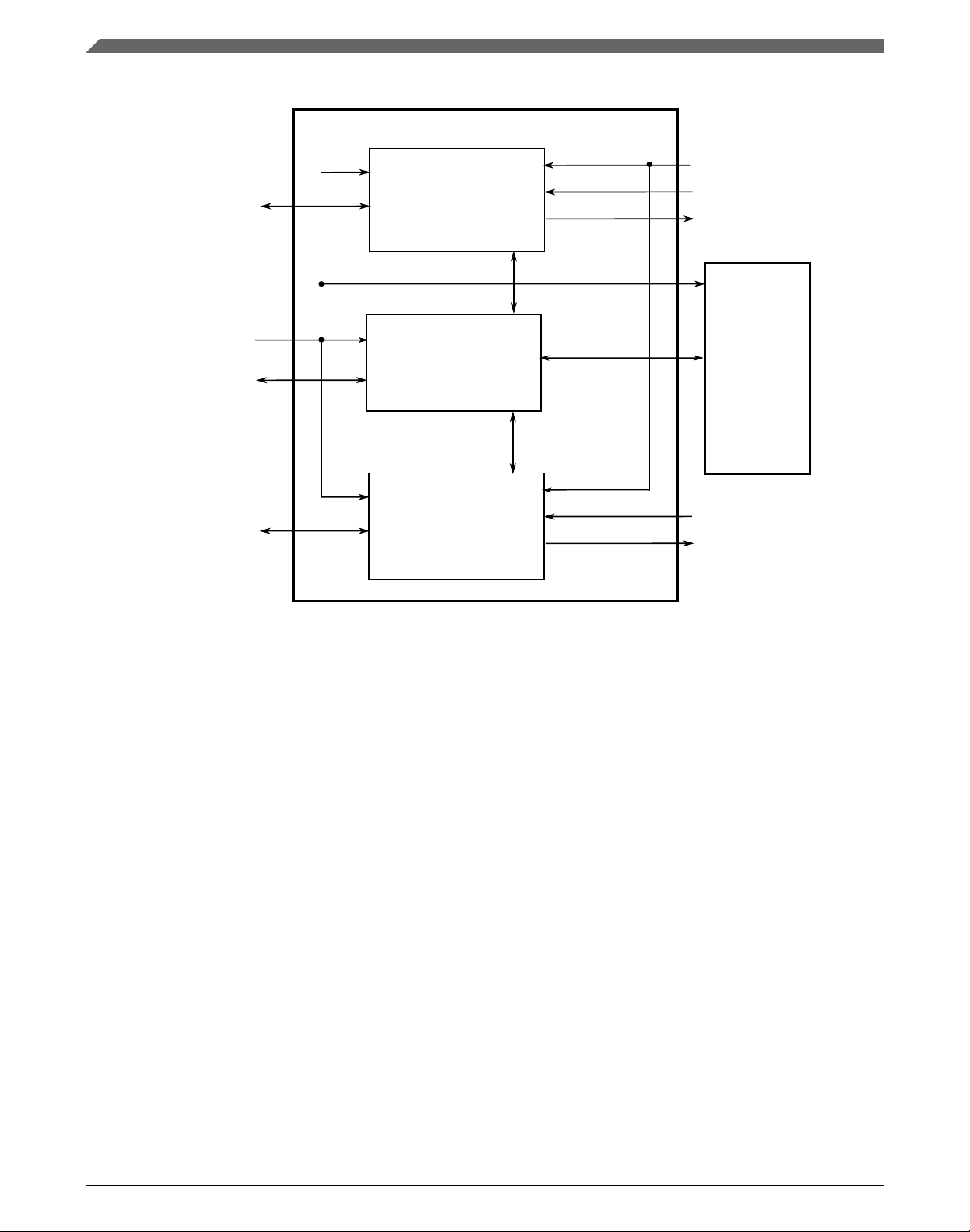

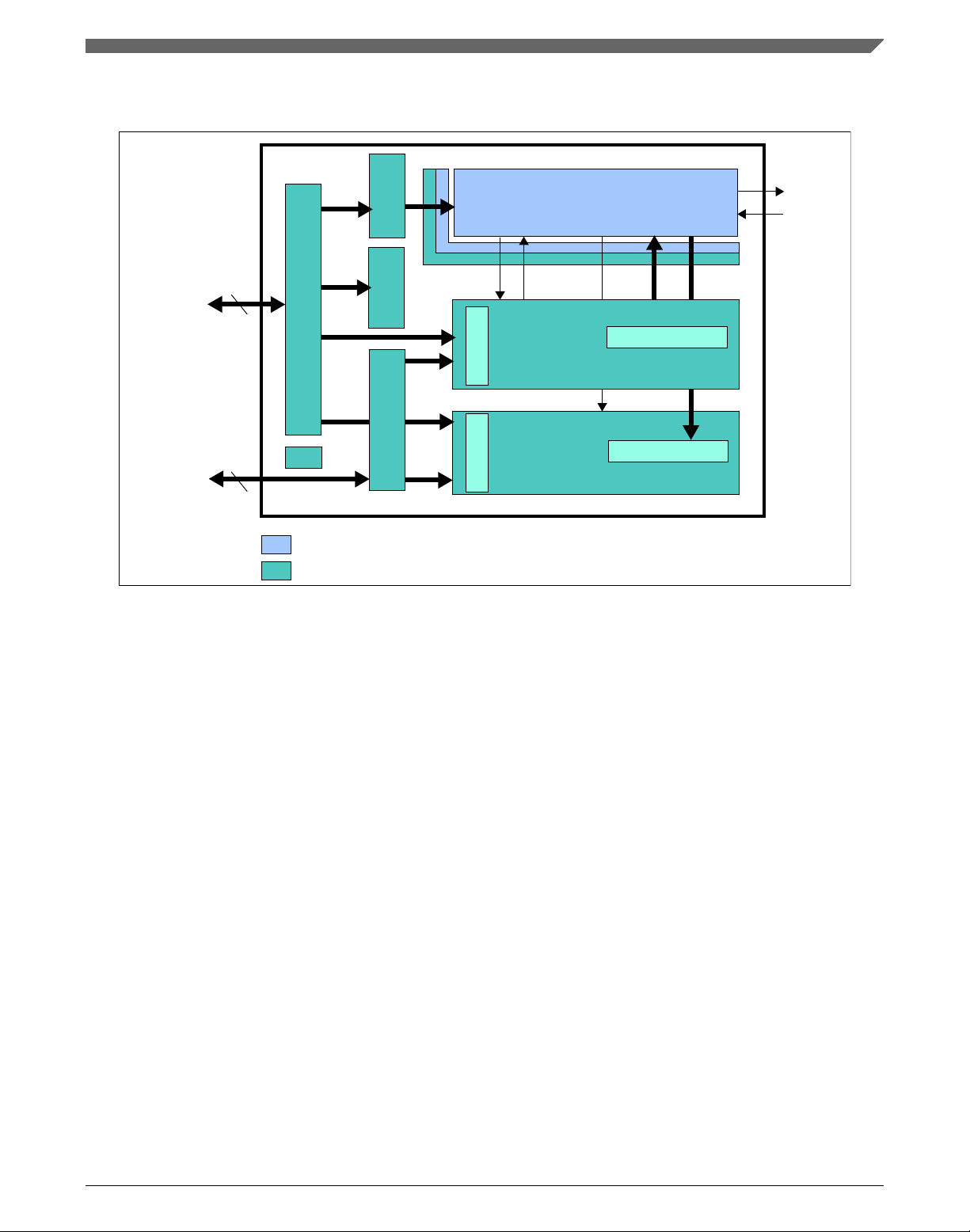

The M_CAN subsystem block diagram is shown in the following figure.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 19

Page 20

M _C AN_0

host clock

M_CAN_0_Rx

M_CAN_0_Tx

CAN protocol clock

Message RAM

Controller

External

Message

RAM

CPU reads/writes

CPU reads/writes

M_CAN Subsystem

CPU clock*

M _C AN_1

host clock

M_CAN_1_Rx

M_CAN_1_Tx

CPU reads/writes

*Refer to the Clocking chapter for M_CAN clock details.

Chip-specific M_CAN information

Figure 3-1. M_CAN subsystem block diagram

3.1.3 Functional Description

3.1.3.1 Message RAM Controller

The Message RAM Controller has the arbiter for the accesses to the external Message

RAM and the ECC (Error Code Correction) Controller for the external Message RAM

data.

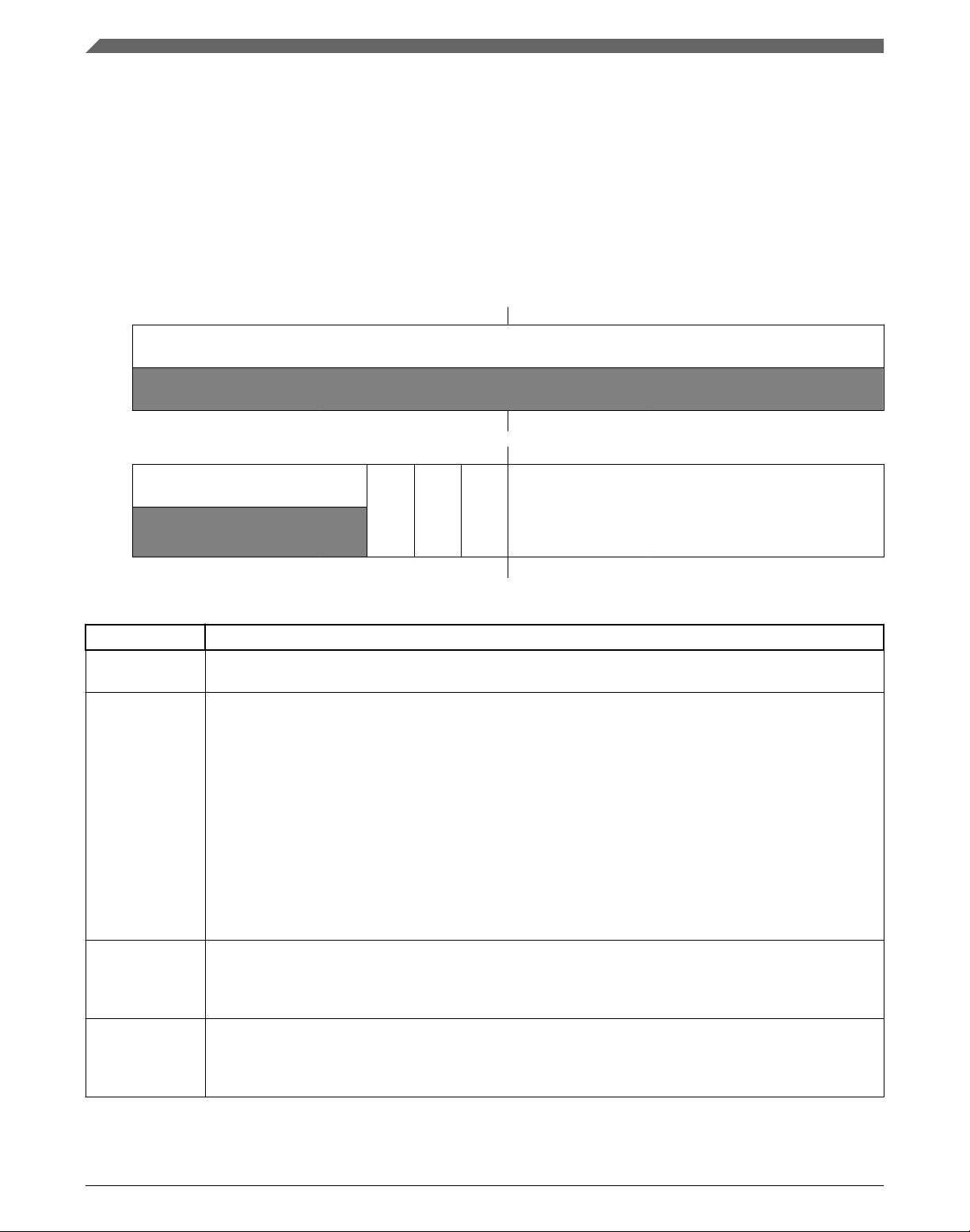

3.1.3.1.1 Message RAM Arbiter

The Message RAM Arbiter is a dynamic round robin arbiter that selects which request is

sent to the external Message RAM. These requests are made by the CPU, M_CAN_0, or

M_CAN_1.

This arbiter ensures:

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

20 Freescale Semiconductor, Inc.

Page 21

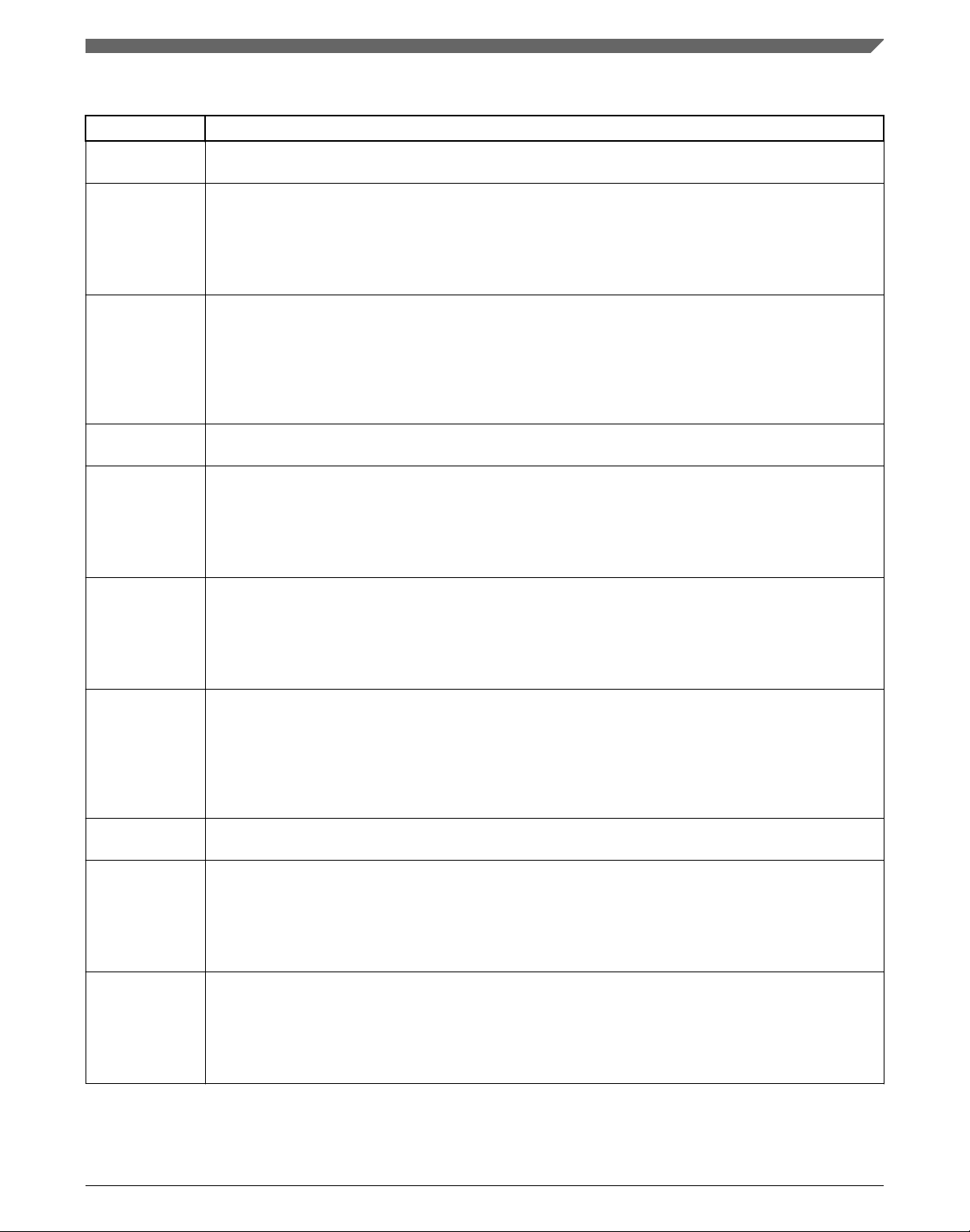

CPU

M_CAN_0

CPU

M_CAN_0

CPU

M_CAN_0

CPU

M_CAN_0

CPU clock

who accesses the

external Message RAM

M_CAN_1 M_CAN_1 M_CAN_1 M_CAN_1

CPU clock

who accesses the

external Message RAM

M_CAN_0 M_CAN_0 M_CAN_0 M_CAN_0

CPU

M_CAN_0

CPU

M_CAN_1

CPU

M_CAN_0

CPU

M_CAN_1

CPU clock

who accesses the

external Message RAM

Chapter 3 Modular CAN (M_CAN)

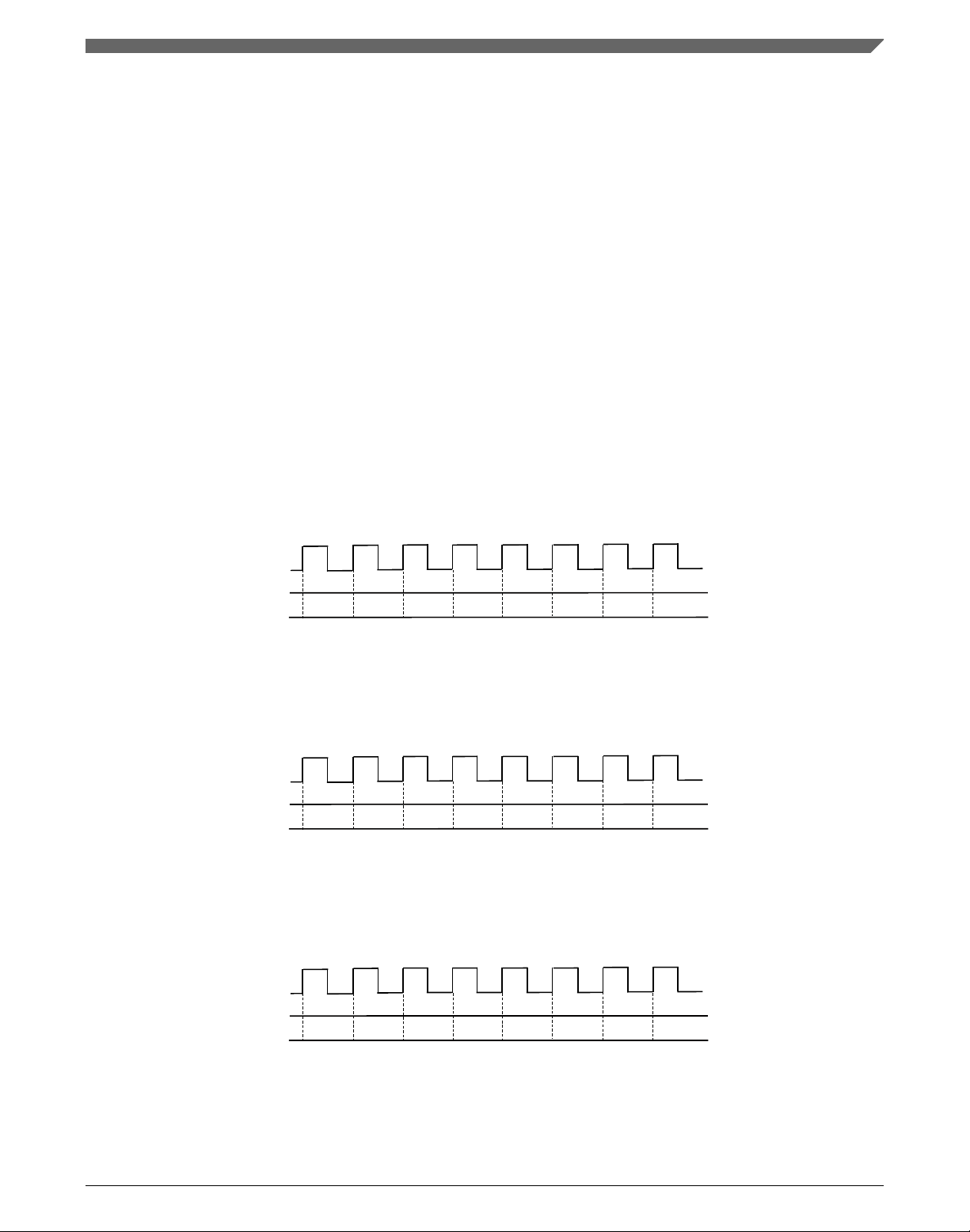

• 50% bandwidth for CPU accesses to the external Message RAM. The CPU does not

wait for more than one clock cycle to access the external Message RAM (see

examples 1 and 3).

• 50% bandwidth is shared between M_CAN_0 and M_CAN_1 accesses to the

external Message RAM. Each M_CAN waits at least one clock cycle to access the

external Message RAM (see examples 1, 2, and 3).

• If there is no CPU request, all bandwidth is distributed to M_CAN_0 and M_CAN_1

(see example 2).

• If there are no M_CAN_0 and M_CAN_1 requests, all bandwidth is distributed to the

CPU.

• If there are requests from only one M_CAN, the other M_CAN's bandwidth is

distributed to the first M_CAN (see example 1).

The following examples illustrate the dynamic arbiter scheme.

• Example 1: The following figure shows who accesses the external Message RAM

when only CPU and M_CAN_0 try to access to it.

• Example 2: The following figure shows who accesses the external Message RAM

when only M_CAN_0 and M_CAN_1 try to access to it.

• Example 3: The following figure shows who accesses the external Message RAM

when the CPU, M_CAN_0, and M_CAN_1 try to access to it.

The read or write accesses to the external Message RAM use two clock cycles. In the first

clock cycle, the address is available, and in the second, the data is available.

Freescale Semiconductor, Inc. 21

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Page 22

Chip-specific M_CAN information

The arbiter has a pseudo address pre-fetching mechanism that allows the data of the

previous access to overlap with the address of the current access. The pseudo address prefetching scheme saves multiple clock cycles when there are multiples accesses to the

external Message RAM.

3.1.3.1.2 ECC Controller

The ECC Controller provides Single Error Correction / Double Error Detection

(SECDED). It guarantees single bit error correction and double bit error detection

(without correction). The SECDED code is not guaranteed to detect more than two bits

with error.

Each 32 data bits of the external Message RAM is associated with 7 ECC bits. If all these

39 bits are zero or one, then it is flagged as non-correctable error.

For writes to the external Message RAM, the ECC bits (7-bit) are calculated using the

data bits (32-bit). The data bits plus ECC bits (39-bit) are written into the specified

memory address. The error detection and correction are performed on the reads from the

external Message RAM.

When an M_CAN accesses the external Message RAM, the ECC bits are calculated by

the ECC Controller and they are sent to this M_CAN.

3.1.3.2 External Message RAM

The external Message RAM supports only 32-bit write and read accesses.

The CPU can access the external Message RAM through the M_CAN subsystem. In this

case, the CPU can do 8/16/32-bit read accesses to the external Message RAM.

3.1.3.3 Transfer Error

The M_CAN subsystem does not report any transfer error.

3.1.4 External Signals

The M_CAN subsystem external signals are shown in the following table.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

22 Freescale Semiconductor, Inc.

Page 23

Chapter 3 Modular CAN (M_CAN)

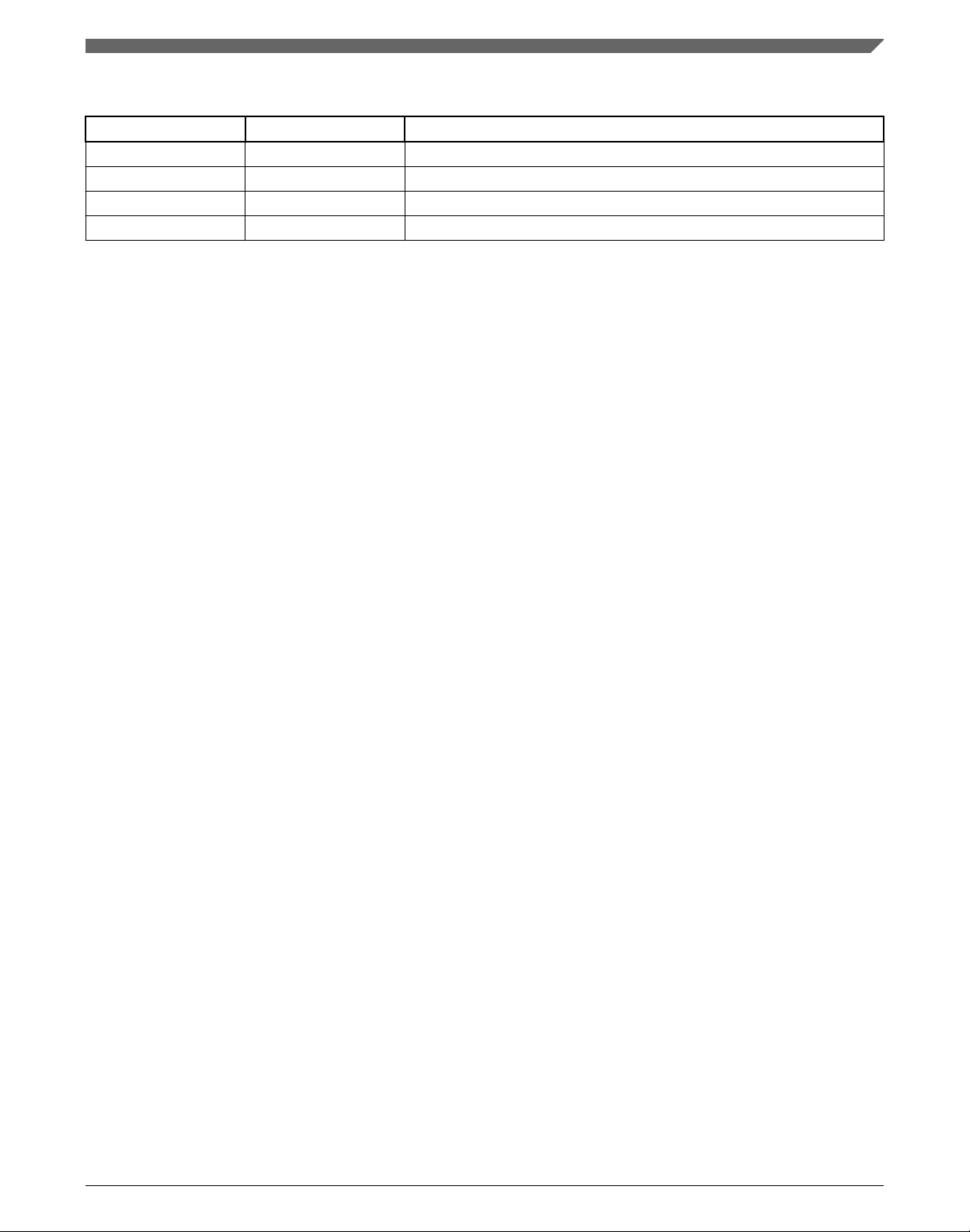

Table 3-1. M_CAN subsystem external signals

Signal name Direction Description

M_CAN_0_Rx input M_CAN_0 CAN Rx signal

M_CAN_0_Tx output M_CAN_0 CAN Tx signal

M_CAN_1_Rx input M_CAN_1 CAN Rx signal

M_CAN_1_Tx output M_CAN_1 CAN Tx signal

3.2 Overview

The M_CAN module is the new CAN Communication Controller IP-module. The

M_CAN performs communication according to ISO11898-1 (Bosch CAN specification

2.0 part A,B) and to Bosch CAN FD specification V1.0. Additional transceiver hardware

is required for connection to the physical layer.

The message storage is intended to be a single- or dual-ported Message RAM outside of

the module. It is connected to the M_CAN via the Generic Master Interface. Depending

on the chosen device, multiple M_CAN controllers can share the same Message RAM.

All functions concerning the handling of messages are implemented by the Rx Handler

and the Tx Handler. The Rx Handler manages message acceptance filtering, the transfer

of received messages from the CAN Core to the Message RAM as well as providing

receive message status information. The Tx Handler is responsible for the transfer of

transmit messages from the Message RAM to the CAN Core as well as providing

transmit status information.

Acceptance filtering is implemented by a combination of up to 128 filter elements where

each one can be configured as a range, as a bit mask, or as a dedicated ID filter.

The M_CAN can be connected to a wide range of Host CPUs via its 8/16/32-bit Generic

Slave Interface. The M_CAN's clock domain concept allows the separation between the

high precision CAN clock and the Host clock, which may be generated by an FM-PLL.

3.2.1 Features

The following are the features of M_CAN.

• Conforms with CAN protocol version 2.0 part A, B and ISO 11898-1

• CAN FD with up to 64 data bytes supported

• CAN Error Logging

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 23

Page 24

Overview

• AUTOSAR optimized

• SAE J1939 optimized

• Improved acceptance filtering

• Two configurable Receive FIFOs

• Separate signalling on reception of High Priority Messages

• Up to 64 dedicated Receive Buffers

• Up to 32 dedicated Transmit Buffers

• Configurable Transmit FIFO

• Configurable Transmit Queue

• Configurable Transmit Event FIFO

• Direct Message RAM access for Host CPU

• Multiple M_CANs may share the same Message RAM

• Programmable loop-back test mode

• Maskable module interrupts

• 8/16/32-bit Generic Slave Interface for connection customer-specific Host CPUs

• Two clock domains (CAN clock and Host clock)

• Power-down support

• Debug on CAN support

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

24 Freescale Semiconductor, Inc.

Page 25

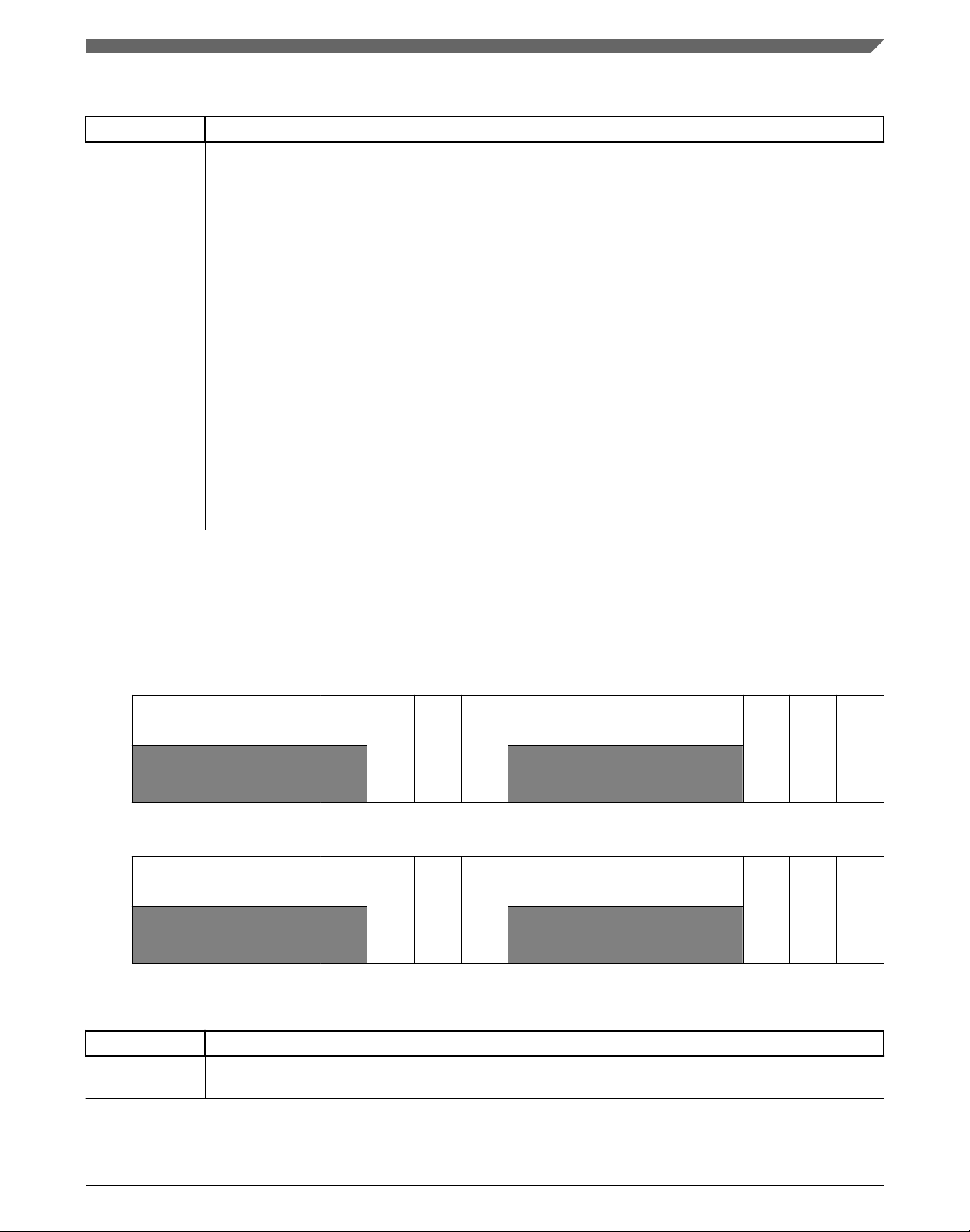

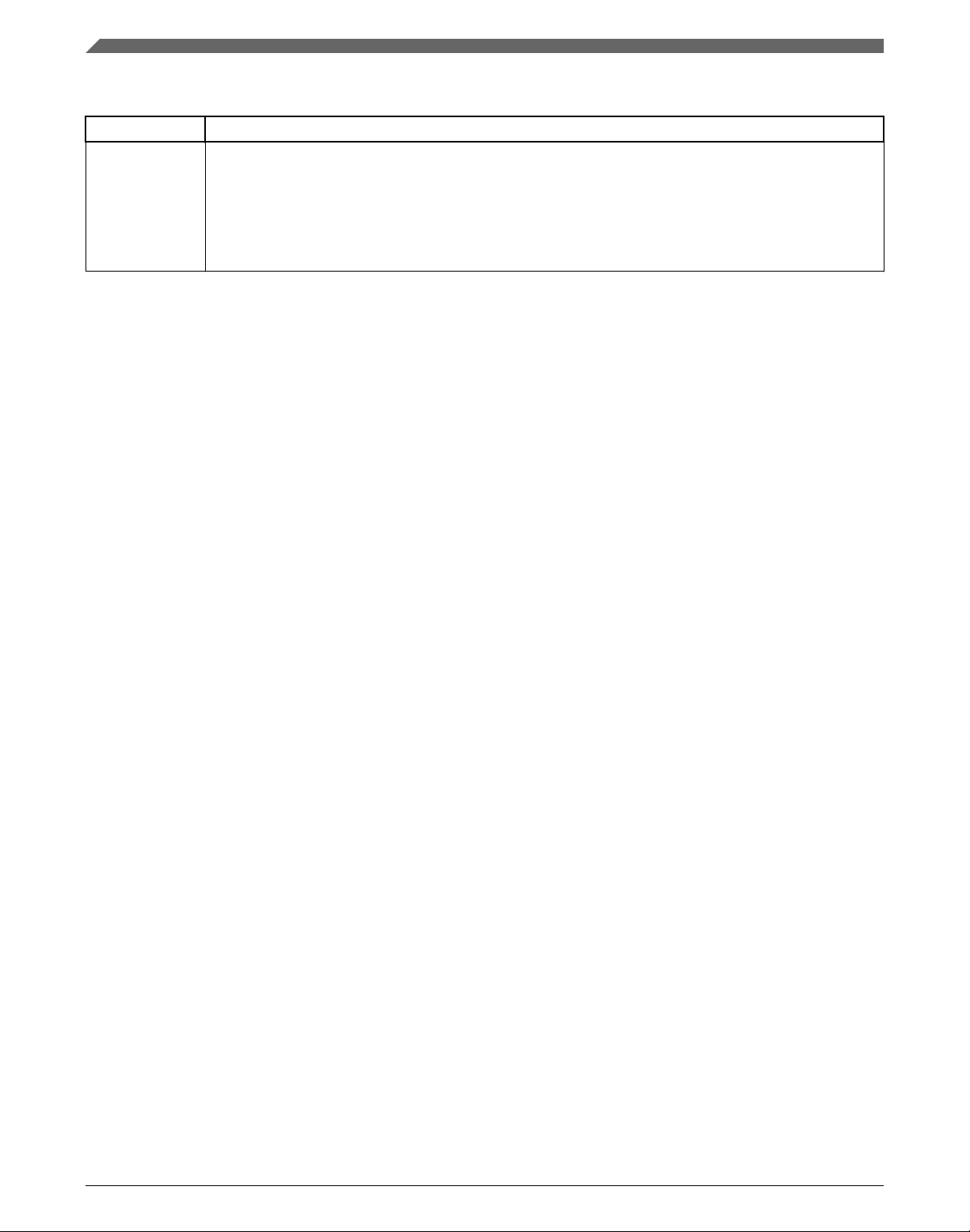

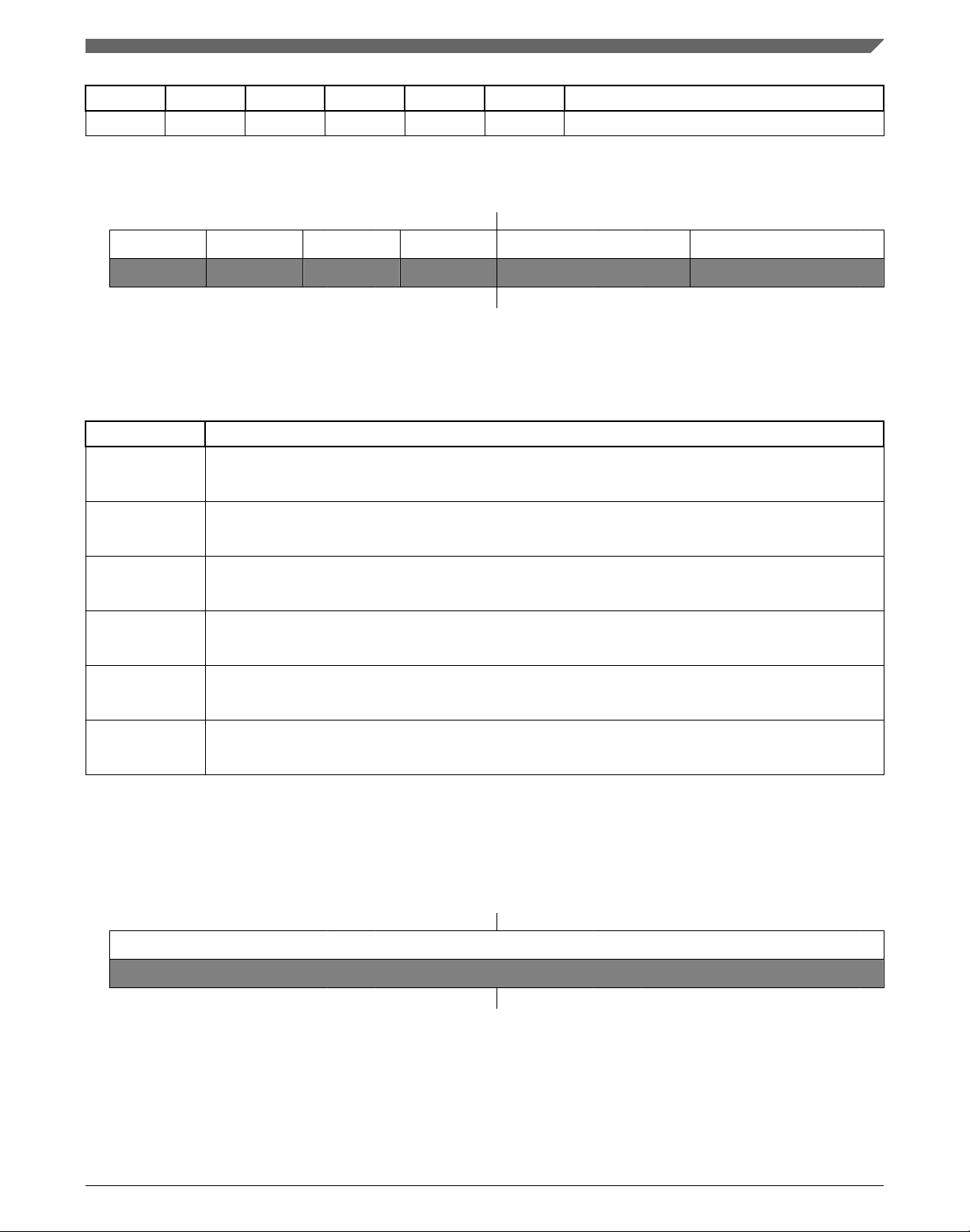

3.2.2 Block Diagram

Timestamp

Cfg and Ctrl

Cfg and Ctrl

Host Clock Domain

Tx Prioritization

Acceptance Filter

8/16/32

Cfg and Ctrl

CAN Clock Domain

Memory IF

M_CAN

Rx Handler

Host IF

Tx Handler

CAN Core

Generic Slave IF

Generic Master IF

Rx_State

Sync

Tx_Req

Tx_State

Clk

32

CAN Tx

CAN

R x

Chapter 3 Modular CAN (M_CAN)

Figure 3-2. M_CAN Block Diagram

• CAN Core: CAN Protocol Controller and Rx/Tx Shift Register. Handles all ISO

11898-1 protocol functions. Supports 11-bit and 29-bit identifiers.

• Sync: Synchronizes signals from the Host clock domain to the CAN clock domain

and vice versa.

• Clk: Synchronizes reset signal to the Host clock domain and to the CAN clock

domain.

• Cfg and Ctrl: CAN Core related configuration and control bits.

• Interrupt and Timestamp: Interrupt control and 16-bit CAN bit time counter for

receive and transmit timestamp generation.

• Tx Handler: Controls the message transfer from the external Message RAM to the

CAN Core. A maximum of 32 Tx Buffers can be configured for transmission. Tx

buffers can be used as dedicated Tx Buffers, as Tx FIFO, part of a Tx Queue, or as a

combination of them. A Tx Event FIFO stores Tx timestamps together with the

corresponding Message ID. Transmit cancellation is also supported.

Freescale Semiconductor, Inc. 25

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Page 26

Overview

• Rx Handler: Controls the transfer of received messages from the CAN Core to the

external Message RAM. The Rx Handler supports two Receive FIFOs, each of

configurable size, and up to 64 dedicated Rx Buffers for storage of all messages that

have passed acceptance filtering. A dedicated Rx Buffer, in contrast to a Receive

FIFO, is used to store only messages with a specific identifier. An Rx timestamp is

stored together with each message. Up to 128 filters can be defined for 11-bit IDs

and up to 64 filters for 29-bit IDs.

• Generic Slave Interface: Connects the M_CAN to a specific Host CPU. The Generic

Slave Interface is capable to connect to an 8/16/32-bit bus to support a wide range of

interconnection structures.

• Generic Master Interface: Connects the M_CAN access to an external 32-bit

Message RAM. The maximum Message RAM size is 16 KB × 32-bit.

• Extension Interface: All flags from the Interrupt Register IR as well as selected

internal status and control signals are routed to this interface. The interface is

intended for connection of the M_CAN to a module-external interrupt unit or other

module-external components. The connection of these signals is optional.

3.2.3 Dual Clock Sources

To improve the EMC behavior, a spread spectrum clock can be used for the Host clock

domain. Due to the high precision clocking requirements of the CAN Core, a separate

clock without any modulation has to be provided as CAN clock.

Within the M_CAN module there is a synchronization mechanism implemented to ensure

save data transfer between the two clock domains.

Note

In order to achieve a stable function of the M_CAN, the Host

clock must always be faster than or equal to the CAN clock.

Also, the modulation depth of a spread spectrum clock must be

regarded.

3.2.4 Dual Interrupt Lines

The module provides two interrupt lines. Interrupts can be routed either to M_CAN

interrupt 0 or to M_CAN interrupt 1. By default all interrupts are routed to interrupt line

M_CAN interrupt 0. By programming ILE[EINT0] and ILE[EINT1], the interrupt lines

can be enabled or disabled separately.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

26 Freescale Semiconductor, Inc.

Page 27

Chapter 3 Modular CAN (M_CAN)

3.3 Memory Map and Register Description

After hardware reset, the registers of the M_CAN hold the reset values. Additionally the

Bus_Off state is reset and the M_CAN Tx is set to recessive (HIGH). The value 0x0001

(CCCR[INIT] = 1) in the CC Control Register enables software initialization. The

M_CAN does not influence the CAN bus until the CPU resets CCCR[INIT] to 0.

The M_CAN module allocates an address space of 256 bytes. All registers are organized

as 32-bit registers. The M_CAN is accessible by the CPU using a data width of 8-bit

(byte access), 16-bit (half-word access), or 32-bit (word access).

The CPU has write access to Protected Write registers and fields when both CCCR[CCE]

is 1 and CCCR[INIT] is 1.

There is a delay from writing to a command register until the update of the related status

register bits due to clock domain crossing.

CAUTION

Any write access to reserved or not implemented registers in

the slot assigned by to the M_CAN IP will not generate any bus

access error.

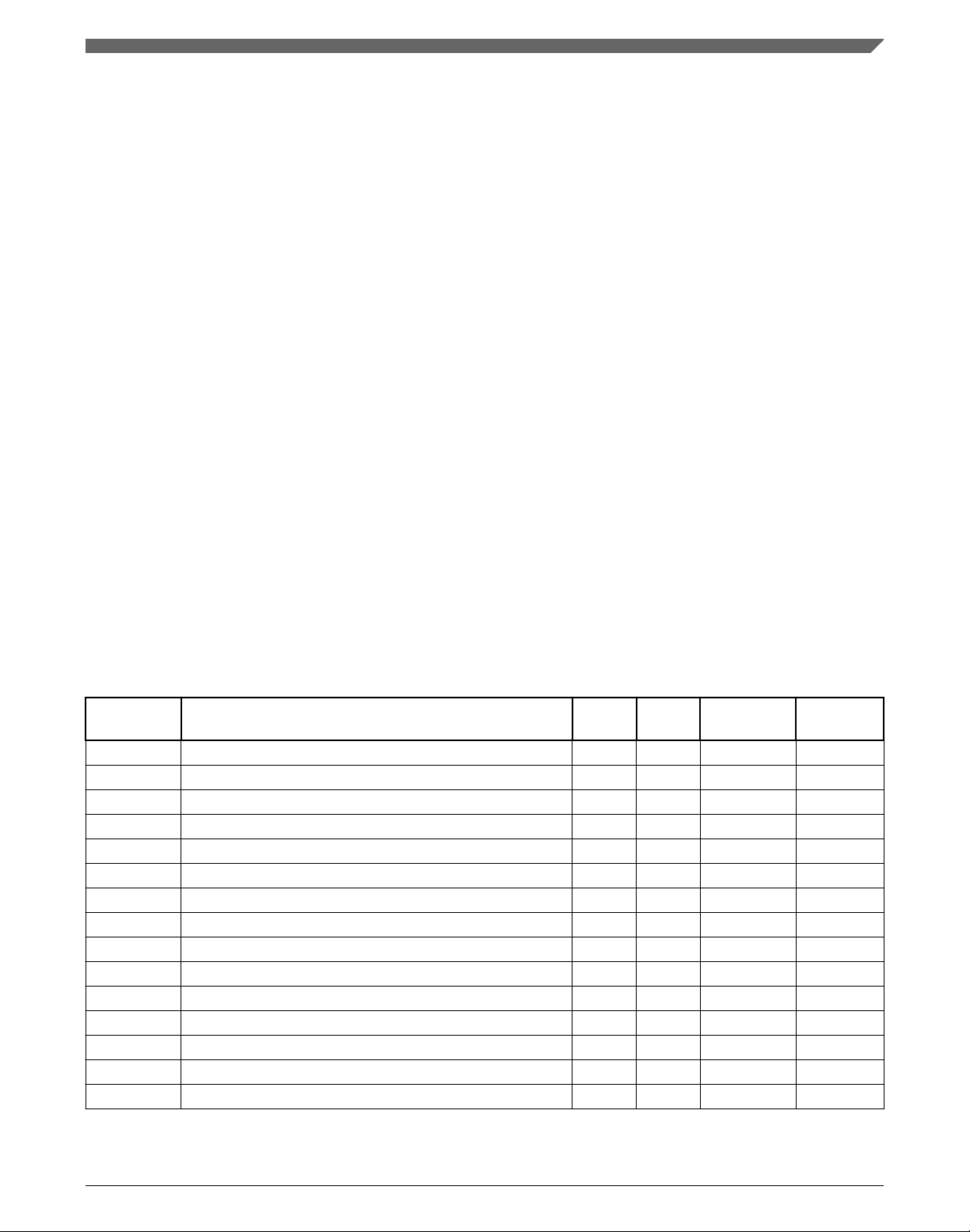

M_CAN memory map

Address

offset (hex)

0 Core Release Register (M_CAN_CREL) 32 R See section 3.3.1/28

4 Endian Register (M_CAN_ENDN) 32 R 8765_4321h 3.3.2/29

C Fast Bit Timing and Prescaler Register (M_CAN_FBTP) 32 R/W 0000_0A33h 3.3.3/30

10 Test Register (M_CAN_TEST) 32 R/W See section 3.3.4/32

14 RAM Watchdog Register (M_CAN_RWD) 32 R/W 0000_0000h 3.3.5/33

18 CC Control Register (M_CAN_CCCR) 32 R/W 0000_0001h 3.3.6/34

1C Bit Timing and Prescaler Register (M_CAN_BTP) 32 R/W 0000_0A33h 3.3.7/36

20 Timestamp Counter Configuration Register (M_CAN_TSCC) 32 R/W 0000_0000h 3.3.8/38

24 Timestamp Counter Value Register (M_CAN_TSCV) 32 w1c 0000_0000h 3.3.9/38

28 Timeout Counter Configuration Register (M_CAN_TOCC) 32 R/W FFFF_0000h 3.3.10/39

2C Timeout Counter Value Register (M_CAN_TOCV) 32 w1c 0000_FFFFh 3.3.11/40

40 Error Counter Register (M_CAN_ECR) 32 R 0000_0000h 3.3.12/41

44 Protocol Status Register (M_CAN_PSR) 32 R 0000_0707h 3.3.13/42

50 Interrupt Register (M_CAN_IR) 32 w1c 0000_0000h 3.3.14/45

54 Interrupt Enable Register (M_CAN_IE) 32 R/W 0000_0000h 3.3.15/49

Register name

Width

(in bits)

Access Reset value

Section/

page

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 27

Page 28

Memory Map and Register Description

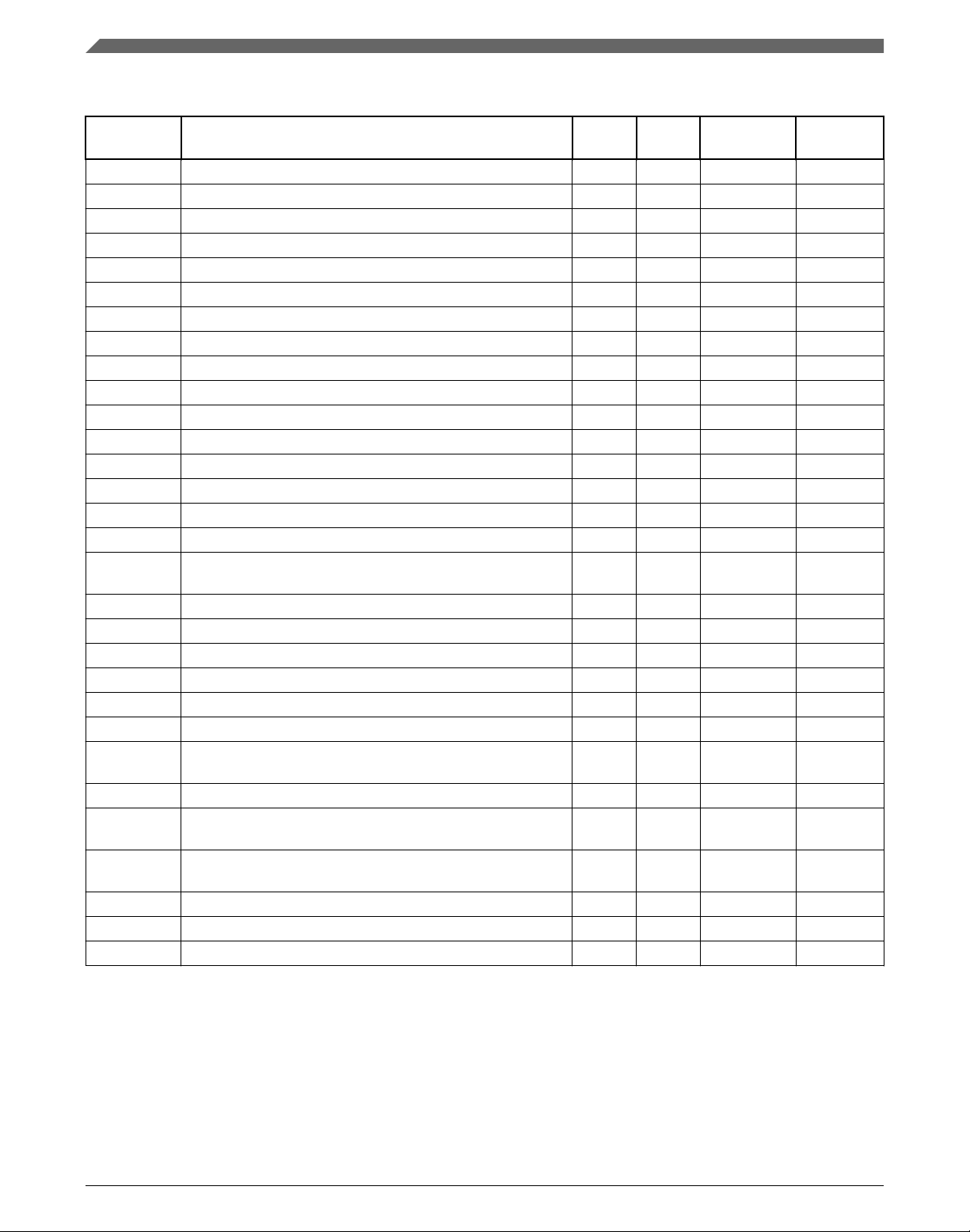

M_CAN memory map (continued)

Address

offset (hex)

58 Interrupt Line Select Register (M_CAN_ILS) 32 R/W 0000_0000h 3.3.16/52

5C Interrupt Line Enable Register (M_CAN_ILE) 32 R/W 0000_0000h 3.3.17/55

80 Global Filter Configuration Register (M_CAN_GFC) 32 R/W 0000_0000h 3.3.18/56

84 Standard ID Filter Configuration Register (M_CAN_SIDFC) 32 R/W 0000_0000h 3.3.19/57

88 Extended ID Filter Configuration Register (M_CAN_XIDFC) 32 R/W 0000_0000h 3.3.20/58

90 Extended ID and Mask Register (M_CAN_XIDAM) 32 R/W 1FFF_FFFFh 3.3.21/59

94 High Priority Message Status Register (M_CAN_HPMS) 32 R 0000_0000h 3.3.22/59

98 New Data 1 Register (M_CAN_NDAT1) 32 R/W 0000_0000h 3.3.23/60

9C New Data 2 Register (M_CAN_NDAT2) 32 R/W 0000_0000h 3.3.24/61

A0 Rx FIFO 0 Configuration Register (M_CAN_RXF0C) 32 R/W 0000_0000h 3.3.25/61

A4 Rx FIFO 0 Status Register (M_CAN_RXF0S) 32 R 0000_0000h 3.3.26/62

A8 Rx FIFO 0 Acknowledge Register (M_CAN_RXF0A) 32 R/W 0000_0000h 3.3.27/63

AC Rx Buffer Configuration Register (M_CAN_RXBC) 32 R/W 0000_0000h 3.3.28/64

B0 Rx FIFO 1 Configuration Register (M_CAN_RXF1C) 32 R/W 0000_0000h 3.3.29/64

B4 Rx FIFO 1 Status Register (M_CAN_RXF1S) 32 R 0000_0000h 3.3.30/65

B8 Rx FIFO 1 Acknowledge Register (M_CAN_RXF1A) 32 R/W 0000_0000h 3.3.31/66

BC

C0 Tx Buffer Configuration Register (M_CAN_TXBC) 32 R/W 0000_0000h 3.3.33/69

C4 Tx FIFO/Queue Status Register (M_CAN_TXFQS) 32 R 0000_0000h 3.3.34/70

C8 Tx Buffer Element Size Configuration (M_CAN_TXESC) 32 R/W 0000_0000h 3.3.35/71

CC Tx Buffer Request Pending Register (M_CAN_TXBRP) 32 R 0000_0000h 3.3.36/72

D0 Tx Buffer Add Request Register (M_CAN_TXBAR) 32 R/W 0000_0000h 3.3.37/73

D4 Tx Buffer Cancellation Request Register (M_CAN_TXBCR) 32 R/W 0000_0000h 3.3.38/73

D8

DC Tx Buffer Cancellation Finished Register (M_CAN_TXBCF) 32 R 0000_0000h 3.3.40/74

E0

E4

F0 Tx Event FIFO Configuration Register (M_CAN_TXEFC) 32 R/W 0000_0000h 3.3.43/76

F4 Tx Event FIFO Status Register (M_CAN_TXEFS) 32 R 0000_0000h 3.3.44/77

F8 Tx Event FIFO Acknowledge Register (M_CAN_TXEFA) 32 R/W 0000_0000h 3.3.45/78

Rx Buffer / FIFO Element Size Configuration Register

(M_CAN_RXESC)

Tx Buffer Transmission Occurred Register

(M_CAN_TXBTO)

Tx Buffer Transmission Interrupt Enable Register

(M_CAN_TXBTIE)

Tx Buffer Cancellation Finished Interrupt Enable Register

(M_CAN_TXBCIE)

Register name

Width

(in bits)

Access Reset value

32 R/W 0000_0000h 3.3.32/67

32 R 0000_0000h 3.3.39/74

32 R/W 0000_0000h 3.3.41/75

32 R/W 0000_0000h 3.3.42/75

Section/

page

3.3.1 Core Release Register (M_CAN_CREL)

The following table shows example field values for this register and explains how they

encode a particular M_CAN core release.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

28 Freescale Semiconductor, Inc.

Page 29

Chapter 3 Modular CAN (M_CAN)

REL STEP SUBSTEP YEAR MON DAY Release

0 2 0 9 3 26 Revision 0.2.0, date 2009/03/26

Address: 0h base + 0h offset = 0h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

Reset

REL STEP SUBSTEP YEAR MON DAY

x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x* x*

* Notes:

The coding of revisions depends on the module version used in the device.x = Undefined at reset.•

M_CAN_CREL field descriptions

Field Description

0–3

REL

4–7

STEP

8–11

SUBSTEP

12–15

YEAR

16–23

MON

24–31

DAY

Core Release

One digit, BCD-coded.

Step of Core Release

One digit, BCD-coded.

Sub-step of Core Release

One digit, BCD-coded.

Time Stamp Year

One digit, BCD-coded.

Time Stamp Month

Two digits, BCD-coded.

Time Stamp Day

Two digits, BCD-coded.

3.3.2 Endian Register (M_CAN_ENDN)

Address: 0h base + 4h offset = 4h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

Reset

1 0 0 0 0 1 1 1 0 1 1 0 0 1 0 1 0 1 0 0 0 0 1 1 0 0 1 0 0 0 0 1

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 29

ETV

Page 30

Memory Map and Register Description

M_CAN_ENDN field descriptions

Field Description

0–31

ETV

Endianness Test Value

The endianness test value is 0x87654321.

3.3.3 Fast Bit Timing and Prescaler Register (M_CAN_FBTP)

The CAN bit time may be programed in the range of 4 to 25 time quanta. The CAN time

quantum may be programmed in the range of 1 to 32 M_CAN clock periods. tq = (FBRP

+ 1) M_CAN clock period.

FTSEG1 is the sum of Prop_Seg and Phase_Seg1. FTSEG2 is Phase_Seg2. Therefore the

length of the bit time is (programmed values) [FTSEG1 + FTSEG2 + 3] tq or (functional

values) [Sync_Seg + Prop_Seg + Phase_Seg1 + Phase_Seg2] tq.

The Information Processing Time (IPT) is zero, meaning the data for the next bit is

available at the first clock edge after the sample point.

NOTE

With a M_CAN clock of 8 MHz, the reset value of

0x00000A33 configures the M_CAN for a fast bit rate of 500

kbit/s.

The bit rate configured for the CAN FD data phase via FBTP

must be higher or equal to the bit rate configured for the

arbitration phase via BTP.

Address: 0h base + Ch offset = Ch

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

Reset

Bit

Reset

R

W

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

0 0 0 0 1 0 1 0 0 0 1 1 0 0 1 1

0

0

TDCO TDC

FTSEG1

0

0

FTSEG2

FBRP

0

M_CAN_FBTP field descriptions

FSJW

Field Description

0–2

Reserved

30 Freescale Semiconductor, Inc.

This field is reserved.

This read-only field is reserved and always has the value 0.

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Page 31

M_CAN_FBTP field descriptions (continued)

Field Description

3–7

TDCO

8

TDC

9–10

Reserved

11–15

FBRP

Transceiver Delay Compensation Offset

NOTE: This field has Protected Write status.

0x00–0x1F Offset value defining the distance between the measured delay from M_CAN Tx to M_CAN

Rx and the secondary sample point. Valid values are 0 to 31 M_CAN clock periods

Transceiver Delay Compensation

NOTE: This field has Protected Write status.

0 Transceiver Delay Compensation disabled

1 Transceiver Delay Compensation enabled

This field is reserved.

This read-only field is reserved and always has the value 0.

Fast Baud Rate Prescaler

(0x000–0x1F)— The value by which the oscillator frequency is divided for generating the bit time quanta.

The bit time is built up from a multiple of this quanta. Valid values for the Baud Rate Prescaler are 0 to 31.

The actual interpretation by the hardware of this value is such that one more than the value programmed

here is used.

Chapter 3 Modular CAN (M_CAN)

16–19

Reserved

20–23

FTSEG1

24

Reserved

25–27

FTSEG2

28–29

Reserved

30–31

FSJW

NOTE: This field has Protected Write status.

This field is reserved.

This read-only field is reserved and always has the value 0.

Fast time segment before sample point

(0x1–0xF)— Valid values are 1 to 15. The actual interpretation by the hardware of this value is such that

one more than the programmed value is used.

NOTE: This field has Protected Write status.

This field is reserved.

This read-only field is reserved and always has the value 0.

Fast time segment after sample point

(0x0–0x7)— Valid values are 0 to 7. The actual interpretation by the hardware of this value is such that

one more than the programmed value is used.

NOTE: This field has Protected Write status.

This field is reserved.

This read-only field is reserved and always has the value 0.

Fast (Re) Synchronization Jump Width

(0x0–0x3)— Valid values are 0 to 3. The actual interpretation by the hardware of this value is such that

one more than the value programmed here is used.

NOTE: This field has Protected Write status.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 31

Page 32

Memory Map and Register Description

3.3.4 Test Register (M_CAN_TEST)

Write access to the Test Register has to be enabled by setting CCCR[TEST] to 1. All Test

Register functions are set to their reset values when CCCR[TEST] is reset.

Loopback mode and software control of M_CAN Tx are hardware test modes.

Programming of Tx other than 00 may disturb the message transfer on the CAN bus.

Address: 0h base + 10h offset = 10h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

W

Reset

Bit

R

W

Reset

* Notes:

u = Unaffected by reset.•

0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

0 TDCV RX

TX

LBCK

0 0 0 0 0 0 0 0 u* 0 0 0 0 0 0 0

0

M_CAN_TEST field descriptions

Field Description

0–17

Reserved

18–23

TDCV

24

RX

32 Freescale Semiconductor, Inc.

This field is reserved.

This read-only field is reserved and always has the value 0.

Transceiver Delay Compensation Value

(0x00–0x3F)— Position of the secondary sample point, defined by the sum of the measured delay from

M_CAN Tx to M_CAN Rx and FBTP[TDCO]. Valid value are 0 to 63 M_CAN clock periods.

Receive Pin

Monitors the actual value of M_CAN Rx

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Page 33

M_CAN_TEST field descriptions (continued)

Field Description

0 The CAN bus is dominant (M_CAN Rx = 0)

1 The CAN bus is recessive (M_CAN Rx = 1)

25–26

TX

27

LBCK

28–31

Reserved

Control of Transmit Pin

NOTE: This field has Protected Write status.

00 Reset value, M_CAN Tx is controlled by the M_CAN, updated at the end of the CAN bit time

01 Sample Point can be monitored at M_CAN Tx

10 Dominant (0) level at M_CAN Tx

11 Recessive (1) at M_CAN Tx

Loopback mode

NOTE: This field has Protected Write status.

0 Reset value, Loopback mode is disabled

1 Loopback mode is enabled (see Test Modes)

This field is reserved.

This read-only field is reserved and always has the value 0.

Chapter 3 Modular CAN (M_CAN)

3.3.5 RAM Watchdog Register (M_CAN_RWD)

The RAM Watchdog monitors when the Message RAM output is available to M_CAN.

When the M_CAN requests a Message RAM access, M_CAN starts the Message RAM

Watchdog Counter with the value configured by the RWD[WDC]. The counter is

reloaded with RWD[WDC] when the M_CAN request to Message RAM is successful

completed. In case there is no response from the Message RAM until the counter has

counted down to zero, the counter stops and interrupt flag IR[WDI] is set.

Address: 0h base + 14h offset = 14h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Field Description

0–15

Reserved

This field is reserved.

This read-only field is reserved and always has the value 0.

0 WDV

WDC

M_CAN_RWD field descriptions

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 33

Page 34

Memory Map and Register Description

M_CAN_RWD field descriptions (continued)

Field Description

16–23

WDV

24–31

WDC

Watchdog Value

Actual Message RAM Watchdog Counter Value.

Watchdog Configuration

Start value of the Message RAM Watchdog Counter. With the reset value of 00 the counter is disabled.

NOTE: This field has Protected Write status.

3.3.6 CC Control Register (M_CAN_CCCR)

For details about setting and resetting of single bits see Software Initialization.

Address: 0h base + 18h offset = 18h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

0

W

Reset

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Bit

R

0

W

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1

TXP

FDBS FDO

CMR CME TEST DAR MON CSR

M_CAN_CCCR field descriptions

Field Description

0–16

Reserved

17

TXP

18

FDBS

19

FDO

This field is reserved.

This read-only field is reserved and always has the value 0.

Transmit Pause

If this bit is set, the M_CAN pauses for two CAN bit times before starting the next transmission after itself

has successfully transmitted a frame (see Tx Handling).

NOTE: This field has Protected Write status.

0 Transmit pause disabled

1 Transmit pause enabled

CAN FD Bit Rate Switching

0 This node transmits no frames with bit rate switching

1 This node transmits all frames (excluding remote frames) with bit rate switching

CAN FD Operation

Table continues on the next page...

CSA

ASM CCE INIT

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

34 Freescale Semiconductor, Inc.

Page 35

M_CAN_CCCR field descriptions (continued)

Field Description

0 This node transmits all frames in CAN format according to ISO11898-1

1 This node transmits all frames (excluding remote frames) in CAN FD format

20–21

CMR

22–23

CME

CAN Mode Request

A change of the CAN operation mode is requested by writing to this bit field. After change to the requested

operation mode the bit field is reset to 00 and the status flags FDBS and FDO are set accordingly. In case

the requested CAN operation mode is not enabled, the value written to CMR is retained until it is

overwritten by the next mode change request. In case CME = 01/10/11 a change to CAN operation

according to ISO 11898-1 is always possible. Default is CAN operation according to ISO11898-1.

00 Unchanged

01 Request CAN FD operation

10 Request CAN FD operation with bit rate switching

11 Request CAN operation according ISO11898-1

CAN Mode Enable

NOTE: When CME = 00, received frames are strictly interpreted according to ISO11898-1, which leads

to the transmission of an error frame when receiving a CAN FD frame. In case CME = 01,

transmission of long CAN FD frames and reception of long and fast CAN FD frames is enabled.

With CME = 10/11, transmission and reception of long and fast CAN FD frames is enabled.

NOTE: This field has Protected Write status.

Chapter 3 Modular CAN (M_CAN)

24

TEST

25

DAR

26

MON

27

CSR

00 CAN operation according to ISO11898-1 enabled

01 CAN FD operation enabled

10 CAN FD operation with bit rate switching enabled

11 CAN FD operation with bit rate switching enabled

Test Mode Enable

Bit TEST can only be set by the CPU when both CCE and INIT are set to 1. The bit can be reset by the

CPU at any time.

0 Normal operation, register TEST holds reset values

1 Test Mode, write access to register TEST enabled

Disable Automatic Retransmission

NOTE: This field has Protected Write status.

0 Automatic retransmission of messages not transmitted successfully enabled

1 Automatic retransmission disabled

Bus Monitoring Mode

Bit MON can only be set by the CPU when both CCE and INIT are set to 1. The bit can be reset by the

CPU at any time.

0 Bus Monitoring Mode is disabled

1 Bus Monitoring Mode is enabled

Clock Stop Request

Table continues on the next page...

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 35

Page 36

Memory Map and Register Description

M_CAN_CCCR field descriptions (continued)

Field Description

0 No clock stop is requested

1 Clock stop requested. When clock stop is requested, first INIT and then CSA will be set after all

pending transfer requests have been completed and the CAN bus reached idle.

28

CSA

29

ASM

30

CCE

31

INIT

Clock Stop Acknowledge

0 No clock stop acknowledged

1 M_CAN may be set in power down by stopping M_CAN input clocks

Restricted Operation Mode

Bit ASM is only set by the CPU when both CCE and INIT are set to 1. The bit can be reset by the CPU at

any time.

0 Normal CAN operation

1 Restricted Operation Mode active

Configuration Change Enable

NOTE: This field has Protected Write status.

0 The CPU has no write access to the protected configuration registers

1 The CPU has write access to the protected configuration registers (while CCCR[INIT] = 1)

Initialization

NOTE: Due to the synchronization mechanism between the two clock domains, there may be a delay

until the value written to INIT can be read back. Therefore the programmer has to assure that the

previous value written to INIT has been accepted by reading INIT before setting INIT to a new

value.

0 Normal Operation

1 Initialization is started

3.3.7 Bit Timing and Prescaler Register (M_CAN_BTP)

The CAN bit time may be programed in the range of [4....81] time quanta. The CAN time

quantum may be programmed in the range of [1....1024] M_CAN clock periods. tq =

(BRP + 1) M_CAN clock period.

TSEG1 is the sum of Prop_Seg and Phase_Seg1. TSEG2 is Phase_Seg2.

Therefore the length of the bit time is (programmed values) [TSEG1 + TSEG2 + 3] tq or

(functional values) [Sync_Seg + Prop_Seg + Phase_Seg1 + Phase_Seg2] tq.

The Information Processing Time (IPT) is zero, meaning the data for the next bit is

available at the first clock edge after the sample point.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

36 Freescale Semiconductor, Inc.

Page 37

Chapter 3 Modular CAN (M_CAN)

NOTE

With a CAN clock of 8 MHz, the reset value of 0x0000_0A33

configures the M_CAN for a bit rate of 500 kBit/s.

Address: 0h base + 1Ch offset = 1Ch

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 0 0 0 1 1 0 0 1 1

Field Description

Reserved

6–15

0–5

BRP

0

BRP

0

TSEG1 TSEG2 SJW

M_CAN_BTP field descriptions

This field is reserved.

This read-only field is reserved and always has the value 0.

Baud Rate Prescaler

(0x000-0x3FF)— The value by which the oscillator frequency is divided for generating the bit time quanta.

The bit time is built up from a multiple of this quanta. Valid values for the Baud Rate Prescaler are 0 to

1023. The actual interpretation by the hardware of this value is such that one more than the value

programmed here is used.

16–17

Reserved

18–23

TSEG1

24–27

TSEG2

28–31

SJW

NOTE: This field has Protected Write status.

This field is reserved.

This read-only field is reserved and always has the value 0.

Time segment before sample point

(0x01-0x3F)— Valid values are 1 to 63. The actual interpretation by the hardware of this value is such that

one more than the programmed value is used.

NOTE: This field has Protected Write status.

Time segment after sample point

(0x0-0xF)— Valid values are 0 to 15. The actual interpretation by the hardware of this value is such that

one more than the programmed value is used.

NOTE: This field has Protected Write status.

(Re) Synchronization Jump Width

(0x0-0xF)— Valid values are 0 to 15. The actual interpretation by the hardware of this value is such that

one more than the value programmed here is used.

NOTE: This field has Protected Write status.

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 37

Page 38

Memory Map and Register Description

3.3.8 Timestamp Counter Configuration Register (M_CAN_TSCC)

For a description of the Timestamp Counter see Timestamp Generation

Address: 0h base + 20h offset = 20h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Field Description

0–11

Reserved

12–15

TCP

0

TCP

0

M_CAN_TSCC field descriptions

This field is reserved.

This read-only field is reserved and always has the value 0.

Timestamp Counter Prescaler

(0x0-0xF)— Configures the timestamp and timeout counters time unit in multiples of CAN bit times [1…

16]. The actual interpretation by the hardware of this value is such that one more than the value

programmed here is used.

TSS

NOTE: This field has Protected Write status.

NOTE: With CAN FD, timestamp generation is not supported.

16–29

Reserved

30–31

TSS

This field is reserved.

This read-only field is reserved and always has the value 0.

Timestamp Select

NOTE: This field has Protected Write status.

00 Timestamp counter value always 0x0000

01 Timestamp counter value incremented according to TCP

10 Reserved

11 Same as 00

3.3.9 Timestamp Counter Value Register (M_CAN_TSCV)

Address: 0h base + 24h offset = 24h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

0 TSC

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

w1c

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

38 Freescale Semiconductor, Inc.

Page 39

Chapter 3 Modular CAN (M_CAN)

M_CAN_TSCV field descriptions

Field Description

0–15

Reserved

16–31

TSC

This field is reserved.

This read-only field is reserved and always has the value 0.

Timestamp Counter

The internal Timestamp Counter value is captured on start of frame (both Rx and Tx). When TSCC[TSS] =

01, the Timestamp Counter is incremented in multiples of CAN bit times [1…16] depending on the

configuration of TSCC[TCP]. A wrap around sets interrupt flag IR[TSW]. Write access resets the counter

to zero.

NOTE: A "wrap around" is a change of the Timestamp Counter value from non-zero to zero not caused

by write access to TSCV.

3.3.10 Timeout Counter Configuration Register (M_CAN_TOCC)

See Timeout Counter for a description of the Timeout Counter or for use of timeout

function with CAN FD.

Address: 0h base + 28h offset = 28h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

TOP

W

Reset

Reset

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Bit

R

W

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0

TOS

M_CAN_TOCC field descriptions

Field Description

0–15

TOP

16–28

Reserved

29–30

TOS

Timeout Period

Start value of the Timeout Counter (down-counter). Configures the Timeout Period.

NOTE: This field has Protected Write status.

This field is reserved.

This read-only field is reserved and always has the value 0.

Timeout Select

Table continues on the next page...

ETOC

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

Freescale Semiconductor, Inc. 39

Page 40

Memory Map and Register Description

M_CAN_TOCC field descriptions (continued)

Field Description

When operating in Continuous mode, a write to TOCV presets the counter to the value configured by

TOCC[TOP] and continues down-counting. When the Timeout Counter is controlled by one of the FIFOs,

an empty FIFO presets the counter to the value configured by TOCC[TOP]. Down-counting is started

when the first FIFO element is stored.

NOTE: This field has Protected Write status.

00 Continuous operation

01 Timeout controlled by Tx Event FIFO

10 Timeout controlled by Rx FIFO 0

11 Timeout controlled by Rx FIFO 1

31

ETOC

Enable Timeout Counte

NOTE: This field has Protected Write status.

0 Timeout Counter disabled

1 Timeout Counter enabled

3.3.11 Timeout Counter Value Register (M_CAN_TOCV)

Address: 0h base + 2Ch offset = 2Ch

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

R

W

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Field Description

0–15

Reserved

16–31

TOC

This field is reserved.

This read-only field is reserved and always has the value 0.

Timeout Counter

The Timeout Counter is decremented in multiples of CAN bit times [1…16] depending on the configuration

of TSCC[TCP]. When decremented to zero, interrupt flag IR[TOO] is set and the Timeout Counter is

stopped. Start and reset/restart conditions are configured via TOCC[TOS].

0 TOC

w1c

M_CAN_TOCV field descriptions

MPC5777C Reference Manual Addendum, Rev. 1, 12/2015

40 Freescale Semiconductor, Inc.

Page 41

Chapter 3 Modular CAN (M_CAN)

3.3.12 Error Counter Register (M_CAN_ECR)

NOTE

When CCCR[ASM] is set, the CAN protocol controller does

not increment TEC and REC when a CAN protocol error is

detected, but CEL is still incremented.

Address: 0h base + 40h offset = 40h

Bit 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

R

W

0 CEL

Reset

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31

Bit

R

RP REC TEC

W

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

M_CAN_ECR field descriptions

Field Description

0–7

Reserved

8–15

CEL

16

RP

17–23

REC

24–31

TEC

This field is reserved.