Page 1

S12 MagniV

Microcontrollers

nxp.com

MC9S12VRP-Series

Reference Manual and

Datasheet

MC9S12VRP64

Rev. 1.3

19 Sep 2017

Page 2

Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://nxp.com

A full list of family members and options is included in the device overview section.

The following revision history table summarizes changes contained in this document.

This document contains information for all constituent modules, with the exception of the CPU. For CPU

information please refer to CPU12-1 in the CPU12 & CPU12X Reference Manual.

Revision History

Date Revision Description

• Updated Data-Flash size for S12VRP48 option, Ta bl e 1 -2

01 MAR 2017 1.0

7 AUG 2017 1.1A

18 AUG 2017 1.1 • Official release

• Removed internal register bit reference 13.3.4/13-376

• Updated NVM timing for Erase D-Flash Sector Ta bl e I -1

• Removed Preliminary marking

• Minor corrections in Chapter 1, “Device Overview S12VRP-Series”, Chapter 2, “Port

Integration Module (S12VRPPIMV1)”, and Chapter 14, “Low-Side Driver - LS2DRV

(S12LS2DRV_V1)”

• Updated electrical specifications in Appendix A to Appendix H

14 SEP 2017 1.2A • Updated electrical specifications in Appendix A and Appendix D

15 SEP 2017 1.2 • Official release

19 SEP 2017 1.3 • Block diagram added to Chapter 15, “Current Sense Amplifier Module (ISENSEV1)

Page 3

Chapter 1

Device Overview S12VRP-Series

1.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.3 S12VRP-Series Comparison . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

1.4 Chip-Level Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

1.5 Module Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.5.1 HCS12 16-Bit Central Processor Unit (CPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.5.2 On-Chip Flash with ECC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20

1.5.3 On-Chip SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.5.4 Main External Oscillator (XOSCLCP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.5.5 Internal RC Oscillator (IRC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.5.6 Internal Phase-Locked Loop (IPLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.5.7 Clock and Power Management Unit (CPMU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

1.5.8 System Integrity Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.5.9 Timer (TIM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.5.10 Pulse Width Modulation Module (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.5.11 LIN physical layer transceiver (LINPHY) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.5.12 Serial Communication Interface Module (SCI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

1.5.13 Analog-to-Digital Converter Module (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.5.14 Supply Voltage Sense (BATS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.5.15 On-Chip Voltage Regulator system (VREG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

1.5.16 Low-side driver (LSDRV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.5.17 Low-side driver (LS2DRV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.5.18 Current Sense Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.5.19 High-side drivers (HSDRV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.5.20 Background Debug (BDM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

1.5.21 Debugger (DBG) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

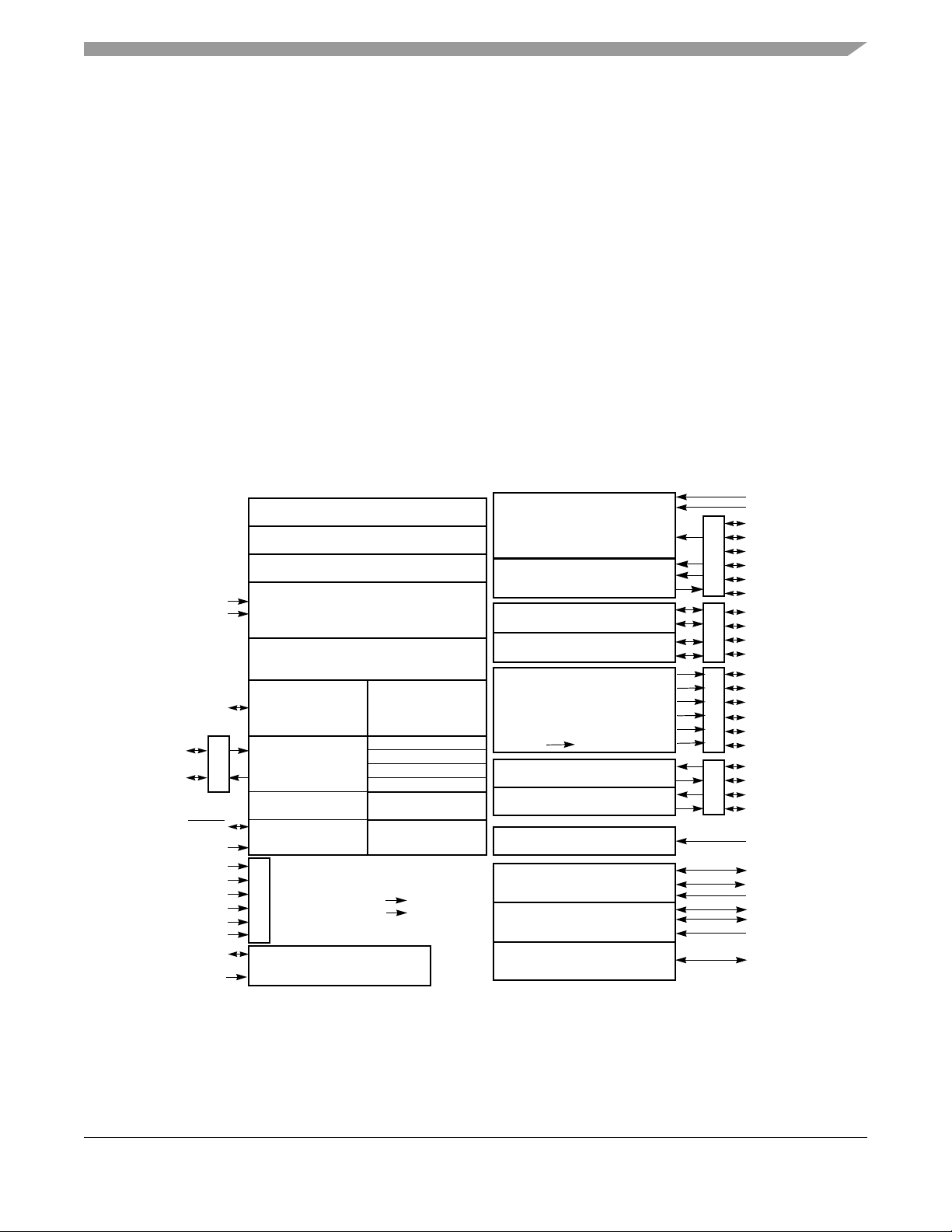

1.6 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

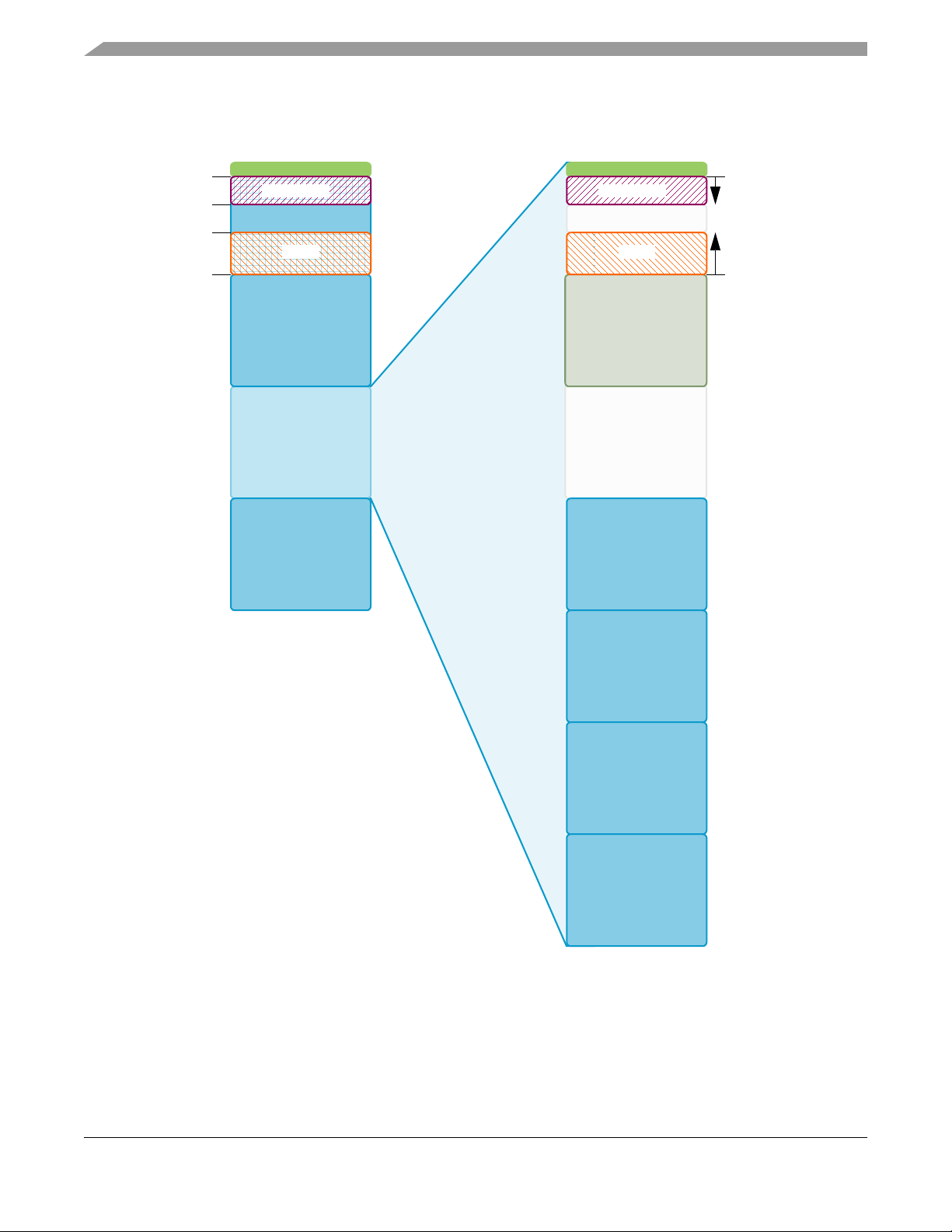

1.7 Family Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 26

1.7.1 Part ID Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.8 Signal Description and Device Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.8.1 Pin Assignment Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.8.2 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

1.8.3 Power Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

1.8.4 Device Pinouts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

1.8.5 MC9S12VRP Pinout 48-pin LQFP . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 35

1.9 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

1.9.1 Chip Configuration Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

1.9.2 Low Power Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 39

1.10 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

1.11 Resets and Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

1.11.1 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

1.11.2 Interrupt Vectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

1.11.3 Effects of Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 3

Page 4

1.12 Module Device level Dependencies . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

1.12.1 ADC External Trigger Input Connection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

1.12.2 ADC Special Conversion Channels . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1.12.3 HVI Digital input enables . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1.12.4 API external clock output (API_EXTCLK) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1.12.5 COP Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

1.12.6 CPMU High Temperature Trimming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

1.12.7 Flash IFR Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 45

Chapter 2

Port Integration Module (S12VRPPIMV1)

2.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.1.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

2.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 50

2.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

2.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

2.3.1 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

2.3.2 Device Specific PIM Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 61

2.3.3 PIM Generic Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

2.3.4 PIM Generic Register Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74

2.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

2.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

2.4.2 Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

2.4.3 Pin I/O Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

2.4.4 Pull Devices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.4.5 Increased Drive Strength on PP2, PP1 and PP0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.4.6 High Side Drivers and Low Side Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.4.7 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

2.4.8 High-Voltage Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

2.5 Initialization and Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

2.5.1 Port Data and Data Direction Register writes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

2.5.2 SCI Baud Rate Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

2.5.3 Over-Current Protection on PP2 and PP0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

2.5.4 Open Input Detection on PL[5:0] (HVI) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 90

Chapter 3

S12G Memory Map Controller (S12GMMCV1)

3.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.1.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

3.1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.1.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.1.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

3.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

MC9S12VRP Family Reference Manual Rev. 1.3

4 NXP Semiconductors

Page 5

3.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

3.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

3.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 96

3.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

3.4.1 MCU Operating Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

3.4.2 Memory Map Scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

3.4.3 Unimplemented and Reserved Address Ranges . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 104

3.4.4 Prioritization of Memory Accesses . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

3.4.5 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Chapter 4

S12 Clock, Reset and Power Management Unit (S12CPMU_UHV_V8)

4.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

4.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

4.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

4.1.3 S12CPMU_UHV_V8 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 113

4.2 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.2.1 RESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.2.2 EXTAL and XTAL . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.2.3 VSUP — Regulator Power Input Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.2.4 VDDA, VSSA — Regulator Reference Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.2.5 VDDX, VSSX— Pad Supply Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 115

4.2.6 VSS— Ground Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

4.2.7 API_EXTCLK — API external clock output pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 116

4.2.8 VDD— Internal Regulator Output Supply (Core Logic) . . . . . . . . . . . . . . . . . . . . . . . 116

4.2.9 VDDF— Internal Regulator Output Supply (NVM Logic) . . . . . . . . . . . . . . . . . . . . . 116

4.2.10 TEMPSENSE — Internal Temperature Sensor Output Voltage . . . . . . . . . . . . . . . . . . 116

4.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

4.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 117

4.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 119

4.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

4.4.1 Phase Locked Loop with Internal Filter (PLL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 153

4.4.2 Startup from Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 155

4.4.3 Stop Mode using PLLCLK as source of the Bus Clock . . . . . . . . . . . . . . . . . . . . . . . . 156

4.4.4 Full Stop Mode using Oscillator Clock as source of the Bus Clock . . . . . . . . . . . . . . . 156

4.4.5 External Oscillator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 158

4.4.6 System Clock Configurations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 159

4.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

4.5.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 160

4.5.2 Description of Reset Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 161

4.5.3 Oscillator Clock Monitor Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

4.5.4 PLL Clock Monitor Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 162

4.5.5 Power-On Reset (POR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

4.5.6 Low-Voltage Reset (LVR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

4.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 164

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 5

Page 6

4.6.1 Description of Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 165

4.7 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

4.7.1 General Initialization information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 166

4.7.2 Application information for COP and API usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 167

Chapter 5

Background Debug Module (S12SBDMV1)

5.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

5.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169

5.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 170

5.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

5.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

5.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

5.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 171

5.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 172

5.3.3 Family ID Assignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

5.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

5.4.1 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

5.4.2 Enabling and Activating BDM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 176

5.4.3 BDM Hardware Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 177

5.4.4 Standard BDM Firmware Commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 178

5.4.5 BDM Command Structure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 179

5.4.6 BDM Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 181

5.4.7 Serial Interface Hardware Handshake Protocol . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 184

5.4.8 Hardware Handshake Abort Procedure . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 186

5.4.9 SYNC — Request Timed Reference Pulse . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

5.4.10 Instruction Tracing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 189

5.4.11 Serial Communication Time Out . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 190

Chapter 6

S12S Debug Module (S12DBGV2)

6.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

6.1.1 Glossary Of Terms . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 193

6.1.2 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

6.1.3 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 194

6.1.4 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

6.1.5 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 195

6.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

6.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

6.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 196

6.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 197

6.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

6.4.1 S12DBGV2 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 214

6.4.2 Comparator Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 215

MC9S12VRP Family Reference Manual Rev. 1.3

6 NXP Semiconductors

Page 7

6.4.3 Match Modes (Forced or Tagged) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 219

6.4.4 State Sequence Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 220

6.4.5 Trace Buffer Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 221

6.4.6 Tagging . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227

6.4.7 Breakpoints . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 228

6.5 Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6.5.1 State Machine scenarios . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6.5.2 Scenario 1 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6.5.3 Scenario 2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 230

6.5.4 Scenario 3 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

6.5.5 Scenario 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 231

6.5.6 Scenario 5 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

6.5.7 Scenario 6 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

6.5.8 Scenario 7 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 233

6.5.9 Scenario 8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

6.5.10 Scenario 9 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

6.5.11 Scenario 10 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 234

Chapter 7

Interrupt Module (S12SINTV1)

7.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

7.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

7.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 237

7.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

7.1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 238

7.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

7.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

7.3.1 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 239

7.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

7.4.1 S12S Exception Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

7.4.2 Interrupt Prioritization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 240

7.4.3 Reset Exception Requests . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

7.4.4 Exception Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 241

7.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

7.5.1 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

7.5.2 Interrupt Nesting . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

7.5.3 Wake Up from Stop or Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 242

Chapter 8

Analog-to-Digital Converter (ADC12B12CV2)

Block Description

8.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

8.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 245

8.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 247

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 7

Page 8

8.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 248

8.2 Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

8.2.1 Detailed Signal Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

8.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

8.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 249

8.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 252

8.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

8.4.1 Analog Sub-Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

8.4.2 Digital Sub-Block . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 268

8.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

8.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 270

Chapter 9

Pulse-Width Modulator (S12PWM8B8CV2)

9.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

9.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

9.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 271

9.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

9.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 272

9.2.1 PWM7 - PWM0 — PWM Channel 7 - 0 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

9.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

9.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

9.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 273

9.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

9.4.1 PWM Clock Select . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 287

9.4.2 PWM Channel Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 291

9.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 299

9.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 300

Chapter 10

Serial Communication Interface (S12SCIV6)

10.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

10.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 301

10.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

10.1.3 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 302

10.1.4 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 303

10.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

10.2.1 TXD — Transmit Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

10.2.2 RXD — Receive Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

10.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

10.3.1 Module Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 304

10.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 305

10.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 317

10.4.1 Infrared Interface Submodule . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

MC9S12VRP Family Reference Manual Rev. 1.3

8 NXP Semiconductors

Page 9

10.4.2 LIN Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 318

10.4.3 Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 319

10.4.4 Baud Rate Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 320

10.4.5 Transmitter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 321

10.4.6 Receiver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 326

10.4.7 Single-Wire Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 334

10.4.8 Loop Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

10.5 Initialization/Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

10.5.1 Reset Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 335

10.5.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336

10.5.3 Interrupt Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 336

10.5.4 Recovery from Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

10.5.5 Recovery from Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 339

Chapter 11

Timer Module (TIM16B2CV3)

11.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

11.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

11.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 341

11.1.3 Block Diagrams . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342

11.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 342

11.2.1 IOC1 - IOC0 — Input Capture and Output Compare Channel 1-0 . . . . . . . . . . . . . . . . 342

11.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

11.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

11.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 343

11.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 354

11.4.1 Prescaler . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 355

11.4.2 Input Capture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

11.4.3 Output Compare . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 356

11.5 Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

11.6 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

11.6.1 Channel [1:0] Interrupt (C[1:0]F) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

11.6.2 Timer Overflow Interrupt (TOF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 357

Chapter 12

High-Side Driver Module - HSDRV2C (HSDRV2CV3)

12.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 359

12.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 359

12.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

12.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 360

12.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

12.2.1 HS[0], HS[1] — High Side Driver Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

12.2.2 VSUPHS — High Side Driver Power Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 361

12.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 9

Page 10

12.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 362

12.3.2 Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 363

12.3.3 Port HS Data Register (HSDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 363

12.3.4 HSDRV2C Configuration Register (HSCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 363

12.3.5 HSDRV2C Slew Rate Control Register (HSSLR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 365

12.3.6 Reserved Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 366

12.3.7 HSDRV2C Status Register (HSSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 367

12.3.8 HSDRV2C Interrupt Enable Register (HSIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 368

12.3.9 HSDRV2C Interrupt Flag Register (HSIF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

12.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

12.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

12.4.2 Open Load Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 369

12.4.3 Over-Current Shutdown . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

12.4.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 370

Chapter 13

Low-Side Drivers - LSDRV (S12LSDRV2)

13.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

13.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 371

13.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

13.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 372

13.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

13.2.1 LS0, LS1— Low Side Driver Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

13.2.2 LSGND — Low Side Driver Ground Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

13.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

13.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 373

13.3.2 Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

13.3.3 Port LS Data Register (LSDR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 375

13.3.4 LSDRV Configuration Register (LSCR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 376

13.3.5 Reserved Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

13.3.6 Reserved Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 377

13.3.7 LSDRV Status Register (LSSR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 378

13.3.8 LSDRV Interrupt Enable Register (LSIE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 379

13.3.9 LSDRV Interrupt Flag Register (LSIF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 380

13.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

13.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

13.4.2 Open-Load Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

13.4.3 Over-Current Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

13.4.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 381

Chapter 14

Low-Side Driver - LS2DRV (S12LS2DRV_V1)

14.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

14.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

MC9S12VRP Family Reference Manual Rev. 1.3

10 NXP Semiconductors

Page 11

14.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 383

14.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 384

14.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

14.2.1 LS2 — Low Side Driver Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

14.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

14.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 385

14.3.2 Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 387

14.3.3 Port LS Data Register (LS2DR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 387

14.3.4 LS2DRV Configuration Register (LS2CR) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 388

14.3.5 Reserved Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 389

14.3.6 LS2DRV Interrupt Enable Register (LS2IE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 390

14.3.7 LS2DRV Interrupt Flag Register (LS2IF) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 391

14.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

14.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

14.4.2 Over-Current Detection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

14.4.3 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 392

Chapter 15

Current Sense Amplifier Module (ISENSEV1)

15.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 393

15.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 393

15.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

15.4 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

15.4.1 AMPP — Current Sense Amplifier Non-Inverting Input Pin . . . . . . . . . . . . . . . . . . . . 394

15.4.2 AMPM — Current Sense Amplifier Inverting Input Pin . . . . . . . . . . . . . . . . . . . . . . . 394

15.4.3 AMP — Current Sense Amplifier Output Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 394

15.5 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

15.5.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

15.5.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 395

15.6 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400

15.6.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 400

15.6.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 402

Chapter 16

LIN Physical Layer (S12LINPHYV2)

16.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

16.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 403

16.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 404

16.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 404

16.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

16.2.1 LIN — LIN Bus Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

16.2.2 LGND — LIN Ground Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

16.2.3 VLINSUP — Positive Power Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

16.2.4 LPTxD — LIN Transmit Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 11

Page 12

16.2.5 LPRxD — LIN Receive Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 406

16.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 407

16.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 407

16.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 408

16.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

16.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

16.4.2 Slew Rate and LIN Mode Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 415

16.4.3 Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 416

16.4.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 419

16.5 Application Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

16.5.1 Module Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 422

16.5.2 Interrupt handling in Interrupt Service Routine (ISR) . . . . . . . . . . . . . . . . . . . . . . . . . . 422

Chapter 17

Supply Voltage Sensor - (BATSV2)

17.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

17.1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

17.1.2 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 425

17.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 426

17.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 426

17.2.1 VSENSE — Supply (Battery) Voltage Sense Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 426

17.2.2 VSUP — Voltage Supply Pin . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 427

17.3 Memory Map and Register Definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 427

17.3.1 Register Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 427

17.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 428

17.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

17.4.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 433

17.4.2 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 434

Chapter 18

64 KByte Flash Module (S12FTMRG64K4KV2)

18.1 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

18.1.1 Glossary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 438

18.1.2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

18.1.3 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 439

18.2 External Signal Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 440

18.3 Memory Map and Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

18.3.1 Module Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 441

18.3.2 Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 445

18.4 Functional Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

18.4.1 Modes of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

18.4.2 IFR Version ID Word . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

18.4.3 Internal NVM resource (NVMRES) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

18.4.4 Flash Command Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 464

MC9S12VRP Family Reference Manual Rev. 1.3

12 NXP Semiconductors

Page 13

18.4.5 Allowed Simultaneous P-Flash and D-Flash Operations . . . . . . . . . . . . . . . . . . . . . . . 469

18.4.6 Flash Command Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 470

18.4.7 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 484

18.4.8 Wait Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

18.4.9 Stop Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

18.5 Security . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

18.5.1 Unsecuring the MCU using Backdoor Key Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . 485

18.5.2 Unsecuring the MCU in Special Single Chip Mode using BDM . . . . . . . . . . . . . . . . . 486

18.5.3 Mode and Security Effects on Flash Command Availability . . . . . . . . . . . . . . . . . . . . . 487

18.6 Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 487

Appendix A

MCU Electrical Specifications

A.1 General . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 489

A.1.1 Parameter Classification . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 489

A.1.2 Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 490

A.1.3 Current Injection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 490

A.1.4 Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 491

A.1.5 ESD Protection and Latch-up Immunity . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 492

A.1.6 Recommended Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

A.1.7 Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 494

A.1.8 Power Dissipation and Thermal Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 495

A.2 General Purpose I/O Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 497

A.2.1 High Voltage Inputs (HVI) Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

A.3 Supply Currents. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

A.3.1 Measurement Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 500

Appendix B

CPMU Electrical Specifications (VREG, OSC, IRC, PLL)

B.1 VREG Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 503

B.2 Reset and Stop Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 504

B.3 OSC Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

B.4 IRC Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

B.5 Phase Locked Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

B.5.1 Jitter Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 505

Appendix C

ADC Electrical Specifications

C.1 ADC Operating Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 508

C.1.1 Factors Influencing Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 508

C.2 ADC Analog Input Parasitics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 511

C.3 ADC Accuracy . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 511

C.3.1 ADC Accuracy Definitions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 512

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 13

Page 14

Appendix D

HSDRV Electrical Specifications

D.1 Static Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 515

D.2 Dynamic Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 516

Appendix E

LINPHY Electrical Specifications

E.1 Static Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 517

E.2 Dynamic Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 518

Appendix F

LSDRV/LS2DRV Electrical Specifications

F.1 LSDRV Static Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 520

F.2 LSDRV Dynamic Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

F.3 LS2DRV Static Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 521

Appendix G

ISENSE Electrical Specifications

G.1 Operating Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 522

Appendix H

BATS Electrical Specifications

H.1 Static Electrical Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 523

H.2 Dynamic Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 524

Appendix I

NVM Electrical Parameters

I.1 NVM Timing Parameters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 525

I.2 NVM Reliability Parameters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 527

Appendix J

Package Information

Appendix K

Ordering Information

Appendix L

Detailed Register Address Map

L.1 0x0000-0x0009 Port Integration Module (PIM) Map 1 of 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 535

L.2 0x000A-0x000B Module Mapping Control (MMC) Map 1 of 2 . . . . . . . . . . . . . . . . . . . . . . . . . 535

L.3 0x000C-0x000D Port Integration Module (PIM) Map 2 of 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 535

L.4 0x000E-0x000F Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 536

MC9S12VRP Family Reference Manual Rev. 1.3

14 NXP Semiconductors

Page 15

L.5 0x0010-0x0017 Module Mapping Control (MMC) Map 2 of 2 . . . . . . . . . . . . . . . . . . . . . . . . . . 536

L.6 0x0018-0x0019 Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 536

L.7 0x001A-0x001B Part ID Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 537

L.8 0x001C-0x001F Port Integration Module (PIM) Map 3 of 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 537

L.9 0x0020-0x002F Debug Module (S12SDBG) Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 537

L.10 0x0030-0x0033 Reserved . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 538

L.11 0x0034-0x003F Clock Reset and Power Management (CPMU) Map . . . . . . . . . . . . . . . . . . . . . 538

L.12 0x0040-0x006F Timer Module (TIM0) Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 539

L.13 0x0070-0x009F Analog to Digital Converter (ATD) Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 540

L.14 0x00A0-0x00C7 Pulse Width Modulator 6-Channels (PWM) Map. . . . . . . . . . . . . . . . . . . . . . . 542

L.15 0x00C8-0x00CF Serial Communication Interface (SCI0) Map . . . . . . . . . . . . . . . . . . . . . . . . . . 543

L.16 0x00D0-0x00D7 Serial Communication Interface (SCI1) Map . . . . . . . . . . . . . . . . . . . . . . . . . . 545

L.17 0x0100-0x0113 NVM Control Register (FTMRG) Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 545

L.18 0x0120 Interrupt Vector Base Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 546

L.19 0x0140-0x0147 High Side Drivers (HSDRV2C) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 547

L.20 0x0150-0x0157 Low Side Drivers (LSDRV) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 547

L.21 0x0158-0x015F Low Side Driver (LS2DRV). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 547

L.22 0x0170-0x0177 Supply Voltage Sense (BATS) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 548

L.23 0x0178-0x017F Current Sense Amplifier (ISENSE) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 549

L.24 0x0180-0x01AF Timer Module (TIM1) Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 549

L.25 0x0240 -0x027F Port Integration Module (PIM) Map 4 of 4 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 551

L.26 0x02F0-0x02FF Clock and Power Management Unit (CPMU) Map 2 of 2. . . . . . . . . . . . . . . . . 554

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 15

Page 16

MC9S12VRP Family Reference Manual Rev. 1.3

16 NXP Semiconductors

Page 17

Chapter 1 Device Overview S12VRP-Series

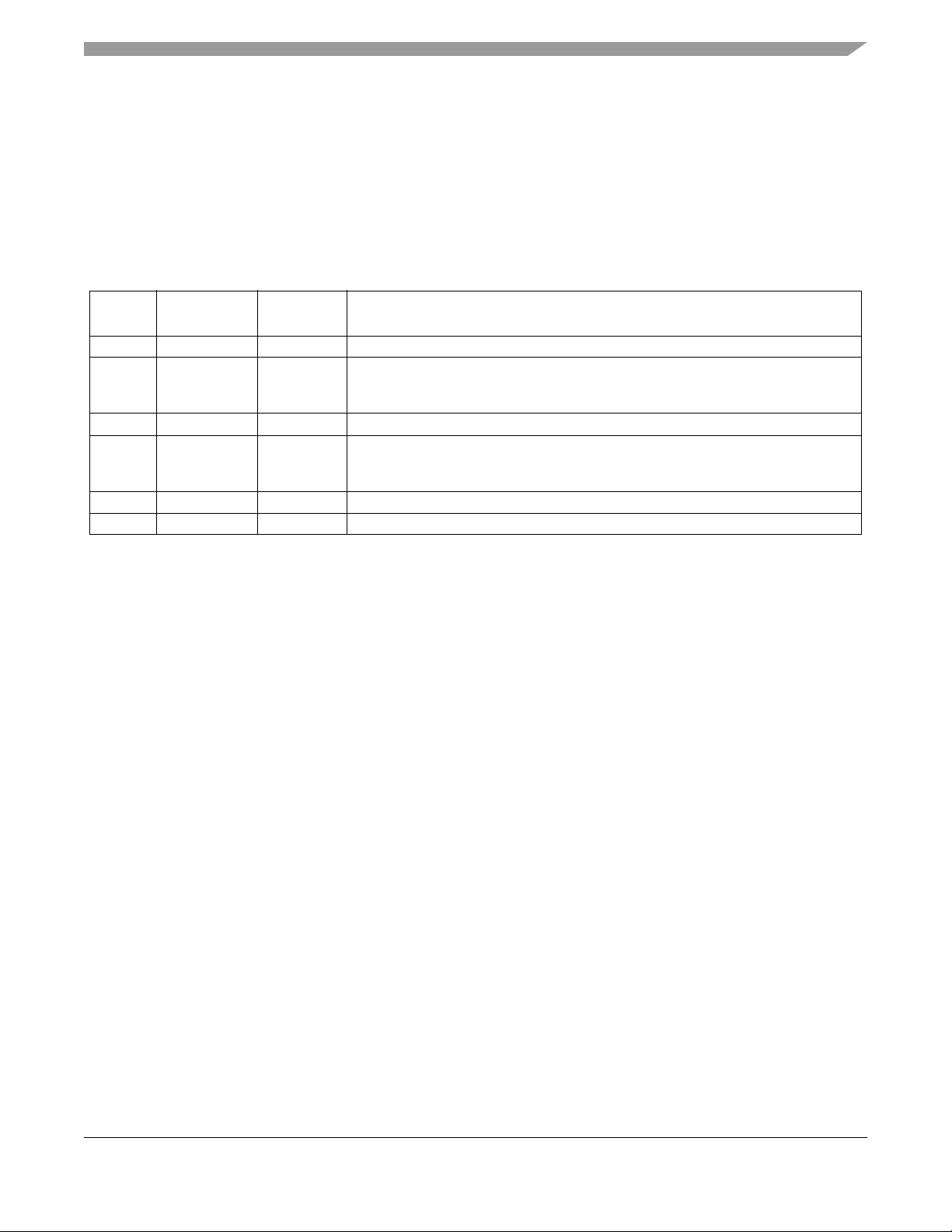

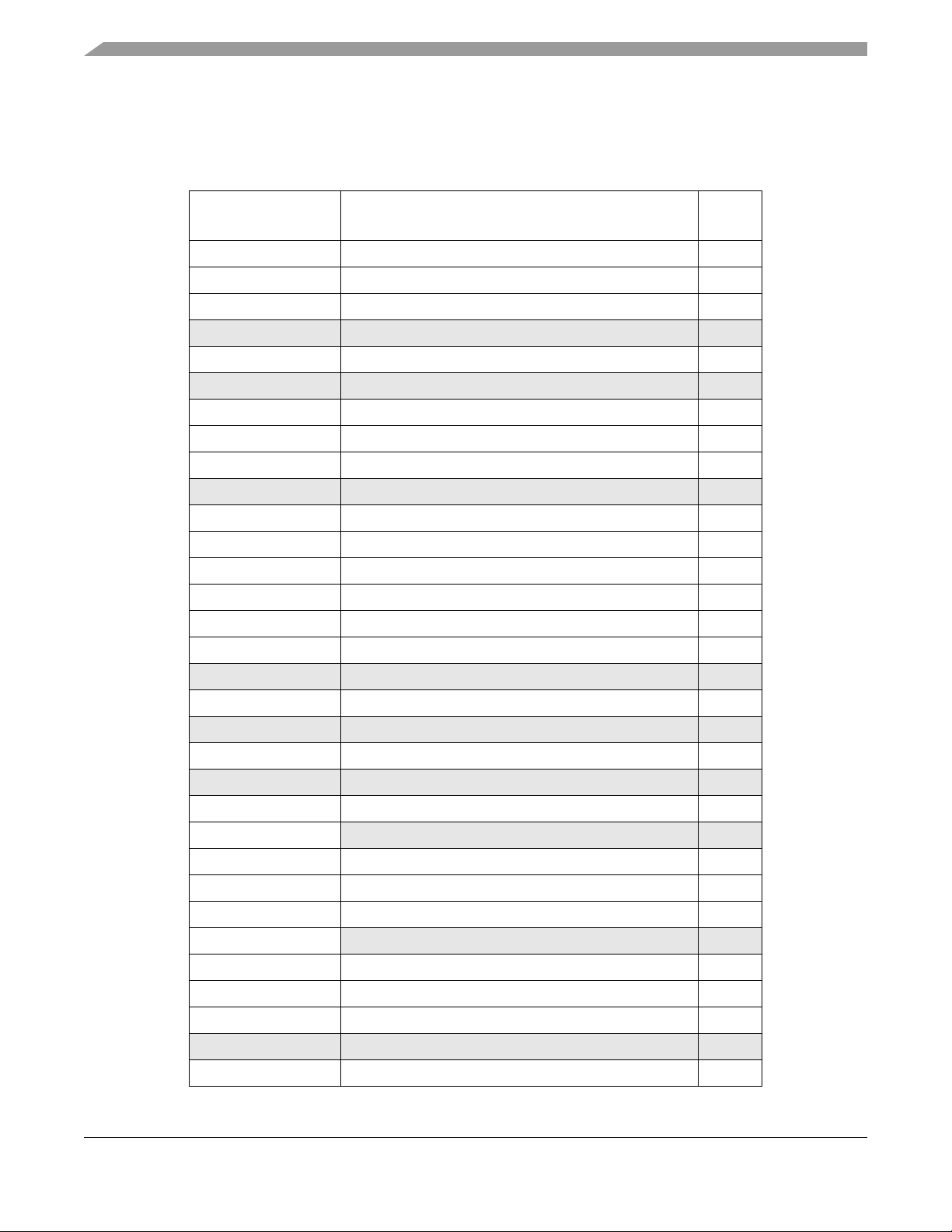

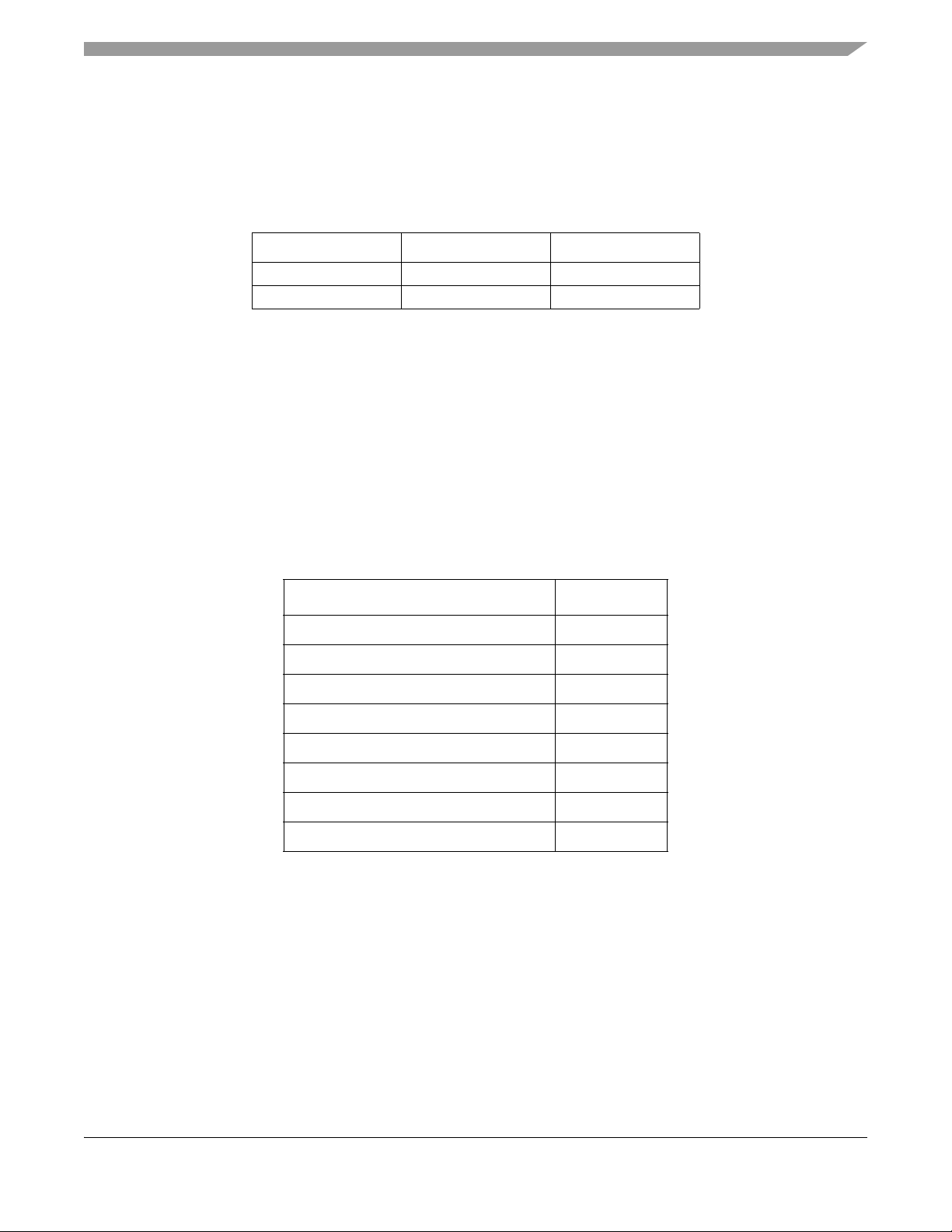

Table 1-1. Revision History

Version

Number

0.1A 8-Apr-2016 All • Initial Draft

0.2 28-Apr-2016 All • Moved API_EXTCLK from PS2 to PT2 following DFT feedback

0.3 02-Jun-2016 All • Minor corrections based on shared review feedback

0.4 08-Jul-2016 Various

0.5 05-Sep-2016 • Removed ADC calibration information

0.6 02-Aug-2017 • Corrected typos and formatting

Revision

Date

Sections

Affected

1.12.3/1-44

Various

Description of Changes

• Removed VSUPHS and specified high-side drive is supplied by VSUP

• Minor corrections from initial draft shared review

• Corrections based on V1.0A shared review feedback

• Documented HVI digital inputs are controlled by PortL DIENL not ATDDIENx

• Removed SC part information

1.1 Introduction

The S12VRP-Series is an optimized automotive 16-bit microcontroller product line focused on low-cost,

high-performance, and low pin-count. Like other MagniV devices, the S12VRP-Series integrates key

components such as a LIN physical interface and a voltage regulator system to supply the microcontroller

directly from the vehicle battery. Being part of the existing MC9S12VR-Family, the S12VRP-Series

integrates key analog blocks to control other elements of the system which operate at vehicle battery level

(e.g. relay drivers, high-side driver outputs, wake up inputs). The S12VRP-Series extends the existing

MC9S12VR-Family with more RAM, more high-voltage inputs, current sensing capabilities and some

other enhancements.

The S12VRP-Series uses many features already found in the MagniV family, including error correction

code (ECC) on flash memory, a separate data-flash module for diagnostic or data storage, a fast

analog-to-digital converter (ADC) and a frequency modulated phase locked loop (IPLL) that improves the

EMC performance.

The S12VRP-Series delivers an optimized solution with the integration of several key system components

into a single device, optimizing system architecture and achieving significant space savings. The

S12VRP-Series delivers all the advantages and efficiencies of a 16-bit MCU while retaining the low cost,

power consumption, EMC, and code-size efficiency advantages currently enjoyed by users of NXP’s

existing 8-bit and 16-bit MCU families. The S12VRP-Series is offered in a 48-pin LQFP package. In

addition to the I/O ports available in each module, further I/O ports are available with interrupt capability

allowing wake-up from stop or wait modes.

The S12VRP-Series is targeted at relay based motor control automotive applications requiring single node

LIN communications. Typical examples of these applications include:

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 17

Page 18

Device Overview S12VRP-Series

• Window lift modules

• Door modules

• Seat controllers

• Smart actuators

• Sun roof modules

1.2 Features

This section describes the key features of the S12VRP-Series.

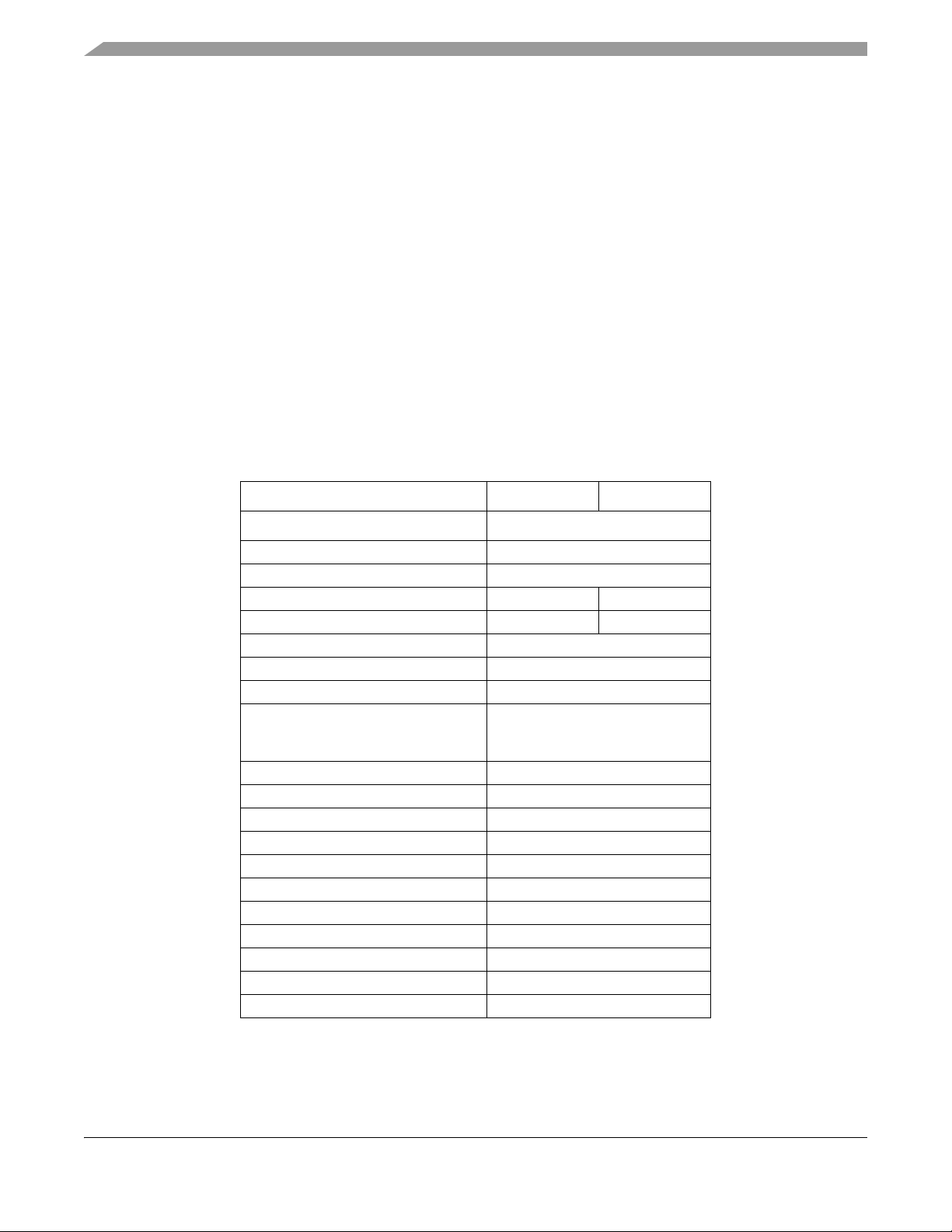

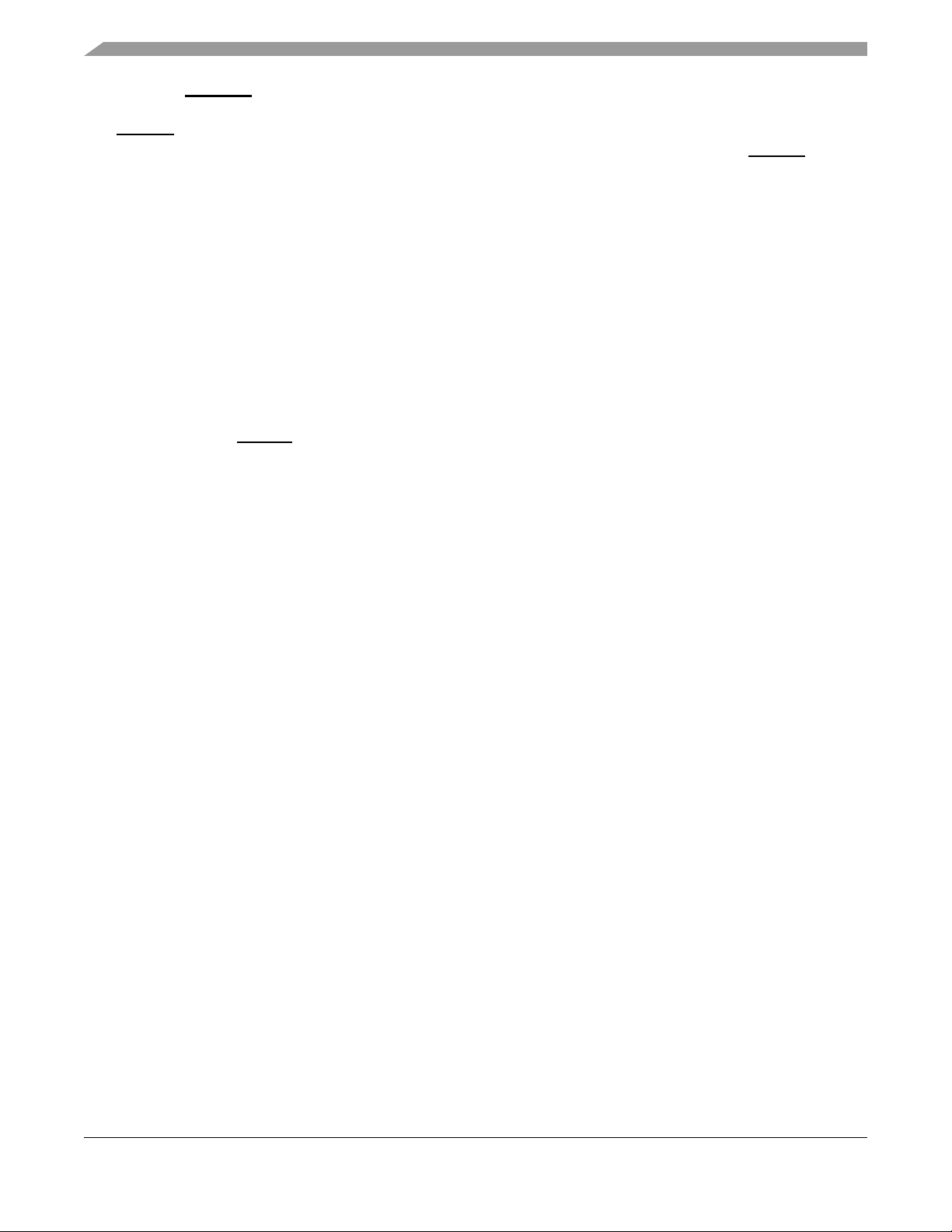

1.3 S12VRP-Series Comparison

Table 1-2 provides a summary of different members of the S12VRP-Series and their features.

S12VRP is part of NXP S12VR-family, commonalities & differences are outlined in AN5328, also

including a comparison to MM912_634.

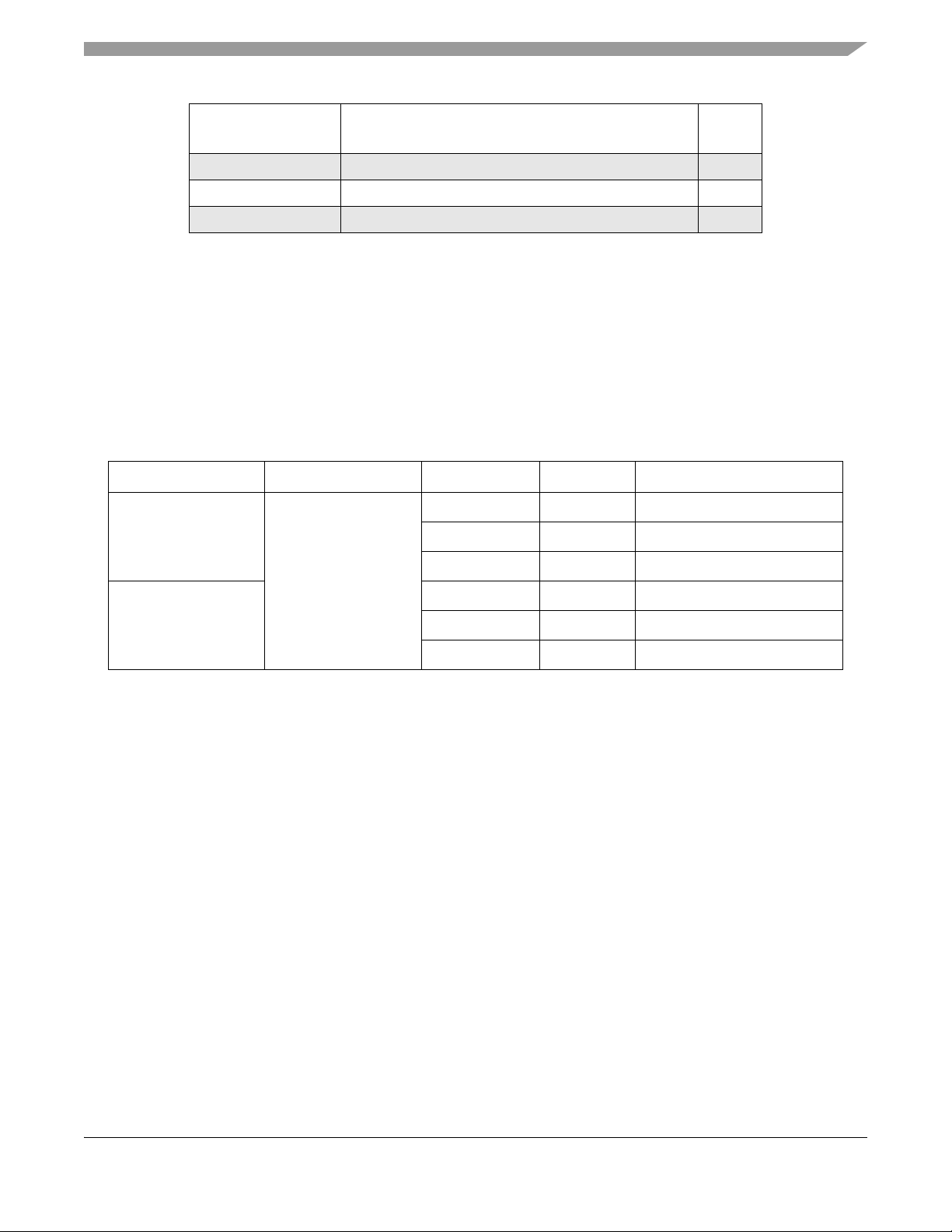

Table 1-2. S1 2 V R P-Serie s

Feature S12VRP48 S12VRP64

Package option 48LQFP

Core HCS12

Bus frequency 25 MHz

Flash memory (ECC) 48 KB 64 KB

Data-Flash 2 KB 4 KB

RAM 6 KB

LIN Physical layer 1

1

SCI

Timer

- TIM0

- TIM1

PWM 8ch x 8-bit or 4ch x 16-bit

10-bit ADC channels 12

Frequency modulated PLL Yes

Internal 1 MHz RC oscillator Yes

Autonomous window watchdog 1

Low side driver (relay driver) 2

Low side driver (general) 1

High side driver 2

Current sense amplifier 1

High voltage Inputs 6

Direct Battery sense pin, Vsense Yes

2

2ch x16-bit

2ch x16-bit

2

MC9S12VRP Family Reference Manual Rev. 1.3

18 NXP Semiconductors

Page 19

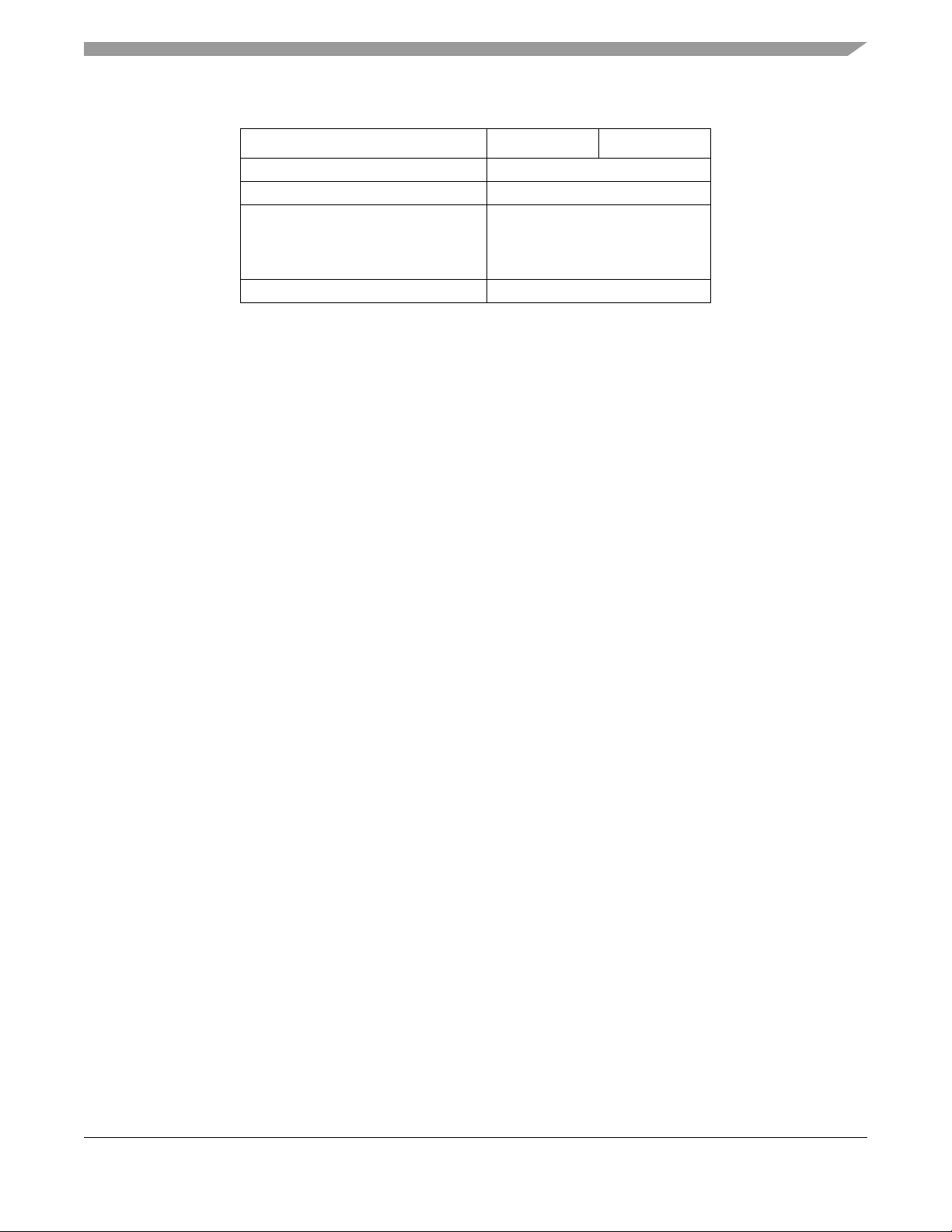

Table 1-2. S1 2 V R P-Serie s

Feature S12VRP48 S12VRP64

Supply voltage sense, Vsup Yes

Chip temperature sensor 1

3

General purpose I/O

- 10mA Driver pin

- 20mA EVDD (e.g. Hall Sensor supply)

- 20mA @5V LL-FET Driver

Interrupt capable pins (5V/12V) 12/6

1

SCI0 is routed to LIN PHY by default

2

6 mapped to PAD pins, 6 mapped to HVI pins

3

All port pins (including PADx and PLx)

including:-

28

1

1

1

1.4 Chip-Level Features

On-chip modules available within the family include the following features:

• HCS12 CPU core

Device Overview S12VRP-Series

• 64 KB or 48 KB on-chip Program-FLASH with ECC

• 4 KB or 2KB Data-FLASH with ECC

• 6 KB on-chip SRAM

• Phase locked loop (IPLL) frequency multiplier with internal filter

• 1 MHz internal RC oscillator with +/-1.3% accuracy over rated temperature range

• 4-20 MHz amplitude controlled pierce oscillator

• Internal COP (watchdog) module (with separate clock source)

• Two timer modules (TIM) supporting input/output channels that provide a range of 16-bit input

capture & output compare (up to 4 channels)

• Pulse width modulation (PWM) module (up to 8x 8-bit channels or 4x 16-bit channels)

• 10-bit resolution successive approximation analog-to-digital converter (ADC) with up to 6

channels mapped to external PAD pins and 6 channels mapped to HVI pins

• One serial communication interface (SCI) module supporting LIN communications (with RX

connected to a timer channel for internal oscillator calibration purposes, if desired)

• One on-chip LIN physical layer transceiver fully compliant with the LIN 2.2A & SAE J2602-2

standards routed to the SCI module supporting LIN communications

• One additional SCI (not connected to LIN physical layer)

• On-chip voltage regulator (VREG) for regulation of input supply and all internal voltages

• Autonomous periodic interrupt (API) (combined with watchdog)

• Two protected low-side driver outputs to drive inductive loads (VSUP domain)

• One further 20mA low-side driver output (VSUP domain)

• Two protected high-side driver outputs (VSUP domain)

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 19

Page 20

Device Overview S12VRP-Series

• Six high-voltage inputs (HVI) with wake-up capability and interface to internal ADC

• 20mA high-current 5V output for use as Hall sensor supply (PP2, EVDD)

• 20mA high-current 5V output to drive external logic level FET (PP0, Power GPIO)

• 10mA high current 5V output (PP1)

• Current sense circuits for over-current detection

• Battery voltage sense with low battery warning, internally reverse battery protected

• Chip temperature sensor

1.5 Module Features

The following sections provide more details of the modules implemented on the S12VRP-Series.

1.5.1 HCS12 16-Bit Central Processor Unit (CPU)

The HCS12 CPU is a high-speed, 16-bit processing unit that has a programming model identical to that of

the industry standard M68HC11 central processor unit (CPU).

• Full 16-bit data paths supports efficient arithmetic operation and high-speed math execution

• Supports instructions with odd byte counts, including many single-byte instructions. This allows

much more efficient use of ROM space.

• Extensive set of indexed addressing capabilities, including:

— Using the stack pointer as an indexing register in all indexed operations

— Using the program counter as an indexing register in all but auto increment/decrement mode

— Accumulator offsets using A, B, or D accumulators

— Automatic index predecrement, preincrement, postdecrement, and postincrement (by –8 to +8)

1.5.2 On-Chip Flash with ECC

On-chip flash memory on the S12VRP-Series features the following:

• 64 or 48 KB of program flash memory

— 32 data bits plus 7 syndrome ECC (error correction code) bits allowing single bit fault

correction and double fault detection

— Erase sector size 512 bytes

— Automated program and erase algorithm

— User margin level setting for reads

— Protection scheme to prevent accidental program or erase

• 4 KB of data flash memory

— Single bit error correction and double fault detection within a word during read operations

— Erase sector size 256 bytes

— Automated program and erase algorithm with verify and generation of ECC parity bits

— Protection scheme to prevent accidental program or erase

MC9S12VRP Family Reference Manual Rev. 1.3

20 NXP Semiconductors

Page 21

— User margin level setting for reads

1.5.3 On-Chip SRAM

• 6 KB of general-purpose RAM

1.5.4 Main External Oscillator (XOSCLCP)

• Loop control Pierce oscillator using 4 MHz to 20 MHz crystal

— Current gain control on amplitude output

— Signal with low harmonic distortion

— Low power

— Good noise immunity

— Eliminates need for external current limiting resistor

— Transconductance sized for optimum start-up margin for typical crystals

— Oscillator pins shared with GPIO functionality

1.5.5 Internal RC Oscillator (IRC)

Device Overview S12VRP-Series

• Factory trimmed internal reference clock

— 1 MHz internal RC oscillator with 1.3% accuracy over rated temperature range

1.5.6 Internal Phase-Locked Loop (IPLL)

• Phase-locked-loop clock frequency multiplier

— No external components required

— Reference divider and multiplier allow large variety of clock rates

— Automatic bandwidth control mode for low-jitter operation

— Automatic frequency lock detector

— Configurable option to spread spectrum for reduced EMC radiation (frequency modulation)

— Reference clock sources:

– Internal 1 MHz RC oscillator (IRC)

– External crystal oscillator

1.5.7 Clock and Power Management Unit (CPMU)

• Real time interrupt (RTI)

• Clock monitor (CM)

• System reset generation

MC9S12VRP Family Reference Manual Rev. 1.3

NXP Semiconductors 21

Page 22

Device Overview S12VRP-Series

1.5.8 System Integrity Support

• Power-on reset (POR)

• Illegal address detection with reset

• Low-voltage detection with interrupt or reset

• Computer operating properly (COP) watchdog with option to run on internal RC oscillator

— Configurable as window COP for enhanced failure detection

— Can be initialized out of reset using option bits located in flash memory

• Clock monitor supervising the correct function of the oscillator

1.5.9 Timer (TIM)