Page 1

MC9S08PA4 Reference Manual

Supports: MC9S08PA4

Document Number: MC9S08PA4RM

Rev. 5, 08/2017

Page 2

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

2 NXP Semiconductors

Page 3

Contents

Section number Title Page

Chapter 1

Device Overview

1.1 Introduction.....................................................................................................................................................................23

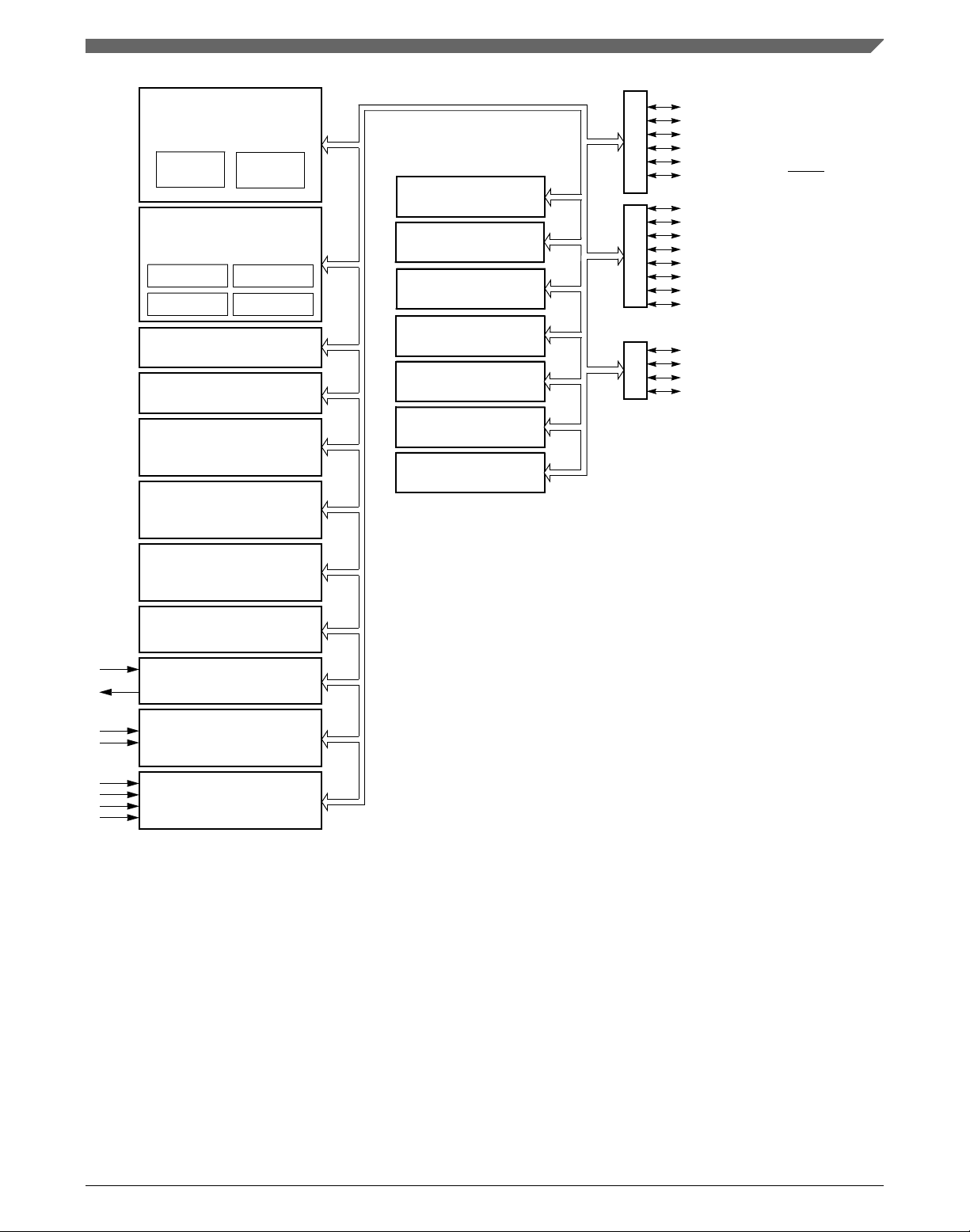

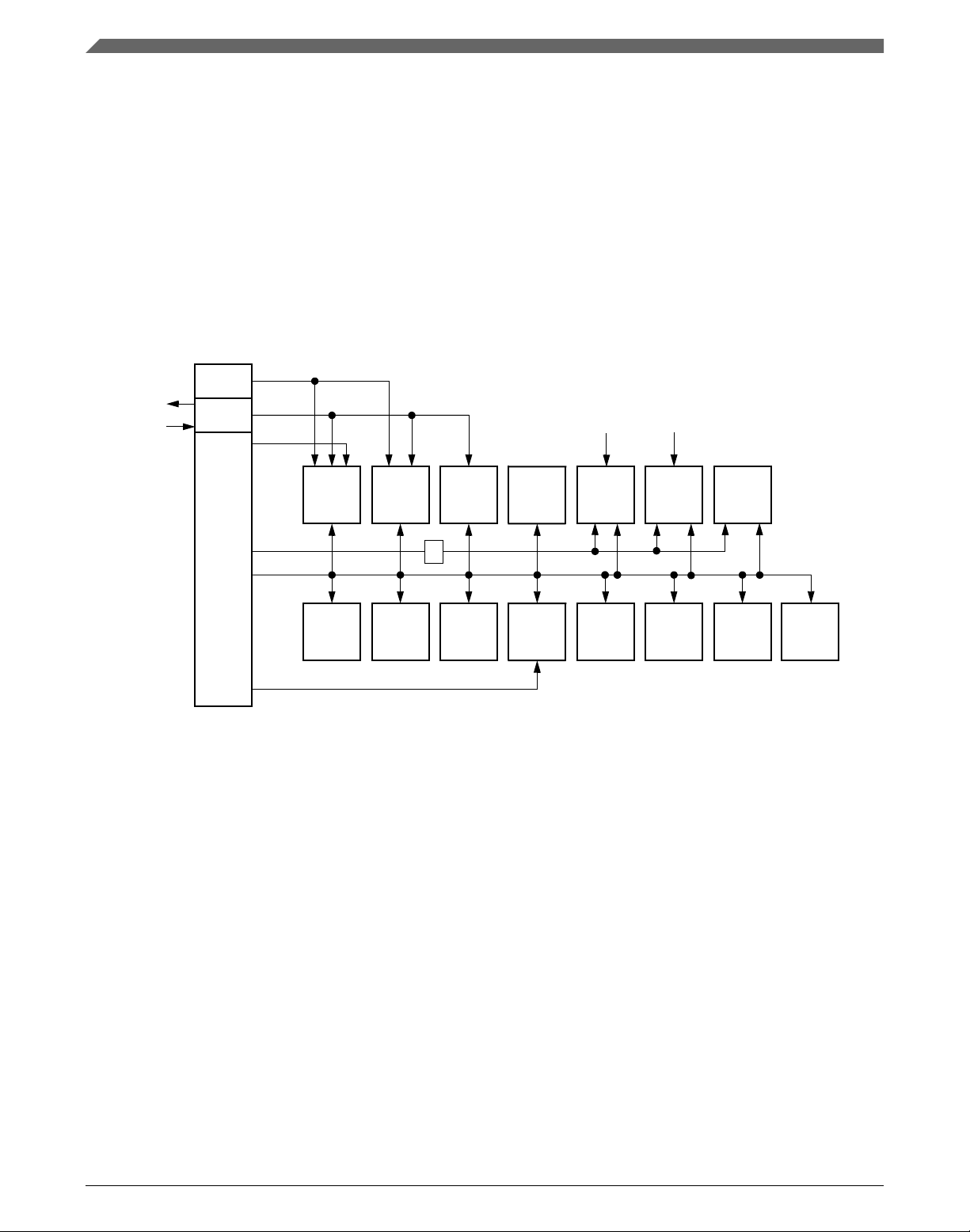

1.2 MCU block diagram....................................................................................................................................................... 24

1.3 System clock distribution................................................................................................................................................25

Chapter 2

Pins and connections

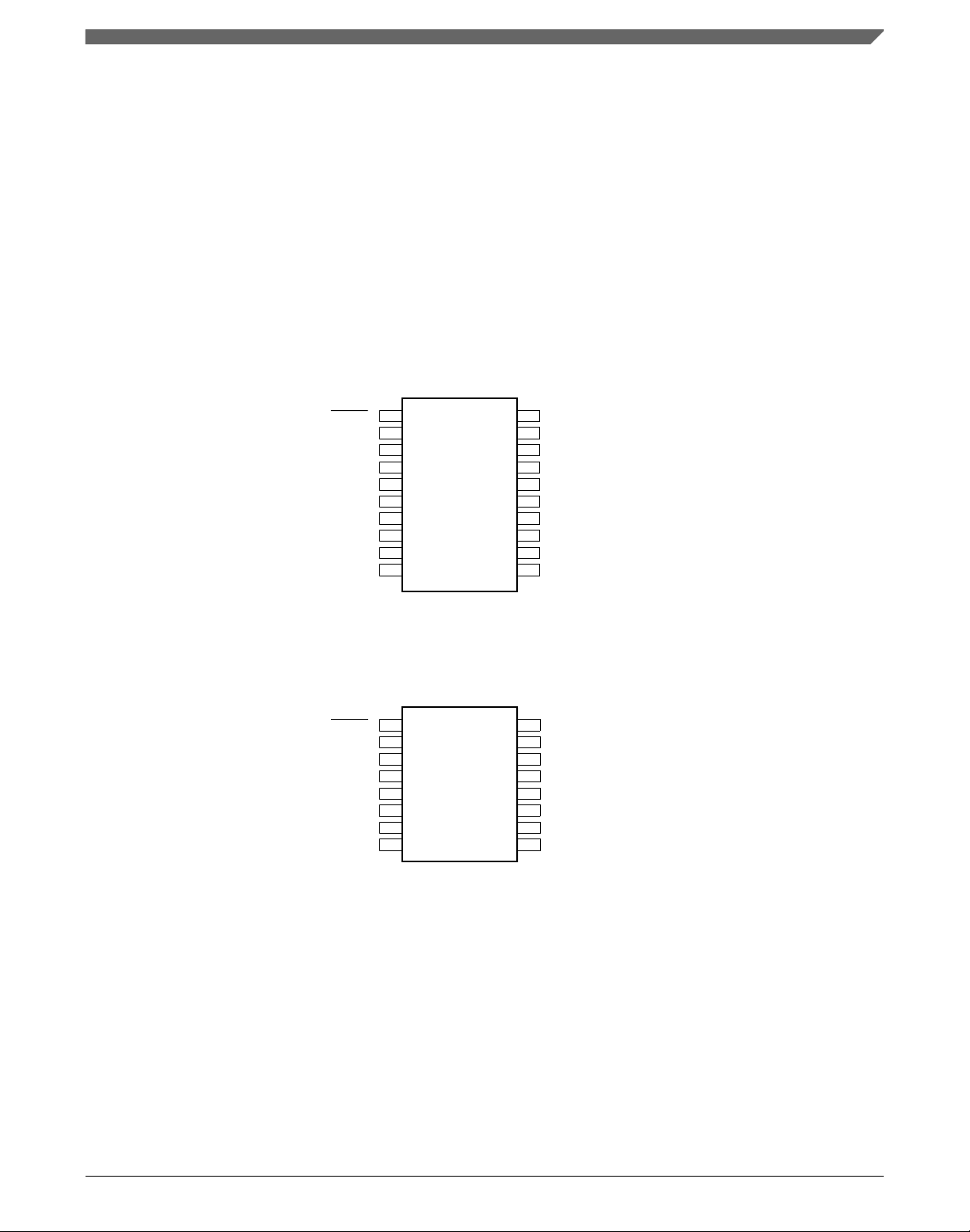

2.1 Device pin assignment.................................................................................................................................................... 29

2.2 Pin functions................................................................................................................................................................... 30

2.2.1 Power (VDD, VSS)..........................................................................................................................................30

2.2.2 Oscillator (XTAL, EXTAL)............................................................................................................................ 31

2.2.3 External reset pin (RESET) and interrupt pin (IRQ)....................................................................................... 32

2.2.4 Background/mode select (BKGD/MS)............................................................................................................ 33

2.2.5 Port A input/output (I/O) pins (PTA5–PTA0)................................................................................................. 34

2.2.6 Port B input/output (I/O) pins (PTB7–PTB0)..................................................................................................34

2.2.7 Port C input/output (I/O) pins (PTC3–PTC0)..................................................................................................34

2.2.8 True open drain pins (PTB0)........................................................................................................................... 34

2.2.9 High current drive pins (PTB4, PTB5)............................................................................................................ 34

2.3 Peripheral pinouts........................................................................................................................................................... 35

Chapter 3

Power management

3.1 Introduction.....................................................................................................................................................................37

3.2 Features...........................................................................................................................................................................37

3.2.1 Run mode......................................................................................................................................................... 37

3.2.2 Wait mode........................................................................................................................................................38

3.2.3 Stop3 mode...................................................................................................................................................... 38

3.2.4 Active BDM enabled in stop3 mode................................................................................................................38

3.2.5 LVD enabled in stop mode.............................................................................................................................. 39

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 3

Page 4

Section number Title Page

3.2.6 Power modes behaviors................................................................................................................................... 39

3.3 Low voltage detect (LVD) system..................................................................................................................................40

3.3.1 Power-on reset (POR) operation......................................................................................................................41

3.3.2 LVD reset operation.........................................................................................................................................41

3.3.3 Low-voltage warning (LVW).......................................................................................................................... 41

3.4 Bandgap reference.......................................................................................................................................................... 42

3.5 Power management control bits and registers................................................................................................................ 42

3.5.1 System Power Management Status and Control 1 Register (PMC_SPMSC1)................................................42

3.5.2 System Power Management Status and Control 2 Register (PMC_SPMSC2)................................................44

Chapter 4

Memory map

4.1 Memory map...................................................................................................................................................................45

4.2 Reset and interrupt vector assignments...........................................................................................................................46

4.3 Register addresses and bit assignments.......................................................................................................................... 47

4.4 Random-access memory (RAM).................................................................................................................................... 55

4.5 Flash and EEPROM........................................................................................................................................................56

4.5.1 Overview..........................................................................................................................................................56

4.5.2 Function descriptions....................................................................................................................................... 58

4.5.2.1 Modes of operation.......................................................................................................................... 58

4.5.2.2 Flash and EEPROM memory map...................................................................................................58

4.5.2.3 Flash and EEPROM initialization after system reset.......................................................................58

4.5.2.4 Flash and EEPROM command operations.......................................................................................59

4.5.2.5 Flash and EEPROM interrupts.........................................................................................................64

4.5.2.6 Protection......................................................................................................................................... 65

4.5.2.7 Security............................................................................................................................................ 68

4.5.2.8 Flash and EEPROM commands.......................................................................................................70

4.5.2.9 Flash and EEPROM command summary........................................................................................ 72

4.6 Flash and EEPROM registers descriptions.....................................................................................................................86

4.6.1 Flash Clock Divider Register (NVM_FCLKDIV)...........................................................................................86

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

4 NXP Semiconductors

Page 5

Section number Title Page

4.6.2 Flash Security Register (NVM_FSEC)............................................................................................................87

4.6.3 Flash CCOB Index Register (NVM_FCCOBIX)............................................................................................ 88

4.6.4 Flash Configuration Register (NVM_FCNFG)............................................................................................... 88

4.6.5 Flash Error Configuration Register (NVM_FERCNFG).................................................................................89

4.6.6 Flash Status Register (NVM_FSTAT).............................................................................................................90

4.6.7 Flash Error Status Register (NVM_FERSTAT).............................................................................................. 91

4.6.8 Flash Protection Register (NVM_FPROT)......................................................................................................92

4.6.9 EEPROM Protection Register (NVM_EEPROT)............................................................................................93

4.6.10 Flash Common Command Object Register:High (NVM_FCCOBHI)............................................................ 94

4.6.11 Flash Common Command Object Register: Low (NVM_FCCOBLO)...........................................................95

4.6.12 Flash Option Register (NVM_FOPT)..............................................................................................................95

Chapter 5

Interrupt

5.1 Interrupts.........................................................................................................................................................................97

5.1.1 Interrupt stack frame........................................................................................................................................ 98

5.1.2 Interrupt vectors, sources, and local masks......................................................................................................99

5.1.3 Hardware nested interrupt................................................................................................................................101

5.1.3.1 Interrupt priority level register.........................................................................................................103

5.1.3.2 Interrupt priority level comparator set............................................................................................. 104

5.1.3.3 Interrupt priority mask update and restore mechanism....................................................................104

5.1.3.4 Integration and application of the IPC............................................................................................. 105

5.2 IRQ..................................................................................................................................................................................105

5.2.1 Features............................................................................................................................................................ 106

5.2.1.1 Pin configuration options.................................................................................................................106

5.2.1.2 Edge and level sensitivity................................................................................................................ 107

5.3 Interrupt pin request register...........................................................................................................................................107

5.3.1 Interrupt Pin Request Status and Control Register (IRQ_SC).........................................................................108

5.4 Interrupt priority control register.................................................................................................................................... 109

5.4.1 IPC Status and Control Register (IPC_SC)......................................................................................................110

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 5

Page 6

Section number Title Page

5.4.2 Interrupt Priority Mask Pseudo Stack Register (IPC_IPMPS)........................................................................ 111

5.4.3

Interrupt Level Setting Registers n (IPC_ILRSn)............................................................................................111

Chapter 6

System control

6.1 System device identification (SDID)..............................................................................................................................113

6.2 Universally unique identification (UUID)......................................................................................................................113

6.3 Reset and system initialization........................................................................................................................................113

6.4 System options................................................................................................................................................................114

6.4.1 BKGD pin enable.............................................................................................................................................114

6.4.2 RESET pin enable............................................................................................................................................114

6.4.3 SCI0 pin reassignment..................................................................................................................................... 114

6.4.4 FTM0 channels pin reassignment.................................................................................................................... 115

6.4.5 FTM1 pin reassignment................................................................................................................................... 115

6.5 System interconnection...................................................................................................................................................115

6.5.1 ACMP output selection....................................................................................................................................115

6.5.2 SCI0 TxD modulation......................................................................................................................................116

6.5.3 SCI0 RxD capture............................................................................................................................................ 116

6.5.4 SCI0 RxD filter................................................................................................................................................ 117

6.5.5 RTC capture..................................................................................................................................................... 117

6.5.6 ADC hardware trigger......................................................................................................................................117

6.6 System Control Registers................................................................................................................................................118

6.6.1 System Reset Status Register (SYS_SRS).......................................................................................................119

6.6.2 System Background Debug Force Reset Register (SYS_SBDFR)..................................................................121

6.6.3 System Device Identification Register: High (SYS_SDIDH)......................................................................... 121

6.6.4 System Device Identification Register: Low (SYS_SDIDL).......................................................................... 122

6.6.5 System Options Register 1 (SYS_SOPT1)...................................................................................................... 122

6.6.6 System Options Register 2 (SYS_SOPT2)...................................................................................................... 124

6.6.7 System Options Register 3 (SYS_SOPT3)...................................................................................................... 125

6.6.8 Illegal Address Register: High (SYS_ILLAH)................................................................................................126

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

6 NXP Semiconductors

Page 7

Section number Title Page

6.6.9 Illegal Address Register: Low (SYS_ILLAL).................................................................................................126

6.6.10 Universally Unique Identifier Register 1 (SYS_UUID1)................................................................................ 127

6.6.11 Universally Unique Identifier Register 2 (SYS_UUID2)................................................................................ 127

6.6.12 Universally Unique Identifier Register 3 (SYS_UUID3)................................................................................ 128

6.6.13 Universally Unique Identifier Register 4 (SYS_UUID4)................................................................................ 128

6.6.14 Universally Unique Identifier Register 5 (SYS_UUID5)................................................................................ 129

6.6.15 Universally Unique Identifier Register 6 (SYS_UUID6)................................................................................ 129

6.6.16 Universally Unique Identifier Register 7 (SYS_UUID7)................................................................................ 130

6.6.17 Universally Unique Identifier Register 8 (SYS_UUID8)................................................................................ 130

Chapter 7

Parallel input/output

7.1 Introduction.....................................................................................................................................................................131

7.2 Port data and data direction.............................................................................................................................................133

7.3 Internal pullup enable..................................................................................................................................................... 133

7.4 Input glitch filter setting..................................................................................................................................................134

7.5 High current drive...........................................................................................................................................................134

7.6 Pin behavior in stop mode...............................................................................................................................................134

7.7 Port data registers............................................................................................................................................................134

7.7.1 Port A Data Register (PORT_PTAD)..............................................................................................................135

7.7.2 Port B Data Register (PORT_PTBD).............................................................................................................. 136

7.7.3 Port C Data Register (PORT_PTCD).............................................................................................................. 136

7.7.4 Port High Drive Enable Register (PORT_HDRVE)........................................................................................137

7.7.5 Port A Output Enable Register (PORT_PTAOE)............................................................................................137

7.7.6 Port B Output Enable Register (PORT_PTBOE)............................................................................................ 138

7.7.7 Port C Output Enable Register (PORT_PTCOE)............................................................................................ 139

7.7.8 Port A Input Enable Register (PORT_PTAIE)................................................................................................140

7.7.9 Port B Input Enable Register (PORT_PTBIE)................................................................................................ 141

7.7.10 Port C Input Enable Register (PORT_PTCIE)................................................................................................ 142

7.7.11 Port Filter Register 0 (PORT_IOFLT0)...........................................................................................................143

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 7

Page 8

Section number Title Page

7.7.12 Port Filter Register 2 (PORT_IOFLT2)...........................................................................................................144

7.7.13 Port Clock Division Register (PORT_FCLKDIV).......................................................................................... 145

7.7.14 Port A Pullup Enable Register (PORT_PTAPE)............................................................................................. 146

7.7.15 Port B Pullup Enable Register (PORT_PTBPE)..............................................................................................147

7.7.16 Port C Pullup Enable Register (PORT_PTCPE)..............................................................................................148

Chapter 8

Clock management

8.1 Clock module..................................................................................................................................................................151

8.2 Internal clock source (ICS)............................................................................................................................................. 152

8.2.1 Function description.........................................................................................................................................153

8.2.1.1 Bus frequency divider...................................................................................................................... 154

8.2.1.2 Low power bit usage........................................................................................................................154

8.2.1.3 Internal reference clock (ICSIRCLK)..............................................................................................154

8.2.1.4 Fixed frequency clock (ICSFFCLK)................................................................................................155

8.2.1.5 BDC clock........................................................................................................................................156

8.2.2 Modes of operation.......................................................................................................................................... 156

8.2.2.1 FLL engaged internal (FEI)............................................................................................................. 157

8.2.2.2 FLL engaged external (FEE)............................................................................................................158

8.2.2.3 FLL bypassed internal (FBI)............................................................................................................158

8.2.2.4 FLL bypassed internal low power (FBILP)..................................................................................... 158

8.2.2.5 FLL bypassed external (FBE)..........................................................................................................159

8.2.2.6 FLL bypassed external low power (FBELP)................................................................................... 159

8.2.2.7 Stop (STOP).....................................................................................................................................160

8.2.3 FLL lock and clock monitor.............................................................................................................................161

8.2.3.1 FLL clock lock.................................................................................................................................161

8.2.3.2 External reference clock monitor.....................................................................................................161

8.3 Initialization / application information........................................................................................................................... 161

8.3.1 Initializing FEI mode....................................................................................................................................... 162

8.3.2 Initializing FBI mode.......................................................................................................................................162

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

8 NXP Semiconductors

Page 9

Section number Title Page

8.3.3 Initializing FEE mode...................................................................................................................................... 162

8.3.4 Initializing FBE mode......................................................................................................................................163

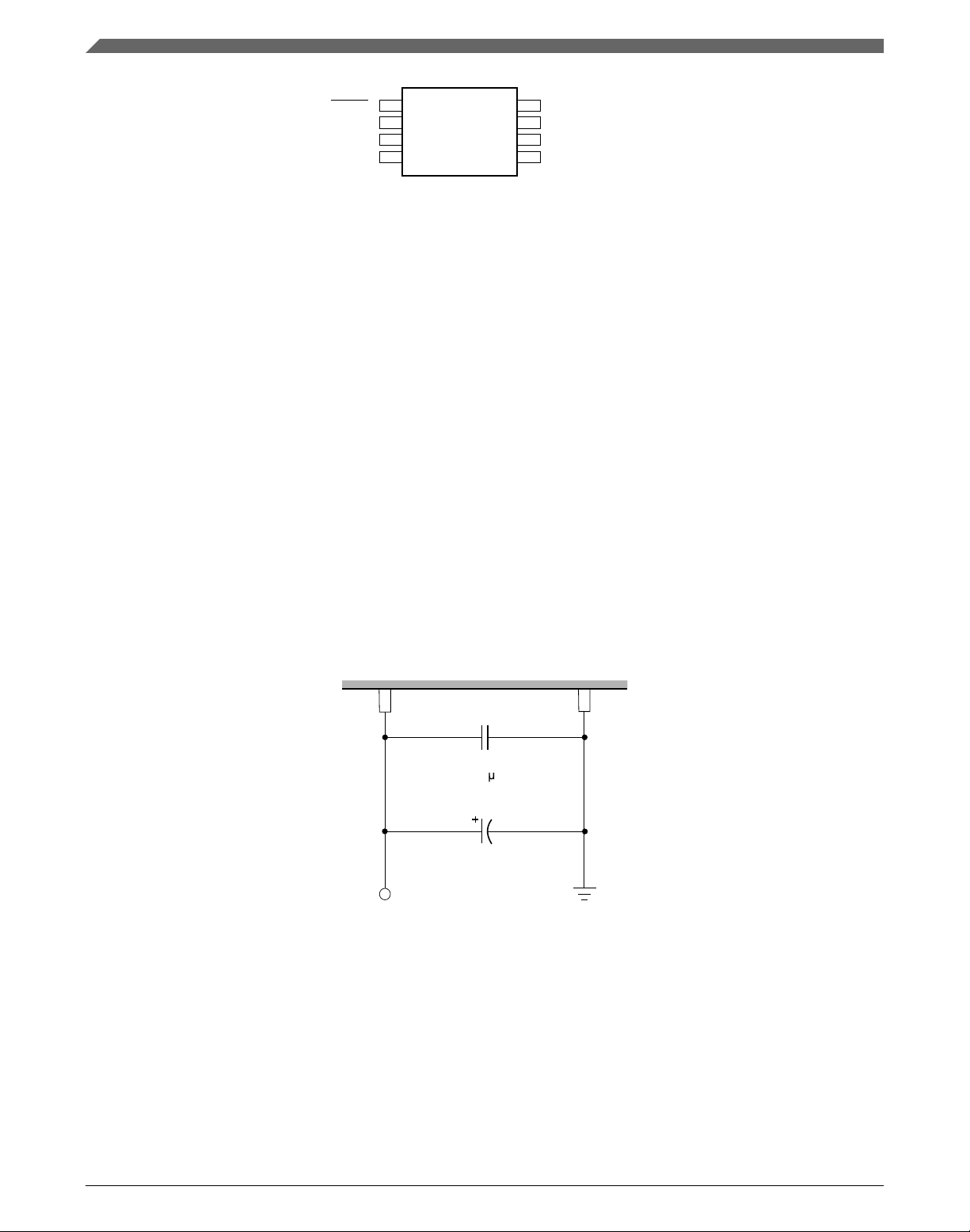

8.3.5 External oscillator (OSC).................................................................................................................................163

8.3.5.1 Bypass mode.................................................................................................................................... 164

8.3.5.2 Low-power configuration................................................................................................................ 164

8.3.5.3 High-gain configuration...................................................................................................................165

8.3.5.4 Initializing external oscillator for peripherals..................................................................................165

8.4 1 kHz low-power oscillator (LPO)................................................................................................................................. 166

8.5 Peripheral clock gating................................................................................................................................................... 166

8.6 ICS control registers....................................................................................................................................................... 166

8.6.1 ICS Control Register 1 (ICS_C1).................................................................................................................... 167

8.6.2 ICS Control Register 2 (ICS_C2).................................................................................................................... 168

8.6.3 ICS Control Register 3 (ICS_C3).................................................................................................................... 169

8.6.4 ICS Control Register 4 (ICS_C4).................................................................................................................... 169

8.6.5 ICS Status Register (ICS_S)............................................................................................................................ 170

8.6.6 OSC Status and Control Register (ICS_OSCSC)............................................................................................ 171

8.7 System clock gating control registers............................................................................................................................. 172

8.7.1 System Clock Gating Control 1 Register (SCG_C1).......................................................................................173

8.7.2 System Clock Gating Control 2 Register (SCG_C2).......................................................................................174

8.7.3 System Clock Gating Control 3 Register (SCG_C3).......................................................................................175

8.7.4 System Clock Gating Control 4 Register (SCG_C4).......................................................................................175

Chapter 9

Chip configurations

9.1 Introduction.....................................................................................................................................................................177

9.2 Core modules.................................................................................................................................................................. 177

9.2.1 Central processor unit (CPU)...........................................................................................................................177

9.2.2 Debug module (DBG)......................................................................................................................................177

9.3 System modules.............................................................................................................................................................. 178

9.3.1 Watchdog (WDOG)......................................................................................................................................... 178

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 9

Page 10

Section number Title Page

9.4 Clock module..................................................................................................................................................................178

9.5 Memory...........................................................................................................................................................................180

9.5.1 Random-access-memory (RAM)..................................................................................................................... 180

9.5.2 Non-volatile memory (NVM).......................................................................................................................... 180

9.6 Power modules................................................................................................................................................................180

9.7 Timers............................................................................................................................................................................. 181

9.7.1 FlexTimer module (FTM)................................................................................................................................181

9.7.1.1 FTM0 interconnection......................................................................................................................182

9.7.1.2 FTM1 interconnection......................................................................................................................183

9.7.2 Real-time counter (RTC)................................................................................................................................. 183

9.8 Communication interfaces.............................................................................................................................................. 185

9.8.1 Serial communications interface (SCI)............................................................................................................185

9.8.1.1 SCI0 infrared functions....................................................................................................................186

9.9 Analog.............................................................................................................................................................................187

9.9.1 Analog-to-digital converter (ADC)..................................................................................................................187

9.9.1.1 ADC channel assignments............................................................................................................... 188

9.9.1.2 Alternate clock................................................................................................................................. 189

9.9.1.3 Hardware trigger.............................................................................................................................. 190

9.9.1.4 Temperature sensor..........................................................................................................................190

9.9.2 Analog comparator (ACMP)............................................................................................................................191

9.9.2.1 ACMP configuration information....................................................................................................192

9.9.2.2 ACMP in stop3 mode.......................................................................................................................193

9.9.2.3 ACMP to FTM configuration information.......................................................................................193

9.9.2.4 ACMP for SCI0 RXD filter............................................................................................................. 193

9.10 Human-machine interfaces HMI.....................................................................................................................................194

9.10.1 Keyboard interrupts (KBI)............................................................................................................................... 194

Chapter 10

Central processor unit

10.1 Introduction.....................................................................................................................................................................197

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

10 NXP Semiconductors

Page 11

Section number Title Page

10.1.1 Features............................................................................................................................................................ 197

10.2 Programmer's Model and CPU Registers....................................................................................................................... 198

10.2.1 Accumulator (A).............................................................................................................................................. 198

10.2.2 Index Register (H:X)........................................................................................................................................199

10.2.3 Stack Pointer (SP)............................................................................................................................................ 199

10.2.4 Program Counter (PC)..................................................................................................................................... 200

10.2.5 Condition Code Register (CCR)...................................................................................................................... 200

10.3 Addressing Modes.......................................................................................................................................................... 201

10.3.1 Inherent Addressing Mode (INH).................................................................................................................... 202

10.3.2 Relative Addressing Mode (REL)....................................................................................................................202

10.3.3 Immediate Addressing Mode (IMM)............................................................................................................... 202

10.3.4 Direct Addressing Mode (DIR)........................................................................................................................203

10.3.5 Extended Addressing Mode (EXT)..................................................................................................................203

10.3.6 Indexed Addressing Mode............................................................................................................................... 204

10.3.6.1 Indexed, No Offset (IX)...................................................................................................................204

10.3.6.2 Indexed, No Offset with Post Increment (IX+)................................................................................204

10.3.6.3 Indexed, 8-Bit Offset (IX1)..............................................................................................................204

10.3.6.4 Indexed, 8-Bit Offset with Post Increment (IX1+).......................................................................... 205

10.3.6.5 Indexed, 16-Bit Offset (IX2)............................................................................................................205

10.3.6.6 SP-Relative, 8-Bit Offset (SP1)....................................................................................................... 205

10.3.6.7 SP-Relative, 16-Bit Offset (SP2)..................................................................................................... 206

10.3.7 Memory to memory Addressing Mode............................................................................................................ 206

10.3.7.1 Direct to Direct.................................................................................................................................206

10.3.7.2 Immediate to Direct......................................................................................................................... 206

10.3.7.3 Indexed to Direct, Post Increment....................................................................................................206

10.3.7.4 Direct to Indexed, Post-Increment................................................................................................... 207

10.4 Operation modes............................................................................................................................................................. 207

10.4.1 Stop mode........................................................................................................................................................ 207

10.4.2 Wait mode........................................................................................................................................................ 207

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 11

Page 12

Section number Title Page

10.4.3 Background mode............................................................................................................................................ 208

10.4.4 Security mode.................................................................................................................................................. 209

10.5 HCS08 V6 Opcodes........................................................................................................................................................211

10.6 Special Operations.......................................................................................................................................................... 211

10.6.1 Reset Sequence................................................................................................................................................ 211

10.6.2 Interrupt Sequence........................................................................................................................................... 211

10.7 Instruction Set Summary.................................................................................................................................................212

Chapter 11

Keyboard Interrupts (KBI)

11.1 Introduction.....................................................................................................................................................................225

11.1.1 Features............................................................................................................................................................ 225

11.1.2 Modes of Operation......................................................................................................................................... 225

11.1.2.1 KBI in Wait mode............................................................................................................................225

11.1.2.2 KBI in Stop modes...........................................................................................................................226

11.1.2.3 KBI in Active Background mode.....................................................................................................226

11.1.3 Block Diagram................................................................................................................................................. 226

11.2 External signals description............................................................................................................................................ 227

11.3 Register definition...........................................................................................................................................................227

11.4 Memory Map and Registers............................................................................................................................................227

11.4.1

11.4.2

11.4.3

11.5 Functional Description....................................................................................................................................................229

11.5.1 Edge-only sensitivity........................................................................................................................................230

11.5.2 Edge and level sensitivity................................................................................................................................ 230

11.5.3 KBI Pullup Resistor......................................................................................................................................... 230

11.5.4 KBI initialization..............................................................................................................................................230

KBI Status and Control Register (KBIx_SC).................................................................................................. 228

KBIx Pin Enable Register (KBIx_PE).............................................................................................................228

KBIx Edge Select Register (KBIx_ES)........................................................................................................... 229

Chapter 12

FlexTimer Module (FTM)

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

12 NXP Semiconductors

Page 13

Section number Title Page

12.1 Introduction.....................................................................................................................................................................233

12.1.1 FlexTimer philosophy...................................................................................................................................... 233

12.1.2 Features............................................................................................................................................................ 233

12.1.3 Modes of operation.......................................................................................................................................... 234

12.1.4 Block diagram.................................................................................................................................................. 234

12.2 Signal description............................................................................................................................................................235

12.2.1 EXTCLK — FTM external clock.................................................................................................................... 236

12.2.2 CHn — FTM channel (n) I/O pin.................................................................................................................... 236

12.3 Memory map and register definition...............................................................................................................................236

12.3.1 Module memory map....................................................................................................................................... 236

12.3.2 Register descriptions........................................................................................................................................ 236

12.3.3

12.3.4

12.3.5

12.3.6

12.3.7

12.3.8

12.3.9

12.3.10

12.4 Functional Description....................................................................................................................................................244

12.4.1 Clock Source.................................................................................................................................................... 245

12.4.2 Prescaler........................................................................................................................................................... 246

12.4.3 Counter.............................................................................................................................................................246

Status and Control (FTMx_SC)....................................................................................................................... 238

Counter High (FTMx_CNTH)......................................................................................................................... 239

Counter Low (FTMx_CNTL).......................................................................................................................... 240

Modulo High (FTMx_MODH)........................................................................................................................ 240

Modulo Low (FTMx_MODL)......................................................................................................................... 241

Channel Status and Control (FTMx_CnSC).................................................................................................... 241

Channel Value High (FTMx_CnVH)...............................................................................................................243

Channel Value Low (FTMx_CnVL)................................................................................................................244

12.4.1.1 Counter Clock Source...................................................................................................................... 245

12.4.3.1 Up counting......................................................................................................................................246

12.4.3.2 Up-down counting............................................................................................................................247

12.4.3.3 Free running counter........................................................................................................................ 248

12.4.3.4 Counter reset.................................................................................................................................... 248

12.4.4 Input capture mode...........................................................................................................................................248

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 13

Page 14

Section number Title Page

12.4.5 Output compare mode...................................................................................................................................... 249

12.4.6 Edge-aligned PWM (EPWM) mode................................................................................................................ 251

12.4.7 Center-aligned PWM (CPWM) mode..............................................................................................................252

12.4.8 Update of the registers with write buffers........................................................................................................254

12.4.8.1 MODH:L registers........................................................................................................................... 254

12.4.8.2 CnVH:L registers............................................................................................................................. 255

12.4.9 BDM mode.......................................................................................................................................................255

12.5 Reset overview................................................................................................................................................................255

12.6 FTM Interrupts................................................................................................................................................................257

12.6.1 Timer overflow interrupt..................................................................................................................................257

12.6.2 Channel (n) interrupt........................................................................................................................................ 257

Chapter 13

Real-time counter (RTC)

13.1 Introduction.....................................................................................................................................................................259

13.2 Features...........................................................................................................................................................................259

13.2.1 Modes of operation.......................................................................................................................................... 259

13.2.1.1 Wait mode........................................................................................................................................259

13.2.1.2 Stop modes.......................................................................................................................................260

13.2.2 Block diagram.................................................................................................................................................. 260

13.3 Register definition...........................................................................................................................................................260

13.3.1 RTC Status and Control Register 1 (RTC_SC1)............................................................................................. 261

13.3.2 RTC Status and Control Register 2 (RTC_SC2)............................................................................................. 262

13.3.3 RTC Modulo Register: High (RTC_MODH).................................................................................................. 263

13.3.4 RTC Modulo Register: Low (RTC_MODL)................................................................................................... 263

13.3.5 RTC Counter Register: High (RTC_CNTH)................................................................................................... 263

13.3.6 RTC Counter Register: Low (RTC_CNTL).................................................................................................... 264

13.4 Functional description.....................................................................................................................................................264

13.4.1 RTC operation example................................................................................................................................... 265

13.5 Initialization/application information............................................................................................................................. 266

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

14 NXP Semiconductors

Page 15

Section number Title Page

Chapter 14

Serial communications interface (SCI)

14.1 Introduction.....................................................................................................................................................................269

14.1.1 Features............................................................................................................................................................ 269

14.1.2 Modes of operation.......................................................................................................................................... 269

14.1.3 Block diagram.................................................................................................................................................. 270

14.2 SCI signal descriptions................................................................................................................................................... 272

14.2.1 Detailed signal descriptions............................................................................................................................. 272

14.3 Register definition...........................................................................................................................................................272

14.3.1

14.3.2

14.3.3

14.3.4

14.3.5

14.3.6

14.3.7

14.3.8

14.4 Functional description.....................................................................................................................................................282

14.4.1 Baud rate generation........................................................................................................................................ 283

14.4.2 Transmitter functional description................................................................................................................... 283

14.4.3 Receiver functional description....................................................................................................................... 285

SCI Baud Rate Register: High (SCIx_BDH)................................................................................................... 273

SCI Baud Rate Register: Low (SCIx_BDL).................................................................................................... 274

SCI Control Register 1 (SCIx_C1)...................................................................................................................274

SCI Control Register 2 (SCIx_C2)...................................................................................................................276

SCI Status Register 1 (SCIx_S1)..................................................................................................................... 277

SCI Status Register 2 (SCIx_S2)..................................................................................................................... 279

SCI Control Register 3 (SCIx_C3)...................................................................................................................280

SCI Data Register (SCIx_D)............................................................................................................................282

14.4.2.1 Send break and queued idle............................................................................................................. 284

14.4.3.1 Data sampling technique..................................................................................................................286

14.4.3.2 Receiver wake-up operation.............................................................................................................287

14.4.4 Interrupts and status flags................................................................................................................................ 288

14.4.5 Baud rate tolerance...........................................................................................................................................289

14.4.5.1 Slow data tolerance.......................................................................................................................... 289

14.4.5.2 Fast data tolerance............................................................................................................................291

14.4.6 Additional SCI functions................................................................................................................................. 292

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 15

Page 16

Section number Title Page

14.4.6.1 8- and 9-bit data modes....................................................................................................................292

14.4.6.2 Stop mode operation........................................................................................................................ 292

14.4.6.3 Loop mode....................................................................................................................................... 292

14.4.6.4 Single-wire operation.......................................................................................................................293

Chapter 15

Analog-to-digital converter (ADC)

15.1 Introduction.....................................................................................................................................................................295

15.1.1 Features............................................................................................................................................................ 295

15.1.2 Block Diagram................................................................................................................................................. 296

15.2 External Signal Description............................................................................................................................................ 296

15.2.1 Analog Power (VDDA)................................................................................................................................... 297

15.2.2 Analog Ground (VSSA)...................................................................................................................................297

15.2.3 Voltage Reference High (VREFH).................................................................................................................. 297

15.2.4 Voltage Reference Low (VREFL)................................................................................................................... 297

15.2.5 Analog Channel Inputs (ADx)......................................................................................................................... 297

15.3 ADC Control Registers...................................................................................................................................................298

15.3.1 Status and Control Register 1 (ADC_SC1)......................................................................................................298

15.3.2 Status and Control Register 2 (ADC_SC2)......................................................................................................300

15.3.3 Status and Control Register 3 (ADC_SC3)......................................................................................................301

15.3.4 Status and Control Register 4 (ADC_SC4)......................................................................................................302

15.3.5 Conversion Result High Register (ADC_RH)................................................................................................. 303

15.3.6 Conversion Result Low Register (ADC_RL).................................................................................................. 304

15.3.7 Compare Value High Register (ADC_CVH)...................................................................................................305

15.3.8 Compare Value Low Register (ADC_CVL)....................................................................................................305

15.3.9 Pin Control 1 Register (ADC_APCTL1)......................................................................................................... 306

15.4 Functional description.....................................................................................................................................................307

15.4.1 Clock select and divide control........................................................................................................................ 307

15.4.2 Input select and pin control.............................................................................................................................. 308

15.4.3 Hardware trigger.............................................................................................................................................. 308

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

16 NXP Semiconductors

Page 17

Section number Title Page

15.4.4 Conversion control........................................................................................................................................... 309

15.4.4.1 Initiating conversions.......................................................................................................................309

15.4.4.2 Completing conversions...................................................................................................................309

15.4.4.3 Aborting conversions....................................................................................................................... 310

15.4.4.4 Power control................................................................................................................................... 311

15.4.4.5 Sample time and total conversion time............................................................................................311

15.4.5 Automatic compare function............................................................................................................................312

15.4.6 FIFO operation................................................................................................................................................. 313

15.4.7 MCU wait mode operation...............................................................................................................................316

15.4.8 MCU Stop3 mode operation............................................................................................................................ 317

15.4.8.1 Stop3 mode with ADACK disabled.................................................................................................317

15.4.8.2 Stop3 mode with ADACK enabled..................................................................................................317

15.5 Initialization information................................................................................................................................................ 318

15.5.1 ADC module initialization example................................................................................................................ 318

15.5.1.1 Initialization sequence......................................................................................................................318

15.5.1.2 Pseudo-code example.......................................................................................................................319

15.5.2 ADC FIFO module initialization example.......................................................................................................319

15.5.2.1 Pseudo-code example.......................................................................................................................320

15.6 Application information..................................................................................................................................................321

15.6.1 External pins and routing................................................................................................................................. 321

15.6.1.1 Analog supply pins...........................................................................................................................321

15.6.1.2 Analog reference pins...................................................................................................................... 321

15.6.1.3 Analog input pins.............................................................................................................................322

15.6.2 Sources of error................................................................................................................................................ 323

15.6.2.1 Sampling error..................................................................................................................................323

15.6.2.2 Pin leakage error.............................................................................................................................. 323

15.6.2.3 Noise-induced errors........................................................................................................................323

15.6.2.4 Code width and quantization error...................................................................................................324

15.6.2.5 Linearity errors.................................................................................................................................325

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 17

Page 18

Section number Title Page

15.6.2.6 Code jitter, non-monotonicity, and missing codes...........................................................................326

Chapter 16

Analog comparator (ACMP)

16.1 Introduction.....................................................................................................................................................................327

16.1.1 Features............................................................................................................................................................ 327

16.1.2 Modes of operation.......................................................................................................................................... 327

16.1.2.1 Operation in Wait mode...................................................................................................................328

16.1.2.2 Operation in Stop3 mode................................................................................................................. 328

16.1.2.3 Operation in Debug mode................................................................................................................328

16.1.3 Block diagram.................................................................................................................................................. 328

16.2 External signal description..............................................................................................................................................329

16.3 Memory map and register definition...............................................................................................................................329

16.3.1 ACMP Control and Status Register (ACMP_CS)........................................................................................... 330

16.3.2 ACMP Control Register 0 (ACMP_C0).......................................................................................................... 331

16.3.3 ACMP Control Register 1 (ACMP_C1).......................................................................................................... 331

16.3.4 ACMP Control Register 2 (ACMP_C2).......................................................................................................... 332

16.4 Functional description.....................................................................................................................................................332

16.5 Setup and operation of ACMP........................................................................................................................................333

16.6 Resets..............................................................................................................................................................................334

16.7 Interrupts.........................................................................................................................................................................334

Chapter 17

Watchdog (WDOG)

17.1 Introduction.....................................................................................................................................................................335

17.1.1 Features............................................................................................................................................................ 335

17.1.2 Block diagram.................................................................................................................................................. 336

17.2 Memory map and register definition...............................................................................................................................337

17.2.1 Watchdog Control and Status Register 1 (WDOG_CS1)................................................................................ 337

17.2.2 Watchdog Control and Status Register 2 (WDOG_CS2)................................................................................ 339

17.2.3 Watchdog Counter Register: High (WDOG_CNTH)...................................................................................... 340

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

18 NXP Semiconductors

Page 19

Section number Title Page

17.2.4 Watchdog Counter Register: Low (WDOG_CNTL)....................................................................................... 340

17.2.5 Watchdog Timeout Value Register: High (WDOG_TOVALH)..................................................................... 341

17.2.6 Watchdog Timeout Value Register: Low (WDOG_TOVALL)...................................................................... 341

17.2.7 Watchdog Window Register: High (WDOG_WINH)..................................................................................... 342

17.2.8 Watchdog Window Register: Low (WDOG_WINL)...................................................................................... 342

17.3 Functional description.....................................................................................................................................................343

17.3.1 Watchdog refresh mechanism.......................................................................................................................... 343

17.3.1.1 Window mode..................................................................................................................................344

17.3.1.2 Refreshing the Watchdog.................................................................................................................344

17.3.1.3 Example code: Refreshing the Watchdog........................................................................................345

17.3.2 Configuring the Watchdog...............................................................................................................................345

17.3.2.1 Reconfiguring the Watchdog........................................................................................................... 345

17.3.2.2 Unlocking the Watchdog................................................................................................................. 346

17.3.2.3 Example code: Reconfiguring the Watchdog.................................................................................. 346

17.3.3 Clock source.....................................................................................................................................................346

17.3.4 Using interrupts to delay resets........................................................................................................................ 348

17.3.5 Backup reset..................................................................................................................................................... 348

17.3.6 Functionality in debug and low-power modes................................................................................................. 348

17.3.7 Fast testing of the watchdog.............................................................................................................................349

17.3.7.1 Testing each byte of the counter...................................................................................................... 349

17.3.7.2 Entering user mode.......................................................................................................................... 350

Chapter 18

Development support

18.1 Introduction.....................................................................................................................................................................351

18.1.1 Forcing active background...............................................................................................................................351

18.1.2 Features............................................................................................................................................................ 351

18.2 Background debug controller (BDC)..............................................................................................................................352

18.2.1 BKGD pin description..................................................................................................................................... 353

18.2.2 Communication details.................................................................................................................................... 354

MC9S08PA4 Reference Manual, Rev. 5, 08/2017

NXP Semiconductors 19

Page 20

Section number Title Page

18.2.3 BDC commands............................................................................................................................................... 356

18.2.4 BDC hardware breakpoint............................................................................................................................... 359

18.3 On-chip debug system (DBG)........................................................................................................................................ 359

18.3.1 Comparators A and B.......................................................................................................................................360

18.3.2 Bus capture information and FIFO operation.................................................................................................. 360

18.3.3 Change-of-flow information............................................................................................................................ 361

18.3.4 Tag vs. force breakpoints and triggers............................................................................................................. 362