Page 1

UM11029

LPC84x User manual

Rev. 1.0 — 16 June 2017 User manual

Document information

Info Content

Keywords LPC84x, LPC84x UM, LPC84x user manual

Abstract LPC84x User manual

Page 2

NXP Semiconductors

UM11029

LPC84x User manual

Revision history

Rev Date Description

v.1 20170616 Initial revision. LPC84x User manual.

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 2 of 515

Page 3

1.1 Introduction

UM11029

Chapter 1: LPC84x Introductory information

Rev. 1.0 — 16 June 2017 User manual

The LPC84x are an ARM Cortex-M0+ based, low-cost 32-bit MCU family operating at

CPU frequencies of up to 30 MHz. The LPC84x support up to 64 KB of flash memory and

16 KB of SRAM.

1.2 Features

.

2

C-bus

The peripheral complement of the LPC84x includes a CRC engine, four I

interfaces, up to five USARTs, up to two SPI interfaces, one multi-rate timer, self-wake-up

timer, SCTimer/PWM, one general purpose 32-bit counter/timer, a DMA, one 12-bit ADC,

two 10-bit DACs, one analog comparator, function-configurable I/O ports through a switch

matrix, an input pattern match engine, and up to 54 general-purpose I/O pins.

Remark: For additional documentation, see Section 32.2 “References”

• System:

– ARM Cortex-M0+ processor (revision r0p1), running at frequencies of up to

30 MHz with single-cycle multiplier and fast single-cycle I/O port.

– ARM Cortex-M0+ built-in Nested Vectored Interrupt Controller (NVIC).

– System tick timer.

– AHB multilayer matrix.

– Serial Wire Debug (SWD) with four break points and two watch points. JTAG

boundary scan (BSDL) supported.

– Micro Trace Buffer (MTB)

• Memory:

– Up to 64 KB on-chip flash programming memory with 64 Byte page write and

erase.

– Fast Initialization Memory (FAIM) allowing the user to configure chip behavior on

power-up.

– Code Read Protection (CRP).

– Up to 16 KB SRAM consisting of two 8 KB contiguous SRAM banks. One 8 KB of

SRAM can be used for MTB.

– Bit-band addressing supported to permit atomic operations to modify a single bit.

• ROM API support:

– Bootloader.

– Supports Flash In-Application Programming (IAP).

– Supports In-System Programming (ISP) through USART, SPI, and I

– FAIM API.

– FRO API.

– Flash In-Application Programming (IAP) and In-System Programming (ISP).

2

C.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 3 of 515

Page 4

NXP Semiconductors

UM11029

Chapter 1: LPC84x Introductory information

– On-chip ROM APIs for integer divide.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 4 of 515

Page 5

NXP Semiconductors

• Digital peripherals:

• Timers:

• Analog peripherals:

• Serial peripherals:

UM11029

Chapter 1: LPC84x Introductory information

– High-speed GPIO interface connected to the ARM Cortex-M0+ IO bus with up to

32 General-Purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors,

programmable open-drain mode, input inverter, and glitch filter. GPIO direction

control supports independent set/clear/toggle of individual bits.

– High-current source output driver (20 mA) on four pins.

– High-current sink driver (20 mA) on two true open-drain pins.

– GPIO interrupt generation capability with boolean pattern-matching feature on

eight GPIO inputs.

– Switch matrix for flexible configuration of each I/O pin function.

– CRC engine.

– DMA with 25 channels and 13 trigger inputs.

– One SCTimer/PWM with five input and seven output functions (including capture

and match) for timing and PWM applications. Inputs and outputs can be routed to

or from external pins and internally to or from selected peripherals. Internally, the

SCTimer/PWM supports 8 match/captures, 8 events, and 8 states.

– One 32-bit general purpose counter/timer, with four match outputs and three

capture inputs. Supports PWM mode, external count, and DMA.

– Four channel Multi-Rate Timer (MRT) for repetitive interrupt generation at up to

four programmable, fixed rates.

– Self-Wake-up Timer (WKT) clocked from either Free Running Oscillator (FRO), a

low-power, low-frequency internal oscillator, or an external clock input in the

always-on power domain.

– Windowed Watchdog timer (WWDT).

– One 12-bit ADC with up to 12 input channels with multiple internal and external

trigger inputs and with sample rates of up to 1.2 Msamples/s. The ADC supports

two independent conversion sequences.

– Comparator with five input pins and external or internal reference voltage.

– Two 10-bit DACs.

– Five USART interfaces with pin functions assigned through the switch matrix and

two fractional baud rate generators.

– Two SPI controllers with pin functions assigned through the switch matrix.

– Four I

2

C-bus interfaces. One I2C supports Fast-mode Plus with 1 Mbit/s data rates

on two true open-drain pins and listen mode. Three I

400 kbit/s on standard digital pins.

2

Cs support data rates up to

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 5 of 515

Page 6

NXP Semiconductors

• Clock generation:

• Power control:

• Unique device serial number for identification.

• Single power supply (1.8 V to 3.6 V).

• Operating temperature range -40 °C to +105 °C.

• Available in LQFP64, LQFP48, HVQFN48, and HVQFN33 packages

UM11029

Chapter 1: LPC84x Introductory information

– Free Running Oscillator (FRO). This oscillator provides a selectable 18 MHz,

24 MHz, and 30 MHz outputs that can be used as a system clock. Also, these

outputs can be divided down to 1.125 MHz, 1.5 MHz, 1.875 MHz, 9 MHz, 12 MHz,

and15 MHz for system clock. The FRO is trimmed to ±1 % accuracy over the entire

voltage and temperature range 0 C to 70 C.

– Low power boot at 1.5 MHz using FAIM memory.

– External clock input for clock frequencies of up to 25 MHz.

– Crystal oscillator with an operating range of 1 MHz to 25 MHz.

– Low power oscillator can be used as a clock source to the watchdog timer.

– Programmable watchdog oscillator with a frequency range of 9.4 kHz to 2.3 MHz.

– PLL allows CPU operation up to the maximum CPU rate without the need for a

high-frequency crystal. May be run from the system oscillator, the external clock

input, or the internal FRO.

– Clock output function with divider that can reflect all internal clock sources.

– Integrated PMU (Power Management Unit) to minimize power consumption.

– Reduced power modes: sleep mode, deep-sleep mode, power-down mode, and

deep power-down mode.

– Wake-up from deep-sleep and power-down modes on activity on USART, SPI, and

I2C peripherals.

– Timer-controlled self wake-up from deep power-down mode.

– Power-On Reset (POR).

– Brownout detect (BOD).

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 6 of 515

Page 7

NXP Semiconductors

1.3 Ordering options

UM11029

Chapter 1: LPC84x Introductory information

Table 1. Ordering information

Type number Package

LPC845M301JBD64 LQFP64 Plastic low profile quad flat package; 64 leads; body 10 10 1.4 mm SOT314-2

LPC845M301JBD48 LQFP48 Plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC845M301JHI48 HVQFN48 HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 48

LPC845M301JHI33 HVQFN33 HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33

LPC844M201JBD64 LQFP64 Plastic low profile quad flat package; 64 leads; body 10 10 1.4 mm SOT314-2

LPC844M201JBD48 LQFP48 Plastic low profile quad flat package; 48 leads; body 7 7 1.4 mm SOT313-2

LPC844M201JHI48 HVQFN48 HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33

LPC844M201JHI33 HVQFN33 HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33

Table 2. Ordering options

Type number Flash/KB SRAM/KB USART I2C SPI DAC GPIO Package

LPC845M301JBD64 64 16 5 4 2 2 54 LQFP64

LPC845M301JBD48 64 16 5 4 2 2 42 LQFP48

LPC845M301JHI48 64 16 5 4 2 2 42 HVQFN48

LPC845M301JHI33 64 16 5 4 2 1 29 HVQFN33

LPC844M201JBD64 64 8 2 2 2 - 54 LQFP64

LPC844M201JBD48 64 8 2 2 2 - 42 LQFP48

LPC844M201JHI48 64 8 2 2 2 - 42 HVQFN48

LPC844M201JHI33 64 8 2 2 2 - 29 HVQFN33

Name Description Version

SOT619-1

terminals; body 7 7 0.85 mm

SOT617-11

terminals; body 5 5 0.85 mm

SOT619-1

terminals; body 5 5 0.85 mm

SOT617-11

terminals; body 5 5 0.85 mm

1.4 General description

1.4.1 ARM Cortex-M0+ core configuration

The ARM Cortex-M0+ core runs at an operating frequency of up to 30 MHz. Integrated in

the core are the NVIC and Serial Wire Debug with four breakpoints and two watch points.

The ARM Cortex-M0+ core supports a single-cycle I/O enabled port (IOP) for fast GPIO

access at address 0xA000 0000. The ARM Cortex M0+ core version is r0p1.

The core includes a single-cycle multiplier and a system tick timer (SysTick).

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 7 of 515

Page 8

NXP Semiconductors

aaa-022793-x

CLKOUT

Vdd

CLKIN

XTALIN

XTALOUT

SWD Port

JTAG Test and

Boundary Scan

interface

RESET

Clock Generation,

Power Control,

and other

System Functions

Voltage Regulator

DEBUG

INTERFACE

IOP bus

GPIOs

GPIOs AND

GPOINT

Flash

interface

Flash

64 kB

General

Purpose

DMA

controller

MTB slave

interface

DMA

registers

CRC

Multilayer

AHB Matrix

AHB to

APB bridge

FAIM

256-bit

T0 Match/

Capture

I2C2,3

COMP

Inputs

ADC Inputs

and Triggers

DAC1 outputs

DAC0 outputs

PIOs

UART0,1,2, 3, 4

SPI0,1

I2C0,1

APB slave group

Watchdog

Osc

Windowed WDT

Note:

SCT Timer/

PWM

ARM

Cortex M0+

System control

IOCON Registers

Flash Registers (NVMC)

CTIMER32

I2C2/3

UARTs 0-4

SPI0/1

I2C0/1

Periph Input Mux Selects

Comparator

PMU Registers

12-bit ADC

10-bit DAC1

10-bit DAC0

FAIM Registers

Switch Matrix

Wakeup Timer

Multi-Rate Timer

Boot ROM

16 kB

SRAM/MTB

8 kB

SRAM

8 kB

Yellow shaded blocks support general purpose DMA

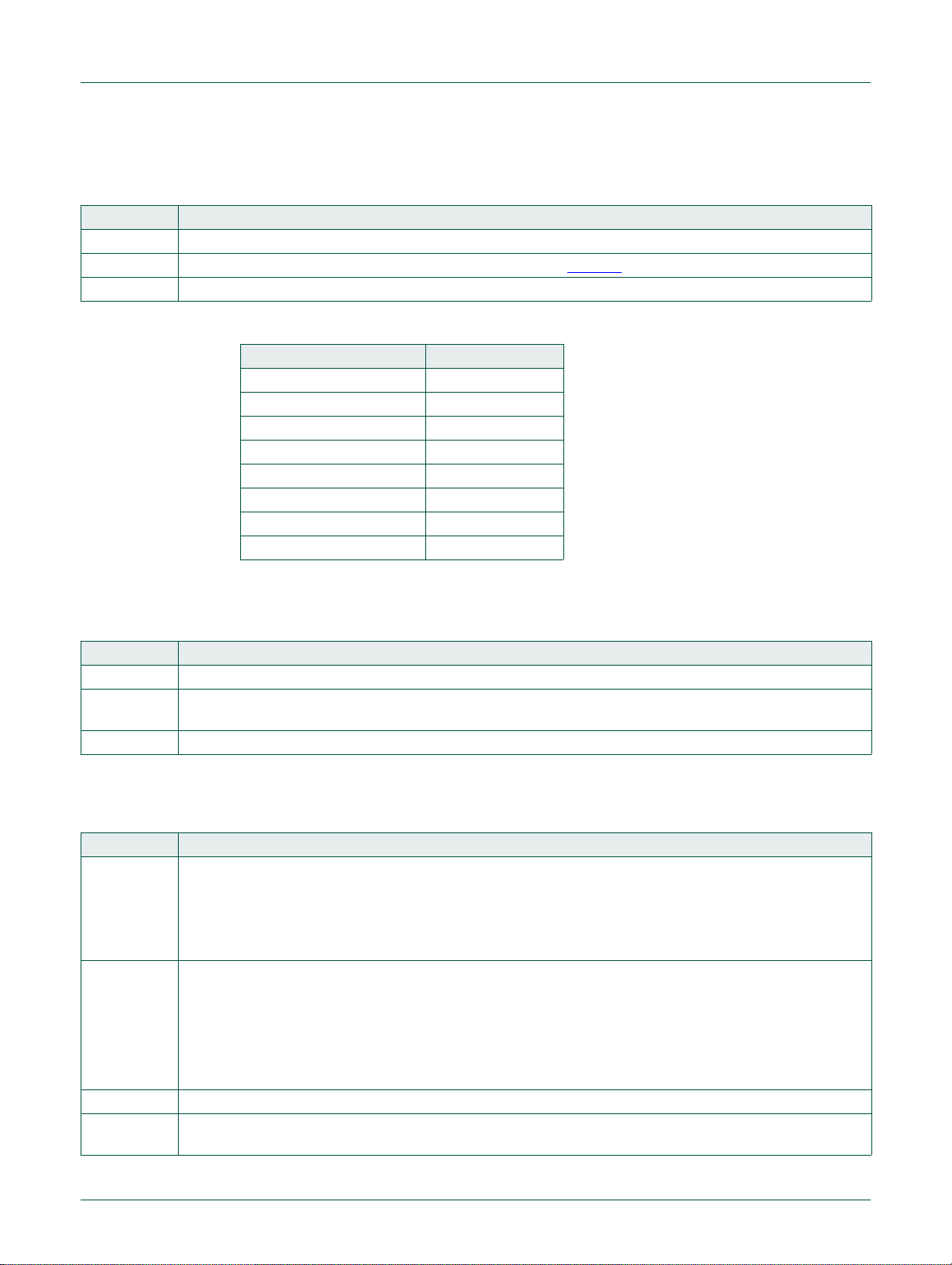

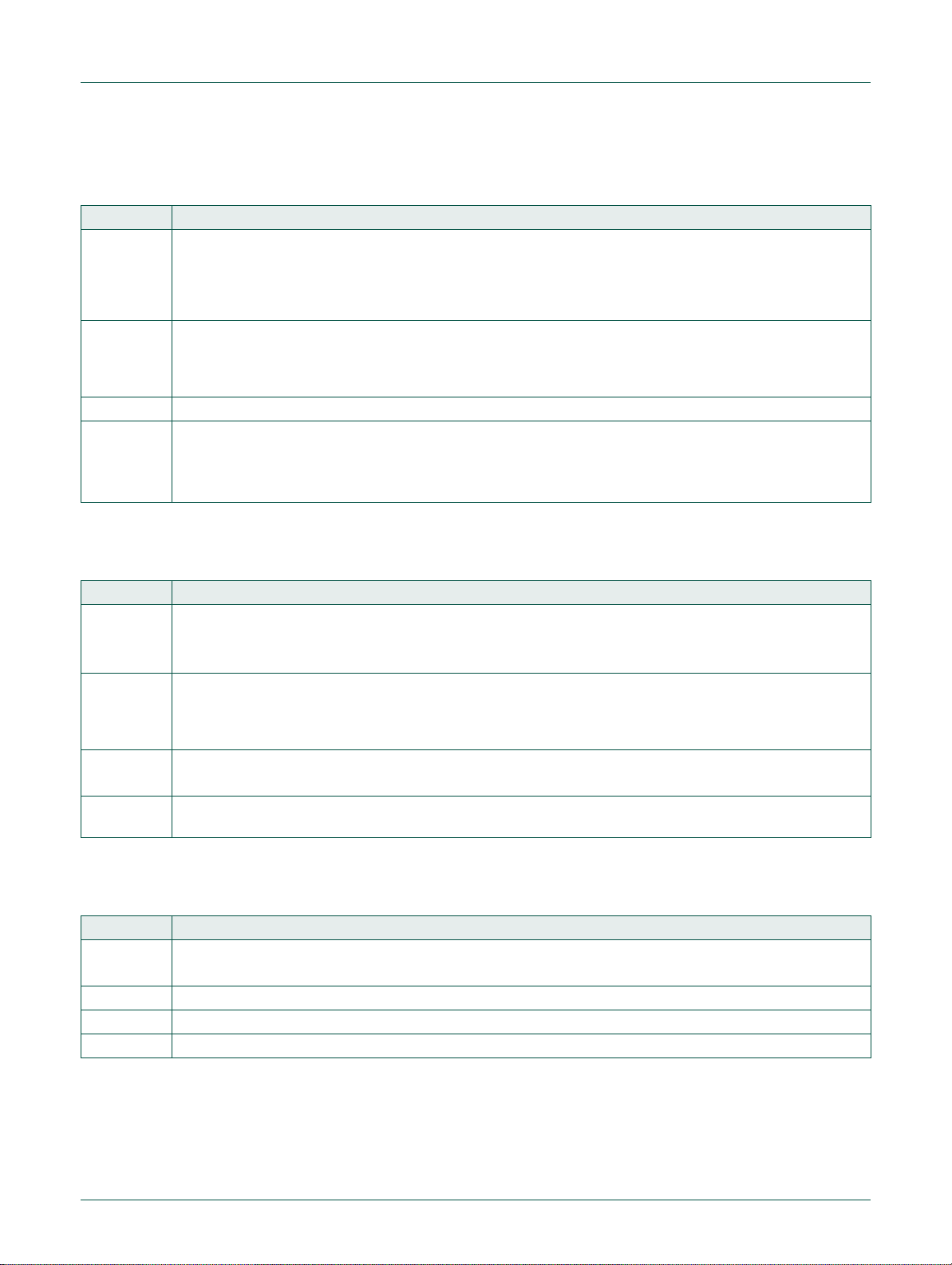

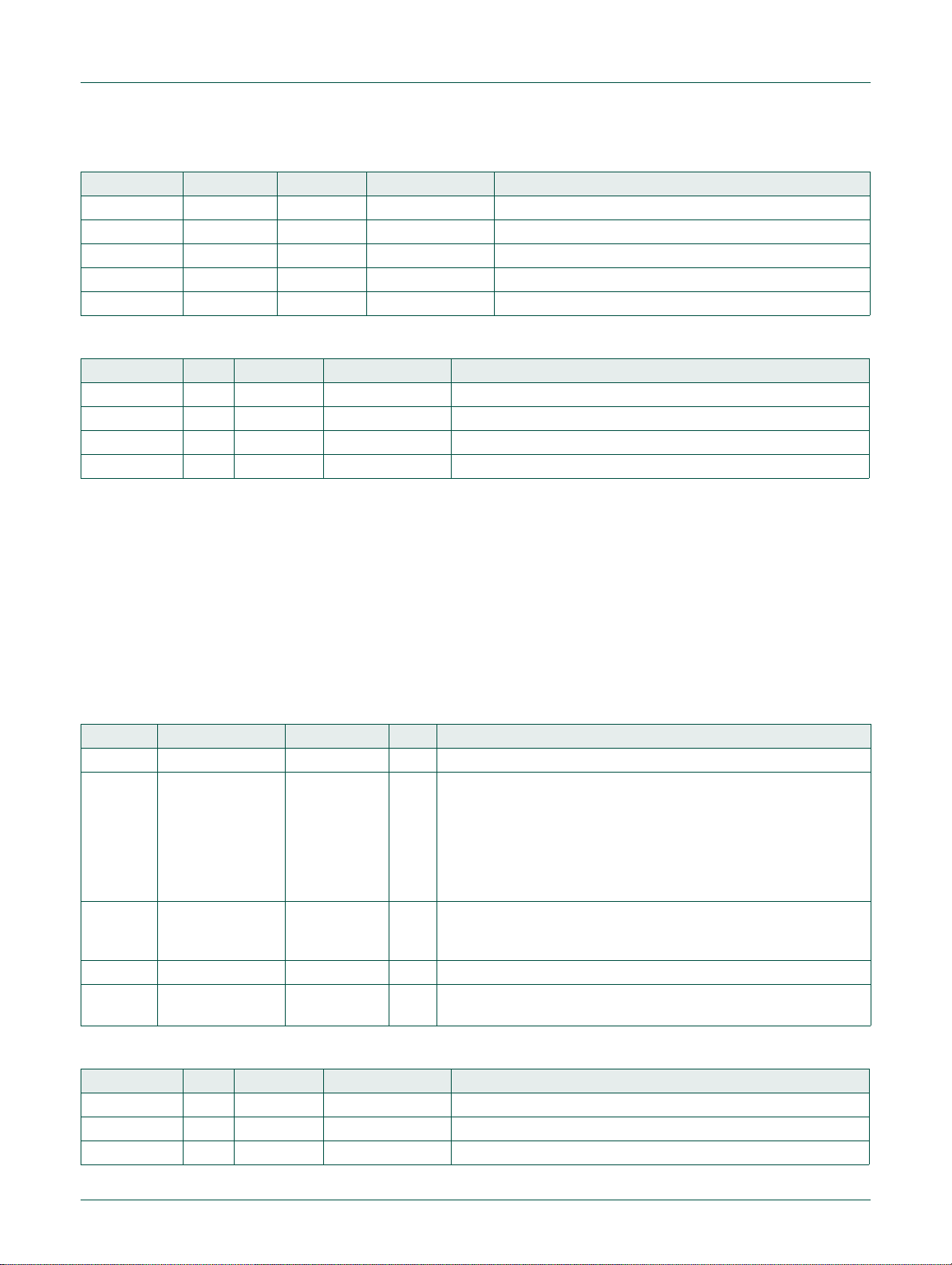

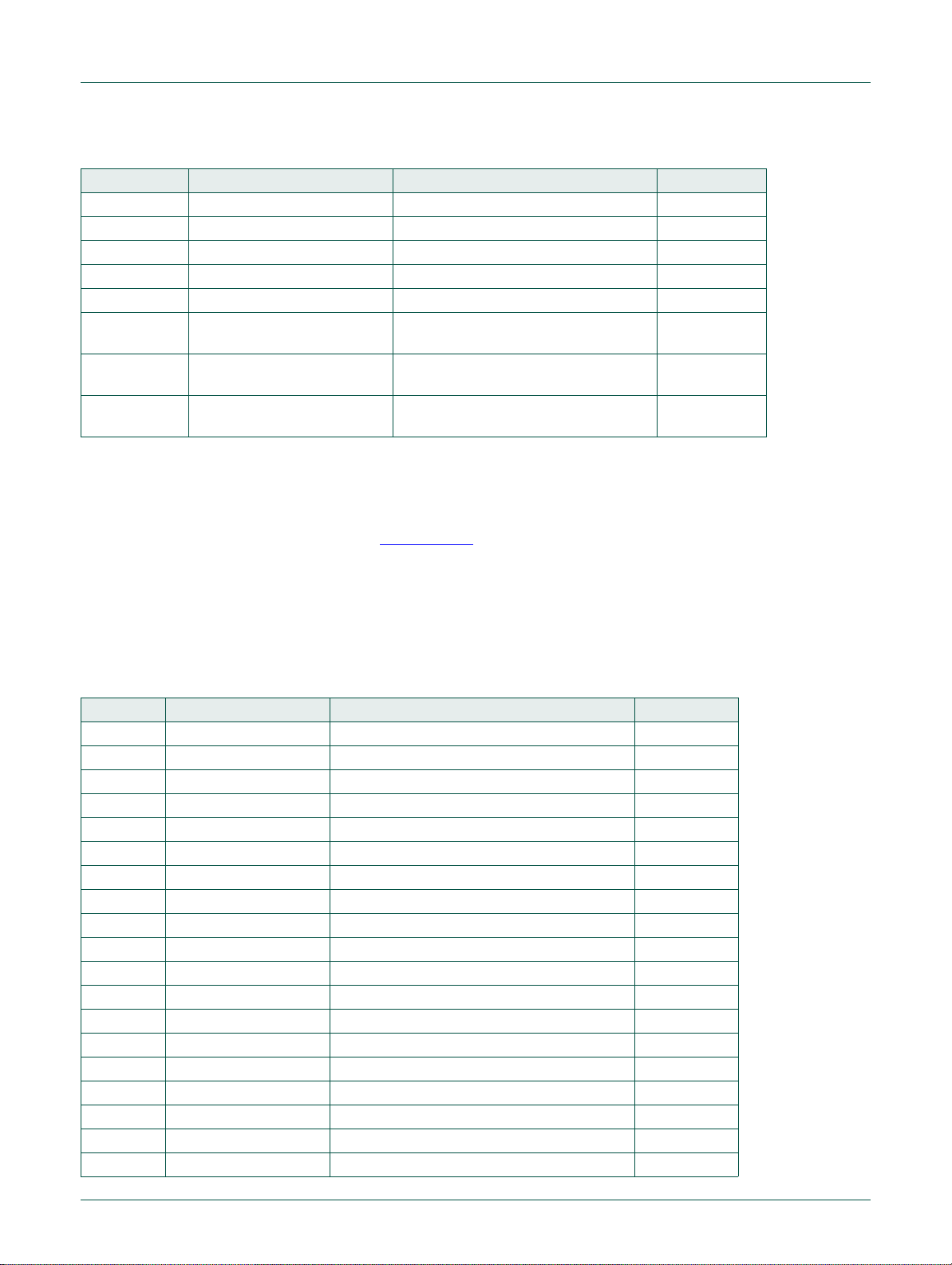

1.5 Block diagram

UM11029

Chapter 1: LPC84x Introductory information

Note: Yellow shaded blocks support general purpose DMA

Fig 1. LPC84x block diagram aaa-022793

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 8 of 515

Page 9

UM11029

Chapter 2: LPC84x memory mapping

Rev. 1.0 — 16 June 2017 User manual

2.1 How to read this chapter

The memory mapping is identical for all LPC84x parts. Different LPC84x parts support

different flash and SRAM memory sizes.

2.2 General description

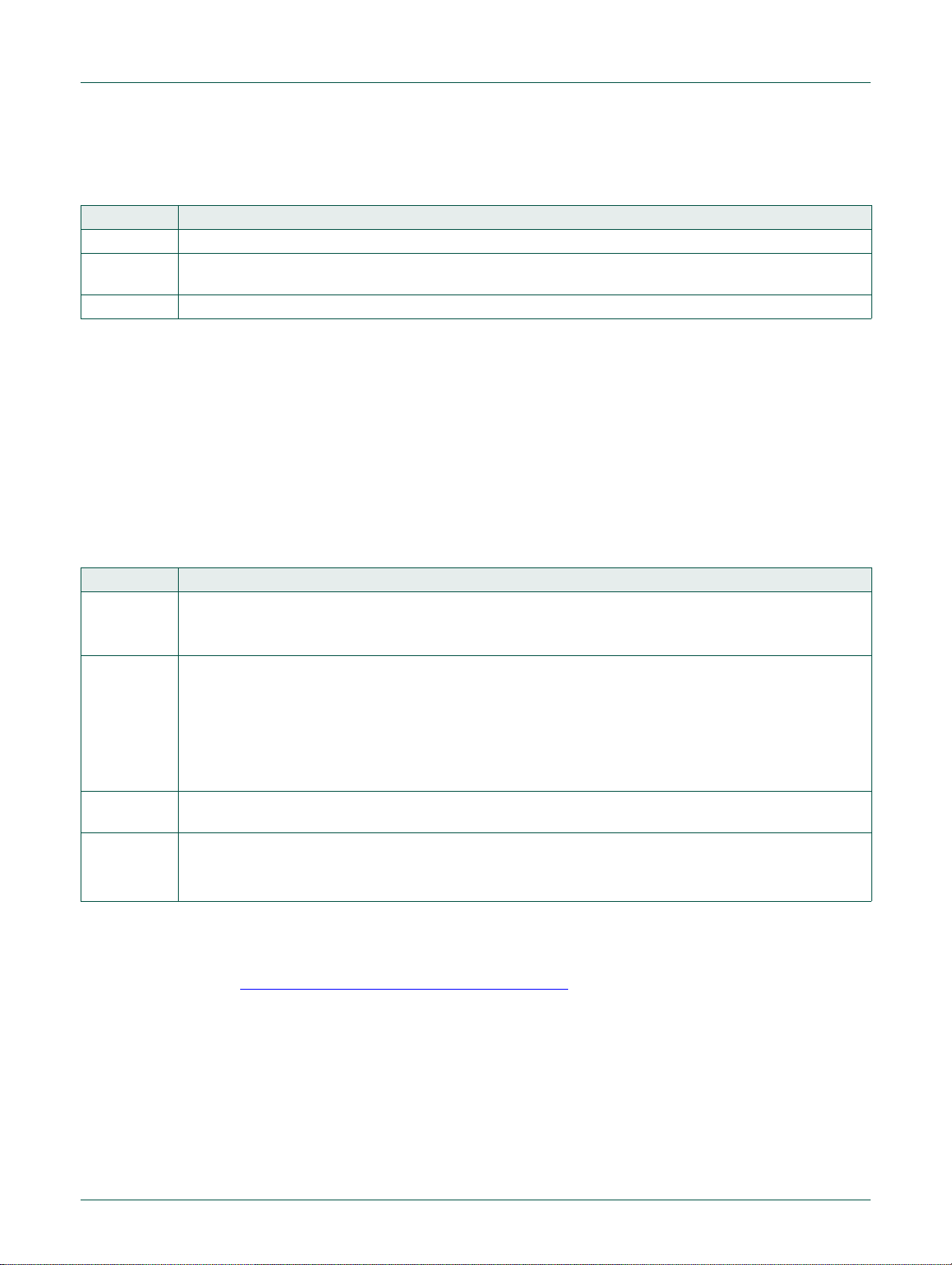

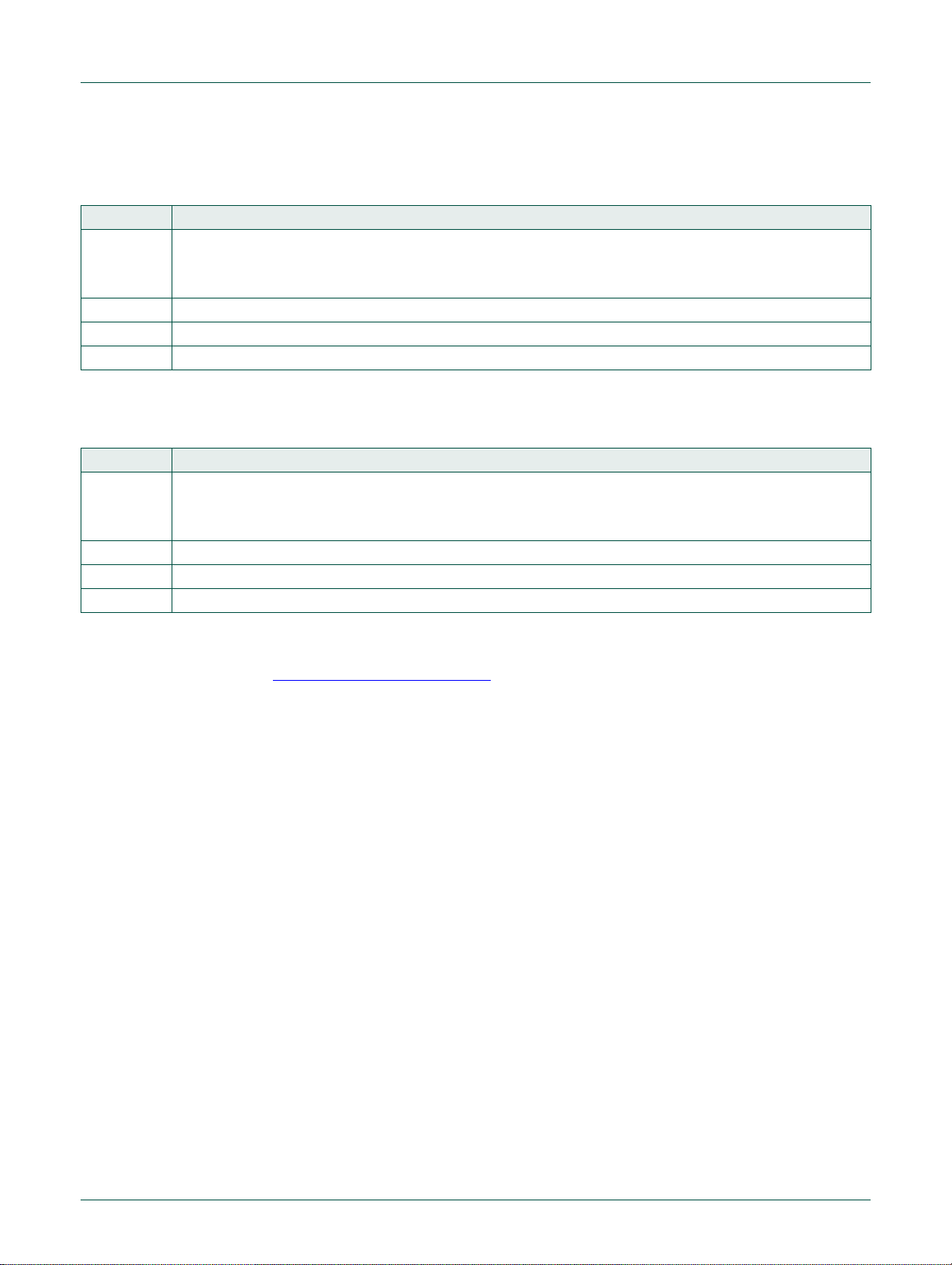

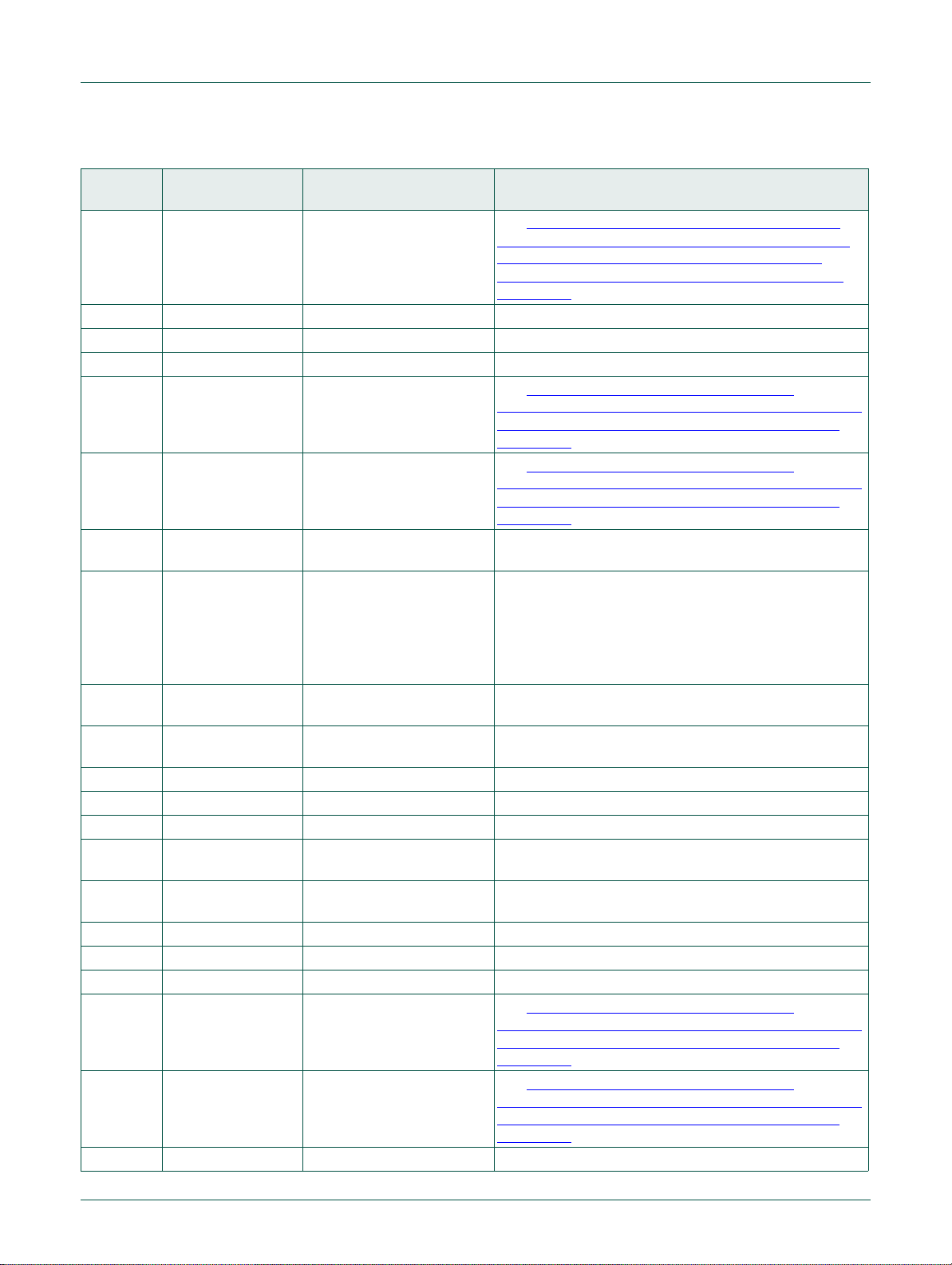

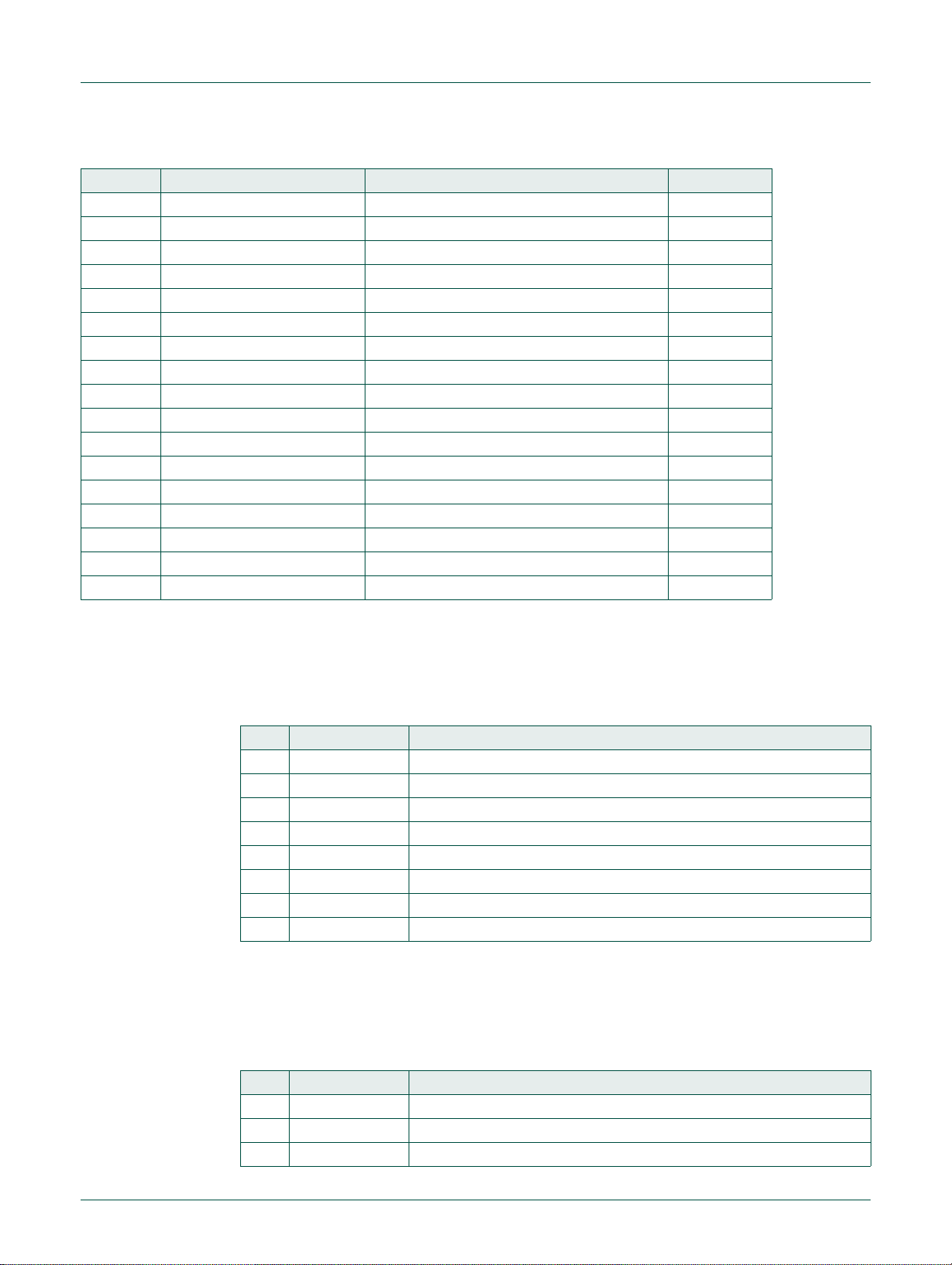

The LPC84x incorporates several distinct memory regions. Figure 2 shows the overall

map of the entire address space from the user program viewpoint following reset.

The APB peripheral area is 512 KB in size and is divided to allow for up to 32 peripherals.

Each peripheral is allocated 16 KB of space simplifying the address decoding.

The registers incorporated into the ARM Cortex-M0+ core, such as NVIC, SysTick, and

sleep mode control, are located on the private peripheral bus.

The GPIO port and pin interrupt/pattern match registers are accessed by the ARM

Cortex-M0+ single-cycle I/O enabled port (IOP).

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 9 of 515

Page 10

NXP Semiconductors

2.2.1 Memory mapping

UM11029

Chapter 2: LPC84x memory mapping

Memory space

(reserved)

private peripheral bus

(reserved)

GPIO interrupts

GPIO

(reserved)

AHB

peripherals

(reserved)

APB

peripherals

(reserved)

RAM1

RAM0

(reserved)

Boot ROM

(reserved)

Flash memory

(up to 64 MB)

active interrupt vectors

0xFFFF FFFF

0xE010 0000

0xE000 0000

0xA008 0000

0xA004 0000

0xA000 0000

0x5001 4000

0x5000 0000

0x4008 0000

0x4000 0000

0x1000 4000

0x1000 2000

0x1000 0000

0x0F00 4000

0x0F00 0000

0x0001 0000

0x0000 0000

0x0000 00C0

0x0000 0000

AHB perpherals

MTB registers

DMA controller

SCTimer / PWM

31-30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

(reserved)

CRC engine

APB perpherals

(reserved)

UART4

UART3

UART2

UART1

UART0

(reserved)

SPI1

SPI0

I2C1

I2C0

(reserved)

Syscon

IOCON

Flash controller

(reserved)

CTIMER 0

I2C3

I2C2

Input Multiplexing

(reserved)

Analog Comparator

PMU

ADC

DAC1

DAC0

(reserved)

Switch Matrix

Wake-up Timer

Multi-Rate Timer

Watchdog timer

0x5001 4000

0x5001 0000

0x5000 C000

0x5000 8000

0x5000 4000

0x5000 0000

0x4007 FFFF

0x4007 8000

0x4007 4000

0x4007 0000

0x4006 C000

0x4006 8000

0x4006 4000

0x4006 0000

0x4005 C000

0x4005 8000

0x4005 4000

0x4005 0000

0x4004 C000

0x4004 8000

0x4004 4000

0x4004 0000

0x4003 C000

0x4003 8000

0x4003 4000

0x4003 0000

0x4002 C000

0x4002 8000

0x4002 4000

0x4002 0000

0x4001 C000

0x4001 8000

0x4001 4000

0x4001 0000

0x4000 C000

0x4000 8000

0x4000 4000

0x4000 0000

aaa-027479

Fig 2. LPC84x Memory mapping

2.2.2 Micro Trace Buffer (MTB)

The LPC84x supports the ARM Cortex-M0+ Micro Trace Buffer. See Section 31.5.4.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 10 of 515

Page 11

UM11029

Chapter 3: LPC84x Boot Process

Rev. 1.0 — 16 June 2017 User manual

3.1 How to read this chapter

The bootloader is identical for all parts.

3.2 Features

• 16 KB on-chip boot ROM

• Contains the bootloader with In-System Programming (ISP) facility over multiple

peripheral communication (UART, I

– In-Application Programming (IAP) of flash memory.

– Integer divide routines.

– FAIM API.

– FRO API.

2

C, and SPI) and the following API:

3.3 Basic configuration

Depending on the FAIM configuration, the boot ROM sets the FRO control register to

select the operating frequency accordingly. If FAIM is not programmed or contains an

invalid value, the ROM begins at 12 MHz.

3.4 Pin description

When the ISP entry pin (PIO0_12) is pulled LOW on reset, the part enters ISP mode and

the ISP command handler starts up.

Table 3. Pin location in ISP mode

ISP mode Default FAIM configuration FAIM ISP selection

USART ISP PIO0_25 is UART0 TX

I2C ISP PIO0_11 is I2C0 SDA

SPI ISP PIO0_15 is SPI0 SCK

PIO0_24 is UART0 RX

Applicable when FAIM content

is invalid.

PIO0_10 is I2C0 SCL

Applicable when FAIM content

is invalid.

PIO0_22 is SPI0 SSEL0

PIO0_26 is SPI0 MISO

PIO0_27 is SPI0 MOSI

FAIM ISP pin

(FAIM word0, bit 30

and 31), Table 5

0x00 See: Table 6

0x01 -

0x02 See: Table 6

function (FAIM

word0, bit 30

and 31)

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 11 of 515

Page 12

NXP Semiconductors

3.5 General description

3.5.1 Bootloader

The bootloader executes every time the device is powered on or reset. Based on the chip

configuration information, the bootloader controls initial operation after reset, including

setting internal voltage regulator, system clock, flash controller, miscellaneous factory

trimming value, and then allows programming and reprogramming of internal flash via a

set of commands on USART, I2C slave, or SPI slave bus. The LPC84x device must be

connected to a host system that provides the UART, I

UM11029

Chapter 3: LPC84x Boot Process

2

C or SPI master connections.

During the boot process, a LOW level after reset on the ISP pin is considered as an

external hardware request to start the ISP command handler via USART, I

interface. Otherwise, the bootloader checks if there is valid user code in flash. If the valid

user code is not found, the bootloader checks the FAIM configuration and enters one of

the ISP modes. Auto detect is selected if FAIM is invalid.

Remark: The sampling of pin the ISP entry pin can be disabled through programming

flash location 0x0000 02FC (see Section 4.3.6 “Code Read Protection (CRP)”

See Chapter 5 “

LPC84x ISP and IAP” for more details.

3.5.2 ROM-based APIs

Once the part has booted, the user can access several APIs located in the boot ROM. The

ROM API supports:

• Boot loader.

• Flash In-Application Programming (IAP).

• In-System Programming (ISP) through USART, SPI, and I

• On-chip ROM APIs for integer divide.

• FAIM API.

• FRO API.

2

C, or SPI

).

2

C.

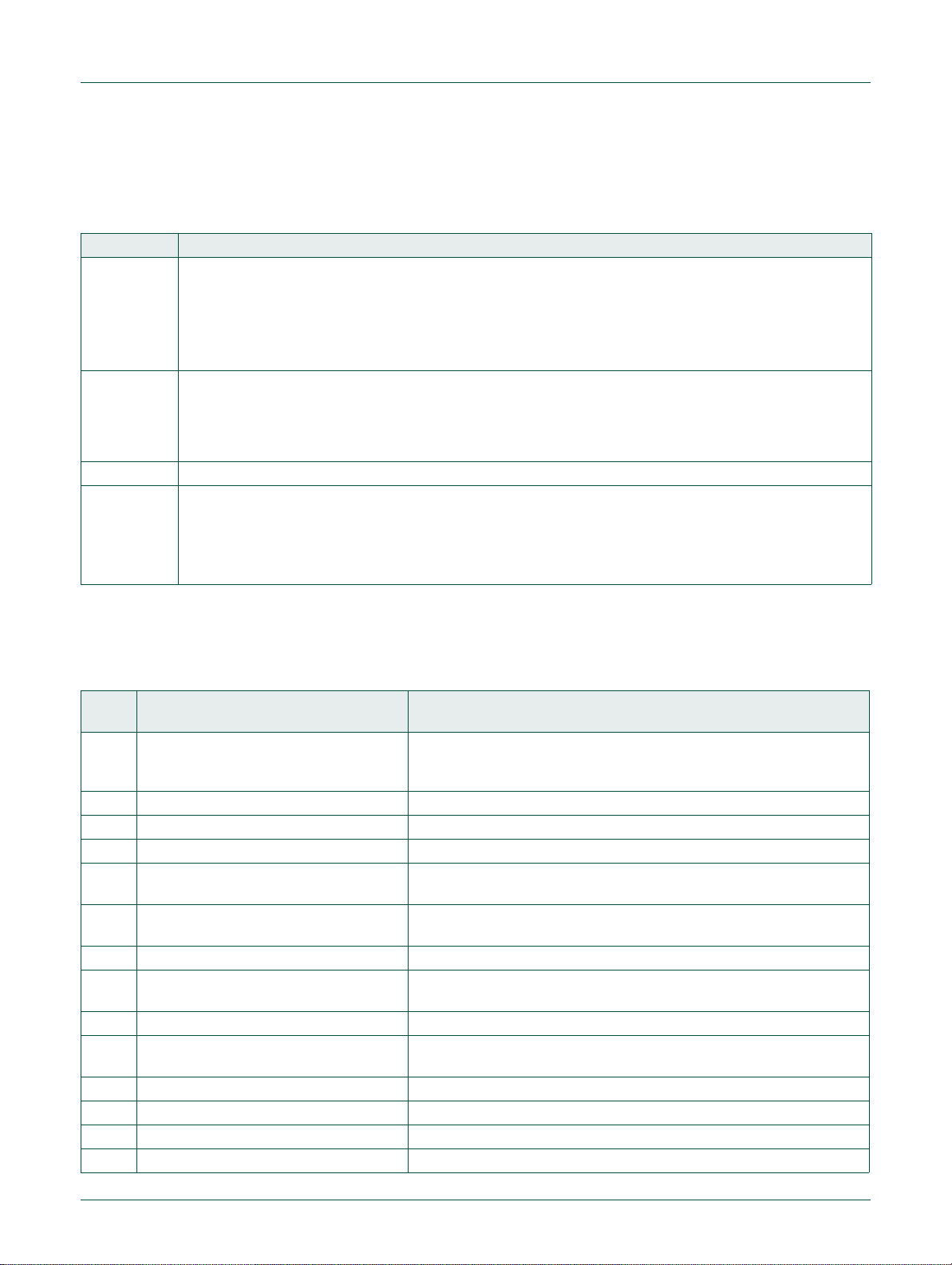

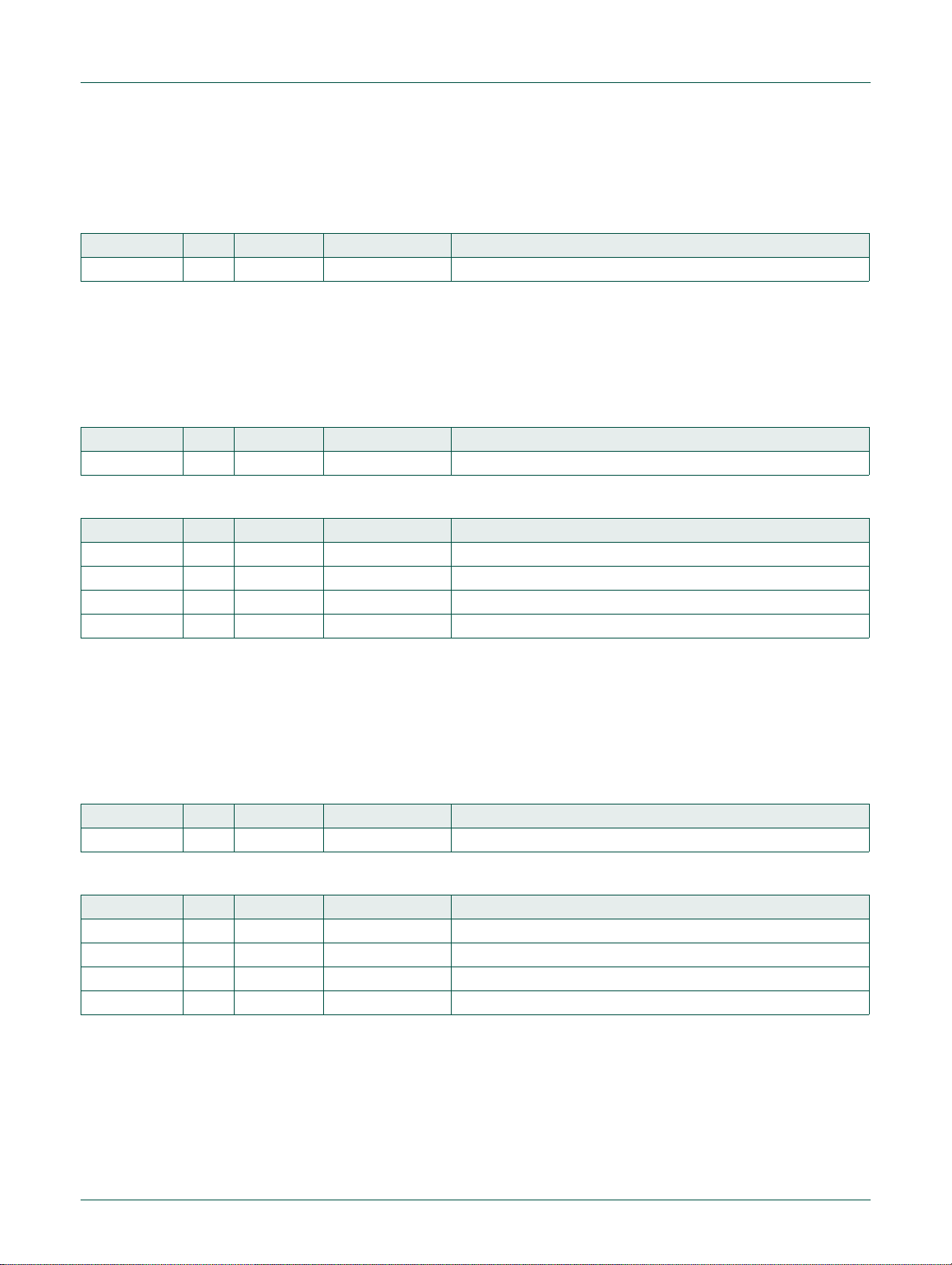

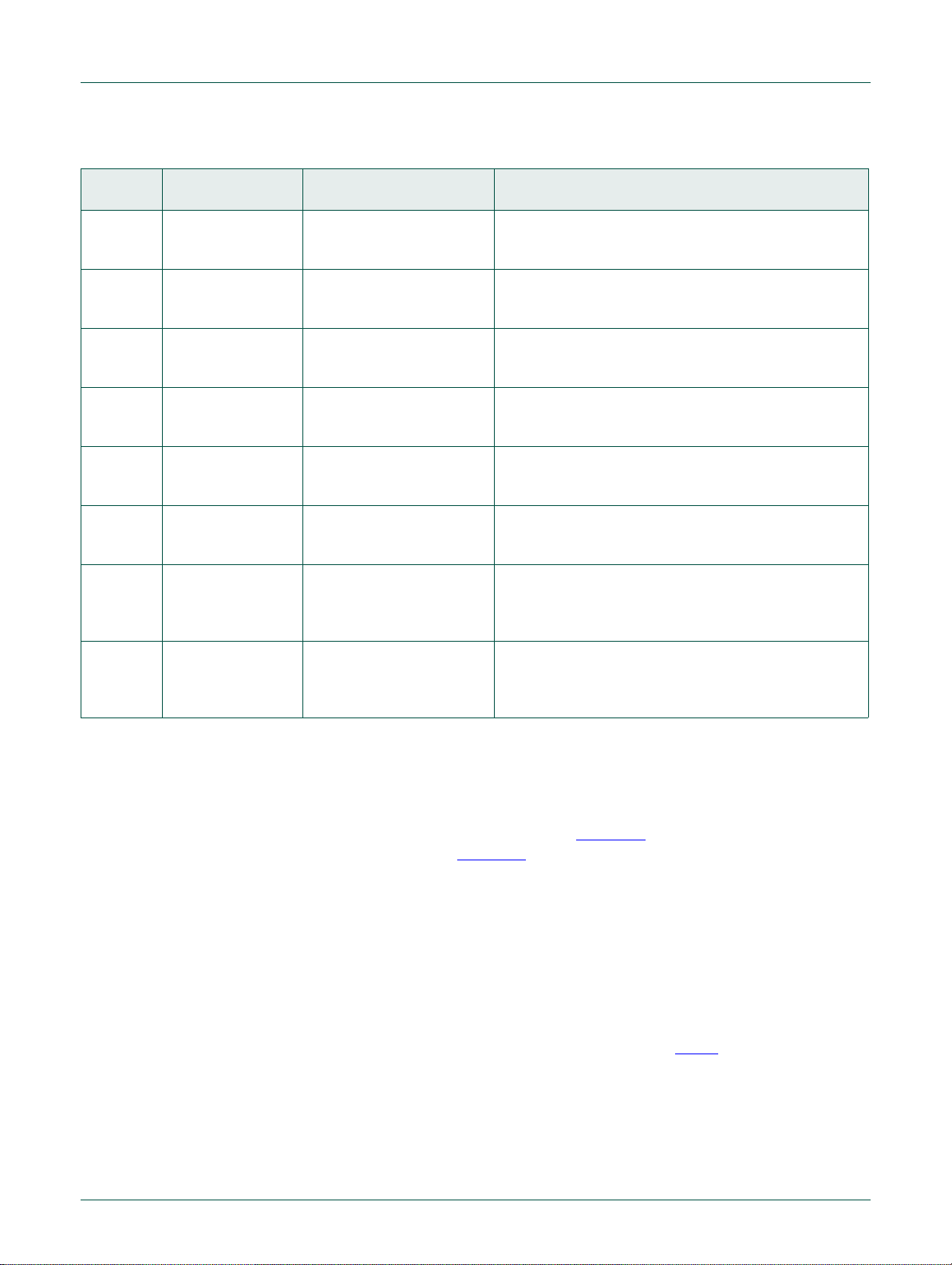

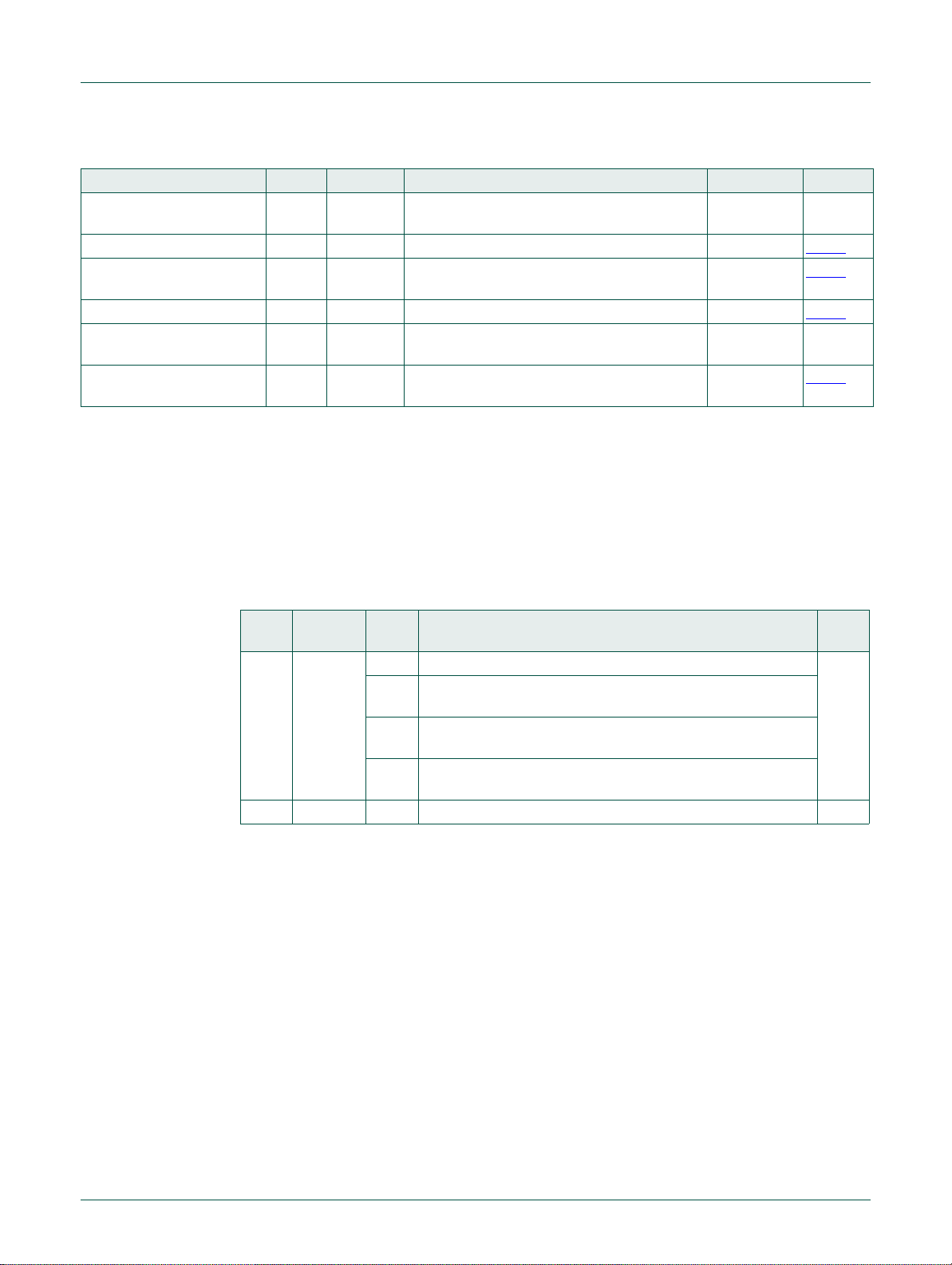

The structure of the boot ROM APIs is shown in Figure 3

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 12 of 515

.

Page 13

NXP Semiconductors

UM11029

Chapter 3: LPC84x Boot Process

+0x0

+0x4

+0x8

+0xC

+0x10

Ptr to IAP

0x0F001FF1

Ptr to ROM Driver table

0x0F001FF8

ROM Driver Table

Reserved

Reserved

Reserved

Clock setting and enter low power mode API

Pointer to 32-bit integer divide routines

…

Ptr to Device API Table n

IAP calls

Device API 3

Power profiles API function table

Device API 4

Integer Divide routines function table

Device API n

Ptr to Function 0

Ptr to Function 1

Ptr to Function 2

…

Ptr to Function n

Fig 3. Boot ROM structure

aaa-026624

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 13 of 515

Page 14

NXP Semiconductors

The boot ROM structure should be included as follows:

typedef struct {

const uint32_t reserved0; /*!< Reserved */

const uint32_t reserved1; /*!< Reserved */

const uint32_t reserved2; /*!< Reserved */

const PWRD_API_T *pPWRD; /*!< Power API function table base address */

const ROM_DIV_API_T *divApiBase; /*!< Divider API function table base address */

} LPC_ROM_API_T;

#define ROM_DRIVER_BASE (0x0F001FF8)

Table 4. API calls

API Description Reference

Flash IAP Flash In-Application programming Table 37

Integer divider API 32-bit integer divide routines Table 471

3.6 Functional description

UM11029

Chapter 3: LPC84x Boot Process

3.6.1 Memory map after any reset

The boot ROM block is 16 KB in size. The boot block is located in the memory region

starting from address 0x0F00 0000. The bootloader is designed to run from this memory

area, but both the ISP and IAP software use parts of the on-chip RAM. The RAM usage is

described in Section 4.3.7 “ISP interrupt and SRAM use”

the boot block of the on-chip flash memory also become active after reset, i.e., the bottom

512 bytes of the boot block are also visible in the memory region starting from the address

0x0000 0000.

. The interrupt vectors residing in

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 14 of 515

Page 15

NXP Semiconductors

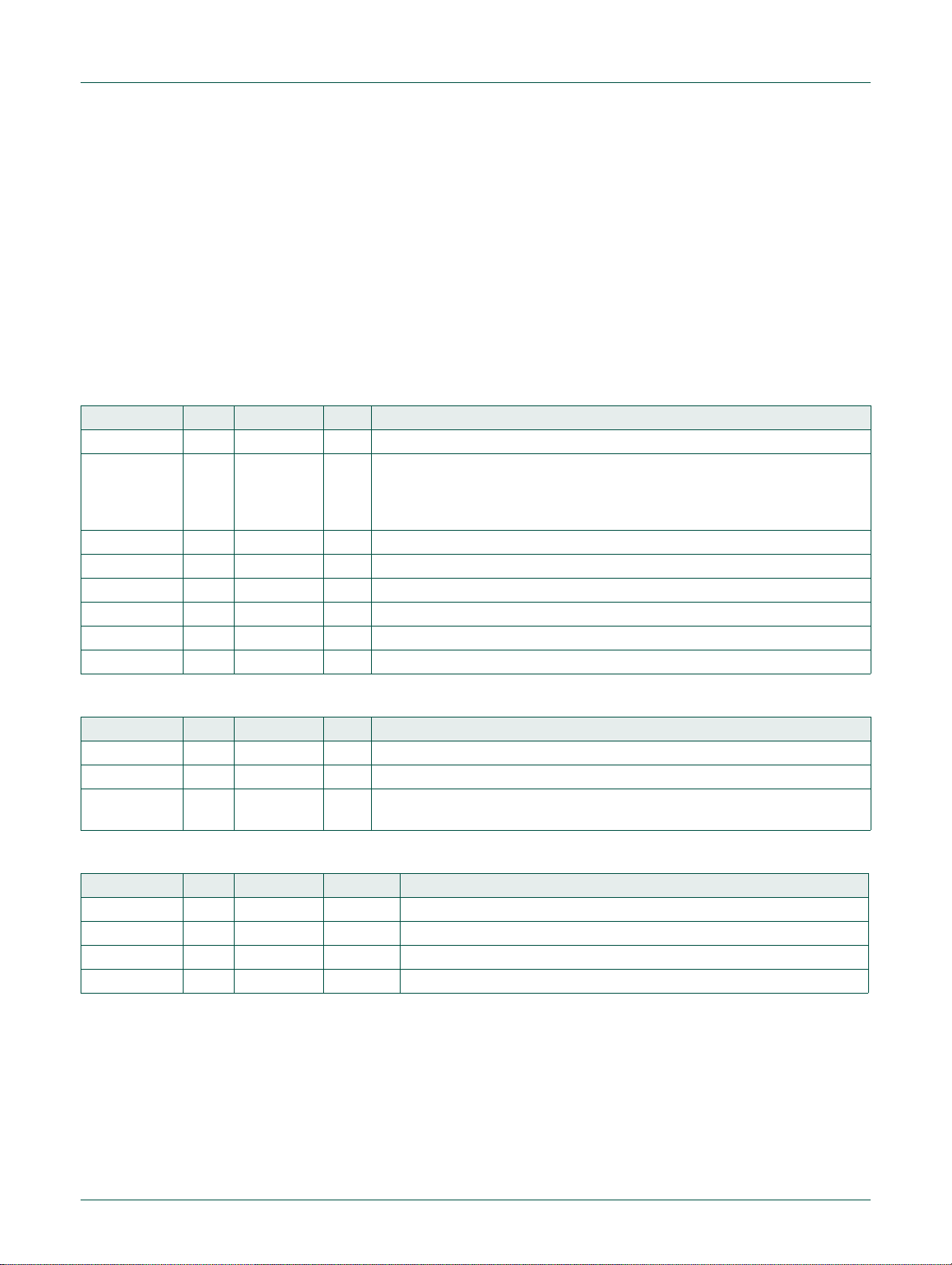

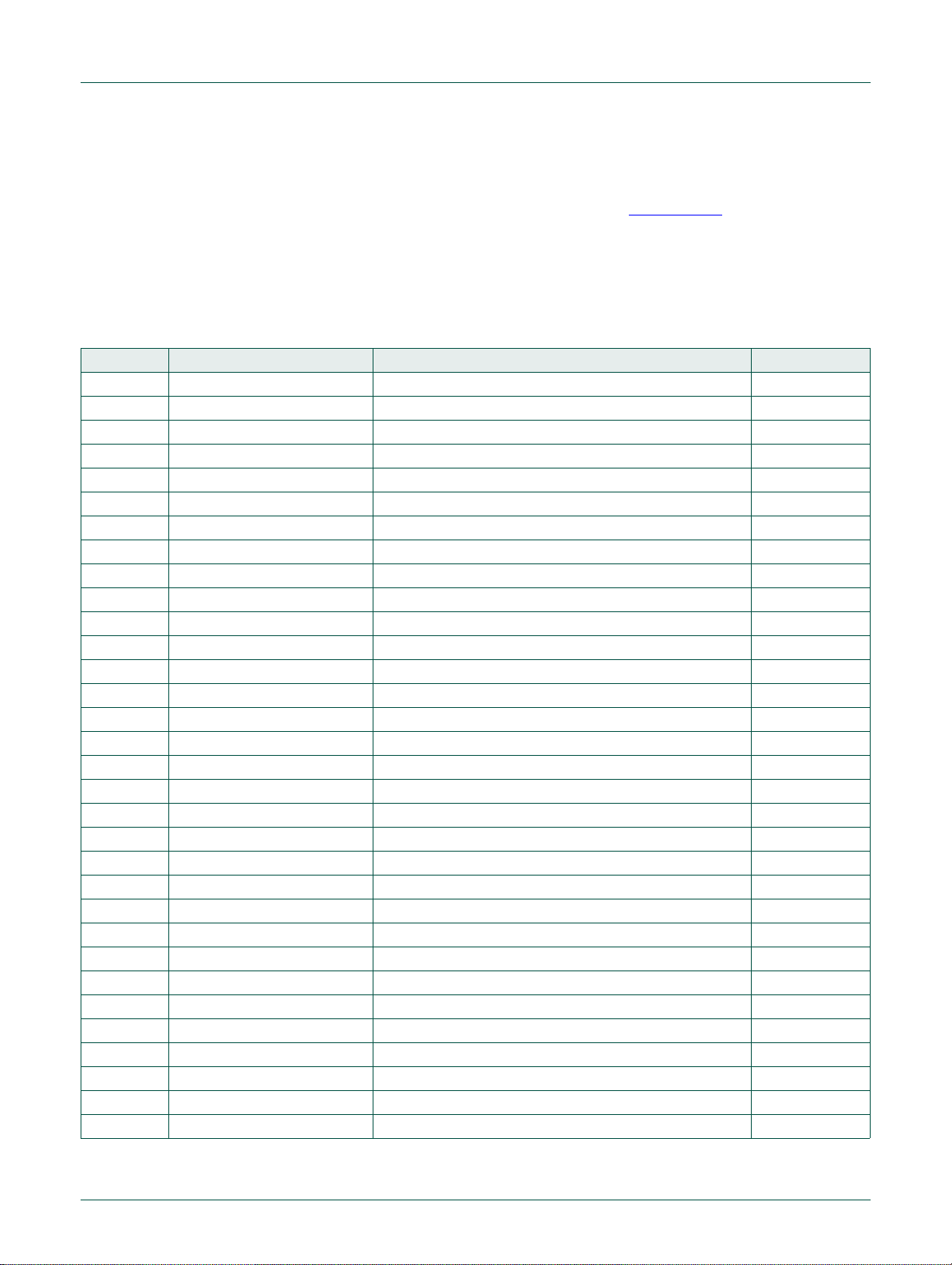

3.6.2 Boot process

Reset

UM11029

Chapter 3: LPC84x Boot Process

CRP 1/2/3

enabled

yes

Device configure/

Initialize

WDT reset

no

No_ISP or

CRP3

enabled

yes

User code

valid

yes

A

no

Enable debugger

no

no

FAIM content invalid,

fixed USART/I2C/

SPI port pins

USART/I2S/

SPI ISP auto

detected

A

ISP pin

low

invalid

yes

no

FAIM content

valid or 0/1/2

FAIM ISP select 0,

USART port/pin

setting

UART ISP

no

yes

0/1/2

0

User code

valid

FAIM ISP select 0,

USART port/pin

setting

I2C ISP

yes

no

User code

21

FAIM ISP select 2,

SPI port/pin

setting

SPI ISP

USART ISP

command handler

I2C/SPI ISP

command handler

aaa-026887

Fig 4. Boot process flowchart

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 15 of 515

Page 16

UM11029

Chapter 4: LPC84x FAIM

Rev. 1.0 — 16 June 2017 User manual

4.1 How to read this chapter

The Fast Initialization Memory (FAIM) is a 256-bit memory configured as eight words (or

rows) of 32-bits per word.

4.2 General description

The FAIM is a multiple time programmable (MTP), ultra low power memory, the full

contents of which are read and latched immediately after reset, with no clocks required.

The FAIM contents provide a user-programmable initial configuration for aspects of the

microcontroller, which take effect immediately after reset, before code begins to run. For

instance, the standard I/O pads normally come out of reset with the internal pull-ups

enabled. In some systems this may cause excess current to flow, until software can

reconfigure the pads. However, by programming the FAIM appropriately, every pad's reset

configuration can be customized. Other aspects which can be controlled by the FAIM are

initial FRO divider value (low power start), serial wire debug disable, default ISP interface

and pins, etc. One 32-bit FAIM row can be programmed, or read, using the ROM IAP calls

FAIMWrite and FAIMRead (see Chapter 5 “

LPC84x ISP and IAP” for details).

After a FAIMMWrite, a FAIMRead is required to update the output of the FAIM. Once a

read has been performed, the FAIM contents are visible in the AHB Peripheral address

space starting at 0x5001_0000.

For the pull-up, pull-down, and HI-Z IOCON pin configuration settings, a reset is needed

to transfer the newly programmed FAIM values into the IOCON pin configuration registers.

Executing a FAIMWrite followed by a FAIMRead does not update the current configuration

in the IOCON pin configuration registers. Only a reset can do so. Software can at any time

rewrite the IOCON pin configuration. Similarly, for SWD Disable, Low Power Start

configuration, ISP interface and pin select, a reset is needed to update the actual startup

configuration.

The FAIM is limited to 200 program cycles, so care must be taken to write this memory

only when necessary during an end-product's development. Also, the FAIM programming

voltage range is 3.0 V Vdd 3.6 V.

Remark: If internal pull-down is enabled via FAIM on the ISP pin (PIO0_12) or the reset

pin (PIO0_5), ensure to have a strong external pull-up to avoid going into ISP mode or into

reset after boot-up.

4.2.1 FAIM bit definitions

The functions of FAIM bits are described in the following tables.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 16 of 515

Page 17

NXP Semiconductors

Table 5. FAIM word 0 bit description

Bit Description Default value

0 SWD disable 0

1 Low Power Boot 0

26:2 Reserved 0

28 Reserved 0

29, 27 FAIM content valid bits 11

31:30 ISP interface select 0

UM11029

Chapter 4: LPC84x FA IM

0 SWD enabled

1 SWD disabled

0 Normal boot (12 MHz)

1 Low Power Boot (1.5 MHz)

00 FAIM content invalid

01 FAIM content invalid

10 FAIM content invalid

11 FAIM content valid

00 USART0

01 I2C0

10 SPI0

11 Reserved

Table 6. FAIM word 1 bit description

Bit Description Default value

4:0 ISP Rx pin select (USART0 Rx, SPI MOSI) 0x18

0x0

0x1

...

0x1F

PIOn_0

PIOn_1

...

PIOn_31

7:5 ISP Rx port select (USART0 Rx, SPI MOSI) 0

0x0 Port 0

0x1 Port 1

12:8 ISP Tx pin select (USART0 Tx, SPI MISO) 0x19

0x0

0x1

...

0x1F

PIOn_0

PIOn_1

...

PIOn_31

15:13 ISP Tx port select (USART0 Tx, SPI MISO) 0

0x0 Port 0

0x1 Port 1

20:16 ISP clock pin select (SPI SCK) 0

0x0

0x1

...

0x1F

PIOnPIOn_0

PIOn_1

...

PIOn_31

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 17 of 515

Page 18

NXP Semiconductors

Table 6. FAIM word 1 bit description

Bit Description Default value

23:21 ISP clock port select (SPI SCK) 0

28:24 ISP SPI0 SSELN0 pin select 0

31:29 ISP SPI0 SSELN0 port select 0

Table 7. FAIM word 2 bit description

Bit Description Default value

31:0 Reserved 0

0x0 Port 0

0x1 Port 1

0x0

0x1

...

0x1F

PIOn_0

PIOn_1

...

PIOn_31

0x0 Port 0

0x1 Port 1

UM11029

Chapter 4: LPC84x FA IM

Table 8. FAIM word 3 bit description

Bit Description Default value

31:0 Reserved 0

Table 9. FAIM word 4 bit description

Bit Description Default value

19:0 Reserved 0

21:20 PIO1_21 0x2

0x0 Hi-Z

0x1 Pull-down

0x2 Pull-up

0x3 Repeater

23:22 PIO1_20. See description of bits of bits 21:20. 0x2

25:24 PIO1_19. See description of bits 21:20. 0x2

27:26 PIO1_18. See description of bits 21:20. 0x2

29:28 PIO1_17. See description of bits 21:20. 0x2

31:30 PIO1_16. See description of bits 21:20. 0x2

Table 10. FAIM word 5 bit description

Bit Description Default value

1:0 PIO1_15

0x0 Hi-Z 0x2

0x1 Pull-down

0x2 Pull-up

0x3 Repeater

3:2 PIO1_14. See description of bits 1:0. 0x2

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 18 of 515

Page 19

NXP Semiconductors

Table 10. FAIM word 5 bit description

Bit Description Default value

5:4 PIO1_13. See description of bits 1:0. 0x2

7:6 PIO1_12. See description of bits 1:0. 0x2

9:8 PIO1_11. See description of bits 1:0. 0x2

11:10 PIO1_10. See description of bits 1:0. 0x2

13:12 PIO1_9. See description of bits 1:0. 0x2

15:14 PIO1_8. See description of bits 1:0. 0x2

17:16 PIO1_7. See description of bits 1:0. 0x2

19:18 PIO1_6. See description of bits 1:0. 0x2

21:20 PIO1_5. See description of bits 1:0. 0x2

23:22 PIO1_4. See description of bits 1:0. 0x2

25:24 PIO1_3. See description of bits 1:0. 0x2

27:26 PIO1_2. See description of bits 1:0. 0x2

29:28 PIO1_1. See description of bits 1:0. 0x2

31:30 PIO1_0. See description of bits 1:0. 0x2

UM11029

Chapter 4: LPC84x FA IM

Table 11. FAIM word 6 bit description

Bit Description Default value

1:0 PIO0_31 0

0x0 Hi-Z 0x2

0x1 Pull-down

0x2 Pull-up

0x3 Repeater

3:2 PIO0_30. See description of bits 1:0. 0x2

5:4 PIO0_29. See description of bits 1:0. 0x2

7:6 PIO0_28. See description of bits 1:0. 0x2

9:8 PIO0_27. See description of bits 1:0. 0x2

11:10 PIO0_26. See description of bits 1:0. 0x2

13:12 PIO0_25. See description of bits 1:0. 0x2

15:14 PIO0_24. See description of bits 1:0. 0x2

17:16 PIO0_23. See description of bits 1:0. 0x2

19:18 PIO0_22. See description of bits 1:0. 0x2

21:20 PIO0_21. See description of bits 1:0. 0x2

23:22 PIO0_20. See description of bits 1:0. 0x2

25:24 PIO0_19. See description of bits 1:0. 0x2

27:26 PIO0_18. See description of bits 1:0. 0x2

29:28 PIO0_17. See description of bits 1:0. 0x2

31:30 PIO0_16. See description of bits 1:0. 0x2

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 19 of 515

Page 20

NXP Semiconductors

Table 12. FAIM word 7 bit description

Bit Description Default value

1:0 PIO0_15 0

3:2 PIO0_14. See description of bits 1:0. 0x2

5:4 PIO0_13. See description of bits 1:0. 0x2

7:6 PIO0_12. See description of bits 1:0. 0x2

9:8 PIO0_11. See description of bits 1:0. 0x2

11:10 PIO0_10. See description of bits 1:0. 0x2

13:12 PIO0_9. See description of bits 1:0. 0x2

15:14 PIO0_8. See description of bits 1:0. 0x2

17:16 PIO0_7. See description of bits 1:0. 0x2

19:18 PIO0_6. See description of bits 1:0. 0x2

21:20 PIO0_5. See description of bits 1:0. 0x2

23:22 PIO0_4. See description of bits 1:0. 0x2

25:24 PIO0_3. See description of bits 1:0. 0x2

27:26 PIO0_2. See description of bits 1:0. 0x2

29:28 PIO0_1. See description of bits 1:0. 0x2

31:30 PIO0_0. See description of bits 1:0. 0x2

UM11029

Chapter 4: LPC84x FA IM

0x0 Hi-Z 0x2

0x1 Pull-down

0x2 Pull-up

0x3 Repeater

UM11029 All information provided in this document is subject to legal disclaimers. © NXP Semiconductors N.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 20 of 515

Page 21

UM11029

Chapter 5: LPC84x ISP and IAP

Rev. 1.0 — 16 June 2017 User manual

5.1 How to read this chapter

All LPC84x devices include ROM-based services for programming and reading the flash

memory in addition to other functions. In-System Programming works on an

unprogrammed or previously programmed device using one from a selection of hardware

interfaces. In-Application Programming allows application software to do the same kinds

of operations.

See specific device data sheets for different flash configurations.

Remark: In addition to the ISP and IAP commands, the flash configuration register

(FLASHCFG) can be accessed in the flash controller block to configure flash memory

access times, see Section 6.4.1

5.2 Features

.

• In-System Programming: In-System programming (ISP) is programming or

reprogramming the on-chip flash memory, using the boot loader software and USART,

2

I

C, or SPI serial port. This can be done when the part resides in the end-user board.

• In Application Programming: In-Application (IAP) programming is performing erase

and write operation on the on-chip flash memory, as directed by the end-user

application code.

• Flexible ISP mode and port pin selection through FAIM memory configuration.

• Small size (64 byte) page erase programming.

5.3 General description

5.3.1 Boot loader

For the boot loader operation and boot pin, see Chapter 3 “LPC84x Boot Process”.

The boot loader version can be read by ISP/IAP calls (see Section 5.5.13

Section 5.6.6

5.3.2 Memory map after any reset

The boot ROM is located in the memory region starting from the address 0x0F00 0000.

The boot loader is designed to run from this memory area, but both the ISP and IAP

software use parts of the on-chip RAM. The RAM usage is described later in

Section 5.3.7

or

).

.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 21 of 515

Page 22

NXP Semiconductors

5.3.3 Flash content protection mechanism

The LPC84x is equipped with the Error Correction Code (ECC) capable Flash memory.

The purpose of an error correction module is twofold. Firstly, it decodes data words read

from the memory into output data words. Secondly, it encodes data words to be written to

the memory. The error correction capability consists of single bit error correction with

Hamming code.

The operation of the ECC is transparent to the running application. The ECC content itself

is stored in a flash memory not accessible by the user’s code to either read from it or write

into it on its own. Six bits of ECC corresponds to every consecutive 32 bit of the user

accessible Flash. Consequently, Flash bytes from 0x0000 0000 to 0x0000 0003 are

protected by the first 6-bit ECC, Flash bytes from 0x0000 0004 to 0x0000 0007 are

protected by the second 6-bit ECC byte, etc.

Whenever the CPU requests a read from user’s Flash, both 32 bits of raw data containing

the specified memory location and the matching ECC byte are evaluated. If the ECC

mechanism detects a single error in the fetched data, a correction will be applied before

data are provided to the CPU. When a write request into the user’s Flash is made, write of

user specified content is accompanied by a matching ECC value calculated and stored in

the ECC memory.

UM11029

Chapter 5: LPC84x ISP and IAP

When a sector of Flash memory is erased, the corresponding ECC bytes are also erased.

Once an ECC byte is written, it can not be updated unless it is erased first. Therefore, for

the implemented ECC mechanism to perform properly, data must be written into the flash

memory in groups of 4 bytes (or multiples of 4), aligned as described above.

5.3.4 Criteria for Valid User Code

The reserved CPU exception vector location 7 (offset 0x0000 001C in the vector table)

should contain the 2’s complement of the check-sum of table entries 0 through 6. This

causes the checksum of the first 8 table entries to be 0. The boot loader code checksums

the first 8 locations in sector 0 of the flash.

If the checksum is not zero indicating valid user code is not found, the bootloader will

check the FAIM configuration and enter UART/I2C/SPI ISP mode automatically.

5.3.5 Flash partitions

Some IAP and ISP commands operate on sectors and specify sector numbers. In

addition, a page erase command is available. The size of a sector is 1 KB and the size of

a page is 64 Byte. One sector contains 16 pages.

Table 13. LPC82x flash configuration <tbd>

Sector

number

0 1 0 -15 0x0000 0000 - 0x0000 03FF yes yes

1 1 16 - 31 0x0000 0400 - 0x0000 07FF yes yes

2 1 32 - 47 0x0000 0800 - 0x0000 0BFF yes yes

3 1 48 - 63 0x0000 0C00 - 0x0000 0FFF yes yes

4 1 64 - 79 0x0000 1000 - 0x0000 13FF yes yes

5 1 80 - 95 0x0000 1400 - 0x0000 17FF yes yes

Sector

size [KB]

Page number Address range 16 KB

flash

32 KB

flash

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 22 of 515

Page 23

NXP Semiconductors

Table 13. LPC82x flash configuration <tbd>

Sector

number

6 1 96 - 111 0x0000 1800 - 0x0000 1BFF yes yes

7 1 112 - 127 0x0000 1C00 - 0x0000 1FFF yes yes

8 1 128 - 143 0x0000 2000 - 0x0000 23FF yes yes

9 1 144 - 159 0x0000 2400 - 0x0000 27FF yes yes

10 1 160 - 175 0x0000 2800 - 0x0000 2BFF yes yes

11 1 176 - 191 0x0000 2C00 - 0x0000 2FFF yes yes

12 1 192 - 207 0x0000 3000 - 0x0000 33FF yes yes

13 1 208 - 223 0x0000 3400 - 0x0000 37FF yes yes

14 1 224 - 239 0x0000 3800 - 0x0000 3BFF yes yes

15 1 240 - 255 0x0000 3C00 - 0x0000 3FFF yes yes

16 1 256 - 271 0x0000 4000 - 0x0000 43FF - yes

17 1 272 - 287 0x0000 4400 - 0x0000 47FF - yes

18 1 288 - 303 0x0000 4800 - 0x0000 4BFF - yes

19 1 304 - 319 0x0000 4C00 - 0x0000 4FFF - yes

20 1 320 - 335 0x0000 5000 - 0x0000 53FF - yes

21 1 336 - 351 0x0000 5400 - 0x0000 57FF - yes

22 1 352 - 367 0x0000 5800 - 0x0000 5BFF - yes

23 1 368 - 383 0x0000 5C00 - 0x0000 5FFF - yes

24 1 384 - 399 0x0000 6000 - 0x0000 63FF - yes

25 1 400 - 415 0x0000 6400 - 0x0000 67FF - yes

26 1 416 - 431 0x0000 6800 - 0x0000 6BFF - yes

27 1 432 - 447 0x0000 6C00 - 0x0000 6FFF - yes

28 1 448 - 463 0x0000 7000 - 0x0000 73FF - yes

29 1 464 - 479 0x0000 7400 - 0x0000 77FF - yes

30 1 480 - 495 0x0000 7800 - 0x0000 7BFF - yes

31 1 496 - 511 0x0000 7C00 - 0x0000 7FFF - yes

Sector

size [KB]

UM11029

Chapter 5: LPC84x ISP and IAP

Page number Address range 16 KB

flash

32 KB

flash

5.3.6 Code Read Protection (CRP)

Code Read Protection is a mechanism that allows the user to enable different levels of

security in the system so that access to the on-chip flash and use of the ISP can be

restricted. When needed, CRP is invoked by programming a specific pattern in the flash

image at offset 0x0000 02FC. IAP commands are not affected by the code read

protection.

Table 1 shows the limitations of the USART ISP commands when CRP (CRP1, CRP2, or

CRP3) is enabled.

Note: Any CRP change becomes effective only after the device has gone through a

power cycle.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 23 of 515

Page 24

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

Table 14. USART ISP command limitations in CRP modes

Name Pattern programmed

in 0x0000 02FC

NO_ISP 0x4E69 7370 Prevents sampling of the pins for entering ISP mode. ISP sampling pin is available for

CRP1 0x1234 5678 Access to chip via the SWD pins is disabled. This mode allows partial flash update using

Description

other applications.

the following USART ISP commands and restrictions:

• Write to RAM command cannot access RAM below 0x1000 0600. Access to

addresses below 0x1000 0600 is disabled.

• Copy RAM to flash command cannot write to Sector 0.

• Erase command can erase Sector 0 only when all sectors are selected for erase.

• Compare command is disabled.

• Read Memory command is disabled.

This mode is useful when CRP is required and flash field updates are needed but all

sectors can not be erased. Since compare command is disabled in case of partial

updates the secondary loader should implement checksum mechanism to verify the

integrity of the flash.

CRP2 0x8765 4321 Access to chip via the SWD pins is disabled. The following ISP commands are disabled:

• Read Memory

• Write to RAM

• Go

• Copy RAM to flash

• Compare

When CRP2 is enabled the ISP erase command only allows erasure of all user sectors.

CRP3 0x4321 8765 Access to chip via the SWD pins is disabled. ISP entry selected via the ISP entry pin is

disabled if a valid user code is present in flash sector 0.

This mode effectively disables ISP override using the entry pin. It is up to the application

of the user to provide a flash update mechanism using IAP calls or call reinvoke ISP

command to enable flash update via USART.

Caution: If CRP3 is selected, no future factory testing can be performed on the

device.

In case a CRP mode is enabled and access to the chip is allowed via the ISP, an

unsupported or restricted ISP command will be terminated with return code

CODE_READ_PROTECTION_ENABLED.

5.3.6.1 ISP entry protection

In addition to the three CRP modes, the user can prevent the sampling of the pin for

entering ISP mode and thereby release the pin for other applications. This is called the

NO_ISP mode. The NO_ISP mode can be entered by programming the pattern

0x4E69 7370 at location 0x0000 02FC.

The NO_ISP mode is identical to the CRP3 mode except for SWD access, which is

allowed in NO_ISP mode but disabled in CRP3 mode. The NO_ISP mode does not offer

any code protection.

5.3.6.2 ISP entry configuration and detection

The LPC84x UART/I2C/SPI ISP mode allows programming and reprogramming of the

internal FLASH via a set of commands on the UART, I2C slave, or SPI slave buses. Two

bits of the FAIM flash are used for ISP mode selection.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 24 of 515

Page 25

NXP Semiconductors

If FAIM content is invalid, the default ISP selection is USART/I2C/SPI or auto detection

mode. In auto detection mode, the LPC84x enables all three interfaces on the fixed GPIO

port and pins, and selects the first one that has either a successful auto baud detection on

USART or a valid probe message response on I2C or SPI.

If FAIM content is valid, USART, I2C, or SPI ISP mode is configured in the FAIM.

Additional SWM configuration for the interface and pins through FAIM is required. For

example, if FAIM ISP selection is 0x02, the GPIO port and pin information for SPI0, such

as SSEL, SCK, MOSI, and MISO is provided by the FAIM. The boot ROM reads the GPIO

port and pin information from the FAIM and writes to the SWM and IOCON registers

accordingly as part of the SPI initialization.

5.3.7 ISP interrupt and SRAM use

5.3.7.1 Interrupts during IAP

The on-chip flash memory is not accessible during erase/write operations. When the user

application code starts executing, the interrupt vectors from the user flash area are active.

Before making any IAP call, either disable the interrupts or ensure that the user interrupt

vectors are active in RAM and that the interrupt handlers reside in RAM. The IAP code

does not use or disable interrupts.

UM11029

Chapter 5: LPC84x ISP and IAP

5.3.7.2 RAM used by ISP command handlers

The stack of UART ISP commands is located at address 0x1000 0600. The maximum

stack usage is 1280 bytes (0x500) and grows downwards.

The DMA is used by the SPI ISP mode. The DMA descriptor table location is located at

address 0x1000 0600. The DMA table size is 512 bytes (0x200) and grows upwards.

Therefore, depending on the ISP mode entered, the maximum RAM used by ISP mode is

2 K starting from the address 0x1000 0000.

Memory for the USART and I2C/SPI ISP commands is allocated dynamically.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 25 of 515

Page 26

NXP Semiconductors

5.4 USART ISP communication protocol

All USART ISP commands should be sent as single ASCII strings. Strings should be

terminated with Carriage Return (CR) and/or Line Feed (LF) control characters. Extra

<CR> and <LF> characters are ignored. All ISP responses are sent as <CR><LF>

terminated ASCII strings. Data is sent and received in plain binary format.

5.4.1 USART ISP initialization

Once the USART ISP mode is entered, the auto-baud routine needs to synchronize with

the host via the serial port (USART).

The host should send a ’?’ (0x3F) as a synchronization character and wait for a response.

The host side serial port settings should be 8 data bits, 1 stop bit and no parity. The

auto-baud routine measures the bit time of the received synchronization character in

terms of its own frequency and programs the baud rate generator of the serial port. It also

sends an ASCII string ("Synchronized<CR><LF>") to the host. In response to this, the

host should send back the same string ("Synchronized<CR><LF>").

The auto-baud routine looks at the received characters to verify synchronization. If

synchronization is verified then "OK<CR><LF>" string is sent to the host. The host should

respond by sending the crystal frequency (in kHz) at which the part is running. The

response is required for backward compatibility of the boot loader code and is ignored.

"OK<CR><LF>" string is sent to the host after receiving the crystal frequency. If

synchronization is not verified then the auto-baud routine waits again for a

synchronization character. In USART ISP mode, the part is clocked by the FAIM

configuration and the crystal frequency is ignored.

UM11029

Chapter 5: LPC84x ISP and IAP

Once the crystal frequency is received the part is initialized and the ISP command handler

is invoked. For safety reasons an "Unlock" command is required before executing the

commands resulting in flash erase/write operations and the "Go" command. The rest of

the commands can be executed without the unlock command. The Unlock command is

required to be executed once per ISP session. The Unlock command is explained in

Section 5.5 “

USART ISP commands”.

5.4.2 USART ISP command format

"Command Parameter_0 Parameter_1 ... Parameter_n<CR><LF>" "Data" (Data only for

Write commands).

5.4.3 USART ISP response format

"Return_Code<CR><LF>Response_0<CR><LF>Response_1<CR><LF> ...

Response_n<CR><LF>" "Data" (Data only for Read commands).

5.4.4 USART ISP data format

The data stream is in plain binary format.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 26 of 515

Page 27

NXP Semiconductors

Chapter 5: LPC84x ISP and IAP

5.5 USART ISP commands

The following commands are accepted by the ISP command handler. Detailed status

codes are supported for each command. The command handler sends the return code

INVALID_COMMAND when an undefined command is received. Commands and return

codes are in ASCII format.

CMD_SUCCESS is sent by ISP command handler only when received ISP command has

been completely executed and the new ISP command can be given by the host.

Exceptions from this rule are "Set Baud Rate", "Write to RAM", "Read Memory", and "Go"

commands.

Table 15. USART ISP command summary

ISP Command Usage Section

Unlock U <Unlock Code> 5.5.1

Set Baud Rate B <Baud Rate> <stop bit> 5.5.2

Echo A <setting> 5.5.3

Write to RAM W <start address> <number of bytes> 5.5.4

Read Memory R <address> <number of bytes> 5.5.5

Prepare sectors for write operation P <start sector number> <end sector number> 5.5.6

Copy RAM to flash C <Flash address> <RAM address> <number of bytes> 5.5.7

Go G <address> <Mode> 5.5.8

Erase sector(s) E <start sector number> <end sector number> 5.5.9

Erase page(s) X <start page number> <end page number> 5.5.10

Blank check sector(s) I <start sector number> <end sector number> 5.5.11

Read Part ID J 5.5.12

Read Boot code version K 5.5.13

Compare M <address1> <address2> <number of bytes> 5.5.14

ReadUID N 5.5.15

Read CRC checksum S <address> <number of bytes> 5.5.16

Read flash signature Z 5.5.17

Read/Write FAIM Page O 5.5.18

UM11029

Ta bl e 1 6 lists the supported USART ISP commands for each CRP level.

Table 16. ISP commands allowed for different CRP levels

ISP command CRP1 CRP2 CRP3 (no entry in

Unlock yes yes n/a

Set Baud Rate yes yes n/a

Echo yes yes n/a

Write to RAM yes; above 0x1000 0600 only no n/a

Read Memory no no n/a

Prepare sectors for write operation yes yes n/a

Copy RAM to flash yes; not to sector 0 no n/a

Go no no n/a

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 27 of 515

ISP mode allowed)

Page 28

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

Table 16. ISP commands allowed for different CRP levels

ISP command CRP1 CRP2 CRP3 (no entry in

ISP mode allowed)

Erase sector(s) yes; sector 0 can only be erased when all

sectors are erased.

Erase page(s) yes; page 0 can only be erased when all

pages are erased (not recommended, use

Erase Sector).

Blank check sectors no no n/a

Read Part ID yes yes n/a

Read Boot code version yes yes n/a

Compare no no n/a

ReadUID yes yes n/a

Read CRC no no n/a

Read flash signature yes (full range of the flash only) no n/a

Read/Write FAIM page yes yes n/a

yes; all sectors only n/a

yes; all pages only n/a

5.5.1 Unlock

Table 17. USART ISP Unlock command

Command U

Input Unlock code: 23130

Return Code CMD_SUCCESS |

INVALID_CODE |

PARAM_ERROR

Description This command is used to unlock Flash Write, Erase, and Go commands.

Example "U 23130<CR><LF>" unlocks the Flash Write/Erase & Go commands.

10

5.5.2 Set Baud Rate

Table 18. USART ISP Set Baud Rate command

Command B

Input Baud Rate, FAIM configuration dependant: 9600 | 19200 | 38400 | 57600 | 115200 | 230400 | 460800

Stop bit: 1 | 2

Return Code CMD_SUCCESS |

INVALID_BAUD_RATE |

INVALID_STOP_BIT |

PARAM_ERROR

Description This command is used to change the baud rate. The new baud rate is effective after the command handler

sends the CMD_SUCCESS return code.

Example "B 57600 1<CR><LF>" sets the serial port to baud rate 57600 bps and 1 stop bit.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 28 of 515

Page 29

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

5.5.3 Echo

Table 19. USART ISP Echo command

Command A

Input Setting: ON = 1 | OFF = 0

Return Code CMD_SUCCESS |

PARAM_ERROR

Description The default setting for echo command is ON. When ON the ISP command handler sends the received serial

data back to the host.

Example "A 0<CR><LF>" turns echo off.

5.5.4 Write to RAM

The host should send the plain binary code after receiving the CMD_SUCCESS return

code. This ISP command handler responds with “OK<CR><LF>” when the transfer has

finished.

Table 20. USART ISP Write to RAM command

Command W

Input Start Address: RAM address where data bytes are to be written. This address should be a word boundary.

Number of Bytes: Number of bytes to be written. Count should be a multiple of 4

Return Code CMD_SUCCESS |

ADDR_ERROR (Address not on word boundary) |

ADDR_NOT_MAPPED |

COUNT_ERROR (Byte count is not multiple of 4) |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to download data to RAM. This command is blocked when code read protection

levels 2 or 3 are enabled. Writing to addresses below 0x1000 0600 is disabled for CRP1.

Example "W 268437504 4<CR><LF>" writes 4 bytes of data to address 0x1000 0800.

5.5.5 Read Memory

Reads the plain binary code of the data stream, followed by the CMD_SUCCESS return

code.

Table 21. USART ISP Read Memory command

Command R

Input Start Address: Address from where data bytes are to be read. This address should be a word boundary.

Number of Bytes: Number of bytes to be read. Count should be a multiple of 4.

Return Code CMD_SUCCESS followed by <actual data (plain binary)> |

ADDR_ERROR (Address not on word boundary) |

ADDR_NOT_MAPPED |

COUNT_ERROR (Byte count is not a multiple of 4) |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to read data from RAM or flash memory. This command is blocked when code read

protection is enabled.

Example "R 268437504 4<CR><LF>" reads 4 bytes of data from address 0x1000 0800.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 29 of 515

Page 30

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

5.5.6 Prepare sectors for write operation

This command makes flash write/erase operation a two-step process.

Table 22. USART ISP Prepare sectors for write operation command

Command P

Input Star t Sec t o r Num b er

End Sector Number: Should be greater than or equal to start sector number.

Return Code CMD_SUCCESS |

BUSY |

INVALID_SECTOR |

PARAM_ERROR

Description This command must be executed before executing "Copy RAM to flash" or "Erase Sector(s)", or “Erase

Pages” command. Successful execution of the "Copy RAM to flash" or "Erase Sector(s)" or “Erase Pages”

command causes relevant sectors to be protected again. To prepare a single sector use the same "Start"

and "End" sector numbers.

Example "P 0 0<CR><LF>" prepares the flash sector 0.

5.5.7 Copy RAM to flash

When writing to the flash, the following limitations apply:

1. The smallest amount of data that can be written to flash by the copy RAM to flash

command is 64 byte (equal to one page).

2. One page consists of 16 flash words (lines), and the smallest amount that can be

modified per flash write is one flash word (one line). This limitation exists because

ECC is applied during the flash write operation, see Section 5.3.3

.

3. To avoid write disturbance (a mechanism intrinsic to flash memories), an erase

should be performed after 16 consecutive writes inside the same page. Note that the

erase operation then erases the entire sector.

Remark: Once a page has been written to 16 times, it is still possible to write to other

pages within the same sector without performing a sector erase (assuming that those

pages have been erased previously).

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 30 of 515

Page 31

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

Table 23. USART ISP Copy command

Command C

Input Flash Address(DST): Destination flash address where data bytes are to be written. The destination address

should be a 64 byte boundary.

RAM Address(SRC): Source RAM address from where data bytes are to be read.

Number of Bytes: Number of bytes to be written. Should be 64 | 128 | 256 | 512 | 1024

Return Code CMD_SUCCESS |

SRC_ADDR_ERROR (Address not on word boundary) |

DST_ADDR_ERROR (Address not on correct boundary) |

SRC_ADDR_NOT_MAPPED |

DST_ADDR_NOT_MAPPED |

COUNT_ERROR (Byte count is not 64 | 128 | 256 | 512 | 1024) |

SECTOR_NOT_PREPARED_FOR WRITE_OPERATION |

BUSY |

CMD_LOCKED |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to program the flash memory. The "Prepare Sector(s) for Write Operation" command

should precede this command. The affected sectors are automatically protected again once the copy

command is successfully executed. This command is blocked when code read protection is enabled. Also see

Section 5.3.3

for the number of bytes that can be written.

Example "C 0 268437504 512<CR><LF>" copies 512 bytes from the RAM address 0x1000 0800 to the flash address

0.

5.5.8 Go

Table 24. USART ISP Go command

Command G

Input Address: Flash or RAM address from which the code execution is to be started. This address should be on

a word boundary.

Mode: T (Execute program in Thumb Mode) |

Return Code CMD_SUCCESS |

ADDR_ERROR |

ADDR_NOT_MAPPED |

CMD_LOCKED |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to execute a program residing in RAM or flash memory. It may not be possible to

return to the ISP command handler once this command is successfully executed. This command is blocked

when code read protection is enabled.

Example "G 0 T<CR><LF>" branches to address 0x0000 0000 in Thumb mode only.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 31 of 515

Page 32

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

5.5.9 Erase sectors

Table 25. USART ISP Erase sector command

Command E

Input Star t Sec t o r Num b er

End Sector Number: Should be greater than or equal to start sector number.

Return Code CMD_SUCCESS |

BUSY |

INVALID_SECTOR |

SECTOR_NOT_PREPARED_FOR_WRITE_OPERATION |

CMD_LOCKED |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to erase one or more sector(s) of on-chip flash memory. This command only allows

erasure of all user sectors when the code read protection is enabled.

Example "E 2 3<CR><LF>" erases the flash sectors 2 and 3.

5.5.10 Erase pages

Table 26. USART ISP Erase page command

Command X

Input Star t Page Number

End Page Number: Should be greater than or equal to start page number.

Return Code CMD_SUCCESS |

BUSY |

INVA L I D _ PAGE |

SECTOR_NOT_PREPARED_FOR_WRITE_OPERATION |

CMD_LOCKED |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to erase one or more page(s) of on-chip flash memory.

Example "X 2 3<CR><LF>" erases the flash pages 2 and 3.

5.5.11 Blank check sectors

Table 27. USART ISP Blank check sector command

Command I

Input Star t Sec t o r Num b er :

End Sector Number: Should be greater than or equal to start sector number.

Return Code CMD_SUCCESS |

SECTOR_NOT_BLANK (followed by <Offset of the first non blank word location> <Contents of non blank

word location>) |

INVALID_SECTOR |

PARAM_ERROR

Description This command is used to blank check one or more sectors of on-chip flash memory.

Example "I 2 3<CR><LF>" blank checks the flash sectors 2 and 3.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 32 of 515

Page 33

NXP Semiconductors

5.5.12 Read Part Identification number

Table 28. USART ISP Read Part Identification command

Command J

Input None.

Return Code CMD_SUCCESS followed by part identification number (see Ta bl e 2 9

Description This command is used to read the part identification number.

Table 29. LPC84x device ID register values

Part number Part ID

LPC844M201JBD48 0x00008442

LPC844M201JBD64 0x00008441

LPC844M201JHI33 0x00008444

LPC844M201JHI48 0x00008442

LPC845M301JBD48 0x00008452

LPC845M301JBD64 0x00008451

LPC845M301JHI33 0x00008454

LPC845M301JHI48 0x00008453

UM11029

Chapter 5: LPC84x ISP and IAP

).

5.5.13 Read Boot code version number

Table 30. USART ISP Read Boot Code version number command

Command K

Input None

Return Code CMD_SUCCESS followed by 2 bytes of boot code version number in ASCII format. It is to be interpreted as

<byte1(Major)>.<byte0(Minor)>.

Description This command is used to read the boot code version number.

5.5.14 Compare

Table 31. USART ISP Compare command

Command M

Input Address1 (DST): Starting flash or RAM address of data bytes to be compared. This address should be a

word boundary.

Address2 (SRC): Starting flash or RAM address of data bytes to be compared. This address should be a

word boundary.

Number of Bytes: Number of bytes to be compared; should be a multiple of 4.

Return Code CMD_SUCCESS | (Source and destination data are equal) |

COMPARE_ERROR | (Followed by the offset of first mismatch) |

COUNT_ERROR (Byte count is not a multiple of 4) |

ADDR_ERROR |

ADDR_NOT_MAPPED |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to compare the memory contents at two locations.

Example "M 8192 268437504 4<CR><LF>" compares 4 bytes from the RAM address 0x1000 0800 to the 4 bytes

from the flash address 0x2000.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 33 of 515

Page 34

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

5.5.15 ReadUID

Table 32. USART ReadUID command

Command N

Input None

Return Code CMD_SUCCESS followed by four 32-bit words of a unique serial number in ASCII format. The word sent at

the lowest address is sent first.

Description This command is used to read the unique ID.

5.5.16 Read CRC checksum

Get the CRC checksum of a block of RAM or flash. CMD_SUCCESS followed by 8 bytes

of CRC checksum in decimal format.

The checksum is calculated as follows:

CRC-32 polynomial: x32 + x26 + x23 + x22 + x16 + x12 + x11 + x10 + x8 + x7 + x5 + x4 +

x2 + x + 1

Seed Value: 0xFFFF FFFF

Table 33. USART ISP Read CRC checksum command

Command S

Input Address: The data are read from this address for CRC checksum calculation. This address must be on a

word boundary.

Number of Bytes: Number of bytes to be calculated for the CRC checksum; must be a multiple of 4.

Return Code CMD_SUCCESS followed by data in decimal format |

ADDR_ERROR (address not on word boundary) |

ADDR_NOT_MAPPED |

COUNT_ERROR (byte count is not a multiple of 4) |

PARAM_ERROR |

CODE_READ_PROTECTION_ENABLED

Description This command is used to read the CRC checksum of a block of RAM or flash memory. This command is

blocked when code read protection is enabled.

Example "S 33587200 4<CR><LF>" reads the CRC checksum for 4 bytes of data from address 0x0200 8000.

If checksum value is 0xCBF43926, then the host will receive:

"3421780262 <CR><LF>"

5.5.17 Read flash signature

Get the signature for the flash memory, using an internal flash signature generator (see

Chapter 6 “

signature of the entire flash can be read and no parameters can be passed.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 34 of 515

LPC84x Flash signature generator”). When CRP1 is enabled, only the

Page 35

NXP Semiconductors

Chapter 5: LPC84x ISP and IAP

Table 34. USART ISP Read flash signature command

Command Z

Input Star t address: Start of flash address.

Default = 0.

Must be 0 when CRP1 is enabled.

End address: End of flash address.

Default = 0xFFFF

Must be 0xFFFF when CRP1 is enabled.

Number of wait states: Number of wait states.

Default = 2.

Mode: Flash controller mode must pass value 0.

Return Code CMD_SUCCESS followed by 32 bit flash signature in decimal format |

When CRP1 is enabled the signature is read for the entire flash |

ADDR_NOT_MAPPED |

PARAM_ERROR

Description This command is used to read the flash signature generated by the flash controller.

Example "Z<CR><LF>" reads the signature of the entire flash generated by the flash controller.

UM11029

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 35 of 515

Page 36

NXP Semiconductors

5.5.18 Read/write FAIM page

This command is used to read/write FAIM page.

Table 35. USART ISP Read/Write FAIM Page command

Command O

Input FAIM access:

0 = FAIM Page read

1 = FAIM Page write

FAIM page number: 0 - 7

FAIM configuration value: user defined (if FAIM access is page write)

Return Code CMD_SUCCESS |

PARAM_ERROR |

INVALID_COMMAND |

INVA LID_PA GE

Description This command is used to read/write FAIM page

Example "O 0 5<CR><LF>" reads the FAIM page 5.

“O 1 7<CR><LF>” initiates a write to FAIM page 7. When the system is ready to receive the data it responds

with 0<CR><LF> [CMD_SUCCESS]. The host should send a raw binary data of 4 bytes. FAIM programming

starts when the fourth byte is received and the ISP command responds with 0<CR><LF> [CMD_SUCCESS]

error code after the programming is completed successfully.

UM11029

Chapter 5: LPC84x ISP and IAP

5.5.19 ISP/IAP Error codes

These error codes are located in the error.h file.

Table 36. ISP/IAP Error codes

Return

Code

0x0 CMD_SUCCESS Command is executed successfully. Sent by ISP handler only when

0x1 INVALID_COMMAND Invalid command.

0x2 SRC_ADDR_ERROR Source address is not on word boundary.

0x3 DST_ADDR_ERROR Destination address is not on a correct boundary.

0x4 SRC_ADDR_NOT_MAPPED Source address is not mapped in the memory map. Count value is

0x5 DST_ADDR_NOT_MAPPED Destination address is not mapped in the memory map. Count value is

0x6 COUNT_ERROR Byte count is not multiple of 4 or is not a permitted value.

0x7 INVALID_SECTOR/INVALID_PAGE Sector/page number is invalid or end sector number is greater than

0x8 SECTOR_NOT_BLANK Sector is not blank.

0x9 SECTOR_NOT_PREPARED_

0xA COMPARE_ERROR Source and destination data not equal.

0xB BUSY Flash programming hardware interface is busy.

0xC PARAM_ERROR Insufficient number of parameters or invalid parameter.

0xD ADDR_ERROR Address is not on word boundary.

Error code Description

FOR_WRITE_OPERATION

command given by the host has been completely and successfully

executed.

taken into consideration where applicable.

taken into consideration where applicable.

start sector number.

Command to prepare sector for write operation was not executed.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 36 of 515

Page 37

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

Table 36. ISP/IAP Error codes

Return

Code

0xE ADDR_NOT_MAPPED Address is not mapped in the memory map. Count value is taken into

0xF CMD_LOCKED Command is locked.

0x10 INVALID_CODE Unlock code is invalid.

0x11 INVALID_BAUD_RATE Invalid baud rate setting.

0x12 INVALID_STOP_BIT Invalid stop bit setting.

0x13 CODE_READ_

0x14 - Reserved.

0x15 USER_CODE_CHECKSUM User code checksum is invalid.

0x16 - Reserved.

0x17 EFRO_NO_POWER FRO not turned on in the PDRUNCFG register.

0x18 FLASH_NO_POWER Flash not turned on in the PDRUNCFG register.

0x19 - Reserved.

0x1A - Reserved.

0x1B FLASH_NO_CLOCK Flash clock disabled in the AHBCLKCTRL register.

0x1C REINVOKE_ISP_CONFIG Reinvoke ISP not successful.

0x1D NO_VALID_IMAGE Invalid image

0x1E FAIM_NO_POWER FAIM not turned on in the PDRUNCFG register.

0x1F FAIM_NO_CLOCK FAIM clock disabled in the AHBCLKCTRL register.

Error code Description

consideration where applicable.

Code read protection enabled.

PROTECTION_ENABLED

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 37 of 515

Page 38

NXP Semiconductors

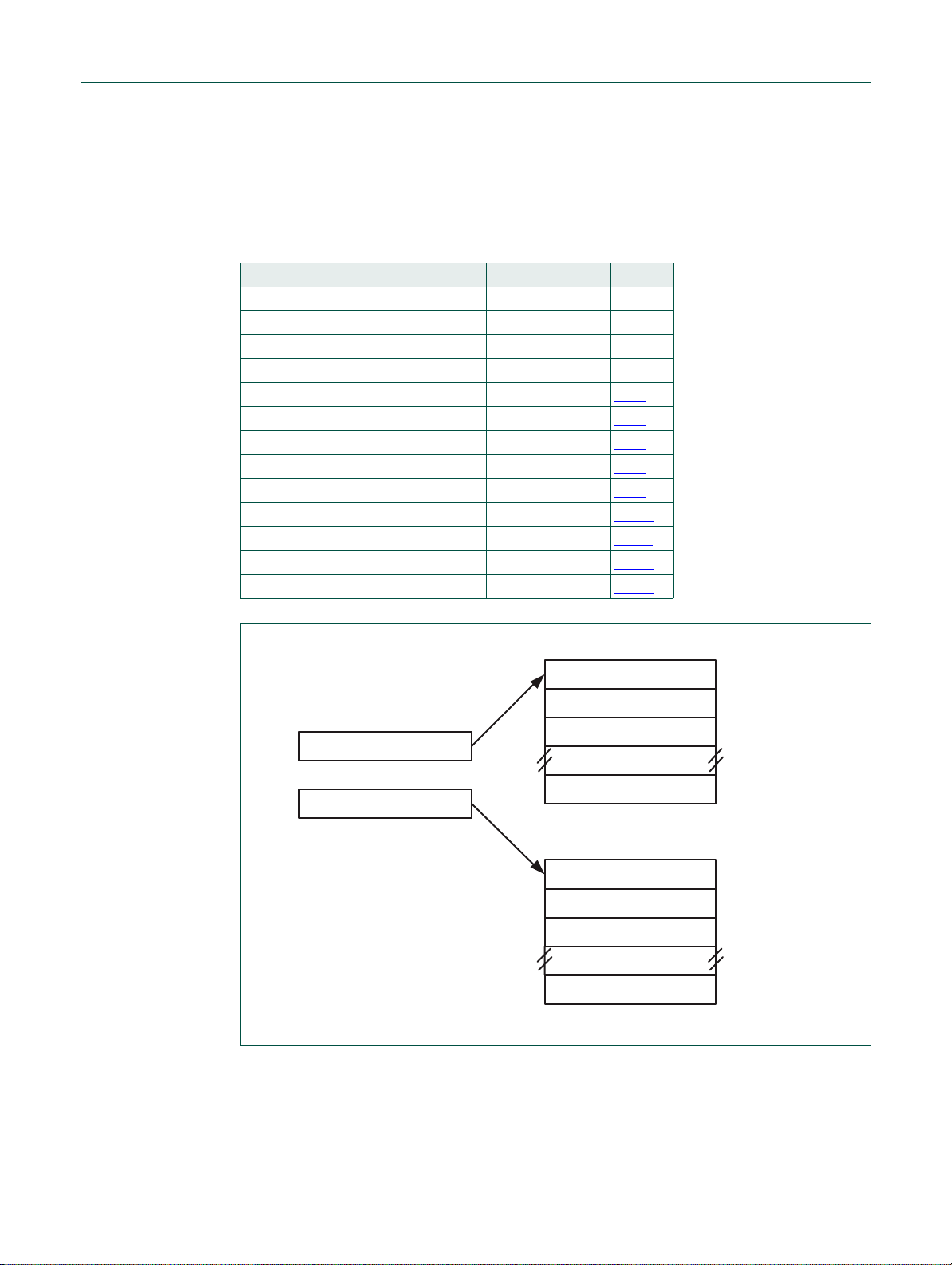

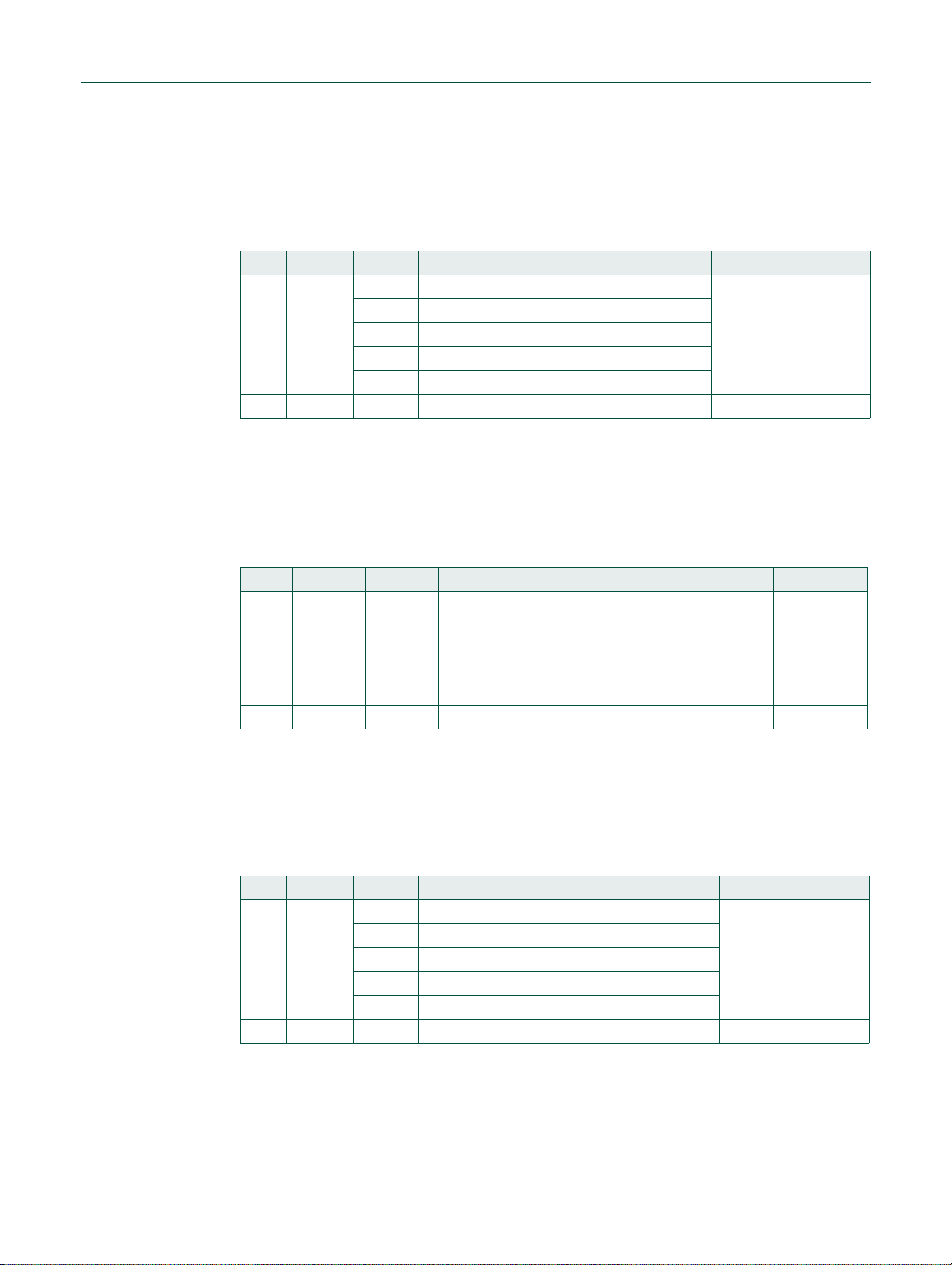

5.6 IAP commands

For in application programming the IAP routine should be called with a word pointer in

register r0 pointing to memory (RAM) containing command code and parameters. The

result of the IAP command is returned in the result table pointed to by register r1. The user

can reuse the command table for result by passing the same pointer in registers r0 and r1.

The parameter table should be big enough to hold all the results in case the number of

results are more than number of parameters. Parameter passing is illustrated in the

Figure 5

The number of parameters and results vary according to the IAP command. The

maximum number of parameters is 5, passed to the "Copy RAM to FLASH" command.

The maximum number of results is 5, returned by the "ReadUID" command. The

command handler sends the status code INVALID_COMMAND when an undefined

command is received. The IAP routine resides at location 0x0F001FF0 and it is thumb

code, therefore called as 0x0F001FF1 by the Cortex-M4 to insure Thumb operation.

The IAP function could be called in the following way using C:

Define the IAP location entry point. Since the least significant bit of the IAP location is set

there will be a change to Thumb instruction set if called by the Cortex-M4.

UM11029

Chapter 5: LPC84x ISP and IAP

.

Define data structure or pointers to pass IAP command table and result table to the IAP

function:

unsigned int command_param[5];

unsigned int status_result[5];

or

unsigned int * command_param;

unsigned int * status_result;

command_param = (unsigned int *) 0x...

status_result =(unsigned int *) 0x...

Define pointer to function type, which takes two parameters and returns void. Note the IAP

returns the result with the base address of the table residing in R1.

typedef void (*IAP)(unsigned int [],unsigned int[]);

IAP iap_entry;

Setting the function pointer:

#define IAP_LOCATION *(volatile unsigned int *)(0x0F001FF1)

iap_entry=(IAP) IAP_LOCATION;

To call the IAP use the following statement.

iap_entry (command_param,status_result);

Up to 4 parameters can be passed in the r0, r1, r2 and r3 registers respectively (see the

ARM Thumb Procedure Call Standard SWS ESPC 0002 A-05). Additional parameters are

passed on the stack. Up to 4 parameters can be returned in the r0, r1, r2 and r3 registers

respectively. Additional parameters are returned indirectly via memory.

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 38 of 515

Page 39

NXP Semiconductors

&RPPDQGFRGH

3DUDP

3DUDP

3DUDPQ

VWDWXVBUHVXOW>@

VWDWXVBUHVXOW>@

6WDWXVFRGH

5HVXOW

5HVXOW

5HVXOWQ

&RPPDQG3DUDPHWHU$UUD\

6WDWXV5HVXOW$UUD\

$505(*,67(5U

$505(*,67(5U

FRPPDQGBSDUDP>@

FRPPDQGBSDUDP>@

FRPPDQGBSDUDP>@

FRPPDQGBSDUDP>Q@

VWDWXVBUHVXOW>@

VWDWXVBUHVXOW>Q@

The flash memory is not accessible during a write or erase operation. IAP commands,

which results in a flash write/erase operation, use 32 bytes of space in the top portion of

the on-chip RAM for execution. The user program should not be use this space if IAP flash

programming is permitted in the application.

T able 37. IAP Command Summary

IAP Command Command code Section

Prepare sector(s) for write operation 50 (decimal) 5.6.1

Copy RAM to flash 51 (decimal) 5.6.2

Erase sector(s) 52 (decimal) 5.6.3

Blank check sector(s) 53 (decimal) 5.6.4

Read Part ID 54 (decimal) 5.6.5

Read Boot code version 55 (decimal) 5.6.6

Compare 56 (decimal) 5.6.7

Reinvoke ISP 57 (decimal) 5.6.8

Read UID 58 (decimal) 5.6.9

Erase page(s) 59 (decimal) 5.6.10

Read Signature 73 (decimal) 5.6.11

Read FAIM Page 80 (decimal) 5.6.12

Write FAIM Page 81 (decimal) 5.6.13

UM11029

Chapter 5: LPC84x ISP and IAP

Fig 5. IAP parameter passing

UM11029 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2017. All rights reserved.

User manual Rev. 1.0 — 16 June 2017 39 of 515

Page 40

NXP Semiconductors

UM11029

Chapter 5: LPC84x ISP and IAP

5.6.1 Prepare sector(s) for write operation

This command makes flash write/erase operation a two step process.

Table 38. IAP Prepare sector(s) for write operation command

Command Pr epare sector(s) for write operation

Input Command code: 50 (decimal)

Param0: Start Sector Number

Param1: End Sector Number (should be greater than or equal to start sector number).

Status code CMD_SUCCESS |

BUSY |

INVALID_SECTOR

Result None

Description This command must be executed before executing "Copy RAM to flash" or "Erase Sector(s)" or “Erase

page(s)” command. Successful execution of the "Copy RAM to flash" or "Erase Sector(s)" or “Erase page(s)”

command causes relevant sectors to be protected again. To prepare a single sector use the same "Start" and

"End" sector numbers.

5.6.2 Copy RAM to flash

See Section 5.5.7 for limitations on the write-to-flash process.

Table 39. IAP Copy RAM to flash command

Command Copy RAM to flash

Input Command code: 51 (decimal)

Param0(DST): Destination flash address where data bytes are to be written. This address should be a 64

byte boundary.

Param1(SRC): Source RAM address from which data bytes are to be read. This address should be a word

boundary.

Param2: Number of bytes to be written. Should be 64 | 128 | 256 | 512 | 1024.

Param3: System Clock Frequency (CCLK) in kHz.

Status code CMD_SUCCESS |

SRC_ADDR_ERROR (Address not a word boundary) |

DST_ADDR_ERROR (Address not on correct boundary) |

SRC_ADDR_NOT_MAPPED |

DST_ADDR_NOT_MAPPED |

COUNT_ERROR (Byte count is not 64 | 128 | 256 | 512 | 1024) |

SECTOR_NOT_PREPARED_FOR_WRITE_OPERATION |

BUSY

Result None

Description This command is used to program the flash memory. The affected sectors should be prepared first by calling

"Prepare Sector for Write Operation" command. The affected sectors are automatically protected again once

the copy command is successfully executed. Also see Section 5.3.3

written.

Remark: All user code must be written in such a way that no master accesses the flash while this command

is executed and the flash is programmed.

for the number of bytes that can be