Page 1

UM10237

LPC24XX User manual

Rev. 02 — 19 December 2008 User manual

Document information

Info Content

Keywords LPC2400, LPC2458, LPC2420, LPC2460, LPC2468, LPC2470, LPC2478,

ARM, ARM7, 32-bit, Single-chip, External memory interface, USB 2.0,

Device, Host, OTG, Ethernet, CAN, I2S, I2C, SPI, UART, PWM, IRC,

Microcontroller

Abstract LPC24XX User manual release

Page 2

NXP Semiconductors

UM10237

LPC24XX User manual

Revision history

Rev Date Description

02 20081219 LPC24XX user manual release.

Modifications:

• Added parts LPC2420.

• Editorial updates.

• AHB1 and AHB2 configuration registers added.

01 20080718 Initial LPC24XX user manual release. Replaces all draft versions UM10237_1.00 to

UM10237_1.05.

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 2 of 792

Page 3

1. Introduction

UM10237

Chapter 1: LPC24XX Introductory information

Rev. 02 — 19 December 2008 User manual

NXP Semiconductor designed the LPC2400 microcontrollers around a 16-bit/32-bit

ARM7TDMI-S CPU core with real-time debug interfaces that include both JTAG and

embedded Trace. The LPC2400 microcontrollers have 512 kB of on-chip high-speed

Flash memory. This Flash memory includes a special 128-bit wide memory interface and

accelerator architecture that enables the CPU to execute sequential instructions from

Flash memory at the maximum 72 MHz system clock rate. This feature is available only

on the LPC2000 ARM Microcontroller family of products. The LPC2400 can execute both

32-bit ARM and 16-bit Thumb instructions. Support for the two Instruction Sets means

Engineers can choose to optimize their application for either performance or code size at

the sub-routine level. When the core executes instructions in Thumb state it can reduce

code size by more than 30 % with only a small loss in performance while executing

instructions in ARM state maximizes core performance.

The LPC2400 microcontrollers are ideal for multi-purpose communication applications. It

incorporates a 10/100 Ethernet Media Access Controller (MAC), a USB full speed

device/host/OTG controller with 4 kB of endpoint RAM, four UARTs, two Controller Area

Network (CAN) channels, an SPI interface, two Synchronous Serial Ports (SSP), three I

interfaces, and an I

interfaces are the following feature components; an on-chip 4 MHz internal precision

oscillator, 98 kB of total RAM consisting of 64 kB of local SRAM, 16 kB SRAM for

Ethernet, 16 kB SRAM for general purpose DMA, 2 kB of battery powered SRAM, and an

External Memory Controller (EMC). These features make this device optimally suited for

communication gateways and protocol converters. Complementing the many serial

communication controllers, versatile clocking capabilities, and memory features are

various 32-bit timers, an improved 10-bit ADC, 10-bit DAC, two PWM units, four external

interrupt pins, and up to 160 fast GPIO lines. The LPC2400 connect 64 of the GPIO pins

to the hardware based Vector Interrupt Controller (VIC) that means these external inputs

can generate edge-triggered, interrupt s. All of these features make the LPC2400

particularly suitable for industrial control and medical systems.

2. How to read this manual

Important: The term “LPC24XX“ in this user manual will be used as a generic name for all

LPC2400 parts. It covers the following parts: LPC2458, LPC2420, LPC2460, LPC2468,

LPC2470, and LPC2478.

2

S interface. Supporting this collection of serial communications

2

C

For information about individual parts refer to Table 1–1

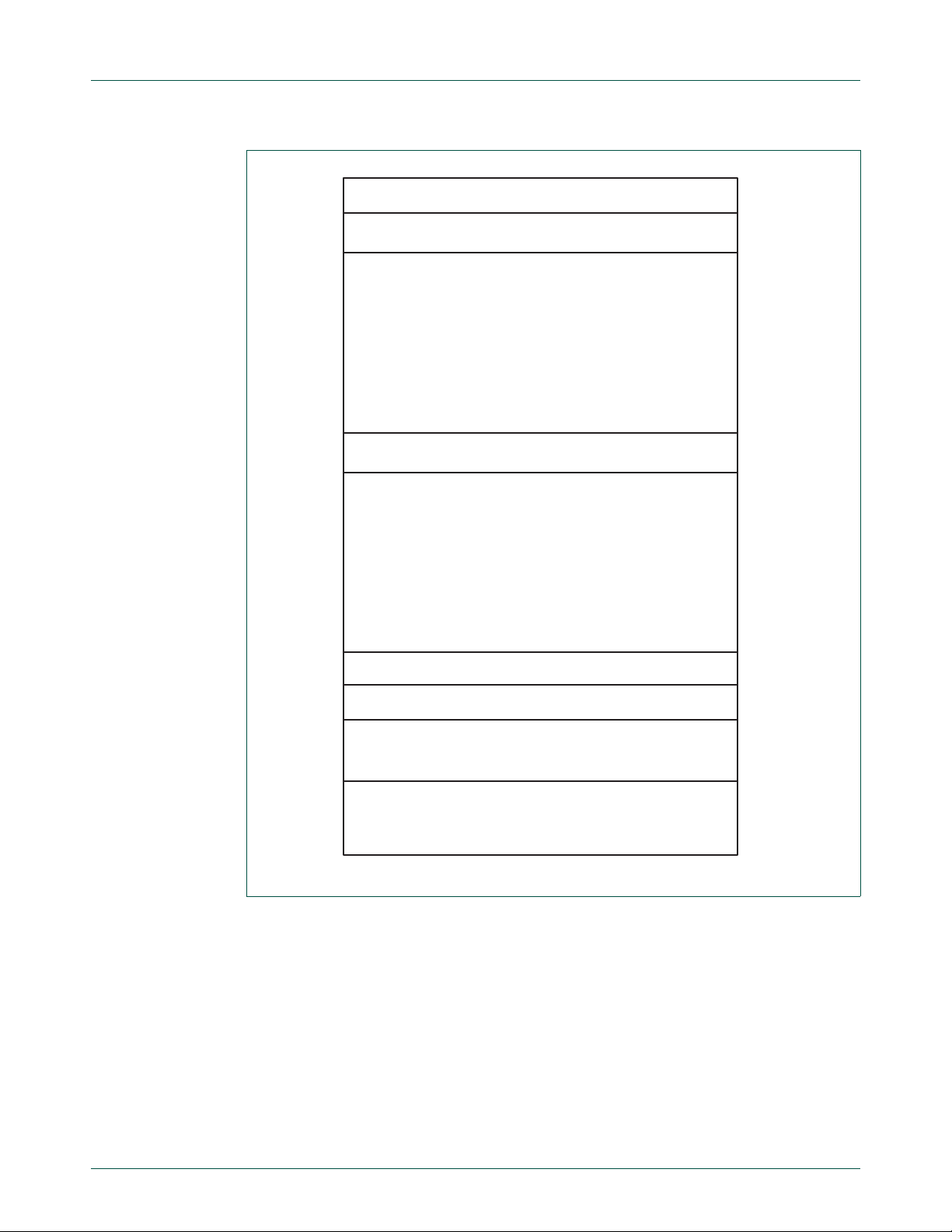

Table 1. LPC24XX overview

LPC2458 LPC2420/60 LPC2468 LPC2470 LPC2478

Features Section 1–3

Ordering options Section 1–5.1 Section 1–5.2 Section 1–5.3 Section 1–5.4 Section 1–5.5

Block diagrams Section 1–9 Section 1–10 Section 1–11 Section 1–12 Section 1–13

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 3 of 792

Section 1–3 Section 1–3 Section 1–3 Section 1–3

and Table 1–2.

Page 4

NXP Semiconductors

Most features and peripherals are identical for all LPC2400 parts. All differences are listed

in Table 1–2

T able 2. Differences between LPC2400 parts

LPC2458 180/136 512 kB 16-bit no

LPC2460/20 208/160 flashless 32-bit no

LPC2468 208/160 512 kB 32-bit no

LPC2470 208/160 flashless 32-bit yes

LPC2478 208/160 512 kB 32-bit yes

3. LPC2400 features

• ARM7TDMI-S processor, running at up to 72 MHz.

• 98 kB on-chip SRAM includes:

– 64 kB of SRAM on the ARM local bus for high performance CPU access.

– 16 kB SRAM for Ethernet interface. Can also be used as general purpose SRAM.

– 16 kB SRAM for general purpose DMA use also accessible by the USB.

– 2 kB SRAM data storage powered from the RTC power domain.

• LPC2458/68/78 only: 512 kB on-chip Flash program memory with In-System

Programming (ISP) and In-Application Programming (IAP) capabilities. Flash program

memory is on the ARM local bus for high performance CPU access.

• Dual Advanced High-performance Bus (AHB) system allows memory access by

multiple resources and simultaneous program execution with no contention.

• EMC provides support for asynchronous static memory devices such as RAM, ROM

and Flash, as well as dynamic memories such as Single Data Rate SDRAM.

• Advanced Vectored Inter rupt Controller ( VIC), supportin g up to 32 vectored interru pt s.

• General Purpose AHB DMA controller (GPDMA) that can be used with the SSP, I

and SD/MM interface as well as for memory-to-memory transfers.

• LPC2470/78 only: LCD controller , sup porting both Super-Twisted Nematic (STN) and

Thin-Film Transistors (TFT) displays.

– Dedicated DMA controller.

– Selectable display resolution (up to 1024 × 768 pixels).

– Supports up to 24-bit true-color mode.

• Serial Interfaces:

– Ethernet MAC with MII/RMII interface and associated DMA controller. These

functions reside on an independent AHB bus.

– USB 2.0 full-speed dual port device/host/OTG controller with on-chip PHY and

associated DMA controller.

– Four UARTs with fractional baud rate generation, one with modem contro l I/O, one

with IrDA support, all with FIFO.

– CAN controller with two channels.

.

Pins/

High-speed

GPIO pins

UM10237

Chapter 1: LPC24XX Introductory information

Flash EMC LCD

2

S,

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 4 of 792

Page 5

NXP Semiconductors

• Other peripherals:

• Standard ARM test/debug interface for compatibility with existing tools.

• Emulation trace module supports real-time trace.

• Single 3.3 V power supply (3.0 V to 3.6 V).

• Three reduced power modes: idle, sleep, and power-down.

• Four external interrupt inputs configurable as edge/level sen sitive. All pins on POR T0

• Processor wake-up from Power-down mode via any interrupt able to operate during

• Two independent power domains allow fine tuning of power consumption based on

• Each peripheral has its own clock divider for further power saving. These dividers help

• Brownout detect with separate thresholds for interrupt and forced reset.

• On-chip power-on reset.

• On-chip crystal oscillator with an operating range of 1 MHz to 24 MHz.

• 4 MHz internal RC oscillator trimmed to 1 % ac curacy that can optionally be used as

• On-chip PLL allows CPU operation up to the maximum CPU rate without the need for

UM10237

Chapter 1: LPC24XX Introductory information

– SPI controller.

– Two SSP controllers, with FIFO and multi-protocol capabilities. One is an alternate

for the SPI port, sharing its interrupt. SSPs can be used with the GPDMA

controller.

2

– Three I

2

– I

the GPDMA.

– SD/MMC memory card interface.

– 160 general purpose I/O pins with configurable pull-up/down resistors.

– 10-bit ADC with input multiplexing among 8 pins.

– 10-bit DAC.

– Four general purpose timers/counters with 8 capture inputs and 10 compare

outputs. Each timer block has an external count input.

– Two PWM/timer blocks with support for three-phase motor control. Each PWM has

an external count inputs.

– Real-Time Clock (RTC) with separate power domain, clock source can be the RTC

oscillator or the APB clock.

– 2 kB SRAM powered from the RTC power pin, allowing data to be stored when the

rest of the chip is powered off.

– WatchDog Timer (WDT). The WDT can be clocked from the internal RC oscillator,

the RTC oscillator, or the APB clock.

and PORT2 can be used as edge sensitive interrupt sources.

Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet

wake-up interrupt, CAN bus activity, PORT0/2 pin interrupt).

needed features.

reducing active power by 20 - 30 %.

the system clock. When used as the CPU clock, does not allow CAN and USB to run.

a high frequency crystal. May be run from the main oscillator, the internal RC

oscillator, or the RTC oscillator.

C-bus interfaces (one with open-drain and two with standard port pins).

S (Inter-IC Sound) interface for digital audio input or output. It can be used with

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 5 of 792

Page 6

NXP Semiconductors

UM10237

Chapter 1: LPC24XX Introductory information

• Boundary scan for simplified board testing.

• Versatile pin function selections allow more possibilities for using on-chip peripheral

functions.

4. Applications

• Industrial control

• Medical systems

• Protocol converter

• Communications

5. Ordering options

5.1 LPC2458 ordering options

Table 3. LPC2458 ordering information

Type number Package

LPC2458FET180 TFBGA180 plastic thin fine-pitch ball grid array package; 180 balls; body 12 x 12 x 0.8 mm SOT570-2

Name Description Version

(kB)

SRAM (kB) External

bus

Local bus

Ethernet buffer

GP/USB

RTC

Total

Ethernet USB

OTG/

OHC/

DEV

+4kB

FIFO

yes 2 yes yes 8 1 −40 °C to

RMII

SD/

MMC

CAN channels

GP

DMA

Temp

range

ADC channels

DAC channels

+85 °C

Table 4. LPC2458 ordering options

Type number Flash

LPC2458FET180 512 64 16 16 2 98 16-bit MII/

5.2 LPC2460 ordering options

Table 5. LPC2420/60 ordering information

Type number Package

LPC2420FBD208 LQFP208 plastic low profil e quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC2460FBD208 LQFP208 plastic low profil e quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC2460FET208 TFBGA208 plastic thin fine-pitch ball grid array package; 208 balls; body 15 × 15 × 0.7 mm SOT950-1

Name Description Version

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 6 of 792

Page 7

NXP Semiconductors

UM10237

Chapter 1: LPC24XX Introductory information

(kB)

SRAM (kB) External

bus

Ethernet USB

OTG/

SD/

MMC

GP

DMA

Temp

range

Table 6. LPC2420/60 ordering options

Type number Flash

OHCI/

DEV

+4kB

FIFO

Local bus

Ethernet buffer

GP/USB

RTC

Total

CAN channels

ADC channels

DAC channels

LPC2420FBD208 N/A 64 - 16 2 82 Full 32-bit - yes - yes yes 8 1 −40 °C to

+85 °C

LPC2460FBD208 N/A 64 16 16 2 98 Full 32-bit MII/RMII yes 2 yes yes 8 1 −40 °C to

+85 °C

LPC2460FET208 N/A 64 16 16 2 98 Full 32-bit MII/RMII yes 2 yes yes 8 1 −40 °C to

+85 °C

5.3 LPC2468 ordering options

Table 7. LPC2468 ordering information

Type number Package

LPC2468FBD208 LQFP208 plastic low profil e quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC2468FET208 TFBGA208 plastic thin fine-pitch ball grid array package; 208 balls; body 15 x 15 x 0.7 mm SOT950-1

Name Description Version

(kB)

SRAM (kB) External

bus

Ethernet USB

OTG/

SD/

MMC

GP

DMA

Temp

range

Table 8. LPC2468 ordering options

Type number Flash

OHC/

DEV

+ 4 kB

FIFO

Local bus

Ethernet buffer

GP/USB

RTC

Total

LPC2468FBD208 512 64 16 16 2 98 Full 32-bi t MII/

RMII

LPC2468FET208 512 64 16 16 2 98 Full 32-bit MII/

RMII

CAN channels

yes 2 yes yes 8 1 −40 °C to

yes 2 yes yes 8 1 −40 °C to

ADC channels

DAC channels

+85 °C

+85 °C

5.4 LPC2470 ordering options

Table 9. LPC2470 ordering information

Type number Package

LPC2470FBD208 LQFP208 plastic low profil e quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC2470FET208 TFBGA208 plastic thin fine-pitch ball grid array package; 208 balls; body 15 × 15 ×

Name Description Version

SOT950-1

0.7 mm

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 7 of 792

Page 8

NXP Semiconductors

UM10237

Chapter 1: LPC24XX Introductory information

(kB)

SRAM (kB) External

Local bus

Ethernet buffer

GP/USB

RTC

bus

Total

32-bit

32-bit

Ethernet USB

OTG/

OHC/

Device

+ 4 kB

FIFO

MII/RMII yes 2 yes yes 8 1 −40 °C

MII/RMII yes 2 yes yes 8 1 −40 °C

SD/

MMC

CAN channels

GP

DMA

ADC channels

Temp

range

DAC channels

to

+85 °C

to

+85 °C

Table 10. LPC2470 ordering options

Type number Flash

LPC2470FBD208 N/A 64 16 16 2 98 Full

LPC2470FET208 N/A 64 16 16 2 98 Full

5.5 LPC2478 ordering options

Table 11. LPC2478 ordering information

Type number Package

LPC2478FBD208 LQFP208 plastic low profil e quad flat package; 208 leads; body 28 × 28 × 1.4 mm SOT459-1

LPC2478FET208 TFBGA208 plastic thin fine-pitch ball grid array package; 208 balls; body 15 × 15 ×

Name Description Version

SOT950-1

0.7 mm

(kB)

SRAM (kB) External

bus

Local bus

Ethernet buffer

GP/USB

RTC

Total

32-bit

32-bit

Table 12. LPC2478 ordering options

Type number Flash

LPC2478FBD208 512 64 16 16 2 98 Full

LPC2478FET208 512 64 16 16 2 98 Full

6. Architectural overview

The LPC2400 microcontroller consists of an ARM7TDMI-S CPU with emulation support,

the ARM7 local bus for closely coupled, high speed ac cess to th e ma jo rity of on- ch ip

memory, the AMBA AHB interfacing to high speed on-chip peripherals and external

memory, and the AMBA APB for connection to other on-chip peripheral functions. The

microcontroller permanently configures the ARM7TDMI-S processor for little-endian byte

order.

Ethernet USB

OTG/

OHC/

Device

+ 4 kB

FIFO

MII/RMII yes 2 yes yes 8 1 −40 °C

MII/RMII yes 2 yes yes 8 1 −40 °C

SD/

GP

MMC

DMA

CAN channels

Temp

range

ADC channels

DAC channels

to

+85 °C

to

+85 °C

The LPC2400 implements two AHB buses in order to allow the Ethernet block to operate

without interference caused by other system activity. The primary AHB, referred to as

AHB1, includes the VIC, GPDMA controller, and EMC.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 8 of 792

Page 9

NXP Semiconductors

The second AHB, referred to as AHB2, includes only the Ethernet block and an

associated 16 kB SRAM. In addition, a bus bridge is provided that allows the secondary

AHB to be a bus master on AHB1, allowing expansion of Ethernet buffer space into

off-chip memory or unused space in memory resid ing on AHB1.

In summary, bus masters with access to AHB1 are the ARM7 itself, the GPDMA function,

and the Ethernet block (via the bus bridge from AHB2). Bus masters with access to AHB2

are the ARM7 and the Ethernet block.

AHB peripherals are allocated a 2 MB range of addresses at the very top of the 4 GB

ARM memory space. Each AHB peripheral is allocated a 16 kB address space within the

AHB address space. Lower speed peripheral functions are connected to the APB bus.

The AHB to APB bridge interfaces the APB bus to the AHB bus. APB peripherals are also

allocated a 2 MB range of addresses, beginning at the 3.5 GB address point. Each APB

peripheral is allocated a 16 kB address space within the APB address space.

The ARM7TDMI-S processor is a general purpose 32-bit microprocessor, which offers

high performance and very low power consumption. The ARM architecture is based on

Reduced Instruction Set Computer (RISC) principles, and the instruction set and related

decode mechanism are much simpler than those of microprogrammed complex

instruction set computers. This simplicity results in a high instruction throughput and

impressive real-time interrupt response from a small and cost-effective processor core.

UM10237

Chapter 1: LPC24XX Introductory information

Pipeline techniques are employed so that all pa rts of the p rocessing and memory systems

can operate continuously. T ypically, while one instruction is being executed, its successor

is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI-S processor also employs a unique architectural strategy known as

Thumb, which makes it ideally suited to high-volume applications with memory

restrictions, or applications where code density is an issue.

The key idea behind Thumb is that of a super-reduced instruction set. Essentially, the

ARM7TDMI-S processor has two instruction sets:

• the standard 32-bit ARM set

• a 16-bit Thumb set

The Thumb set’s 16-bit instruction length allows it to approach higher density comp ared to

standard ARM code while retaining most of the ARM’s performance.

7. On-chip flash programming memory (LPC2458/68/78)

The LPC2400 incorporates 512 kB Flash memory system. This memory may be used for

both code and data storage. Programming of the Flash memory may be accomplished in

several ways. It may be programmed In System via the serial port (UART0). The

application program may also erase and/or program the Flash while the application is

running, allowing a great degree of flexibility for data storage field and firmware upgrades.

The Flash memory is 128 bits wide and includes pre-fetching and buffering techniques to

allow it to operate at speeds of 72 MHz.

The LPC2400 provides a minimum of 100 000 writ e/ eras e cycles and 20 years of data

retention.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 9 of 792

Page 10

NXP Semiconductors

8. On-chip SRAM

The LPC2400 includes a SRAM memory of 64 kB reserved for the ARM processor

exclusive use. This RAM may be used for code and/o r data sto rage and may be accessed

as 8 bits, 16 bits, and 32 bits.

A 16 kB SRAM block serving as a buffer for the Ethernet controller and a 16 kB SRAM

associated with the second AHB bus can be used both for data and code storage, too.

Remaining SRAM such as a 4 kB USB FIFO and a 2 kB RTC SRAM can be used for data

storage only . The R TC SRAM is battery powered a nd retains the content in the absence of

the main power supply.

UM10237

Chapter 1: LPC24XX Introductory information

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 10 of 792

Page 11

NXP Semiconductors

power domain 2

LPC2458

A[19:0]

D[15:0]

EXTERNAL

MEMORY

CONTROLLER

ALARM

002aad093

PWM0, PWM1

ARM7TDMI-S

PLL

EINT3 to EINT0

FLASH

P3, P4

P0, P1, P2,

LEGACY GPI/O

64 PINS TOTAL

P0, P1

SCK, SCK0

MOSI, MOSI0

SSEL, SSEL0

SCK1

MOSI1

MISO1

SSEL1

SCL0, SCL1, SCL2

I2SRX_CLK

I2STX_CLK

I2SRX_WS

I2STX_WS

8 × AD0

RTCX1

RTCX2

MCICLK, MCIPWR

RXD0, RXD2, RXD3

TXD1

RXD1

RD1, RD2

TD1, TD2

CAN1, CAN2

port 1

XTAL1

TCK TDO

EXTIN0

XTAL2

RESET

TRST

TDITMS

HIGH-SPEED

GPI/O

136 PINS

TOTAL

port 2

64 kB

SRAM

512 kB

FLASH

INTERNAL

CONTROLLERS

TEST/DEBUG

INTERFACE

EMULATION

TRACE MODULE

trace signals

AHB

BRIDGE

AHB

BRIDGE

ETHERNET

MAC WITH

DMA

16 kB

SRAM

MASTER

PORT

AHB TO

AHB BRIDGE

SLAVE

PORT

system

clock

SYSTEM

FUNCTIONS

INTERNAL RC

OSCILLATOR

V

DDA

V

DD(3V3)

V

DD(DCDC)(3V3)

VREF

V

SSA

, V

SSIO, VSSCORE

VIC

16 kB

SRAM

USB DEVICE/

HOST/OTG WITH

4 kB RAM AND DMA

GP DMA

CONTROLLER

I2S INTERFACE

SPI, SSP0 INTERFACE

I2SRX_SDA

I2STX_SDA

MISO, MISO0

SSP1 INTERFACE

SD/MMC CARD

INTERFACE

MCICMD,

MCIDAT[3:0]

TXD0, TXD2, TXD3

UART0, UART2, UART3

UART1

DTR1, RTS1

DSR1, CTS1, DCD1,

RI1

I

2

C0, I2C1, I2C2

SDA0, SDA1, SDA2

EXTERNAL INTERRUPTS

CAPTURE/COMPARE

TIMER0/TIMER1/

TIMER2/TIMER3

A/D CONVERTER

D/A CONVERTER

2 kB BATTERY RAM

RTC

OSCILLATOR

REAL-

TIME

CLOCK

WATCHDOG TIMER

SYSTEM CONTROL

2 × CAP0/CAP1/

CAP2/CAP3

4 × MAT2,

2 × MAT3,

2 × MAT1/MAT0

6 × PWM0, PWM1

1 × PCAP0,

2 × PCAP1

AOUT

VBAT

AHB TO

APB BRIDGE

SRAM

MII/RMII

V

BUS

DBGEN

P0, P2

AHB2

AHB1

control lines

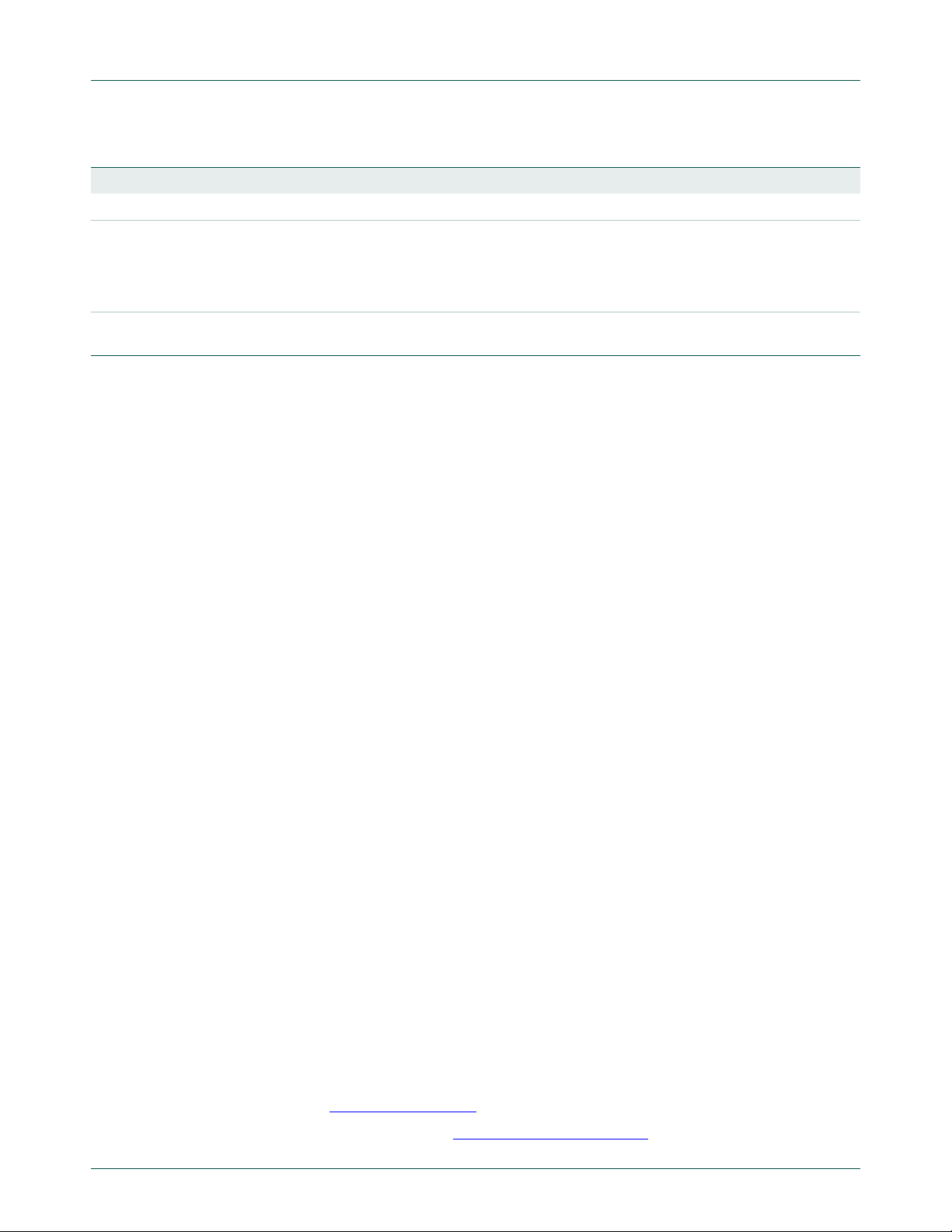

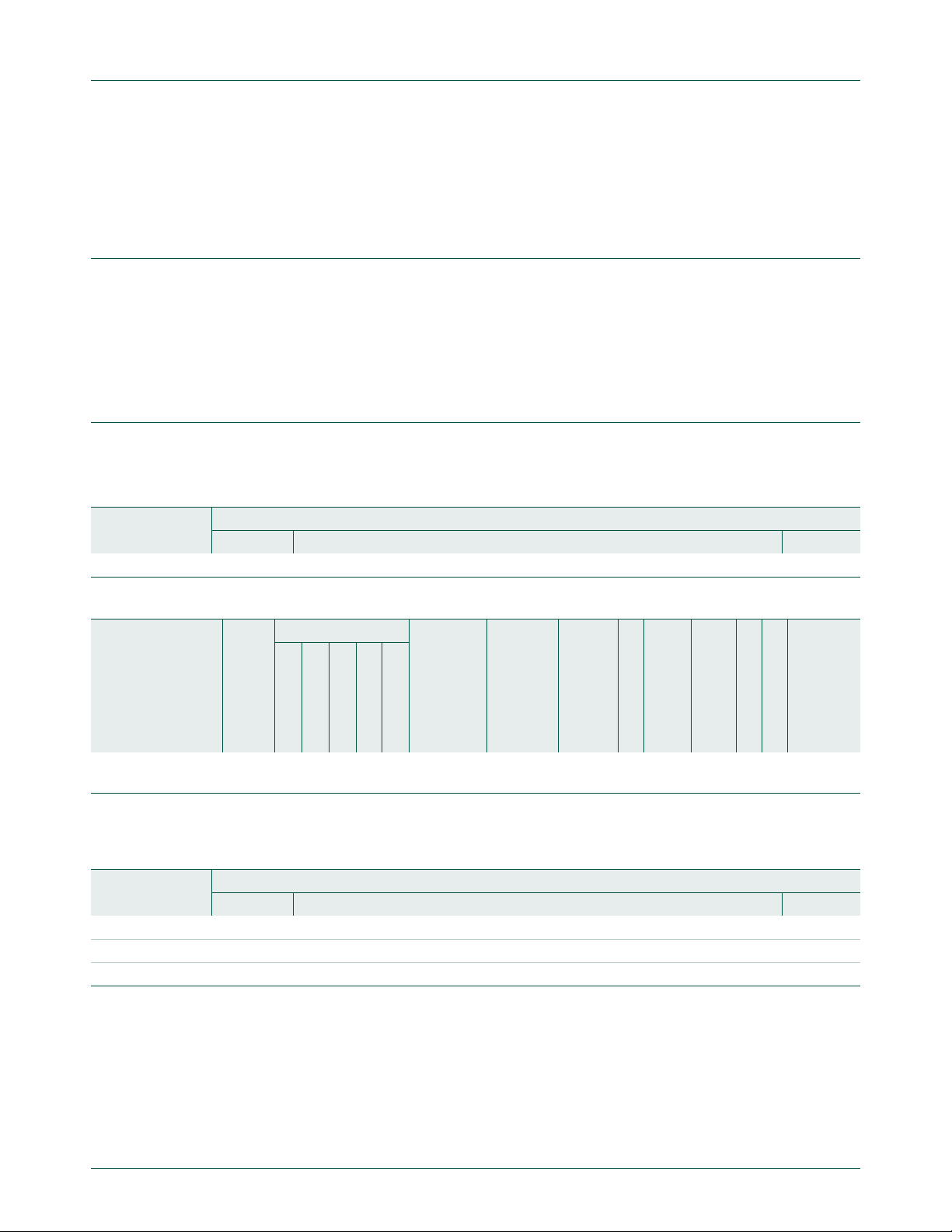

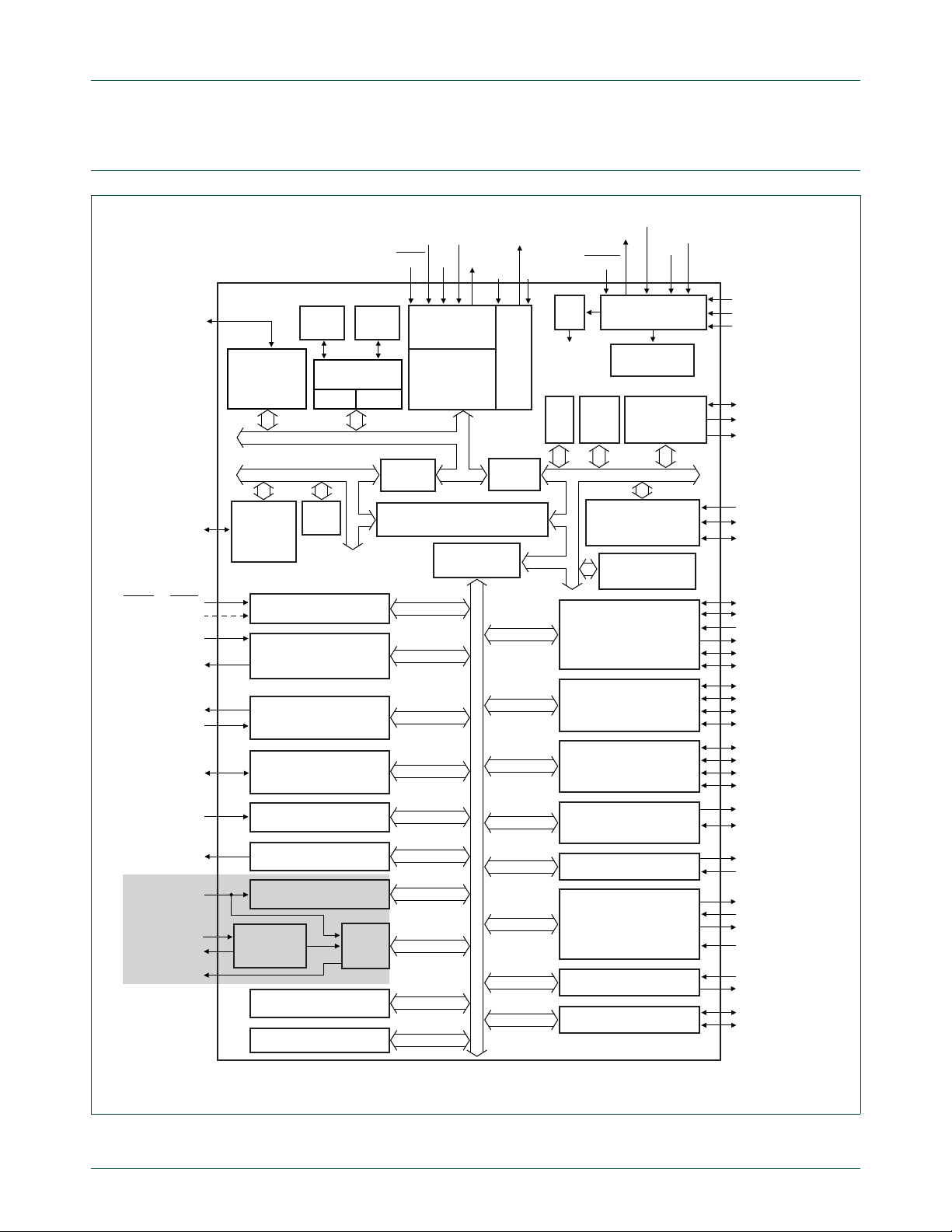

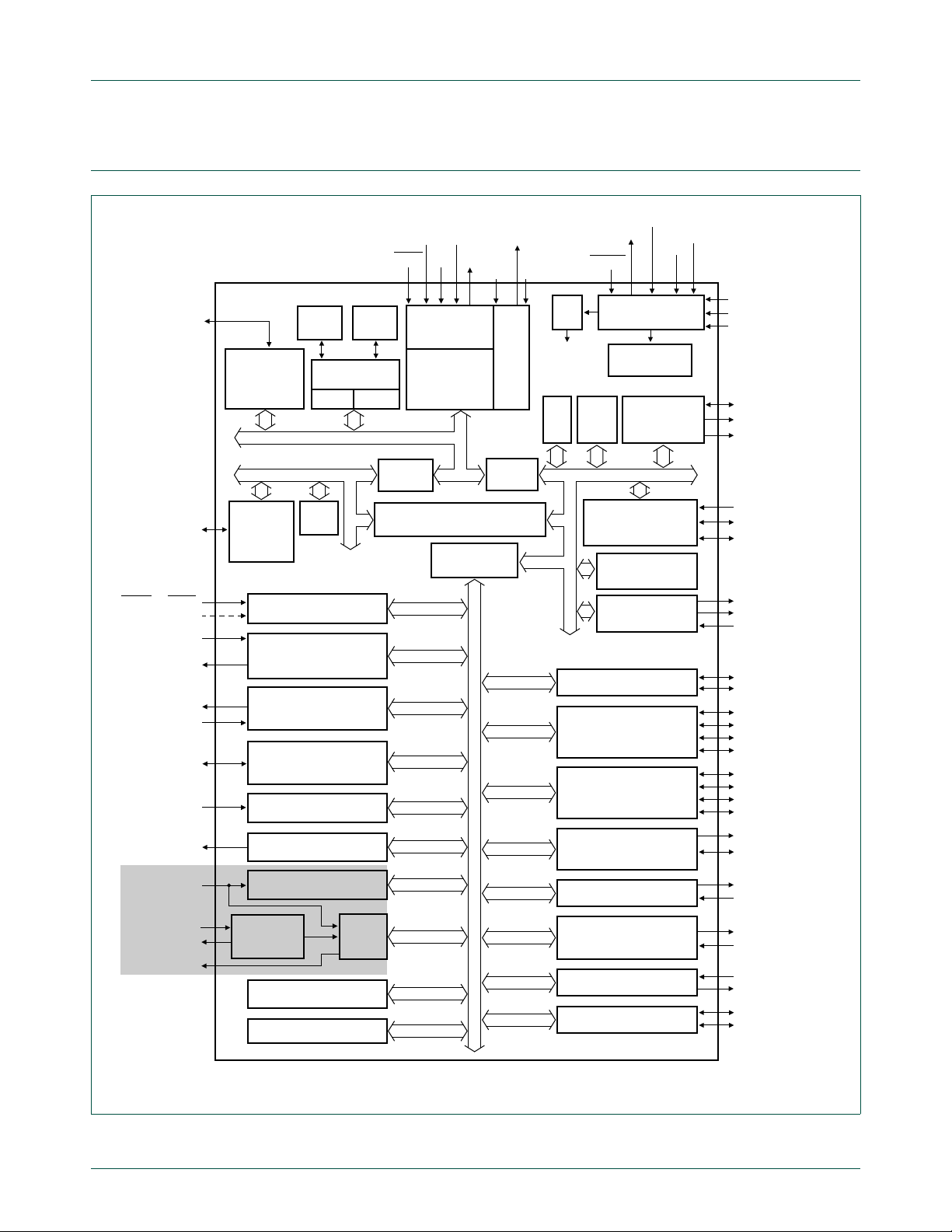

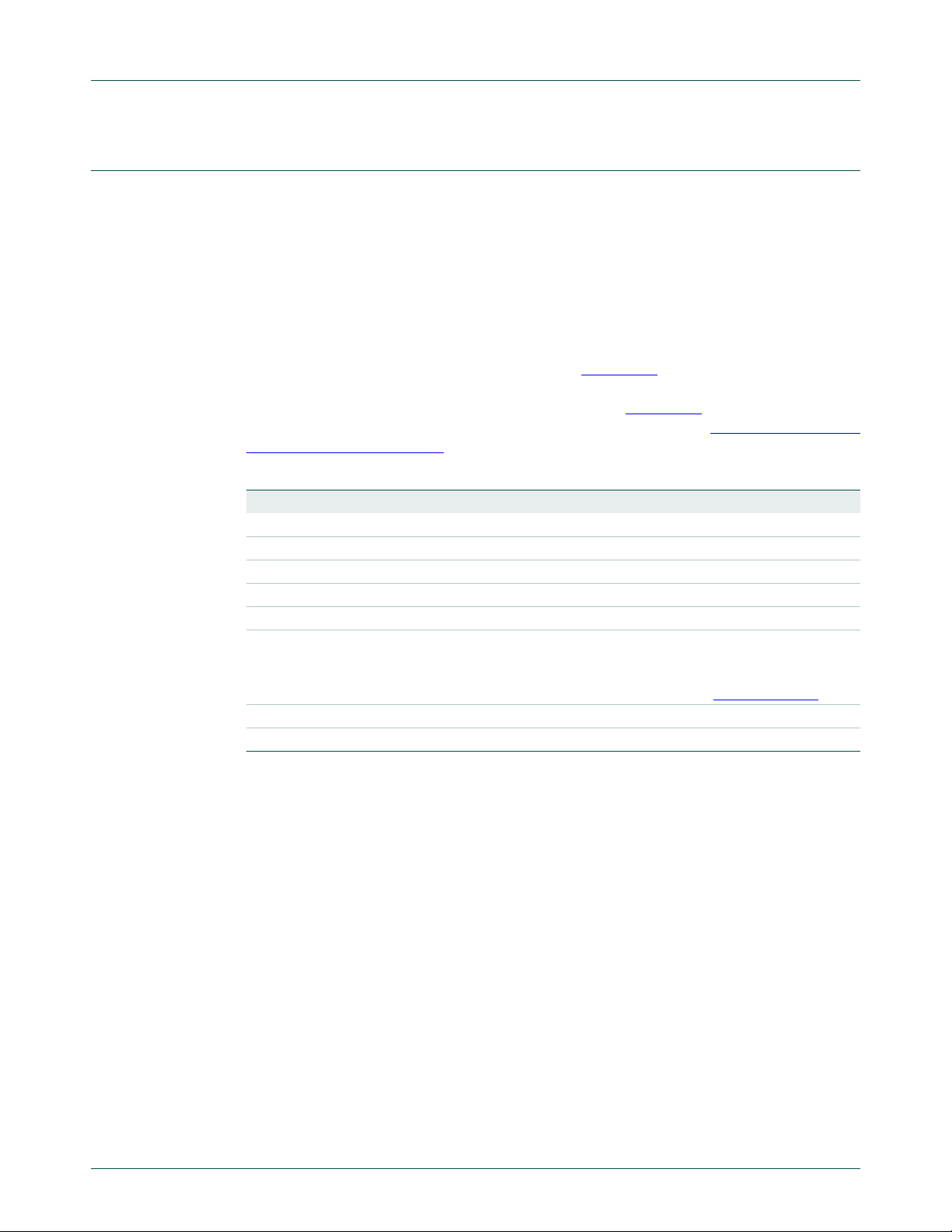

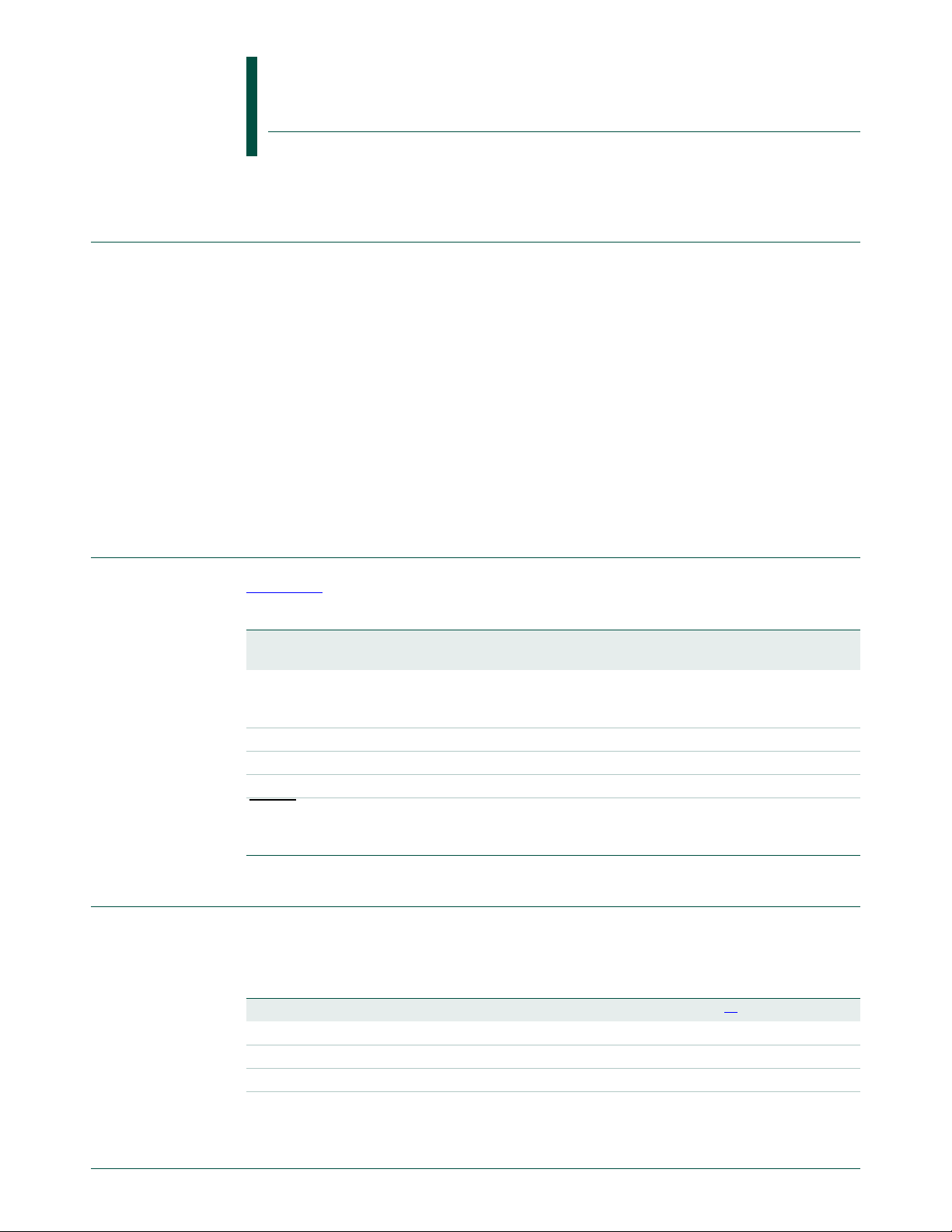

9. LPC2458 block diagram

UM10237

Chapter 1: LPC24XX Introductory information

Fig 1. LPC2458 block diagram

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 11 of 792

Page 12

NXP Semiconductors

power domain 2

LPC2420/2460

A[23:0]

D[31:0]

EXTERNAL

MEMORY

CONTROLLER

ALARM

002aad313

PWM0, PWM1

ARM7TDMI-S

PLL

EINT3 to EINT0

P3, P4

P0, P1, P2,

LEGACY GPI/O

64 PINS TOTAL

P0, P1

SCK, SCK0

MOSI, MOSI0

SSEL, SSEL0

SCK1

MOSI1

MISO1

SSEL1

SCL0, SCL1, SCL2

I2SRX_CLK

I2STX_CLK

I2SRX_WS

I2STX_WS

8 × AD0

RTCX1

RTCX2

MCICLK, MCIPWR

RXD0, RXD2, RXD3

TXD1

RXD1

RD1, RD2

TD1, TD2

CAN1

(1)

, CAN2

(1)

port1

XTAL1

TCK TDO

EXTIN0

XTAL2

RESET

TRST

TDITMS

HIGH-SPEED

GPI/O

160 PINS

TOTAL

port2

64 kB

SRAM

INTERNAL

SRAM

CONTROLLER

TEST/DEBUG

INTERFACE

EMULATION

TRACE MODULE

trace signals

AHB

BRIDGE

AHB

BRIDGE

ETHERNET

MAC WITH

DMA

(1)

16 kB

SRAM

(1)

MASTER

PORT

AHB TO

AHB BRIDGE

SLAVE

PORT

system

clock

SYSTEM

FUNCTIONS

INTERNAL RC

OSCILLATOR

V

DDA

V

DD(3V3)

V

DD(DCDC)(3V3)

VREF

V

SSA

, V

SSCORE

, V

SSIO

VIC

16 kB

SRAM

USB DEVICE/

HOST/OTG WITH

4 kB RAM AND DMA

GP DMA

CONTROLLER

I2S INTERFACE

SPI, SSP0 INTERFACE

I2SRX_SDA

I2STX_SDA

MISO, MISO0

SSP1 INTERFACE

SD/MMC CARD

INTERFACE

MCICMD,

MCIDAT[3:0]

TXD0, TXD2, TXD3

UART0, UART2, UART3

UART1

DTR1, RTS1

DSR1, CTS1, DCD1,

RI1

I

2

C0, I2C1, I2C2

SDA0, SDA1, SDA2

EXTERNAL INTERRUPTS

CAPTURE/COMPARE

TIMER0/TIMER1/

TIMER2/TIMER3

A/D CONVERTER

D/A CONVERTER

2 kB BATTERY RAM

RTC

OSCILLATOR

REAL-

TIME

CLOCK

WATCHDOG TIMER

SYSTEM CONTROL

2 × CAP0/CAP1/

CAP2/CAP3

4 × MAT2/MAT3,

2 × MAT0,

3 × MAT1

6 × PWM0/PWM1

1 × PCAP0,

2 × PCAP1

AOUT

VBAT

AHB TO

APB BRIDGE

MII/RMII

V

BUS

DBGEN

P0, P2

AHB2

AHB1

control lines

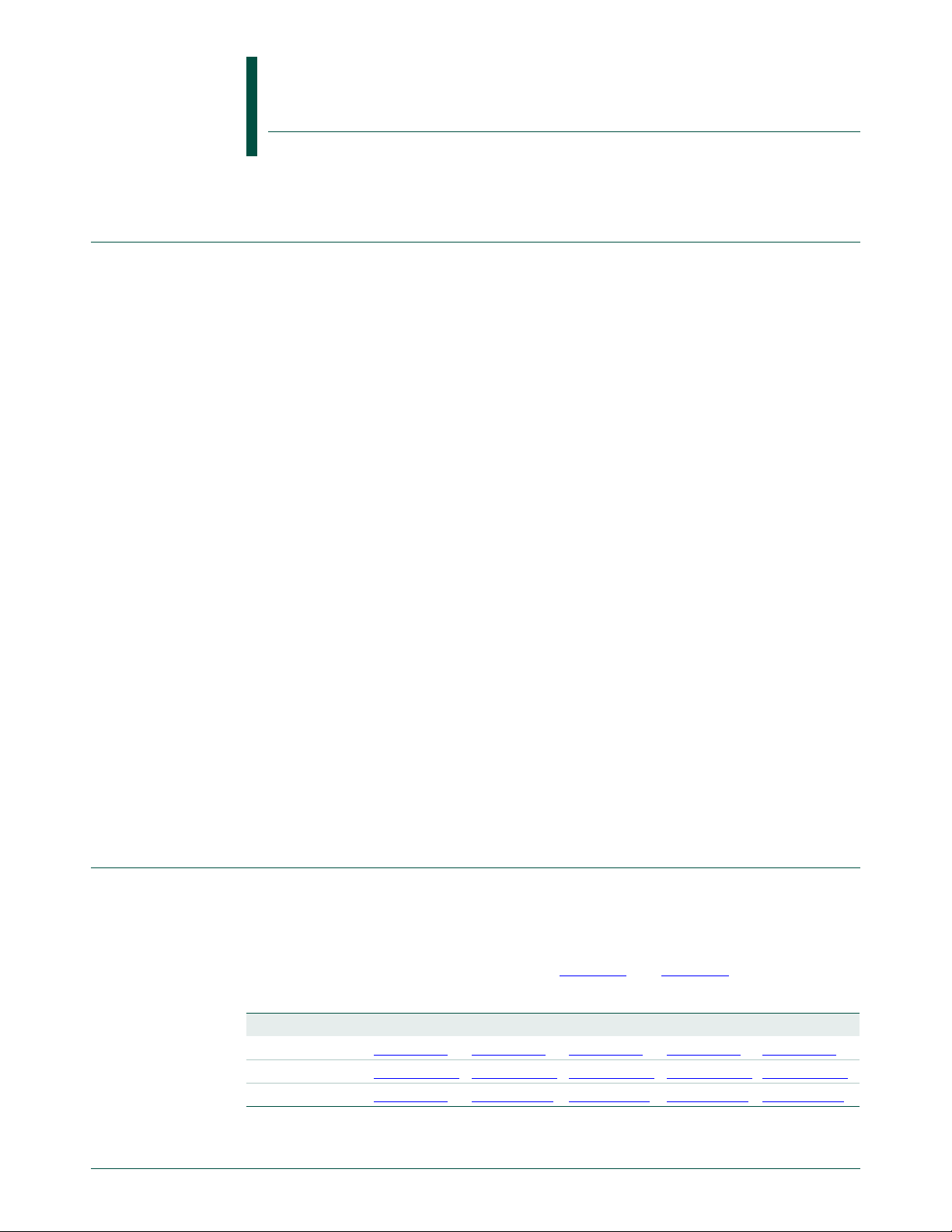

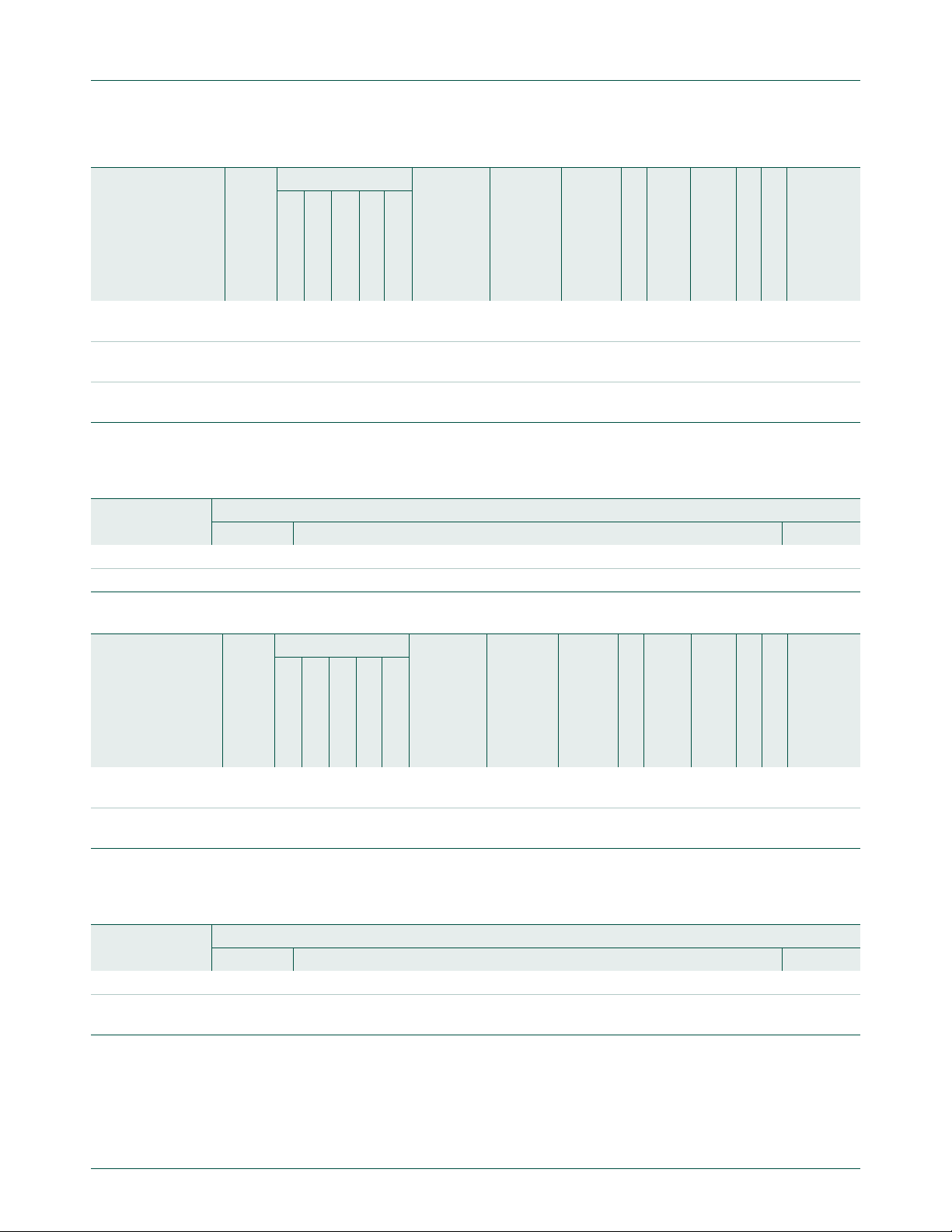

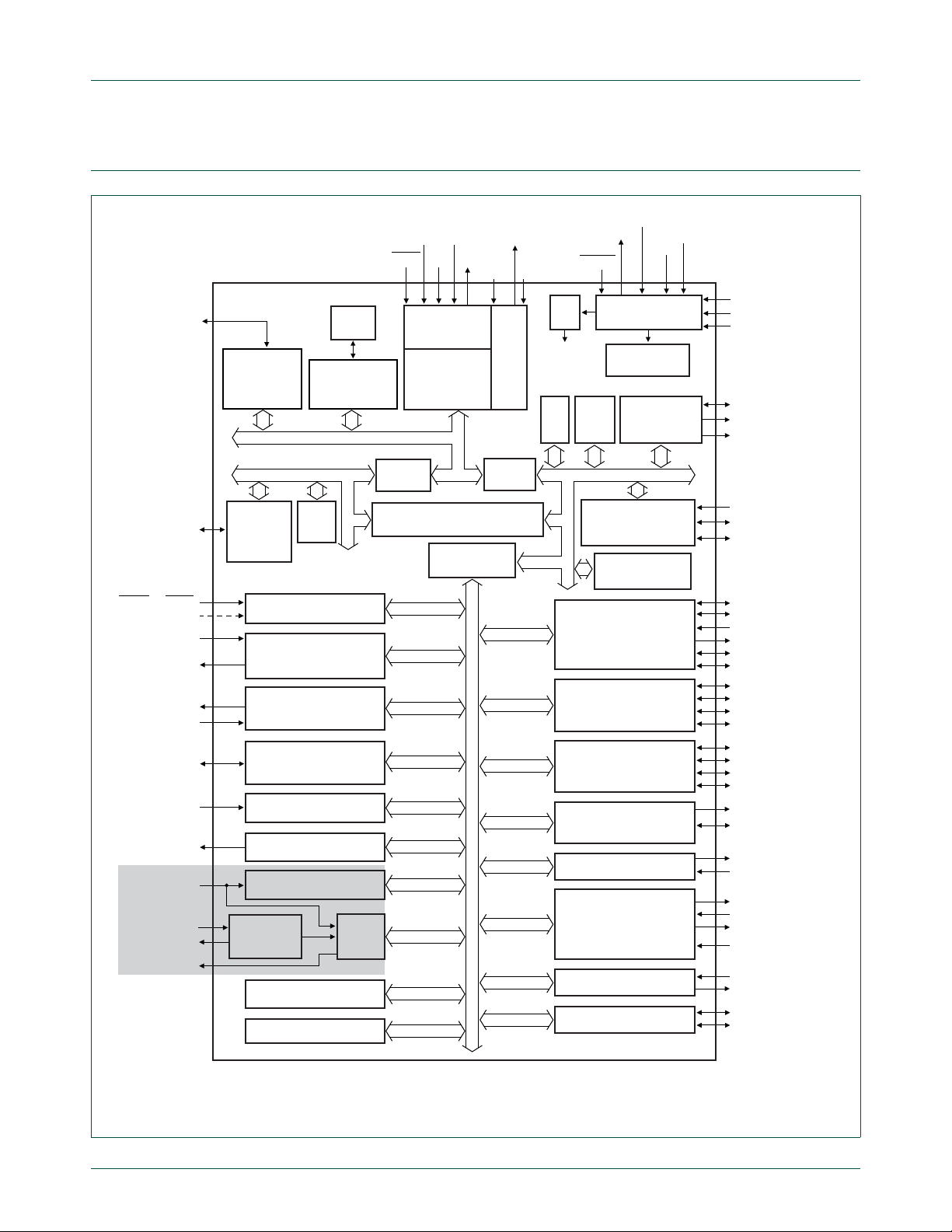

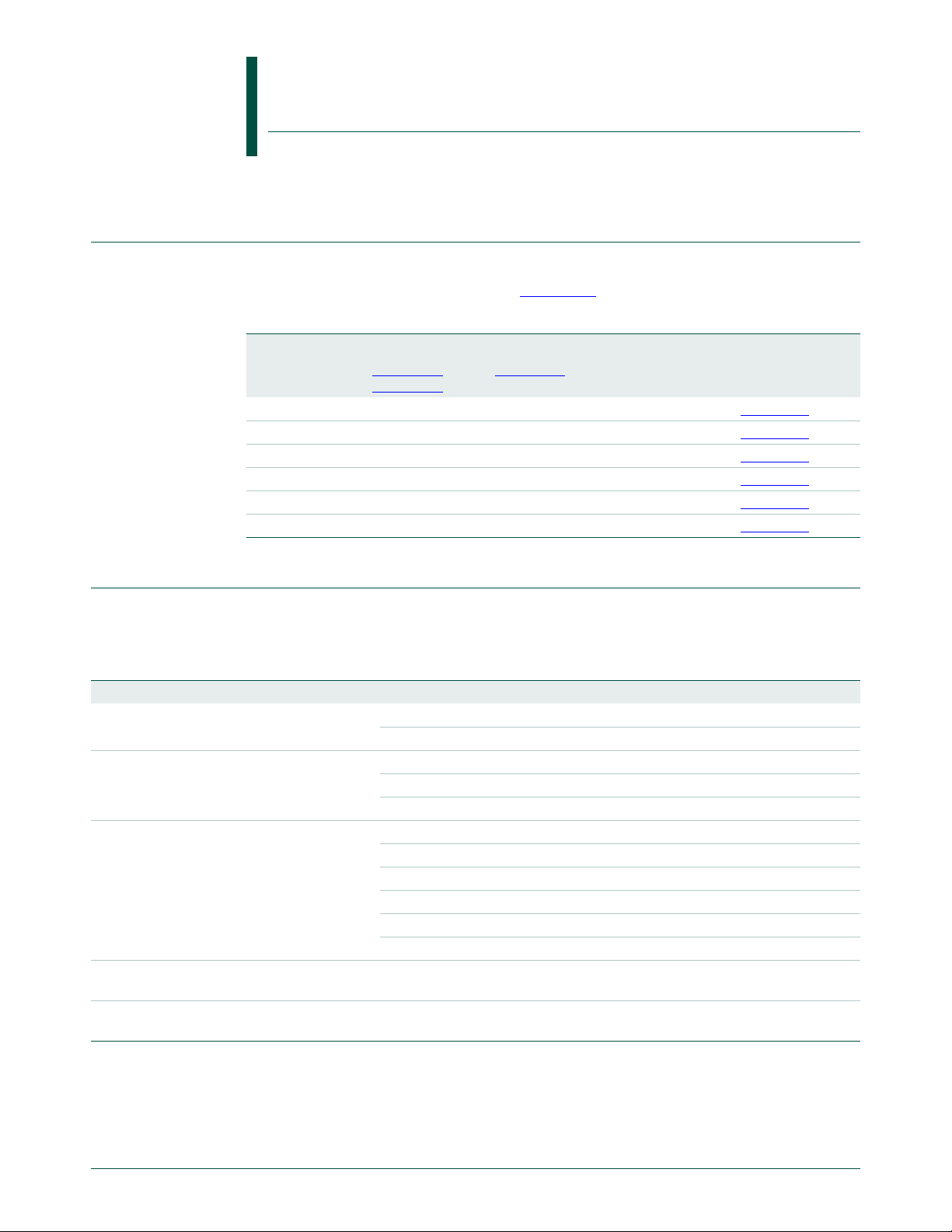

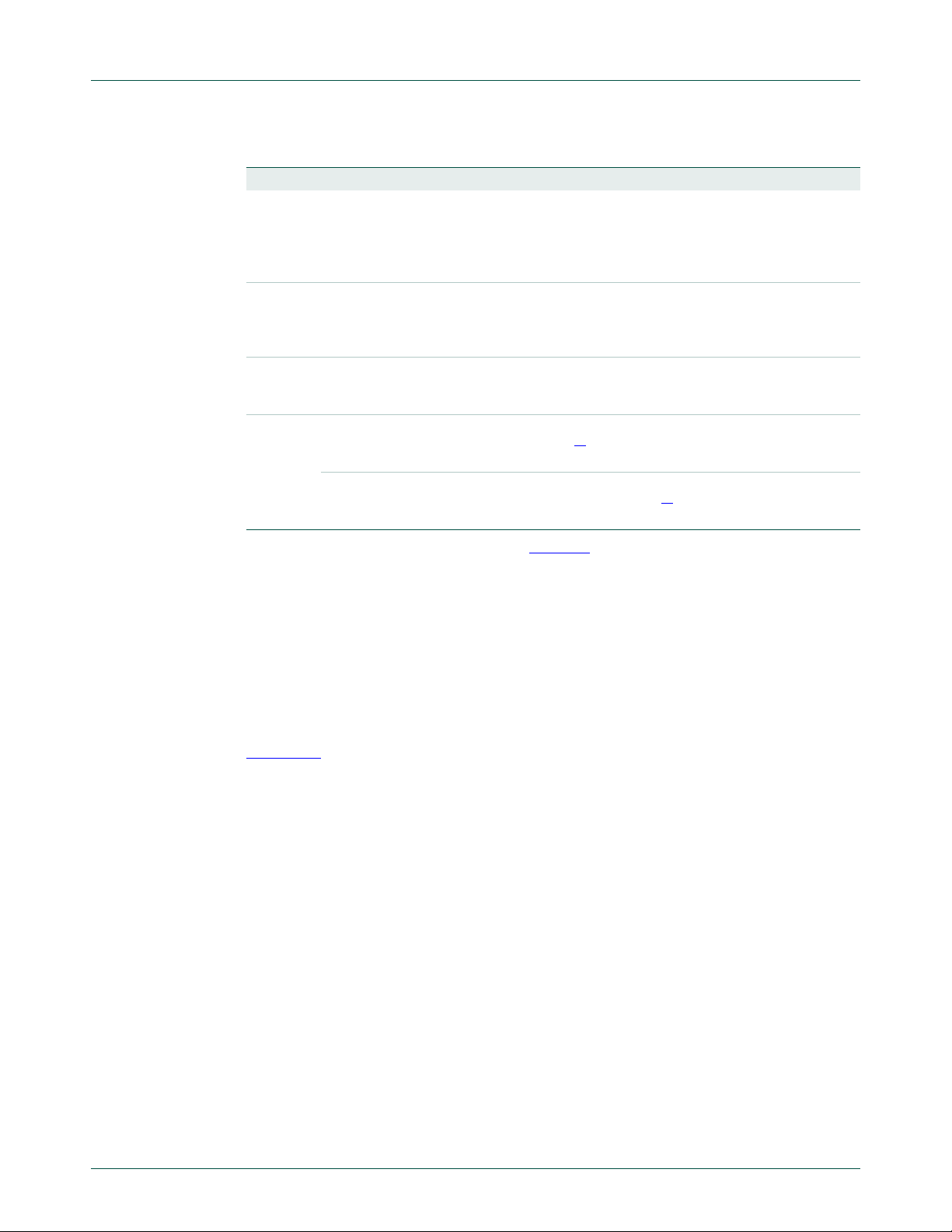

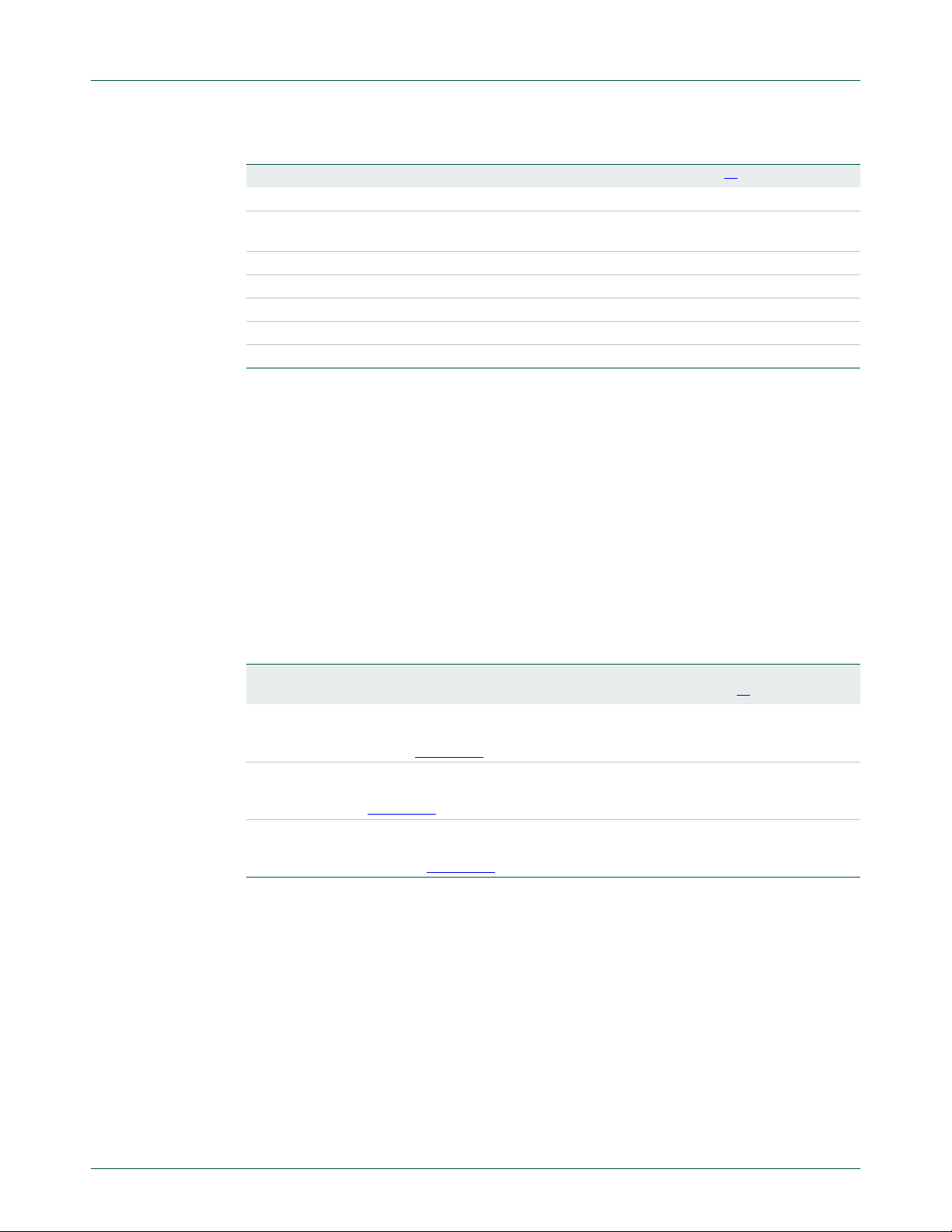

10. LPC2420/60 block diagram

UM10237

Chapter 1: LPC24XX Introductory information

(1) LPC2460 only.

Fig 2. LPC2460 block diagram

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 12 of 792

Page 13

NXP Semiconductors

power domain 2

LPC2468

A[23:0]

D[31:0]

EXTERNAL

MEMORY

CONTROLLER

ALARM

002aac721

PWM0, PWM1

ARM7TDMI-S

PLL

EINT3 to EINT0

FLASH

P3, P4

P0, P1, P2,

LEGACY GPI/O

64 PINS TOTAL

P0, P1

SCK, SCK0

MOSI, MOSI0

SSEL, SSEL0

SCK1

MOSI1

MISO1

SSEL1

SCL0, SCL1, SCL2

I2SRX_CLK

I2STX_CLK

I2SRX_WS

I2STX_WS

8 × AD0

RTCX1

RTCX2

MCICLK, MCIPWR

RXD0, RXD2, RXD3

TXD1

RXD1

RD1, RD2

TD1, TD2

CAN1, CAN2

port1

XTAL1

TCK TDO

EXTIN0

XTAL2

RESET

TRST

TDITMS

HIGH-SPEED

GPI/O

160 PINS

TOTAL

port2

64 kB

SRAM

512 kB

FLASH

INTERNAL

CONTROLLERS

TEST/DEBUG

INTERFACE

EMULATION

TRACE MODULE

trace signals

AHB

BRIDGE

AHB

BRIDGE

ETHERNET

MAC WITH

DMA

16 kB

SRAM

MASTER

PORT

AHB TO

AHB BRIDGE

SLAVE

PORT

system

clock

SYSTEM

FUNCTIONS

INTERNAL RC

OSCILLATOR

V

DDA

V

DD(3V3)

V

DD(DCDC)(3V3)

VREF

V

SSA

, V

SSIO, VSSCORE

VIC

16 kB

SRAM

USB DEVICE/

HOST/OTG WITH

4 kB RAM AND DMA

GP DMA

CONTROLLER

I2S INTERFACE

SPI, SSP0 INTERFACE

I2SRX_SDA

I2STX_SDA

MISO, MISO0

SSP1 INTERFACE

SD/MMC CARD

INTERFACE

MCICMD,

MCIDAT[3:0]

TXD0, TXD2, TXD3

UART0, UART2, UART3

UART1

DTR1, RTS1

DSR1, CTS1, DCD1,

RI1

I

2

C0, I2C1, I2C2

SDA0, SDA1, SDA2

EXTERNAL INTERRUPTS

CAPTURE/COMPARE

TIMER0/TIMER1/

TIMER2/TIMER3

A/D CONVERTER

D/A CONVERTER

2 kB BATTERY RAM

RTC

OSCILLATOR

REAL-

TIME

CLOCK

WATCHDOG TIMER

SYSTEM CONTROL

2 × CAP0/CAP1/

CAP2/CAP3

4 × MAT2/MAT3,

2 × MAT0,

3 × MAT1

6 × PWM0/PWM1

1 × PCAP0,

2 × PCAP1

AOUT

VBAT

AHB TO

APB BRIDGE

SRAM

MII/RMII

V

BUS

DBGEN

P0, P2

AHB2

AHB1

control lines

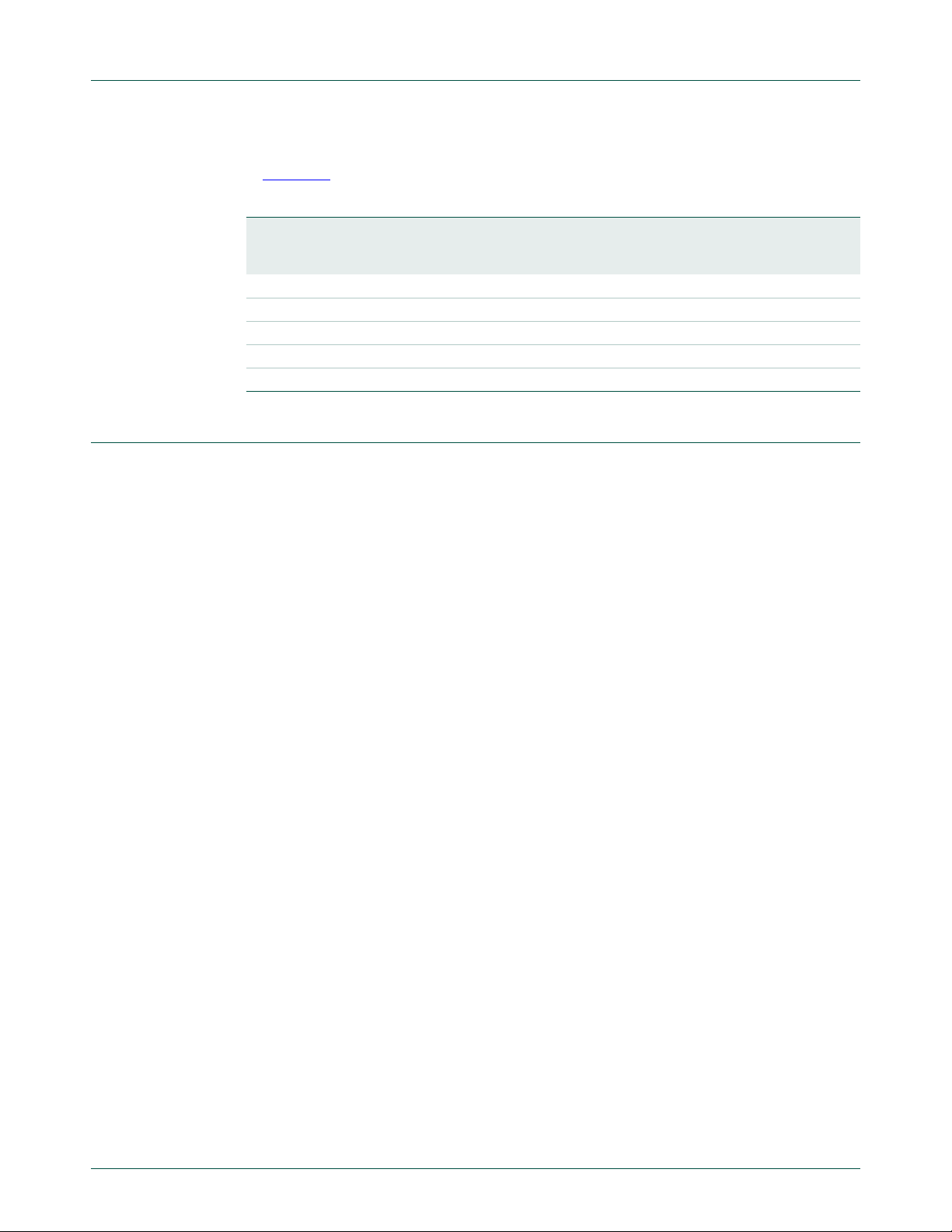

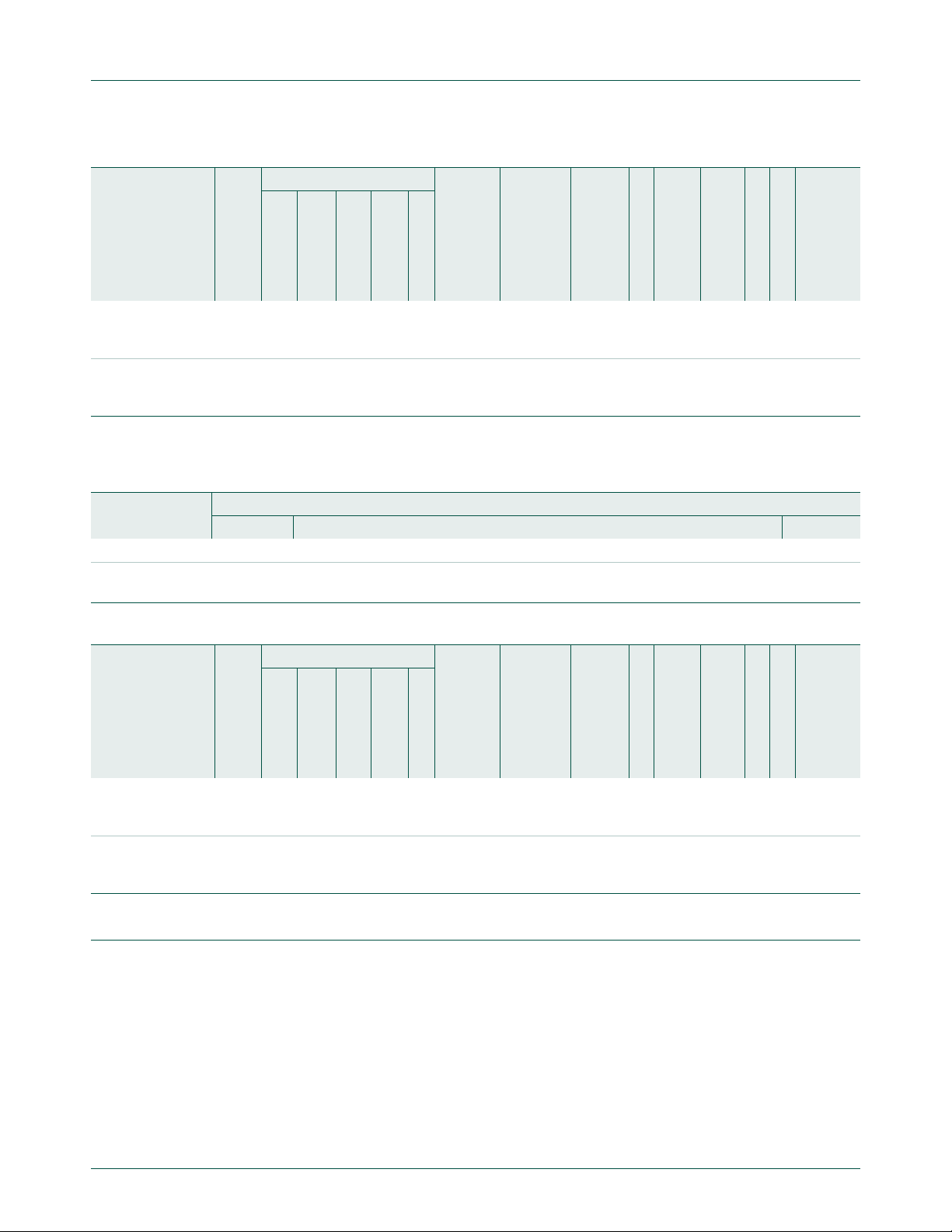

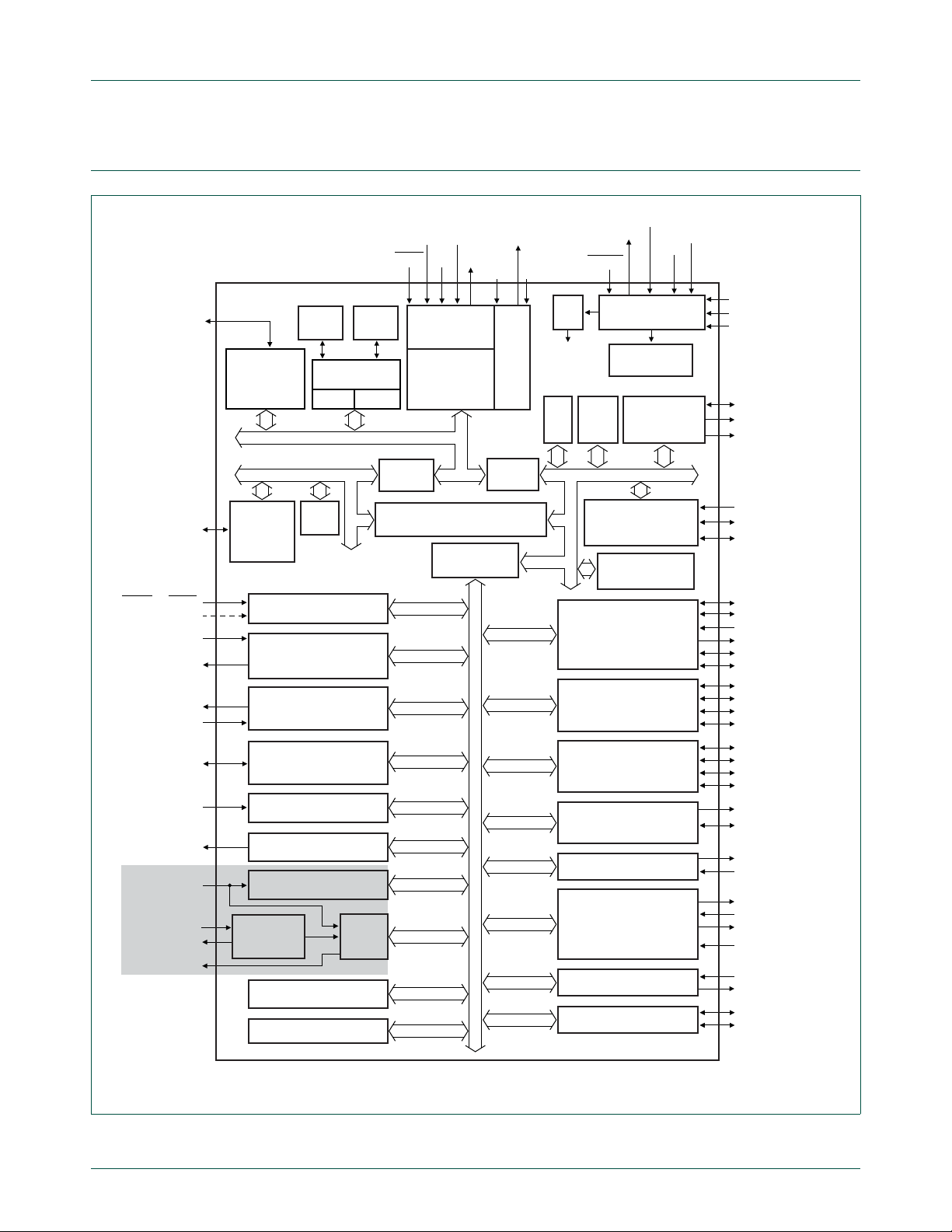

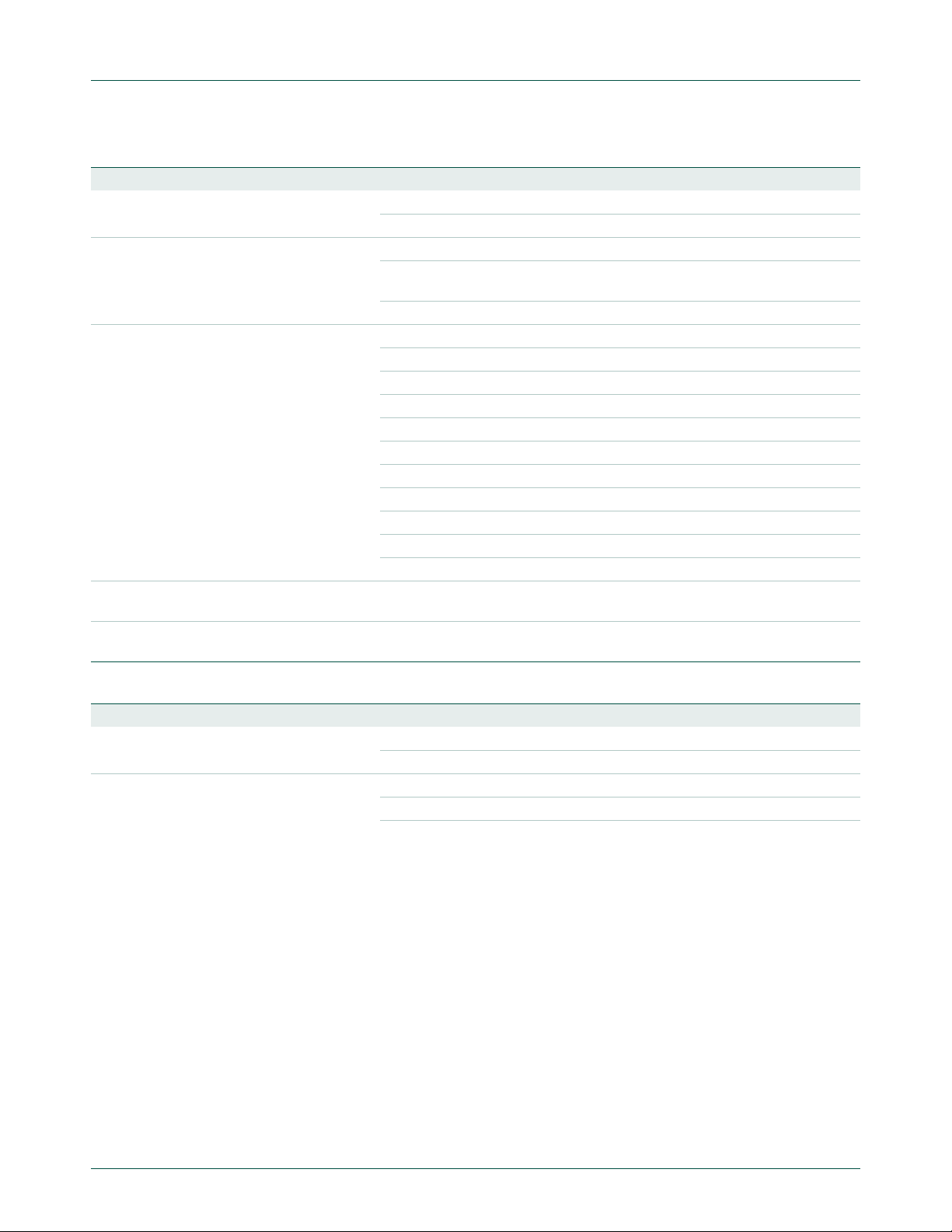

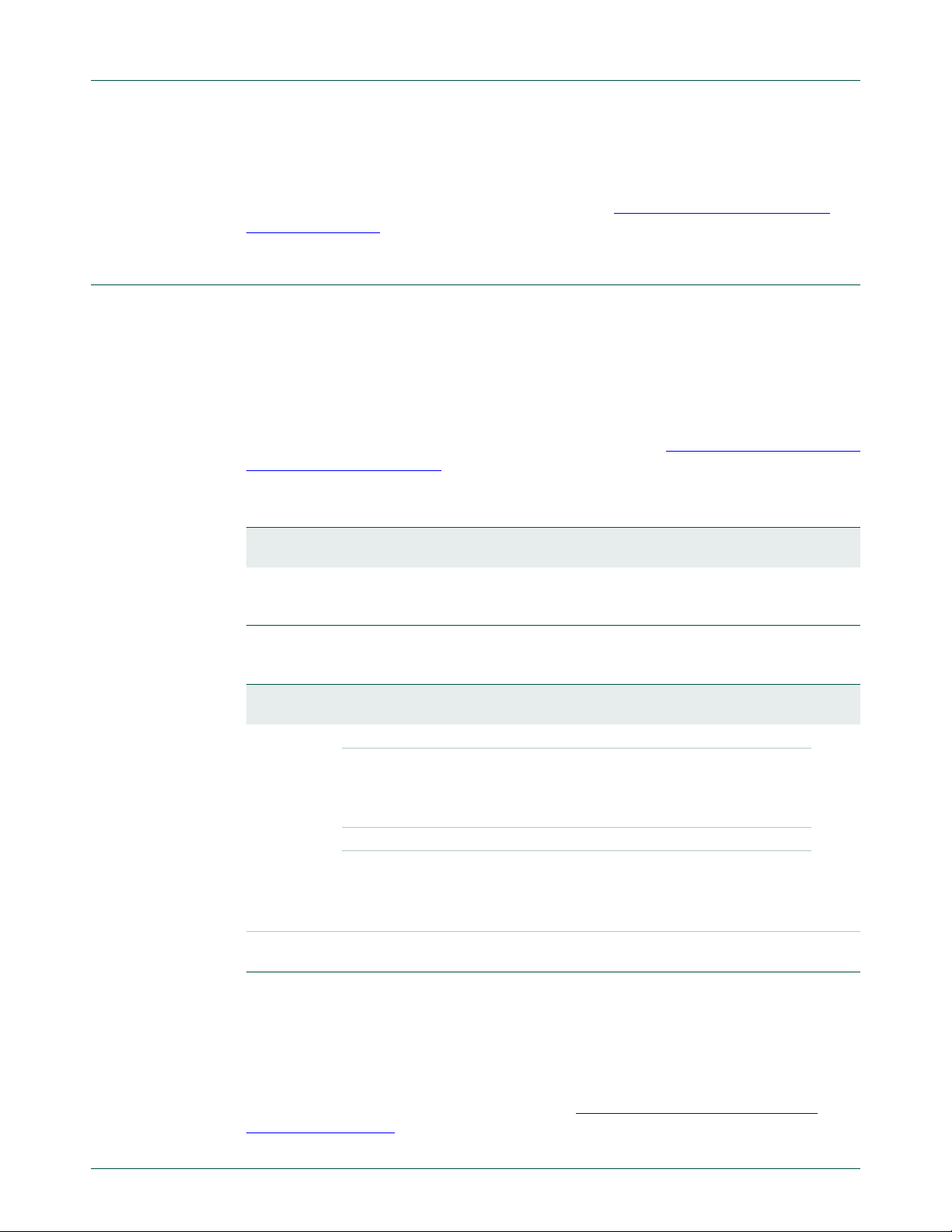

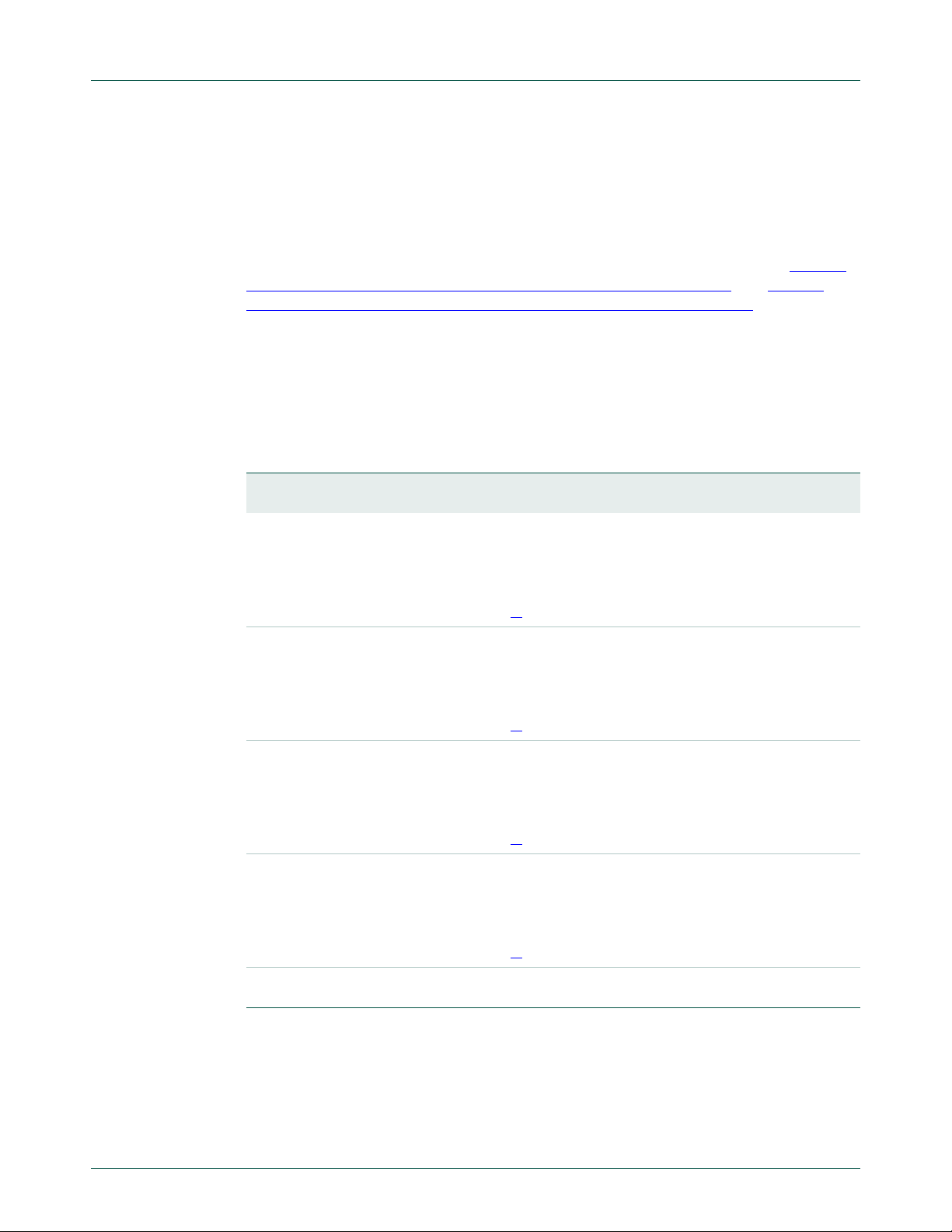

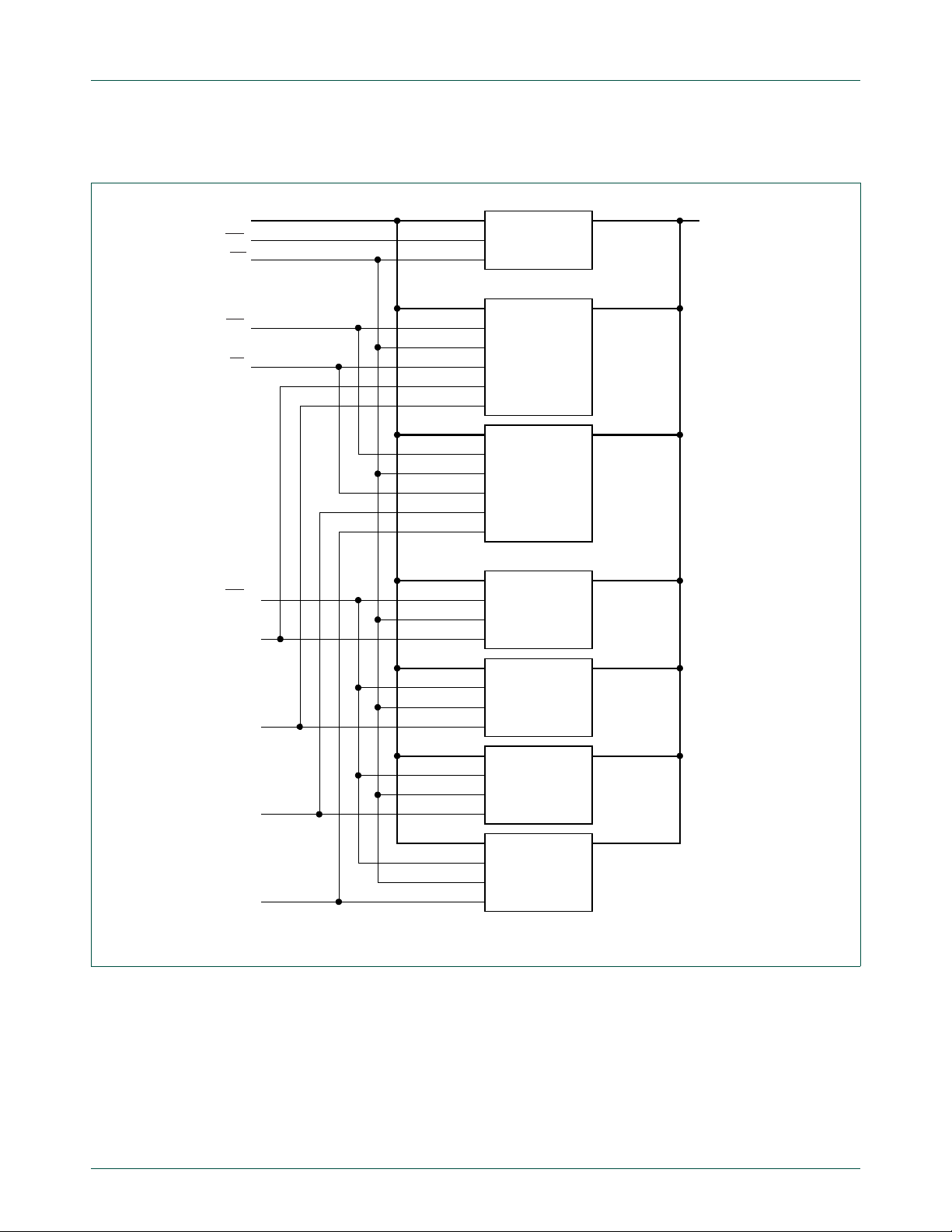

11. LPC2468 block diagram

UM10237

Chapter 1: LPC24XX Introductory information

Fig 3. LPC2468 block diagram

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 13 of 792

Page 14

NXP Semiconductors

power domain 2

LPC2470

A[23:0]

D[31:0]

EXTERNAL

MEMORY

CONTROLLER

ALARM

002aad317

PWM0, PWM1

ARM7TDMI-S

PLL

EINT3 to EINT0

P3, P4

P0, P1, P2,

LEGACY GPI/O

64 PINS TOTAL

P0, P1

SCK, SCK0

3 × I2STX

3 × I2SRX

8 × LCD control

LCDVD[23:0]

LCDCLKIN

MOSI, MOSI0

SSEL, SSEL0

SCK1

MOSI1

MISO1

SSEL1

SCL0, SCL1, SCL2

8 × AD0

RTCX1

RTCX2

MCICLK, MCIPWR

RXD0, RXD2, RXD3

RD1, RD2

TD1, TD2

CAN1, CAN2

port1

XTAL1

TCK TDO

EXTIN0

XTAL2

RESET

TRST

TDITMS

HIGH-SPEED

GPI/O

160 PINS

TOTAL

port2

64 kB

SRAM

INTERNAL

SRAM

CONTROLLER

TEST/DEBUG

INTERFACE

EMULATION

TRACE MODULE

trace signals

AHB

BRIDGE

AHB

BRIDGE

ETHERNET

MAC WITH

DMA

16 kB

SRAM

MASTER

PORT

AHB TO

AHB BRIDGE

SLAVE

PORT

system

clock

SYSTEM

FUNCTIONS

INTERNAL RC

OSCILLATOR

V

DDA

V

DD(3V3)

V

DD(DCDC)(3V3)

VREF

VIC

16 kB

SRAM

USB DEVICE/

HOST/OTG WITH

4 kB RAM AND DMA

GP DMA

CONTROLLER

LCD INTERFACE

WITH DMA

I2S INTERFACE

SPI, SSP0 INTERFACE

MISO, MISO0

SSP1 INTERFACE

SD/MMC CARD

INTERFACE

MCICMD,

MCIDAT[3:0]

TXD0, TXD2, TXD3

UART0, UART2, UART3

UART1

TXD1, DTR1, RTS1

RXD1, DSR1, CTS1,

DCD1, RI1

I

2

C0, I2C1, I2C2

SDA0, SDA1, SDA2

EXTERNAL INTERRUPTS

CAPTURE/COMPARE

TIMER0/TIMER1/

TIMER2/TIMER3

A/D CONVERTER

D/A CONVERTER

2 kB BATTERY RAM

RTC

OSCILLATOR

REAL-

TIME

CLOCK

WATCHDOG TIMER

SYSTEM CONTROL

2 × CAP0/CAP1/

CAP2/CAP3

4 × MAT2/MAT3,

2 × MAT0,

3 × MAT1

6 × PWM0/PWM1

1 × PCAP0,

2 × PCAP1

AOUT

VBAT

AHB TO

APB BRIDGE

MII/RMII

V

BUS

DBGEN

P0, P2

AHB2

AHB1

control lines

V

SSA

, V

SSCORE

, V

SSIO

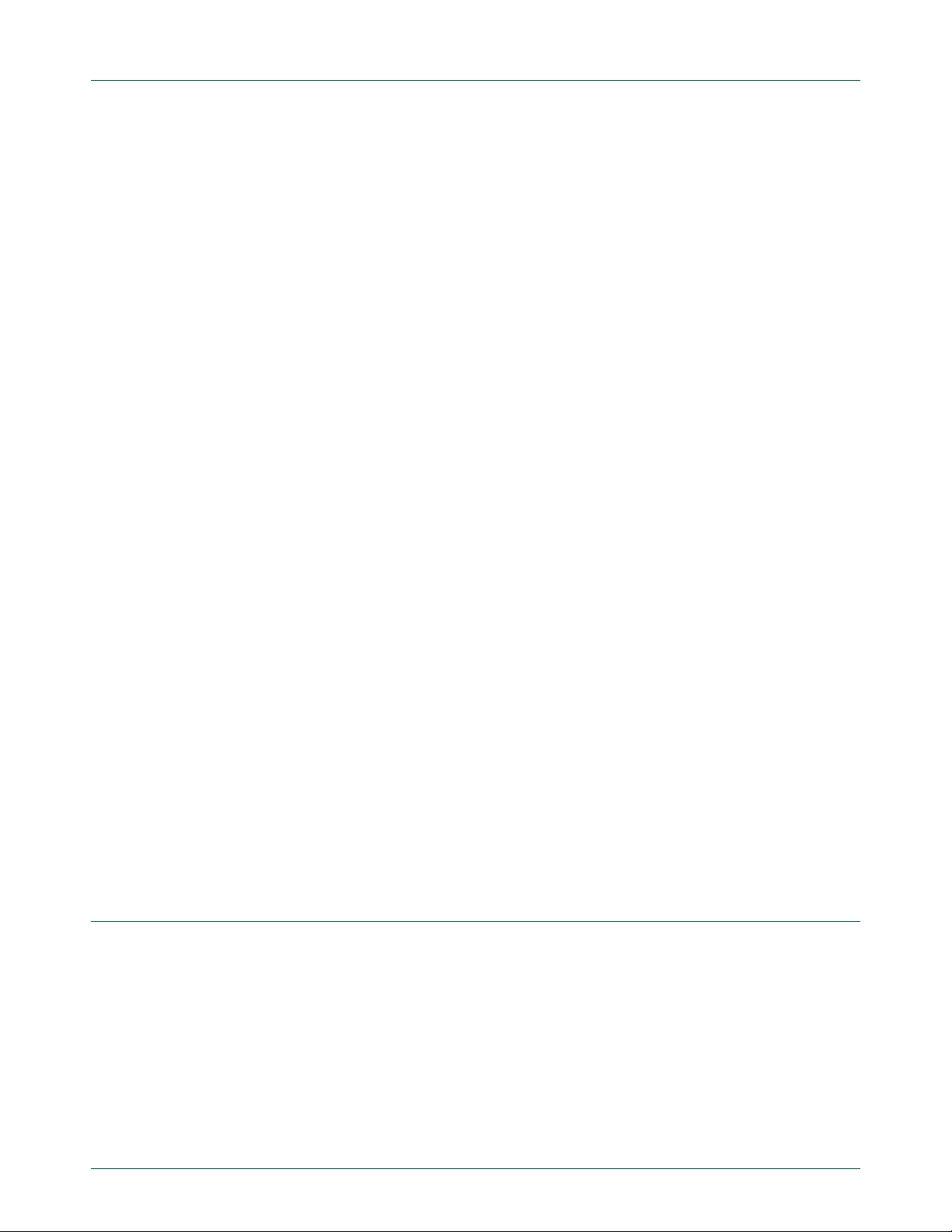

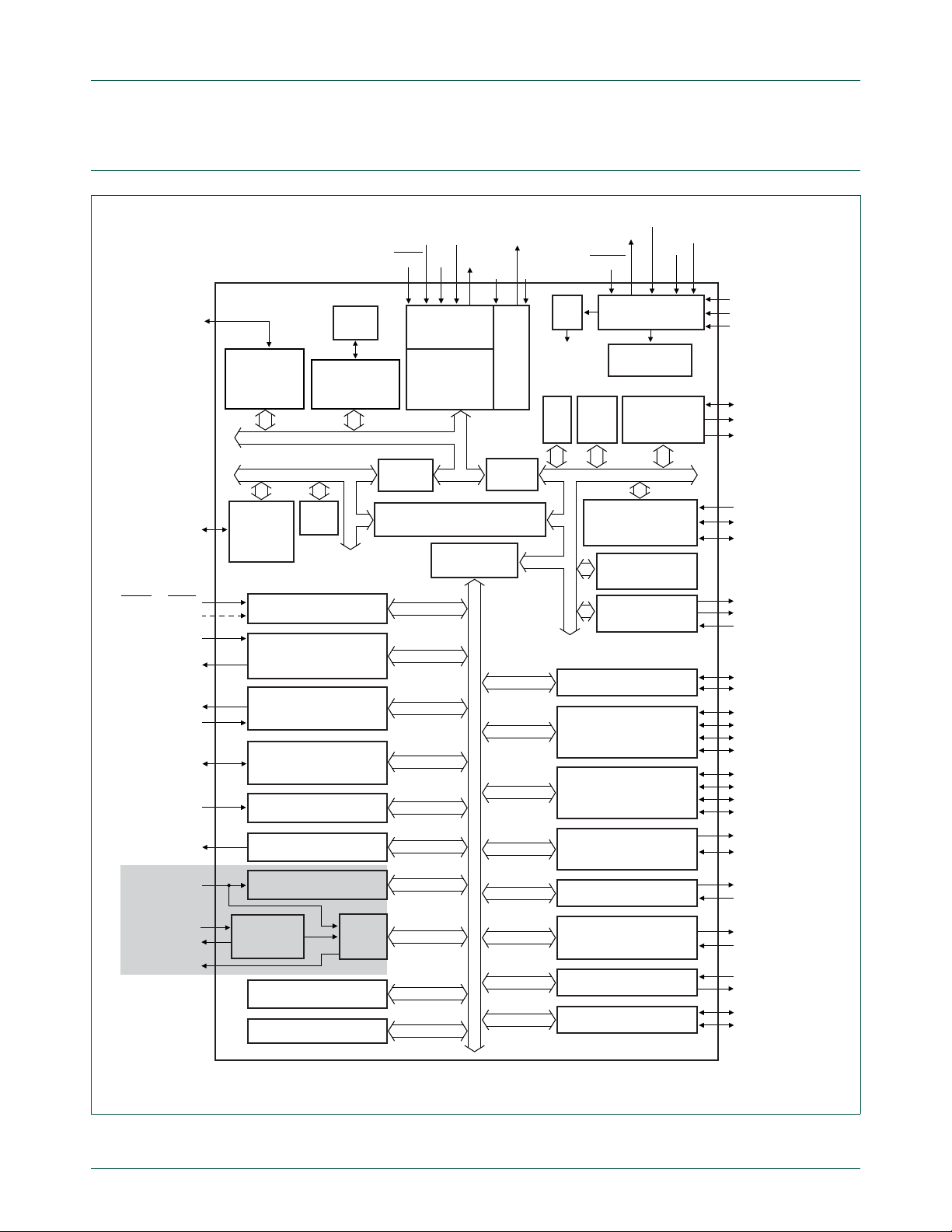

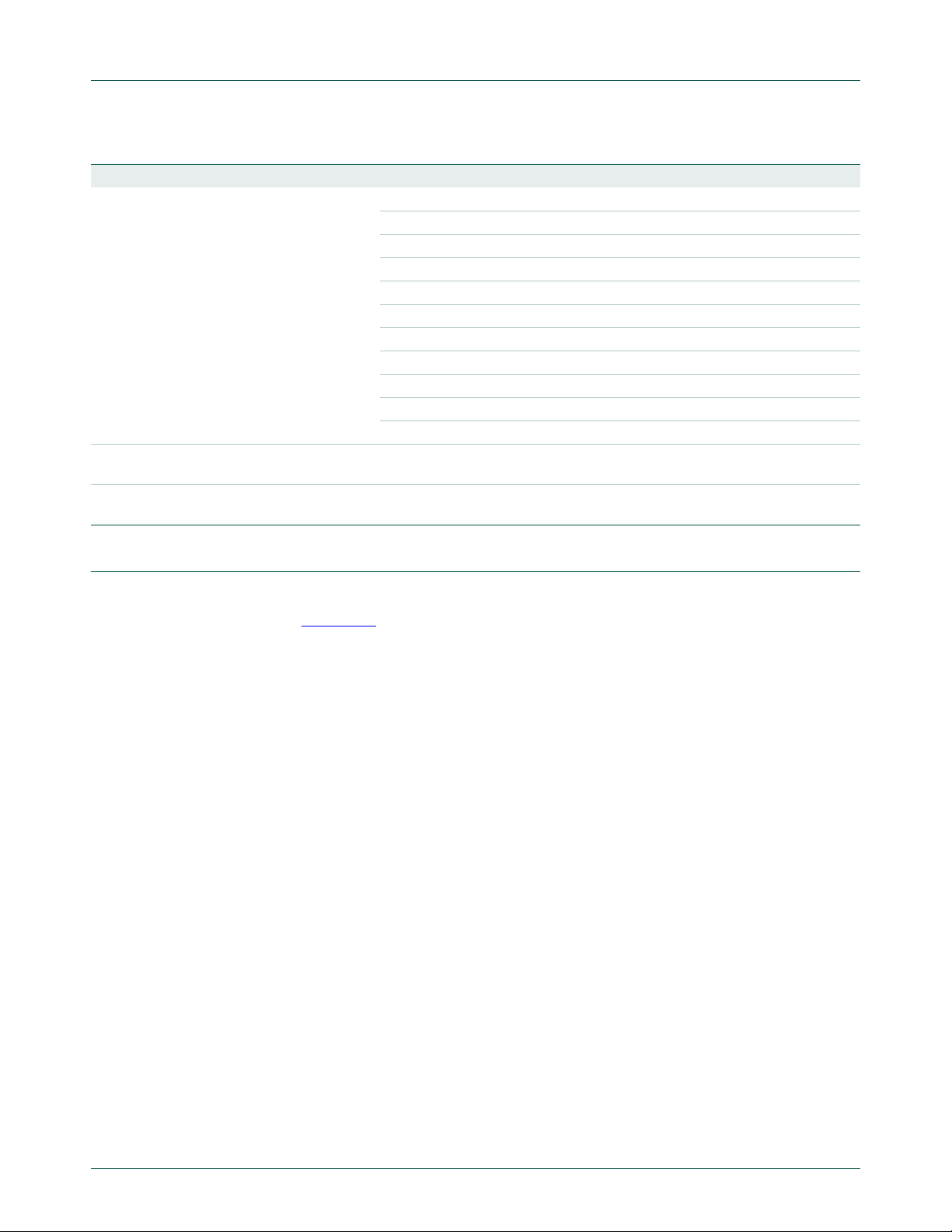

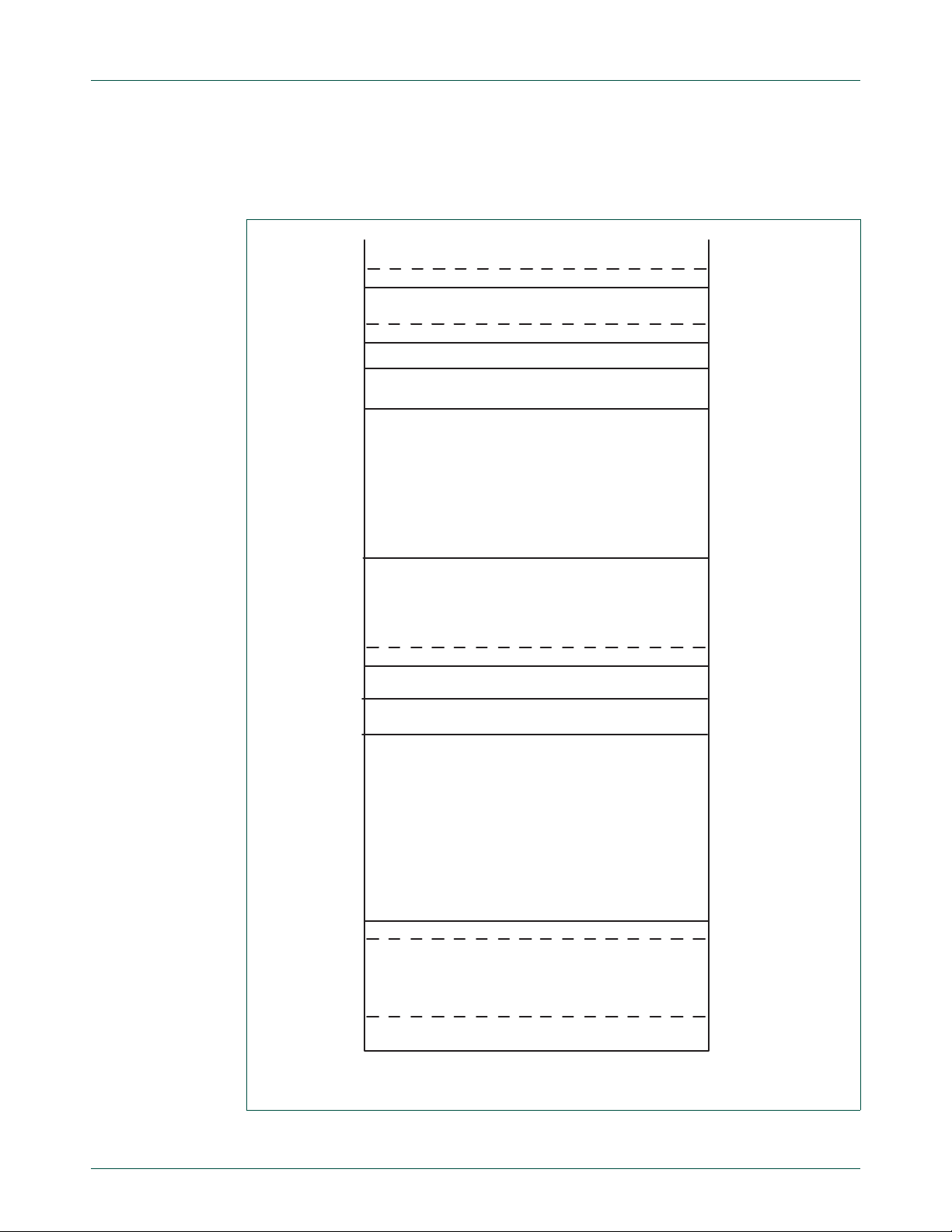

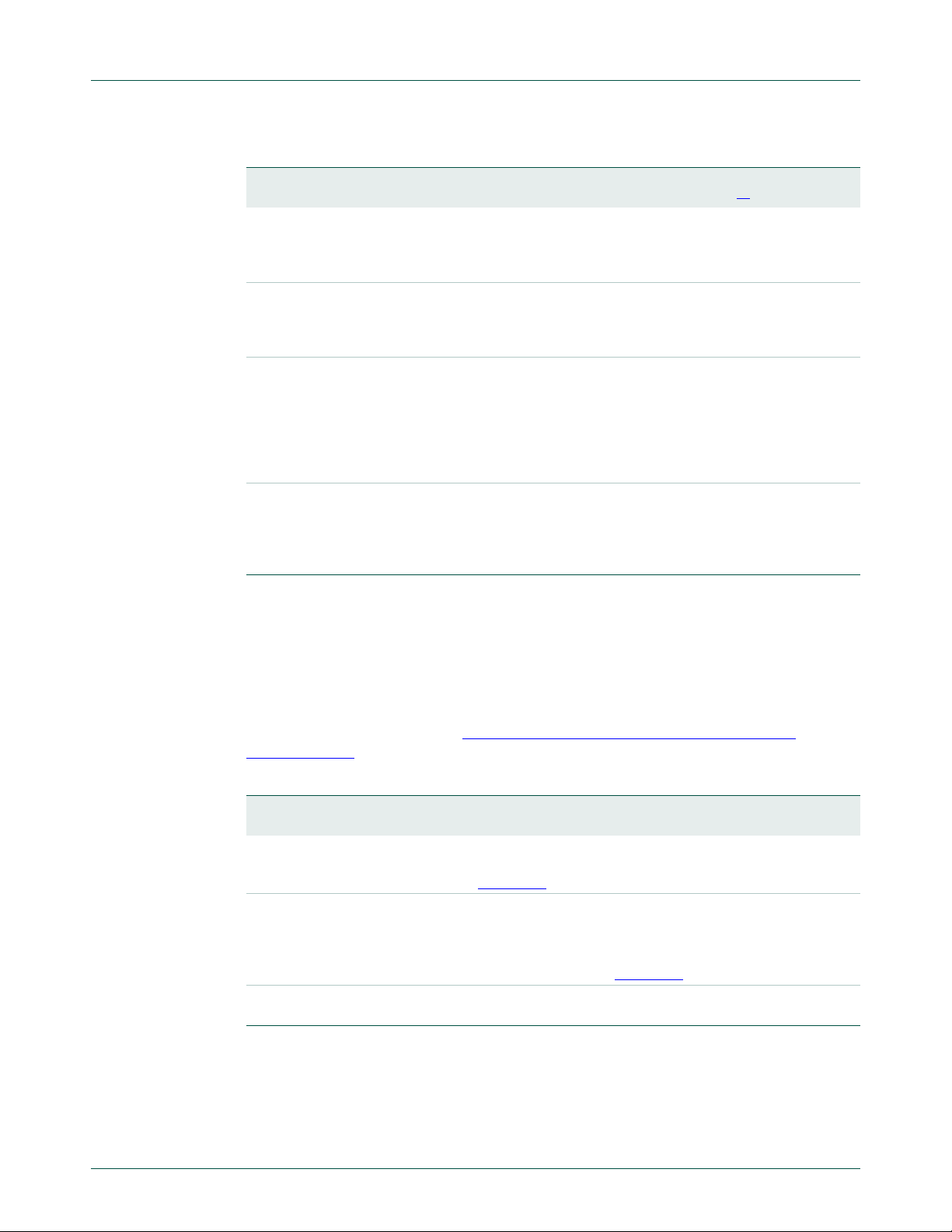

12. LPC2470 block diagram

UM10237

Chapter 1: LPC24XX Introductory information

Fig 4. LPC2470 block diagram

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 14 of 792

Page 15

NXP Semiconductors

power domain 2

LPC2478

A[23:0]

D[31:0]

EXTERNAL

MEMORY

CONTROLLER

ALARM

002aac805

PWM0, PWM1

ARM7TDMI-S

PLL

EINT3 to EINT0

FLASH

P3, P4

P0, P1, P2,

LEGACY GPI/O

64 PINS TOTAL

P0, P1

SCK0, SCK

3 × I2STX

3 × I2SRX

8 × LCD control

LCDVD[23:0]

LCDCLKIN

MOSI0, MOSI

SSEL0, SSEL

SCK1

MOSI1

MISO1

SSEL1

SCL0, SCL1, SCL2

8 × AD0

RTCX1

RTCX2

MCICLK, MCIPWR

RXD0, RXD2, RXD3

RD1, RD2

TD1, TD2

CAN1, CAN2

port1

XTAL1

TCK TDO

EXTIN0

XTAL2

RESET

TRST

TDITMS

HIGH-SPEED

GPI/O

160 PINS

TOTAL

port2

64 kB

SRAM

512 kB

FLASH

INTERNAL

CONTROLLERS

TEST/DEBUG

INTERFACE

EMULATION

TRACE MODULE

trace signals

AHB

BRIDGE

AHB

BRIDGE

ETHERNET

MAC WITH

DMA

16 kB

SRAM

MASTER

PORT

AHB TO

AHB BRIDGE

SLAVE

PORT

system

clock

SYSTEM

FUNCTIONS

INTERNAL RC

OSCILLATOR

V

DDA

V

DD(3V3)

V

DD(DCDC)(3V3)

VREF

V

SSA

, V

SSIO, VSSCORE

VIC

16 kB

SRAM

USB DEVICE/

HOST/OTG WITH

4 kB RAM AND DMA

GP DMA

CONTROLLER

LCD INTERFACE

WITH DMA

I2S INTERFACE

SSP0/SPI INTERFACE

MISO0, MISO

SSP1 INTERFACE

SD/MMC CARD

INTERFACE

MCICMD,

MCIDAT[3:0]

TXD0, TXD2, TXD3

UART0, UART2, UART3

UART1

TXD1, DTR1, RTS1

RXD1, DSR1, CTS1,

DCD1, RI1

I

2

C0, I2C1, I2C2

SDA0, SDA1, SDA2

EXTERNAL INTERRUPTS

CAPTURE/COMPARE

TIMER0/TIMER1/

TIMER2/TIMER3

A/D CONVERTER

D/A CONVERTER

2 kB BATTERY RAM

RTC

OSCILLATOR

REAL-

TIME

CLOCK

WATCHDOG TIMER

SYSTEM CONTROL

2 × CAP0/CAP1/

CAP2/CAP3

4 × MAT2/MAT3,

2 × MAT0,

3 × MAT1

6 × PWM0/PWM1

1 × PCAP0,

2 × PCAP1

AOUT

VBAT

AHB TO

APB BRIDGE

SRAM

MII/RMII

V

BUS

DBGEN

P0, P2

AHB2

AHB1

control lines

13. LPC2478 block diagram

UM10237

Chapter 1: LPC24XX Introductory information

Fig 5. LPC2478 block diagram

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 15 of 792

Page 16

UM10237

Chapter 2: LPC24XX Memory mapping

Rev. 02 — 19 December 2008 User manual

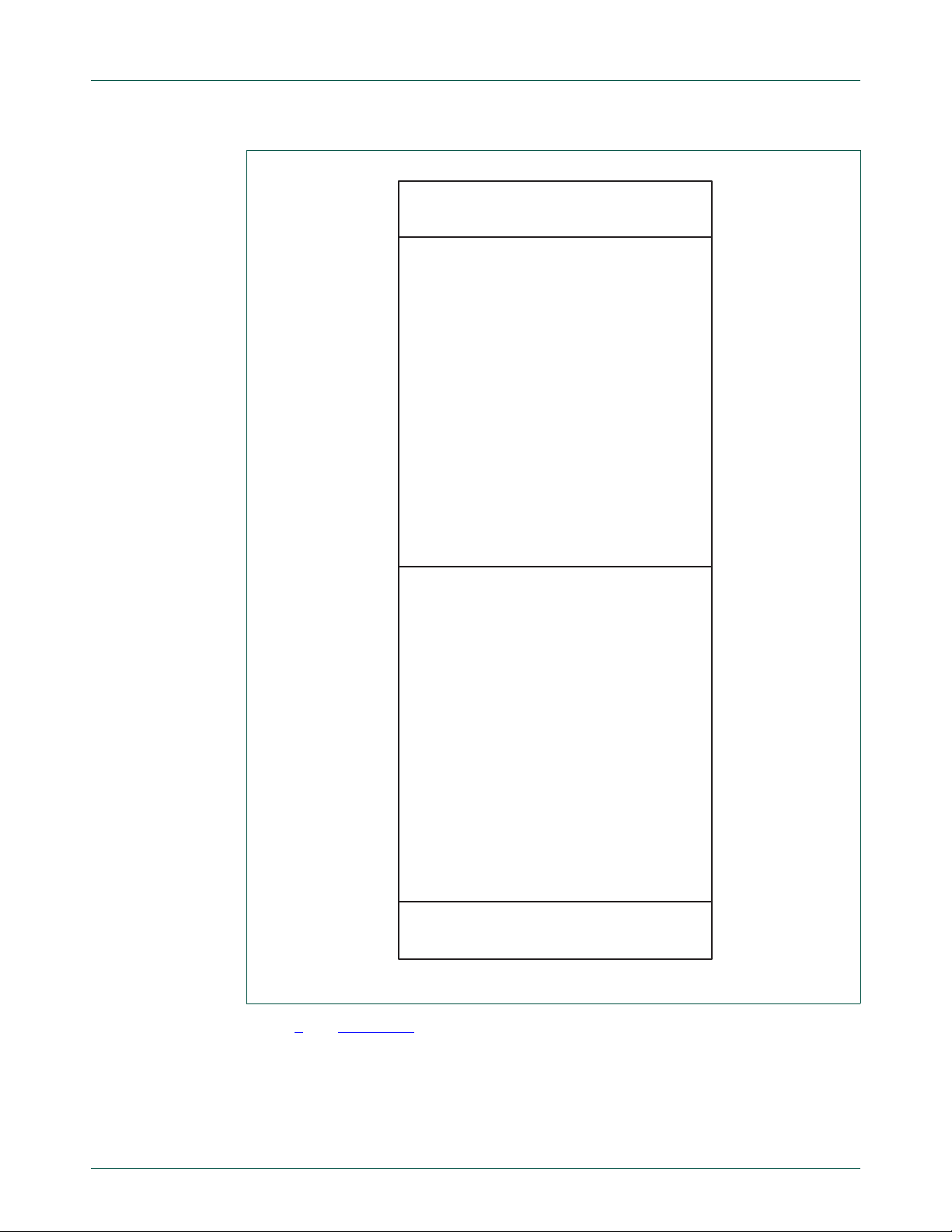

1. How to read this chapter

The memory addressing and mapping for dif fere nt LPC2400 parts depends on flash size,

EMC size, and the LCD peripheral, see Table 2–13

T able 13. LPC2400 memory options and addressing

LPC2458 512 kB no 16-bit Table 2–14

LPC2420 flashless no 32-bit Table 2–15

LPC2460 flashless no 32-bit Table 2–15

LPC2468 512 kB no 32-bit Table 2–16

LPC2470 flashless yes 32-bit Table 2–15

LPC2478 512 kB yes 32-bit Table 2–16

.

Flash LCD EMC Memory map

T able 2–19;

T able 2–21

Figure 2–8

2. Memory map and peripheral addressing

ARM processors have a single 4 GB address space. The following table shows how this

space is used on NXP embedded ARM devices.

Table 14. LPC2458 memory usage and details

Address range General use Address range details and description

0x0000 0000 to

0x3FFF FFFF

0x4000 0000 to

0x7FFF FFFF

0x8000 0000 to

0xDFFF FFFF

0xE000 0000 to

0xEFFF FFFF

0xF000 0000 to

0xFFFF FFFF

On-chip non-volatile

memory and Fast I/O

On-chip RAM 0x4000 0000 - 0x4000 FFFF RAM (64 k B)

Off-Chip Memory Two static memory banks, 16 MB each

APB Peripherals 36 peripheral blocks, 16 kB each

AHB peripherals

0x0000 0000 - 0x0007 FFFF Flash Memory (512 kB)

0x3FFF C 000 - 0x3FFF FFFF Fast GPIO registers

0x7FE0 0000 - 0x7FE0 3FFF Ethernet RAM (16 kB)

0x7FD0 000 0 - 0x7FD0 3FFF USB RAM (16kB)

0x8000 0000 - 0x80FF FFFF Static memory bank 0

0x8100 0000 - 0x81FF FFFF Static memory bank 1

Two dynamic memory banks, 256 MB each

0xA000 0000 - 0xAFFF FFFF Dynamic memory bank 0

0xB000 0000 - 0xBFFF FFFF Dynamic memory bank 1

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 16 of 792

Page 17

NXP Semiconductors

UM10237

Chapter 2: LPC24XX Memory mapping

Table 15. LPC2420/60/70 memory usage and details

Address range General use Address range details and description

0x0000 0000 to

0x3FFF FFFF

0x4000 0000 to

0x7FFF FFFF

Fast I/O 0x0000 0000 - 0x0007 FFFF Reserved (flashless parts)

0x3FFF C 000 - 0x3FFF FFFF Fast GPIO registers

On-chip RAM 0x4000 0000 - 0x4000 FFFF RAM (64 k B)

0x7FE0 0000 - 0x7FE0 3FFF Ethernet RAM (16 kB) (LPC2460

0x7FD0 000 0 - 0x7FD0 3FFF USB RAM (16kB)

0x8000 0000 to

0xDFFF FFFF

Off-Chip Memory Four static memory banks, 16 MB each

0x8000 0000 - 0x80FF FFFF Static memory bank 0

0x8100 0000 - 0x81FF FFFF Static memory bank 1

0x8200 0000 - 0x82FF FFFF Static memory bank 2

0x8300 0000 - 0x83FF FFFF Static memory bank 3

Four dynamic memory banks, 256 MB each

0xA000 0000 - 0xAFFF FFFF Dynamic memory bank 0

0xB000 0000 - 0xBFFF FFFF Dynamic memory bank 1

0xC000 0000 - 0xCFFF FFFF Dynamic memory bank 2

0xD000 0000 - 0xDFFF FFFF Dynamic memory bank 3

0xE000 0000 to

APB Peripherals 36 peripheral blocks, 16 kB each

0xEFFF FFFF

0xF000 0000 to

AHB peripherals

0xFFFF FFFF

only)

Table 16. LPC2468/78 memory usage and details

Address range General use Address range details and description

0x0000 0000 to

0x3FFF FFFF

0x4000 0000 to

0x7FFF FFFF

On-chip non-volatile

memory and Fast I/O

0x0000 0000 - 0x0007 FFFF Flash Memory (512 kB)

0x3FFF C 000 - 0x3FFF FFFF Fast GPIO registers

On-chip RAM 0x4000 0000 - 0x4000 FFFF RAM (64 k B)

0x7FE0 0000 - 0x7FE0 3FFF Ethernet RAM (16 kB)

0x7FD0 000 0 - 0x7FD0 3FFF USB RAM (16kB)

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 17 of 792

Page 18

NXP Semiconductors

Chapter 2: LPC24XX Memory mapping

Table 16. LPC2468/78 memory usage and details

Address range General use Address range details and description

0x8000 0000 to

0xDFFF FFFF

0xE000 0000 to

0xEFFF FFFF

0xF000 0000 to

0xFFFF FFFF

Off-Chip Memory Four static memory banks, 16 MB each

0x8000 0000 - 0x80FF FFFF Static memory bank 0

0x8100 0000 - 0x81FF FFFF Static memory bank 1

0x8200 0000 - 0x82FF FFFF Static memory bank 2

0x8300 0000 - 0x83FF FFFF Static memory bank 3

Four dynamic memory banks, 256 MB each

0xA000 0000 - 0xAFFF FFFF Dynamic memory bank 0

0xB000 0000 - 0xBFFF FFFF Dynamic memory bank 1

0xC000 0000 - 0xCFFF FFFF Dynamic memory bank 2

0xD000 0000 - 0xDFFF FFFF Dynamic memory bank 3

APB Peripherals 36 peripheral blocks, 16 kB each

AHB peripherals

UM10237

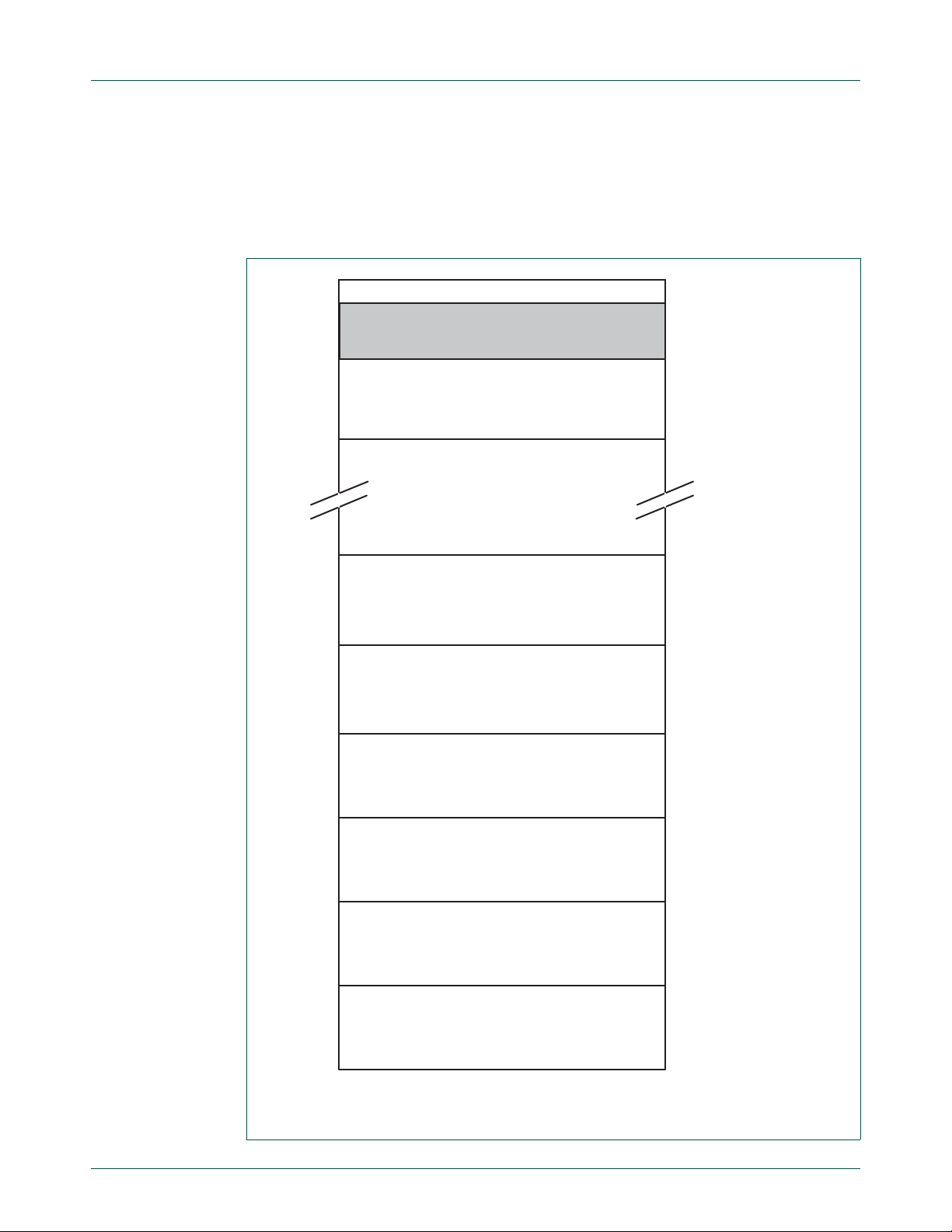

3. Memory maps

The LPC2400 incorporates several distinct memory regions, shown in the following

figures. Figure 2–6

program viewpoint following reset. The interrupt vector area supports address remapping,

which is described later in this section.

shows the overall map of the entire address space from the user

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 18 of 792

Page 19

NXP Semiconductors

0.0 GB

1.0 GB

ON-CHIP NON-VOLATILE MEMORY OR RESERVED

0x0000 0000

RESERVED ADDRESS SPACE

SPECIAL REGISTERS

ON-CHIP STATIC RAM

RESERVED ADDRESS SPACE

0x4000 0000

0x3FFF 8000

0x3FFF FFFF

2.0 GB 0x8000 0000

0x7FFF FFFF

BOOT ROM AND BOOT FLASH

EXTERNAL STATIC AND DYNAMIC MEMORY

3.75 GB

4.0 GB

3.5 GB

AHB PERIPHERALS

APB PERIPHERALS

0xE000 0000

0xF000 0000

0xFFFF FFFF

UM10237

Chapter 2: LPC24XX Memory mapping

Fig 6. LPC2400 system memory map

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 19 of 792

Page 20

NXP Semiconductors

RESERVED

RESERVED

0xF000 0000

0xEFFF FFFF

APB PERIPHERALS

0xE020 0000

0xE01F FFFF

0xE000 0000

AHB PERIPHERALS

0xFFFF FFFF

0xFFE0 0000

0xFFDF FFFF

3.75 GB

3.5 GB

3.5 GB + 2 MB

4.0 GB - 2 MB

4.0 GB

UM10237

Chapter 2: LPC24XX Memory mapping

Fig 7. Peripheral memory map

Figure 8 and Table 2–17 show different views of the peripheral address space. Both the

AHB and APB peripheral areas are 2 megabyte spaces which are divided up into 128

peripherals. Each peripheral space is 16 kilobytes in size. This allows simplifying the

address decoding for each peripheral.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 20 of 792

Page 21

NXP Semiconductors

VECTORED INTERRUPT CONTROLLER

(AHB PERIPHERAL #0)

0xFFFF F000 (4G - 4K)

0xFFFF C000

0xFFFF 8000

(AHB PERIPHERAL #4)

(AHB PERIPHERAL #3)

(AHB PERIPHERAL #2)

(AHB PERIPHERAL #1)

(AHB PERIPHERAL #126)

0xFFE1 8000

0xFFE1 4000

0xFFE1 0000

0xFFE0 C000

0xFFE0 8000

0xFFE0 4000

0xFFE0 0000

ETHERNET CONTROLLER

GENERAL PURPOSE DMA CONTROLLER

EXTERNAL MEMORY CONTROLLER

USB CONTROLLER

LCD

(1)

(AHB PERIPHERAL #5)

NOT USED

All peripheral register addresses are word aligned (to 32 bit boundaries) regardless of

their size. This eliminates the need for byte lane mapping hardware that would be required

to allow byte (8 bit) or half-word (16 bit) accesses to occur at smaller boundaries. An

implication of this is that word and half-word registers must be accessed all at once. For

example, it is not possible to read or write the upper byte of a word register separately.

UM10237

Chapter 2: LPC24XX Memory mapping

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 21 of 792

(1) LPC247x only.

Fig 8. AHB periphera l map

Page 22

NXP Semiconductors

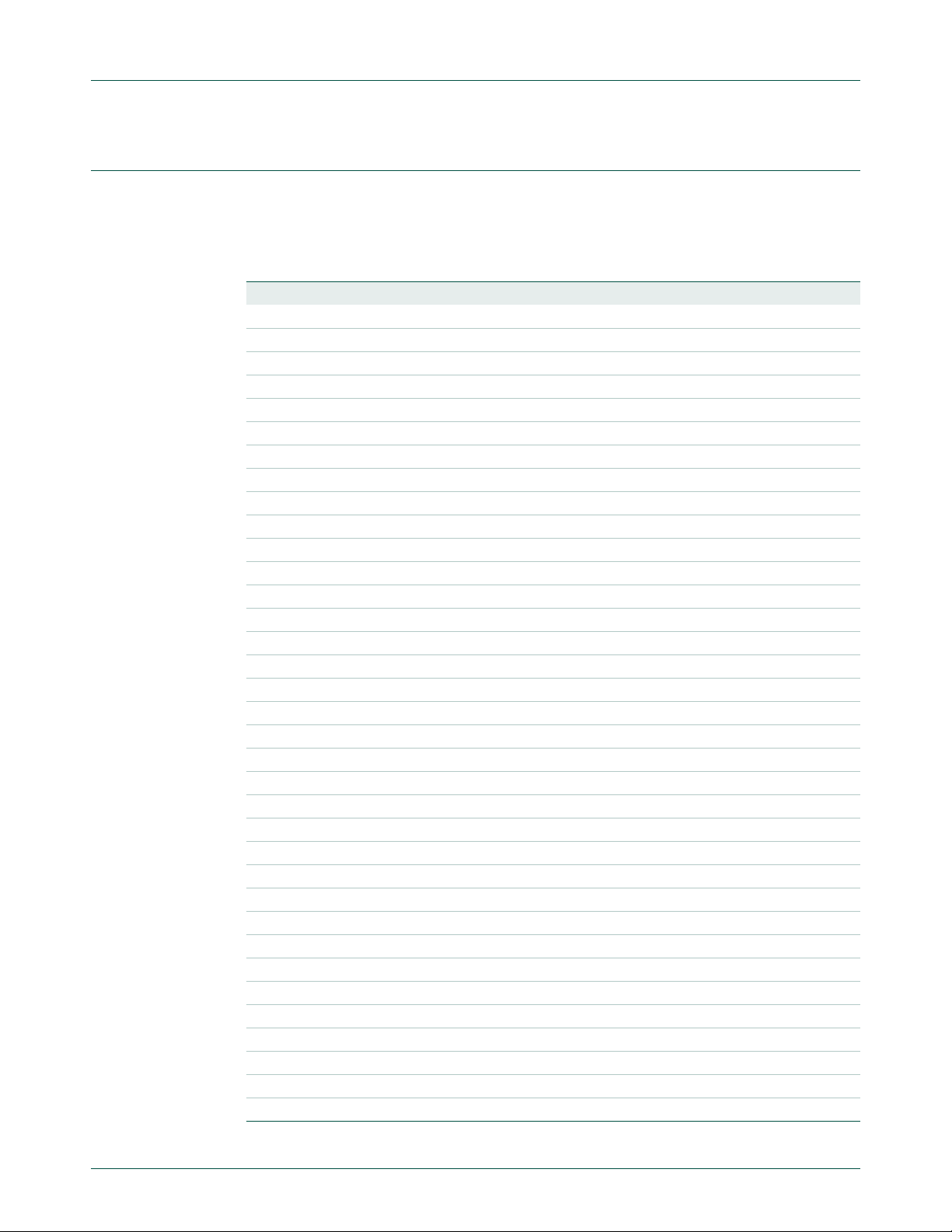

4. APB peripheral addresses

The following table shows the APB address map. No APB peripheral uses all of the 16 kB

space allocated to it. T ypically each device’ s registers are "aliased" or re peated at multiple

locations within each 16 kB range.

Table 17. APB peripherals and base addresses

APB Peripheral Base Address Peripheral Name

0 0xE000 0000 Watchdog Timer

1 0xE000 400 0 Timer 0

2 0xE000 800 0 Timer 1

3 0xE000 C000 UART0

4 0xE001 0000 UART1

5 0xE001 4000 PWM0

6 0xE001 8000 PWM1

7 0xE001 C000 I

8 0xE002 0000 SPI

9 0xE002 4000 RTC

10 0xE002 8000 GPIO

1 1 0xE002 C000 Pin Connect Block

12 0xE003 0000 SSP1

13 0xE003 4000 ADC

14 0xE003 800 0 CAN Acceptance Filter RAM

15 0xE003 C000 CAN Acceptance Filter Registers

16 0xE004 000 0 CAN Common Registers

17 0xE004 400 0 CAN Con trol ler 1

18 0xE004 800 0 CAN Con trol ler 2

19 to 22 0xE004 C000 to 0xE005 8000 Not used

23 0xE005 C000 I

24 0xE006 0000 Not used

25 0xE006 4000 Not used

26 0xE006 8000 SSP0

27 0xE006 C000 DAC

28 0xE007 000 0 Timer 2

29 0xE007 400 0 Timer 3

30 0xE007 8000 UART2

31 0xE007 C000 UART3

32 0xE008 0000 I

33 0xE008 4000 Battery RAM

34 0xE008 8000 I2S

35 0xE008 C000 SD/MMC Card Interface

36 to 126 0xE009 0000 to 0xE01F BFFF Not used

127 0xE01F C000 System Control Block

UM10237

Chapter 2: LPC24XX Memory mapping

2

C0

2

C1

2

C2

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 22 of 792

Page 23

NXP Semiconductors

Chapter 2: LPC24XX Memory mapping

5. LPC2400 memory re-mapping and boot ROM

5.1 Memory map concepts and operating modes

The basic concept on the LPC2400 is that each memory area has a "natural" location in

the memory map. This is the address range for which code residing in that area is written.

The bulk of each memory space remains permanently fixed in the same location,

eliminating the need to have portions of the code designed to run in different address

ranges.

Because of the location of the interrupt vectors on the ARM7 processor (at addresses

0x0000 0000 through 0x0000 001C, as shown in Table 2–18

Boot ROM and SRAM spaces need to be re-mapped in order to allow alternative uses of

interrupts in the differen t operating modes described in Table 2–19

interrupts is accomplished via the Memory Mapping Contro l feature (Section 2–6 “

mapping control” on page 25).

Table 18. ARM exception vector locations

Address Exception

0x0000 0000 Reset

0x0000 0004 Undefined Instruction

0x0000 0008 Software Interrupt

0x0000 000C Prefetch Abort (instruction fetch memory fault)

0x0000 0010 Data Abort (data access memory fault)

0x0000 0014 Reserved

Note: Identified as reserved in ARM documentation, this location is used

by the Boot Loader as the Valid User Program key when booting from

on-chip flash memory. This is described in detail in Section 30–5.1.1

0x0000 0018 IRQ

0x0000 001C FIQ

UM10237

below), a small portion of the

. Re-mapping of the

Memory

.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 23 of 792

Page 24

NXP Semiconductors

Table 19. LPC2400 Memory mapping modes

Mode Activation Usage

Boot

Loader

mode

User

Flash

mode

User RAM

mode

User

External

memory

mode

Hardware

activation by

any Reset

Software

activation by

Boot code

Software

activation by

User program

Software

activation by

user code

Software

activation by

boot code

UM10237

Chapter 2: LPC24XX Memory mapping

The Boot Loader always executes after any reset. The Boot ROM

interrupt vectors are mapped to the bottom of memory to allow

handling exceptions and using interrupts during the Boot Loading

process. A sector of the flash memory (the Boot flash) is available to

hold part of the Boot Code.

For LPC2400 parts with flash only . Activated by the Boot Loader when

a valid User Program Signature is recognized in memory and Boot

Loader operation is not forced. Interrupt vectors are not re-mapped

and are found in the bottom of the flash memory.

Activated by a User Program as desired. Interrupt vectors are

re-mapped to the bottom of the Static RAM.

For LPC2400 parts with flash. Interrupt vectors are re-mapped to

external memory bank 0.

For flashless parts LPC2420/60/70 only. Interrupt vectors are

re-mapped to external memory bank 0.

[1]

[2]

[1] See EMCControl register address mirror bit in Table 5–68 for address of external memory bank 0.

[2] Connect external boot memory to chip select 1. During boot from external memory, the address mirror bit is

set and memory bank addresses 0 and 1 are swapped.

5.2 Memory re-mapping

In order to allow for compatibility with future derivatives, the entire Boot ROM is mapped

to the top of the on-chip memory space. In this manner, the use of larger or smaller flash

modules will not require changing the location of the Boot ROM (which would require

changing the Boot Loader code itself) or changing the mapping of the Boot ROM interru pt

vectors. Memory spaces other than the interrupt vectors remain in fixed locations.

Figure 2–9

The portion of memory that is re-mapped to allow interrupt processing in different modes

includes the interrupt vector area (32 bytes) and an additional 32 bytes for a total of

64 bytes, that facilitates branching to interrupt handlers at distant physical addresses. The

remapped code locations overlay addresses 0x0000 0000 through 0x0000 003F. A typical

user program in the flash memory can place the entire FIQ handler at address

0x0000 001C without any nee d to cons ide r me mory boundaries. The vector contained in

the SRAM, external memory , and Boot ROM must cont ain branches to the actual interrupt

handlers, or to other instructions that accomplish the branch to the interrupt hand lers.

There are three reasons this configuration was chosen:

1. To give the FIQ handler in the flash memory the advantage of not having to take a

2. Minimize the need to for the SRAM and Boot ROM vectors to deal with arbitrary

3. To provide space to store constants for jumping beyond the range of single word

shows the on-chip memory mapping in the modes defined above.

memory boundary caused by the remapping into account.

boundaries in the middle of code space.

branch instructions.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 24 of 792

Page 25

NXP Semiconductors

Re-mapped memory areas, including the Boot ROM and interrupt vectors, continue to

appear in their original location in addition to the re-mapped address.

UM10237

Chapter 2: LPC24XX Memory mapping

Details on re-mapping and examples can be found in Section 2–6 “

control” on page 25.

6. Memory mapping control

The Memory Mapping Control alters the mapping of the interrupt vectors that appear

beginning at address 0x0000 0000. This allows code running in different memory spaces

to have control of the interrupts.

6.1 Memory Mapping Control Register (MEMMAP - 0xE01F C040)

Whenever an exception handling is necessary , the microcontroller will fetch an instruction

residing on exception corresponding address as described in Table 2–18 “

vector locations” on page 23. The MEMMAP register determines the source of data that

will fill this table.

Table 20. Memory mapping control registers

Name Description Access Reset

MEMMAP Memory mapping control. Selects whether the

ARM interrupt vectors are read from the Boot

ROM, User Flash, or RAM.

Table 21. Memory Mapping control register (MEMMAP - address 0xE01F C040) bit

description

Bit Symbol Value Description Reset

1:0 MAP 00 Boot Loader Mode. Interrupt vectors are re-mapped to Boot ROM. 00

01 User Flash Mode. Interrupt vectors are not re-mapped and reside

10 User RAM Mode. Interrupt vect ors are re-mapped to Static RAM.

11 User External Memory Mode. Interrupt vectors are re-mapped to

Warning: Improper setting of this value may result in incorrect operation of

the device.

7:2 - - Reserved, user software should not write ones to reserved bits.

Memory mapping

ARM exception

Address

value

R/W 0x00 0xE01F C040

value

in Flash.

Remark: This mode is for parts with flash only. Value 01 is

reserved for flashless parts LPC2420/60/70.

external memory bank 0.

NA

The value read from a reserved bit is not defined.

6.2 Memory mapping control usage notes

Memory Mapping Control simply selects one out of three available sources of data (set s of

64 bytes each) necessary for handling ARM exceptions (interrupts).

For example, whenever a Software Interrupt request is generated, ARM core will always

fetch 32 bit data "residing" on 0x0000 0008 see Table 2–18 “

locations” on page 23. This means that when MEMMAP[1:0] = 10 (User RAM Mode),

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 25 of 792

ARM exception vector

Page 26

NXP Semiconductors

0.0 GB

0x8000 0000

0x4000 0000

0x3FFF FFFF

0x0000 0000

1.0 GB

2.0 GB - 8 kB

2.0 GB

ACTIVE INTERRUPT VECTORS

(FROM FLASH, SRAM, BOOT ROM, OR EXT MEMORY)

BOOT FLASH

RESERVED ADDRESS SPACE

(SRAM INTERRUPT VECTORS)

512 kB FLASH MEMORY

RESERVED FOR ADDRESS SPACE

(BOOT ROM INTERRUPT VECTORS)

8 kB BOOT ROM

64 kB STATIC RAM

0x7FFF FFFF

FAST GPIO REGISTERS

PARTCFG REGISTERS

0x3FFF 8000

0x3FFF C000

0x3FFF BFFF

8 kB BOOT FLASH

(RE-MAPPED FROM TOP OF FLASH MEMORY)

EXTERNAL MEMORY INTERRUPT VECTORS

0x7FFF E000

0x7FFE FFFF

0x7FFE E000

2.0 GB - 64 kB

2.0 GB - 72 kB

0x0007 FFFF

0x0008 0000

0x4001 0000

0x4000 FFFF

read/fetch from 0x0000 0008 will provide data stored in 0x4000 0008. In case of

MEMMAP[1:0] = 00 (Boot Loader Mode), read/fetch from 0x0000 0008 will provide data

available also at 0x7FFF E008 (Boot ROM remapped from on-chip Bootloader).

UM10237

Chapter 2: LPC24XX Memory mapping

Fig 9. Map of lower memory is showing re-mapped and re-mappable areas for a

UM10237_2 © NXP B.V. 2008. All rights reserved.

LPC2400 part with flash

User manual Rev. 02 — 19 December 2008 26 of 792

Page 27

NXP Semiconductors

7. Prefetch abort and data abort exceptions

The LPC2400 generates the appropriate bus cycle abort exception if an access is

attempted for an address that is in a reserved or unassigned address region. The regions

are:

• Areas of the memory map that are not implemented for a specific ARM derivative. Fo r

the LPC2400, these are:

– Address space between On-Chip Non-Volatile Memory and the Special Register

space. Labelled "Reserved for On-Chip Memory" in Figure 2–6

– Address space between On-Chip Static RAM and the Boot ROM. Labelled

"Reserved Address Space" in Figure 2–6

– External Memory

– Reserved regions of the AHB and APB spaces. See Figure 2–7

• Unassigned AHB peripheral spaces. See Figure 2–8.

• Unassigned APB peripheral spaces. See Table 2–17.

For these areas, both attempted data acce ss and in struction fetch genera te an exception.

In addition, a Prefetch Abort exception is generated for an y instruction fetch that maps to

an AHB or APB peripheral address, or to the Special Register space located just below

the SRAM at addresses 0x3FFF8000 through 0x3FFFFFFF.

UM10237

Chapter 2: LPC24XX Memory mapping

.

.

.

Within the address space of an existing APB peripheral, a data abort exception is not

generated in response to an access to an undefined address. Address decoding within

each peripheral is limited to that needed to distinguish defined registers within the

peripheral itself. For example, an access to address 0xE000 D000 (an undefined address

within the UART0 space) may result in an access to the register defined at address

0xE000 C000. Details of such address aliasing within a peripheral space are not defined

in the LPC2400 documentation and are not a supported feature.

If software executes a write directly to the flash mem ory, the MAM generates a data abort

exception. Flash programming must be accomplished by using the specified flash

programming interface provided by the Boot Code.

Note that the ARM core stores the Prefetch Abort flag along with the associated

instruction (which will be meaningless) in the pipeline and processes the abort only if an

attempt is made to execute the instruction fetched from the illegal address. This prevents

accidental aborts that could be caused by prefetches that occur when code is executed

very near a memory boundary.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 27 of 792

Page 28

UM10237

Chapter 3: LPC24XX System control

Rev. 02 — 19 December 2008 User manual

1. Summary of system control block functions

The System Control Block includes several system features and control registers for a

number of functions that are not related to specific peripheral devices. These include:

• Reset

• Brown-Out Detection

• External Interrupt Input s

• Miscellaneous System Controls and Status

• Code Security vs. Debugging

Each type of function has its own register(s) if any are required and unneeded bit s are

defined as reserved in order to allow future expansion. Unrelated functions never share

the same register addresses

2. Pin description

Table 3–22 shows pins that are associated with system control block functions.

Table 22. Pin summary

Pin name Pin

EINT0 Input External Interrupt Input 0 - An active low/high level or

EINT1 Input External Interrupt Input 1 - See the EINT0 description above.

EINT2 Input External Interrupt Input 2 - See the EINT0 description above.

EINT3 Input External Interrupt Input 3 - See the EINT0 description above.

RESET

3. Register description

All registers, regardless of size, are on word address boundaries. Details of the registers

appear in the description of each function.

T able 23. Summary of system control registers

Name Description Access Reset value

External interrupts

EXTINT External Interrupt Flag Register R/W 0x00 0xE01F C140

EXTMODE External Interrupt Mode register R/W 0x00 0xE01F C148

EXTPOLAR External Interrupt Polarity Register R/W 0x00 0xE01F C14C

Pin description

direction

falling/rising edge general purpose interrupt input. This pin may be

used to wake up the processor from Idle or Power down modes.

Input External Reset input - A LOW on this pin resets the chip, causing

I/O ports and peripherals to take on their default states, and the

processor to begin execution at address 0x0000 0000.

[1]

Address

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 28 of 792

Page 29

NXP Semiconductors

T able 23. Summary of system control registers

Name Description Access Reset value

Reset

RSID Reset Source Identification

Syscon miscellaneous registers

SCS System Control and Status R/W 0x00 0xE01F C1A0

AHB priority scheduling registers

AHBCFG1 Configures the AHB1 arbiter R/W 0x0000 0145 0xE01F C188

AHBCFG2 Configures the AHB2 arbiter R/W 0x0000 0145 0xE01F C18C

[1] Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

3.1 External interrupt inputs

The LPC2400 includes four External Interrupt Inputs as selectable pin functions. In

addition, external interrupts have the ability to wake up the CPU from Power down mode.

This is controlled by the register INTWAKE, which is described in the Clocking and Power

Control chapter under the Power Control heading

Register

UM10237

Chapter 3: LPC24XX System control

[1]

Address

R/W see text 0xE01F C180

3.1.1 Register description

The external interrupt function has four registers associated with it. The EXTINT register

contains the interrupt flags. The EXTMODE and EXTPOLAR registers specify the level

and edge sensitivity parameters.

Table 24. External Interrupt registers

Name Description Access Reset

EXTINT The External Interrupt Flag Register contains

interrupt flags for EINT0, EINT1, EINT2 and

EINT3. See Table 3–25

EXTMODE The External Interrupt Mode Registe r control s

whether each pin is edge- or level-sensitive.

See Table 3–26

EXTPOLAR The External Interrupt Polarity Register controls

which level or edge on each pin will cause an

interrupt. See Table 3–27

[1] Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

.

.

.

R/W 0x00 0xE01F C140

R/W 0x00 0xE01F C148

R/W 0x00 0xE01F C14C

3.1.2 External Interrupt flag register (EXTINT - 0xE01F C140)

When a pin is selected for its external interrupt function, the level or edge on that pin

(selected by its bits in the EXTPOLAR a nd EXTMODE registers) will set its interrup t flag in

this register. This asserts the corresponding interrupt request to the VIC, which will cause

an interrupt if interrupts from the pin are enabled.

value

Address

[1]

Writing ones to bits EINT0 through EINT3 in EXTINT register clears the corresponding

bits. In level-sensitive mode the interrupt is cleared only when the pin is in its inactive

state.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 29 of 792

Page 30

NXP Semiconductors

Once a bit from EINT0 to EINT3 is set and an appropriate code st arts to execute (hand ling

wakeup and/or external interrupt), this bit in EXTINT register must be cleared. Otherwise

event that was just triggered by activity on the EINT pin will not be recognized in future.

Important: whenever a change of external interrupt operating mode (i.e. active

level/edge) is performed (including the initialization of an external interrupt),

corresponding bit in the EXTINT register must be cleared! For details see Section

3–3.1.3 “External Interrupt Mode register (EXTMODE - 0xE01F C148)” and Section

3–3.1.4 “External Interrupt Polarity register (EXTPOLAR - 0xE01F C14C)”.

For example, if a system wakes up from power-down using low level on external interrupt

0 pin, its post-wakeup code must reset EINT0 bit in order to allow future entry into the

power-down mode. If EINT0 bit is left set to 1, subsequent attempt(s) to invoke

power-down mode will fail. The same goes for external interrupt handling.

More details on power-down mode will be discussed in the following chapters.

Table 25. External Interrupt Flag register (EXTINT - address 0xE01F C140) bit description

Bit Symbol Description Reset

0 EINT0 In level-sensitive mode, this bit is set if the EINT0 function is selected for its

1 EINT1 In level-sensitive mode, this bit is set if the EINT1 function is selected for its

2 EINT2 In level-sensitive mode, this bit is set if the EINT2 function is selected for its

3 EINT3 In level-sensitive mode, this bit is set if the EINT3 function is selected for its

7:4 - Reserved, user software should not write ones to reserved bits. The value

UM10237

Chapter 3: LPC24XX System control

pin, and the pin is in its active state. In edge-sensitive mode, this bit is set if

the EINT0 function is selected for its pin, and the selected edge occurs on

the pin.

This bit is cleared by writing a one to it, except in level sensitive mode when

the pin is in its active state.

pin, and the pin is in its active state. In edge-sensitive mode, this bit is set if

the EINT1 function is selected for its pin, and the selected edge occurs on

the pin.

This bit is cleared by writing a one to it, except in level sensitive mode when

the pin is in its active state.

pin, and the pin is in its active state. In edge-sensitive mode, this bit is set if

the EINT2 function is selected for its pin, and the selected edge occurs on

the pin.

This bit is cleared by writing a one to it, except in level sensitive mode when

the pin is in its active state.

pin, and the pin is in its active state. In edge-sensitive mode, this bit is set if

the EINT3 function is selected for its pin, and the selected edge occurs on

the pin.

This bit is cleared by writing a one to it, except in level sensitive mode when

the pin is in its active state.

read from a reserved bit is not defined.

[1]

[1]

[1]

[1]

value

0

0

0

0

NA

[1] Example: If the EINTx is selected to be low level sensitive and low level is present on corresponding pin,

this bit can not be cleared; this bit can be cleared only when signal on the pin becomes high.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 30 of 792

Page 31

NXP Semiconductors

3.1.3 External Interrupt Mode register (EXTMODE - 0xE01F C148)

The bits in this register select whether ea ch EINT pin is le vel- or edge- sensitive. Only pins

that are selected for the EINT function (see Section 9–5.5

VICIntEnable register (Section 7–3.4 “

0xFFFF F010)”) can cause interrupts from the External Interrupt function (though of

course pins selected for other functions may cause interrupts from those functions).

Note: Software should only change a bit in this register when its interrupt is

disabled in VICIntEnable, and should write the corresponding 1 to EXTINT before

enabling (initializing) or re-enabling the interrupt. An extraneous interrupt(s) could

be set by changing the mode and not having the EXTINT cleared.

Table 26. External Interrupt Mode register (EXTMODE - address 0xE01F C148) bit

Bit Symbol Value Description Reset

0 EXTMODE0 0 Level-sensitivity is selected for EINT0

1 EXTMODE1 0 Level-sensitivity is selected for EINT1

2 EXTMODE2 0 Level-sensitivity is selected for EINT2

3 EXTMODE3 0 Level-sensitivity is selected for EINT3

7:4 - - Reserved, user software should not write ones to reserved

description

1EINT0

1EINT1

1EINT2

1EINT3

UM10237

Chapter 3: LPC24XX System control

) and enabled in the

Interrupt Enable Register (VICIntEnable -

value

.0

is edge sensitive.

.0

is edge sensitive.

.0

is edge sensitive.

.0

is edge sensitive.

NA

bits. The value read from a reserved bit is not defined.

3.1.4 External Interrupt Polarity register (EXTPOLAR - 0xE01F C14C)

In level-sensitive mode, the bits in this register select whether the corresponding pin is

high- or low-active. In edge-sensitive mode, they select whether the pin is rising- or

falling-edge sensitive. Only pins that are selected for the EINT function (see

Section 9–5.5

Register (VICIntEnable - 0xFFFF F010)”) can cause interrupts from the External Interrupt

function (though of course pins selected for other functions may cause interrupts from

those functions).

Note: Software should only change a bit in this register when its interrupt is

disabled in VICIntEnable, and should write the corresponding 1 to EXTINT before

enabling (initializing) or re-enabling the interrupt. An extraneous interrupt(s) could

be set by changing the polarity and not having the EXTINT cleared.

) and enabled in the VICIntEnable register (Section 7–3.4 “Interrupt Enable

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 31 of 792

Page 32

NXP Semiconductors

Table 27. External Interrupt Polarity register (EXTPOLAR - address 0xE01F C14C) bit

Bit Symbol Value Description Reset

0EXTPOLAR00 EINT0

1EXTPOLAR10 EINT1

2EXTPOLAR20 EINT2

3EXTPOLAR30 EINT3

7:4 - - Reserved, user software should not write ones to reserved

description

1EINT0

1EINT1

1EINT2

1EINT3

UM10237

Chapter 3: LPC24XX System control

is low-active or falling-edge sensitive (depending on

EXTMODE0).

is high-active or rising-edge sensitive (depending on

EXTMODE0).

is low-active or falling-edge sensitive (depending on

EXTMODE1).

is high-active or rising-edge sensitive (depending on

EXTMODE1).

is low-active or falling-edge sensitive (depending on

EXTMODE2).

is high-active or rising-edge sensitive (depending on

EXTMODE2).

is low-active or falling-edge sensitive (depending on

EXTMODE3).

is high-active or rising-edge sensitive (depending on

EXTMODE3).

bits. The value read from a reserved bit is not defined.

value

0

0

0

0

NA

3.2 Reset

Reset has four sources on the LPC2400: the RESET pin, the Watchdog Reset, Power On

Reset (POR) and the Brown Out Detection circuit (BOD). The RESET

trigger input pin. Assertion of chip Reset by any source, once the operating volt age attains

a usable level, starts the W akeup Timer (see description in Section 4–5 “

this chapter), causing reset to remain asserted until the external Reset is de-asserted, the

oscillator is running, a fixed number of clocks have passed, and the flash controller has

completed its initialization. The reset logic is shown in Figure 3–10

pin is a Schmitt

Wakeup timer” in

.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 32 of 792

Page 33

NXP Semiconductors

C

Q

S

APB read of

PDBIT

in PCON

power

down

C

Q

S

F

OSC

to other

blocks

WAKEUP TIMER

watchdog

reset

external

reset

START

COUNT 2

n

internal RC

oscillator

Reset to the

on-chip circuitry

Reset to

PCON.PD

write “1”

from APB

reset

EINT0 wakeup

EINT1 wakeup

EINT2 wakeup

POR

BOD

EINT3 wakeup

RTC wakeup

BOD wakeup

Ethernet MAC wakeup

USB need_clk wakeup

CAN wakeup

GPIO0 port wakeup

GPIO2 port wakeup

UM10237

Chapter 3: LPC24XX System control

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 33 of 792

Fig 10. Reset block diagram including the wakeup timer

On the assertion of any of reset sources (POR, BOD reset, External reset and Watchdog

reset), the following two sequences start simultaneously:

1. After IRC-start-up time (maximum of 60 μs on power-up), IRC provides stable clock

output, the reset signal is latched and synchronized on the IRC clock. The 2-bit IRC

wakeup timer starts counting when the synchronized reset is de-asserted. The boot

code in the ROM starts when the 2-bit IRC wakeup timer times out. The boot code

performs the boot tasks and may jump to the flash. If the flash is not ready to access,

the MAM will insert wait cycles until the flash is ready.

2. After IRC-start-up time (maximum of 60 μs on power-up), IRC provides stable clock

output, the reset signal is synchronized on the IRC clock. The flash wakeup-timer

(9-bit) starts counting when the synchronized reset is de-asserted. The flash

wakeup-timer generates the 100 μs flash start-up time. Once it times out, the flash

initialization sequence is started, which takes about 250 cycles. When it’s do ne, the

MAM will be granted access to the flash.

When the internal Reset is removed, the processor begins executing at address 0, which

is initially the Reset vector mapped from the Boot Block. At that point, all of the processor

and peripheral registers have been initialized to predetermined values.

Figure 3–11

processor status when the LPC2400 star ts up af ter reset. For the st art-up sequence of the

main oscillator if enabled by the user code, see Section 4–2.2 “

shows an example of the relationship between the RESET, the IRC, and the

Main oscillator”.

Page 34

NXP Semiconductors

valid threshold

processor status

V

DD(3V3)

IRC status

RESET

GND

002aad482

30 μs

1 μs; IRC stability count

8 μs

170 μs

160 μs

boot time user code

boot code

execution

finishes;

user code starts

IRC

starts

IRC

stable

flash read

finishes

flash read

starts

supply ramp-up

time

UM10237

Chapter 3: LPC24XX System control

Fig 11. E xample of start-up after reset

The various Resets have some small dif ferences. For example, a Power On Reset causes

the value of certain pins to be latched to configure the part.

For more details on Reset, PLL and startup/boot code interaction see Section 4–3.2.2

“PLL and startup/boot code interaction”.

3.2.1 Reset Source Identification Register (RSIR - 0xE01F C180)

This register contains one bit for each source of Reset. Writing a 1 to any of these bits

clears the corresponding read-side bit to 0. The interactions among the four sources are

described below.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 34 of 792

Page 35

NXP Semiconductors

Table 28. Reset Source Identification register (RSID - address 0xE01F C180) bit description

Bit Symbol Description Reset

0 POR Assertion of the POR signal sets this bit, and clears all of the other bits in

1 EXTR Assertion of the RESET

2 WDTR This bit is set when the Watchdog Timer times out and the WDTRESET

3 BODR This bit is set when the 3.3 V power reaches a level below 2.6 V.

7:4 - Reserved, user software should not write ones to reserved bits. The

UM10237

Chapter 3: LPC24XX System control

this register. But if another Reset signal (e.g., External Reset) remains

asserted after the POR signal is negated, then its bit is set. This bit is not

affected by any of the other sources of Reset.

signal sets this bit. This bit is cleared by POR,

but is not affected by WDT or BOD reset.

bit in the Watchdog Mode Register is 1. It is cleared by any of the other

sources of Reset.

If the V

will be set to 1.

If the V

to the level at which POR is asserted (nominally 1 V), the BODR bit is

cleared.

if the V

2.6 V, the BODR will be set to 1.

This bit is not affected by External Reset nor Watchdog Reset.

Note: Only in case when a reset occurs and the POR = 0, the BODR bit

indicates if the V

value read from a reserved bit is not defined.

voltage dips from 3.3 V to 2.5 V and backs up, the BODR bit

DD

voltage dips from 3.3 V to 2.5 V and continues to decline

DD(3V3)

voltage rises continuously from below 1 V to a level above

DD(3V3)

voltage was below 2.6 V or not.

DD(3V3)

value

See text

See text

See text

See text

NA

3.3 Other system controls and status flags

Some aspects of controlling LPC2400 operation that do not fit into peripheral or other

registers are grouped here.

3.3.1 System Controls and Status register (SCS - 0xE01F C1A0)

Table 29. System Controls and Status register (SCS - address 0xE01F C1A0) bit description

Bit Symbol Value Description Access Reset

0 GPIOM GPIO access mode selection. R/W 0

1EMC Reset

[1]

Disable

value

0 GPIO ports 0 and 1 are accessed via APB addresses in a fashion

compatible with previous LPC2000 devices.

1 High spe ed GPIO is enabled on ports 0 and 1, accessed via addresses in

the on-chip memory range. This mode includes the port masking feature

described in the GPIO chapter.

External Memory Controller Reset Disable. R/W 0

0 Both EMC resets are asserted when any type of reset event occurs. In this

mode, all registers and functions of the EMC are initialized upon any reset

condition.

1 Many portions of the EMC are only reset by a power-on or brown-out event,

in order to allow the EMC to retain its state through a warm reset (external

reset or watchdog reset). If the EMC is configured correctly, auto-refresh can

be maintained through a warm reset.

UM10237_2 © NXP B.V. 2008. All rights reserved.

User manual Rev. 02 — 19 December 2008 35 of 792

Page 36

NXP Semiconductors

UM10237

Chapter 3: LPC24XX System control

Table 29. System Controls and Status register (SCS - address 0xE01F C1A0) bit description

Bit Symbol Value Description Access Reset

value

2 - - Reserved. User software should not write ones to reserved bits. The value

read from a reserved bit is not defined.

3 MCIPWR

Active

[1]

Level

4 OSCRANGE Main oscillator range select. R/W 0

5 OSCEN Main oscillator enable. R/W 0

6 OSCSTAT Main oscillator status. RO 0

31:7 - - Reserved. User software should not write ones to reserved bits. The value

0 The MCIPWR pin is low.

1 The MCIPWR pin is high.

0 The frequency range of the main oscillator is 1 MHz to 20 MHz.

1 The frequency range of the main oscillator is 15 MHz to 24 MHz.

0 The main oscillator is disabled.

1 The main oscillator is enabled, and will start up if the correct external

0 The main oscillator is not ready to be used as a clock source.

1 The main oscillator is ready to be used as a clock source. The main

MCIPWR pin control. R/W 0

circuitry is connected to the XTAL1 and XTAL2 pins.

oscillator must be enabled via the OSCEN bit.