Page 1

AN10881

TEA1713 resonant power supply control IC with PFC

Rev. 2 — 26 September 2011 Application note

Document information

Info Content

Keywords TEA1713, adapter, LCD TV, Plasma TV, resonant, converter, PFC,

Burst mode

Abstract The TEA1713 integrates a controller for Power Factor Correction (PFC)

and a controller for a half-bridge resonant converter (HBC).

It provides the drive function for the discrete MOSFET for the up-converter

and for the two discrete power MOSFETs in a resonant half-bridge

configuration.

The resonant controller part is a high-voltage controller for a zero voltage

switching LLC resonant converter. The resonant controller part of the IC

includes a high-voltage level shift circuit and several protection features

such as overcurrent protection, open-loop protection, Capacitive mode

protection and a general purpose latched protection input.

In addition to the resonant controller, the TEA1713 also contains a Power

Factor Correction (PFC) controller. The efficient operation of the PFC is

obtained by functions such as quasi-resonant operation at high power

levels and quasi-resonant operation with valley skipping at lower power

levels. Overcurrent protection, overvoltage protection and

demagnetization sensing, ensures safe operation in all conditions.

The proprietary high-voltage BCD Powerlogic process makes direct

start-up possible from the rectified universal mains voltage in an efficient

way. A second low voltage Silicon-On-Insulator (SOI) IC is used for

accurate, high speed protection functions and control.

The combination of PFC and a resonant controller in one IC makes the

TEA1713 suitable for power supplies in LCD TV, plasma televisions, PC

power supplies, high-power office equipment and adapters.

This application note discusses the TEA1713 functions for applications.

Page 2

NXP Semiconductors

AN10881

TEA1713 resonant power supply control IC with PFC

Table 1. Revision history

Rev Date Description

02 20110926 Second, updated release

01 20100322 First release

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 2 of 102

Page 3

NXP Semiconductors

1. Introduction

1.1 Scope and setup

This application note discusses the TEA1713 functions for applications in general.

Because the TEA1713 provides extensive functionality, many subjects are discussed.

This document is set up in such a way, that a chapter or paragraph of a selected subject

can be read as a standalone explanation with a minimum of cross-references to other

document parts or the data sheet. This leads to some repetition of information within the

application note and to descriptions or figures that are similar to those published in the

TEA1713 data sheet. In most cases typical values are given to enhance the readability.

• Section 1 “Introduction”

• Section 2 “TEA1713 highlights and features”

• Section 3 “Pin overview with functional description”

• Section 4 “Application diagram and block diagrams”

• Section 5 “Supply functions”

• Section 6 “MOSFET drivers GATEPFC, GATELS and GATEHS”

• Section 7 “PFC functions”

• Section 8 “HBC functions”

• Section 9 “Burst mode operation”

• Section 10 “Protection functions”

• Section 11 “Miscellaneous advice and tips”

• Section 12 “Application examples and topologies”

• Section 13 “Differences between TEA1713T and TEA1713LT”

AN10881

TEA1713 resonant power supply control IC with PFC

An overview of the TEA1713 pins with a summary of the functionality.

Sections 6, 7, 8, 9, and 10 describe the main functions of the TEA1713, providing an

in-depth explanation of the issues relating to the subject. The functions are written

from an application point of view .

An overview of the protection functions of th e TEA1713 with an exte nded expl anation

and related issues on the subject. These functions are described and seen from an

applications point of view.

A collection of subjects related to PCB design and debugging are discussed, including

proposals for the way of working.

This section contains examples of applications (circuit diagrams) and possible

topologies.

An overview of the differences between the TEA1713T and the TEA1713LT.

Remark: All values provided throughout this document are typical values unless

otherwise stated.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 3 of 102

Page 4

NXP Semiconductors

1.2 Related documents

Additional information and tools can be found in other TEA1713 documents such as:

• Data sheet

• User manual of demo board

• Calculation sheet

AN10881

TEA1713 resonant power supply control IC with PFC

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 4 of 102

Page 5

NXP Semiconductors

2. TEA1713 highlights and features

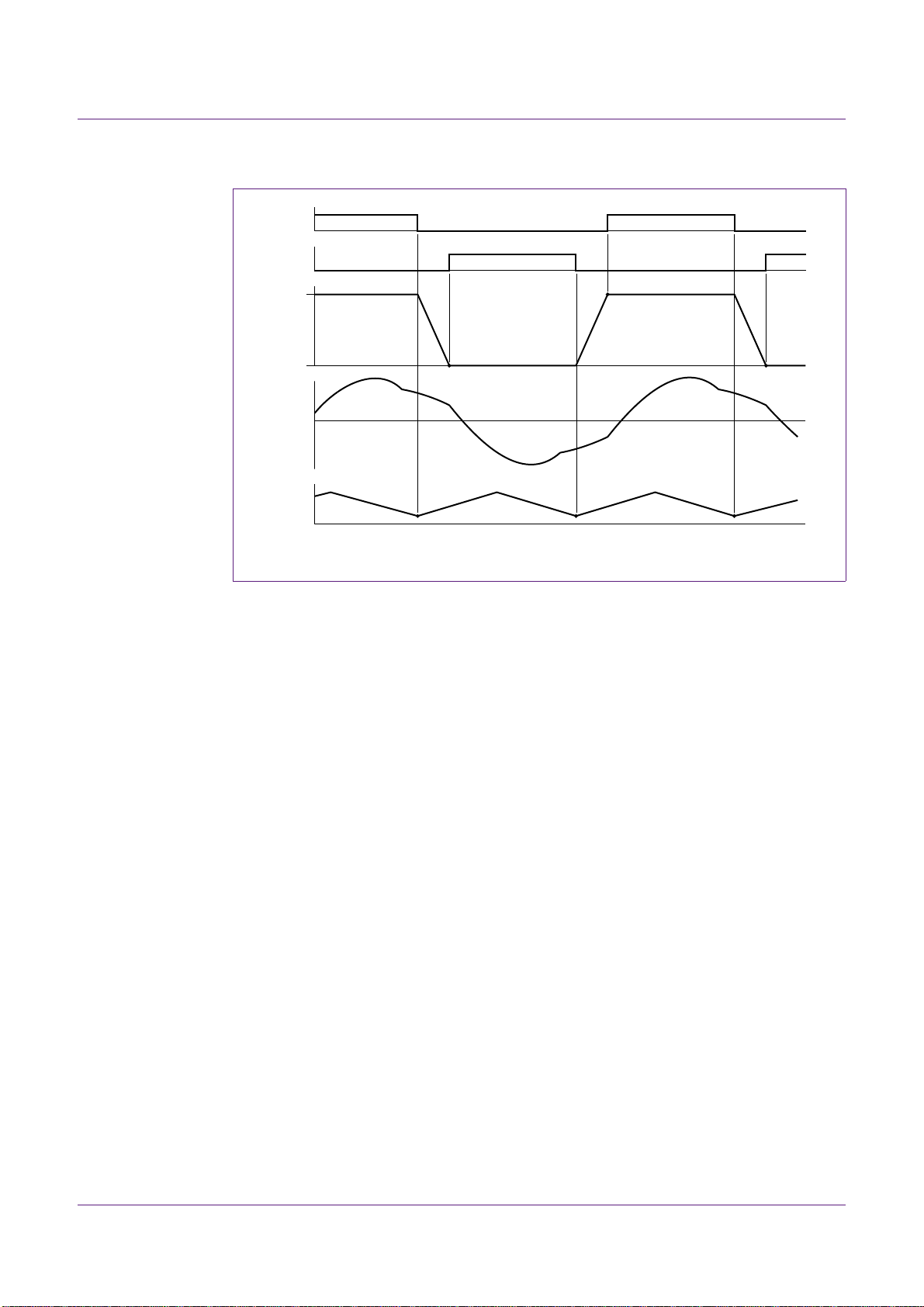

2.1 Resonant conversion

Today’s market demands high-quality, reliable, small, lightweight and efficient power

supplies.

In principle, the higher the operating frequency, the smaller and lighter the transformers,

filter inductors and capacitors can be. On the other hand, the core, switching and winding

losses of the transformer increase at higher frequencies and become dominant. This

effect reduces the efficiency at a high frequency, which limits the minimum size of the

transformer.

The corner frequency of the output filter usually determines the bandwidth of the control

loop. A well-chosen corner frequency allows high operating frequencies to achieve a fast

dynamic response.

Pulse Width Modulated (PWM) power converters, such as flyback, up and down

converters, are widely used in low and medium power applications. A disadvantage of

these converters is that the PWM rectangular voltage and current waveforms cause

turn-on and turn-off losses that limit the operating frequency. The rectangular waveforms

also generate broadband electromagnetic energy that can produce ElectroMagnetic

Interference (EMI).

AN10881

TEA1713 resonant power supply control IC with PFC

A resonant DC-to-DC converter produces sinusoidal waveforms and reduces the

switching losses, which provide the possibility of operation at higher frequencies.

Recent environmental considerations have resulted in a need for high efficiency

performance at low loads. Burst mode operation of the resonant converter can provide

this if the converter is required to remain active as is the case for adapter applications.

Why resonant conversion?

• High power

• High efficiency

• EMI friendly

• Compact

2.2 Power factor correction conversion

Most switch mode power supplies result in a non-linear impedance (load characteristic) to

the mains input. Current taken from the mains supply occurs only at the highest voltage

peaks and is stored in a large capacitor. The energy is taken from this capacitor storage,

in accordance with the switch mode power supply operation characteristics.

Government regulations dictate special requirements for the load characteristics of certain

applications. Two main requirements can be distinguished:

• Mains harmonics requirements EN61000-3-2

• Power factor (real power/apparent power)

The requirements work towards a more resistive characteristic of the mains load.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 5 of 102

Page 6

NXP Semiconductors

Measures are required regarding the input circuit of the power supply to fulfill these

requirements. Passive (often a series coil) or active (often a boost converter) circuits can

be used to modify the mains load characteristics accordingly.

An additional market requirement for the added mains input circuit is that it works with a

good efficiency and have a low cost.

Using a boost converter to meet these requirements provides the benefit of a fixed DC

input voltage when combined with a resonant converter. The fixed input voltage provides

easier design of the resonant converter (specially for wide mains input voltage ra nge

applications) and the possibility to reach a higher efficiency.

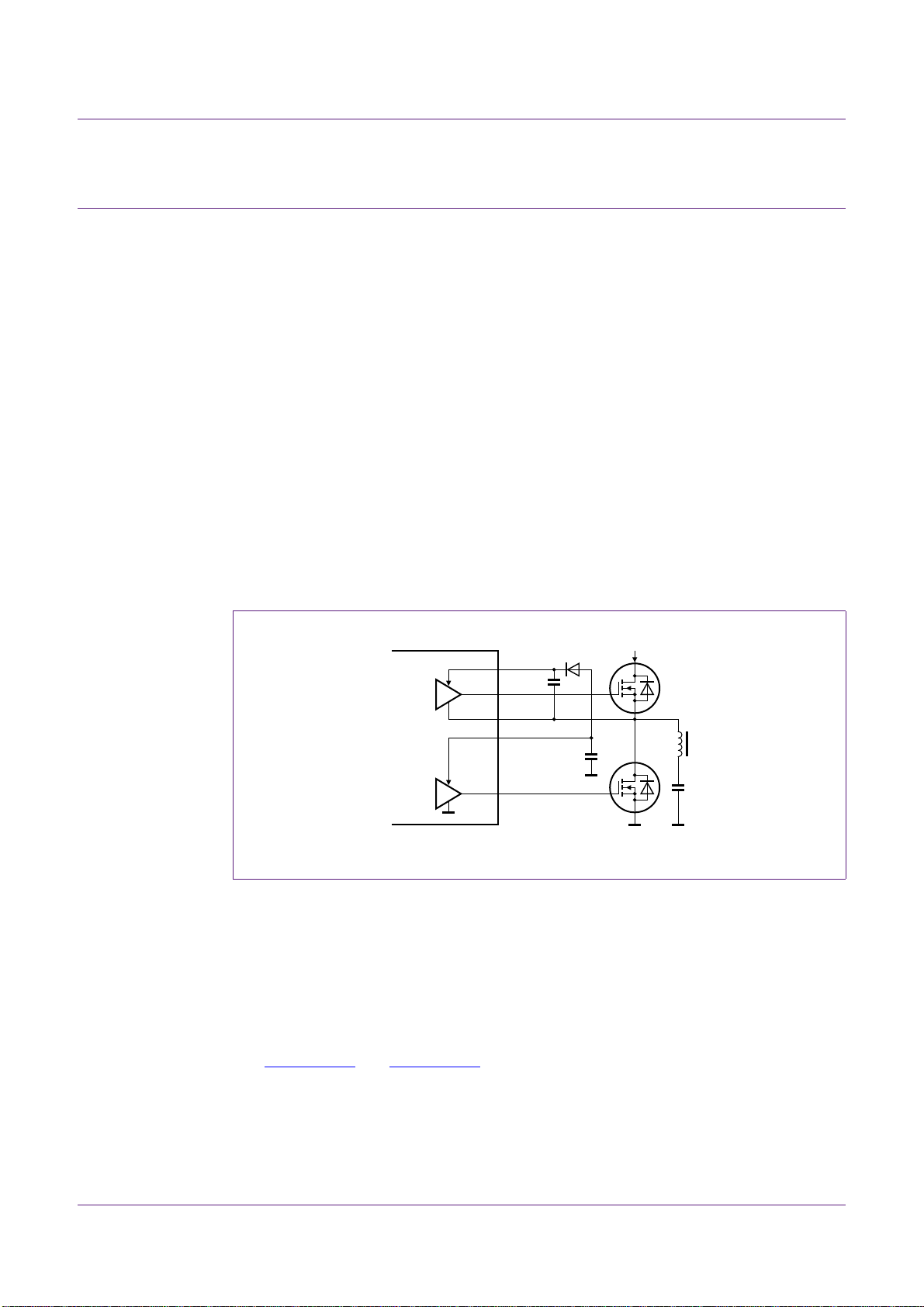

2.3 TEA1713 resonant power supply control IC with PFC

The TEA1713 integrates two controllers, one for Power Factor Correction (PFC) and one

for a half-bridge resonant converter (HBC). It provides the drive function for the discrete

MOSFET for the up-converter and for the two discrete power MOSFETs in a resonant

half-bridge configuration.

The resonant controller part is a high-voltage controller for a zero voltage switching LLC

resonant converter.

AN10881

TEA1713 resonant power supply control IC with PFC

The resonant controller part of the IC includes a high-volt age leve l shift circuit and severa l

protection features such as overcurrent protection, open-loop protection, Ca pacitive mode

protection and a general purpose latched protection input.

In addition to the resonant controller, the TEA1713 also contains a Power Factor

Correction (PFC) controller. The efficient operation of the PFC is obtained by functions

such as quasi-resonant operation at high power levels and quasi-resonant operation with

valley skipping at lower power levels. Overcurrent protection, overvoltage protection and

demagnetization sensing ensures safe operation in all conditions.

The proprietary high-voltage BCD Powerlogic process ma kes direct start-up possible from

the rectified universal mains voltage in an efficient way. A second internal low-voltage SOI

die is used for accurate, high-speed protection functions and control.

The topology of a PFC and a resonant converter controlled by the TEA1713 is flexible and

enables a broad range of applications for wide input (85 V to 264 V) AC mains voltages.

The combination of PFC and resonant controller in one IC makes the TEA1713 suitable

for compact power supplies with a high level of integration and functionality.

2.4 Features

2.4.1 General features

• Integrated power factor controller and resonant controller

• Universal mains supply operation

• High level of integration, resulting in a low external component count and a cost

effective design

• Enable input. Also allows enabling of PFC only

• On-chip high-voltage start-up sour ce

• Standalone operation or IC supply from external DC supply

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 6 of 102

Page 7

NXP Semiconductors

2.4.2 Power factor controller features

• Boundary mode operation with on-time control for highest efficiency

• Valley/zero voltage switching for minimum switching losses

• Frequency limitation to reduce switching losses

• Accurate boost voltage regulation

• Burst mode switching with soft-start and soft-stop

2.4.3 Resonant half-bridge controller features

• Integrated high-voltage level shifter

• Adjustable minimum and maximum frequency

• Maximum 500 kHz half-bridge switching frequency

• Adaptive non-overlap timing

• Burst mode switching

2.4.4 Protection features

• Safe restart mode for system fault conditions

• General latched protection input for output overvoltage protection or external

• Protection timer for time-out and restart

• OverTemperature Protection (OTP)

• Soft (re)start for both converters

• Undervoltage protection for mains (brownout), boost, IC supply and output voltage

• Overcurrent regulation and protection for both converters

• Accurate overvoltage protection for boost voltage

• Capacitive mode protection for resonant converter

AN10881

TEA1713 resonant power supply control IC with PFC

temperature protection

2.5 Protection

The TEA1713 provides several protection functions that combine detection with a

response to solve the problem. By regulating the frequency as a reaction to, for example,

overpower or bad half-bridge switching, the problem can be solved or operation kept safe

until it is decided to stop and restart (timer function).

2.6 Typical areas of application

• LCD television

• Plasma television

• High-power adapters

• Slim notebook adapters

• PC power supplies

• Office equipment

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 7 of 102

Page 8

NXP Semiconductors

TEA1713 resonant power supply control IC with PFC

3. Pin overview with functional description

AN10881

Table 2. Pinning overview

Pin Name Functional description

1 COMPPFC Frequency compensation for the PFC control-loop.

2 SNSMAINS Sense input for mains voltage.

Externally connected filter with typical values: 150 nF (33 k + 470 nF)

Externally connected to resistive divided mains voltage.

This pin has four functions:

• Mains enable level: V

start(SNSMAINS)

• Mains stop level (brownout): V

=1.15V

stop(SNSMAINS)

=0.9V

• Mains-voltage compensation for the PFC control-loop gain bandwidth

• Fast latch reset: V

The mains enable and mains stop level enable and disable the PFC. Enabling and disabling of

the resonant controller is based on the voltage on SNSBOOST.

The voltage on the SNSMAINS pin must be an averaged DC value, representing the AC line

voltage. Do not use the pin for sensing the phase of the mains voltage.

Open pin detection is included by an internal current source (33 nA).

3 SNSAUXPFC Sense input from an auxiliary winding of the PFC coil for demagnetization timing and valley

detection to control the PFC switching. It is 100 mV level with a time-out of 50 s.

Connect the auxiliary winding via an impedance to the pin (recommended is a 5.1 k series

resistor) to prevent damage of the input during surges (e.g. lightning).

Open pin detection is included by an internal current source (33 nA).

4 SNSCURPFC Current sense input for PFC.

This input is used to limit the maximum peak-current in the PFC core. The PFCSENSE is a

cycle-by-cycle protection. The PFC MOSFET is switched off when the level reaches 0.5 V.

The internal logic controls a 60 A internal current source connected to the pin. This current

source is used to implement a soft-start and soft-stop function for the PFC to prevent audible

noise in Burst mode.

The pin is also used to enable the PFC. The PFC only starts when the internal current source

(60 A) is able to charge the soft-start capacitor to a voltage of 0.5V. A minimum soft-start

resistor of 12 k is required to guarantee enabling of the PFC.

The value of the capacitor on SNSCURPFC provides the soft-start and soft-stop timing in

combination with the parallel resistor value.

5 SNSOUT Input for indirectly sensing the output voltage of the resonant converter. It is normally connected

to an auxiliary winding of HBC and is also an input for the Burst mode of HBC or PFC + HBC.

This pin has four functions related to internal comparators:

rst(SNSMAINS)

=0.75V

• Overvoltage protection: SNSOUT > 3.5 V, latched

• Undervoltage protection: SNSOUT < 2.3 V, protection timer

• Hold HBC: SNSOUT < 1.0 V, stop switching HBC (Burst mode)

• Hold HBC + PFC: SNSOUT < 0.4 V, stop switching HBC and PFC (Burst mode)

The pin also contains an internal current source of 100 A that, initially, generates a voltage up

to 1.5 V across an external impedance (> 20 k recommended) to avoid unintended Burst

mode operation.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 8 of 102

Page 9

NXP Semiconductors

AN10881

TEA1713 resonant power supply control IC with PFC

Table 2. Pinning overview

Pin Name Functional description

6 SUPIC IC voltage supply input and output of the internal HV start-up source.

…continued

All internal circuits are directly or indirectly (via SUPREG) supplied from this pin, except for the

high-voltage circuit.

The buffer capacitor on SUPIC can be charged in several ways:

• Internal High-Voltage (HV) start-up source

• Auxiliary winding from HBC transformer or capacitive supply from switching half-bridge

node

• External DC supply, for example a standby supply

The IC enables operation when the SUPIC voltage has reached the start level of 22 V (for

HV-start) or 17 V (for external supply). It stops operation below 15 V and a shutdown reset is

activated at 7 V.

7 GATEPFC Gate driver output for PFC MOSFET.

8 PGND Power ground. Reference (ground) for HBC low-side and PFC driver.

9 SUPREG Output of the internal regulator: 10.9 V.

Internal IC functions such as the MOSFET drivers use the supply created by this function . It can

also be used to supply an external circuit.

SUPREG can provide a minimum of 40 mA.

SUPREG becomes operational after SUPIC has reached its start level.

The IC starts full operation when SUPREG has reached 10.7 V.

UVP: If SUPREG drops below 10.3 V after start, the IC stops operating and the current from

SUPIC is limited to 5.4 mA, to allow recovery.

10 GA T E LS Gate driver output for low side MOSFET o f HBC.

11 n.c. Not connected, high-voltage spacer.

12 SUPHV High-voltage supply input for internal HV start-up source.

In a standalone power supply application, this pin is connected to the boost voltage. SUPIC and

SUPREG are charged with a constant current by the internal start-up source. SUPHV operates

at a voltage above 25 V .

Initially the charging current is low (1.1 mA). When the SUPIC exceeds the short circuit

protection level of 0.65 V , the generated current increases to 5.1 mA. The source is switched off

when SUPIC reaches 22 V which initiates a start operation. During start operation, an auxiliary

supply takes over the supply of SUPIC. If the takeover is not successful, the SUPHV source is

reactivated and a restart is made (SUPIC below 15 V).

13 GA T E H S Gate driver output for high-side MOSFET of HBC.

14 SUPHS High-side driver supply connected to an external bootstrap capacitor between HB and SUPHS.

The supply is obtained using an external diode between SUPREG and SUPHS.

15 HB Reference for the high-side driver GATEHS.

It is an input for the internal half-bridge slope detection circuit for adaptive non-overlap

regulation and Capacitive mode protection. It is externally connected to a half-bridge node

between the MOSFETs of HBC.

16 n.c. Not connected, high-voltage spacer.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 9 of 102

Page 10

NXP Semiconductors

AN10881

TEA1713 resonant power supply control IC with PFC

Table 2. Pinning overview

Pin Name Functional description

17 SNSCURHBC Sense input for the momentary current of the HBC. If the voltage level (that represents the

18 SGND Signal ground, reference for IC.

19 CFMIN Oscillator pin.

20 RFMAX Oscillator frequency pin.

21 SNSFB Sense input for HBC output regulation feedback by voltage.

…continued

primary current) becomes too high, internal comparators determine the regulation to a higher

frequency (SNSCURHBC = 0.5 V) or protect (SNSCURHBC = 1 V) by switching immediately

to maximum frequency.

The provided additional current from SNSCURHBC can compensate variations at protection

level, caused by HBC input voltage variations. This current leads to a voltage offset across the

external series resistance value. The current measurement resistor and an extra series

resistance, which has a typical value of 1 k, normally provide this series resistance .

The value of the external capacitor determines the minimum switching frequency of the HBC. In

combination with the resistor value on RFMAX, it sets the operating frequency range.

A triangular waveform is generated on the CFMIN capacitor (V

V

high(CFMIN)

150 A determines the minimum frequency. During special conditions, the (dis)charging current

is reduced to 30 A to slow do wn the charging temporarily.

An internal function limits the operating frequency to 670 kHz.

The value of the resistor connected between this pin and ground, determines the frequency

range. Both the minimum and maximum frequencies of the HBC are preset. CFMIN sets the

minimum frequency. The absolute maximum frequency is internally limited to 670 kHz.

The voltage on RFMAX and the value of the resistor connected to it, determine the variable part

(in addition to the fixed 150 A) of the (dis)charging current of the CFMIN capacitor. The voltage

on RFMAX can vary between 0 V (minimum frequency) and 2.5 V (maximum frequency).

SNSFB and the SSHBC/EN function drive the RFMAX voltage (running frequency).

The protection timer is started when the voltage level is above 1.88 V. An error is assumed

when the HBC is operating at high frequency for a longer time.

Sinking a current from SNSFB creates the feedback voltage on SNSFB. The regulation voltage

is produced by feeding this current through a 1.5 k internal resistor which is internally

connected to 8.4 V.

The regulation voltage range is from 4.1 V to 6.4 V . It corresponds with the maximum and

minimum frequencies that are controlled by SNSFB. The SNSFB range is limited to 65 % of the

maximum frequency preset by RFMAX.

The provision of open-loop detection activates the protection timer when SNSFB exceeds 7.7 V.

= 3 V)) to facilitate switching timing. A fixed minimum (dis)charging current of

low(CFMIN)

= 1 V and

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 10 of 102

Page 11

NXP Semiconductors

AN10881

TEA1713 resonant power supply control IC with PFC

Table 2. Pinning overview

Pin Name Functional description

22 SSHBC/EN Combined soft-start/protection frequency control of HBC and IC enable input (PFC or

…continued

PFC + HBC). Externally connected to a soft-start capacitor and an enable pull-down function.

This pin has three functions:

• Enable PFC (> 1 V) and PFC + HBC (> 2 V)

• Frequency sweep during soft-start from 3.2 V to 8 V

• Frequency control during protection between 8 V to 3.2 V

Seven internal current sources operate the frequency control, depending on which one of the

following actions is required:

• Soft-start + OverCurrent Protection: high/low charge (160 A/40 A) + high/low discharge

(160 A/40 A)

• Capacitive mode regulation: high/low discharge (1800 A/440 A)

• General: bias discharge (5 A)

23 RCPROT Timer presetting for time-out and restart. The values of an externally connected resistor and

capacitor determine the timing.

A 100 A charge current activates the timer during certain protection events:

• Overcurrent regulation (SNSCURHBC)

• High-frequency protection (RFMAX)

• Open-loop protection (SNSFB)

• Undervoltage protecti on (SNSOUT)

When the level of 4 V is reached the protection is activated. The resistor discharges the

capacitor and at a level of 0.5 V, a restart is made.

If an SCP (SNSBOOST) occurs, the RCPROT capacitor is quickly charged by 2.2 mA. After it

reaches the 4 V level, the capacitor is discharged after which a new start is initiated.

24 SNSBOOST Sense input for boost voltage regulation (output voltage of the PFC stage). It is externally

connected to a resistive divided boost voltage.

This pin has four functions:

• Pin SNSBOOST short detection: V

• Regulation of PFC output voltage: V

• PFC soft-OVP (cycle-by-cycle): V

SCP(SNSBOOST)

reg(SNSBOOST)

OVP(SNSBOOST)

• Brownout function for HBC: converter enable voltage: V

converter disable voltage: V

UVP(SNSBOOST)

2.63 V

=1.6V

0.4 V

=2.5V

start(SNSBOOST)

= 2.3 V and

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 11 of 102

Page 12

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

001aal015

TEA1713

mains

rect Boost

SupHs

SupIc

Tr

Pfc

Tr

Hbc

C

SoStPfc

R

Curcmp

R

CurHbc

C

Res

C

HB

C

SupHs

R

CurPfc

C

SupReg

C

SupIc

Output

D

SupHs

R

CurPfc

R

Prot

C

Prot

C

SoStHbc

SSHbcEn

C

fmin

R

fmax

AuxPfc

DrPfc

SNSBOOST GATEHS

HB

Hb

GATELS

SNSCURHBC

SNSOUT

SNSFB

RFMAX

CFMIN

SSHBC/EN

SNSAUXPFC

SNSMAINS

SNSCURPFC

GATEPFC

COMPPFC

RCPROT

SUPHV SUPIC SUPREG

SupReg

CurHbc

SUPHS

SGNDPGND

POWER FACTOR CONTROLLER

Disable

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

Application note Rev. 2 — 26 September 2011 12 of 102

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

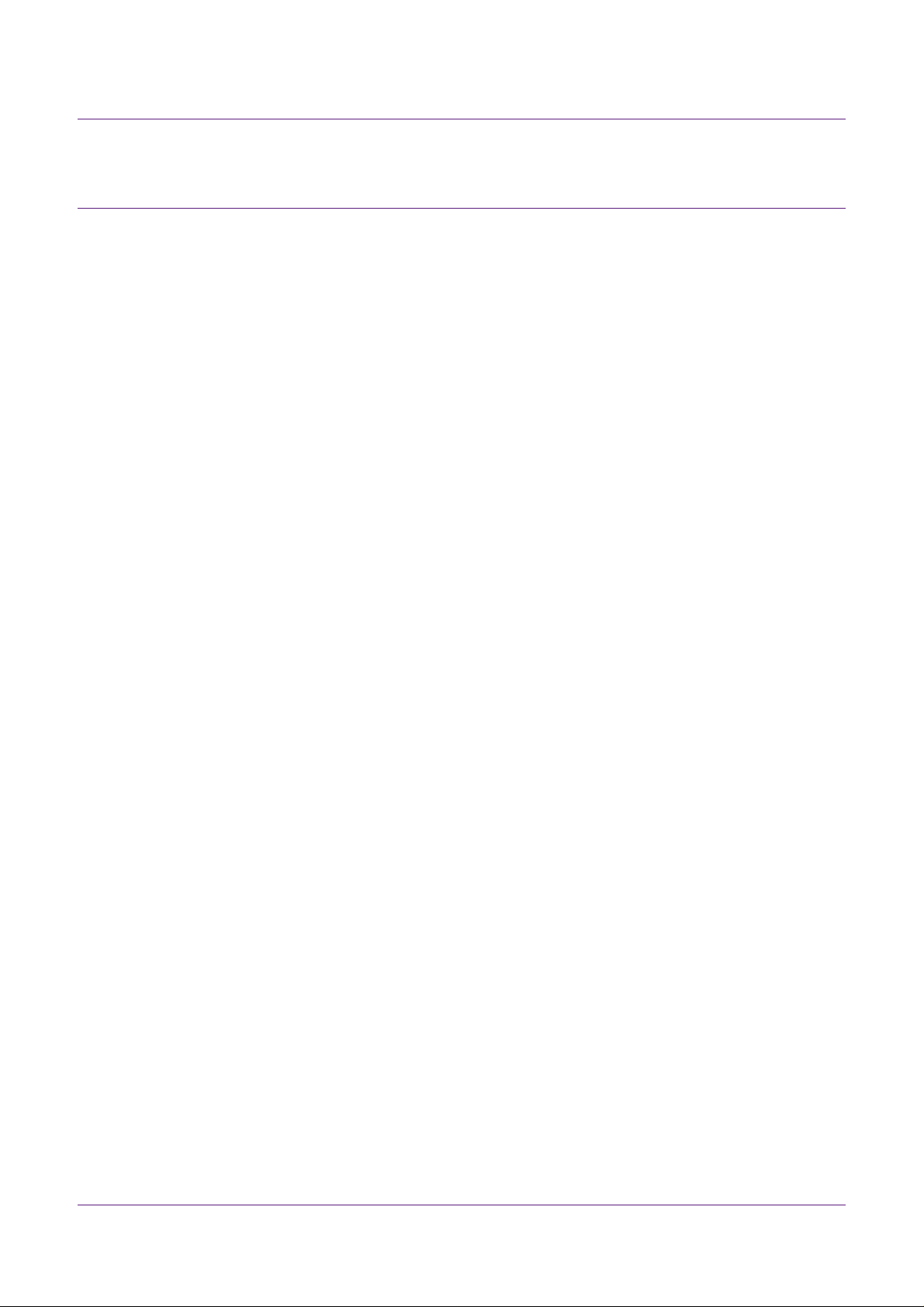

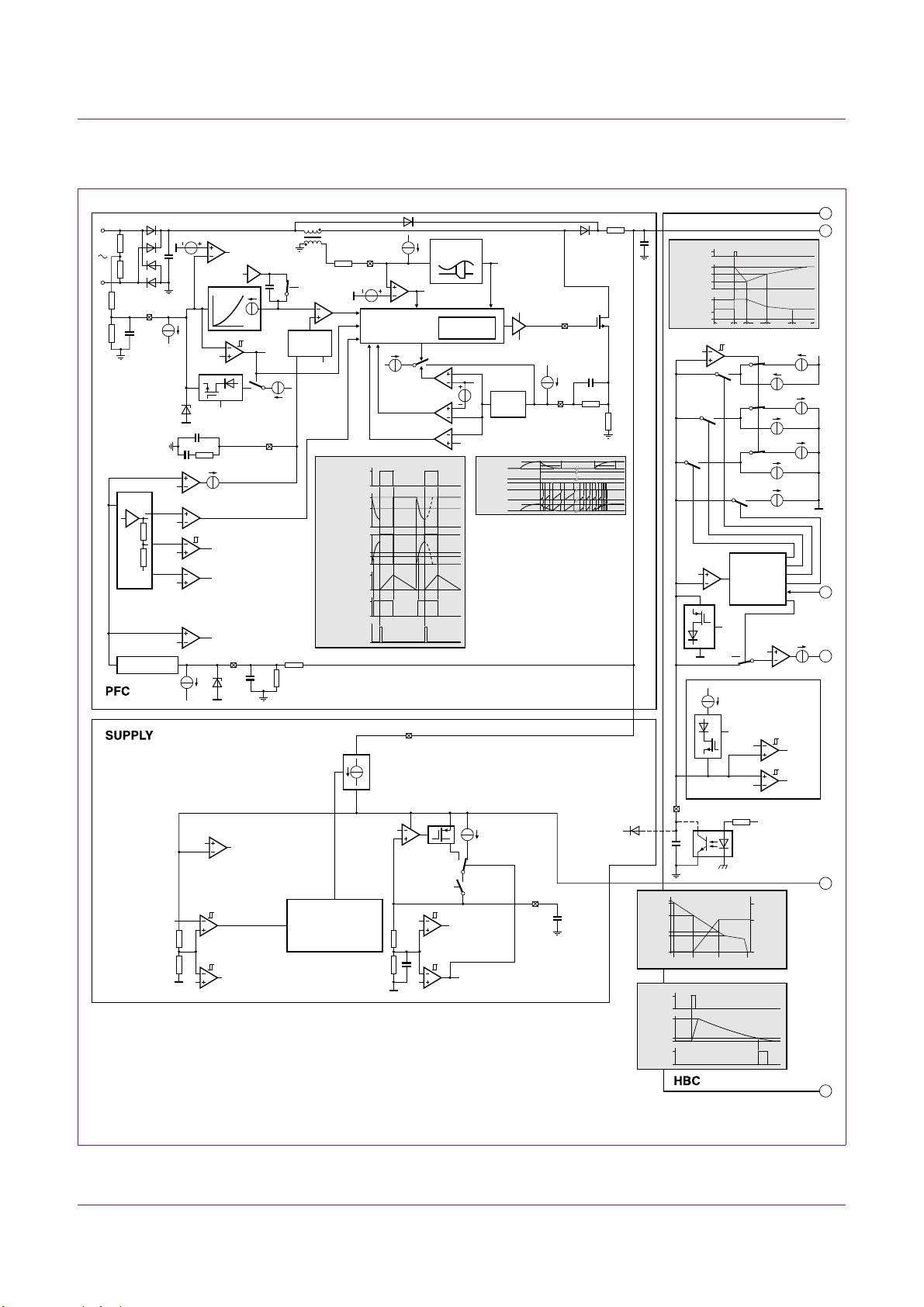

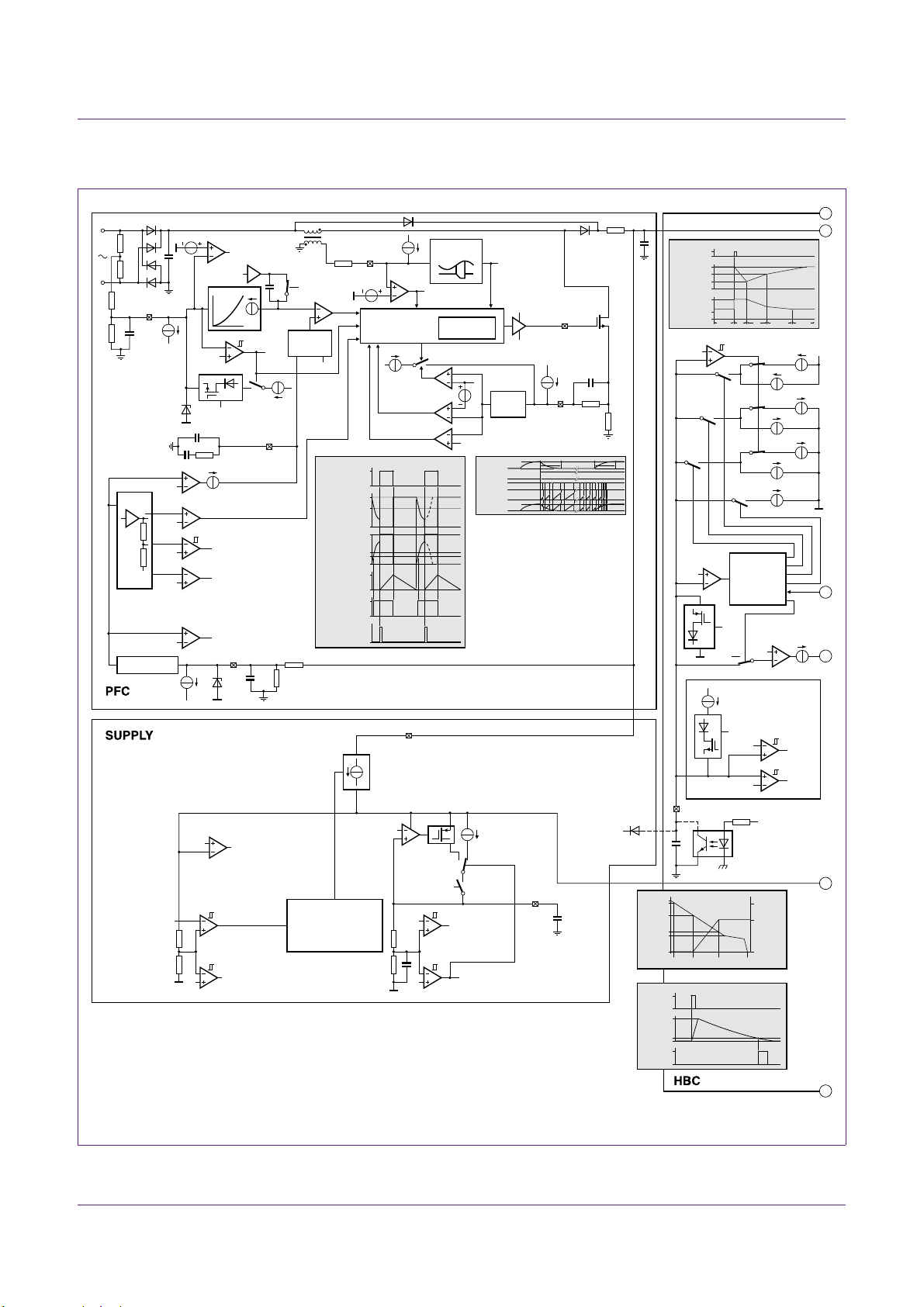

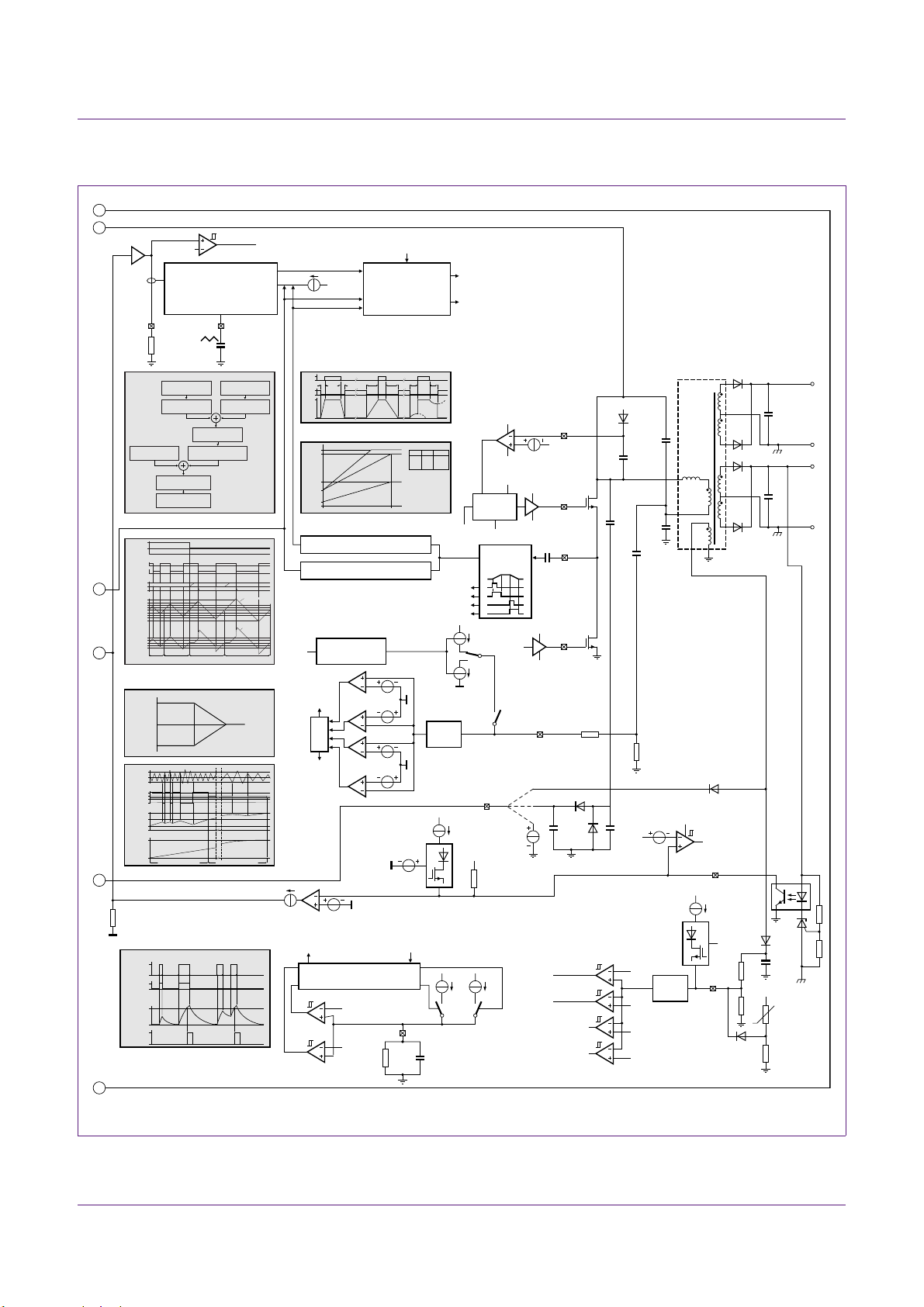

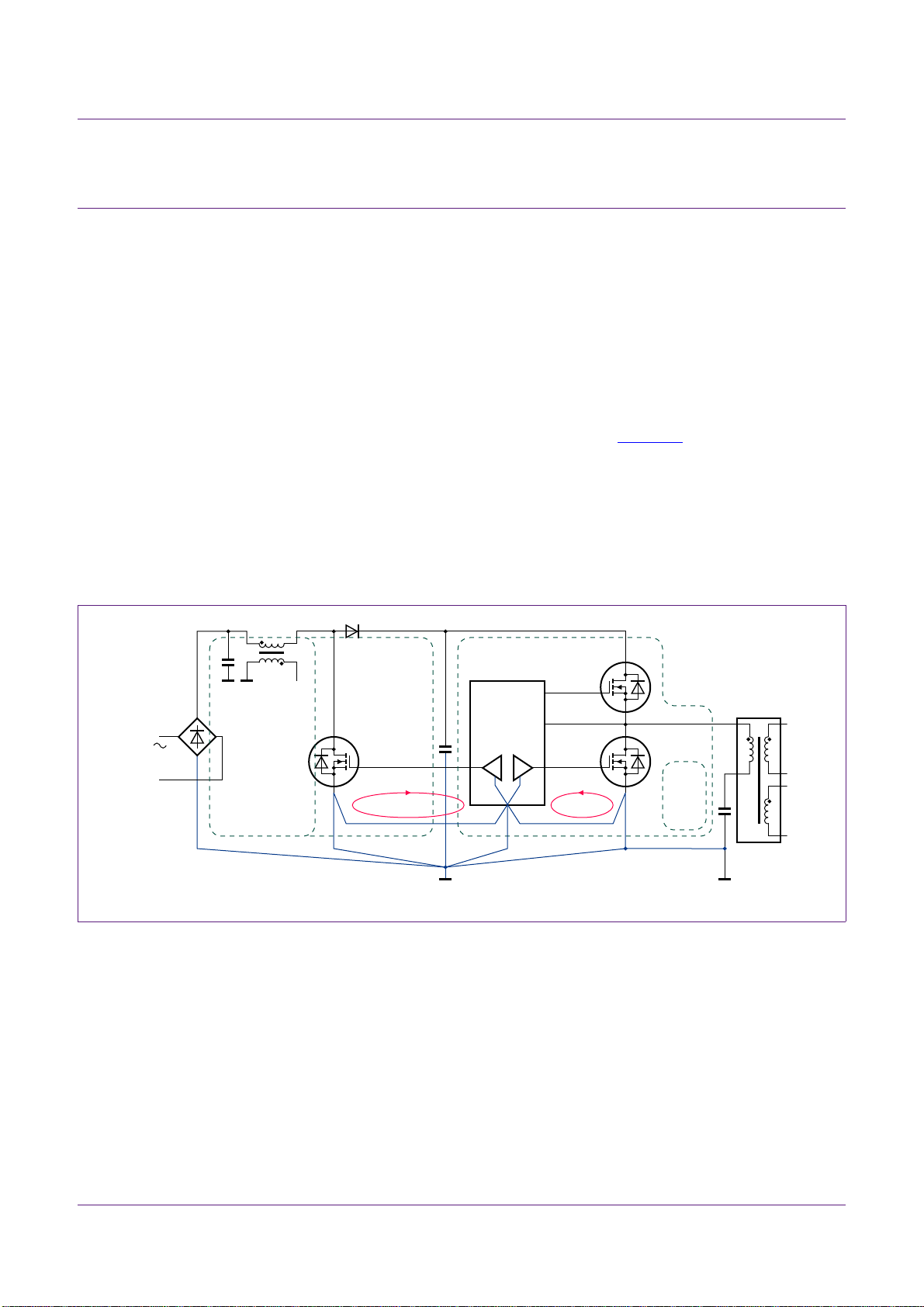

4. Application diagram and block diagrams

NXP Semiconductors

Fig 1. Basic application diagram TEA1713

TEA1713 resonant power supply control IC with PFC

AN10881

Page 13

NXP Semiconductors

coa073

1.2

MΩ

1.2

MΩ

1.2

MΩ

SNSMAINS

MainsReset

MainsUV

SoftStart

min

Ton

max

Ton

14

kΩ

9.8 MΩ

62 kΩ

3.3 μF

47 μA

60 μA

−39.....+39 μA

GmAmplifier

33 nA

800 mV

1 ×

5.8 V

2.5 V

120 μA

5.6 V

2.2 V

1.0 V

Enable

ENABLE DETECTION

EnablePfc

3.2 V

3.2 V

8.0 V

ClampEndSoftStart

40 μA

120 μA

40 μA

1360 μA

440 μA

5 μA

42 μA

FREQUENCY

CONTROL

HBC

D

C

B

A

E

F

33 nA

33 nA

R

SoStPfct

R

CurPfc

C

SoStPfct

45 nA

5.8 V

1 nF

2.5 V

0.4 V

Demag

ValleyPfc

DRIVE CONTROL

SPIKE

FILTER

0.1 V

0.5 V

0.52 V

50 mV

COMPPFC

SPIKE FILTER

BoostOv

BoostSCProt

BoostOv level = 2.63 V

BoostStart = 2.3 V

BoostUvp = 1.6 V

SNSBOOST

SUPHV

SNSAUXPFC

AuxPfc

SNSCURPFC

open pin

detection

PGND

SupReg

SSHBC/EN

Disable supply

Enable supply

0 to >2 V

GATEPFC

Boost

SUPREG

1.05 V

UV-Clamp

3.0 V

0.89 V

1.15 V

1.25 V

3.5 V

GatePfcDig

Ton

SoftStopEnd

OCPfc

I = c*V

2

8.4 V

demagnetized

V

Rect

/N

V

Rect

V

Boost

(V

Boost

− V

Rect

)/N

V

aux,demag

0

0

magnetized

Demagnetization

VALLEY SWITCHING

l

TrPfc

AuxPfc

DrPfc

GatePfc

Valley

(= top for detection)

0

off

on

t

VALLEY

DETECTION

frequency limit

125 kHz

SuplcChargeLow = 1.1 mA

SuplcCharge = 5.1 mA

HV START-UP SOURCE

CONTROL

0.65 V

10.9 V

5.4 mA

SUPIC

SupReg

EnableSupReg

reduced

current

SuplcShort

startlevel Hv = 22 V

startlevel Lv = 17 V

stoplevel = 15 V

SupRegUvStart

startlevel = 10.7 V

SupRegUvStop

stoplevel = 10.3 V

SupHvPresent

C

SUPREG

Protection

HBC softstart reset

0

V

fmax(SSHBC)

V

SSHBC/EN

V

fmin(SSHBC)

0

f

min

f

HB

f

max

t

off

on

f

max

forced

fast

sweep

slow sweep regulationregulation

V

ss(hf-lf)(SSHBC)

PFCsense

Iswitch

OCP_lvl

OCP_lvl

PFC driver

Start Rdy

0

0

0

0

0

Softstart, Softstop

Softstart Softstop

0

I

SNSFB

V

open

= 8.4 V

0.66 mA

I

fmin

V

RFMAX

2.2 mA

I

fmax

00

V

SSHBC

= 8 V

260 μA

I

OLP

V

OLP

= 7.7 V

V

fmin

= 6.4 V

V

fmax

= 4.1 V

V

clamp,fmax

= 3.2 V

V

SNSFB

8 mA

I

clamp,max

2.5 V

typ

= V

fmax

1.5 V

typ

= 0.6

× V

fmax

passed

0

no

yes

V

high(RCPROT)

V

low(RCPROT)

restart request

V

RCPROT

t

restart time

RESTART TIMER

014aaa864

001aal029

001aal040

001aal064

AN10881

TEA1713 resonant power supply control IC with PFC

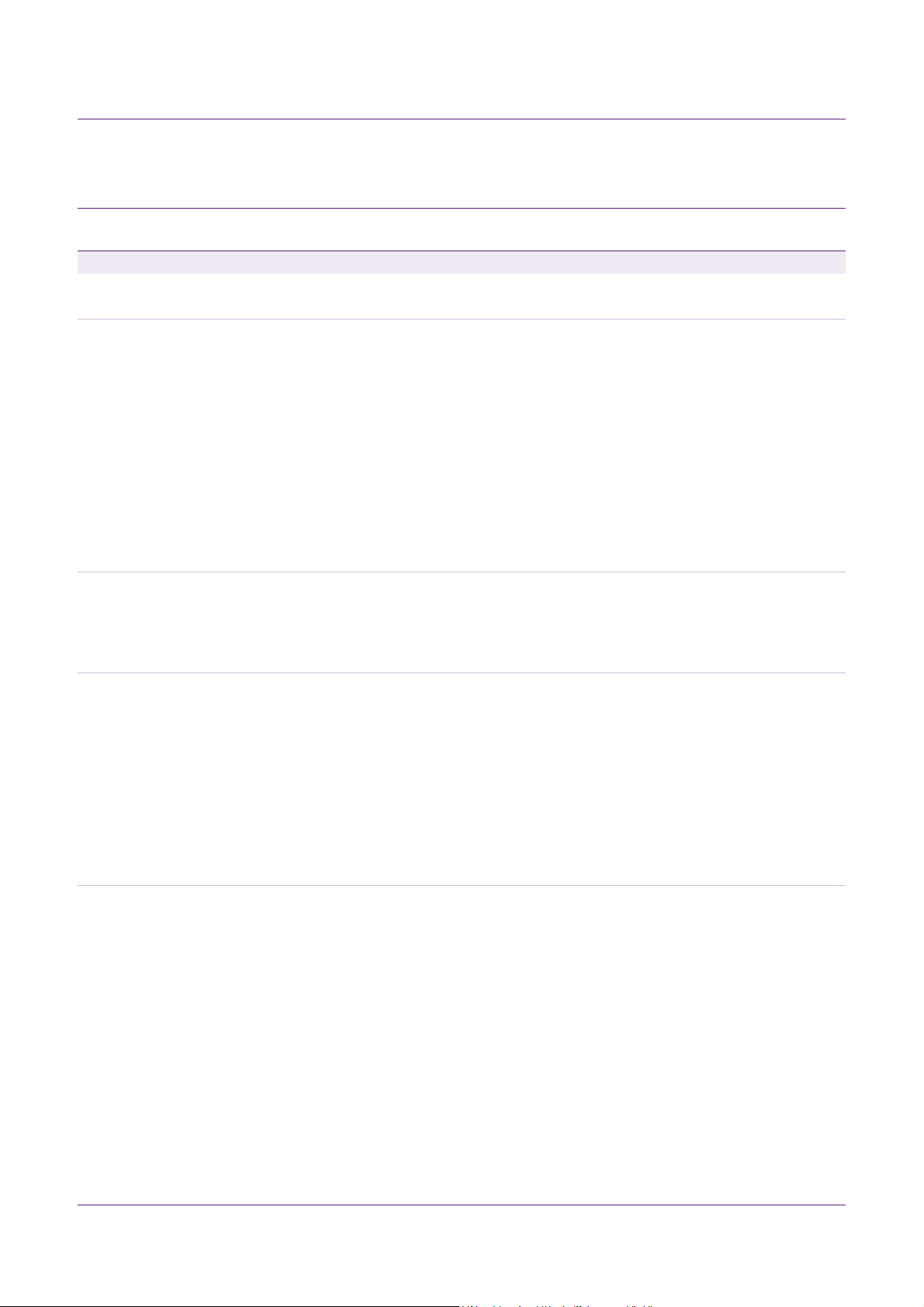

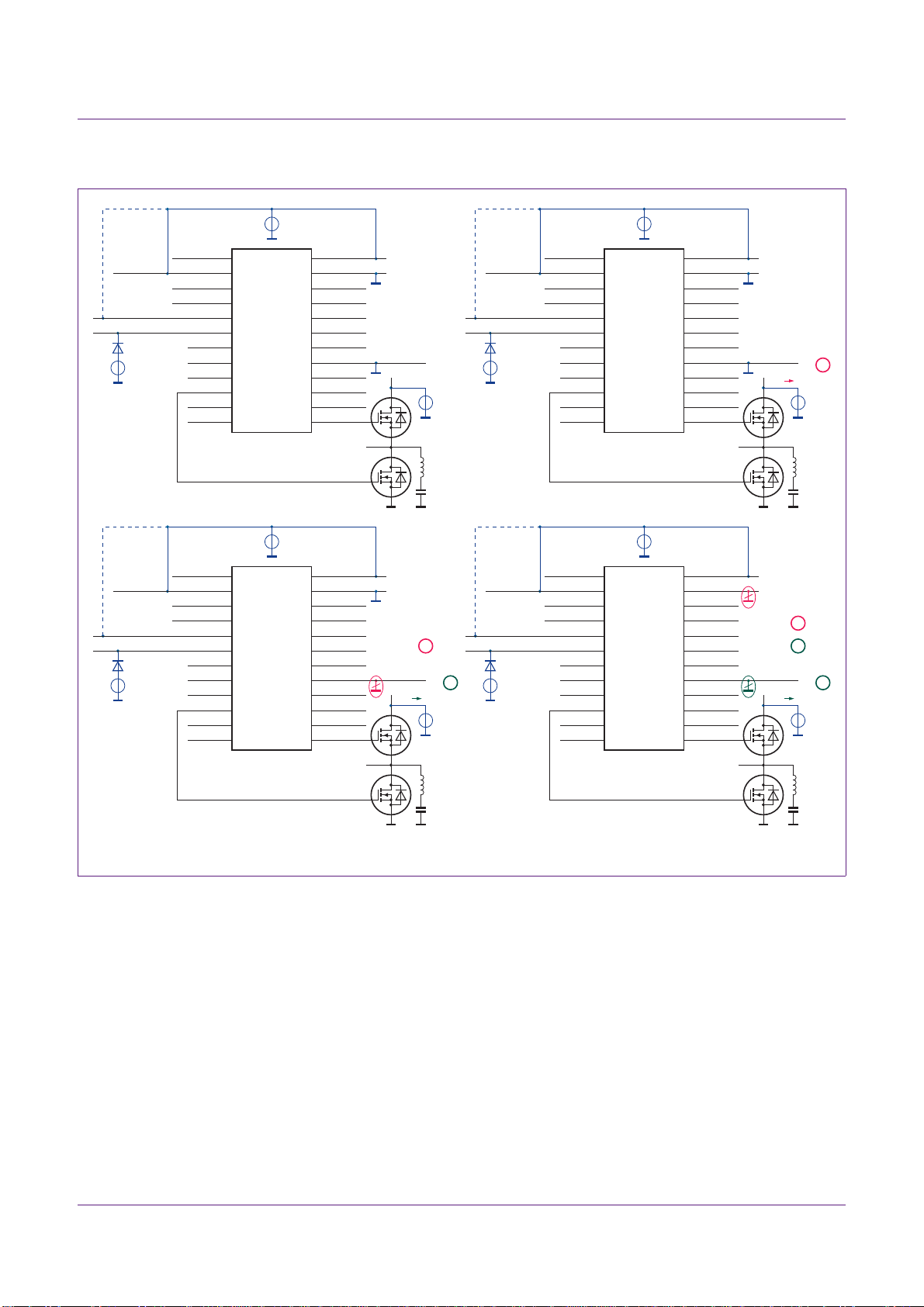

Fig 2. Block diagram TEA1713

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 13 of 102

Page 14

NXP Semiconductors

coa073

1.2

MΩ

1.2

MΩ

1.2

MΩ

SNSMAINS

MainsReset

MainsUV

SoftStart

min

Ton

max

Ton

14

kΩ

9.8 MΩ

62 kΩ

3.3 μF

47 μA

60 μA

−39.....+39 μA

GmAmplifier

33 nA

800 mV

1 ×

5.8 V

2.5 V

120 μA

5.6 V

2.2 V

1.0 V

Enable

ENABLE DETECTION

EnablePfc

3.2 V

3.2 V

8.0 V

ClampEndSoftStart

40 μA

120 μA

40 μA

1360 μA

440 μA

5 μA

42 μA

FREQUENCY

CONTROL

HBC

D

C

B

A

E

F

33 nA

33 nA

R

SoStPfct

R

CurPfc

C

SoStPfct

45 nA

5.8 V

1 nF

2.5 V

0.4 V

Demag

ValleyPfc

DRIVE CONTROL

SPIKE

FILTER

0.1 V

0.5 V

0.52 V

50 mV

COMPPFC

SPIKE FILTER

BoostOv

BoostSCProt

BoostOv level = 2.63 V

BoostStart = 2.3 V

BoostUvp = 1.6 V

SNSBOOST

SUPHV

SNSAUXPFC

AuxPfc

SNSCURPFC

open pin

detection

PGND

SupReg

SSHBC/EN

Disable supply

Enable supply

0 to >2 V

GATEPFC

Boost

SUPREG

1.05 V

UV-Clamp

3.0 V

0.89 V

1.15 V

1.25 V

3.5 V

GatePfcDig

Ton

SoftStopEnd

OCPfc

I = c*V

2

8.4 V

demagnetized

V

Rect

/N

V

Rect

V

Boost

(V

Boost

− V

Rect

)/N

V

aux,demag

0

0

magnetized

Demagnetization

VALLEY SWITCHING

l

TrPfc

AuxPfc

DrPfc

GatePfc

Valley

(= top for detection)

0

off

on

t

VALLEY

DETECTION

frequency limit

125 kHz

SuplcChargeLow = 1.1 mA

SuplcCharge = 5.1 mA

HV START-UP SOURCE

CONTROL

0.65 V

10.9 V

5.4 mA

SUPIC

SupReg

EnableSupReg

reduced

current

SuplcShort

startlevel Hv = 22 V

startlevel Lv = 17 V

stoplevel = 15 V

SupRegUvStart

startlevel = 10.7 V

SupRegUvStop

stoplevel = 10.3 V

SupHvPresent

C

SUPREG

Protection

HBC softstart reset

0

V

fmax(SSHBC)

V

SSHBC/EN

V

fmin(SSHBC)

0

f

min

f

HB

f

max

t

off

on

f

max

forced

fast

sweep

slow sweep regulationregulation

V

ss(hf-lf)(SSHBC)

PFCsense

Iswitch

OCP_lvl

OCP_lvl

PFC driver

Start Rdy

0

0

0

0

0

Softstart, Softstop

Softstart Softstop

0

I

SNSFB

V

open

= 8.4 V

0.66 mA

I

fmin

V

RFMAX

2.2 mA

I

fmax

00

V

SSHBC

= 8 V

260 μA

I

OLP

V

OLP

= 7.7 V

V

fmin

= 6.4 V

V

fmax

= 4.1 V

V

clamp,fmax

= 3.2 V

V

SNSFB

8 mA

I

clamp,max

2.5 V

typ

= V

fmax

1.5 V

typ

= 0.6

× V

fmax

passed

0

no

yes

V

high(RCPROT)

V

low(RCPROT)

restart request

V

RCPROT

t

restart time

RESTART TIMER

014aaa864

001aal029

001aal040

001aal064

AN10881

TEA1713 resonant power supply control IC with PFC

Fig 3. Block diagram TEA1713

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 14 of 102

Page 15

coa076

1.5 kΩ

R

Prot

340 kΩ

C

Prot

640 nF

TEA1713 pin list:

1. COMPPFC

2. SNSMAINS

3. SNSAUXPFC

4. SNSCURPFC

5. SNSOUT

6. SUPIC

7. GATEPFC

8. PGND

9.SUPREG

10. GATELS

11. n.c.

12. SUPHV

24. SNSBOOST

23. RCPROT

22. SSHBC/EN

21. SNSFB

20. RFMAX

19. CFMIN

18. SGND

17. SNSCURHBC

16. n.c.

15. HB

14. SUPHS

13. GATEHS

Output

High

Voltage

Output

Low

Voltage

Output

Vout

CCO

RFMAX

FreqHigh

ProtTimer

30 μA

F

MAX,limit

R

fmax

C

fmin

FreqHbc

(75 % of max)

1.8 V

Slowed

down

current

CFMIN

V

high

= 3.0 V

V

low

= 1.0 V

HBC DRIVE CONTROL

Drive GateHS

Drive GateLS

Enable

Logic

SUPHS

GATEHS

Hb

HB

7.3 mA

3.2 V

6.4 V

2.2 mA

100 μA

100 μA

VOLTAGE PIN SSHBC

POLARITY INVERSION

(max 2.5 V)

VOLTAGE PIN RFMAX

HBC OSCILLATOR

CONVERSION TO CURRENT

via R

fmax

FEEDBACK CURRENT

PIN SNSFB

FIXED f

min

CURRENT

CONVERSION TO

VOLTAGE (max 1.5 V)

(DIS-)CHARGE CURRENT

PIN CFMIN

CONVERSION TO

FRQUENCY via C

fmin

V

Cur(HBC)

= R

cur(HBC)

× I

Cur(HBC)

I

ocr(high)

I

ocp(high)

I

ocp(nom)

I

ocr(nom)

−I

ocr(nom)

−I

ocp(nom)

−I

ocr(high)

−I

ocp(high)

I

Cur(HBC)

I

SNSCURHBC

HBC BOOST COMPENSATION

V

reg

V

uvp

V

Boost

GATELS

GATEHS

sink current only with positive V

SNSCURHBC

sink

source

0

0

0

t

t

t

t

low V

Boost

strong compensation

high OCP

low V

Boost

strong compensation

high OCR

nominal V

Boost

no compensation

nominal OCP

nominal V

Boost

no compensation

nominal OCR

V

SNSCURHBC

t

t

V

SNSCURHBC

V

ocr(HBC)

−V

ocr(HBC)

V

ocp(HBC)

−V

ocp(HBC)

0 μA

0 V 1.8 V

V

SNSBOOST

I

compensation on SNSCURHBC

2.5 V =

V

regulation

170 μA

−170 μA

500 mV

−500 mV

V

SNSCURHBC

160 μA

40 μA

−40 μA

−160 μA

I

SSHBC/EN

V

SSHBC/EN

8 V

5.6 V

3.2 V

V

Output

V

regulate

0

0

0

HBC 0CR

t

t

t

t

Fast soft-start sweep (charge and discharge) Slow soft-start sweep (charge and discharge)

ADAPTIVE NON OVERLAP

LEVEL

SHIFTER

Hb

SupHs

Drive GateHS

Drive GateLS

CAPACITIVE MODE REGULATION

fast HB slope

V

Boost

Hb

GateLs

GateHs

0

slow HB slope incomplete HB slope

t

f

HB,limit

f

max,B

V

fmax

V

RFMAX

A

curve C

fminRfmax

A high high

B low low

C low too low

B

C

f

max,A

f

min,

B and C

f

min,A

0

f

HB

SLOPE

DETECTION

SlopeNeg

SlopeNegStart

SlopePos

SlopePosStart

SupHs

SupHs

Hb

GATELS

SNSOUT

SNSFB

SupReg

1.5 V

3.5 V

2.35 V

1.1 V

0.4 V

ProtTimer

(latched)

ProtSd

OutputUv

OutputOv

HoldHbc

HoldPfc

RCPROT

Restart

Over Current Regulation HBC

High Frequency Protection HBC

Open Loop Protection SNSFB

Under Voltage Protection SNSOUT

Short Circuit Protection SNSBOOST (2.2 mA)

4.0 V

0.5 V

SNSCURHBC

SPIKE

FILTER

SUPIC

SupReg

PGND

HB

4.5 V

HB

SupReg

C

SupReg

C

Res2

C

CurHbc

C

Suplc

R

CurHbc

R

Curcmp

1 kΩ

C

Hb

C

Res1

SPIKE

FILTER

BOOST VOL TAGE

COMPENSATION

SnsBoost

2.5 V => 0 μA

1.7 V => 100 μA

1 V

1 V

0.5 V

0.5 V

0.4 V

8.1 V

8.4 V

ProtTimer

open loop level = 7.7 V

Freq.

Control

ProtTimer

Standby

(external)

supply

passed

0

0

none

present

short

error

long

error

PROTECTION TIMER

repetative

error

V

high(RCPROT)

I

slow(RCPROT)

I

RCPROT

Error

V

RCPROT

t

Protection time

Θ

RESTART/

PROTECTION TIMER CONTROL

014aaa865

014aaa860

001aal033

001aal037

001aal063

001aal044

B

C

D

E

F

A

NXP Semiconductors

AN10881

TEA1713 resonant power supply control IC with PFC

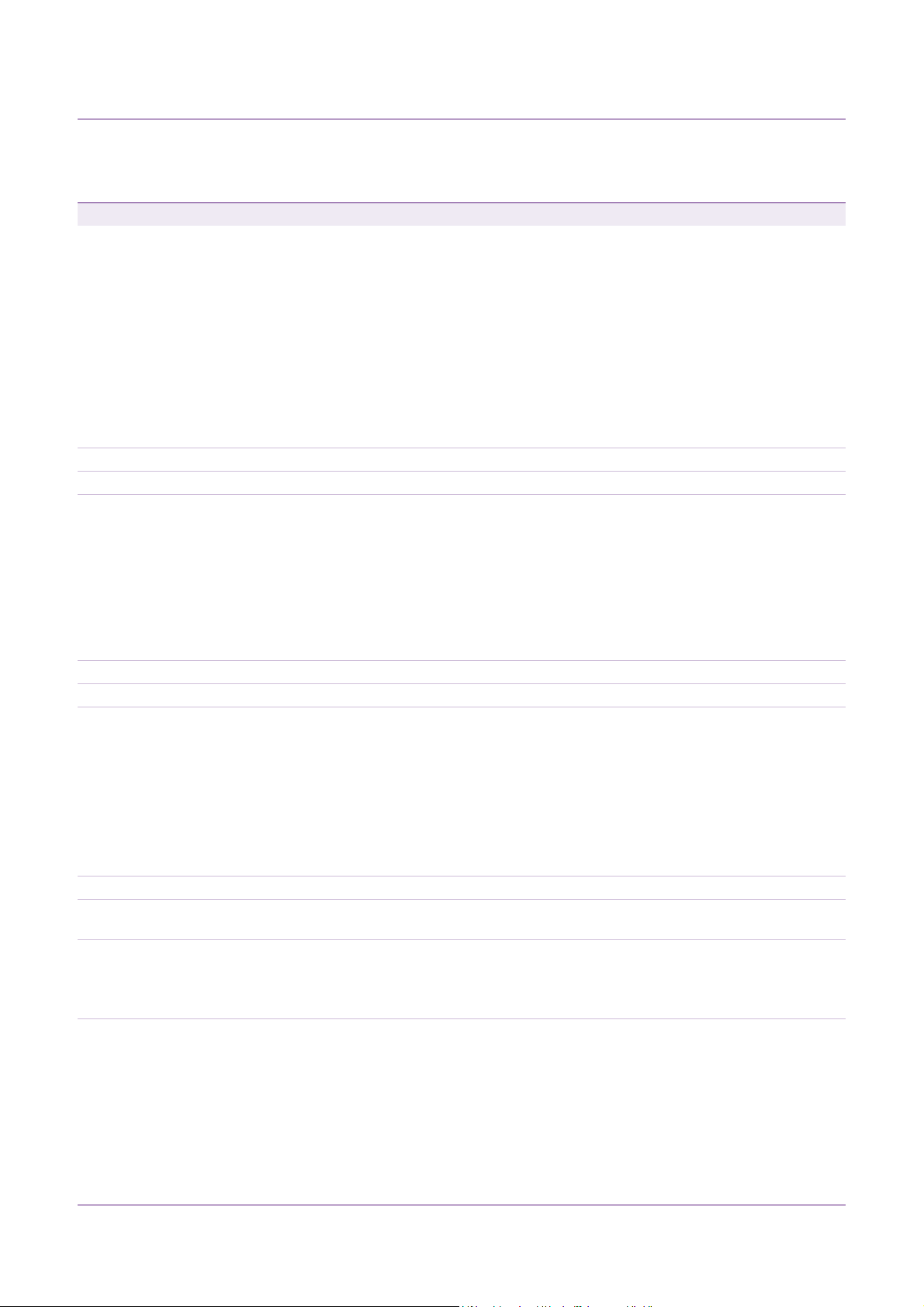

Fig 4. Block diagram TEA1713

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 15 of 102

Page 16

NXP Semiconductors

001aal017

TEA1713

MAINS

VOLT AGE

12

SUPHV

22 V

start when HVsupply

enable HVsource

start when LVsupply

stop, UVP

shutdown reset

COMP

0.65 V

COMP

17 V

COMP

7 V

COMP

15 V

COMP

start

EXTERNAL

stop

10.7 V

10.9 V

COMP

GATEPFC

GATEHS

14

15

9

SUPHS

HB

SUPREG

6 SUPIC

V

AUXILIARY

5 SNSOUT

GATELS

10.3 V

COMP

OVP

latched

shutdown

UVP

protection

timer

3.5 V

COMP

2.35 V

COMP

1.1 mA5.1 mA

HV

STARTUP

CONTROL

V

BOOST

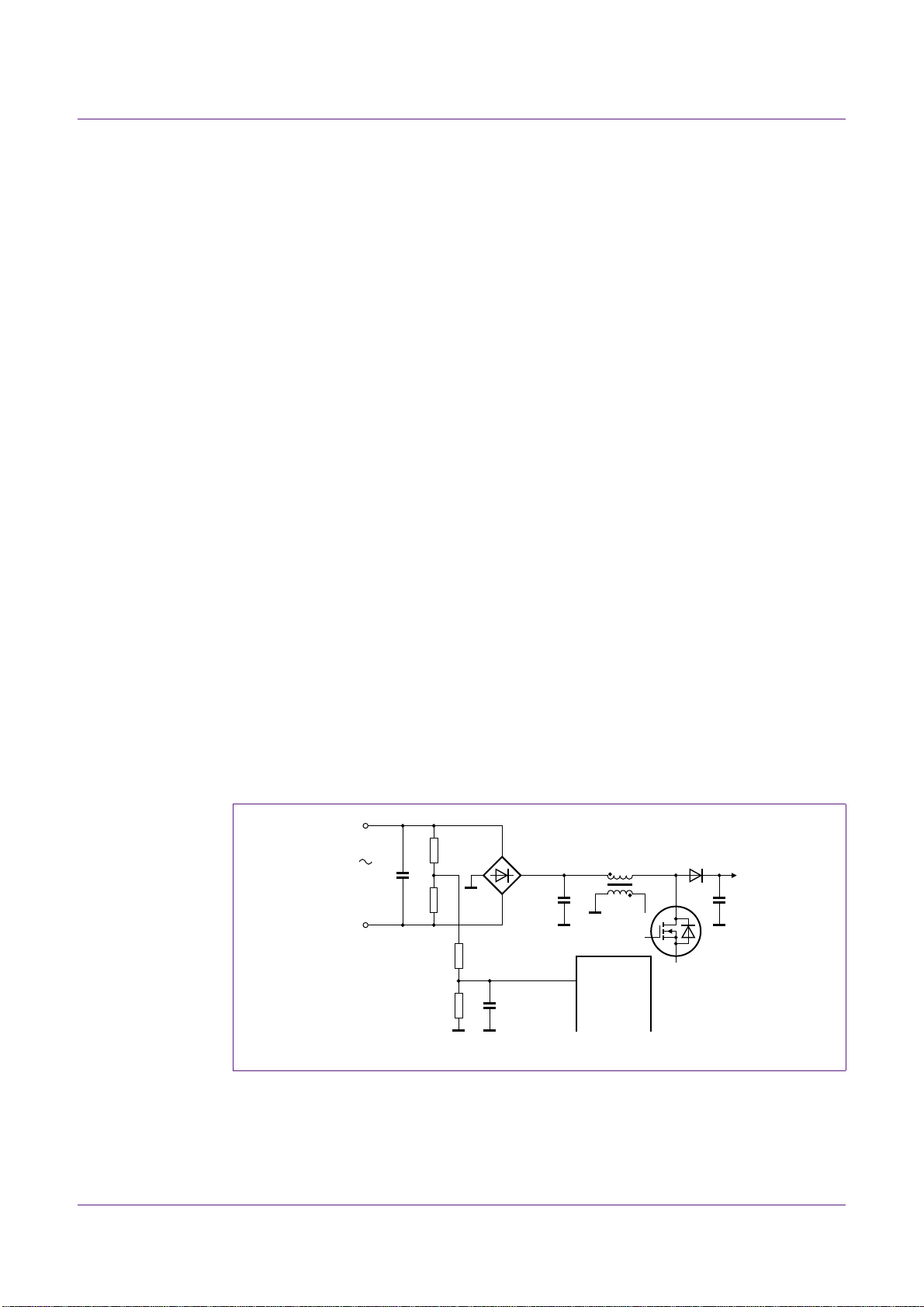

5. Supply functions

5.1 Basic supply system overview

AN10881

TEA1713 resonant power supply control IC with PFC

Fig 5. Basic overview internal IC supplies

5.1.1 TEA1713 supplies

The main supply for the TEA1713 is SUPIC.

SUPHV can be used to charge SUPIC for starting the supply. During operation a supply

voltage is applied to SUPIC and the SUPHV source is switched off. The SUPHV source is

only switched on again at a new start-up.

The internal regulator SUPREG generates a fixed voltage of 10.9 V to supply the internal

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 16 of 102

MOSFET drivers: GATEPFC, GATELS and GATEHS. A bootstrap function with an

external diode is used to make supply SUPHS.This is used to supply GATEHS.

SUPIC and SUPREG also supply other internal TEA1713 circuits.

Page 17

NXP Semiconductors

5.1.2 Supply monitoring and protection

The supply voltages are internally monitored to determine when to initiate certain actions,

such as starting, stopping or protection.

In several applications (e.g. when using an auxiliary winding construction) the SUPIC

voltage can also be used to monitor the HBC output voltage by protection input SNSOUT.

5.2 SUPIC - the low voltage IC supply

SUPIC is the main IC supply. Except for the SUPHV circuit, all internal circuits are either

directly or indirectly supplied from this pin.

5.2.1 SUPIC start-up

Connect SUPIC to an external buffer capacitor. This buffer capacitor can be charged in

several ways:

• Internal high-voltage (HV) start-up source

• Auxiliary supply , e.g. from a winding on the HBC transformer

• External DC supply, e.g. from a standby supply

AN10881

TEA1713 resonant power supply control IC with PFC

The IC starts operating when the SUPIC and SUPREG voltage have reached the start

level. The start level value of SUPIC depends on the condition of the SUPHV pin.

5.2.1.1 SUPHV 25 V

This is the case in a standalone application where the HV start-up source initially charges

SUPIC. The SUPIC start level is 22 V. The large difference between start level and stop

level (15 V) is used to allow discharge of the SUPIC capacitor until the auxiliary supply

can take over the IC supply.

5.2.1.2 SUPHV not connected/used

This is the case when the TEA1713 is supplied from an external DC supply. The SUPIC

start level is now 17 V. During start-up and operation the IC is continuously supplied by

the external DC supply. The SUPHV pin must not be connected for this kind of application.

max

5.2.2 SUPIC stop, UVP and SCP

The IC stops operating when the SUPIC voltage drops below 15 V which is the

UnderVoltage Protection (UVP) of SUPIC. While in the process of stopping, the HBC

continues until the low-side MOSFET is active, before stopping the PFC and HBC

operation.

SUPIC has a low level detection at 0.65 V to detect a short circuit to ground. This level

also controls the current source from the SUPHV pin.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 17 of 102

Page 18

NXP Semiconductors

5.2.3 SUPIC current consumption

The SUPIC current consumption depends on the state of the TEA1713.

• Disabled IC state:

• SUPIC charge, SUPREG charge, thermal hold, restart and shutdown state:

• Boost charge state:

• Operating supply state:

AN10881

TEA1713 resonant power supply control IC with PFC

When the IC is disabled via the SSHBC/EN pin, the current consumption is low at

250 A.

During the charging of SUPIC and SUPREG before start-up, during a restart

sequence or during shutdown after activation of protection, only a small part of the IC

is active. The PFC and HBC are disabled. The current consumption from SUPIC in

these states is small at 400 A.

PFC is switching and HBC is still off. The current from the high-voltage start-up source

is large enough to supply SUPIC, so current consumption is below the maximum

current (5.1 mA) that SUPHV can de live r.

Both PFC and HBC are switching. The current consumption is larger. The MOSFET

drivers are dominant in the current consumption (see Section 5.5.5

soft-start of the HBC, when the switching frequency is high, and also during normal

operation. Initially, the stored energy in the SUPIC capacitor delivers the SUPIC

current. After a short time the current supply is taken over by the supply source on

SUPIC during normal operation.

), especially during

5.3 SUPIC supply using HBC transformer auxiliary winding

5.3.1 Start-up by SUPHV

In a standalone power supply application, the IC can be started by a high-voltage source

such as the rectified mains voltage by connecting the high-voltage input SUPHV to the

boost voltage (PFC output voltage).

The internal HV start-up source, which delivers a const ant current from SUPHV to SUPIC,

charges the SUPIC and SUPREG. SUPHV is operational at a voltage > 25 V.

As long as the voltage at SUPIC is below the short circuit protection level (0.65 V), the

current from SUPHV is low (1.1 mA). This is to limit the dissipation in the HV start-up

source when SUPIC is shorted to ground.

During normal conditions, SUPIC quickly exceeds the protection level and the HV st art-up

source switches to normal current (5.1 mA). The HV start-up source switches off when

SUPIC has reached the start level (22 V). The current consumption from SUPHV is low

(7 A) when switched off.

When SUPIC has reached the start level (22 V), SUPREG is charged. When SUPREG

reaches the level of 10.7 V, it enables operation of HBC and PFC.

The auxiliary winding supply of the HBC transformer must take over the supply of SUPIC

before it is discharged to the SUPIC under voltage stop level (15 V).

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 18 of 102

Page 19

NXP Semiconductors

001aal018

SuplcChargeLow = 1.1 mA

SuplcCharge = 5.1 mA

SuplcCharge = off

HV START-UP SOURCE

CONTROL

0.65 V

10.9 V

5.5 mA

SUPIC

SUPHV

SUPREGSupReg

EnableSupReg

V

AUXILIARY

reduced

current

SuplcShort

startlevel Hv = 22 V

startlevel Lv = 17 V

stoplevel = 15 V

SupRegUvStart

startlevel = 10.7 V

SupRegUvStop

stoplevel = 10.3 V

SupHvPresent

C

SUPREG

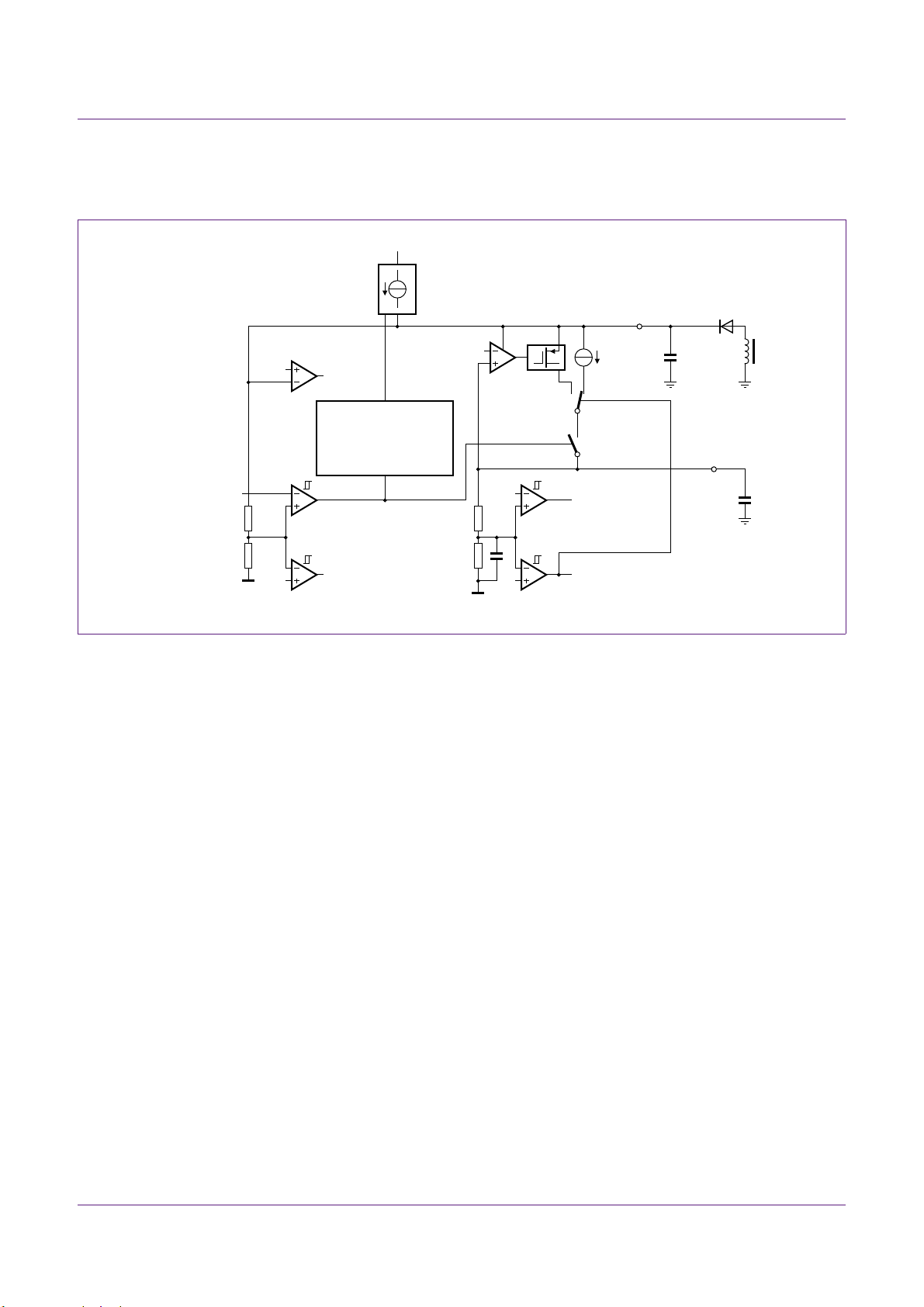

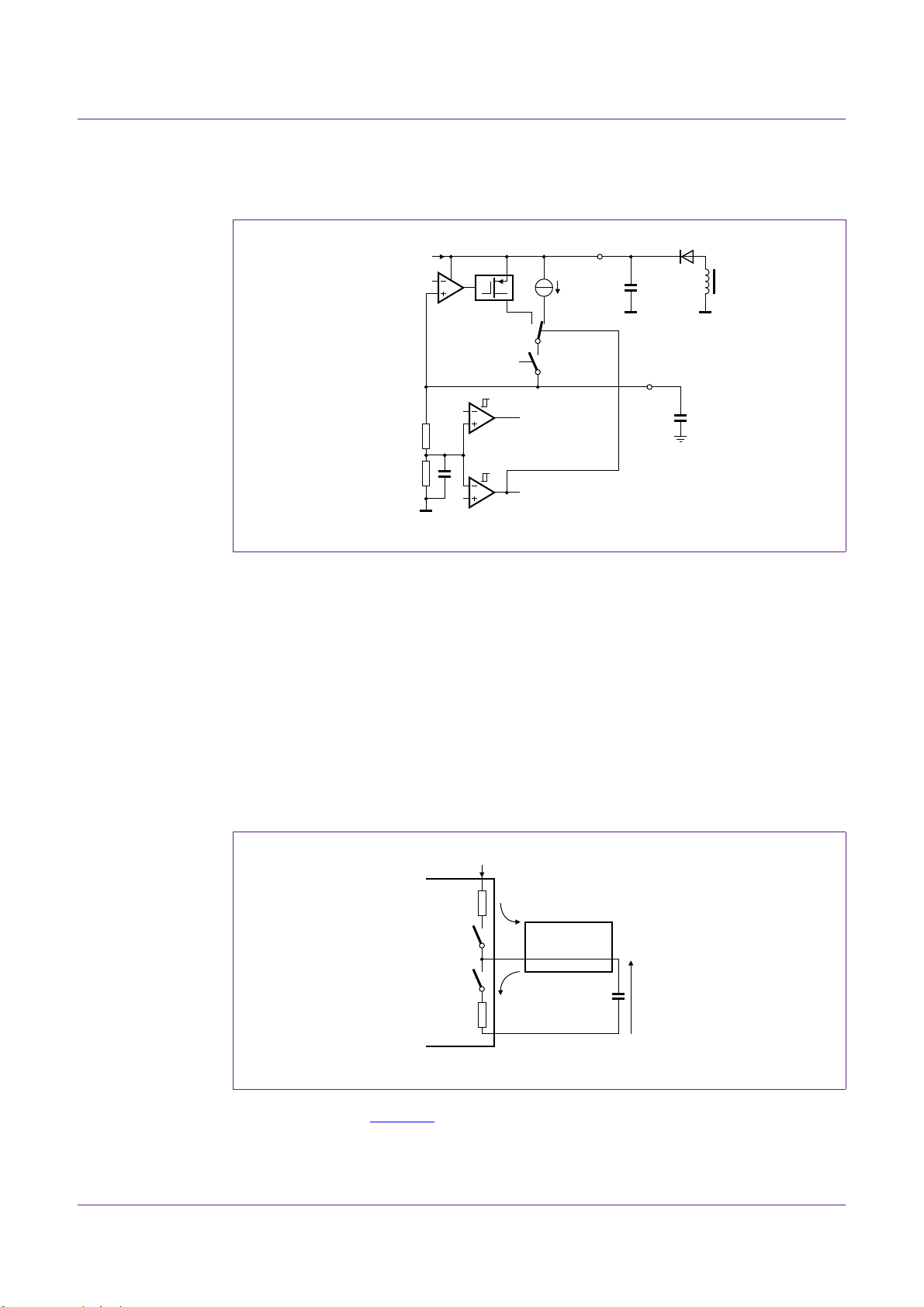

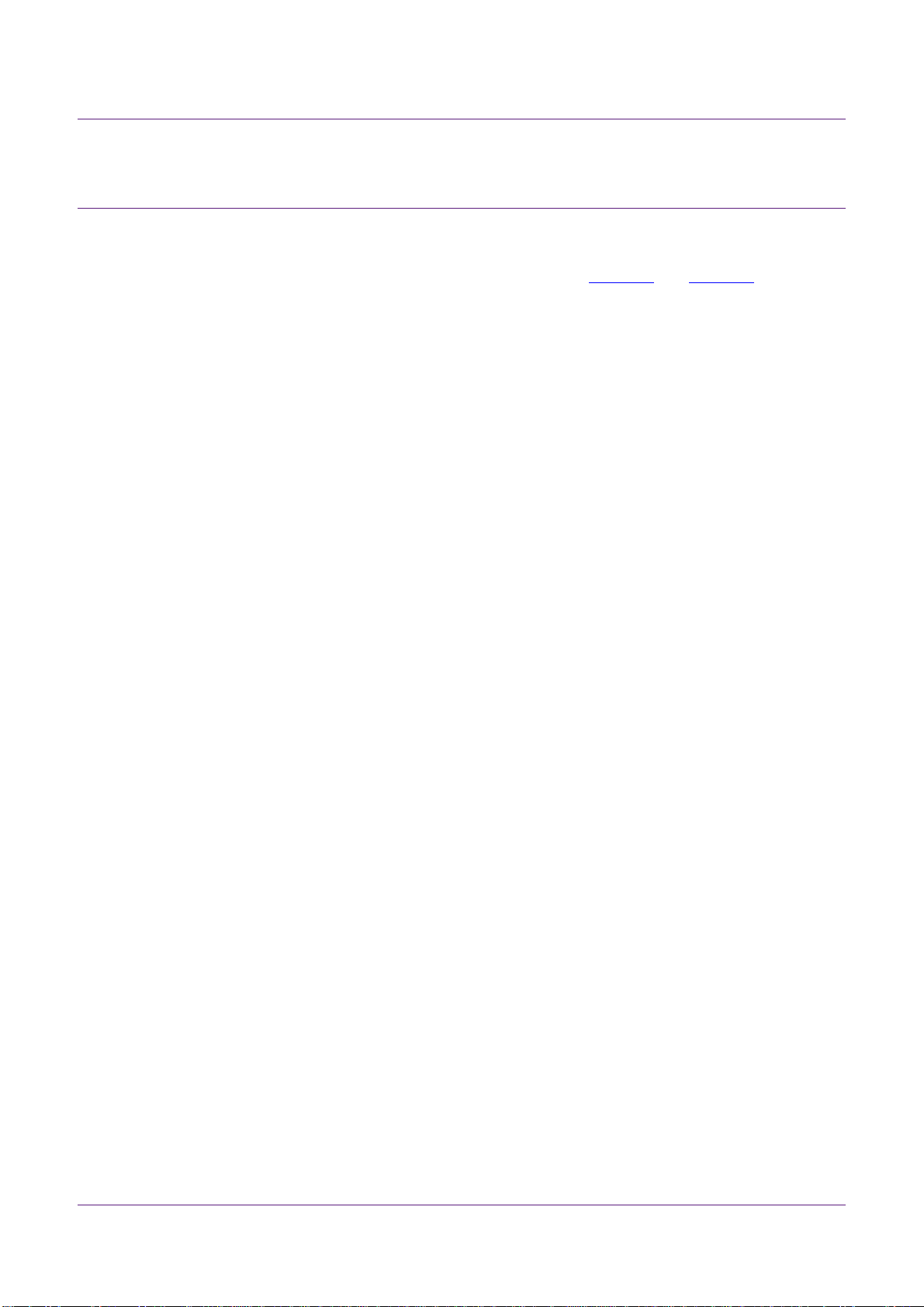

5.3.2 Block diagram for SUPIC start-up

AN10881

TEA1713 resonant power supply control IC with PFC

Fig 6. Block diagram: SUPIC and SUPREG start-up with SUPHV and auxiliary supply

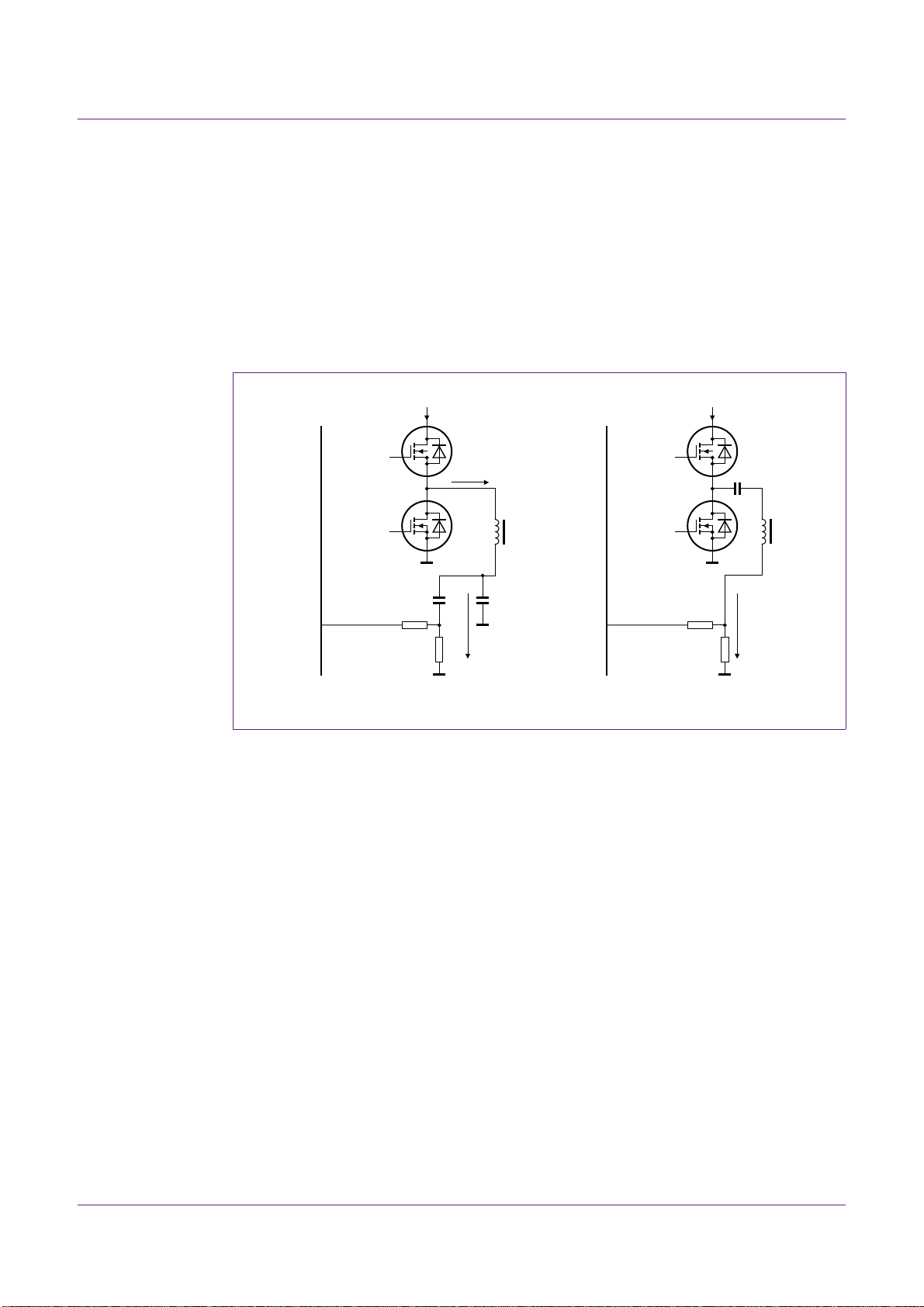

5.3.3 Auxiliary winding on the HBC transformer

An auxiliary winding on the HBC transformer can be used to obtain a supply voltage for

SUPIC during operation. As SUPIC has a wide operational voltage range (15 V to 38 V),

this is not a critical parameter.

But:

• The voltage on SUPIC must be low for low power consumption.

• The auxiliary supply must be made accurately representing the output voltage to use

the voltage from the auxiliary winding for IC supply and HBC output voltage

measurement (by SNSOUT). Place this winding on the secondary (output) side to

ensure good coupling.

• When mains insulation is included in the HBC transformer, it can impact the

construction of the auxiliary winding. Triple insulated wire is needed when the

auxiliary winding is placed on the mains-insulated area of the transformer

construction.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 19 of 102

Page 20

NXP Semiconductors

001aal019

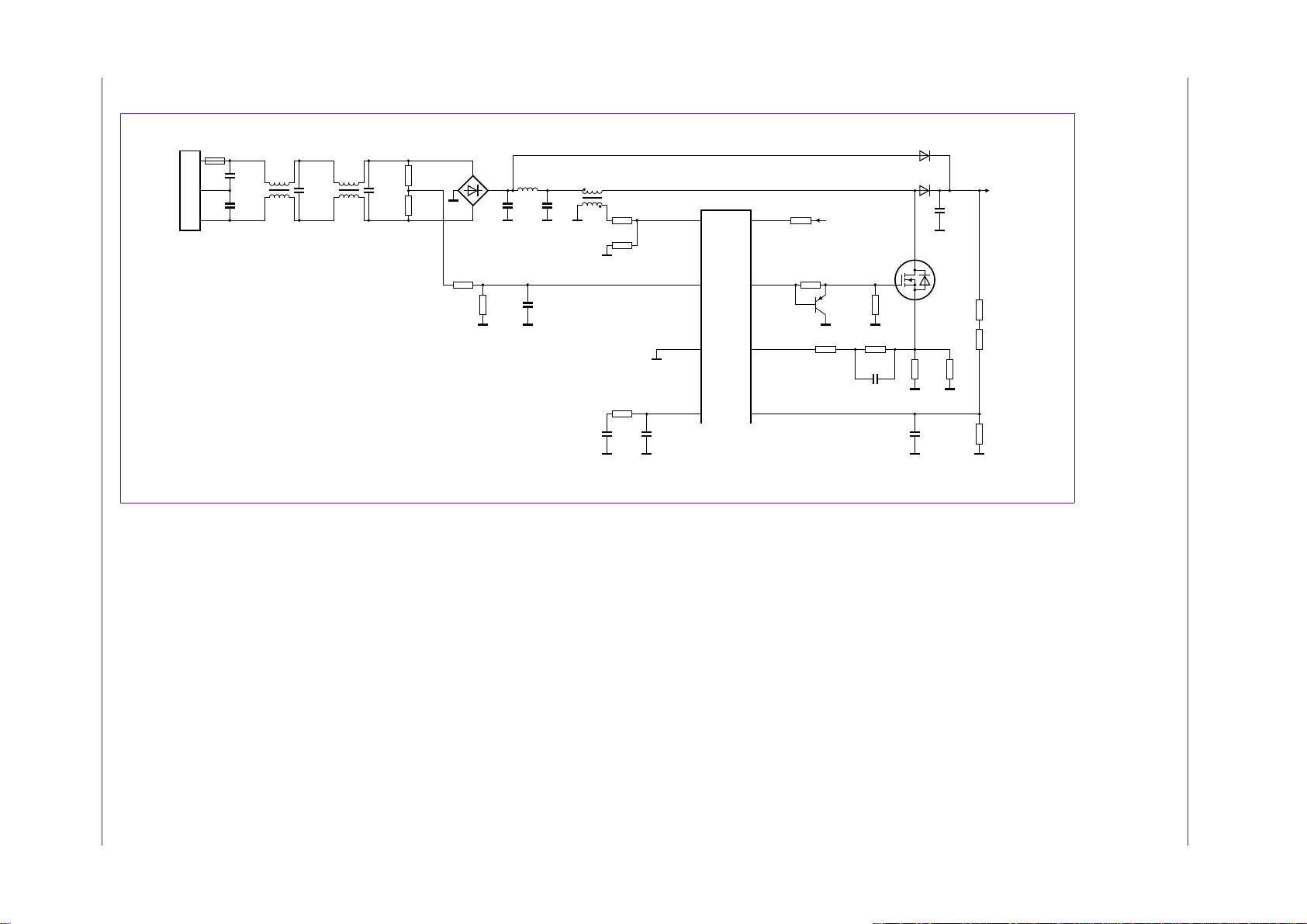

Fig 7. Auxiliary winding on primary side (left) and secondary side (right)

5.3.3.1 SUPIC and SNSOUT by auxiliary winding

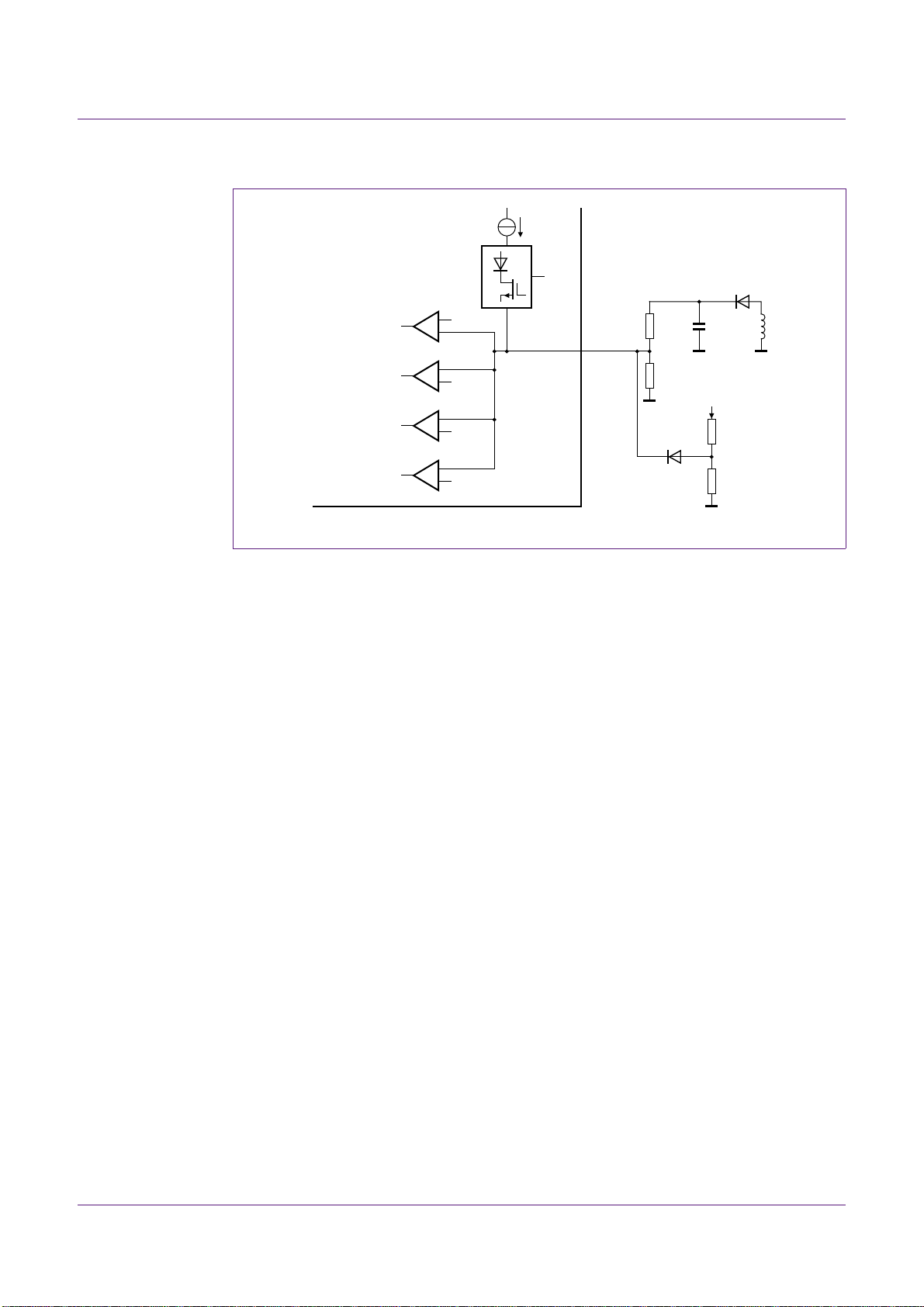

The SNSOUT input provides a combination of four functions:

• Overvoltage protection: SNSOUT > 3.5 V, latched

• Undervoltage protection: SNSOUT < 2.35 V, protection timer

• Hold HBC: SNSOUT < 1.1 V, stop switching HBC (for Burst mode)

• Hold HBC + PFC: SNSOUT < 0.4 V, stop switching HBC and PFC (for Burst mode)

AN10881

TEA1713 resonant power supply control IC with PFC

Remark: A more detailed explanation of the SNSOUT functions can be found in

Section 10.3.1

Often, a circuit is used which combines SUPIC and the output voltage monitoring by

SNSOUT, with one auxiliary winding on the HBC transformer. But an independent

construction for SUPIC and SNSOUT is also possible. This could be in a situation where

SUPIC is supplied by a separate standby supply and an auxiliary winding is only used for

output voltage sensing. It is also possible not to use SNSOUT for output sensing but as a

general-purpose protection input. See Section 10.3.3

In a combined function of SUPIC and SNSOUT by an auxiliary winding on the HBC

transformer, some issues must be addressed to obtain a good representation of the output

voltage for SNSOUT measurement.

The advantage of a good coupling/representation of the auxiliary winding with the output

windings is also that a stable auxiliary voltage is obtained for SUPIC. A low SUPIC voltage

value can be designed more easily for lowest power consumption.

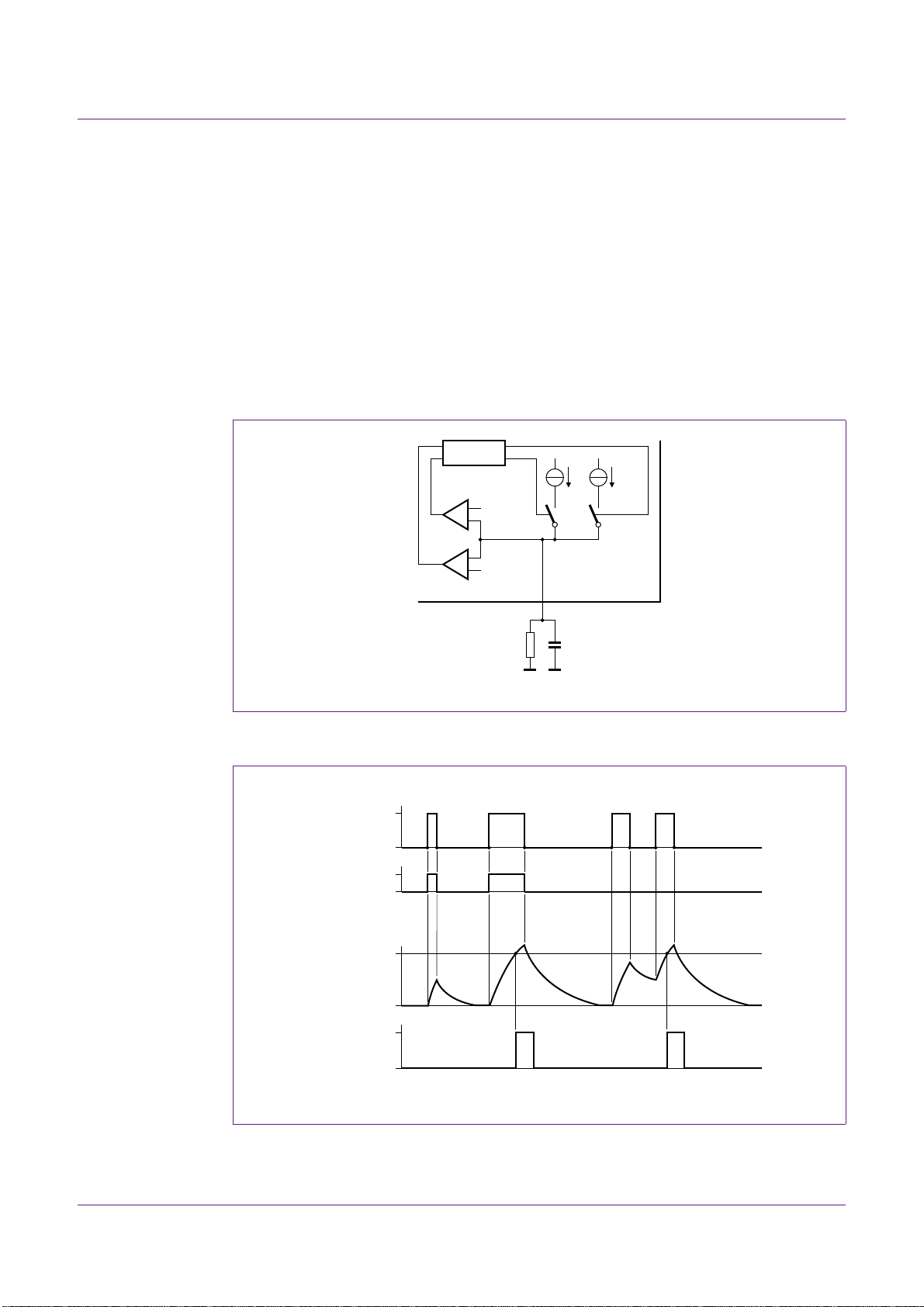

5.3.3.2 Auxiliary supply voltage variations by output current

At high (peak) current loads, the voltage drop across the series components of the HBC

output stage (resistance and diodes) is compensated by regulation. This results in a

higher voltage on the windings at higher output currents due to the higher currents

causing a larger voltage drop across the series components. An auxiliary winding supply

shows this variation caused by the HBC output.

and Section 10.3.2.

for more information.

5.3.3.3 Voltage variations by auxiliary winding position: primary side component

Due to a less optimal position of the auxiliary winding, the voltage for SNSOUT and/or

SUPIC can contain a certain amount of undesired primary voltage component. This can

seriously endanger the feasibility of the SNSOUT sensing function.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 20 of 102

Page 21

NXP Semiconductors

001aal020

secondary side

primary side

V

aux

V

aux

V

aux.new

V

aux.new

V

O

V

O

V

O

Bad coupling V

aux

to VO at high

output current

Good coupling

V

aux.new

to VO at

high output current

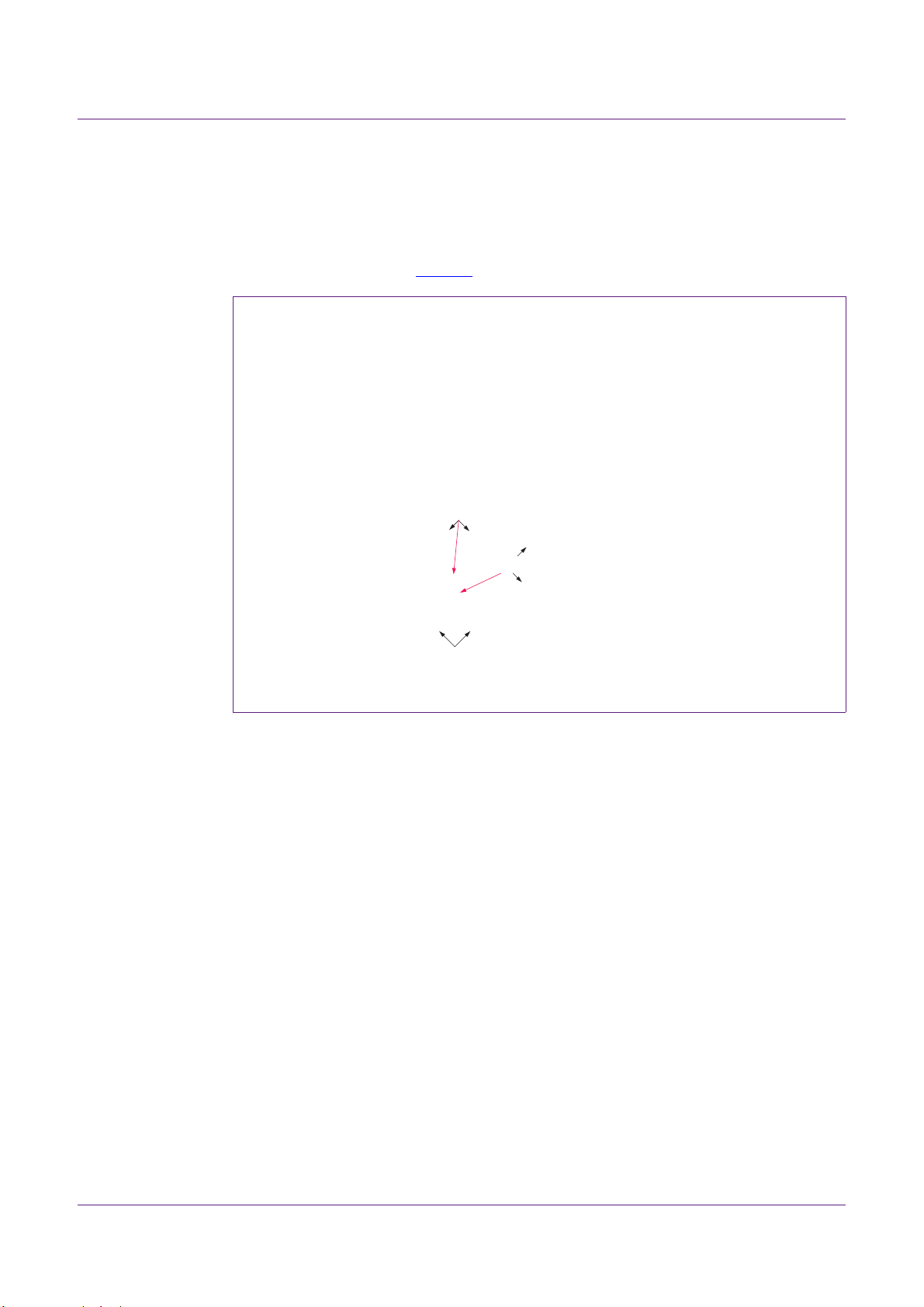

The coupling of the auxiliary winding with the primary winding must be as small as

possible to avoid a primary voltage component on the auxiliary voltage. Place the auxiliary

winding on the secondary winding(s) and as physically remote as possible from the

primary winding to obtain this. See differences in results given by comparison on

secondary side position in Figure 8

AN10881

TEA1713 resonant power supply control IC with PFC

.

Fig 8. Position the auxiliary winding for good output coupling

5.3.4 Difference between UVP on SNSOUT and SNSCURHBC OCP/OCR

In a system that uses output voltage sensing with the SNSOUT function, there can be an

overlap in functionality in an over power or short-circuit situation. In such a situation, often

both the SNSOUT UVP and the OCP/OCR on SNSCURHBC, activate the protection

timer.

There are basic differences between both functions:

• SNSOUT monitors (indirectly) the HBC output voltage or another external protection

circuit (such as NTC temperature measurement)

• OCP/OCR monitors the power in the system by sensing the primary current in detail

SNSOUT is a more general usable protection input while SNSCURHBC is specifically

designed for HBC operation. In addition, SNSOUT also of fers three other functions:

• OVP (latched)

• hold HBC

• hold HBC + PFC (for Burst mode)

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 21 of 102

Page 22

NXP Semiconductors

5.4 SUPIC supply by external voltage

5.4.1 Start-up

When the TEA1713 is supplied by an external DC supply, the SUPHV pin can remain

unconnected. The SUPIC start level is now 17 V.

When the SUPIC exceeds 17 V the internal regulator is activated and charge SUPREG.

At SUPREG 10.7 V, GATELS is switched on for the bootstrap function to charge

SUPHS. And at the same time the PFC operation is internally enabled. When all enable

conditions are met, the TEA1713 starts the PFC function and when V

approximately 90 % (SNSBOOST 2.3 V) of its nominal value, the HBC starts.

5.4.2 Stop

Operation of the TEA1713 can be stopped by switching off the external source for SUPIC.

When the voltage level on SUPIC drops below 15 V, operation is stopped.

In case of shutdown (because of protection), this state is reset by internal logic when the

SUPIC voltage drops below 7 V.

AN10881

TEA1713 resonant power supply control IC with PFC

reaches

boost

5.5 SUPREG

SUPIC has a wide voltage range for easy application. Because of this, SUPIC cannot be

directly used to supply the internal MOSFET drivers as this would exceed the allowed

gate voltage of many external MOSFETs.

The TEA1713 contains an integrated series stabilizer to avoid this issue and to create a

few other benefits. The series stabilizer generates an accurate regulated voltage on

SUPREG on the external buffer capacitor.

This stabilized SUPREG voltage is used for:

• Supply of internal PFC driver

• Supply of internal low-side HBC driver

• Supply of internal high-side driver via external components

• Reference voltage for optional external circuits

The series stabilizer for SUPREG is enabled after SUPIC has been charged. In this way

optional external circuitry at SUPREG does not consume from the start-up current during

the charging of SUPIC. The capacitor on SUPIC acts as a buffer at charge of SUPREG

and start-up of the IC.

The SUPREG voltage must reach the V

ensure that the external MOSFETs receive sufficient gate drive, provided that the SUPIC

voltage has also reached the start level.

start(SUPREG)

level before the IC starts operating to

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 22 of 102

Page 23

NXP Semiconductors

001aal002

SUPREG load current (mA)

0604020

10.905

10.895

10.915

10.925

SUPREG

voltage

(V)

10.885

SUPIC = 17 V

SUPIC = 20 V

Temperature (°C)

−50 150100050

001aal021

10.85

10.90

10.80

10.95

11.00

SUPREG

voltage

(V)

10.75

The SUPREG has an UnderVoltage Protection. When the SUPREG voltage drops below

the 10.3 V two actions take place:

• The IC stops operating to prevent unreliable switching due to too low gate driver

• The maximum current from the internal SUPREG series stabilizer is reduced to

It is important to realize that in principle, SUPREG can only source current.

The drivers of GATELS and GATEPFC are supplied by this volt age and dr aw current fr om

it during operation depending on the operating condition. Some change in value can be

expected due to current load and temperature:

AN10881

TEA1713 resonant power supply control IC with PFC

voltage. The PFC controller stops switching immediately, but the HBC continues until

the low-side stroke is active.

5.4 mA. In case of an overload at SUPREG in combination with an external DC supply

for SUPIC, this action reduces the dissipation in the series stabilizer.

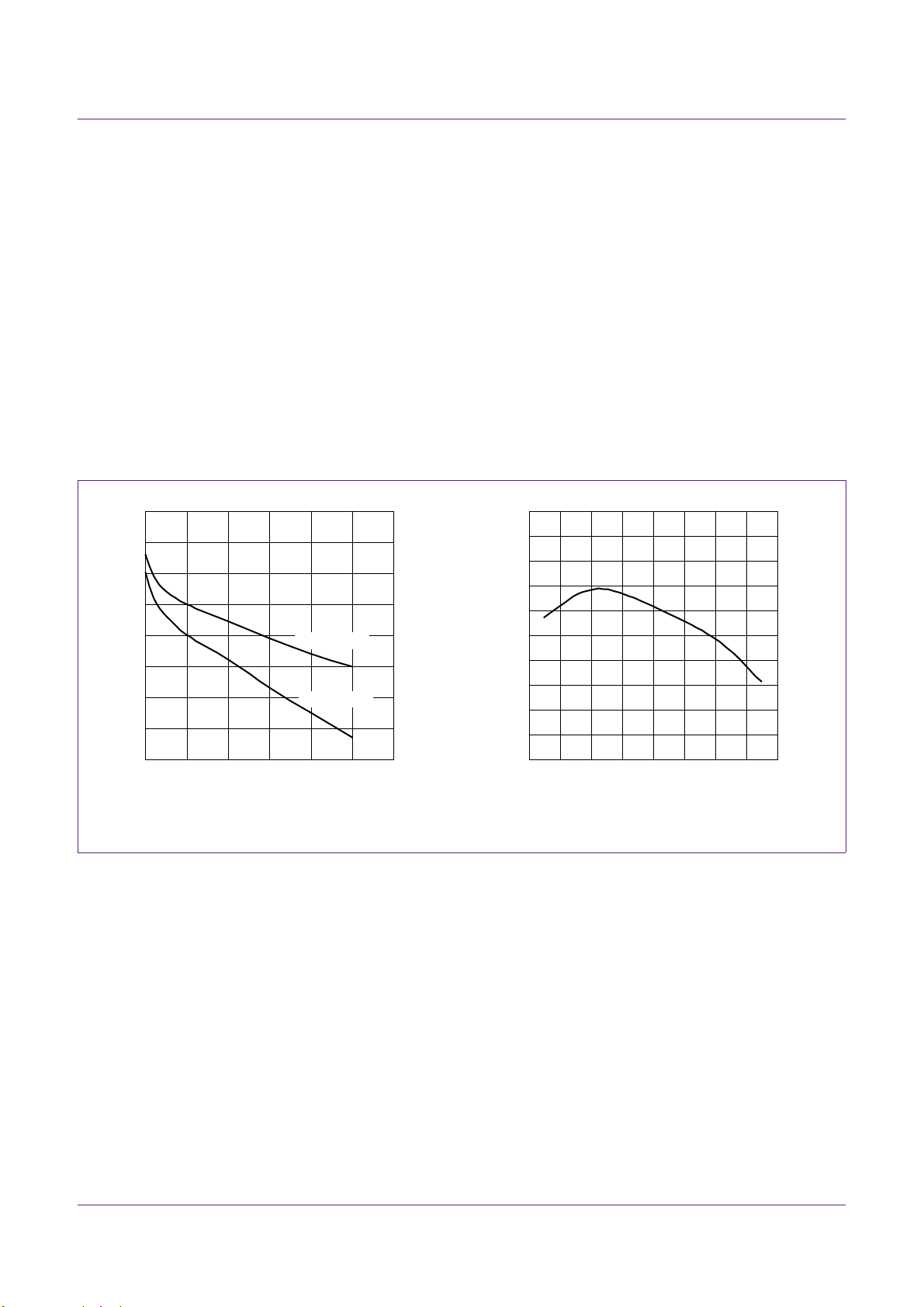

Voltage characteristics for load Voltage characteristics for temperature

Fig 9. Typical SUPREG voltage characteristics for load and temperature

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 23 of 102

Page 24

NXP Semiconductors

001aal022

11 V

5.4 mA

C

SUPIC

C

SUPREG

SUPIC

SUPREGSupReg

EnableSupReg

SUPHV SOURCE

V

AUXILIARY

reduced

current

SupRegUvStart

startlevel = 10.7 V

SupRegUvStop

stoplevel = 10.3 V

001aal023

EXTERNAL

GATE CIRCUIT

SUPREG

R

DS-ON

Cgs

Vgs

I

discharge

I

charge

R

DS-ON

TEA1713

5.5.1 Block diagram of SUPREG regulator

Fig 10. Block diagram of internal SUPREG regulator

AN10881

TEA1713 resonant power supply control IC with PFC

5.5.2 SUPREG during start-up

SUPREG is supplied by SUPIC. SUPIC is the unregulated external powe r sou rc e th at

provides the input voltage for the internal voltage regulator that provides SUPREG.

At start-up SUPIC must reach a specific voltage level before SUPREG is activated:

• Using the internal HV supply, SUPREG is activated when SUPIC 22 V

• Using an external low voltage supply, SUPREG is activated when SUPIC 17 V

5.5.3 Supply voltage for the output drivers: SUPREG

The TEA1713 has a powerful output stage for GATEPFC and GATELS to drive large

MOSFETs. These internal drivers are supplied by SUPREG that provides a fixed voltage.

Fig 11. Simplified model of MOSFET drive

It can be seen from Figure 11 that current is taken from SUPREG when the external

MOSFET is switched on by charging the gate to a high voltage.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 24 of 102

Page 25

NXP Semiconductors

The shape of the current from SUPREG at switch-on is related to:

• The supply voltage for the internal driver (10.9 V)

• The characteristic of the internal driver

• The gate capacitance to be charge d

• The gate threshold voltage for the MOSFET to switch on

• The external circuit to the gate

Remark: The switching moments of GATEPFC and GATELS are independent in time.

The charging of SUPHS for GATEHS is synchronized in time with GATELS but has a

different shape because of the bootstrap function.

5.5.4 Supply voltage for the output drivers: SUPHS

The high-side driver is supplied by an external bootstrap buffer capacitor. The bootstrap

capacitor is connected between the high-side reference pin HB and the high-side driver

supply input pin SUPHS. During the time that HB is low an external diode from SUPREG

charges this capacitor. By selecting a suitable external diode, the voltage drop between

SUPREG and SUPHS can be minimized. This is especially important when using a

MOSFET that needs a large amount of gate charge and/or when switching at high

frequencies.

AN10881

TEA1713 resonant power supply control IC with PFC

Instead of using SUPREG as the power source for charging SUPHS, another supply

source can be used. In such a construction it is important to check for correct start/stop

sequences and to prevent the voltage exceeding the maximum value of HB +14 V.

Remark: The current taken from SUPREG to charge SUPHS differs for each cycle in time

and shape from the current taken by drivers GATEPFC and GATELS.

5.5.4.1 Initial charging of SUPHS

At start-up, SUPHS is charged by the bootstrap function by setting GATELS high to switch

on the low side MOSFET. While SUPHS is being charged, GATELS is switched on for

charging and the PFC operation is started. The time betwe en start charging and start HBC

operation is normally sufficient to charge SUPHS completely. Start HBC operation is when

SNSBOOST reaches 2.3 V which is approximately 90 % of the nominal V

5.5.4.2 Current load on SUPHS

The current taken from SUPHS consists of two parts:

• Internal MOSFET driver GATEHS

• Internal circuit to control GATEHS (37 A, quiescent current)

Figure 12

shape of the current from SUPHS at switch-on is related to:

shows that the current taken by the driver GATEHS occurs at switch-on. The

• The value of the supply voltage for the internal driver

• The characteristic of the internal driver

• The gate capacitance to be charge d

• The gate threshold voltage for the MOSFET to switch on

• The external circuit to the gate

boost

.

The voltage value of SUPHS can vary.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 25 of 102

Page 26

NXP Semiconductors

001aal024

14 SUPHS

GATEHS

GATELS

15 HB

9 SUPREG

V

BOOST

TEA1713

I

SUPIC

2Q

gatefbridge

=

Fig 12. Typical application of SUPHS

5.5.4.3 Lower voltage on SUPHS

During normal operation, each time the Half-Bridge (HB) node is switched to grou nd level,

the bootstrap function charges the SUPHS capacitor. Because of the voltage drop across

the bootstrap diode, the value of SUPHS is normally lower than SUPREG (or other

bootstrap supply input).

AN10881

TEA1713 resonant power supply control IC with PFC

The voltage drop across the bootstrap diode is directly related to the am ount of current

that is required to charge SUPHS. The resultant SUPHS voltage also has a relation to the

time available for charging.

A large voltage drop occurs when an externa l MOSFET with a large gate capacit ance has

to be switched at high frequency (high current and a short time).

Also, during Burst mode operation, a low voltage on SUPHS can occur. In Burst mode

there are (long) periods of not switching and therefore no ch arging of SUPHS. Dur ing th is

time the circuit supplied by SUPHS slowly discharges the supply volt age cap a citor. When

a new burst starts, the SUPHS voltage is lower than during normal operation. During the

first switching cycles SUPHS is recharged to its normal level. During Burst mode, at low

output power , the switching frequency is normally rather high which limits a fast recovery

of the SUPHS voltage.

Although in most applications the voltage drop is limited, it is an important issue to be

evaluated. It can influence the selection of the best diode type for the bootstrap function

and the value of the buffer capacitor on SUPHS.

5.5.5 SUPREG power consumed by MOSFET drivers

During operation the drivers GATEPFC, GATELS and GATEHS charging the gate

capacitances of the external MOSFETs are a major part of the power consumption from

SUPREG. The amount of energy required in time is linear to the switching frequency.

Often, for the MOSFETs used, the total charge is specified for certain conditions. With this

figure an estimation can be made for the amount of current needed from SUPREG.

5.5.5.1 GATELS and GATEHS (driving a total of two MOSFETs)

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 26 of 102

(1)

Page 27

NXP Semiconductors

I

SUPIC

240 nC 100 kHz 8 mA==

I

SUPIC

Q

gatefPFC

=

I

SUPIC

40 nC 100 kHz 4 mA==

Example:

AN10881

TEA1713 resonant power supply control IC with PFC

• Q

• f

gate

bridge

=40nC

=100kHz

Remark: The calculated value is generally higher than the practical value, because the

switching operation deviates from the MOSFET specification for Q

5.5.5.2 GATEPFC

Example:

• Q

• f

gate

bridge

=40nC

=100kHz

5.5.6 SUPREG supply voltage for other circuits

The regulated voltage of SUPREG can also be used as a regulated supply for an external

circuit. The load of the external circuits affects the start-up (time) and the total load

(IC + extern al circ uit ) of SUPREG durin g op e ra tio n.

gate

.

(2)

5.5.6.1 Current available for supplying an external circuit from SUPREG

The total current available from SUPREG is a minimum of 40 mA. How much current the

IC is using must be determined to ensure how much current is available for an external

circuit.

I

SUPREG_for_external

=40mA I

SUPREG_for_IC

With respect to the IC, by far the greatest amount of current from SUPREG is consumed

by the MOSFET drivers (GATELS, GA TEHS and GATEPFC). Other circuit pa rt s in the IC,

consume a maximum of 3 mA.

I

SUPREG_for_IC=ISUPREG_for_MOSFET-drivers+ISUPREG_for_other_IC-circuits

I

SUPREG_for_IC=ISUPREG_for_MOSFET-drivers

I

SUPREG_for_MOSFET-drivers

can be estimated by the method provided in Section 12

+4mA

max

5.5.6.2 An estimation by measurement

The current used by SUPIC, while supplying the circuit from an external power supply , can

be assumed as a first approximation of how much current the IC circuits take from

SUPREG. Using this value, an estimation can be made of the power available for external

circuits.

Remark: The highest power consumption value is reached when the MOSFET drivers

are switching at the highest frequency.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 27 of 102

Page 28

NXP Semiconductors

C

SUPICISUPIC start-up

t

Vaux 15 V

V

SUPIC start-up

----------------------------------------- -

10 mA

70 ms

7 V

-------------- -

100 F==

Example:

AN10881

TEA1713 resonant power supply control IC with PFC

I

SUPIC(maximum measured)

I

SUPREG(for IC circuits)=ISUPIC(maximum measured)

I

SUPREG(for externals)

=18mA

=40mA I

=18mA

SUPREG(for IC circuits)

=40mA 18 mA = 22 mA

Remark: SUPREG must remain above the undervoltage protection level of 10.3 V to

maintain full functionality. During start-up, high external current loads can lead to

problems.

5.6 Value of the capacitors on SUPIC, SUPREG and SUPHS

Some practical examples are provided in Section 12.

5.6.1 Value of the capacitor on SUPIC

5.6.1.1 General

Use two types of capacitors on SUPIC. An SMD ceramic type with a smaller value located

close to the IC and an electrolytic type with the major part of the capacitance.

5.6.1.2 Start-up

When the supply is initially provided by an HV source, before being handled by an

auxiliary winding, a larger capacitor is needed. The capacitor value must be large enough

to handle the start-up before the auxiliary winding takes over the supply of SUPIC.

Example:

• I

SUPIC(start-up)

• V

SUPIC(start-up)

• t

Vaux>15V

=10mA

=22V 15 V = 7 V

=70ms

5.6.1.3 Normal operation

The main purpose of the capacitors on SUPIC for normal operation is to keep the current

load variations (e.g. gate drive currents) local.

5.6.1.4 Burst mode operation

When Burst mode operation is applied, the supply construction often uses an auxiliary

winding and start-up from an HV source. While in Burst mode there is a long period during

which the auxiliary winding is not able to charge the SUPIC because there is no HBC

switching (time between two bursts). Therefore, the capacitor value on SUPIC must be

large enough to keep the voltage above 15 V to prevent activating the SUPIC

undervoltage stop level.

(3)

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 28 of 102

Page 29

NXP Semiconductors

C

SUPICISUPIC start-up between 2 bursts

t

between 2 bursts

V

SUPIC burst

---------------------------------------- -

4 mA

25 ms

4 V

-------------- -

25 F==

Example:

AN10881

TEA1713 resonant power supply control IC with PFC

• I

SUPIC(between 2 bursts)

• V

SUPIC(burst)=Vaux burst

• t

between 2 bursts

=4mA

15 V = 19 V 15 V = 4 V

=25ms

5.6.2 Value of the capacitor for SUPREG

The capacitor on SUPREG must not be larger than the capacitor on SUPIC to support

charging of SUPREG during an HV source start. This is to prevent a severe voltage drop

on SUPIC due to the charge of SUPREG. If SUPIC is supplied by an external (standby)

source, this is not important.

SUPREG is the supply for the current of the gate drivers. Keepin g current peaks lo cal can

be achieved using an SMD ceramic capacitor supported by an electrolytic capacitor. This

is necessary to provide sufficient capacitance to prevent voltage drop during high current

loads. The value of the capacitor on SUPREG must be much larger than the (total)

capacitance of the MOSFETs that must be driven (including the SUPHS parallel load and

capacitor bootstrap construction) to prevent significant voltage drop.

When considering the internal voltage regu lator , the value of the cap acitance on SUPREG

must be 1 F. Often a much larger value is used for the reasons mentioned previously.

(4)

5.6.3 Value of the capacitor for SUPHS

The SUPHS capacitor must be much larger than the gate capacitance to support charging

the gate of the high side MOSFET. This is to prevent a significant voltage drop on SUPHS

by the gate charge. When Burst mode is applied, SUPHS is discharged by 37 A during

the time between two bursts.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 29 of 102

Page 30

NXP Semiconductors

001aal024

14 SUPHS

GATEHS

GATELS

15 HB

9 SUPREG

V

BOOST

TEA1713

TEA1713 resonant power supply control IC with PFC

6. MOSFET drivers GATEPFC, GATELS and GATEHS

The TEA1713 provides three outputs for driving external high- voltage power MOSFETs:

• GATEPFC for driving the PFC MOSFET

• GATELS for driving the low side of the HBC MOSFET

• GATEHS for driving the low side of the HBC MOSFET

6.1 GATEPFC

The TEA1713 has a strong output stage for PFC to drive a high-voltage power MOSFET.

It is supplied by the fixed voltage from SUPREG = 10.9 V.

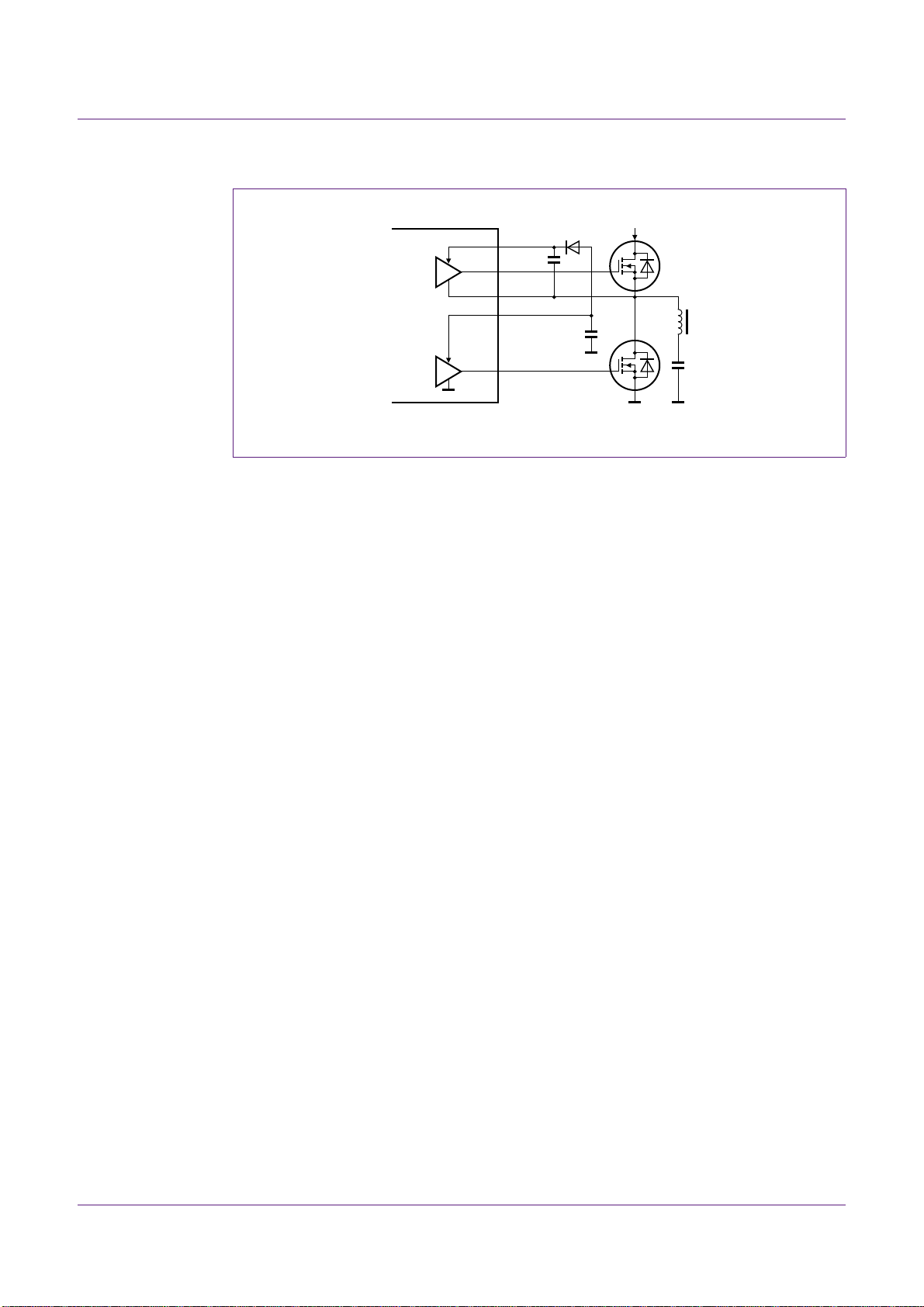

6.2 GATELS and GATEHS

Both drivers have identical driving capabilities for the gate of an external high-voltage

power MOSFET. The low-side driver is referenced to pin PGND and is supplied from

SUPREG. The high-side driver is floating, referenced to HB, the connection to the

midpoint of the external half-bridge. The high-side driver is supplie d by a capacitor on

SUPHS that is supplied by an external bootstrap function by SUPREG. The bootstrap

diode charges the capacitor on SUPHS when the low-side MOSFET is on.

AN10881

Fig 13. GATELS and GATEHS drivers

Both HBC drivers have a strong current source capability and an extra strong current sink

capability. In general operation of the HBC, fast switch-on of the external MOSFET is not

critical, as the HB node swings automatically to the correct state after switch-off. Fast

switch off however, is important to limit switching losses and prevent delay especially at

high frequency.

6.3 Supply voltage and power consumption

See Section 5.5.3 and Section 5.5.5.for a description of the supply voltages and power

consumption by the MOSFET drivers.

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 30 of 102

Page 31

NXP Semiconductors

001aal025

GATEPFC

GATEPFC

GATEPFC

GATEPFC

d.

c.

b.

a.

6.4 General subjects on MOSFET drivers

6.4.1 Switch on

The time to switch on depends on:

• The supply voltage for the internal driver

• The characteristic of the internal driver

• The gate capacitance to be charge d

• The gate threshold voltage for the MOSFET to switch on

• The external circuit to the gate

6.4.2 Switch off

The time to switch off depends on:

• The characteristic of the internal driver

• The gate capacitance to be discharged

• The voltage on the gate just before discharge

• The gate threshold voltage for the MOSFET to switch off

• The external circuit to the gate

AN10881

TEA1713 resonant power supply control IC with PFC

Because the timing for switching off the MOSFET is more critical than switching it on, the

internal driver can sink more current than it can source . At higher frequencies and/or short

on-time, timing becomes more critical for correct switching. Sometimes a compromise

must be made between fast switching and EMI effects. A gate circuit between the driver

output and the gate can be used to optimize the switching behavior.

Fig 14. Gate circuits examples

Switching the MOSFETs on and off by the drivers can be approximated by alternating

charge and discharge of a (gate-source) capacitance of the MOSFET through a resistor

(R

of the internal driver MOSFET).

DSon

AN10881 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2011. All rights reserved.

Application note Rev. 2 — 26 September 2011 31 of 102

Page 32

NXP Semiconductors

001aal023

EXTERNAL

GATE CIRCUIT

SUPREG

R

DS-ON

Cgs

Vgs

I

discharge

I

charge

R

DS-ON

TEA1713

Fig 15. Simplified model of a MOSFET drive

6.5 Specifications

The main function of the internal MOSFET drivers is to source current and sink current to