Page 1

Online UPS

Designer Reference Manual

56800E

16-bit Digital Signal Controllers

DRM069

Rev. 0

06/2005

freescale.com

Page 2

Online UPS

Designer Reference Manual

To provide the most up-to-date i nformation, the revisi on of our documents on the Worl d Wide Web will be

the most current. Your printed copy may be an earlier revision. To verify that you have the latest

information available, refer to http://www.freescale.com

The following revision history table summarizes changes contained in this document. For your

convenience, the page number designators have been linked to the appr opriate location.

Revision History

Date

06/2005 0 Initial release N/A

Revision

Level

Description

Page

Number(s)

Page 3

TABLE OF CONTENTS

Chapter 1 Online UPS Theory and Description

1.1 Introduction. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1.1 The Concept of an Online UPS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1.2 Input Power Factor Control (PFC). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1.1.3 DC-to-DC Converters . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.1.4 Phase Locked Loop (PLL). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.1.5 Bypass Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-2

1.1.6 Rail Ripple. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.1.7 Pulse Width Modulation (PWM) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.1.8 A Controller Solution to Control a UPS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-3

1.2 System Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1.3 System Actuators. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-5

1.4 Input Rectifier Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1.4.1 Rectifier Soft Start. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1.5 Power Factor Corrector (PFC) Theory of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1.6 Battery Charger Theory of Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1.7 Battery Booster Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

1.8 Inverter Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

1.9 Pulse Width Modulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

1.10 Auxiliary Circuits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

1.10.1 Power Supplies and Isolation Circuitry . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-20

1.10.2 Sensing Circuits and Reference Voltage Generator. . . . . . . . . . . . . . . . . . . . . . . 1-23

1.10.3 Voltage Reference Supply . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-25

1.10.4 Silicon Controlled Rectifier (SCR) Gate Drivers . . . . . . . . . . . . . . . . . . . . . . . . . . 1-26

1.10.5 IGBT and MOSFET Gate Drivers Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-26

1.11 Power Transfer Circuits (Bypass) Theory of Operation . . . . . . . . . . . . . . . . . . . . . . . 1-27

1.12 Overcurrent Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-28

1.13 Battery Temperature Sensing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30

Chapter 2 Control Loops In The Online UPS

2.1 Control Algorithms Discrete Equivalents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

2.2 PFC and Rail Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-2

2.3 Battery Charger Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2.4 Inverter Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2.5 Battery Booster Control Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-8

2.6 Minimizing Delay in the Control Loops. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-10

Table of Contents, Rev. 0

Freescale Semiconduc tor i

Preliminary

Page 4

Chapter 3 Control Board Design Considerations

3.1 56F8346 Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

3.2 Reset/Modes/Clock . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3.3 Program And Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3.4 RS-232 Serial Communications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3.5 LCD Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3.6 Peripheral Expansion Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.6.1 Wireless Board Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.6.2 PWM Ports Expansion Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3.6.3 A/D Ports Expansion Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.6.4 Timer A Expansion Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3.6.5 GPIOPort C Expansion Connector (Bits 0—1) . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.6.6 GPIOPort D Expansion Connector (Bits 10—11) . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.7 Daughter Card Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3.8 CAN Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3.9 Debug Support. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.9.1 JTAG Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3.9.2 Parallel JTAG Interface Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3.10 A/D Filters. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3.11 Power Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

Chapter 4 Operational Description

4.1 Panel Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4.2 Operation with EVM or Control Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-2

4.2.1 Jumper Configuration for EVM and Control Board Operation. . . . . . . . . . . . . . . . . 4-3

4.3 Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.3.1 Installing Batteries. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.3.2 Before Applying Power to the UPS. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-7

4.3.3 Turning the UPS On . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

4.3.4 Turning the UPS Off . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-8

Chapter 5 Control Software Design Considerations

5.1 Peripheral and I/O Pins Assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5.2 Main Execution Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-2

5.3 Interrupt Handlers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.3.1 ADC End of Conversion Interrupt Service Routine. . . . . . . . . . . . . . . . . . . . . . . . . 5-4

5.3.2 UPS Overcurrent Protection Interrupt Handlers . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5.3.3 Battery Temperature Reading. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-11

5.3.4 Delay_Timer_OnInterrupt . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

Online UPS Designer Reference Manual, Rev. 0

ii Freescale Semiconductor

Preliminary

Page 5

5.4 Program Loop Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5.5 Inverter Control Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

5.6 PFC Control Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

5.7 Battery Booster Control Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

5.8 Battery Charger Control Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

5.9 Phase Locked Loop Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5.9.1 Phase Discriminator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5.9.2 Control Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-18

5.9.3 Sine Wave Look-Up Table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

5.10 Frequency Measurement Routine . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-20

5.11 Rectifier Soft Start Routine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

5.12 Root Mean Square (RMS) Sensing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

5.13 Power Sensing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

5.14 Routine for Measurement of the Battery Stored Charge . . . . . . . . . . . . . . . . . . . . . . 5-23

5.15 General Purpose Digital Filters Used in the Implementation . . . . . . . . . . . . . . . . . . . 5-24

5.15.1 10Hz Low Pass Filter, 2 Stages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-24

5.15.2 High-Frequency Noise Rejection Filter. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

5.16 Flash Memory Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

5.17 Development Tools Used for Software Implementation . . . . . . . . . . . . . . . . . . . . . . . 5-26

5.17.1 Processor ExpertTM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-26

5.17.2 Intrinsic 56800E Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

5.17.3 Direct Register Writes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

5.17.4 Assembly Inlines. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-27

Chapter 6 Connectivity Software Design Considerations

6.1 Connectivity Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.2 Peripheral and I/O Pins Assignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6.3 Implementation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.1 LAN91C111 Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.2 Network Buffers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6.3.3 Ethernet Abstraction Layer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.3.4 OpenTCP Stack . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.3.5 Application Level Processing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.4 Connectivity Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-3

6.4.1 System Services Initialization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6.4.2 Physical Layer Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.4.3 Network Layers Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6.4.4 Application Layer Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

Table of Contents, Rev. 0

Freescale Semiconduc tor iii

Preliminary

Page 6

6.5 Main Application. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6.5.1 Stack Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

6.6 Interrupt Handlers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

Chapter 7 Results

7.1 Inverter Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1.1 Inverter Waveforms Under No Load Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7.1.2 Inverter Voltage Harmonics Under No Load Conditions. . . . . . . . . . . . . . . . . . . . . 7-2

7.1.3 Inverter Waveforms Under Linear Load Conditions . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7.1.4 Inverter Voltage Harmonics Under No Load Conditions. . . . . . . . . . . . . . . . . . . . . 7-3

7.1.5 Inverter Waveforms Under Full Load Conditions—Battery Operated. . . . . . . . . . . 7-3

7.1.6 Inverter Voltage Harmonics Under Full Load Conditions—Battery Operated. . . . . 7-4

7.1.7 Inverter Transient Response—60W Cold Bulb. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7.1.8 Inverter Transient Response to a Resistive Load (200W) . . . . . . . . . . . . . . . . . . . 7-5

7.2 PFC Performance Measurements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-5

7.2.1 PFC Performance Under Full Load Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.2.2 PFC Performance at 298W Linear Load Conditions. . . . . . . . . . . . . . . . . . . . . . . . 7-6

7.2.3 PFC Performance at 59W Linear Load Conditions. . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.2.4 PFC—Transient Response to a Load Step. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7.3 Frequence Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

7.4 Battery Charger Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.4.1 Battery Charger Performance, Current and Voltage Waveforms . . . . . . . . . . . . . . 7-9

7.4.2 Battery Charger—Floating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7.5 Bypass Switch Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

7.5.1 Inverter Bypass Switch Operation. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

Appendix A Schematics

A.1 Control Board Schematics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . A-2

A.2 Power Board Schematics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .A-15

Appendix B Bill of Materials

B.1 Specifications of Ferromagnetic Materials . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .B-9

Online UPS Designer Reference Manual, Rev. 0

iv Freescale Semiconductor

Preliminary

Page 7

LIST OF FIGURES

1-1 A Basic Online UPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

1-2 UPS Simplified Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1-3 Prototype UPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-4

1-4 Relationship between a 56800E and Power Actuators. . . . . . . . . . . . . . . . . . . . . . 1-5

1-5 Simplified Schematic Diagram of the UPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-6

1-6 Input Rectifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-7

1-7 Full Wave-Controlled Rectifier Bridge. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1-8 Relationship between Rectifier Soft Start Operation / Actuator Signals

and the AC Main Line Voltage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-8

1-9 Typical Rectifier Current vs. AC Line Voltage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-9

1-10 PFC Current and Voltage Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-10

1-11 PFC Schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-11

1-12 Partial PFC Schematic when U1 Is Open and U2 Is Closed. . . . . . . . . . . . . . . . . 1-11

1-13 Partial PFC Schematic when U1 Is Closed and U2 Is Open. . . . . . . . . . . . . . . . . 1-12

1-14 Resulting Parallel Connection between C3 and C7 . . . . . . . . . . . . . . . . . . . . . . . 1-13

1-15 Voltage Boost across Capacitors C3 and C8 . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-13

1-16 Battery Charger Schematic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-14

1-17 Battery Booster Schematic . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-15

1-18 Drive Signals for Battery Booster Switches. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-16

1-19 Signals at Transformer Secondary Windings L10 and L9. . . . . . . . . . . . . . . . . . . 1-16

1-20 Signals at the Cathode of D25 and Anode of D26 . . . . . . . . . . . . . . . . . . . . . . . . 1-17

1-21 Inverter Schematic Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-18

1-22 Generation of a PWM Signal. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-19

1-23 H Bridge Configuration used to Provide Multiple Floating Power Supplies. . . . . . 1-20

1-24 Waveforms at A and B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-21

1-25 Current Waveforms. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-22

1-26 Control Power Supply. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-23

1-27 Partial View of the Auxiliary Power Supply and Optoisolation Network . . . . . . . . 1-24

1-28 General Design of the Sensing Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-24

1-29 Voltage Reference Generator. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-25

1-30 SCR Gate Driver. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-26

1-31 IGBT and MOSFET Gate Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-26

1-32 Bypass Relay Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-27

1-33 Relay Driver . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-28

List of Figures, Rev. 0

Freescale Semiconduc tor v

Preliminary

Page 8

1-34 Overcurrent Protection for Rectifier and Inverter . . . . . . . . . . . . . . . . . . . . . . . . . 1-29

1-35 Overcurrent Protection for Charger and Push-Pull . . . . . . . . . . . . . . . . . . . . . . . . 1-29

1-36 Battery Temperature Sensing Circuitry. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-30

1-37 Battery Temperature Sensor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-31

2-1 PFC and Rail Control Loops (Positive Semicycle) . . . . . . . . . . . . . . . . . . . . . . . . . 2-3

2-2 Battery Charger Control Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-5

2-3 Inverter Control Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-7

2-4 Battery Booster Control Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-9

3-1 56F8346 Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-2

3-2 Reset Logic. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-3

3-3 Selection Mode and Reset Button. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-4

3-4 Program and Data Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-5

3-5 RS-232 Serial Communications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3-6 LCD Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-6

3-7 Wireless Board Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-7

3-8 PWM Ports Expansion Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3-9 A/D Ports Expansion Connectors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3-10 Timer A Expansion Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-8

3-11 GPIO Port C Expansion Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3-12 GPIO Port D Expansion Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-9

3-13 Daughter Card Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-10

3-14 CAN Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-11

3-15 JTAG Connector. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-12

3-16 Parallel JTAG Interface Connector . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-13

3-17 Passive Low-pass Filters of the A/D Ports . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-14

3-18 Power Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-15

3-19 External Power Input. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

3-20 Power Supply LEDs and Test Points . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-16

4-1 UPS Switches and Connectors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

4-2 The OUPS with a Control Board Installed. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-3

4-3 Functional Components and Location of Jumpers on the Power Board. . . . . . . . . 4-5

4-4 Jumpers on the Control Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-6

4-5 The Right Side of the UPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-9

5-1 Main Routine Flow Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-3

5-2 Flow Diagram for the Interrupt Service Routine AD1_OnEnd (1 of 5) . . . . . . . . . . 5-5

5-3 Flow Diagram for the Interrupt Service Routine AD1_OnEnd (2 of 5) . . . . . . . . . . 5-6

Online UPS Designer Reference Manual, Rev. 0

vi Freescale Semiconducto r

Preliminary

Page 9

5-4 Flow Diagram for the Interrupt Service Routing AD1_OnEnd (3 of 5) . . . . . . . . . . 5-7

5-5 Flow Diagram for the Interrupt Service Routine AD1_OnEnd (4 of 5) . . . . . . . . . . 5-8

5-6 Flow Diagram for the Interrupt Service Routine AD1_OnEnd (5 of 5) . . . . . . . . . . 5-9

5-7 Overcurrent Management. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-10

5-8 Battery Temperature Reading. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-12

5-9 Program Loop Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-13

5-10 Inverter Control Loop Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-14

5-11 PFC Control Loop Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-15

5-12 Battery Booster Control Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

5-13 Battery Charger Control Loop. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-16

5-14 Synchronous Phase Discriminator State Machine . . . . . . . . . . . . . . . . . . . . . . . . 5-17

5-15 PLL Control Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-19

5-16 Frequency Measurement Routine. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-21

5-17 SCR Control Signal Generation at the Beginning and End of the Rectifier

Soft Start . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

5-18 RMS Sensing System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-22

5-19 Power Sensing System. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-23

5-20 Implementation of Low-Pass Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-25

5-21 Implementation of the High Frequency Reject Filter. . . . . . . . . . . . . . . . . . . . . . . 5-26

6-1 Implementation of OpenTCP for OUPS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-2

6-2 Connectivity Initialization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6-3 Main Application Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-6

6-4 Main Loop Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-7

7-1 Inverter Waverforms—No Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

7-2 Inverter Voltage Harmonics—No Load. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7-3 Inverter Waveforms—Linear Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-2

7-4 Inverter Voltage Harmonics Under Linear Load Conditions . . . . . . . . . . . . . . . . . . 7-3

7-5 Inverter Waveforms Under Full Load Conditions—Battery Operated. . . . . . . . . . . 7-3

7-6 Inverter Voltage Harmonics—Full Load, Battery Operated. . . . . . . . . . . . . . . . . . . 7-4

7-7 Inverter Transient Response—60W Bulb . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-4

7-8 Inverter Transient Response—Resistive Load (200W). . . . . . . . . . . . . . . . . . . . . . 7-5

7-9 PFC Waveforms—Full Load Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7-10 PFC Waveforms—Linear Load Conditions (298W) . . . . . . . . . . . . . . . . . . . . . . . . 7-6

7-11 PFC Waveforms—Linear Load Conditions (59W) . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7-12 PFC Performance—Transient. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-7

7-13 Freerun Frequency Measurement. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-8

List of Figures, Rev. 0

Freescale Semiconduc tor vii

Preliminary

Page 10

7-14 Battery Charger Performanc—Charging. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7-15 Battery Charger—Floating . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-9

7-16 Bypass Switching Time. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-10

Online UPS Designer Reference Manual, Rev. 0

viii Freescale Semiconductor

Preliminary

Page 11

LIST OF TABLES

4-1 Jumper Position for Configuration of the Power Board. . . . . . . . . . . . . . . . . . . . . . 4-4

4-2 Jumper Position for Configuration of the Control Board . . . . . . . . . . . . . . . . . . . . . 4-6

5-1 Assignment of the Analog-to-Digital Converters. . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5-2 Digital Outputs and Inputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

5-3 Transitions of the Synchronous Phase Discriminator . . . . . . . . . . . . . . . . . . . . . . 5-18

6-1 Digital Outputs and Inputs Used for Connectivity . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

6-2 System Services Initialization Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-4

6-3 Physical Layer Initialization Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6-4 Network Layers Initialization Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6-5 Application Layer Initialization Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-5

6-6 Defines Used by Main Connectivity Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6-7 Functions Used by Main Connectivity Loop . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-8

6-8 Interrupts Used by Connectivity Software. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-9

List of Tables, Rev. 0

Freescale Semiconduc tor ix

Preliminary

Page 12

Online UPS Designer Reference Manual, Rev. 0

x Freescale Semiconductor

Preliminary

Page 13

About This Document

This manual describes the Online Uninterruptible Power Supply (OUPS) application.

Audience

This manual targets design engineers interested in developing a UPS using a 56F83xx device.

Organization

This User’s Manual consists of the following sections:

• Chapter 1, Online UPS Theory and Description -- provides an introduction to the concepts of UPS and

describes the theory of operation.

• Chapter 2, Control Loops In The Online UPS-- describes methods and algorithms for control of the

OUPS.

• Chapter 3, Control Board Design Considerations -- describes the Control Board and its features.

• Chapter 4, Operational Description -- explains how the OUPS connects to and operates with an EVM.

• Chapter 5, Control Software Design Considerations -- describes routines and interrupt handlers for a

variety of control functions.

• Chapter 6, Connectivity Software Design Considerations -- explains how to communicate with the

OUPS using TCP/IP protocol.

• Chapter 7, Results -- discusses and illustrates OUPS performance in a variety of conditions.

• Appendix A, Schematics -- contains schematics for both Control Board and Power Board.

• Appendix B, Bill of Materials -- includes a detailed listing of parts used in the OUPS.

Preface, Rev. 0

Freescale Semiconduc tor xi

Preliminary

Page 14

Conventions

This document uses the following notational conventions:

Typeface, Symbol

or Term

Courier

Monospaced Type

Italic Directory names,

Code examples //Process command for line flash

project names,

calls,

functions,

statements,

procedures,

routines,

arguments,

file names,

applications,

variables,

directives,

code snippets

in text

Meaning Examples

Bold Reference sources,

paths,

emphasis

...and contains these core directories:

applications contains applications software...

...CodeWarrior project, 3des.mcp is...

...the pConfig argument....

...defined in the C header file, aec.h....

...refer to the Targeting DSP56F83xx Platfo r m

manual....

...see: C:\Program Files\Frees cal e\h elp\t uto -

rials

Blue Text Linkable on-line ...refer to Chapter 7, License....

Number Any number is considered a

positive value, unless preceded by a minus symbol to

3V

-10

DES

-1

signify a negative value

ALL CAPITAL

LETTERS

# defines/

defined constants

# define INCLUDE_STACK_CHECK

Brackets [...] Function keys ...by pressing function key [F7]

Quotation

Returned messages ...the message, “Test Passed” is displayed....

marks, “...”

...if unsuccessful for any reason, it will return

“NULL”...

Online UPS Design Reference Manual, Rev. 0

xii Freescale Semiconductor

Preliminary

Page 15

Definitions, Acronyms, and Abbreviations

The following list defines the acronyms and abbreviations used in this document. As this

template develops, this list will be generated from the document. As we develop more group

resources, these acronyms will be easily defined from a common acronym dictionary. Please note

that while the acronyms are in solid caps, terms in the definition should be initial capped ONLY

IF they are trademarked names or proper nouns.

AC Alternating Current

ARP Address Resolution Protocol

DC Direct Current

DCO Digitally Controlled Oscillator

IIR Infinite Impulse Response

OUPS Online Uninterruptible Power Supply

PFC Power Factor Correction

PI Proportional-Integral

PID Proportional-Integral-Derivative

PLL Phase Locked Loop

PWM Pulse Width Modulation

RMS Root Mean Square

SCR Silicon Controlled Rectifier

TCB Transmission Control Block

UDP User Datagram Protocol

UPS Uninterruptible Power Supply

References

The following sources were used to produce this book; we recommend that you have a copy of

these references:

1. DSP56800E Reference Manual, Freescale, DSP56800ERM

2. 56F8300 Peripheral User Manual, Freescale, MC56F8300UM

Preface, Rev. 0

Freescale Semiconduc tor xiii

Preliminary

Page 16

Online UPS Design Reference Manual, Rev. 0

xiv Freescale Semiconductor

Preliminary

Page 17

Introduction

Chapter 1 Online UPS Theory and

Description

1.1 Introduction

Uninterruptible Power Supplies (UPS) are electronic devices designed to provide power to

critical mission systems. An Online UPS (OUPS) provides continuous power to the load during

power outage or glitches caused by power source switching.

1.1.1 The Concept of an Online UPS

The minimum components needed to design an Online UPS are the rectifier, the battery bank and

the inverter. The rectifier converts the distribution line’s AC (Alternating Current) power to DC

(Direct Current), the form of current suitable to store energy in a battery bank. At all times, this

DC is also fed to an inverter, which reconverts the DC power to an AC waveform connected to

any equipment utilizing AC that a user considers as mission critical. If the AC supply fails for

any reason, the inverter will continue to draw power from the batteries.

Figure 1-1. A Basic Online UPS

1.1.2 Input Power Factor Control (PFC)

When a sinusoidal input signal is connected to a full wave rectifier, conduction will occur only

during the peaks of the signal. This causes a two-fold inconvenience to the electricity distribution

line:

• Insertion of harmonics to the lines

• High current peaks, which imply greater losses on the distribution

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-1

Preliminary

Page 18

These effects are aggravated by the long distances the electric distribution networks usually span.

From the electrical utility’s point of view, the best possible load is the pure resistive: The current

waveform should be a pure sinusoidal waveform identical to the voltage waveform and of the

same frequency and phase.

In order to show a resistive load to the utility lines, the input current to the UPS is controlled (i.e.,

modulated), to make it match a set point. This set point depends on the input voltage waveform,

and its amplitude is dependent on the equipment’s power consumption.

1.1.3 DC-to-DC Converters

If a rectifier is connected to the AC line supply, then the DC voltage will be equal to the peak

voltage of the line. (i.e., in a 120 V

configured for 12 or 24 V

, the UPS works by using DC-to-DC converters.

DC

line, the peak will be 120√2, 170V). If the battery bank is

RMS

For an online UPS, two power DC-to-DC converters are required. One converter operates as the

battery charger, and the other boosts the battery voltage in the absence of line input and generates

the appropriate DC required by the inverter.

1.1.4 Phase Locked Loop (PLL)

This UPS can operate in the Free Running mode or in the Locked-to-Line mode. If the AC main

line frequency is at the nominal value of 50Hz or 60Hz ± 5%, then the PLL locks the inverter

output to the line. If the AC main line frequency runs out of limits for any reason, the UPS will

automatically switch to run locked to the internal frequency reference.

The UPS will also work in the Free Running mode if commanded to operate as a frequency

converter. For example, it can connect to a 60Hz AC main line frequency and output a signal of

50Hz frequency, and vice versa.

The purpose of Phase-Locking the inverter to the line input is to enable the automatic bypass

feature, and to avoid signal “mixing” at the rails. These two features are detailed in the following

sections.

1.1.5 Bypass Operation

In order to allow a UPS bypass without loss of power at the load, two conditions must be met:

• The inverter output must be locked to the frequency and phase of the AC main line

• The inverter output and the AC main line’s RMS voltages must be within 10% of one

another

Online UPS Designer Reference Manual, Rev. 0

1-2 Freescale Semicond uctor

Preliminary

Page 19

Introduction

When the bypass conditions are met, the bypass switch can transfer the load to the AC main line

in the event of a UPS failure or when commanded by the operator during routine maintenance. It

can also switch the load back to the inverter after any maintenance.

1.1.6 Rail Ripple

The energy to support the load is stored in the rail capacitors. These capacitors are current-fed by

the PFC circuitry in the Online mode or by the battery booster in the Battery Back-up mode.

In the Online mode, a ripple with the phase and twice the frequency of the AC main line will be

present at the rails, superimposed with a ripple with the phase and twice the frequency of the

inverter current. In this situation, if a frequency offset ∆f is present, lower-order components can

appear. Locked operation is preferred to minimize the effects of frequency mixing.

1.1.7 Pulse Width Modula tion (PWM)

High-power control requires switchable electronic devices, precluding their use in the active

region, where power dissipation in the device is very high. For this reason, control is made by

pulse width modulation, where the duty cycle of a signal is modified, then a linear filtering

device passes the desired signal value to the analog components.

PWM is then used to implement inverters, PFCs, and DC-to-DC converters.

1.1.8 A Controller Solution to Control a UPS

The control system for a UPS must accomplish the following functions:

• Control strategies for inverter, PFC, PLL, and DC-to-DC converters. Every control loop

starts at an Analog-to-Digital Converter (ADC) in order to sense the signals, and ends at a

Pulse Width Modulator as an actuator.

• Deciding when to activate or deactivate a component

• Detecting failure conditions and implementing any required action

• Enabling Monitor and Control (M & C) communications

Compared to traditional analog controls, today’s low-cost and high-performance controllers

provide a better solution in performance and cost. A single MCU includes a powerful processor

core and such peripherals as PWMs, Timers, and Analog-to-Digital Converters. A single 56800E

device is able to assume the monitoring and real-time control required by an Online UPS.

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-3

Preliminary

Page 20

1.2 System Overview

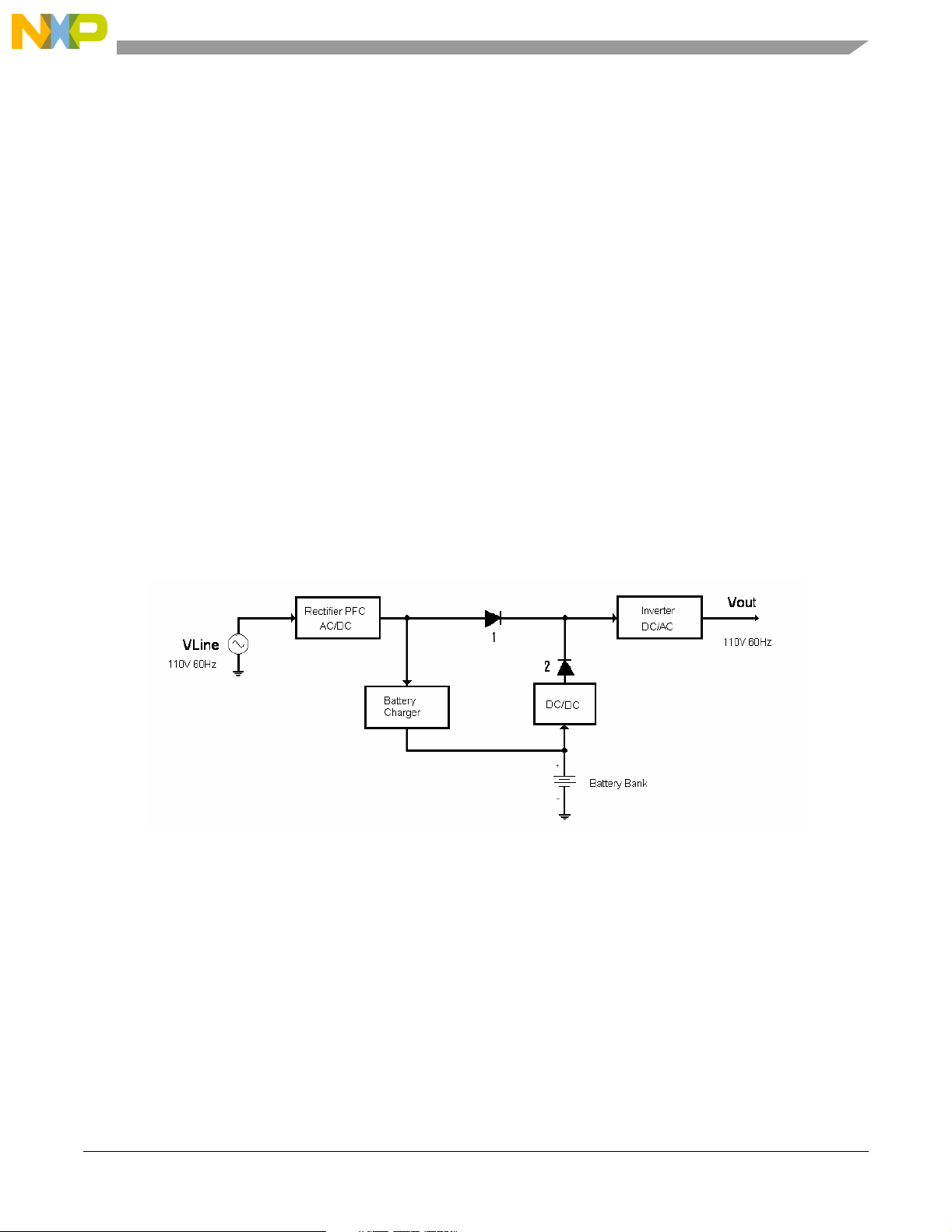

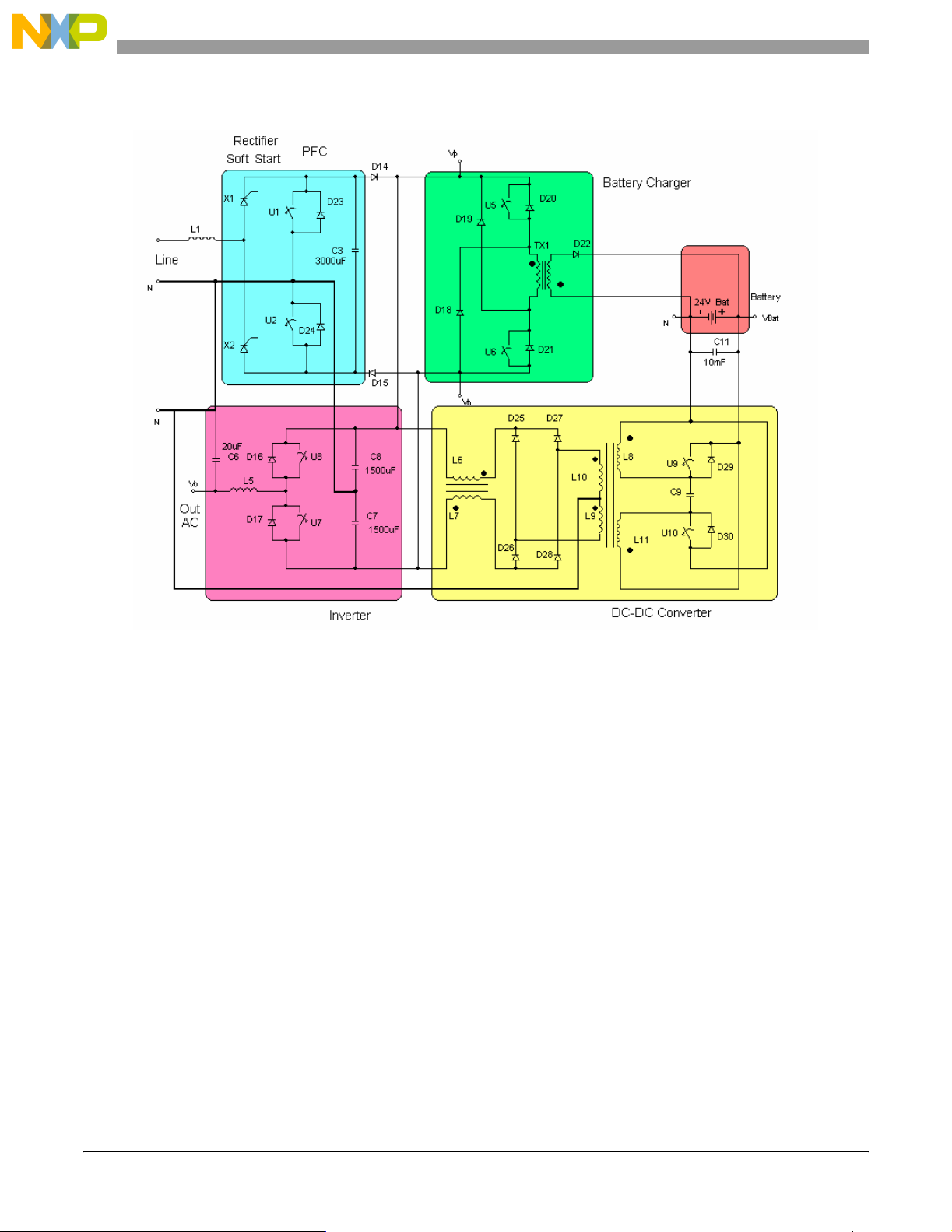

Figure 1-2 depicts a simplified UPS system.

Figure 1-2. UPS Simplified Schematic

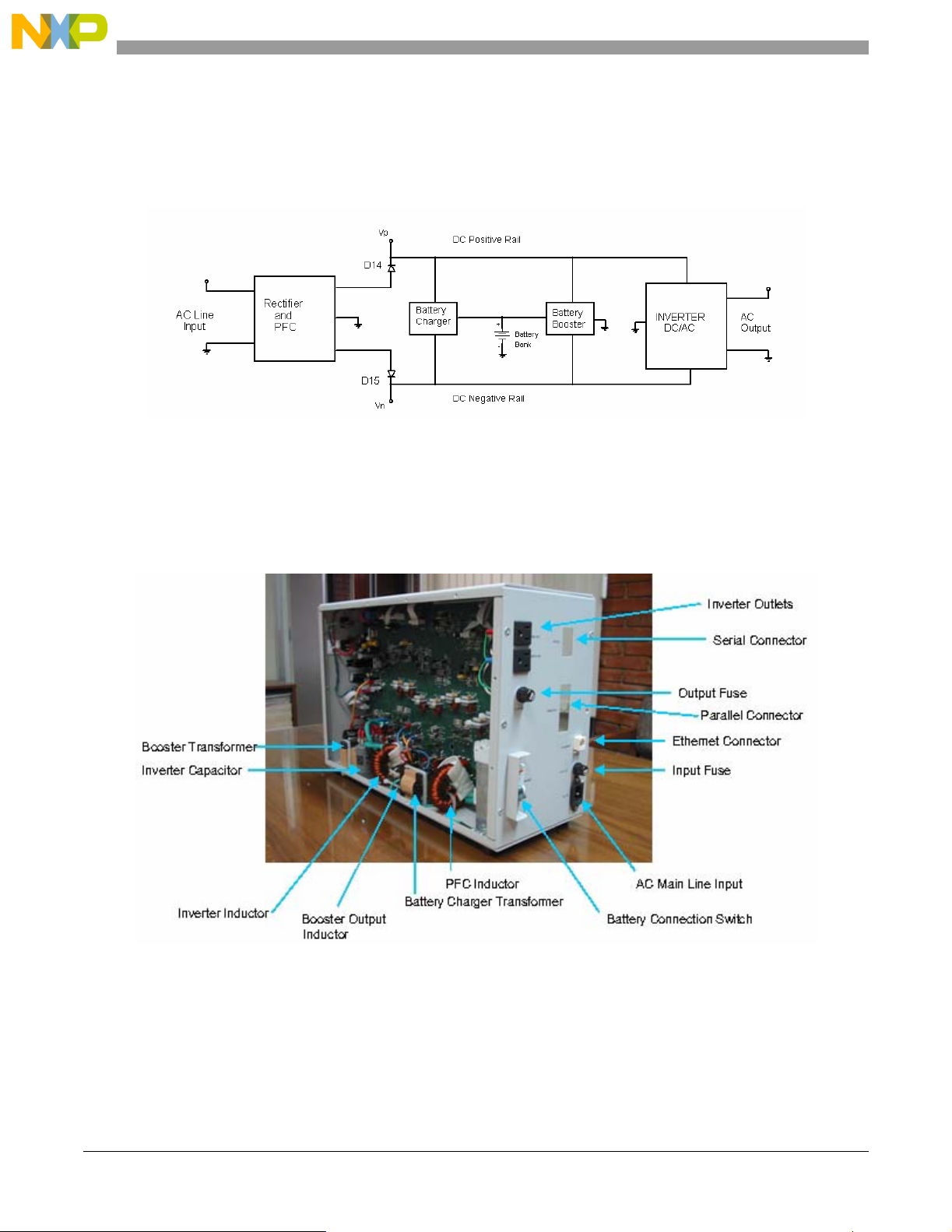

Figure 1-3 shows a photo of a completed UPS prototype. The system’s power electronics and

ferromagnetic components are detailed on the left side of the the figure.

Figure 1-3. Prototype UPS

Online UPS Designer Reference Manual, Rev. 0

1-4 Freescale Semicond uctor

Preliminary

Page 21

System Actuators

1.3 System Actuators

A simplified schematic of the controller’s relationship with actuators is shown in Figure 1-4,

where all switches represent MOSFETs or IGBTs.

56800E Controller

Figure 1-4. Relationship between a 56800E and Power Actuators

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-5

Preliminary

Page 22

Figure 1-5. Simplified Schematic Diagram of the UPS

1.4 Input Rectifier Theory of Operation

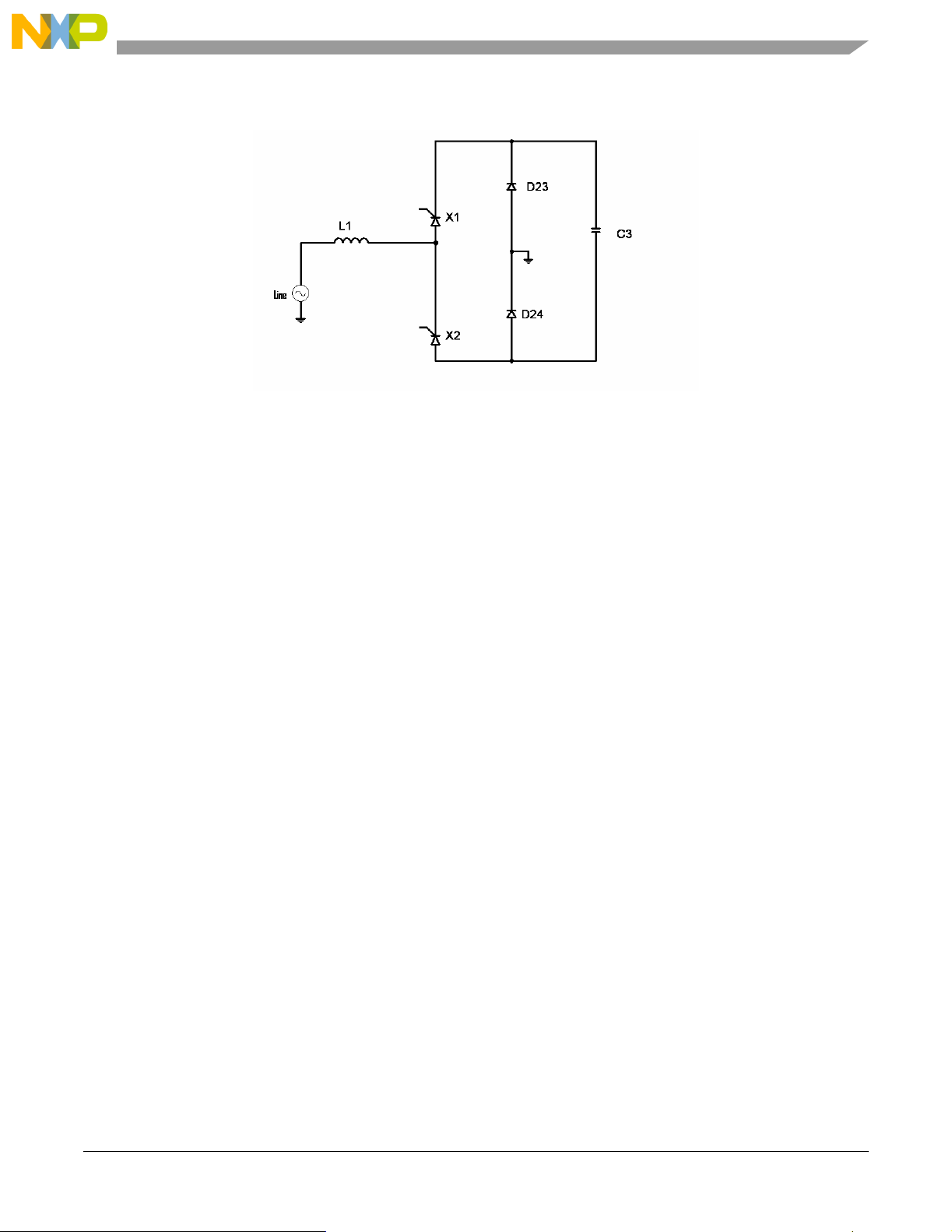

The input rectifier is implemented as a four-diode bridge (X1, X2, D24, and D23). A soft start

system implemented with SCRs can prevent a huge in-rush current when the system starts, while

the system’s internal capacitors get charged to the line’s peak voltage.

Online UPS Designer Reference Manual, Rev. 0

1-6 Freescale Semicond uctor

Preliminary

Page 23

Input Rectifier Theory of Operation

Figure 1-6. Input Rectifier

1.4.1 Rectifier Soft Start

If a high voltage is applied to a discharged capacitor, its low impedance will result in a very high

inrush current across the circuit, reducing the components’ longevity.

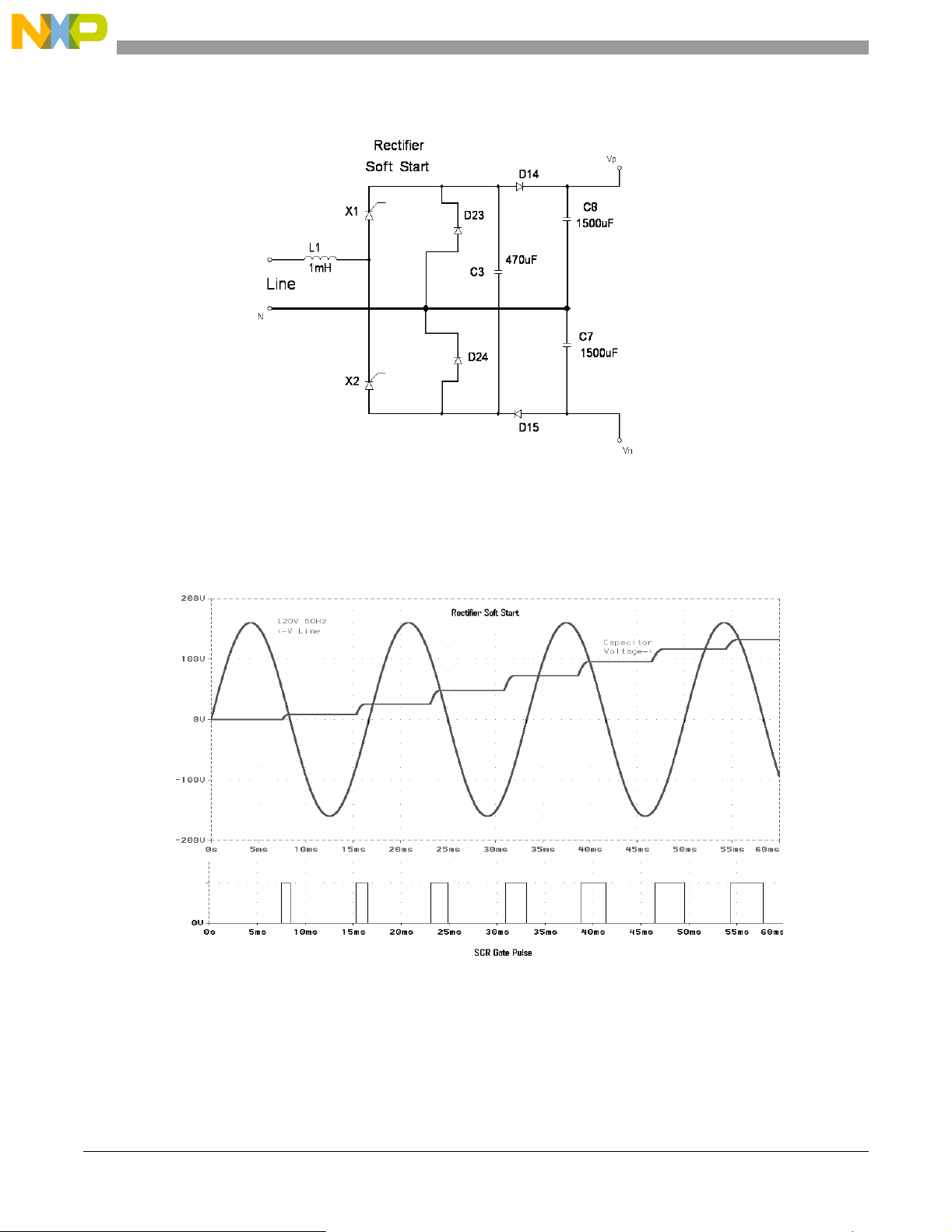

A soft start circuit is designed to avoid that circumstance. Figure 1-7 shows a full

wave-controlled rectifier bridge. If the trigger angle of X1 and X2 is gradually decreased from

the zero crossing towards the peak voltage, as demonstrated in Figure 1-8, the capacitor voltage

will then increase slowly. As the current on a capacitor equals the capacitance value times the

voltage derivative with respect to time, the input current will be proportional to the slope of the

voltage applied to the capacitor.

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-7

Preliminary

Page 24

Figure 1-7. Full Wave-Controlled Rectifier Bridge

Figure 1-8. Relationship between Rectifier Soft Start Operation / Actuator Signals

and the AC Main Line Voltage

Online UPS Designer Reference Manual, Rev. 0

1-8 Freescale Semicond uctor

Preliminary

Page 25

Power Factor Corrector (PFC) Theory of Operation

1.5 Power Factor Corrector (PFC) Theory of Operation

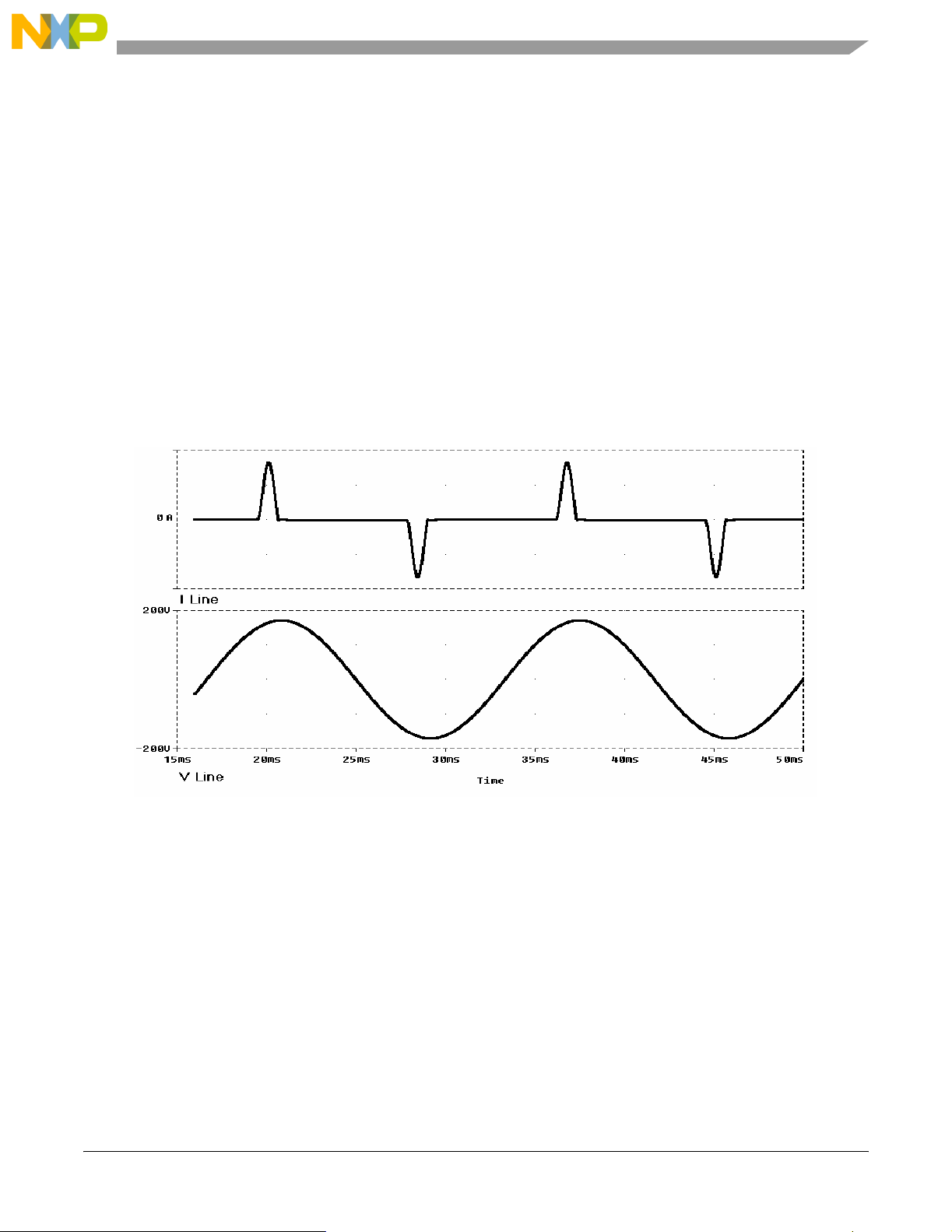

After the rectifier soft start finishes, X1 and X2 must act as diodes with continuous trigger. When

no PFC is implemented, the line current will be similar to that shown in Figure 1-9, due to the

diode–capacitor nature of a rectifier.

The objective of the PFC circuit is to simulate a resistive load to the power line; in other words, to

obtain a unity power factor and low harmonic content in the current waveform. A fast control

must be implemented in order to make the current waveform follow the AC voltage, while

elevating and controlling the rail voltage and supplying the average power required to the load.

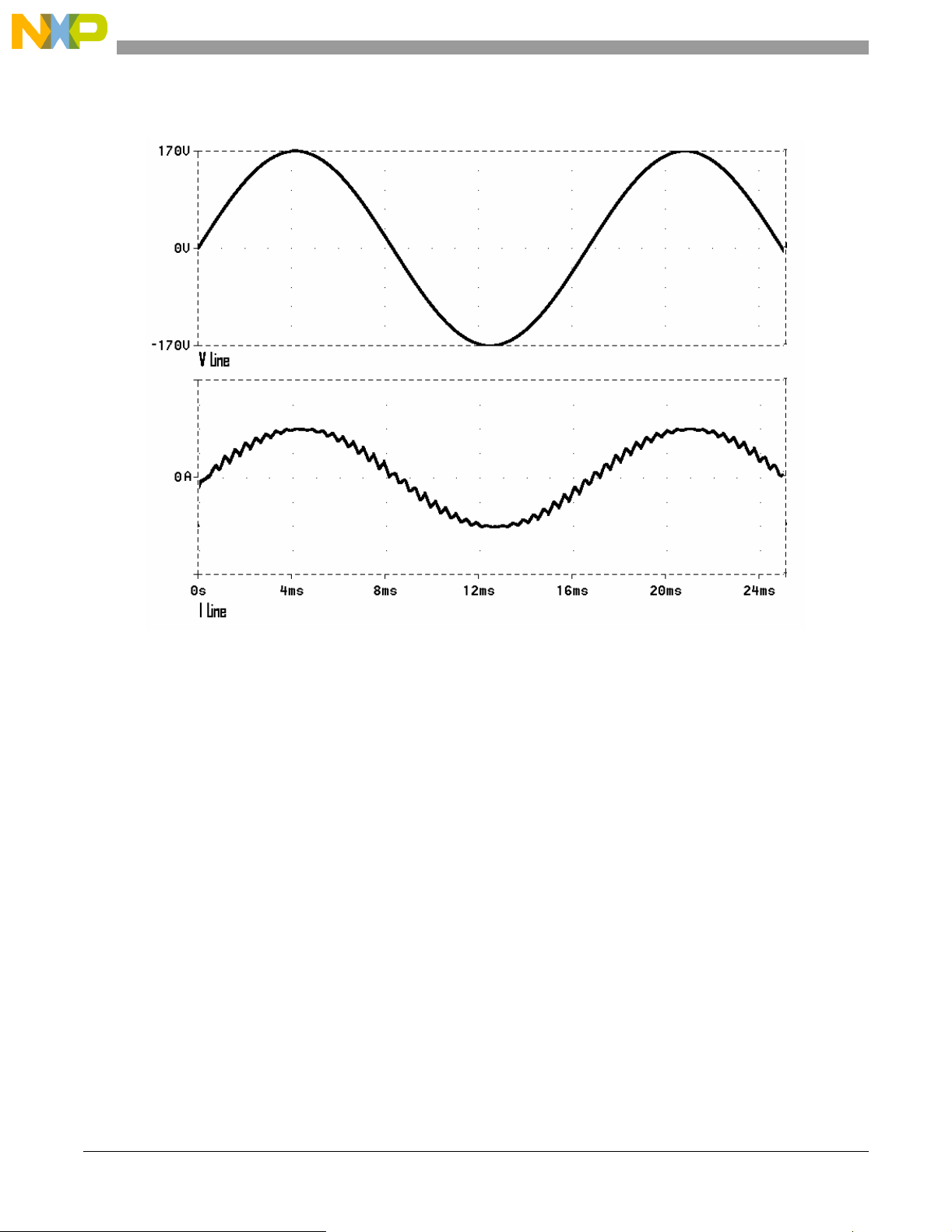

Figure 1-10 shows how the PFC works, illustrating a current signal waveform similar in form to

the voltage waveform. The ripple in the figure is a consequence of the IGBT high frequency

switching.

Figure 1-9. Typical Rectifier Current vs. AC Line Voltage

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-9

Preliminary

Page 26

Figure 1-10. PFC Current and Voltage Waveforms

Once the voltage on capacitors C3, C7 and C

shown in Figure 1-11 reach the AC main supply

8

peak after the rectifier soft start, the PFC is turned on, correcting the power factor presented to

the line and generating the rail DC voltages V

Online UPS Designer Reference Manual, Rev. 0

and VN at a value higher than the line peak.

P

1-10 Freescale Semicond uctor

Preliminary

Page 27

Power Factor Corrector (PFC) Theory of Operation

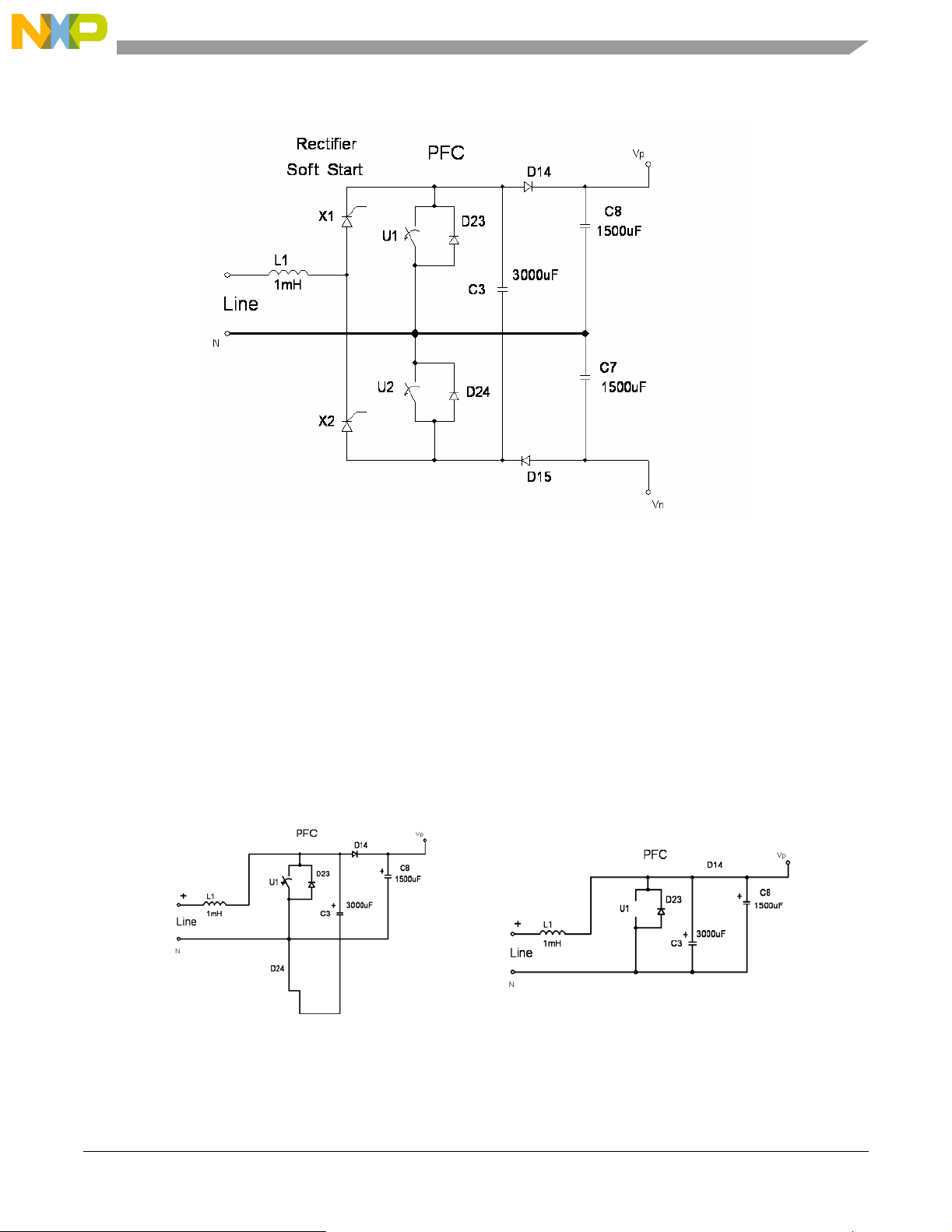

Figure 1-11. PFC Schematic

In order to work as a PFC, U1 and U

When U

is on, U2 is off, and vice versa.

1

in Figure 1-11 turn on and off in complementary mode.

2

The switching frequency of operation is 20kHz . The line nominal frequencies are 50Hz or 60Hz,

so it is a valid approximation to consider the line voltage as a constant during a switching period.

For positive values of the line, when U

that shown in Figure 1-12, where C

capacitors to be the same, thus reducing the ripple voltage on C

is on (closed) and U1 is off (open), the circuit reduces to

2

is connected in parallel to C8, causing the voltages on these

3

.

8

Figure 1-12. Partial PFC Schematic when U1 Is Open and U2 Is Closed

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-11

Preliminary

Page 28

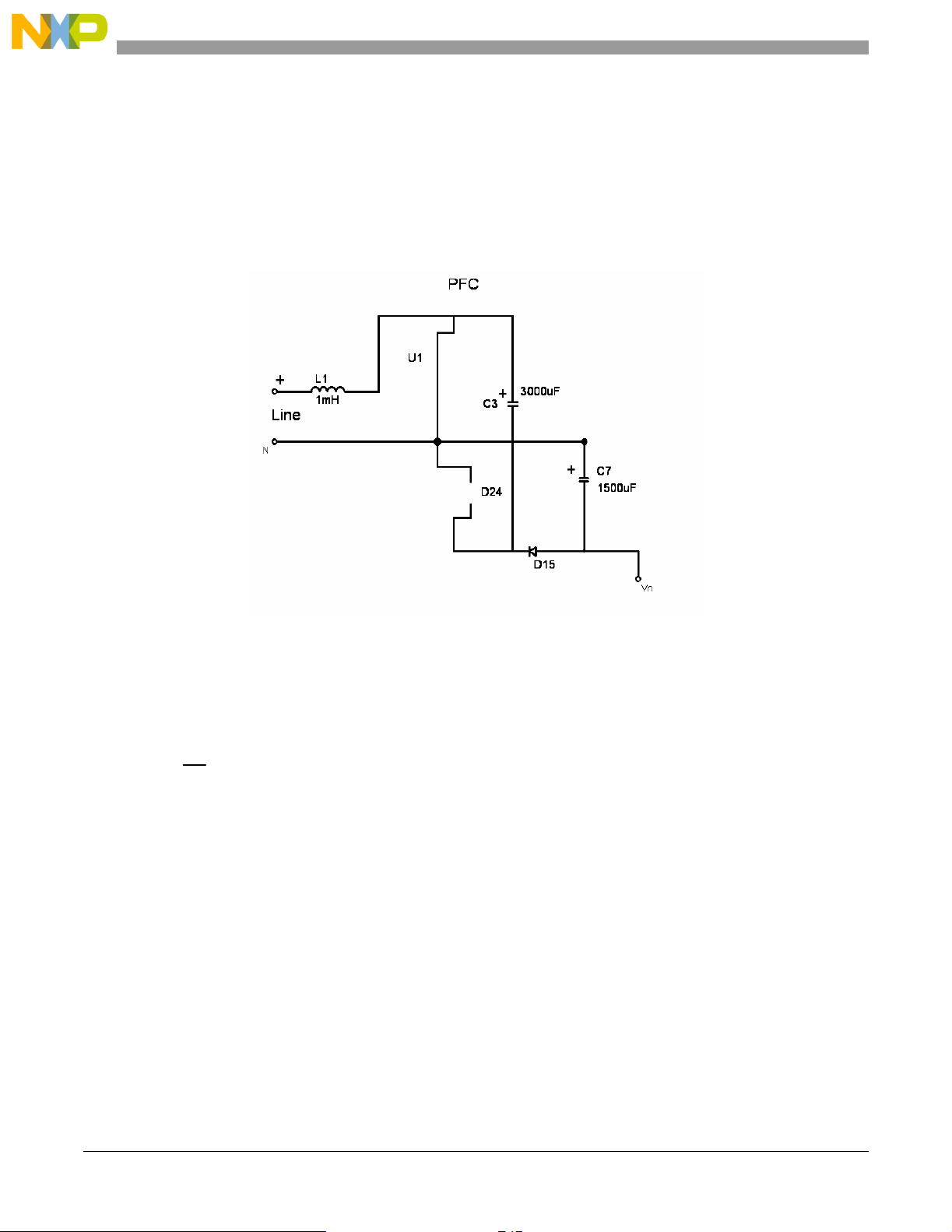

For positive values of the line, when U1 is closed, and U2 is open, the circuit reduces as shown in

Figure 1-13, where C

line is applied directly to L

voltage could be considered constant, and the inductor current, which corresponds to the current

in the line (I

), depends on the voltage across its terminals.

LINE

is now connected in parallel to C7, thus reducing its ripple voltage. The

3

, increasing the current across it with a constant slope, because line

1

Figure 1-13. Partial PFC Schematic when U1 Is Closed and U2 Is Open

Inductor current is calculated by the equation:

t

1

I

=∆

L

Where:

V

is the voltage across the inductor terminals

L1

The peak current across the inductor at time t2 depends, among other factors, on the instant value

of the line voltage and the time difference t

2

∫

t

1

dtV

Lline

1

, which is the time that U1 remains closed.

2 – t1

Online UPS Designer Reference Manual, Rev. 0

1-12 Freescale Semicond uctor

Preliminary

Page 29

Power Factor Corrector (PFC) Theory of Operation

Figure 1-14. Resulting Parallel Connection between C3 and C7

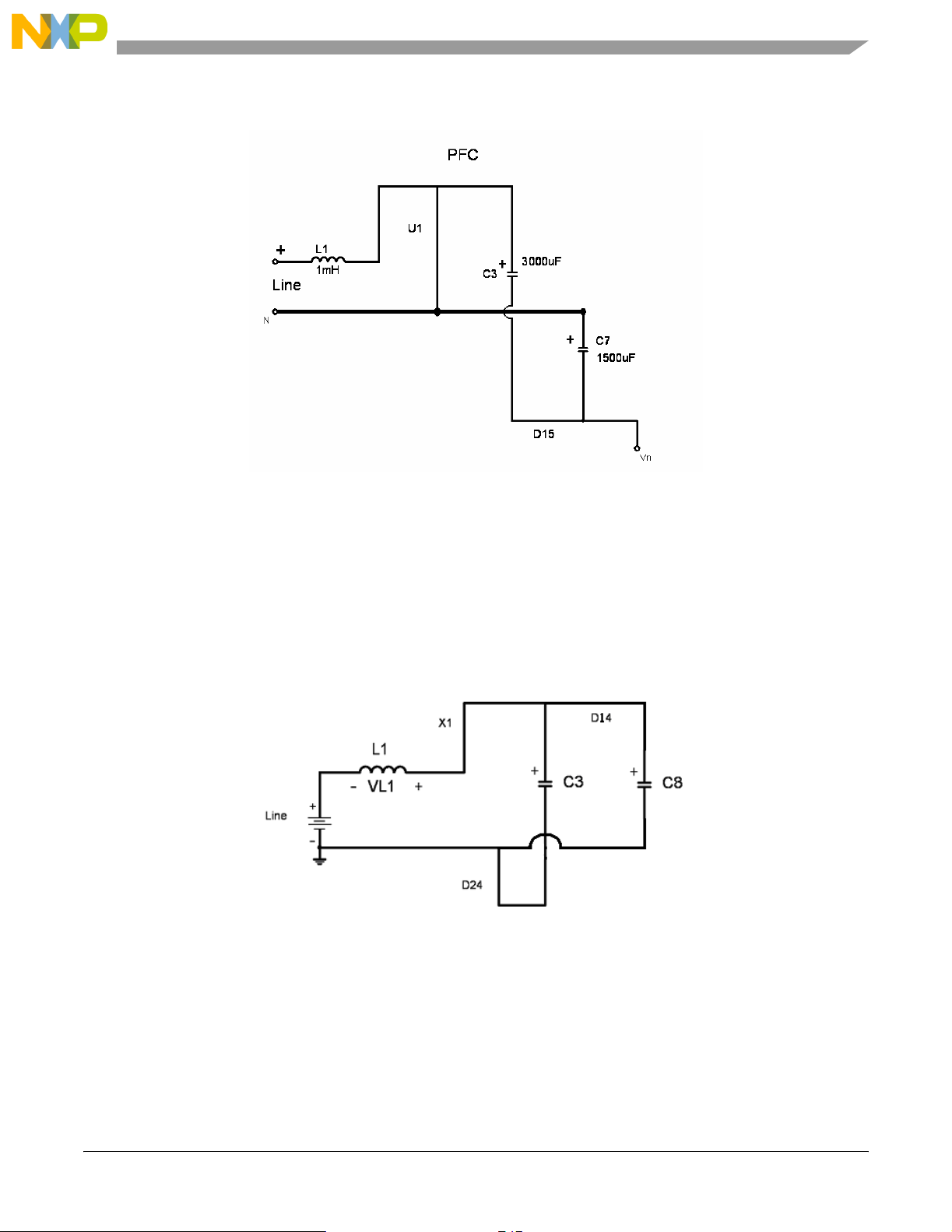

The voltage-boosting characteristic of the PFC is accomplished by increasing the voltage across

(and consequently, across C7 and C8). Given that a current is circulating in the inductor L1,

C

3

when U

forces D

opens, the voltage across L

1

into a conduction state and C3 and C8 to charge to the addition of the line and the

24

inductor terminal voltage, V

Figure 1-15. Voltage Boost across Capacitors C3 and C

. This is a typical boost configuration.

L1

adds to the line voltage as shown in Figure 1-15. This

1

8

Due to symmetry, this circuit works in the same way for negative values in line voltage.

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-13

Preliminary

Page 30

1.6 Battery Charger Theory of Operation

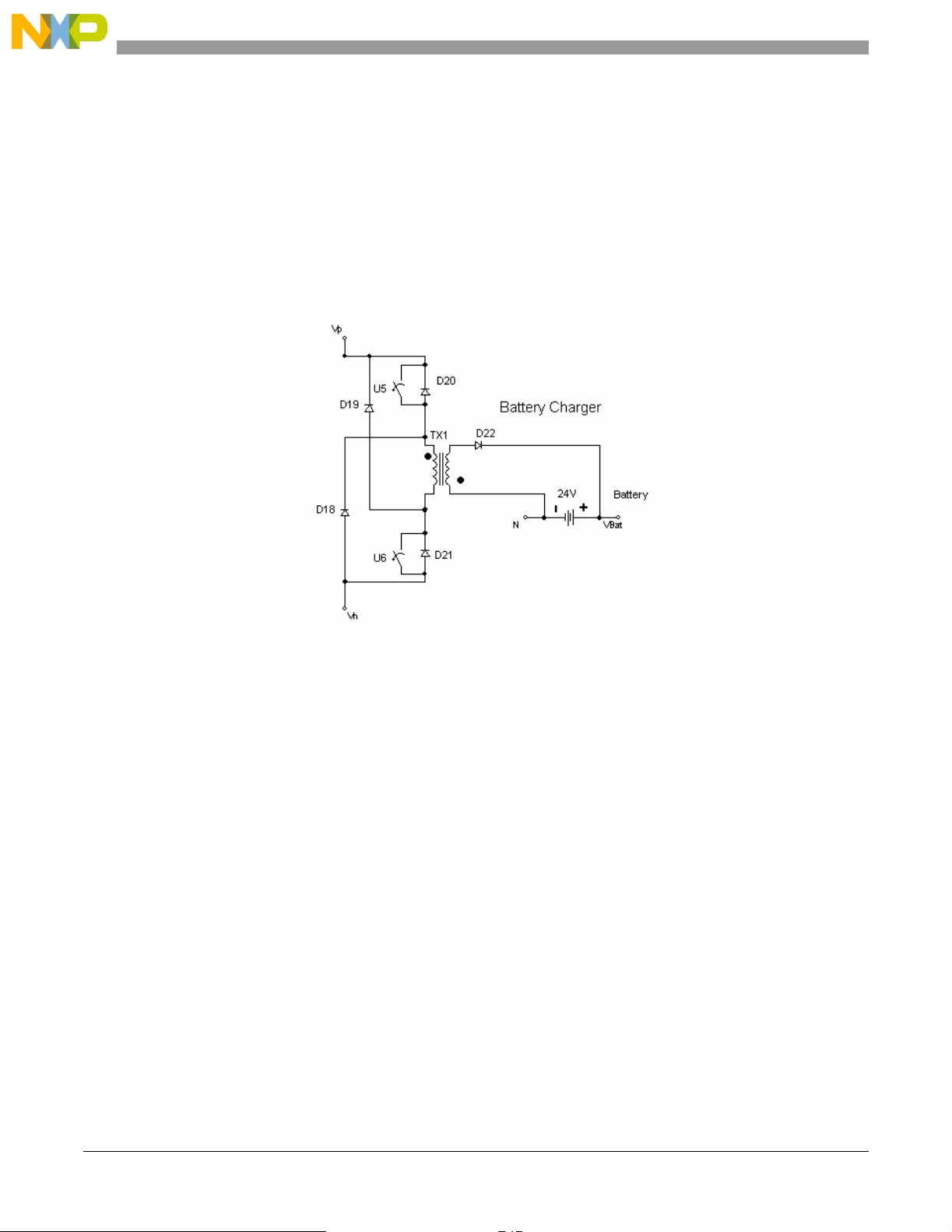

Figure 1-16 has been extracted from the UPS schematic shown in Figure 1-5. Using the high DC

voltages V

charge conditions for a battery bank formed by two 12V batteries connected in series, which must

be charged with constant current. When the float condition is reached, the charger must preserve

a constant voltage while providing the battery bank’s self-discharge current.

rail positive and VN rail negative as its power sources, this circuit provides the

P

Figure 1-16. Battery Charger Schematic

The battery charger is an application of a two-transistor flyback configuration using a coupling

inductor rather than a transformer. Because this operating mode implies no flow of current in the

secondary when the primary has a non-zero current, and vice versa, it means that no current flows

simultaneously in both windings.

Figure 1-16 shows a two-transistor version of a flyback converter, where U

and U6 are turned

5

on and off simultaneously. The advantage of such a topology over a single-transistor flyback

converter is that the switches’ voltage rating is V

through the diodes D

and D19, which are connected to the primary winding, a dissipative

18

- VN. Moreover, since a current path exists

P

snubber across the primary winding is not needed to dissipate the energy associated with the

transformer primary-winding leakage inductance.

The design, calculations and construction of TX

voltage from secondary to primary rising higher than V

are critical in order to prevent the reflected

1

- VN when D22 is on.

P

Online UPS Designer Reference Manual, Rev. 0

1-14 Freescale Semicond uctor

Preliminary

Page 31

Battery Booster Theory of Operation

1.7 Battery Booster Theory of Operation

The battery booster is a DC-to-DC converter and transforms the battery voltage of 24VDC to the

required differential 440V

the positive rail, and V

N

Although the topology of Figure 1-17 is usually called “booster” because its output voltage is

higher than input voltage, it is actually a push-pull converter with an arrangement of two forward

converters working alternatively and a transformer to increase the output voltage.

between rails. The rails are symmetric, implying VP = 220VDC at

DC

= -220V

at the negative rail, as shown in Figure 1-17.

DC

Figure 1-17. Battery Booster Schematic

The switches U9 and U10 cannot be closed at the same time. Typical drive signals are illustrated

in Figure 1-18.

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-15

Preliminary

Page 32

Figure 1-18. Drive Signals for Battery Booster Switches

Using a control signal like the one shown in Figure 1-18, the waveforms at the transformer

secondary over L

and L9 are illustrated with positive and negative values of voltage in

10

Figure 1-19.

Figure 1-19. Signals at Transformer Secondary Windings L10 and L

C9 remains charged to V

and is added because the coupling factor is not equal to one,

BAT

implying that a leakage inductor must be considered. C

acts as a snubber, creating a current path

9

9

to avoid an uncontrolled voltage peak at the primary windings of the transformer.

Online UPS Designer Reference Manual, Rev. 0

1-16 Freescale Semicond uctor

Preliminary

Page 33

Battery Booster Theory of Operation

The four diodes D25, D26, D27 and D28 form a conventional full-wave rectifier bridge and

generate only positive values in the cathodes of D25 and D27 and negative values at the anodes

of D26 and D28, as shown in Figure 1-20.

Figure 1-20. Signals at the Cathode of D25 and Anode of D

26

The objective of DC/DC converters is to generate a DC voltage. In order to filter any undesirable

AC components, two LC filters are added:

•L

•L

for the negative rail

7-C7

for the positive rail

6-C8

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-17

Preliminary

Page 34

1.8 Inverter Theory of Operation

⎞

⎛

Figure 1-21. Inverter Schematic Diagram

The chosen inverter configuration is a half-bridge monophasic circuit. It must generate a

low-distortion sinusoidal waveform in the output terminals from the V

To produce such a signal, V

and VN must be higher than the AC positive and negative peak

P

voltages, respectively.

and VN DC rail voltages.

P

Consider a switching period of T seconds. Assume that U

is open. During the remaining T – T

of the low-pass filter composed by inductor L

seconds, U7 is closed and U8 open. If the cutoff frequency

P

and C6 is low enough to reject the 1/T Hz

5

switching frequency, then the output approximates to:

t

p

VV

Po

T

t

p

T

1

,1

=<

T

Where:

tp/T is the duty cycle of the control signal

t

p

⎜

N

⎜

⎝

⎟

1V

−+=

⎟

T

⎠

kHz20

is closed during TP seconds, while U7

8

Online UPS Designer Reference Manual, Rev. 0

1-18 Freescale Semicond uctor

Preliminary

Page 35

Auxiliary Circuits

The expression simplifies to :

t

()

p

VVV

NPo

V

+−=

T

N

As 1/T = 20kHz is much higher than 50Hz or 60Hz, then the output voltage will result

proportional to T

, and the sinusoidal signal can be considered constant during T seconds.

P

1.9 Pulse Width Modulation

If a sinusoidal reference signal is compared to a symmetric triangle wave, the resulting signal is

pulse width modulated, as shown in Figure 1-22. The triangle waveform frequency corresponds

to the PWM switching frequency.

Figure 1-22. Generation of a PWM Signal

1.10 Auxiliary Circuits

Additional circuits are required to make the complete system operational and include.

• Power supplies

• Signal sensing circuitry

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-19

Preliminary

Page 36

• Limiters

• Isolation circuits

• Driver circuits for SCRs, NMOSFETs and IGBTs

1.10.1 Power Supplies and Isolation Circuitry

This system requires multiple power supplies with floating references. The typical configuration

is shown in Figure 1-23, and consists of a flyback converter similar to the one used in the battery

charger. A 100kHz switching signal with a duty cycle of 35% is provided by the 56800E

controller and applied to an NMOS technology H bridge.

Figure 1-23. H Bridge Configuration used to Provide Multiple Floating Power Supplies

The output of the isolating transformer is half-wave rectified and applied to the load. Positive and

negative voltages are generated. The 39Ω resistor limits the current of the transformer’s

secondary when M

and M2 are on. Resistors RL1 and RL2 represent the load.

1

All isolated power supplies are connected in parallel to the rail voltage, depicted as nodes A and

B in Figure 1-23.

Online UPS Designer Reference Manual, Rev. 0

1-20 Freescale Semicond uctor

Preliminary

Page 37

Figure 1-24. Waveforms at A and B

Auxiliary Circuits

While M1 and M2 are on, VCC is connected directly to the primary, increasing the current

linearly, as shown in Figure 1-25. C

acts as a current limiter. M

, M2, Dp, Cp, and the transformer shape a traditional flyback power

1

is simultaneously charging across Dn. The 39Ω resistor

n

supply.

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-21

Preliminary

Page 38

Figure 1-25. Current Waveforms

When M1 and M2 are off, an inverted voltage is induced in the primary and D1, D2 which limit

that voltage to 15V plus 1.2 from two diode junctures, turning D

on and charging Cp.

p

There are several transformers connected to the rails A and B which generate isolated power

supplies to drive SCRs, IGBTs, and MOSFETs used in the rectifier, inverter, battery charger, and

battery booster.

Figure 1-26 shows the control power supply, which uses a LM2576 step-down voltage regulator,

to generate +V

additional power supply V

= 15V fed by the redundant DC voltage coming from 18VAC or +V

CC

coming from the battery charger. This circuit also generates the

DCR

Control Board Power Supply, which is isolated from +V

CC

.

BAT

or an

Online UPS Designer Reference Manual, Rev. 0

1-22 Freescale Semicond uctor

Preliminary

Page 39

Figure 1-26. Control Power Supply

1.10.2 Sensing Circuits and Reference Voltage Generator

Auxiliary Circuits

All signals that require sensing as voltages, currents, and temperature at the Analog-to-Digital

Converters are converted to the appropriate input levels and diode-limited to avoid damage to the

ADCs; this process uses differential amplifiers as seen in Figure 1-28, because of the different

ground references shown in Figure 1-27.

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-23

Preliminary

Page 40

Controller

Figure 1-27. Partial View of the Auxiliary Power Supply and Optoisolation Network

Figure 1-28. General Design of the Sensing Circuits

Online UPS Designer Reference Manual, Rev. 0

1-24 Freescale Semicond uctor

Preliminary

Page 41

Auxiliary Circuits

The value of the resistors required to sense every signal are calculated in order to guarantee full

swing, minimizing analog and quantization noise at the ADCs.

The reference level of the ADC is used to shift the AC input signal to swing from 0 to V

0 volts in the input signal are mapped to V

/2). If the output of the operational amplifier tends

RH

RH

to go out of limits for any reason, the diodes protect the ADC inputs.

1.10.3 Voltage Reference Supply

The voltage reference, V

a buffer to the reference voltage V

auxiliary voltage outputs:

•V

•V

equal to one diode voltage Vγ

A

with value VRH-Vγ

B

These voltages will be used to limit the values of voltage applied to A/D modules inside the

controller.

, is generated by the circuit shown in Figure 1-29. This circuit acts as

RH

from the controller. This circuit also generates two

REFH

(i.e.,

Figure 1-29. Voltage Reference Generator

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-25

Preliminary

Page 42

1.10.4 Silicon Controlled Rectifier (SCR) Gate Drivers

The circuit in Figure 1-30 shows the basic driver which handles the SCRs’ gates using an 4N35

optocoupler to generate an isolated current supply to trigger the rectifier’s SCRs.

Figure 1-30. SCR Gate Driver

1.10.5 IGBT and MOSFET Gate Drivers Circuit

Figure 1-31 illustrates the basic isolated circuit implemented to drive the IGBT’s and

MOSFET’s gates. It is based in a HCPL 3101 gate drive optocoupler.

Figure 1-31. IGBT and MOSFET Gate Driver

Online UPS Designer Reference Manual, Rev. 0

1-26 Freescale Semicond uctor

Preliminary

Page 43

Power Transfer Circuits (Bypass) Theory of Operation

1.11 Power Transfer Circuits (Bypass) Theory of Operation

Under normal conditions, the UPS inverter feeds all power to the load. However, in order to

ensure that the load is supported in the event of a failure, or during maintenance, the equipment

must also allow for direct connection to the AC main line. A switching relay is connected as

shown in Figure 1-32.

Figure 1-32. Bypass Relay Configuration

The relay’s transfer time must be shorter than a period of the AC line. A transfer time of less than

20ms is fast enough to comply with this constraint. The transfer is allowed if phase and voltage

conditions are satisfied, as explained in

Figure 1-33 shows the circuit implemented to turn the bypass relay on and off using the BP

Section 1.1.4.

1

signal. Please note the three different grounds used in the system.

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-27

Preliminary

Page 44

Figure 1-33. Relay Driver

1.12 Overcurrent Protection

Figure 1-34 shows the rectifier and inverter current sensing circuit. Figure 1-35 shows the

circuits implemented to sense the battery charger and battery booster currents. These circuits

generate overcurrent signals when the current value reaches a defined level. These two signals

are connected directly to the controller’s FAULT 0 and FAULT 1 pins.

Online UPS Designer Reference Manual, Rev. 0

1-28 Freescale Semicond uctor

Preliminary

Page 45

Overcurrent Protection

Figure 1-34. Overcurrent Protection for Rectifier and Inverter

Figure 1-35. Overcurrent Protection for Charger and Push-Pull

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-29

Preliminary

Page 46

The battery charger overcurrent protection generates a fault signal, named “SIC”, which turns off

the charger PWM signal. Likewise, the battery booster’s overcurrent protection circuit generates

the FPP signal, which turns off the drive signal for the MOSFETS.

1.13 Battery Temperature Sensing

The battery temperature sensing circuit is shown in Figure 1-36; it uses an LM-35-CZ, which is a

precision centigrade temperature sensor. The output of this circuit is a voltage that is proportional

to the temperature. This sensor must be located near the battery.

Figure 1-36. Battery Temperature Sensing Circuitry

Online UPS Designer Reference Manual, Rev. 0

1-30 Freescale Semicond uctor

Preliminary

Page 47

Battery Temperature Sensing

Figure 1-37. Battery Temperature Sensor

Online UPS Theory and Description, Rev. 0

Freescale Semiconduc tor 1-31

Preliminary

Page 48

Online UPS Designer Reference Manual, Rev. 0

1-32 Freescale Semicond uctor

Preliminary

Page 49

Control Algorithms Discrete Equivalents

⎞

⎛

Chapter 2 Control Loops In The Online

UPS

The UPS’s control algorithms are digitally implemented. The topology chosen for the

compensators is the PID (Proportional – Integral – Derivative) and the PI (Proportional –

Integral), with a 3- bit resolution. All gain constants are 16-bit implemented. The accumulators

are all 32-bit, unless otherwise specified.

2.1 Control Algorithms Discrete Equivalents

An ideal PID analog controller is expressed as follows:

1

⎜

KsGc

1)(

+=

p

⎜

⎝

s

τ

⋅

i

⎟

s

⋅+

τ

d

⎟

⎠

An appropriate technique to discretize this transfer function is the backward difference method,

which is based on numerical integration theory and has the following equivalence rule:

1

−

d

s

→→

dt

z

)1(

−

T

s

Where:

is the sampling period

T

s

The PID transfer function in discrete time domain is:

1

−

TK

⋅

K)z(G

+=

pc

i

sp

+

1

−

)z1(

−⋅τ

dp

T

s

)z1(K

−⋅τ⋅

It is implemented as follows:

k

∑

IP

j

0

=

Freescale Semiconduc tor 2-1

Preliminary

[]

D

Control Loops In The Online UPS, Rev. 0

)1()()()()(

kekeKjeKkeKkC

−−⋅+⋅+⋅=

Page 50

Where:

TK

⋅

K

=

I

sp

τ

i

is the discrete time integrator gain

and

K

τ

⋅

K

=

D

dp

T

s

is the discrete time differential gain

The proportional gain constant, K

, remains unmodified.

P

2.2 PFC and Rail Control

Figure 2-1 shows a simplified PFC control loop, valid only for positive AC line voltages. The

PFC is a current loop with a set point calculated as the product of the rail voltage control output

times the AC line voltage.

The voltage control must keep a constant DC rail. V. Positive Rail is sensed and compared to

Voltage Setpoint. The error signal then passes through a PI control network, which outputs one of

the operands used to calculate the current set point. The other operand is the AC Line Voltage,

V

control loop.

. This signal is then used as the set point of a second PI control, which forms the current

LINE

Online UPS Designer Reference Manual, Rev. 0

2-2 Freescale Semicond uctor

Preliminary

Page 51

PFC and Rail Control

⎞

⎛

Figure 2-1. PFC and Rail Control Loops (Positive Semicycle)

The goal of the rectifier stage is to maintain the rail DC voltage at ± 220V and to control the input

current to mimic the voltage waveform (and thus to make the complete system appear as a

resistive load to the AC main line). In order to achieve these two goals, two control loops are

required:

A current control loop, implemented with a PI controller, which generates a current as required

by the input inductor. Due to the circuit symmetry, it is possible to implement a control using the

line voltage absolute value to control the signal, regardless of its sign. A suitable controller for

this application is a PI compensator with the following parameters:

14.6)s(Gc

⎜

⎝

1

+=

⎟

s0002.0

⋅

⎠

Control Loops In The Online UPS, Rev. 0

Freescale Semiconduc tor 2-3

Preliminary

Page 52

Using the backward difference method yields the following discrete time equivalent:

⎞

⎛

k

jeKkeKkC

)()()(

∑

⋅+⋅=

IP

j

0

=

With :

K

= 6.4

P

and

= 1.6

K

I

The second controller keeps the rail voltage constant and uses a low pass filter to reject the 60Hz

and 120Hz ripple. The process is much slower than any of these frequencies, and therefore should

not attempt to correct higher harmonic disturbances. The chosen controller is a PI. The output of

this controller modulates the AC main line voltage to obtain the reference for the current loop.

The low-pass filter is a first-order Infinite Impulse Response (IIR) filter with a 3dB cutoff

frequency of 5Hz, implemented with the following transfer function:

zf

)(

)(

ze

zb

⋅

0

=

az

−

1

With:

= 0.01

b

0

= 0.9984

a

1

The following is the proper PI controller:

sGc

19.0)(

⎜

⎝

1

+=

0563.0

⎟

s

⋅

⎠

Using the backward difference method yields the following discrete time equivalent:

k

jeKkeKkC

)()()(

∑

⋅+⋅=

IP

j

0

=

With:

= 0.9

K

P

and

K

= 0.0008

I

Online UPS Designer Reference Manual, Rev. 0

2-4 Freescale Semicond uctor

Preliminary

Page 53

Battery Charger Control

2.3 Battery Charger Control

The circuit in Figure 2-2 shows a schematic battery charger control loop, consisting of an inner

voltage loop and an outer current loop. The sensed battery voltage determines the charging

current (limited to 1 Ampere). This current is a function of the PWM duty cycle.

Figure 2-2. Battery Charger Control Loop

Given that the battery voltage is a slow signal, the sampling frequency for this control is

decimated by 16 relative to the 20kHz (20kHz/16 = 1250Hz) sampling frequency used elsewhere

in the system. The PWM switching frequency is preserved at 20kHz.

In order to avoid saturation of the voltage compensating network’s integrator, its input is

deactivated if the control output is above a predefined threshold.

The batteries are charged using the constant current–constant voltage approach. While the battery

voltage is lower than the floating voltage (in this case 28V), a constant current of 1A is applied.

When the battery terminal voltage reaches 28V, the voltage is kept constant, decreasing the

charge current. The battery charger system is implemented by two nested loops. The inner loop

controls the charging current and uses a PI control. The reference for this control is delivered by a

voltage control loop, whose output is limited from 0 to 1/3, where 1/3 (in Frac16 notation)

represents 1A. When the batteries are discharged, the voltage control increases the current

Control Loops In The Online UPS, Rev. 0

Freescale Semiconduc tor 2-5

Preliminary

Page 54

reference, looking for a 28V voltage. However, when the voltage control loop reaches 1/3, the

⎞

⎛

⎞

⎛

integral action is disconnected and the output is limited, forcing the current loop to set a 1A

charging current to the battery. When floating voltage is reached, the voltage control loop reduces

its output, reducing the current applied to the batteries.

The controller chosen for the current control loop is a PI compensator with the following

parameters:

17.0)s(Gc

⎜

⎝

1

+=

⎟

s001.0

⋅

⎠

Using the backward difference method results in the following discrete time equivalent system:

k

jeKkeKkC

)()()(

∑

⋅+⋅=

IP

j

0

=

With:

= 0.7

K

P

and

K

= 0.035

I

The controller chosen for the voltage control loop is a PI compensator with the following

parameters:

sGc

12.0)(

⎜

⎝

1

+=

⎟

se

332

⋅−

⎠

Using the backward difference method results in the following discrete time equivalent system:

k

jeKkeKkC

)()()(

∑

⋅+⋅=

IP

j

0

=

with:

= 0.02

K

P

and

= 0.0005

K

I

Online UPS Designer Reference Manual, Rev. 0

2-6 Freescale Semicond uctor

Preliminary

Page 55

Inverter Control

⎟

⎠

⎞

⎛

2.4 Inverter Control

The objective of the inverter control loop is to supply the load with a voltage defined by the

reference signal. This reference signal is generated by the PLL system, at a sampling frequency

of 20kHz, high above the 50/60Hz nominal frequency. For this reason, it is reasonable to

consider the set point a constant.

Figure 2-3. Inverter Control Loop

The inverter control is implemented with a nested topology. The outer loop controls the output

voltage and the inner loop controls the inductor current. This configuration allows better stability

of the feedback system and an implicit limitation of the current delivered to the load. The inner

control loop stabilizes the system, acting as a damper for the LC output circuit.

The controller chosen for the current control loop is a PI compensator with the following

parameters:

sGc

Freescale Semiconduc tor 2-7

Preliminary

184.0)(

⎜

⎝

1

+=

0017.0

s

⋅

Control Loops In The Online UPS, Rev. 0

Page 56

Using the backward difference method results in the following discrete time equivalent system:

⎞

⎛

k

jeKkeKkC

)()()(

∑

⋅+⋅=

IP

j

0

=

With:

K

= 0.84

P

and

K

= 0.0024

I

The outer loop is the voltage control. The goal of this loop is to keep a sinusoidal voltage

waveform, regardless of the load characteristics. When nonlinear loads (as a full wave rectifier)

are connected, a high current is drawn at the peaks of the signal. The action taken to overcome

this condition is to inhibit the integral action by disconnecting the integrator input when the

current draw is high. This action reduces the output distortion and enhances the controller

response when the load requires high currents.

The controller chosen for the current control loop is a PI compensator with the following

parameters:

142.3)s(Gc

+=

⎜

⎝

1

s00036.0

⋅

s0001688.0

⋅+

⎟

⎠

Using the backward difference method results in the following discrete time equivalent system:

k

∑

j

IP

0

=

[]

D

)1()()()()(

kekeKjeKkeKkC

−−⋅+⋅+⋅=

With:

= 3.42

K

P

K

= 0.475

I

and

= 11.75

K

D

2.5 Battery Booster Control Loop

The function of this controller is to keep the rail DC voltage at ±220V while the system is

supported by the battery.

Online UPS Designer Reference Manual, Rev. 0

2-8 Freescale Semicond uctor

Preliminary

Page 57

Battery Booster Control Loop

⎞

⎛

Figure 2-4. Battery Booster Control Loop

Given that the rail voltage is a slow signal, the sampling frequency for this control is decimated

by 16 relative to the 20kHz (20kHz/16 = 1250Hz) sampling frequency used in other sections of

the system. The PWM switching frequency is preserved at 20kHz.

The system is implemented with a PID compensator in order to regulate the rail DC voltage. The

control output modulates the duty cycle of a push-pull power supply. The following are the

parameters of such a controller:

116)s(Gc

⎜

⎝

1

+=

s064.0

⋅

s000005.0

⋅+

⎟

⎠

Using the backward difference method yields the following discrete time equivalent system:

k

∑

j

[]

IP

0

=

D

)1()()()()(

kekeKjeKkeKkC

−−⋅+⋅+⋅=

With:

= 16

K

P

K

= 0.2

I

and

= 0.1

K

D

Control Loops In The Online UPS, Rev. 0

Freescale Semiconduc tor 2-9

Preliminary

Page 58

2.6 Minimizing Delay in the Control Loops

⎞

⎛

The triangular signal used as a carrier wave for the PWM is created from a counter that

accumulates at the controller’s clock speed (60MHz). The pulse width of the PWM is updated at

a rate of 20kHz. This implies that in order to obtain both the 20kHz sampling frequency and a