Page 1

UM10360

LPC17xx User manual

Rev. 2 — 19 August 2010 User manual

Document information

Info Content

Keywords LPC1769, LPC1768, LPC1767, LPC1766, LPC1765, LPC1764, LPC1763,

LPC1759, LPC1758, LPC1756, LPC1754, LPC1752, LPC1751, ARM, ARM

Cortex-M3, 32-bit, USB, Ethernet, CAN, I2S, Microcontroller

Abstract LPC17xx user manual

Page 2

NXP Semiconductors

UM10360

LPC17xx user manual

Revision history

Rev Date Description

2 20100819 LPC17xx user manual revision.

Modifications:

• UART0/1/2/3: FIFOLVL register removed.

• ADC: reset value of the ADCTRM register changed to 0xF00 (Table 536).

• Timer0/1/2/3: Description of DMA operation updated.

• USB Device: Corrected error in the USBCmdCode register (0x01 = write, 0x02 = read)

(Table 220

).

• Clocking and power control: add bit 15 (PCGPIO) to PCONP register (Table 46).

• Part LPC1763 added.

• Update register bit description of USBIntStat register in Host and Device mode (Table 191 and

Table 257).

• Motor control PWM: update description of match and limit registers.

• GPIO: update register bit description of the FIOPIN register (Table 109).

• Numerous editorial updates throughout the user manual.

1 20100104 LPC17xx user manual revision.

Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 2 of 840

Page 3

1.1 Introduction

UM10360

Chapter 1: LPC17xx Introductory information

Rev. 2 — 19 August 2010 User manual

The LPC17xx is an ARM Cortex-M3 based microcontroller for embedded applications

requiring a high level of integration and low power dissipation. The ARM Cortex-M3 is a

next generation core that offers system enhancements such as modernized debug

features and a higher level of support block integration.

High speed versions (LPC1769 and LPC1759) operate at up to a 120 MHz CPU

frequency. Other versions operate at up to an 100 MHz CPU frequency. The ARM

Cortex-M3 CPU incorporates a 3-stage pipeline and uses a Ha rvard architecture with

separate local instruction and data buses as well as a third bus for peripherals. The ARM

Cortex-M3 CPU also includes an internal prefetch unit that supports speculative

branches.

The peripheral complement of the LPC17xx includes up to 512 kB of flash memory, up to

64 kB of data memory, Ethernet MAC, a USB interface that can be configured as either

Host, Device, or OTG, 8 channel general purpose DMA controller, 4 UARTs, 2 CAN

channels, 2 SSP controllers, SPI interface, 3 I

interface, 8 channel 12-bit ADC, 10-bit DAC, motor control PWM, Quadrature Encoder

interface, 4 general purpose timers, 6-output ge neral purpose PWM, ultra-low power RTC

with separate battery supply, and up to 70 general purpose I/O pins.

2

C interfaces, 2-input plus 2-output I2S

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 3 of 840

Page 4

NXP Semiconductors

1.2 Features

Refer to Section 1.4.1 for details of features on specific part numbers.

• ARM Cortex-M3 processor, running at frequencies of up to 120 MHz on high speed

• ARM Cortex-M3 built-in Nested Vectored Interrupt Controller (NVIC).

• Up to 512 kB on-chip flash program memory with In-System Programming (ISP) and

• Up to 64 kB on-chip SRAM includes:

• Eight channel General Purpose DMA controller (GPDMA) on the AHB multilayer

• Multilayer AHB matrix interconnect provides a separate bus for each AHB master.

• Split APB bus allows for higher throughput with fewer stalls between the CPU and

• Serial interfaces:

UM10360

Chapter 1: LPC17xx Introductory information

versions (LPC1769 and LPC1759), up to 100 MHz on other versions. A Memory

Protection Unit (MPU) supporting eight regions is included.

In-Application Programming (IAP) capabilities. The combination of an enhanced flash

memory accelerator and location of the flash memory on the CPU local code/data bus

provides high code performance from flash.

– Up to 32 kB of SRAM on the CPU with local code/data bus for high-performance

CPU access.

– Up to two 16 kB SRAM blocks with separate access paths for higher throughput.

These SRAM blocks may be used for Ethernet, USB, and DMA memory, as well as

for general purpose instruction and data storage.

matrix that can be used with the SSP, I

Digital-to-Analog converter peripherals, timer match signals, GPIO, and for

memory-to-memory transfers.

AHB masters include the CPU, General Purpose DMA controller, Ethernet MAC, and

the USB interface. This interconnect provides communication with no arbitration

delays unless two masters attempt to access the same slave at the same time.

DMA. A single level of write buffering allows the CPU to continue without waiting for

completion of APB writes if the APB was not already busy.

– Ethernet MAC with RMII interface and dedicated DMA controller.

– USB 2.0 full-speed controller that can be configured for either device, Host, or

OTG operation with an on-chip PHY for device and Ho st functions and a dedicated

DMA controller.

– Four UARTs with fractional baud rate generation, internal FIFO, IrDA, and DMA

support. One UART has modem control I/O and RS-485/EIA-485 support.

– Two-channel CAN controller.

– Two SSP controllers with FIFO and multi-protocol capabilities. The SSP interfaces

can be used with the GPDMA controller.

– SPI controller with synchronous, serial, full duplex communication and

programmable data length. SPI is included as a legacy peripheral and can be used

instead of SSP0.

2

– Three enhanced I

2

full I

C specification and Fast mode plus with data rates of 1Mbit/s, two with

standard port pins. Enhancements include multiple address recognition and

monitor mode.

C-bus interfaces, one with an open-drain output supporting the

2

S, UART, the Analog-to-Digital and

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 4 of 840

Page 5

NXP Semiconductors

UM10360

Chapter 1: LPC17xx Introductory information

– I2S (Inter-IC Sound) interface for digital audio input or output, with fractional rate

control. The I

3-wire data transmit and receive or 4-wire combined transmit and receive

connections, as well as master clock output.

2

S interface can be used with the GPDMA. The I2S interface supports

• Other peripherals:

– 70 (100 pin package) or 52 (80-pin package) General Purpose I/O (GPIO) pins with

configurable pull-up/down resistors, open drain mode, and repeater mode. All

GPIOs are located on an AHB bus for fast access, and support Cortex-M3

bit-banding. GPIOs can be accessed by the General Purpose DMA Co ntroller. Any

pin of ports 0 and 2 can be used to generate an interrupt.

– 12-bit Analog-to-Digital Converter (ADC) with input multiplexing among eight pins,

conversion rates up to 200 kHz, and multiple result registers. The 12-bit ADC can

be used with the GPDMA controller.

– 10-bit Digital-to-Analog Converter (DAC) with dedicated conversion timer and DMA

support.

– Four general purpose timers/counters, with a total of eight capture inputs and ten

compare outputs. Each timer block has an external count input. Specific timer

events can be selected to generate DM A requests.

– One moto r control PWM with support for three-phase motor control.

– Quadrature encoder interface that can monitor one external quadrature encoder.

– One standard PWM/timer block with external count input.

– Real-Time Clock (RTC) with a separate power domain. The RTC is clocked by a

dedicated RTC oscillator. The R TC block includes 20 bytes of battery-powered

backup registers, allowing system status to be stored when the rest of the chip is

powered off. Battery power can be supplied from a standard 3 V Lithium button

cell. The RTC will continue working when the battery voltage drops to as low as

2.1 V. An RTC interrupt can wake up the CPU from any reduced power mode.

– Watchdog Timer (WDT). The WDT can be clocked from the internal RC oscillator,

the RTC oscillator, or the APB clock.

– Cortex-M3 system tick timer, including an external clock input option.

– Repetitive interrupt timer provides programmable and repeating timed interrupts.

• Standard JTAG test/debug interface as well as Serial Wire Debug and Serial Wire

Trace Port options.

• Emulation trace module supports real-time trace.

• Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep

power-down.

• Single 3.3 V power supply (2.4 V to 3.6 V). Temperature range of -40 °C to 85 °C.

• Four external interrupt inputs configurable as edge/level sen sitive. All pins on POR T0

and PORT2 can be used as edge sensitive interrupt sources.

• Non-maskable Interrupt (NMI) input.

• Clock output function that can reflect the main oscillator clock, IRC clock, RTC clock,

CPU clock, or the USB clock.

• The Wakeup Interrupt Contr oller (WIC) allows the CPU to automatically wake up from

any priority interrupt that can occur while the clocks are stopped in deep sleep,

Power-down, and Deep power-down modes.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 5 of 840

Page 6

NXP Semiconductors

• Processor wake-up from Power-down mode via any interrupt able to operate during

• Each peripheral has its own clock divider for further power savings.

• Brownout detect with separate threshold for interrupt and forced reset.

• On-chip Power-On Reset (POR).

• On-chip crystal oscillator with an operating range of 1 MHz to 25 MHz.

• 4 MHz internal RC oscillator trimmed to 1% accuracy that can optionally be used as a

• An on-chip PLL allows CPU operation up to the maximum CPU rate without the nee d

• A second, dedicated PLL may be used for the USB interface in order to allow added

• Versatile pin function selection feature allows many possibilities for using on-chip

• Available as 100-pin LQFP (14 x 14 x 1.4 mm) and 80-pin LQFP (12 x 12 x 1.4 mm)

UM10360

Chapter 1: LPC17xx Introductory information

Power-down mode (includes external interrupts, RTC interrupt, USB activity, Ethernet

wake-up interrupt, CAN bus activity, PORT0/2 pin interrupt, and NMI).

system clock.

for a high-frequency crystal. May be run from the main oscillator, the internal RC

oscillator, or the RTC oscillator.

flexibility for the Main PLL settings.

peripheral functions.

packages.

1.3 Applications

• eMetering

• Lighting

• Industrial networking

• Alarm systems

• White goods

• Motor control

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 6 of 840

Page 7

NXP Semiconductors

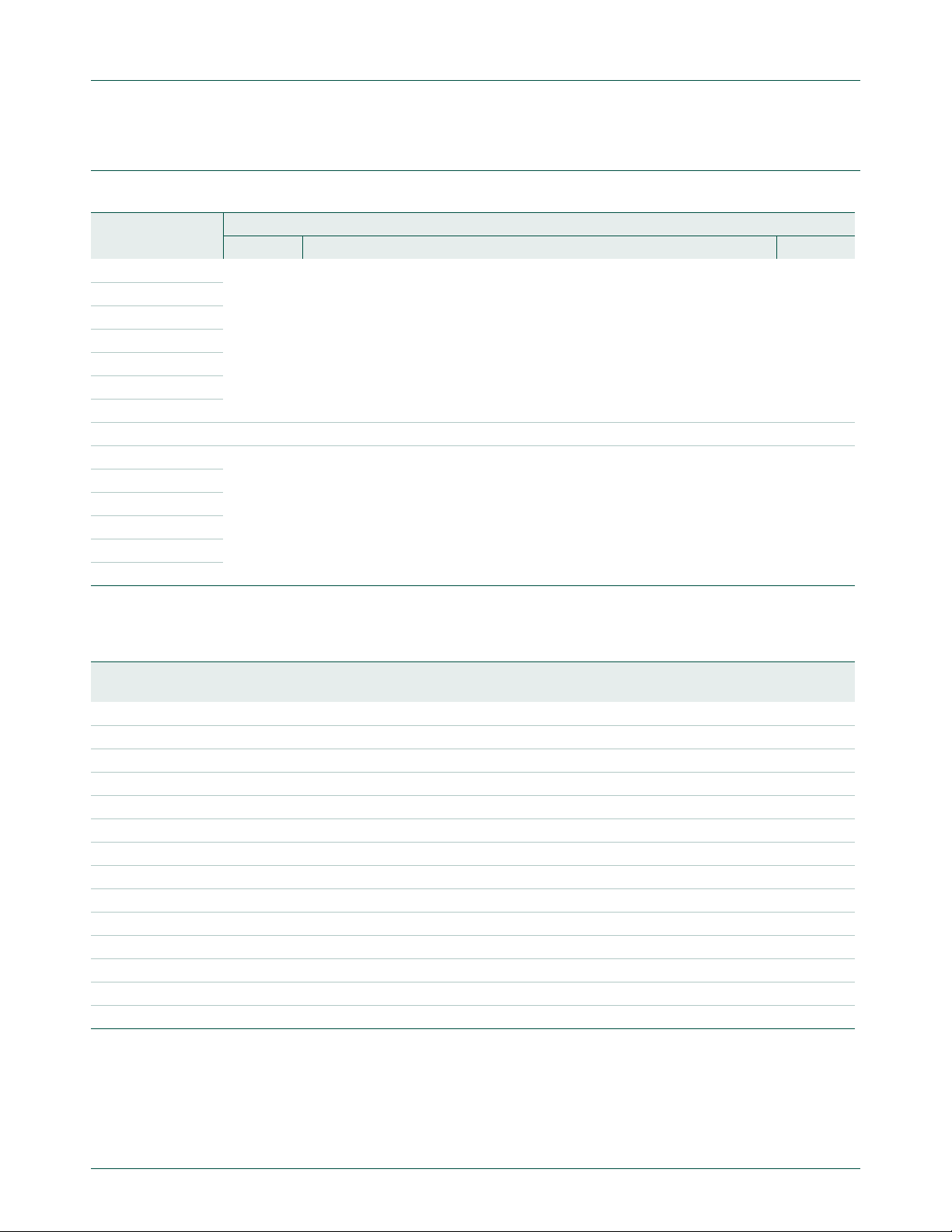

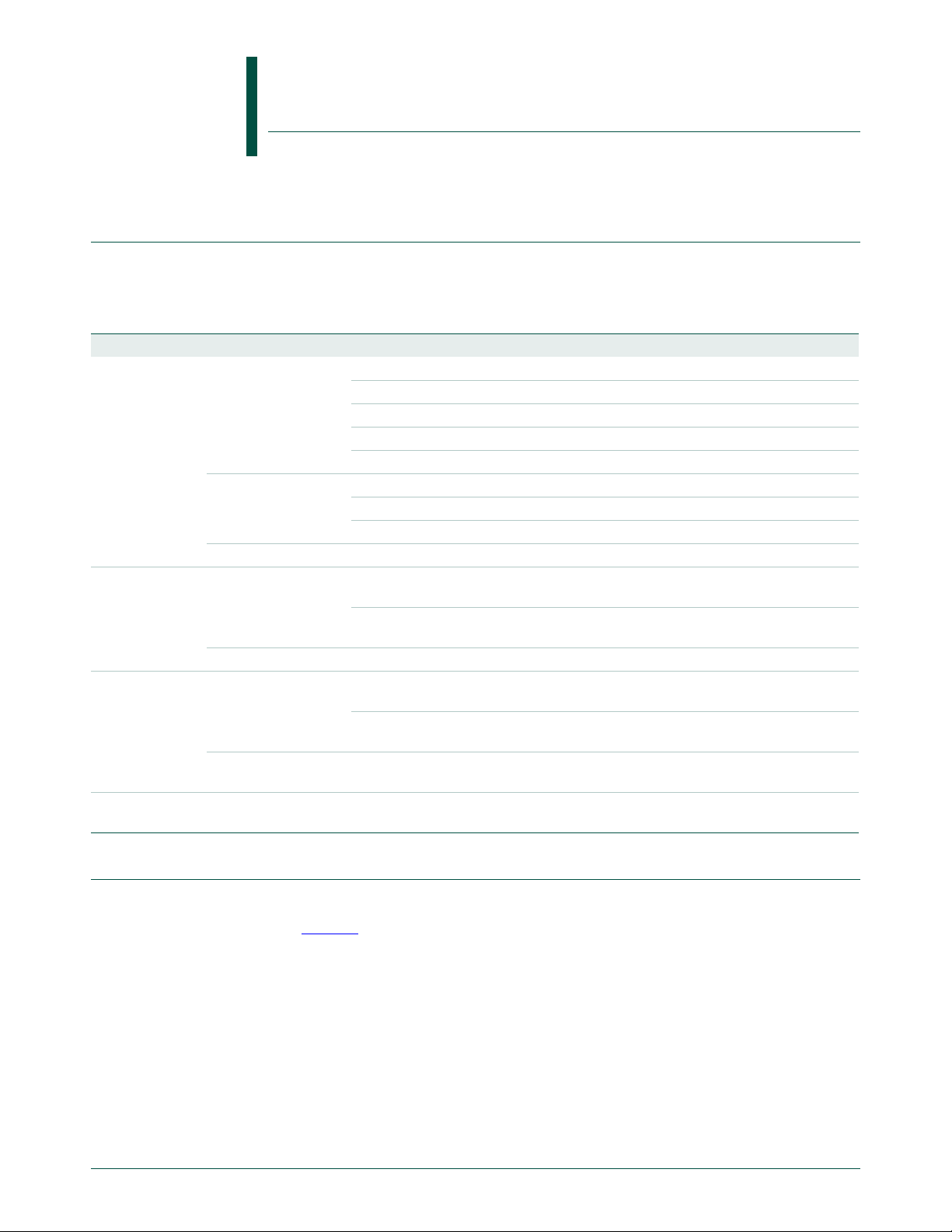

1.4 Ordering information

UM10360

Chapter 1: LPC17xx Introductory information

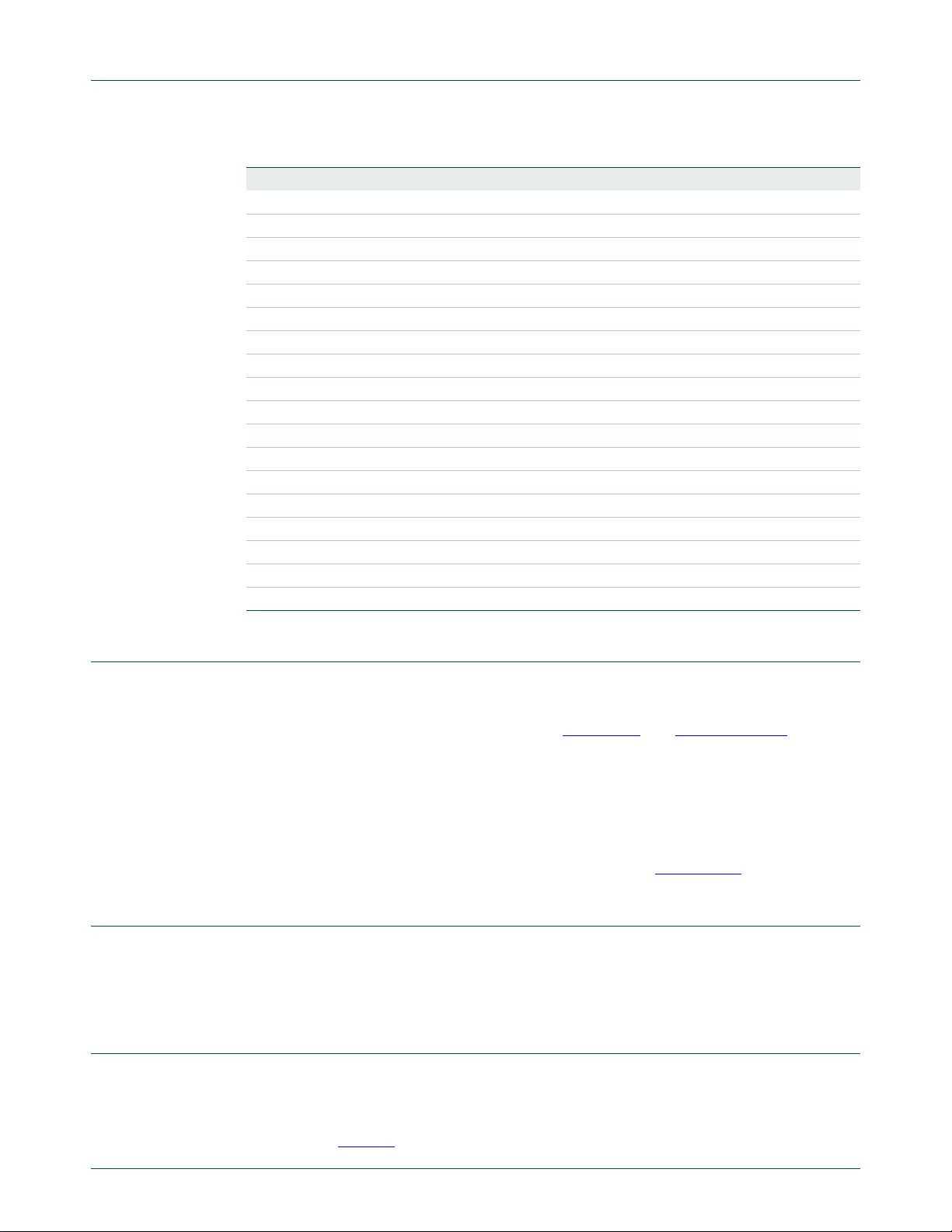

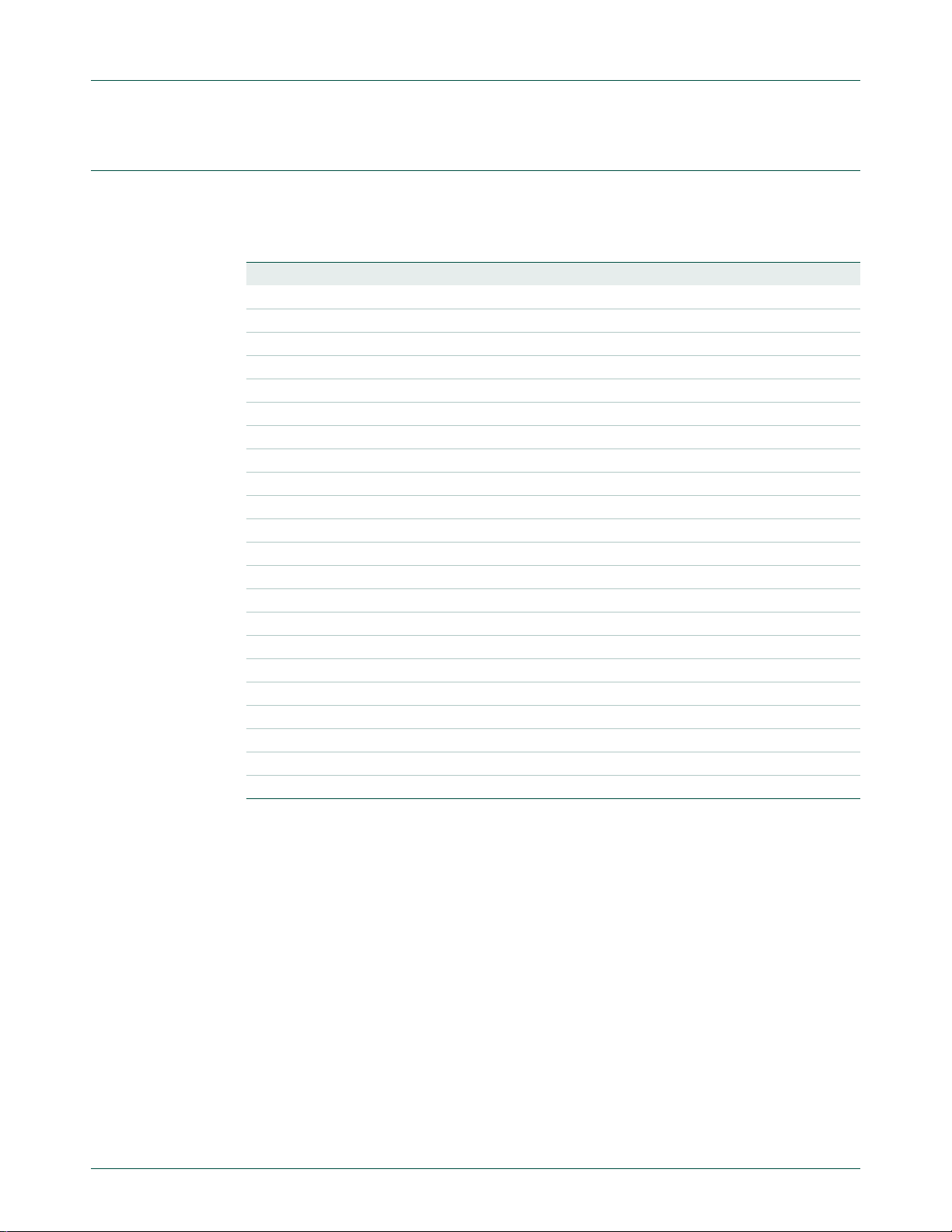

Table 1. Ordering information

Type number Package

LPC1769FBD100

LPC1768FBD100

LPC1767FBD100

LPC1766FBD100

LPC1765FBD100

LPC1764FBD100

LPC1763FBD100

LPC1768FET100 TFBGA100 plastic thin fine-pitch ball grid array package; 100 balls; body 9 x 9 x 0.7 mm SOT926-1

LPC1759FBD80

LPC1758FBD80

LPC1756FBD80

LPC1754FBD80

LPC1752FBD80

LPC1751FBD80

Name Description Version

LQFP100 plastic low profile quad flat package; 100 leads; body 14 × 14 × 1.4 mm SOT407-1

LQFP80 plastic low profile quad flat package; 80 leads; body 12 × 12 × 1.4 mm SOT315-1

1.4.1 Part options summary

Table 2. Ordering options for LPC17xx parts

Type number Max. CPU

LPC1769FBD100 120 MHz 512 kB 64 kB yes Device/Host/OTG 2 yes yes 100 pin

LPC1768FBD100 100 MHz 512 kB 64 kB yes Device/Host/OTG 2 yes yes 100 pin

LPC1768FET100 100 MHz 512 kB 64 kB yes Device/Host/OTG 2 yes yes 100 pin

LPC1767FBD100 100 MHz 512 kB 64 kB yes no no yes yes 100 pin

LPC1766FBD100 100 MHz 256 kB 64 kB yes Device/Host/OTG 2 yes yes 100 pin

LPC1765FBD100 100 MHz 256 kB 64 kB no Device/Host/OTG 2 yes yes 100 pin

LPC1764FBD100 100 MHz 128 kB 32 kB yes Device 2 no no 100 pin

LPC1763FBD100 100 MHz 256 kB 64 kB no no no yes yes 100 pin

LPC1759FBD80 120 MHz 512 kB 64 kB no Device/Host/OTG 2 yes yes 80 pin

LPC1758FBD80 100 MHz 512 kB 64 kB yes Device/Host/OTG 2 yes yes 80 pin

LPC1756FBD80 100 MHz 256 kB 32 kB no Device/Host/OTG 2 yes yes 80 pin

LPC1754FBD80 100 MHz 128 kB 32 kB no Device/Host/OTG 1 no yes 80 pin

LPC1752FBD80 100 MHz 64 kB 16 kB no Device 1 no no 80 pin

LPC1751FBD80 100 MHz 32 kB 8 kB no Device 1 no no 80 pin

speed

Flash Total

SRAM

Ethernet USB CAN I2S DAC Package

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 7 of 840

Page 8

NXP Semiconductors

AHB to

APB bridge

AHB to

APB bridge

APB slave group 1APB slave group 0

Note: shaded peripheral blocks

support General Purpose DMA

RTC Power Domain

Multilayer AHB Matrix

I2C2

I2S

UARTs 2 & 3

SSP0

Real Time Clock

20 bytes of backup

registers

SSP1

UARTs 0 & 1

CAN 1 & 2

I2C 0 & 1

SPI0

Capture/Compare

Timers 0 & 1

Watchdog Timer

PWM1

12-bit ADC

Pin Connect Block

GPIO Interrupt Ctl

32 kHz

oscillator

DMA

controller

Clock Generation,

Power Control,

Brownout Detect,

and other

system functions

RST

Xtalin

Xtalout

Clocks

and

Controls

Ethernet

PHY

interface

Ethernet

10/100

MAC

USB

device,

host,

OTG

USB

interface

JTAG

interface

ARM Cortex-M3

Test/Debug Interface

System

bus

D-code

bus

I-code

bus

ROM

8 kB

SRAM

64 kB

Trace

Port

Trace Module

High Speed GPIO

Capture/Compare

Timers 2 & 3

External Interrupts

DAC

System Control

Motor Control PWM

Quadrature Encoder

Repetitive Interrupt

Timer

Flash

512 kB

Flash

Accelerator

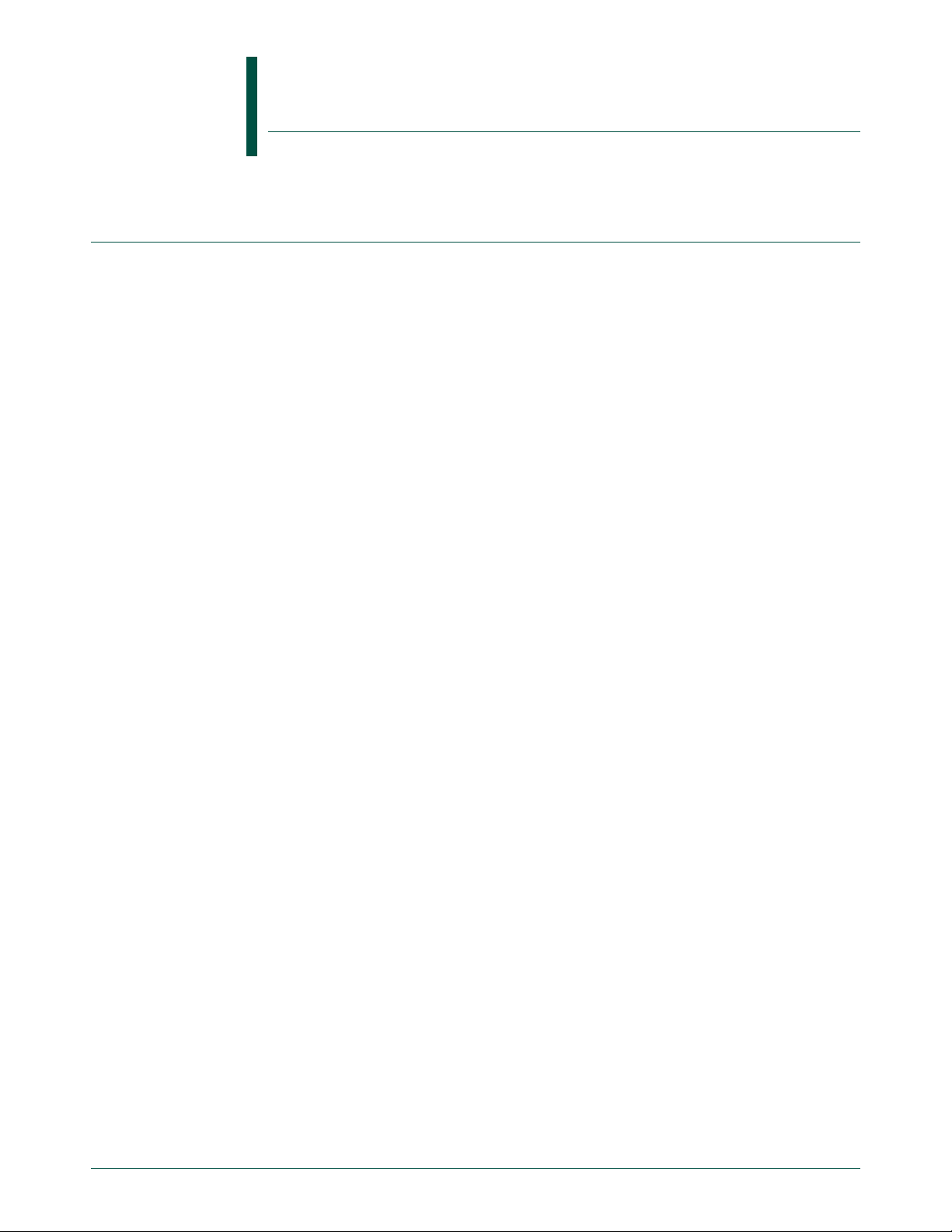

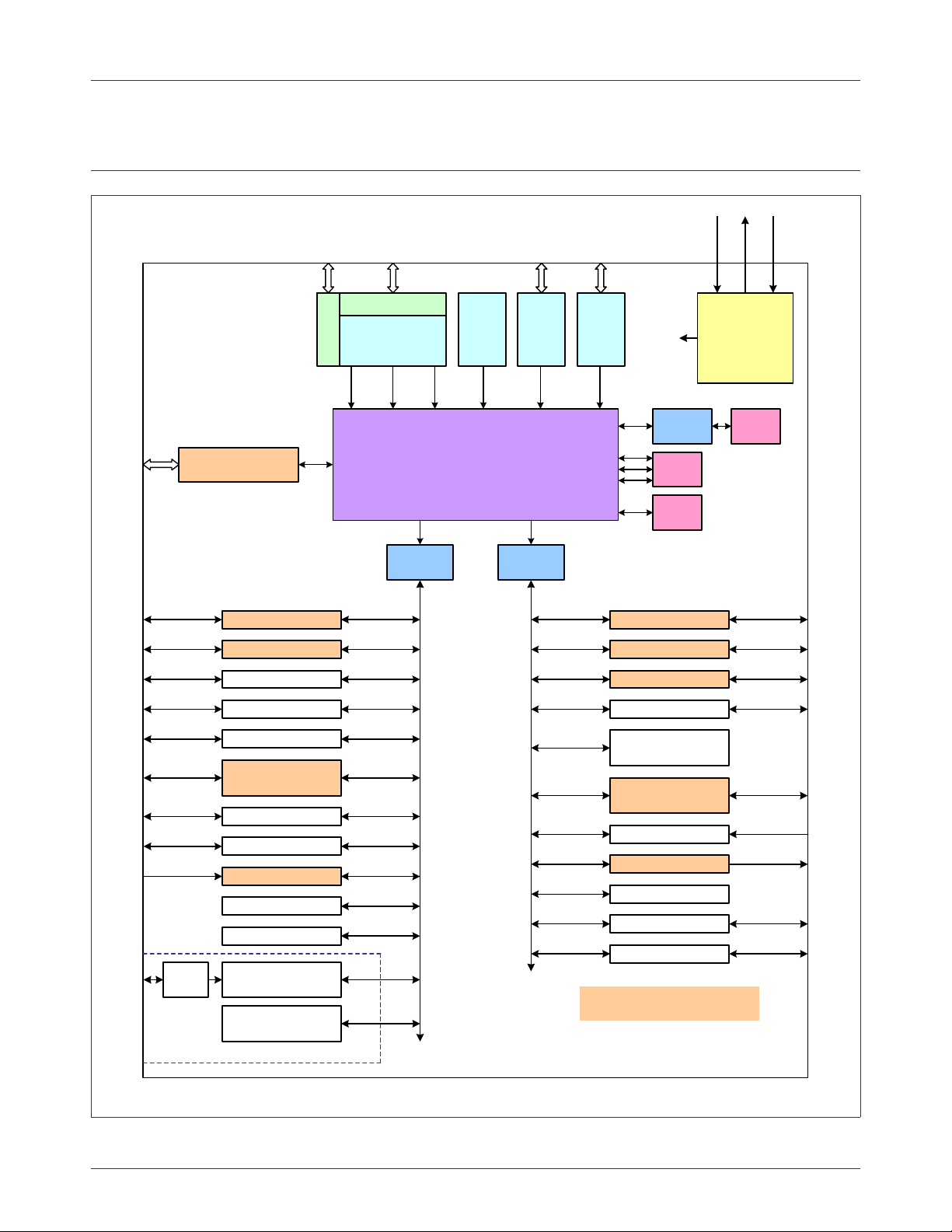

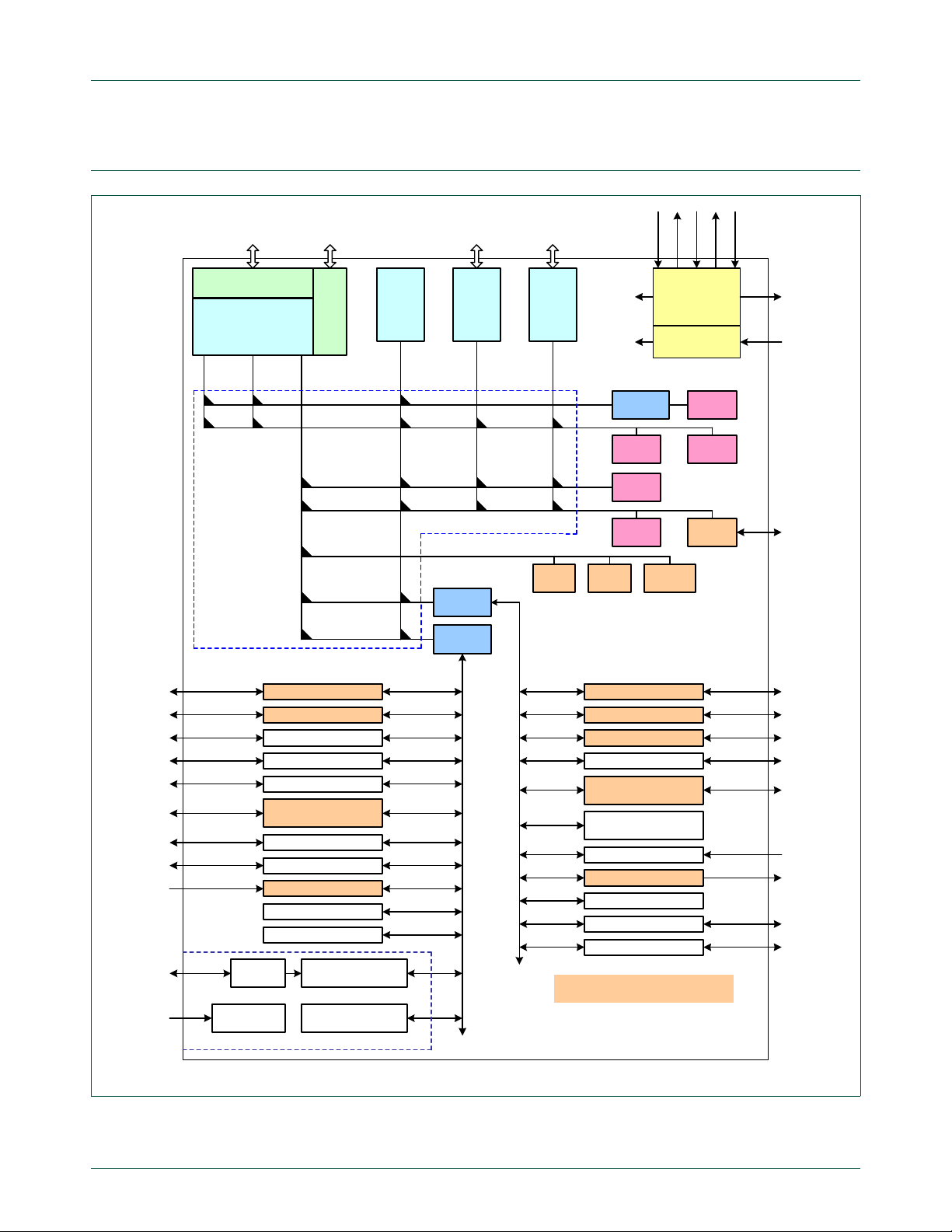

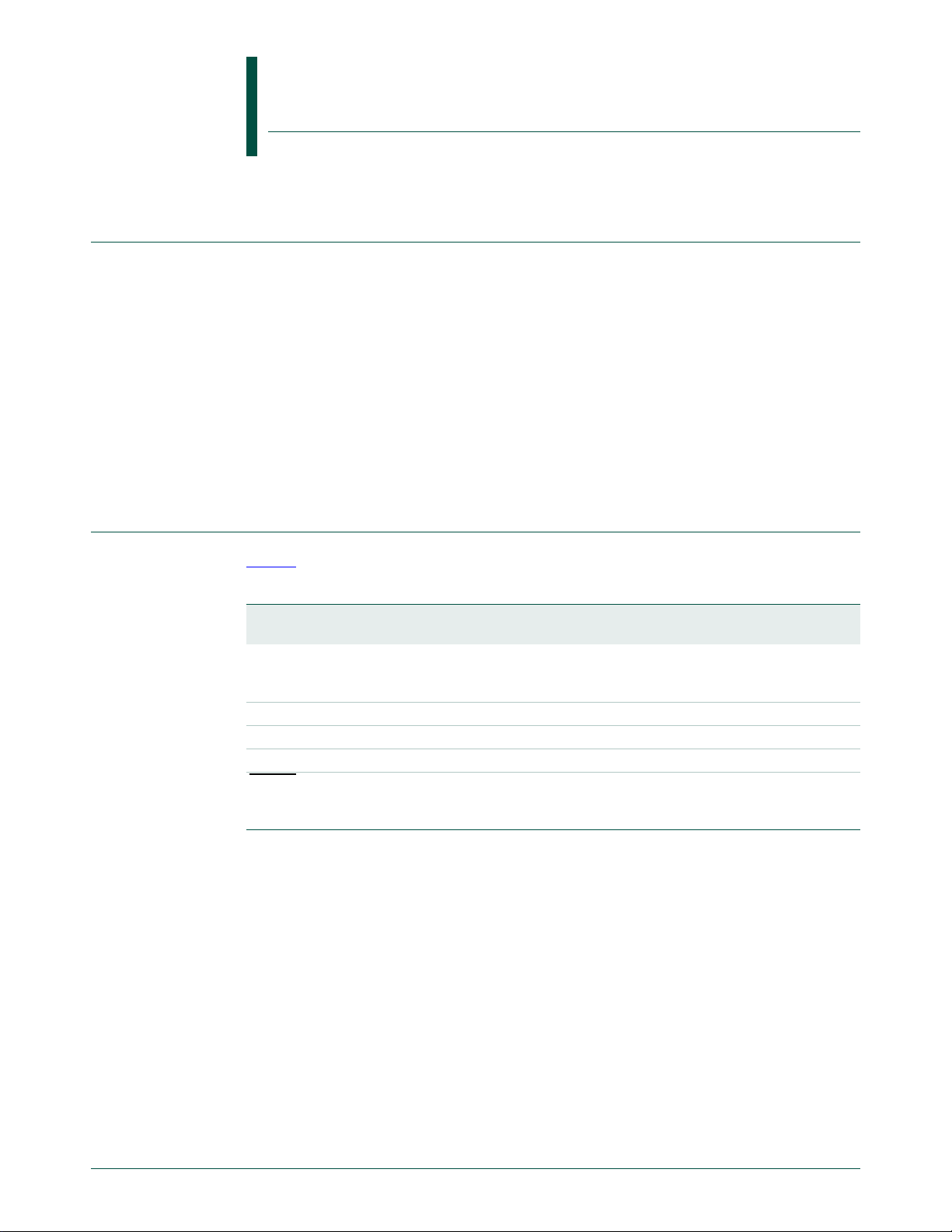

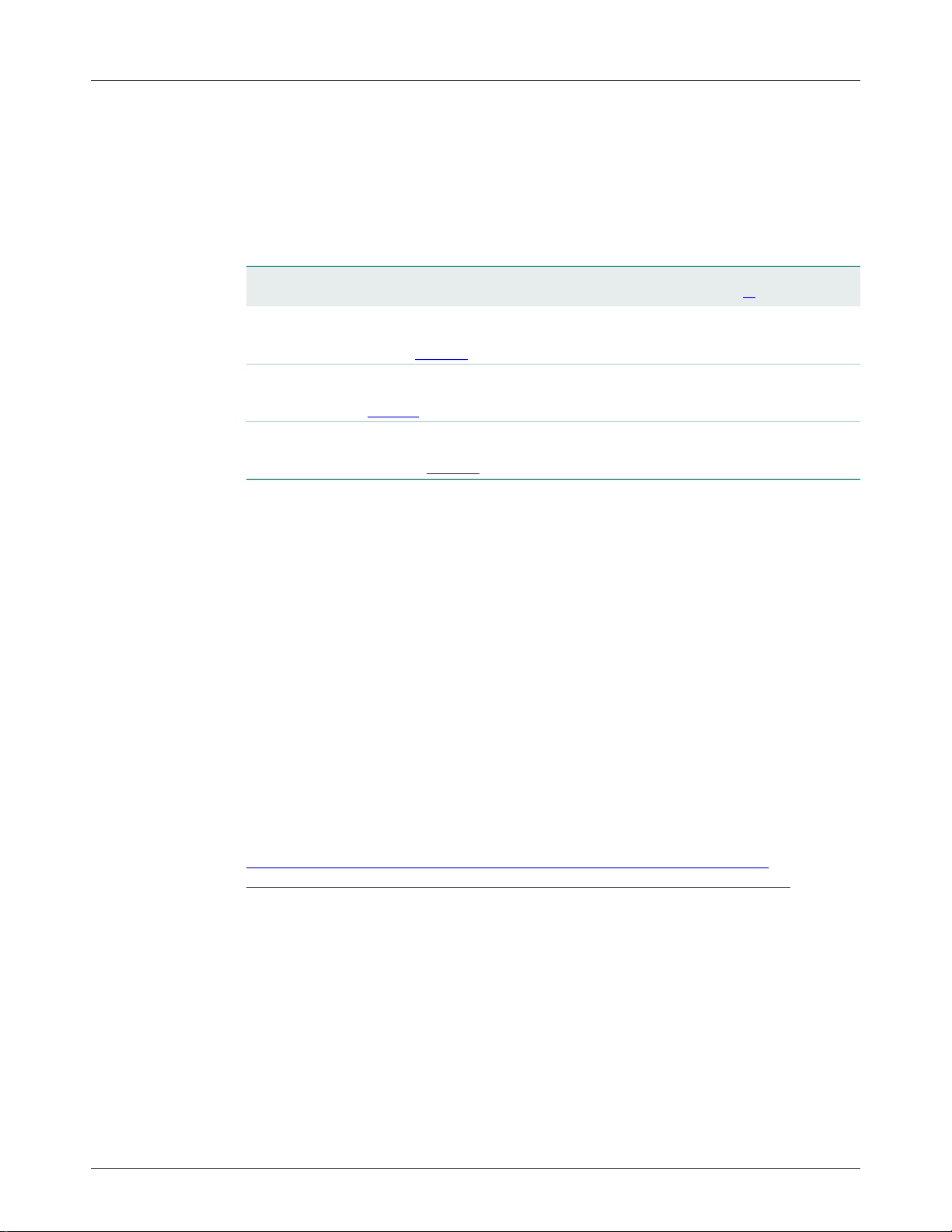

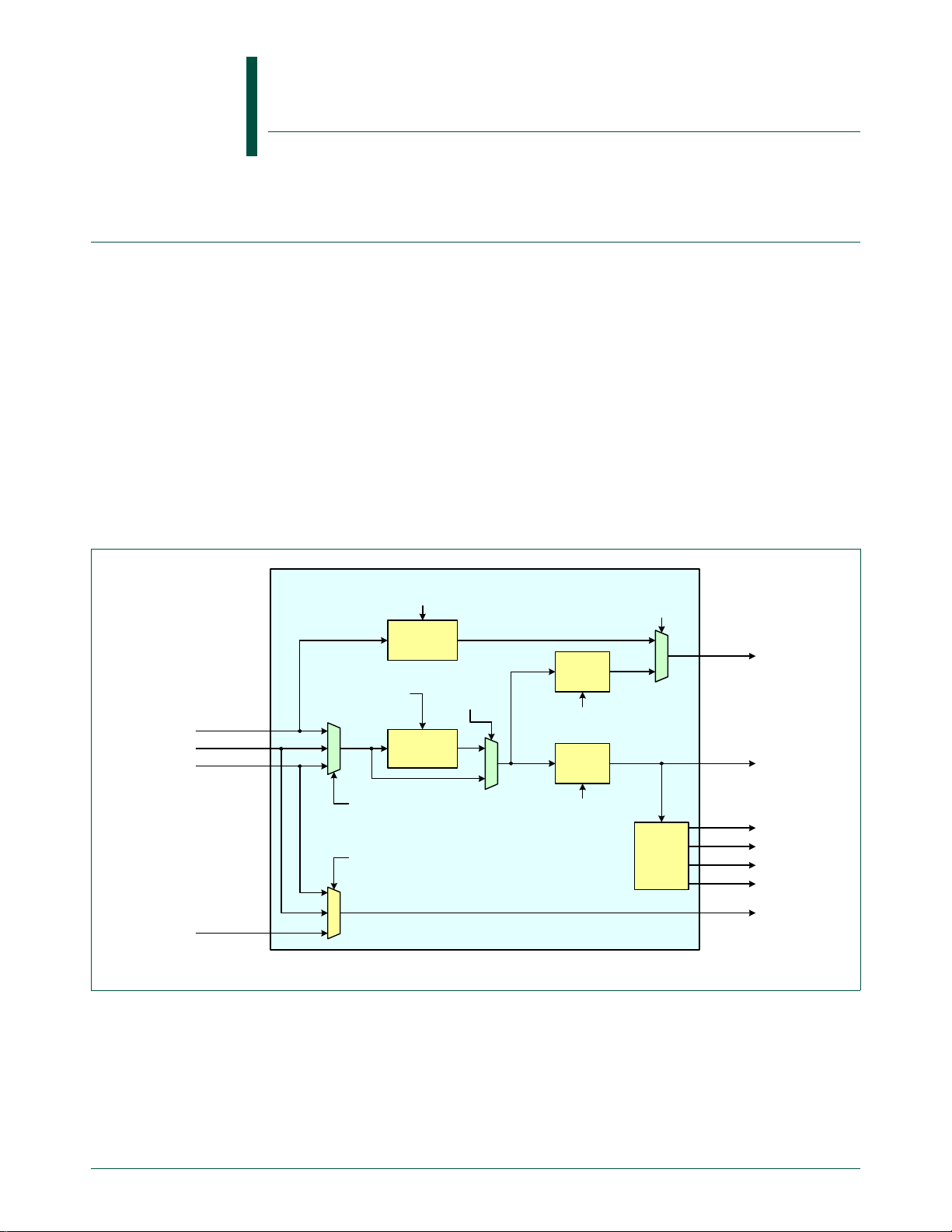

1.5 Simplified block diagram

UM10360

Chapter 1: LPC17xx Introductory information

Fig 1. LPC1768 simplified block diagram

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 8 of 840

Page 9

NXP Semiconductors

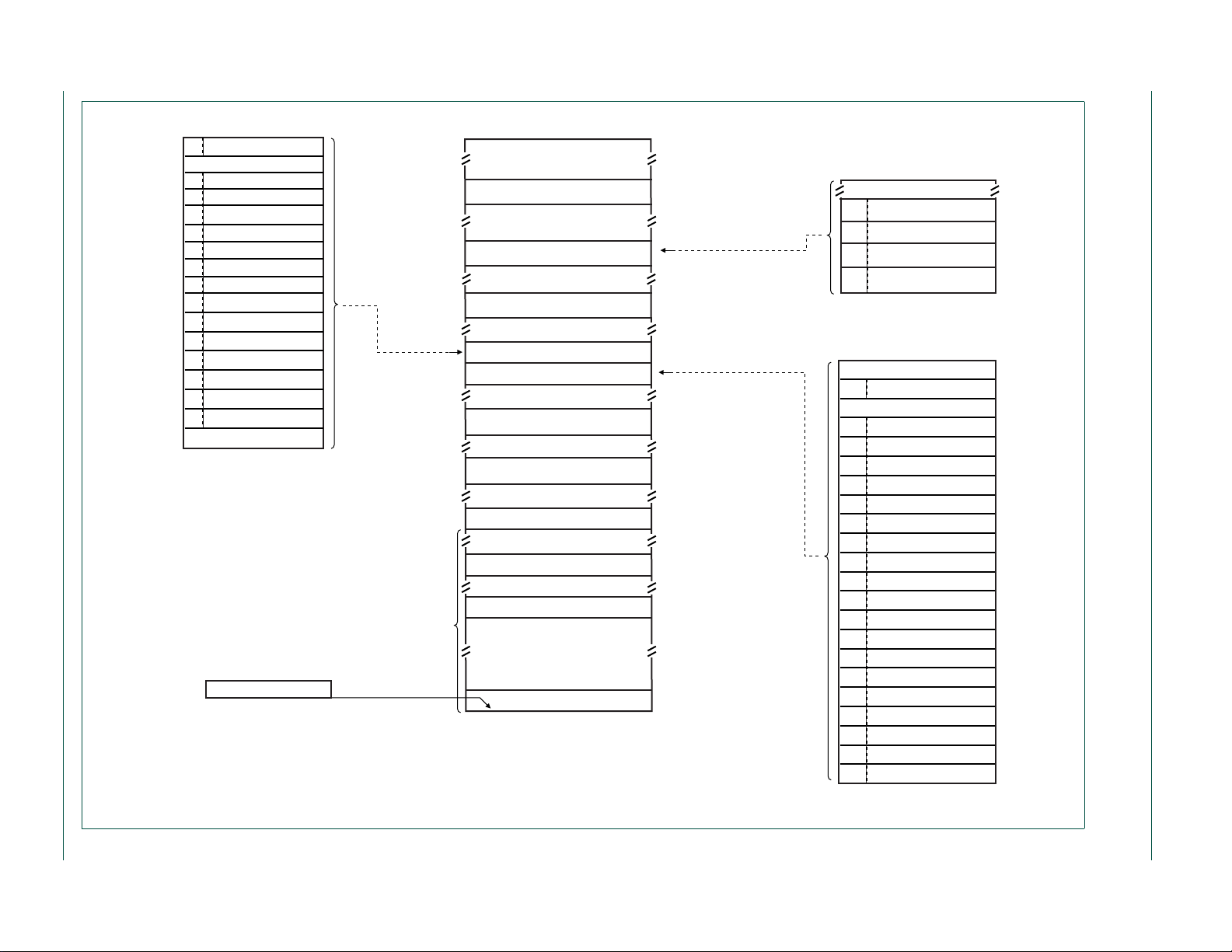

1.6 Architectural overview

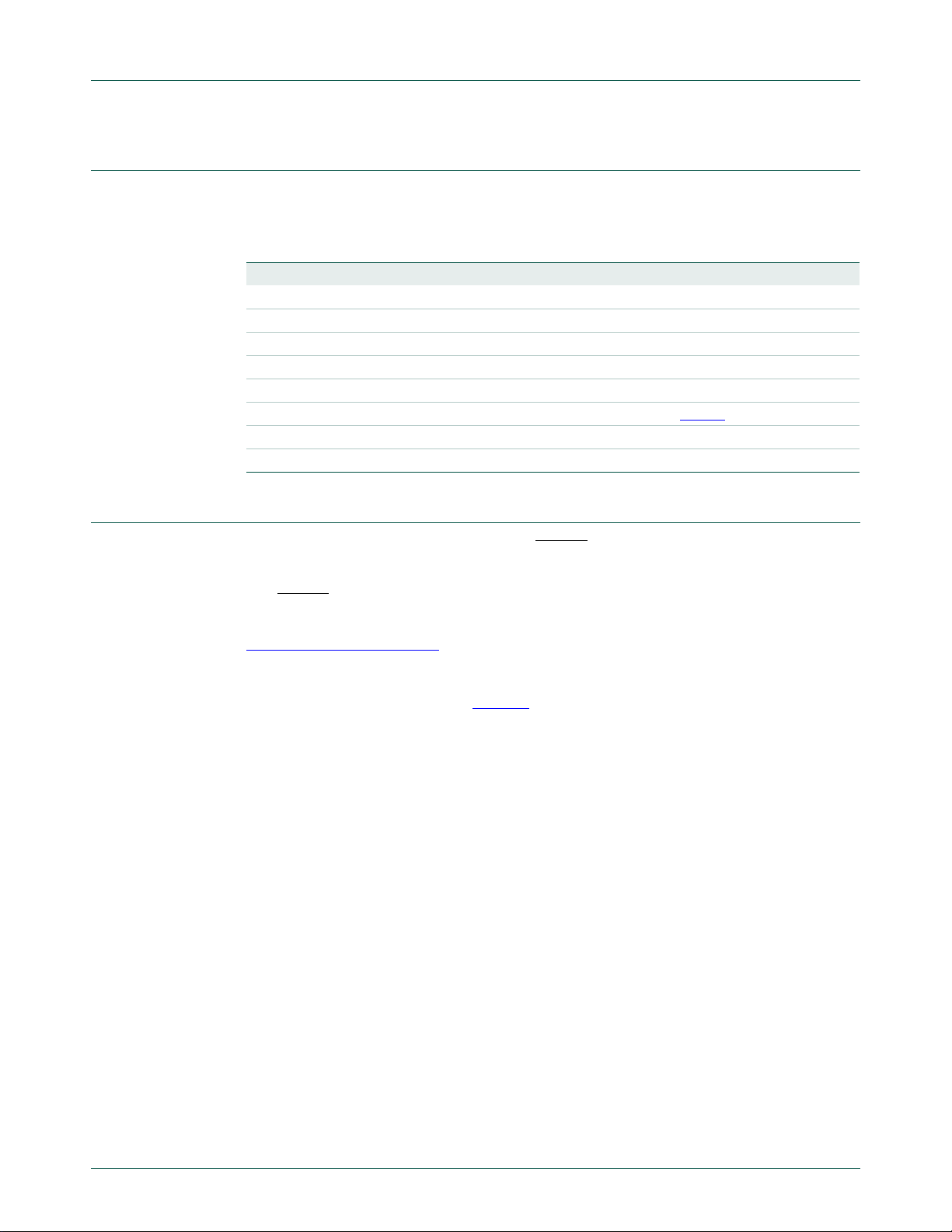

The ARM Cortex-M3 includes three AHB-Lite buses, one system bus and the I-code and

D-code buses which are faster and are used similarly to TCM interfaces: one bus

dedicated for instruction fetch (I-code) and one bus for data access (D-code). The use of

two core buses allows for simultaneous operations if concurrent ope rations target dif ferent

devices.

The LPC17xx uses a multi-layer AHB matrix to connect the Cortex-M3 buses and other

bus masters to peripherals in a flexible manner that optimizes performance by allowing

peripherals on different slaves ports of the matrix to be accessed simultaneously by

different bus masters. Det ails of the multilayer matrix connections are shown in Figure 2

APB peripherals are connected to the CPU via two APB busses using separate slave

ports from the multilayer AHB matrix. This allows for better performance by reducing

collisions between the CPU and the DMA controller. The APB bus bridges are configured

to buffer writes so that the CPU or DMA controller can write to APB devices without

always waiting for APB write completion.

UM10360

Chapter 1: LPC17xx Introductory information

.

1.7 ARM Cortex-M3 processor

The ARM Cortex-M3 is a general purpose 32-bit microprocessor, which offers high

performance and very low power consumption. The Cortex-M3 offers many new features,

including a Thumb-2 instruction set, low interrupt latency, hardware divide,

interruptible/continuable multiple load and store instructions, automatic state save and

restore for interrupts, tightly integrated interrupt controller with Wakeup Interrupt

Controller, and multiple core buses capable of simultaneous accesses.

Pipeline techniques are employed so that all pa rts of the p rocessing and memory systems

can operate continuously. T ypically, while one instruction is being executed, its successor

is being decoded, and a third instruction is being fetched from memory.

The ARM Cortex-M3 processor is described in detail in the Cortex-M3 User Guide that is

appended to this manual.

1.7.1 Cortex-M3 Configuration Options

The LPC17xx uses the r2p0 version of the Cortex-M3 CPU, which includes a number of

configurable options, as noted below.

System options:

• The Nested Vectored Inter rupt Controller (NVIC) is included. The NVIC includes the

SYSTICK timer.

• The Wakeup Interrupt Controller (WIC) is included. The WIC allows more powerful

options for waking up the CPU from reduced power modes.

• A Memory Protection Unit (MPU) is included.

• A ROM Table in included. The ROM Table provides addresses of debug components

to external debug systems.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 9 of 840

Page 10

NXP Semiconductors

Debug related options:

• A JTAG debug interface is included.

• Serial Wire Debug is included. Serial Wire Debug allows debug op erations u sing only

• The Embedded Trace Macrocell (ETM) is included. The ETM provides instruction

• The Data Watchpoint and Trace (DWT) unit is included. The DWT allows data

• An Instrumentation T race Macrocell (ITM) is included. Software can write to the ITM in

• The Trace Port Interface Unit (TPIU) is included. The TPIU encodes and provides

• A Flash Patch and Breakpoint (FPB) is included. The FPB can generate hardware

UM10360

Chapter 1: LPC17xx Introductory information

2 wires, simple trace functions can be added with a third wire.

trace capabilities.

address or data value matches to be trace information or trigger other events. The

DWT includes 4 comparators and counters for certain internal events.

order to send messages to the trace port.

trace information to the outside world. This can be on the Serial Wire V iewer pin or the

4-bit parallel trace port.

breakpoints and remap specific addresses in code space to SRAM as a temporary

method of altering non-volatile code. The FPB include 2 literal comparators and 6

instruction comparators.

1.8 On-chip flash memory system

The LPC17xx contains up to 512 kB of on-chip flash memory. A flash memory accelerator

maximizes performance for use with the two fast AHB-Lite buses. This memory may be

used for both code and data storage. Programming of the flash memory may be

accomplished in several ways. It may be programmed In System via the serial port. The

application program may also erase and/or program the flash while the application is

running, allowing a great degree of flexibility for data storage field firmware upgrades, etc.

1.9 On-chip Static RAM

The LPC17xx contains up to 64 kB of on-chip static RAM memory. Up to 32 kB of SRAM,

accessible by the CPU and all three DMA controllers are on a higher-speed bus. Devices

containing more than 32 kB SRAM have two additional 16 kB SRAM blocks, each situated

on separate slave ports on the AHB multilayer matrix.

This architecture allows the possibility for CPU and DMA accesses to be separated in

such a way that there are few or no delays for the bus masters.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 10 of 840

Page 11

NXP Semiconductors

Multilayer

AHB Matrix

AHB to

APB bridge

AHB to

APB bridge

JTAG

interface Debug Port

Ethernet PHY

interface

SRAM

16 kB

SRAM

16 kB

EMULATION

TRACE MODULE

ARM Cortex-M3

TEST/DEBUG

INTERFACE

USB

device,

host,

OTG

USB

interface

DMA

controller

Ethernet

10/100

MAC

System

bus

D-code

bus

I-code

bus

DMAC

regs

USB

regs

Ethernet

regs

clock generation,

power control,

and other

system functions

SRAM

32 kB

ROM

8 kB

Flash

512 kB

Flash

Accelerator

RST

Xtalin

Xtalout

X32Kin

X32Kout

APB slave group 1

Note: shaded peripheral blocks

support General Purpose DMA

Capture/compare

timers 2 & 3

I2C2

I2S

UARTs 2 & 3

SSP0

External interrupts

DAC

System control

Motor control PWM

Quadrature encoder

APB slave group 0

RTC Power Domain

Real Time Clock

SSP1

UARTs 0 & 1

CAN 1 & 2

I2C 0 & 1

SPI0

Capture/compare

timers 0 & 1

Watchdog timer

PWM1

12-bit ADC

Pin connect block

GPIO interrupt control

32 kHz

oscillator

Backup registers

(20 bytes)

Repetitive interrupt

timer

ultra-low power

regulator

Vbat

voltage regulator

clocks

and

controls

internal

power

Vdd

CLK

OUT

HS

GPIO

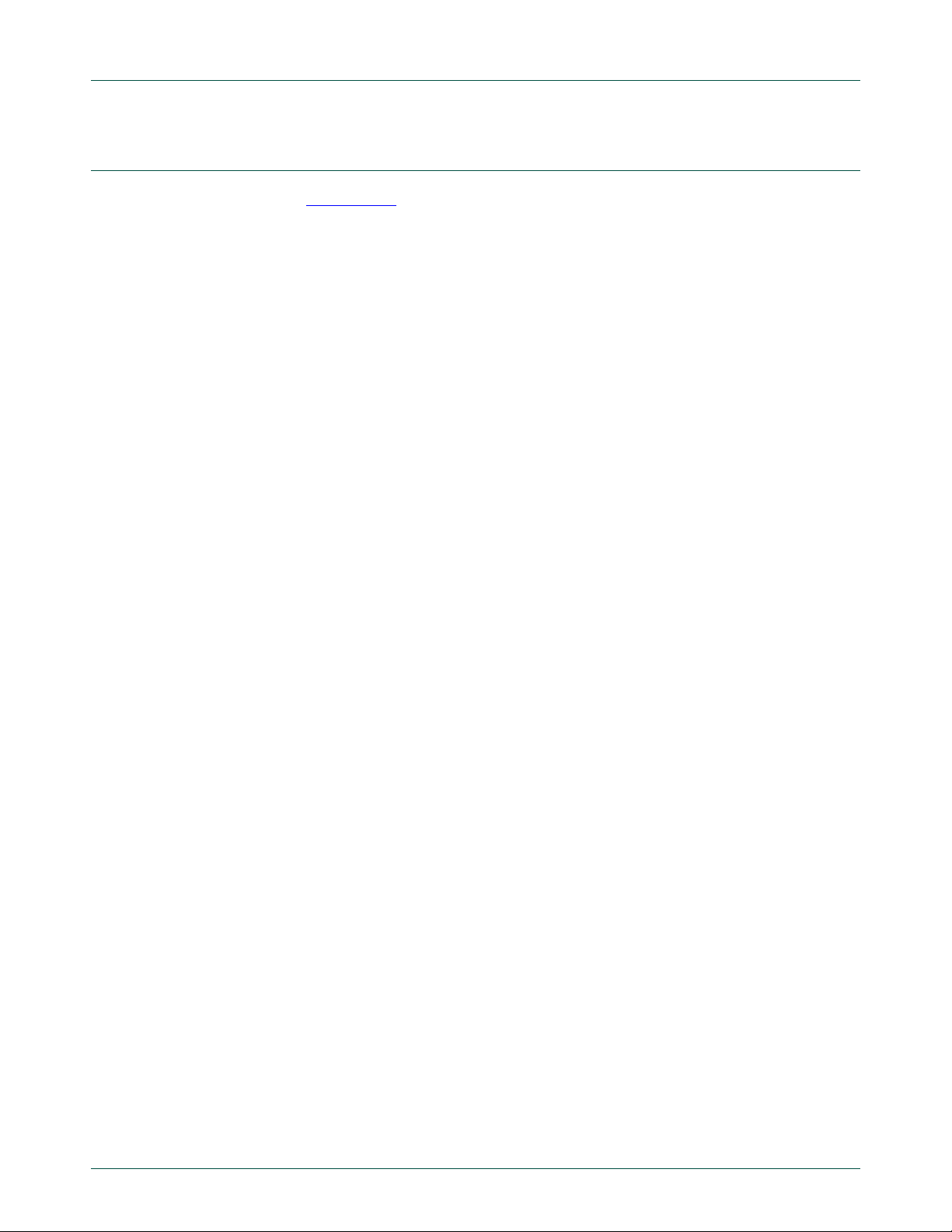

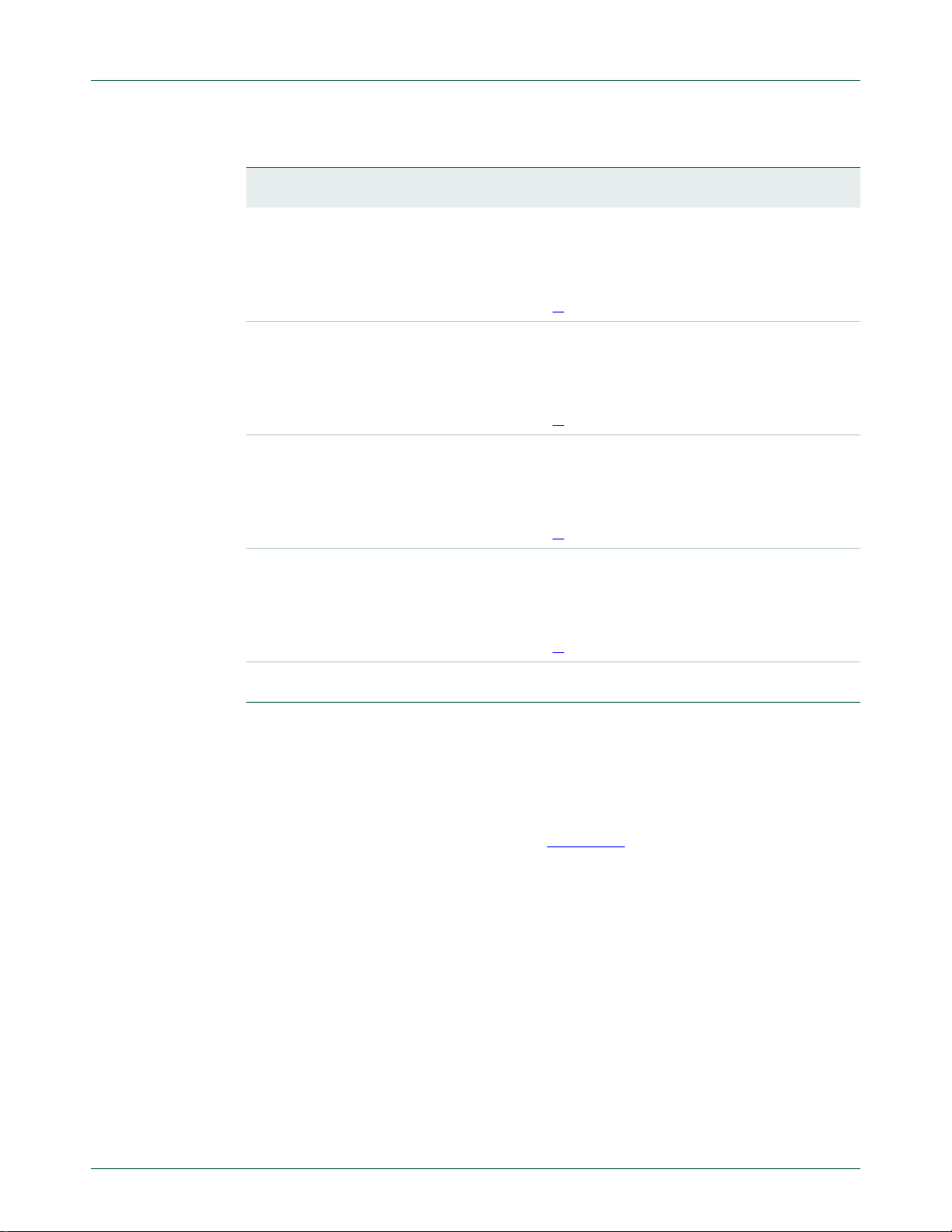

1.10 Block diagram

UM10360

Chapter 1: LPC17xx Introductory information

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 11 of 840

Fig 2. LPC1768 block diagram, CPU and buses

Page 12

UM10360

Chapter 2: LPC17xx Memory map

Rev. 2 — 19 August 2010 User manual

2.1 Memory map and peripheral addressing

The ARM Cortex-M3 processor has a single 4 GB address space. The following table

shows how this space is used on the LPC17xx.

Table 3. LPC17xx memory usage and details

Address range General Use Address range details and description

0x0000 0000 to

0x1FFF FFFF

0x2000 0000 to

0x3FFF FFFF

0x4000 0000 to

0x5FFF FFFF

0xE000 0000 to

0xE00F FFFF

On-chip non-volatile

memory

On-chip SRAM 0x1000 0000 - 0x1000 7FFF For devices with 32 kB of local SRAM.

Boot ROM 0x1FFF 0000 - 0x1FFF 1FFF 8 kB Boot ROM with flash services.

On-chip SRAM

(typically used for

peripheral data)

GPIO 0x2009 C000 - 0x2009 FFFF GPIO.

APB Peripherals 0x4000 0000 - 0x4007 FFFF APB0 Peripherals, up to 32 peripheral blocks,

AHB peripherals 0x5000 0000 - 0x501F FFFF DMA Controller, Ethernet interface, and USB

Cortex-M3 Private

Peripheral Bus

0x0000 0000 - 0x0007 FFFF For devices with 512 kB of flash memory.

0x0000 0000 - 0x0003 FFFF For devices with 256 kB of flash memory.

0x0000 0000 - 0x0001 FFFF For devices with 128 kB of flash memory.

0x0000 0000 - 0x0000 FFFF For devices with 64 kB of flash memory.

0x0000 0000 - 0x0000 7FFF For devices with 32 kB of flash memory.

0x1000 0000 - 0x1000 3FFF For devices with 16 kB of local SRAM.

0x1000 0000 - 0x1000 1FFF For devices with 8 kB of local SRAM.

0x2007 C000 - 0x2007 FFFF AHB SRAM - bank 0 (16 kB), present on

devices with 32 kB or 64 kB of total SRAM.

0x2008 0000 - 0x2008 3FFF AHB SRAM - bank 1 (16 kB), present on

devices with 64 kB of total SRAM.

16 kB each.

0x4008 0000 - 0x400F FFFF APB1 Peripherals, up to 32 peripheral blocks,

16 kB each.

interface.

0xE000 0000 - 0xE00F FFFF Cortex-M3 related functions, includes the

NVIC and System Tick Timer.

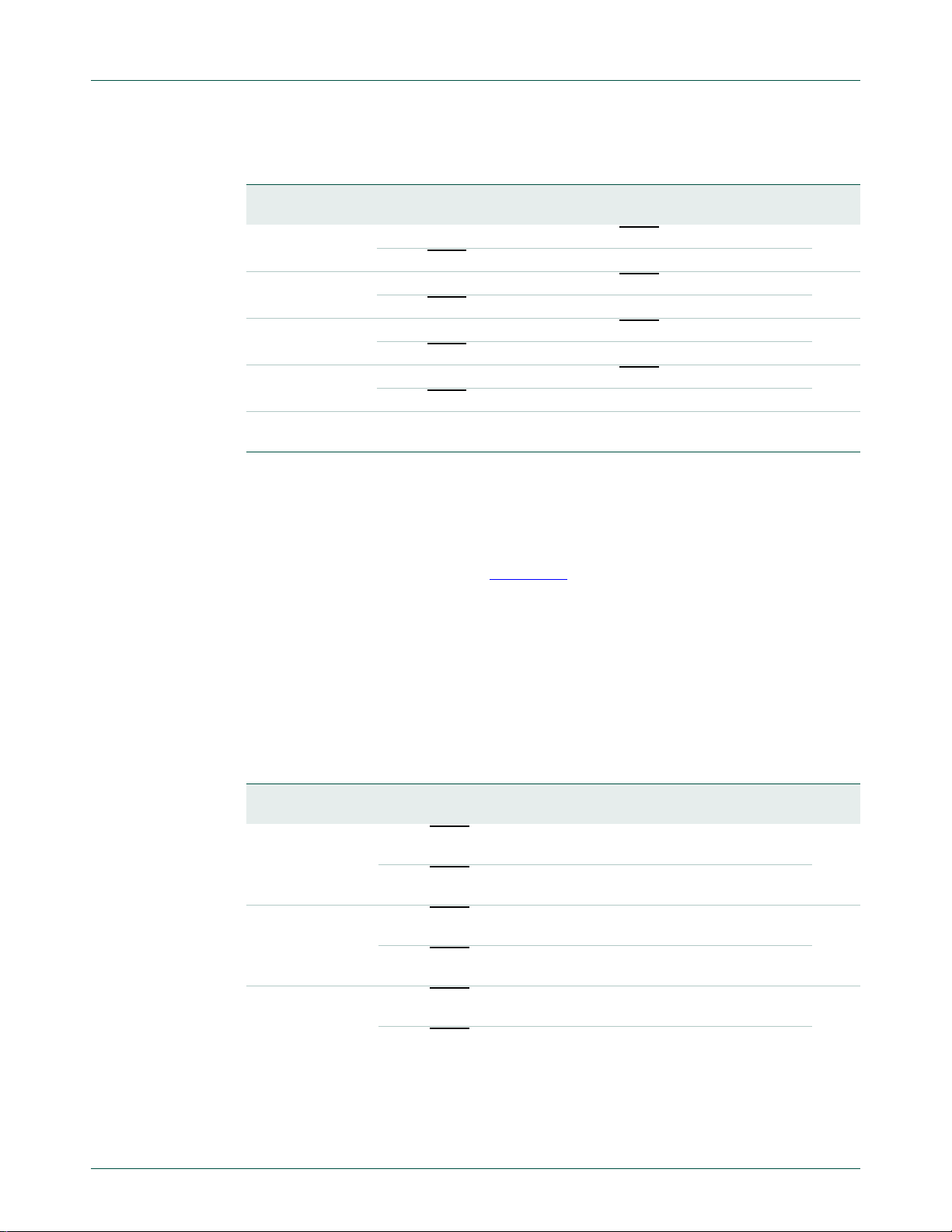

2.2 Memory maps

The LPC17xx incorporates several distinct memory regions, shown in the following

figures. Figure 3

program viewpoint following reset. The interrupt vector area supports address remapping,

which is described later in this section.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 12 of 840

shows the overall map of the entire address space from the user

Page 13

User manual Rev. 2 — 19 August 2010 13 of 840

0x5000 0000

0x5000 4000

0x5000 8000

0x5000 C000

0x5020 0000

AHB peripherals

Ethernet controller

USB controller

reserved

127- 4 reserved

GPDMA controller

0

1

2

3

APB0 peripherals

0x4000 4000

0x4000 8000

0x4000 C000

0x4001 0000

0x4001 8000

0x4002 0000

0x4002 8000

0x4002 C000

0x4003 4000

0x4003 0000

0x4003 8000

0x4003 C000

0x4004 0000

0x4004 4000

0x4004 8000

0x4004 C000

0x4005 C000

0x4006 0000

0x4008 0000

0x4002 4000

0x4001 C000

0x4001 4000

0x4000 0000

WDT

TIMER0

TIMER1

UART0

UART1

reserved

I2C0

SPI

RTC + backup registers

GPIO interrupts

pin connect

SSP1

ADC

CAN AF RAM

CAN AF registers

CAN common

CAN1

CAN2

22 - 19 reserved

I2C1

31 - 24 reserved

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

23

APB1 peripherals

0x4008 0000

0x4008 8000

0x4008 C000

0x4009 0000

0x4009 4000

0x4009 8000

0x4009 C000

0x400A 0000

0x400A 4000

0x400A 8000

0x400A C000

0x400B 0000

0x400B 4000

0x400B 8000

0x400B C000

0x400C 0000

0x400F C000

0x4010 0000

SSP0

DAC

Timer 2

Timer 3

UART2

UART3

reserved

I2S

I2C2

1 - 0 reserved

2

3

4

5

6

7

8

9

10

reserved

repetitive interrupt timer

11

12

reserved

motor control PWM

30 - 16 reserved

13

14

15

system control31

reserved

reserved

32 kB local static RAM

reserved

reserved

private peripheral bus

0x0000 0000

0 GB

0.5 GB

4 GB

1 GB

0x0008 0000

0x1000 0000

0x1000 8000

0x1FFF 0000

0x1FFF 2000

0x2007 C000

0x2008 4000

0x2009 C000

0x200A 0000

0x2200 0000

0x2400 0000

0x4000 0000

0x4008 0000

0x4010 0000

0x4200 0000

0x4400 0000

0x5000 0000

0x5020 0000

0xE000 0000

0xE010 0000

0xFFFF FFFF

reserved

reserved

GPIO

reserved

reserved

reserved

reserved

APB0 peripherals

AHB periherals

APB1 peripherals

AHB SRAM bit band alias addressing

peripheral bit band alias addressing

AHB SRAM (2 blocks of 16 kB)

LPC1768 memory space

512 kB on-chip flash

QEI

PWM1

8 kB boot ROM

0x0000 0000

0x0000 0400

active interrupt vectors

+ 256 words

I-code/D-code

memory space

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxx x x x xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xx xx xxxxx

xxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxx xxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxx x x

xxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxx xxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxx

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

xxxxxxxxxxxxxxxxxxxxxxxxx xxxxxxxxxxxxxxxxxxxx xxx

NXP Semiconductors

Fig 3. LPC17xx system memory map

Chapter 2: LPC17xx Memory map

UM10360

Page 14

NXP Semiconductors

Figure 3 and Table 4 show different views of the peripheral address space. The AHB

peripheral area is 2 megabyte in size, and is divided to allow for up to 128 peripherals.

The APB peripheral area is 1 megabyte in size and is divided to allow for up to 64

peripherals. Each peripheral of either type is allocated 16 kilobytes of space. This allows

simplifying the address decoding for each peripheral.

All peripheral register addresses are word aligned (to 32-bit boundaries) regardless of

their size. This eliminates the need for byte lane mapping hardware that would be required

to allow byte (8-bit) or half-word (16-bit) accesses to occur at smaller boundaries. An

implication of this is that word and half-word registers must be accessed all at once. For

example, it is not possible to read or write the upper byte of a word register separately.

2.3 APB peripheral addresses

The following table shows the APB0/1 address maps. No APB peripheral uses all of the

16 kB space allocated to it. Typically each device’s registers are "aliased" or repeated at

multiple locations within each 16 kB range.

T able 4. APB0 peripherals and base addresses

APB0 peripheral Base address Peripheral name

0 0x4000 0000 Watchdog Timer

1 0x4000 4000 Timer 0

2 0x4000 8000 Timer 1

3 0x4000 C000 UART0

4 0x4001 0000 UART1

5 0x4001 4000 reserved

6 0x4001 8000 PWM1

7 0x4001 C000 I

8 0x4002 0000 SPI

9 0x4002 4000 RTC

10 0x4002 8000 GPIO interrupts

11 0x4002 C000 Pin Connect Block

12 0x4003 0000 SSP1

13 0x4003 4000 ADC

14 0x4003 8000 CAN Acceptance Filter RAM

15 0x4003 C000 CAN Acceptance Filter Registers

16 0x4004 0000 CAN Common Registers

17 0x4004 4000 CAN Controller 1

18 0x4004 8000 CAN Controller 2

19 to 22 0x4004 C000 to 0x4005 8000 reserved

23 0x4005 C000 I

24 to 31 0x4006 0000 to 0x4007 C000 reserved

UM10360

Chapter 2: LPC17xx Memory map

2

C0

2

C1

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 14 of 840

Page 15

NXP Semiconductors

T able 5. APB1 peripherals and base addresses

APB1 peripheral Base address Peripheral name

0 0x4008 0000 reserved

1 0x4008 4000 reserved

2 0x4008 8000 SSP0

3 0x4008 C000 DAC

4 0x4009 0000 Timer 2

5 0x4009 4000 Timer 3

6 0x4009 8000 UART2

7 0x4009 C000 UART3

8 0x400A 0000 I

9 0x400A 4000 reserved

10 0x400A 8000 I

11 0x400A C000 reserved

12 0x400B 0000 Repetit ive interrupt timer

13 0x400B 4000 reserved

14 0x400B 8000 Motor control PWM

15 0x400B C000 Quadrature Encoder Interface

16 to 30 0x400C 0000 to 0x400F 8000 reserved

31 0x400F C000 System control

UM10360

Chapter 2: LPC17xx Memory map

2

C2

2

S

2.4 Memory re-mapping

The Cortex-M3 incorporates a mechanism that allows remapping the interrupt vector table

to alternate locations in the memory map. This is controlled via the Vector Table Offset

Register contained in the Cortex-M3. Refer to Section 6.4

and Section 34.4.3.5 of the

Cortex-M3 User Guide appended to this manual for details of the Vector Table Offset

feature.

Boot ROM re-mapping

Following a hardware reset, the Boot ROM is temporarily mapped to address 0. This is

normally transparent to the user . However , if execution is halted imm ediately after reset by

a debugger, it should correct the mapping for the user. See Section 33.6

.

2.5 AHB arbitration

The Multilayer AHB Matrix arbitrates between several masters. By default, the Cortex-M3

D-code bus has the highest priority, followed by the I-Code bus. All other masters share a

lower priority.

2.6 Bus fault exceptions

The LPC17xx generates Bus Fault exception if an access is a ttempted for an add ress that

is in a reserved or unassigned address region. The regions are are as of the memor y map

that are not implemented for a specific derivative. These include all spaces marked

“reserved” in Figure 3

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 15 of 840

.

Page 16

NXP Semiconductors

For these areas, both attempted data acce ss and in struction fetch genera te an exception.

In addition, a Bus Fault exception is generated for any instruction fetch that maps to an

AHB or APB peripheral address.

Within the address space of an existing APB peripheral, an exception is not generated in

response to an access to an undefined address. Address decoding within e ach peripheral

is limited to that needed to distinguish defined registers within the peripheral itself. For

example, an access to address 0x4000 D000 (an undefined address within the UART0

space) may result in an access to the register defined at address 0x4000C000. Details of

such address aliasing within a peripheral space are not defined in the LPC17xx

documentation and are not a supported feature.

If software executes a write directly to the flash memory, the flash accelerator will

generate a Bus Fault exception. Flash prog r amm i ng must be acco m plis he d by using the

specified flash programming interface provided by the Boot Code.

Note that the Cortex-M3 core stores the exception flag along with the associated

instruction in the pipeline and processes the exception only if an attempt is made to

execute the instruction fetched from the disallowed address. This prevents accidental

aborts that could be caused by prefetches that occur when code is executed very near a

memory boundary.

UM10360

Chapter 2: LPC17xx Memory map

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 16 of 840

Page 17

3.1 Introduction

UM10360

Chapter 3: LPC17xx System control

Rev. 2 — 19 August 2010 User manual

The system control block includes several system features and control registers for a

number of functions that are not related to specific peripheral devices. These include:

• Reset

• Brown-Out Detection

• External Interrupt Input s

• Miscellaneous System Controls and Status

Each type of function has its own register(s) if any are required and unneeded bits are

defined as reserved in order to allow future expansion. Unrelated functions never share

the same register addresses

3.2 Pin description

Table 6 shows pins tha t ar e as soc i at ed with Syst em Con tr ol block fu nctions.

Table 6. Pin summary

Pin name Pin

EINT0 Input External Interrupt In put 0 - An active low/high level or falling/rising

EINT1 Input

EINT2 Input

EINT3 Input

RESET

Pin description

direction

edge general purpose interrupt input. This pin may be used to wake up

the processor from Sleep, Deep-sleep, or Power-down modes.

External Interrupt Input 1 - See the EINT0 description above.

External Interrupt Input 2 - See the EINT0 description above.

External Interrupt Input 3 - See the EINT0 description above.

Input External Reset input - A LOW on this pin resets the chip, causing I/O

ports and peripherals to take on their default states, and the processor to

begin execution at address 0x0000 0000.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 17 of 840

Page 18

NXP Semiconductors

3.3 Register description

All registers, regardless of size, are on word address boundaries. Details of the registers

appear in the description of each function.

T able 7. Summary of system control registers

Name Description Access Reset value Address

External Interrupts

EXTINT External Interrup t Flag Register R/W 0 0x400F C140

EXTMODE External Interrupt Mode register R/W 0 0x400F C148

EXTPOLAR External Interrupt Polarity Register R/W 0 0x 400F C14C

Reset

RSID Reset Source Iden tif icatio n Register R/W see Table 8 0x400F C180

Syscon Miscellaneous Registers

SCS System Control and Status R/W 0 0x400F C1A0

3.4 Reset

UM10360

Chapter 3: LPC17xx System control

Reset has 4 sources on the LPC17xx: the RESET pin, Watchdog Reset, Power On Reset

(POR), and Brown Out Detect (BOD).

The RESET

pin is a Schmitt trigger input pin. Assertion of chip Reset by any source, once

the operating voltage attains a usable level, starts the wake-up timer (see description in

Section 4.9 “

Wake-up timer” in this chapter), causing reset to remain asserted until the

external Reset is de-asserted, the oscillator is running, a fixed number of clocks have

passed, and the flash controller has completed it s initialization. The reset logic is shown in

the following block diagram (see Figure 4

).

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 18 of 840

Page 19

NXP Semiconductors

C

Q

S

APB read of

PDBIT

in PCON

power-down

C

Q

S

F

OSC

to other

blocks

WAKE-UP TIMER

watchdog

reset

external

reset

START

COUNT 2

n

internal RC

oscillator

Reset to the

on-chip circuitry

Reset to

PCON.PD

write “1”

from APB

reset

EINT0 wake-up

EINT1 wake-up

EINT2 wake-up

POR

BOD

EINT3 wake-up

RTC wake-up

BOD wake-up

Ethernet MAC wake-up

USB need_clk wake-up

CAN wake-up

GPIO0 port wake-up

GPIO2 port wake-up

UM10360

Chapter 3: LPC17xx System control

Fig 4. Reset block diagram including the wake-up timer

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 19 of 840

On the assertion of a reset source external to the Cortex-M3 CPU (POR, BOD reset,

External reset, and Watchdog reset), the IRC starts up. After the IRC-start-up time

(maximum of 60 μs on power-up) and after the IRC provides a stable clock output, the

reset signal is latched and synchronized on the IRC clock. Then the following two

sequences start simultaneously:

1. The 2-bit IRC wake-up timer starts counting when the synchronized reset is

de-asserted. The boot code in the ROM starts when the 2-bit IRC wake-up timer times

out. The boot code performs the boot tasks and may jump to the flash. If the flash is

not ready to access, the Flash Accelerator will insert wait cycles until the flash is

ready.

2. The flash wake-up timer (9-bit) starts counting when the synchronized reset is

de-asserted. The flash wakeup-timer generates the 100 μs flash start-up time. Once it

times out, the flash initialization sequence is started, which takes about 250 cycles.

When it’s done, the Flash Accelerator will be granted access to the flash.

When the internal Reset is removed, the processor begins executing at address 0, which

is initially the Reset vector mapped from the Boot Block. At that point, all of the processor

and peripheral registers have been initialized to predetermined values.

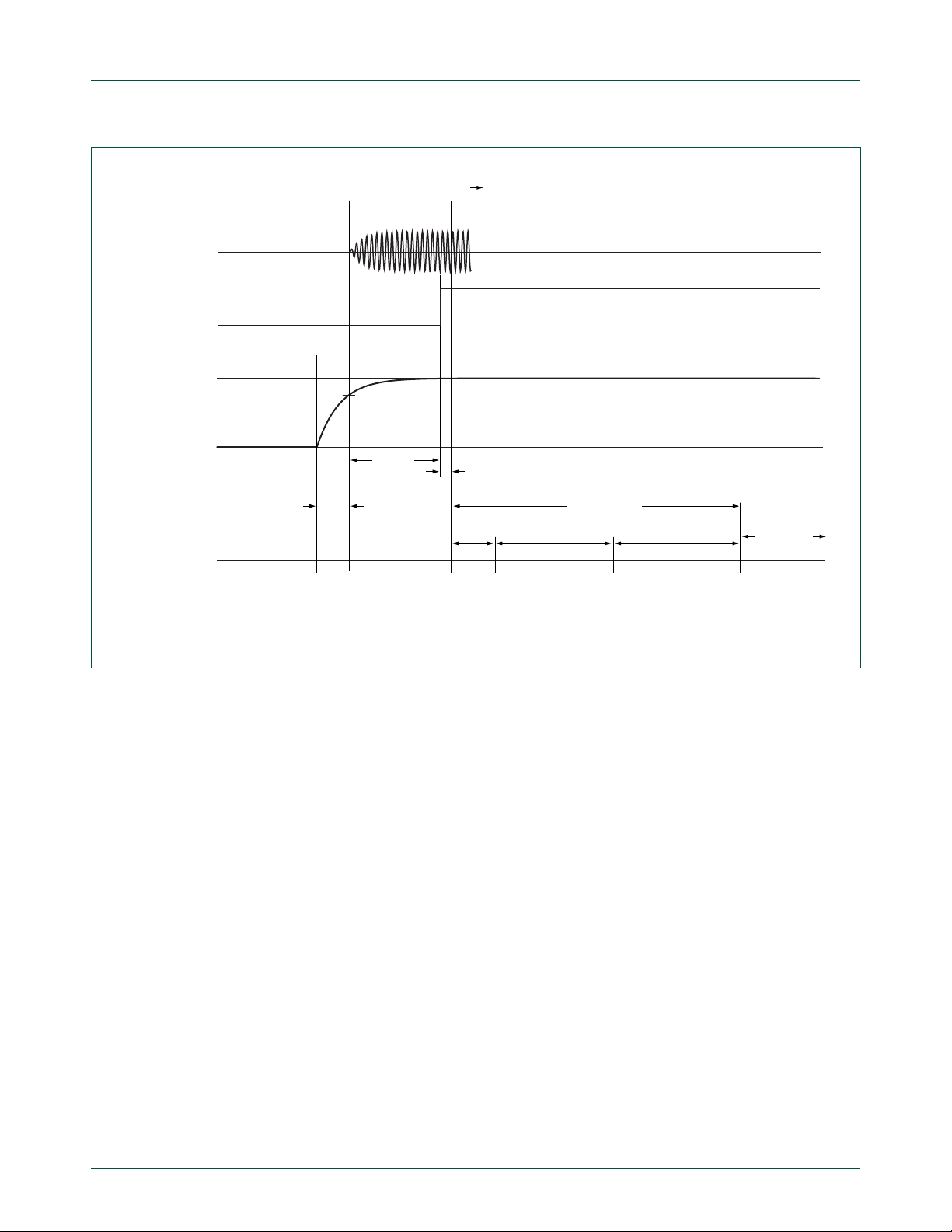

Figure 5

shows an example of the relationship between the RESET, the IRC, and the

processor status when the LPC17xx starts up after reset. See Section 4.3.2 “

oscillator” for start-up of the main oscillator if selected by the user code.

Main

Page 20

NXP Semiconductors

valid threshold

processor status

V

DD(REG)(3V3)

IRC status

RESET

GND

60 μs

1 μs; IRC stability count

boot time

user code

boot code

execution

finishes;

user code starts

flash read

starts

flash read

finishes

IRC

starts

IRC

stable

supply ramp-up

time

7 μs 181 μs 224 μs

UM10360

Chapter 3: LPC17xx System control

Fig 5. Example of start-up after reset

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 20 of 840

Page 21

NXP Semiconductors

3.4.1 Reset Source Identification Register (RSID - 0x400F C180)

This register contains one bit for each source of Reset. Writing a 1 to any of these bits

clears the corresponding read-side bit to 0. The interactions among the four sources are

described below.

Table 8. Reset Source Identification register (RSID - address 0x400F C180) bit description

Bit Symbol Description Reset

0 POR Assertion of the POR signal sets this bit, and clears all of the other bits in

1 EXTR Assertion of the RESET

2 WDTR This bit is set when the Watchdog Timer times out and the WDTRESET bit

3 BODR This bit is set when the V

31:4 - Reserved, user software should not write ones to reserved bits. The value

UM10360

Chapter 3: LPC17xx System control

this register. But if another Reset signal (e.g., External Reset) remains

asserted after the POR signal is negated, then its bit is set. This bit is not

affected by any of the other sources of Reset.

signal sets this bit. This bit is cleared only by

software or POR.

in the Watchdog Mode Register is 1. This bit is cleared only by software or

POR.

BOD reset trip level (typically 1.85 V under nominal room temperature

DD(REG)(3V3)

conditions).

If the V

DD(REG)(3V3)

voltage dips from the normal operating range to below

the BOD reset trip level and recovers, the BODR bit will be set to 1.

If the V

DD(REG)(3V3)

voltage dips from the normal operating range to below

the BOD reset trip level and continues to decline to the level at which POR

is asserted (nominally 1 V), the BODR bit is cleared.

If the V

DD(REG)(3V3)

voltage rises continuously from below 1 V to a level

above the BOD reset trip level, the BODR will be set to 1.

This bit is cleared only by software or POR.

Note: Only in the case where a reset occurs and the POR = 0, the BODR

bit indicates if the V

DD(REG)(3V3)

or not.

read from a reserved bit is not defined.

voltage reaches a level below the

voltage was below the BOD reset trip level

value

See

text

See

text

See

text

See

text

NA

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 21 of 840

Page 22

NXP Semiconductors

3.5 Brown-out detection

The LPC17xx includes a Brown-Out Detector (BOD) that provides 2-stage monitoring of

the voltage on the V

(typically 2.2 V under nominal room temperature conditions), the BOD asserts an interrupt

signal to the NVIC. This signal can be enabled for interrupt in the Interrupt Enable

Register in the NVIC in order to cause a CPU interrupt; if not, software can monitor the

signal by reading the Raw Interrupt Status Register.

The second stage of low-voltage d etection a sse rts Reset to inactivate the LPC17xx when

the voltage on the V

under nominal room temperature cond itio ns ). T his Rese t pre ve nts altera tio n of th e flas h

as operation of the various elements of the chip would otherwise become unreliable due

to low voltage. The BOD circuit maintains this reset down below 1 V, at which point the

Power-On Reset circuitry maintains the overall Reset.

Both the BOD reset interrupt level and the BOD reset trip level thresholds include some

hysteresis. In normal operation, this hysteresis allows the BOD reset interrupt level

detection to reliably interrupt, or a regularly-executed event loop to sense the condition.

DD(REG)(3V3)

DD(REG)(3V3)

UM10360

Chapter 3: LPC17xx System control

pins. If this voltage falls below the BOD interrupt trip level

pins falls below the BOD reset trip level (typically 1.85 V

But when Brown-Out Detection is enabled to bring the LPC17xx out of Power-down mode

(which is itself not a guaranteed operation -- see Section 4.8.7 “

register (PCON - 0x400F C0C0)”), the supply voltage may re cover from a transient b efore

the wake-up timer has completed its delay. In this case, the net result of the transient BOD

is that the part wakes up and continues operation after the instructions that set

Power-down mode, without any interrupt occurring and with the BOD bit in the RSID being

0. Since all other wake-up conditions have latching flags (see Section 3.6.2 “

Interrupt flag register (EXTINT - 0x400F C140)” and Section 27.6.2), a wake-up of this

type, without any apparent cause, can be assumed to be a Brown-Out that has gone

away.

Power Mode Control

External

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 22 of 840

Page 23

NXP Semiconductors

Interrupt flag

(one bit of EXTINT)

write to EXTINTi

internal reset

EINTi to wakeup timer

EINTi pin

EXTMODEi

PCLK

to interrupt

controller

EXTPOLARi

EINTi interrupt enable

PCLK

1

GLITCH

FILTER

APB read

of EXTINTi

Q

S

R

Q

S

R

Q

S

D

100621

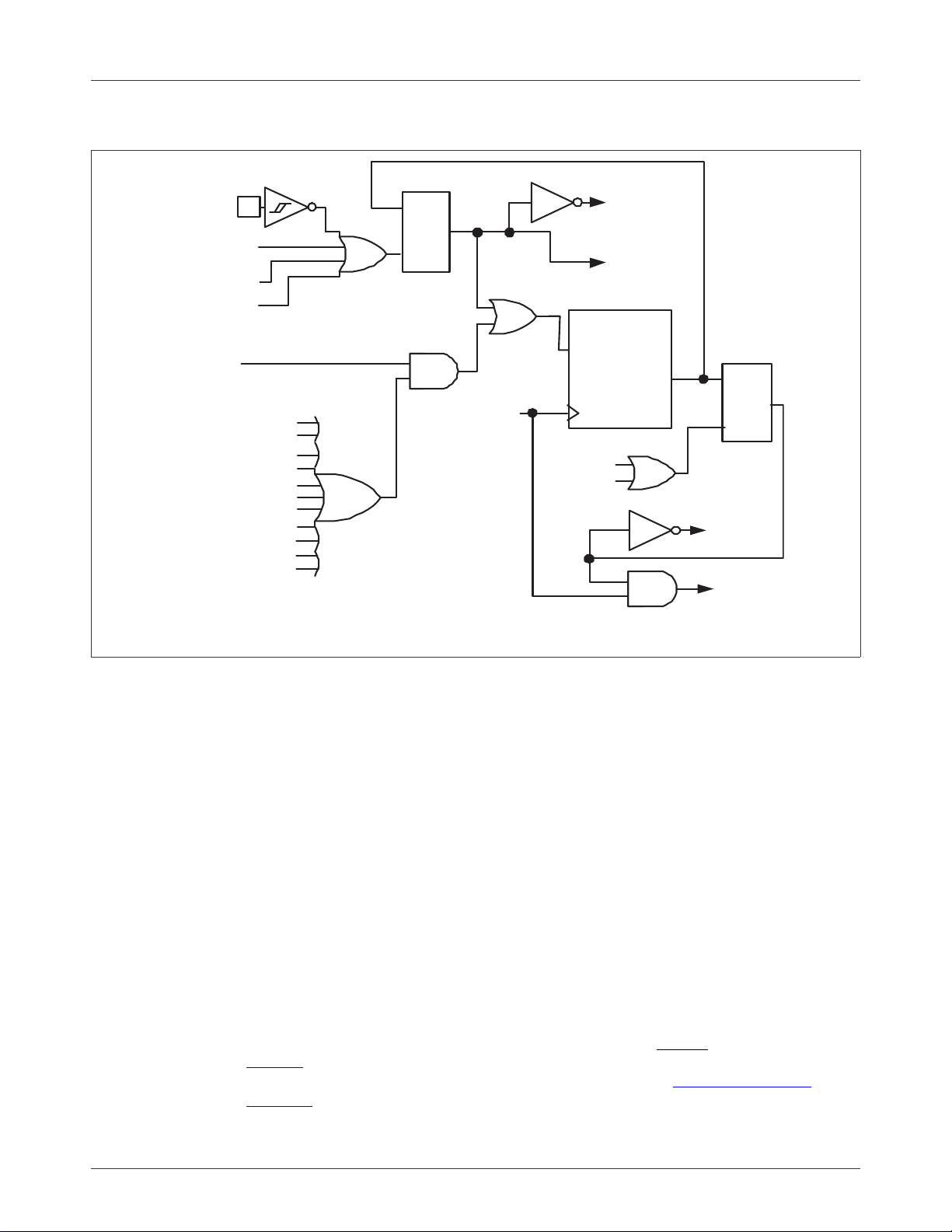

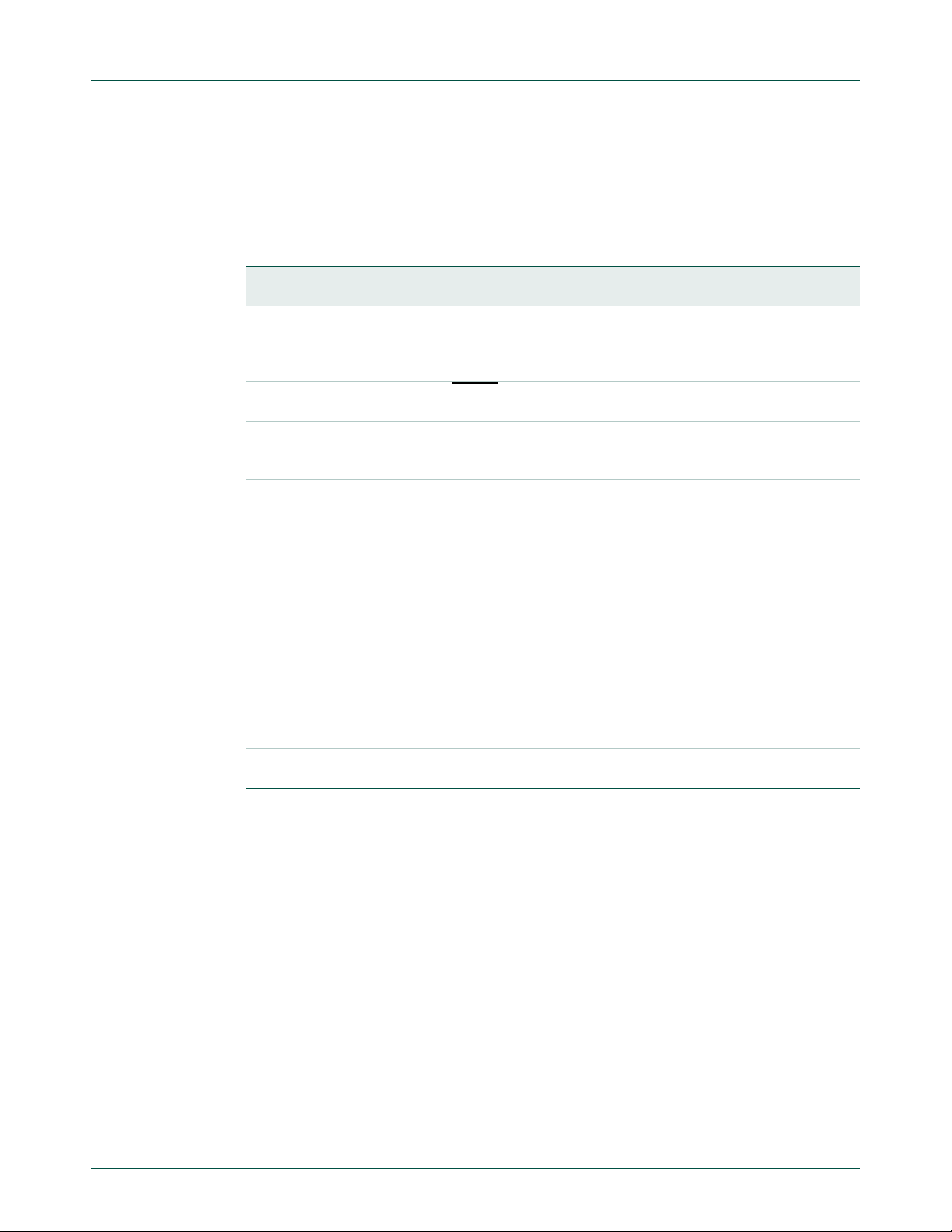

3.6 External interrupt inputs

TheLPC17xx includes four External Interrupt Inputs as selectable pin functions. The logic

of an individual external interrupt is r epresented in Figure 6

have the ability to wake up the CPU from Power-down mode. Refer to Section 4.8.8

“Wake-up from Reduced Power Modes” for details.

UM10360

Chapter 3: LPC17xx System control

. In addition, external interrupts

Fig 6. External interrupt logic

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 23 of 840

Page 24

NXP Semiconductors

3.6.1 Register description

The external interrupt function has four registers associated with it. The EXTINT register

contains the interrupt flags. The EXTMODE and EXTPOLAR registers specify the level

and edge sensitivity parameters.

Table 9. External Interrupt registers

Name Description Access Reset

EXTINT The External Interrupt Flag Register contains

EXTMODE The External Interrupt Mode Register controls

EXTPOLAR The External Interrupt Polarity Register controls

[1] Reset Value reflects the data stored in used bits only. It does not include reserved bits content.

Chapter 3: LPC17xx System control

interrupt flags for EINT0, EINT1, EINT2 and

EINT3. See Table 10

whether each pin is edge- or level-sensitive.

See Table 11

which level or edge on each pin will cause an

interrupt. See Table 12

.

.

.

UM10360

Address

[1]

value

R/W 0x00 0x400F C140

R/W 0x00 0x400F C148

R/W 0x00 0x400F C14C

3.6.2 External Interrupt flag register (EXTINT - 0x400F C140)

When a pin is selected for its external interrupt function, the level or edge on that pin

(selected by its bits in the EXTPOLAR a nd EXTMODE registers) will set its interrup t flag in

this register. This asserts the corresponding interrupt request to the NVIC, which will

cause an interrupt if interrupts from the pin are enabled.

Writing ones to bits EINT0 through EINT3 in EXTINT register clears the corresponding

bits. In level-sensitive mode the interrupt is cleared only when the pin is in its inactive

state.

Once a bit from EINT0 to EINT3 is set and an appropriate code st arts to execute (hand ling

wake-up and/or external interrupt), this bit in EXTINT register must be cleared. Otherwise

event that was just triggered by activity on the EINT pin will not be recognized in future.

Important: whenever a change of external interrupt operating mode (i.e. active

level/edge) is performed (including the initialization of an external interrupt), the

corresponding bit in the EXTINT register must be cleared! For details see

Section 3.6.3 “

Section 3.6.4 “

For example, if a system wakes up from Power-down using low level on external interrupt

0 pin, its post wake-up code must reset EINT0 bit in order to allow future entry into the

Power-down mode. If EINT0 bit is left set to 1, subsequent attempt(s) to invoke

Power-down mode will fail. The same goes for external interrupt handling.

External Interrupt Mode register (EXTMODE - 0x400F C148)” and

External Interrupt Polarity register (EXTPOLAR - 0x400F C14C)”.

More details on Power-down mode will be discussed in the following chapters.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 24 of 840

Page 25

NXP Semiconductors

Table 10. External Interrupt Flag reg ister (EXTINT - address 0x400F C140) bit description

Bit Symbol Description Reset

0 EINT0 In level-sensitive mode, this bit is set if the EINT0 function is selected for

1 EINT1 In level-sensitive mode, this bit is set if the EINT1 function is selected for

2 EINT2 In level-sensitive mode, this bit is set if the EINT2 function is selected for

3 EINT3 In level-sensitive mode, this bit is set if the EINT3 function is selected for

31:4 - Reserved, user software should not write ones to reserved bits. The value

UM10360

Chapter 3: LPC17xx System control

its pin, and the pin is in its active state. In edge-sensitive mode, this bit is

set if the EINT0 function is selected for its pin, and the selected edge

occurs on the pin.

This bit is cleared by writing a one to it, except in level sensitive mode

when the pin is in its active state.

its pin, and the pin is in its active state. In edge-sensitive mode, this bit is

set if the EINT1 function is selected for its pin, and the selected edge

occurs on the pin.

This bit is cleared by writing a one to it, except in level sensitive mode

when the pin is in its active state.

its pin, and the pin is in its active state. In edge-sensitive mode, this bit is

set if the EINT2 function is selected for its pin, and the selected edge

occurs on the pin.

This bit is cleared by writing a one to it, except in level sensitive mode

when the pin is in its active state.

its pin, and the pin is in its active state. In edge-sensitive mode, this bit is

set if the EINT3 function is selected for its pin, and the selected edge

occurs on the pin.

This bit is cleared by writing a one to it, except in level sensitive mode

when the pin is in its active state.

read from a reserved bit is not defined.

[1]

[1]

[1]

[1]

value

0

0

0

0

NA

[1] Example: e .g. if the EINTx is selected to be low level sensitive and low level is present on

corresponding pin, this bit can not be cleared; this bit can be cleared only when signa l on the

pin becomes high.

3.6.3 External Interrupt Mode register (EXTMODE - 0x400F C148)

The bits in this register select whether ea ch EINT pin is le vel- or edge- sensitive. Only pins

that are selected for the EINT function (see Section 8.5

NVIC register) can cause interrupts from the External Interr up t fun ction (tho ugh of co ur se

pins selected for other functions may cause interrupts from those functions).

Note: Software should only change a bit in this register when its interrupt is

disabled in the NVIC (state readable in the ISERn/ICERn registers), and sho uld write

the corresponding 1 to EXTINT before enabling (initializing) or re-enabling the

interrupt. An extraneous interrupt(s) could be set by changing the mode and not

having the EXTINT cleared.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 25 of 840

) and enabled in the appropriate

Page 26

NXP Semiconductors

Table 11. External Interrupt Mode register (EXTMODE - address 0x400F C148) bit

Bit Symbol Value Description Reset

0 EXTMODE0 0 Level-sensitivity is selected for EINT0.0

1 EXTMODE1 0 Level-sensitivity is selected for EINT1

2 EXTMODE2 0 Level-sensitivity is selected for EINT2

3 EXTMODE3 0 Level-sensitivity is selected for EINT3

31:4 - - Reserved, user software should not write ones to reserved

3.6.4 External Interrupt Polarity register (EXTPOLAR - 0x400F C14C)

In level-sensitive mode, the bits in this register select whether the corresponding pin is

high- or low-active. In edge-sensitive mode, they select whether the pin is rising- or

falling-edge sensitive. Only pins that are selected for the EINT function Only pins that are

selected for the EINT function (see Section 8.5

register) can cause interrupts from the External Interrupt function (though of course pins

selected for other functions may cause interrupts from those functions).

description

1EINT0

1EINT1

1EINT2

1EINT3

UM10360

Chapter 3: LPC17xx System control

value

is edge sensitive.

.0

is edge sensitive.

.0

is edge sensitive.

.0

is edge sensitive.

NA

bits. The value read from a reserved bit is not defined.

) and enabled in the appropriate NVIC

Note: Software should only change a bit in this register when its interrupt is

disabled in the NVIC (state readable in the ISERn/ICERn registers), and sho uld write

the corresponding 1 to EXTINT before enabling (initializing) or re-enabling the

interrupt. An extraneous interrupt(s) could be set by changing the polarity and not

having the EXTINT cleared.

Table 12. External Interrupt Polarity register (EXTPOLAR - address 0x400F C14C) bit

description

Bit Symbol Value Description Reset

value

0 EXTPOLAR0 0 EINT0 is low-active or falling-edge sensitive (depending on

EXTMODE0).

1 EINT0

1 EXTPOLAR1 0 EINT1

1 EINT1

2 EXTPOLAR2 0 EINT2

1 EINT2

is high-active or rising-edge sensitive (depending on

EXTMODE0).

is low-active or falling-edge sensitive (depending on

EXTMODE1).

is high-active or rising-edge sensitive (depending on

EXTMODE1).

is low-active or falling-edge sensitive (depending on

EXTMODE2).

is high-active or rising-edge sensitive (depending on

EXTMODE2).

0

0

0

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 26 of 840

Page 27

NXP Semiconductors

Table 12. External Interrupt Polarity register (EXTPOLAR - address 0x400F C14C) bit

Bit Symbol Value Description Reset

3 EXTPOLAR3 0 EINT3 is low-active or falling-edge sensitive (depending on

31:4 - - Reserved, user software should not write ones to reserved

description

1 EINT3

UM10360

Chapter 3: LPC17xx System control

value

0

EXTMODE3).

is high-active or rising-edge sensitive (depending on

EXTMODE3).

NA

bits. The value read from a reserved bit is not defined.

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 27 of 840

Page 28

NXP Semiconductors

3.7 Other system controls and status flags

Some aspects of controlling LPC17xx operation that do not fit into peripheral or other

registers are grouped here.

3.7.1 System Controls and Status register (SCS - 0x400F C1A0)

The SCS register contains several control/status bits related to the main oscillator. Since

chip operation always begins using the Internal RC Oscillator, and the main oscillator may

not be used at all in some applications, it will only be started by software request. This is

accomplished by setting the OSCEN bit in the SCS register , as described in Table 3-13.

The main oscillator provides a status flag (the OSCSTAT bit in the SCS register) so that

software can determine when the oscillator is running and stable. At that point, software

can control switching to the main oscillator as a clock source. Prior to starting the main

oscillator, a frequency range must be selected by configuring the

OSCRANGE bit in the SCS register.

T able 13. System Controls and Status register (SCS - address 0x400F C1A0) bit description

Bit Symbol Value Description Access Reset

3:0 - - Reserved. User software should not write ones to

reserved bits. The value read from a reserved bit is

not defined.

4 OSCRANGE Main oscillator range select. R/W 0

0 The frequency range of the main oscillator is 1 MHz

to 20 MHz.

1 The frequency range of the main oscillator is

15 MHz to 25 MHz.

5 OSCEN Main oscillator enable. R/W 0

0 The main oscillator is disabled.

1 The main oscillator is enabled, and will start up if

the correct external circuitry is connected to the

XT AL1 and XTAL2 pins.

6 OSCSTAT Main oscillator status. RO 0

0 The main oscillator is not ready to be used as a

clock source.

1 The main oscillator is ready to be used as a clock

source. The main oscillator must be enabled via the

OSCEN bit.

31:7 - - Reserved. User software should not write ones to

reserved bits. The value read from a reserved bit is

not defined.

UM10360

Chapter 3: LPC17xx System control

value

-NA

-NA

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 28 of 840

Page 29

`

USB

Clock

Divider

osc_clk

irc_osc

system clock select

CLKSRCSEL[1:0]

USB PLL settings

(PLL1...)

USB clock divider setting

USBCLKCFG[3:0]

PCLK_WDT

Peripheral

Clock

Divider

wd_clk

usb_clk

pclk1

pclk8

pclk4

pclk2

USB PLL

(PLL1)

main PLL

settings

(PLL0...)

USB PLL

select

(PLL1CON)

Main PLL

(PLL0)

CPU

Clock

Divider

pllclk

CPU PLL

select

(PLL0CON)

cclk

watchdog clock select

WDCLKSEL[1:0]

rtc_clk

CPU clock divider setting

CCLKCFG[7:0]

sysclk

UM10360

Chapter 4: LPC17xx Clocking and power control

Rev. 2 — 19 August 2010 User manual

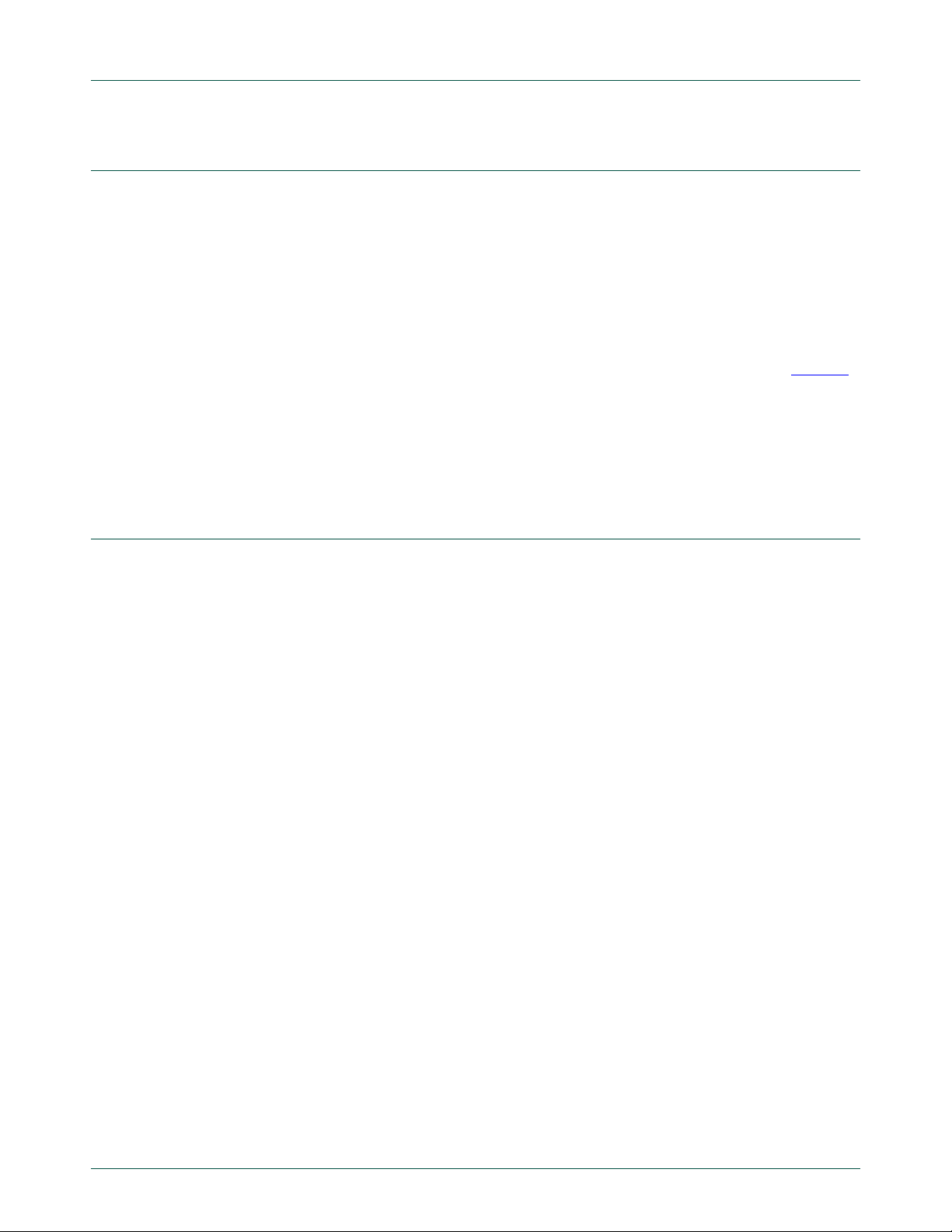

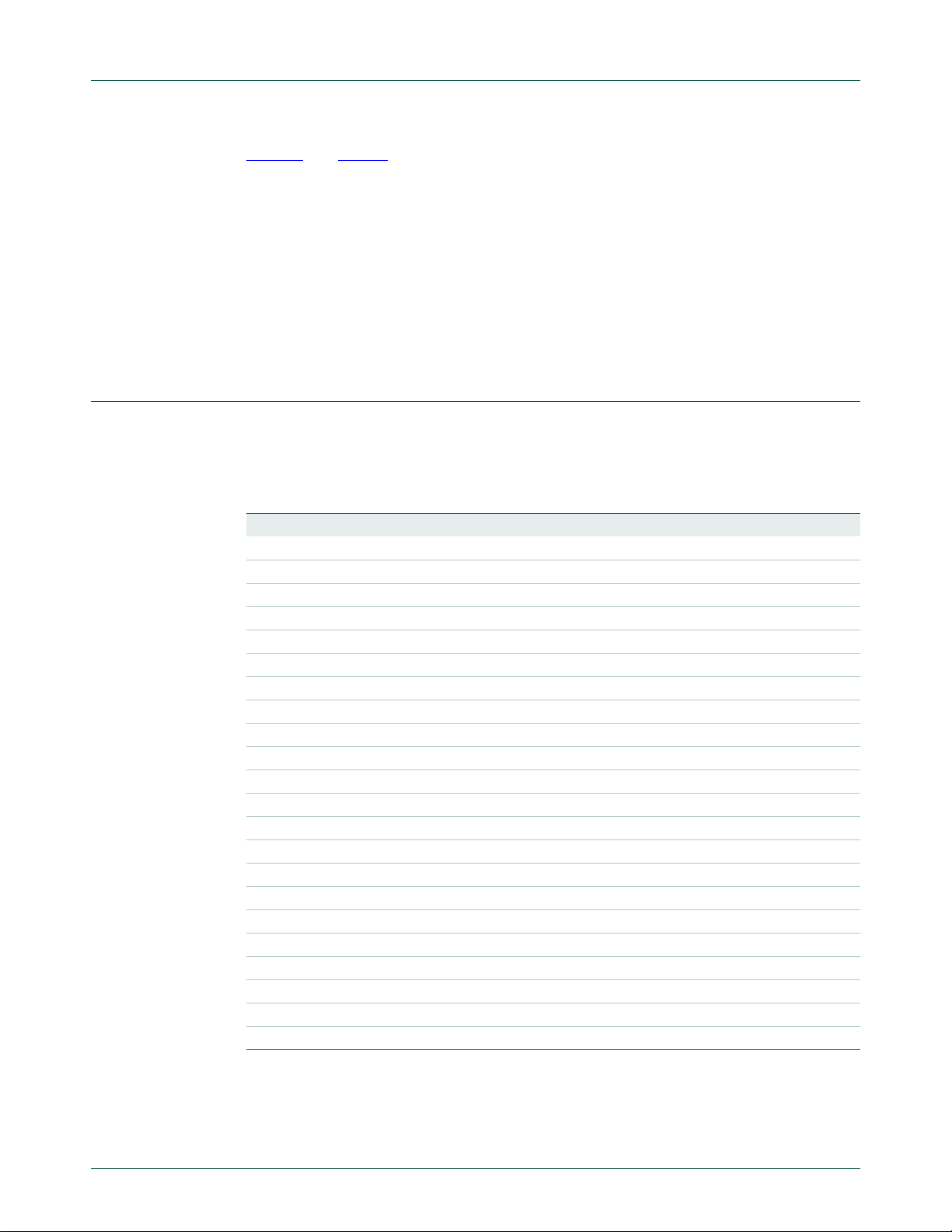

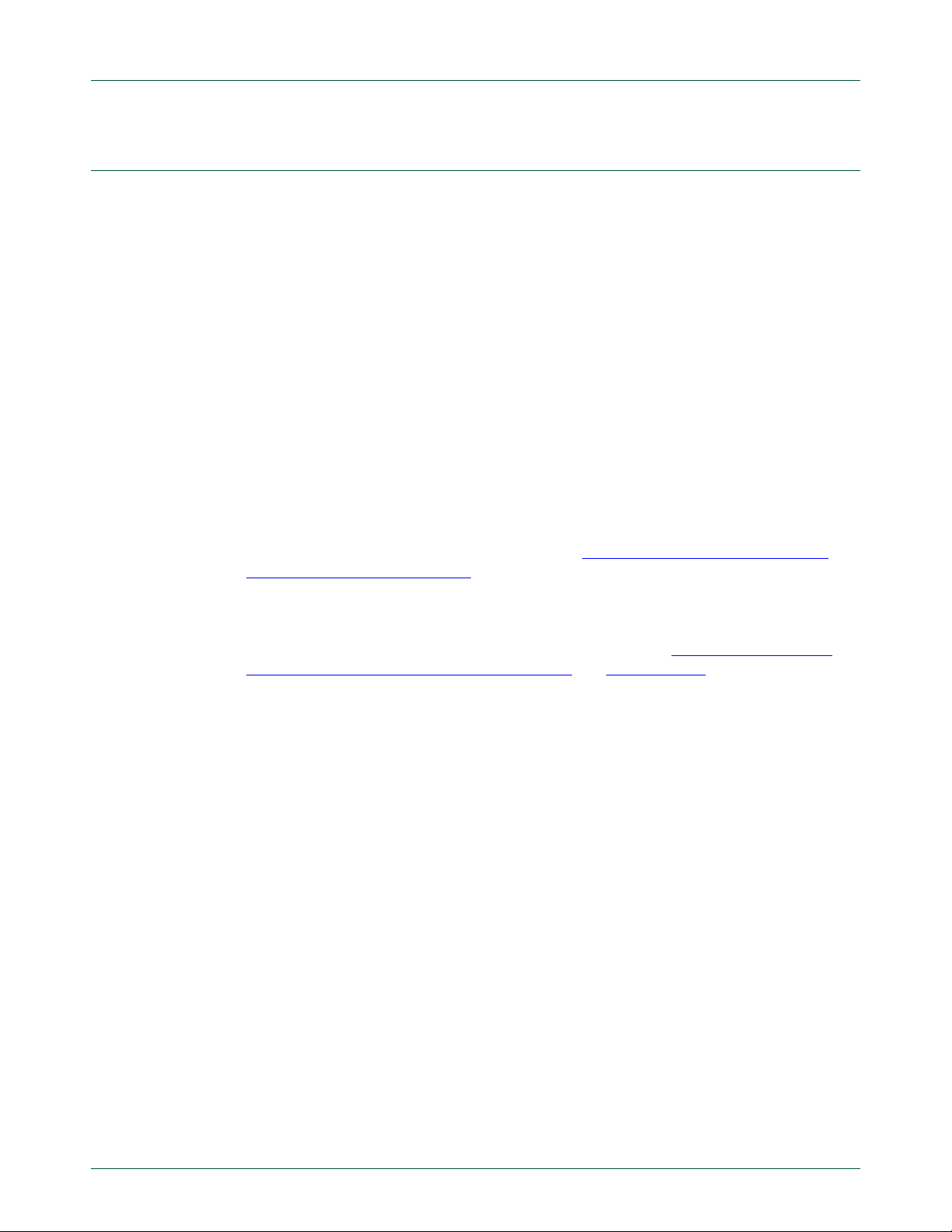

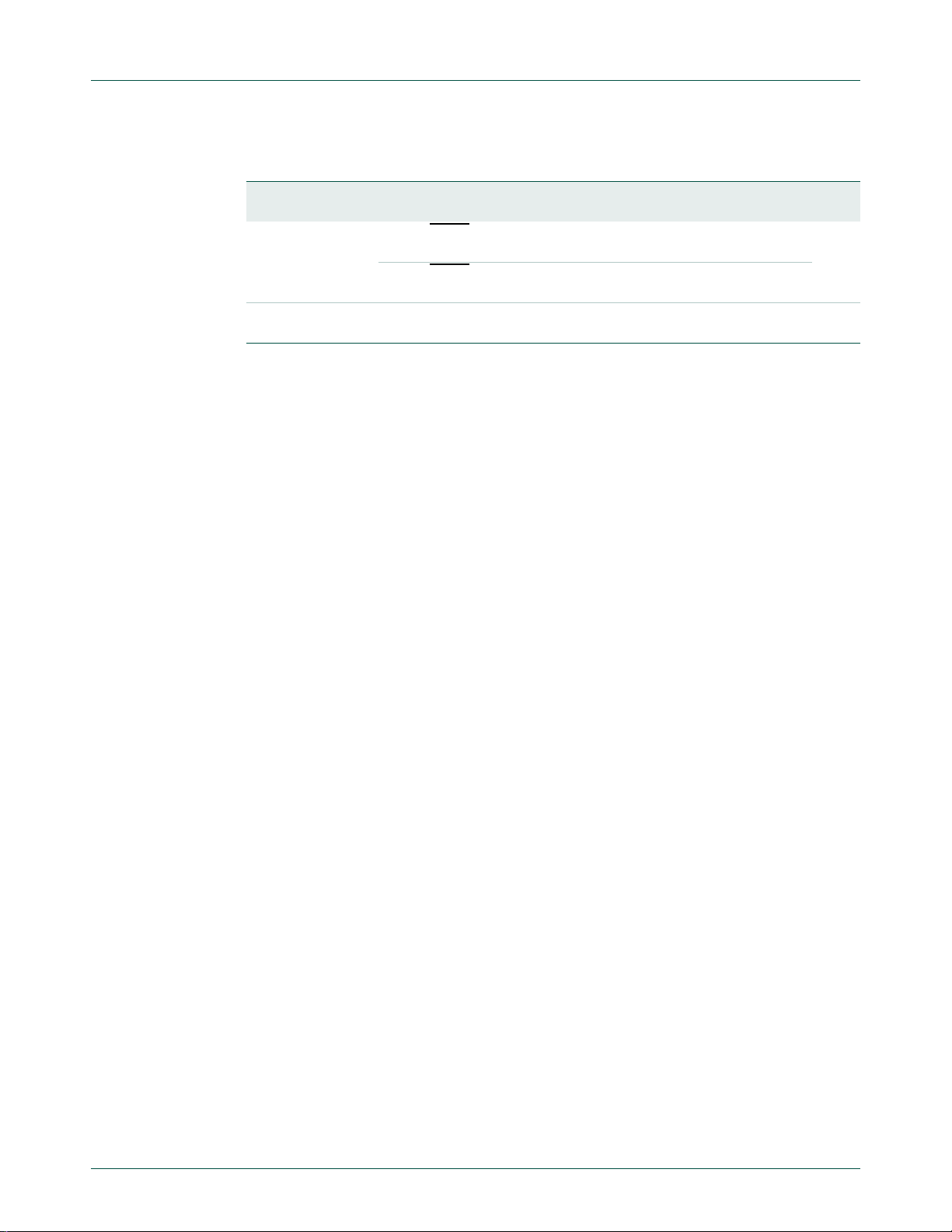

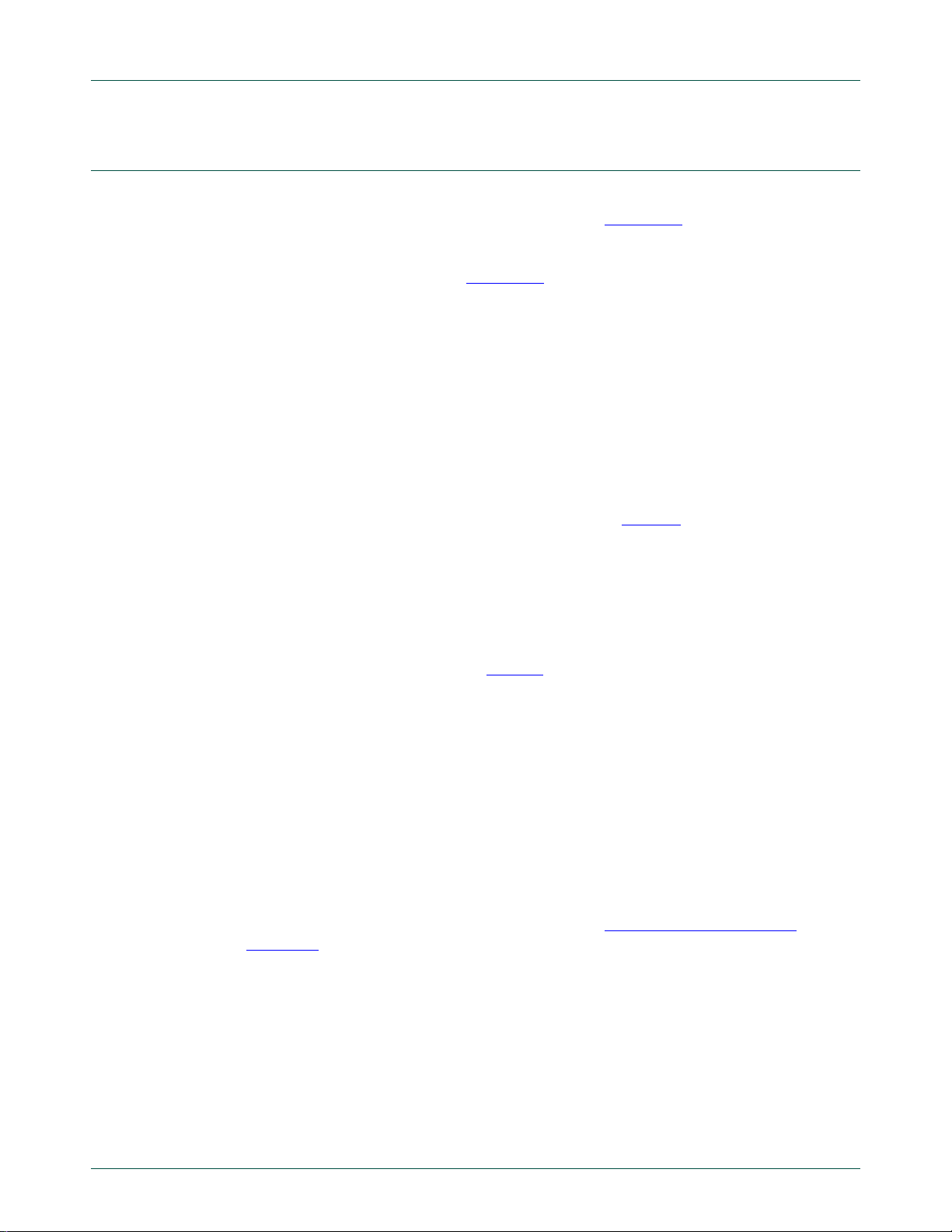

4.1 Summary of clocking and power control functions

This section describes the generation of the various clocks needed by the LPC17xx and

options of clock source selection, as well as power control and wake-up from reduced

power modes. Functions described in the following subsections include:

• Oscillators

• Clock source selection

• PLLs

• Clock dividers

• APB dividers

• Power control

• Wake-up timer

• External clock output

Fig 7. Clock generation for the LPC17xx

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 29 of 840

Page 30

NXP Semiconductors

4.2 Register description

All registers, regardless of size, are on word address boundaries. Details of the registers

appear in the description of each function.

T able 14. Summary of system control registers

Name Description Access Reset value Address

Clock source selection

CLKSRCSEL Clock Source Select Register R/W 0 0x400F C10C

Phase Locked Loop (PLL0, Main PLL)

PLL0CON PLL0 Control Register R/W 0 0x400F C080

PLL0CFG PLL0 Configuration Register R/W 0 0x400F C084

PLL0STAT PLL0 Status Register RO 0 0x400F C088

PLL0FEED PLL0 Feed Register WO NA 0x400F C08C

Phase Locked Loop (PLL1, USB PLL)

PLL1CON PLL1 Control Register R/W 0 0x400F C0A0

PLL1CFG PLL1 Configuration Register R/W 0 0x400F C0A4

PLL1STAT PLL1 Status Register RO 0 0x400F C0A8

PLL1FEED PLL1 Feed Register WO NA 0x400F C0AC

Clock dividers

CCLKCFG CPU Clock Configuration Register R/W 0 0x400F C104

USBCLKCFG USB Clock Configuration Register R/W 0 0x400F C108

PCLKSEL0 Peripheral Clock Selection register 0. R/W 0 0x400F C1A8

PCLKSEL1 Peripheral Clock Selection register 1. R/W 0 0x400F C1AC

Power control

PCON Power Control Register R/W 0 0x400F C0C0

PCONP Power Control for Peripherals Register R/W 0x03BE 0x400F C0C4

Utility

CLKOUTCFG Clock Output Configurat ion Register R/W 0 0x400F C1C8

UM10360

Chapter 4: LPC17xx Clocking and power control

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 30 of 840

Page 31

NXP Semiconductors

4.3 Oscillators

The LPC17xx includes three independent oscillators. These are the Main Oscillator, the

Internal RC Oscillator, and the RTC oscillator. Each oscillator can be used for more than

one purpose as required in a particular application. This can be seen in Figure 7

Following Reset, the LPC17xx will operate from the Internal RC Oscillator until switched

by software. This allows systems to operate without any external crystal, and allows the

boot loader code to operate at a known frequency.

4.3.1 Internal RC oscillator

The Internal RC Oscillator (IRC) may be used as the clock source for the watchdog timer,

and/or as the clock that drives PLL0 and subsequently the CPU. The precision of the IRC

does not allow for use of the USB interface, which requires a much more precise time

base in order to comply with the USB specification. Also, the IRC should not be used with

the CAN1/2 block if the CAN baud rate is higher than 100 kbit/s.The nominal IRC

frequency is 4 MHz.

Upon power-up or any chip reset, the LPC17xx uses the IRC as the clock source.

Software may later switch to one of the other available clock sources.

UM10360

Chapter 4: LPC17xx Clocking and power control

.

4.3.2 Main oscillator

The main oscillator can be used as the clock source for the CPU, with or without using

PLL0. The main oscillator operates at frequencies of 1 MHz to 25 MHz. This frequency

can be boosted to a higher frequency, up to the maximum CPU operating frequency, by

the Main PLL (PLL0). The oscillator output is called OSC_CLK. The clock selected as the

PLL0 input is PLLCLKIN and the ARM processor clock frequency is referred to as CCLK

for purposes of rate equations, etc. elsewh er e in th is doc ume nt. The frequencies of

PLLCLKIN and CCLK are the same value unless the PLL0 is active and connected. Refer

to Section 4.5 “

The on-board oscillator in the LPC17xx can operate in one of two modes: slave mode and

oscillation mode.

In slave mode the input clock signal should be coupled by means of a capacitor of 100 pF

in Figure 8, drawing a), with an amplitude between 200 mVrms and 1000 mVrms.

(C

C

This corresponds to a square wave signal with a signal swing of betwee n 280 mV and 1.4

V. The XTAL2 pin in this configuration can be left unconnected.

External components and models used in oscillation mode are shown in Figure 8

drawings b and c, and in Table 15

integrated on chip, only a crysta l and the cap acit ances C

externally in case of fundamental mode oscillation (the fundamental frequency is

represented by L, C

parallel package capacitance and should not be larger than 7 pF. Parameters F

and C

are supplied by the crystal manufacturer.

P

PLL0 (Phase Locked Loop 0)” for details.

,

and Table 16. Since the feedback resistance is

and CX2 need to be connected

X1

and RS). Capacitance CP in Figure 8, drawing c, represents the

L

, CL, RS

C

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 31 of 840

Page 32

NXP Semiconductors

LPC17xx LPC17xx

Clock

C

C

C

X1

C

X2

C

L

C

P

L

R

S

< = >

a) b) c)

Xtal

XTAL1 XTAL2

XTAL1 XTAL2

UM10360

Chapter 4: LPC17xx Clocking and power control

Fig 8. Oscillator modes and models: a) slave mode of operation, b) oscillation mode of operation, c) external

crystal model used for CX1/X2 evaluation

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 32 of 840

T able 15. Recommended values for C

in oscillation mode (crystal and external

X1/X2

components parameters) low frequency mode (OSCRANGE = 0, see Table 13)

Fundamental oscillation

frequency F

OSC

Crystal load

capacitance C

Maximum crystal

series resistance R

L

External load

capacitors CX1,

S

CX2

1 MHz - 5 MHz 10 pF < 300 Ω 18 pF, 18 pF

20 pF < 300

30 pF < 300

5 MHz - 10 MHz 10 pF < 300

20 pF < 200

30 pF < 100

10 MHz - 15 MHz 10 pF < 160

20 pF < 60

15 MHz - 20 MHz 10 pF < 80

T able 16. Recommended values for C

in oscillation mode (crystal and external

X1/X2

components parameters) high frequency mode (OSCRANGE = 1, see Table 13

Fundamental oscillation

frequency F

OSC

Crystal load

capacitance C

L

Ω 39 pF, 39 pF

Ω 57 pF, 57 pF

Ω 18 pF, 18 pF

Ω 39 pF, 39 pF

Ω 57 pF, 57 pF

Ω 18 pF, 18 pF

Ω 39 pF, 39 pF

Ω 18 pF, 18 pF

Maximum crystal

series resistance R

External load

capacitors C

S

)

X1, CX2

15 MHz - 20 MHz 10 pF < 180 Ω 18 pF, 18 pF

20 pF < 100

20 MHz - 25 MHz 10 pF < 160

20 pF < 80

Since chip operation always begins using the Internal RC Oscillator, and the main

oscillator may not be used at all in some applications, it will only be started by software

request. This is accomplished by setting the OSCEN bit in the SCS register, as described

in Table 13

register) so that software can determine when the oscillator is running and stable. At that

. The main oscillator provides a status flag (the OSCSTAT bit in the SCS

Ω 39 pF, 39 pF

Ω 18 pF, 18 pF

Ω 39 pF, 39 pF

Page 33

NXP Semiconductors

point, software can control switching to the main oscillator as a clock source. Prior to

starting the main oscillator, a frequency range must be selected by configuring the

OSCRANGE bit in the SCS register.

4.3.3 RTC oscillator

The RTC oscillator provides a 1 Hz clock to the RTC and a 32 kHz clock output that can

be used as the clock source for PLL0 and CPU and/or the watchdog timer.

Remark: The RTC oscillator must not be used as a clock source when the PLL0 output is

selected to drive the USB controller. In this case select the main oscillator as clock source

for PLL0 (see also Table 17

UM10360

Chapter 4: LPC17xx Clocking and power control

).

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 33 of 840

Page 34

NXP Semiconductors

4.4 Clock source selection multiplexer

Several clock sources may be chosen to drive PLL0 and ultimately the CPU and on-chip

peripheral devices. The clock sources available are the main oscillator, the RTC oscillator,

and the Internal RC oscillator.

The clock source selection can only be changed safely when PLL0 is not connected . For a

detailed description of how to change the clock source in a system using PLL0 see

Section 4.5.13 “

Note the following restrictions regarding the choice of clock sources:

• Only the main oscillator must be used (via PLL0) as the clock source for the USB

subsystem. The IRC or RTC oscillators do not provide the proper tolerances for this

use.

• The IRC oscillator should not be used (via PLL0) as the clock source for the CAN

controllers if the CAN baud rate is higher than 100 kbit/s.

4.4.1 Clock Source Select register (CLKSRCSEL - 0x400F C10C)

PLL0 setup sequence”.

UM10360

Chapter 4: LPC17xx Clocking and power control

The CLKSRCSEL register contains the bits that sel e ct the clock source for PLL0.

Table 17. Clock Source Select register (CLKSRCSEL - address 0x400F C10C) bit

description

Bit Symbol Value Description Reset

value

1:0 CLKSRC Selects the clock source for PLL0 as follows: 0

00 Selects the Internal RC oscillator as the PLL0 clock source

(default).

01 Selects the main oscillator as the PLL0 clock source.

Remark: Select the main oscillator as PLL0 clock source if the

PLL0 clock output is used for USB or for CAN with baudrates

> 100 kBit/s.

10 Selects the RTC oscillator as the PLL0 clock source.

1 1 Reserved, do not use this setting.

Warning: Improper setting of this value, or an incorrect sequence of

changing this value may result in incorrect operation of the device.

31:2 - 0 Reserved, user software should not write ones to reserved bits.

The value read from a reserved bit is not defined.

NA

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 34 of 840

Page 35

NXP Semiconductors

4.5 PLL0 (Phase Locked Loop 0)

PLL0 accepts an input clock frequency in the range of 32 kHz to 50 MHz. The clock

source is selected in the CLKSRCSEL register (see Section 4.4

multiplied up to a high frequency, then divided down to provide the actual clock used by

the CPU, peripherals, and optionally the USB subsystem. Note that the USB subsystem

has its own dedicated PLL (see Section 4.6

maximum allowed for the CPU, which is 120 MHz on high speed versions (LPC1769 and

LPC1759), and 100 MHz on other versions.

4.5.1 PLL0 operation

The PLL input, in the range of 32 kHZ to 50 MHz, may initially be divided down by a value

"N", which may be in the range of 1 to 256. This input division provides a greater number

of possibilities in providing a wide range of output frequencies from the same input

frequency.

Following the PLL input divider is the PLL multiplier. This can multiply the input divider

output through the use of a Current Controlled Oscillator (CCO) by a value "M", in the

range of 6 through 512, plus additional values listed in Table 21

must be in the range of 275 MHz to 550 MHz. The multiplier works by dividing the CCO

output by the value of M, then using a phase-frequency detector to compare the divided

CCO output to the multiplier input. The error value is used to adjust the CCO frequency.

UM10360

Chapter 4: LPC17xx Clocking and power control

). The input frequency is

). PLL0 can produce a clock up to the

. The resulting frequency

There are additional dividers at the output of PLL0 to bring the frequency down to what is

needed for the CPU, peripherals, and potentially the USB subsystem. PLL0 output

dividers are described in the Clock Dividers section following the PLL0 description. A

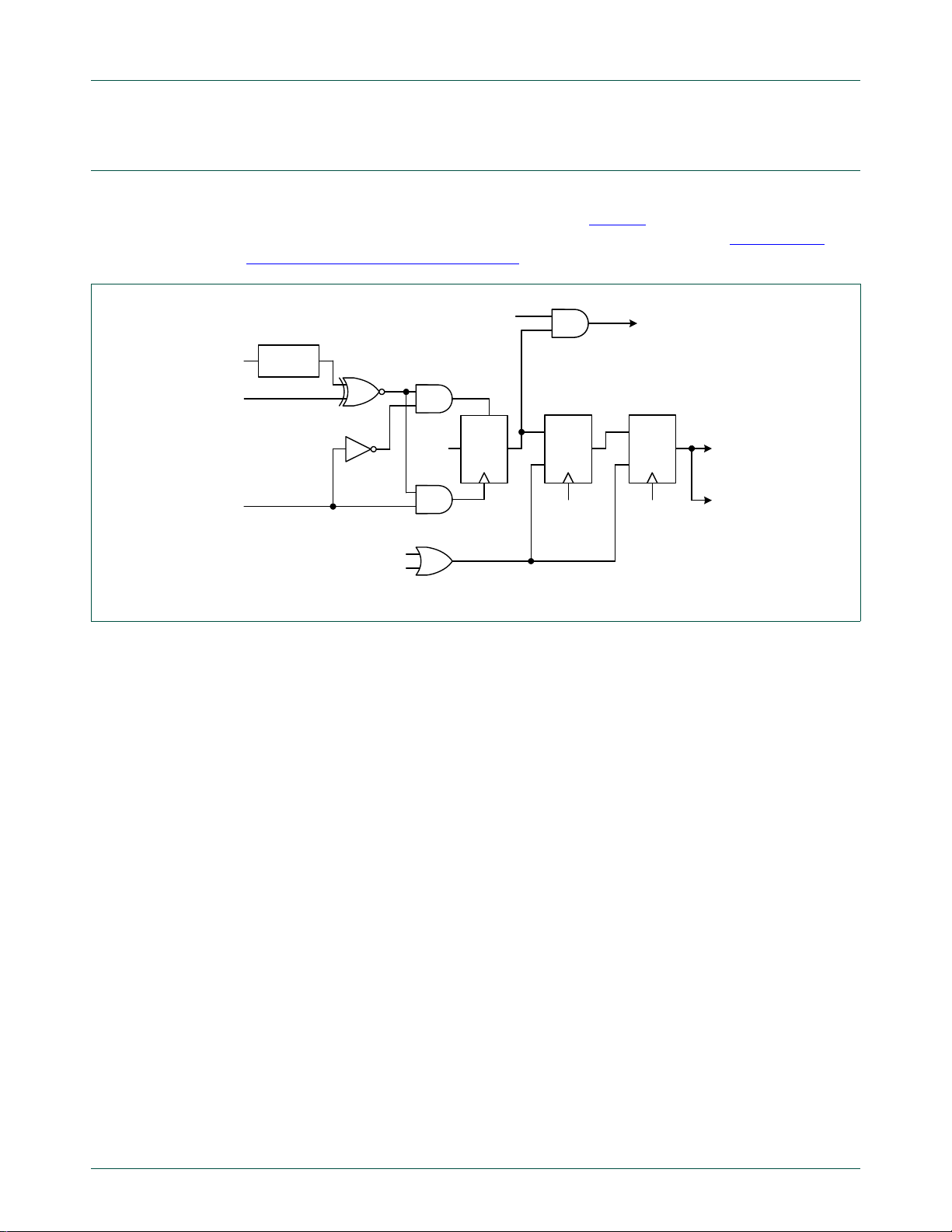

block diagram of PLL0 is shown in Figure 9

PLL activation is controlled via the PLL0CON register. PLL0 multiplier and divider values

are controlled by the PLL0CFG register. These two registers are protected in order to

prevent accidental alteration of PLL0 parameters or dea ctivation of the PLL. Since all chip

operations, including the Watchdog Timer, could be dependent on PLL0 if so configured

(for example when it is providing the chip clock), accidental changes to the PLL0 setup

values could result in unexpected or fatal behavior of the microcontroller. The protection is

accomplished by a feed sequence similar to that of the Watchdog Timer. Details are

provided in the description of the PLL0FEED register.

PLL0 is turned off and bypassed following a chip Reset and by entering Power-down

mode. PLL0 must be configured, enabled, and connected to the system by software.

It is important that the setup procedure described in Section 4.5.13 “

sequence” is followed or PLL0 might not operate at all!

4.5.1.1 PLL0 and startup/boot code interaction

When there is no valid user code (determined by the checksum word) in the user flash or

the ISP enable pin (P2.10) is pulled low on startup, the ISP mode will be entered and the

boot code will setup the PLL with the IRC. Therefore it can not be assumed that the PLL is

disabled when the user opens a debug session to debug the application code. The user

startup code must follow the steps describe d in this chapter to disconnect the PLL.

PLL0 setup

UM10360 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2010. All rights reserved.

User manual Rev. 2 — 19 August 2010 35 of 840

Page 36

NXP Semiconductors

N-DIVIDER

M-DIVIDER

NSEL

[7:0]

PHASE-

FREQUENCY

DETECTOR

FILTER CCO

/2

MSEL

[14:0]

PLOCK

PLLE

PLLC

pd

refclk

pllclkin

pllclk

4.5.2 PLL0 register description

PLL0 is controlled by the registers shown in Table 18. More detailed descriptions follow.

Warning: Improper setting of PLL0 values may result in incorrect operation of the

device!

Table 18. PLL0 registers

Name Description Access Reset

PLL0CON PLL0 Control Register. Holding register for

PLL0CFG PLL0 Configuration Register. Holding register for

PLL0STAT PLL0 Status Register. Read-back register for

PLL0FEED PLL0 Feed Register. This register enables

Chapter 4: LPC17xx Clocking and power control

updating PLL0 control bits. Values written to this

register do not take effect un ti l a valid PL L0 fee d

sequence has taken place.

updating PLL0 configuration values. Values

written to this register do not take effect until a

valid PLL0 feed sequence has taken place.

PLL0 control and configuration information. If