Page 1

NXP Semiconductors

IMXRT500EC

Data Sheet: Technical Data Rev. 0, 02/2021

i.MX RT500 Low-Power

Crossover Processor

The i.MX RT500 is a family of dual-core microcontrollers for

embedded applications featuring an Arm Cortex-M33 CPU

combined with a Cadence® Xtensa® Fusion F1 Audio Digital

Signal Processor CPU. The Cortex-M33 includes two hardware

coprocessors providing enhanced performance for an array of

complex algorithms along with a 2D Vector GPU with LCD

Interface and MIPI DSI PHY. The family offers a rich set of

peripherals and very low power consumption. The device has up

to 5 MB SRAM, two FlexSPIs (Octal/Quad SPI Interfaces) each

with 32 KB cache, one with dynamic decryption, high-speed USB

device/host + PHY, 12-bit 1 MS/s ADC, Analog Comparator,

Audio subsystems supporting up to 8 DMIC channels, 2D GPU

and LCD Controller with MIPI DSI PHY, SDIO/eMMC; FlexIO;

AES/SHA/Crypto M33 coprocessor and PUF key generation

Control processor core

• Arm Cortex-M33 processor, running at frequencies of

up to 200 MHz

• Arm TrustZone

• Arm Cortex-M33 built-in Memory Protection Unit (MPU)

supporting eight regions

• Single-precision Hardware Floating Point Unit (FPU).

• Arm Cortex-M33 built-in Nested Vectored Interrupt

Controller (NVIC).

• Non-maskable Interrupt (NMI) input.

• Two coprocessors for the Cortex-M33: a hardware

accelerator for fixed and floating point DSP functions

(PowerQuad) and a Crypto/FFT engine (Casper). The

DSP coprocessor uses a bank of four dedicated 2 KB

SRAMs. The Crypto/FFT engine uses a bank of two 2

KB SRAMs that are also AHB accessible by the CPU

and the DMA engine.

• Serial Wire Debug with eight break points, four watch

points, and a debug timestamp counter. It includes

Serial Wire Output (SWO) trace and ETM trace.

• Cortex-M33 System tick timer

DSP processor core

• Cadence Tensilica Fusion F1 DSP processor, running

at frequencies of up to 200 MHz.

• Hardware Floating Point Unit.

• Serial Wire Debug (shared with Cortex-M33 Control

Domain CPU).

Communication interface

• 9 configurable universal serial interface modules

(Flexcomm Interfaces). Each module contains an

integrated FIFO and DMA support. Each of the nine

modules can be configured as:

• Two additional high-speed SPI interfaces supporting

50 MHz operation

• One additional I2C interface with open-drain pads

• Two I3C bus interfaces

• A digital microphone interface supporting up to 8

channels with associated decimators and Voice

MIMXRT5XXSFFOC

MIMXRT5XXSFFOCR

MIMXRT5XXSFAWCR

249 FOWLP 7.0mm x

7.0mm x 0.725mm,

0.4mm pitch

• A USART with dedicated fractional baud rate

generation and flow-control handshaking

signals. The USART can optionally be clocked

at 32 kHz and operated when the chip is in

reduced power mode, using either the 32 kHz

clock or an externally supplied clock. The

USART also provides partial support for

LIN2.2.

• An I2C-bus interface with multiple address

recognition, and a monitor mode. It supports

400 Kb/sec Fast-mode and 1 Mb/sec Fastmode Plus. It also supports 3.4 Mb/sec highspeed when operating in slave mode.

• An SPI interface.

• An I2S (Inter-IC Sound) interface for digital

audio input or output. Each I2S supports up to

four channel-pairs.

141 WLCSP 4.525mm

x 4.525mm x 0.49mm,

0.35mm pitch

NXP reserves the right to change the production detail specifications as may be

required to permit improvements in the design of its products.

Page 2

Five I/O Power Rails

• Five independent supplies powering different clusters

of pins to permit interfacing directly to off-chip

peripherals operating at different supply levels.

On-chip memory

• Up to 5 MB of system SRAM accessible by both CPUs,

both DMA engines, the Graphics Subsystem and all

other AHB masters.

• Additional SRAMs for USB traffic (16 KB), Cortex-M33

co-processors (4 x 2 KB), SDIO FIFOs (2 x 512 B dualport), PUF secure key generation (2 KB), FlexSPI

caches (32 KB each), SmartDMA commands (32 KB),

and a variety of dual and single port RAMs for

graphics.

• 16 kbits OTP fuses

• Up to 192 KB ROM memory for factory-programmed

drivers and APIs

• System boot from High-speed SPI, FlexSPI Flash, HS

USB, I2C, UART or eMMC via on-chip bootloader

software included in ROM. FlexSPI boot mode will

include an option for Execute-in-place start-up for nonsecure boot.

Digital peripherals

• Two general purpose DMA engines, each with 37

channels and up to 27 programmable request/trigger

sources.

• Can be configured such that one DMA is secure

and the other non-secure and/or one can be

designated for use by the M33 CPU and the

other by the DSP

• Smart DMA Controller with dedicated 32KB code RAM

• USB high-speed host/device controller with on-chip

PHY and dedicated DMA controller.

• Two FlexSPI (Octal/Quad) Interfaces up to 200 MHz

DDR/SDR (target). 32 KB caches with selectable

cache policies based on programmable address

regions. One of the FlexSPI interface will include onthe-fly decryption for execute-in-place and addressremapping to support dual-image boot. DMA supported

(both modules).

• Two SD/eMMC memory card interfaces with dedicated

DMA controllers. One supports eMMC 5.0 with

HS400/DDR operation.

Analog peripherals

• One 12-bit ADC with sampling rates of 1 Msamples/sec

and an enhanced ADC controller. It supports up to 10

single-ended channels or 5 differential channels. The

ADC supports DMA.

• Temperature sensor.

• Analog comparator

Activation Detect. One pair of channels can be

streamed directly to I2S. The DMIC supports DMA.

Timers

• One 32-bit SCTimer/PWM module (SCT). Multipurpose timer with extensive event-generation,

match/compare, and complex PWM and output

control features.

• 10 general-purpose/PWM outputs, 8 generalpurpose inputs

• It supports DMA and can trigger external DMA

events

• It supports fractional match values for high

resolution

• Five general purpose, 32-bit timer/counter modules

with PWM capability

• 24-bit multi-rate timer module with 4 channels each

capable of generating repetitive interrupts at

different, programmable frequencies.

• Two Windowed Watchdog Timers (WDT) with

dedicated watchdog oscillator (1 MHz LPOSC)

• Frequency measurement module to determine the

frequency of a selection of on-chip or off-chip clock

sources.

• Real-Time Clock (RTC) with independent power

supply and dedicated oscillator. Integrated wake-up

timer can be used to wake the device up from lowpower modes. The RTC resides in the “always-on”

voltage domain. RTC includes eight 32-bit generalpurpose registers which can retain contents when

power is removed from the rest of the chip.

• Ultra-low power micro-tick Timer running from the

Watchdog oscillator with capture capability for

timestamping. Can be used to wake up the device

from low-power modes.

• 64-bit OS/Event Timer common to both processors

with individual match/capture and interrupt

generation logic. Enabled on POR

Clocks

• Crystal oscillator with an operating range of 4 MHz

to 26 MHz.

• Dual trim option: Internal 192/96 MHz FRO

oscillator. Trimmed to 1% accuracy.

• FRO capable of being tuned using an accurate

reference clock (eg. XTAL Osc) to 0.1% accuracy

with 46% duty cycle to support MIPI PHY and

FlexSPI.

• Internal 1 MHz low-power oscillator with 5%

accuracy. Serves as the watchdog oscillator and

clock for the OS/Event Timer and the Systick among

others. Also available as the system clock to both

domains.

• 32 kHz real-time clock (RTC) oscillator that can

optionally be used as a system clock.

• Main System PLL:

• allows CPU operation up to the maximum rate

without the need for a high-frequency crystal.

2

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 3

Graphics/Multimedia

• 2D Vector Graphics Processing Unit, running at

frequencies of up to 200 MHz.

• LCD Display Interface supporting smart LCD displays

and video mode.

• MIPI DSI Interface with on-chip PHY supporting

transfer rates up to 895.1 Mbps.

• FlexIO can be configured to provide a parallel interface

to an LCD

I/O Peripherals

• Up to 136 general purpose I/O (GPIO) pins with

configurable pull-up/pull-down resistors. Ports can be

written as words, half-words, bytes, or bits.

• Mirrored, secure GPIO0.

• Individual GPIO pins can be used as edge and level

sensitive interrupt sources, each with its own interrupt

vector.

• All GPIO pins can contribute to one of two ganged

(OR’d) interrupts from the GPIO_HS module.

• A group of up to 7 GPIO pins (from Port0/1) can be

selected for Boolean pattern matching which can

generate interrupts and/or drive a “pattern-match”

output.

• Adjustable output driver slew rates.

• JTAG boundary scan

Security

• Secure Isolation: Protection from software and remote

attacks using Trustzone for armV8M. Hardware

isolation of AES keys

• Secure Boot: firmware in ROM providing immutable

root of trust

• Secure Storage: Physically Unclonable Function

(PUF) based key store, On-the-fly-AES decryption

(OTFAD) of off-chip flash for code storage

• Secure Debug: Certificate based debug authentication

mechanism

• Secure Loader: Supports firmware update mechanism

with authenticity (RSA signed) and confidentiality

(AES-CTR encrypted) protection

• Secure Identity: 128-bit Universal Unique Identifier

(UUID), 256-bit Compound Device Identifier (CDI) per

TCG DICE specification

Cryptographic Accelerators

•

• Symmetric cryptography (AES) with

128/192/256-bit key strength and protection

against Side-channel analysis (Differential Power

Analysis and Template attacks)

• Asymmetric cryptography acceleration using

CASPER co-processor

• NIST SP 800-90b compliant TRNG design with

512-bit output per call

• Hash engine with SHA-256 and SHA1

May be run from the FRO, the crystal

oscillator or the CLKIN pin.

• a second, independent PLL output provides

alternate high-frequency clock source for the

DSP CPU if the required frequency is different

from the main system clock. (Note: 2nd PFD

output from Main System PLL)

• two additional PLL outputs provide potential

clock sources to various peripherals.

• Audio PLL for the audio subsystem.

Power Control

• Main external power supply: 1.8V ± 5%

• Vddcore supply (from PMIC or internal PMU):

adjustable from 0.6 V to 1.1 V (including retention

mode)

• Analog supply: 1.71-3.6 V

• Five VDDIO supplies (can be shared or

independent): 1.71 - 3.6 V

• USB Supply: 3.0-3.6 V

• Reduced power modes:

• Sleep mode: CPU clock shut down (each CPU

independently)

• Deep_sleep mode: User-selectable

configuration via PDSLEEPCFG

• Deep_powerdown mode: Internal power

removed from entire chip except “always-on”

domain

• Each individual SRAM partition can be

independently powered-off or put into a lowpower retain mode

• DSP Domain can be powered-off

independently from the rest of the system.

• Ability to operate the synchronous serial

interfaces in sleep or deep-sleep as a slave or

USART clocked by the 32 kHz RTC oscillator

• Wake-up from low-power modes via interrupts

from various peripherals including the RTC

and the OS/Event timer

• RBB/FBB to provide additional control over power/

performance trade-offs

• Power-On Reset (POR).

Operating characteristics

• Temperature range (ambient): -20 °C to +70 °C

• VDDCORE: 0.7 V - 1.155 V

• VDDIO_0/1/2/4: 1.71 V - 1.89 V

• VDDIO_3: 1.71 V - 3.6 V

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

3

NXP Semiconductors

Page 4

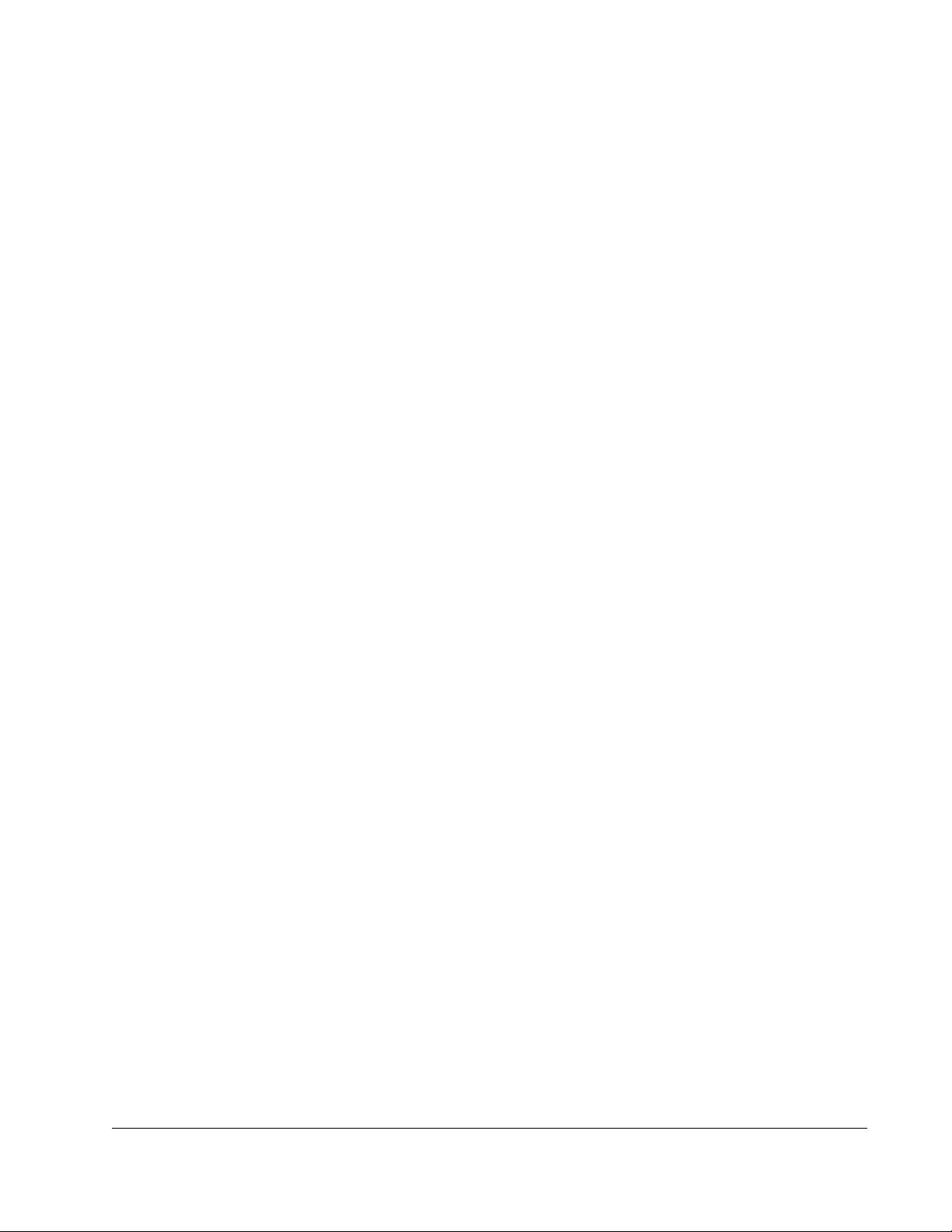

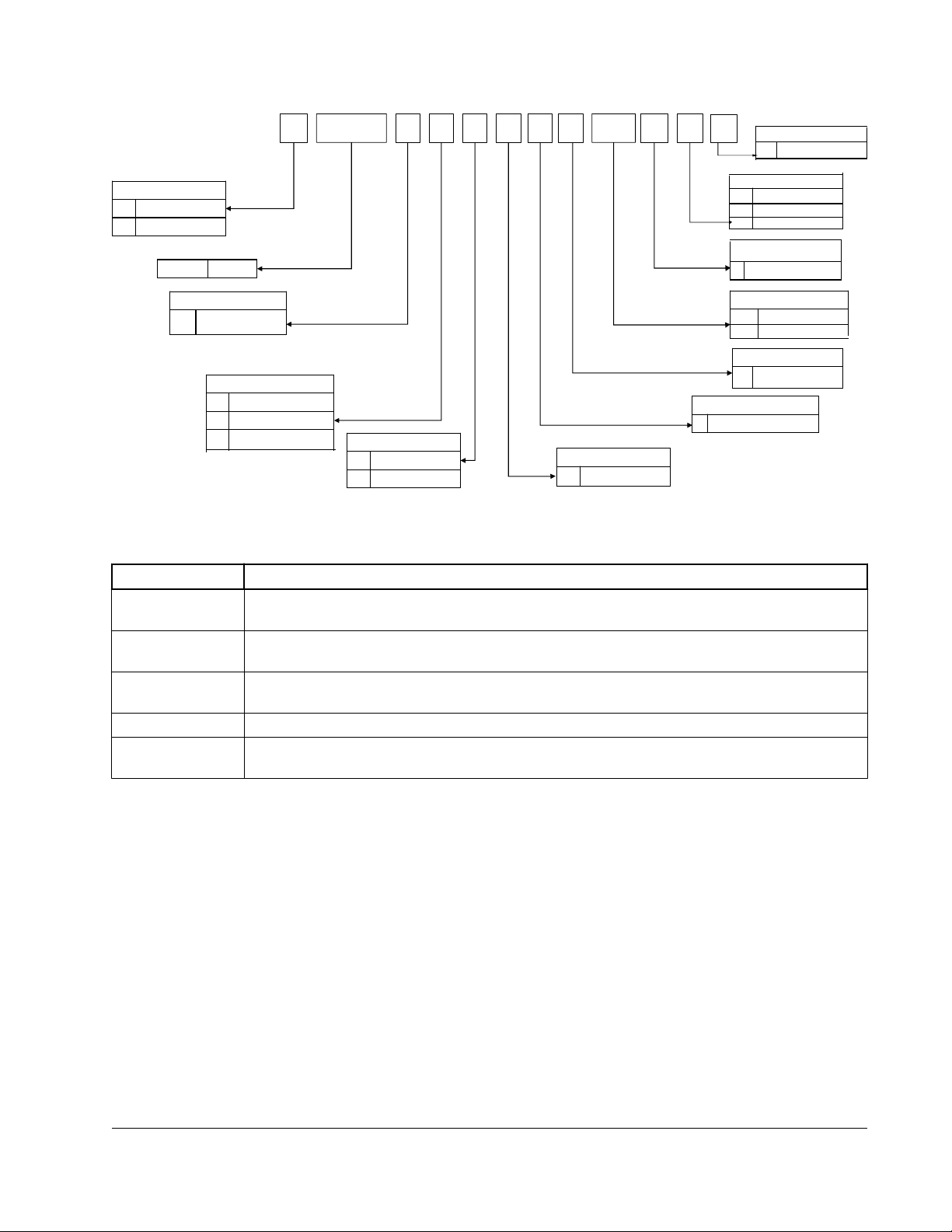

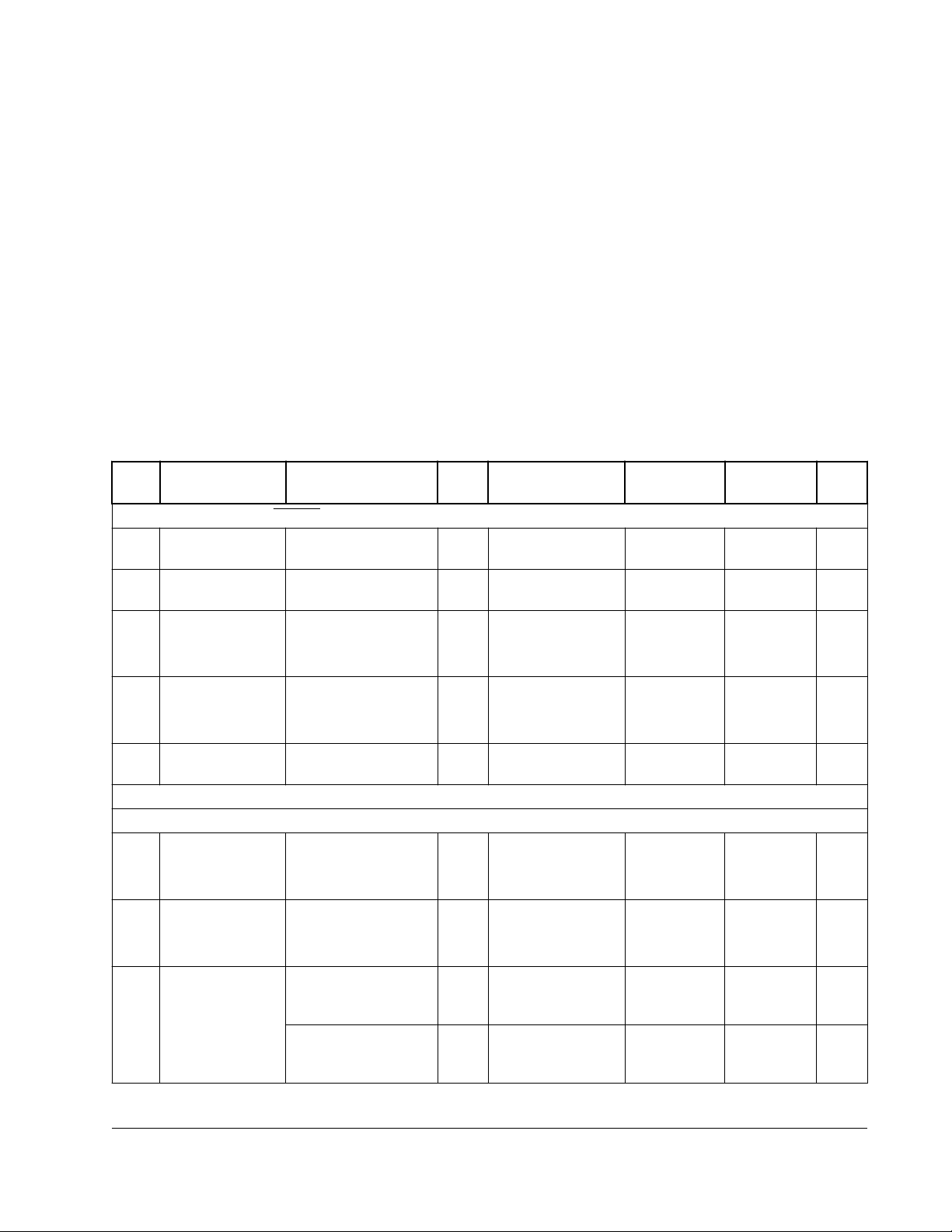

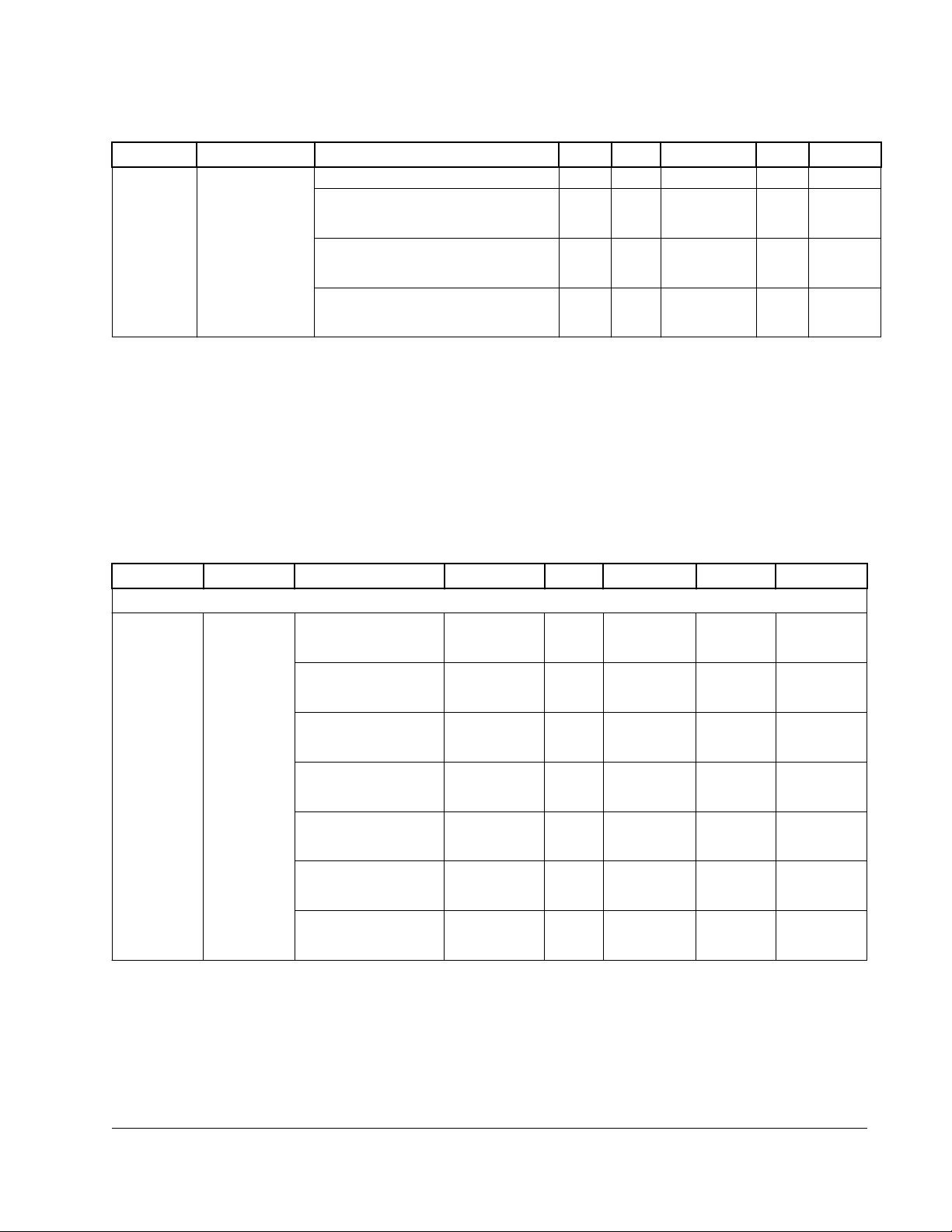

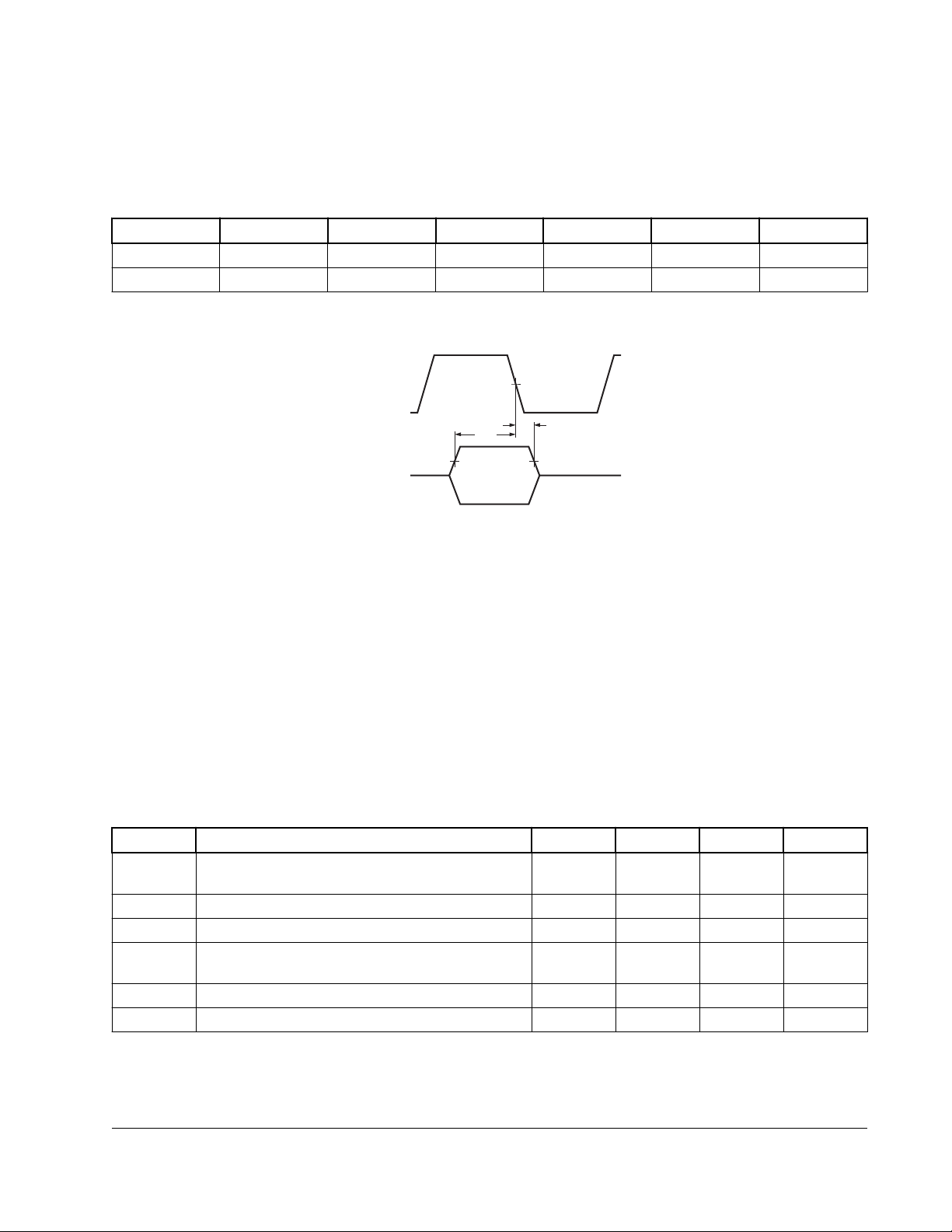

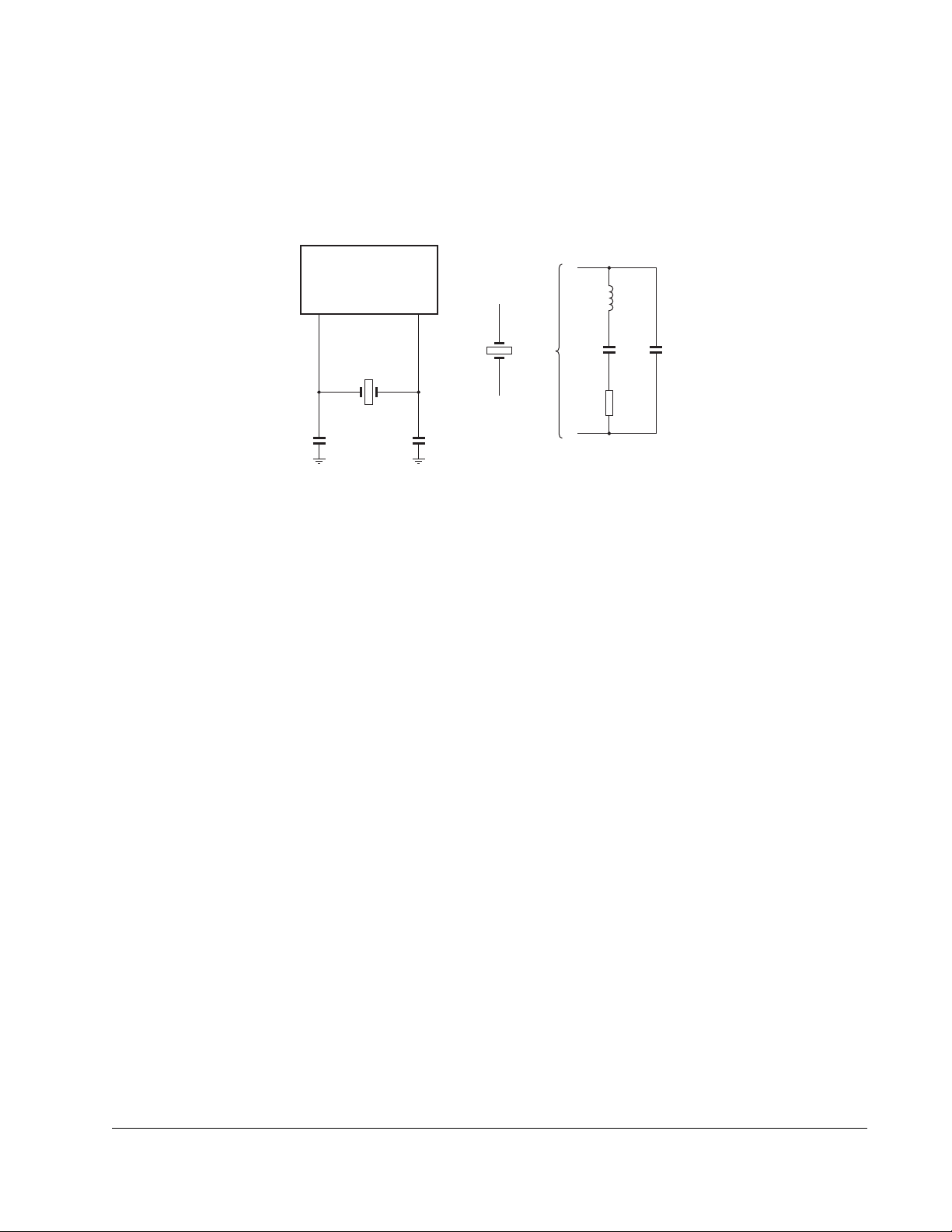

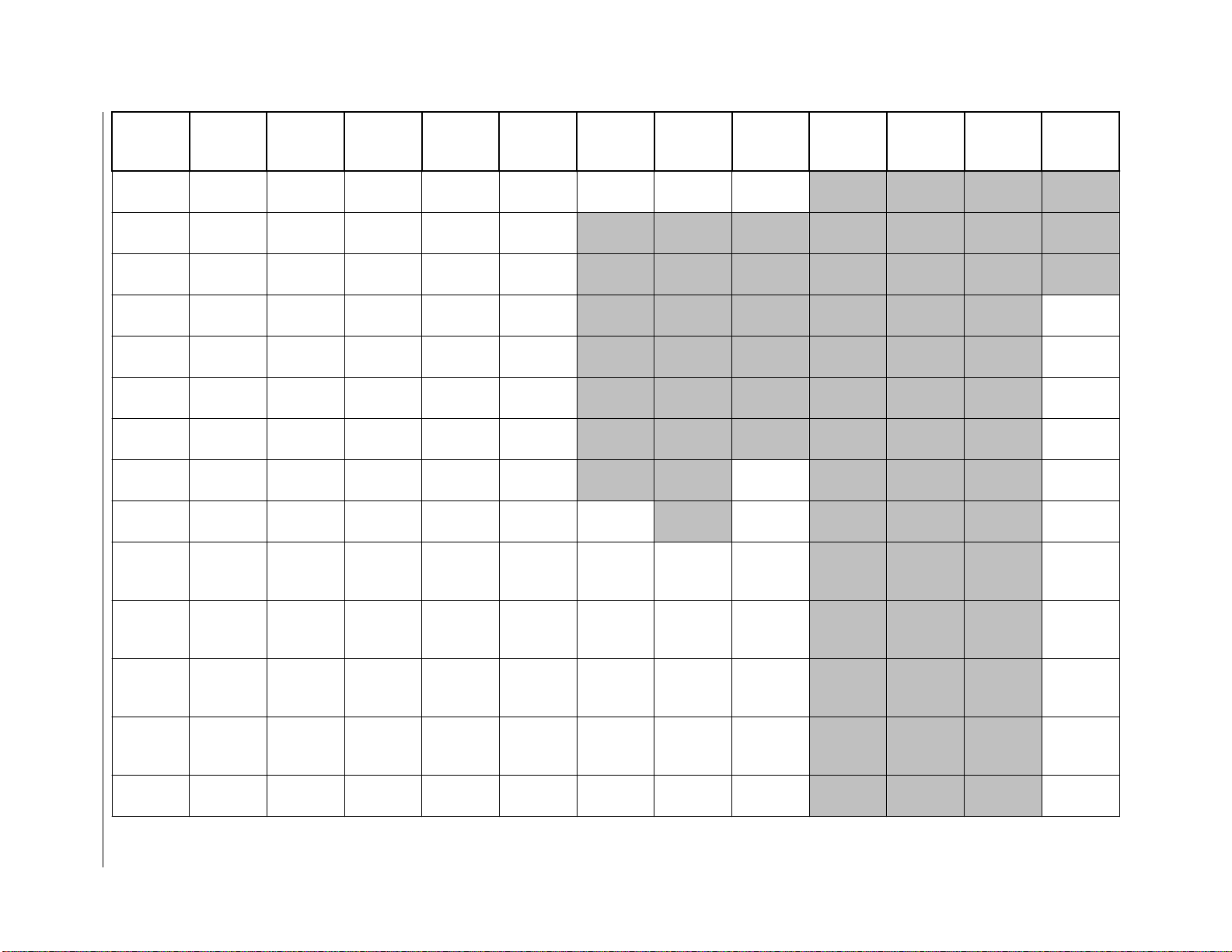

CPU Platform

ARM® Cortex-® M33

FPU

MPU

NVIC

DSP Accelerator

TrustZone® M

Fusion F1 DSP

DSP Processor

System Control

Security

SRAM PUF

AES-256

RNG

SHA-1/SHA-2

Upto 5 MB shared

low-leakage SRAM

192 KB ROM

Internal Memory

2x 32 KB FlexSPI Cache

16 KB USB RAM

FlexSPI(Quad/Octal) with

On-The-Fly OTFAD Decryption

External Memory

FlexSPI (Quad/Octal)

Connectivity

Analog Comparator

Analog

12-bit, 1MSPS ADC

2x Temp Sensor

Crypto Accelerators

Timers

(up to 200 MHz)

(up to 200 MHz)

2x PLL

FRO/OSC

PMC

Semaphore

Message unit

2x DMA

CRC engine

JTAG/SWD

System Tick Timers

Frequency Measure

OS/Event Timer

RTC

2x Watch Dog

5x Counter Timers

32-bit SCTimer/PWM

Multi-Rate Timer

Available on certain product families

FPU

Multimedia

2D GPU (up to 200 MHz)

MIPI®-DSI

(2 lane)

Display LCD

Controller

10x Frac rate gen

8-Ch DMIC

1x I2C

FlexIO

2xMIPI-I

3

GPIOs

2x HS SPI

2x SDIO/

eMMC/SD

Up to 9x Flexcomm

(UART/I2C/SPI/I2S)

HS USB Host/Device

+ DCD w/ PHY

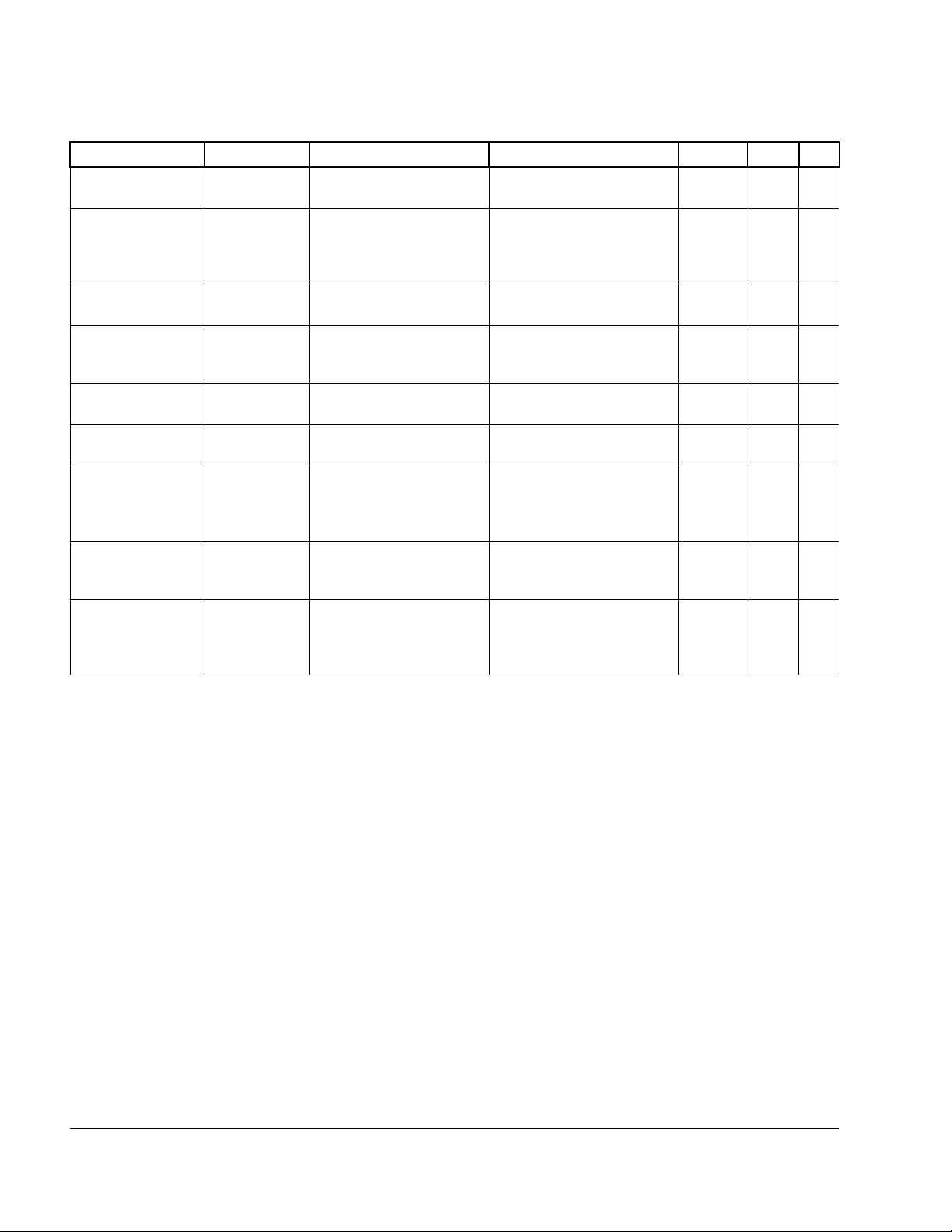

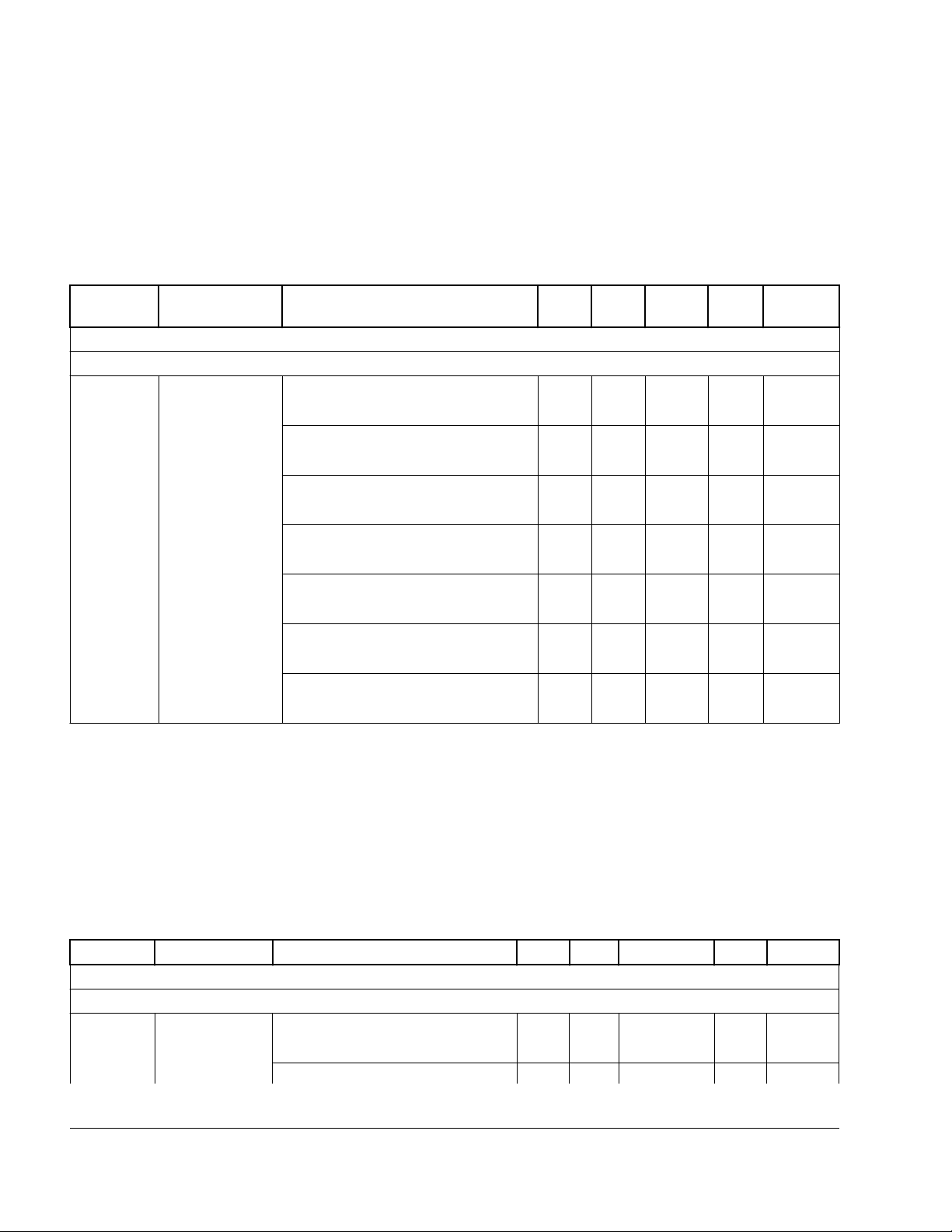

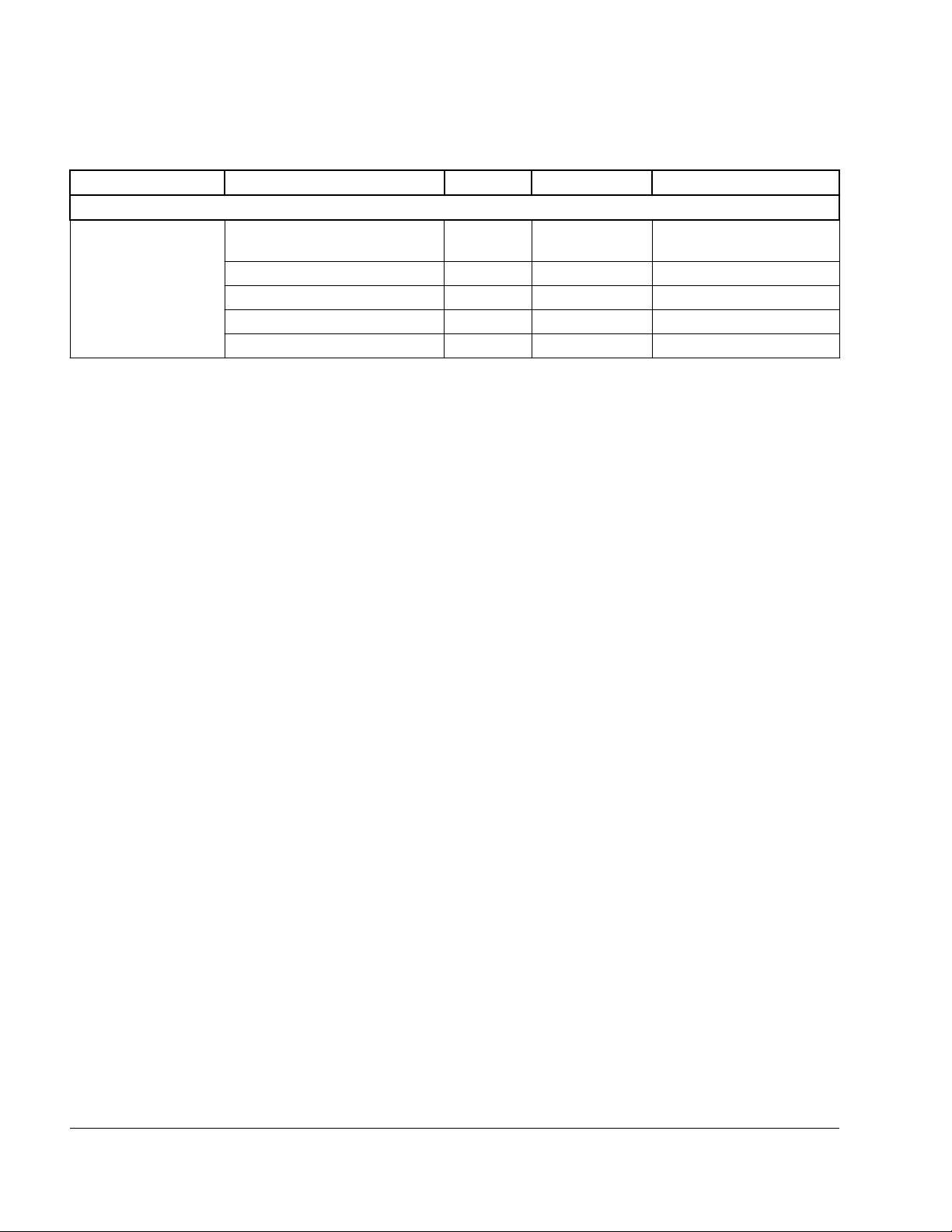

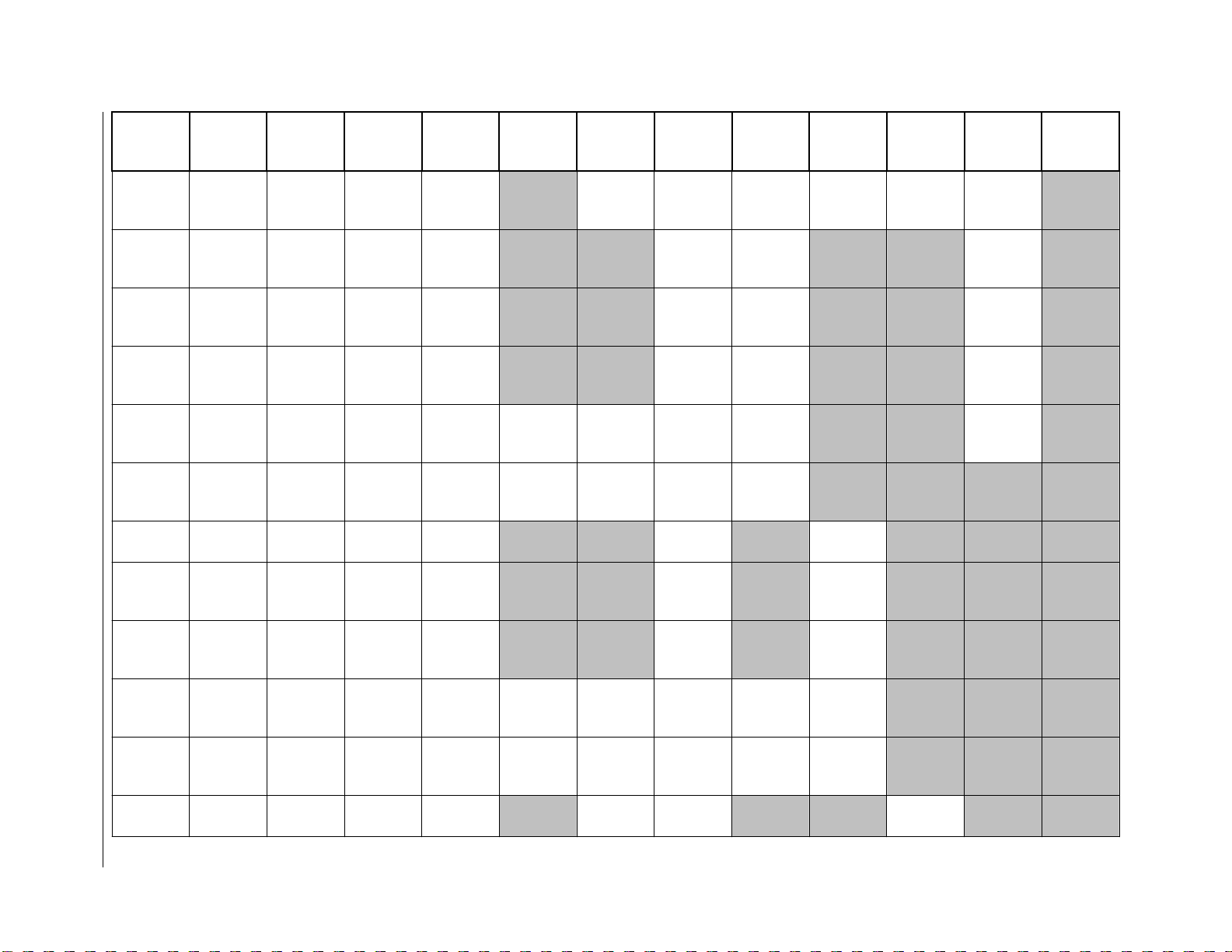

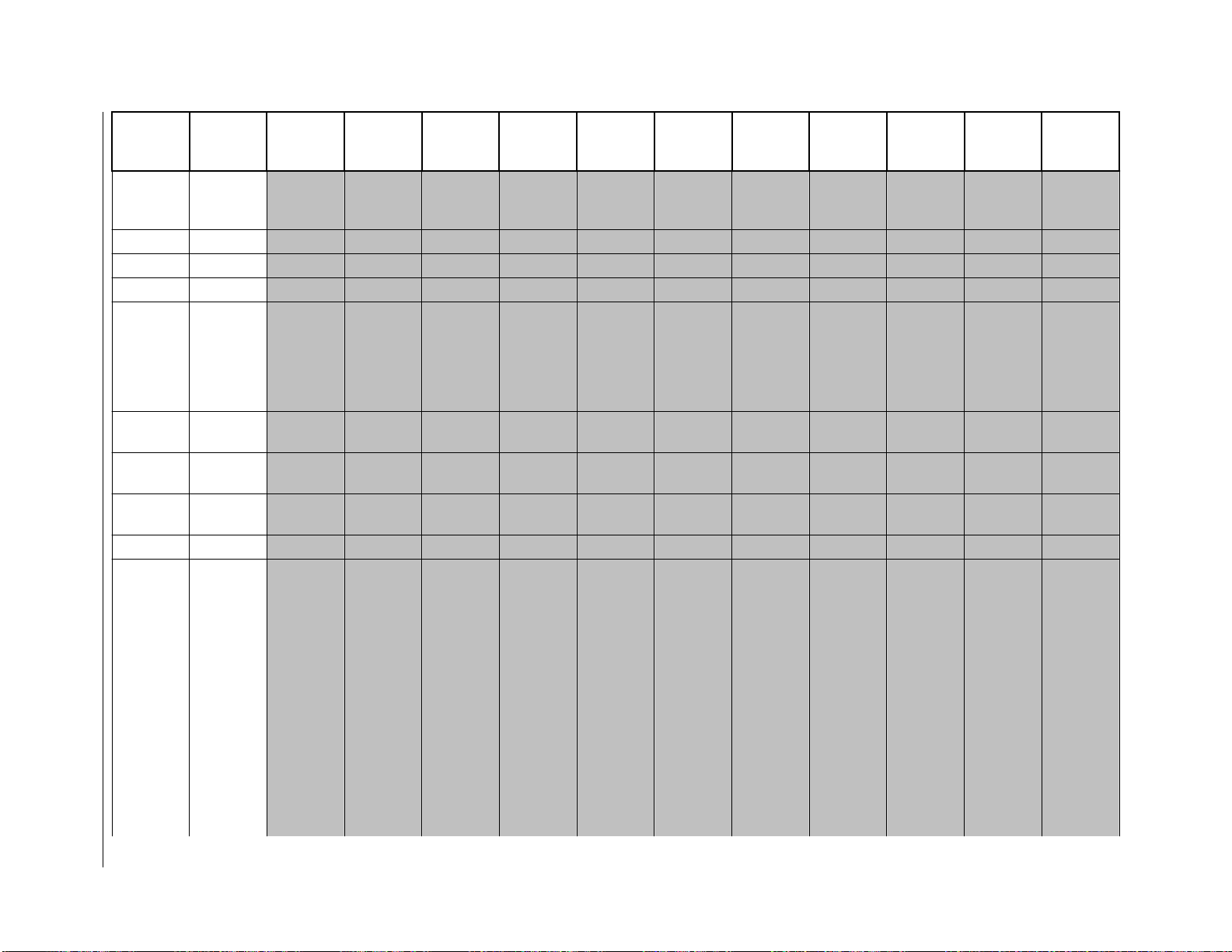

The following table provides examples of orderable sample part numbers covered by this data sheet.

4

NXP Semiconductors

Figure 1. i.MX RT500 Block Diagram

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 5

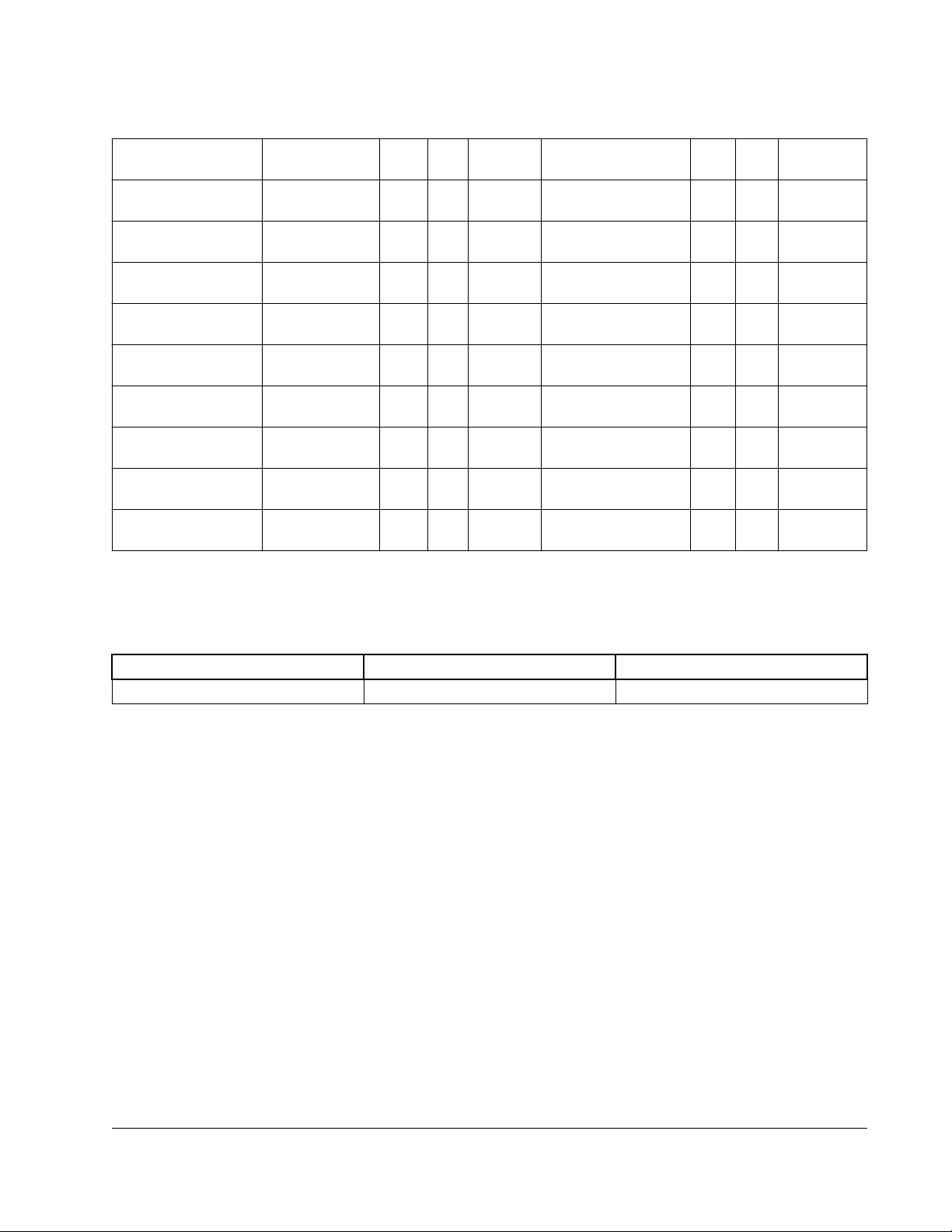

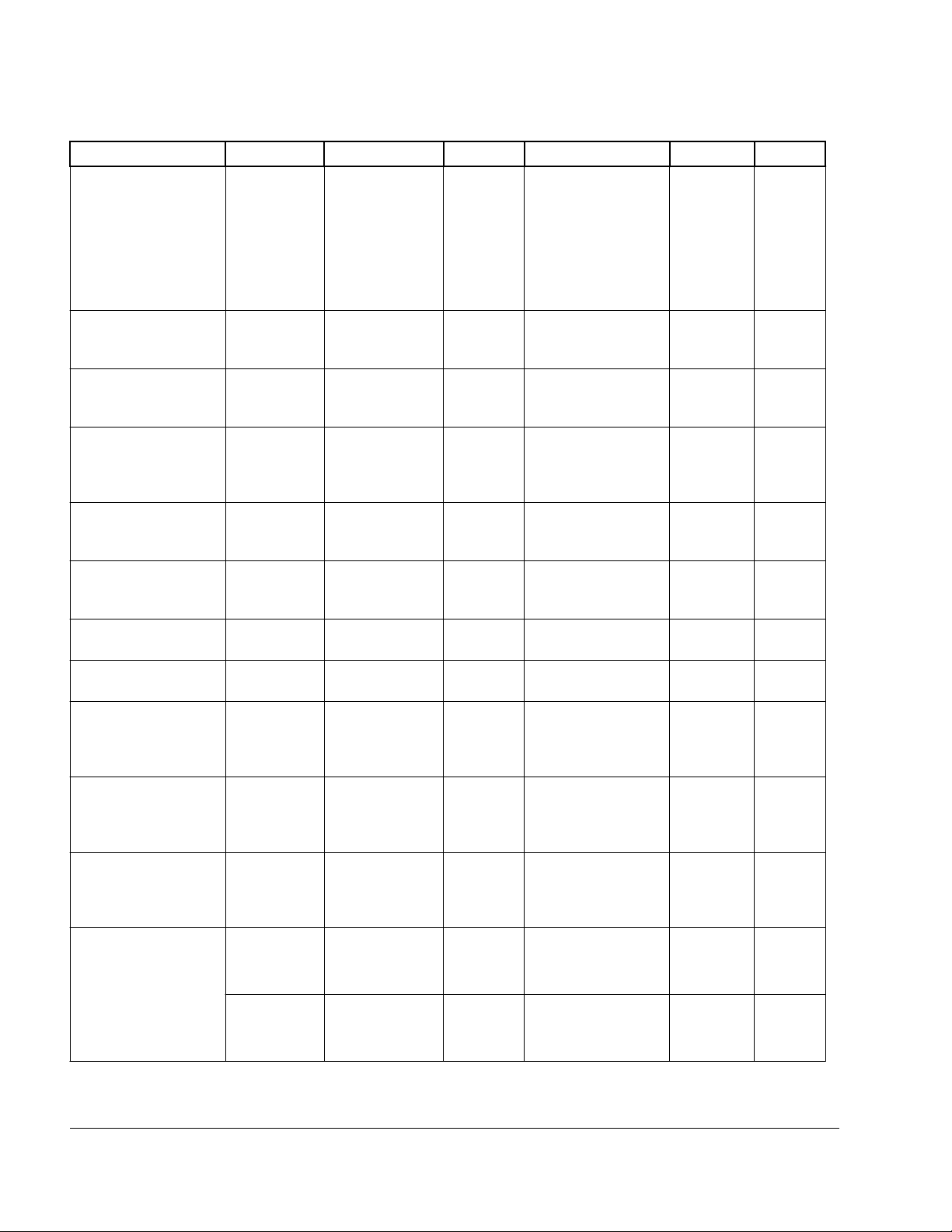

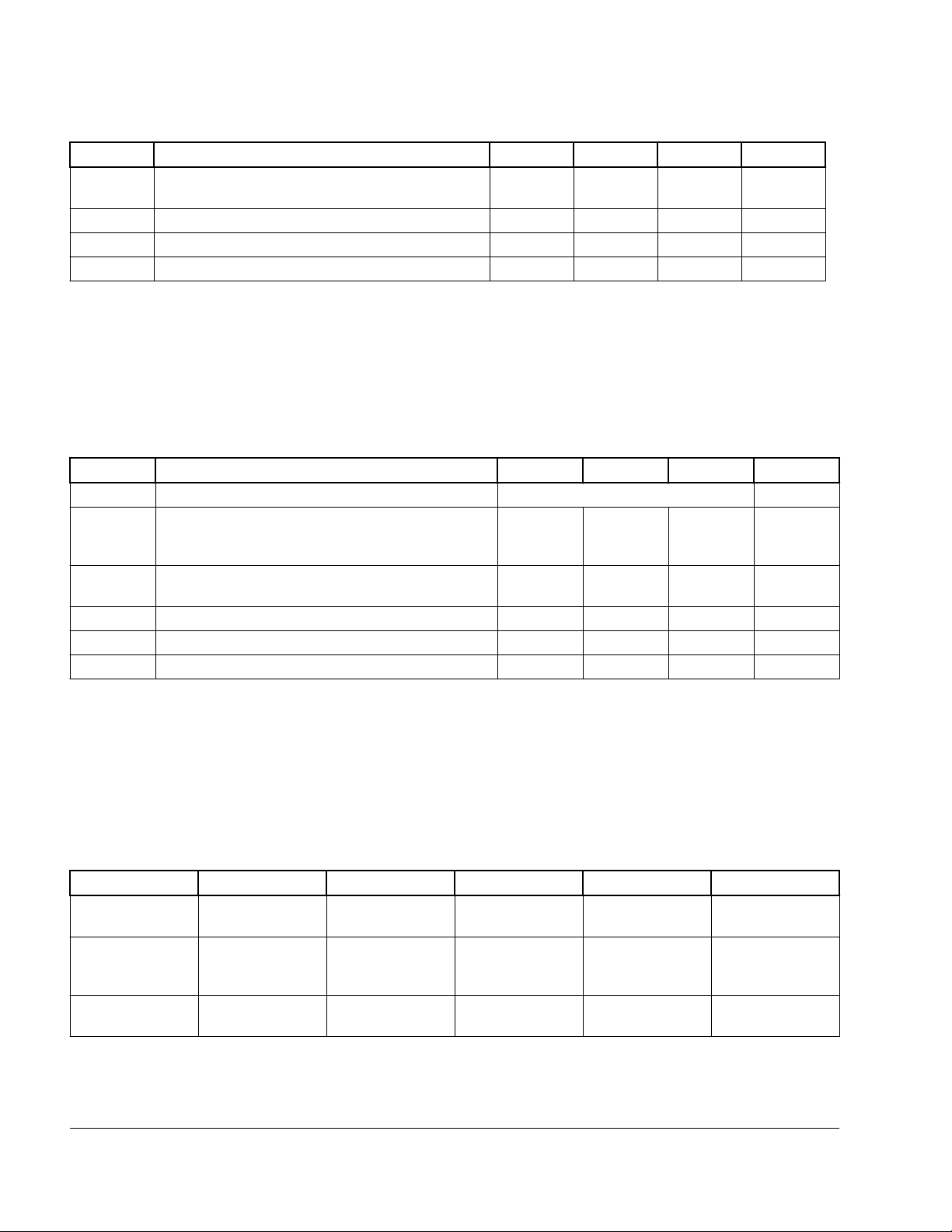

Orderable part number table

Orderable part

Part number

number

MIMXRT595SFFOC MRT595SFFOC 5 Yes Yes SRAM PUF, AES256,

MIMXRT555SFFOC MRT555SFFOC 5 No Yes SRAM PUF, AES256,

MIMXRT533SFFOC MRT533SFFOC 3 No No SRAM PUF, AES256,

MIMXRT595SFFOCR MRT595SFFOC 5 Yes Yes SRAM PUF, AES256,

MIMXRT555SFFOCR MRT555SFFOC 5 No Yes SRAM PUF, AES256,

MIMXRT533SFFOCR MRT533SFFOC 3 No No SRAM PUF, AES256,

MIMXRT533SFAWCR MRT533SFAWC 3 No No SRAM PUF, AES256,

MIMXRT555SFAWCR MRT555SFAWC 5 No Yes SRAM PUF, AES256,

MIMXRT595SFAWCR MRT595SFAWC 5 Yes Yes SRAM PUF, AES256,

1

SRAM

DSP Graphics Security USB I2S Package

(MB)

HASH

HASH

HASH

HASH

HASH

HASH

HASH

HASH

HASH

HS 9 FOWLP249

HS 9 FOWLP249

HS 9 FOWLP249

HS 9 FOWLP249

HS 9 FOWLP249

HS 9 FOWLP249

HS 6 WLCSP141

HS 6 WLCSP141

HS 6 WLCSP141

2

2

1. As marked on package

2. 249-pin Fan-out wafer-level package

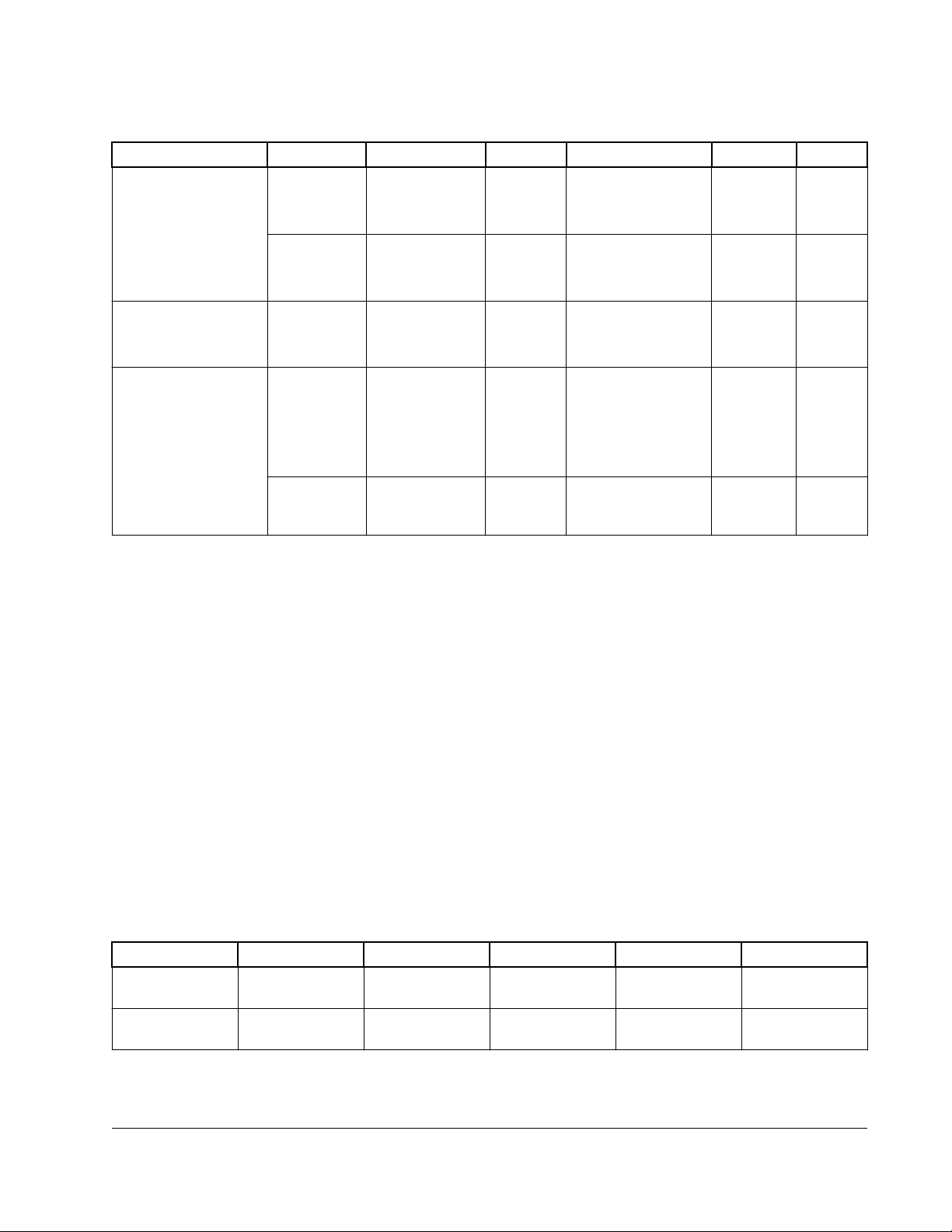

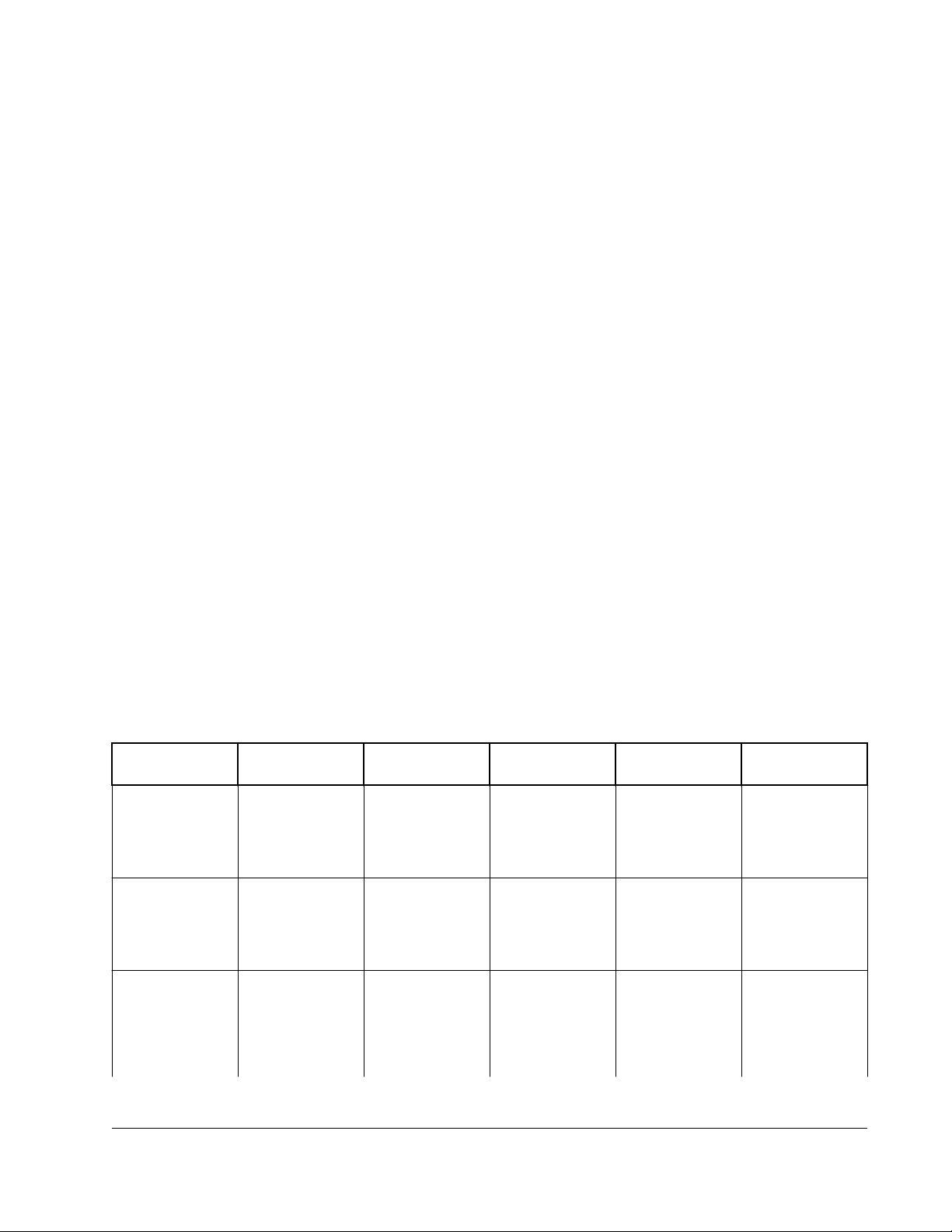

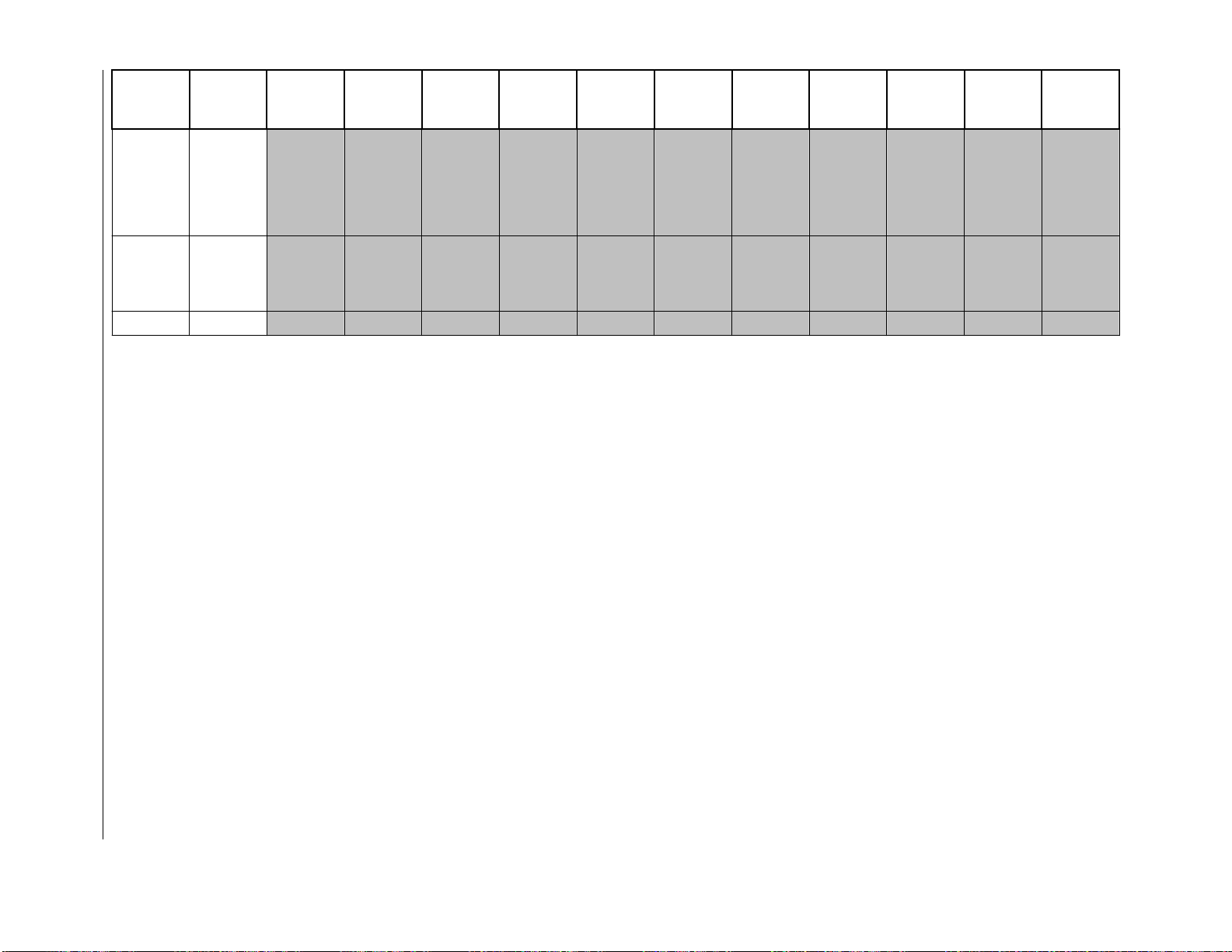

Device revision number

Device Mask Set Number SILICONREV_ID JTAG_ID[CHIPREV]

2P43B 0x000B0002 0x2

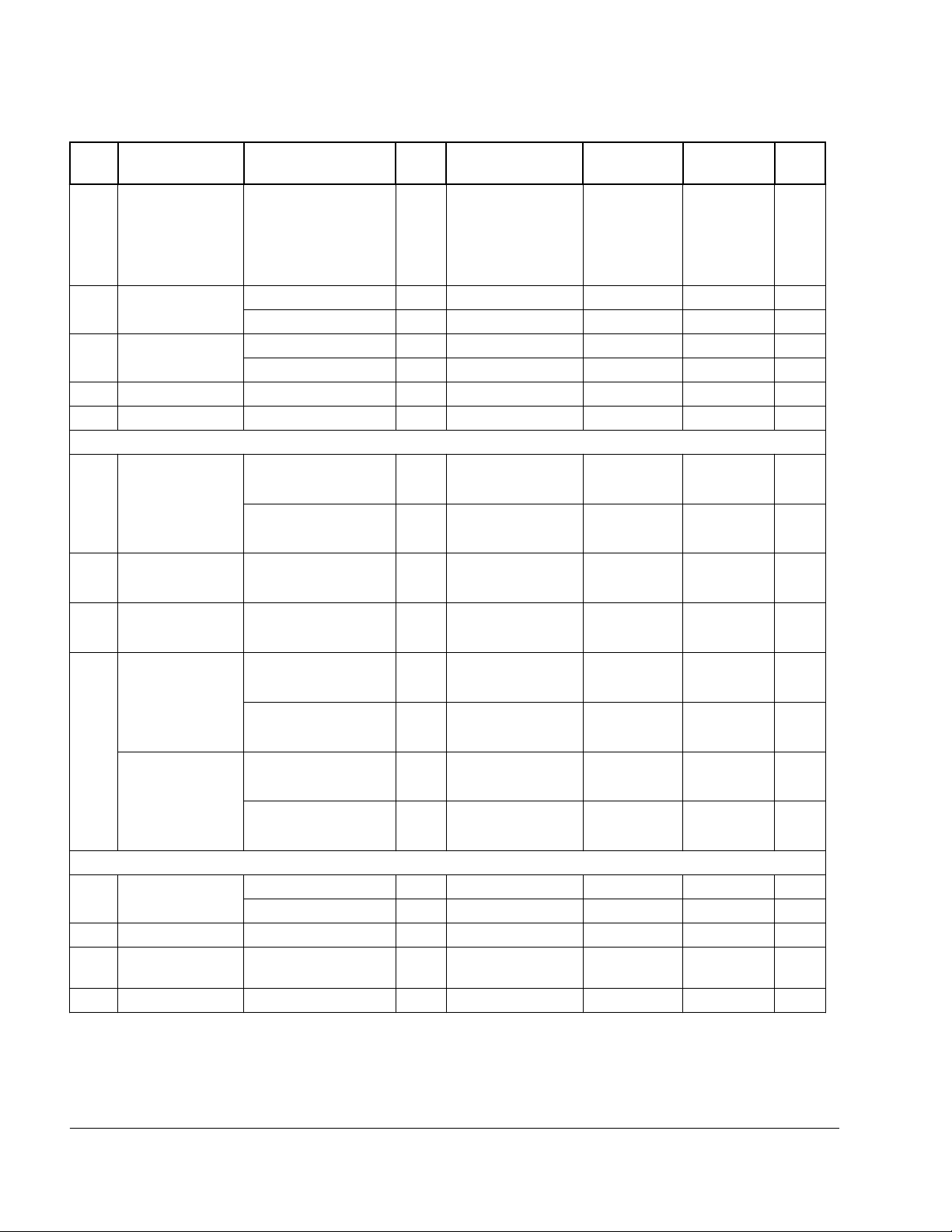

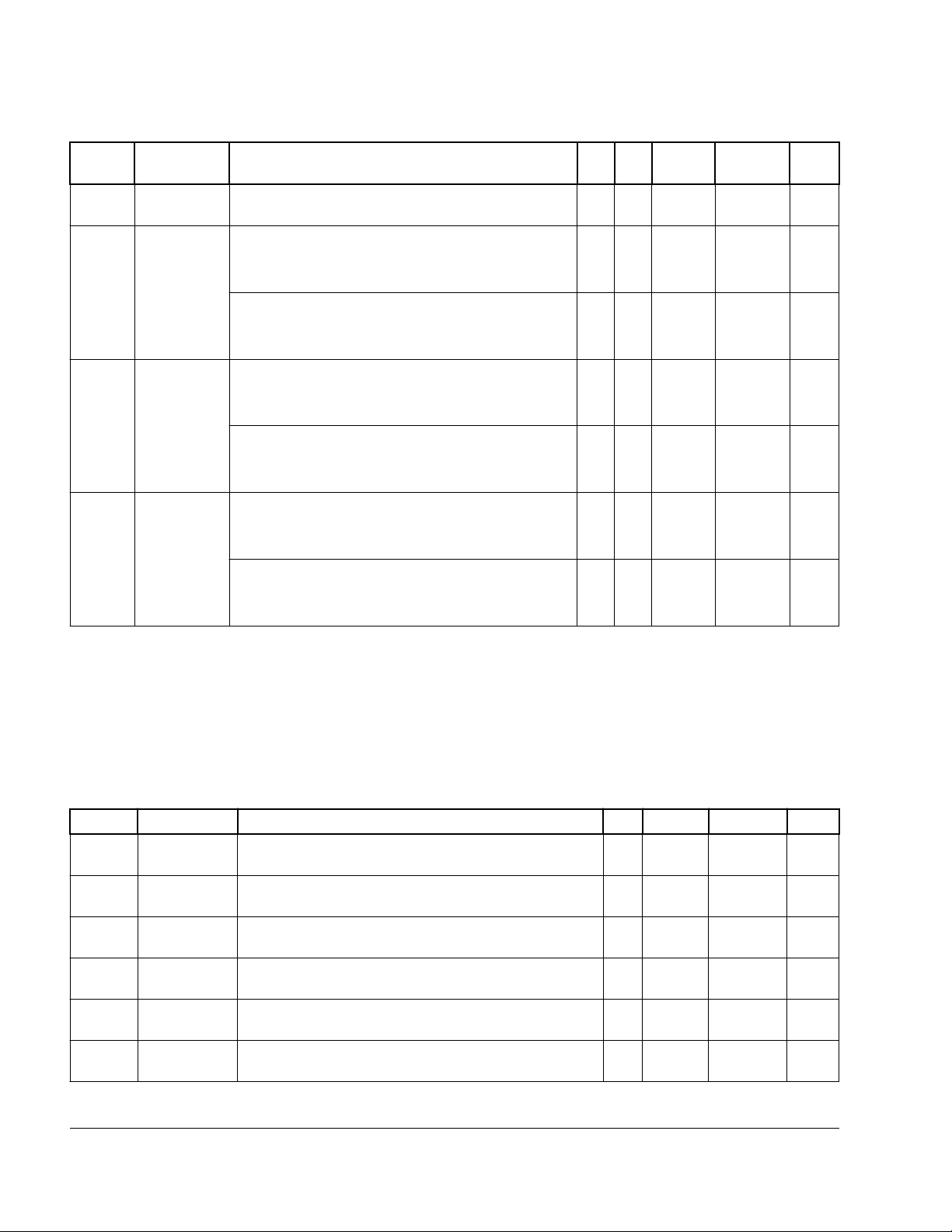

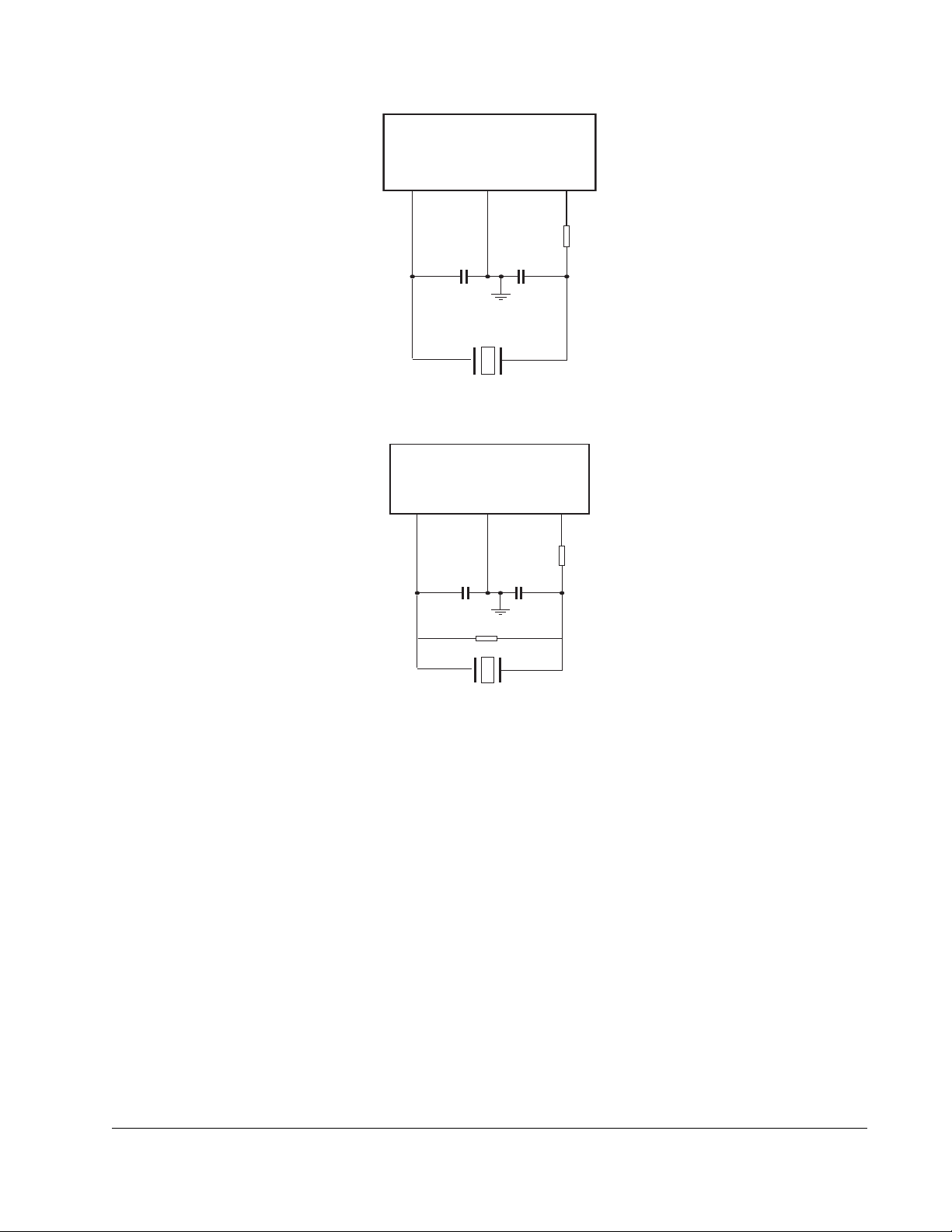

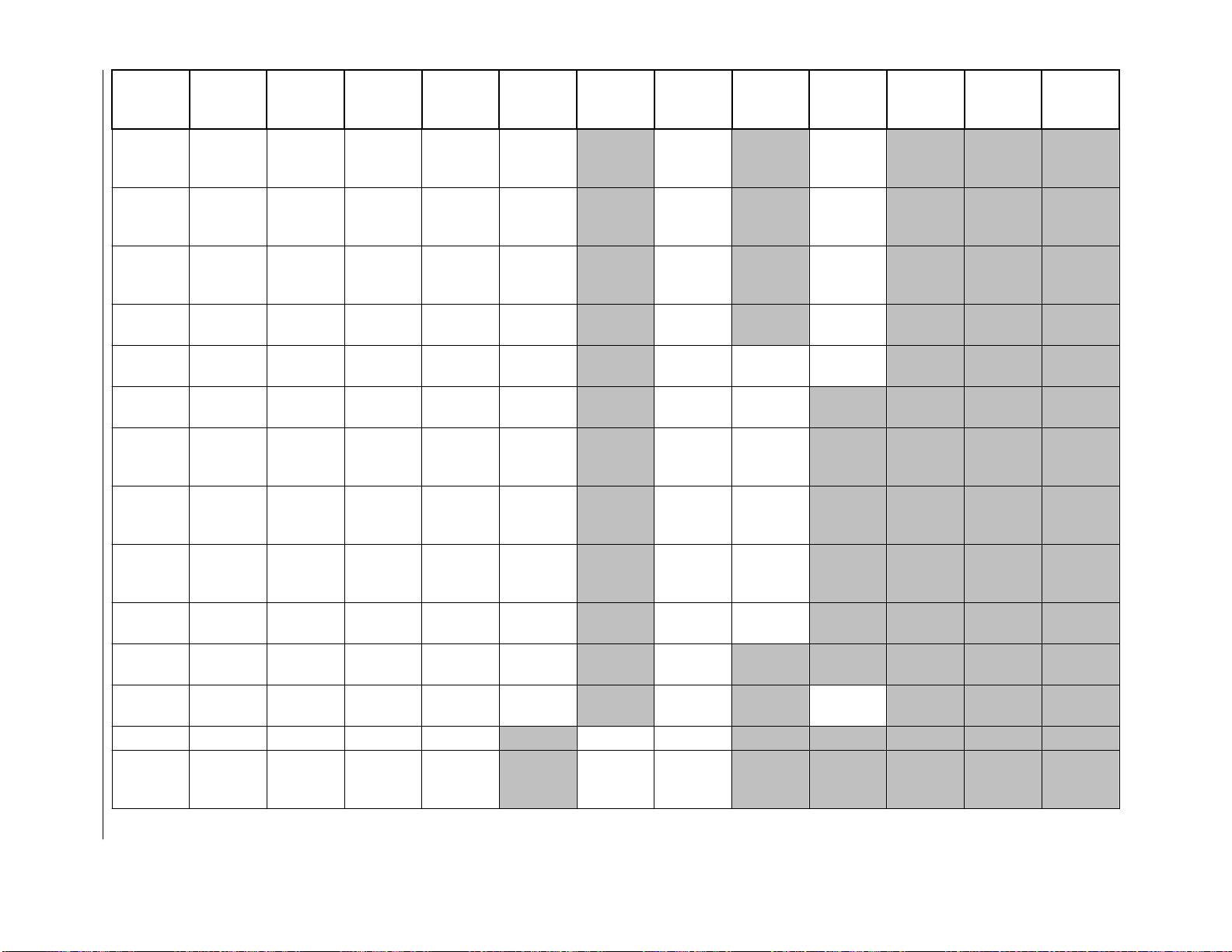

Package markings for i.MX RT devices consist of 4 sets of identifiers as shown below.

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

5

NXP Semiconductors

Page 6

Figure 2. Package markings

• The 1st identifier defines the Part Number and is composed of 11 characters.

• The 2nd and 4th identifiers define the Traceability markings.

• The 3rd identifier defines the Date Code for the week of manufacture is a subset of the standard 5

character format.

The standard date code format is “xYYWW”:

• The leading digit represented by “x” can be ignored and “YYWW” indicate the Date Code.

• “YY" represents an encoding of the calendar year (for example, 19 corresponds to year 2019).

• “WW” represents an encoding of the work week within the calendar year (for example, 07 corresponds to

work week 7).

Please provide this information to your local NXP representative for further details.

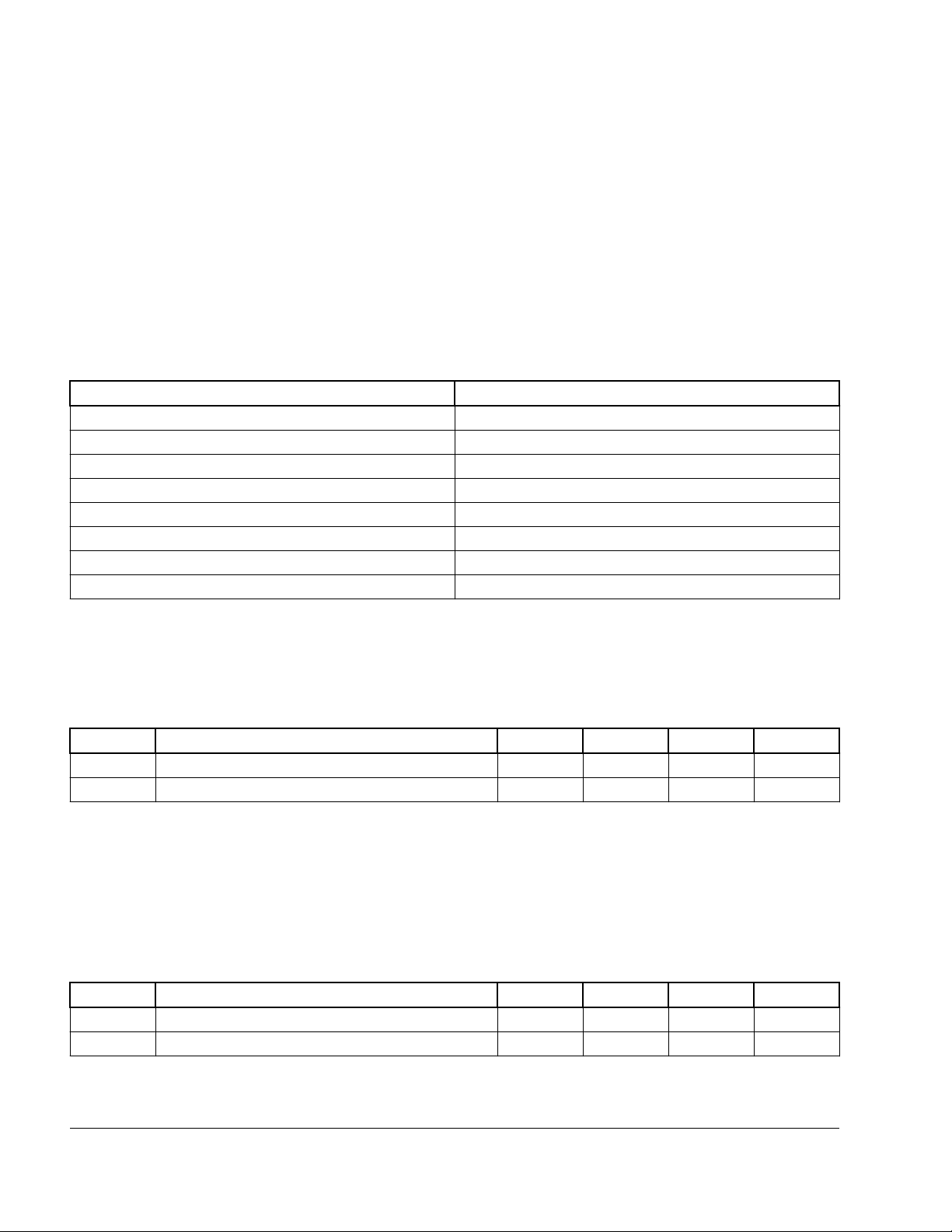

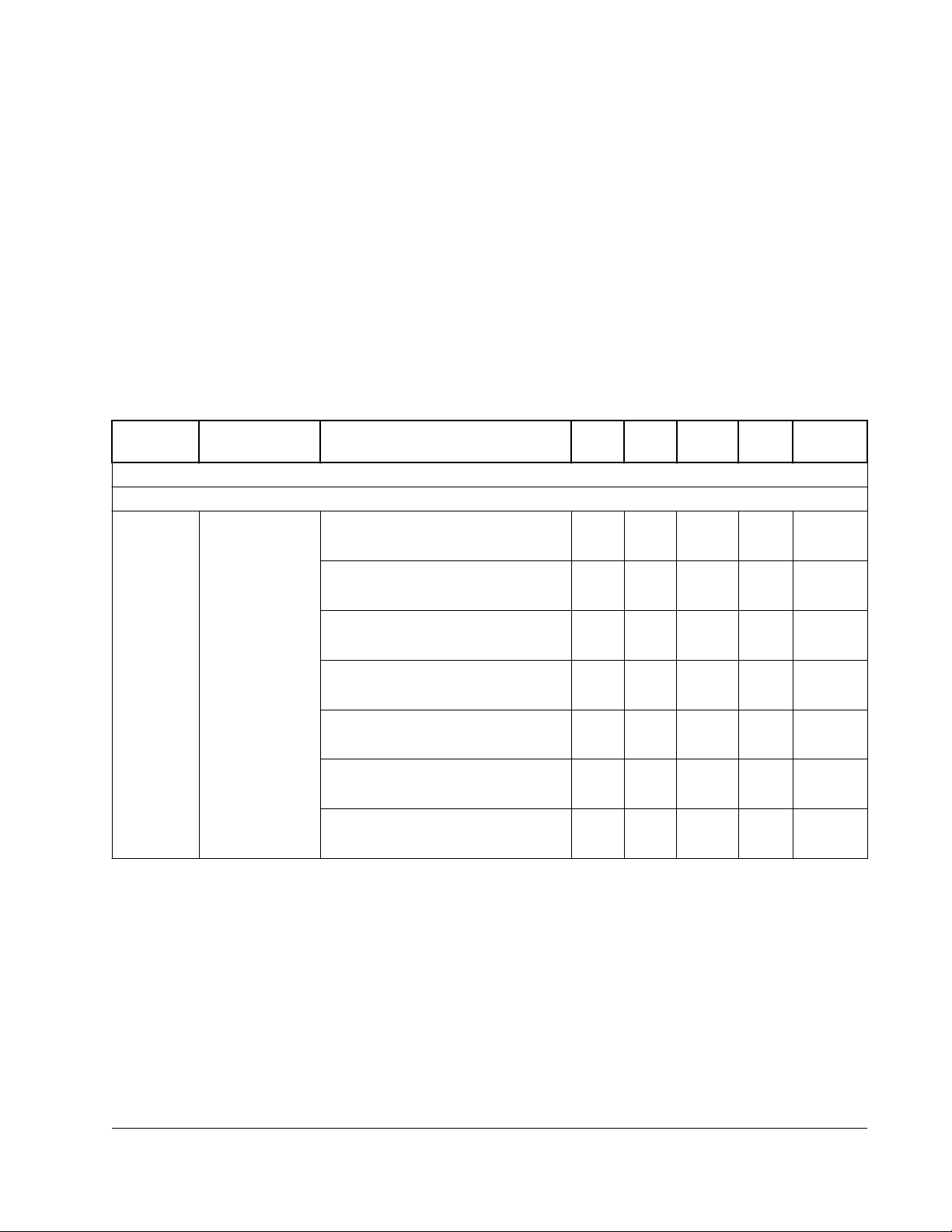

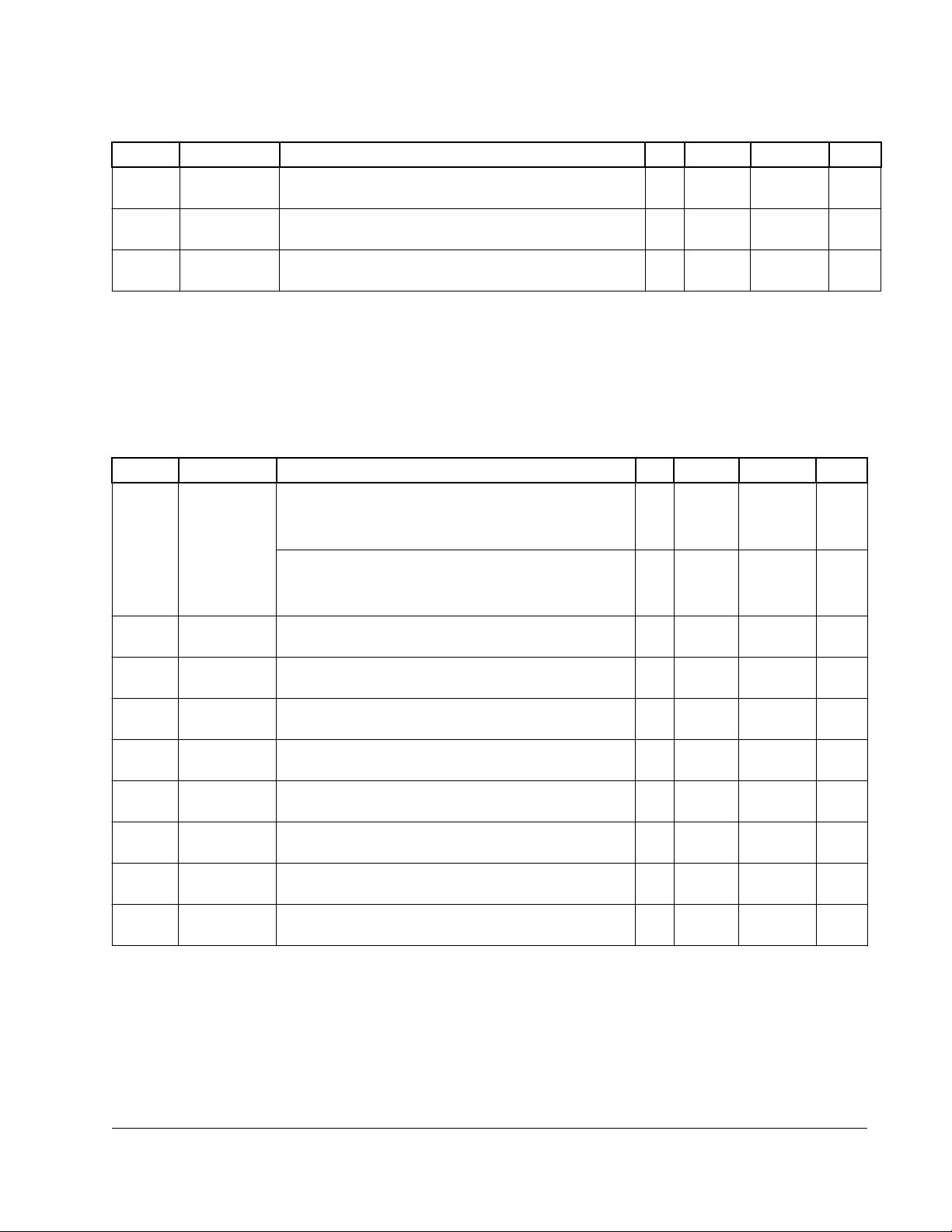

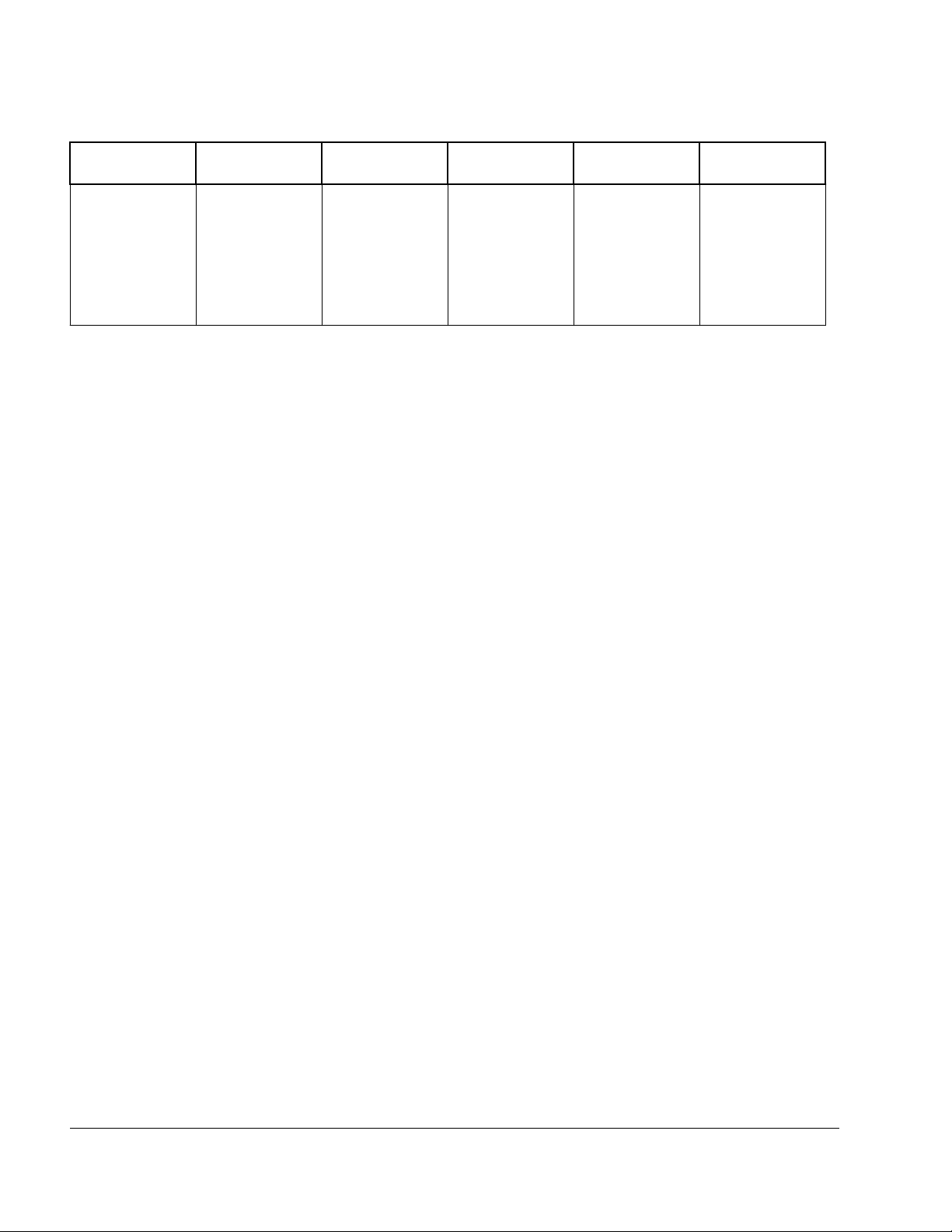

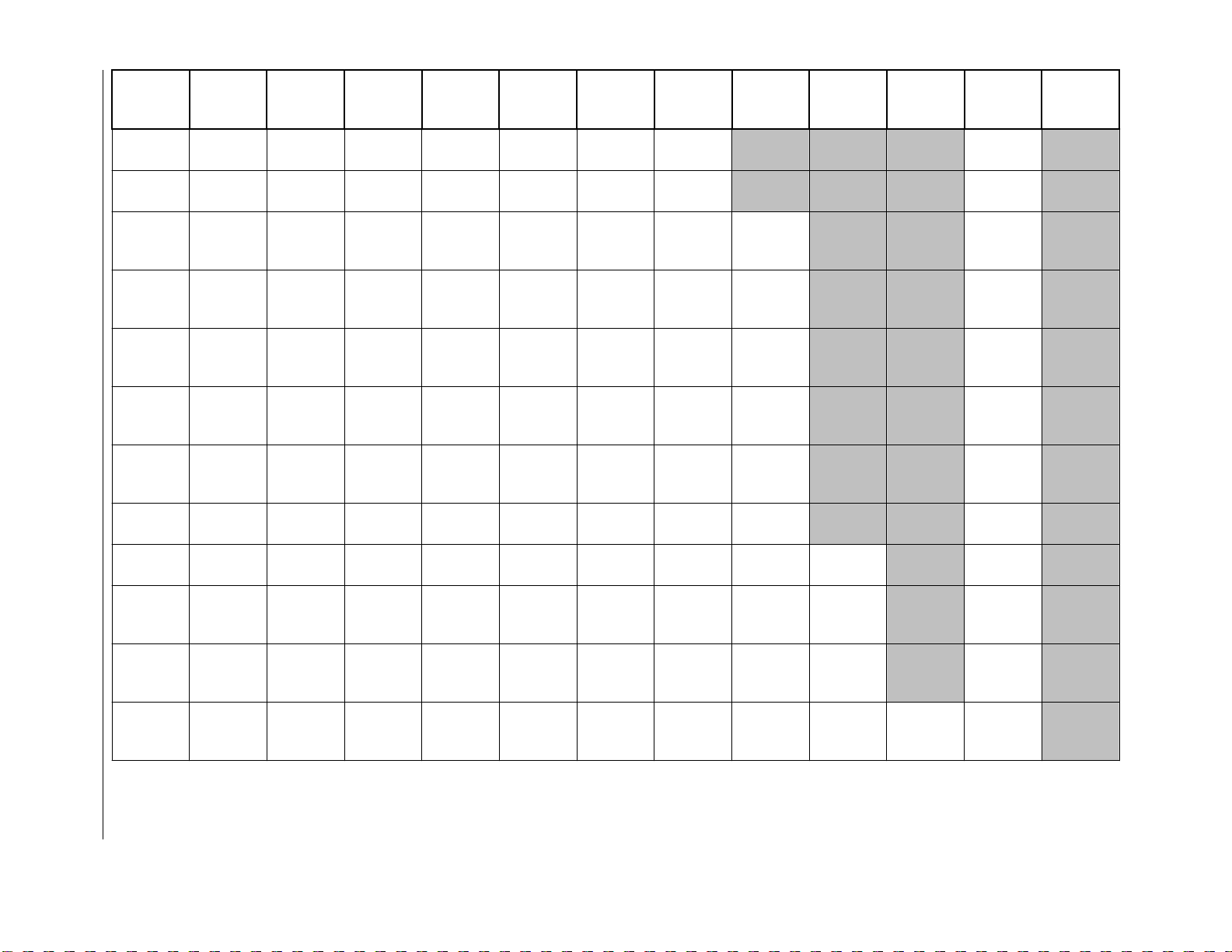

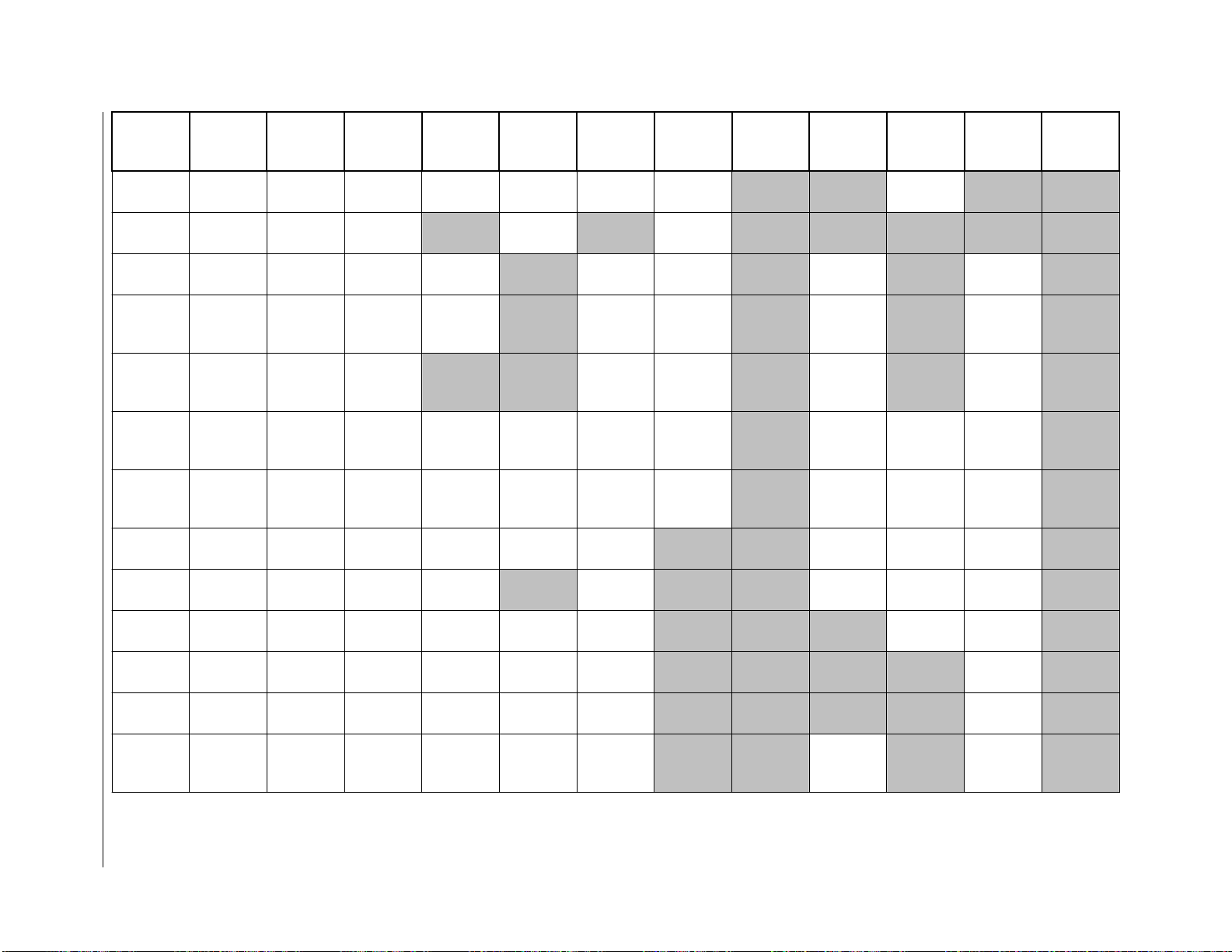

The following figure explains the part number for this device.

6

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 7

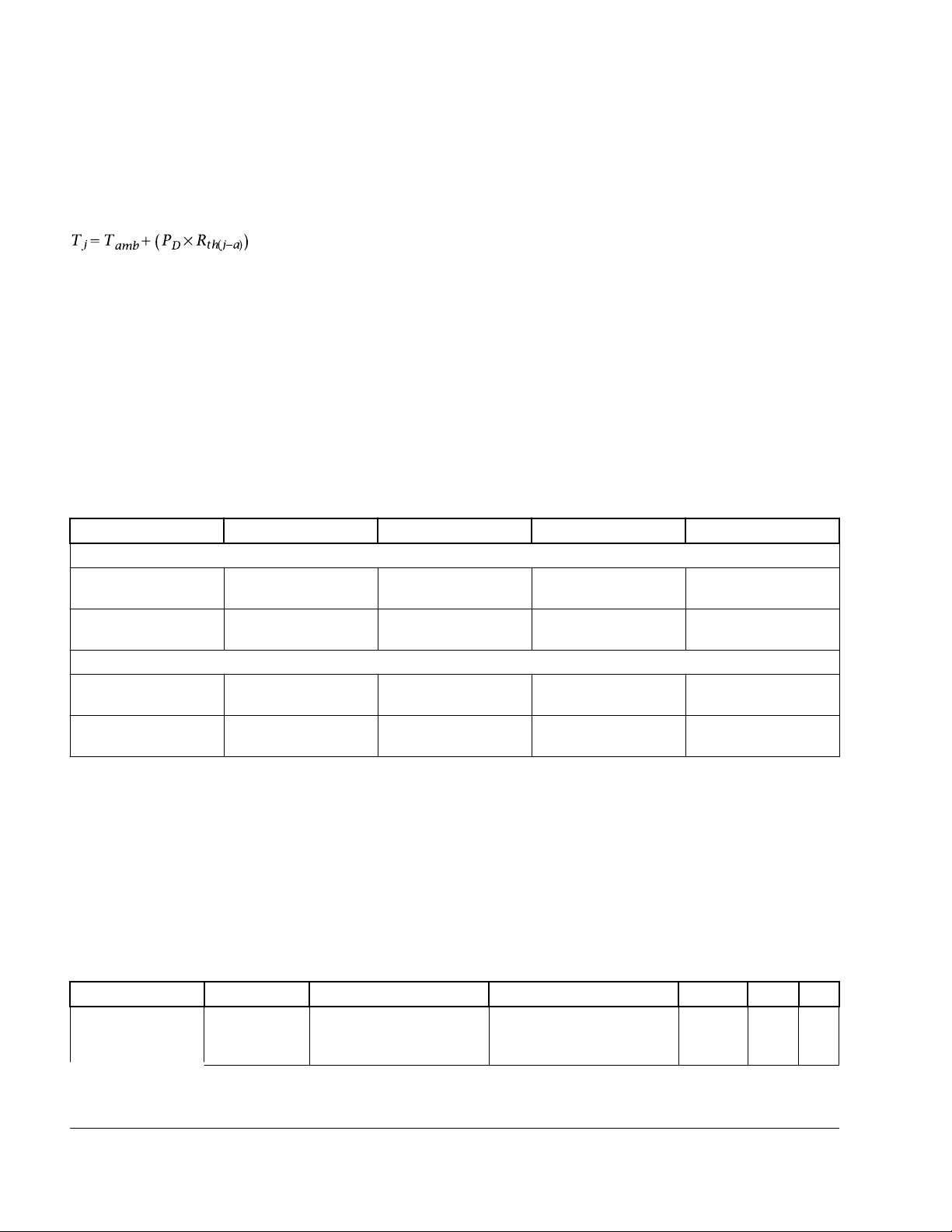

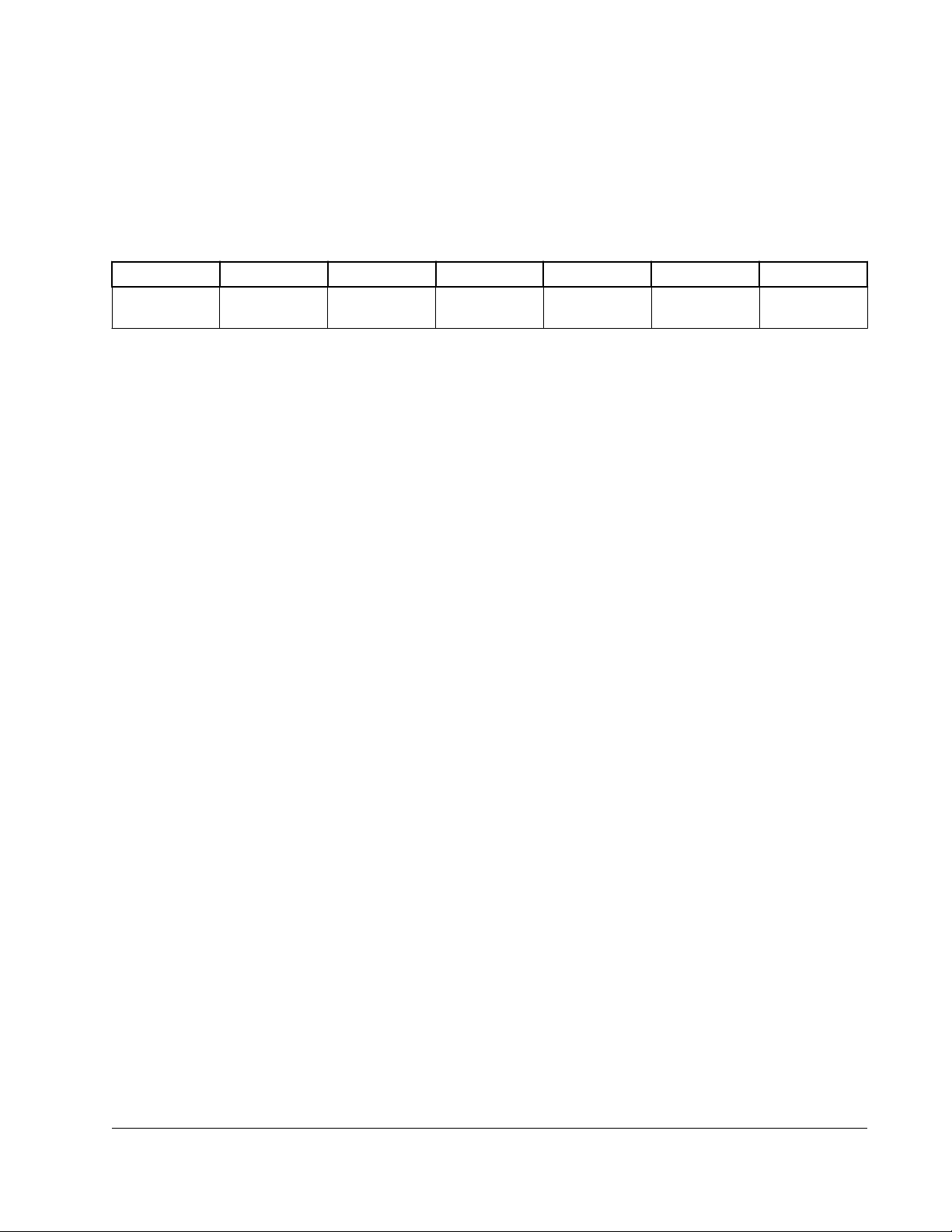

M IMXRT # # # # A AA x A

Qualification Level

M Mass Production

P Prototype

IMXRT Family

Series

5 RT500 series

Feature 2 (SRAM)

3 3MB

5 5MB

Feature 3

S Security

Temperature Range

F -20 – 70 C

Package

FO FOWLP 249

Silicon Revision

A Rev A

B

Rev B

Feature 1

3 no DSP, no Graphic

5 no DSP, w Graphic

w DSP, w Graphic

#

Feature 4 (Optional)

Speed/ Power

x

Reserved

Reserved

9

AW

WLCSP 141

Rev C

C

A

Packing Method

R

Reel

Figure 3. Part number diagram

Related Resources

Type Description

Selector Guide The Solution Advisor is a web-based tool that features interactive application wizards and a

dynamic product selector.

Product Brief The Product Brief contains concise overview/summary information to enable quick evaluation of a

device for design suitability.

Reference Manual The i.MX RT500 Low-Power Crossover MCU Reference Manual contains a comprehensive

description of the structure and function (operation) of a device.

Data Sheet Refers to this document which includes electrical characteristics and signal connections.

Chip Errata The chip mask set Errata provides additional or corrective information for a particular device mask

set.

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

7

NXP Semiconductors

Page 8

8

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 9

Table of Contents

1 Electrical characteristics........................................................10

1.1 Chip-level conditions......................................................10

1.1.1 Thermal handling ratings................................. 10

1.1.2 Moisture handling ratings................................ 10

1.1.3 ESD handling ratings....................................... 11

1.1.4 Absolute maximum voltage and current

ratings..............................................................11

1.1.5 Thermal specifications..................................... 13

1.1.6 General operating conditions...........................14

1.1.7 I/O parameters.................................................17

1.1.8 Power consumption operating behavior.......... 19

1.1.9 CoreMark data................................................. 23

1.2 System power and clocks.............................................. 24

1.2.1 Power sequence.............................................. 24

1.2.2 Free-running oscillator FRO-192/96M

specifications................................................... 27

1.2.3 Crystal oscillator.............................................. 28

1.2.4 RTC oscillator.................................................. 29

1.2.5 External Clock Input (CLKIN) pin.....................29

1.2.6 Internal low-power oscillator (1 MHz).............. 29

1.3 System modules............................................................ 30

1.3.1 Reset timing parameters................................. 30

1.3.2 Serial Wire Debug (SWD) timing

specifications .................................................. 30

1.3.3 JTAG timing specifications.............................. 31

1.3.4 Wake-up process.............................................34

1.4 External memory interface.............................................35

1.4.1 FlexSPI Flash interface................................... 35

1.5 Display and graphics..................................................... 38

1.5.1 LCDIF.............................................................. 38

1.5.2 MIPI DSI timing................................................38

1.5.3 Flexible IO controller (FlexIO)..........................38

1.6 Analog characteristics....................................................39

1.6.1 12-bit ADC characteristics............................... 39

1.6.2 Temperature sensor........................................ 42

1.6.3 Comparator characteristics..............................43

1.7 Communication interfaces............................................. 45

1.7.1 USART interface..............................................45

1.7.2 I2C-bus............................................................ 46

1.7.3 I2S-bus interface............................................. 47

1.7.4 SPI interfaces (Flexcomm interfaces 0-8)....... 49

1.7.5 High-Speed SPI interface (Flexcomm

interface 14).....................................................51

1.7.6 SD/MMC and SDIO......................................... 53

1.7.7 DMIC subsystem............................................. 56

1.7.8 USB interface characteristics.......................... 57

1.7.9 USB DCD electrical specifications...................57

1.7.10 USB High Speed Transceiver and PHY

specifications................................................... 58

1.7.11 Improved Inter-Integrated Circuit Interface

(MIPI-I3C) specifications................................. 58

1.8 Timer modules............................................................... 60

1.8.1 SCTimer/PWM output timing........................... 61

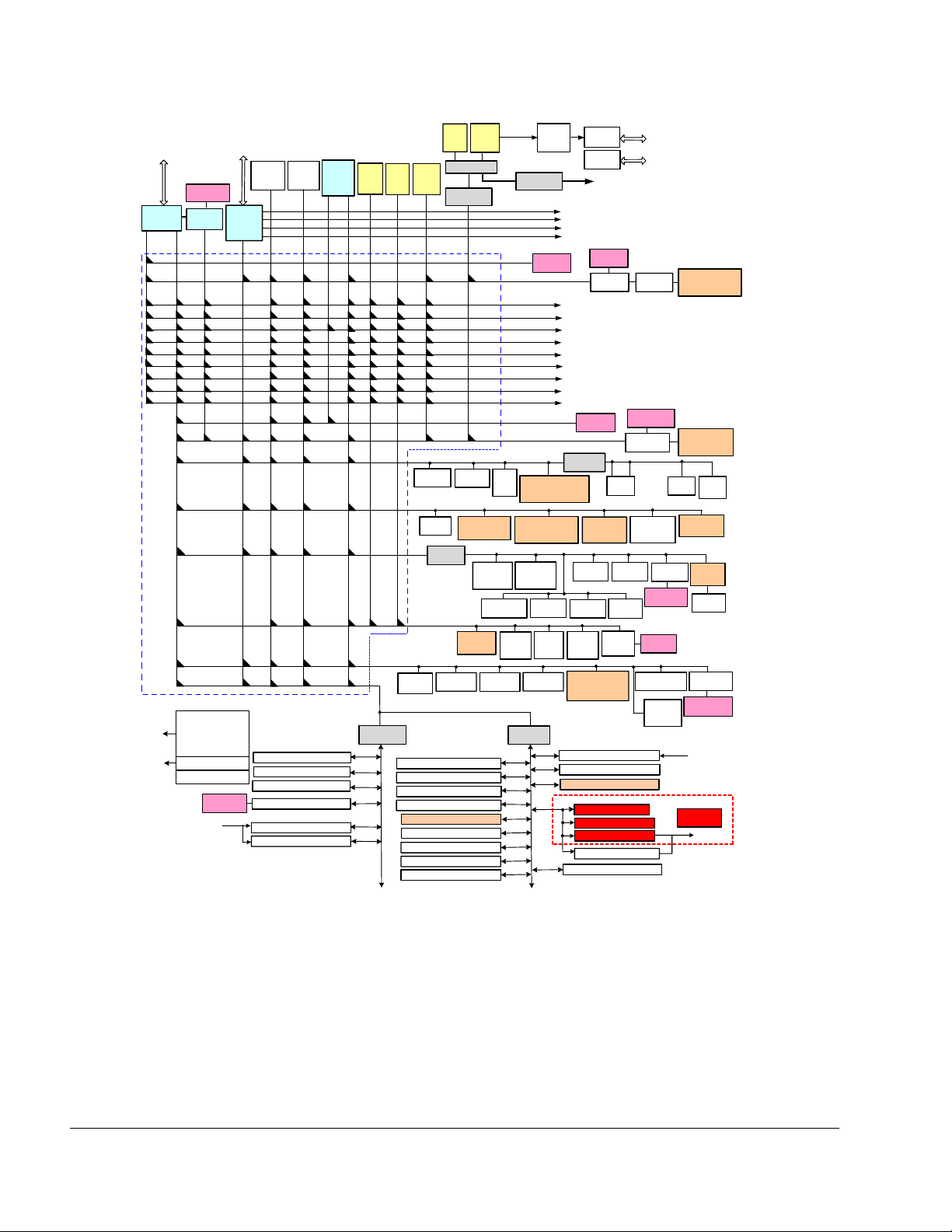

2 Architectural overview...........................................................61

2.1 Detailed block diagram.................................................. 61

2.2 Shared system SRAM................................................... 62

2.3 RT500 modules list........................................................ 63

3 Application information..........................................................72

3.1 Current consumption vs. memory partitions.................. 72

3.2 Standard I/O pin configuration....................................... 73

3.3 I/O power consumption..................................................74

3.4 RTC oscillator................................................................ 74

3.4.1 RTC Printed Circuit Board (PCB) design

guidelines........................................................ 76

3.5 XTAL oscillator...............................................................76

3.5.1 XTAL Printed Circuit Board (PCB) design

guidelines........................................................ 78

3.5.2 Thermally compensated crystal oscillator

(TCXO)............................................................ 79

3.6 Suggested USB interface solutions............................... 79

4 Abbreviations........................................................................ 81

5 Pinouts.................................................................................. 81

5.1 Signal multiplexing and pinouts..................................... 81

5.2 i.MXRT500 Pinouts: 249 FOWLP package................... 82

5.3 i.MX RT500 Pinouts: 141 CSP package........................97

5.4 249-pin FOWLP and 141-pin WLCSP ballmaps............106

5.5 Termination of unused pins........................................... 107

5.6 Pin states in different power modes...............................108

5.7 Obtaining package dimensions......................................108

6 Power supply for pins............................................................108

7 Revision history.....................................................................110

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

9

NXP Semiconductors

Page 10

Electrical characteristics

Electrical characteristics

1

1.1 Chip-level conditions

This section provides the device-level electrical characteristics for the IC. See the

following table for a quick reference to the individual tables and sections.

Table 1. i.MX RT500 chip-level conditions

For these charateristics Topic appears

Absolute maximum voltage and current ratings Absolute maximum voltage and current ratings

Thermal handling ratings Thermal handling ratings

Moisture handling ratings Moisture handling ratings

ESD handling ratings ESD handling ratings

Thermal characteristics Thermal characteristics

General operating conditions General operating conditions

I/O parameters I/O parameters

Power consumption operating behavior Power consumption operating behavior

1.1.1 Thermal handling ratings

Symbol Description Min. Max. Unit Notes

T

STG

T

SDR

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

Storage temperature — 150 °C 1

Solder temperature, lead-free — 260 °C 2

1.1.2 Moisture handling ratings

Symbol Description Min. Max. Unit Notes

MSL Moisture sensitivity level (FOWLP) — 3 — 1

MSL Moisture sensitivity level (WLCSP) — 1 — 1

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

10

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 11

Electrical characteristics

1.1.3 ESD handling ratings

Symbol Description Min. Max. Unit Notes

V

HBM

V

CDM

I

LAT

1. Determined according to JEDEC Standard JESD22-A114, Electrostatic Discharge (ESD) Sensitivity Testing Human

Body Model (HBM).

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for

Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

3. Determined according to JEDEC Standard JESD78, IC Latch-Up Test.

Electrostatic discharge voltage, human body model -2000 2000 V 1

Electrostatic discharge voltage, charged-device

model

Latch-up current at ambient temperature of 70 °C -100 100 mA 3

-500 500 V 2

1.1.4 Absolute maximum voltage and current ratings

Stress beyond those listed under the following table may

cause permanent damage to the device. These are stress

ratings only. Functional operation of the device at these or

any other conditions beyond those indicated under

“recommended operating conditions” is not implied.

Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability.

Table 2. Absolute maximum ratings1

Symbol Parameter Conditions Notes Min. Max. Unit

VDD_AO1V8 Supply 1.8 V

supply for

“always on”

features

VDD1V8 1.8 V supply

voltage for onchip analog

functions

other than the

ADC and

comparator.

VDD1V8_1 1.8 V supply

voltage for onchip digital

logic

Caution

- 2 -0.3 1.98 V

- 2 -0.3 1.98 V

- 2 -0.3 1.98 V

Table continues on the next page...

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

11

NXP Semiconductors

Page 12

Electrical characteristics

Table 2. Absolute maximum ratings1 (continued)

Symbol Parameter Conditions Notes Min. Max. Unit

VDDCORE 1.1 V input

supply for

core logic

VDDIO_0/1/2/4 Supply

voltage for

GPIO pins

VDDIO_3 Supply

voltage for

GPIO pins

VDDA_ADC1V8 1.8 V analog

supply voltage

for ADC and

comparator

VDDA_BIAS Bias voltage

for ADC and

comparator

VREFP ADC positive

reference

voltage

USB1_VDD3V3 USB1 analog

3.3 V supply

USB1_VBUS USB1_VBUS

detection

MIPI_DSI_VDD11 MIPI DSI 1.1

V PHY input

core voltage

supply

MIPI_DSI_VDD18 MIPI DSI 1.8

V PHY IO

input voltage

supply

MIPI_DSI_VDDA_CAP MIPI DSI 1.1

V capacitor

output voltage

supply

I

DD

supply current

(FOWLP249)

supply current

(WCLSP141)

On-chip regulator

not used.

LDO_ENABLE=0.

Power supplied

by an off-chip

power

management IC

(PMIC).

- 2 -0.3 1.98 V

- 2 -0.3 3.96 V

- 2 -0.3 1.98 V

- 2 -0.3 3.96 V

- 2 -0.3 1.98 V

- 2 -0.3 3.96 V

- - -0.3 5.6 V

- - -0.3 1.155 V

- - -0.3 1.98 V

- - -0.3 1.155 V

per supply pin,

1.71 V ≤ VDD <

3.6 V

per supply pin,

1.71 V ≤ VDD <

3.6 V

2 -0.3 1.155 V

3 - 100 mA

3 - 100 mA

12

NXP Semiconductors

Table continues on the next page...

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 13

Table 2. Absolute maximum ratings1 (continued)

Symbol Parameter Conditions Notes Min. Max. Unit

I

I

latch

P

tot(pack)

SS

ground current

(FOWLP249)

ground current

(WLCSP141)

I/O latch-up

current

total power

dissipation

(per package)

total power

dissipation

(per package)

per ground pin,

1.71 V ≤ VDD <

3.6 V

per ground pin,

1.71 V ≤ VDD <

3.6 V

-(0.5VDD) < VI <

(1.5VDD);

Tj < 105 °C

FOWLP 249,

based on

package heat

transfer, not

device power

consumption

WLCSP141 - 1.42 W

Thermal specifications

3 - 100 mA

3 - 100 mA

- 100 mA

4 - 1.86 W

1. In accordance with the Absolute Maximum Rating System (IEC 60134). The following applies to the limiting values:

• This product includes circuitry specifically designed for the protection of its internal devices from the damaging

effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid

applying greater than the rated maximum.

• Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect

to VSS unless otherwise noted.

• The limiting values are stress ratings only and operating the part at these values is not recommended and

proper operation is not guaranteed. The conditions for functional operation are specified in Table 1.

2. Maximum/minimum voltage above the maximum operating voltage (see Table 1) and below ground that can be

applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of

reliability and shorter lifetime of the device.

3. The peak current should not exceed the total supply current.

4. Determined in accordance to JEDEC JESD51-2A natural convection environment (still air).

1.1.5

1.1.5.1

Thermal specifications

Thermal operating requirements

Table 3. Thermal operating requirements

Symbol Description Min. Max. Unit Notes

T

j

T

A

Die junction

temperature

Ambient

temperature

-20 105 °C 1

-20 70 °C 1

1. Maximum TA can be exceeded only if the user ensures that TJ does not exceed maximum TJ. The simplest method to

determine TJ is: TJ = TA + R

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

× chip power dissipation.

ΘJA

NXP Semiconductors

13

Page 14

Thermal specifications

1.1.5.2 Thermal characteristics

The average chip junction temperature, Tj (°C), can be calculated using the following

equation:

(1)

• T

• R

= ambient temperature (°C),

amb

= the package junction-to-ambient thermal resistance (°C/W)

th(j-a)

• PD = sum of internal and I/O power dissipation

The internal power dissipation is the product of IDD and VDD. The I/O power dissipation

of the I/O pins is often small and many times can be negligible. However it can be

significant in some applications.

Table 4. Thermal resistance1

Symbol Parameter Conditions Max/Min Unit

249 FOWLP Package

R

R

R

R

th(j-a)

Ψ(JT)

th(j-a)

Ψ(JT)

thermal resistance from

junction to ambient

thermal resistance from

junction to package top

thermal resistance from

junction to ambient

thermal resistance from

junction to package top

JESD51-9, 2s2p, still

air

JESD51-9, 2s2p, still

air

141 WCLSP Package

JESD51-9, 2s2p, still

air

JESD51-9, 2s2p, still

air

29.6 °C/W

0.2 °C/W

35.3 °C/W

0.1 °C/W

1. Determined in accordance to JEDEC JESD51-2A natural convection environment (still air). Thermal resistance data in

this report is solely for a thermal performance comparison of one package to another in a standardized specified

environment. It is not meant to predict the performance of a package in an application-specific environment

1.1.6 General operating conditions

T

= -20 °C to +70 °C, unless otherwise specified.

amb

Table 5. General operating conditions

Symbol Parameter Conditions Min. Typ.

f

clk

14

NXP Semiconductors

CPU (CortexM33) clock

frequency

- - - 200 MHz

Table continues on the next page...

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

1

Max. Unit

Page 15

Table 5. General operating conditions (continued)

Symbol Parameter Conditions Min. Typ.

CPU (CortexM33) clock

frequency

f

clk

DSP clock

frequency

GPU clock

frequency

VDD_AO1V8 Supply 1.8 V

supply for

“always on”

features.

VDD1V8 1.8 V supply

voltage for onchip analog

functions other

than the ADC

and comparator

VDD1V8_1

2

1.8 V supply

voltage for onchip digital

logic

VDDCORE3, 4, 5, 61.1 V supply for

core logic. Onchip regulator

not used.

LDO_ENABLE

=0. Power

supplied by an

off-chip power

management

IC (PMIC).

VDDCORE

3

1.1 V supply for

core logic. Onchip regulator

not used.

LDO_ENABLE

=0. Power

supplied by an

off-chip power

management

IC (PMIC).

VDDIO_0/1/2/4 supply voltage

for GPIO rail

For USB high-speed device

90 - 200 MHz

and host operations

For OTP programming only - - 120 MHz

- - - 200 MHz

- - - 200 MHz

- 1.71 - 1.89 V

- 1.71 - 1.89 V

- 1.71 - 1.89 V

Retention mode 0.6 - 1.155 V

Active Mode (M33 Max

Freq = 60 MHz, FBB)

Active Mode (M33 Max

7

0.7 - - V

0.8 V

Freq = 100 MHz, FBB)

Active Mode (M33 Max

0.9 - - V

Freq = 192 MHz, FBB)

Active Mode (M33 Max

1.0 - - V

Freq = 230 MHz8, FBB)

Active Mode (M33 Max

1.1 - - V

Freq = 275 MHz8, FBB)

Retention mode 0.6 - 1.155 V

Active Mode (DSP Max

Freq = 60 MHz, FBB)

Active Mode (DSP Max

7

0.7 - - V

0.8 V

Freq = 100 MHz, FBB)

Active Mode (DSP Max

0.9 - - V

Freq = 192 MHz, FBB)

Active Mode (DSP Max

1.0 - - V

Freq = 230 MHz8, FBB)

Active Mode (DSP Max

1.1 - - V

Freq = 275 MHz8, FBB)

- 1.71 - 1.89 V

Thermal specifications

1

Max. Unit

Table continues on the next page...

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

15

NXP Semiconductors

Page 16

Thermal specifications

Table 5. General operating conditions (continued)

Symbol Parameter Conditions Min. Typ.

VDDIO_3 supply voltage

for GPIO rail

VDDA_1V8 1.8 V analog

supply voltage

for ADC and

comparator

VDDA_BIAS

9

Bias for ADC

and comparator

VREFP ADC positive

reference

voltage

USB1_VDD3V3 USB1 analog

3.3 V supply

USB0_VBUS USB0_VBUS

detection

MIPI_DSI_VDD11 MIPI DSI 1.1V

digital core

input voltage

supply

MIPI_DSI_VDD18 MIPI DSI 1.8V

PHY IO input

voltage supply

MIPI_DSI_VDDA_CAPMIPI DSI 1.1V

digital core

output voltage

supply

- 1.71 - 3.6 V

- 1.71 - 1.89 V

- 1.71 - 3.6 V

- 1.71 - 1.89 V

- 3.0 - 3.6 V

- 4.010 or 3.0

, 11

- 0.85 - 1.155 V

- 1.71 - 1.89 V

- -0.3 - 1.155 V

1

Max. Unit

5.0 5.5 V

1. Typical ratings are not guaranteed. The values listed are for room temperature (25 °C), nominal supply voltages.

2. 1.8 V supply voltage for on-chip digital logic during active mode. In deep-sleep mode, this pin can be powered off to

conserve additional current (~20 uA).

3. The maximum frequency for the specified VDDCORE voltage is the frequency of the main clock. This is before the CPU

CLOCK Divider. The VDDCORE voltage has to be set according to the chosen main clock frequency.

4. When LDO_ENABLE is externally tied low, the user must boot at VDDCORE = 1.0 V or higher (Low power/Normal clock

mode - OTP setting - BOOT_CLK_SPEED) or VDDCORE = 1.13 V (High Speed clock - OTP setting BOOT_CLK_SPEED). Thereafter, the VDDCORE can be adjusted to the desired level.

5. When LDO_ENABLE is externally tied high, the on-chip regulator to the VDDCORE Core voltage in PMC is set to the

default value 1.05 V (Low power/Normal clock mode - OTP setting - BOOT_CLK_SPEED) or 1.13 V (High Speed clock OTP setting - BOOT_CLK_SPEED). Thereafter, the POWER_SetLdoVoltageForFreq API function can be used to

internally configure the on-chip regulator voltage to the VDDCORE.

6. When performing any OTP read/write function, the VDDCORE voltage must be set to 1.0 V or higher when

LDO_ENABLE is externally tied high or low.

7. GPU, SPI, and CTIMER are disabled.

8. Although i.MX RT500 is targeted to operate up to 200 MHz for low power operation, it can operate up to 275 MHz;

however, there will be an increase in current consumption.

9. VDD_BIAS must be equal to maximum ADC input voltage or maximum comparator input voltage.

10. The USB PHY provides two options for reporting VBUS valid back to the USB controller:

• A programmable internal VBUS_VALID comparator (the default option), or

• An alternate VBUS_VALID_3V detector that will report VBUS valid for voltages above 3 V

16

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

NXP Semiconductors

Page 17

Thermal specifications

USBPHY_USB1_VBUS_DETECTn[VBUSVALID_SEL] selects which option is used. If the VBUS_VALID comparator is

used, USBPHY_USB1_VBUS_DETECTn[VBUSVALID_THRESH] determines the threshold voltage for a valid VBUS.

The programmable range is 4.0V to 4.4V (default).

11. The USB PHY provides two options for reporting VBUS valid back to the USB controller:

• A programmable internal VBUS_VALID comparator (the default option), or

• An alternate VBUS_VALID_3V detector that will report VBUS valid for voltages above 3 V

USBPHY_USB1_VBUS_DETECTn[VBUSVALID_SEL] selects which option is used. If the VBUS_VALID_3V detector

is used, the detector voltage is not programmable.

1.1.7 I/O parameters

1.1.7.1 I/O DC parameters

T

= -20 °C to +70 °C, unless otherwise specified. Values tested in production unless otherwise specified.

amb

Table 6. I/O DC characteristics

Sym

bol

VIHHIGH-level input

VILLOW-level input

VOHHIGH-level output

VOLLOW-level output

V

hys

IILLOW-level input

I

IH

Parameter Conditions Notes Min. Typ.

RESET pin, LDO_ENABLE pin, PMIC_IRQ_N pin, PMIC_MODE pins

0.7 x VDD_AO1V8 - VDD_AO1V8 V

voltage

-0.3 - 0.3 x

voltage

IOL = -2.9 mA;

voltage

voltage

hysteresis voltage 2 - 0.06 x

current

HIGH-level input

current

1.71 V ≤ VDD_AO1V8

< 1.89 V

IOL = 2.9 mA;

1.71 V ≤ VDD_AO1V8

< 1.89 V

Standard I/O pins and PMIC I2C pins

Input characteristics

VI = 0 V; on-chip pullup resistor disabled.

1.71 V ≤ VDD < 1.98 V

VI = 0 V; on-chip pull-

up resistor disabled.

3.0 V ≤ VDD < 3.6 V

VI = VDD; on-chip pull-

down resistor disabled.

1.71 V ≤ VDD < 1.98 V

VI = VDD; on-chip pull-

down resistor disabled.

3.0 V ≤ VDD < 3.6 V

0.8 x VDD_AO1V8 - - V

- - 0.2 x

-1 - 1 μA

-1 - 1 μA

-1 0.5 1 μA

-1 0.5 1 μA

VDD_AO1V8

1

Max. Unit

VDD_AO1V8

VDD_AO1V8

- V

V

V

Table continues on the next page...

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

17

NXP Semiconductors

Page 18

Thermal specifications

Table 6. I/O DC characteristics (continued)

Sym

Parameter Conditions Notes Min. Typ.

bol

VIinput voltage pin configured to

3

provide a digital

function, except the

following pins:

V

= 0 V

DDIO

VIHHIGH-level input

voltage

VILLOW-level input

voltage

V

hysteresis voltage 1.71 V ≤ VDD < 1.98 V 2 0.15 - - V

hys

1.71 V ≤ VDD < 1.98 V 0.7 x VDDIO - VDDIO V

3.0 V ≤ VDD ≤ 3.6 V 0.7 x VDDIO - VDDIO V

1.71 V ≤ VDD < 1.98 V -0.3 - 0.3 x VDDIO V

3.0 V ≤ VDD ≤ 3.6 V -0.3 - 0.7 V

0 - 3.6 V

3.0 V ≤ VDD ≤ 3.6 V 2 0.15 - - V

Output characteristics

V

HIGH-level output

OH

voltage (Normal

drive)

IOH = -2.9 mA;

1.71 V ≤ VDD < 1.98 V

IOH = -4 mA;

0.8 x VDDIO - - V

0.8 x VDDIO - - V

3.0 V ≤ VDD ≤ 3.6 V

V

HIGH-level output

OH

voltage (Full drive)

IOH = -5.8 mA;

1.71 V ≤ VDD < 1.98 V

IOH = -8 mA;

0.8 x VDDIO - - V

0.8 x VDDIO - - V

3.0 V ≤ VDD ≤ 3.6 V

VOLLOW-level output

voltage (Normal

Drive)

IOL = 2.9 mA;

1.71 V ≤ VDD < 1.98 V

IOL = 4 mA;

- - 0.2 x VDDIO V

- - 0.2 x VDDIO V

3.0 V ≤ VDD ≤ 3.6 V

LOW-level output

voltage (Full Drive)

IOL = 5.8 mA;

1.71 V ≤ VDD < 1.98 V

IOL = 8 mA;

- - 0.2 x VDDIO V

- - 0.2 x VDDIO V

3.0 V ≤ VDD ≤ 3.6 V

Weak input pull-up/pull-down characteristics

Ipdpull-down current VI = V

DD

34 - 180 μA

VI = 3.6 V 4 72 - 180 μA

Ipupull-up current VI = 0 V -34 - -180 μA

Rpdpull-down

20 - 50 kΩ

resistance

Rpupull-up resistance 20 - 50 kΩ

1

Max. Unit

1. Typical ratings are not guaranteed. The values listed are at room temperature (25 C), nominal supply voltage.

2. Guaranteed by design, not tested in production.

18

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

NXP Semiconductors

Page 19

Thermal specifications

3. All GPIO pins are fail safe up to 3.6 V when VDDIO supply = 0 V except following pins: PIO1_18 to PIO1_29, PIO1_30

to PIO1_31, PIO2_0 to PIO2_8, PIO2_24 to PIO2_31, PIO3_8 to PIO3_18, PIO4_11 to PIO4_17, and PIO5_15 to

PIO5_18.

4. Based on characterization. Not tested in production.

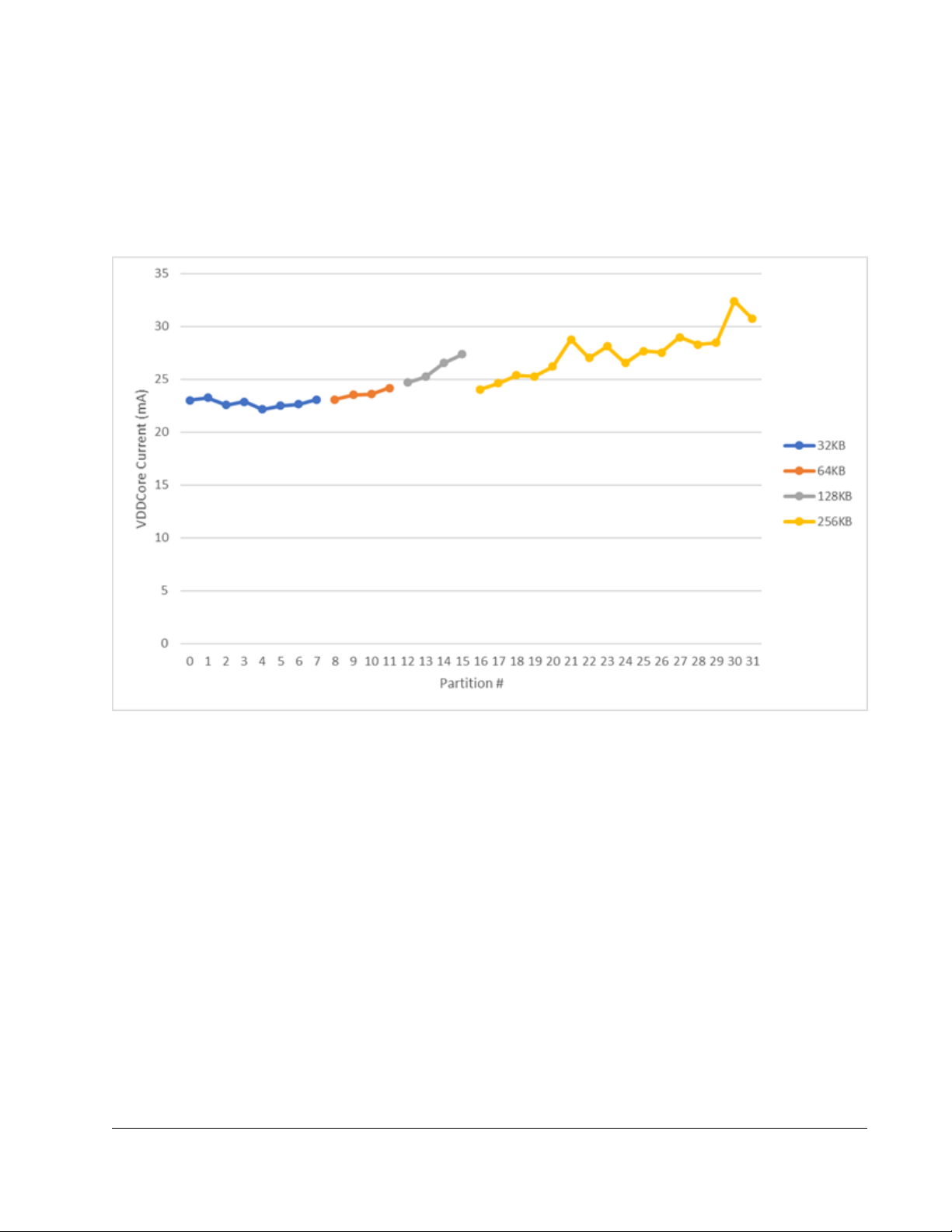

1.1.8 Power consumption operating behavior

NOTE

For the lowest power consumption, use the lowest SRAM

partition number.

T

= -20 °C to +70 °C, unless otherwise specified.

amb

Table 7. Power consumption in active mode

Symbol Parameter Conditions Notes Min. Typ.1,

Cortex M33 in Active mode, DSP no clock

enhanced while (1) code executed from SRAM partition 305; Internal LDO disabled

I

DDVDDCORE

VDDCORE supply

current

HCLK = 12 MHz

VDDCORE = 0.7 V

HCLK = 24 MHz

VDDCORE = 0.7 V

HCLK = 48 MHz

VDDCORE = 0.7 V

HCLK = 96 MHz

VDDCORE = 0.8 V

HCLK = 192 MHz

VDDCORE = 0.9 V

HCLK = 192 MHz

VDDCORE = 1.0 V

HCLK = 192 MHz

VDDCORE = 1.1 V

4

6 - 1.62 - mA

6 - 2.50 - mA

6 - 4.33 - mA

6 - 9.35 - mA

6 - 20.73 - mA

6 - 23.97 - mA

6 - 28.01 - mA

2, 3

Max. Unit

1. Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C). VDD_AO1V8 = VDD1V8 =

VDDIO_0/1/2/3/4 = VDDA_ADC1V8 = 1.8 V. VDDA_BIAS = VREFP = 1.8 V. USB1_VDD3V3 = 3.3

2. Characterized through bench measurements using typical samples.

3. Compiler settings: IAR C/C++ Compiler for Arm ver 8.40.1. High, Speed, No Size Constraints. The optimization level is

Low, Balanced.

4. Based on the power API library from the SDK software package available on nxp.com

5. SRAM partition 30 represents the worst case partition.

6. FRO clock source, FBB enabled

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

NXP Semiconductors

19

Page 20

Thermal specifications

T

= -20 °C to +70 °C, unless otherwise specified.

amb

Table 8. Power consumption in active mode

Symbol Parameter Conditions Min Typ1, 2,3Max Unit

Cortex M33 in Active mode, DSP no clock

CoreMark code executed from SRAM partition 30

I

DDVDDCORE

VDDCORE supply

current

HCLK = 12 MHz

VDDCORE = 0.7 V

HCLK = 24 MHz

4

5

- 1.61 - mA

- 2.51 - mA

VDDCORE = 0.7 V

HCLK = 48 MHz

- 4.26 - mA

VDDCORE = 0.7 V

HCLK = 96 MHz

- 9.28 - mA

VDDCORE = 0.8 V

HCLK = 192 MHz

- 20.44 - mA

VDDCORE = 0.9 V

HCLK = 192 MHz

- 23.73 - mA

VDDCORE = 1.0 V

HCLK = 192 MHz

- 27.87 - mA

VDDCORE = 1.1 V

1. Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C). VDD_AO1V8 = VDD1V8 =

VDDIO_0/1/2/3/4 = VDDA_ADC1V8 = 1.8 V. VDDA_BIAS = VREFP = 1.8 V. USB1_VDD3V3 = 3.3 V

2. Characterized through bench measurements using typical samples.

3. Compiler settings: IAR C/C++ Compiler for Arm ver 8.40. High Speed, No Size constraints. The optimization level is

Low, Balanced.

4. Based on the power API library from the SDK software package available on nxp.com

5. SRAM partition 30 represents the worst case partition.

T

= -20 °C to +70 °C, unless otherwise specified.

amb

Table 9. Power consumption in active mode

Symbol Parameter Conditions Notes Min Typ1, 2,

FFT code executed from SRAM partition 30 and 314; Internal LDO disabled

DSP in Active mode, M33 in WFI

I

DDVDDCORE

VDDCORE

supply current

20

NXP Semiconductors

5

HCLK = 10 MHz

6 - 1.80 - mA

VDDCORE = 0.7 V

HCLK = 40 MHz 6 5.30 mA

Table continues on the next page...

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

3

Max Unit

Page 21

Thermal specifications

Table 9. Power consumption in active mode (continued)

Symbol Parameter Conditions Notes Min Typ1, 2,

VDDCORE = 0.8 V

HCLK = 100 MHz

6 - 10.74 - mA

VDDCORE = 0.8 V

HCLK = 150 MHz

6 - 17.81 - mA

VDDCORE = 0.9 V

HCLK = 200 MHz

6 - 22.94 - mA

VDDCORE = 0.9 V

1. Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C). VDD_AO1V8 = VDD1V8 =

VDDIO_0/1/2/3/4 = VDDA_ADC1V8 = 1.8 V. VDDA_BIAS = VREFP = 1.8 V. USB1_VDD3V3 = 3.3 V

2. Characterized through bench measurements using typical samples.

3. Compiler settings: IAR C/C++ Compiler for Arm ver 8.40. High Speed, No Size constraints. The optimization level is

Low, Balanced.

4. SRAM partitions 30 and 31 represent the worst case partitions. The Fusion F1 DSP requires DRAM and IRAM in

different partitions. DSP_DRAM is in partition 30, DSP_IRAM is in partition 31.

5. Based on the power API library from the SDK software package available on nxp.com

6. PLL clock source, FBB enabled

3

Max Unit

Table 10. Power consumption in sleep mode

Symbol Parameter Conditions Notes Min. Typ. Max. Unit

Cortex-M33 in Sleep mode, DSP no clock

I

DDVDDCORE

supply

current

HCLK=12 MHz

VDDCORE=0.7 V

HCLK=12 MHz

VDDCORE=1.0 V

HCLK=24 MHz

VDDCORE=1.0 V

HCLK=48 MHz

VDDCORE=1.0 V

HCLK=96 MHz

VDDCORE=1.0 V

HCLK=192 MHz

VDDCORE=0.9 V

HCLK=192 MHz

VDDCORE=1.0 V

1. 256 KB SRAM, internal LDO enabled

2. All peripheral clocks gated

3. PLL disabled

4. FRO used as clock source

5. IAR C/C++ Compiler for Arm ver 8.4.2.1.236

1

2, 3, 4, 5 - 1.8 - mA

2, 3, 4, 5 - 4.27 - mA

2, 3, 4, 5 - 4.78 - mA

2, 3, 4, 5 - 5.78 - mA

2, 3, 4, 5 - 7.78 - mA

2, 3, 4, 5 - 9.66 - mA

2, 3, 4, 5 - 11.74 - mA

T

= -20 °C to +70 °C, unless otherwise specified.

amb

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

21

NXP Semiconductors

Page 22

Thermal specifications

Table 11. Power consumption in deep sleep mode

Symbol Parameter Conditions NotesMin Typ1,

2

Max

3

Unit

I

VDD1V8

I

VDDCORE

I

VDDCORE

I

VDDCORE

supply

current

supply

current

supply

current

supply

current

Deep-sleep mode; SRAM (128 KB) powered, Internal

LDO disabled. Array On, Periphery Off

Deep-sleep mode; SRAM (32 KB) powered, Internal

LDO disabled. Array On, Periphery Off

T

= 25 °C

amb

Deep-sleep mode; SRAM (32 KB) powered, Internal

LDO disabled. Array On, Periphery Off

T

= 70 °C

amb

Deep-sleep mode; SRAM (128 KB) powered, Internal

LDO disabled. Array On, Periphery Off

T

= 25 °C

amb

Deep-sleep mode; SRAM (128 KB) powered, Internal

LDO disabled. Array On, Periphery Off

T

= 70 °C

amb

Deep-sleep mode; SRAM (5 MB) powered, Internal

LDO disabled. Array On, Periphery Off

T

= 25 °C

amb

Deep-sleep mode; SRAM (5 MB) powered, Internal

LDO disabled. Array On, Periphery Off

T

=70 °C

amb

4 - 8.5 - μA

4 - 40.7 - μA

4 - 200 μA

4 - 42.0 - μA

4 - 210 - μA

4 - 74 120 μA

4 - 432 - μA

1. Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C). All power supplies = 1.8 V,

except USB1_VDD3V3=3.3 V

2. Characterized through bench measurements using typical samples.

3. Guaranteed by characterization, not tested in production.

4. VDDCORE = 0.6 V, RBB Enabled

T

= -20 °C to +70 °C, unless otherwise specified.

amb

Table 12. Power consumption in deep sleep mode

Symbol Parameter Conditions Min Typ1,

I

VDD_AO1V

8

I

VDDIO_0

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

LDO disabled. Array On, Periphery Off

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

- 0.79 - μA

- 2.4 - μA

LDO disabled. Array On, Periphery Off

I

VDDIO_1

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

- 1.7 - μA

LDO disabled. Array On, Periphery Off

I

VDDIO_2

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

- 0.35 - μA

LDO disabled. Array On, Periphery Off

I

VDDIO_3

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

- 0.8 - μA

LDO disabled. Array On, Periphery Off

I

VDDIO_4

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

- 0.36 - μA

LDO disabled. Array On, Periphery Off

Table continues on the next page...

2

Max

3

Unit

22

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 23

Thermal specifications

Table 12. Power consumption in deep sleep mode (continued)

Symbol Parameter Conditions Min Typ1,

I

VDDA_1V8

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

- 11.8 - μA

2

LDO disabled. Array On, Periphery Off

I

VREFP

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

- 0.02 - μA

LDO disabled. Array On, Periphery Off

I

USB1_VDD

3V3

supply current Deep-sleep mode; SRAM (128 KB) powered, Internal

LDO disabled. Array On, Periphery Off

- 1.10 - μA

1. Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C). All power supplies = 1.8 V,

except USB1_VDD3V3=3.3 V

2. Characterized through bench measurements using typical samples.

3. Guaranteed by characterization, not tested in production.

T

= -20 °C to +70 °C, unless otherwise specified.

amb

Max

3

Unit

Table 13. Power consumption in deep power-down mode and full deep power-down modes

Symbol Parameter Conditions Min Typ1,

I

VDD_AO1

V8

supply current Full Deep power-down mode; Internal LDO disabled.

RTC Off

T

= 25 °C

amb

Full Deep power-down mode; Internal LDO disabled.

- 0.51 - μA

- 1.79 - μA

RTC Off

T

= 70 °C

amb

I

VDDIO_0

supply curent Deep power-down mode; Internal LDO disabled. RTC

- 2.4 - μA

Off

I

VDDIO_1

supply current Deep power-down mode; Internal LDO disabled. RTC

- 1.68 - μA

Off

I

VDDIO_2

supply current Deep power-down mode; Internal LDO disabled. RTC

- 0.45 - μA

Off

I

VDDIO_3

supply current Deep power-down mode; Internal LDO disabled. RTC

- 0.37 - μA

Off

I

VDDIO_4

supply current Deep power-down mode; Internal LDO disabled. RTC

- 0.44 - μA

Off

I

VDD1V8

supply current Deep power-down mode; Internal LDO disabled. RTC

- 7.8 - μA

Off

I

VREFP

supply current Deep power-down mode; Internal LDO disabled. RTC

- 0.01 - μA

Off

I

USB1_VDD

3V3

supply current Deep power-down mode; Internal LDO disabled. RTC

Off

- 1.1 - μA

2

Max

3

Unit

1. Typical ratings are not guaranteed. Typical values listed are at room temperature (25 °C). All power supplies = 1.8 V,

except USB1_VDD3V3=3.3V

2. Characterized through bench measurements using typical samples.

3. Guaranteed by characterization, not tested in production.

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

NXP Semiconductors

23

Page 24

Thermal specifications

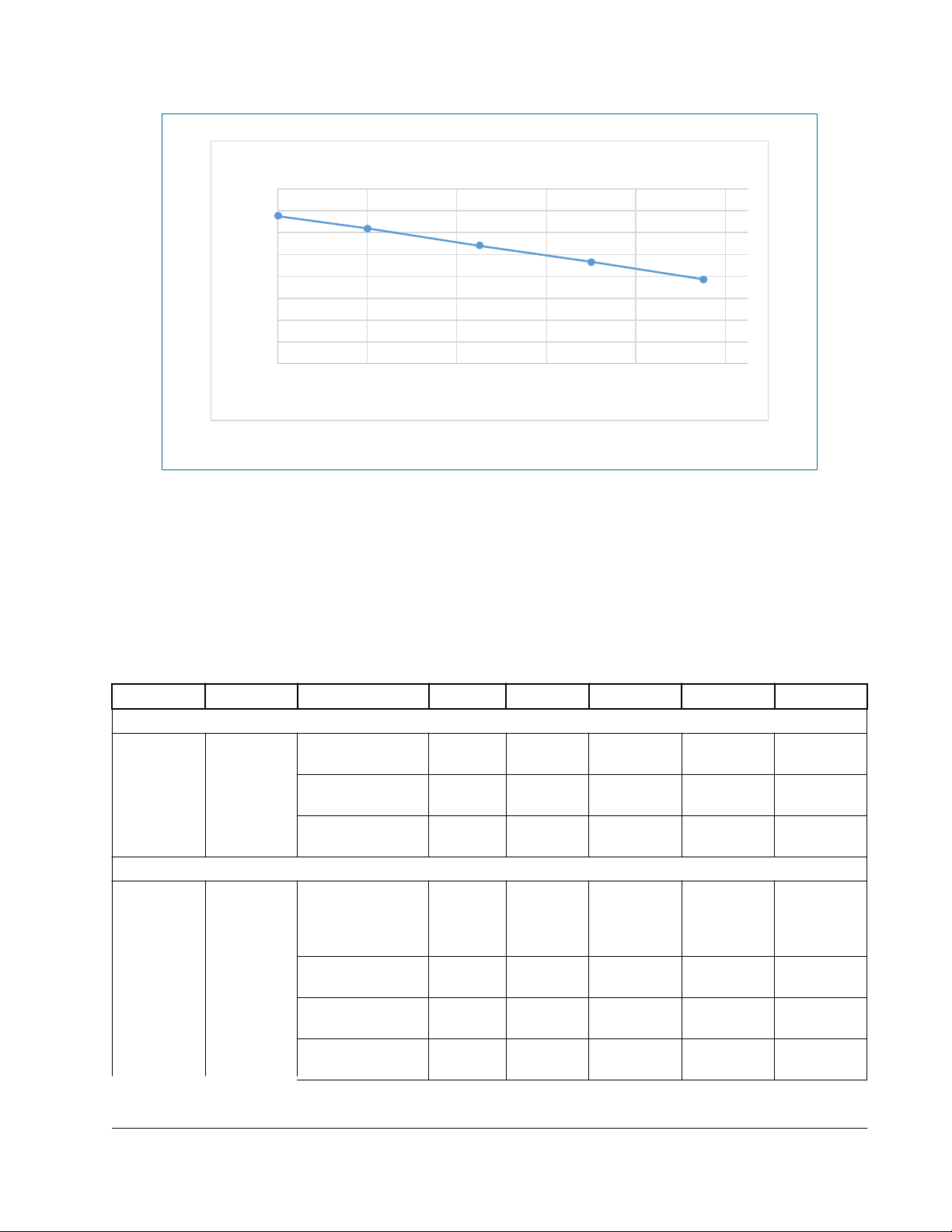

1.1.9 CoreMark data

Table 14. Coremark data

Parameters Conditions Notes Typ.1, 2,

ARM Cortex-M33 in active mode

CoreMark Score CoreMark code executed from

SRAM; HCLK = 12 MHz

HCLK = 24 MHz 4 3.85 (Iterations/s) / MHz

HCLK = 48 MHz 4 3.85 (Iterations/s) / MHz

HCLK = 96 MHz 5 3.85 (Iterations/s) / MHz

HCLK = 192 MHz 5 3.85 (Iterations/s) / MHz

1. Characterized through bench measurements using typical samples.

2. Compiler settings: IAR C/C++ Compiler for Arm ver 8.22.2, optimization level 3, optimized for time on.

3. VDD_AO1V8 = VDD1V8 = VDDIO_0/1/2/3/4 = VDDA_ADC1V8 = VREFP = 1.8 V. VDDA_BIAS = USB1_VDD3V3 = 3.3

V

4. Clock source FRO. PLL disabled

5. Clock source external clock to XTALIN (bypass mode). PLL enabled.

4 3.85 (Iterations/s) / MHz

3

Unit

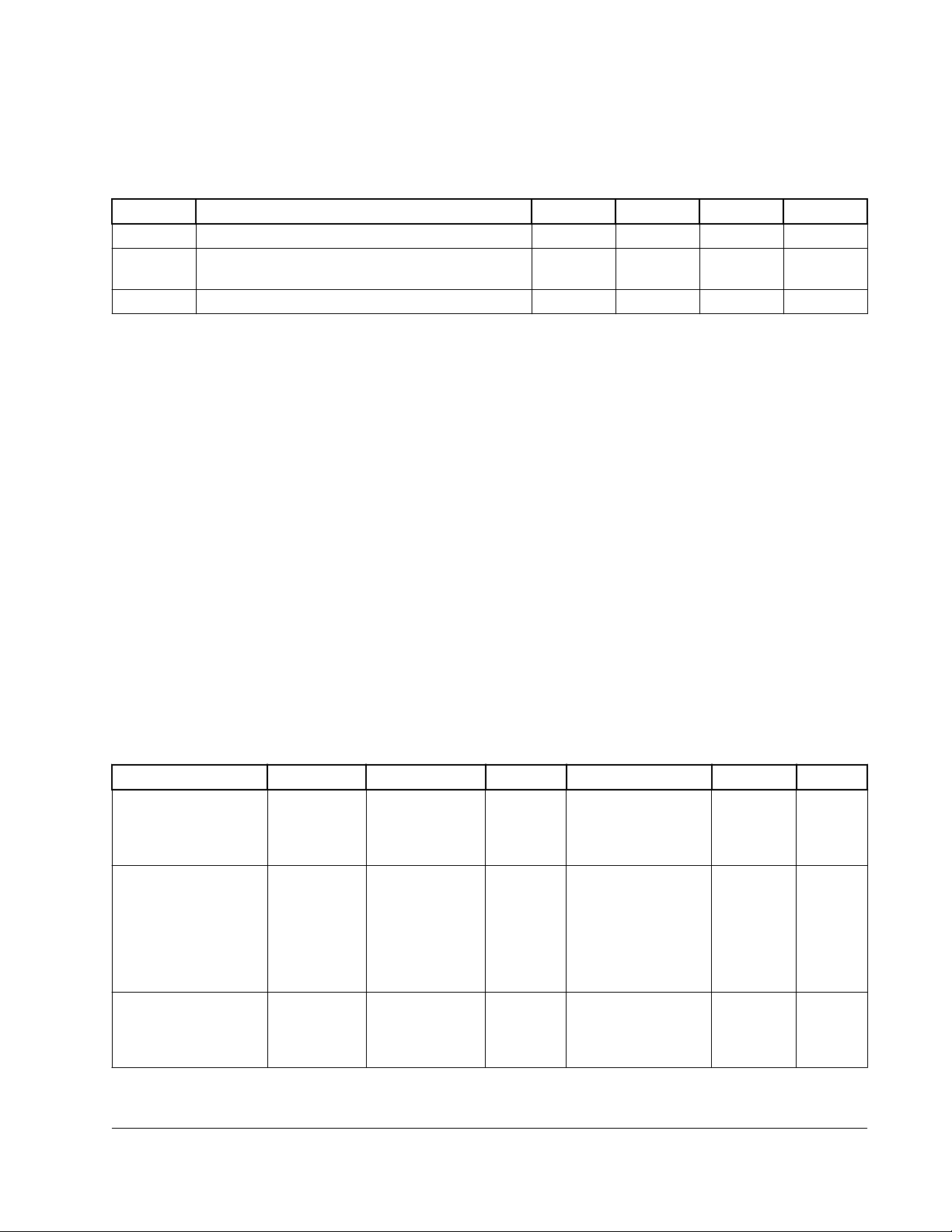

1.2 System power and clocks

1.2.1 Power sequence

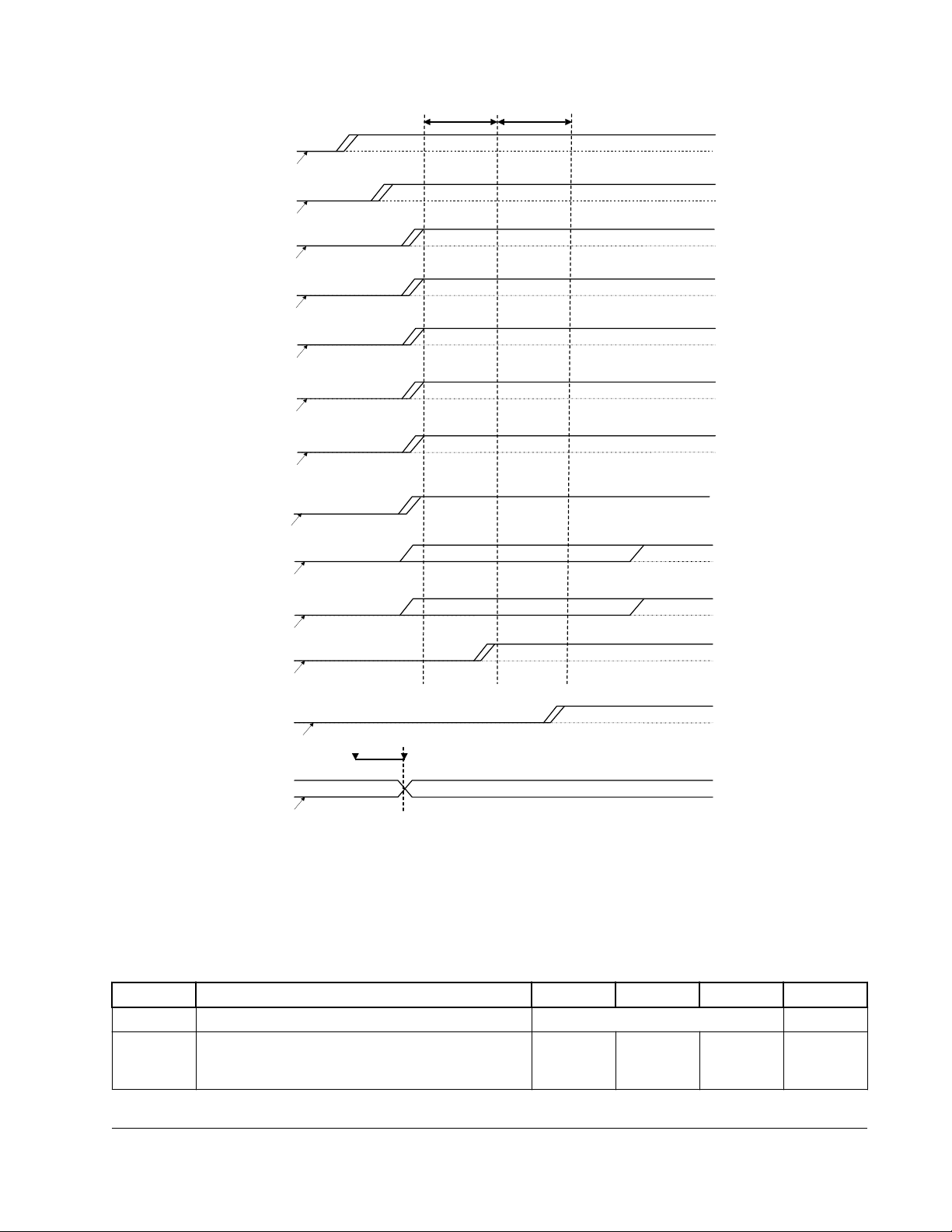

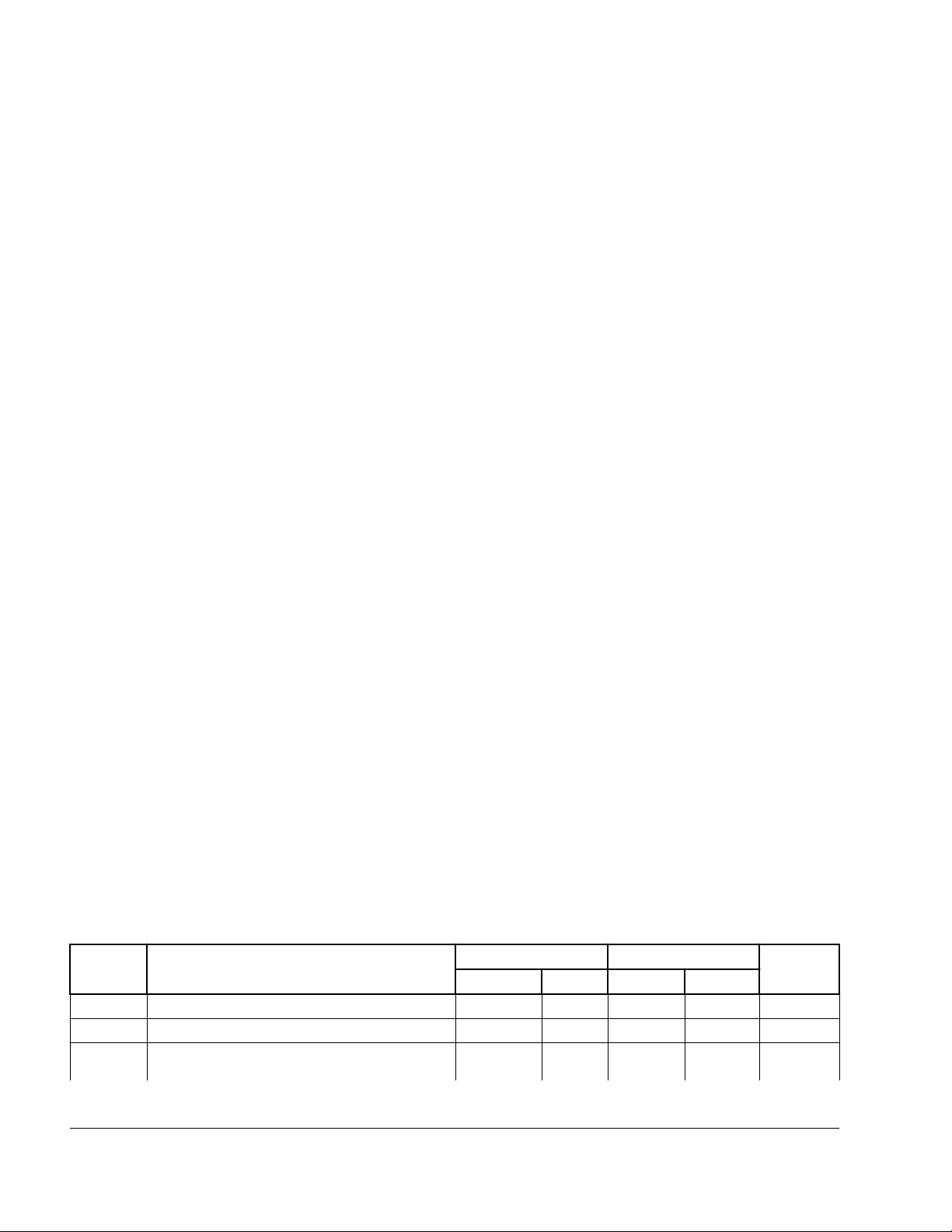

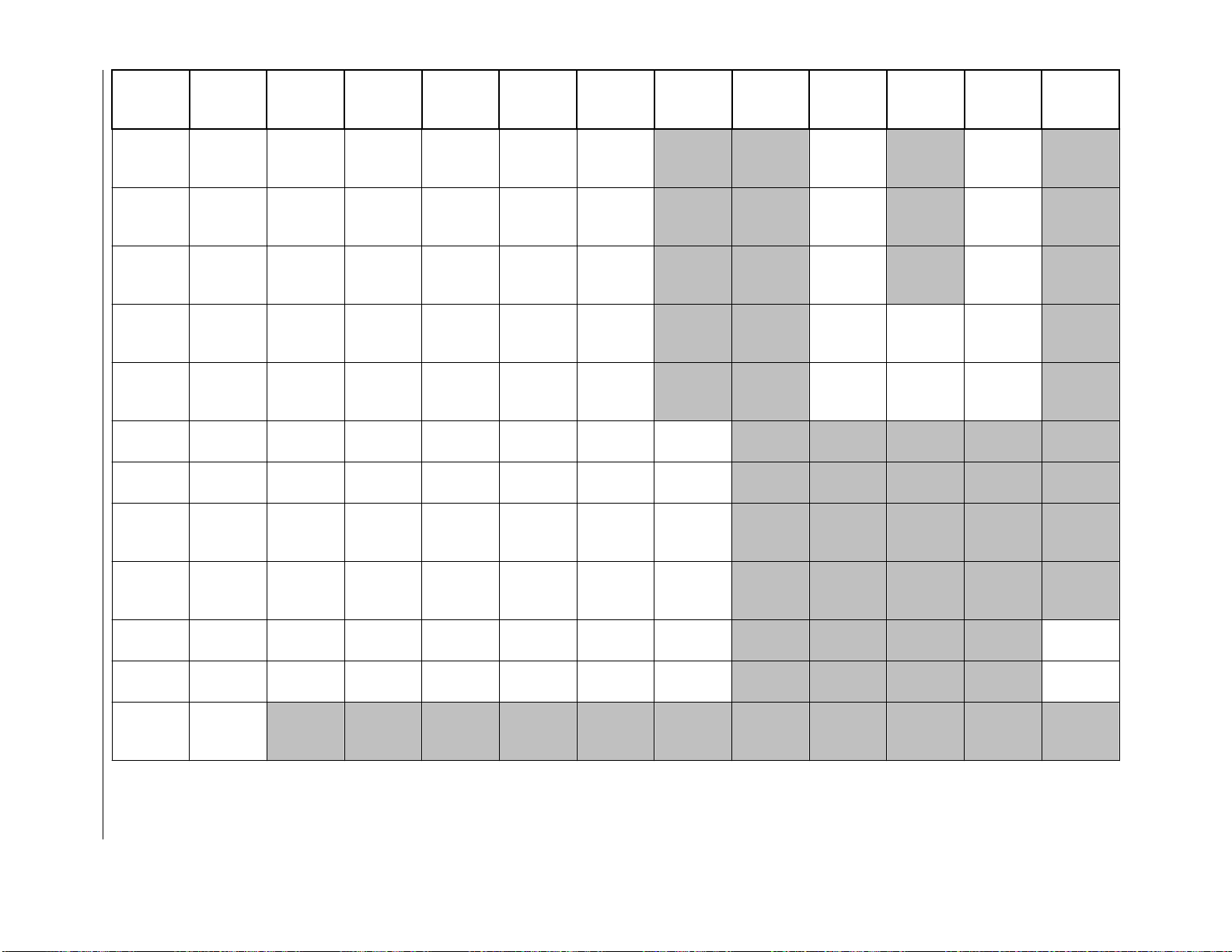

Following power-on sequence should be followed when using the internal LDO in i.MX

RT500:

1. VDD_AO1V8, VDD1V8, and VDD1V8_1 pins should be powered first. There is

no power sequence requirement between powering the VDD_AO1V8 and

VDD1V8 pins.

2. VDDA_ADC1V8 and VREFP can be powered concurrently with VDD_AO1V8

and VDD1V8 or later

3. VDDIO_x and VDDA_BIAS pins can be powered concurrently with

VDD_AO1V8 and VDD1V8 if these pins are 1.8 V range or later if these pins are

3.3 V range. If the VDDIO_x is not powered concurrently with the VDD1V8, the

delta voltage between VDDIO_x and VDD1V8 must be 1.89 V or less.

The VDDCORE pin will be supplied from the internal LDO and the LDO is powered

from the VDD1V8. An external capacitor (4.7 uF) must be connected on the

VDDCORE pin. USB1_VDD3V3 can be powered at any time, independent of the other

supplies.

24

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 25

Thermal specifications

Following power-on sequence should be followed when using an external PMIC or

external IC to drive the VDDCORE pin (internal LDO is disabled, see timing diagram

below):

1. VDD_AO1V8, VDD1V8, and VDD1V8_1 pins should be powered first. There is

no power sequence requirement between powering the VDD_AO1V8 and

VDD1V8 pins.

2. VDDA_ADC1V8 and VREFP can be powered concurrently with VDD_AO1V8

and VDD1V8 or later.

3. VDDIO_x and VDDA_BIAS pins can be powered concurrently with VDD1V8 if

these pins are 1.8 V range or later if these pins are 3.3 V range. If the VDDIO_x

is not powered concurrently with the VDD1V8, the delta voltage between

VDDIO_x and VDD1V8 must be 1.89 V or less.

4. Power up the VDDCORE. The external RESETN should be held low until

VDDCORE is valid in the timing diagram.VDDCORE should not be ramped up

until after all the other supplies have completed ramp up.

USB1_VDD3V3 can be powered at any time, independent of the other supplies.

Sequence of operations is handled internally so there is no specific timing requirement

between the supplies. The time delays caused by any of the bypass capacitors will

have no effect on the operation of the part. The internal POR detectors on

VDD_AO1V8, VDD1V8 pins, and the Low Voltage Detector on VDDCORE pin,

require a fall time of at least 10us (preliminary) to trigger. There is no restriction on

the rise time, except for the sequencing defined above.

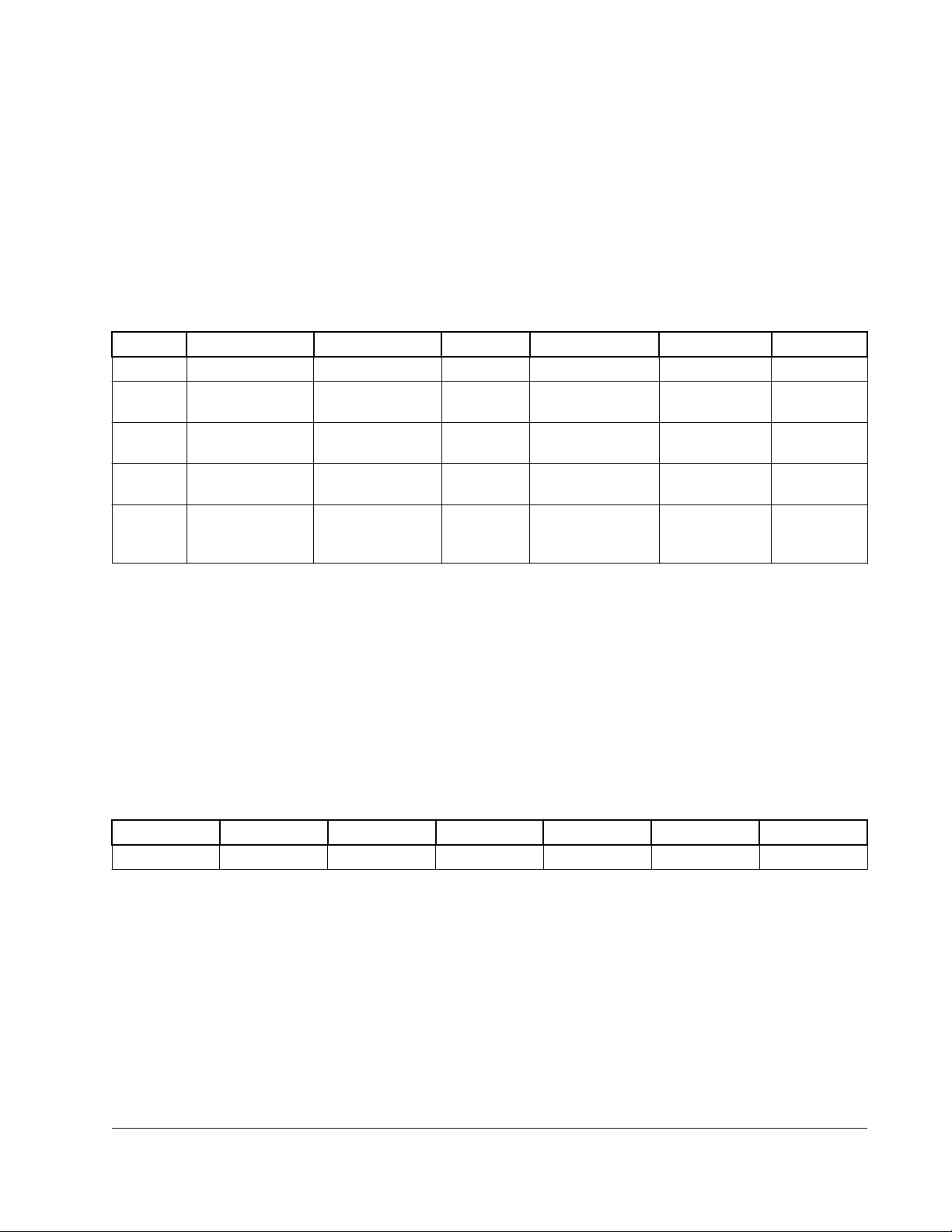

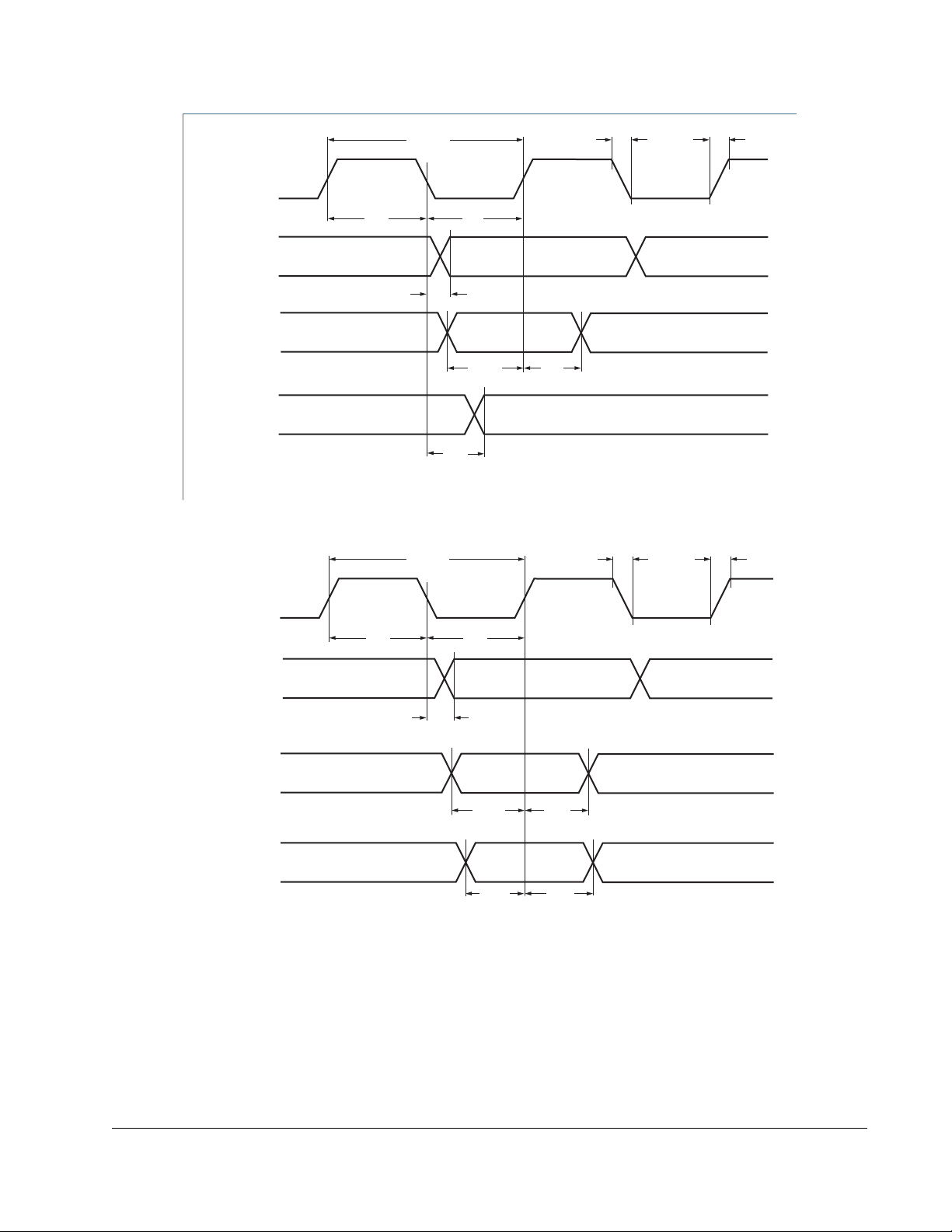

Table 15. Power-on characteristics

Symbol Timing

Parameter

A VDDIO_x valid to

VDDCORE valid

B VDDCORE valid to

De-assertion of

RESETN

AA Mode pin valid When the mode

Description Min. Max. Unit

The delay from

when the IO pad

voltages become

valid to core

voltage valid

The delay from

when the VDD

core is valid to

when the RESETN

can be released

pins becomes

valid. On power-

on, the mode pins

are reset to 00 and

are controlled via a

10 - μs

20 - μs

- 2 μs

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

25

NXP Semiconductors

Page 26

Thermal specifications

Table 15. Power-on characteristics

Symbol Timing

Parameter

Description Min. Max. Unit

POR circuit in the

always-on domain.

The timing is from

when the

VDD_AO1V8 is

valid to when the

mode pins are

reset to 00.

26

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 27

VDDIO_2

(Pad group 2 power)

VDDIO_3

(Pad group 3 power)

VDDIO_4

(Pad group 4 power)

VDDCORE

(Core Power needs DVFS

control)

VDDA_ADC1V8

(ADC/Comp power 1.8 volts)

VREFP

(ADC Ref voltage)

RESETN

(External Chip reset)

PMIC_MODE0/1

(PMIC Mode pins (outputs))

XXXXXXXXX

00

VDD_AO_1V8

(Always on voltage to RTC)

VDD1V8

(Chip PMC power)

A B

AA

VDDA_BIAS

(ADC comparator bias)

VDDIO_0

(Pad group 0 power)

VDDIO_1

(Pad group 1 power)

Thermal specifications

Figure 4. Power-up ramp

1.2.2

Free-running oscillator FRO-192/96M specifications

Table 16. FRO-192M specifications

Symbol Characteristic Min. Typ. Max. Unit

f

fro192m

Δf

fro192m

FRO-192M frequency (nominal) 192 MHz

Frequency deviation

• 1T trim (Open loop)

— — ±1 %

Table continues on the next page...

%

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

27

NXP Semiconductors

Page 28

Thermal specifications

Table 16. FRO-192M specifications (continued)

Symbol Characteristic Min. Typ. Max. Unit

t

startup

Start-up time

— 75 — μs

jit

cyc

I

fro192m

V

min

Cycle to cycle jitter — 105 — ps

Current consumption — 45 111 μA

Minimum voltage 0.8

1

— — V

1. Vmin =0.8 V is derived from FRO192 MHz divided by 2/4/8.

NOTE

Any divided versions of the FRO that are not being used

anywhere should be turned off to save power.

Table 17. FRO-96M specifications

Symbol Characteristic Min. Typ. Max. Unit

f

fro96m

Δf

t

startup

jit

I

fro96m

V

fro96m

cyc

min

FRO-96M frequency (nominal) 96 MHz

Frequency deviation

• 1T trim (Open loop)

Start-up time

— — ±1 %

— 120 — μs

Cycle to cycle jitter — 180 — ps

Current consumption — 23 63 μA

Minimum voltage 0.7

1

— — V

%

1. Vmin =0.7 V is derived from FRO96 MHz divided by 2/4/8.

1.2.3 Crystal oscillator

T

= -20 °C to +70 °C; 1.71 V ≤ V

amb

≤ 1.89 V.1,

DD

Table 18. Crystal oscillator characteristics

Symbol Parameter Min. Typ.

f

range

Rf feedback resistor

ESR Equivalent series

1. Parameters are valid over operating temperature range unless otherwise specified.

2. See XTAL oscillator

3. Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

28

NXP Semiconductors

oscillator frequency

range

high gain mode

4

only

resistance

2

3

Max. Unit

4 - 32 MHz

- 1 - MΩ

- - 80 Ω

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 29

Thermal specifications

4. CLKCTL0_SYSOSCCTL0[LP_ENABLE] = 1 sets High Gain Mode, which requires a 1 MΩ feedback resistor.

1.2.4 RTC oscillator

See RTC oscillator for connecting the RTC oscillator to an external clock source.

T

= -20 °C to +70 °C; 1.71 ≤ V

amb

Table 19. RTC oscillator characteristics

Symbol Parameter Conditions Min. Typ.

f

input frequency - - 32.768 - kHz

1

ESR Equivalent series

resistance

, 2

t

start_xtal

t

start_bypass

V

Crystal oscillator

start-up time

Bypass oscillator

2

start-up time

3

Peak-to-Peak

pp

amplitude of

oscillation

- - 50 100K kΩ

- - 250 - ms

With oscillator

bypass mode

enabled

DD

≤ 1.89

1

1 - ms

0.7 - VDD_AO1V8 V

Max. Unit

1. Typical ratings are not guaranteed. The values listed are at room temperature (25 C), nominal supply voltages.

2. Proper PCB layout procedures must be followed to achieve specifications.

3. In bypass mode, using an input square wave only on RTCXIN with RTXOUT floating.

1.2.5 External Clock Input (CLKIN) pin

T

= -20 °C to +70 °C; 1.71 V to 1.89 V

amb

Table 20. Dynamic characteristic: CLKIN

Symbol Parameter Conditions Min. Typ.

F

i

1. Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages

input frequency - - - 50 MHz

1

Max Unit

1.2.6 Internal low-power oscillator (1 MHz)

The IRC is trimmed to 10% accuracy over the entire voltage and temperature range.

T

= -20 °C to +70 °C; 1.71 ≤ V

amb

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

≤ 1.89 V

DD

29

NXP Semiconductors

Page 30

RESETN

CC1

(Input)

Thermal specifications

Table 21. LPOSC characteristics

Symbol Parameter Conditions Min Typ

f

osc (RC)

1. Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

LPOSC clock

frequency

- 0.9 1 1.1 MHz

1

Max Unit

1.3 System modules

1.3.1 Reset timing parameters

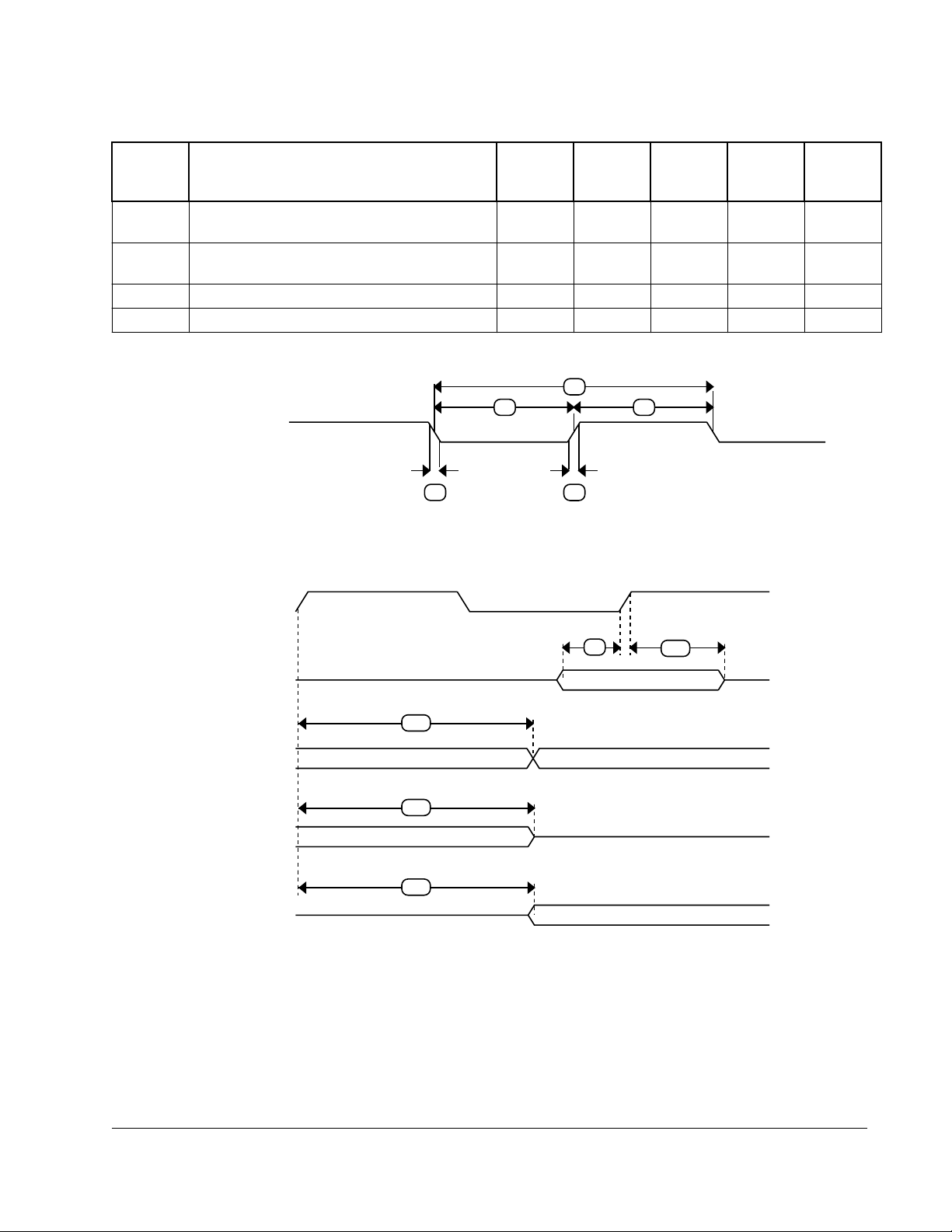

The following figure shows the reset timing and Table 22 lists the timing parameters.

Figure 5. Reset timing diagram

Table 22. Reset timing parameters

ID Parameter Min Max Unit

CC1 Duration of POR_B to

be qualified as valid

40 - ns

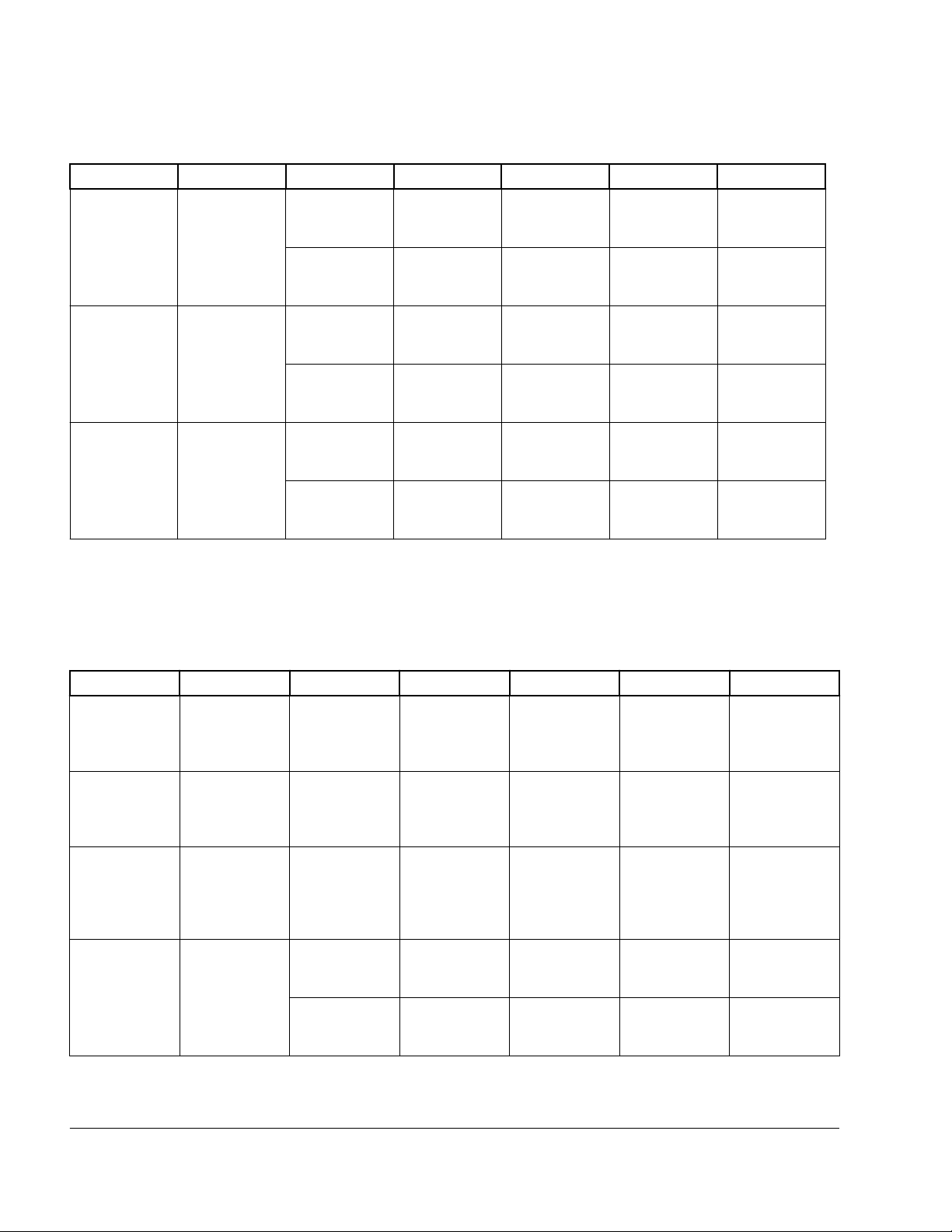

1.3.2 Serial Wire Debug (SWD) timing specifications

Table 23. SWD timing specifications

Symbol Description Min. Max. Min.—

VLPR

mode

J1 SWD_CLK frequency of operation

J2 SWD_CLK cycle period 1000/J1 — 1000/J1 — ns

J3 SWD_CLK clock pulse width

• Serial wire debug

0 25 0 10 MHz

20 — 20 — ns

Max.—

VLPR

mode

Unit

J4 SWD_CLK rise and fall times — 3 — 3 ns

Table continues on the next page...

30

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 31

Table 23. SWD timing specifications (continued)

J2

J3 J3

J4 J4

SWD_CLK (input)

J11

J12

J11

J9

J10

Input data valid

Output data valid

Output data valid

SWD_CLK

SWD_DIO

SWD_DIO

SWD_DIO

SWD_DIO

Thermal specifications

Symbol Description Min. Max. Min.—

VLPR

mode

J9 SWD_DIO input data setup time to SWD_CLK

rise

J10 SWD_DIO input data hold time after SWD_CLK

rise

J11 SWD_CLK high to SWD_DIO data valid — 37 — 37 ns

J12 SWD_CLK high to SWD_DIO high-Z 2 — 2 — ns

10 — 19 — ns

0 — 0 — ns

Max.—

VLPR

mode

Figure 6. Serial wire clock input timing

Unit

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Figure 7. Serial wire data timing

31

NXP Semiconductors

Page 32

J2

J3 J3

J4 J4

TCLK (input)

Thermal specifications

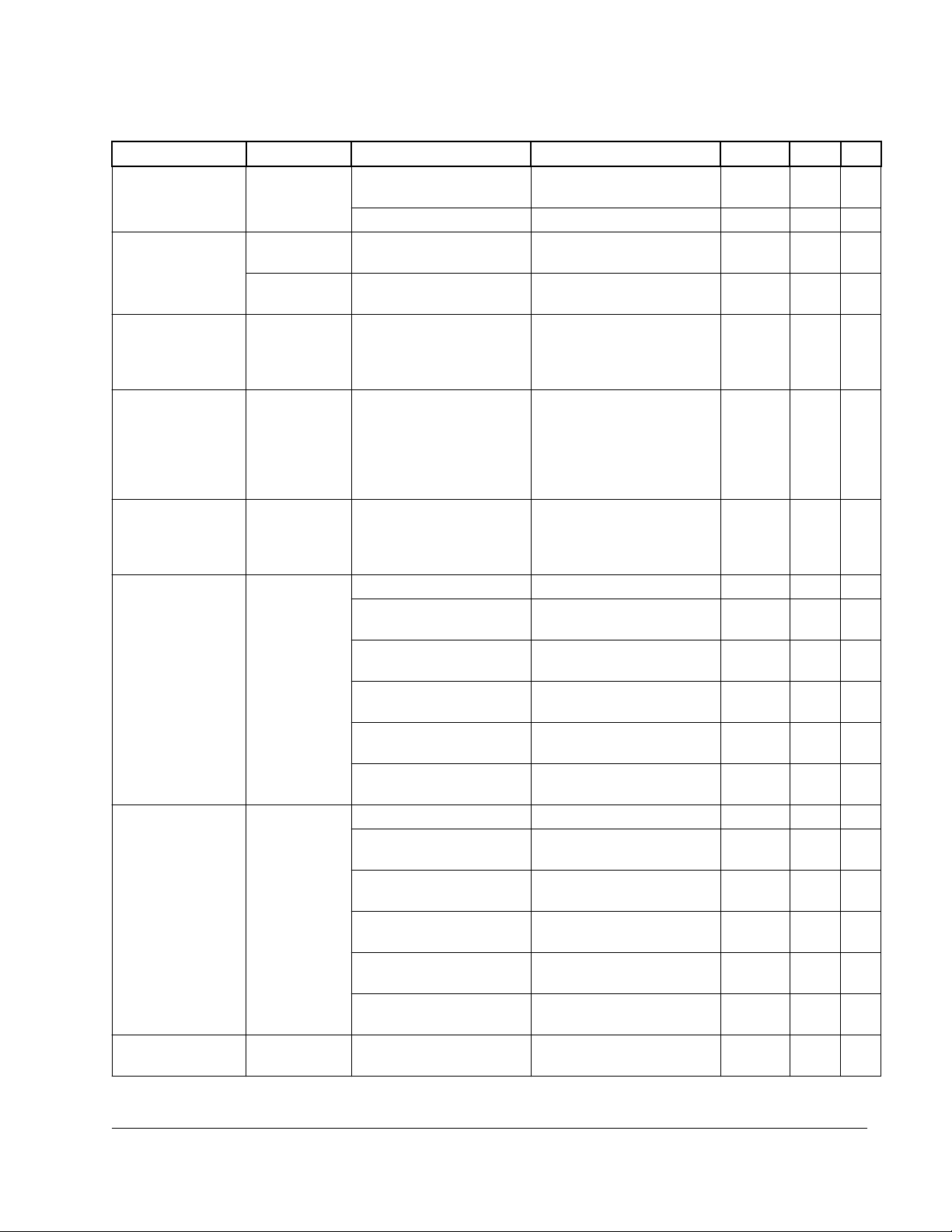

1.3.3 JTAG timing specifications

Table 24. JTAG timing specifications

Symbol Parameter Min. Max. Min.—

VLPR

mode

J1 TCLK frequency of operation

• Boundary Scan 0 10 0 10 MHz

• JTAG 0 25 0 10 MHz

J2 TCLK cycle period 1000/J1 — 1000/J1 — ns

J3 TCLK clock pulse width

• Boundary Scan 50 — 50 — ns

• JTAG 20 — 20 — ns

J4 TCLK rise and fall times — 3 — 3 ns

J5 Boundary scan input data setup time to TCLK

rise

J6 Boundary scan input data hold time after TCLK

rise

J7 TCLK low to boundary scan output data valid — 28 — 28 ns

J8 TCLK low to boundary scan output high-Z — 25 — 25 ns

J9 TMS, TDI input data setup time to TCLK rise 10.5 — 19 — ns

J10 TMS, TDI input data hold time after TCLK rise 2.5 — 2 — ns

J11 TCLK low to TDO data valid — 19 — 19 ns

J12 TCLK low to TDO high-Z 2 — 2 — ns

J13 TRST assert time 100 — 100 — ns

J14 TRST setup time (negation) to TCLK high 8 — 8 — ns

20 — 20 — ns

5 — 5 — ns

Max.—

VLPR

mode

Unit

32

NXP Semiconductors

Figure 8. Test clock input timing

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 33

J7

J8

J7

J5

J6

Input data valid

Output data valid

Output data valid

TCLK

Data inputs

Data outputs

Data outputs

Data outputs

J11

J12

J11

J9

J10

Input data valid

Output data valid

Output data valid

TCLK

TDI/TMS

TDO

TDO

TDO

Thermal specifications

Figure 9. Boundary scan (JTAG) timing

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Figure 10. Test Access Port timing

33

NXP Semiconductors

Page 34

J14

J13

TCLK

TRST

Thermal specifications

1.3.4 Wake-up process

Figure 11. TRST timing

VDD = 3.3 V;T

= 25 °C; using FRO as the system clock.

amb

Table 25. Typical wake-up times from low power modes

Symbol Parameter Conditions Notes Min. Typ.

t

wake

t

wake

t

wake

wake-up time from sleep

mode, 200

MHz

wake-up time from deep-

sleep mode,

using

RESETN.

from deepsleep mode,

using

PMIC_IRQ_N

.

wake-up time from full deep

power-down

mode, using

RESETN

from full deep

power-down

mode, using

PMIC_IRQ_N

2, 3 - 150 - μs

4 - 120 - μs

4 - 120 - μs

4 - 8.64 - ms

4 - 8.64 - ms

1

Max. Unit

1. Typical ratings are not guaranteed. The values listed are at room temperature (25 C), nominal supply voltages.

2. The wake-up time measured is the time between when a GPIO input pin is triggered to wake the device up from the low

power modes and from when a GPIO output pin is set in the interrupt service routine (ISR) wake-up handler.

3. FRO disbled, all peripherals off. PLL disabled.

4. Wake up from deep power-down causes the part to go through entire reset process. The wake-up time measured is the

time between when the Wake-Up pin is triggered to wake the device up and when a GPIO output pin is set in the reset

handler.

34

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 35

External memory interface

1.4

External memory interface

1.4.1 FlexSPI Flash interface

Tamb = -20 °C to +70 °C, VDDIO_x = 1.71 V to 1.89 V; VDDCORE = 1.13 V; CL =

5 pF balanced loading on all pins; Full Drive Mode on all pins, Input slew = 1 ns,

SLEW setting = standard mode for all pins; Parameters sampled at the 50 % level of

the rising or falling edge.

Table 26. Dynamic characteristics: FlexSPI flash interface1

Symbol Parameter Conditions Min. Typ. Max. Unit

SDR mode

f

clk

t

DS

t

DH

t

V(Q)

DDR Mode (with and without DQS)

f

clk

clock frequency Transmit — — 200 MHz

RX clock source = 0 — — 60 MHz

RX clock source = 1 — — 116 MHz

RX clock source = 3 — — 200 MHz

data set-up time RX clock source = 0

(internal dummy read

strobe and loopbacked

internally)

RX clock source = 1

(internal dummy read

strobe and loopbacked

from DQS pad)

source = 3 (external

DQS, Flash provides

read strobe)

data hold time RX clock source = 0

(internal dummy read

strobe and loopbacked

internally)

RX clock source = 1

(internal dummy read

strobe and loopbacked

from DQS pad)

source = 3 (external

DQS, Flash provides

read strobe)

data output valid

time

clock frequency Transmit — — 200 MHz

Table continues on the next page...

6 — — ns

1 — — ns

0 — 0.6 ns

1 — — ns

0 — — ns

0 — — ns

0 — 3 ns

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

35

NXP Semiconductors

Page 36

t

DStDH

fclk

t

DStDH

nternal Sample Clock

IO[0:7]

External memory interface

Table 26. Dynamic characteristics: FlexSPI flash interface1 (continued)

Symbol Parameter Conditions Min. Typ. Max. Unit

RX clock source = 0 — — 30 MHz

RX clock source = 1 — — 58 MHz

t

DS

t

DH

t

V(Q)

RX clock source = 3, with

external DQS.

data set-up time RX clock source = 0

(internal dummy read

strobe and loopbacked

internally)

RX clock source = 1

(internal dummy read

strobe and loopbacked

from DQS pad)

source = 3 (external

DQS, Flash provides

read strobe)

data hold time RX clock source = 0

(internal dummy read

strobe and loopbacked

internally)

RX clock source = 1

(internal dummy read

strobe and loopbacked

from DQS pad)

source = 3 (external

DQS, Flash provides

read strobe)

data output valid

time

— — 200 MHz

6 — — ns

1 — — ns

0 — 0.6 ns

1 — — ns

0 — — ns

0 — — ns

0 — — ns

1. Based on simulation; not tested in production.

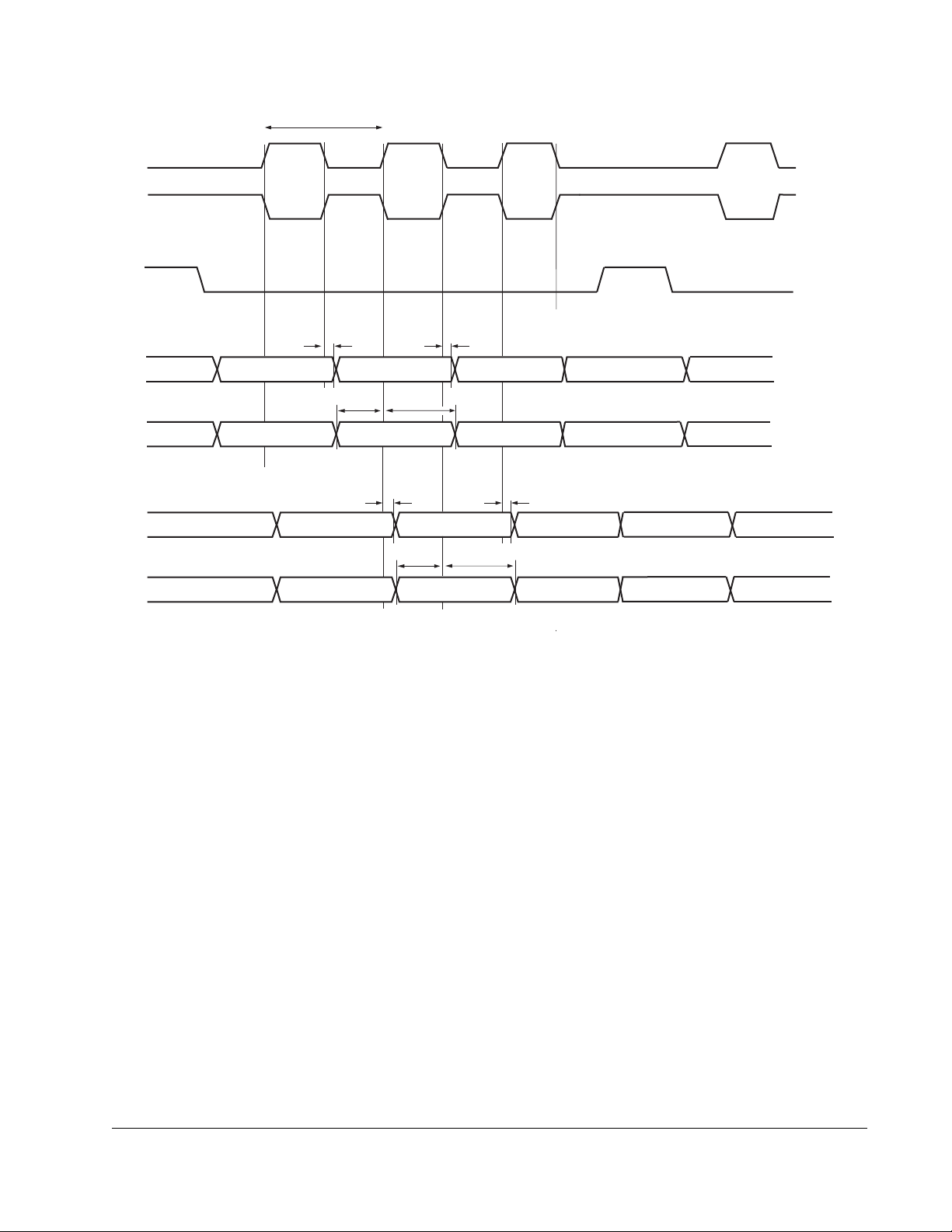

Following are the FlexSPI timing diagrams for SDR and DDR input and output timing

modes.

Figure 12. SDR mode (input timing, mode 0 and 1)

36

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 37

tDSt

DH

DQS

IO[0:7]

tDSt

DH

nternal Sample Clock

T

CLK

t

V(Q)max

t

V(Q)min

t

t

fclk

V(Q)max

V(Q)min

T

CLK

t

V(Q)max

t

V(Q)min

t

t

DQS

IO[0:7]

V(Q)max

V(Q)min

t

DStDH

t

DStDH

IO[0:7]

fclk

tDSt

DH

t

DStDH

IO[0:7]

DQS

External memory interface

Figure 13. SDR mode (input timing, mode 3)

Figure 14. SDR mode (output timing, mode 0 and 1)

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Figure 15. SDR mode (output timing, mode 3)

Figure 16. DDR mode (input timing, mode 0 and 1)

Figure 17. DDR mode (input timing, mode 3)

37

NXP Semiconductors

Page 38

T

CLK

t

V(Q)min

t

t

V(Q)min

fclk

V(Q)max

t

V(Q)max

T

CLK

t

V(Q)max

t

V(Q)min

t

V(Q)max

t

IO[0:7]

DQS

V(Q)min

External memory interface

Figure 18. DDR mode (output timing, mode 0 and 1)

Figure 19. DDR mode (output timing, mode 3)

1.5

Display and graphics

1.5.1 LCDIF

T

= -20 °C to 70 °C; VDD = 2.7 V to 3.6 V; CL = 30 pF. Simulated values.

amb

Table 27. LCDIF characteristics

Symbol Parameter Conditions Min. Typ. Max. Unit

f

t

v(Q)

clk

clock frequency on pin LCD_DCLK - - 60 MHz

data output valid time on all LCD output pins 0.3 - 4.5 ns

1.5.2 MIPI DSI timing

The i.MX RT500 conforms to the MIPI D-PHY electrical specifications MIPI DSI

Version 1.01 and D-PHY specification Rev. 1.0 (and also DPI version 2.0, DBI version

2.0, DSC version 1.0a at protocol layer) for MIPI display port x2 lanes.

38

NXP Semiconductors

i.MX RT500 Low-Power Crossover Processor, Rev. 0, 02/2021

Page 39

External memory interface

1.5.3 Flexible IO controller (FlexIO)

Table 28. FlexIO timing specifications

Symbol Description Min Typ. Max. Unit Notes

t

ODS

t

IDS

1. Assumes pins muxed on same VDD_IO domain with same load

Output delay skew between any

two FlexIO_Dx pins configured

as outputs that toggle on same

internal clock cycle

Input delay skew between any

two FlexIO_Dx pins configured

as inputs that are sampled on

the same internal clock cycle

0 — 1.957 ns 1

0 — 1.403 ns 1

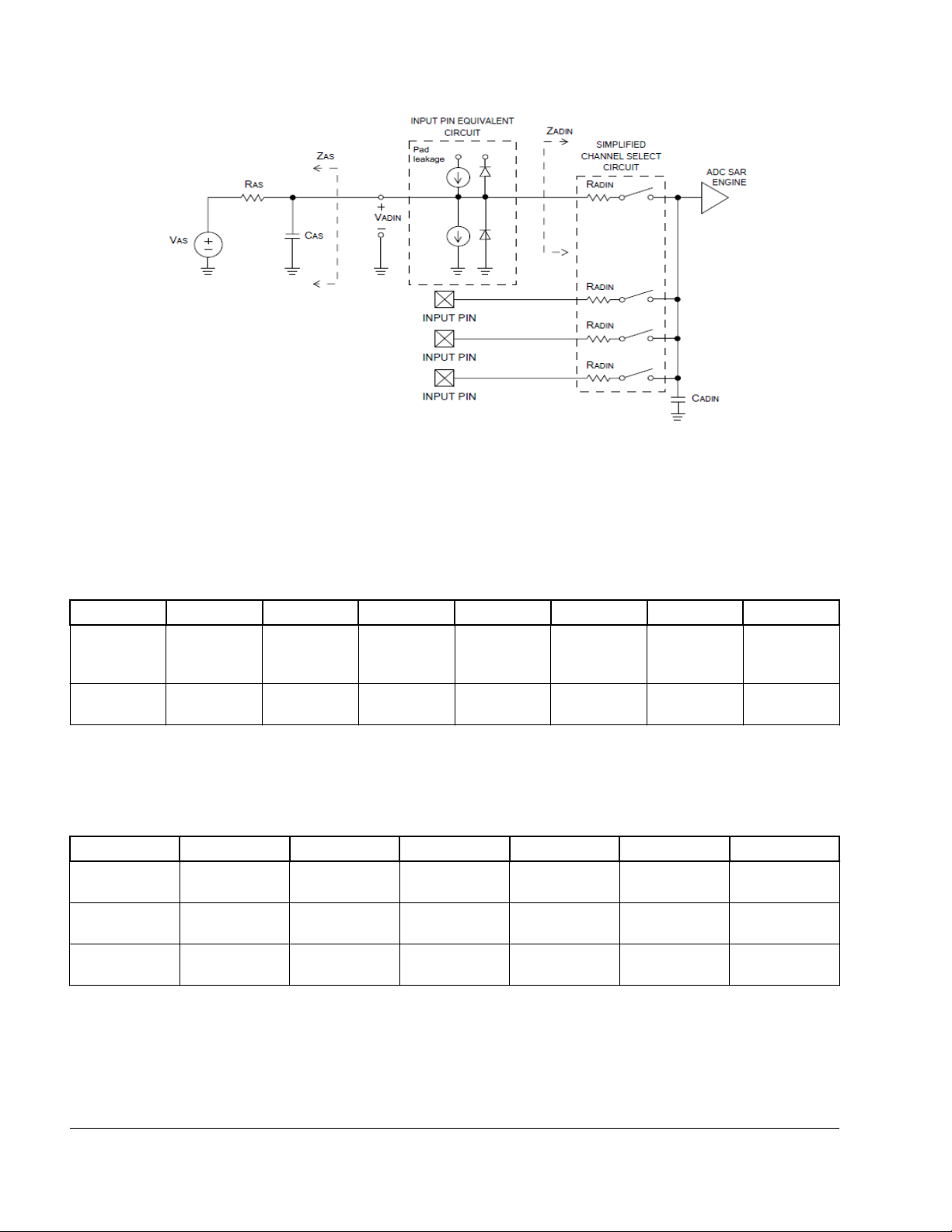

1.6 Analog characteristics

1.6.1 12-bit ADC characteristics

T

= -20 °C to +70 °C; 1.71 V ≤ VDD≤ 3.6 V; V

amb

Table 29. 12-bit ADC static characteristics

Symb

ol

VADIN analog input voltage See Figure 21 VREFN - VREFP V

f

clk(ADC)

f

s

C

sample

s

C

compar

e

C

convers

ion

CADIN Analog input

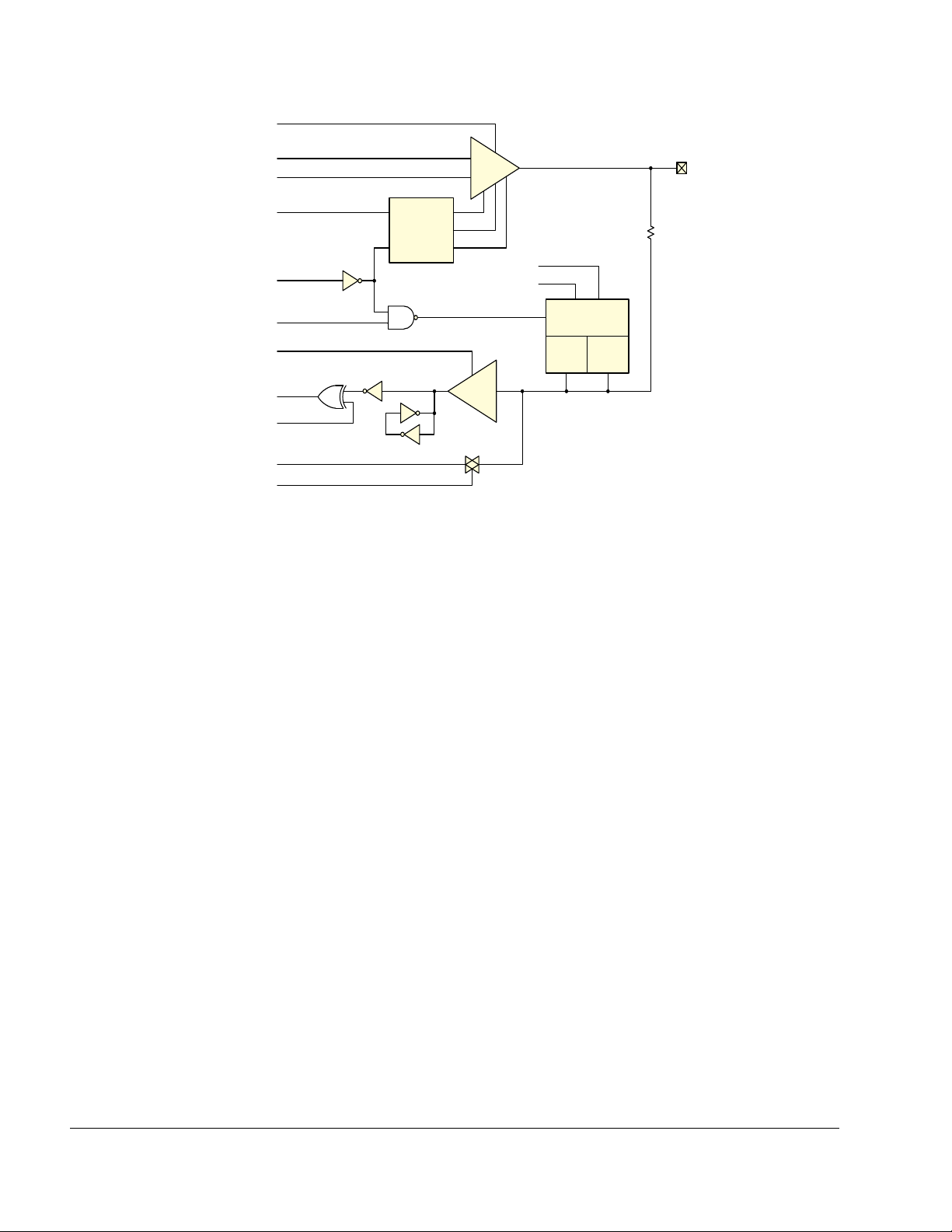

RADIN Input resistance See Figure 21 - 500 - Ω