Page 1

NXP Semiconductors

IMX7ULPCECB2

Data Sheet: Technical Data Rev. 0, 09/2020

i.MX 7ULP Applications

Processor—Consumer

MCIMX7U5DVP07SD

MCIMX7U5DVK07SD

MCIMX7U3DVK07SD

The i.MX 7ULP product family members are optimized for powersensitive applications benefiting from NXP's Heterogeneous

Multicore Processing (HMP) architecture. Achieving an efficient

balance between processing power and deterministic processing

needs, the i.MX 7ULP is an asymmetric processor consisting of

two separate processing domains: an application domain and a

real-time domain. The application domain is built around an

ARM® Cortex®-A7 processor with an ARM NEON™ SIMD

engine and floating point unit (FPU) and is optimized for rich OS

based applications. The real-time domain is built around an ARM

Cortex-M4 processor (with FPU) optimized for lowest possible

leakage. Both domains are completely independent, with

separate power, clocking, and peripheral domains, but the bus

fabric of each domain is tightly integrated for efficient

communication. The part is streamlined to minimize pin count, enabling small packages and simple system

integration.

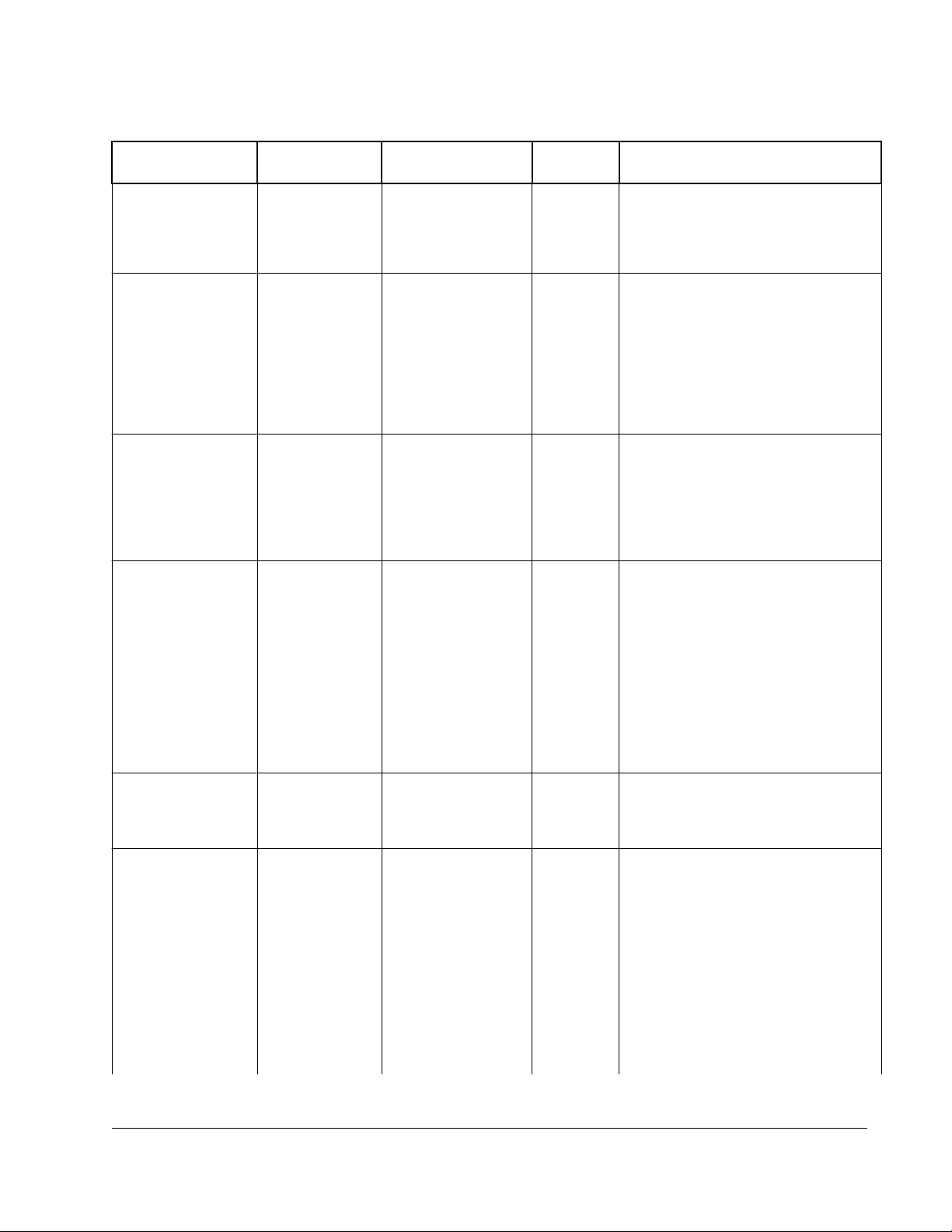

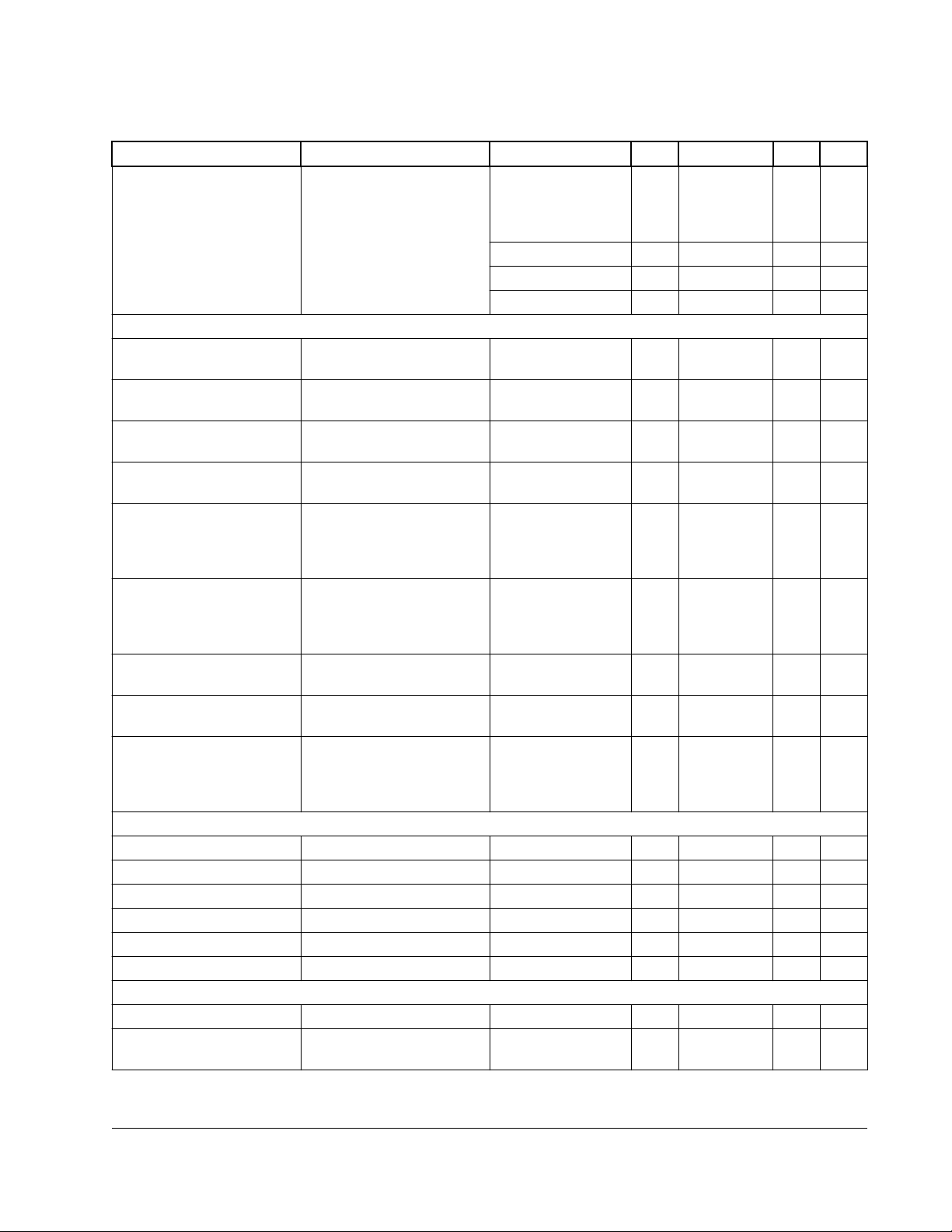

i.MX 7ULP features

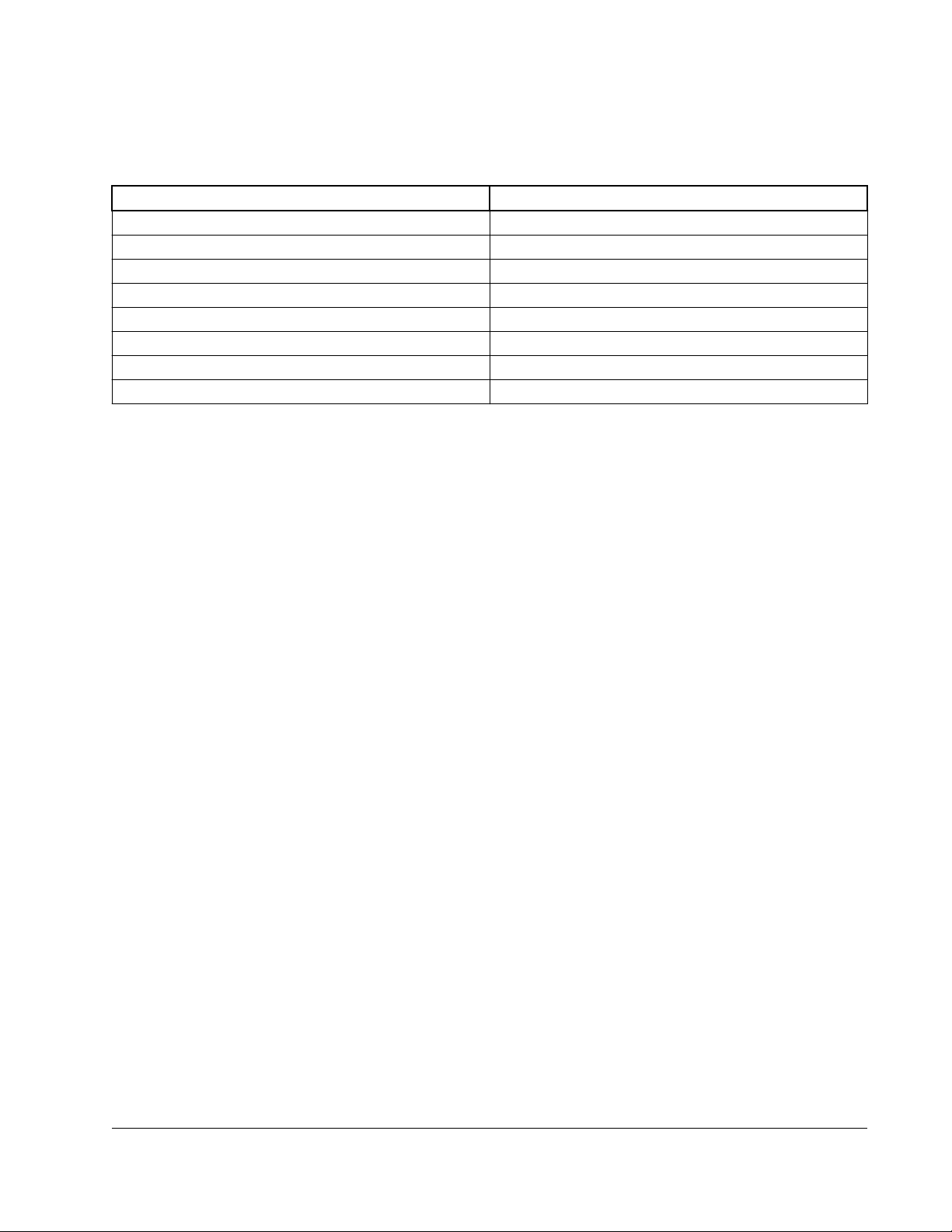

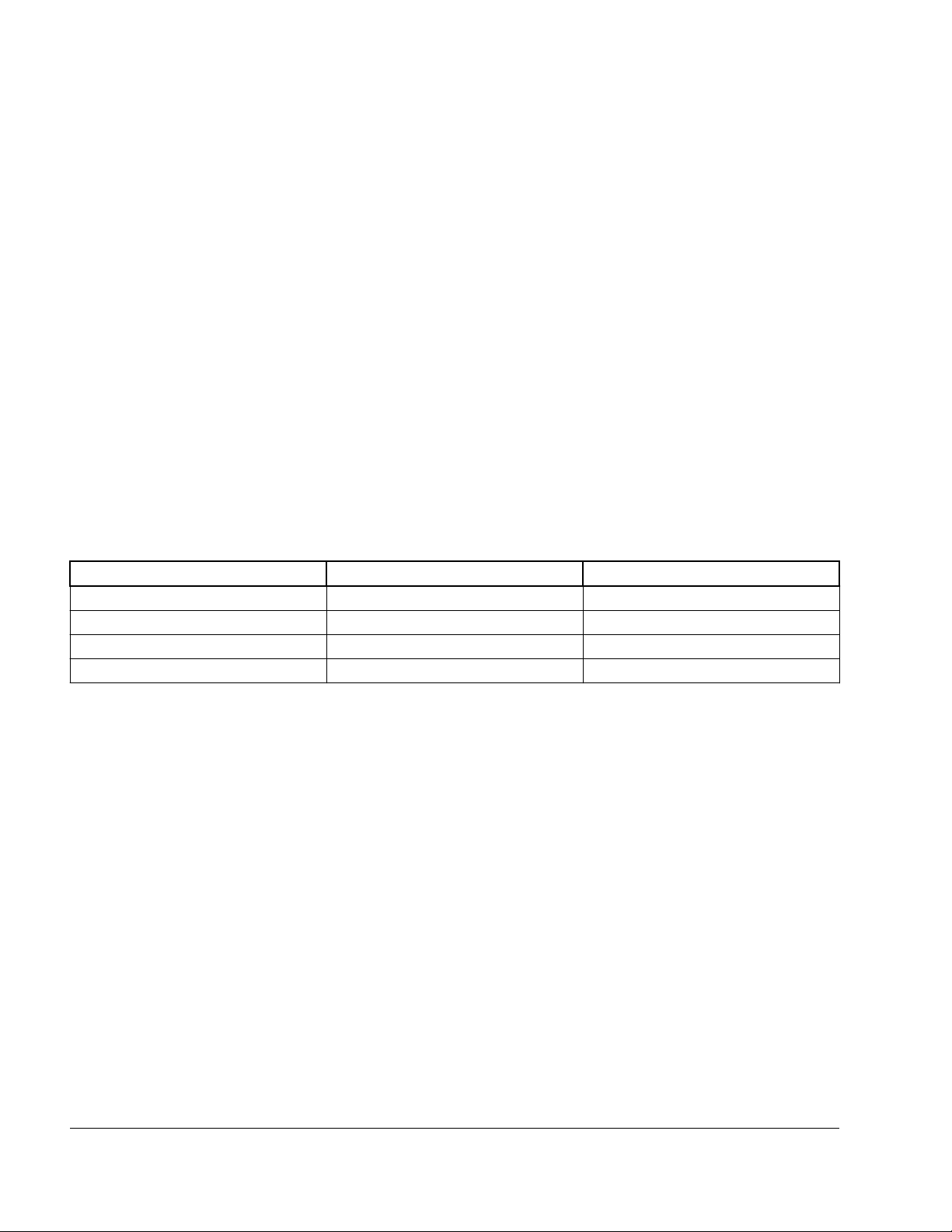

Feature type Application processor domain Real-time processor domain

ARM Processor

Cortex®-A7 Cortex®-M4

• Nominal (RUN) frequency: 500 MHz

• Overdrive (HSRUN) frequency: 720

MHz

• Very Low Power Run (VLPR)

frequency: 48 MHz

Plastic packages: BGA 14x14mm, 0.5mm pitch,

and BGA 10 x 10 mm, 0.5 mm pitch

• Nominal (RUN) frequency: 120 MHz

• Overdrive (HSRUN) frequency: 200

MHz

• Very Low Power Run (VLPR)

frequency: 48 MHz

32 KB instruction and data caches FPU

256 KB L2 cache MPU

NEON™ SIMD engine —

FPU —

On-chip memory

External memory

interfaces

Security

NXP reserves the right to change the production detail specifications as may be

required to permit improvements in the design of its products.

256 KB of RAM 256 KB of tightly coupled RAM allocated into

— 8 KB of OTP memory

16/32-bit LPDDR2/LPDDR3 interface

running at 380.16 MHz

eMMC 5.0 interface —

Secure boot Secure boot

Table continues on the next page...

Optimized for lowest leakage current

32 KB switchable blocks

Serial flash interface supporting x4 and x8

IOs

Page 2

i.MX 7ULP features (continued)

Feature type Application processor domain Real-time processor domain

Serial peripherals

Timers

Signing and encrypt/decrypt engines

(CAAM)

Simple tamper detection —

Four I2C Fast mode plus Four I2C Fast mode plus

SD 3.0/MMC 5.0 FlexI/O

Four UARTs with flow control Four UARTs with flow control

Two LPSPI peripherals Two LPSPI peripherals

Four 32-bit general-purpose timers with

capture and compare; one 64-bit timer

Watchdog timer Watchdog timer

Encrypt/decrypt engines (LTC)

Four 32-bit general purpose-timers with

capture and compare; one 64-bit timer

2

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 3

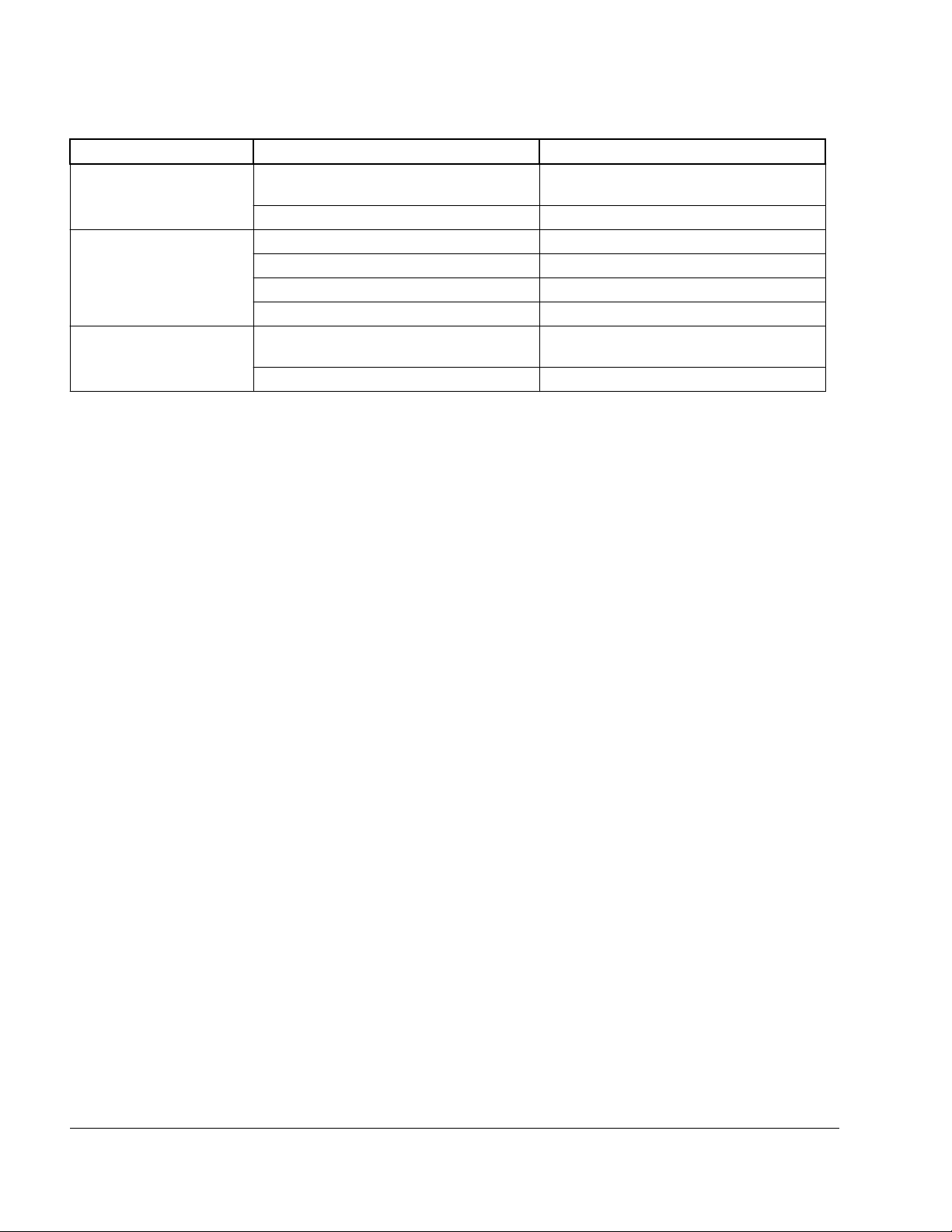

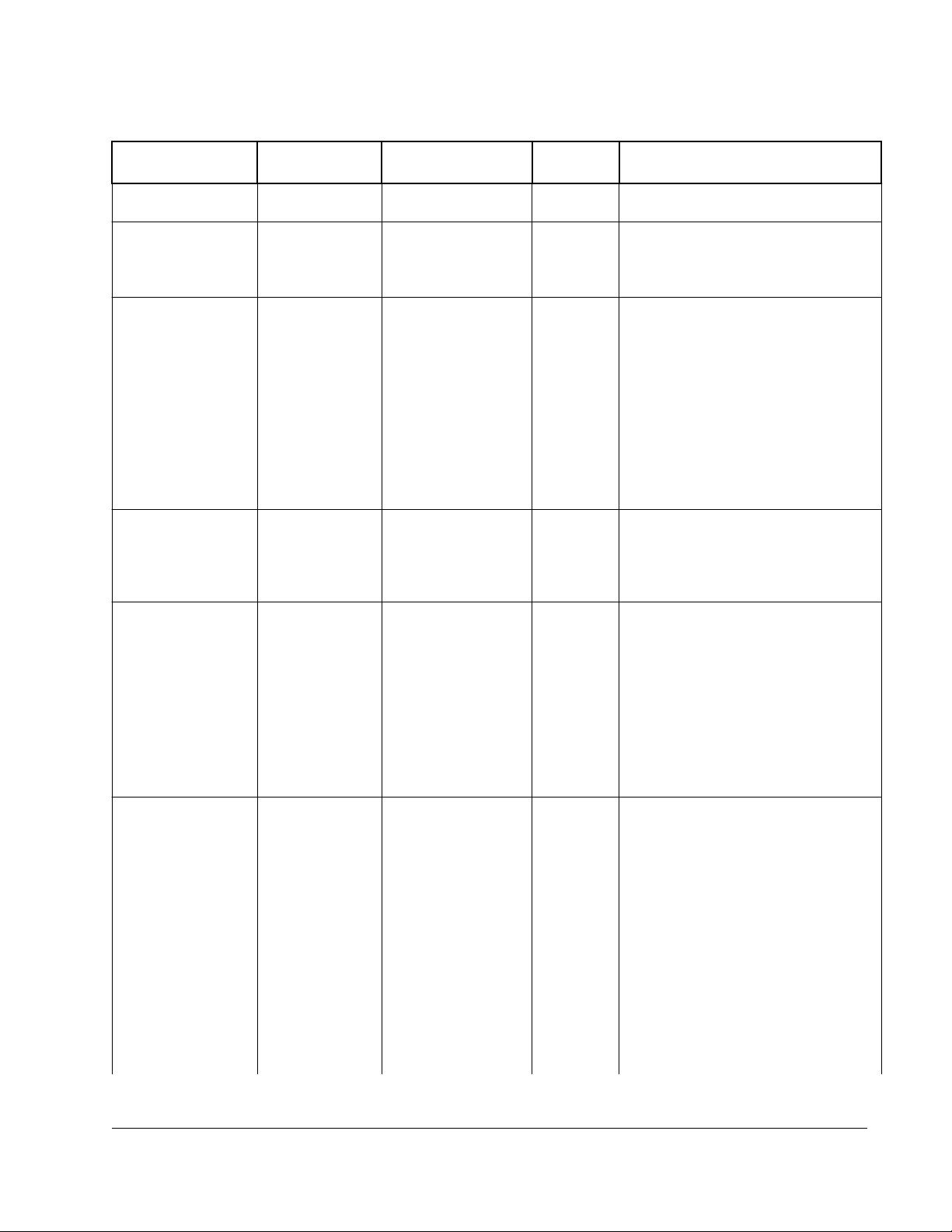

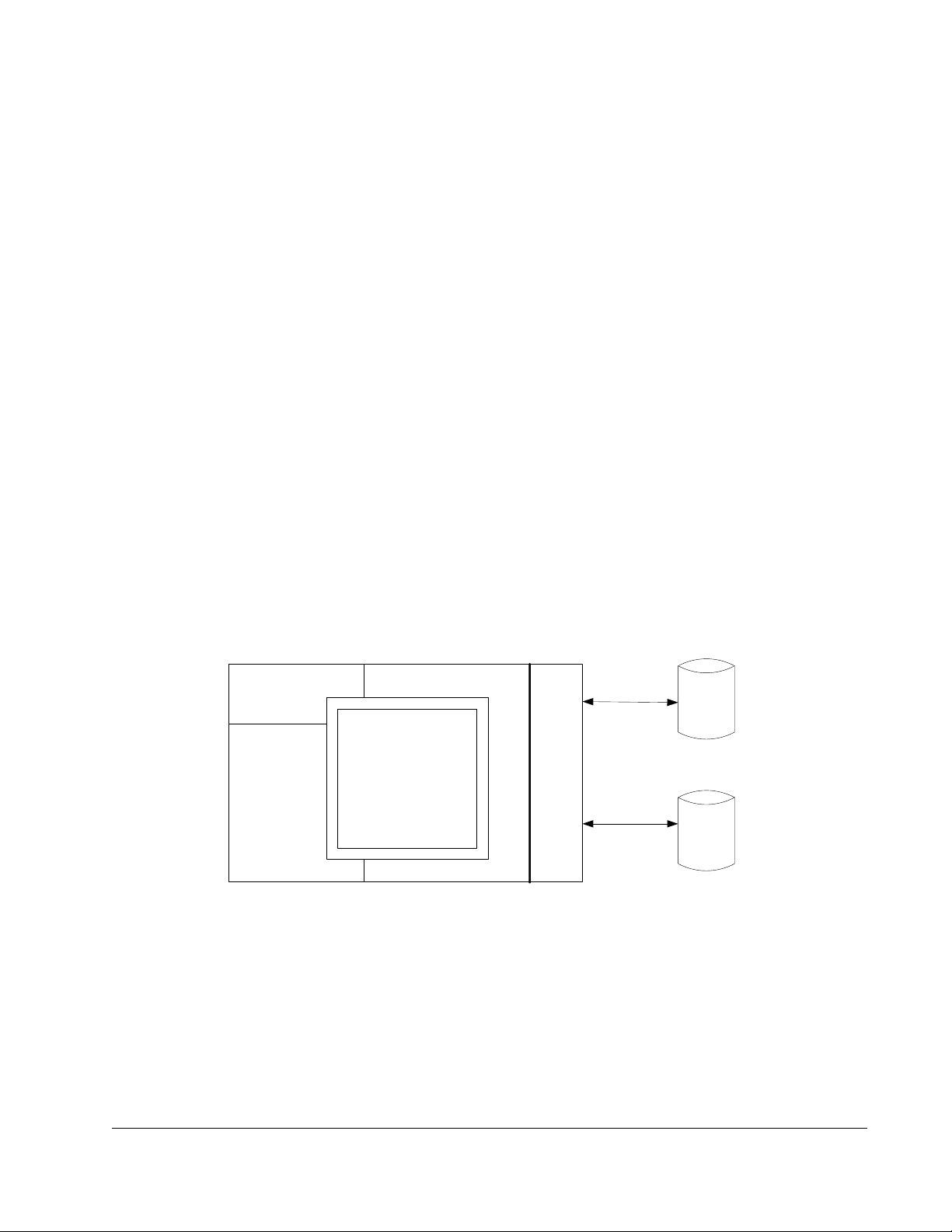

Application Domain

Real Time Domain

i.MX 7ULP

A7 Connectivity

Security

Secure JTAG

Internal Memory

256K RAM

UART x 4

I2C x4

3.3V/1.8V GPIO

USB2.0 HOST

(w/ HSIC)

Analog

2x 12 bit ADC

HAB – Secure Boot

Graphics

GC7000

NanoULTRA

External Memory

MMC5.0/SDIO x 2

16/32-bit LPDDR2/3

Power

Manager

SPI x 2

Arm Cortex -A7

NEON

Trust Zone

32KB I-cache 32KB D-cache

FPU

ETM

256KB L2 cache

Analog Comparators

External Memory

Quad SPI (OTFAD)

Timers

Watch Dog

32 bit Timer x4

System timers

Crypto / TRNG

FPUMPU

M4 Connectivity

UART x 4

I2C x4

3.3V/1.8V GPIO

SPI x2

FlexIO

2x 12 -bit DAC

Internal Memory

256K RAM

Timers

Watch Dog

32 bit Timer x4

System timers

Clock/Reset

Arm Cortex -

- M4

DAP

DSP Extensions

USB2.0 OTG

(w/ PHY)

8KB I/D

- cache

MIPI DSI

Display

Secure Fuse

FlexBUS

I2S x 2

eFuses / OTP

SEMA4 / Msg Unit

DMA

VIU

Camera

FlexIO

GC320

Composition

Security

uHAB – Secure Boot

Clock and Power

Management System

Secure

RTC

Tamper

Detection

Security – Batt Domain

Key

Storage

Crypto / TRNG

XRDC

Access and IPC

PLL/OSC

32K Secure

Memory

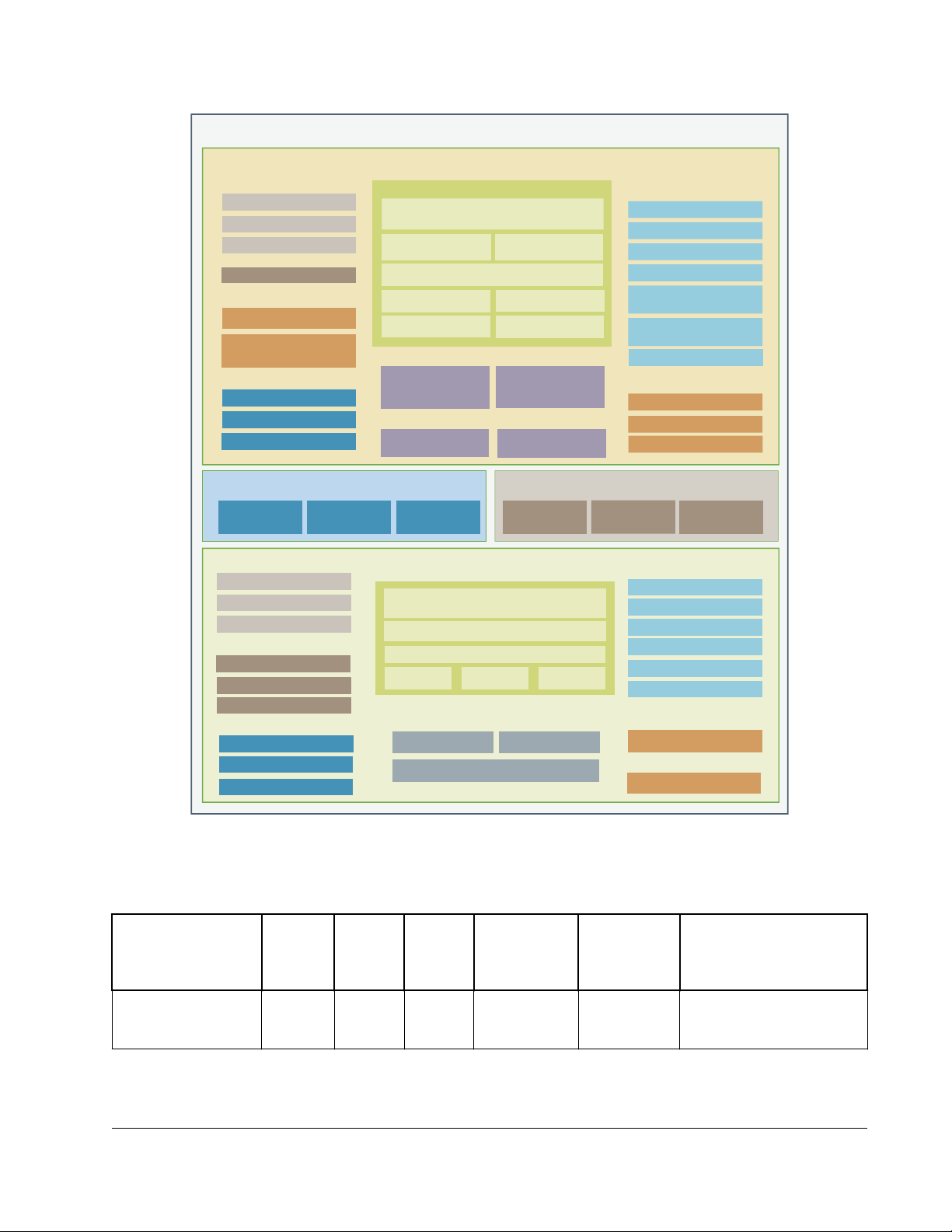

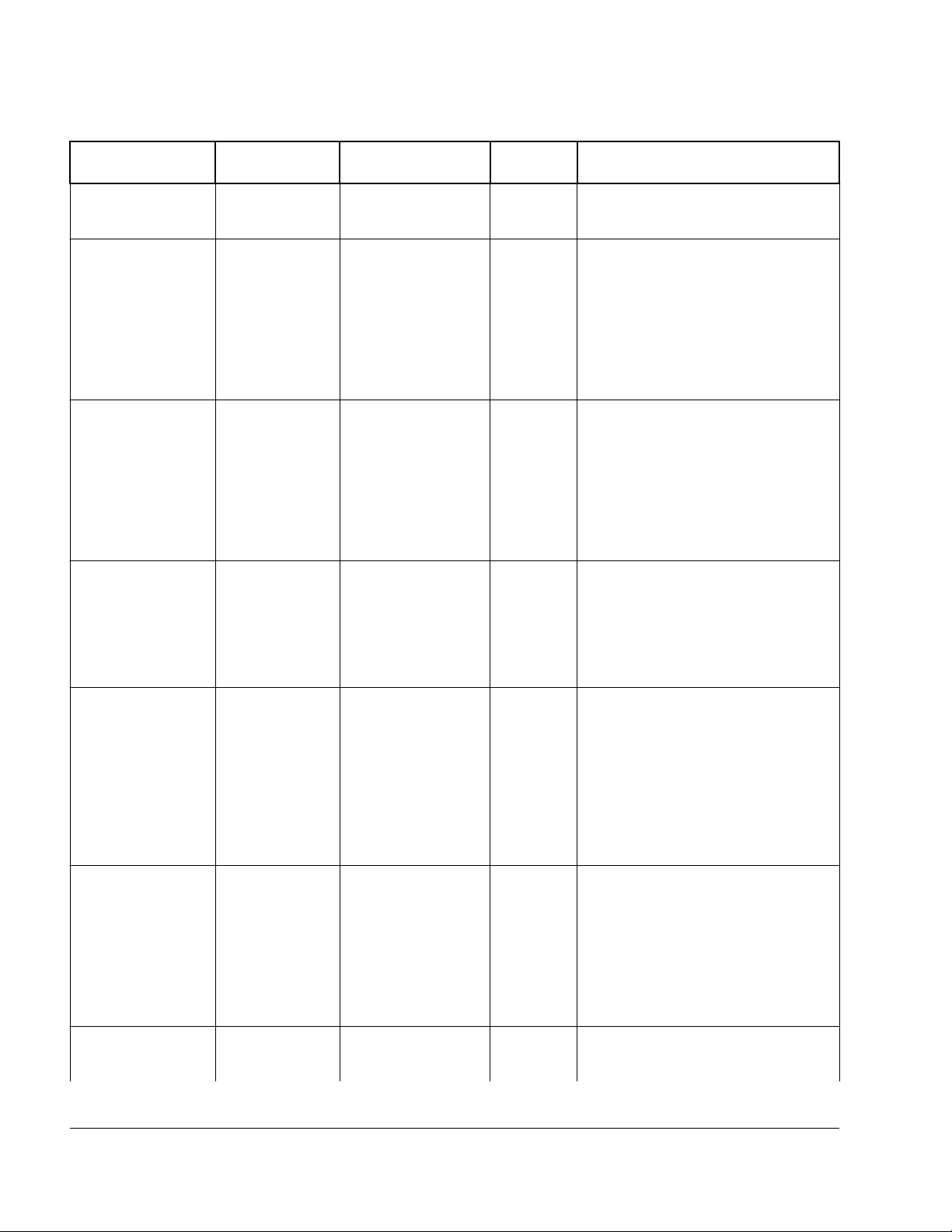

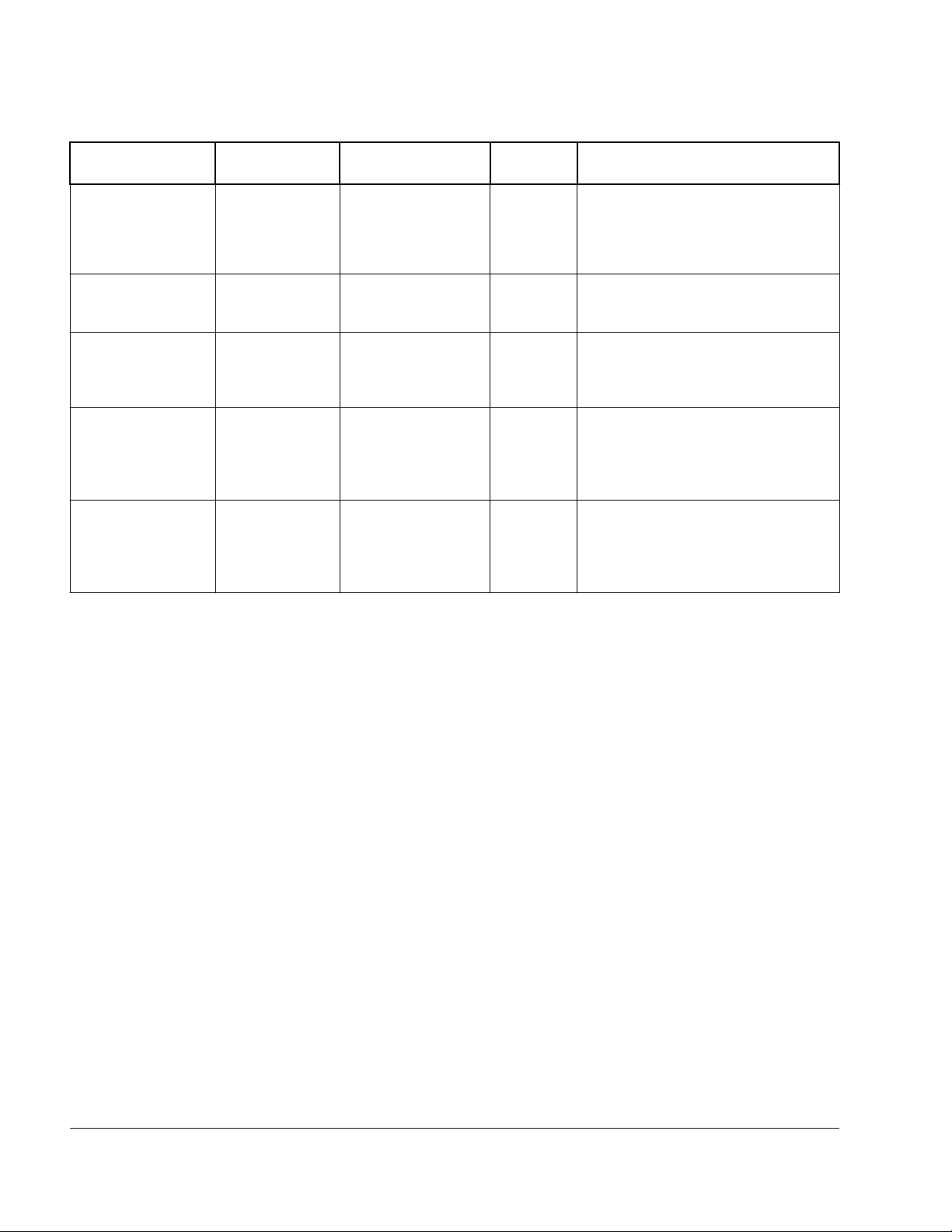

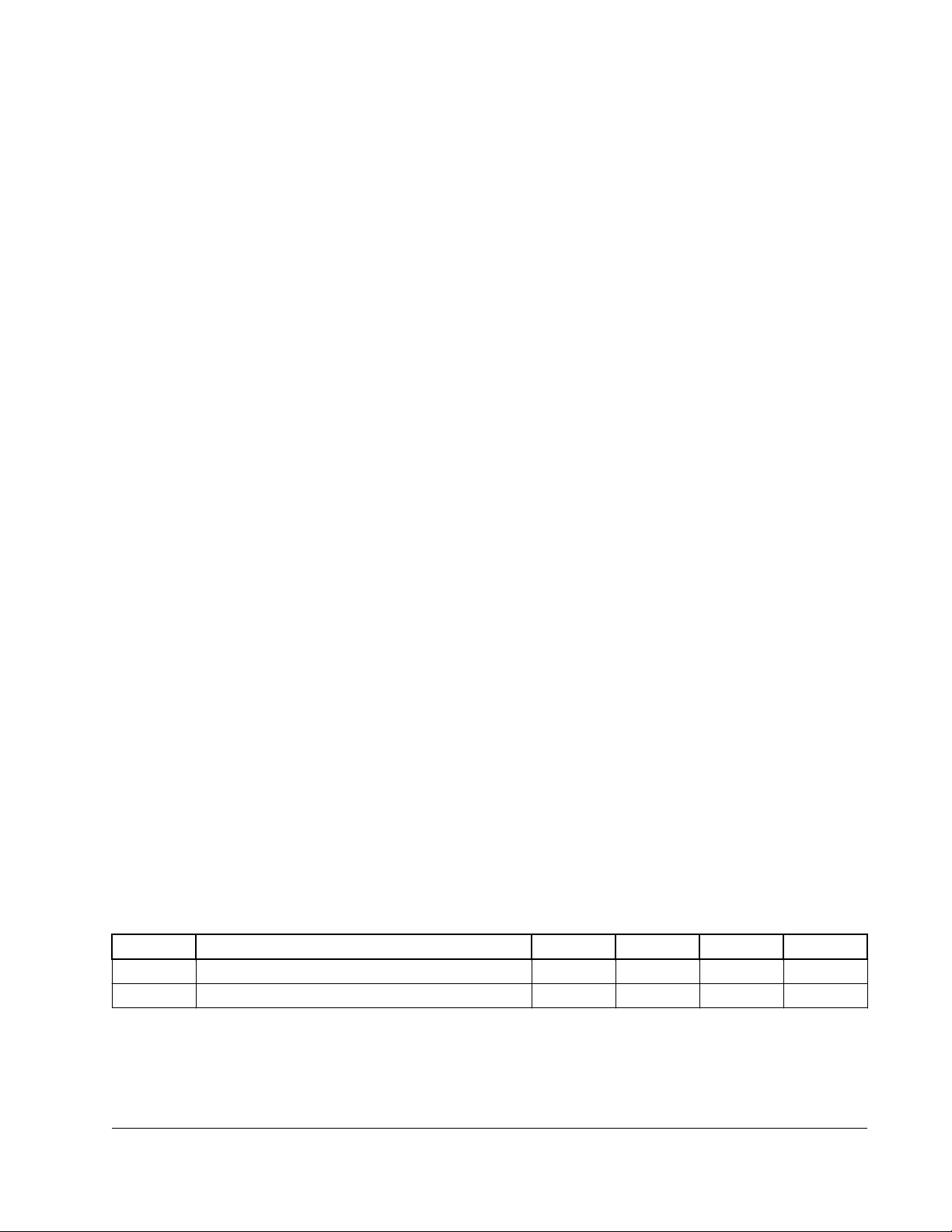

The following table provides examples of orderable sample part numbers covered by this data sheet.

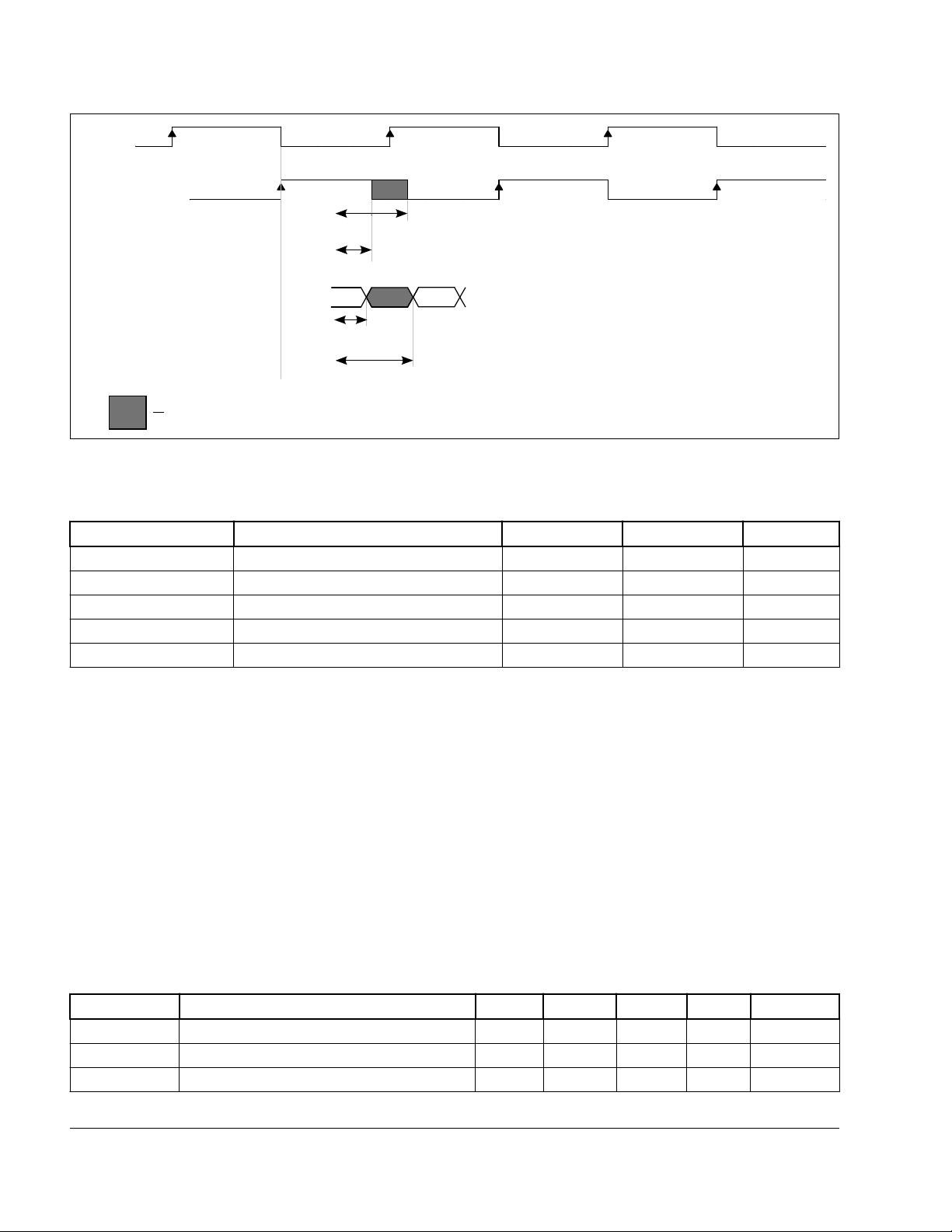

Figure 1. i.MX 7ULP Block Diagram

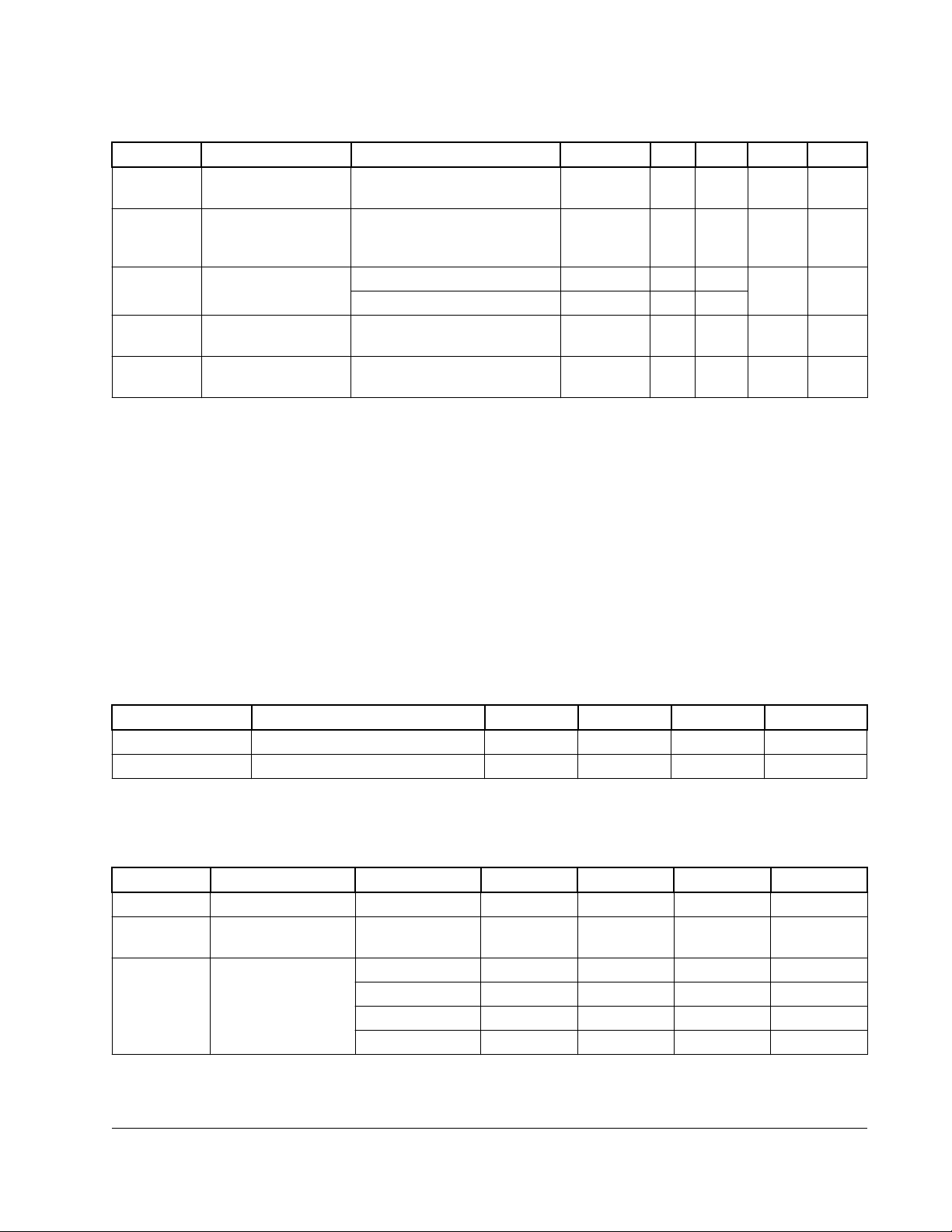

Part Number Options Cortex-

MCIMX7U5DVP07SD GPU-2D,

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

GPU-3D

supported

Ordering information

A7

Speed

Grade

720 MHz 200 MHz Commercial

Cortex-

M4

Speed

Grade

Table continues on the next page...

Qualification

Tier

(Consumer)

Junction

Temperature

Range

0 to +95 °C 14 mm x 14 mm, 0.5 mm

pitch BGA, Package code

"VP"

Package

NXP Semiconductors

3

Page 4

Ordering information (continued)

Part Number Options Cortex-

A7

Speed

Grade

MCIMX7U5DVK07SD GPU-2D,

GPU-3D

supported

MCIMX7U3DVK07SD No GPU 720 MHz 200 MHz Commercial

720 MHz 200 MHz Commercial

Cortex-

M4

Speed

Grade

Qualification

Tier

(Consumer)

(Consumer)

Junction

Temperature

Range

0 to +95 °C 10 mm x 10 mm, 0.5 mm

pitch BGA, Package code

"VK"

0 to +95 °C 10 mm x 10 mm, 0.5 mm

pitch BGA, Package code

"VK"

Package

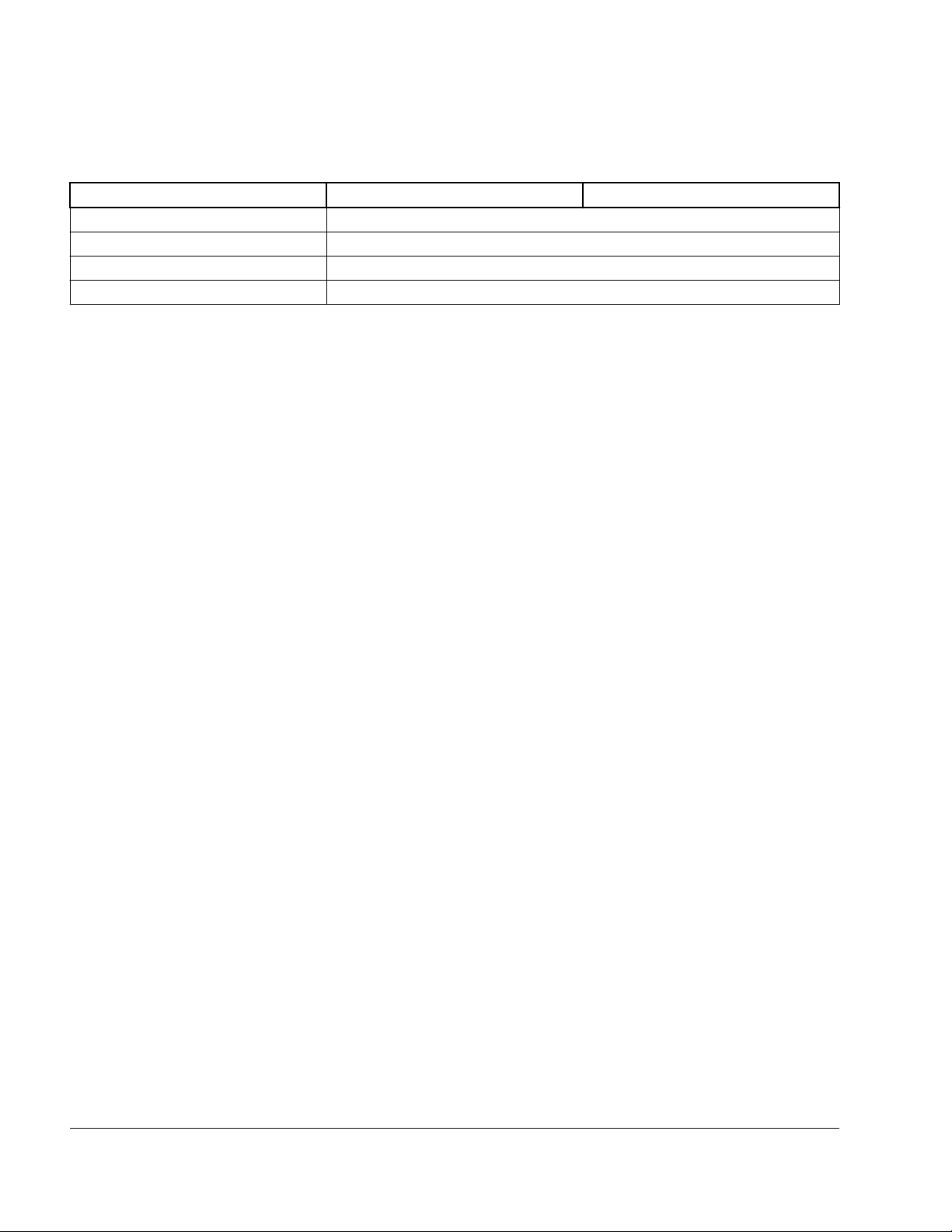

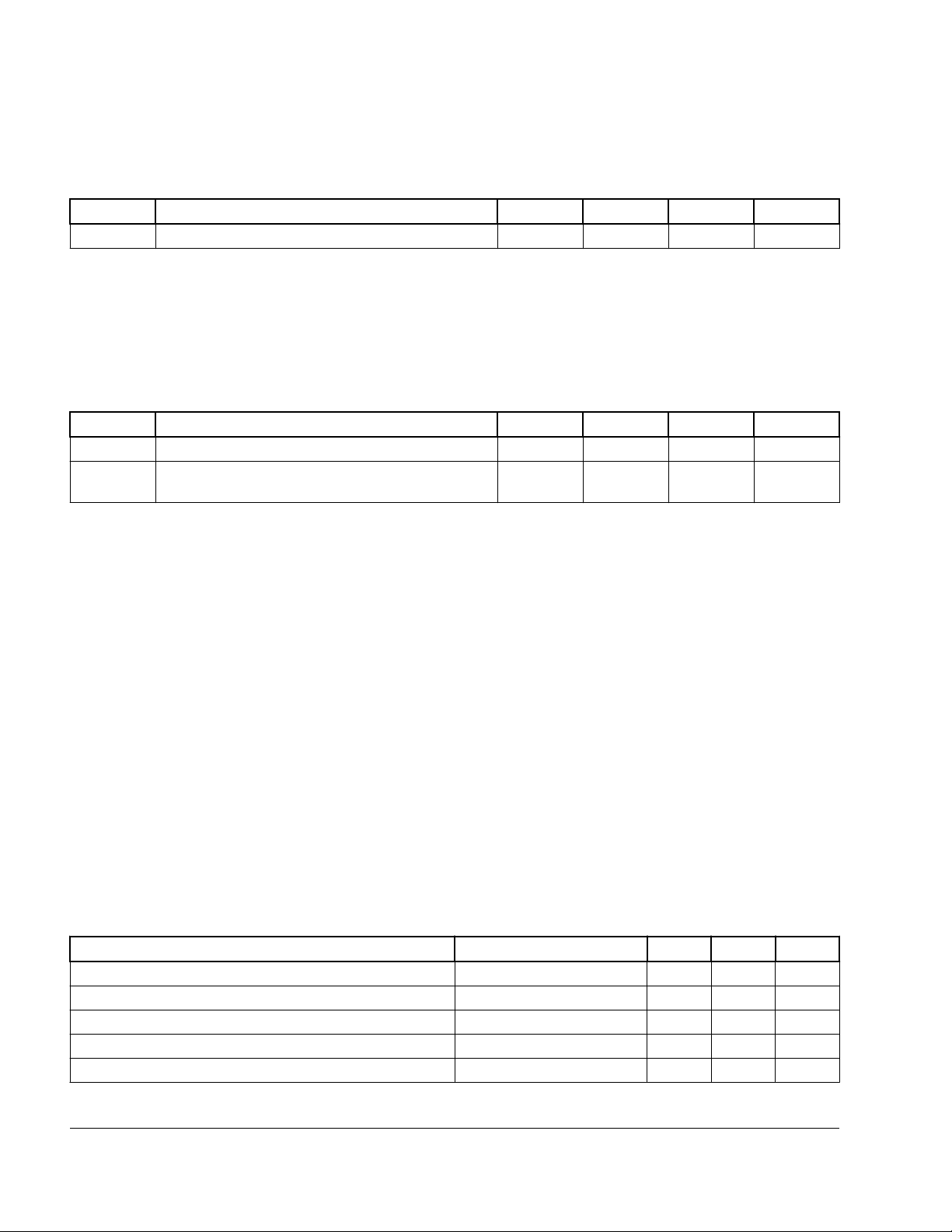

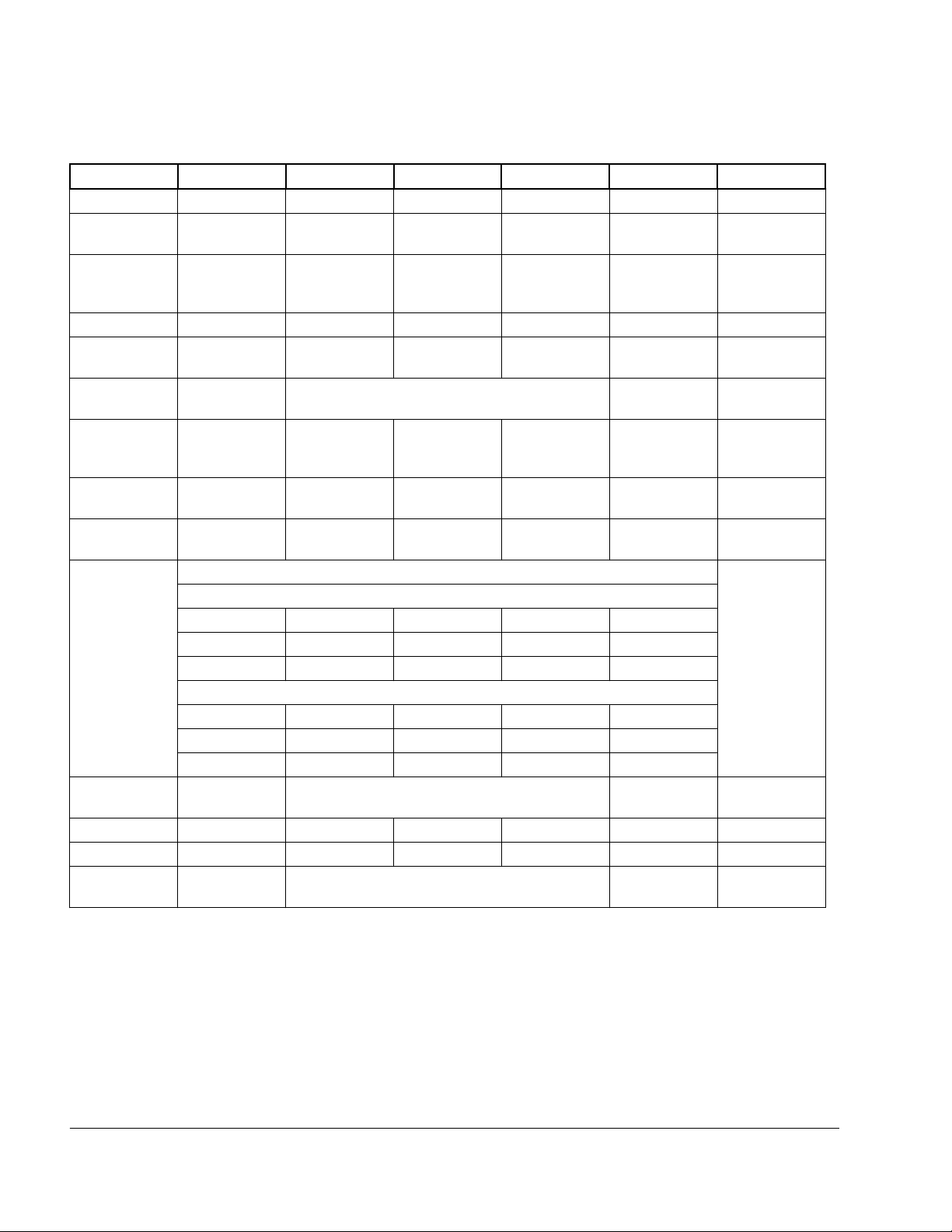

The following figure describes the part number nomenclature so users can identify the characteristics of the

specific part number.

Figure 2. i.MX 7 Family Part Number Definition

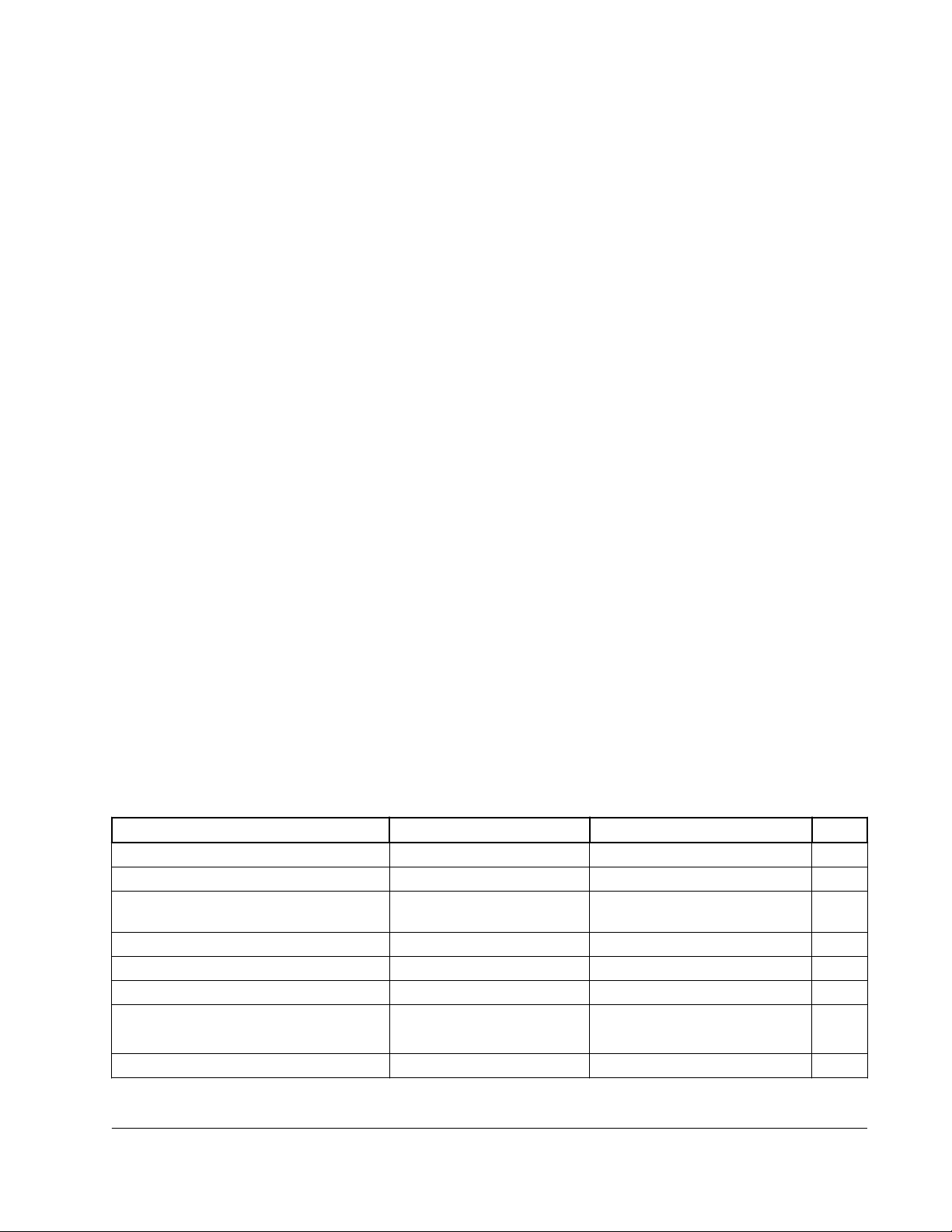

Related Resources

Type Description

Reference Manual The i.MX 7ULP Applications Processor Reference Manual contains a comprehensive description of

the structure and function (operation) of the SoC.

Data Sheet The Data Sheet includes electrical characteristics and signal connections.

Chip Errata The chip mask set errata provides additional or corrective information for a particular device mask

set.

Package drawing Package dimensions are provided in Package information and contact assignments

4

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 5

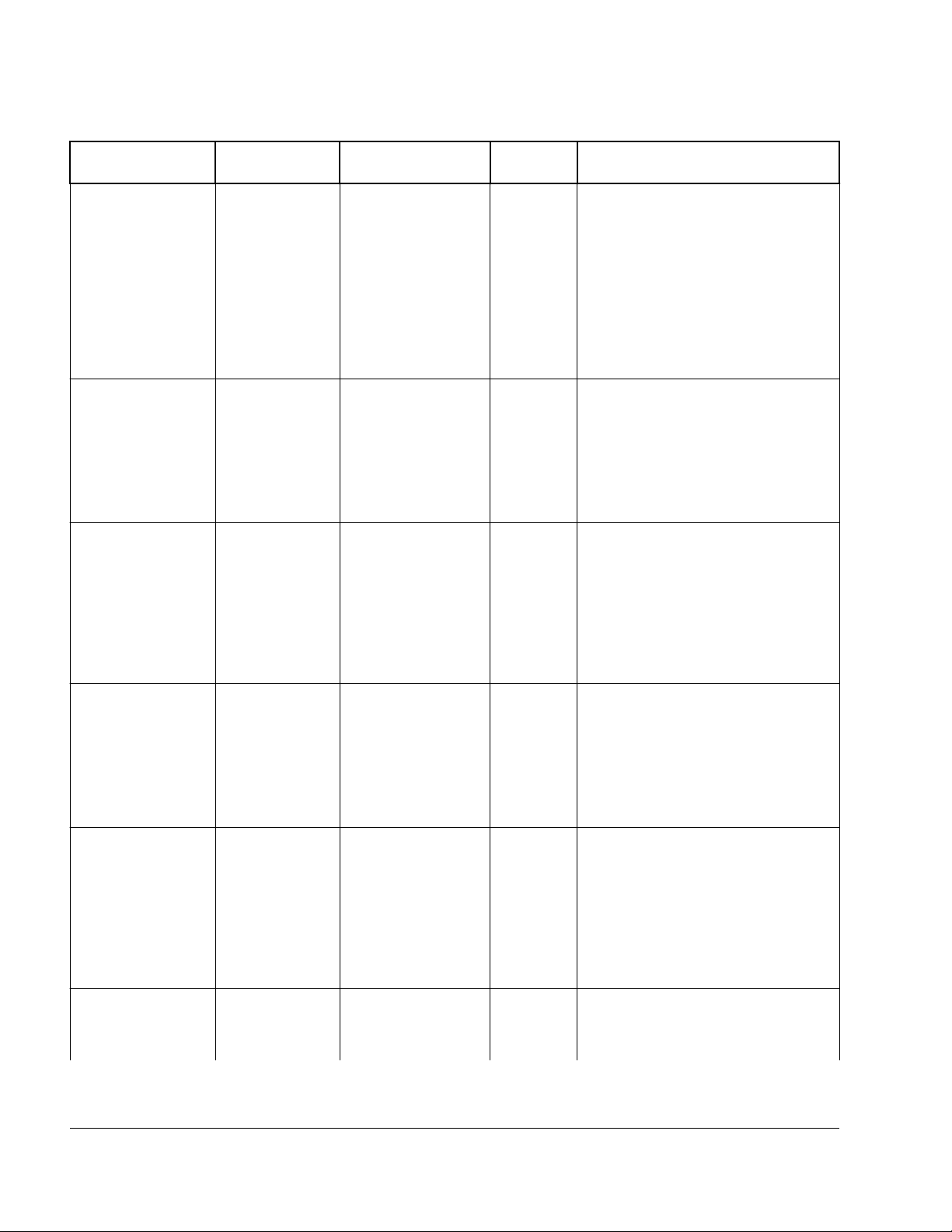

The power mode acronyms used throughout this document are defined as follows.

Power mode acronym table

Power mode acronym Power mode name

HSRUN High-speed run mode

RUN Nominal speed run mode

VLPR Very low power run mode

PSTOP Partial stop mode

STOP Stop mode

VLPS Very low power stop mode

LLS Low leakage stop mode

VLLS Very low leakage stop mode

For details on each of these operating modes, see the i.MX 7ULP Applications Processor Reference Manual

(IMX7ULPRM).

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

5

NXP Semiconductors

Page 6

Table of Contents

1 i.MX 7ULP modules list......................................................... 8

2 Clocking................................................................................ 22

2.1 Introduction..................................................................22

2.2 Clock distribution......................................................... 23

2.3 External clock sources.................................................23

2.4 Oscillators....................................................................23

2.5 Internal clock sources..................................................24

3 Application domain (implementing ARM Cortex-A7).............25

3.1 Memory system—application domain..........................25

3.1.1 Internal memory (application domain)...........25

3.1.2 Multi Mode DDR Controller (MMDC).............25

3.1.3 eMMC............................................................26

3.2 Peripherals—application domain.................................26

3.2.1 Graphics processor human machine

interfaces.......................................................26

3.2.2 Security—application domain........................26

3.2.3 Timers—application domain..........................28

3.2.4 Connectivity and communications—

applications domain...................................... 28

4 Real-time domain (implementing ARM Cortex-M4).............. 28

4.1 Memory system—real-time domain.............................28

4.1.1 Internal memory—real-time domain..............28

4.1.2 QuadSPI flash...............................................29

4.2 Peripherals—real-time domain.................................... 29

4.2.1 Analog—real-time domain.............................29

4.2.2 Connectivity and communications—real-

time domain...................................................29

5 System control modules........................................................29

5.1 JTAG—system control.................................................30

5.2 JTAG device identification register.............................. 30

5.3 Oscillators and PLLs....................................................30

5.3.1 System oscillator (SYS OSC)........................30

5.3.2 Real-Time Clock Oscillator (RTC OSC)........30

5.3.3 USB PLL....................................................... 31

5.3.4 Fixed Frequency PLL (Fixed-freq PLL).........31

5.3.5 Fractional-N PLL (FracN PLL).......................31

5.4 Power Management.................................................... 31

5.4.1 Digital PMC................................................... 32

5.4.2 Analog power management controller

(Analog PMC)................................................32

6 i.MX 7ULP LDO Bypass versus LDO-enabled modes.......... 32

6.1 Real-time domain LDO Enabled mode........................32

6.2 Application domain LDO Enabled mode......................33

6.3 Application domain LDO BYPASS mode.................... 33

7 System specifications............................................................33

7.1 Ratings........................................................................ 33

7.1.1 Thermal handling ratings...............................33

7.1.2 Moisture handling ratings..............................34

7.1.3 ESD handling ratings.................................... 34

7.1.4 Absolute maximum ratings............................34

7.1.5 Recommended operating conditions—

system...........................................................35

7.1.6 Estimated maximum supply currents............ 39

7.2 System clocks..............................................................41

7.2.1 Clock modules...............................................41

7.2.2 Core, platform, and system bus clock

frequency limitations..................................... 43

7.2.3 Peripheral clock frequencies.........................44

7.2.4 PLL PFD output.............................................47

7.2.5 Audio tunable clock.......................................48

7.3 Power sequencing—system........................................ 49

7.3.1 Power-on sequencing................................... 49

7.3.2 Power-off sequencing................................... 50

7.4 Requirements for unused interfaces............................50

7.5 Electrical Characteristics and Thermal Specifications.51

7.5.1 AC electrical characteristics..........................51

7.5.2 Nonswitching electrical characteristics..........52

7.5.3 Switching electrical characteristics................54

7.5.4 Debug and trace modules.............................56

7.5.5 Thermal specifications.................................. 59

8 Specifications—application domain...................................... 61

8.1 Peripheral operating requirements and behaviors.......61

8.1.1 DDR timing—application domain.................. 61

8.1.2 Ultra-high-speed SD/SDIO/MMC host

interface (uSDHC) AC timing—application

domain.......................................................... 61

8.1.3 Flexbus switching specifications................... 66

8.1.4 Display, Video, and Audio Interfaces............ 69

8.1.5 Timer specifications—application domain.....70

8.1.6 Connectivity and communications

specifications—application domain...............70

9 Specifications—real-time domain..........................................79

9.1 Power sequencing—real-time domain.........................79

9.2 Peripheral operating requirements and behaviors—

real-time domain..........................................................80

9.2.1 QuadSPI AC specifications...........................80

9.2.2 Analog modules............................................ 84

9.2.3 Timer specifications—real-time domain........92

9.2.4 Connectivity and communications

specifications—real-time domain.................. 92

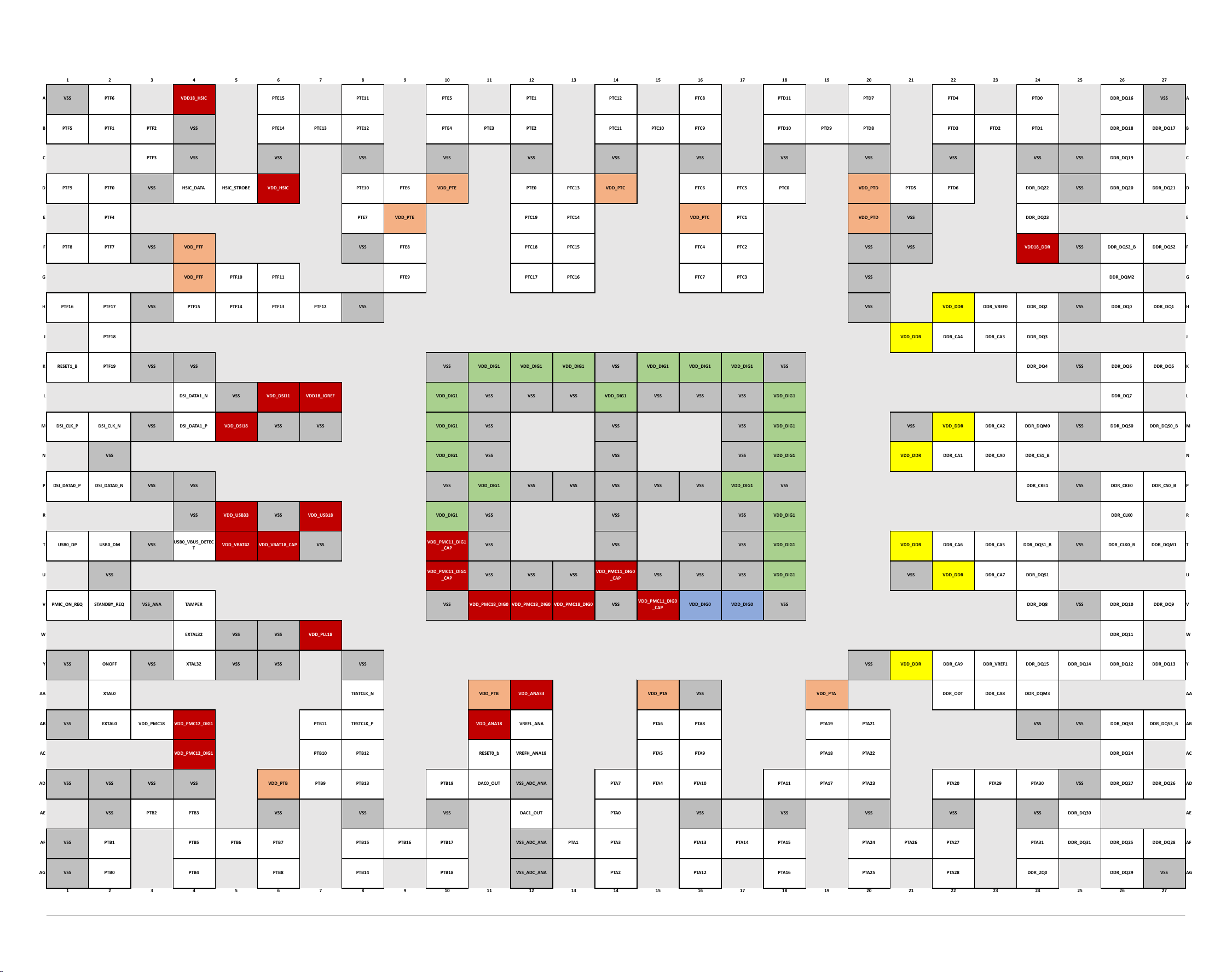

10 Package information and contact assignments.....................96

10.1 BGA, 14 x 14 mm, 0.5 mm pitch (VP suffix)................96

10.1.1 14 x 14 mm package case outline.................96

10.1.2 14 x 14 mm, 0.5 mm pitch, ball map............. 98

10.1.3 14 x 14 mm power supply and functional

contact assignments..................................... 100

10.2 BGA, 10 x 10 mm, 0.5 mm pitch (VK suffix)................108

10.2.1 10 x 10 mm package case outline.................108

10.2.2 10 x 10 mm, 0.5 mm pitch, ball map............. 110

6

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 7

10.2.3 10 x 10 mm power supply and functional

contact assignments....................................112

11 Revision History.................................................................. 120

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

7

NXP Semiconductors

Page 8

i.MX 7ULP modules list

1 i.MX 7ULP modules list

The i.MX 7ULP applications processor contains a variety of digital and analog

modules. The following table describes these modules in alphabetical order.

In the Domain column in this table:

• AD = Application Power Domain (primarily controlled by the Cortex-A7)

• RT = Real-Time Power Domain (primarily controlled by the Cortex-M4)

• VBAT = RTC/VBAT power domain Real-Time Domain

• DGO = “always-on” DGO power domain

• SYS = system-level functions that are implemented separately from the domains

listed above.

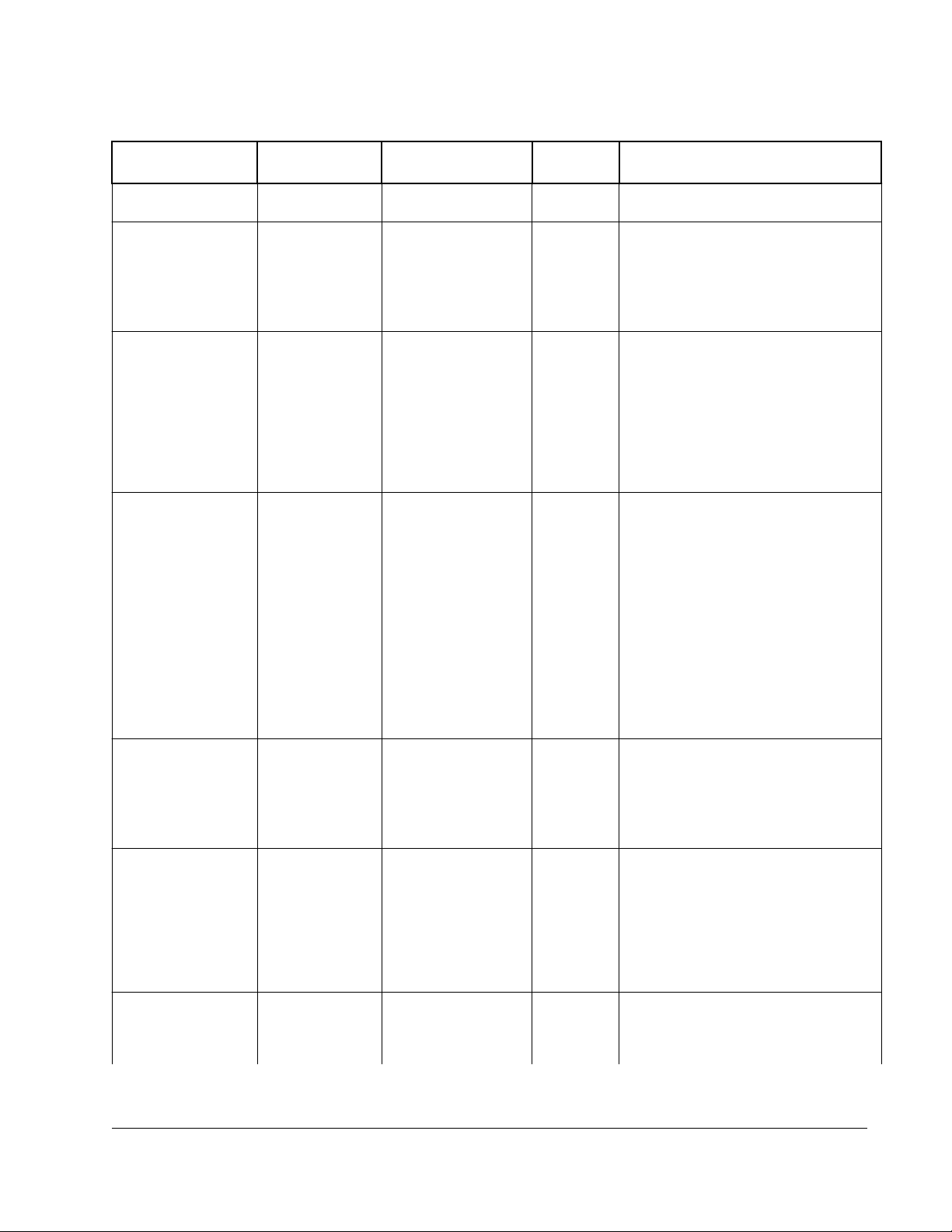

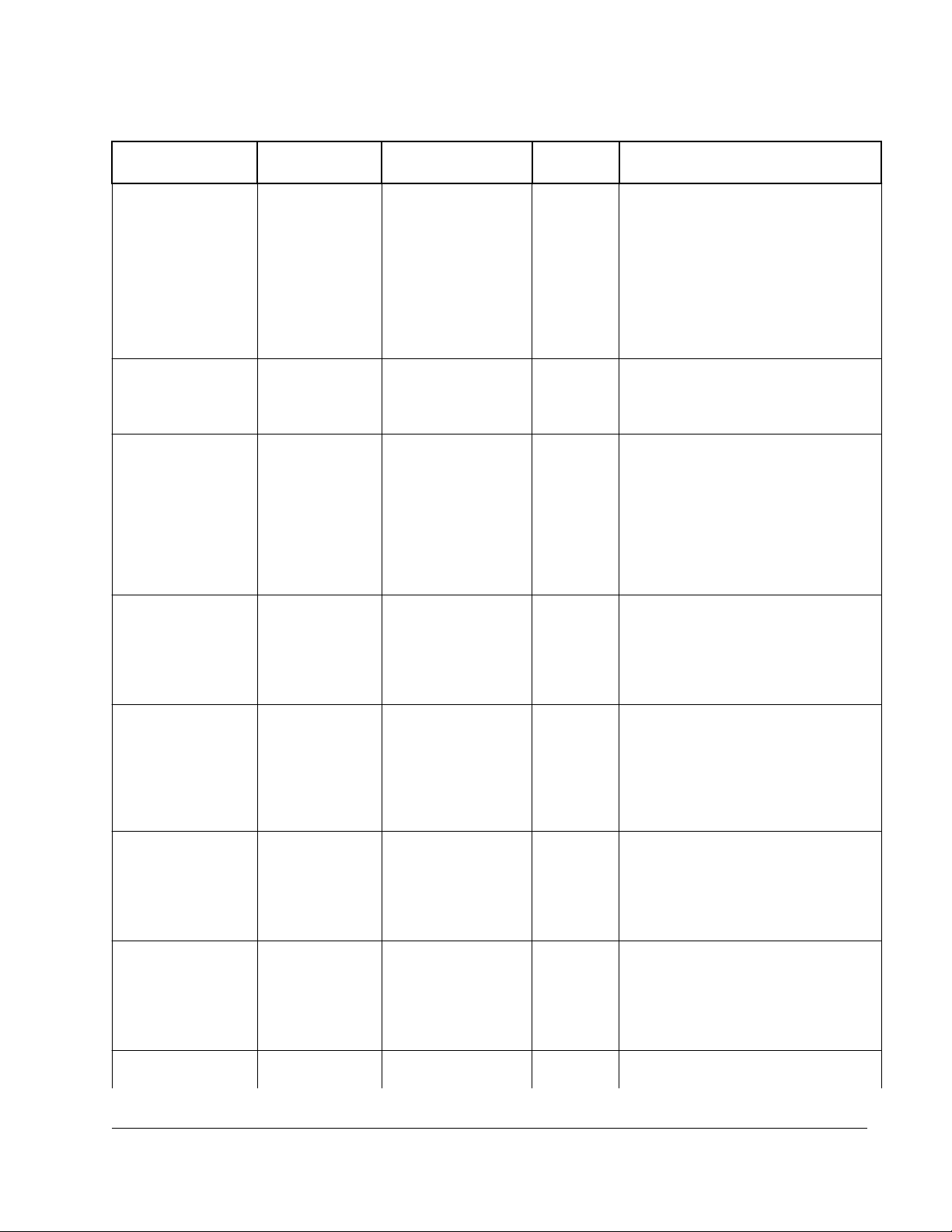

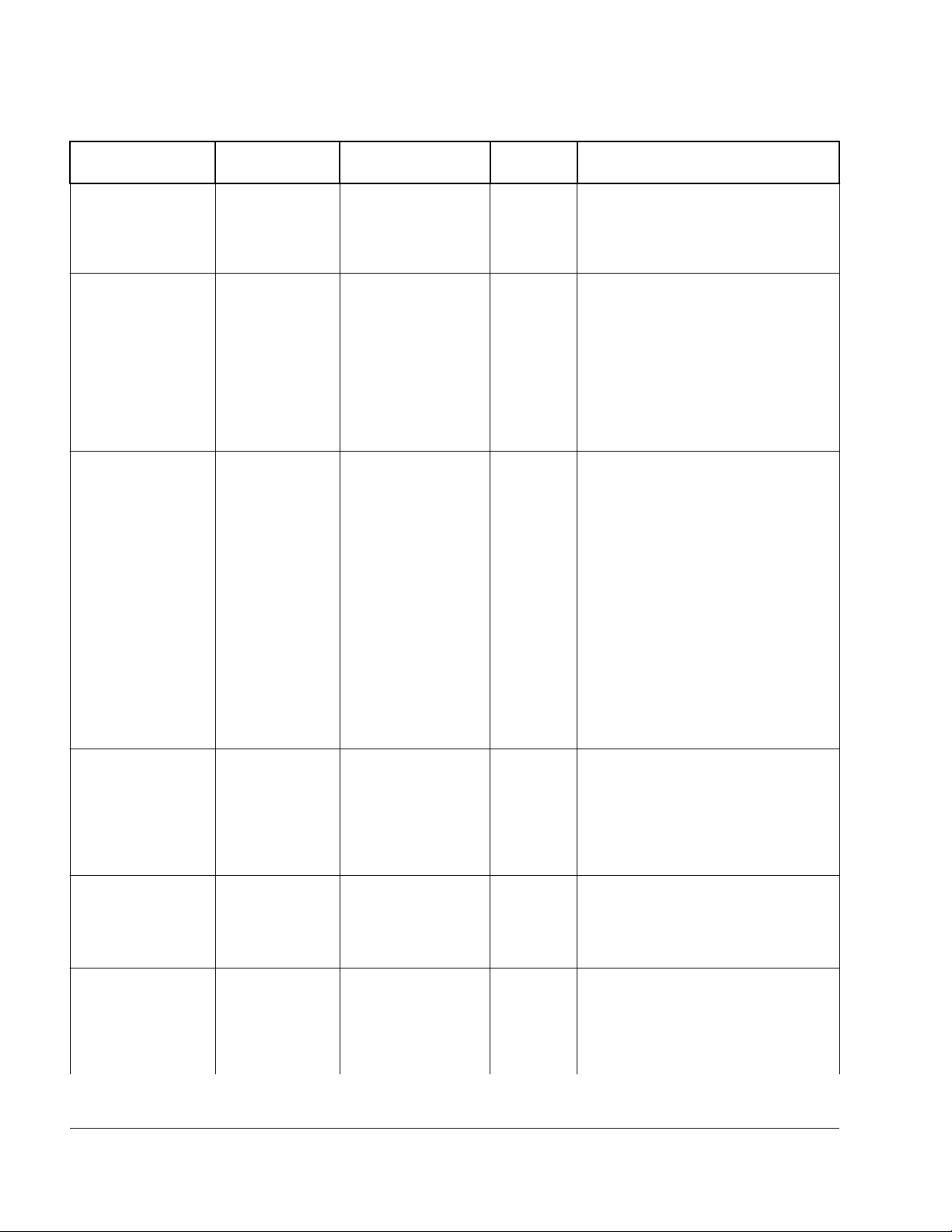

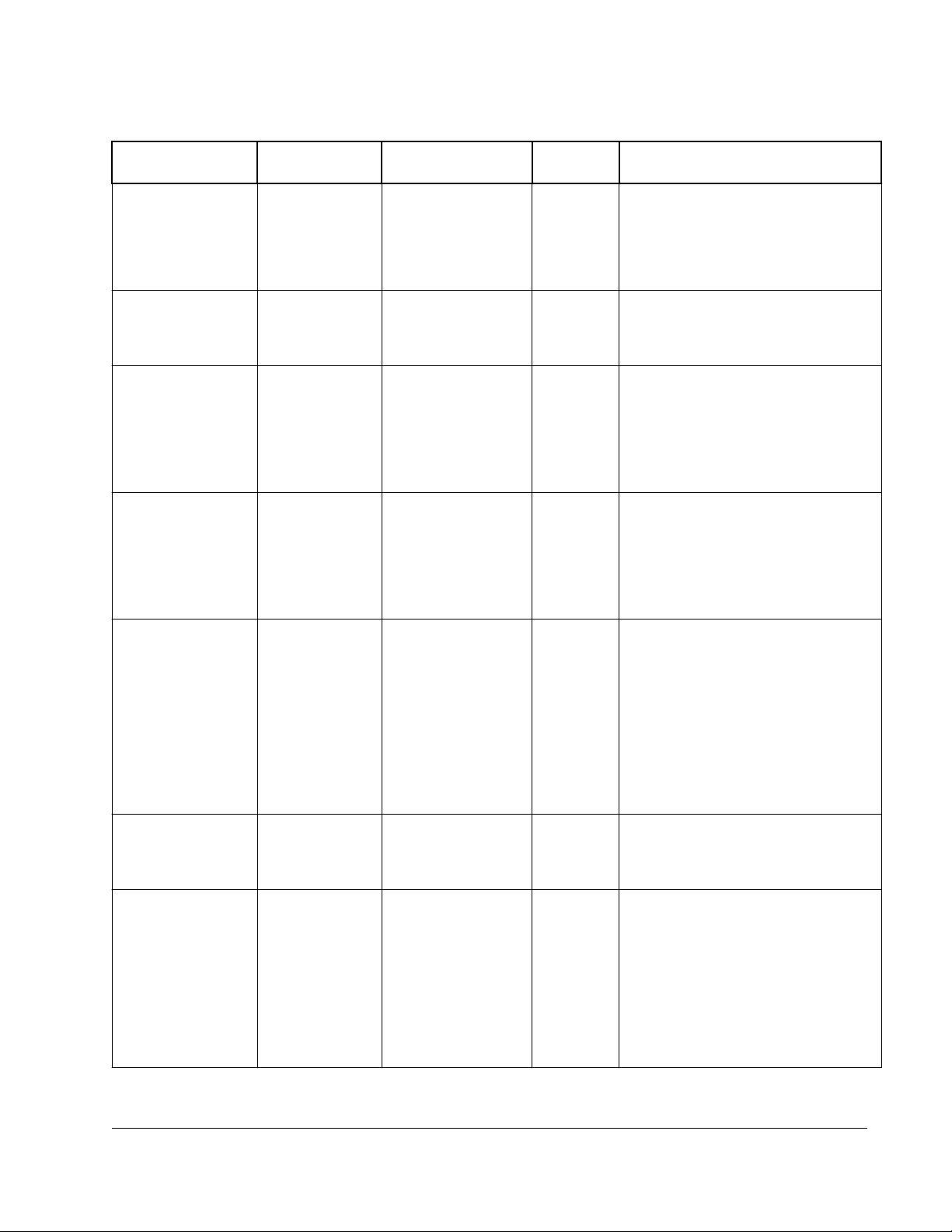

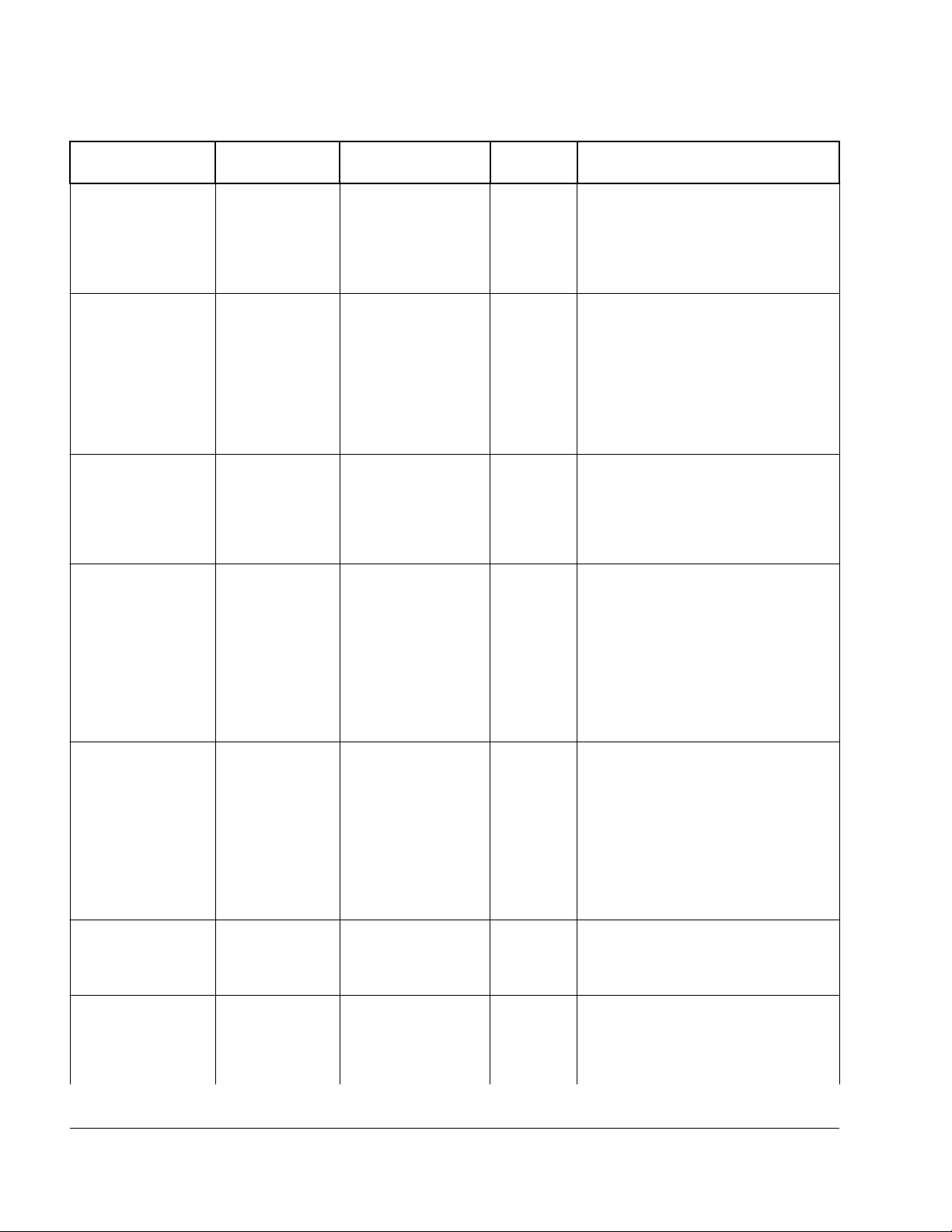

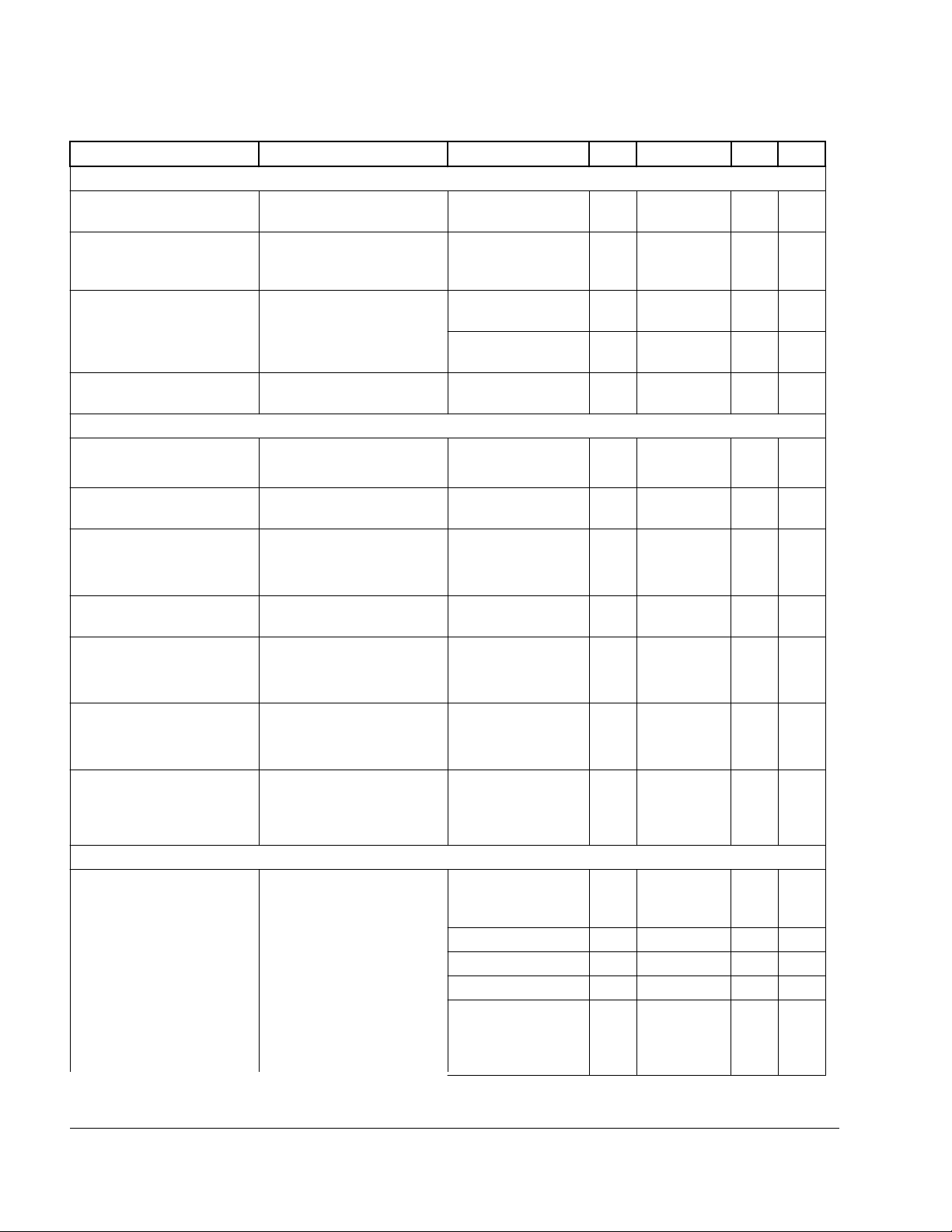

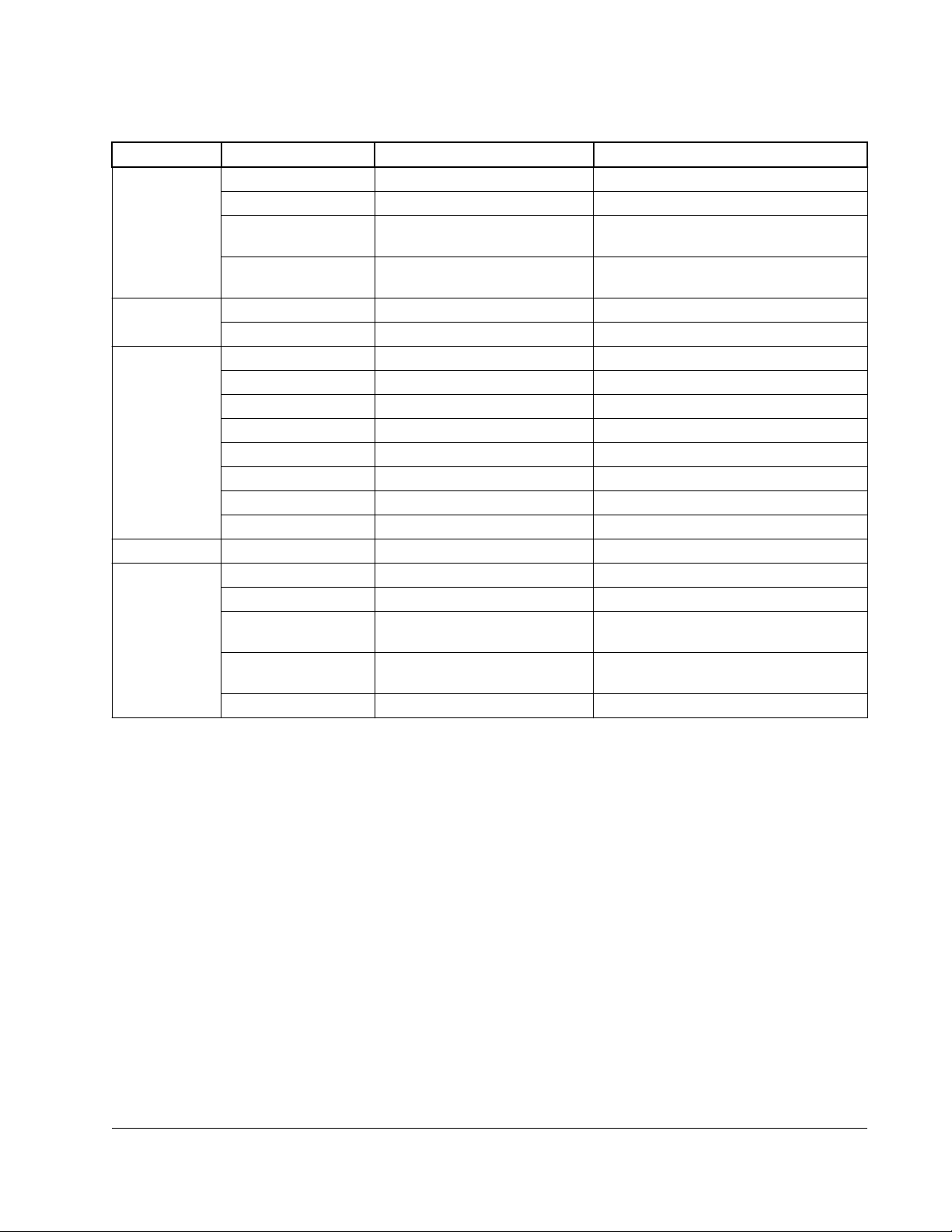

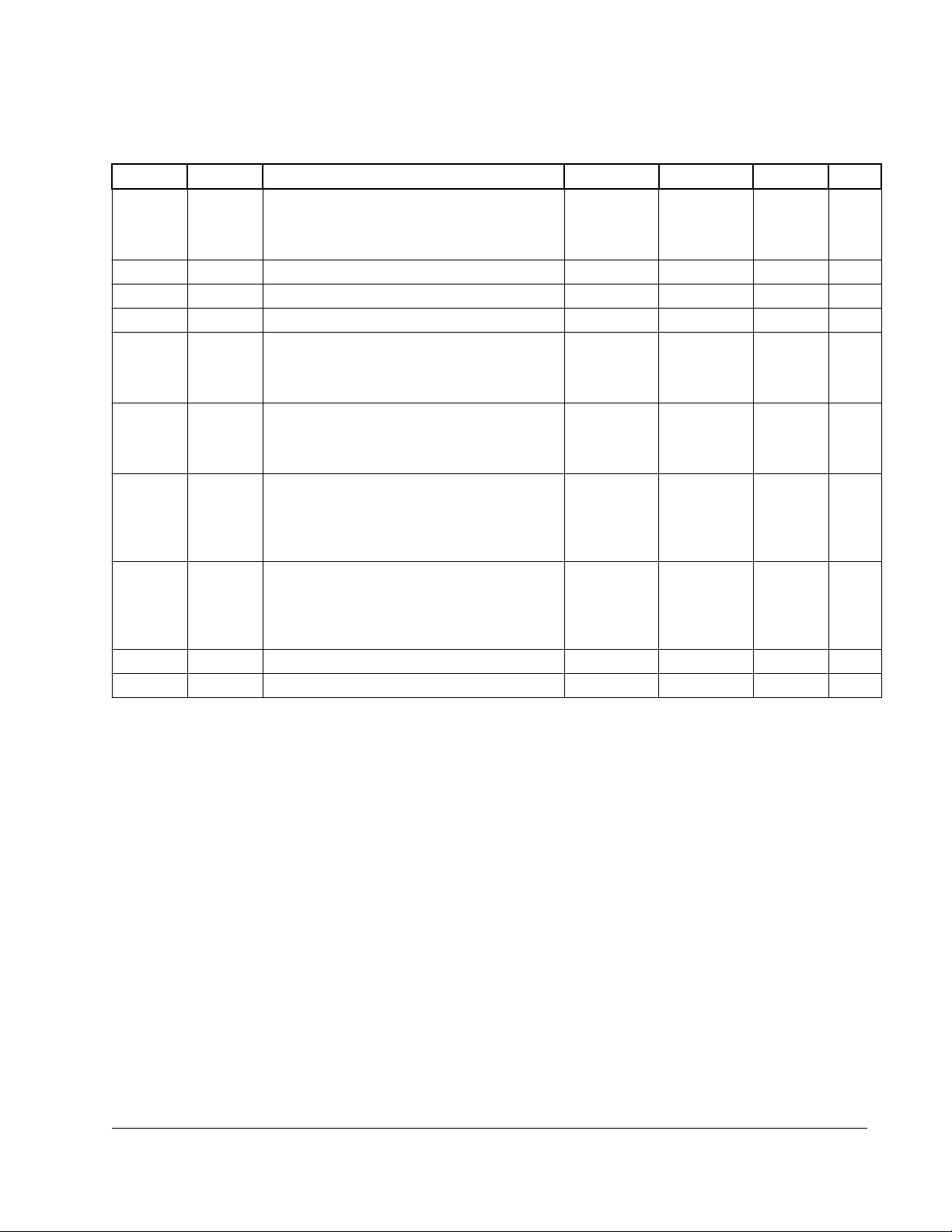

Table 1. i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

AMBA Network

Interconnect Crossbar

Analog PMC

Analog-to-Digital

Converter

NIC0-1 DMA and Bus Fabrics AD The AMBA Network Interconnect

Analog PMC Power Management SYS The Analog PMC consists of voltage/

ADC0-1 Analog RT Analog-to-Digital Converter (ADC) is a

Table continues on the next page...

Brief description

Domain

Crossbar (NIC) is a highly configurable

and high performance AMBA-compliant

network infrastructure which arbitrates

between multiple AXI or AHB masters to

grant access to internal or external

memories or other slave devices. It

supports connectivity between several

slave and master ports for parallel

processing. It uses a hybrid round-robin

arbitration scheme and contains

frequency converters, data width

converters, bus protocol converter, and

AXI channel buffers.

current references, core logic supply

regulators, memory supply regulators,

Back and Forward Biasing regulators,

monitors and power switches, etc. There

are two Analog PMC subsystems in i.MX

7ULP, one associated with the M4 power

domain and the other with the A7 power

domain.

12-bit resolution, successive

approximation analog to digital

converter. The ADC module supports up

to 16 single-ended external analog

inputs. It outputs 12-bit, 10-bit, or 8-bit

digital signal in right-justified unsigned

8

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 9

Table 1. i.MX 7ULP modules list (continued)

i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

Domain

format. The ADC can achieve 1

microsecond conversion rate.

Asynchronous

Wakeup Interrupt

Controller

Bit Manipulation

Engine

Comparator CMP0-1 Analog DGO The (CMP) module provides a circuit for

Cross Trigger Matrix CTM Debug RT Cross Trigger Matrix (CTM) is a

Cryptographic

Acceleration and

Assurance

AWIC System Control RT The Asynchronous Wakeup Interrupt

Controller (AWIC) module is capable of

interrupt detection and wake-up of a

processor when it is in low power mode.

BME Multicore peripherals

and resource domain

control submodules

CAAM Security AD Cryptographic Acceleration and

Table continues on the next page...

RT The Bit Manipulation Engine (BME)

provides hardware support for atomic

read-modify-write memory operations to

the peripheral address space. This

architectural capability is also known as

"decorated storage" as it defines a

mechanism for providing additional

semantics for load and store operations

to memory-mapped peripherals beyond

just the reading and writing of data

values to the addressed memory

locations.

comparing two analog input voltages.

The comparator circuit is designed to

operate across the full range of the

supply voltage (rail to rail operation).

component of the Embedded Cross

Trigger (ECT), which is key in the

multicore debug strategy. The CTM

receives signals from various sources

(i.e. cores and peripherals) and

propagates or routes them to the

different debug resources of the SoC.

Those debug resources can include time

stamping capability, real-time trace,

triggers and debug interrupts.

Assurance Module (CAAM) is a

multifunction accelerator that supports

the cryptographic functions common in

many security protocols. This includes

AES128, AES256, DES, 3DES, SHA1,

SHA224, SHA256, and a random

number generator with a true entropic

seed. CAAM includes a DMA engine that

is descriptor based to reduce processoraccelerator interaction. Security feature

clear keys and memories when on-chip

security monitor detects tampering. The

Secure RAM is implemented and

provides secure storage of sensitive

information both in on-chip RAM and in

Brief description

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

9

NXP Semiconductors

Page 10

i.MX 7ULP modules list

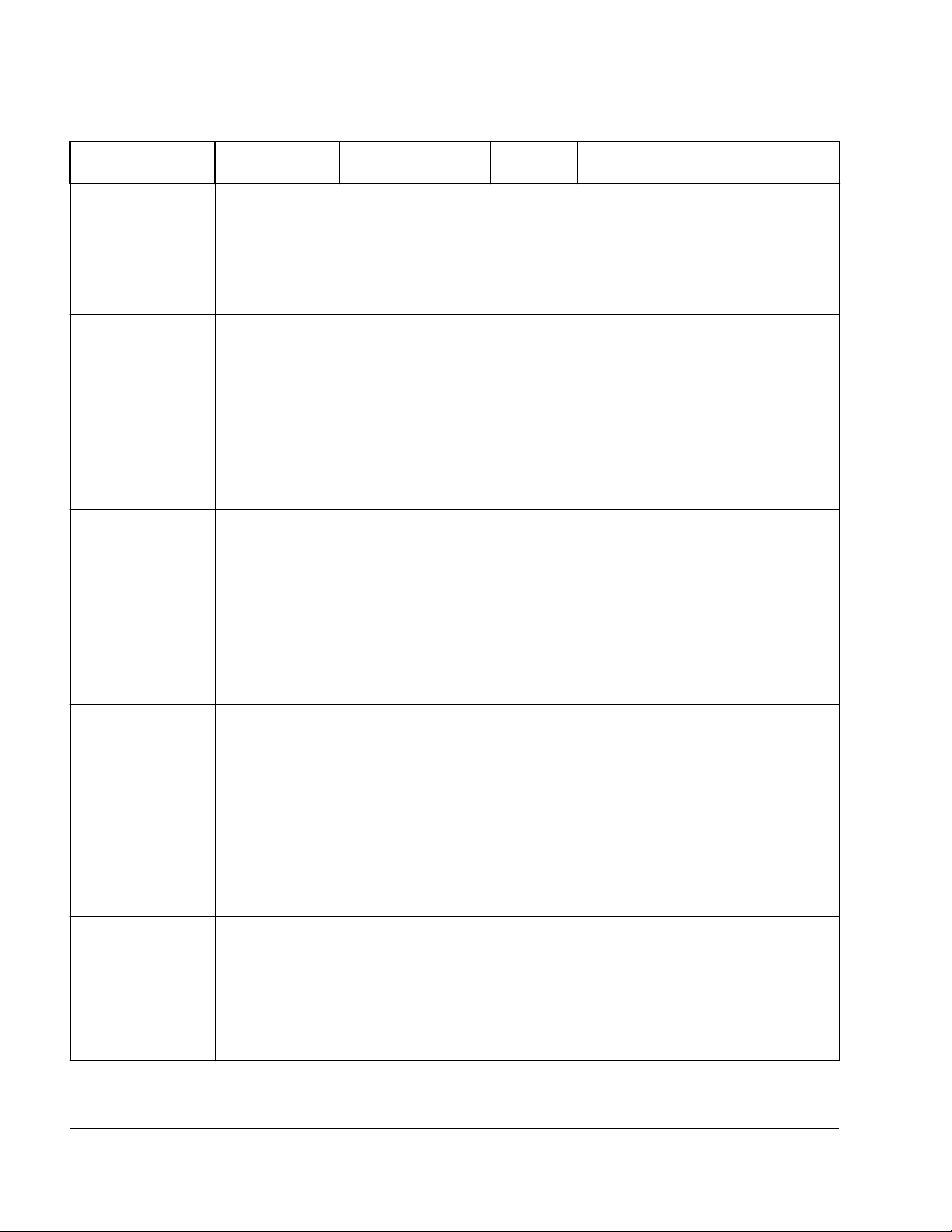

Table 1. i.MX 7ULP modules list (continued)

Block Name Block Mnemonic Subsystem Power

Domain

off-chip, nonvolatile memory. For details,

see the i.MX 7ULP Security Reference

Manual.

Cyclic Redundancy

Check

Debug Access Port DAP Debug RT Debug Port Access (DAP) provides

Digital PMC Digital PMC Power Management SYS The Digital PMC module allows user

Digital-to-Analog

Converter

Direct Memory

Access

Direct Memory

Access Multiplexer

CRC Connectivity and

Communications

DAC0-1 Analog RT Digital-to-Analog Converter (DAC) is the

DMA0-1 DMA and Bus Fabrics AD, RT Direct Memory Access (DMA) is capable

DMAMUX0-1 DMA and Bus Fabrics AD, RT The Direct Memory Access Multiplexer

Table continues on the next page...

RT The Cyclic Redundancy Check (CRC)

module is a hardware CRC generator

circuit using 16/32-bit shift register. The

CRC module supports error detection for

all single, double, odd, and most multibits errors, programmable initial seed

value, and optional feature to transpose

input data and CRC result via transpose

register.

debugger access to on-chip system

resources via the SWJ-DP port. The

DAP provides internal system access to

A7 Debug Port, M4 Debug Port, System

Bus, JTAG controller, and SoC Control

and Status. The DAP also enables

system access to CoreSight debug

subsystem through the APBIC port.

software to control power modes of the

chip and to optimize power consumption

for the level of functionality needed.

There are two instances of Digital PMC

on this device, one for each main power

domain.

12-bit resolution digital-to-analog

converters with programmable reference

generator output. The output of the DAC

can be placed on an external pin or set

as one of the inputs to the analog

comparator or ADC. The DAC is capable

of achieving 1 ms conversion rate for

high-speed signals and 2 ms conversion

rate for low-speed signals.

of performing complex data transfers

with minimal intervention from a host

processor. Each DMA module supports

32 DMA channels. The transfer control

descriptors for each of the 32 channels

locate in system memory. DMA0 is in the

real-time domain. DMA1 is in the

application domain.

(DMAMUX) module routes DMA

sources, called slots, to any of the

Brief description

10

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 11

Table 1. i.MX 7ULP modules list (continued)

i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

Embedded Trace

FIFO

Embedded Trace

Router

Extended Resource

Domain Controller

External Bus Interface

ETF Debug RT The Embedded Trace FIFO (ETF)

ETR Debug RT The ETR is a trace sink that redirects the

XRDC Multicore Peripherals

and Resource Domain

Control submodules

FlexBus Memories and Memory

Controllers

Brief description

Domain

supported DMA channels. DMAMUX0 is

in the real-time domain. DMAMUX1 is in

the application domain.

consists of a formatter, control, and the

trace RAM. It is a configuration of the

Trace Memory Controller (TMC). The

ETF will have a memory size of

16Kbytes. The ETF and associated

memory should be connected in the

system such that it will retain the

information though a warm or cold reset

of the system. This is to allow for debug

information to be retained for debugging

problems that may arise and cause a

reset of the system.

trace stream onto the AXI bus to external

storage. It can utilize a single contiguous

region or a scattered allocation of blocks

for a circular buffer. Reading of the AXI

based trace buffer can either be done

directly over AXI from a normal bus

master. The ETR is a configuration

option of the TMC as is the ETF.

AD, RT The Extended Resource Domain

Controller (XRDC) provides an

integrated, scalable architectural

framework for access control, system

memory protection and peripheral

isolation. It allows software to assign

chip resources (like processor cores,

non-core bus masters, memory regions

and slave peripherals) to processing

domains, to support enforcement of

robust operational environments. The

XRDC implementation is distributed

across multiple submodules instantiated

throughout the device.

AD The External Bus Interface (FlexBus)

module provides external memory

expansion and provides connection to

external peripherals with a parallel,

memory-mapped interface. The FlexBus

supports asynchronous and

synchronous interface to external ROM,

NOR flash, SRAM, PSRAM,

programmable logic devices and other

memory-mapped slave devices.

Table continues on the next page...

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

11

NXP Semiconductors

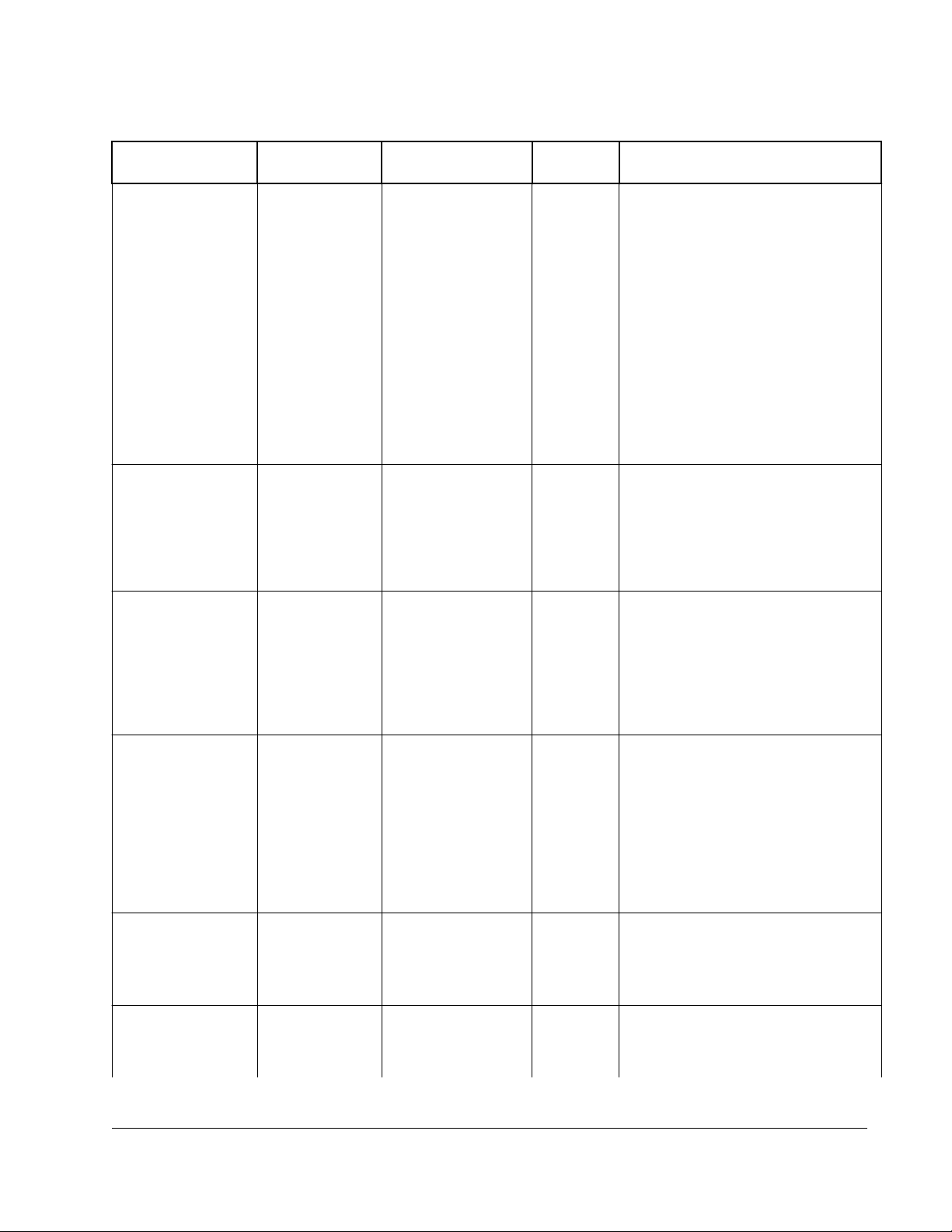

Page 12

i.MX 7ULP modules list

Table 1. i.MX 7ULP modules list (continued)

Block Name Block Mnemonic Subsystem Power

External Watchdog

Monitor

Fast Internal

Reference Clock

Fixed-frequency PLL Fixed-Freq PLL

Flexible Input/Output FLEXIO0-1 Connectivity and

Fractional-N PLL Frac-N PLL

GC320 Composition

Processing Core

EWM Timers RT The External Watchdog Monitor (EWM)

FIRC Clock Sources and

Control

Clock Sources and

(PLL0)

(PLL1-3)

GPU-2D Multimedia AD Vivante GC320 is a Composition

Control

Communications

Clock Sources and

Control

Table continues on the next page...

Brief description

Domain

module is designed to monitor external

circuits, as well as the software flow.

This provides a back-up mechanism to

the internal WDOG that can reset the

system. The EWM differs from the

internal WDOG in that it does not reset

the system. The EWM, if allowed to timeout, provides an independent trigger pin

that when asserted resets or places an

external circuit into a safe mode.

SYS The Fast Internal Reference Clock

(FIRC) module is an internal oscillator

that can generate a reference clock in

the range from 48 MHz to 60 MHz. The

FIRC output clock is used as a reference

to the SCG module, and it is also used

as a clock option to most on-chip

modules.

SYS The Fixed-frequency PLL is the same as

the USB PLL. In addition to the main

clock output, this PLL also includes 4

Phase Fractional Dividers (PFDs) that

can generate other clock frequencies.

There is one instance of the Fixed-freq

PLL (PLL0) provides clocks for M4 core

and buses and peripherals in the Realtime domains.

AD, RT The Flexible Input/Output (FlexIO)

module is capable of supporting a wide

range of protocols including, but not

limited to: UART, I2C, SPI, I2S, camera

interface, display interface, PWM

waveform generation, etc. FlexIO0 is in

the real-time domain. FlexIO1 is in the

application domain.

SYS The Fractional-N (Frac-N) PLL can

generate an output clock of 528 MHz

from a supported reference clock. In

addition to the main clock output, this

PLL also includes up to 4 Phase

Fractional Dividers (PFDs) that can

generate other clock frequencies. This

PLL also supports tunable clock for

audio applications.

Processing Core (CPC) GPU. It supports

user interface rendering and performs

functions like blending, filtering, rotation,

12

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 13

Table 1. i.MX 7ULP modules list (continued)

i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

GC7000 Nano Ultra

Graphic Processing

Unit

Hardware Semaphore SEMA42_0 and

Input/Output

Multiplexing

Controller

Internal Reference

Clock 1kHz

Joint Test Action

Group Controller

LCD Interface

Controller

GPU-3D Multimedia AD i.MX 7ULP integrates the Vivante

Multicore Peripherals

SEMA42_1

IOMUXC0-1 &

IOMUXC_DDR

IRC1K Clock Sources and

JTAGC Debug RT Joint Test Action Group Controller

LCDIF Multimedia AD The LCDIF is a general purpose display

and Resource Domain

Control submodules

System Control AD, RT The Input/Output Multiplexing Controller

Control

Table continues on the next page...

Brief description

Domain

overlay, resizing, transparency, and

other dynamic effects.

GC7000 Nano Ultra Graphic Processing

Unit (GPU-3D). supporting OpenGL

ES2.0/1.1, Desktop OpenGL 2.1,

OpenVG1.1, and GLSL shading

language support.

AD, RT The Hardware Semaphore (SEMA42)

module provides the hardware support

needed in multicore systems for

implementing semaphores and provide a

simple mechanism to achieve "lock/

unlock" operations via a single write

access. SEMA42_0 is in the real-time

domain. SEMA42_1 is in the application

domain.

(IOMUXC) enables the chip to share one

pad for multiple signals from different

peripheral interfaces. This pad sharing

mechanism is done by multiplexing the

pad's input and output signals. The

IOMUXC also controls the pads setting

parameters and digital filter functions of

the pad. In addition, the IOMUXC

controls input multiplexing logic for input

signals multiplexed at multiple locations.

IOMUXC0 is in the real-time domain.

IOMUXC1 and IOMUXC_DDR are in the

application domain.

SYS The Internal Reference Clock 1kHz

(IRC1K) module is an internal oscillator

that can generate a reference clock of

1kHz. The IRC1K clock is enabled in all

modes of operation, including all low

power modes.

(JTAGC) provides the means to test chip

functionality and connectivity while

remaining transparent to system logic

when not in test mode. Testing is

performed via a boundary scan

technique, as defined in the IEEE

1149.1-2001 standard.

controller used to drive a wide range of

display devices varying in size and

capabilities. The LCDIF is used as a

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

13

NXP Semiconductors

Page 14

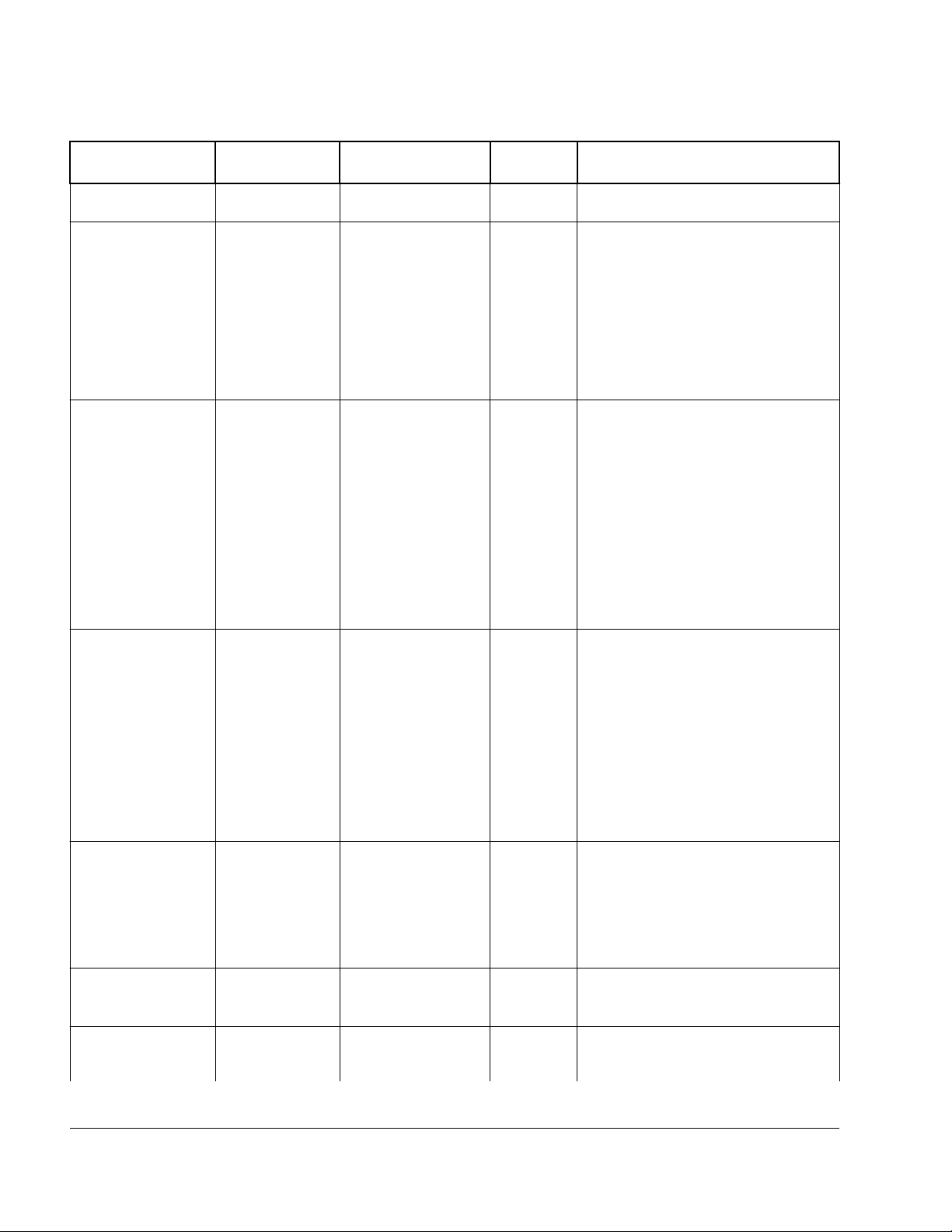

i.MX 7ULP modules list

Table 1. i.MX 7ULP modules list (continued)

Block Name Block Mnemonic Subsystem Power

Low-Leakage WakeUp Unit

Low Power InterIntegrated Circuit

Low Power Periodic

Interrupt Timer

Low Power Serial

Peripheral Interface

Low-power Trusted

Cryptography

LLWU System Control DGO The Low-Leakage Wake-Up Unit (LLWU)

LPI2C0-7 Connectivity and

Communications

LPIT0-1 Timers AD, RT Low Power Periodic Interrupt Timer

LPSPI0-3 Connectivity and

Communications

LTC Security RT Low-power Trusted Cryptography is an

Brief description

Domain

bridge between the DSI controller and

the NIC0 crossbar.

module allows user to select up to 32

external pin sources and up to 8 internal

modules as a wakeup source from low

leakage power modes.

AD, RT The Low Power Inter-Integrated Circuit

(LPI2C) module implements an efficient

interface to an I2C bus as a master. The

LPI2C can continue operating while the

processor is in stop mode provided an

appropriate peripheral clock is available.

This module is designed for low CPU

overhead with DMA offloading of FIFO

register accesses. LPI2C0 - LPI2C3 are

in the real-time domain. LPI2C4 LPI2C7 are in the application domain.

(LPIT) is a multichannel timer module

that can generate independent pretrigger and trigger outputs. These timer

channels can operate individually or can

be chained together. The pre-trigger and

trigger outputs can be used to trigger

other modules on the device. The LPIT

can also operate in low power modes.

LPIT0 is in the real-time domain. LPIT1

is in the application domain.

AD, RT The Low Power Serial Peripheral

Interface (LPSPI) module implements an

efficient interface to an SPI bus as a

master and/or a slave. The LPSPI can

continue operating while the processor is

in stop mode if an appropriate peripheral

clock is available. This module is

designed for low CPU overhead with

DMA offloading of FIFO register

accesses. LPSPI0 and LPSPI1 are in the

real-time domain. LPSPI2 and LPSPI3

are in the application domain.

architecture that allows multiple

cryptographic hardware accelerator

engines to be instantiated and share

common registers. This version of LTC

supports 128-bit AES. For details, see

the i.MX 7ULP Security Reference

Manual.

14

NXP Semiconductors

Table continues on the next page...

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 15

Table 1. i.MX 7ULP modules list (continued)

i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

Low Power Universal

Asynchronous

Receiver/Transmitter

Low Power Timer

Memory-Mapped

Cryptographic

Acceleration Unit

Messaging Unit MU Multicore Peripherals

MIPI Display Serial

Interface Controller

MIPI Display Serial

Interface Physical

Layer

LPUART0-7 Connectivity and

Communications

LPTMR0-1 Timers DGO The Low Power Timer (LPTMR) module

MMCAU Security RT Memory-Mapped Cryptographic

and Resource Domain

Control submodules

DSI Controller Multimedia AD The MIPI Display Serial Interface

DSI PHY Multimedia AD The MIPI Display Serial Interface

Table continues on the next page...

Brief description

Domain

AD, RT The Low Power Universal Asynchronous

Receiver/Transmitter (LPUART) module

provides asynchronous, serial

communication capability with external

devices. LPUART supports non-returnto-zero (NRZ) encoding format and IrDAcompatible infrared (low-speed) SIR

format. The LPUART can continue

operating while the processor is in stop

mode if an appropriate peripheral clock

is available. This module is designed for

low CPU overhead with DMA offloading

of FIFO register accesses. LPUART0 –

LPUART3 are in the real-time domain.

LPUART4 – LPUART7 are in the

application domain.

is a 16-bit timer which operates as realtime interrupt or pulse accumulator. This

LPTMR module can remain functional

when the chip is in low power modes,

provided the reference clock to this timer

is active.

Acceleration Unit (MMCAU) is an

optimized security accelerator that

supports the cryptographic functions

common in many security protocols. This

includes DES, 3DES, AES, MD5, SHA-1,

SHA-256 algorithms via simple C calls to

optimized security functions.

RT Messaging Unit (MU) is a shared

peripheral with a 32-bit IP bus interface

and interrupt request signals to each

host processor. The MU exposes a set

of registers to each processor which

facilitate inter-processor communication

via 32-bit words, interrupts and flags.

Interrupts may be independently masked

by each processor to allow polled-mode

operation.

Controller (DSI Controller) is responsible

for serializing display data from the GPU.

Data can come from either the GPU or

the processor/DMA controller.

Physical Layer (DSI PHY) is a two-lane

interface that supports up to 1 Gbps of

data on each lane. DSI PHY includes a

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

15

NXP Semiconductors

Page 16

i.MX 7ULP modules list

Table 1. i.MX 7ULP modules list (continued)

Block Name Block Mnemonic Subsystem Power

Multicore System

Mode Controller

Multi Mode DDR

Controller

On-The-Fly AES

Decryption

Peripheral Clock

Control

Reset Mode

Controller

On-Chip One-TimeProgrammable

Controller

MSMC System Control DGO Multicore System Mode Controller

MMDC Memories and Memory

Controllers

OTFAD Security RT The On-The-Fly AES Decryption

PCC0-3 Clock Sources and

Control

RMC System Control DGO Reset Mode Controller (RMC)

OCOTP_CTRL System Control RT The On-Chip One-Time-Programmable

Table continues on the next page...

Brief description

Domain

PLL which output clock is dedicated DSI

uses.

(MSMC) is responsible for sequencing

the system into and out of all low power

Stop and Run modes. MSMC monitors

events to trigger transitions between

power modes, while controlling the

power, clocks, and memories of the

system to achieve the power

consumption and functionality of that

mode.

AD The Multi Mode DDR Controller (MMDC)

is a configurable DDR controller that

provides interface to LPDDR2 or

LPDDR3 memory. The MMDC consists

of a core and PHY. The core is

responsible for communication with the

system through AXI interface, DDR

commands generation, DDR command

optimizations, and read/ write data path.

The PHY performs timing adjustment

using special calibration mechanisms to

ensure data capture margin at the

supported clock rate.

(OTFAD) module provides an advanced

hardware implementation that minimizes

any incremental cycles of latency

introduced by the decryption in the

overall external memory access time.

The OTFAD engine also includes

complete hardware support for a

standard AES key unwrap mechanism to

decrypt a key BLOB data instruction

containing the parameters needed for up

to 4 unique AES contexts.

AD, RT The Peripheral Clock Control (PCC)

module is responsible for clock selection,

optional division and clock gating mode

for peripherals in their respected power

domain. PCC0 and PCC1 are in the realtime domain. PCC2 and PCC3 are in the

application domain.

implements reset modes and reset

functions of the chip.

Controller (OCOTP_CTRL) module

provides an interface for reading,

16

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 17

Table 1. i.MX 7ULP modules list (continued)

i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

Domain

programming and/or overriding

identification and control information

stored in on-chip fuse elements. The

module supports electricallyprogrammable poly fuses. The

OCOTP_CTRL also provides a set of

volatile software-accessible signals

which can be used for software control of

hardware elements, not requiring nonvolatility.

Peripheral Trigger

Multiplexing

Port Control PCTL_A-F System Control AD, RT The Port Control (PCTL) module

Quad Serial

Peripheral Interface

Rapid GeneralPurpose Input and

Output

Read-only memory

Controller

Real Time Clock

Oscillator

Single Wire Output SWO Debug RT Single Wire Output (SWO) is a trace

TRGMUX0-1 System Control AD, RT Peripheral Trigger Multiplexing

(TRGMUX) TRGMUX0 is in the real-time

domain. TRGMUX1 is in the application

domain.

provides control for GPIO interrupt

function. GPIO interrupt can be

configured independently for each pin in

the 32-bit port. There is one instance of

the PCTL module for each port. PCTL_A

and PCTL_B are in the real-time domain.

PCTL_C - PCTL_F are in the application

domain.

QSPI Memories and Memory

Controllers

RGPIO2P0-1 System Control AD, RT The Rapid General-Purpose Input and

ROMCP0/1 Memories and Memory

Controllers

RTC OSC Clock Sources and

Control

Table continues on the next page...

RT The Quad Serial Peripheral Interface

(QSPI) module provides an interface to

various types of serial flash memory.

The QSPI interface allows one serial

flash connection. It supports 1-bit, 4-bit

and 8-bit SPI bus width.

Output with 2 Ports (RGPIO2P) is similar

to the RGPIO module, except it has an

AHB-lite port, in addition to the IPS port,

for faster access. RGPIO2P0 is in the

real-time domain. RGPIO2P1 is in the

application domain.

AD, RT A ROM controller and boot ROM are

present in for both the A7 and M4 CPU

cores. ROMCP0 and a 64 kB ROM are

in the real-time domain. ROMCP1 and a

96 kB ROM are in the application

domain.

VBAT The Real Time Clock Oscillator (RTC

OSC) module provides the clock source

for the Real-Time Clock module. The

RTC OSC module, in conjunction with an

external crystal, generates a 32.678 kHz

reference clock for the RTC.

data drain that acts as bridge between

Brief description

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

17

NXP Semiconductors

Page 18

i.MX 7ULP modules list

Table 1. i.MX 7ULP modules list (continued)

Block Name Block Mnemonic Subsystem Power

Secure JTAG

Controller

Secure Non-Volatile

Storage

Slow Internal

Reference Clock

Synchronous Audio

Interface

System Clock

Generation

SJC Debug RT The Secure JTAG Controller (SJC) is an

SNVS Security VBAT The Secure Non-Volatile Storage

SIRC Clock Sources and

Control

SAI0-1 Multimedia RT The Synchronous Audio Interface (SAI)

SCG0-1 Clock Sources and

Control

Table continues on the next page...

Brief description

Domain

the on-chip trace data to a data stream

that is captured by the Trace Port

Analyzer. It is a TPIU-like device that

supports a limited subset of the full TPIU

functionality for a simple debug solution.

authenticated debug module that

implements a challenge/response

mechanism using a standard

cryptographic algorithm. This allows post

production silicon debug without

compromising security requirements.

The SJC is connected in parallel with the

JTAGC module, but it is only used for

authenticated debug.

(SNVS) module is designed to safely

hold security-related data such as

cryptographic key, time counter,

monotonic counter, and general purpose

security information. A part of the SNVS

module belongs to the VBAT domain

that has its own dedicated power supply

which is always on. This enables SNVS

to keep this data valid and continue to

increment the time counter when the

power goes down in the rest of the SoC.

SNVS includes the Real-Time Clock

(RTC) module, which provides 64-bit

monotonic counter with roll-over

protection, 32-bit seconds counter with

roll-over protection and 32-bit alarm.

SYS The Slow Internal Reference Clock

(SIRC) module is an internal oscillator

that can generate a reference clock of 16

MHz. The SIRC output clock is used as

a reference to the SCG module, and it is

also used as a clock option to most onchip modules.

module implements full-duplex serial

interfaces with frame synchronization

such as I2S, AC97, and CODEC/DSP

interfaces.

AD, RT The System Clock Generation (SCG)

module is responsible for clock

generation and distribution across this

device. Functions performed by the SCG

include: clock reference selection,

generation of clock used to derive

18

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 19

Table 1. i.MX 7ULP modules list (continued)

i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

Domain

processor, system, peripheral bus and

external memory interface clocks; source

selection for peripheral clocks; and,

control of power saving clock gating

mode. SCG0 is in the real-time domain.

SCG1 is in the application domain.

System Integration

Module

System Oscillator SYS OSC Clock Sources and

Tightly-Coupled

Memory

Timer/Pulse Width

Modulation

TimeStamp

Components

Timestamp timer TSTMR Timers AD, RT The TSTMR module is a free running

SIM System Control AD, RT The System Integration Module (SIM)

provides system control and chip

configuration registers. The SIM includes

the TSTMR module.

SYS The System Oscillator (SYS OSC)

Control

TCM Memories and Memory

Controllers

LPTPM0-7 Timers AD, RT The Timer/Pulse Width Modulation

TimeStamp

Components

Debug RT The timestamp components generate

RT Tightly Coupled Memory (TCM) RAM.

module is a crystal oscillator. The SYS

OSC, in conjunction with an external

crystal or resonator, generates a

reference clock for this device. It also

optionally supports an external input

clock provided to EXTAL signal directly.

This RAM is tightly integrated to the M4

processor. M4 accesses this memory

with zero wait-state. There is a backdoor

port that allows M4 DMA and other bus

masters in the SoC to access this

memory.

Module (TPM) is a multichannel timer

module that supports input capture,

output compare, and the generation of

PWM signals. The counter, compare and

capture registers are clocked by an

asynchronous clock that can remain

enabled in low power modes. LPTPM0 –

LPTPM3 are in the real-time domain.

LPTPM4 – LPTPM7 are in the

application domain.

and distribute a consistent timestamp

value for multiple processors and other

blocks in a SoC.

incrementing counter that starts running

after system reset de-assertion and can

be read at any time by the software for

determining the software ticks. The

TSTMR is a 64-bit clock cycle counter. It

runs off the 1 MHz clock and resets on

every system reset. The counter only

stops when the clock to the TSTMR is

disabled.

Brief description

Table continues on the next page...

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

19

NXP Semiconductors

Page 20

i.MX 7ULP modules list

Table 1. i.MX 7ULP modules list (continued)

Block Name Block Mnemonic Subsystem Power

Domain

Trace Funnel FUNL Debug RT The Trace Funnel (FUNL) is used when

there is more than one trace source. The

Trace Funnel combines multiple trace

streams onto a single ATB bus. The

Trace Funnel includes an arbiter that

determines the priority of the ATB inputs.

Trace Port Interface

Unit

Trace Replicator Replicator Debug RT The Trace Replicator (Replicator)

True Random

Number Generator

ultra Secured Digital

Host Controller

Universal Serial Bus

High-Speed Inter

Chip Physical Layer

Universal Serial Bus

On-The-Go

TPIU Debug RT Trace Port Interface Unit (TPIU) acts as

a bridge between on-chip trace data, ID

distinguishable, and a TPA. It receives

ATB trace data and sends it off chip via

ARM’s standard trace interface. The

TPIU includes ATB interface, APB

interface, Formatter, Asynchronous

FIFO, Register bank, Trace out

serializer, and a pattern generator.

enables two trace sinks (TPIU and TMC)

to be wired together and receive ATB

trace data from the same trace source. It

takes incoming data from a single source

and replicates it to two master ports.

TRNG Security RT The True Random Number Generator

(TRNG) module is to generate high

quality, cryptographically secure, random

data. The TRNG module is capable of

generating its own entropy using an

integrated ring oscillator. In addition, the

module’s NIST certifiable PseudoRandom Number Generator (PRNG)

provides accelerated processing of

pseudo-random data.

uSDHC0/1 Memories and Memory

Controllers

HSIC-PHY Connectivity and

Communications

USB-OTG Connectivity and

Communications

Table continues on the next page...

AD The ultra Secured Digital Host Controller

(uSDHC) provides the interface between

the host system and SD, SDIO or eMMC

cards. The uSDHC acts as a bridge,

passing host bus transactions to the

cards by sending commands and

performing data accesses to/from the

cards or devices. It handles SD, SDIO

and eMMC protocol at transmission

level.

AD USB High-Speed Inter Chip Physical

Layer (HSIC-PHY) is a complete digital

IP designed to implement USB 2.0 HSIC

connectivity interface.

AD The Universal System Bus On-The-Go

(USB-OTG) module is a USB 2.0compliant implementation. The registers

and data structures of this USB

controller are based on the Enhanced

Brief description

20

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 21

Table 1. i.MX 7ULP modules list (continued)

i.MX 7ULP modules list

Block Name Block Mnemonic Subsystem Power

Domain

Host Controller Interface Specification

for Universal Serial Bus (EHCI). This

module can act as a host, a device or an

On-The-Go negotiable host/device on

the USB bus.

Universal Serial Bus

Phase Locked Loop

Universal Serial Bus

Physical Layer

Video Input Unit VIU Multimedia AD The Video Input Unit (VIU) provides a

Wakeup Unit WKPU System Control AD Wakeup Unit (WKPU) module is capable

Watchdog Timer WDOG0-2 Timers AD, RT The Watchdog Timer (WDOG) module

USB PLL Clock Sources and

Control

USB-PHY Connectivity and

Communications

Table continues on the next page...

AD USB Phase Locked Loop (USB PLL) is

embedded in the USB transceiver block.

This PLL allows an exact 480 MHz to be

generated from a supported reference

clock of 24 MHz. The output of this PLL

is primarily used for PLL operation. The

USB PLL clock is also made available as

a clock source for other peripherals in

the SoC.

AD The Universal System Bus Physical

Layer (USB-PHY) implements USB

physical layer connecting to USB host/

device systems at low-speed, full-speed,

and high-speed. USB-PHY provides a

standard UTMI interface for connection

to the USB-OTG controller.

parallel interface for digital video. The

VIU accepts various types of digital

video input on its parallel interface,

decodes it and optionally performs

processes such as down-scaling,

horizontal up-scaling, brightness and

contrast adjustment, pixel format

conversion, deinterlacing and horizontal

mirroring. The resultant video stream is

then stored to system memory for

subsequent post-processing and display.

of interrupt detection and wake-up of the

Cortex-A processor when it is in low

power mode.

keeps a watch on the system functioning

and resets it in case of its failure.

Reasons for failure include run-away

software code and the stoppage of the

system clock that in a safety critical

system can lead to serious

consequences. In such cases, the

WDOG brings the system into a safe

state of operation. The WDOG monitors

the operation of the system by expecting

periodic communication from the

software, generally known as servicing

Brief description

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

21

NXP Semiconductors

Page 22

Clocking

Table 1. i.MX 7ULP modules list (continued)

Block Name Block Mnemonic Subsystem Power

XRDC Manager MGR Multicore Peripherals

and Resource Domain

Control submodules

XRDC Master Domain

Assignment Controller

XRDC Memory

Region Controller

XRDC Peripheral

Access Controller

MDAC Multicore Peripherals

and Resource Domain

Control submodules

MRC Multicore Peripherals

and Resource Domain

Control submodules

PAC Multicore Peripherals

and Resource Domain

Control submodules

Brief description

Domain

or refreshing the WDOG. If this periodic

refreshing does not occur, the WDOG

resets the system. WDOG0 is in the realtime domain. WDOG1 and WDOG2 are

in the application domain.

RT The XRDC Manager (MGR) submodule

coordinates all programming model

reads and writes.

AD, RT The XRDC Master Domain Assignment

Controller (MDAC) submodule handles

resource assignments and generation of

the domain identifiers.

AD, RT The XRDC Memory Region Controller

(MRC) submodule implements the

access controls for slave memories

based on the pre-programmed region

descriptor registers.

AD, RT The XRDC Peripheral Access Controller

(PAC) implements the access controls

for slave peripherals based on the preprogrammed domain access control

registers.

2 Clocking

2.1 Introduction

This section details the clock sources, distribution and management within the i.MX

7ULP. These functions are under joint control of the System Clock Generation (SCG)

modules, Peripheral Clock Control (PCC) modules, and Core Mode Controller (CMC)

blocks.

NOTE

References in this chapter to “Core 0” or “Processor A”

correspond to the Cortex M4 core. References in this chapter

to “Core 1” or “Processor B” correspond to the Cortex A7

core.

22

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 23

Clocking

The clocking scheme provides clear separation between M4 domain and A7 domain.

Except for a few clock sources shared between two domains, such as the System

Oscillator clock, the Slow IRC (SIRC), and the Fast IRC clock (FIRC), clock sources

and clock management are separated and contained within each domain.

M4 clock management consists of SCG0, PCC0, PCC1, and CMC0 modules.

A7 clock management consists of SCG1, PCC2, PCC3, and CMC1 modules.

2.2 Clock distribution

The SCG modules generate and distribute clocks on the device. SCG functions

include:

• clock reference selection

• generation of clock used to derive processor, system, peripheral bus and external

memory interface clocks

• source selection for peripheral clocks

• control of power-saving clock-gating mode

PCC modules control clock selection, optional division and clock gating mode for

peripherals.

NOTE

• To bypass system oscillator and directly apply clock

from pin, SCG_SOSCCFG[EREFS] should be set to 0.

The direct clock should be applied on the EXTAL pin.

• For using oscillator reference,

SCG_SOSCCSR[SOSCEN] and

SCG_SOSCCFG[EREFS] should both be set to 1.

2.3

External clock sources

In normal functional mode, this device operates off two primary external reference

clocks: System oscillator clock (SOSC) and RTC oscillator clock (ROSC):

• System oscillator clock is a high frequency reference clock with a frequency in

the range of 16 MHz to 32 MHz. This clock is used as a reference clock to the onchip PLLs which generate all the required high frequency clocks.

• RTC oscillator clock is the 32.768 kHz constant frequency, real-time clock.

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

23

NXP Semiconductors

Page 24

Clocking

2.4 Oscillators

The system oscillator, in conjunction with an external crystal or resonator, generates a

reference clock for the device. The system oscillator module supports 16-32 MHz

crystals or resonators. It also provides the option for an external input clock to EXTAL

signal directly.

The RTC oscillator is in the VBAT domain. The RTC oscillator module, in conjunction

with an external crystal, generates a 32.768 kHz real-time reference clock for the RTC

and will always be enabled and supplying clock to SRTC. This is the default clock

source.

2.5

Internal clock sources

This device is capable of generating these internal reference clocks:

• The FIRC is the fast IRC clock with nominal frequency in the range from 48 to 60

MHz. In addition, the FIRC provides a clock selection option for peripherals.

• The SIRC is the slow IRC clock with nominal frequency of 16 MHz. The SIRC

provides a clock selection option for peripherals.

• The IRC1K generates 1 kHz clock that is enabled in all modes of operation,

including all low power modes.

• The RTC OSC has the capability to provide nominal 32 kHz (not recommended for

accurate clock and normal operation) IRC in absence of the external OSC reference

clock if the VBAT domain is enabled.

NOTE

The internal oscillator is automatically multiplexed in the

clocking system when the system detects a loss of clock. The

internal oscillator will provide clocks to the same on-chip

modules as the external 32 kHz oscillator. The internal

oscillator is not precise relative to a crystal. While it will

provide a clock to the system, it generally will not be precise

enough for long-term time keeping. The internal oscillator is

anticipated to be useful for quicker start-up times and

tampering prevention, but should not be used as the exclusive

source for the 32 kHz clocks. An external 32 kHz clock

source must be used for production systems.

24

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 25

Application domain (implementing ARM Cortex-A7)

3 Application domain (implementing ARM Cortex-A7)

The application domain is built around an ARM Cortex-A7 processor optimized to

run nominally at 500 MHz, supported by a 32 KB L1 instruction and data cache, a

large L2 cache, and an LPDDR2/LPDDR3 memory interface. The Cortex-A7

processor is a high-performance low-power processor that implements the ARMv7-A

architecture. It uses the generic interrupt controller (GIC), generic 64-bit OS timer,

FPU and the ARM NEON SIMD engine. Additionally, all the optional debug features

are included.

3.1

Memory system—application domain

3.1.1 Internal memory (application domain)

3.1.2 Multi Mode DDR Controller (MMDC)

The Multi Mode DDR Controller is a dedicated interface to LPDDR2/LPDDR3

SDRAM.

The i.MX 7ULP MMDC is compatible with the following JEDEC-compliant memory

types:

• LPDDR2 SDRAM compliant to JESD209-2F LPDDR2 JEDEC standard released

June, 2013

• LPDDR3 SDRAM compliant to JESD209-3C JEDEC standard released August,

2015

MMDC operation with the standards stated above is contingent upon the board DDR

design adherence to the DDR design and layout requirements stated in the Hardware

Development Guide for the i.MX 7ULP Applications Processor (IMX7ULPHDG).

NOTE

For more information on MMDC, please refer to the

following Engineering Bulletin: EB00913 - LPDDR2/

LPDDR3 Parameter Optimizations for i.MX 7ULP.

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

25

NXP Semiconductors

Page 26

Application domain (implementing ARM Cortex-A7)

The table below shows the supported LPDDR2/LPDDR3 configurations:

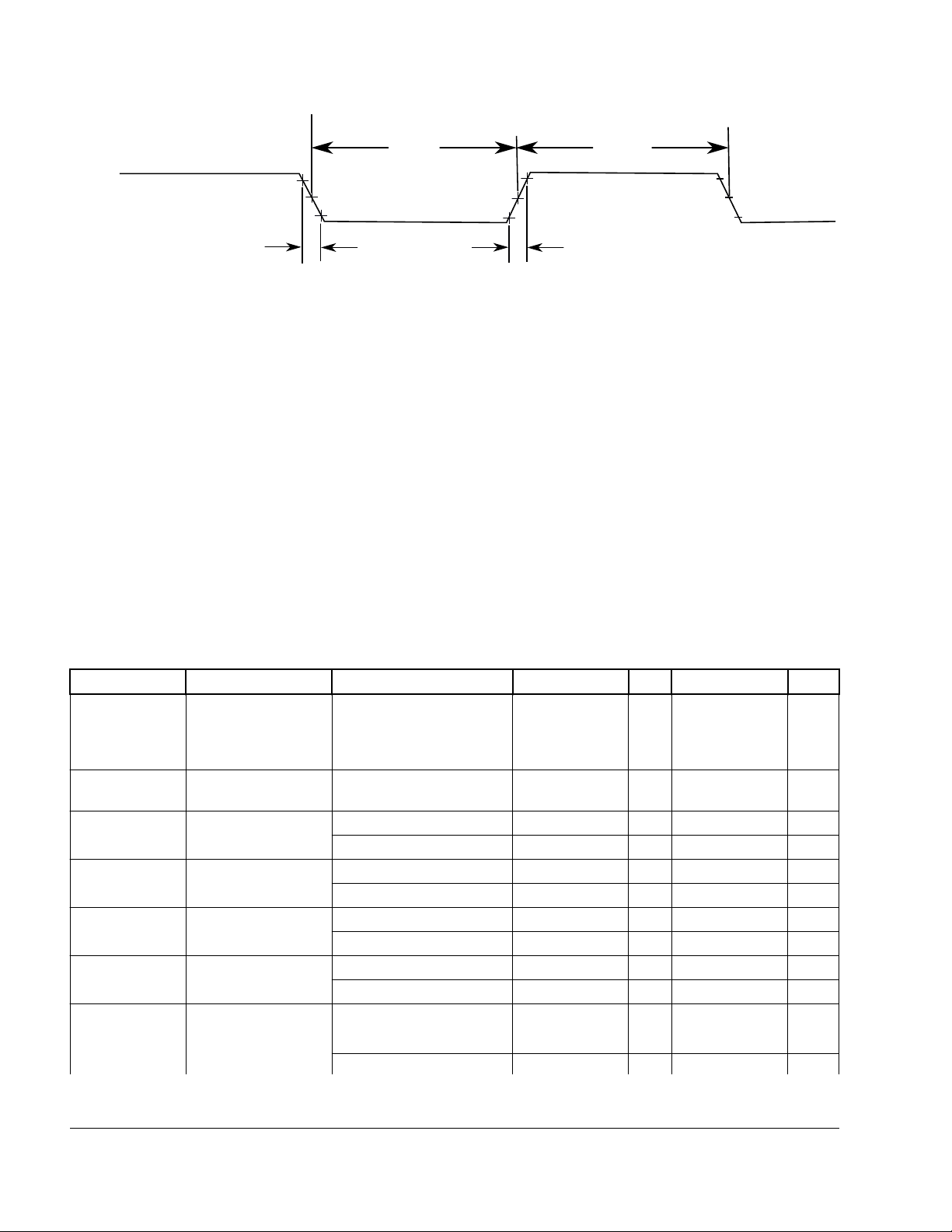

Table 2. i.MX 7ULP supported LPDDR2/LPDDR3 configurations

Parameter LPDDR2 LPDDR3

Clock frequency up to 380.16 MHz

Bus width x16/x32

Channel Single

Chip select Up to two

3.1.3 eMMC

eMMC is a managed NAND device.

See Ultra-high-speed SD/SDIO/MMC host interface (uSDHC) AC timing—application

domain.

3.2

Peripherals—application domain

3.2.1 Graphics processor human machine interfaces

The i.MX 7ULP Application Domain implements the following graphics processor

human machine interfaces:

• 3D graphics processing unit (GPU-3D)

• 2D graphics processing unit (GPU-2D)

• MIPI Display Serial Interface Controller (MIPI DSI)

• Video Interface Unit (VIU)

See the i.MX 7ULP modules list for more details.

3.2.2

3.2.2.1 True Random Number Generator (TRNG)

The TRNG module is used to generate high quality, cryptographically secure, random

data. The TRNG module is capable of generating its own entropy using an integrated

ring oscillator. In addition, the module’s Pseudo-Random Number Generator (PRNG)

provides accelerated processing of pseudo-random data.

Security—application domain

26

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 27

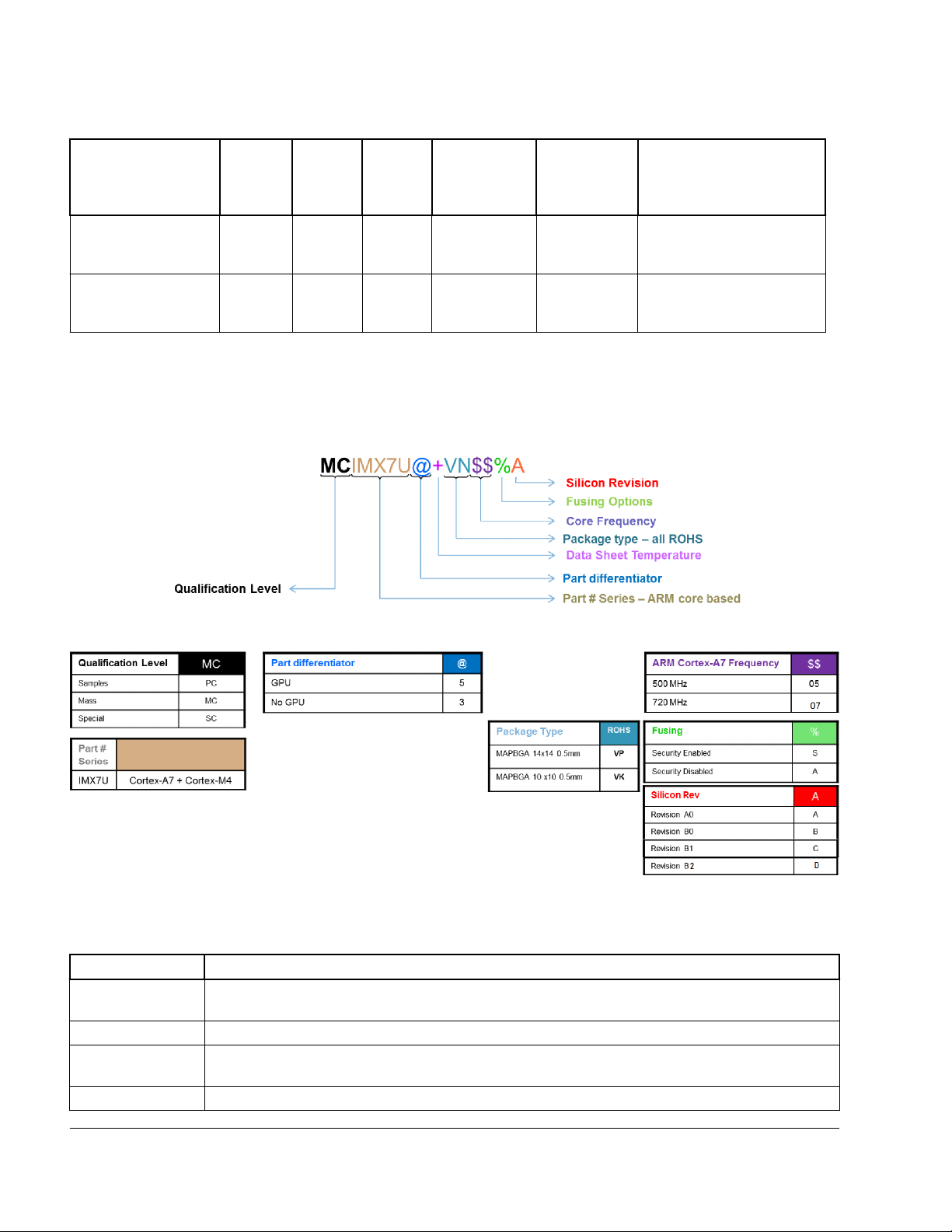

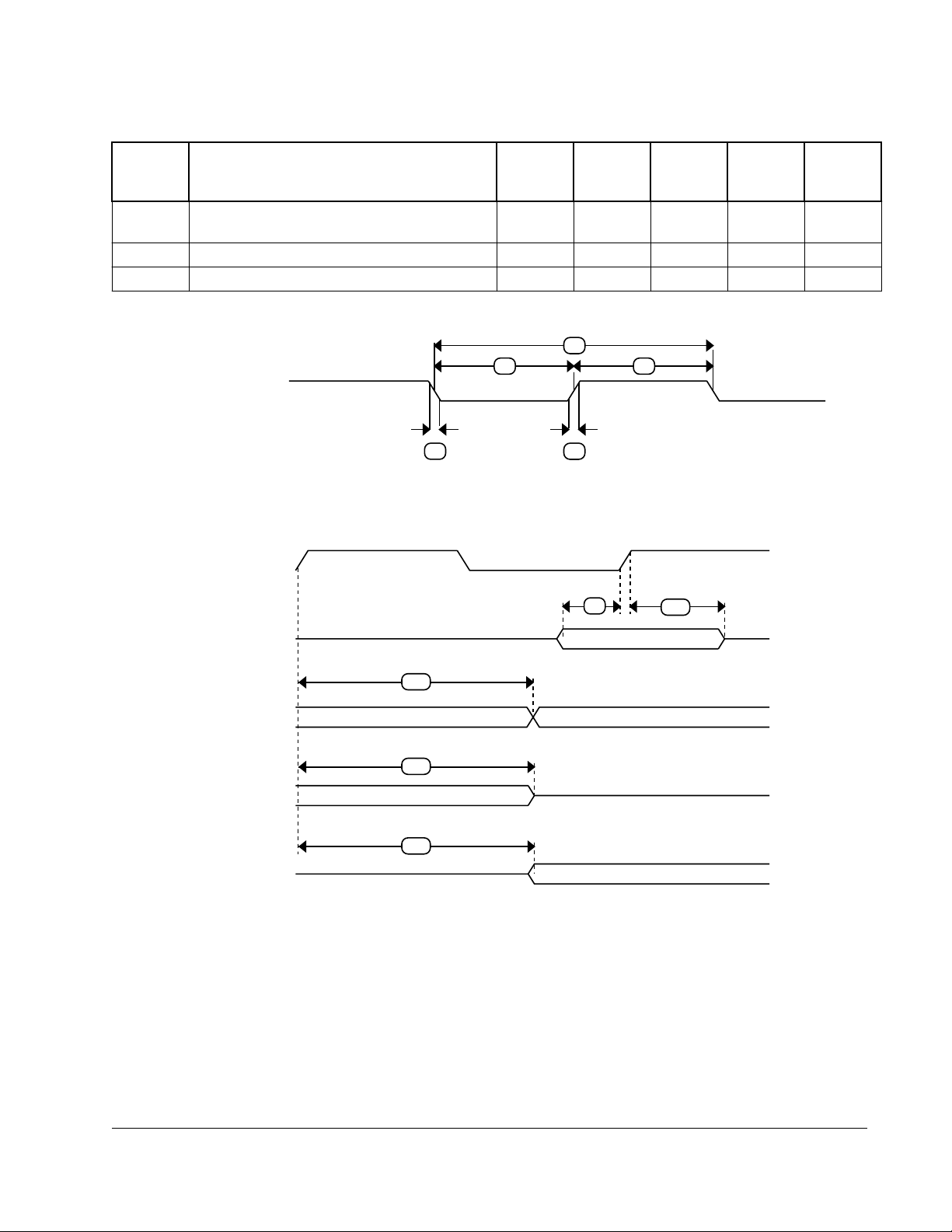

S

NVS

CAAM

Core Processor

HAB

R

O

M

Flash

RAM

Application domain (implementing ARM Cortex-A7)

3.2.2.2 Real-Time Clock (RTC)

The RTC module provides 64-bit monotonic counter with roll-over protection, 32-bit

seconds counter with roll-over protection and 32-bit alarm. This timer module is

extremely low power that allows it to operate on a backup power supply when the

main power supply is cut off. The RTC remains functional in all low power modes

and can generate an interrupt to exit any low power mode.

3.2.2.3 High Assurance Boot (HAB)

The High Assurance Boot (HAB) component of the ROM protects against the

potential threat of attackers modifying areas of code or data in programmable memory

to make it behave in an incorrect manner. The HAB also prevents attempts to gain

access to features which should not be available.

The integration of the HAB feature with the ROM code ensures that the chip does not

enter an operational state if the existing hardware security blocks have detected a

condition that may be a security threat or areas of memory deemed to be important

have been modified. The HAB uses RSA digital signatures to enforce these policies.

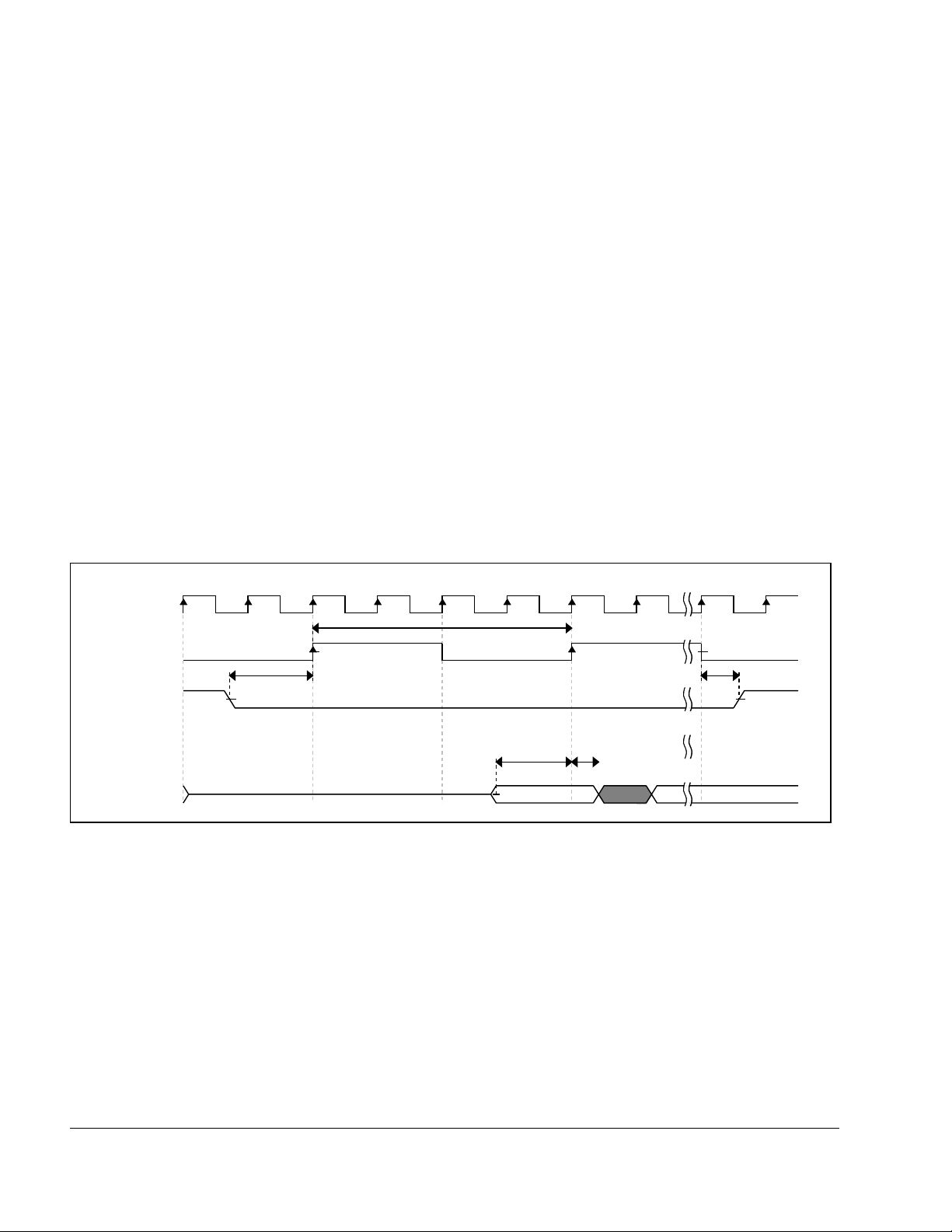

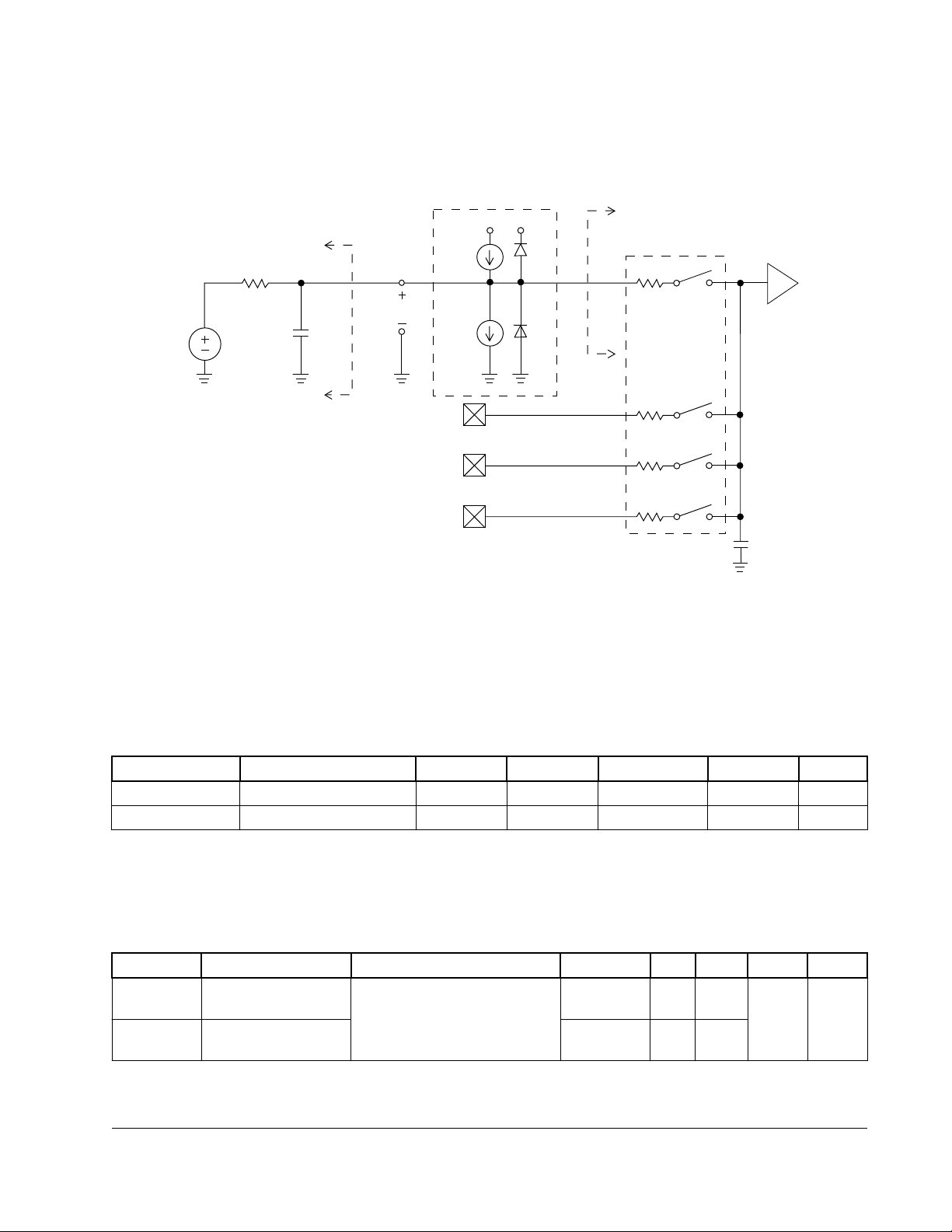

Figure 3. Secure Boot Components

NXP provides a reference Code Signing Tool (CST) for key

generation, certificate generation and code signing for use

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

with the HAB library. The CST can be found by searching

for "IMX_CST_TOOL" at http://www.nxp.com.

NOTE

27

NXP Semiconductors

Page 28

Real-time domain (implementing ARM Cortex-M4)

NOTE

For further details on making use of the secure boot feature

using HAB, contact your local NXP representative.

3.2.3 Timers—application domain

The i.MX 7ULP Application Domain implements the following timers:

• Low Power Periodic Interrupt Timer (LPIT)

• Timer/PWM Module (LPTPM)

• Low Power Timer (LPTMR)

• External Watchdog Monitor (EWM)

• Time stamp timer module (TSTMR)

• WDOG (Watchdog Timer)

See i.MX 7ULP modules list for more details.

3.2.4 Connectivity and communications—applications domain

The i.MX 7ULP Application Domain implements the following connectivity and

communications peripherals:

• Secure Digital (SD) Interface via the uSDHC

• Low Power Universal Asynchronous Receiver/Transmitter (LPUART)

• Low Power Inter-Integrated Circuit (LPI2C)

• Low Power Serial Peripheral Interface (LPSPI)

• Universal System Bus On-The-Go (USB-OTG)

• USB High-Speed Inter-Chip Physical Layer (HSIC-PHY)

See i.MX 7ULP modules list for more details.

4

Real-time domain (implementing ARM Cortex-M4)

The real-time domain is built around an ARM Cortex-M4 processor that contains a

floating-point unit and is optimized for lowest possible leakage.

4.1

28

NXP Semiconductors

Memory system—real-time domain

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 29

System control modules

4.1.1 Internal memory—real-time domain

The real-time domain contains 256 kB of SRAM organized in sub-blocks of 32 kB

each. Each sub-block can be power-gated under software control to optimize power

consumption.

4.1.2 QuadSPI flash

The Quad Serial Peripheral Interface (QSPI) module provides an interface to various

types of serial flash memory. It allows one serial flash connection and supports 1-bit,

4-bit and 8-bit SPI bus width.

4.2

Peripherals—real-time domain

4.2.1 Analog—real-time domain

The i.MX 7ULP Real-Time Domain implements the following analog peripherals:

• 12-bit Analog to Digital Converter

• 12-bit Digital to Analog Converter

• Comparators

See i.MX 7ULP modules list for more details.

4.2.2

The i.MX 7ULP Real-Time Domain implements the following connectivity and

communications peripherals:

• Low Power Universal Asynchronous Receiver/Transmitter (LPUART)

• Low Power Inter-Integrated Circuit (LPI2C)

• Low Power Serial Peripheral Interface (LPSPI)

• Rapid General-Purpose Input and Output with 2 Ports (RGPIO2P)

• Flexible Input/Output (FlexIO)

Connectivity and communications—real-time domain

See the i.MX 7ULP modules list for more details.

System control modules

5

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

29

NXP Semiconductors

Page 30

System control modules

5.1 JTAG—system control

Joint Test Action Group Controller (JTAGC) provides the means to test chip

functionality and connectivity while remaining transparent to system logic when not in

test mode. Testing is performed via a boundary scan technique, as defined in the IEEE

1149.1-2001 standard.

5.2 JTAG device identification register

The device identification register (JTAG ID) allows the revision number and part

number to be read through the TAP. See the device identification register section of the

i.MX 7ULP Applications Processor Reference Manual for details. This table shows the

Part Identification Number (PIN) and the Part Revision Number (PRN) for each i.MX

7ULP silicon revision.

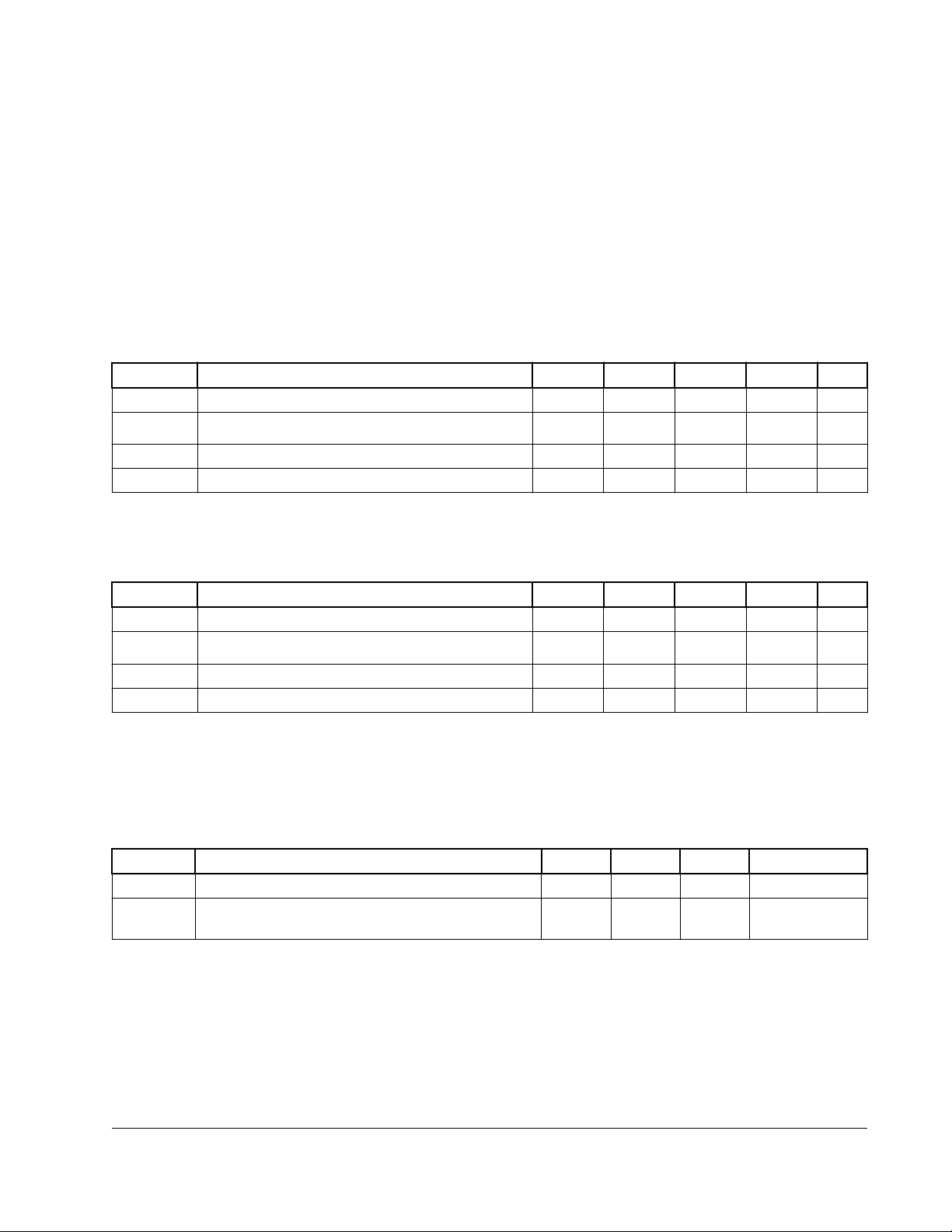

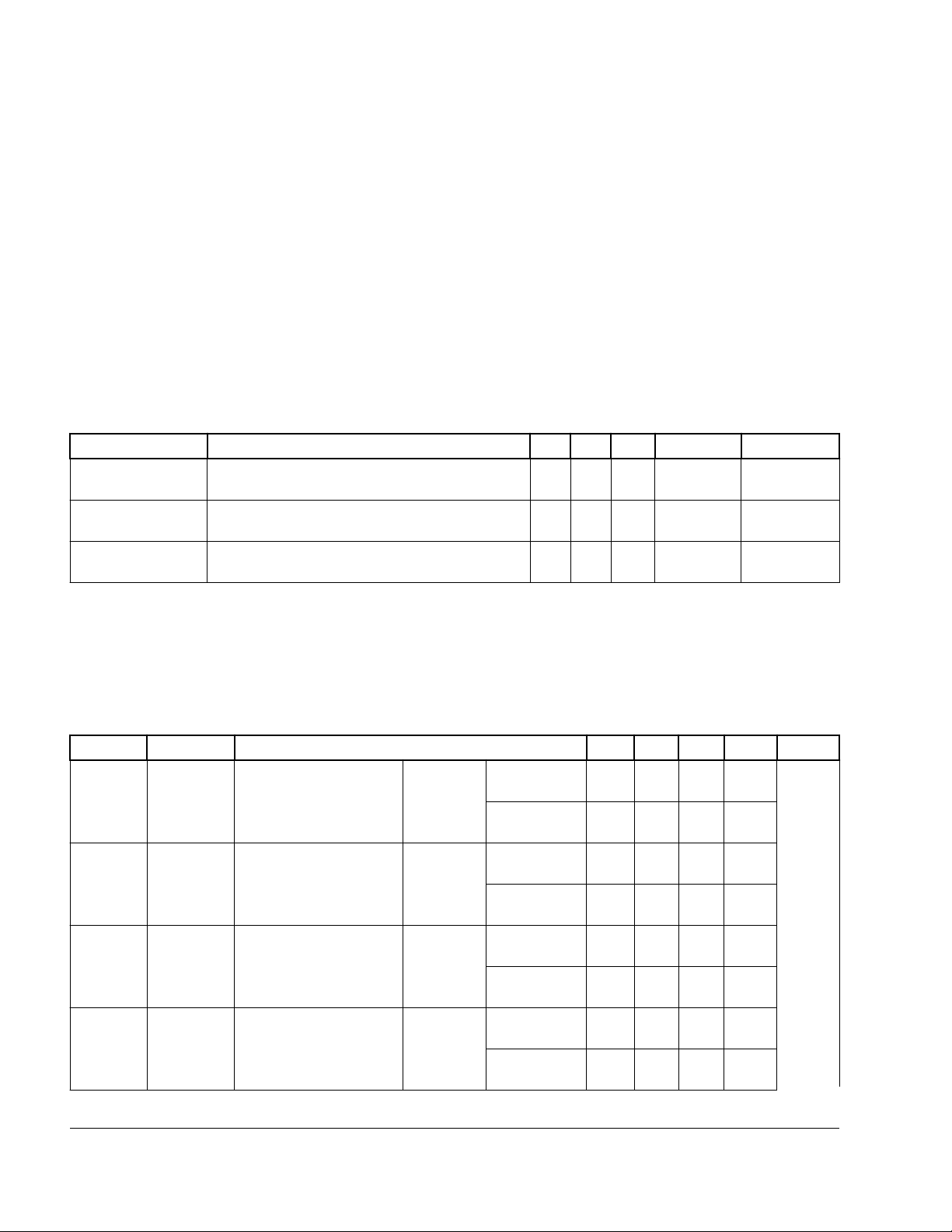

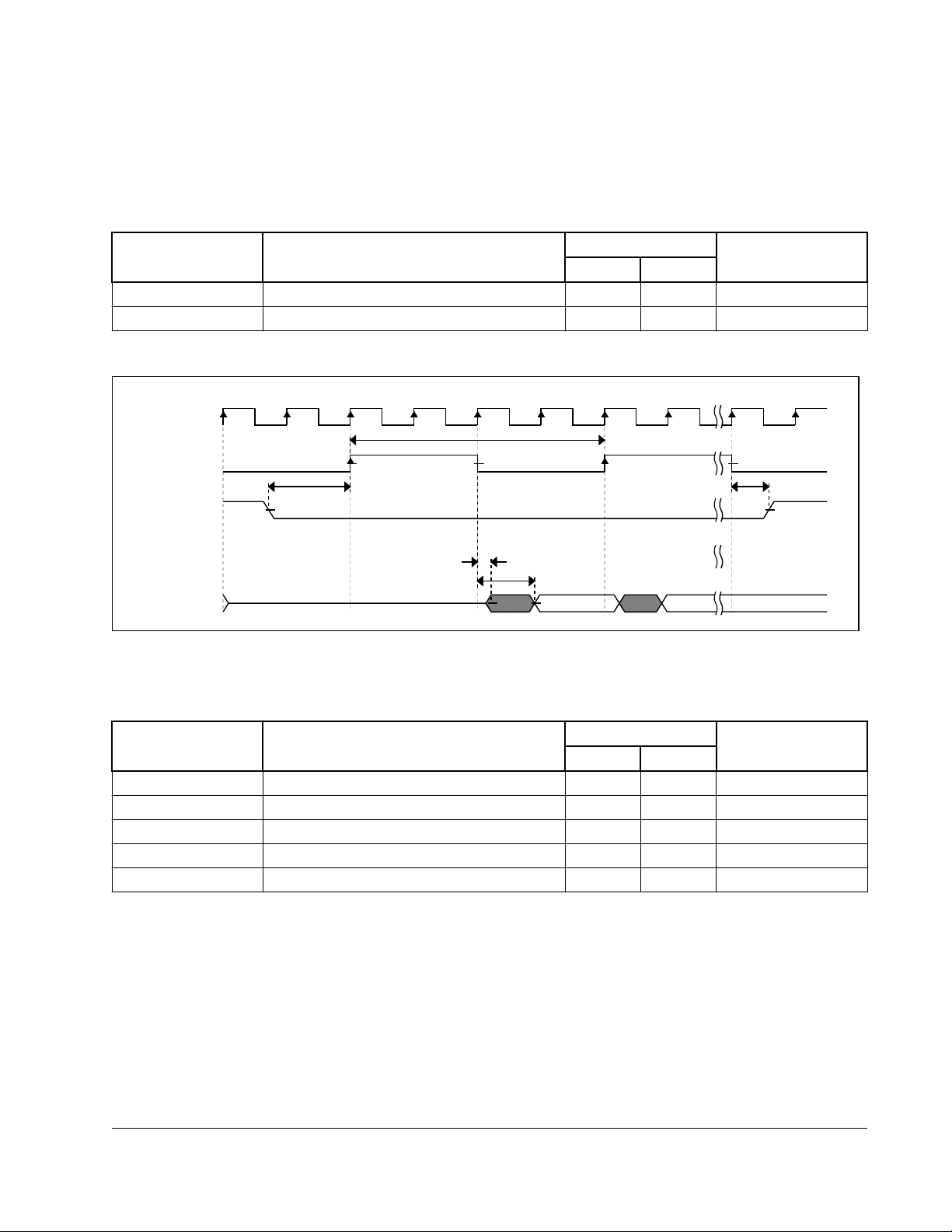

Table 3. JTAG device identification register information

Silicon Revision Part Identification Number (PIN) Part Revision Number (PRN)

A0 10'b0011100001 4’b0000

B0 10'b0011100001 4’b0001

B1 10'b0011100001 4’b0010

B2 10'b0011100001 4’b0011

The contents of the JTAD ID register are also mirrored in a SIM register called

JTAG_ID_REG (address 0x410A_308C).

5.3

Oscillators and PLLs

5.3.1 System oscillator (SYS OSC)

The system oscillator (SYS OSC) is a crystal oscillator. The SYS OSC, in conjunction

with an external crystal or resonator, generates a reference clock for this chip. It also

provides the option for an external input clock to EXTAL signal directly.

30

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 31

System control modules

5.3.2 Real-Time Clock Oscillator (RTC OSC)

The RTC OSC module provides the clock source for the Real-Time Clock module.

The RTC OSC module, in conjunction with an external crystal, generates a 32.678

kHz reference clock for the RTC.

5.3.3 USB PLL

The USB PLL is embedded in the USB transceiver block. This PLL allows an exact

480 MHz to be generated from a supported reference clock of 24 MHz. The output of

this PLL is primarily used for USB operations. The USB PLL clock is also made

available as a clock source for other peripherals in the SoC.

5.3.4 Fixed Frequency PLL (Fixed-freq PLL)

In addition to the main clock output, this PLL also includes 4 Phase Fractional

Dividers (PFDs) that can generate other clock frequencies. There is one instance of the

Fixed-freq PLL (PLL0), which provides clocks for the M4 core, buses, and

peripherals in the real-time domain.

5.3.5

Fractional-N PLL (FracN PLL)

The Fractional-N (Frac-N) PLL can generate an output clock 528 MHz from a

supported reference clock. In addition to the main clock output, this PLL also includes

up to four Phase Fractional Dividers (PFDs) that can generate other clock frequencies.

This PLL also supports a tunable clock for audio applications.

5.4

Power Management

The i.MX 7ULP implements multiple options minimizing application power

consumption:

• On-chip power management including regulators, drivers and switches for

flexible power supplies, efficient power consumption and short wake up time

• Multiple power domains and ultra-low power modes allow flexible power saving

• Voltage and frequency scaling in dynamic operating modes

• Software-controlled clock gating for cores and peripherals

• Dynamic Process Monitor (DPM)

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

31

NXP Semiconductors

Page 32

i.MX 7ULP LDO Bypass versus LDO-enabled modes

5.4.1 Digital PMC

The digital PMC module allows user software to control power modes and of the chip

and to optimize power consumption for the level of functionality needed. There are two

instances of digital PMC on this chip, one for each main power domain.

5.4.2 Analog power management controller (Analog PMC)

The Analog PMC consists of voltage/current references, core logic supply regulators,

memory supply regulators, back and forward biasing regulators, monitors and power

switches, etc. There are two Analog PMC subsystems, one associated with the M4

power domain and the other with the A7 power domain.

6

i.MX 7ULP LDO Bypass versus LDO-enabled modes

i.MX 7ULP has internal low-dropout (LDO) regulators to power certain sections of the

core logic. In LDO Enabled mode, the internal LDO is used to regulate the core logic

voltage under software control. In LDO Bypass mode, the internal LDO is disabled and

the core logic supply voltage is provided externally.

The Real-time domain only supports LDO Enabled mode. The Application Domain

supports either mode. The LDO modes require specific board-level connections. LDO

Bypass vs. Enabled mode must be chosen prior to board design because the physical

connection is different.

6.1

Real-time domain LDO Enabled mode

A 1.8 V nominal voltage supply is provided externally to the VDD_PMC18_DIG0

supply. The internal LDO output is routed to VDD_PMC11_DIG0_CAP.

VDD_PMC11_DIG0_CAP must be routed back to VDD_DIG0 at the board-level with

appropriate bypass capacitors to VSS. This connection has a maximum board routing

impedance requirement. See parameter RDIG0 in Table 5.

See the i.MX 7ULP Hardware Development Guide (IMX7ULPHDG) for details on the

required bypass capacitors.

32

NXP Semiconductors

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 33

System specifications

6.2 Application domain LDO Enabled mode

A 1.2 V nominal voltage supply is provided externally to the VDD_PMC12_DIG1

supply. The internal LDO output is routed to VDD_PMC11_DIG1_CAP.

VDD_PMC11_DIG1_CAP must be routed back to VDD_DIG1 at the board-level

with appropriate bypass capacitors to VSS. This connection has a maximum board

routing impedance requirement. See parameter RDIG1 in Table 5.

See the i.MX 7ULP Hardware Development Guide (IMX7ULPHDG) for details on

the required bypass capacitors.

6.3

Application domain LDO BYPASS mode

The desired core logic supply voltage is provided externally to the

VDD_PMC12_DIG1, VDD_PMC11_DIG1_CAPand VDD_DIG1 which are all tied

together.

See the i.MX 7ULP Hardware Development Guide (IMX7ULPHDG) for details on

the required bypass capacitors.

7

System specifications

7.1 Ratings

7.1.1 Thermal handling ratings

Symbol Description Min. Max. Unit Notes

T

STG

T

SDR

1. Determined according to JEDEC Standard JESD22-A103, High Temperature Storage Life.

2. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Storage temperature -55 150 °C 1

Solder temperature, lead-free — 260 °C 2

NXP Semiconductors

33

Page 34

System specifications

7.1.2 Moisture handling ratings

Symbol Description Min. Max. Unit Notes

MSL Moisture sensitivity level — 3 — 1

1. Determined according to IPC/JEDEC Standard J-STD-020, Moisture/Reflow Sensitivity Classification for Nonhermetic

Solid State Surface Mount Devices.

7.1.3 ESD handling ratings

Symbol Description Min. Max. Unit Notes

V

V

HBM

CDM

Electrostatic discharge voltage, human body model -1000 +1000 V 1

Electrostatic discharge voltage, charged-device

model

-250 +250 V 2

1. Determined according to JEDEC Standard JESD22-A114, Electrostatic Discharge (ESD) Sensitivity Testing Human

Body Model (HBM).

2. Determined according to JEDEC Standard JESD22-C101, Field-Induced Charged-Device Model Test Method for

Electrostatic-Discharge-Withstand Thresholds of Microelectronic Components.

7.1.4 Absolute maximum ratings

CAUTION

Stresses beyond those listed under this table may cause

permanent damage to the device. These are stress ratings only.

Functional operation of the device at these or any other

conditions beyond those indicated under “recommended

operating conditions” is not implied. Exposure to absolutemaximum-rated conditions for extended periods may affect

device reliability.

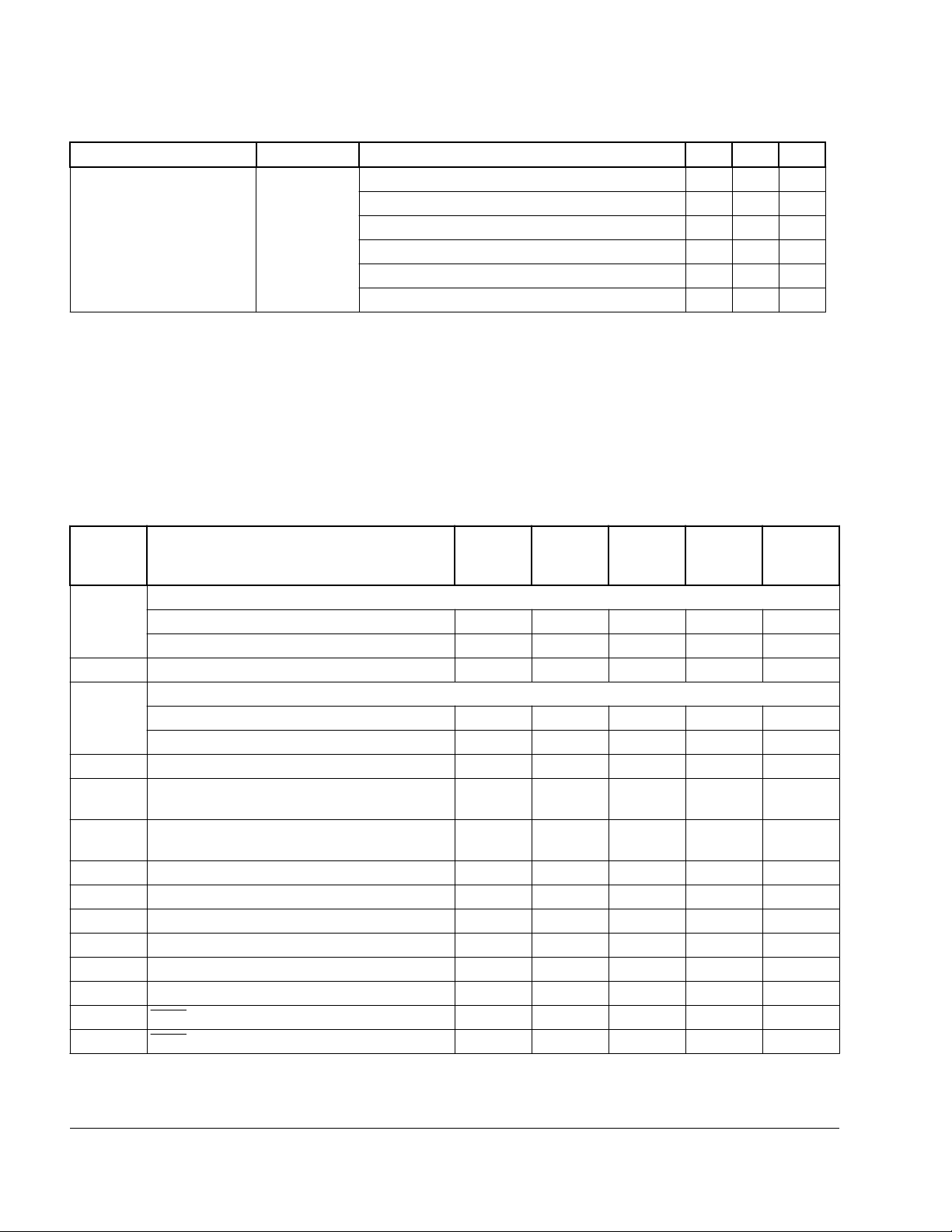

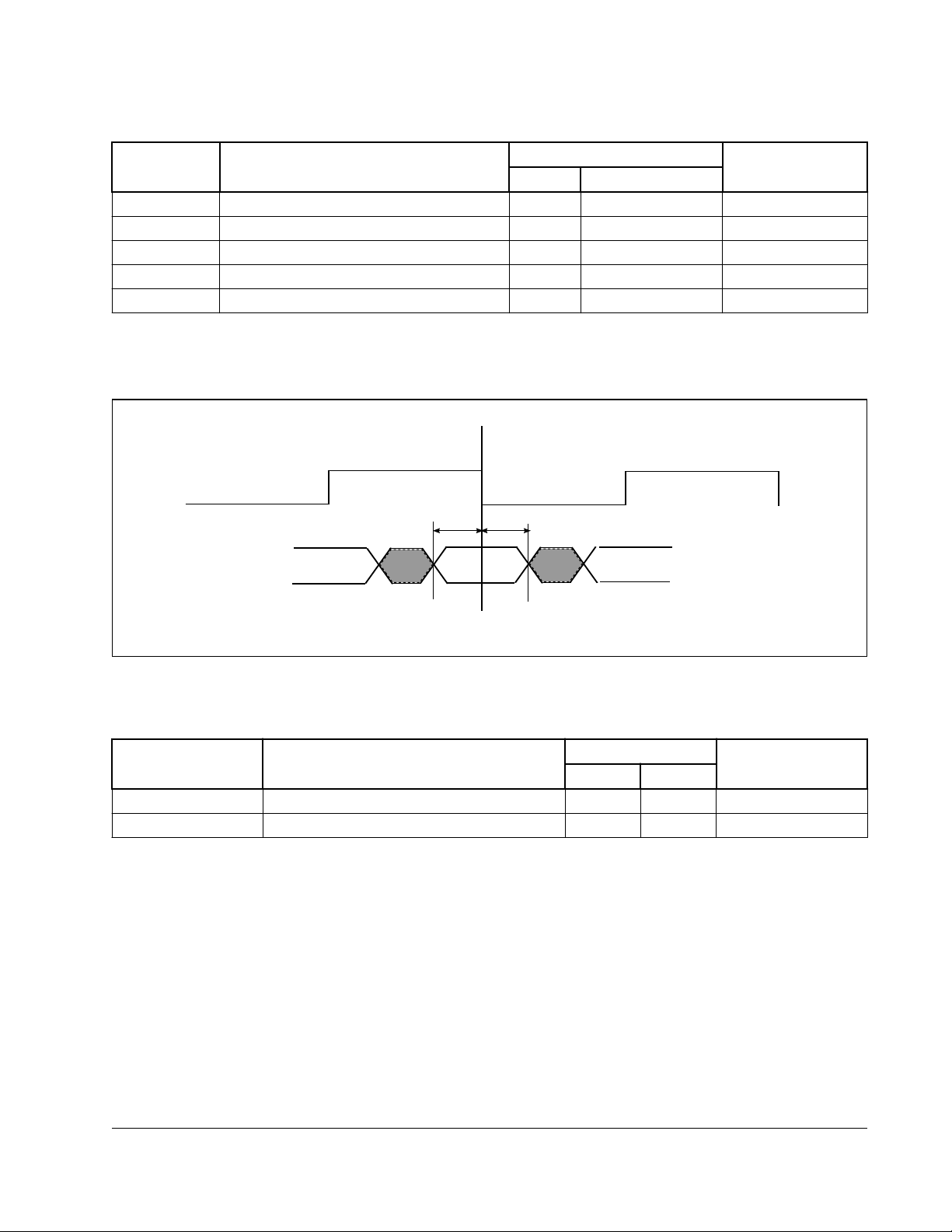

Table 4. Absolute maximum ratings

Parameter Description Symbol Min Max Unit

SNVS domain LDO supply input VDD_VBAT42 -0.3 4.25 V

M4/A7 PMC and PMC IO supply input VDD_PMC18 -0.3 1.98 V

1.8V IO supply reference and A7 supply reference input VDD18_IOREF -0.3 1.98 V

M4 domain LDO and internal memory LDO supply input VDD_PMC18_DIG0 -0.3 1.98 V

M4 domain core and logic supply input VDD_DIG0 -0.3 1.155 V

34

NXP Semiconductors

Table continues on the next page...

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

Page 35

System specifications

Table 4. Absolute maximum ratings (continued)

Parameter Description Symbol Min Max Unit

A7 domain core and logic supply inputs VDD_PMC12_DIG1 -0.3 1.65 V

VDD_PMC11_DIG1_CAP

VDD_DIG1 -0.3 1.155 V

GPIO Port A supply input VDD_PTA -0.3 3.96 V

GPIO Port B supply input VDD_PTB -0.3 1.98 V

GPIO Port C supply input VDD_PTC -0.3 3.96 V

GPIO Port D supply input VDD_PTD -0.3 3.96 V

GPIO Port E supply input VDD_PTE -0.3 3.96 V

GPIO Port F supply input VDD_PTF -0.3 3.96 V

HSIC supply input VDD_HSIC -0.3 1.98 V

HSIC 1.8V pre-driver supply input VDD18_HSIC -0.3 1.98 V

DDR I/O supply input VDD_DDR -0.3 1.98 V

DDR 1.8V pre-driver supply input VDD18_DDR -0.3 1.98 V

MIPI DSI 1.1V supply input VDD_DSI11 -0.3 1.155 V

MIPI DSI 1.8V supply input VDD_DSI18 -0.3 1.98 V

USB PHY 3.3V supply input VDD_USB33 -0.3 3.6 V

USB PHY 1.8V supply input VDD_USB18 -0.3 1.98 V

USB0 VBUS detection USB0_VBUS -0.3 5.6 V

PLL analog supply input VDD_PLL18 -0.3 1.98 V

ADC high reference supply input VREFH_ANA18 -0.3 1.98 V

ADC analog and IO 1.8V supply input VDD_ANA18 -0.3 1.98 V

ADC analog and IO 3.3V supply input VDD_ANA33 -0.3 3.96 V

1

-0.3 1.155 V

1. When used as an input in LDO Bypass Mode

7.1.5 Recommended operating conditions—system

NOTE

All supply inputs shown represent the voltage at the package

ball.

Table 5. Recommended operating conditions

Symbol Description Conditions Min Typ Max Units

SNVS (Always On) Domain Supply Voltage Requirements

VDD_VBAT42 SNVS domain LDO supply

input

VDD_VBAT18_CAP SNVS domain LDO output — — 1.8 — V

Table continues on the next page...

i.MX 7ULP Applications Processor—Consumer, Rev. 0, 09/2020

— 2.4 3.0 4.2 V

NXP Semiconductors

35

Page 36

System specifications

Table 5. Recommended operating conditions (continued)

Symbol Description Conditions Min Typ Max Units

Real Time Domain (M4 domain) Supply Voltage Requirements (LDO-Enabled Mode only supported)

VDD_PMC18

VDD18_IOREF