Page 1

AN10609_3

PN532 C106 application note

Rev. 1.2 — January 5, 2010 Application note

Document information

Info Content

Keywords PN532C106, PN532 v1.6, Low Battery mode

Abstract This document described

- functionalities of PN532

- changes between PN532C104 and PN532C106

Page 2

NXP Semiconductors

PN532 C106 application note

Revision history

Rev Date Description

1.0 March 10, 2008 First draft of AN10609_2, PN532 application note, C106 appendix.

It is based on AN10609_1 rev 1.1

1.1 September 7, 2009 update on application diagrams: RX path

1.2 January 5, 2010 Merge PN532 C104 and PN532 C106 application note

Add PN532 C106 SPI workaround, add SPI waveforms

Add how to use PN532 to read new Mifare cards.

AN10609_3

Contact information

For additional information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 2 of 75

Page 3

NXP Semiconductors

1. Introduction

The PN532 is a highly integrated transmission module for contactless communication at

13.56 MHz including microcontroller functionality based on a 80C51 core with 40 Kbytes

of ROM and 1 Kbyte of RAM.

The PN532 combines a modulation and demodulation concept completely integrated for

different kinds of contactless communication methods and protocols at 13.56 MHz

(particularly Near Field Communication NFC), with an easy-to-use firmware for the

different supported modes and the required host interfaces.

The PN532 includes a switch to power an external SAM connected to S2C interface. It is

controlled by the embedded firmware.

AN10609_3

PN532 C106 application note

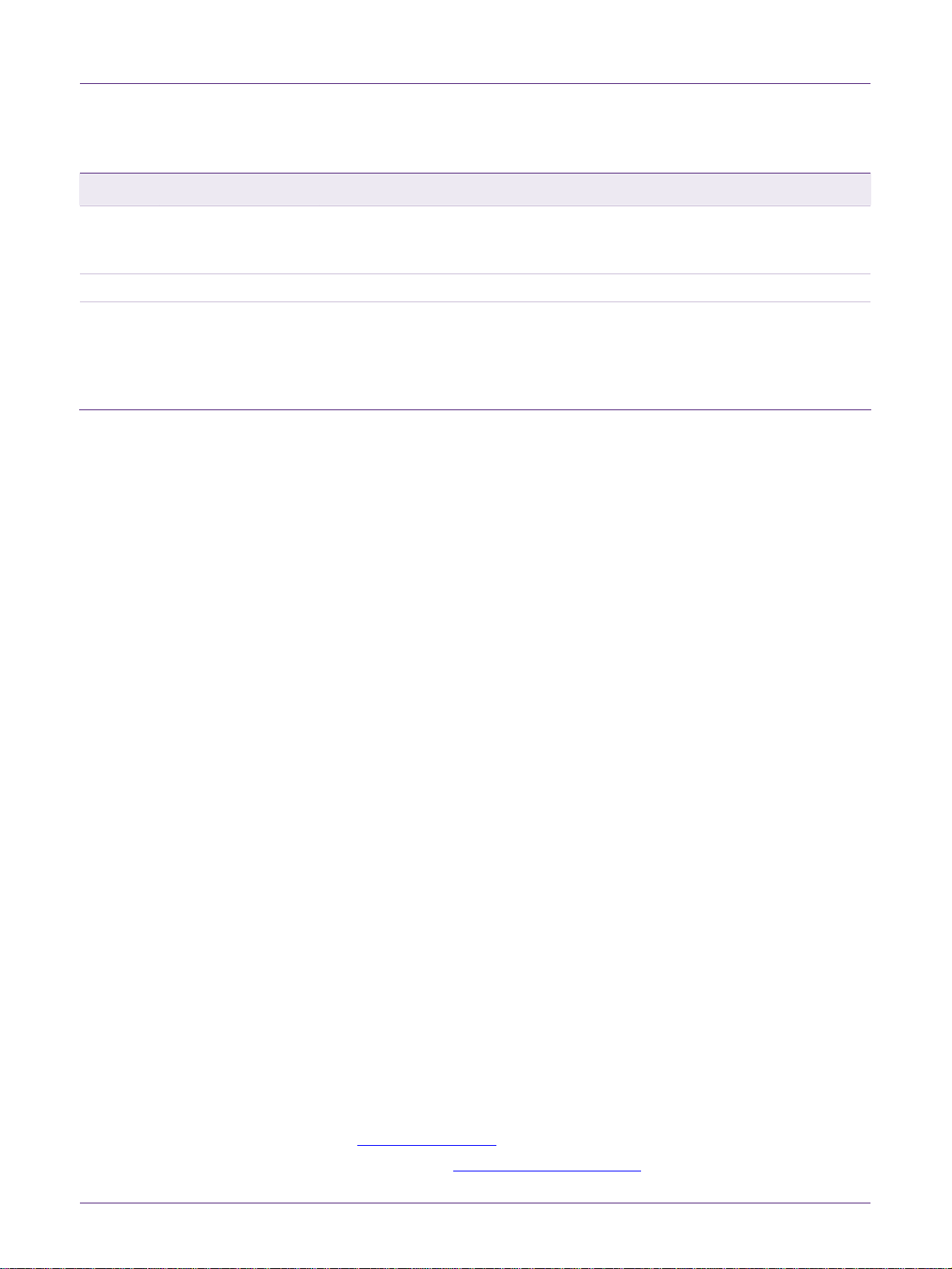

HOST

CONTROLLER

Interface with host controller : SPI or I2C or HSU.

Possibly one or two additional lines (H_REQ, IRQ).

PN532

antenna

RF communication

Fig 1. Simplified system view

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 3 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 4

NXP Semiconductors

This document intends to allow the customer getting quickly started with the PN532. It

summarizes commands needed to use the PN532 as a reader, as a card, or in a NFC

peer-to-peer communication. It gives an overview on possible interfaces with the host

controller.

Detailed description of the PN532 firmware can be found in the PN532 User manual (cf.

References table below).

Full description of the PN532 IC can be found in the PN532 Datasheet.

This document underlines differences between PN532C104 (p revious version not

produced anymore) and PN532C106.

The PN532C106 main differences compared with PN532C104:

“Low battery” mode is the start up mode of PN532C106. It is described page 21.

AN10609_3

PN532 C106 application note

- Possible host interface: HSU, I2C or SPI mode 0 (no more SPI mode 1, 2, 3)

- “Low battery” mode

References

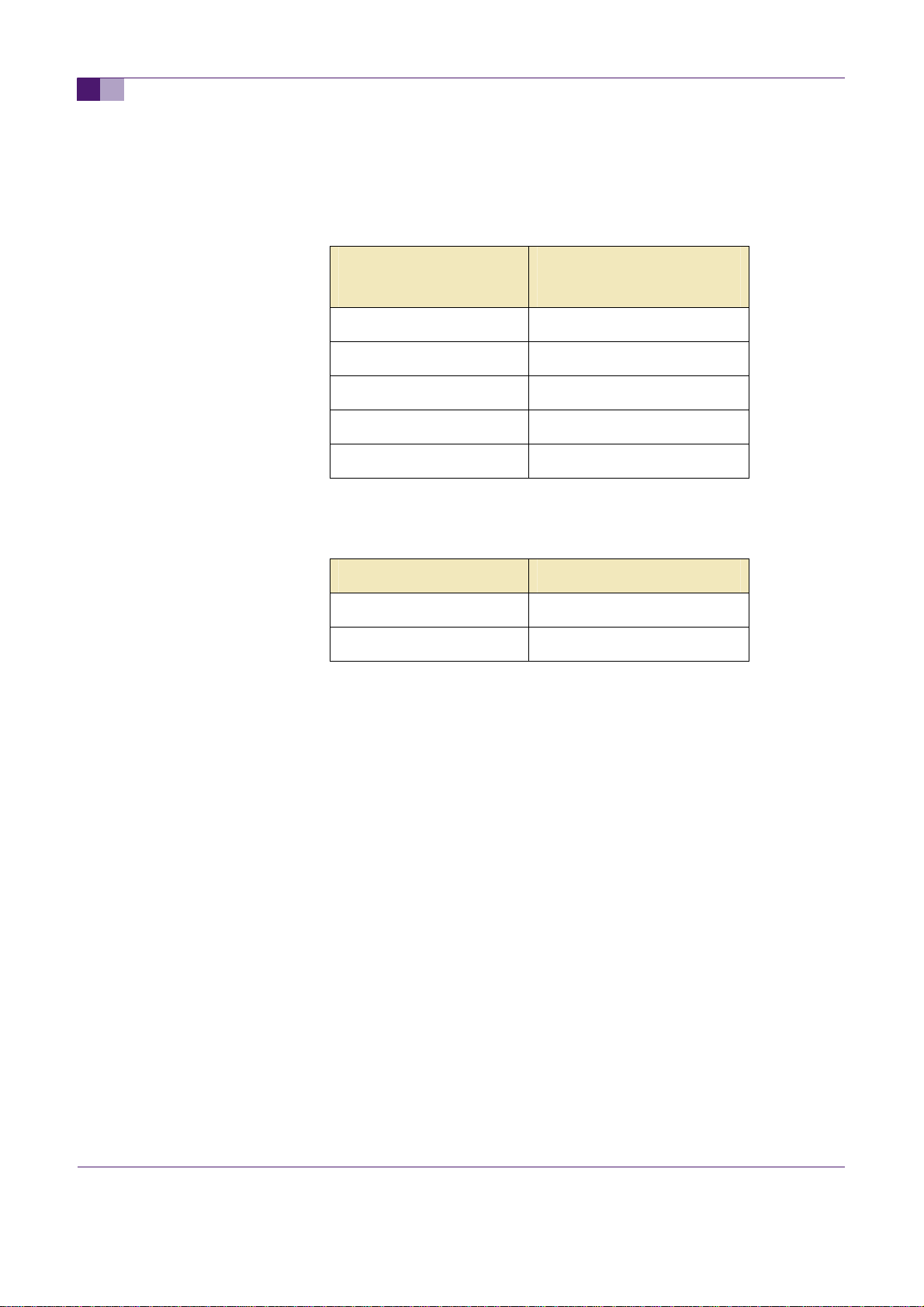

Ref.number Document name

1 PN532 C106 user manual UM0701-02

2 PN532 Product Datasheet 115430.pdf

3 NFC Transmission Module Antenna and RF

100720.pdf

Design Guide

4 Desfire cards specification M075031.pdf

5 Mifare cards specification http://www.nxp.com/products/identification/datasheets/

6 ISO/IEC 14443 specification (T=CL) ISO/IEC 14443-3 specification

ISO/IEC 14443-4 specification

7 NFCIP-1 specification ISO/IEC 18092 or ECMA340 specification

Glossary

NFC Near Field Communication

HSU High Speed UART

SMX Philips SmartMX (Memory Extension)

PCR Power, Clock and Reset controller

SAM Secure Access Module

MINT Multiple Interfaces

PMU Power Management Unit

DEP Data Exchange Protocol (see reference 7)

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 4 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 5

NXP Semiconductors

Pin correspondence: In the documents the following correspondence can be used in

the names of the pins:

AN10609_3

PN532 C106 application note

PN532 Datasheet name Application Note name

(C104 or C106) (C104 or C106)

P70_IRQ IRQ

P32_INT0 H_REQ

P50_SCL SCL

HSU_RX T_RX

HSU_TX T_TX

IC correspondence: In the documents the following correspondence can be used in the

names of the IC:

Commercial Name Application Note name

PN5321A3HN/C106 PN532C106

P5CN072 SMX

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 5 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 6

NXP Semiconductors

2. Interfaces with the host controller

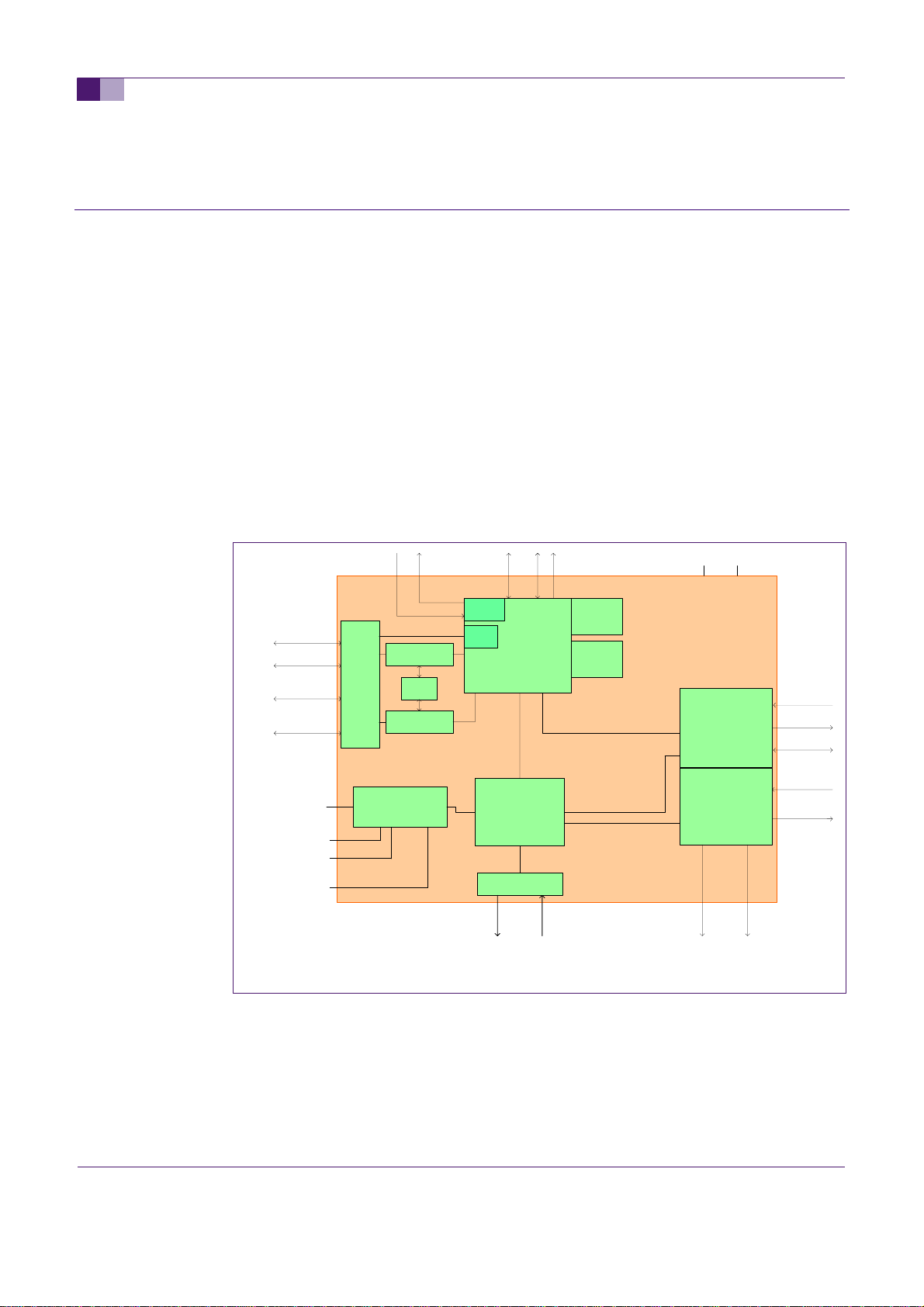

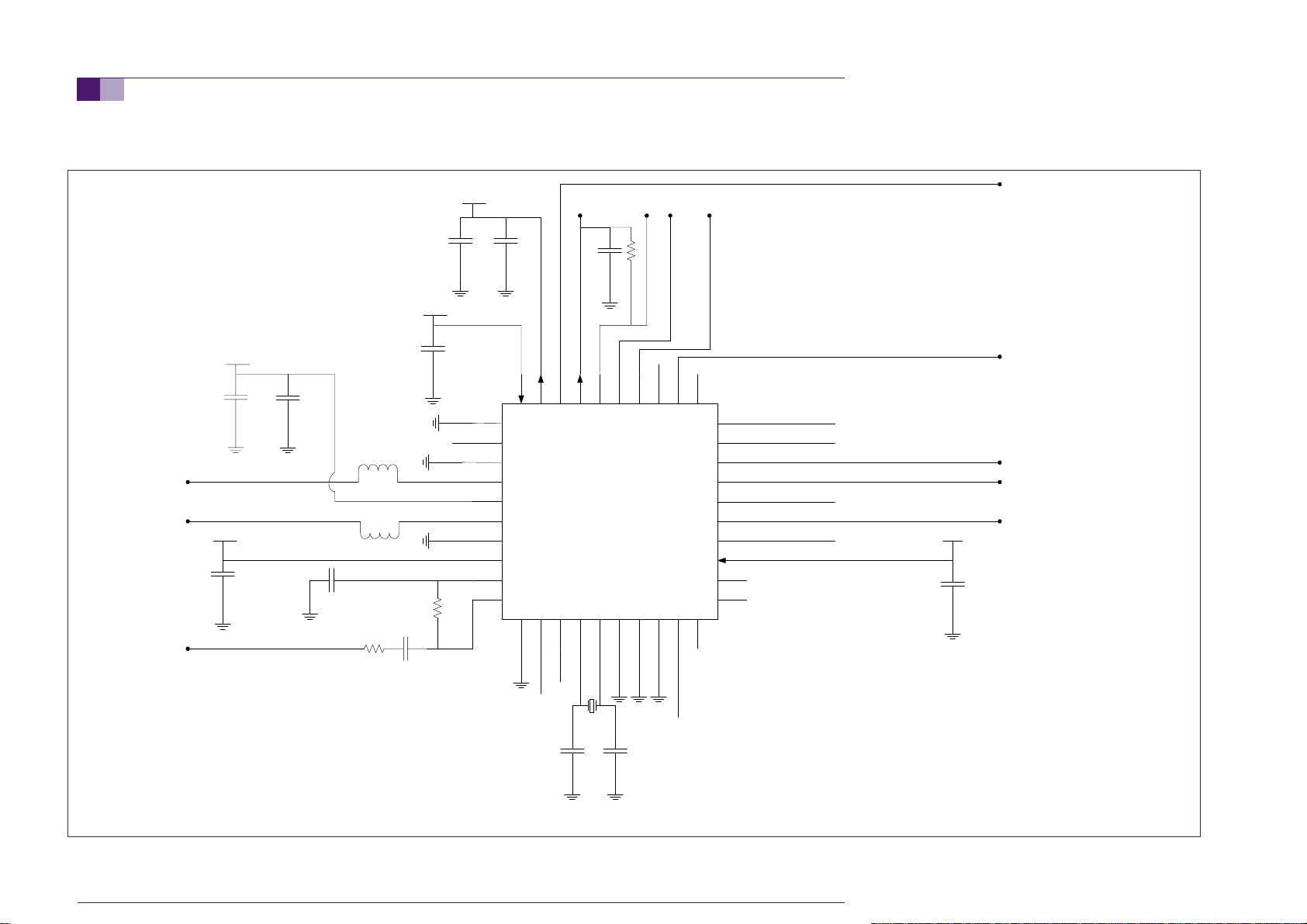

2.1 PN532 block diagram

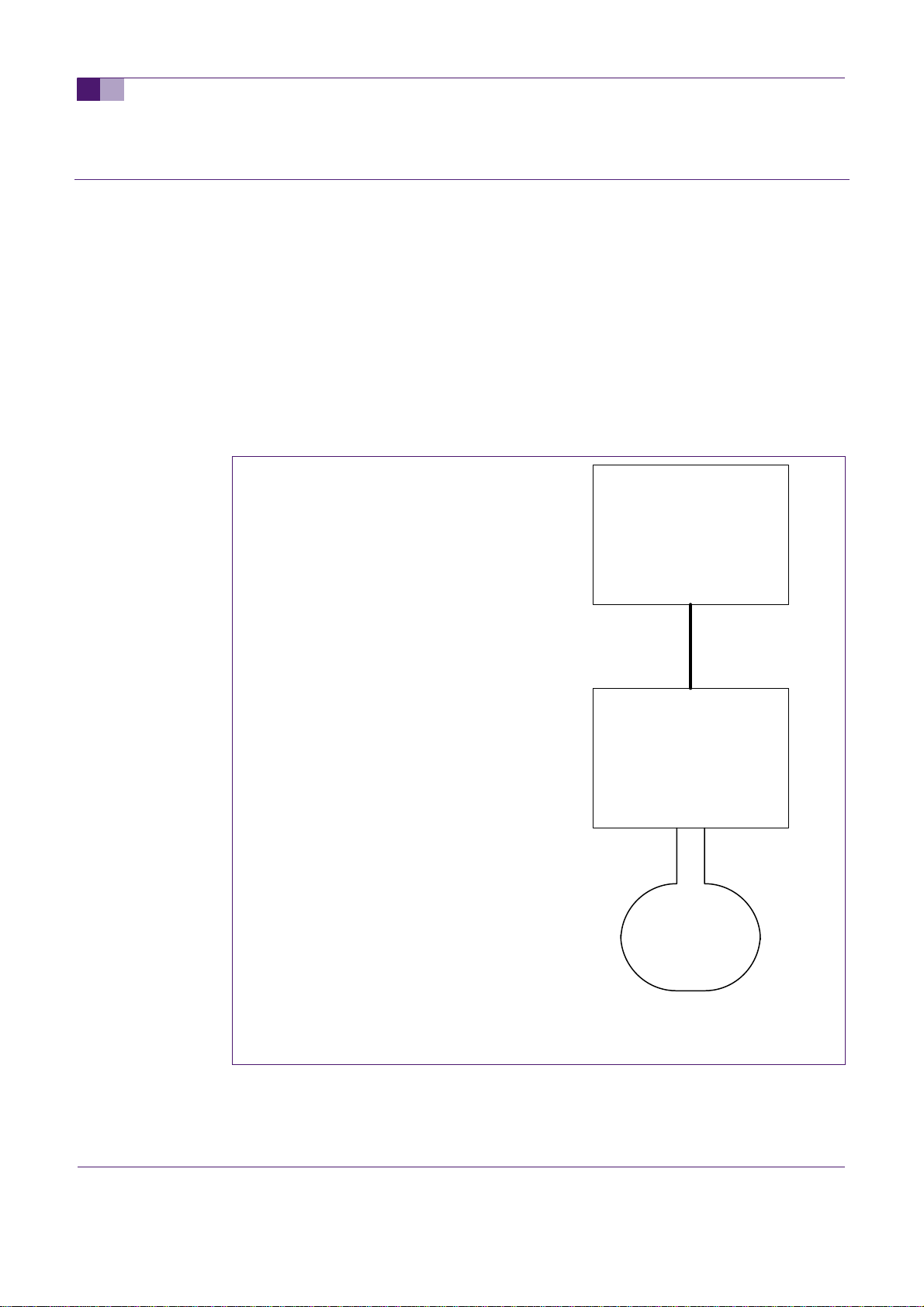

The PN532 is based on an 8051 core, with 40 Kbytes of ROM and 1Kbyte of RAM. The

chip contains a contactless UART, a contactless front end, a “PCR” block that controls

clocks and power.

It can be connected to the host controller in I2C, SPI or HSU (High Speed UART). One or

two more lines (IRQ and H_REQ) can be added. The interface is selectable using I0 and

I1 pins.

A SAM companion chip can be attached using S2C interface.

A part of the IC can be powered directly from a mobile battery (VBAT between 2.7V and

5.4V). The Pad power supply (PVDD) must be between 1.6V and 3.6V.

The SAM power supply SVDD is provided by the PN532.

AN10609_3

PN532 C106 application note

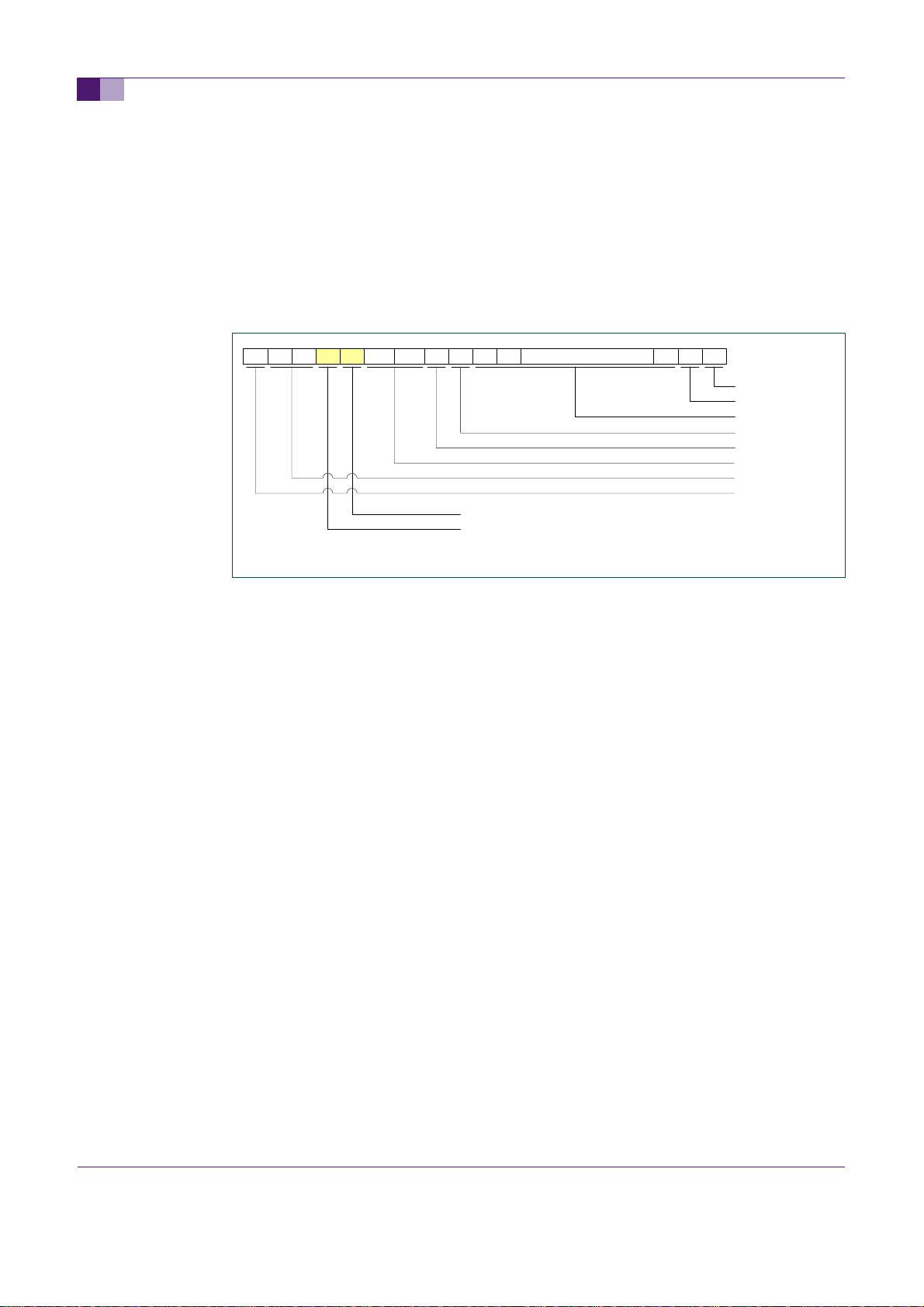

SCK or P72

MISO or P71

MOSI or SDA

or D- or Tx

NSS or SCL

or D+ or Rx

RSTPD

SVDD (output)

power for SAM interface

VDD (1.6 V to 3.6V)

VBAT (2.7 to 5.4V)

P30 P31

HSU

MINT

LDO, power on reset

FIFO

SPI

Power

switch, regulator,

RS232

I2C

8051

PCR

(Power Clock and

Reset controller)

OSC 27.12MHz

Xtal

IRQP32 P33

ROM

40 kbyte

RAM

1 kbyte

I0 I1

ContactLess

UART

FIFO, Mifare

Classic Unit, Frame

generation and

check

ContactLess

Front End

RF Detector,

Demod, Antenna

driver

TX1 TX2

SIGIN

SIGOUT

P34

RX

LOADMOD

Fig 2. PN532 block diagram

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 6 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 7

NXP Semiconductors

2.2 Hardware changes compared to PN532C104

2.2.1 Hardware configuration pins

At start up, the normal mode must be selected by connecting P35 and IRQ as defined

below. The two other modes (RF field on and Emu Joiner) are special modes useful only

for tests purposes.

No external resistors are required on P35 and IRQ pins.

Interface Selection Pin

P35 IRQ

Normal mode 1 1

Normal mode 1 0

EmuJoiner 0 1

RF field On 0 0

(pin #19) (pin #25)

DVDD/VBAT PVDD

DVDD/VBAT GND

GND PVDD

GND GND

AN10609_3

PN532 C106 application note

Three interfaces are available: I2C, SPI and HSU (high speed UART). The interface is

selectable by hardware (pin I0 and I1).

Interface Selection Pin

I0 I1

(pin #16) (pin #17)

HSU 0 0

GND GND

I2C 1 0

DVDD GND

SPI 0 1

GND DVDD

The embedded software manages the communication with the host controller (I2C, SPI,

or HSU interface, protocol on the host link) and the communication on the RF side.

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 7 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 8

NXP Semiconductors

2.2.1.1 Additional lines (IRQ and H_REQ)

P31 is not used to choose between handshake or standard mode: PN532C106

implements only handshake mode, whatever P31 configuration (It can be let not

connected).

2.2.1.2 SPI

Only SPI mode 0 is implemented in PN532C106. Consequently, P30 (pin 24) and P33

(pin 33) states don’t configure anymore the SPI mode. They can be let not connected

To stay in LowVbat mode, NSS must be kept in high state even when PVDD is not

present (NSS low is a wake up condition).

2.3 Host link protocol

No changes compared to PN532C104. Refer to [1] and [8]

The protocol used on host link is fully described in the PN532 User manual (cf.

References table on page 4)

AN10609_3

PN532 C106 application note

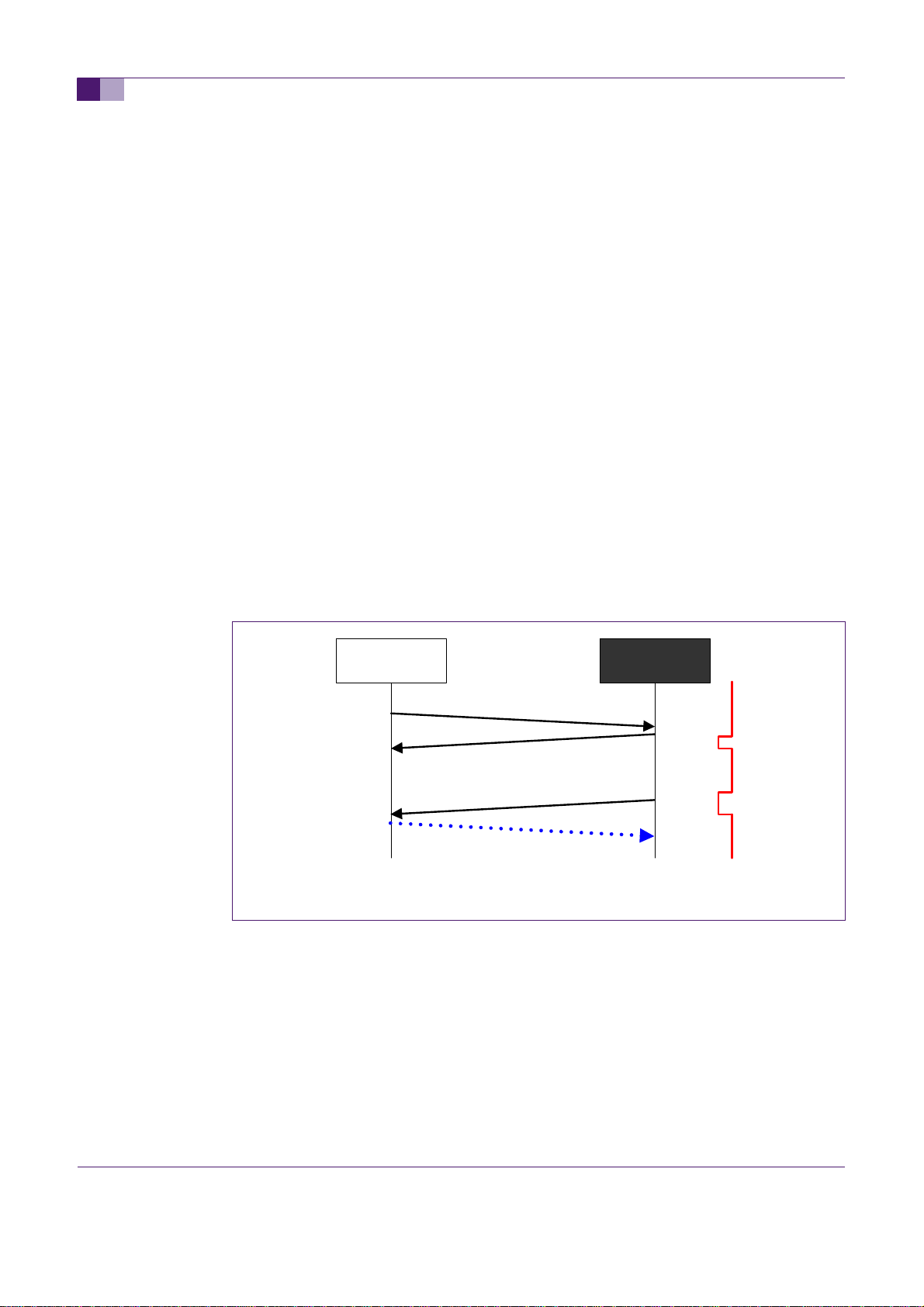

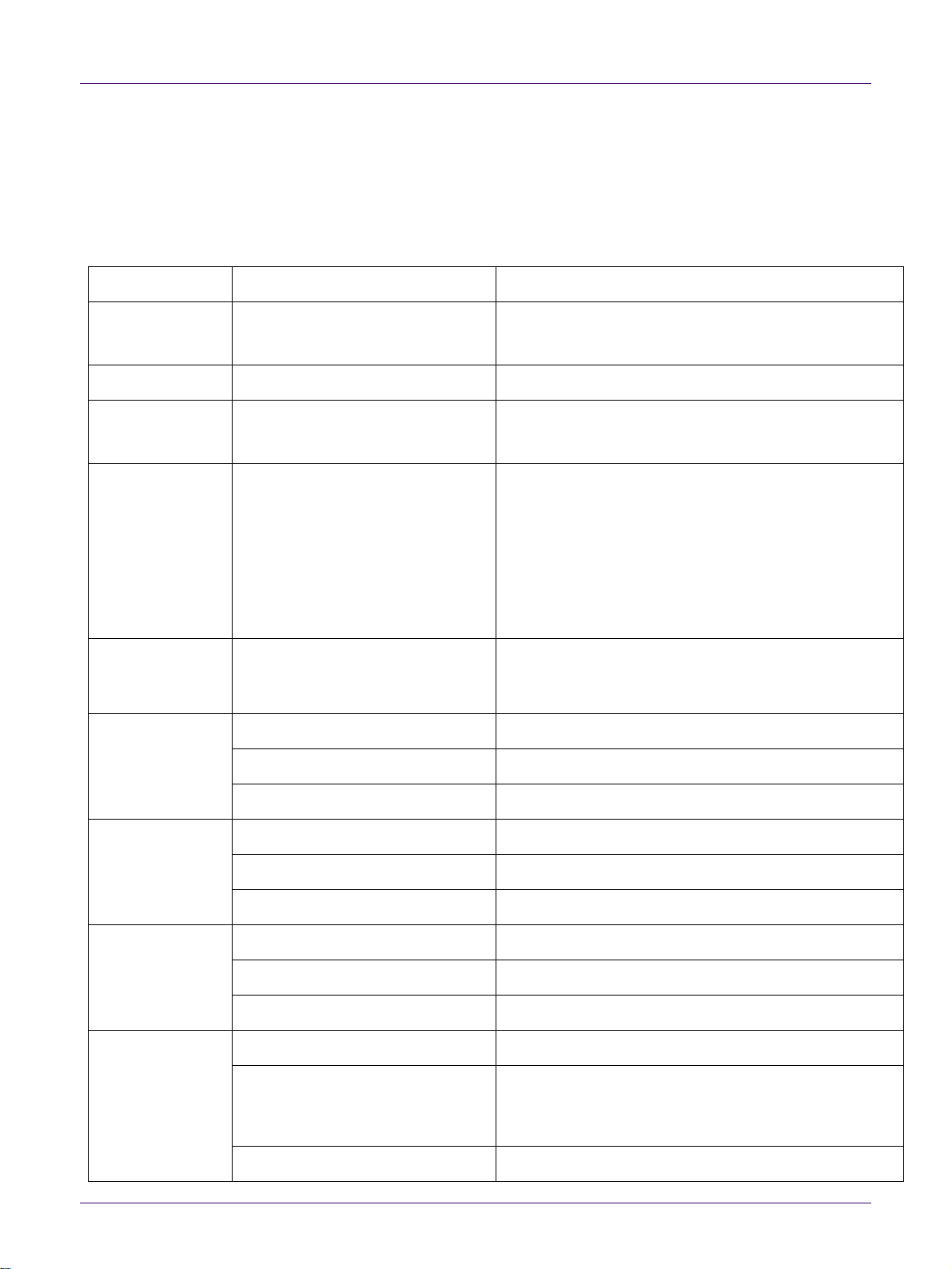

2.3.1 Standard frame

A basic exchange consists in a command frame sent by the host controller to the PN532,

an ACK frame sent by the PN532 as soon as the command is correctly received, and a

response frame, read by the host controller (polling mechanism or use of IRQ).

Fig 3. Normal exchange between host controller and the PN532

I

0 1

R

Q

PN532Controller

C

o

m

m

a

n

d

P

a

c

k

e

t

K

C

A

et

k

c

a

P

e

s

n

o

p

s

e

R

A

C

K

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 8 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 9

NXP Semiconductors

Command and response frame structure is shown in figure 3.

Fig 4. Information frame

¾ PREAMBLE 1 byte

¾ START CODE 2 bytes (00h and FFh)

AN10609_3

PN532 C106 application note

0000 LENFF TFILCS PD0 PD1 ……... DCSPDn 00

Postamble

Packet Data Checksum

Packet Data

Specific PN532 Frame Identifier

Packet Length Checksum

Packet Length

Start of Packet Code

Preamble

¾ LEN 1 byte indicating the number of bytes in the data field

(TFI and PD0 to PDn)

¾ LCS 1 Packet Length Checksum LCS byte that satisfies the relation:

Lower byte of [LEN + LCS] = 00h

¾ TFI 1 byte the PN532 Frame Identifier, the value of this byte depends

on the way of the message

- D4h in case of a frame from the system controller to the the PN532

- D5h in case of a frame from the the PN532 to the system controller

¾ DATA LEN-1 bytes of Packet Data Information

The first byte PD0 is the Command Code

¾ DCS 1 Data Checksum DCS byte that satisfies the relation:

Lower byte of [TFI + PD0 + PD1 + … + PDn + DCS] = 00h

¾ POSTAMBLE 1 byte

ACK frame is described in figure 4.

0000 FF

FF00 00

Postamble

ACK Packet Code

Start of Packet Code

Preamble

Fig 5. ACK frame

List of available commands (PD0 byte) is provided in paragraph

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 9 of 75

3.2 on page 26.

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 10

NXP Semiconductors

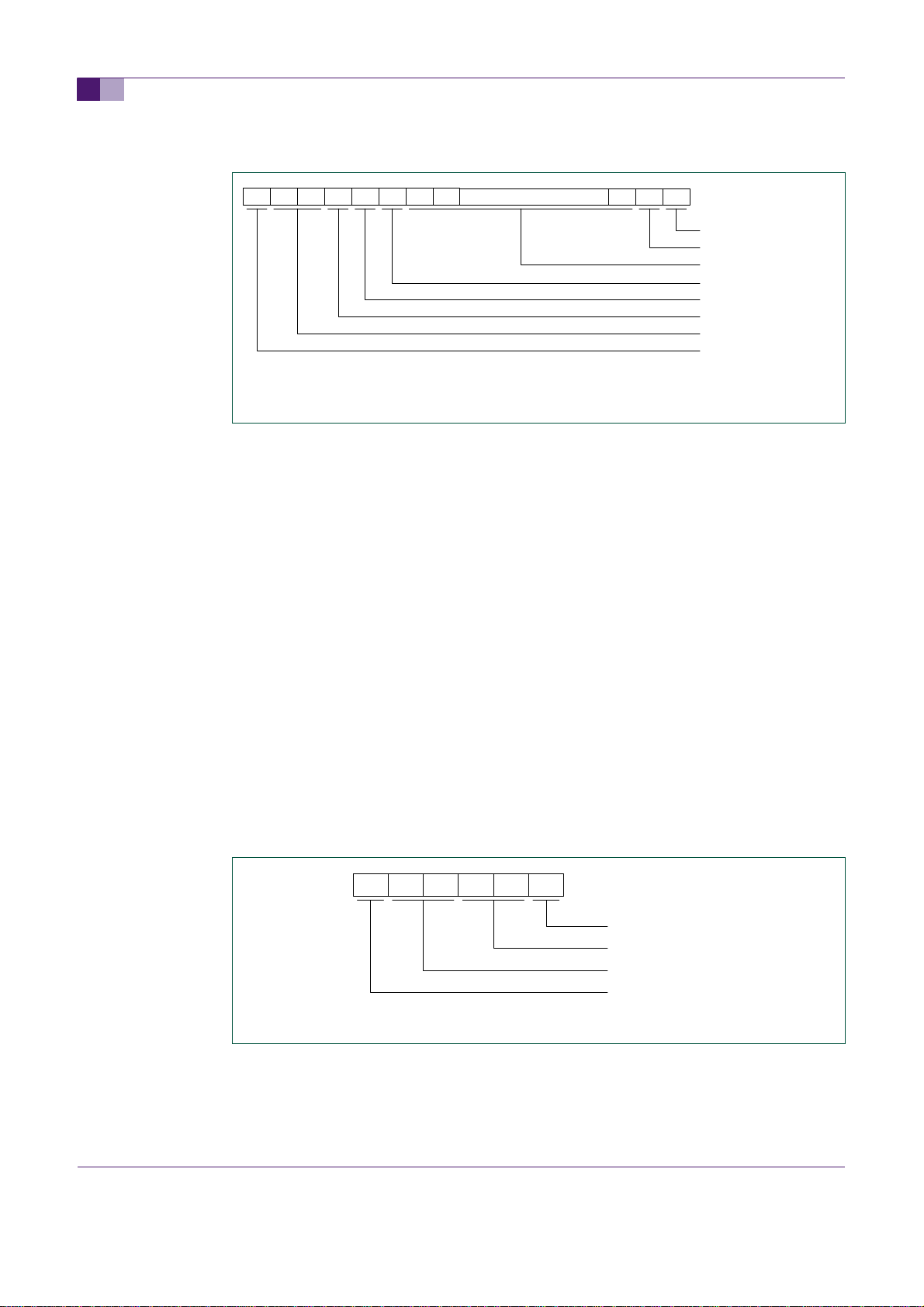

2.3.2 Extended frame

The information frame has an extended definition allowing exchanging more data

between the host controller and the the PN532 (theoretically up to 64kB).

In the firmware implementation of the the PN532, the maximum length of the packet data

is limited to 264 bytes (265 bytes with TFI included).

The structure of this frame is the following:

AN10609_3

PN532 C106 application note

0000 FF TFILCS PD0 PD1 ……... DCSPDn 00

FF LEN

FF LEN

M

L

Normal Packet Length Checksum : Fixed to FF value

Normal Packet Length : Fixed to FF value

Postamble

Packet Data Checksum

Packet Data

Specific TFI

Packet Length Checksum

Packet Length

Start of Packet Code

Preamble

Fig 6. Extended Information frame

The normal LEN and LCS fields are fixed to the 0xFF value, which is normally

considered as an erroneous frame, due to the fact that the checksum does not fit.

The real length is then coded in the two following bytes LEN

(MSByte) and LEN

M L

(LSByte) with:

LENGTH = LEN

x 256 + LEN

M L

coding the number of bytes in the data field (TFI and

PD0 to PDn)

¾ LCS 1 Packet Length Checksum LCS byte that satisfies the relation:

Lower byte of [LEN

+ LEN + LCS] = 0x00,

M L

¾ DATA LENGTH-1 bytes of Packet Data Information

The first byte PD0 is the Command Code.

The host controller, for sending frame whose length is less than 255 bytes, can also use

this type of frame.

But, the the PN532 always uses the suitable type of frame, depending on the length

(Normal Information Frame for frame <= 255 bytes and Extended Information Frame for

frame > 255 bytes).

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 10 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 11

NXP Semiconductors

2.4 Typical application diagrams

AN10609_3

PN532 C106 application note

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 11 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 12

NXP Semi

conductors

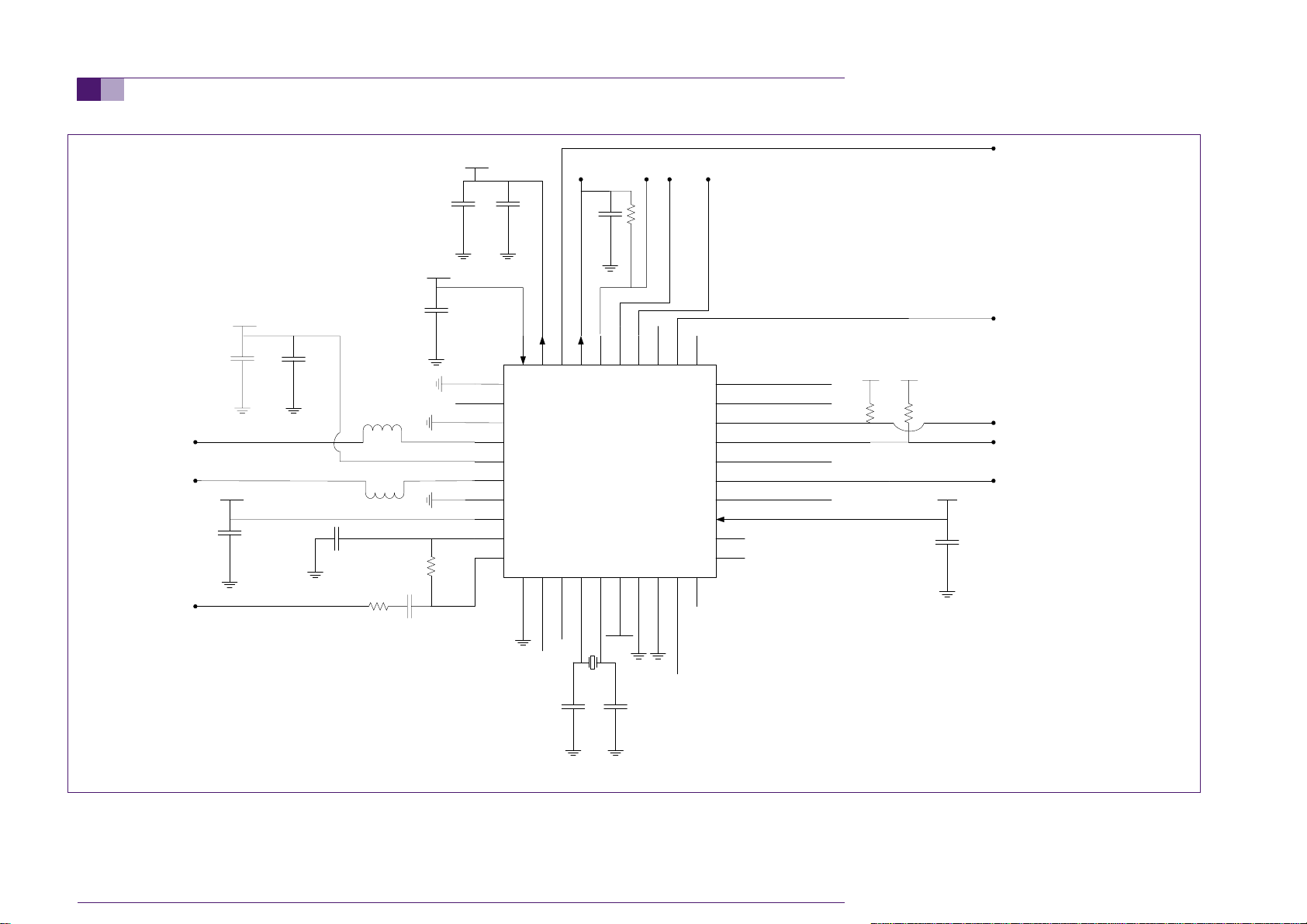

2.4.1 I2C application diagram

DVDD

100 nF

To antenna

To antenna

DVDD

100 nF

To antenna

4.7 µF

100 nF

560nH

560nH

2.7 k

100 nF

1 nF

AN10609_3

PN532 C106 application note

DVDD

10 µF

100 nF

VBAT

1

D

D

G

N

T

G

N

TX1

TVDD

TX2

TGND2

AVDD

VMID

RX

2

3

1

D

4

5

6

7

8

9

10

Test point

LOADMOD

1 k

To SMX To SMX To SMX

VBAT

DVDD

RSTPDN

39 38 37 36 35 34 33 32 3140

AUX1

AUX2

AGND

Test point

27.12 MHz

100 nF

SVDD

XTAL1

SIGIN

PN532

XTAL2

DVDD

47 k

To SMX

SIGOUT

I0

P34

I1

NC

NC

P33

P32

P31

30

SCK

29

MISO

28

MOSI

27

NSS

26

RSTOUTN

25

IRQ

24

P30

23

PVDD

22

NC3

21

NC2

20191817161514131211

P35

NC1

TESTEN

DVDD)

connected to

NC (internally

HREQ

NC

NC

NC

NC

PVDDPVDD

3.3 k 3.3k

SDA

SCL

To host controller. Low state = reset. High

state = functional mode. RSTPD_N must not

exceed min(VBAT, 3.6V) (e.g. use a resistor

PVDD

100 nF

bridge on VBAT)

To Host controller

To Host controller

To Host controller

To Host controller

start up high (PVDD) or low

22 pF

22 pF

Fig 7. I2C PN532C106 application diagram

Error! Unknown document property name.

Application note Rev 1.2 —1/14/2010 12 of75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 13

NXP Semi conductors

2.4.2 SPI communication

2.4.2.1 SPI and LowVbat mode

Using Low Vbat functionality and SPI interface requires the following work around.

1. In case LowVbat functionality is not required

Always keep PVDD (and Vbat) present. Proceed as described in paragraph 2.5.2

2. In case LowVbat functionality is required

The interface pins will be used to achieve LowVbat mode. Therefore they must be connected to the host

controller.

Before switching off the host controller, change I0 to 1 and I1 to 0 (this put the PN532 in I2C

configuration)

Host sends a reset pulse (minimum 20ns, see datasheet p209) to PN532 via RSTPD_N

Wait a time off (2ms, see datasheet p209)

The PN532 will go in LowVbat mode and stays in this mode (25µA)

AN10609_3

PN532 C106 application note

Î An external reader can communicate with the SMX as a card

To wake up the PN532 (to exit LowVbat mode) and recover SPI communication

Host controller change I0 to 0 and I1 to 1 (restore SPI configuration)

Host controller sends a reset pulse (minimum 20ns) to PN532 via RSTPD_N

Wait a time off (2 ms)

Host controller sets NSS wake-up (high to low, CSN)

Î SPI communication can be performed (e.g. send command SAMConfiguration ’14 01’ to

switch to standard mode).

When changing I0 and I1, the internal configuration of pins 27, 28, 29, 30 (interface lines) is changed. See

table in paragraph 2.4.4 Default pin configuration.

Warning: It is also possible to switch to I0 and I1 to 0 (HSU). The advantage is that only I1 need to be

toggle. But in this mode, pin 28 MOSI/TX is strongly push pulled to high by PN532, which can prevent the

communication between the host controller and other chips on the SPI bus.

2.4.2.2 SPI application diagram

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 13 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 14

NXP Semiconductors

DVDD

100 nF

To antenna

To antenna

DVDD

100 nF

To antenna

4.7 µF

100 nF

560nH

560nH

2.7 k

100 nF

1 nF

AN10609_3

PN532 C106 application note

DVDD

10 µF

100 nF

VBAT

1

D

D

G

N

T

G

N

TX1

TVDD

TX2

TGND2

AVDD

VMID

RX

2

3

1

D

4

5

6

7

8

9

10

Test point

LOADMOD

1 k

To SMX To SMX To SMX

VBAT

DVDD

RSTPDN

39 38 37 36 35 34 33 32 3140

AUX1

AUX2

AGND

Test point

27.12 MHz

100 nF

SVDD

XTAL1

SIGIN

PN532

XTAL2

47 k

To SMX

SIGOUT

I0I

NC

NC

P34

P33

P32

P31

30

SCK

29

MISO

28

MOSI

27

NSS

26

RSTOUTN

25

IRQ

24

P30

23

PVDD

22

NC3

21

NC2

20191817161514131211

1

N

5

3

E

C

T

P

1

N

S

E

T

o

lly

t

a

)

d

n

r

e

D

t

e

c

t

D

e

V

in

n

(

D

n

C

o

c

N

NC

NC

To host controller. Low state = reset. High

state = functional mode. RSTPD_N must not

exceed min(VBAT, 3.6V) (e.g. use resistor

bridge on VBAT)

To Host controller

To Host controller

To Host controller

To Host controller

To Host controller

PVDD

start up high (PVDD) or low

100 nF

22 pF

22 pF

Fig 8. SPI PN532C106 application diagram

Error! Unknown document property name.

Application note Rev 1.2 —1/14/2010 14 of75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

To Host controller

To Host controller

Page 15

NXP Semiconductors

2.4.2.3 SPI communication details

The PN532 is slave. A Status byte (Bit 0 of Status byte) indicates if the PN532 is ready to give a response

or not. First byte sent on MOSI by the host controller indicates which operation will be performed:

xxxx xx10 : Read (by the host) Status byte

xxxx xx01 : Write data (transmission from the host to the PN532)

xxxx xx11 : Read data (transmission from the PN532 to the host)

After having sent a command, the host controller must wait for bit 0 of Status byte equals 1 before reading

the data from the PN532.

Bytes are transmitted LSB first.

NSS must be toggle as shown in the user manual (reference 1) or in the next figures.

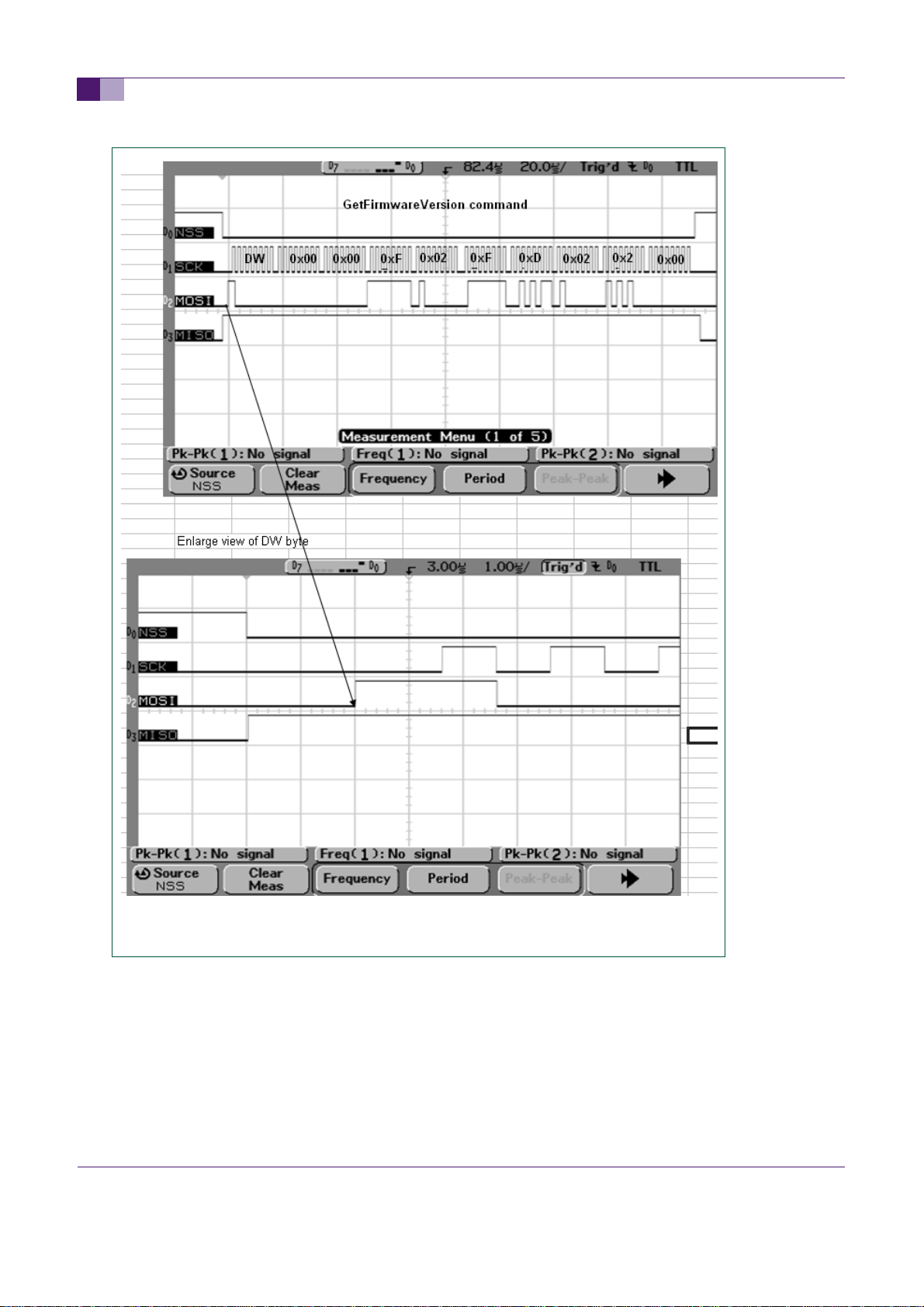

2.4.2.4 SPI waveforms

SPI waveforms for GetFirmware version command (example with SPI freq. 500 kHz).

AN10609_3

PN532 C106 application note

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 15 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 16

NXP Semiconductors

AN10609_3

PN532 C106 application note

Fig 9. Write the command.

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 16 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 17

NXP Semiconductors

AN10609_3

PN532 C106 application note

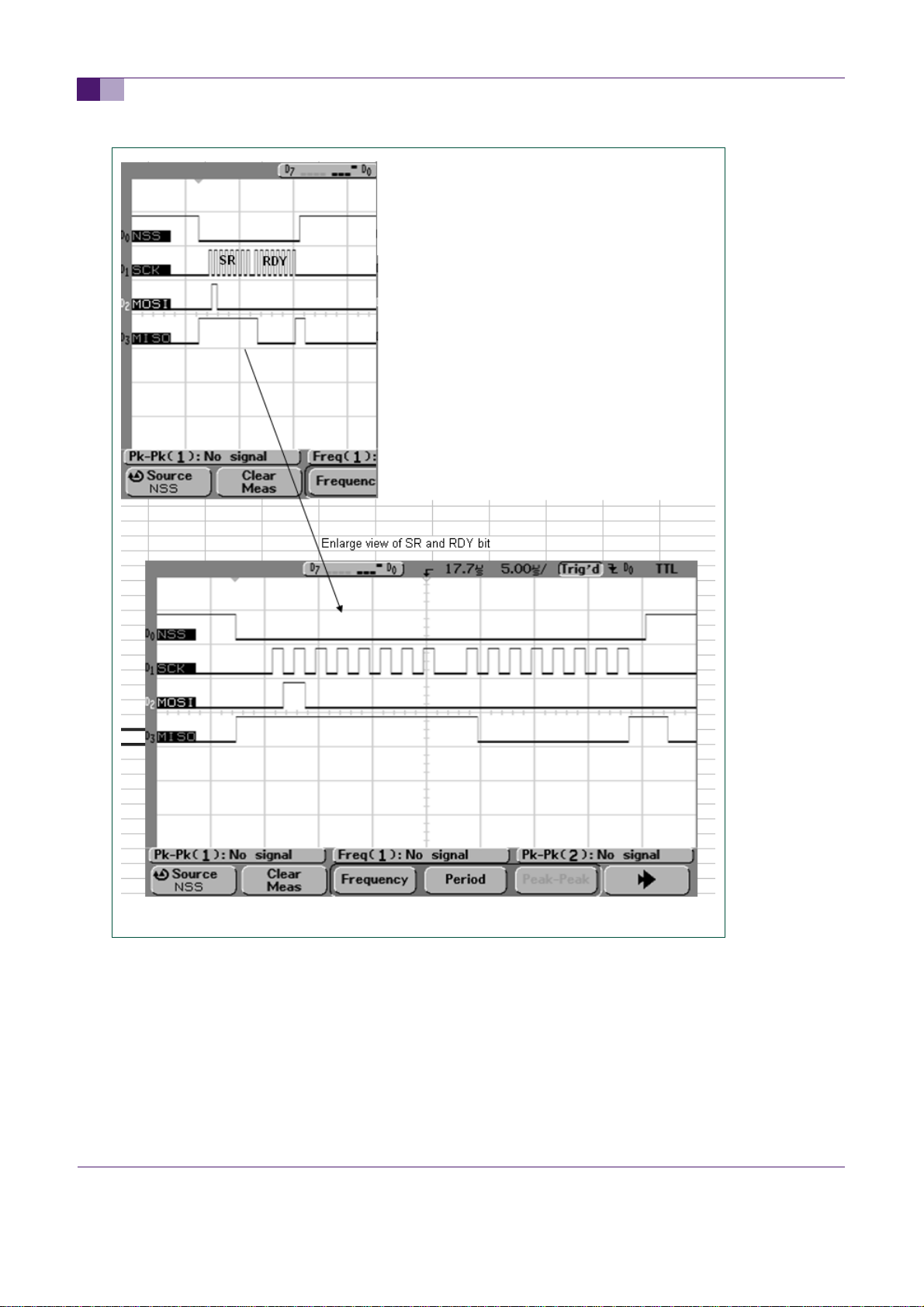

Fig 10. Read the Status.

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 17 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 18

NXP Semiconductors

AN10609_3

PN532 C106 application note

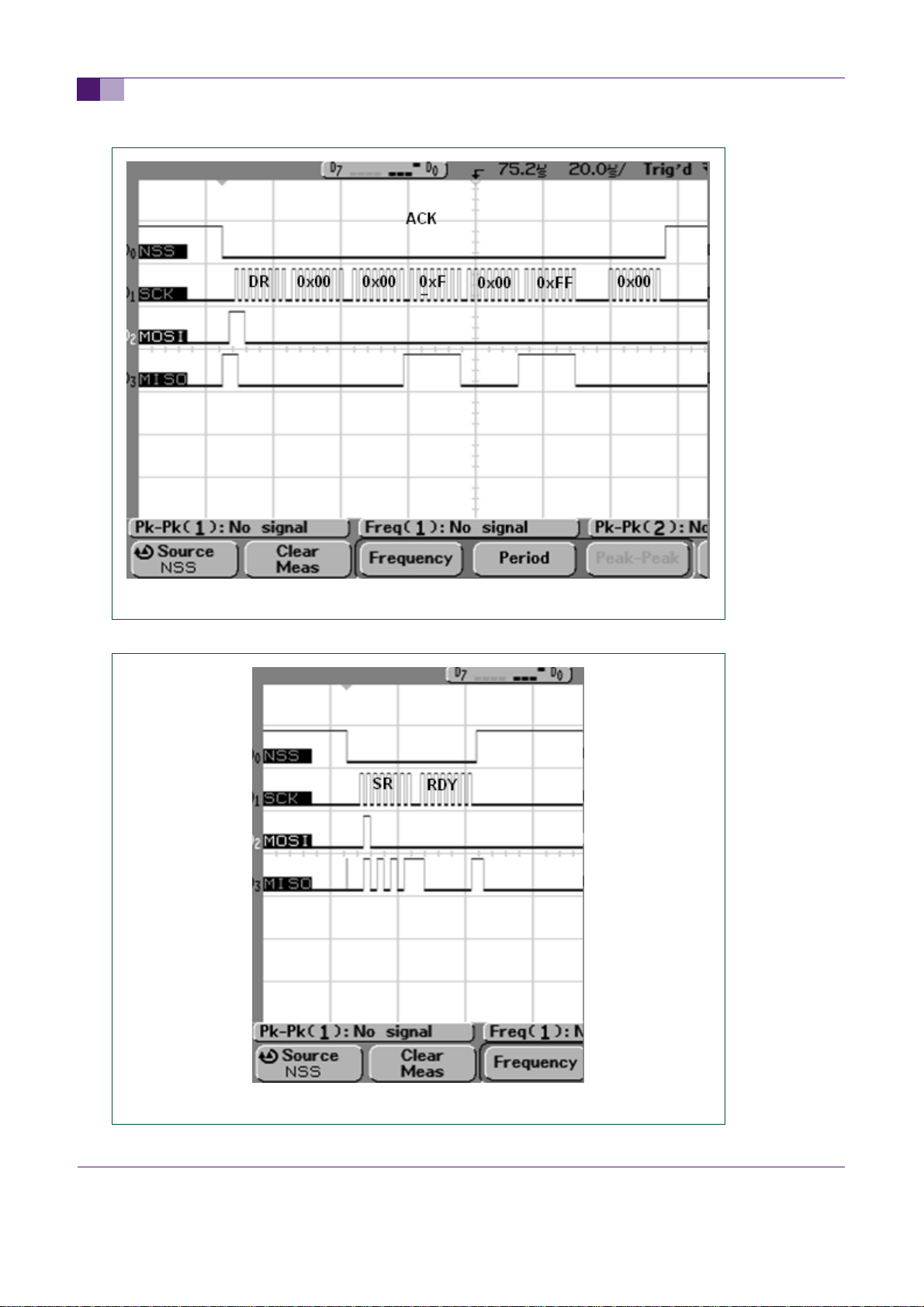

Fig 11. Read the ACK frame.

Fig 12. Read the Status.

Error! Unknown document property name.

Application note Rev 1.2 — 1/14/2010 18 of 75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 19

NXP Semi conductors

AN10609_3

PN532 C106 application note

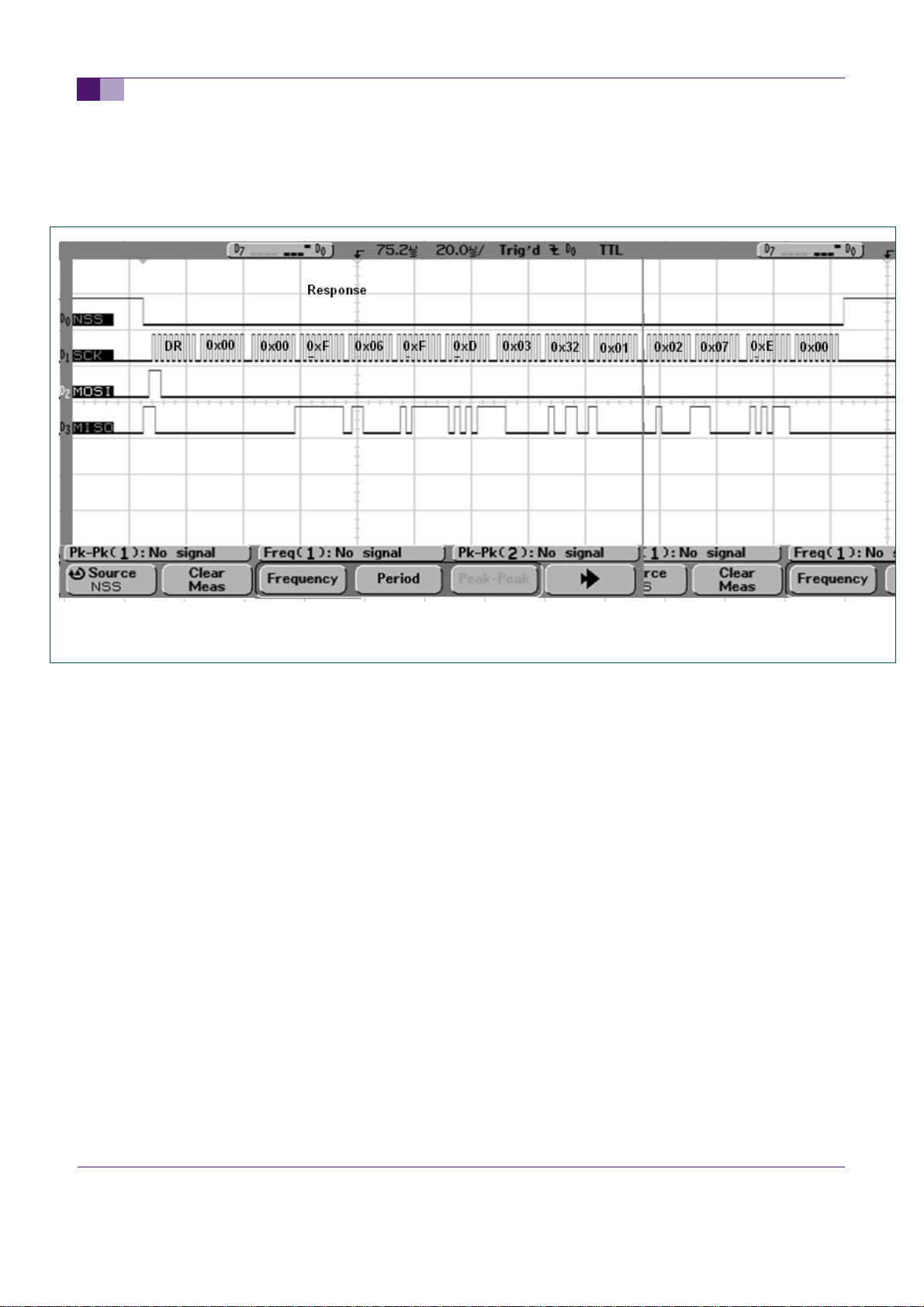

Fig 13. Read the Response frame.

Error! Unknown document property name.

Application note 19 of 75

Rev 1.2 — 1/14/2010

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 20

NXP Semiconductors

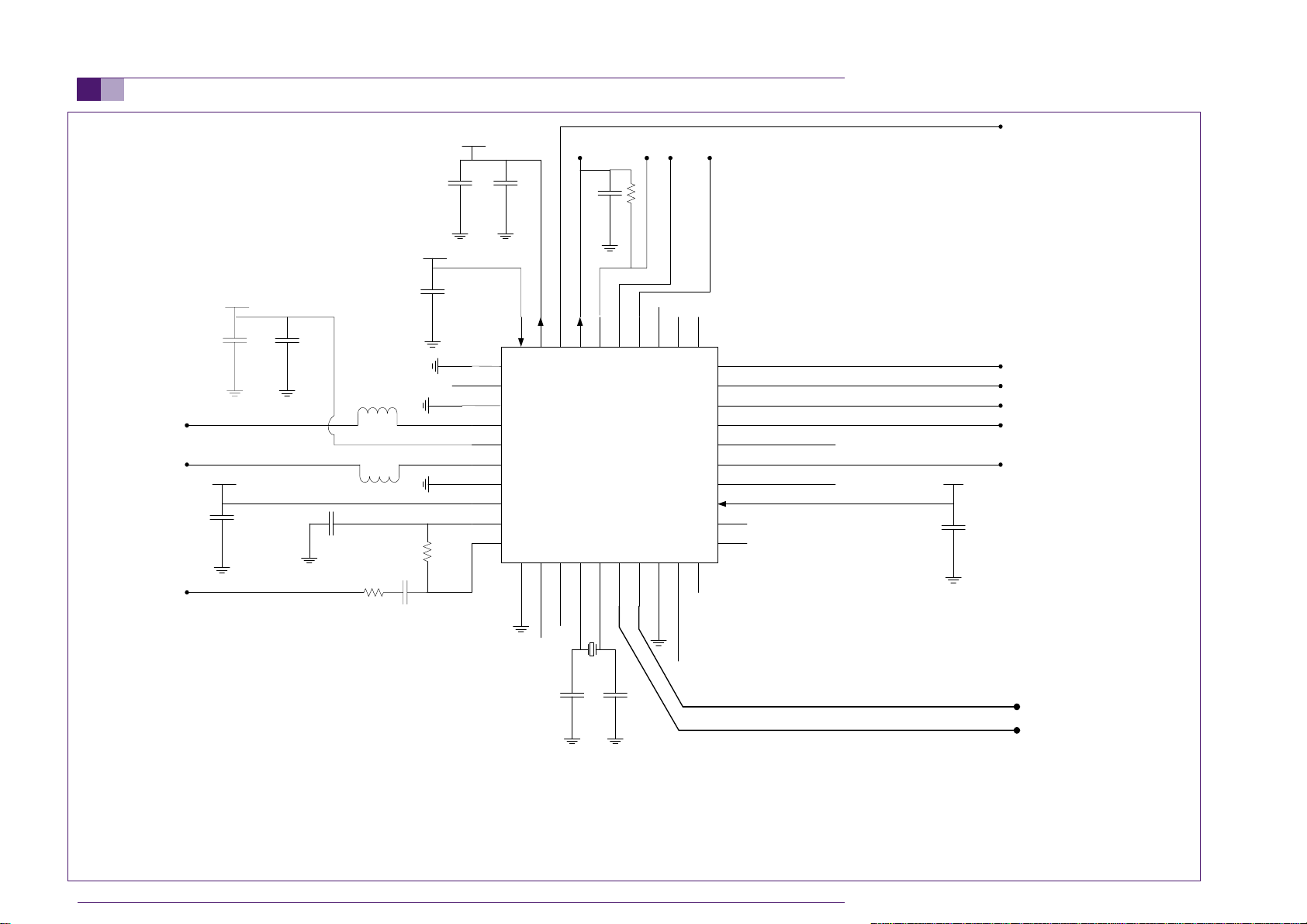

2.4.3 HSU application diagram

DVDD

100 nF

To antenna

To antenna

DVDD

100 nF

To antenna

4.7 µF

100 nF

560nH

560nH

2.7 k

100 nF

1 nF

VBAT

1 k

DVDD

100 nF

D

G

LOADMOD

T

D

G

N

TX1

TVDD

TX2

TGND2

AVDD

VMID

RX

AN10609_3

PN532 C106 application note

To host controller. Low state = reset. High

state = functional mode. RSTPD_N must not

exceed min(VBAT, 3.6V) (e.g. use a resistor

PVDD

100 nF

bridge on VBAT)

To Host controller

To Host controller

To Host controller

To Host controller

start up high (PVDD) or low

100 nF

SVDD

XTAL1

SIGIN

PN532

XTAL2

47 k

To SMX

SIGOUT

I0I

NC

NC

P34

P33

P32

P31

30

SCK

29

MISO

28

MOSI

27

NSS

26

RSTOUTN

25

IRQ

24

P30

23

PVDD

22

NC3

21

NC2

20191817161514131211

1

N

5

3

E

C

T

P

1

N

S

E

T

o

lly

t

a

)

d

n

r

e

D

t

e

c

t

D

e

V

in

n

(

D

n

C

o

c

N

HREQ

NC

NC

Tx

Rx

NC

NC

To SMX To SMX To S MX

10 µF

VBAT

DVDD

RSTPDN

39 38 37 36 35 34 33 32 3140

1

D

N

2

3

1

4

5

6

7

8

9

10

AUX1

AUX2

AGND

Test point

Test point

27.12 MHz

22 pF

22 pF

Fig 14. HSU PN532C106 application diagram

Error! Unknown document property name.

Application note Rev 1.2 —1/14/2010 20 of75

© Koninklijke Philips Electronics N.V. 2006. All rights reserved.

Page 21

NXP Semiconductors

PN532 C106 application note

AN10609_3

2.4.4 Default pin configuration

Consequently, the default pin configuration is as described in the PN532 datasheet. (The

default pin configuration is not changed by the PN532C106 firmware).

Pin Configuration Additional information

I0 Input Connect directly to DVDD or to GND (no need of

I1

PVDD Power pin Externally supplied regulated voltage, 1.6V to 3.6V

RSTPD_N Input NFC reset signal. (Low state = reset)

P30 / UART_RX Quasi bi directional No need of external resistor.

P31 / UART_TX

P32_INT0

P33_INT1

P34 / SIC_CLK

P35

external resistor)

RSTPD_N must never exceed min(3.6 V, VBAT)

When connected to the P5CN072, to be used in Virtual

Card mode, P34 / SIC_CLK shall be connected to

P5CN072 I02

P70_IRQ Quasi bi directional No need of external resistor.

In the Application Note P70_IRQ will be written as IRQ

when used as interrupt line.

In I2C mode: Quasi bi directional No need of external resistor. MISO / P71

MOSI / SDA /

HSU_TX

NSS / P50_SCL /

HSU_RX

In SPI: Push pull No need of external resistor

In HSU: Quasi bi directional No need of external resistor

In I2C mode: Quasi bi directional No need of external resistor. SCK / P72

In SPI: Input No need of external resistor.

In HSU: Quasi bi directional No need of external resistor

In I2C mode: Open drain Use pull up, 1k/V. E.g. for PVDD = 3.3V, 3.3 k pull-up.

In SPI: Input No need of external resistor

In HSU: Push pull No need of external resistor

In I2C mode: Open drain Use pull up, 1k/V. E.g. for PVDD = 3.3V, 3.3 k pull-up.

In SPI: Input

Use resistor bridge or LDO and pull up to be able

• to keep NSS high even when PVDD =

0 (to stay in LowV

• to force a low state to wake up.

mode)

BAT

In HSU: Input No need of external resistor

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 21 of 75

Page 22

NXP Semiconductors

AN10609_3

PN532 C106 application note

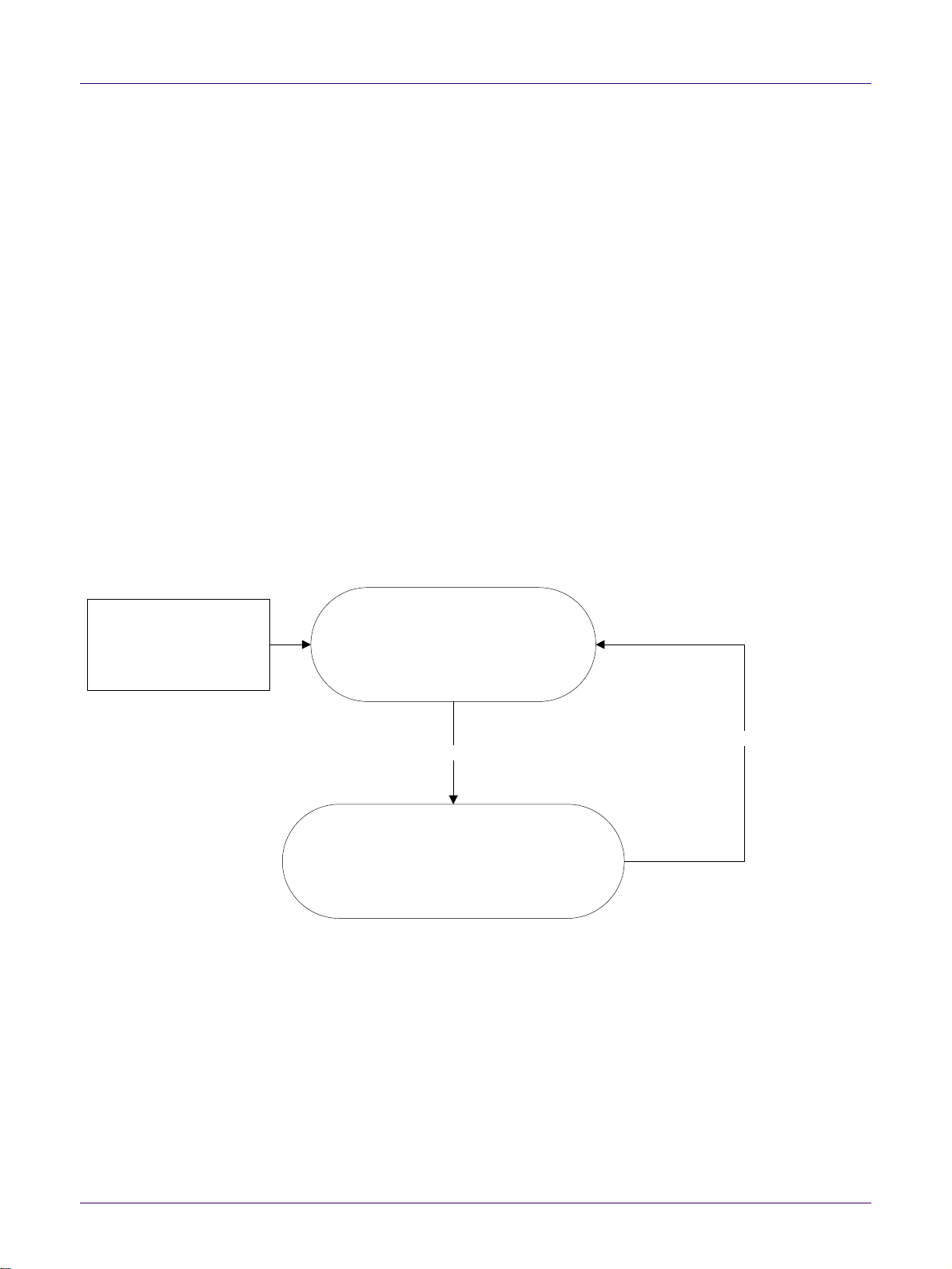

2.5 How to start the PN532C106?

2.5.1 LowVbat mode (PN532C106 start up default mode)

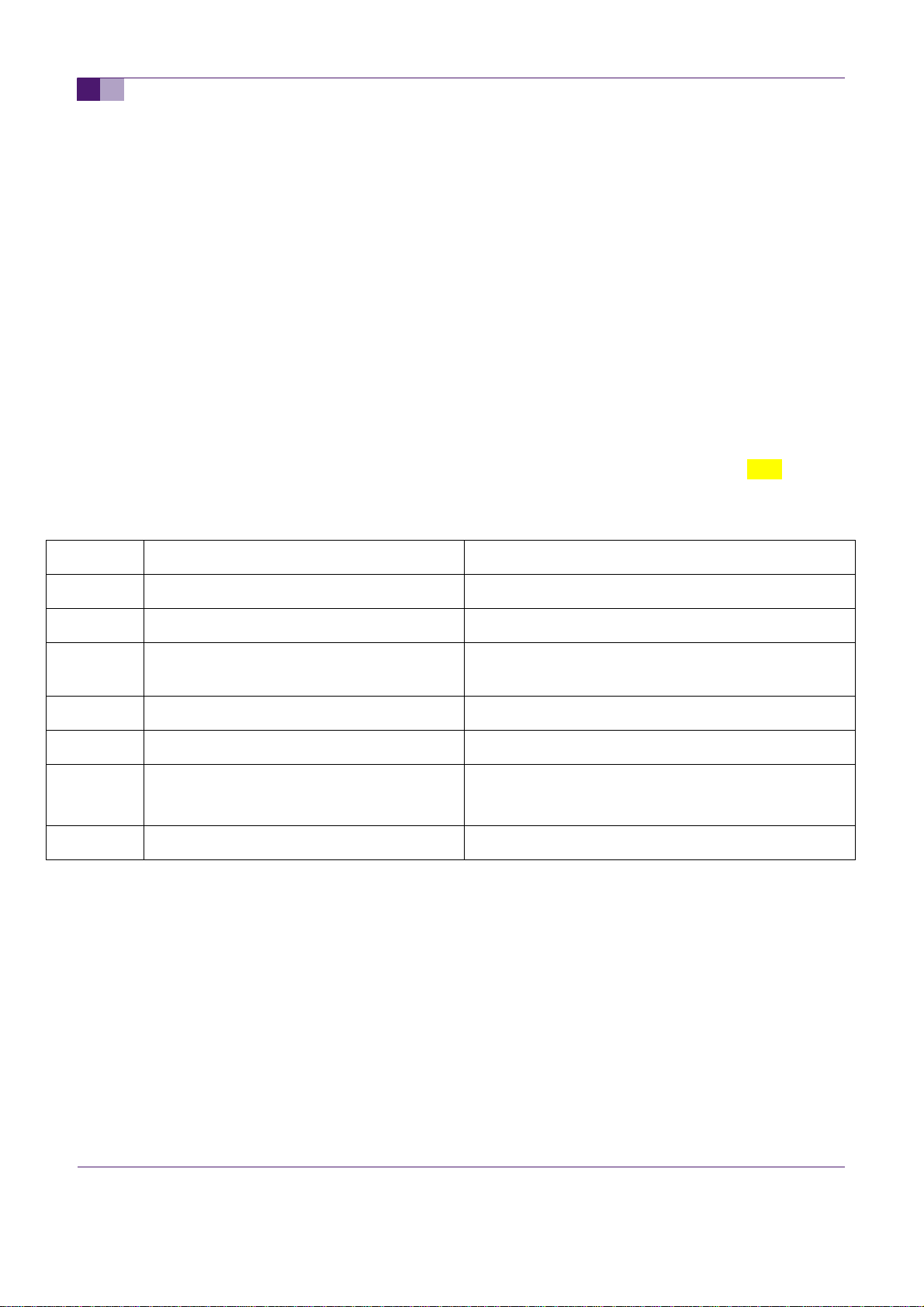

PN532C106 starts in “Low Vbat” mode.

In this mode, the PN532C106 is in virtual card mode when an external field is

present, and in power down mode otherwise. In this mode, an external reader can

communicate with the SMX (connected to PN532C106 via its S2C interface).

¾ No interrupt (IRQ) will be returned by PN532C106 to its host controller.

¾ The host controller cannot wake up PN532 using HREQ/P32 line (pin 32).

This mode is functional even if PVDD = 0V. (V

LowV

diagram and power consumption:

BAT

between 2.7V and 5.5V)

BAT

Power-up the VBAT

of the PN532 C106

(PVDD = baseband supply

has no influence)

The PN532 is configured in the so-called

LowVbat mode

The functional mode of the PN532 is

Soft Power Down mode.

Its current consumption is ar ound 20uA.

PN532 C106 goes out of external fie l d

PN532 C106 goes into external RF field

The PN532 is configured in th e so-called

LowVbat mode

The functional mode of the PN532 in the field is

Card Emualtion mode.

Its current consumption is around 20mA .

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 22 of 75

Page 23

NXP Semiconductors

PN532 C106 application note

AN10609_3

2.5.2 To go out Low Vbat mode (i.e. to wake up PN532C106 after start up)

To go out “Low Vbat” mode, there are three conditions

• PVDD must be present.

• More over, to wake up the PN532C106, the host controller must

• In I2C

Send PN532 I2C address (48h). The PN532 will stretch low the SCL line during

1 ms (can be less depending on the quartz). The host controller shall wait for the

end of the stretching.

• In SPI

Set NSS low during 1 ms (can be less depending on the quartz)

• In HSU

Send a preamble 55 55 00 00 00 00 00 FF then Len LCS ….

• The ho st controller must send one of the following commands (using the wake up

conditions described just above)

− Either it wants to stay in virtual card mode. Then it shall send a command to

enable the interrupt generation (IRQ) by PN532C106. (The IRQ warns the host

controller that a transaction occurred between an external reader and the SMX).

The command to send is “SAM Configuration” with parameter Mode = virtual (02h)

and parameter IRQ use = yes (either put value 01h or omit the parameter).

So the command is ‘14 02 00’ (or ‘14 02 00 01’)

− Or it wants to go to normal mode. Then it shall send “SAM Configuration” with

parameter Mode = normal (01h). So the command is ‘14 01’

Once woken up, any command can be send like in PN532C104 (with handshake

mode)

NB: As soon as PVDD is present, the host controller must send a command to

enable the interrupt generation (IRQ) by PN532C106. (The IRQ warns the host

controller that a transaction occurred between an external reader and the

SMX). The command to send is “SAM Configuration” with parameter Mode = virtual

(02h) and parameter IRQ use = yes (either put value 01h or omit the parameter)

14 02 00 (or 14 02 00 01)

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 23 of 75

Page 24

NXP Semiconductors

AN10609_3

PN532 C106 application note

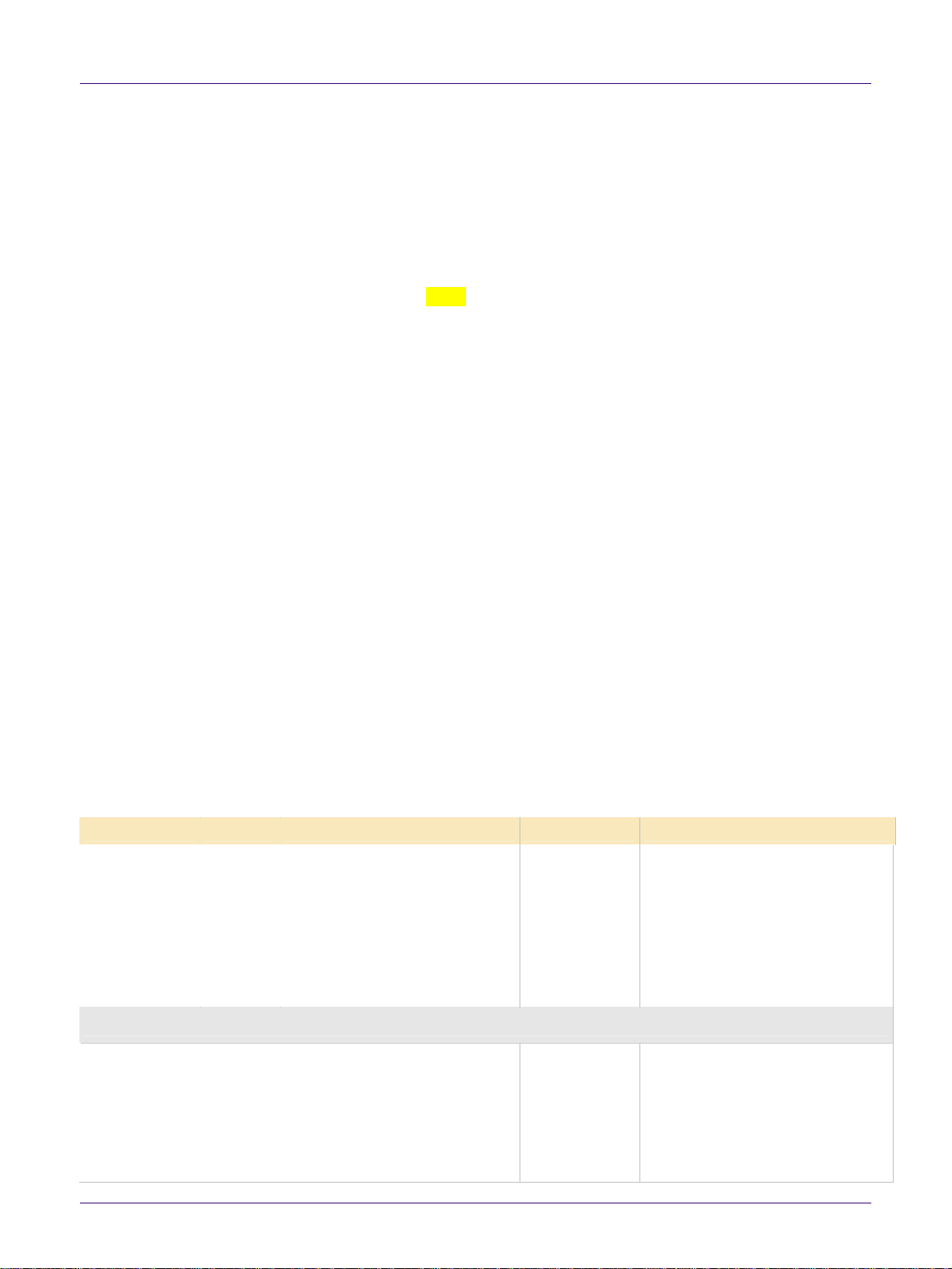

Instructions described in this paragraph are represented on the following diagram:

Power-Off

VBAT present (>2.5V)

PVDD has no impact

LowVbat mode

= Card Emulation with

No HREQ functionality

Send 14 01

(with no HREQ during command)

Send 14 02 00

(with no HREQ during command)

Card Emulation mode

Normal mode

with HREQ and IRQ informations

See Remark.

Battery Voltage too low for Mobile Call

Send 14 02 00 00

(with HREQ and IRQ informations)

Remark: In that modes, in order to fullfill the application requirements, any commands of t he User

Manual can be sent using HREQ and IRQ informations. These scenarios are not described in the

diagram.

with HREQ and IRQ informations

See Remark.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 24 of 75

Page 25

NXP Semiconductors

PN532 C106 application note

AN10609_3

3. The PN532 commands

3.1 Global view

The PN532 can be access using directly the firmware API described in reference 1 and

in the following pages (interface B in the figure 17). Or an upper software layer can be

used (NXP can provide this layer called Hardware Abstraction Layer (HAL) – HAL is the

interface A in the figure 17).

Note: PN51x, PNxxx, RCxxx represents other NXP NFC products. PN53x represents

PN531 or the PN532 product.

Fig 15. Possible softw are/hardware interface

The next paragraph described the “interface B”, i.e. the firmware commands.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 25 of 75

Page 26

NXP Semiconductors

AN10609_3

PN532 C106 application note

3.2 The PN532 embedded software API: commands and errors lists

3.2.1 Commands codes

The PN532 The PN532 Command

Command as Initiator as Target Code

Miscellaneous

Diagnose X X

GetFirmwareVersion X X

GetGeneralStatus X X

ReadRegister X X

WriteRegister X X

ReadGPIO X X

WriteGPIO X X

0x00

0x02

0x04

0x06

0x08

0x0C

0x0E

SetSerialBaudRate X X

SetParameters X X

SAMConfiguration X X

PowerDown X X

RF communication

RFConfiguration X X

RFRegulationTest X X

Initiator

InJumpForDEP X

InJumpForPSL X

InListPassiveTarget X

InATR X

InPSL X

0x10

0x12

0x14

0x16

0x32

0x58

0x56

0x46

0x4A

0x50

0x4E

InDataExchange X

InCommunicateThru X

InDeselect X

InRelease X

InSelect X

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 26 of 75

0x40

0x42

0x44

0x52

0x54

Page 27

NXP Semiconductors

AN10609_3

PN532 C106 application note

The PN532 The PN532 Command

Command as Initiator as Target Code

InAutoPoll X

Target

TgInitAsTarget X

TgSetGeneralBytes X

TgGetData X

TgSetData X

TgSetMetaData X

TgGetInitiatorCommand X

TgResponseToInitiator X

0x60

0x8C

0x92

0x86

0x8E

0x94

0x88

0x90

TgGetTargetStatus X

3.2.2 Errors codes

Error cause Error code

Time Out, the target has not answered 0x01

A CRC error has been detected by the contactless UART 0x02

A Parity error has been detected by the contactless UART 0x03

During a MIFARE anticollision/select operation, an erroneous

Bit Count has been detected

Framing error during MIFARE operation 0x05

An abnormal bit-collision has been detected during bit wise

anticollision at 106 kbps

Communication buffer size insufficient 0x07

RF Buffer overflow has been detected by the contactless

UART (bit BufferOvfl of the register CL_ERROR)

0x8A

0x04

0x06

0x09

In active communication mode, the RF field has not been

switched on in time by the counterpart (as defined in NFCIP-1

standard)

RF Protocol error (cf. reference [4], description of the

CL_ERROR register)

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 27 of 75

0x0A

0x0B

Page 28

NXP Semiconductors

AN10609_3

PN532 C106 application note

Error cause Error code

Temperature error: the internal temperature sensor has

detected overheating, and therefore has automatically

switched off the antenna drivers

Internal buffer overflow 0x0E

Invalid parameter (range, format, …) 0x10

DEP Protocol: The the PN532 configured in target mode does

not support the command received from the initiator (the

command received is not one of the following: ATR_REQ,

WUP_REQ, PSL_REQ, DEP_REQ, DSL_REQ, RLS_REQ,

ref. [1]).

DEP Protocol / Mifare / ISO/IEC 14443-4: The data format

does not match to the specification.

Depending on the RF protocol used, it can be:

• Bad length of RF received frame,

• Incorrect value of PCB or PFB,

• Invalid or unexpected RF received frame,

• NAD or DID incoherence.

0x0D

0x12

0x13

Mifare: Authentication error 0x14

ISO/IEC 14443-3: UID Check byte is wrong 0x23

DEP Protocol: Invalid device state, the system is in a state

which does not allow the operation

Operation not allowed in this configuration (host controller

interface)

This command is not acceptable due to the current context of

the the PN532 (Initiator vs. Target, unknown target number,

Target not in the good state, …)

The the PN532 configured as target has been released by its

initiator

The PN5321 and ISO/IEC 14443-3B only: the ID of the card

does not match, meaning that the expected card has been

exchanged with another one.

The PN5321 and ISO/IEC 14443-3B only: the card previously

activated has disappeared.

Mismatch between the NFCID3 initiator and the NFCID3

target in DEP 212/424 kbps passive.

An over-current event has been detected 0x2D

0x25

0x26

0x27

0x29

0x2A

0x2B

0x2C

NAD missing in DEP frame 0x2E

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 28 of 75

Page 29

NXP Semiconductors

AN10609_3

PN532 C106 application note

3.3 The PN532 various modes

This paragraph summarizes the PN532 functionalities and sho w s which commands are

associated to them.

The PN532 firmware implements functions to easily behave:

- As a NFC initiator or a NFC target (according to NFCIP-1 specification).

In this mode, RF communication is according to NFCIP-1 specification. Two NFC

devices can communicate together (peer to peer communication). One device is the

initiator: it starts the exchange and chooses the mode. The other device is the target.

Passive mode or active mode can be used. In active mode, each device generates

RF field when it transmits data (and switches RF field off at the end of the

transmission). In passive mode, only the initiator generates RF field. The target

answers in a load modulation scheme.

HOST

CONTROLLER

e.g. Mobile phone

RF com m unication

Fig 16. Peer to peer communication (NFC initiator and NFC target)

PN532PN532

CONTROLLER

- As a Mifare reader (Mifare protocol).

In this mode, RF communication is according to Mifare specification. the PN532

behaves as a Mifare reader. It can communicate with Mifare cards.

HOST

CONTROLLER

e.g. Mobile phone

PN532

RF communication

HOST

e.g. PDA

Fig 17. The PN532 as a Mifare reader

The PN532 has been tested with Mifare 1k, 4k, Ultralight, and DesFire cards.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 29 of 75

Page 30

NXP Semiconductors

PN532 C106 application note

- As a T=CL reader (ISO/IEC 14443-4 protocol)

In this mode, RF communication is according to ISO/IEC 14443-4 specification. the

PN532 behaves as an ISO/IEC 14443-4 reader. It can communicate with ISO/IEC

14443-4 cards (only ISO compliant cards are supported).

(The PN532 has been tested with CD97BX, CD light, Desfire, P5CN072 (SMX) as

ISO/IEC 14443-4 (with JCOP OS))

- As a Jewel card reader

The PN532 can communicate with Innovision Jewel cards. It has been tested with

IRT5001 card.

- As a FeliCa reader (FeliCa protocol)

In this mode, RF communication is according to FeliCa specification. the PN532 has

been tested with FeliCa RCS_860 and RCS_854

AN10609_3

- As a ISO/IEC 1443-A card

The PN532 is able to answer to an ISO/IEC 1443-4A reader. It contains a predefined

ATS (only historical bytes are configurable). In this mode, ATS will be sent

automatically to the reader which has sent a RATS. the PN532 handles automatically

waiting time extension (S(WTX)). The command from the reader is transmitted to the

host controller. The host controller builds the response and transmits it to the PN532.

the PN532 handles the encapsulation in ISO/IEC 1443-4 frame. Maximum up to 256

data bytes can be transmitted between the reader and the the PN532 (“short

APDU”).

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 30 of 75

Page 31

NXP Semiconductors

AN10609_3

PN532 C106 application note

- As a virtual card (in combination with a secure smart card)

In this mode, the PN532 is combined with a secure smart card. An external reader

sees the set the PN532+secure smart card as a contactless card.

HOST

CONTROLLER

PN532 SMX

S2C interface

Connection with secure

smart card

RF communication

Mifare Reader

Fig 18. Virtual card mode

RFConfiguration command

This command, described in reference 1, allows changing some registers settings than

can influence the RF communication. The default values are described in reference 1.

The tuning depends on the environment, on the antenna and on the communication

mode.

Very few commands are needed to set up RF communication between the PN532 and

another device (reader, card, or other NFC device). The PN532 executes different RF

processes, depending on the type of communication, but from the host con troller to

the PN532, same commands are used (whatever the baudrate, the mode etc):

Paragraphs below explain which functions to use to communicate in each mode.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 31 of 75

Page 32

NXP Semiconductors

AN10609_3

PN532 C106 application note

3.3.1 How to use the PN532 as a Mifare reader?

3.3.1.1 Command supported by PN532 firmware

The Mifare commands supported by the PN532 firmware are listed in reference 1 and in

the following paragraphs.

For other commands, see 3.3.1.2

Typical sequence (example):

- Scanning for targets (cards) in the field,

- Possibly authenticate with the card,

- Read out the card memory (or any other Mifare commands, such as write),

- Halt the card, select another one, and perform any Mifare command with it

This typical sequence can be performed with the following commands:

- InListPassivTarget, to initialise one (several) cards (maximum two cards at the

same time)

- InDataExchange, to send Mifare commands

- InSelect, InDeselect, and InRelease to select, and release the card (this is

optional, see paragraph

3.3.7.3 on page 56).

Warning:

In case the card initialized indicates it supports ISO/IEC 14443-4 protocol (bit 5 of SAK,

cf. ISO/IEC 14443-3 specification), InListPassiveTarget command of the PN532 performs

automatically ISO/IEC 14443-4 activation (i.e. RATS sending). To disable automatic

RATS sending, SetParameter command must be used (cf. REFERENCE 1).

Table 1. SetParameter command usage to enable or disable automatic RATS sending (ISO/IEC 14443-4 mode)

Action Command

Disable automatic

sending of RATS

command

RATS will not be performed automatically by next InListPassiveTarget.command, even if the card indicates it supports ISO 14443-4

12 13

24

1

Command explanation Response Response explanation

Command code: SetParameters Response command code

Automatic ATR_RES = 1

Automatic ISO/IEC 1443-4A card emu =

1

Enable automatic

sending of RATS

command

(default

configuration of the

PN532 at power

up)

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 32 of 75

12

34

Command code: SetParameters

Automatic ATR_RES = 1

Automatic RATS = 1

Automatic ISO/IEC 1443-4A card emu =

1

13

Response command code

Page 33

NXP Semiconductors

PN532 C106 application note

RATS will be performed automatically by next InListPassiveTarget.command, if the card indicates it supports ISO 14443-4

Mifare commands are briefly described hereafter. Refer to Mifare card

documentation to have a more detailed description of the Mifare command set

The Mifare specific command byte Cmd may take one of the possible values:

60h / 61h Authentication A / Authentication B (Mifare Standard)

Performs authentication sequence.

30h 16 bytes reading

Read one data block (16 bytes) at the selected address of the card.

A0h 16 bytes writing (Mifare Standard)

Write one data block (16 bytes) to the selected address of the card.

A2 h 4 bytes writing (Mifare Ultralight)

Write one data block (16 bytes) to the selected address of the card.

C1 h Increment

Increment the value block at the selected address of the card. The data structure of

the value block must be written in advance with a standard write command.

Data structure

Byte 0 3 4 7 8

11

Value Value

complement

C0 h Decrement

Decrement the value block at the selected address of the card. The data structure of

the value block must be written in advance with a standard write command.

B0h Transfer:

This function writes the prior calculated at the selected address of the card. It must

be called directly after Increment, Decrement or Restore.

C2h Restore

This function restores the value block at the selected address of the card.

Value Addr Addr

12 13 14 15

complement

AN10609_3

Addr Addr

complement

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 33 of 75

Page 34

NXP Semiconductors

PN532 C106 application note

Mifare Ultralight cards

They support only A2h and 30h commands.

Command code Command

Parameter

30h 1 byte address - 16 bytes

A2h 1 byte address 4 bytes -

Mifare Standard cards

Authentication is required before any access to Mifare Standard memory.

Command code Command

Parameter

60h 1 byte address KeyA (6 bytes,

61h 1 byte address KeyB (6 bytes,

30h 1 byte address - 16 bytes

A0h 1 byte address 16 bytes C1h 1 byte address 4 byte increment

C0h 1 byte address 4 byte decrement

B0h 1 byte address - C2h 1 byte address - -

Refer to Mifare card documentation to have a more detailed description of the

Mifare command set

The table on next page shows how to use some of those commands (how to fill the

parameters, which bytes are returned in response…).

Command Data

field

Command Data

field

default value FFh)

followed by UID (4

bytes)

default value FFh)

followed by UID (4

bytes)

value (lower byte

first)

value (lower byte

first)

AN10609_3

Response

Response

-

-

-

-

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 34 of 75

Page 35

NXP Semiconductors

AN10609_3

PN532 C106 application note

Table 2. The PN532 as a Mifare reader

Action Command

Scan for 2 targets

in the field and

initialize them

Target 1 is a Mifare Standard card and target 2 is a Mifare Ultralight card. The 2 cards are initialised. Card 1 is in halt state.

Authenticate with

Mifare Standard

card

4A 4B

02 02

01

00 04 00

40

01

60

07

FF FF FF

FF FF FF

12 67 58 32

1

Command explanation Response Response explanation

Command code: InListPassivTargets

Number of cards to initialize (if present

in the field)

Baud rate = 106 kbits/sec.

Command code: InDataExchange 41 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

Mifare cmd code (authenticate)

Mifare address

Default authentication key (last bytes

are NFCID1 bytes)

08

04

12 67 58 32

02

44 00

00

08

88 04 B6 E4 00 00

00 00

Response command code

2 targets detected

Target number 1

SENS_RES(2) of target 1

SEL_RES(2) of target 1

NFCID1 length = 4 bytes

NFCID1 of target 1

Target number 2

SENS_RES(2) of target 2

SEL_RES(2) of target 2

NFCID1 length = 8 bytes

NFCID1 of target 2

Card2 has been put in halt state. Card1 has been wake up and authentication has been performed.

Read out card 1

memory

Card2 is still in halt state. Any Mifare commands, for example Read 16 bytes, can be sent to card 2 with InDataExchange function.

Halt card 1, select

card 2 and write in

card 2 memory

Halt card 2

01 The cmd is intended to target number 1 00

30 Mifare cmd code (read 16 bytes) EE EE EE EE EE

04 Mifare address

40

02 The cmd is intended to target number 2

A2 Mifare cmd code (write 4 bytes)

08 Mifare address

FF FF FF

FF

Any Mifare commands, for example Write 4 bytes, can be sent to card 2 with InDataExchange function.

01

Command code: InDataExchange 40 41 Response command code

Status = 0 (OK, no error)

EE EE EE

EE EE EE EE EE

EE EE EE

Command code: InDataExchange

Bytes to be written

Card1 has been put in halt state. Card 2 has been wake up.

Command code: InDeselect 44 45 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

HALT REQ is sent with InDeselect command.

41 Response command code

00

Bytes read (example)

Status = 0 (OK, no error)

(1)

Command code and command parameters. Mandatory protocol encapsulation is not represented.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 35 of 75

Page 36

NXP Semiconductors

AN10609_3

PN532 C106 application note

(2)

SENS_RES and SEL_RES coding is described in ISO/IEC 18092 specification.

Timeout and number of retries

Activation phase (InListPassiveTarget command)

By default, the PN532 is configured to retry to detect a card as long as there is no

card detected. It can be changed using RFConfiguration command, item 5

(MaxRtyPassiveActivation parameter, c.f. UM0502-05).

If there is no card in the field, a timeout occurs after 5 ms. Either the PN532 retries to

find a card, if MaxRtyPassiveActivation > 1, or it sends a response to its host

controller, indicating that zero target has been found.

Communication phase (InDataExchange command)

By default, the timeout is set to 51.2 ms. It can be changed using RFConfiguration

command item 2 (UM0501-02 page 80).

Deactivation phase (InDeselect/InRelease command)

InDeselect or InRelease commands perform a HALTA request. The return status is

always “No error” (00h), even if the card did not respond (within 5 ms).

Note: It is not needed to use InDeselect (and InSelect) command to handle two

cards. Indeed, when using InDataExchange command, the PN532 automatically

wakes up the card corresponding to the desired TgNb, and automatically put in

HALT state the other one.

3.3.1.2 Other Mifare commands

PN532 InDataExchange command supports Mifare commands listed in the user manual

(reference 1). Commands not mentioned will return an error. However, it is possible to

send other commands (e.g. Mifare Plus new commands), using InCommunicateT hru

command.

// test InCommunicateThru for sending commands to Mifare Plus card

// disable autoRATS to stay in the Mifare mode

PC -> IFD : SET TAMA PARAMETERS

00 00 FF 03 FD D4 12 00 1A 00

IFD -> PC : ACK

00 00 FF 00 FF 00

IFD -> PC : SET TAMA PARAMETERS EXECUTED

00 00 FF 02 FE D5 13 18 00

// Look for a 106 kbps card

PC -> IFD : INITIATOR : LIST PASSIVE TARGETS

00 00 FF 04 FC D4 4A 01 00 E1 00

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 36 of 75

Page 37

NXP Semiconductors

PN532 C106 application note

IFD -> PC : ACK

00 00 FF 00 FF 00

IFD -> PC : INITIATOR : LIST PASSIVE TARGETS EXECUTED

00 00 FF 0F F1 D5 4B 01 01 00 42 18 07 04 66 C5

04 05 06 07 38 00

// read TxMode and RxMode registers

PC -> IFD : READ REGISTERS

00 00 FF 06 FA D4 06 63 02 63 03 5B 00

IFD -> PC : ACK

00 00 FF 00 FF 00

IFD -> PC : READ REGISTERS EXECUTED

00 00 FF 04 FC D5 07 80 80 24 00

AN10609_3

// Change CRC of RxMode : disable CRC Rx

PC -> IFD : WRITE REGISTERS

00 00 FF 05 FB D4 08 63 03 00 BE 00

IFD -> PC : ACK

00 00 FF 00 FF 00

IFD -> PC : WRITE REGISTERS EXECUTED

00 00 FF 02 FE D5 09 22 00

// send Mifare Plus command A8

PC -> IFD : INITIATOR : COMMUNICATE THRU

00 00 FF 15 EB D4 42 A8 02 90 11 11 11 11 11 11

11 11 11 11 11 11 11 11 11 11 A0 00

IFD -> PC : ACK

00 00 FF 00 FF 00

IFD -> PC : INITIATOR : COMMUNICATE THRU EXECUTED

00 00 FF 04 FC D5 43 00 0A DE 00

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 37 of 75

Page 38

NXP Semiconductors

PN532 C106 application note

AN10609_3

3.3.2 How to use the PN532 as a T=CL reader (ISO/IEC 14443-4)?

A typical sequence can be:

- Scan for targets (cards) in the field, (initialisation and activation of the card)

- Perform any T=CL command

- Deselect the card

This typical sequence can be performed with the following commands:

- InListPassivTarget, to initialise one (several) cards (maximum two cards at the

same time).

In case of Type A card, the RATS is sent automatically by this command. CID

parameter is set to 0 and FSDI is set to 5 (Î FSD = 64 bytes).

In case of Type B card, the default method used is the timeslot one. It can be

changed by indicated in the parameter of this command that the probabilistic

polling method must be used.

- InDataExchange, to send ISO/IEC 14443-4 commands

- InSelect, InDeselect, and InRelease to select, and release the card (this is

optional, see paragraph

3.3.7.3 on page 56).

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 38 of 75

Page 39

NXP Semiconductors

AN10609_3

PN532 C106 application note

Table 3. The PN532 as a ISO/IEC 1443-4 reader. Type A card activation

Action Command

Scan for 1 target

in the field and

initialize it

Bit 5 of SEL_RES indicates the target is ISO/IEC 14443-4 compliant.

In that case the PN532 automatically sends the RATS(2). ATS is indicated in the response.

4A Command code: InListPassivTargets 4B

01 Number of cards to initialize (if present

01

00 Baud rate = 106 kbits/sec. Type A. 04 07

4

in the field) = 1

Command explanation Response Response explanation

Response command code

01

28

04

00 D4 1E 92

0D 77 80 81 02 00

73 C8 40 13 00 90

00

1 target detected

Target number 1

SENS_RES(1) of target 1

SEL_RES(1) of target 1

NFCID1 length = 4 bytes

NFCID1 of target 1

ATS

Read 16 bytes 40 Command code: InDataExchange

01 The cmd is intended to target number 1

00 B0 81 00

10

ISO/IEC 14443-4 commands, for example Read 16 bytes command, can be sent with InDataExchange command(3).

Deselect the card 44

01

ISO/IEC 14443-4 command

Command code: InDeselect 45

The cmd is intended to target number 1 00

S(deselect)REQ is sent with InDeselect command.

(1)

SENS_RES and SEL_RES coding is described in ISO/IEC 18092 specification. Please refer to this

document for further details.

(2)

The automatic sending of RATS can be disabled with SetThe PN532Parameters command. Please

refer to the PN532 User manual (cf. References table on page 4).

(3)

the PN532 handles chaining, time out extension, and error handling, according to ISO/IEC 14443-4

protocol.

(4)

Command code and command parameters. Mandatory protocol encapsulation is not represented.

41

00

00 11 22 33 44 55

66 77 88 99 AA BB

CC DD EE FF

90 00

Response command code

Status = 0 (OK, no error)

Response of the card

Response command code

Status = 0 (OK, no error)

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 39 of 75

Page 40

NXP Semiconductors

AN10609_3

PN532 C106 application note

Table 4. The PN532 as a ISO/IEC 1443-4 reader. Type B card activation (timeslot method)

Action Command

Scan for 1 target

in the field and

initialize it

Type B card is activated. The default method used is the timeslot approach.

4A

01

03

00

4

Command explanation Response Response explanation

Command code: InListPassivTargets

Number of cards to initialize (if present

in the field) = 1

Baud rate = 106 kbits/sec Type B.

AFI

No other parameter : default timeslot

method will be used.

4B

01

01

50 01 02 03 04 00

00 00 00 00 00 00

01

01

Response command code

1 target detected

Target number 1

ATQB_RES (12 bytes)

ATTRIB_RES length

ATTRIB_RES

Read 16 bytes 40 Command code: InDataExchange 41

01 The cmd is intended to target number 1 00

94 A4 00 00

02 3F 00

ISO/IEC 14443-4 commands, for exampleSelect File with CD light card, can be sent with InDataExchange command(3).

Deselect the card 44 Command code: InDeselect 45 Response command code

01 The cmd is intended to target number 1 00 Status = 0 (OK, no error)

ISO/IEC 14443-4 command 85 17 00 01 00 00

00 10 10 00 00 01

03 00 00 00 7E 7E

7E 00 00 00 00 00

00 90 00

S(deselect)REQ is sent with InDeselect command.

Response command code

Status = 0 (OK, no error)

Response of the card

Table 5. The PN532 as a ISO/IEC 1443-4 reader. Type B card activation (probabilistic polling method)

Action Command

Scan for 1 target

in the field and

initialize it

4A Command code: InListPassivTargets

01 Number of cards to initialize (if present

03 Baud rate = 106 kbits/sec Type B.

00 AFI

01 Method = 01: probabilistic polling

4

Command explanation Response Response explanation

in the field) = 1

method will be used

4B

01

01

50 01 02 03 04 00

00 00 00 00 00 00

01

01

Response command code

1 target detected

Target number 1

ATQB_RES (12 bytes)

ATTRIB_RES length

ATTRIB_RES

Type B card is activated. The method used is the probabilistic approach.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 40 of 75

Page 41

NXP Semiconductors

PN532 C106 application note

3.3.2.1 Timeout and number of retries Activation phase (InListPassiveTarget command)

By default, the PN532 is configured to retry to detect a card as long as there is no

card detected. It can be changed using RFConfiguration command, item 5

(MaxRtyPassiveActivation parameter). The command is described in reference 1.

If there is no card in the field, a timeout occurs after 5 ms. Either the PN532 retries to

find a card, if MaxRtyPassiveActivation > 1, or it sends a response to its host

controller, indicating that zero target has been found.

Communication phase (InDataExchange command)

It depends on value returned by the card (FWT), as specified in ISO/IEC 14443-3

and -4. The waiting time extension mechanism is fully embedded inside the PN532.

The error handling and the chaining are also fully managed by the PN532.

Deactivation phase (InDeselect/InRelease command)

InDeselect or InRelease commands perform a S(Deselect) request.

AN10609_3

Note: It is not needed to use InDeselect (and InSelect) command to handle two

cards. Indeed, when using InDataExchange command, the PN532 automatically

wakes up the card corresponding to the desired TgNb, and automatically put in

HALT state the other one.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 41 of 75

Page 42

NXP Semiconductors

AN10609_3

PN532 C106 application note

3.3.3 How to use the PN532 as a DESfire cards reader?

DESfire cards can be read/write as other ISO/IEC 1443-4 cards.

Table 6. The PN532 as a DESfire card reader

Action Command

Scan for 1 target

in the field and

initialize it

01

00

4

Command explanation Response Response explanation

Command code: InListPassivTargets 4A Response command code

Number of cards to initialize (if present

in the field) = 1

Baud rate = 106 kbits/sec.

4B

01

01

44 03

20

08

88 04 4A 5B 09 2C

1C 80

06 75 77 81 02 80

1 target detected

Target number 1

SENS_RES of target 1

SEL_RES

NFCID1 length = 8 bytes

NFCID1 of target 1

ATS

(1)

(1)

of target 1

Get application ID

Select application

Bit 5 of SEL_RES indicates the target is ISO/IEC 14443-4 compliant.

In that case the PN532 automatically sends the RATS . ATS is indicated in the response.

40

01

6A

DESfire commands, for example GetApplicationID command, can be sent with InDataExchange command .

01

5A 06 00 00

Command code: InDataExchange 41 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

DESfire command: GetApplicationID 00 01 00 00 02 00

Command code: InDataExchange 40 41 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

SelectApplication 06 00 00 00 Response of the card

(2)

00 03 00 00 40 00

00 04 00 00 05 00

00 06 00 00

Response of the card

(3)

3.3.3.1 Timeout and number of retries

Cf. paragraph

3.3.2.1.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 42 of 75

Page 43

NXP Semiconductors

AN10609_3

PN532 C106 application note

3.3.4 How to use the PN532 as a FeliCa reader?

A typical sequence can be:

- Scan for targets (cards) in the field.

- Exchange data with the card.

This typical sequence can be performed with the following commands:

- InListPassivTarget, to initialise one (several) cards (maximum two cards at the

same time)

- InDataExchange, to transfer data/command bytes to the card (The PN532 does

not embed FeliCa protocol: it has to be included in the data bytes).

- InSelect, InDeselect, and InRelease to select, and release the card.

Table 7. The PN532 as a FeliCa reader

Action Command

Scan for 1 target

in the field and

initialize it

4A

01

01

00 FF FF

00 00

1

Command explanation Response Response explanation

Command code: InListPassivTargets Response command code

Number of cards to initialize (if present

in the field) = 1

Baud rate = 212 kbits/sec.

Payload field of polling request

4B

01

01

12

01

01 01 06 01 46 05

C3 1A

04 01 4B 02 4F 49

93 FF

1 target detected

Target number 1

POL_RES length

Response code

NFCID2

PAD

FeliCa™ card has been initialised.

Exchange data

with the card

40

01

06

F0

00 FF AA

BB

The PN532 transfers the data. Len and Cmd bytes of FeliCa™ protocol must be present in the buffer.

Command code: InDataExchange

The cmd is intended to target number 1

Length of data + 2

FeliCa™ command (echo back) 2

Data

(1)

Command code and command parameters. Mandatory protocol encapsulation is not represented.

(2)

Exemple of FeliCa command. Not all the FeliCa cards support this command. Refer to FeliCa card

specification.

41 Response command code

00 Status = 0 (OK, no error)

06 Response of the card

F0

00 FF AA BB

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 43 of 75

Page 44

NXP Semiconductors

PN532 C106 application note

3.3.4.1 Timeout and number of retries Activation phase (InListPassiveTarget command)

By default, the PN532 is configured to retry to detect a card as long as there is no

card detected. It can be changed using RFConfiguration command, item 5

(MaxRtyPassiveActivation parameter). The command is described in reference 1

If there is no card in the field, a timeout occurs after 2.42 ms +(TSN+1)*1.21 ms.

TSN is the Time Slot Number field of the command.

Either the PN532 retries to find a card, if MaxRtyPassiveActivation > 1, or it sends a

response to its host controller, indicating that zero target has been found.

Communication phase (InDataExchange command)

By default, the timeout is set to 51.2 ms. It can be changed using RFConfiguration

command item 2. The command is described in reference 1.

Deactivation phase (InDeselect/InRelease command)

AN10609_3

InDeselect or InRelease commands perform no request. The return status is always

“No error” (00h),

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 44 of 75

Page 45

NXP Semiconductors

AN10609_3

PN532 C106 application note

3.3.5 How to use the PN532 as a Jewel cards reader ?

A typical sequence can be:

- Scan for targets (cards) in the field.

- Exchange data with the card.

This typical sequence can be performed with the following commands:

- InListPassivTarget, to initialise one (several) cards (maximum two cards at the

same time)

- InDataExchange, to transfer data/command bytes to the card

- InSelect, InDeselect, and InRelease to select, and release the card.

Table 8. The PN532 as a Jewel card reader

Action Command

Scan for 1 target

in the field and

initialize it

4A Command code: InListPassivTargets 4B Response command code

01 Number of cards to initialize (if present

04 Baud rate = 106 kbits/sec, type =

1

Command explanation Response Response explanation

in the field) = 1

Innovison Jewel

01 1 target detected

01 Target number 1

04 00 ATQA_RES

92 2E 58 32 Jewel ID

Exchange data

with the card

Jewel card has been initialised.

40

01

00

Command code: InDataExchange

The cmd is intended to target number 1

Command code

The PN532 transfers the data.

41 Response command code

00 Status = 0 (OK, no error)

01..FF Response of the card (exemple : 255

bytes, 01 to FF. Not all bytes are shown

here)

InDataExchange command is used to send the Jewel commands, described in Jewel

documentation.

Jewel command

Command description

code

0x00 Read all bytes

0x01 Read a single byte

0x1A Write-no-Erase a single byte

0x1C Write-no-Erase 8 bytes

0x53 Write-with-Erase a single byte

0x55 Write-with-Erase 8 bytes

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 45 of 75

Page 46

NXP Semiconductors

PN532 C106 application note

AN10609_3

3.3.6 How to use the PN532 as a reader for several types of cards (or targets)?

In case different types of cards can be used to communicate with the PN532 as reader,

InAutopoll command, described in reference 1, allows polling for several types of cards.

The host controller can poll for Mifare cards, FeliCa cards, Jewel cards, ISO/IEC 14443-4

cards, NFC targets.

A maximum of two cards, or one card and one NFC target, can be handled by the PN532

(except in case of FeliCa card, where only one card can be detected with InAutopoll

command).

The latest card/target detected remains in active mode, whereas the first one is put in

HALT/SLEEP state.

The host controller can specify up to 15 different modes to be polled (combining the type

such as Mifare, FeliCa, ISO/IEC 14443-4, Jewel, the baudrate (106, 212 or 424 kbps),

and possible the mode (active or passive) for NFC target).

The host controller also specifies the number of polling to be performed (1 to 254 or

infinite), and the polling period (i.e. the time duration of one polling, per unit of 150 ms).

After InAutoPoll command has been used, the card or the target is ready to communicate

with InDataExchange command.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 46 of 75

Page 47

NXP Semiconductors

PN532 C106 application note

AN10609_3

3.3.7 How to use the PN532 in a NFC peer-to-peer communication?

3.3.7.1 How to use the PN532 as an initiator in a NFC peer-to-peer communication?

Goal: exchange data between two NFC devices.

The host controller of the initiator chooses the mode (active or passive) and the baudrate

of the communication. Same command codes are used whatever the mode (only

parameters are different).

Typical sequence (example 1):

- Initialise and activate a target

- Exchange some data with the target

- Release the target

Another typical sequence (example 2): compared to example 1, initialisation and

activation are done “step by step”:

- Scan for targets in the field

- Activate NFC target

- Perform parameters selection (PSL REQ)

- Exchange some data with the target

Those typical sequences can be performed with the following commands:

- InJumpForDEP, or InJumpForPSL, to initialise and activate the target (active or

passive mode)

OR InListPassivTarget (to initialise), and InATR (to activate) the target (passive

mode only).

- InPSL, to change the baud rate (except if InJumpForDep has been used for

activation)

- InDataExchange, to exchange data with the target (NFCIP-1 transport protocol

fully embedded). Please read also paragraph

- InRelease to release the target (

3.3.7.3 on page 56).

0.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 47 of 75

Page 48

NXP Semiconductors

AN10609_3

PN532 C106 application note

Table 9. The PN532 as a NFC initiator (“reader”) example 1

Action Command

Initialize and

activate a target

Initiator has chosen the active mode. the PN532 performed automatically activation and possibly parameter selection

01

02

01

00 FF FF

00 00

1

Command explanation Response Response explanation

Command code: InJumpForDep 56

Mode (1= active mode)

Baud rate = 424 kbits/sec.

Optional field present (Payload)

Payload field of polling request

(ATR_REQ and possibly PSL_REQ) .

57 Response command code

00

01

AA 99 88 77 66 55

44 33 22 11

00 00 00 09 01 22

(2)

Status (0=no error)

Target number 1

ATR_RES received (except cmd0 and

cmd1 bytes)

Exchange data

with the card

The PN532 transfers the data according to NFCIP-1 transport protocol. Error handling, chaining, time out extension are automatically

Deselect

Select

Release the target

40

01

00 01 02 03

04 05 06 07

08 09 0A

0B 0C 0D

0E 0F

01

01

52

01

Command code: InDataExchange 41 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

Data 99 88 77 Data (Response of the target)

handled.

Command code: InDeselect 44 45 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

DSL_REQ is sent with InDeselect command.

Command code: InSelect 54 55 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

WUP_REQ is sent with InSelect command.

Command code: InRelease 53 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

RLS_REQ is sent with InRelease command.

(1)

Command code and command parameters. Mandatory protocol encapsulation is not represented.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 48 of 75

Page 49

NXP Semiconductors

AN10609_3

PN532 C106 application note

(2)

Would passive mode have been chosen by the initiator, the PN532 would have performed initialisation

(POL_REQ at 212/424 kbits/sec or SENS_REQ, SDD, SEL_REQ at 106 kbits/sec), plus activation

(ATR_REQ) and possible parameter selection (PSL_REQ).

Table 10. The PN532 as NFC initiator (“reader”) example 2

Action Command

Scan for 1 target

in the field and

initialize it

01

02

00 FF FF

00 00

1

Command explanation Response Response explanation

Command code: InListPassivTargets 4A

Number of cards to initialize (if present

in the field) = 1

Baud rate = 212 kbits/sec.

Payload field of polling request

4B Response command code

01

01

12

01

01 FE A2 A3 A4

A5 A6 A7

C0 C1 C2 C3 C4

C5 C6 C7

1 target detected

Target number 1

POL_RES length

Response code

NFCID2

PAD

Activate the target

Change

parameters

Exchange data

with the card

The target has been initialised (in passive mode) at the requested baud rate.

Command code: InATR 50 51

01 00

4E

01

00 00

40

01

00 01 02 03

04 05 06 07

08 09 0A

0B 0C 0D

0E 0F

The cmd is intended to target number 1

The target has been activated.

Command code: InPSL 4F Response command code

The cmd is intended to target number 1 Status = 0 (OK, no error)

New baud rate = 106 kbits/sec

The baud rate has been changed.

Command code: InDataExchange 41 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

Data 99 88 77 Data (Response of the target)

AA 99 88 77 66 55

44 33 22 11 00 00

00 09 01

00

Response command code

Status = 0 (OK, no error)

The PN532 transfers the data according to NFCIP-1 transport protocol. Error handling, chaining, time out extension are automatically

handled.

Release the target

01

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 49 of 75

Command code: InRelease 52 53 Response command code

The cmd is intended to target number 1 00 Status = 0 (OK, no error)

RLS_REQ is sent with InRelease command.

Page 50

NXP Semiconductors

AN10609_3

PN532 C106 application note

(1)

Command code and command parameters. Mandatory protocol encapsulation is not represented.

<DOC_ID> © NXP B.V. 2006. All rights reserved.

Application note Rev. 1.2 — 1/14/2010 50 of 75

Page 51

NXP Semiconductors

PN532 C106 application note

About PSL (Parameter Selection)

When using InJumpForDEP command, the PN532 performs autom atically PSL_REQ

if the target indicates a Length Reduction value corresponding to a buffer greater

than 64 bytes. But the actual LR used remains 64 bytes since the PN532 does not

support more. Moreover, the baudrate is not changed automatically.

However, as defined in NFCIP-1 specification, further PSL_REQ sending is not

allowed. Consequently, if the user wants to change the baudrate (in reception and in

transmission), he has to use InJumpForPSL command, followed by InPSL

command.

About InDeselect command

During Data Exchange Protocol (as defined in NFCIP-1), the host controller can use

this command to resynchronise target packet numbers (PNI).

Example:

The initiator sends InDataExchange command, an error is returned. Maybe the PNI

of the response is incorrect. The initiator sends InDeselect command followed by

InDataExchange. The PNI are re-synchronised.

AN10609_3

Timeout and number of retries

• Initialization phase in passive mode (InListPassiveTarget, InJumpForDEP

in passive, InJumpForPSL in passive)

By default, the PN532 is configured to retry to detect a card as long as there is no

target detected. It can be changed using RFConfiguration command, item 5

(MaxRtyPassiveActivation parameter).

The timeout depends on the baudrate. At 106 kbps, paragraph

424 kbps, paragraph

Either the PN532 retries to find a card, if MaxRtyPassiveActivation > 1, or it sends a

response to its host controller, indicating that zero target has been found.

• Activation phase in passive mode (InATR)

The default timeout is set to 102.4 ms. It can be changed using RFConfiguration

command item 2.

By default, the PN532 is configured to retry an infinite number of times in case no

targets are responding. It can be changed using RFConfiguration command, item 5

(MaxRtyATR parameter).