Page 1

A B

D

HGFEC

P25Z PG611 A00

12GB GDDR5X, 384b, 256Mx32

1

TALL DVI-D + DP + DP + HDMI/DP + DP

TABLE OF CONTENTS

Page

2

3

4

Description

1

Table of Contents

2

BLOCK DIAGRAM

3

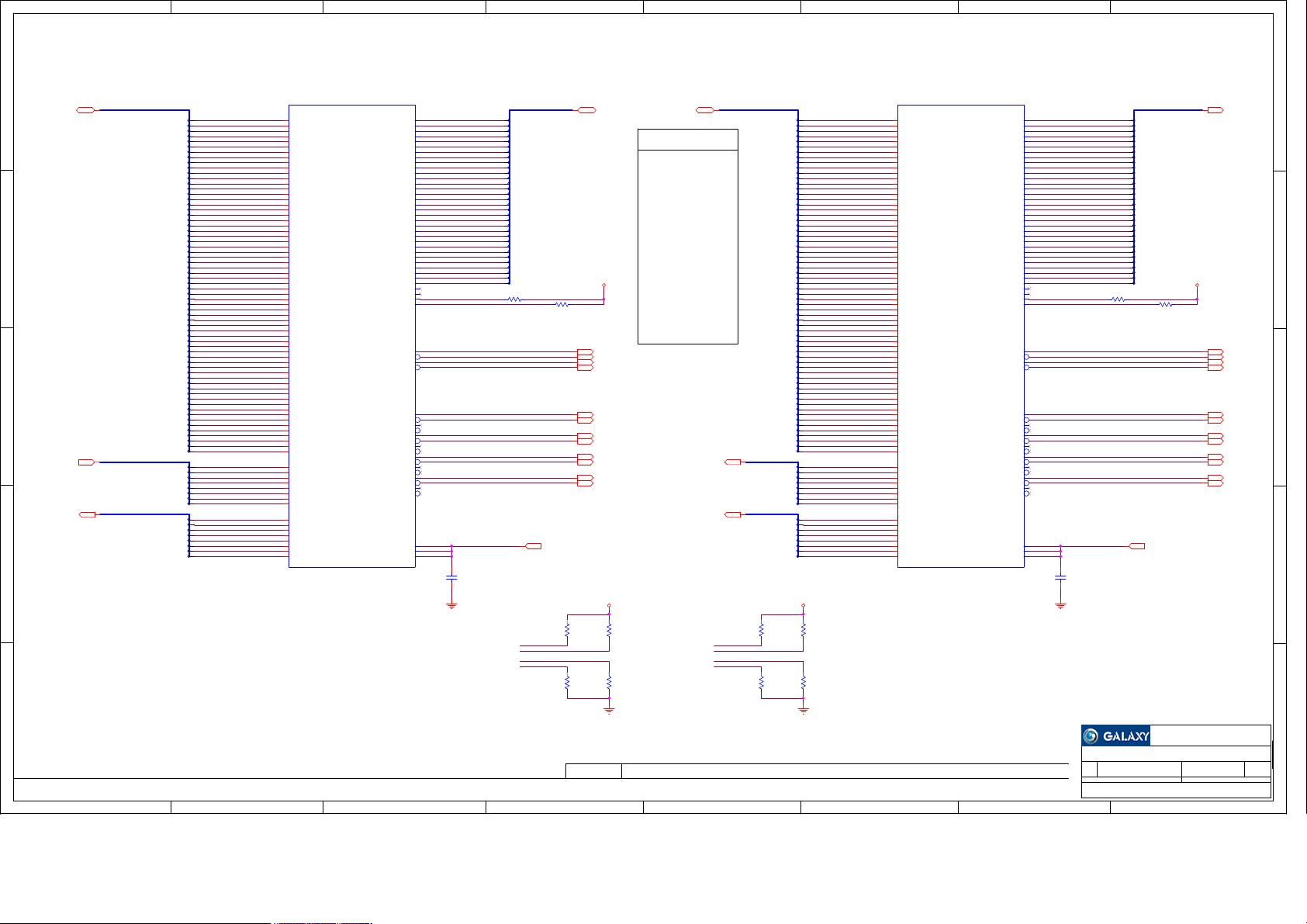

PCI EXPRESS

4

MEMORY: GPU PARTITION A/B

MEMORY: FBA PARTITION[31:0]

5

6

MEMORY: FBA PARTITION[63:32]

MEMORY: FBB PARTITION[31:0]

7

MEMORY: FBB PARTITION[63:31]

8

MEMORY: GPU PARTITION C/D

9

MEMORY: FBC PARTITION[31:0]

10

MEMORY: FBC PARTITION[63:32]

11

MEMORY: FBD PARTITION[31:0]

12

MEMORY: FBD PARTITION[63:32]

13

MEMORY: GPU PARTITION E/F

14

MEMORY: FBE PARTITION[31:0]15

MEMORY: FBE PARTITION[63:32]

16

MEMORY: FBF PARTITION[31:0]

17

MEMORY: FBF PARTITION[63:32]

18

GPU PWR AND GND

19

20

GPU DECOUPLING

21

IFPAB DVI-D-DL

22

IFPE DP

23

IFPF DP

24

IFPC HDMI/DP

25

IFPD DP

Page

Description

26

MIOA/B INTERFACE & FRAME LOCK

27

MISC: FAN, THERMAL, JTAG, GPIO, STEREO

28

MISC: ROM, STRAPS

29

MISC: XTAL, PLL

30

PS: 5V, PEXVDD

31

PS: 1V8 Rails

32

PS: FBVDDQ

33

PS: NVVDD Controller_OVR8

34

PS: NVVDD Controller_PWR-MODULE

35

PS: NVVDD Phase 1, 2

36

PS: NVVDD Phase 3, 4

37

PS: NVVDD Phase 5

38

PS: NVVDD Phase 6, 7

39

PS: Dynamic power balance phase

40

PS: Dynamic power balance logic

41

PS: Input, filtering, and Monitoring

42

PS: Current Sterring, Hot Unplug

43

PS: NVVDD ENABLE

44

PS: GC6 MISC

45

GEFORCE LED AND SLI LED

46

PS: NV3V3, NV12V

PS: MCU47

48

MECH

49

VR Thermal Protection

1

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B D F H

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

Table of Contents

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

EC

G

Galaxy Microsystems (HK) Ltd.

Table of Contents

Table of Contents

Table of Contents

Design By:

Design By:

P25Z

P25Z

P25Z

Design By:

Neston V10

Neston V10

Neston V10

152Friday, March 03, 2017

152Friday, March 03, 2017

152Friday, March 03, 2017

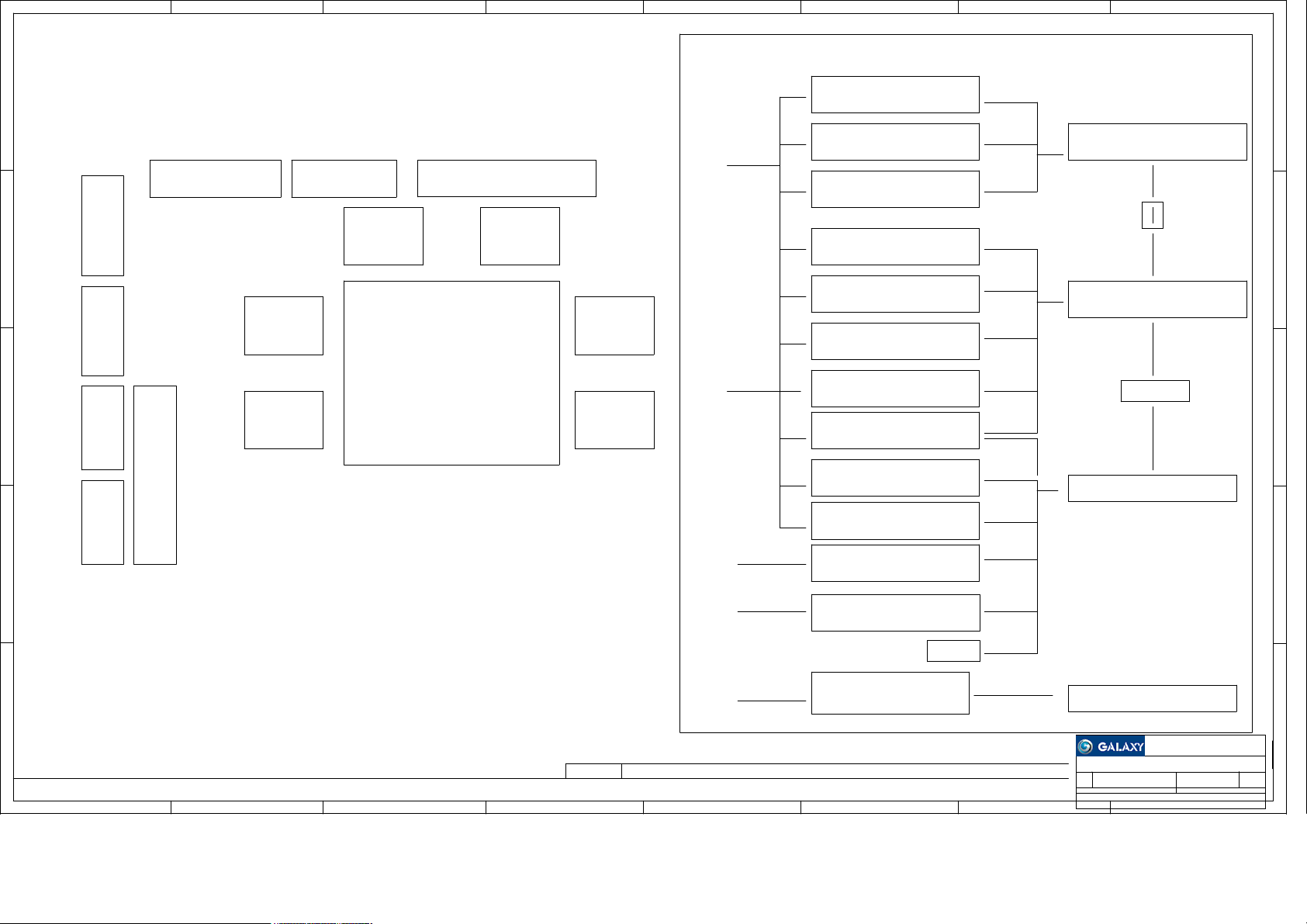

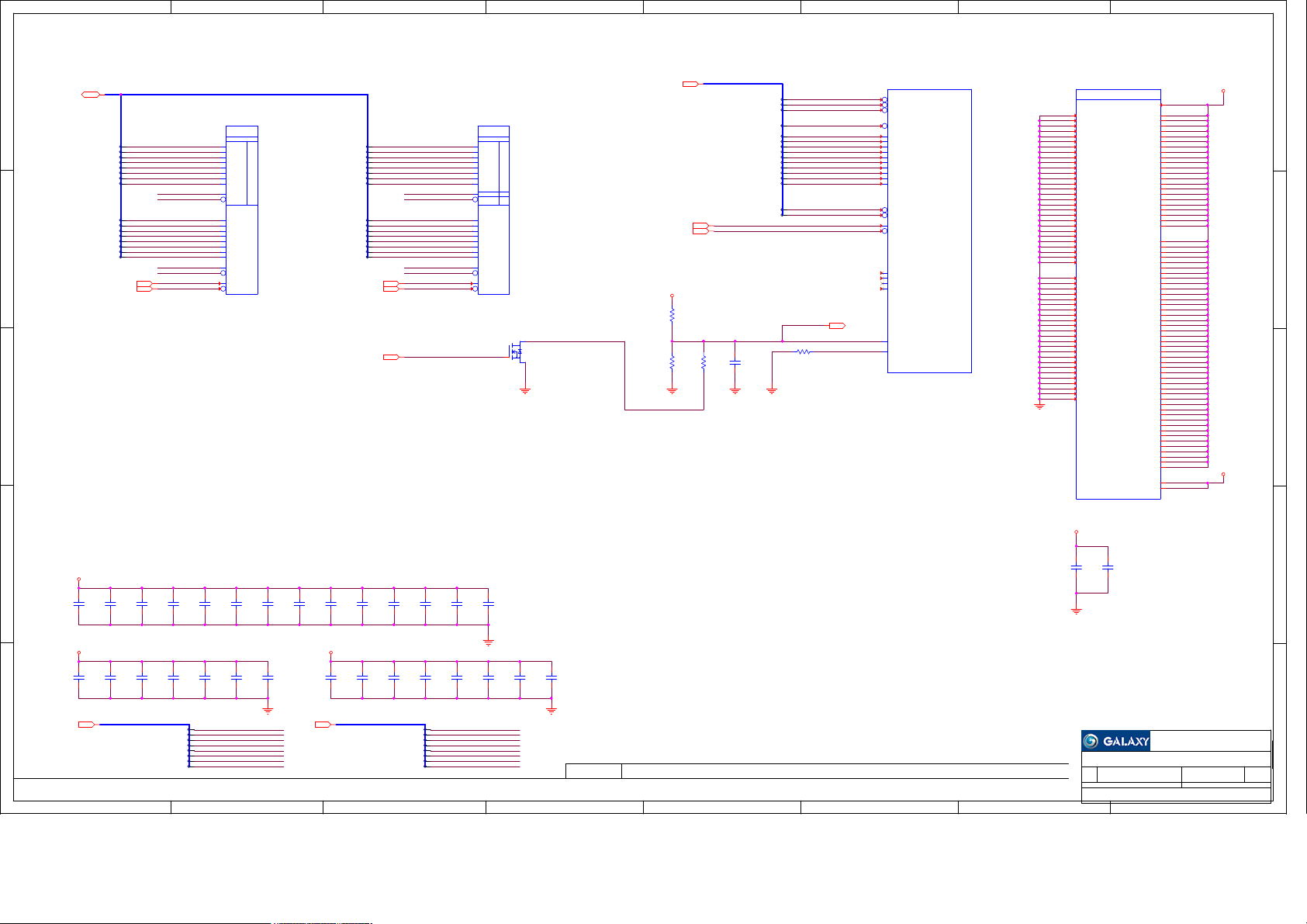

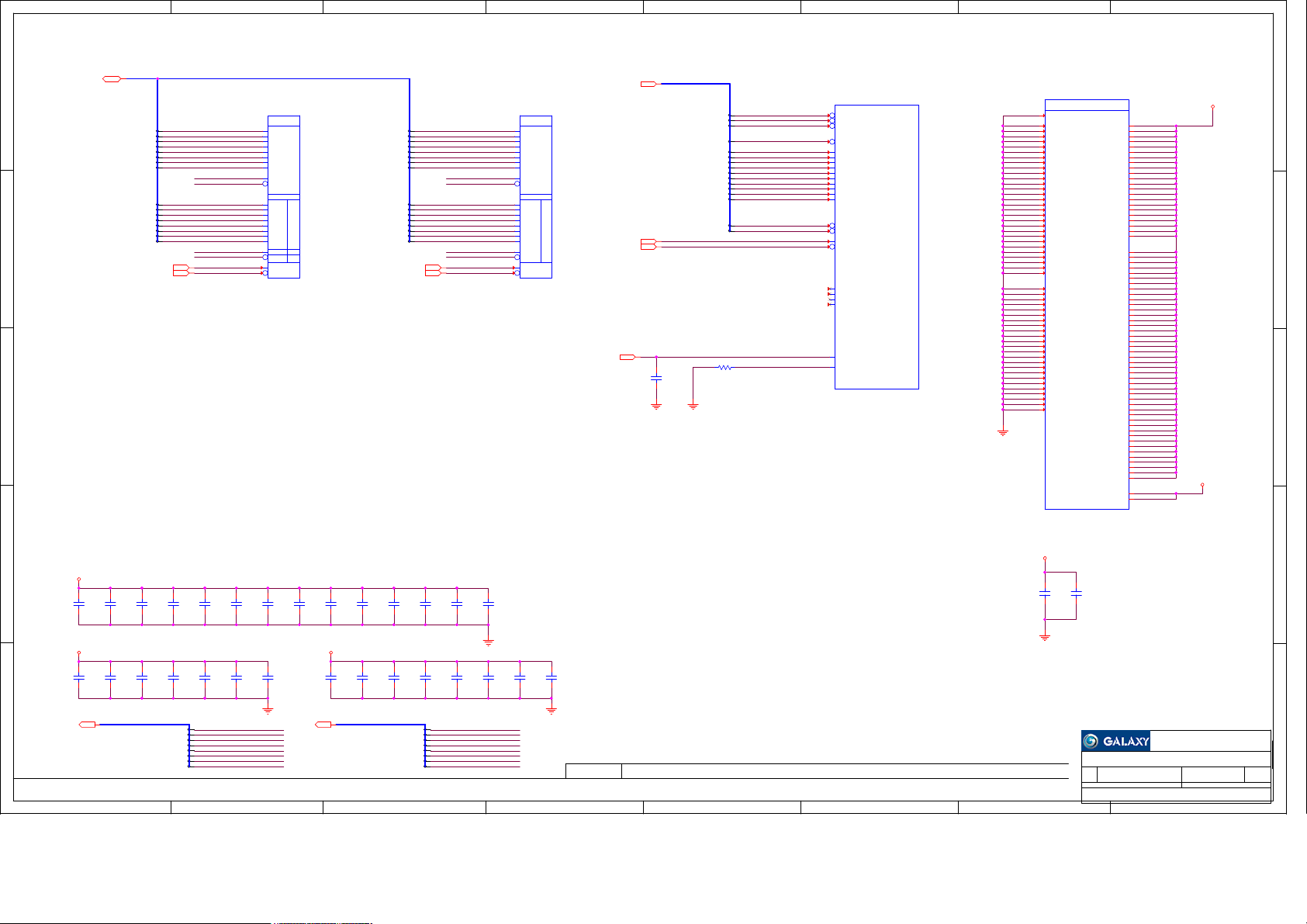

Page 2

A B C D E F G H

Page2: Block Diagram

1

NVVDD

SLI

STEREO

FRAME LOCK

Power Supply

NVVDD-PH2

Power Supply

NVVDD-PH3

Power Supply

1

EXT_12V 2x3 PWR 1

DYNAMIC NVVDD-PH4

MEM

2

DP/HDMI DP

MEM

E

D MEM C

MEM

Power Supply

NVVDD-PH4

Power Supply

NVVDD-PH5

EXT_12V 2x4 PWR 2

B

Power Supply

STUFF OPTION

2

DYNAMIC NVVDD-PH1

GP102

FBVDDQ

3

MEM

F

MEM A

DP

DVI-D

DP

4

1V8

Power Supply

FBVDD/Q PH1&PH2

Power Supply

NVVDD-PH7

Power Supply

NVVDD-PH6

Power Supply

NVVDD-PH1

Power Supply

1V8

STEER

PEX_12V Finger

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

BLOCK DIAGRAM

5V

PEX_VDD

Power Supply

5V SWITCHER

Power Supply

PEX_VDD

FAN

OVREG

FDBA

PEX_3V3 Finger

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet of

Date: Sheet of

Date: Sheet of

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

G

Galaxy Microsystems (HK) Ltd.

Block Diagram

Block Diagram

Block Diagram

P25Z

P25Z

P25Z

Design By:

Design By:

Design By:

H

Neston V10

Neston V10

Neston V10

252Friday, March 03, 2017

252Friday, March 03, 2017

252Friday, March 03, 2017

5

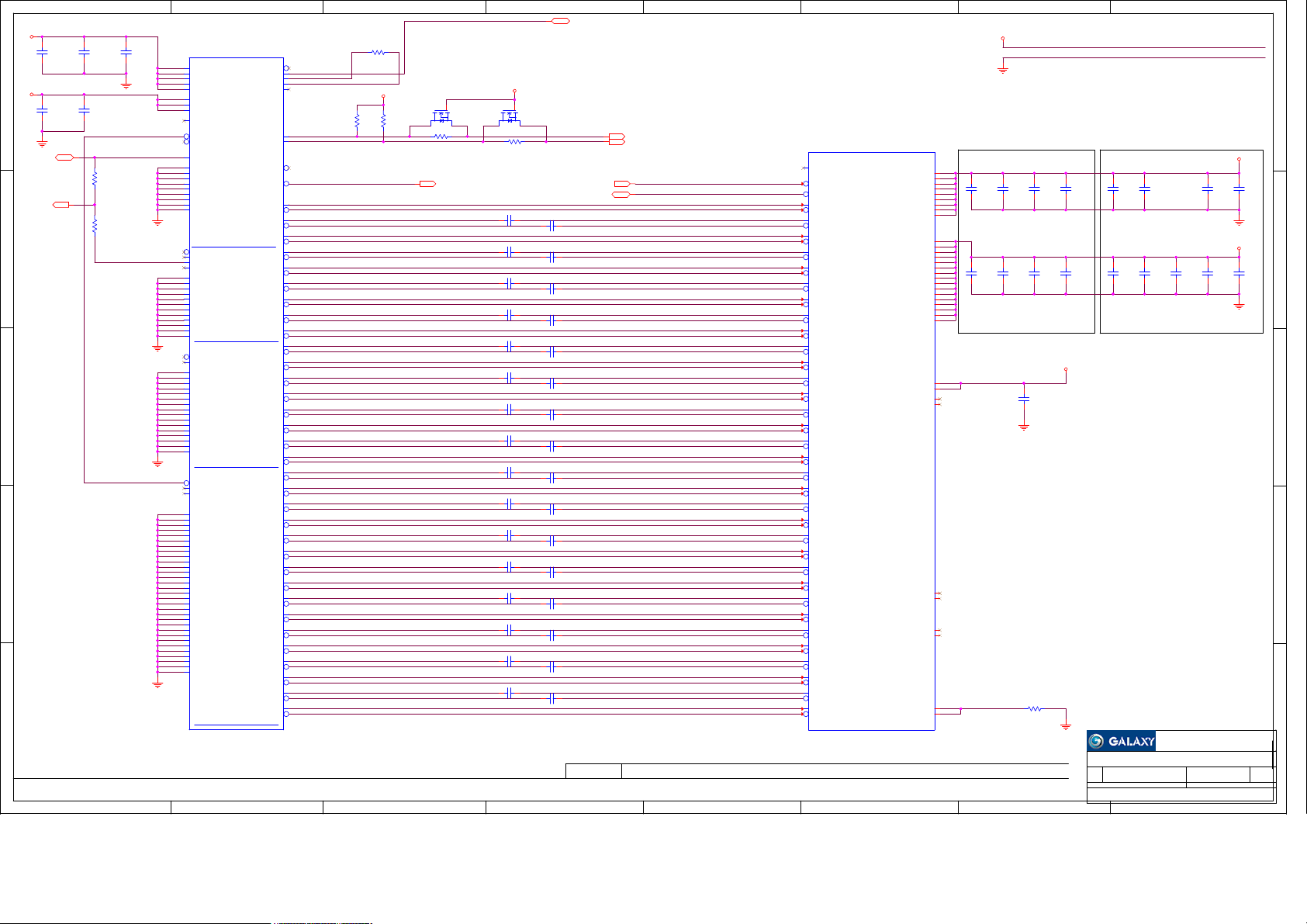

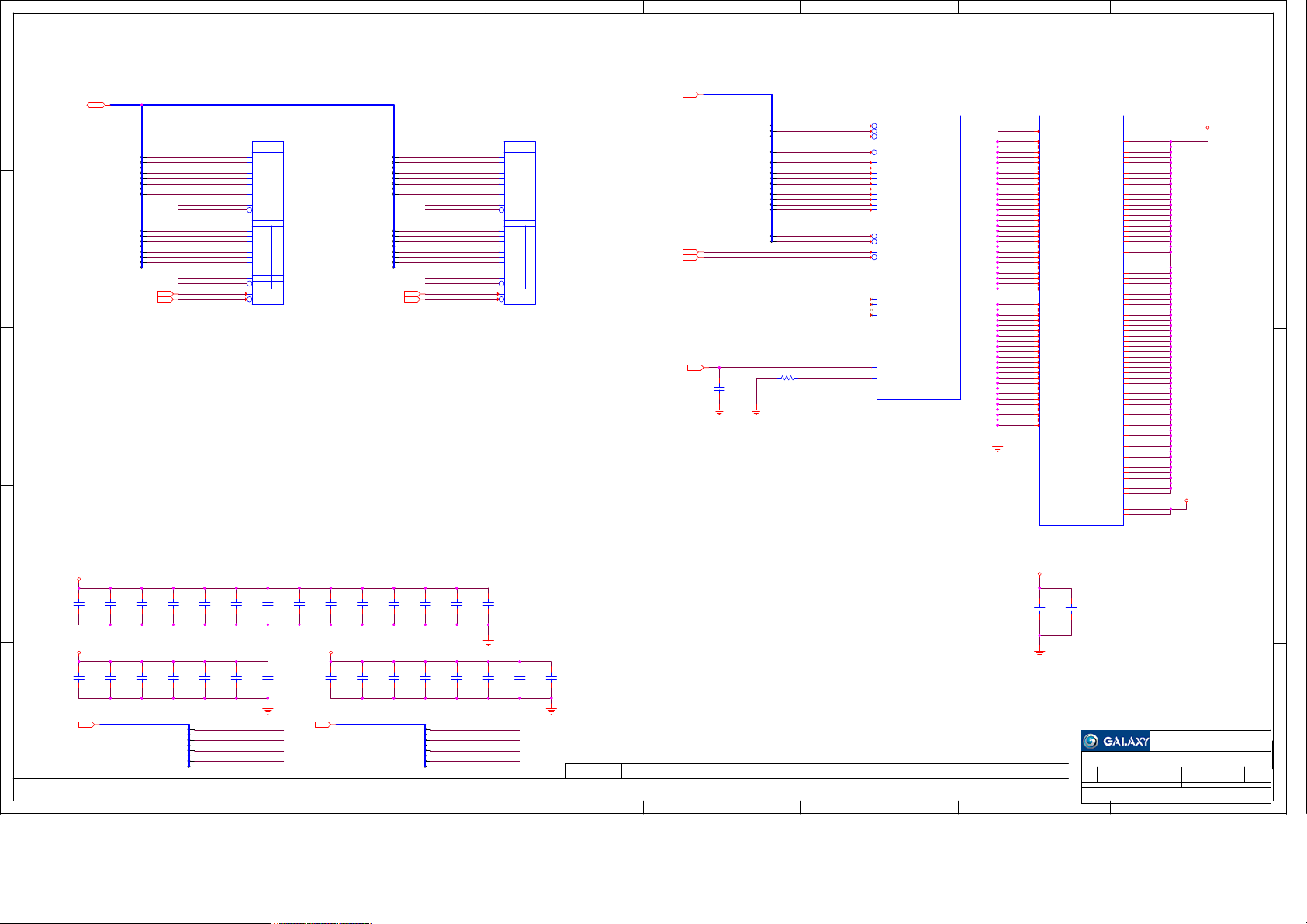

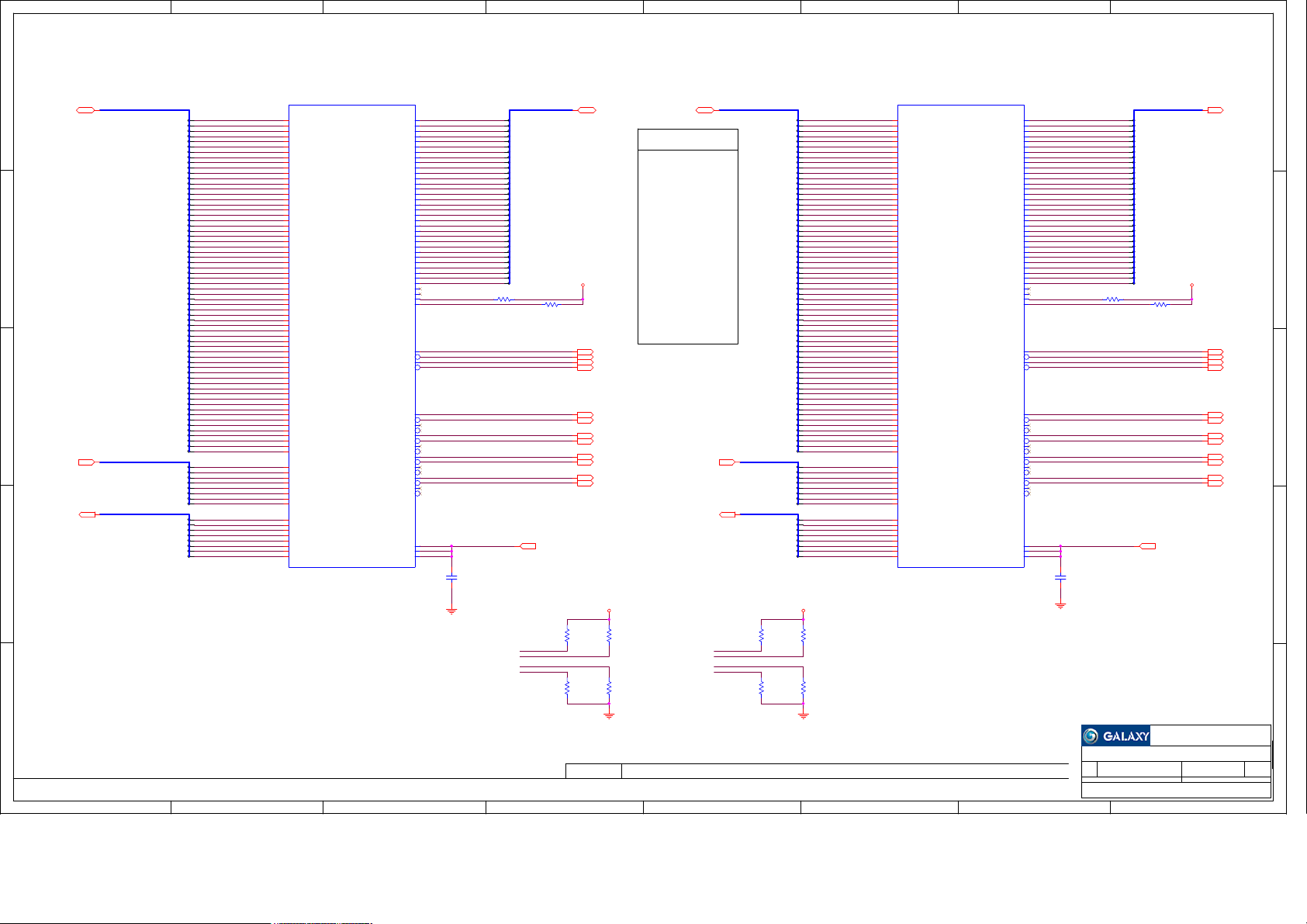

Page 3

nv_cap

Page3: PCI Express

12V

3V3

1

0603

GND

2

3

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

A B C D E F G H

C1317

10uF/16V

16V

20%

X6S

0805

C62

4.7uF

6.3V

20%

X6S

nv_cap

GND

GND

GND

GND

B1

B2

A2

A3

B3

B8

A9

A10

B10

A1

B17

B12

B4

A4

B7

A12

B13

A15

B16

B18

A18

B31

A19

B30

A32

A20

B21

B22

A23

A24

B25

B26

A27

A28

B29

A31

B32

B48

A33

A34

B35

B36

A37

A38

B39

B40

A41

A42

B43

B44

A45

A46

B47

B49

A49

B81

A50

B82

A51

B52

B53

A54

A55

B56

B57

A58

A59

B60

B61

A62

A63

B64

B65

A66

A67

B68

B69

A70

A71

B72

B73

A74

A75

B76

B77

A78

A79

B80

A82

CON_FINGER_PEX_164

CN2

CON_X16

@electro_mechanic.con_pci_express(sym_1):page3_i243

+12V

+12V

+12V

+12V

+12V/RSVD

+3V3

+3V3

+3V3

+3V3AUX

PRSNT1

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

PRSNT2

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

TRST* JTAG1

END OF X1

END OF X4

END OF X8

PRSNT2

RSVD

RSVD

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

GND

END OF X16

N/A

TCLK JTAG2

TDI JTAG3

TDO JTAG4

TMS JTAG5

SMCLK

SMDAT

PERST

REFCLK

REFCLK

PERP0

PERN0

PETP0

PETN0

PERP1

PERN1

PETP1

PETN1

PERP2

PERN2

PETP2

PETN2

PERP3

PERN3

PETP3

PETN3

PERP4

PERN4

PETP4

PETN4

PERP5

PERN5

PETP5

PETN5

PERP6

PERN6

PETP6

PETN6

PERP7

PERN7

PETP7

PETN7

PERP8

PERN8

PETP8

PETN8

PERP9

PERN9

PETP9

PETN9

PERP10

PERN10

PETP10

PETN10

PERP11

PERN11

PETP11

PETN11

PERP12

PERN12

PETP12

PETN12

PERP13

PERN13

PETP13

PETN13

PERP14

PERN14

PETP14

PETN14

PERP15

PERN15

PETP15

PETN15

R891 0ohm

0.05 ohm

B9

PEX_TCLK

A5

A6

PEX_TDI

PEX_TDO

A7

A8

PEX_SMCLK

B5

PEX_SMDAT

B6

B11

WAKE

PEX_RST* PEX_RST_BUF*

A11

PEX_REFCLK

A13

PEX_REFCLK*

A14

PEX_TXX0

A16

PEX_TXX0*

A17

PEX_RX0

B14

PEX_RX0*

B15

PEX_TXX1

A21

PEX_TXX1*

A22

PEX_RX1

B19

PEX_RX1*

B20

PEX_TXX2

A25

PEX_TXX2*

A26

PEX_RX2

B23

PEX_RX2*

B24

PEX_TXX3

A29

PEX_TXX3*

A30

PEX_RX3

B27

PEX_RX3*

B28

PEX_TXX4

A35

PEX_TXX4*

A36

PEX_RX4

B33

PEX_RX4*

B34

PEX_TXX5

A39

PEX_TXX5*

A40

PEX_RX5

B37

PEX_RX5*

B38

PEX_TXX6

A43

PEX_TXX6*

A44

PEX_RX6

B41

PEX_RX6*

B42

PEX_TXX7

A47

PEX_TXX7*

A48

PEX_RX7

B45

PEX_RX7*

B46

PEX_TXX8

A52

PEX_TXX8*

A53

PEX_RX8

B50

PEX_RX8*

B51

PEX_TXX9

A56

PEX_TXX9*

A57

PEX_RX9

B54

PEX_RX9*

B55

PEX_TXX10

A60

PEX_TXX10*

A61

PEX_RX10

B58

PEX_RX10*

B59

PEX_TXX11

A64

PEX_TXX11*

A65

PEX_RX11

B62

PEX_RX11*

B63

PEX_TXX12

A68

PEX_TXX12*

A69

PEX_RX12

B66

PEX_RX12*

B67

PEX_TXX13

A72

PEX_TXX13*

A73

PEX_RX13

B70

PEX_RX13*

B71

PEX_TXX14

A76

PEX_TXX14*

A77

PEX_RX14

B74

PEX_RX14*

B75

PEX_TXX15

A80

PEX_TXX15*

A81

PEX_RX15

B78

PEX_RX15*

B79

0402

3V3

R898

R897

100k/NC

100k/NC

5 %

5 %

0402

0402

OUT

PEX_REFCLK PEXGEN3_SIGNALS

PEX_TXC0 PEXGEN3_SIGNALS

PEX_RX0 PEXGEN3_SIGNALS

PEX_RX0 PEXGEN3_SIGNALS

PEX_RX1 PEXGEN3_SIGNALS

PEX_TXC2 PEXGEN3_SIGNALS

PEX_TXC2 PEXGEN3_SIGNALS

PEX_RX2 PEXGEN3_SIGNALS

PEX_RX2 PEXGEN3_SIGNALS

PEX_TXC3 PEXGEN3_SIGNALS

PEX_TXC3 PEXGEN3_SIGNALS

PEX_TXC4 PEXGEN3_SIGNALS

PEX_TXC5 PEXGEN3_SIGNALS

PEX_RX5 PEXGEN3_SIGNALS

PEX_TXC6 PEXGEN3_SIGNALS

PEX_TXC6 PEXGEN3_SIGNALS

PEX_RX6 PEXGEN3_SIGNALS

PEX_TXC7 PEXGEN3_SIGNALS

PEX_TXC7 PEXGEN3_SIGNALS

PEX_RX7 PEXGEN3_SIGNALS

PEX_TXC8 PEXGEN3_SIGNALS

PEX_TXC8 PEXGEN3_SIGNALS

PEX_RX8 PEXGEN3_SIGNALS

PEX_TXC10 PEXGEN3_SIGNALS

PEX_TXC10 PEXGEN3_SIGNALS

PEX_TXC11 PEXGEN3_SIGNALS

PEX_TXC12 PEXGEN3_SIGNALS

PEX_TXC12 PEXGEN3_SIGNALS

PEX_RX12 PEXGEN3_SIGNALS

PEX_TXC13 PEXGEN3_SIGNALS

PEX_TXC13 PEXGEN3_SIGNALS

PEX_RX13 PEXGEN3_SIGNALS

PEX_TXC14 PEXGEN3_SIGNALS

PEX_TXC14 PEXGEN3_SIGNALS

PEX_RX14 PEXGEN3_SIGNALS

PEX_TXC15 PEXGEN3_SIGNALS

PEX_TXC15 PEXGEN3_SIGNALS

PEX_RX15 PEXGEN3_SIGNALS

PEXGEN3_SIGNALSPEX_REFCLK

PEXGEN3_SIGNALSPEX_TXC0

PEXGEN3_SIGNALSPEX_TXC1

PEXGEN3_SIGNALSPEX_TXC1

PEXGEN3_SIGNALSPEX_RX1

PEXGEN3_SIGNALSPEX_RX3

PEXGEN3_SIGNALSPEX_RX3

PEXGEN3_SIGNALSPEX_TXC4

PEXGEN3_SIGNALSPEX_RX4

PEXGEN3_SIGNALSPEX_RX4

PEXGEN3_SIGNALSPEX_TXC5

PEXGEN3_SIGNALSPEX_RX5

PEXGEN3_SIGNALSPEX_RX6

PEXGEN3_SIGNALSPEX_RX7

PEXGEN3_SIGNALSPEX_RX8

PEXGEN3_SIGNALSPEX_TXC9

PEXGEN3_SIGNALSPEX_TXC9

PEXGEN3_SIGNALSPEX_RX9

PEXGEN3_SIGNALSPEX_RX9

PEXGEN3_SIGNALSPEX_RX10

PEXGEN3_SIGNALSPEX_RX10

PEXGEN3_SIGNALSPEX_TXC11

PEXGEN3_SIGNALSPEX_RX11

PEXGEN3_SIGNALSPEX_RX11

PEXGEN3_SIGNALSPEX_RX12

PEXGEN3_SIGNALSPEX_RX13

PEXGEN3_SIGNALSPEX_RX14

PEXGEN3_SIGNALSPEX_RX15

5

G

D

3

Q_FET_N_ENH/NC

R244

0.05 ohm

SC70_6

0402

Q35B

@discrete.q_fet_n_enh(sym_7):page3_i280

S

4

0ohm/NC

C E

C1316

C1278

4.7uF

0.1uF

16V

16V

10%

20%

X7R

X6S

0603_LARGE

0402

GND

C64

0.1uF

16V

10%

X7R

PEX_CONN_B12

R874

0ohm/NC

0.05 ohm

0402

POWER_BRAKE*

R875

0ohm/NC

0.05 ohm

0402

PEX_RSVD4_POWER_BRAKE

PEX_PRSNT*

0402

BI

OUT

{47}

PEX_TCLK

NV3V3

2

G

D

6

Q_FET_N_ENH/NC

R237

SC70_6

0.05 ohm

0402

C1202

0.22uF

6.3V

X7R

C0402

C1184

0.22uF

6.3V

X7R

C0402

C1177

0.22uF

6.3V

X7R

C0402

C1170

0.22uF

6.3V

X7R

C0402

C1157

0.22uF

6.3V

X7R

C0402

C980

0.22uF

6.3V

X7R

C0402

C961

0.22uF

6.3V

X7R

C0402

C940

0.22uF

6.3V

X7R

C0402

C918

0.22uF

6.3V

X7R

C0402

C893 0.22uF

6.3V

X7R

C0402

C889 0.22uF

6.3V

X7R

C0402

C882 0.22uF

6.3V

X7R

C0402

C878

0.22uF

6.3V

X7R

C0402

C876

0.22uF

6.3V

X7R

C0402

C872

0.22uF

6.3V

X7R

C0402

C865

0.22uF

6.3V

X7R

C0402

Q35A

@discrete.q_fet_n_enh(sym_7):page3_i279

S

1

0ohm/NC

{47}

{47}

C1203 0.22uF

C0402

C1185

C0402

C1178 0.22uF

C0402

C1171

C0402

C1158

C0402

C972 0.22uF

C0402

C950 0.22uF

C0402

C934 0.22uF

C0402

C902

C0402

C892

C0402

C885

C0402

C879

C0402

C877

C0402

C875

C0402

C866

C0402

C863

C0402

6.3V

0.22uF

6.3V

6.3V

0.22uF

6.3V

0.22uF

6.3V

6.3V

6.3V

6.3V

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V

0.22uF

6.3V

BI

I2CS_SCL_R

I2CS_SDA_R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

X7R

ASSEMBLY

PAGE DETAIL

{47}

OUT

OUT

IN

BI

PEX_TXC0 PEXGEN3_SIGNALS

PEX_TXC0 PEXGEN3_SIGNALS

PEX_TXC1 PEXGEN3_SIGNALS

PEX_TXC2 PEXGEN3_SIGNALS

PEX_TXC5 PEXGEN3_SIGNALS

PEX_TXC6 PEXGEN3_SIGNALS

PEX_TXC7 PEXGEN3_SIGNALS

PEX_TXC7 PEXGEN3_SIGNALS

PEX_TXC8 PEXGEN3_SIGNALS

PEX_TXC8 PEXGEN3_SIGNALS

PEX_TXC9 PEXGEN3_SIGNALS

PEX_TXC10 PEXGEN3_SIGNALS

PEX_TXC11 PEXGEN3_SIGNALS

PEX_TXC11 PEXGEN3_SIGNALS

PEX_TXC12 PEXGEN3_SIGNALS

PEX_TXC12 PEXGEN3_SIGNALS

PEX_TXC13 PEXGEN3_SIGNALS

PEX_TXC13 PEXGEN3_SIGNALS

PEX_TXC14 PEXGEN3_SIGNALS

{27}

{27}

GPU_PEX_CLKREQ*

PEX_TX0

PEX_TX0*

PEX_TX1

PEX_TX1*

PEX_TX2

PEX_TX2*

PEX_TX3

PEX_TX3*

PEX_TX4

PEX_TX4*

PEX_TX5

PEX_TX5*

PEX_TX6

PEX_TX6*

PEX_TX7

PEX_TX7*

PEX_TX8

PEX_TX8*

PEX_TX9

PEX_TX9*

PEX_TX10

PEX_TX10*

PEX_TX11

PEX_TX11*

PEX_TX12

PEX_TX12*

PEX_TX13

PEX_TX13*

PEX_TX14

PEX_TX14*

PEX_TX15

PEX_TX15*

<ASSEMBLY_DESCRIPTION>

PCI EXPRESS

NET MAX_CURRENTVOLTAGE MIN_WIDTH

3V3

3V3

GND

GND

8.5A 0.400

0.4003.0A

1

G1A

@digital.u_gpu_gb3c_384(sym_1):page3_i288

1/24 PCI_EXPRESS

BA32

NC

BD31

PEX_RST

BE32

PEX_CLKREQ

BG40

PEX_REFCLK

BF40

PEX_REFCLK

BJ32

PEX_TX0

BK32

PEX_TX0

BM32

PEX_RX0

BM33

PEX_RX0

BH32

PEX_TX1

PEXGEN3_SIGNALSPEX_TXC1

PEXGEN3_SIGNALSPEX_TXC2

PEXGEN3_SIGNALSPEX_TXC3

PEXGEN3_SIGNALSPEX_TXC3

PEXGEN3_SIGNALSPEX_TXC4

PEXGEN3_SIGNALSPEX_TXC4

PEXGEN3_SIGNALSPEX_TXC5

PEXGEN3_SIGNALSPEX_TXC6

PEXGEN3_SIGNALSPEX_TXC9

PEXGEN3_SIGNALSPEX_TXC10

PEXGEN3_SIGNALSPEX_TXC14

PEXGEN3_SIGNALSPEX_TXC15

PEXGEN3_SIGNALSPEX_TXC15

BG32

PEX_TX1

BM34

PEX_RX1

BN34

PEX_RX1

BG33

PEX_TX2

BF33

PEX_TX2

BN35

PEX_RX2

BN36

PEX_RX2

BK34

PEX_TX3

BJ34

PEX_TX3

BM36

PEX_RX3

BL36

PEX_RX3

BF35

PEX_TX4

BG35

PEX_TX4

BM37

PEX_RX4

BL37

PEX_RX4

BG36

PEX_TX5

BH36

PEX_TX5

BN38

PEX_RX5

BM38

PEX_RX5

BH37

PEX_TX6

BJ37

PEX_TX6

BN39

PEX_RX6

BN40

PEX_RX6

BJ38

PEX_TX7

BK38

PEX_TX7

BM40

PEX_RX7

BL40

PEX_RX7

BG41

PEX_TX8

BH41

PEX_TX8

BM41

PEX_RX8

BL41

PEX_RX8

BH42

PEX_TX9

BJ42

PEX_TX9

BN42

PEX_RX9

BM42

PEX_RX9

BJ43

PEX_TX10

BK43

PEX_TX10

BN43

PEX_RX10

BN44

PEX_RX10

BK44

PEX_TX11

BJ44

PEX_TX11

BM44

PEX_RX11

BM45

PEX_RX11

BF44

PEX_TX12

BG44

PEX_TX12

BM46

PEX_RX12

BN46

PEX_RX12

BG45

PEX_TX13

BH45

PEX_TX13

BN47

PEX_RX13

BN48

PEX_RX13

BJ46

PEX_TX14

BJ47

PEX_TX14

BM48

PEX_RX14

BM49

PEX_RX14

BK47

PEX_TX15

BK48

PEX_TX15

BM50

PEX_RX15

BN50

PEX_RX15

BGA_2397_P090_P085_P080_P100_450X450

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_DVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_HVDD

PEX_PLL_HVDD

PEX_PLL_HVDD

PEX_TERMP

PEX_TERMP

NC

NC

NC

NC

NC

NC

FDBA

Place near balls

BB37

BC37

C933

C923

C925

0402

1005_BGA

C956

0.1uF

16V

10%

X7R

1 %

C917

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

C967

C971

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

1V8_MAIN

2.49k

GND

BC38

1uF

1005_BGA

1005_BGA

50OHM_NETCLASS1

PEX_TERMP

1uF

6.3V

6.3V

10%

10%

X6S

X6S

1005_BGA

C978

C985

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

1005_BGA

1005_BGA

GND

R840

0402

BC39

BC40

BD37

BD38

BD39

BD40

BA33

BA34

BA37

BB33

BB34

BC31

BC32

BC33

BC34

BC35

BC36

BD32

BD33

BD34

BD35

BD36

BB35

BA35

BB32

BC25

BC30

BD42

BB29

BB31

BA36

BB36

G

Place between

GPU and PS

C86

C87

4.7uF

4.7uF

6.3V

6.3V

20%

20%

X6S

X6S

0603

0603

C957

C1017

4.7uF

6.3V

20%

X6S

0603

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

C70

4.7uF

10uF

6.3V

6.3V

20%

10%

X6S

X7R

0603

0805

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

PCI Express

PCI Express

PCI Express

P25Z

P25Z

P25Z

Design By:

Design By:

Design By:

H

0805

0805

PEX_VDD

C88

C89

22uF

22uF

6.3V

6.3V

20%

10%

X6S

X7R

0805

GND

1V8_MAIN

C71

C69

10uF

22uF

6.3V

6.3V

10%

20%

X7R

X6S

0805

GND

Neston V10

Neston V10

Neston V10

of

of

of

352Friday, March 03, 2017

352Friday, March 03, 2017

352Friday, March 03, 2017

2

3

4

5

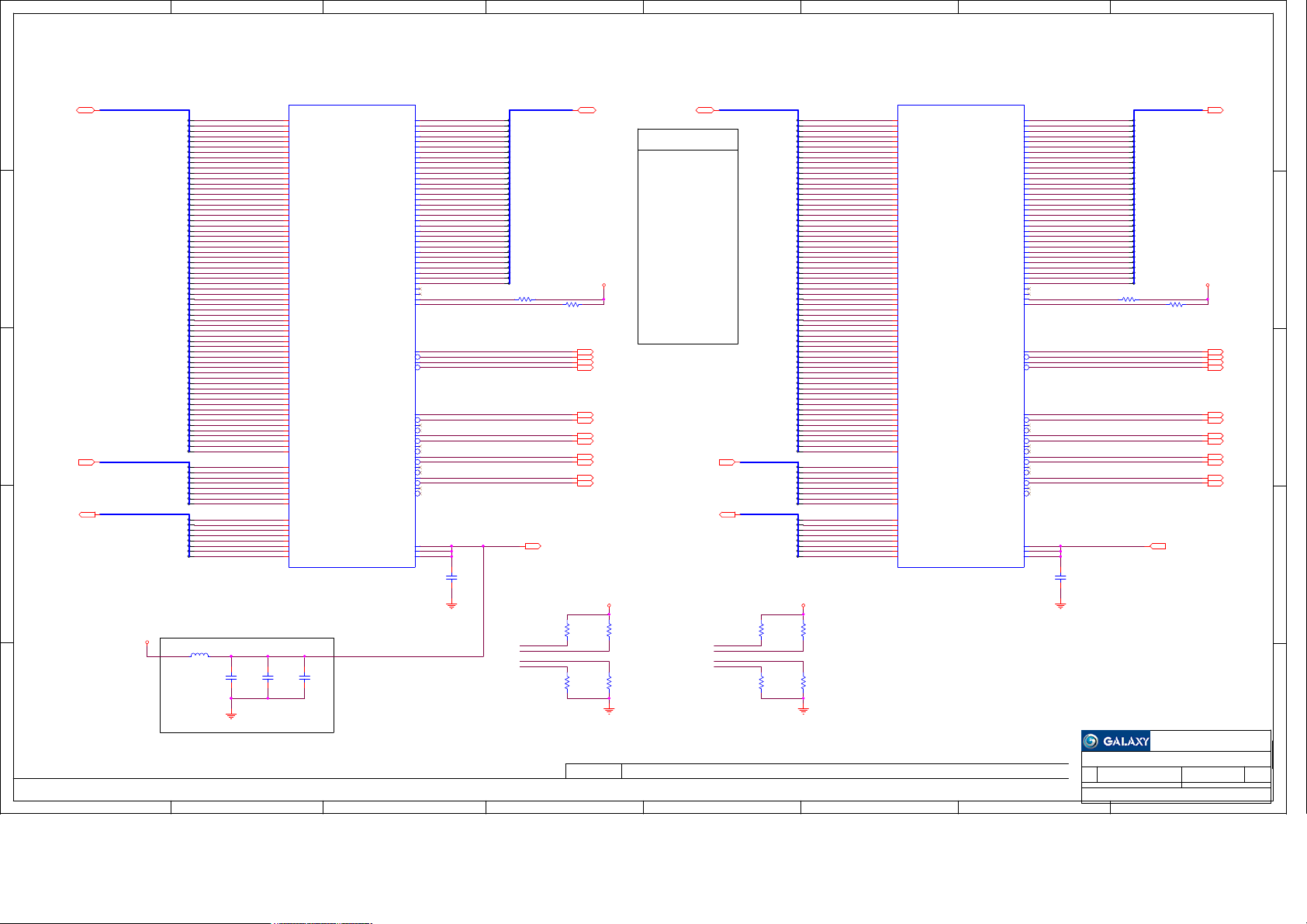

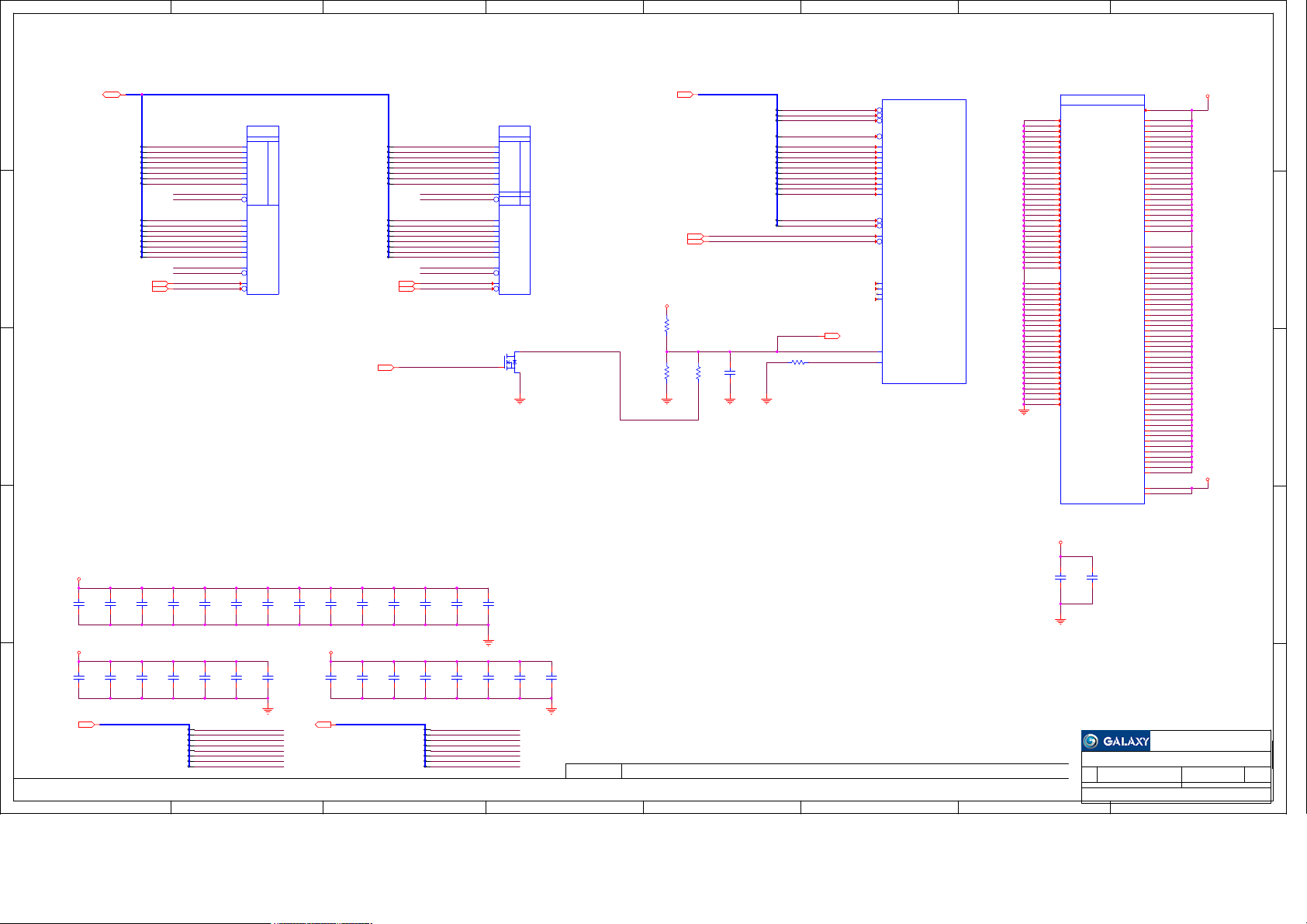

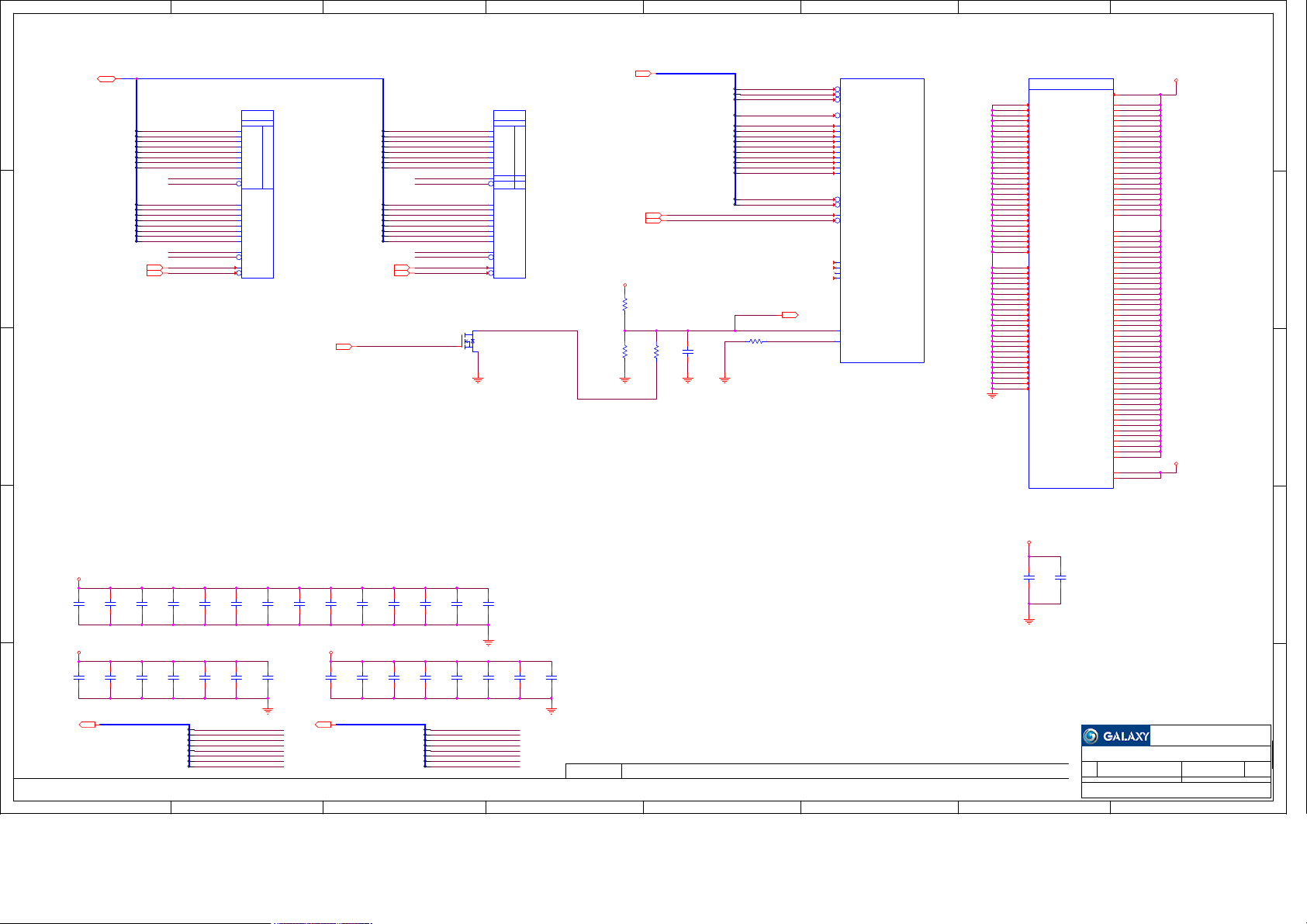

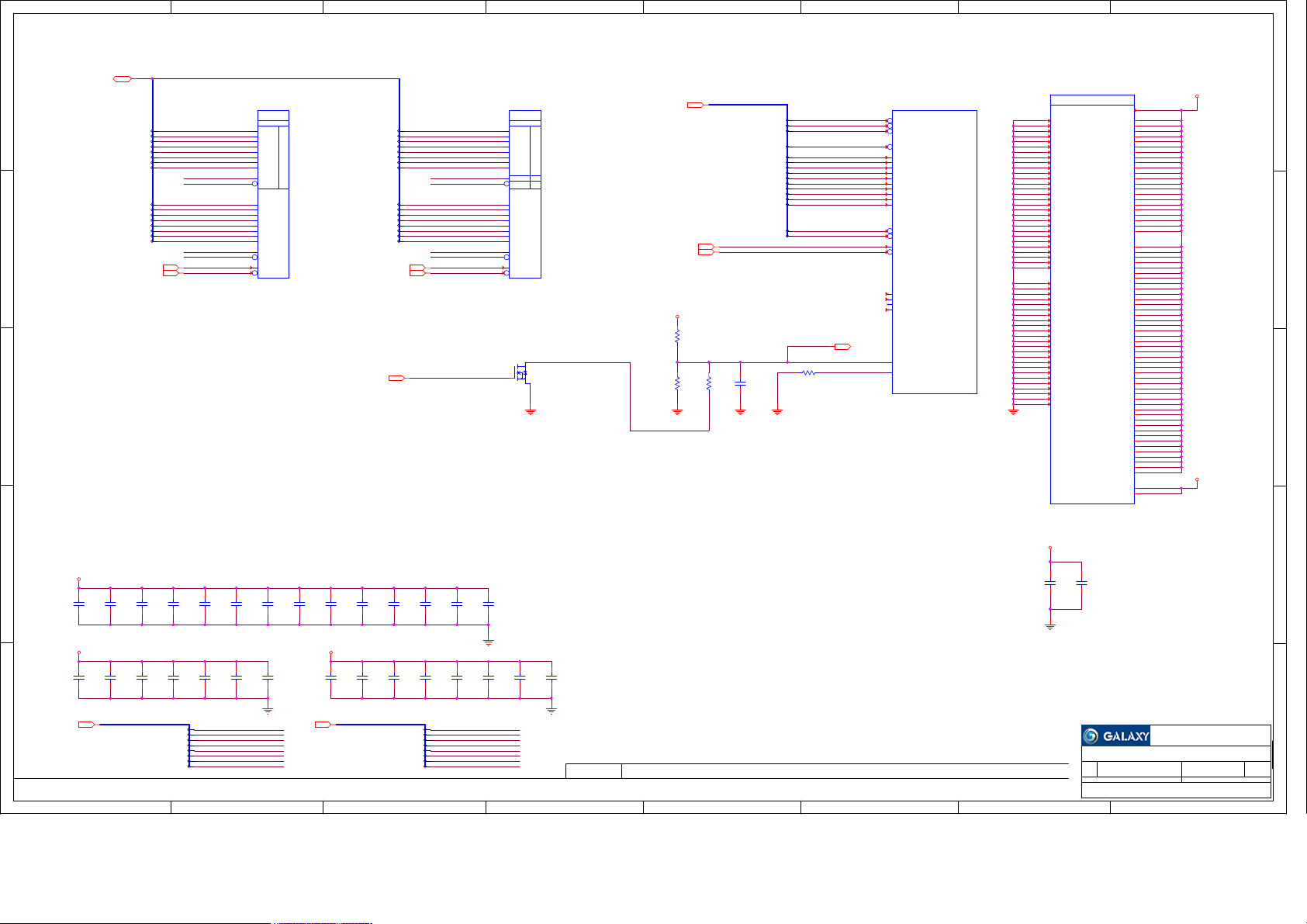

Page 4

A B C D E F G H

Page4: MEMORY: GPU Partition A/B

1

{5,6}

2

3

{5,6}

{5,6}

4

5

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

FB_DATA

FBA_D[63..0]

BI

FB_DBI

FBA_DBI[7..0]

IN

FB_EDC

FBA_EDC[7..0]

OUT

1V8_MAIN

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

Place near GPU

LB1 30ohm

IND_SMD_0603

C83

22uF

6.3V

20%

X6S

0805

GND

G1B

@digital.u_gpu_gb3c_384(sym_2):page4_i626

2/24 FBA

AH43

FBA_D0

AH46

FBA_D1

AH44

FBA_D2

AH45

FBA_D3

AH50

FBA_D4

AH51

FBA_D5

AH53

FBA_D6

AH52

FBA_D7

AK51

FBA_D8

AK53

FBA_D9

AK50

FBA_D10

AK52

FBA_D11

AK47

FBA_D12

AJ47

FBA_D13

AK45

FBA_D14

AJ46

FBA_D15

AP52

FBA_D16

AP53

FBA_D17

AP50

FBA_D18

AP51

FBA_D19

AP46

FBA_D20

AP45

FBA_D21

AP43

FBA_D22

AP44

FBA_D23

AN46

FBA_D24

AN47

FBA_D25

AM45

FBA_D26

AM47

FBA_D27

AM50

FBA_D28

AM52

FBA_D29

AM51

FBA_D30

AM53

FBA_D31

BH52

FBA_D32

BH50

FBA_D33

BH53

FBA_D34

BH51

FBA_D35

BK51

FBA_D36

BK53

FBA_D37

BL52

FBA_D38

BK52

FBA_D39

BF49

FBA_D40

BE47

FBA_D41

BF50

FBA_D42

BE48

FBA_D43

BG51

FBA_D44

BG50

FBA_D45

BG48

FBA_D46

BF51

FBA_D47

AW49

FBA_D48

AW50

FBA_D49

AW47

FBA_D50

AW48

FBA_D51

BA49

FBA_D52

BB49

FBA_D53

BA47

FBA_D54

AY47

FBA_D55

AW43

FBA_D56

BA43

FBA_D57

AW44

FBA_D58

AY44

FBA_D59

BB46

FBA_D60

BB44

FBA_D61

BA44

FBA_D62

BB43

FBA_D63

AH49

FBA_DQM0

AK49

FBA_DQM1

AP47

FBA_DQM2

AM49

FBA_DQM3

BJ51

FBA_DQM4

BG53

FBA_DQM5

BA50

FBA_DQM6

BB47

FBA_DQM7

AH48

FBA_DQS_WP0

AK48

FBA_DQS_WP1

AP49

FBA_DQS_WP2

AM48

FBA_DQS_WP3

BJ50

FBA_DQS_WP4

BF48

FBA_DQS_WP5

AW46

FBA_DQS_WP6

BB48

FBA_DQS_WP7

BGA_2397_P090_P085_P080_P100_450X450

C85

4.7uF

6.3V

20%

X6S

0603

0603

FB_CMD

FBA_CMD0

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_CMD32

FBA_CMD33

FBA_CMD34

FBA_CMD35

FBA_CLK0

FBA_CLK0

FBA_CLK1

FBA_CLK1

FBA_WCK01

FBA_WCK01

FBA_WCKB01

FBA_WCKB01

FBA_WCK23

FBA_WCK23

FBA_WCKB23

FBA_WCKB23

FBA_WCK45

FBA_WCK45

FBA_WCKB45

FBA_WCKB45

FBA_WCK67

FBA_WCK67

FBA_WCKB67

FBA_WCKB67

FBA_PLL_AVDD

FBA_PLL_AVDD

FBA_PLL_AVDD

AT52

AT53

AT51

AU52

AU51

AV52

AV53

AW51

AW52

AY53

AT48

AT50

AT47

AT46

AT45

BF53

BF52

BE51

BD51

BD52

BD53

BC52

BB51

BB53

BB52

BA51

AU48

AU50

AU47

AU46

AU45

AY52

AY51

AT49

AU49

AT43

AT44

AU43

AU44

AK44

AK43

AJ43

AJ44

AM43

AM44

AN43

AN44

BC49

BC50

BC47

BC48

BC46

BD46

BC44

BC45

AL41

AL42

AL43

FBA_CMD1

FBA_CMD2

FBA_CMD3

FBA_CMD4

FBA_CMD5

FBA_CMD6

FBA_CMD7

FBA_CMD8

FBA_CMD9

FBA_CMD10

FBA_CMD11

FBA_CMD12

FBA_CMD13

FBA_CMD14

FBA_CMD15

FBA_CMD16

FBA_CMD17

FBA_CMD18

FBA_CMD19

FBA_CMD20

FBA_CMD21

FBA_CMD22

FBA_CMD23

FBA_CMD24

FBA_CMD25

FBA_CMD26

FBA_CMD27

FBA_CMD28

FBA_CMD29

FBA_CMD30

FBA_CMD31

FBA_DEBUG0

FBA_DEBUG1

FBA_CLK0

FBA_CLK0*

FBA_CLK1

FBA_CLK1*

FBA_WCK01

FBA_WCK01*

FBA_WCK23

FBA_WCK23*

FBA_WCK45

FBA_WCK45*

FBA_WCK67

FBA_WCK67*

0402

GND

C895

0.1uF

16V

10%

X7R

FBA_CMD0

AR53

1V8_FB_PLL_REF

C84

4.7uF

6.3V

20%

X6S

FBA_CMD[31..0]

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

R833

1 %

0402

FBA_CLK0 FB_CLK

FB_CLKFBA_CLK0

FBA_CLK1 FB_CLK

FBA_CLK1 FB_CLK

FBA_WCK01 FB_WCK

FB_WCKFBA_WCK01

FB_WCKFBA_WCK23

FB_WCKFBA_WCK23

FB_WCKFBA_WCK45

FBA_WCK45 FB_WCK

FB_WCKFBA_WCK67

FBA_WCK67 FB_WCK

OUT

FBA_CMD13

FBA_CMD29

FBA_CMD1

FBA_CMD17

60.4ohm/NC

R832

0402

nv_res

0402

nv_res

0402

C E

BI

60.4ohm/NC

1 %

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

{4,9,14,29}

R345

10k

5 %

R348

10k

5 %

ASSEMBLY

PAGE DETAIL

FBVDDQ

FBVDDQ

0402

0402

nv_res

R349

10k

5 %

nv_res

R350

10k

5 %

GND

{5,6}BI{7,8}

GDDR5X CMD Mapping

CMD

CMD0

CMD1

CMD2

CMD3

CMD4

CMD5

CMD6

CMD7

CMD8

CMD9

CMD10

CMD11

CMD12

CMD13

CMD14

CMD15

CMD16

CMD17

CMD18

CMD19

CMD20

CMD21

CMD22

CMD23

CMD24

CMD25

CMD26

CMD27

CMD28

CMD29

CMD30

CMD31

CMD32

CMD33

CMD34

CMD35

{5}

{5}

{6}

{6}

{5}

{5}

{5}

{5}

{6}

{6}

{7,8}

{6}

{6}

{7,8}

<ASSEMBLY_DESCRIPTION>

MEMORY: GPU PARTITION A/B

CAS*

RST*

RAS*

A1_A9

A0_A10

A12_A13

ABI*

A6_A11

A7_A8

A4_BA2

A5_BA1

A3_BA3

A2_BA0

CKE*

A14_A15

WE*

DBG0

DBG1

32..630..31

CAS*

RST*

RAS*

A1_A9

A0_A10

A12_A13

ABI*

A6_A11

A7_A8

A4_BA2

A5_BA1

A3_BA3

A2_BA0

CKE*

A14_A15

WE*

DBG0

DBG1

FBB_CMD13

FBB_CMD29

FBB_CMD1

FBB_CMD17

IN

OUT

FB_DATA

FBB_D[63..0]

FB_DBI

FBB_DBI[7..0]

FB_EDC

FBB_EDC[7..0]

nv_res

0402

nv_res

0402

G1C

@digital.u_gpu_gb3c_384(sym_3):page4_i627

FBB_D0

0

FBB_D1

1

FBB_D2

2

FBB_D3

3

FBB_D4

4

FBB_D5

5

FBB_D6

6

FBB_D7

7

FBB_D8

8

FBB_D9

9

FBB_D10

10

FBB_D11

11

FBB_D12

12

FBB_D13

13

FBB_D14

14

FBB_D15

15

FBB_D16

16

FBB_D17

17

FBB_D18

18

FBB_D19

19

FBB_D20

20

FBB_D21

21

FBB_D22

22

FBB_D23

23

FBB_D24

24

FBB_D25

25

FBB_D26

26

FBB_D27

27

FBB_D28

28

FBB_D29

29

FBB_D30

30

FBB_D31

31

FBB_D32

32

FBB_D33

33

FBB_D34

34

FBB_D35

35

FBB_D36

36

FBB_D37

37

FBB_D38

38

FBB_D39

39

FBB_D40

40

FBB_D41

41

FBB_D42

42

FBB_D43

43

FBB_D44

44

FBB_D45

45

FBB_D46

46

FBB_D47

47

FBB_D48

48

FBB_D49

49

FBB_D50

50

FBB_D51

51

FBB_D52

52

FBB_D53

53

FBB_D54

54

FBB_D55

55

FBB_D56

56

FBB_D57

57

FBB_D58

58

FBB_D59

59

FBB_D60

60

FBB_D61

61

FBB_D62

62

FBB_D63

63

FBB_DBI0

0

FBB_DBI1

1

FBB_DBI2

2

FBB_DBI3

3

FBB_DBI4

4

FBB_DBI5

5

FBB_DBI6

6

FBB_DBI7

7

FBB_EDC0

0

FBB_EDC1

1

FBB_EDC2

2

FBB_EDC3

3

FBB_EDC4

4

FBB_EDC5

5

FBB_EDC6

6

FBB_EDC7

7

FBVDDQ

nv_res

R346

R351

10k

10k

5 %

5 %

0402

nv_res

R347

R352

10k

10k

5 %

5 %

0402

GND

3/24 FBB

F52

FBB_D0

F50

FBB_D1

F53

FBB_D2

F51

FBB_D3

D51

FBB_D4

D53

FBB_D5

C52

FBB_D6

D52

FBB_D7

H49

FBB_D8

J47

FBB_D9

H50

FBB_D10

J48

FBB_D11

G51

FBB_D12

G50

FBB_D13

G48

FBB_D14

H51

FBB_D15

R49

FBB_D16

R50

FBB_D17

R47

FBB_D18

R48

FBB_D19

N49

FBB_D20

M49

FBB_D21

N47

FBB_D22

P47

FBB_D23

R43

FBB_D24

N43

FBB_D25

R44

FBB_D26

P44

FBB_D27

M46

FBB_D28

M44

FBB_D29

N44

FBB_D30

M43

FBB_D31

AF43

FBB_D32

AF46

FBB_D33

AF44

FBB_D34

AF45

FBB_D35

AF50

FBB_D36

AF51

FBB_D37

AF53

FBB_D38

AF52

FBB_D39

AD51

FBB_D40

AD53

FBB_D41

AD50

FBB_D42

AD52

FBB_D43

AD47

FBB_D44

AE47

FBB_D45

AD45

FBB_D46

AE46

FBB_D47

Y52

FBB_D48

Y53

FBB_D49

Y50

FBB_D50

Y51

FBB_D51

Y46

FBB_D52

Y45

FBB_D53

Y43

FBB_D54

Y44

FBB_D55

AA46

FBB_D56

AA47

FBB_D57

AB45

FBB_D58

AB47

FBB_D59

AB50

FBB_D60

AB52

FBB_D61

AB51

FBB_D62

AB53

FBB_D63

E51

FBB_DQM0

G53

FBB_DQM1

N50

FBB_DQM2

M47

FBB_DQM3

AF49

FBB_DQM4

AD49

FBB_DQM5

Y47

FBB_DQM6

AB49

FBB_DQM7

E50

FBB_DQS_WP0

H48

FBB_DQS_WP1

R46

FBB_DQS_WP2

M48

FBB_DQS_WP3

AF48

FBB_DQS_WP4

AD48

FBB_DQS_WP5

Y49

FBB_DQS_WP6

AB48

FBB_DQS_WP7

BGA_2397_P090_P085_P080_P100_450X450

FBB_CMD0

FBB_CMD1

FBB_CMD2

FBB_CMD3

FBB_CMD4

FBB_CMD5

FBB_CMD6

FBB_CMD7

FBB_CMD8

FBB_CMD9

FBB_CMD10

FBB_CMD11

FBB_CMD12

FBB_CMD13

FBB_CMD14

FBB_CMD15

FBB_CMD16

FBB_CMD17

FBB_CMD18

FBB_CMD19

FBB_CMD20

FBB_CMD21

FBB_CMD22

FBB_CMD23

FBB_CMD24

FBB_CMD25

FBB_CMD26

FBB_CMD27

FBB_CMD28

FBB_CMD29

FBB_CMD30

FBB_CMD31

FBB_CMD32

FBB_CMD33

FBB_CMD34

FBB_CMD35

FBB_CLK0

FBB_CLK0

FBB_CLK1

FBB_CLK1

FBB_WCK01

FBB_WCK01

FBB_WCKB01

FBB_WCKB01

FBB_WCK23

FBB_WCK23

FBB_WCKB23

FBB_WCKB23

FBB_WCK45

FBB_WCK45

FBB_WCKB45

FBB_WCKB45

FBB_WCK67

FBB_WCK67

FBB_WCKB67

FBB_WCKB67

FBB_PLL_AVDD

FBB_PLL_AVDD

FBB_PLL_AVDD

FDBA

FBB_CMD0

H53

FBB_CMD1

H52

FBB_CMD2

J51

FBB_CMD3

K51

FBB_CMD4

K52

FBB_CMD5

K53

FBB_CMD6

L52

FBB_CMD7

M51

FBB_CMD8

M53

FBB_CMD9

M52

FBB_CMD10

N51

FBB_CMD11

U48

FBB_CMD12

U50

FBB_CMD13

U47

FBB_CMD14

U46

FBB_CMD15

U45

FBB_CMD16

W53

FBB_CMD17

V52

FBB_CMD18

V53

FBB_CMD19

V51

FBB_CMD20

U52

FBB_CMD21

U51

FBB_CMD22

T52

FBB_CMD23

T53

FBB_CMD24

R51

FBB_CMD25

R52

FBB_CMD26

P53

FBB_CMD27

V48

FBB_CMD28

V50

FBB_CMD29

V47

FBB_CMD30

V46

FBB_CMD31

V45

P51

P52

FBB_DEBUG0

U49

FBB_DEBUG1

V49

FBB_CLK0

U43

FBB_CLK0*

U44

FBB_CLK1

V43

FBB_CLK1*

V44

FBB_WCK01

L49

FBB_WCK01*

L50

L47

L48

FBB_WCK23

K46

FBB_WCK23*

L46

L45

L44

FBB_WCK45

AD44

FBB_WCK45*

AD43

AE43

AE44

FBB_WCK67

AB43

FBB_WCK67*

AB44

AA43

AA44

1V8_FB_PLL_REF

AC41

AC42

AC43

C898

0.1uF

16V

10%

X7R

0402

GND

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

G

FB_CMD

FBB_CMD[31..0]

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

R831 60.4ohm/NC

1 %

0402

FBB_CLK0 FB_CLK

FBB_CLK0 FB_CLK

FBB_CLK1 FB_CLK

FB_CLKFBB_CLK1

FB_WCKFBB_WCK01

FB_WCKFBB_WCK01

FB_WCKFBB_WCK23

FB_WCKFBB_WCK23

FBB_WCK45 FB_WCK

FB_WCKFBB_WCK45

FB_WCKFBB_WCK67

FBB_WCK67 FB_WCK

IN

MEMORY: GPU Partition A/B

MEMORY: GPU Partition A/B

MEMORY: GPU Partition A/B

P25Z

P25Z

P25Z

OUT

FBVDDQ

R830 60.4ohm/NC

1 %

0402

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

{4,9,14,29}

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Design By:

Design By:

Design By:

Neston V10

Neston V10

Neston V10

452Friday, March 03, 2017

452Friday, March 03, 2017

452Friday, March 03, 2017

H

1

{7,8}

2

{7}

{7}

{8}

{8}

3

{7}

{7}

{7}

{7}

{8}

{8}

{8}

{8}

4

5

of

of

of

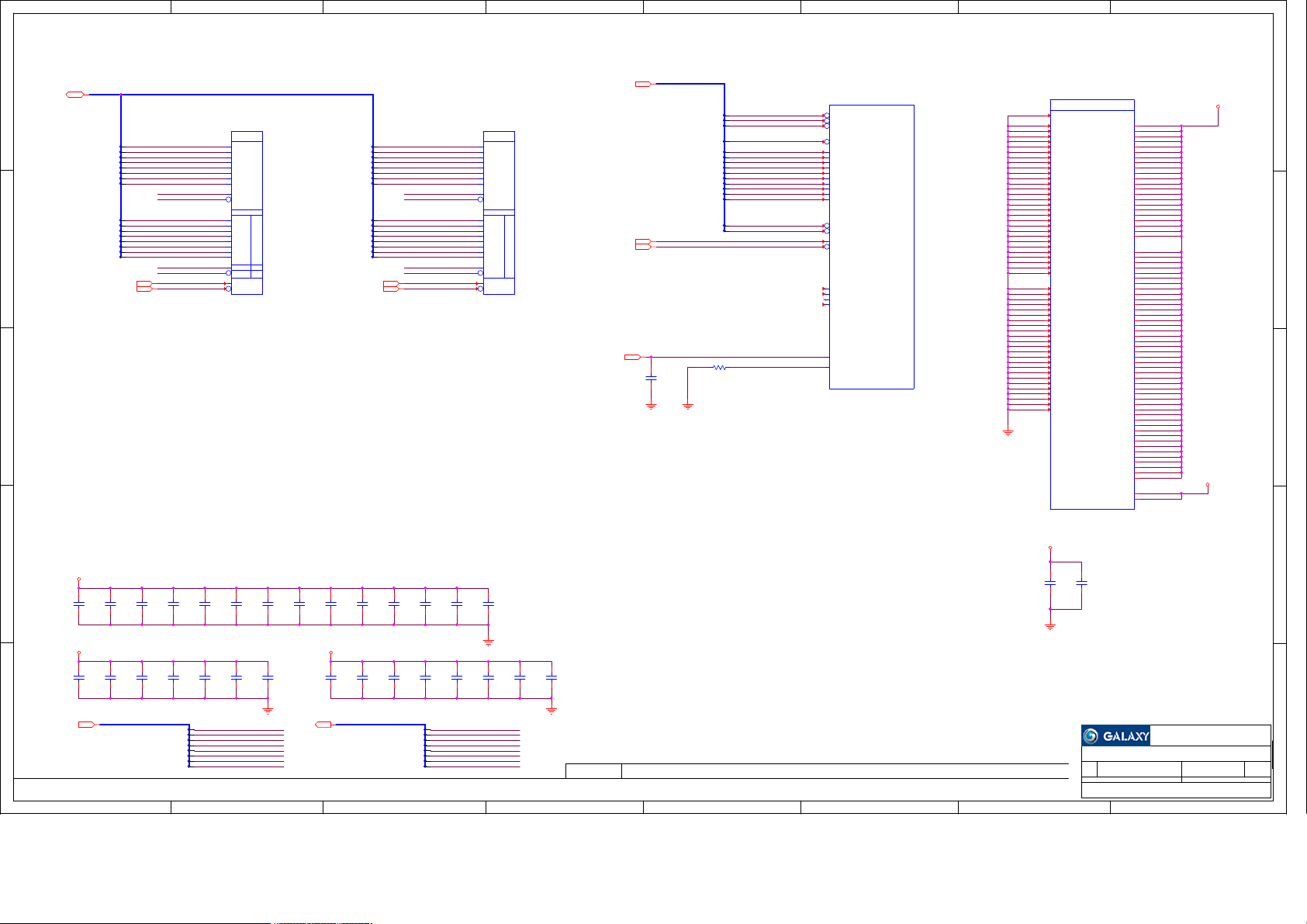

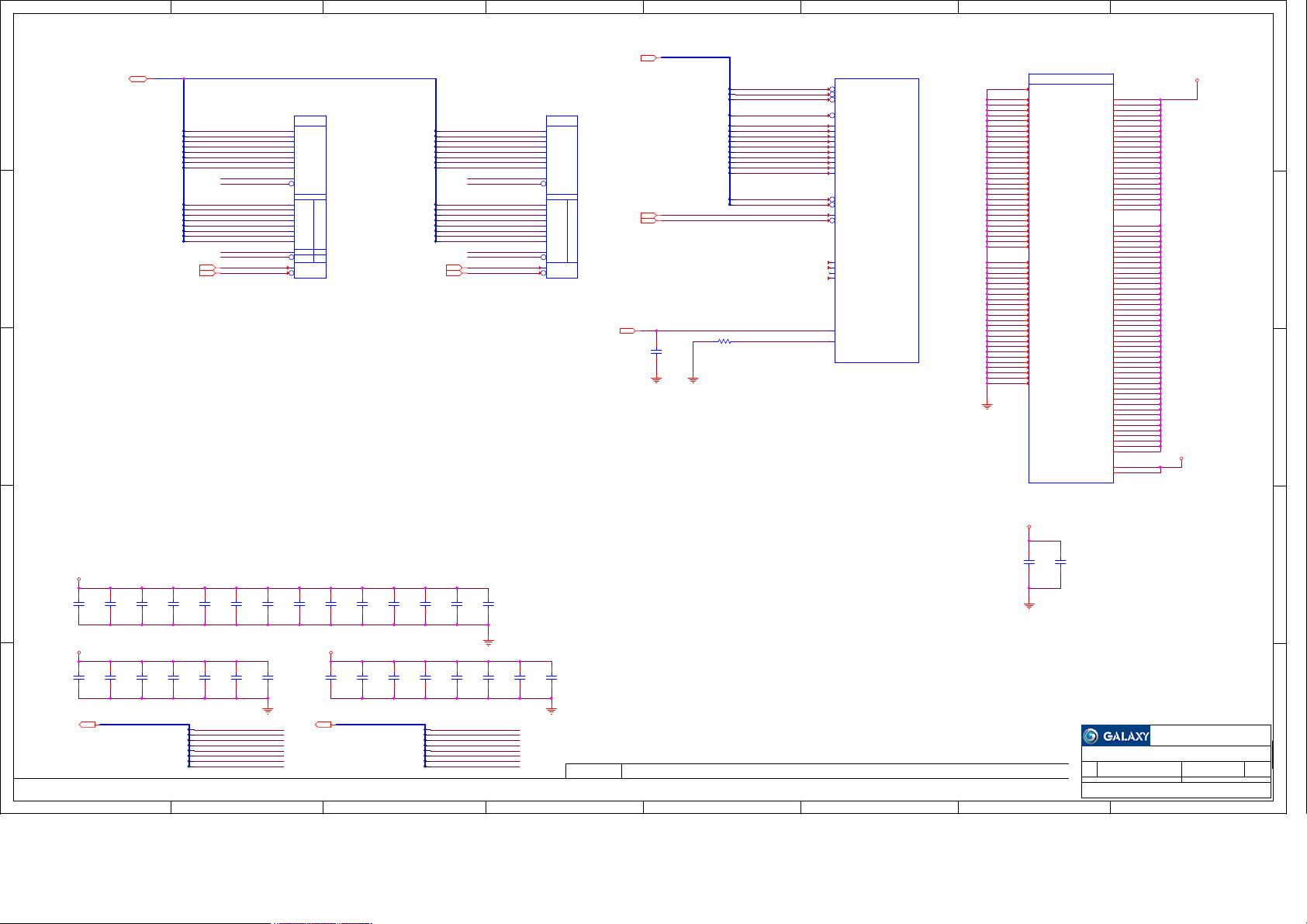

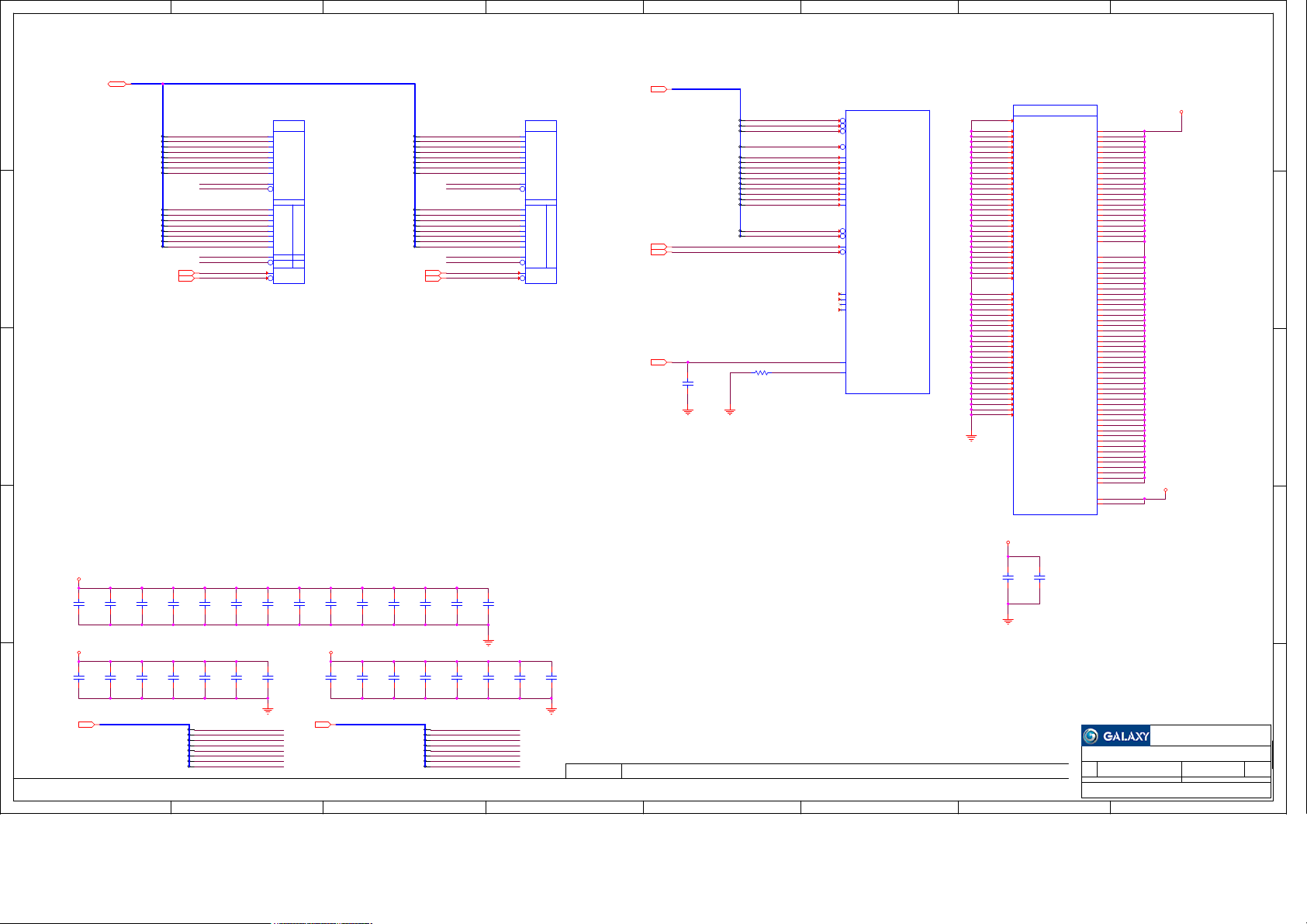

Page 5

A B C D E F G H

Page5: MEMORY: FBA Partition 31..0

GND

M11C

@memory.u_mem_gddr5x_x32(sym_7):page5_i578

Mirrored

A10

VSS

A5

VSS

B1

VSS

B14

VSS

D1

VSS

D11

VSS

D14

VSS

F1

VSS

F14

VSS

H1

VSS

H14

VSS

J12

VSS

J3

VSS

K1

VSS

K14

VSS

K3

VSS

L12

VSS

L3

VSS

M1

VSS

M14

VSS

P1

VSS

P14

VSS

T1

VSS

T11

VSS

T14

VSS

V1

VSS

V14

VSS

W10

VSS

W5

VSS

B13

VSSQ

B2

VSSQ

C10

VSSQ

C5

VSSQ

D13

VSSQ

D2

VSSQ

E10

VSSQ

E5

VSSQ

F13

VSSQ

F2

VSSQ

G10

VSSQ

G5

VSSQ

N10

VSSQ

N5

VSSQ

P13

VSSQ

P2

VSSQ

R10

VSSQ

R5

VSSQ

T13

VSSQ

T2

VSSQ

U10

VSSQ

U5

VSSQ

V13

VSSQ

V2

VSSQ

add 1k to VDD

FBVDDQ

W12

MF

A1

VDD

A11

VDD

A14

VDD

A4

VDD

D10

VDD

G1

VDD

G14

VDD

H10

VDD

H5

VDD

J1

VDD

J14

VDD

L1

VDD

L14

VDD

M10

VDD

M5

VDD

N1

VDD

N14

VDD

T10

VDD

W1

VDD

W11

VDD

W14

VDD

W4

VDD

A13

VDDQ

A2

VDDQ

B10

VDDQ

B5

VDDQ

C1

VDDQ

C13

VDDQ

C14

VDDQ

C2

VDDQ

E1

VDDQ

E11

VDDQ

E13

VDDQ

E14

VDDQ

E2

VDDQ

E4

VDDQ

F10

VDDQ

F5

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

J13

VDDQ

J2

VDDQ

L13

VDDQ

L2

VDDQ

M12

VDDQ

M3

VDDQ

N13

VDDQ

N2

VDDQ

P10

VDDQ

P5

VDDQ

R1

VDDQ

R11

VDDQ

R13

VDDQ

R14

VDDQ

R2

VDDQ

R4

VDDQ

U1

VDDQ

U13

VDDQ

U14

VDDQ

U2

VDDQ

V10

VDDQ

V5

VDDQ

W13

VDDQ

W2

VDDQ

A3

VPP

W3

VPP

1V8_AON

1

2

3

M11B

{4}

1

BI

2

{4}

{4}

3

FBA_D[31..0]

M11D

@memory.u_mem_gddr5x_x32(sym_2):page5_i499

MIRRORED

x32

FBA_D0

0

FBA_D1

1

FBA_D2

2

FBA_D3

3

FBA_D4

4

FBA_D5

5

FBA_D6

6

FBA_D7

7

FBA_EDC0

FBA_DBI0

FBA_D8

8

FBA_D9

9

FBA_D10

10

FBA_D11

11

FBA_D12

12

FBA_D13

13

FBA_D14

14

FBA_D15

15

FBA_EDC1

FBA_DBI1

FBA_WCK01

IN

FBA_WCK01*

IN

x16

V4

DQ0

NC

V3

DQ1

NC

U4

DQ2

NC

U3

DQ3

NC

P4

DQ4

NC

P3

DQ5

NC

N4

DQ6

NC

N3

DQ7

NC

T3

EDC0

NC

R3

DBI0

NC

V11

DQ8

V12

DQ9

U11

DQ10

U12

DQ11

P11

DQ12

P12

DQ13

N11

DQ14

N12

DQ15

T12

EDC1

R12

DBI1

T4

WCK01

T5

WCK01

{4}

{4}

{7,10,12,15,17,27}

FBA_D16

16

FBA_D17

17

FBA_D18

18

FBA_D19

19

FBA_D20

20

FBA_D21

21

FBA_D22

22

FBA_D23

23

FBA_EDC2

FBA_DBI2

FBA_D24

24

FBA_D25

25

FBA_D26

26

FBA_D27

27

FBA_D28

28

FBA_D29

29

FBA_D30

30

FBA_D31

31

FBA_EDC3

FBA_DBI3

FBA_WCK23

IN

FBA_WCK23*

IN

GPIO10_FBVREF_SEL

IN

M11A

@memory.u_mem_gddr5x_x32(sym_4):page5_i544

MIRRORED

x32

x16

B11

DQ16

B12

DQ17

C11

DQ18

C12

DQ19

F11

DQ20

F12

DQ21

G11

DQ22

G12

DQ23

D12

EDC2

GND

E12

DBI2

B4

DQ24

B3

DQ25

C4

DQ26

C3

DQ27

F4

DQ28

F3

DQ29

G4

DQ30

G3

DQ31

D3

EDC3

E3

DBI3

D4

WCK23

D5

WCK23

1G1D1S

NC

NC

NC

NC

NC

NC

NC

NC

NC

D

G

1

S

SOT23

GND

3

Q12

@discrete.q_fet_n_enh(sym_2):page5_i595

2

AO3416L

30V

0.3A

1900mohm@10V / 1900mohm@4.5V / 1900mohm@2.5V

1.2A

0.2W

12V

{4,6}

{4}

{4}

FBA_VREF_Q

0.300

FBVDDQ

R112

549ohm

1 %

R106

1.33k

1 %

GND

FBA_CMD[31..0]

IN

FBA_CLK0

IN

FBA_CLK0*

IN

R113

931ohm

1 %

0.300

C99

820pF

50V

10%

X7R

GND GND

FBA_CMD2

2

FBA_CMD0

0

FBA_CMD15

15

FBA_CMD6

6

FBA_CMD4

4

FBA_CMD3

3

FBA_CMD12

12

FBA_CMD11

11

FBA_CMD9

9

FBA_CMD10

10

FBA_CMD7

7

FBA_CMD8

8

FBA_CMD5

5

FBA_CMD14

14

FBA_CMD1

1

FBA_CMD13

13

OUT

FBA_VREFC

0.140A

R111

FBA_ZQ_1

121ohm

1 %

@memory.u_mem_gddr5x_x32(sym_5):page5_i580

M4

RAS

H4

CAS

H11

WE

K4

ABI

L4

A0_A10

L5

A1_A9

L11

A2_BA0

L10

A3_BA3

J11

A4_BA2

J10

A5_BA1

J5

A6_A11

J4

A7_A8

K5

A12_A13

K12

A15_A14

K2

RESET

M11

CKE

K11

CLK

K10

CLK

M2

TCK

M13

TDI

A12

TDO

H2

TMS

{6}

K13

VREFC

H13

ZQ

4

FBVDDQ

C721

10uF

4V

20%

X6S

FBVDDQ

C712

22uF

4V

20%

X6S

5

{4,6}

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

IN

C791

10uF

4V

20%

X6S

C743

22uF

4V

20%

X6S

FB_DBI

FBA_DBI[7..0]

CLOSE DRAM

C815

10uF

4V

20%

X6S

AROUND DRAM

C822

22uF

4V

20%

X6S

C1281

C823

10uF

4V

20%

X6S

C738

22uF

4V

20%

X6S

0

1

2

3

4

5

6

7

FBA_DBI0

FBA_DBI1

FBA_DBI2

FBA_DBI3

FBA_DBI4

FBA_DBI5

FBA_DBI6

FBA_DBI7

C711

C780

C826

1uF

1uF

6.3V

10%

X6S

C742

22uF

4V

20%

X6S

1uF

6.3V

6.3V

10%

10%

X6S

X6S

C794

C810

10uF

10uF

4V

4V

20%

20%

X6S

X6S

GND

{4,6}

1uF

6.3V

10%

X6S

IN

C804

1uF

6.3V

10%

X6S

FBVDDQ

UNDER DRAM FOR X32

C725

1uF

6.3V

10%

X6S

FB_EDC

FBA_EDC[7..0]

C720

C727

1uF

6.3V

10%

X6S

C779

1uF

6.3V

10%

X6S

C801

C767

C811

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

C774

C760

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

GND

C747

C753

C783

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

C776

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

GND

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

MEMORY: FBA PARTITION[31:0]

1V8_AON

C1469

C285

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

GND

4

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FDBA

G

Galaxy Microsystems (HK) Ltd.

MEMORY: FBA Partition 31..0

MEMORY: FBA Partition 31..0

MEMORY: FBA Partition 31..0

Design By:

Design By:

P25Z

P25Z

P25Z

Design By:

Neston V10

Neston V10

Neston V10

552Friday, March 03, 2017

552Friday, March 03, 2017

552Friday, March 03, 2017

H

of

of

of

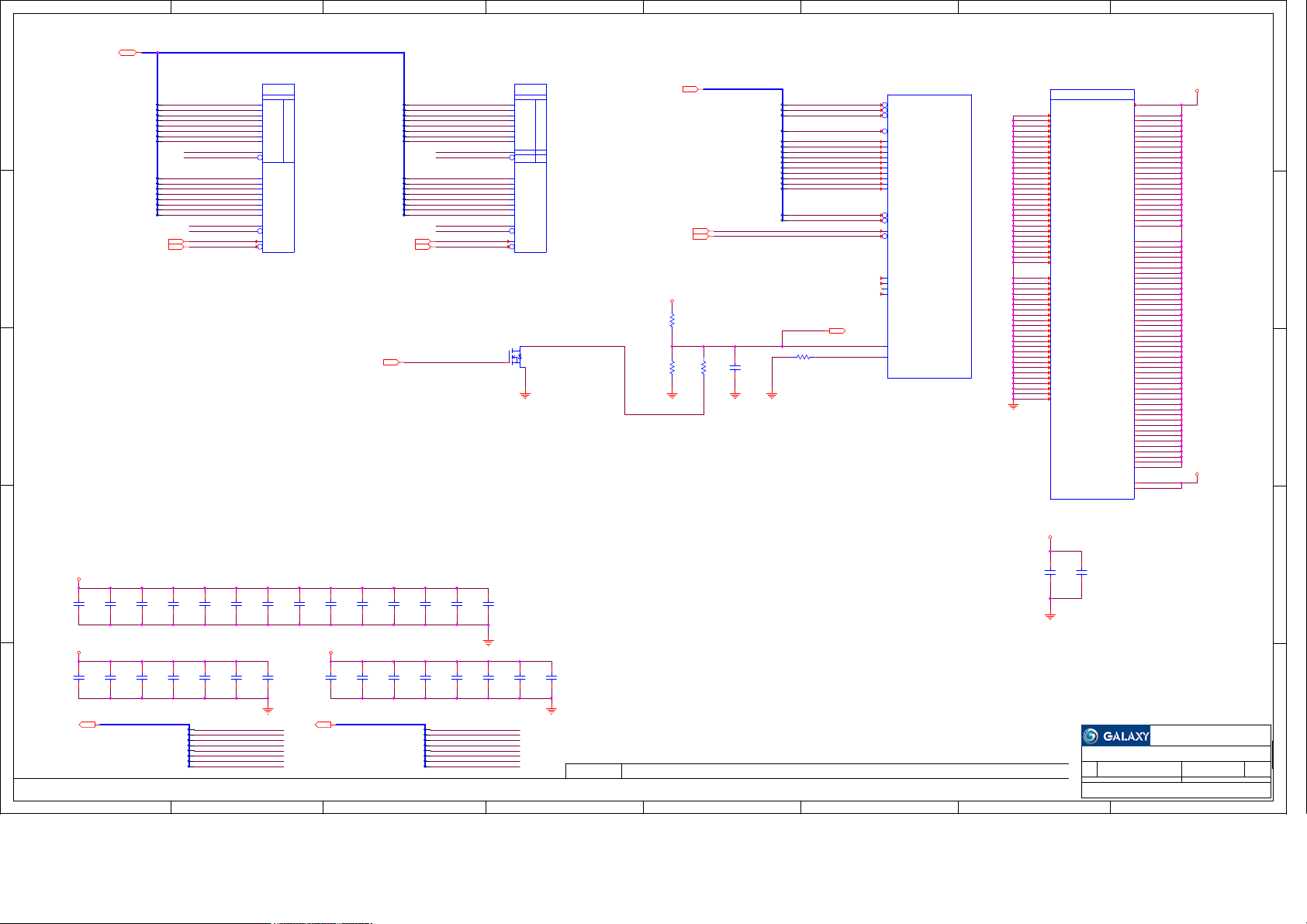

Page 6

A B C D E F G H

Page6: MEMORY: FBA Partition 63..32

1

{4}

2

FBA_D[63..32]

BI

M12D

@memory.u_mem_gddr5x_x32(sym_1):page6_i467

BGA190

COMMON

FBA_D32

32

FBA_D33

33

FBA_D34

34

FBA_D35

35

FBA_D36

36

FBA_D37

37

FBA_D38

38

FBA_D39

39

FBA_EDC4

FBA_DBI4

FBA_D40

40

FBA_D41

41

FBA_D42

42

FBA_D43

43

FBA_D44

44

FBA_D45

45

FBA_D46

46

FBA_D47

47

FBA_EDC5

FBA_DBI5

{4}

{4}

FBA_WCK45

IN

FBA_WCK45*

IN

NORMAL

B4

DQ0

B3

DQ1

C4

DQ2

C3

DQ3

F4

DQ4

F3

DQ5

G4

DQ6

G3

DQ7

D3

EDC0

E3

DBI0

x32

x16

B11

DQ8

NC

B12

DQ9

NC

C11

DQ10

NC

C12

DQ11

NC

F11

DQ12

NC

F12

DQ13

NC

G11

DQ14

NC

G12

DQ15

NC

D12

EDC1

GND

E12

DBI1

NC

D4

WCK01

D5

WCK01

{4}

{4}

FBA_D48

48

FBA_D49

49

FBA_D50

50

FBA_D51

51

FBA_D52

52

FBA_D53

53

FBA_D54

54

FBA_D55

55

FBA_EDC6

FBA_DBI6

FBA_D56

56

FBA_D57

57

FBA_D58

58

FBA_D59

59

FBA_D60

60

FBA_D61

61

FBA_D62

62

FBA_D63

63

FBA_EDC7

FBA_DBI7

FBA_WCK67

IN

FBA_WCK67*

IN

M12A

@memory.u_mem_gddr5x_x32(sym_3):page6_i497

BGA190

COMMON

NORMAL

V11

DQ16

V12

DQ17

U11

DQ18

U12

DQ19

P11

DQ20

P12

DQ21

N11

DQ22

N12

DQ23

T12

EDC2

R12

DBI2

x32

x16

V4

DQ24

NC

V3

DQ25

NC

U4

DQ26

NC

U3

DQ27

NC

P4

DQ28

NC

P3

DQ29

NC

N4

DQ30

NC

N3

DQ31

NC

T3

EDC3

NC

R3

DBI3

NC

T4

WCK23

T5

WCK23

{4,5}

{4}

{4}

{5}

3

IN

IN

IN

IN

FBA_CMD[31..0]

FBA_CLK1

FBA_CLK1*

C101

820pF

50V

10%

X7R

0402

COMMON

GND GND

FBA_VREFC

GND

M12C

@memory.u_mem_gddr5x_x32(sym_6):page6_i522

BGA190

COMMON

Normal

W12

MF

add 1k to VSS

A10

VSS

A5

VSS

B1

VSS

B14

VSS

D1

VSS

D11

VSS

D14

VSS

F1

VSS

F14

VSS

H1

VSS

H14

VSS

J12

VSS

J3

VSS

K1

VSS

K14

VSS

K3

VSS

L12

VSS

L3

VSS

M1

VSS

M14

VSS

P1

VSS

P14

VSS

T1

VSS

T11

VSS

T14

VSS

V1

VSS

V14

VSS

W10

VSS

W5

VSS

B13

VSSQ

B2

VSSQ

C10

VSSQ

C5

VSSQ

D13

VSSQ

D2

VSSQ

E10

VSSQ

E5

VSSQ

F13

VSSQ

F2

VSSQ

G10

VSSQ

G5

VSSQ

N10

VSSQ

N5

VSSQ

P13

VSSQ

P2

VSSQ

R10

VSSQ

R5

VSSQ

T13

VSSQ

T2

VSSQ

U10

VSSQ

U5

VSSQ

V13

VSSQ

V2

VSSQ

FBVDDQ

A1

VDD

A11

VDD

A14

VDD

A4

VDD

D10

VDD

G1

VDD

G14

VDD

H10

VDD

H5

VDD

J1

VDD

J14

VDD

L1

VDD

L14

VDD

M10

VDD

M5

VDD

N1

VDD

N14

VDD

T10

VDD

W1

VDD

W11

VDD

W14

VDD

W4

VDD

A13

VDDQ

A2

VDDQ

B10

VDDQ

B5

VDDQ

C1

VDDQ

C13

VDDQ

C14

VDDQ

C2

VDDQ

E1

VDDQ

E11

VDDQ

E13

VDDQ

E14

VDDQ

E2

VDDQ

E4

VDDQ

F10

VDDQ

F5

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

J13

VDDQ

J2

VDDQ

L13

VDDQ

L2

VDDQ

M12

VDDQ

M3

VDDQ

N13

VDDQ

N2

VDDQ

P10

VDDQ

P5

VDDQ

R1

VDDQ

R11

VDDQ

R13

VDDQ

R14

VDDQ

R2

VDDQ

R4

VDDQ

U1

VDDQ

U13

VDDQ

U14

VDDQ

U2

VDDQ

V10

VDDQ

V5

VDDQ

W13

VDDQ

W2

VDDQ

A3

VPP

W3

VPP

1V8_AON

M12B

@memory.u_mem_gddr5x_x32(sym_5):page6_i509

BGA190

FBA_CMD18

18

FBA_CMD16

16

FBA_CMD31

31

FBA_CMD22

22

FBA_CMD20

20

FBA_CMD19

19

FBA_CMD28

28

FBA_CMD27

27

FBA_CMD25

25

FBA_CMD26

26

FBA_CMD23

23

FBA_CMD24

24

FBA_CMD21

21

FBA_CMD30

30

FBA_CMD17

17

FBA_CMD29

29

R107

0402

FBA_ZQ_2

121ohm

COMMON

1 %

COMMON

H4

RAS

M4

CAS

M11

WE

K4

ABI

J4

A0_A10

J5

A1_A9

J11

A2_BA0

J10

A3_BA3

L11

A4_BA2

L10

A5_BA1

L5

A6_A11

L4

A7_A8

K5

A12_A13

K12

A15_A14

K2

RESET

H11

CKE

K11

CLK

K10

CLK

M2

TCK

M13

TDI

A12

TDO

H2

TMS

K13

VREFC

H13

ZQ

1

2

3

4

FBVDDQ

C805

10uF

4V

20%

X6S

0603

COMMON

FBVDDQ

C741

22uF

4V

20%

X6S

0603W

COMMON

5

{4,5}

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

IN

C705

10uF

4V

20%

X6S

0603

COMMON

C824

22uF

4V

20%

X6S

0603W

COMMON

FB_DBI

FBA_DBI[7..0]

CLOSE DRAM

C799

10uF

4V

20%

X6S

0603

COMMON

AROUND DRAM

C702

22uF

4V

20%

X6S

0603W

COMMON

C788

10uF

4V

20%

X6S

0603

COMMON

C809

22uF

4V

20%

X6S

0603W

COMMON

C787

C723

C768

C817

C773

1uF

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

C785

C828

22uF

10uF

4V

4V

20%

20%

X6S

X6S

0603

0603W

COMMON

COMMON

{4,5}

FBA_DBI0

0

FBA_DBI1

1

FBA_DBI2

2

FBA_DBI3

3

FBA_DBI4

4

FBA_DBI5

5

FBA_DBI6

6

FBA_DBI7

7

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

C709

10uF

4V

20%

X6S

0603

COMMON

GND

IN

1uF

6.3V

10%

X6S

0402

COMMON

FBVDDQ

UNDER DRAM FOR X32

C758

1uF

6.3V

10%

X6S

0402

COMMON

FB_EDC

FBA_EDC[7..0]

C734

1uF

6.3V

10%

X6S

0402

COMMON

C706

1uF

6.3V

10%

X6S

0402

COMMON

C759

1uF

6.3V

10%

X6S

0402

COMMON

C772

1uF

6.3V

10%

X6S

0402

COMMON

C728

C713

1uF

6.3V

10%

X6S

0402

COMMON

C770

1uF

6.3V

10%

X6S

0402

COMMON

C769

1uF

6.3V

10%

X6S

0402

COMMON

GND

C766

1uF

6.3V

10%

X6S

0402

COMMON

C754

1uF

6.3V

10%

X6S

0402

COMMON

GND

C752

1uF

6.3V

10%

X6S

0402

COMMON

1uF

6.3V

10%

X6S

0402

COMMON

C737

1uF

6.3V

10%

X6S

0402

COMMON

FBA_EDC0

0

FBA_EDC1

1

FBA_EDC2

2

FBA_EDC3

3

FBA_EDC4

4

FBA_EDC5

5

FBA_EDC6

6

FBA_EDC7

7

C E

ASSEMBLY

PAGE DETAIL

<ASSEMBLY_DESCRIPTION>

MEMORY: FBA PARTITION[63:32]

1V8_AON

C1470

C268

1uF

1uF

6.3V

6.3V

10%

10%

X6S

X6S

0402

0402

COMMON

COMMON

GND

4

5

Galaxy Microsystems (HK) Ltd.

Galaxy Microsystems (HK) Ltd.

Page Name:

Page Name:

Page Name:

Size Project Name: Rev

Size Project Name: Rev

Size Project Name: Rev

Custom

Custom

Custom

Date: Sheet

Date: Sheet

Date: Sheet

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

PROPERTY NOTE: This document contains information confidential and

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

property to Galaxy Microsystems (HK) Ltd.

FDBA

G

Galaxy Microsystems (HK) Ltd.

MEMORY: FBA Partition 63..32

MEMORY: FBA Partition 63..32

MEMORY: FBA Partition 63..32

P25Z

P25Z

P25Z

Design By:

Design By:

Design By:

H

Neston V10

Neston V10

Neston V10

of

of

of

652Friday, March 03, 2017

652Friday, March 03, 2017

652Friday, March 03, 2017

Page 7

A B C D E F G H

Page7: MEMORY: FBB Partition 31..0

{4}

1

BI

2

{4}

{4}

3

FBB_D[31..0]

FBB_D0

0

FBB_D1

1

FBB_D2

2

FBB_D3

3

FBB_D4

4

FBB_D5

5

FBB_D6

6

FBB_D7

7

FBB_EDC0

FBB_DBI0

FBB_D8

8

FBB_D9

9

FBB_D10

10

FBB_D11

11

FBB_D12

12

FBB_D13

13

FBB_D14

14

FBB_D15

15

FBB_EDC1

FBB_DBI1

FBB_WCK01

IN

FBB_WCK01*

IN

M9D

@memory.u_mem_gddr5x_x32(sym_2):page7_i510

BGA190_MIRR

COMMON

MIRRORED

x32

x16

V4

DQ0

V3

DQ1

U4

DQ2

U3

DQ3

P4

DQ4

P3

DQ5

N4

DQ6

N3

DQ7

T3

EDC0

R3

DBI0

V11

DQ8

V12

DQ9

U11

DQ10

U12

DQ11

P11

DQ12

P12

DQ13

N11

DQ14

N12

DQ15

T12

EDC1

R12

DBI1

T4

WCK01

T5

WCK01

M9C

GND

@memory.u_mem_gddr5x_x32(sym_7):page7_i573

BGA190_MIRR

COMMON

Mirrored

A10

VSS

A5

VSS

B1

VSS

B14

VSS

D1

VSS

D11

VSS

D14

VSS

F1

VSS

F14

VSS

H1

VSS

H14

VSS

J12

VSS

J3

VSS

K1

VSS

K14

VSS

K3

VSS

L12

VSS

L3

VSS

M1

VSS

M14

VSS

P1

VSS

P14

VSS

T1

VSS

T11

VSS

T14

VSS

V1

VSS

V14

VSS

W10

VSS

W5

VSS

B13

VSSQ

B2

VSSQ

C10

VSSQ

C5

VSSQ

D13

VSSQ

D2

VSSQ

E10

VSSQ

E5

VSSQ

F13

VSSQ

F2

VSSQ

G10

VSSQ

G5

VSSQ

N10

VSSQ

N5

VSSQ

P13

VSSQ

P2

VSSQ

R10

VSSQ

R5

VSSQ

T13

VSSQ

T2

VSSQ

U10

VSSQ

U5

VSSQ

V13

VSSQ

V2

VSSQ

add 1k to VDD

FBVDDQ

W12

MF

A1

VDD

A11

VDD

A14

VDD

A4

VDD

D10

VDD

G1

VDD

G14

VDD

H10

VDD

H5

VDD

J1

VDD

J14

VDD

L1

VDD

L14

VDD

M10

VDD

M5

VDD

N1

VDD

N14

VDD

T10

VDD

W1

VDD

W11

VDD

W14

VDD

W4

VDD

A13

VDDQ

A2

VDDQ

B10

VDDQ

B5

VDDQ

C1

VDDQ

C13

VDDQ

C14

VDDQ

C2

VDDQ

E1

VDDQ

E11

VDDQ

E13

VDDQ

E14

VDDQ

E2

VDDQ

E4

VDDQ

F10

VDDQ

F5

VDDQ

G13

VDDQ

G2

VDDQ

H12

VDDQ

H3

VDDQ

J13

VDDQ

J2

VDDQ

L13

VDDQ

L2

VDDQ

M12

VDDQ

M3

VDDQ

N13

VDDQ

N2

VDDQ

P10

VDDQ

P5

VDDQ

R1

VDDQ

R11

VDDQ

R13

VDDQ

R14

VDDQ

R2

VDDQ

R4

VDDQ

U1

VDDQ

U13

VDDQ

U14

VDDQ

U2

VDDQ

V10

VDDQ

V5

VDDQ

W13

VDDQ

W2

VDDQ

A3

VPP

W3

VPP

1V8_AON

1

2

3

M9B

M9A

{4,8}

@memory.u_mem_gddr5x_x32(sym_4):page7_i544

BGA190_MIRR

COMMON

MIRRORED

x32

B11

B12

C11

C12

F11

F12

G11

G12

D12

E12

B4

B3

C4

C3

F4

F3

G4

G3

D3

E3

D4

D5

1G1D1S

x16

DQ16

NC

DQ17

NC

DQ18

NC

DQ19

NC

DQ20

NC

DQ21

NC

DQ22

NC

DQ23

NC

EDC2

GND

DBI2

NC

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

EDC3

DBI3

WCK23

WCK23

D

Q11

@discrete.q_fet_n_enh(sym_2):page7_i588

SOT323_1G1D1S

G

1

COMMON

S

30V

0.3A

1900mohm@10V / 1900mohm@4.5V / 1900mohm@2.5V

1.2A

0.2W

12V

SOT23

GND

{4}

{4}

FBVDDQ

R109

549ohm

1 %

0402

COMMON

3

R104

2

AO3416L

FBB_VREF_Q

0.300

1.33k

1 %

0402

COMMON

GND

IN

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

FBB_D16

FBB_D17

FBB_D18

FBB_D19

FBB_D20

FBB_D21

FBB_D22

FBB_D23

FBB_D24

FBB_D25

FBB_D26

FBB_D27

FBB_D28

FBB_D29

FBB_D30

FBB_D31

IN

IN

GPIO10_FBVREF_SEL

FBB_EDC2

FBB_DBI2

FBB_EDC3

FBB_DBI3

FBB_WCK23

FBB_WCK23*

NC

NC

NC

NC

NC

NC

NC

NC

NC

NC

{4}

{4}

{5,10,12,15,17,27}

FBB_CMD[31..0]

IN

FBB_CLK0

IN

FBB_CLK0*

IN

R110

931ohm

1 %

0402

COMMON

0.300

C98

820pF

50V

10%

X7R

0402

COMMON

GND GND

FBB_CMD2

2

FBB_CMD0

0

FBB_CMD15

15

FBB_CMD6

6

FBB_CMD4

4

FBB_CMD3

3

FBB_CMD12

12

FBB_CMD11

11

FBB_CMD9

9

FBB_CMD10

10

FBB_CMD7

7

FBB_CMD8

8

FBB_CMD5

5

FBB_CMD14

14

FBB_CMD1

1

FBB_CMD13

13

OUT

FBB_VREFC

0.140A

FBB_ZQ_1

R108

121ohm

0402

COMMON

1 %

@memory.u_mem_gddr5x_x32(sym_5):page7_i554

BGA190_MIRR

COMMON

M4

RAS

H4

CAS

H11

WE

K4

ABI

L4

A0_A10

L5

A1_A9

L11

A2_BA0

L10

A3_BA3

J11

A4_BA2

J10

A5_BA1

J5

A6_A11

J4

A7_A8

K5

A12_A13

K12

A15_A14

K2

RESET

M11

CKE

K11

CLK

K10

CLK

M2

TCK

M13

TDI

A12

TDO

H2

TMS

{8}

K13

VREFC

H13

ZQ

4

FBVDDQ

C813

10uF

4V

20%

X6S

0603

COMMON

FBVDDQ

C724

22uF

4V

20%

X6S

0603W

COMMON

5

{4,8}

ALL NVIDIA DESIGN SPECIFICATIONS, REFERENCE SPECIFICATIONS, REFERENCE BOARDS, FILES, DRAWINGS, DIAGNOSTICS, LISTS AND OTHER DOCUMENTS OR INFORMATION (TOGETHER AND SEPARATELY, 'MATERIALS') ARE BEING PROVIDED 'AS IS'. THE MATERIALS MAY

CONTAIN KNOWN AND UNKNOWN VIOLATIONS OR DEVIATIONS OF INDUSTRY STANDARDS AND SPECIFICATIONS. NVIDIA MAKES NO WARRANTIES, EXPRESSED, IMPLIED, STATUTORY OR OTHERWISE WITH RESPECT TO THE MATERIALS OR OTHERWISE, AND EXPRESSLY DISCLAIMS ALL

IMPLIED WARRANTIES INCLUDING, WITHOUT LIMITATION, THE WARRANTIES OF DESIGN, OF NONINFRINGEMENT, MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE, OR ARISING FROM A COURSE OF DEALING, TRADE USAGE, TRADE PRACTICE, OR INDUSTRY STANDARDS.

IN

C751

10uF

4V

20%

X6S

0603

COMMON

C793

22uF

4V

20%

X6S

0603W

COMMON

FB_DBI

FBB_DBI[7..0]

CLOSE DRAM

C722

10uF

4V

20%

X6S

0603

COMMON

C786

22uF

4V

20%

X6S

0603W

COMMON

C790

10uF

4V

20%

X6S

0603

COMMON

C755

22uF

4V

20%

X6S

0603W

COMMON

C803

C829

C744

C718

1uF

1uF

6.3V

10%

X6S

0402

COMMON

C703

22uF

4V

20%

X6S

0603W

COMMON

FBB_DBI0

0

FBB_DBI1

1

FBB_DBI2

2

FBB_DBI3

3

FBB_DBI4

4

FBB_DBI5

5

FBB_DBI6

6

FBB_DBI7

7

6.3V

10%

X6S

0402

COMMON

C730

10uF

4V

20%

X6S

0603

COMMON

1uF

6.3V

10%

X6S

0402

COMMON

C820

10uF

4V

20%

X6S

0603

COMMON

GND

{4,8}

1uF

6.3V

10%

X6S

0402

COMMON

C731

1uF

6.3V

10%

X6S

0402

COMMON

FBVDDQ

UNDER DRAM FOR X32AROUND DRAM

C827

1uF

6.3V

10%

X6S

0402

COMMON

FB_EDC

FBB_EDC[7..0]

OUT

C771

1uF

6.3V

10%

X6S

0402

COMMON

C756

1uF

6.3V

10%

X6S

0402

COMMON

C814

1uF

6.3V

10%

X6S

0402

COMMON

C806

1uF

6.3V

10%

X6S

0402

COMMON

C765

C802

1uF

6.3V

10%

X6S

0402

COMMON

C761

1uF

6.3V

10%

X6S

0402

COMMON

C715

1uF

6.3V

10%

X6S

0402

COMMON

GND

C781

C757

1uF

6.3V

10%

X6S

0402

COMMON

C762

1uF

6.3V

10%

X6S

0402

COMMON

GND

1uF

6.3V

10%

X6S